# AN4253 Application note

# SPC564Lx device startup flow

#### Introduction

This document describes the startup process of the SPC564Lx between the reset to the first instructions of the application startup code.

It describes all the necessary steps involved to successfully achieve application startup. It also describes possible modifications in the low level startup blocks that may be changed, replaced or edited depending on the system needs.

This document is intended as a guideline for software developers responsible for low level startup code and building blocks.

September 2013 DocID024255 Rev 2 1/44

Contents AN4253

# **Contents**

| 1 | Start | up flow diagram                                             | . 7 |

|---|-------|-------------------------------------------------------------|-----|

| 2 | Afte  | reset init                                                  | . 8 |

|   | 2.1   | Core Register Init (LSM)                                    | . 8 |

|   |       | 2.1.1 Code sequence                                         | . 8 |

|   | 2.2   | Memory Management Unit (MMU)                                | . 8 |

|   |       | 2.2.1 Default reset configuration                           | . 9 |

|   |       | 2.2.2 Code sequence                                         | . 9 |

| 3 | SSC   | /I HW configuration check                                   | 10  |

|   | 3.1   | Code sequence                                               | 10  |

|   | 3.2   | SSCM fault handler                                          | 10  |

| 4 | FCC   | J block                                                     | 11  |

|   | 4.1   | FCCU status check                                           | 12  |

|   |       | 4.1.1 Code sequence                                         | 12  |

|   | 4.2   | Read critical and non-critical faults in FCCU (FCCU.CF/NCF) | 12  |

|   |       | 4.2.1 Code sequence                                         | 13  |

|   | 4.3   | Analyze FCCU faults                                         | 13  |

|   | 4.4   | STCU fault analysis                                         | 13  |

|   |       | 4.4.1 Code sequence                                         | 13  |

|   | 4.5   | Save FCCU faults                                            | 13  |

|   | 4.6   | Reset FCCU faults                                           | 14  |

|   |       | 4.6.1 Code sequence                                         | 14  |

|   | 4.7   | FCCU fault handler                                          | 14  |

| 5 | RGM   | block                                                       | 15  |

|   | 5.1   | Read RGM status (both destructive and functional resets)    | 15  |

|   |       | 5.1.1 Code sequence                                         | 16  |

|   | 5.2   | POR/destructive/external reset check                        | 16  |

|   |       | 5.2.1 Code sequence                                         | 16  |

|   | 5.3   | Expected functional reset                                   | 16  |

|   | 5.4   | User specific code for given expected reset                 | 16  |

|   |       |                                                             |     |

|   | 5.5  | Save reset flags                         |

|---|------|------------------------------------------|

|   | 5.6  | Clear reset flags                        |

|   |      | 5.6.1 Code sequence                      |

|   | 5.7  | RGM fault handler                        |

| 6 | Safe | mode block                               |

|   | 6.1  | Read current mode of the microcontroller |

|   |      | 6.1.1 Code sequence                      |

|   | 6.2  | Safe mode check                          |

|   |      | 6.2.1 Code sequence                      |

|   | 6.3  | Mode change to DRUN request              |

|   |      | 6.3.1 Code sequence                      |

|   | 6.4  | DRUN mode check                          |

|   |      | 6.4.1 Code sequence                      |

|   | 6.5  | ME fault handler                         |

| 7 | HW r | esource initialization21                 |

|   | 7.1  | AIPS protection                          |

|   |      | 7.1.1 Default reset configuration        |

|   | 7.2  | PFlash controller setup                  |

|   |      | 7.2.1 Default reset configuration        |

|   |      | 7.2.2 Code sequence                      |

|   | 7.3  | Core registers initialization            |

|   |      | 7.3.1 Code sequence                      |

|   | 7.4  | Cache memory initialization              |

|   |      | 7.4.1 Default reset configuration        |

|   |      | 7.4.2 Code sequence                      |

|   | 7.5  | Branch prediction                        |

|   |      | 7.5.1 Default reset configuration        |

|   |      | 7.5.2 Code sequence                      |

|   | 7.6  | Clock system initialization              |

|   |      | 7.6.1 Default reset configuration        |

|   | 7.7  | CLK fault handler 28                     |

|   | 7.8  | Software Watchdog Timer (SWT) disable    |

|   |      | 7.8.1 Default reset value                |

|   |      |                                          |

|          |        | 7.8.2 Code sequence                   |

|----------|--------|---------------------------------------|

| 8        | RAM    | initialization                        |

|          | 8.1    | Init whole RAM 30                     |

|          |        | 8.1.1 Code sequence                   |

| 9        | Appli  | cation 'asm' startup                  |

| 10       | Appli  | cation 'C' startup                    |

| Appendix | A as   | sm examples 33                        |

|          | A.1    | Symbol defines                        |

|          | A.2    | Core register init (LSM)              |

|          | A.3    | MMU entry configuration               |

|          | A.4    | SSCM HW configuration check           |

|          | A.5    | FCCU handling block                   |

|          | A.6    | RGM block                             |

|          | A.7    | Safe mode block                       |

|          | A.8    | AIPS protection                       |

|          | A.9    | Cache memory initialization           |

|          | A.10   | Branch prediction                     |

|          | A.11   | Clock system initialization           |

|          | A.12   | Software Watchdog Timer (SWT) disable |

|          | A.13   | Init whole RAM                        |

| Appendix | B Fu   | urther information                    |

|          | B.1    | Reference documents                   |

|          | B.2    | Acronyms                              |

| Revision | histor | y43                                   |

AN4253 List of tables

# List of tables

| Table 1. | Acronyms                  | 42 |

|----------|---------------------------|----|

| Table 2. | Document revision history | 43 |

List of figures AN4253

# **List of figures**

| Figure 1.  | General startup flow                                              | 7  |

|------------|-------------------------------------------------------------------|----|

| Figure 2.  | Flow of the "After reset init" phase                              | 8  |

| Figure 3.  | MMU reset configuration                                           | 9  |

| Figure 4.  | Flow of the "SSCM HW configuration check" phase                   | 10 |

| Figure 5.  | Flow of the "FCCU check block" phase                              | 11 |

| Figure 6.  | FCCU block diagram                                                | 11 |

| Figure 7.  | Flow of the "Reset analysis" phase                                | 15 |

| Figure 8.  | Flow of the "Safe mode handling" phase                            | 18 |

| Figure 9.  | Flow of the "Initialization of backbone hardware resources" phase | 21 |

| Figure 10. | AIPS block scheme                                                 | 21 |

| Figure 11. | PFlash controller                                                 | 22 |

| Figure 12. | Clock subsystem                                                   | 24 |

| Figure 13. | Peripheral clock gating scheme                                    | 27 |

| Figure 14  | Flow of the "RAM initialization" phase                            | 30 |

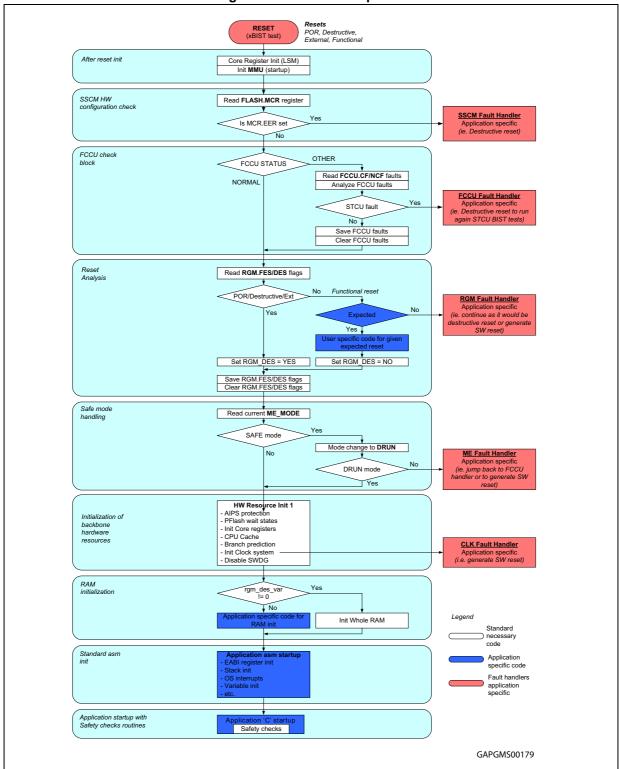

# 1 Startup flow diagram

Figure 1. General startup flow

After reset init AN4253

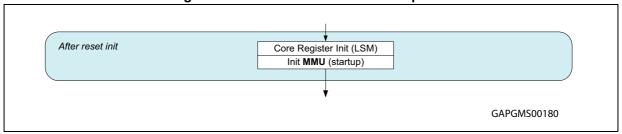

# 2 After reset init

Figure 2. Flow of the "After reset init" phase

# 2.1 Core Register Init (LSM)

In Lock Step (LSM) Mode it is mandatory to initialize the core specific purpose register to avoid redundant checker faults under specific circumstances. The reason for the faults comes from the fact that not all core specific purpose registers are initialized after reset and their difference can cause RCCU fault later on.

It is not necessary to initialize the core SPRs registers when the device is operating in decoupled mode.

#### 2.1.1 Code sequence

1. Write to selected Core Specific Purpose Registers (SPRs) any value

# 2.2 Memory Management Unit (MMU)

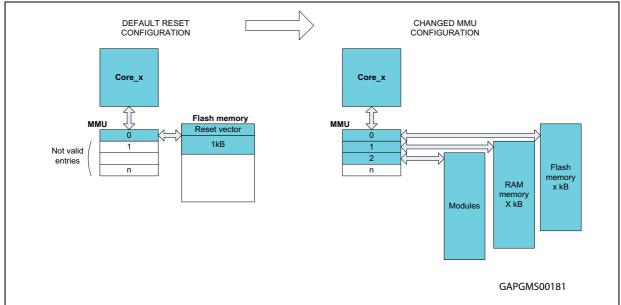

Default reset MMU configuration in each core enables instruction fetch from 4 KB memory block area starting from a reset vector address. 4 KB code area may or may not be sufficient for the startup code, but a main issue of the default MMU configuration is missing access setup for RAM memory and for peripheral modules. They must be explicitly added to the MMU table before any access is executed to them by the startup code.

AN4253 After reset init

Figure 3. MMU reset configuration

#### 2.2.1 Default reset configuration

4 KB code Flash area starting at reset vector

#### 2.2.2 Code sequence

Memory management unit is a part of the core with its dedicated register interface (MASx) to access an internal MMU configuration.

#### Read operation sequence

- 1. Prepare MMU item number in MASO register (mtspr instruction)

- 2. Execute tlbre instruction

- Content of table entry is read to MASO-3 register (mfspr instruction)

#### Write operation sequence

- 1. Prepare configuration in MASO-3 registers (mtspr instruction)

- 2. Execute tlbwe instruction

- 3. Content of MASO-3 registers is written to MMU entry  $\,$

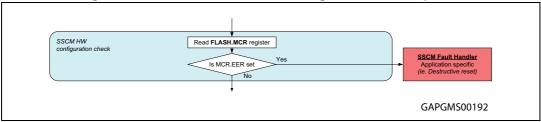

# 3 SSCM HW configuration check

Figure 4. Flow of the "SSCM HW configuration check" phase

Before the microcontroller exits the Reset phase several operations are executed. One of them is device HW configuration controlled by System Status and Configuration module (SSCM). Target of the configuration process is to setup all important analog modules to predefined factory setting plus to initialize default values of several key registers.

Configuration values are stored in the shadow flash memory region which is read by SSCM module during reset phase. As any other flash memory it can happen that values stored there are corrupted with multi bit error. Unlike the application exception system triggering ECC fault in such case, the SSCM module does not have such possibility. The system is still under reset. The SSCM module behavior is that it ignores any ECC faults that might happen during read operation.

The consequence of such silent behavior is that the device can be configured wrongly. Such faulty configuration can remain unnoticed or can have severe safety impact in the application. The distinction between the two is difficult because there is no trace information which data were corrupted and how much.

There is only one possible check to identify if an ECC fault occurred or not. Any read operation from flash memory having ECC fault leaves MCR.EER bit inside the flash module registers set regardless if the read operation is executed by the Core or SSCM module. This can be used to identify if the SSCM module has faced ECC error during configuration or not.

# 3.1 Code sequence

- 1. Read FLASH.MCR register (0xC3F8 8000)

- 2. Test EER bit (bit 16)

- 3. If set ('1') => ECC fault has happened, might be wrong device

configuration => SSCM Faul Handler

#### 3.2 SSCM fault handler

SSCM fault handler is an application specific piece of code. Most probable solution would be to trigger a long reset or external one to re-run SSCM configuration.

10/44 DocID024255 Rev 2

AN4253 FCCU block

# 4 FCCU block

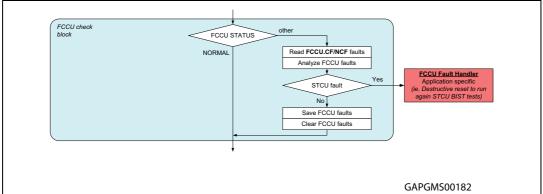

Figure 5. Flow of the "FCCU check block" phase

FCCU blocks monitors various fault signals coming from different parts of the SPC564Lx microcontroller during runtime. FCCU module works in parallel to RGM module. It provides safety measures to signal the fault when reset module fails. Details of FCCU module can be found in AN3235 (see *B.1: Reference documents*).

Microcontroller internal fault signals RGM RGM FCCU Hard RGM\_FCCU\_Safe RGM FCCU Soft RGM\_SRC\_x RGM\_SRC\_y Non-Critical critical faults faults **FCCU** Core access interface (Autonomous HW FSM machine) ME\_SAFE Mode Entry NMI signal Core 2x uC fault output signal GAPGMS00183

Figure 6. FCCU block diagram

After the reset FCCU module can be in two states depending on the reset type:

- Destructive/external FCCU initialized completely, all faults cleared by HW resets

- Functional resets FCCU untouched, status registers contain captured faults

FCCU block AN4253

There are three different error paths reported by FCCU when any fault occurs:

Reset Critical fault or non-critical fault with a configured reset reaction

Safe mode FCCU fault state entry always initiates safe mode request, where

the HW resources are limited and the user has to solve the faults

before asking for a change of the mode.

NMI FCCU fault state entry always generates non-maskable signal.

This signal will generate an exception to the core for faults without reset generation reaction or in case when the reset is not present because of a fault in the reset module (safety measure against

failures in RGM module)

Caution:

Whenever microcontroller is in safe mode, all faults in the FCCU status registers must be cleared before any attempt to leave the safe mode.

#### 4.1 FCCU status check

The first part of FCCU handler checks the state of the FCCU module after the reset. There are four possibilities:

NORMAL Everything is fine from the point of FCCU module, a reset was

either destructive or caused by a non-critical fault that is masked in the configuration, i.e. default behavior of SW functional reset.

ALARM There is a non-critical fault pending in alarm state waiting for SW

intervention.

FAULT All critical faults and non-critical faults without alarm timeout

enabled.

• OTHER Unknown state. It should not happen at all.

The FCCU handler shall resolve all states except NORMAL with the read, analyze, save and clear procedure. No accesses to FCCU registers other than reading the FCCU.CTRL.OPS shall be done between the setting of the key and the actual clear of the status flag.

#### 4.1.1 Code sequence

- 1. Write command OPR=3 to FCCU\_CTRL register

- 2. Wait for operation to finish (FCCU.CTRL.OPS = SUCCESS)

- 3. Read the FCCU STATUS register

- 4. Decide if Status == 0x0 (NORMAL)

# 4.2 Read critical and non-critical faults in FCCU (FCCU.CF/NCF)

The FCCU module contains two groups of faults, critical faults and non-critical faults. Both groups should be read for later analysis.

AN4253 FCCU block

#### 4.2.1 Code sequence

#### Reading Critical Faults (CF)

- 1. Write command OPR=9 to FCCU\_CTRL register

- 2. Wait for operation to finish (FCCU.CTRL.OPS = SUCCESS)

- 3. Read the FCCU\_CF register

#### **Reading Non-Critical Faults (NCF)**

- 1. Write command OPR=9 to FCCU CTRL register

- 2. Wait for operation to finish (FCCU.CTRL.OPS = SUCCESS)

- 3. Read the FCCU NCF register

# 4.3 Analyze FCCU faults

In most cases this block will be skipped unless application requires special startup code for different faults.

### 4.4 STCU fault analysis

This analysis is recommended as any issue found during the built-in self test can signal a presence of latent faults.

There are three signals routed from STCU to FCCU unit to report different kind of issues:

- CF[20] Critical fault found by xBIST test

- CF[27] STCU fault of starting the xBIST tests during the runtime, which leads

to content corruption in the RAM array or in the digital logic

NCF[12] Non-critical fault found by xBIST test

It is recommended to monitor all three fault signals and take an appropriate action when any STCU fault is active.

#### 4.4.1 Code sequence

- 1. Test bits b'20 and b'27 in Critical faults

- 2. Test bit b'12 in Non-critical faults

- 3. If any of the testing bits is '1' > Jump to FCCU Fault handler Otherwise continue in startup

#### 4.5 Save FCCU faults

It is usually required to keep fault values for later analysis by the application code. This cannot be done by simply leaving status registers untouched and read them later. The reason is that any present fault in FCCU status register would prevent successful transition from SAFE mode to DRUN mode.

FCCU block AN4253

In such case it is necessary to store the read values somewhere else.

Some possibilities are:

Non-volatile RAM used to exchange data between the startup code and the application.

In case of destructive reset, code has to initialize non-volatile block to default values.

One of the core registers like SPRGx. These registers are usually used by the application or operating system for non specific purposes.

#### 4.6 Reset FCCU faults

Any fault latched by the FCCU prevents successful transition from Safe mode to DRUN. Therefore whenever the microcontroller is in safe mode, FCCU flags must be cleared before executing mode transition.

#### 4.6.1 Code sequence

#### Clearing Critical Faults (CF) sequence

- 1. Write the Key 0x618B7A50 to FCCU CFK register

- 2. Write CF status value back to FCCU CF register

- 3. Wait for operation to finish (OPS == SUCCESS)

#### Clearing Non-Critical Faults (NCF) sequence

- 1. Write the Key 0xAB3498FE to FCCU NCFK register

- 2. Write NCF status back to FCCU NCF register

- 3. Wait for operation to finish (OPS == SUCCESS)

#### 4.7 FCCU fault handler

FCCU fault handler is an application specific piece of code. There might be several possibilities like:

- Analyzing which LBIST partition or MBIST block failed and decide if it is critical for the application or not.

- Example can be failing memory block belonging to Flexray module. If Flexray module is not used then the fault found by STCU self test is of no harm for the application and startup can continue.

- Generate destructive reset to restart microcontroller from the very beginning including STCU Self tests. If the fault was because of a temporary failure, re-initiated self test will finish ok, which enables to continue with the startup.

AN4253 RGM block

#### 5 RGM block

Reset Read RGM.FES/DES flags Analysis Functional reset POR/Destructive/Ext RGM Fault Handler Application specific (ie. continue as it would be No Expected destructive reset or generate SW reset) Yes User specific code for given expected reset Set RGM\_DES = YES Set RGM\_DES = NO Save RGM.FES/DES flags Clear RGM.FES/DES flags GAPGMS00184

Figure 7. Flow of the "Reset analysis" phase

The reset module (RGM) centralizes the reset functionality of the microcontroller. Its decision for the reset event is based on evaluation of selected number of HW signals coming from various parts of the microcontroller.

RGM categorizes signals into two groups:

| • | Destructive reset signals | Signals notifying problem with the power supply with the consequence of corrupted RAM memory content. In such case complete RAM initialization is required.        |

|---|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Functional reset signals  | All other signals that might report serious problem in the hardware with consequence on application behavior. RGM offers limited configurability for some of them. |

Complete list of reset signals is in RM0032 (see B.1: Reference documents).

# 5.1 Read RGM status (both destructive and functional resets)

Both groups of flags can be read from RGM base address with simple 32 bit read instruction. The upper 16 bits store functional reset signals, the lower 16 bits destructive ones.

RGM block AN4253

#### 5.1.1 Code sequence

1. 32b read from RGM address 0xC3FE4000

#### 5.2 POR/destructive/external reset check

POR, destructive and external resets are destructive to RAM memory content. It means that the entire RAM memory must be initialized in the startup.

External reset is destructive only if STCU BIST tests are enabled. If STCU built–in self test is not used, external reset can be omitted from the check.

#### 5.2.1 Code sequence

- 1. Do AND operation between read FES DES value and mask 0x8000FFFF

- 2. If the result != 0x0 > destructive reset, RAM corrupted

# 5.3 Expected functional reset

This analysis is application specific as some reset can be used from the application to change the mode of the ECU.

In most cases the startup analysis requires additional information from the application to decide if the reset was expected or unexpected. One possibility is to use a small RAM memory block that serves as non-volatile storage, valid only if the reset is functional one.

# 5.4 User specific code for given expected reset

If the reset was expected the user provides the necessary startup code. In most case it can be by setting special flags or to set appropriate values in the non-volatile RAM block.

# 5.5 Save reset flags

Similar to FCCU save operation:

- Non-volatile RAM is used to exchange data between the startup code and the application. In case of a destructive reset the entire memory will be cleared.

- One of the core registers like SPRGx. These registers are usually used by the application or operating system for non specific purposes.

# 5.6 Clear reset flags

Reset flags are cleared with write-'1'-to-clear operation to RGM base address (FES+DES registers). A clear operation is needed in case the microcontroller is in safe state to enable mode entry transition.

16/44 DocID024255 Rev 2

AN4253 RGM block

# 5.6.1 Code sequence

1. Write '1's to RGM base address 0xC3FE4000

#### 5.7 RGM fault handler

If the functional reset was unexpected, the next steps depends on the application. Unexpected reset always means a sudden critical problem that had happened in the microcontroller.

Some of the possibilities of next steps are:

- Continue as it would be destructive reset with complete initialization

- Generate a destructive reset to run STCU built in self tests again to check if there is no new fault present in the microcontroller

Safe mode block AN4253

#### 6 Safe mode block

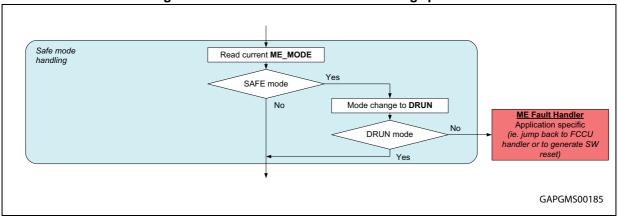

Figure 8. Flow of the "Safe mode handling" phase

Safe mode is a special mode of the microcontroller where only limited part of the hardware functionality is enabled to the user. All attempts to change the HW configuration are blocked until fault conditions are removed.

Very often safe mode is observed in the startup phase after a functional reset other then functional reset initiated from software. In such situation startup has to leave safe mode prior to any mode change transition.

Conditions to leave safe mode are:

- No FCCU fault pending

- FCCU flags in RGM.FES register cleared

#### 6.1 Read current mode of the microcontroller

Current mode of the microcontroller is reported in Mode Entry Global Status (ME.GS) register.

### 6.1.1 Code sequence

1. 32 bit read of ME.GS register (0xC3FDC000)

#### 6.2 Safe mode check

It is needed to extract S\_CURRENT\_MODE bit field from the read value. There are only two possible values after the reset:

- 2 = SAFE

- 3 = DRUN

AN4253 Safe mode block

#### 6.2.1 Code sequence

- 1. Extract the S CURRENT MODE bit field

- 2. Check if the value is equal to 2 (safe mode)

- 3. If Yes > go to mode transition step, otherwise continue with next startup block

# 6.3 Mode change to DRUN request

Mode change request consist of a sequence of two 32 bit writes instruction containing requested mode (3=DRUN) together with a key, where the second key is the inverted value of the first one.

It is necessary to wait for the end of the transition. Ongoing transition is reported by MTRANS bit in ME.GS register.

#### 6.3.1 Code sequence

- Write value 0x30005AF0 (DRUN + 1.key) to ME.MCTL register (0xC3FDC004)

- 2. Write value 0x3000A50F (DRUN + 2.key) to ME.MCTL register (0xC3FDC004)

- 3. Read ME.GS register

- 4. Check MTRANS bit, if '1' > go back to step 3 (Read ME.GS

register)

#### 6.4 DRUN mode check

If there is no pending FCCU fault and FCCU reset flags in the RGM module are cleared, mode transition should finish successfully. If not, a fault handler must handle this problem.

S\_CURRENT\_MODE bit field should equal to number 3 (DRUN).

#### 6.4.1 Code sequence

- 1. Read ME.GS register

- 2. Extract S CURRENT MODE bit field

- 3. Check if the value equals to 3 (DRUN), if No > go to  ${\tt ME\_Fault\_handler}$

#### 6.5 ME fault handler

ME\_Fault\_handler shall handle the situation when a requested transition from safe mode to DRUN mode fails and the microcontroller remains in the safe mode. A reason can be an unsuccessful clear operation of FCCU faults or the presence of another hardware fault.

Safe mode block AN4253

In such case the decision for the next steps is user specific. Some possibilities can be:

- Go back to FCCU step to re-run again through FCCU and RGM blocks.

- Force the reset to start the device from the very beginning of HW reset initialization, which might be appropriate if the transition failure was because of undefined temporary fault.

### 7 HW resource initialization

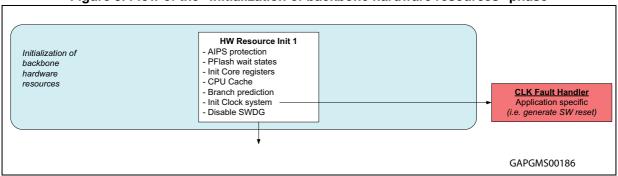

Figure 9. Flow of the "Initialization of backbone hardware resources" phase

This block is responsible for the initialization of the hardware resources that have an impact on startup time, like optimizing the flash access time, initialization of the core cache, setting up clock subsystem etc.

Anything that does not have an impact on the startup should be left on the application startup executed later on.

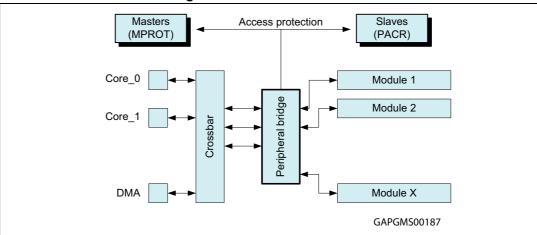

# 7.1 AIPS protection

AIPS protection is a feature implemented in a peripheral bridge module to control access rights of bus masters accessing peripheral modules.

Figure 10. AIPS block scheme

#### 7.1.1 Default reset configuration

- Core\_0/1 Both are privileged and trusted to access peripherals.

- DMA,Flexray Not privileged, forced to an user mode. They cannot access peripheral memory space without modification of AIPS configuration.

If the startup relies on a code execution from the core, there is no need to change the configuration of the AIPS. But when the startup wants to use DMA capability, it is necessary to change *MPROT.MPL* bit field.

#### Code sequence

1. Write value 0x77770070 to AIPS MPROT register

# 7.2 PFlash controller setup

PFlash controller acts as an interface between masters (AHB bus) and a Flash memory array. It controls timing access time and buffering scheme for instruction fetches and data read.

Core\_0

Core\_1

64bits

64bits

64bits

128bits

FLASH memory array

Line buffers

4x / each AHB port

Figure 11. PFlash controller

## 7.2.1 Default reset configuration

Instruction fetch

Buffers enabled (3x for instruction fetch), prefetch enabled

Data read Buffer disabledAccess timing 3 wait states

Default setting is optimal for startup code execution that will run on 120 MHz clock. An assumption is that the startup code does not use many constants placed in Flash as data buffer is disabled.

Note: PFlash register modification shall be done when executing the code from RAM

#### 7.2.2 Code sequence

No need to change default reset configuration.

# 7.3 Core registers initialization

When running the Leopard device in Lock-Step mode (LSM) it is important to initialize some of the Core registers to a value that are identical for both Cores. The reason behind this is that some Core registers are un-initialized by the reset and it can happen that under certain

circumstances different values in both cores can lead to the reset because of RCCU (checker blocks) event.

In decoupled mode, it is not necessary to have this explicit initialization.

#### 7.3.1 Code sequence

No need to initialize core registers.

# 7.4 Cache memory initialization

Cache memory initialization does not bring any advantage for a simple startup code with a sequential flow and small loops that fit into buffer lines of PFlash controller. Default PFlash setup can store up to twelve 32 bit instruction or twenty-four 16 bit instructions.

Of course cache memory should be enabled somewhere in the startup code, because it brings significant increase in performance (~30 %). If the startup code is the place of initialization, cache enable bit in L1CSR1 special function register must be set.

#### 7.4.1 Default reset configuration

Cache disabled

#### 7.4.2 Code sequence

1. Enable cache (bit ICE) in Core L1CSR1 special function register

# 7.5 Branch prediction

Z4 core implemented on the SPC564Lx device contains simple branch target buffer prediction feature that brings small performance increase for an application code.

It is not really needed to be done in the startup code, but if the startup is the place of initialization, code shall enable the branch prediction in *BUCSR* special purpose register.

#### 7.5.1 Default reset configuration

Branch target buffer prediction disabled

#### 7.5.2 Code sequence

1. Set BPEN bit in BUCSR core register

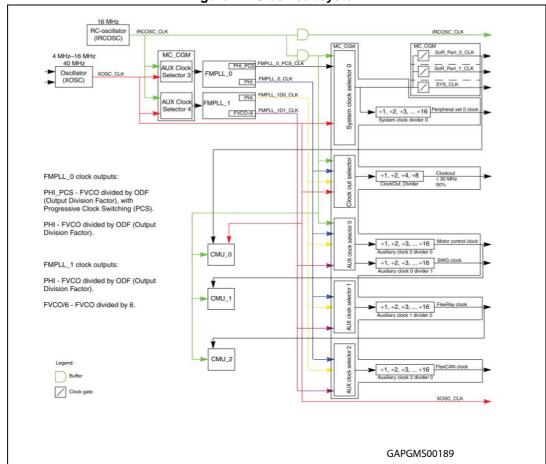

# 7.6 Clock system initialization

Clock subsystem consists of clock generators, clock selectors with dividers and clock monitor units.

HW resource initialization AN4253

Figure 12. Clock subsystem

#### 7.6.1 Default reset configuration

System clock IRC 16 MHz Oscillator Disabled **FMPLLs** Disabled Clock output Disabled Peripheral clock Enabled, PCLK = IRC\_16 MHz Motor clock Enabled, MCLK = IRC\_16 MHz Flexray clock Enabled, FCLK = system FMPLL CAN clock Enabled, CCLK = system FMPLL FMPLL0 input IRC\_16 MHz FMPLL1 input IRC\_16 MHz

As seen from the default configuration above, the system clock used for code execution is the internal IRC oscillator running on 16 MHz. It is advised to change the clock setting before RAM initialization and before the application startup to make the process faster.

It is recommended to split clock subsystem setup to several parts to make the clock transition safe with minimum impact on voltage regulator load. All mode transitions issued here use DRUN mode as a target mode.

- 1. Configure oscillator module

- 2. Enable oscillator block (mode transition)

- 3. Configure input clock to FMPLL0

- 4. Configure FMPLL0

- 5. Enable FMPLL0 block (mode transition)

- Wait for FMPLL0 lock

- 7. Enable peripherals needed in the startup (clock gating)

- 8. Switch system clock to FMPLL0 output (mode transition)

#### Configure oscillator block

Here one parameter shall be tuned with respect to ECU design and selected crystal oscillator. It is end of count value parameter, *EOCV* bit field in *RC\_CTL* register.

Count value to reach = EOCV\*512

This parameter tells how many clock pulses will be counted before an external crystal clock can be considered as stable and possible to select as the system clock.

EOCV value shall satisfy the following formula:

EOCV >= (TXOSCHSSU \* fXOSCHS) / 512

where fXOSCHS is the "oscillator frequency" and TXOSCHSSU is the "oscillator start-up time" whose value can be found in the DS.

#### Default reset value

• EOCV = 128 It gives 1.63 ms delay for 40 MHz crystal oscillator

#### Code sequence

1. Write required value to EOCV bit field in OSC CTL register

#### **Enable oscillator block (mode transition)**

In order to enable the crystal oscillator block, mode transition is required with bit XOSCON in ME\_DRUN\_MC register set on.

#### Code sequence

- 1. Set bit XOSCON in ME\_DRUN\_MC register

- 2. Write DRUN with Key 1 in ME MCTL register

- 3. Write DRUN with Key\_2 in ME\_MCTL register

- 4. Wait mode transition to finish (ME GS.MTRANS bit = 0)

HW resource initialization AN4253

#### Configure input clock to FMPLL0

External crystal oscillator shall be used as input to FMPLL block. A selection is done in the *AUX Clock selector 3* block.

#### Default reset value

• FMPLL0 input IRC\_16 MHz. It is necessary to change it to XOSC.

#### Code sequence

1. Set SELCTL bit field of CGM AC3 SC register to 1 (XOSC)

#### **Configure FMPLL0**

The FMPLL0 configuration consists in setting right values to, IDF, ODF and NDIV, in FMPLL0.CR register. Values have to fulfill equations given in RM0032 (see *B.1: Reference documents*). Their values depend on selected crystal oscillator and target system frequency.

#### **Default reset values**

- IDF=1 Input frequency divided by 2. It must be changed to fulfill 4-16 MHz input range in case of 40 MHz crystal oscillator

- ODF=1 Divide VCO output frequency by 4.

- NDIV=64 Input frequency divided by IDF block multiplied by NDIV to get VCO frequency, which must be within 256-512 MHz frequency range.

#### Example 1

Setting for 120 MHz system clock derived from 40 MHz crystal oscillator

IDF=3 40 MHz / 4 = 10 MHz as input to FMPLL

NDIV=48 10 MHz \* 48 = 480 MHz as VCO frequency

ODF=1 480 MHz / 4 = 120 MHz system clock

#### Code sequence

Write IDF,ODF and NDIV values to FMPLLO.CR register (0xC3FE\_00A0)

#### **Enable FMPLL0 block (mode transition)**

It is necessary to set *PLLOON* bit in *ME\_DRUN\_MC* register and then to initiate a mode transition to DRUN.

#### Code sequence

- 1. Set bit PLLOON in ME DRUN MC register

- 2. Write DRUN with Key 1 in ME MCTL register

- 3. Write DRUN with Key 2 in ME MCTL register

- 4. Wait mode transition to finish (ME\_GS.MTRANS bit = 0)

#### Wait for FMPLL0 lock

Before FMPLL0 can be used as a system clock it is necessary to wait for the PLL lock event. CR register in the FMPLL0 block contains S LOCK bit that tells the LOCK status:

- 0 = FMPLL unlocked

- 1 = FMPLL locked

Usual lock time delay is around 200 µs.

#### Code sequence

- 1. Read FMPLL0 CR register

- 2. Test s\_lock bit

- 3. If '0' > wait loop to step 1

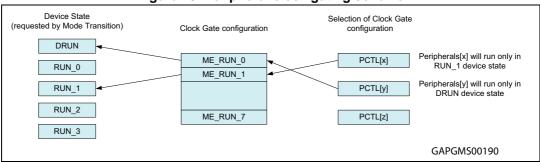

#### Enable peripherals needed in the startup

There is a set of peripherals that are clock gated (all peripherals having PCTL configuration register inside mode entry module). Each peripheral within this group has to be explicitly configured to run in dedicated mode. This configuration is done via pair of registers, *ME\_RUN\_PC0-7* and *ME\_PCTLx*.

ME\_RUN\_PC[0-7] registers indicate if the peripherals are active and when they are inactive (clock gated). The peripheral clock for a given mode transition must be configured by the user.

Figure 13. Peripheral clock gating scheme

#### **Default reset state**

ME\_RUN\_PCx

No mode selected, no clock enabled to any gated peripheral

PCTLx They point to ME\_RUN\_PC0

Note:

Any change in ME\_RUN\_PC0 will be used by all peripherals if they are not reconfigured to use another ME\_RUN\_PCx register. Result can be that all peripherals, even peripherals that are not needed, are enabled if ME\_RUN\_PC0 is enabled for current device state mode.

Good practice is not to use ME\_RUN\_PC0 register, but to configure one of the ME\_RUN\_PC[1-7] and configure needed peripherals accordingly.

HW resource initialization AN4253

#### Code sequence

- 1. Set DRUN bit in ME\_RUN\_PC1 register (enable DRUN in ME\_RUN\_PC1 configuration)

- 2. Set RUN\_CFG bit field to 1 in ME\_PCTL register of peripherals to be activated

- 3. Peripherals will be activated with next Mode Transition to DRUN

#### Switch system clock to FMPLL0 (mode transition)

In order to change system clock another mode transition is required. This transition will be used for enabling the clock gated peripherals that were prepared in previous step.

#### Code sequence

- Set SYSCLK field to 6 in ME\_DRUN\_MC register (PLL as system clock)

- 2. Write DRUN with Key 1 in ME MCTL register

- 3. Write DRUN with Key 2 in ME MCTL register

- 4. Wait mode transition to finish (ME GS.MTRANS bit = 0)

- 5. Read ME.GS register and check that SYSCLK field equals to 4 (FMPLL0)

- 6. If not > go to CLK Fault Handler

#### 7.7 CLK fault handler

It is up to an application what to do in case of a problem with system clock initialization. There might be several reasons for the failure of the initialization

- Crystal oscillator does not start

- Crystal oscillator starts at wrong frequency

- FMPLL0 does not lock (here software watchdog expires and trigger reset earlier than going to CLK fault handler)

The standard solution might be to ask for reset to try initialization from the very beginning again.

# 7.8 Software Watchdog Timer (SWT) disable

Depending on the Option byte configuration in the shadow Flash memory the software watchdog is enabled after the reset or disabled. SWT module always runs on IRC\_16 MHz clock base.

It is recommended to leave it enabled after the reset up to this point as it monitors progression of the startup code and hardware initialization. Any fault leading to lockup situation in the previous steps will finish in a reset event caused by SWT expiration event.

The reason why the software watchdog is going to be disabled here is time needed for HW initialization (mainly contribution of clock initialization) plus RAM memory initialization that takes significant time. Both contributors can take longer than it is a default SWT expiration time.

#### 7.8.1 Default reset value

• SWT expiration ~16 ms

# 7.8.2 Code sequence

- 1. Clear SLK (soft lock bit) in CR register by sequence of two writes to SR register using proper keys

- 2. Clear WEN bit in CR register

47/

DocID024255 Rev 2

RAM initialization AN4253

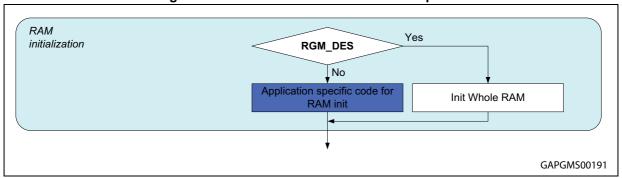

#### 8 RAM initialization

Figure 14. Flow of the "RAM initialization" phase

An Important part of the startup code is linked to RAM initialization. Especially in case of destructive resets when the content of the RAM cells, data plus ECC syndrome bits, are undefined. In such case the entire RAM memory or at least all used sections must be initialized to update ECC syndrome bits. Not doing this can lead to multiple bit ECC faults during any read operation or byte, half word write operation.

#### **Default reset state**

- Destructive reset RAM undefined. It is needed to initialize it completely.

- Functional reset

RAM preserves its content. It can be used as non-volatile storage.

#### 8.1 Init whole RAM

There are mainly two ways how to initialize the RAM. Both need supportive information from linker file.

- Using multiple word store instructions e\_stmw, that store set of GPRs registers in consecutive order

- Using standard 32 bit store instructions e stwu

This part of startup code can be used for initializing the RAM memory to specific value, i.e. zero.

#### 8.1.1 Code sequence

- Determine number of cycles to execute in multiples of words. It depends on type of instructions.

- 2. Place iteration count to core counter register

- 3. Prepare start address and adjust it if e stwu instruction will be used

- 4. Prepare value to write. In case of *e\_stmw* instruction, the value must be written to all involved GPRs

- 5. Issue store instruction

- 6. Decrement counter and jump for next store cycle if not zero

# 9 Application 'asm' startup

Before jumping to 'C' language to continue with the startup there are still some steps required. These steps are completely under user or any other software vendor (i.e. OS supplier) responsibility. Simply this 'asm' part shall prepare a base for the 'C' programming environment.

Among usual steps belongs:

- Initialization of r1 register (link register)

- Initialization of r2 register (sdata2 base pointer)

- Initialization of r13 register (sdata base pointer)

- Stack initialization

- Initialization of initialized variables

# 10 Application 'C' startup

High level language application startup is under user responsibility.

Examples of application 'C' startup routines are:

- External hardware initialization

- EEPROM control block initialization, reading stored data

- Software layers initialization

- Application blocks initialization

Part of the application startup shall be safety checks. Safety checks related to microcontroller hardware are described more in AN3324 (see *B.1: Reference documents*).

AN4253 asm examples

# Appendix A asm examples

All 'asm' examples here are built with WindRiver compiler toll with preprocessing on assembly files set on. Preprocessor directives are used to make the code more readable. Readable code is prioritized to time or space optimization.

### A.1 Symbol defines

```

// MSR value to set after the reset

#define STARTUP MSR 0x21200 // CE | ME | DE

// Software watchdog module

#define SWT BASE

0xFFF38000 // Software watchdog base address

#define SWT REG CR

// registers offset

0x0000

#define SWT_REG_SR 0x0010

#define SWT_UNLOCK_KEY1 0xC520

// key1 for soft_lock unlock

#define SWT UNLOCK KEY2 0xD928

// key2 for soft lock unlock

// FLASH registers

0xC3F88000 // Flash registers base address

#define FLASH_BASE

#define FLASH_REG_MCR 0x0000  // registers offset

#define FLASH EER MASK 0x00008000 // EER bit

// FCCU module constants

#define FCCU BASE 0xFFE6C000 // FCCU module base address

#define FCCU_REG_CTRL 0x0000

// registers offset

#define FCCU REG NCF 0x0080

#define FCCU REG NCFK 0x0090

#define FCCU REG STATUS 0x00C0

#define FCCU_REG_IRQ 0x00E0

// command to read Status

#define FCCU_OPR_STATUS 0x3

#define FCCU OPR CF READ 0x9

// command to read CF

#define FCCU_OPR_NCF_READ 0xA // command to read NCF

#define FCCU_CFK_KEY 0x618B7A50 // key for CF faults clear operation

#define FCCU_NCFK_KEY 0xAB3498FE // key for NCF faults clear operation

#define FCCU_OPS_SUCCESS 3 // command successful status to wait for

#define FCCU_CF_STCU 0x0850 // upper half word for compare instruction

#define FCCU_NCF12

// BSTI instr has inverse bit numbering

19

// RGM module constants

#define RGM BASE

0xC3FE4000 // Reset module base address

#define RGM_REG_FESDES 0x0000 // register offset from RGM_BASE

#define RGM DES MASK

0x8000FFFF // Destructive resets status bit mask

// MODE ENTRY module constants

#define ME_REG_GS

// register offsets from ME_BASE

0x0000

#define ME_REG_MCTL

0x0004

#define ME REG DRUN MC 0x002C

#define ME_REG_RUN_PC1 0x0084

#define ME REG PCTL CRC 0x00FA

#define ME GS MODE SAFE 2

// current mode SAFE

```

asm examples AN4253

```

#define ME GS MODE DRUN 3

// current mode DRUN

#define ME GS MTRANS 4

// position of bit for e btsti instr.

#define ME_GS_SYSCLK_MASK 0x000F // mask of system clk field

#define ME_MCTL_DRUN_R1 0x30005AF0 // 1.step in mode transition request

#define ME_MC_XOSCON 26

// bit position for se bseti instr.

#define ME MC PLLOON

// bit position for se_bseti instr.

25

#define ME MC SYSCLK PLL 0x0004

// value for e_or2i instr.

#define ME RUNPC DRUN

28

// bit position for se bseti instr.

#define ME PCTL RUNPC1

// pointer to RUN PC1 configuration

// AIPS peripheral bridge

0xFFF00000 // peripheral bridge base address

#define AIPS BASE

#define AIPS_REG_MPROT 0x0000

// register offset from AIPS BASE

#define AIPS_MPROT_ENABLE 0x77770070 // Core0,1, DMA0, FlexRay as superuser

// Core Cache memory

#define CACHE REG L1CSR1

1011 // SPR register number

#define CACHE ICE BIT

0x0001 // for e_li instruction

// CGM block

#define CGM BASE

0xC3FE0000 // base address of CGM module

#define CGM REG AC3SC 0x0398 // register offset from CGM_BASE

#define CGM AC3SC XOSC 0x0100

// value for PLL input AUX3 bridge

// XOSC block (CGM base)

#define XOSC_REG_OSCCTL 0x0000 // register offset from CGM_BASE

#define XOSC_EOCV_IMASK 0xFF00 // mask to clear EOCV default value

#define XOSC_EOCV_VALUE 0x009C  // cca 2ms for 40MHz crystal

// FMPLL0 block (CGM base)

#define FMPLL0_REG_CR 0x00A0

// register offset from CGM_BASE

// bit position for e_btsti instr.

#define FMPLL0_SLOCK 28

// 3 = divide by 4

#define FMPLL0 IDF 0x0C00

// 1 = divide by 4

#define FMPLL0_ODF

0x0100

// 48 = multiply by 48

#define FMPLL0 NDIV 0x0030

#define FMPLL0 VALUE (FMPLL0 IDF | FMPLL0 ODF | FMPLL0 NDIV)

```

# A.2 Core register init (LSM)

```

// selected core SPRs

mtcrf 0xFF,r31 // Condition register

mtspr 285,r31 // TBU

mtspr 284,r31 // TBL

mtspr 272,r31 // SPRG0

mtspr 273,r31 // SPRG1

mtspr 274,r31 // SPRG2

mtspr 275,r31 // SPRG3

mtspr 276,r31 // SPRG4

mtspr 277,r31 // SPRG5

mtspr 278,r31 // SPRG6

mtspr 279,r31 // SPRG6

mtspr 279,r31 // SPRG7

mtspr 604,r31 // SPRG8

mtspr 605,r31 // SPRG9

```

34/44 DocID024255 Rev 2

AN4253 asm examples

```

mtspr 26,r31 // SRR0

mtspr 27,r31 // SRR1

mtspr 58,r31 // CSRR0

mtspr 59,r31 // CSRR1

mtspr 63,r31 // IVPR

mtspr 61,r31 // DEAR

mtspr 62,r31 // ESR

mtspr 570,r31 // MCSRR0

mtspr 571,r31 // MCSRR1

mtspr 340,r31 // TCR

mtspr 512,r31 // SPEFSCR

mtspr 1,r31 // XER

mtspr 256,r31 // USPRG0

mtspr 9,r31 // CTR

mtspr 8,r31 // LR

mtspr 308,r31 // DBCR0

mtspr 309,r31 // DBCR1

mtspr 310,r31 // DBCR2

mtspr 561,r31 // DBCR3

mtspr 563,r31 // DBCR4

mtspr 564,r31

mtspr 603,r31

```

# A.3 MMU entry configuration

```

// Table 0

e lis r0, 0x1000

e or2i r0, 0x0000

// fix bits + TLB entry

mtspr mas0, r0

e lis r0, 0xC000

e or2i r0, 0x0500

mtspr mas1, r0

// cfg bits + Page SIZE

e lis r0, 0x0000

e or2i r0, 0x0028

mtspr mas2, r0

// EPN + page atrib

e_lis

r0, 0x0000

e_or2i r0, 0x003F

// RPN + access atrib

mtspr mas3, r0

tlbwe

```

# A.4 SSCM HW configuration check

asm examples AN4253

```

se_bc 00,02,sscm_error_handler  // if yes - jump to SSCM Error handler

...

sscm_error:

// user code - handler of SSCM error

se_b .  // break due to SSCM fault

```

# A.5 FCCU handling block

```

// Base address of FCCU module to r7

e lis r7, FCCU BASE@h

e_or2i r7, FCCU_BASE@l

// Read Status

e li r0, FCCU OPR STATUS

// prepare command

e_stw

r0, FCCU REG CTRL (r7) // issue command

.read status:

e_lwz r0, FCCU_REG_CTRL (r7) // read FCCU_CTRL register

e_rlwinm r0, r0, 26, 30, 31 // rotate OPS field and mask it

se_cmpi r0, FCCU_OPS_SUCCESS // look for OPS = SUCCESS

se_bc 00,02,.read_status

// wait to finish the command

e_lwz

r5, FCCU REG STATUS (r7) // read Status

se_cmpi r5,0

// Status == NORMAL?

se_bc 1,2,fccu_no_fault

// no fault in fccu > skip fault handling

// Read CF faults

e_li r0, FCCU_OPR_CF_READ

// prepare command

e stw

r0, FCCU REG CTRL (r7)

// issue command

.read cf:

e lwz r0, FCCU REG CTRL (r7)

// read FCCU CTRL register

// rotate OPS field and mask it

e rlwinm r0,r0,26,30,31

se_cmpi r0, FCCU_OPS_SUCCESS

// look for OPS = SUCCESS

// wait to finish the command

se_bc 00,02,.read_cf

e_lwz r3, FCCU_REG_CF (r7)

// read CF register to r3 register

mtsprg0 r3

// save them to Core SPRG0 register

// Read NCF faults

e li r0, FCCU OPR NCF READ

// prepare command

r0, FCCU REG CTRL (r7) // issue command

e stw

.read ncf:

e lwz r0, FCCU REG CTRL (r7) // read FCCU CTRL register

e rlwinm r0,r0,26,30,31 // rotate OPS field and mask it

se cmpi r0, FCCU OPS SUCCESS // look for OPS = SUCCESS

se_bc 00,02,.read_ncf // wait to finish the command

e_lwz r4, FCCU_REG_NCF (r7) // read NCF register to r4 register

mtsprg1 r4

// save them to Core SPRG1 register

// Check STCU faults

se_mr r0,r3

// take copy of CF faults

e_and2is. r0,0x0850

// mask bits CF[27,22,20]

se_cmpi r0,0

// is one of them '1' ?

se_bc 00,02,fccu_stcu_error // if yes - jump to error handler

{\tt se\_btsti} \quad {\tt r4, FCCU\_NCF12} \qquad \qquad // \ {\tt check \ bit \ NCF[12]}

se_bc 1,2,fccu_analyze

// jump if all STCU bits are '0'

```

36/44 DocID024255 Rev 2

AN4253 asm examples

```

fccu stcu error:

// user code - handler of STCU errors

se_b .

// break due to STCU faults

fccu analyze:

// user code - analyze FCCU faults, if there are any

// ...

se b

fccu clear

// continue with clear operation

fccu clear:

// clear FCCU Critical faults CF

e_lis r0, FCCU_CFK_KEY@h

e or2i r0, FCCU CFK KEY@l

e stw r0, FCCU REG CFK (r7) // write Key to clear CF faults

e_stw r3, FCCU_REG_CF (r7) // clear known CF faults

.wait_cf_clear:

r0, FCCU_REG_CTRL (r7) // read FCCU_CTRL register

e_lwz

// rotate OPS field and mask it

e rlwinm r0, r0, 26, 30, 31

se_cmpi r0, FCCU_OPS_SUCCESS // look for OPS = SUCCESS

00,02,.wait_cf_clear // wait to finish the command

se_bc

// clear FCCU Non-Critical faults (NCF)

e lis r0, FCCU NCFK KEY@h

e or2i r0, FCCU NCFK KEY@l

e stw r0, FCCU REG NCFK (r7) // write Key to clear CF faults

r4, FCCU REG NCF (r7) // clear known NCF faults

e stw

.wait_ncf_clear:

e_lwz r0, FCCU_REG_CTRL (r7) // read FCCU_CTRL register

e_rlwinm r0,r0,26,30,31 // rotate OPS field and mask it

se_cmpi r0, FCCU_OPS_SUCCESS // look for OPS = SUCCESS

se_bc 00,02,.wait_ncf_clear // wait to finish the command

// continue with next block

se_b

fccu_end

// no FCCU faults

fccu no fault:

e lis r0,0

mtsprg0 r0

// save no CF fault to Core register

mtsprg1 r0

// save no CF fault to Core register

fccu end:

```

#### A.6 RGM block

asm examples AN4253

```

// look for destructive resets

se and r0, r1

// is one of them '1' ?

se cmpi r0,0

se bc 01,02,rgm_fes_handler

// if no - jump to Functional handler

rgm des handler:

// do what is needed for destructive path

// ....

se b

rgm clear

// go to flag reset operation

rgm fes handler:

// analyze if the reset was expected or not

// ...

rgm_clear:

e_lis r1, 0xFFFF

e_or2i r1, 0xFFFF

// prepare value for clear-write-1 oper.

e_stw r1, RGM_REG_FESDES (r7)

// write '1' to clear all flags

rgm_end:

```

#### A.7 Safe mode block

```

// Base address of ME module to r7

e_lis

r7, ME BASE@h

e_or2i

r7, ME_BASE@l

// read status & check SAFE mode

e lwz r0, ME REG GS (r7)

// read GS register

// shift S_CURRENT_MODE field for comparison

se srwi

r0, 0x1C

se_cmpi r0, ME_GS_MODE_SAFE

// compare with SAFE mode value

se bc

0,2,me end

// not in SAFE mode > end SAVE handler

me_save_drun_change:

// SAFE mode is present, request change to DRUN

r7, ME_BASE@h

e_lis

e_or2i

r7, ME_BASE@l

r0, ME_MCTL_DRUN_R1@h

e_lis

e_or2i

ro, ME MCTL DRUN R1@l

r0, ME_REG_MCTL (r7)

r0, ME_MCTL_DRUN_R2@h

// 1. step - normal key

e stw

e_lis

e or2i r0, ME MCTL DRUN R2@l

r0, ME_REG_MCTL (r7)

// 2. step - inverted key

e_stw

// wait for transition to complete (test of GS.MTRANS bit)

me wait transition:

r0, ME REG GS (r7)

// read GS register

se_btsti r0,ME_GS_MTRANS

// test the MTRANS bit

se_bc

0,2,me_wait_transition

// if '1' > wait in loop

// read status & check DRUN mode

// shift S_CURRENT_MODE rigth for comparison

se_srwi r0, 0x1C

se_cmpi r0, ME_GS_MODE_DRUN

// compare with DRUN value

// if DRUN=TRUE > end the ME handler

se_bc

1,2,me_end

// DRUN is not entered

// execute Fault management

me drun fault:

// execute fault handler in the case of unsuccessful Mode transition

```

AN4253 asm examples

## A.8 AIPS protection

# A.9 Cache memory initialization

# A.10 Branch prediction

# A.11 Clock system initialization

```

// setup CGM and ME base addresses

e lis r6, CGM BASE@h

e_or2i r6, CGM_BASE@l

e_lis

r7, ME_BASE@h

e_or2i r7, ME_BASE@l

// setup EOCV value in XOSC block

e_lhz r0, XOSC_REG_OSCCTL (r6) // get half word with EOCV bit field

e_and2i. r0, XOSC_EOCV_IMASK // clear EOCV field

e_or2i r0, XOSC_EOCV_VALUE

// set new value

e_sth

r0, XOSC_REG_OSCCTL (r6) // write it back

// enable XOSC in DRUN mode

e_lwz r0, ME_REG_DRUN_MC (r7) // read ME_DRUN_MC register

se_bseti r0, ME_MC_XOSCON

// set on XOSCON bit

r0, ME REG DRUN MC (r7) // write value back

// mode transition -> DRUN

r0, ME MCTL DRUN R1@h

e lis

e or2i r0, ME MCTL DRUN R1@l

e stw r0, ME REG MCTL (r7)

// 1. step - normal key

e lis r0, ME MCTL DRUN R2@h

e_or2i r0, ME_MCTL_DRUN_R2@l

```

asm examples AN4253

```

r0, ME REG MCTL (r7) // 2. step - inverted key

e stw

// wait for transition to complete (test of GS.MTRANS bit)

me_wait_xoscon:

r0, ME_REG_GS (r7)

// read GS register

e lwz

se btsti r0, ME GS MTRANS

// test the MTRANS bit

0,2,me wait xoscon

// if '1' > wait in loop

// select XOSC as input to FMPLL0 block

e li

r0, CGM AC3SC XOSC

// prepare value

e_sth

r0, CGM_REG_AC3SC (r6)

// write it to CGM_AC3SC register

// configure FMPLL0

e li

r0, FMPLL0 VALUE

// prepare value for FMPPL0 configuration

r0, FMPLL0_REG_CR (r6)

e_sth

// write it to FMPLLO_CR register

// enable FMPLL0 in DRUN mode

se_bseti r0, ME_MC_PLL00N

// set bit PLL00N

r0, ME_REG_DRUN_MC (r7) // update ME_DRUN_MC register

e_stw

// mode transition -> DRUN

e lis

r0, ME MCTL DRUN R1@h

e or2i

r0, ME_MCTL_DRUN_R1@l

e_stw r0, ME_REG_MCTL (r7)

// 1. step - normal key

e lis

r0, ME MCTL DRUN R2@h

e or2i r0, ME MCTL DRUN R2@1

e_stw r0, ME_REG_MCTL (r7)

// 2. step - inverted key

// wait for transition to complete (test of GS.MTRANS bit)

me wait pll0on:

e lwz

r0, ME REG GS (r7)

// read GS register

se btsti r0, ME GS MTRANS

// test the MTRANS bit

// if '1' > wait in loop

se bc

0,2,me wait pll0on

// wait for PLL lock event

pll_wait_lock:

r0, FMPLL0 REG CR (r6) // read FMPLL0.CR register

e lwz

se_btsti r0, FMPLL0 SLOCK

// test LOCK bit

// if '0' > wait in loop

se bc

1,2,pll wait lock

// enable peripherals needed in next startup steps

r0, ME_REG_RUN_PC1 (r7) // read value of ME_RUN_PC1 register

e lwz

r0, ME_RUNPC_DRUN // set DRUN bit r0, ME_REG_RUN_PC1 (r7) // write value back

r0, ME RUNPC DRUN

se bseti

e stw

e li

r0, ME PCTL RUNPC1

// prepare value for PCTL

r0, ME_REG_PCTL_CRC (r7) // set value to ME_PCTL_CRC register

e stb

// select PLL for system clock

r0, ME REG DRUN MC (r7) // read current value of ME DRUN MC reg

e lwz

r0, ME MC SYSCLK PLL

// set PLL as system clock

e or2i

e_stw

r0, ME_REG_DRUN_MC (r7) // write the value back

// mode transition -> DRUN

r0, ME_MCTL_DRUN_R1@h

e_lis

r0, ME_MCTL_DRUN_R1@l

e_or2i

r0, ME_REG_MCTL (r7) // 1. step - normal key

e_stw

```

40/44 DocID024255 Rev 2

AN4253 asm examples

```

r0, ME_MCTL_DRUN R2@h

e lis

e_or2i

r0, ME_MCTL_DRUN R2@l

e_stw

r0, ME REG MCTL (r7) // 2. step - inverted key

// wait for transition to complete (test of GS.MTRANS bit)

me wait sysclk:

e lwz r0, ME REG GS (r7)

// read GS register

se btsti r0, ME GS MTRANS

// test the MTRANS bit

se bc

0,2,me wait pll0on

// if '1' > wait in loop

// check that system clock is FMPLL0

e_and2i. r0, ME_GS_SYSCLK_MASK // get system clock status

// check the value

se_cmpi r0, ME_MC_SYSCLK_PLL

se_bc 1,2,clk_startup_end

// continue if PLL is the system clock

clk_fault_handler:

// fault handler loop, app code needed

se_b .

clk startup end:

```

# A.12 Software Watchdog Timer (SWT) disable

```

e lis

r7, SWT BASE@h

e or2i r7, SWT BASE@l

// base address of SWT module

ro, SWT UNLOCK KEY1

e li

r0, SWT REG SR (r7)

// 1. key

e stw

e li

r0, SWT UNLOCK KEY2

e_stw

r0, SWT_REG_SR (r7)

// 2. key -> soft lock disabled

r0, SWT_REG_CR (r7)

// read CR register

se_bclri r0, 31

// clear WEN bit (disable WEN)

// write modified value back

e stw

r0, SWT_REG_CR (r7)

```

# A.13 Init whole RAM

```

// size of ECC prot. SRAM in words

e lis

r3,__wrs_ramsize_words@h

e_or2i

r3,__wrs_ramsize_words@l

// = size in bytes /4

mtctr

// copy this value to counter gpr

r3

e lis

r7,__wrs_ramstart@h

// r7 is now our ram pointer

r7,__wrs_ramstart@l

// initialized to start of SRAM

e or2i

// and now to 1 word location less

se subi r7,0x04

r3,ECC RAM INIT VALUE@h

e lis

r3,ECC_RAM_INIT_VALUE@1

e_or2i

sram loop:

e_stwu r3,0x04(r7)

// write r3, to r7+4 and update r7

e_bdnz sram_loop

// decr. counter gpr,loop if not 0

```

Further information AN4253

# Appendix B Further information

#### **B.1** Reference documents

• SPC56EL60 32-bit MCU family built on the embedded Power Architecture® (RM0032, Doc ID 15265)

- Using SPC56EL60x fault collection and control unit (FCCU) (AN4124 Doc ID 023294)

- Implementing power-on self tests for SPC56EL60 in locked step (AN3324 Doc ID 18311)

# B.2 Acronyms

Table 1. Acronyms

| Acronym | Name                                                              |

|---------|-------------------------------------------------------------------|

| DPM     | SPC564Lx in Decoupled Parallel mode. Two cores run independently. |

| LSM     | SPC564Lx in Lock Step mode. One core is checked by the other.     |

| RGM     | Reset module                                                      |

| FCCU    | Fault collection unit                                             |

| ECSM    | Error correction status module                                    |

| SSCM    | System Status and Configuration module.                           |

AN4253 Revision history

# **Revision history**

Table 2. Document revision history

| Date        | Revision | Changes             |

|-------------|----------|---------------------|

| 03-Apr-2013 | 1        | Initial release.    |

| 17-Sep-2013 | 2        | Updated Disclaimer. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

44/44 DocID024255 Rev 2