# AN4353 Application note

SPC57xx/SPC58xx: Debug over CAN

#### Introduction

The SPC57xx/SPC58xx family of multicore 32-bit microcontrollers is initially intended for automotive power train applications. It is based on e200 Power Architecture<sup>®</sup> cores.

This application note describes SPC57xx/SPC58xx the new 'Debug over CAN' feature that is implemented on those devices and its implementation is given, background information about the involved modules (MCAN, DMA and JTAGM) is provided, and the sequence of operation is described on a high level. This application note explains how debug messages are handled by the MCAN module. The DMA data transfers between the MCAN and the JTAGM modules are also detailed along with how JTAG traffic is generated. A practical example to implement the theory from the application note is provided. A glossary of terms and definitions is provided in the appendix.

'Debug over CAN' is a new additional feature of the SPC57xx/SPC58xx microcontrollers. The feature is intended to allow debugging of ECUs in the field, where standard debug interfaces like JTAG or Nexus are usually not readily available but access to the CAN interface is possible.

This application note is intended to:

- Explain the feature to the user and give a thorough understanding to enable engineers to develop applications around it

- Detail the capabilities and operation of Debug over CAN

- · Supply example application level initialization code to enable the feature

- Supply example CAN debug traffic to allow tool developers to test the feature

March 2017 DocID025201 Rev 3 1/32

Contents AN4353

# **Contents**

| 1      | Ove       | rview                                          | 5  |

|--------|-----------|------------------------------------------------|----|

|        | 1.1       | MCAN                                           | 6  |

|        | 1.2       | eDMA                                           | 7  |

|        | 1.3       | JTAGM                                          | 7  |

|        | 1.4       | Sequence description                           | 8  |

| 2      | MCA       | AN debug message handling                      | 10 |

| 3      | DMA       | A Transfers between MCAN and JTAGM             | 14 |

|        | 3.1       | Enabling the eDMA trigger from the MCAN        | 14 |

|        | 3.2       | DMA Transfers: JTAGM to MCAN                   | 15 |

|        | 3.3       | MCAN to JTAGM                                  | 15 |

|        | 3.4       | MCAN TX Trigger                                | 15 |

| 4      | JTA       | G Traffic Generation                           | 16 |

|        | 4.1       | JTAG Master (JTAGM)                            | 16 |

|        | 4.2       | JTAG Controller (JTAGC)                        | 18 |

|        |           | 4.2.1 JTAGC Instruction Register               | 18 |

|        |           | 4.2.2 JTAGC TAP Controller                     | 19 |

| 5      | Exar      | mple: Reading the JTAG ID: using SPC57xx       | 23 |

|        | 5.1       | Example Set-up overview                        | 23 |

| 6      | Exar      | mple: Reading the JTAG ID using SPC58xx        | 25 |

|        | 6.1       | Example mainboard and minimodule configuration | 25 |

|        | 6.2       | Example set-up overview                        | 25 |

|        | 6.3       | Example: Reading the JTAG ID                   | 26 |

|        | 6.4       | JTAGC block instructions for SPC58xx           | 27 |

| Apper  | ndix A F  | Further information                            | 30 |

|        | A.1       | Terms and abbreviations                        | 30 |

| Revisi | ion histo | ory                                            | 31 |

AN4353 List of tables

# List of tables

|          | Device list                         | . 5 |

|----------|-------------------------------------|-----|

| Table 2. | Debug Message Filter Definition     | 11  |

|          | DMA Mux - MCAN Allocation           | 14  |

| Table 4. | 6-bit JTAG Instructions for SPC57xx | 21  |

| Table 5. | 6-bit JTAG instructions for SPC58xx | 27  |

|          | Terms and abbreviations             |     |

| Table 7. | Document revision history           | 31  |

List of figures AN4353

# **List of figures**

| Figure 1.  | Debug over CAN sequence                    | 6    |

|------------|--------------------------------------------|------|

| Figure 2.  | Debug over CAN sequence - detailed         | 8    |

| Figure 3.  | Message RAM configuration for SPC57xx      | . 10 |

| Figure 4.  | MCAN RX FIFO Element                       | . 10 |

| Figure 5.  | Standard Message ID Filter Element         | . 11 |

| Figure 6.  | Extended Message ID Filter Element         | . 11 |

| Figure 7.  | Debug Message Handling State Machine (DMS) | . 12 |

| Figure 8.  | MCAN TX Buffer Element                     | . 13 |

| Figure 9.  | JTAGM block diagram                        | . 16 |

| Figure 10. | JTAGM block diagram                        | . 17 |

| Figure 11. | JTAGM to DCI serial interface diagram      | . 17 |

| Figure 12. | JTAGC block diagram                        | . 18 |

| Figure 13. | 6-bit Instruction Register                 | . 19 |

| Figure 14. | TAP controller state machine               | . 20 |

| Figure 15  | Message RAM configuration for SPC58xx      | 29   |

AN4353 Overview

# 1 Overview

'Debug over CAN' is a new feature that will be implemented on various devices of the SPC57xx/SPC58xx family of microcontrollers targeted towards automotive applications. *Table 1* gives an overview of the implementation on different devices:

Devices

SPC57EM80 (cut2)

SPC582B60 CH1M

SPC574K72 (cut2)

SPC58EC80 CH4M

SPC572L64 (cut1)

SPC572L64 (cut1)

Table 1. Device list

'Debug over CAN' allows debug of application hardware where access to the dedicated JTAG/LFAST interface signals is not easily available. The debug over CAN mechanism is intended to provide basic debug functionality with some reduction in bandwidth and features compared to use of the dedicated JTAG or LFAST interfaces.

Use of the CAN interface for debug purposes requires the use of the following resources to be exclusively used for that application:

- MCAN resources: 3 CAN filters need to be configured for the 3 CAN debug messages. Furthermore two dedicated TX elements are needed for the transmission of the debug messages that are to be sent back to the external tool

- DMA resources: a total of six DMA transfers is required per Debug over CAN cycle.

When using the scatter/gather mechanism of the DMA module only one DMA channel is needed, plus 192 byte of flash memory (32 byte for each of the 6 required Transfer Control Descriptors)

Initialization of both MCAN and DMA via software is required, but once this initialization has completed, debugging over CAN is possible without any further software overhead. The initialization can be performed in the boot code.

As the debug over CAN scheme generates internal JTAG messages based on received CAN data, all JTAG clients and included debug resources are accessible. Basic device trace capability is also possible by configuring the device trace hardware to stream to a device overlay/trace RAM, which can be read later using debug over CAN.

Note:

No other (external) JTAG tool / debugger can be connected when using 'Debug over CAN'. If a JTAG tool is connected, the JTAGM is not able to access the DCI resources.

Overview AN4353

The debug over CAN scheme supports the following features:

- Operation through MCAN\_1 or MCAN\_2 interfaces

- Makes use of MCAN debug enhancements

- Debug message selected by filter configuration SFEC/EFEC=111

- Allows debug of hardware where JTAG access is not available

- Debug traffic carried over application CAN bus

- Debug traffic on CAN coexists with application traffic

- No software overhead after initialization

- Flexible selection of CAN identifiers for debug use

- Access to all JTAG debug facilities, including CPU run control

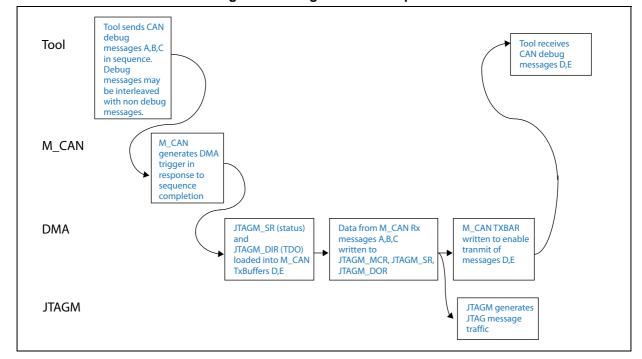

Figure 1 gives a high-level overview of the 'Debug over CAN' sequence and the modules that are involved.

Tool

MCAN

Figure 1. Debug over CAN sequence

In a typical application in the field, an external debug tool sends debug CAN messages to one of the MCAN modules of the MCU. The debug messages have specific identifiers and have to be sent/received in a specific order but may be interleaved with non-debug CAN messages. A mechanism internal to the MCAN module consisting of debug message filtering and a debug message state machine handles the incoming CAN debug messages, stores them correctly in a specified RX Buffer and triggers DMA data transfers between MCAN and JTAGM.

The JTAGM acts as a JTAG master within the device and is used to generate internal JTAG messages. Three CAN messages are necessary to generate the JTAG messages.

The following resources need to be initialized in the application software to use the 'Debug over CAN' feature:

- Three MCAN message filters need to be configured for the debug messages

- The DMA channel mux needs to be enabled for MCAN triggering

- DMA channel(s) need to be programmed for message transfer between MCAN and JTAGM, and to trigger the MCAN transmission to send the debug data back to the tool

#### 1.1 MCAN

The Modular CAN (MCAN) modules are part of the Controller Area Network (CAN) subsystem alongside the Time Triggered CAN (TTCAN) modules and the CAN RAM controller. The MCAN performs communication according to the CAN protocol specification 2.0 part A, B and to CAN FD 1.0.

5/

AN4353 Overview

All functions concerning the handling of messages are implemented by the RX Handler and the TX Handler. The RX Handler manages message acceptance filtering, the transfer of received messages from the CAN Core to the Message RAM as well as providing receive message status information. The TX Handler is responsible for the transfer of transmit messages from the Message RAM to the CAN Core as well as providing transmit status information. Acceptance filtering is implemented by a combination of up to 128 standard filter elements or 64 extended filter elements where each one can be configured as a range, as a bit mask, or as a dedicated ID filter.

MCAN modules \_1 and \_2 can be used for the 'Debug over CAN' application. Its role in this application is to receive and handle the incoming debug messages from an external tool, trigger the DMA transfer sequence, and to send internal debug messages back to the external tool.

Incoming messages are identified as debug messages through a unique CAN message identifier and then stored in a specified location in the receive buffer. After the three CAN debug messages have been received correctly and stored in the debug receive buffer, the MCAN triggers a DMA transfer to send the data to the JTAGM. The MCAN also receives data back from the JTAGM via the DMA. This data is to be sent back to external tool. The CAN reception and transmission of these debug messages has to be configured by the user.

#### 1.2 eDMA

The Enhanced Direct Memory Access (eDMA) module is a highly-programmable data-transfer engine optimized to minimize the intervention from the host processor. It is intended for use in applications where the data size to be transferred is statically known and not defined within the data packet itself.

The eDMA is used to transfer the information between the MCAN module, that sends and receives the debug messages to and from an external tool, and the JTAGM, that creates the internal JTAG traffic.

Six DMA transfers are required to accomplish one full cycle of the 'Debug over CAN' sequence. A sequence of DMA transfers is triggered by one of the MCAN modules in response to receiving debug messages from an external tool. A DMA Mux has to be configured to route the MCAN trigger to a DMA channel, and the DMA has to be enabled for MCAN triggering.

Any of the available DMA channels can be used and it is up to the user to set up Transfer Control Descriptor (TCD). Only the first of the sequence of five DMA transfers is triggered by the MCAN. The subsequent triggers have to be generated from the DMA itself. Both channel linking or the scatter/gather mechanism may be used. It is recommended to use the more resourceful scatter/gather mechanism. However, for ease of understanding, channel linking is the method of choice for the example in this application note. For more details on scatter/gather and channel linking please refer to the device's reference manual and/or related application notes.

#### 1.3 JTAGM

The JTAG Master (JTAGM) is a module that is able to act as JTAG master inside the device. The module has a parallel interface that can exchange data with the debug LFAST module and also a register interface that can be accessed via customer software or in the case of Debug over CAN, via eDMA. Data transferred to this module is used to produce TCK, TMS,

Overview AN4353

TDI and TRST outputs and to accept TDO inputs. The JTAGM is connected in the device to allow these five signals to connect to the JTAG controller (JTAGC) as if the JTAG data is coming from an outside tool. The JTAGM generates all required JTAG scan chains to allow software and high speed serial communication access to all JTAG mapped resources.

## 1.4 Sequence description

Figure 2 gives a detailed overview of the Debug over CAN sequence.

Figure 2. Debug over CAN sequence - detailed

Typically debugging over CAN takes several individual 'Debug over CAN' cycles to accomplish a given task, e.g. a Nexus Read/Write Access. In one 'Debug over CAN' cycle an external tool sends three CAN debug messages A, B and C sequentially to the MCAN of the microcontroller. The debug messages may be interleaved with none debug messages but must be in the correct order. The CAN debug messages are identified by a unique CAN message identifier. When a debug message has been identified it is stored in the user defined RX Buffer in the CAN message RAM.

After the correct reception of debug messages A, B and C the MCAN triggers a DMA transfer. First, the content of the JTAGM status register (JTAGM\_SR) and the JTAGM DATA IN 0 (JTAGM\_DIR0) and JTAGM DATA IN 1 (JTAGM\_DIR1) registers are transferred to the user defined MCAN TX buffer in the CAN message RAM. JTAGM\_DIR0 and \_DIR1 hold the debug data from the previous 'Debug over CAN' cycle and hence needs to be read back before starting a JTAG traffic generation sequence.

After reading back the data from the JTAGM Status and Data In registers, the relevant data from the debug messages A, B and C in the RX Buffer of the CAN message RAM is transferred to the JTAGM's module control register (MCR), status register (SR) and data out registers (DOR0-3).

57

AN4353 Overview

Writing the LSB in DOR3 sets the JTAGM\_DOR3\_SEND bit and internal JTAG traffic is generated depending on the data written to the JTAGM registers.

Parallel to that the MCAN sends the data that has just been stored in TX Buffers back to the external as debug messages D and E. The MCAN transmission is initiated using a DMA transfer to write transmission start bit of the given TX element.

Before starting the next 'Debug over CAN' cycle the external tool waits for the two CAN messages D and E coming back from the MCU's MCAN. This provides enough time for the internal JTAG traffic to be finished and the data in JTAGM\_DIR0 and \_DIR1 has been updated.

# 2 MCAN debug message handling

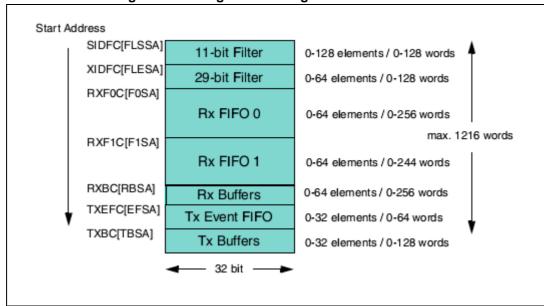

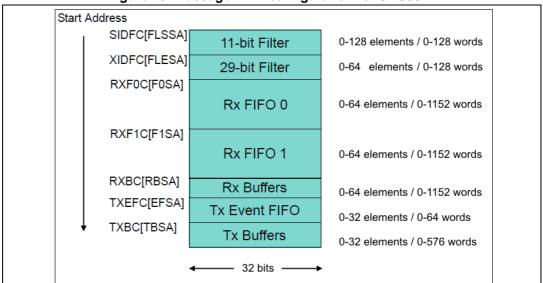

Generally, the CAN modules on the SPC57xx/SPC58xx devices share 16 kByte of common CAN message RAM space. Within this CAN message RAM the user defines an individual area for each of the CAN modules. This area contains the message filters, Rx FIFO blocks, Rx Buffers, a Tx Event FIFO block and Tx Buffers as illustrated in the Figure 3.

Figure 3. Message RAM configuration for SPC57xx

The CAN modules accept CAN messages with matching ID. Any CAN message that is accepted by the CAN module will be stored as an element in either Rx FIFO\_0, Rx FIFO\_1 or Rx Buffer depending on the message filter that is configured for a given message ID. For debug messages the MCAN Rx Elements always follow the 16byte structure shown in *Figure 4*.

19 18 17 16 15 14 13 12 11 10 9 8 21 6 XTD RTR ESI ID[28:0] ANMF BRS EDL res DCL[3:0] R1 FIDX[6:0] RXTS[15:0] DB3[7:0] DB2[7:0] DB1[7:0] DB0[7:0] R3 DB6[7:0] DB5[7:0] DB4[7:0] DB7[7:0]

Figure 4. MCAN RX FIFO Element

The 8 data bytes DB0 to DB7 contain the data that will be transferred to the JTAGM by the DMA. If an extended filter is used the XTD bit is set to '1' and all 29 bits of the ID field are used. For a standard ID bit [28:18] are used for the 11 bit long ID.

In order for the MCAN module to receive/accept messages and handle debug messages as desired the correct filter settings have to be programmed into the filter blocks of the CAN Message RAM Configuration area. A standard filter element is illustrated in *Figure 5* and an extended message filter element is illustrated in *Figure 6*.

10/32 DocID025201 Rev 3

#### Figure 5. Standard Message ID Filter Element

| 31 | 30      | 29 | 28   | 27   | 26 | 25 | 24 | 23 | 22  | 21   | 20   | 19 | 18 | 17 | 16 | 15 | 14 | 13  | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5    | 4    | 3 | 2 | 1 | 0 |

|----|---------|----|------|------|----|----|----|----|-----|------|------|----|----|----|----|----|----|-----|----|----|----|---|---|---|-----|------|------|---|---|---|---|

| ;  | or []oj | SF | EC[2 | ::0] |    |    | -  | -  | SFI | D1[1 | 0:0] |    |    |    |    |    |    | res |    |    |    |   |   |   | SFI | D2[1 | 0:0] | - |   | , |   |

#### Figure 6. Extended Message ID Filter Element

| 31       | 30   | 29   | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15   | 14    | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|------|-------|------|----|----|----|---|---|---|---|---|---|---|---|---|---|

| EF       | EC[2 | 2:0] |    |    |    |    |    |    |    |    |    |    |    |    |    | EFIC | 1[28  | 3:0] |    |    |    |   |   |   |   |   |   |   |   |   |   |

| EET[1-0] | _    | res  |    |    |    |    |    |    |    |    |    |    |    |    |    | EFIC | )2[28 | 3:0] |    |    |    |   |   |   |   |   |   |   |   |   |   |

SFID1/EFID1 is a unique identifier that matches the ID of the received CAN messages. The settings of SFEC/EFEC and SFID2/EFID2 determine how the received message will be handled, i.e. where it will be stored, if it is a debug message and so on.

The setting of SFEC/EFEC determines in which block of the configure message RAM the received CAN message is to be stored. For debug messages the SFEC/EFEC must be set to '111', and then the message is stored in the Rx Buffer. The setting of SFT/EFT will be ignored in this case and will not be discussed in this application note. The bits SFID2[10:9]/EFID2[10:9] decide whether the message will be treated as message A, B or C of the debug message sequence with the following key:

- 01 Debug Message A

- 10 Debug Message B

- 11 Debug Message C

SFID2[5:0]/ EFID2[5:0] defines the offset to the Rx Buffer Start Address RXBC.RBSA for storage of a matching message.

Table 2 gives an overview of typical settings:

**Table 2. Debug Message Filter Definition**

| Debug Message                   | SFID1[10:0]<br>EFID1[28:0] | SFID2[10:9]<br>EFID2[10:9] | SFID2[5:0]<br>EFID2[5:0] |

|---------------------------------|----------------------------|----------------------------|--------------------------|

| Message A, Rx FIFO 1 element 61 | ID debug message A         | 01                         | 00 0000                  |

| Message B, Rx FIFO 1 element 62 | ID debug message B         | 10                         | 00 0001                  |

| Message C, Rx FIFO 1 element 63 | ID debug message C         | 11                         | 00 0010                  |

SFID2/EFID2[8:6] are used to control the filter event pins at the Extension Interface. For more details please refer to the device's reference manual.

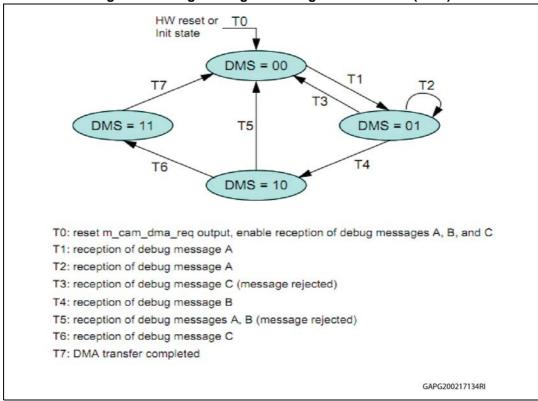

The debug messages A, B and C may be interleaved with other CAN messages but must be received in the correct order. The so called Debug Message Handling State Machine controls that the correct order of debug messages is received, and the status of the status machine is indicated by the DMS bit field in the JTAGM status register (JTAGM\_SR[DMS]). Debug messages that arrive in the wrong order are rejected, and the state machine is reset to its initial state (JTAGM\_SR[DMS] = 00). Figure 7shows a transition diagram of the DMS.

Figure 7. Debug Message Handling State Machine (DMS)

The correct reception of debug message C triggers a DMA transfer (if configured correctly). However, before the debug data is transferred to the JTAGM, the status and the debug data from the previous 'Debug over CAN' cycle must be read back from the JTAGM and transferred to the MCAN to be sent to the external tool.

*Figure 8* illustrates the structure of the 16byte MCAN Tx Buffer element recommended to use for 'Debug over CAN'.

Figure 8. MCAN TX Buffer Element

#### 2.4.3 Tx Buffer Element The Tx Buffers section can be configured to hold dedicated Tx Buffers as well as a Tx FIFO / Tx Queue. In case that the Tx Buffers section is shared by dedicated Tx buffers and a Tx FIFO / Tx Queue, the dedicated Tx Buffers start at the beginning of the Tx Buffers section followed by the buffers assigned to the Tx FIFO or Tx Queue. The Tx Handler distinguishes between dedicated Tx Buffers and Tx FIFO / Tx Queue by evaluating the Tx Buffer configuration TXBC.TFQS and 24 23 16 15 8 7 X X X res ID[28:0] EFC MM[7:0] DLC[3:0] res DB3[7:0] DB2[7:0] DB1[7:0] DB0[7:0] DB7[7:0] DB6[7:0] DB5[7:0] DB4[7:0]

The lower 8byte contain the debug data. The upper 8 byte have to be configured so the external tool receiving the CAN message will successfully accept the CAN message.

Two dedicated Tx Buffer elements should be used for the two CAN messages that are send back to the external CAN debug tool. The data bytes of these Tx Buffer elements are written by the DMA with the data from the JTAGM. It is recommended to initialize the 8 byte of message overhead during the initialization of the 'Debug over CAN' feature.

#### 3 DMA Transfers between MCAN and JTAGM

The DMA transfer sequence is triggered by the MCAN when debug message C has been received successfully. A total of six DMA transfers is required to complete one sequence of debug message transfer between MCAN and JTAGM.

- First, two transfers are required to send data from the JTAGM to the transmit buffers of the MCAN

- Thereafter, three transfers are required to send the new debug messages from the MCAN debug message RX buffer to the JTAGM

- One transfer is required to trigger the MCAN transmission to send data back to the external CAN debug tool

Note:

One additional transfer is required when using the 'Debug over CAN' feature with SPC5744K cut1. Due to an errata the new data flags in the MCAN\_NDAT registers have to be reset by a DMA transfer at the end of each 'Debug over CAN' cycle. It is recommended to do that before triggering the MCAN transmission with the final DMA transfer.

## 3.1 Enabling the eDMA trigger from the MCAN

The modules MCAN\_1 and MCAN\_2 have the DMA trigger mechanism implemented. The DMA Mux must be configured to route MCAN to one of the 16 DMA channels. The *Table 3* lists the DMA Mux and source numbers for the two MCAN modules:

| DMA Mux instance        | Source | MCAN instance |

|-------------------------|--------|---------------|

| DMAMUX_0                | 12     | MCAN_1        |

| DMAMUX_0                | 13     | MCAN_2        |

| DMAMUX_5 <sup>(1)</sup> | 34     | MCAN_1        |

| DMAMUX_5 <sup>(1)</sup> | 35     | MCAN_2        |

**Table 3. DMA Mux - MCAN Allocation**

The DMA Mux instance is configured in the DMACHMUX\_CHCONFIG register. The channel must be enabled and the source of the trigger needs to be selected: The MSB in this 8bit register enable the channel and the six LSBs select the source.

Furthermore, the DMA itself needs to be configured to enable triggering from the same afore-configured DMA Mux channel.

Finally, the Transfer Control Descriptors (TCD) have to be configured. In the TCDs the user defines properties for the DMA transfers like source and destination address and size, channel linking options, and more. Please refer to the example section or the device reference manual for more details.

In order to make the sequence of six DMA transfers happen it is recommended to use channel linking or scatter-gather mechanism.

14/32 DocID025201 Rev 3

<sup>1.</sup> Not available on SPC574K72.

#### 3.2 DMA Transfers: JTAGM to MCAN

The JTAGM status register (SR) and the data in registers (DIR0-1, containing the JTAG TDO data) hold the debug data from the previous messaging cycle and have to be transferred to the MCAN TX buffers.

The following three register contents need to be transferred to the MCAN TX Buffer to form CAN debug messages D and E that will be send back to the external CAN debug tool to complete the 'Debug over CAN' cycle:

- 1. Read JTAGM\_SR -> Write to DB[3:0] of M\_CAN Tx element configured for ID D

- 2. Read JTAGM\_DIR0 -> Write to DB[7:4] of M\_CAN Tx element configured for ID D

- Read JTAGM\_DIR1 -> Write to DB[3:0] of M\_CAN Tx element configured for ID E

#### 3.3 MCAN to JTAGM

The data from the three CAN debug messages has to be transferred to six JTAGM registers to generate the internal JTAG traffic. The following list defines which data portions from the CAN debug messages are transferred to the individual JTAGM registers:

- Read DB[3:0] of M\_CAN Rx element configured for ID A -> Write to JTAGM\_MCR

- 2. Read DB[7:4] of M\_CAN Rx element configured for ID A -> Write to JTAGM\_SR

- 3. Read DB[3:0] of M\_CAN Rx element configured for ID B -> Write to JTAGM\_DOR0

- 4. Read DB[7:4] of M\_CAN Rx element configured for ID B -> Write to JTAGM\_DOR1

- 5. Read DB[3:0] of M\_CAN Rx element configured for ID C -> Write to JTAGM\_DOR2

- 6. Read DB[7:4] of M\_CAN Rx element configured for ID C -> Write to JTAGM\_DOR3

# 3.4 MCAN TX Trigger

The final DMA transfer is used to trigger the MCAN transmission to send data back to the tool.

The MCAN transmission is triggered by writing the transmission start bit of the dedicated Tx Buffer elements in the MCAN\_TXBAR register. Using the DMA this can be done by configuring the address of a constant value as the source address in the TCD, and the MCAN\_TXBAR register as its destination address.

JTAG Traffic Generation AN4353

#### 4 JTAG Traffic Generation

The JTAGM master is used to generate internal JTAG traffic by programming the JTAGM registers to interface with JTAG controller (JTAGC) and the Debug and Calibration Interface (DCI).

## 4.1 JTAG Master (JTAGM)

The JTAG Master (JTAGM) is a module that is able to act as JTAG master inside the device. The module has a parallel interface that can exchange data with another serial communication module (such as the LFAST module) or via customer software writing to the JTAGM registers.

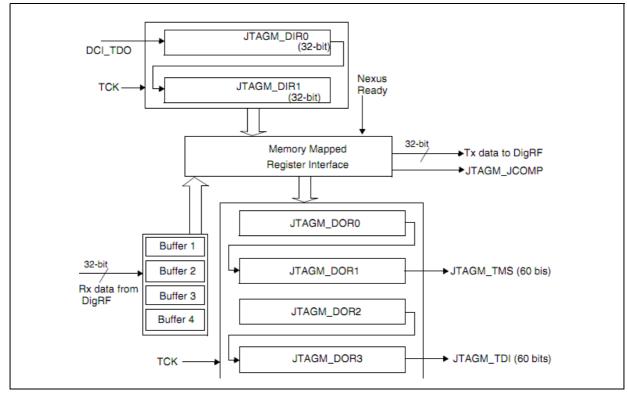

Figure 9 provides a block diagram for the JTAGM.

Figure 9. JTAGM block diagram

The JTAGM has the capability to differentiate between data from software and LFAST. It then sends this data on TDI, TMS and TCK to the Debug and Calibration Interface (DCI). The JTAGM also receives serial data through TDO from the DCI and transfers this data to the software accessible registers or the LFAST through another parallel interface.

57

The JTAGM has the following registers:

- Configuration register (MCR)

- Status register (SR)

- Four data output registers (DOR0 3)

- Two data input registers (DIR0 1)

To generate JTAG signals by software the MCR and the DOR0 – 3 have to be written:

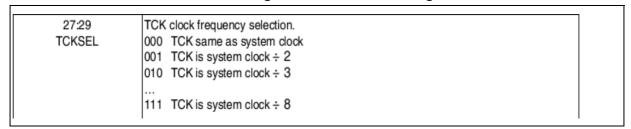

TCK is generated from the device system clock and may be divided depending on the configuration of TCKSEL in JTAGM\_MCR:

Figure 10. JTAGM block diagram

Furthermore the MCR bits jtag\_JCOMP, DTM and evti0\_assert need to be written to '1'.

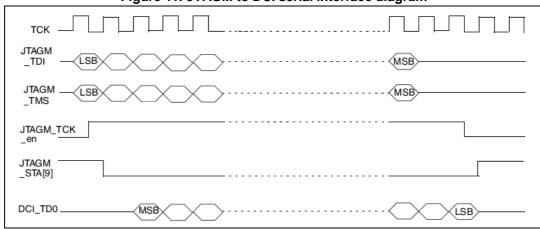

Data is pushed to the modules via a 32-bit wide parallel interface. The data is in the form of 60 bits of **TMS** data and 60 bits of **TDI** data. This data is the logical state to be driven onto the TMS and TDI output pins on each of the 60 TCK cycles. During these 60 TCK cycles, the TDO pin is sampled and the 60 bits of sampled data is transferred to the 32-bit wide module interface. This concept allows complete flexible generation on TMS and TDI data and capture of TDO data. The only limitation is that JTAG signals can only be generated in 60 TCK cycles packets. Extra cycles are wasted in idle cycles at the end of a scan chain.

The TMS signals are generated by the 60 MSBs of JTAGM\_DOR0 + \_DOR1. The TDI signals are generated by the 60 MSBs of JTAGM\_DOR2 + \_DOR3. The LSB in JTAGM\_DOR3 is the 'Send' bit. Writing '1' to it will start the JTAG generation. *Figure 11* shows a diagram of the signals between the JTAGM and the DCI.

Figure 11. JTAGM to DCI serial interface diagram

Bit 'Idle' in JTAGM\_SR indicates if JTAG traffic is ongoing or finished.

JTAG Traffic Generation AN4353

# 4.2 JTAG Controller (JTAGC)

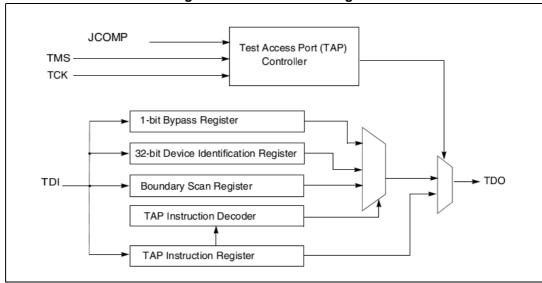

The JTAGC block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. Testing is performed via a boundary scan technique, as defined in the IEEE 1149.1-2001 standard. All data input to and output from the JTAGC block is communicated in serial format. *Figure 12* shows the block of the JTAGC.

Figure 12. JTAGC block diagram

The JTAGC consists of five signals that connect to off-chip and on-chip development tools and allow access to test support functions:

- Test Clock Input (TCK) is an input pin used to synchronize the test logic and control register access through the TAP.

- Test Data Input (TDI) is an input pin that receives serial test instructions and data.

TDI is sampled on the rising edge of TCK

- Test Data Output (TDO) is an output pin that transmits serial output for test instructions and data. TDO is three-stateable and is actively driven only in the Shift-IR and Shift-DR states of the TAP controller state machine

- Test Mode Select (TMS) is an input pin used to sequence the IEEE 1149.1-2001 test control state machine. TMS is sampled on the rising edge of TCK.

- The JCOMP signal provides IEEE 1149.1-2001 compatibility and provides the ability to share the TAP. The JTAGC TAP controller is enabled when JCOMP is set to the JTAGC enable encoding, otherwise the JTAGC TAP controller remains in reset.

#### 4.2.1 JTAGC Instruction Register

The JTAGC block registers are not memory mapped and only accessible through the TAP interface, including data registers and the instruction register.

The JTAGC block uses a 6-bit instruction register as shown in *Figure 13*.

577

Figure 13. 6-bit Instruction Register

|        | 5 | 4 | 3         | 2       | 1 | 0 |

|--------|---|---|-----------|---------|---|---|

| R      | 0 | 0 | 0         | 0       | 0 | 1 |

| W      |   |   | Instructi | on Code |   |   |

| Reset: | 0 | 0 | 0         | 0       | 0 | 1 |

The instruction register allows instructions to be loaded into the block to select the test to be performed or the test data register to be accessed or both. Instructions are shifted in through TDI while the TAP controller is in the Shift-IR state, and latched on the falling edge of TCK in the Update-IR state. The latched instruction value can only be changed in the Update-IR and Test-Logic-Reset TAP controller states. Synchronous entry into the Test-Logic-Reset state results in the IDCODE instruction being loaded on the falling edge of TCK. Asynchronous entry into the Test-Logic-Reset state results in asynchronous loading of the IDCODE instruction. During the Capture-IR TAP controller state, the instruction shift register is loaded with the value 000001b, making this value the register's read value when the TAP controller is sequenced into the Shift-IR state.

For information on the other JTAGC registers please refer to the reference manual.

#### 4.2.2 JTAGC TAP Controller

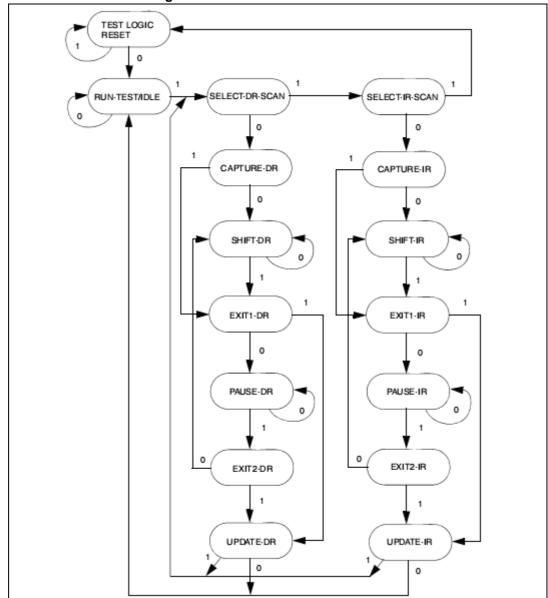

The TAP controller is a synchronous state machine that interprets the sequence of logical values on the TMS pin. *Figure 14* shows the machine's states. The value shown next to each state is the value of the TMS signal sampled on the rising edge of the TCK signal.

JTAG Traffic Generation AN4353

Figure 14. TAP controller state machine

To initialize the JTAGC block and enable access to registers, the following sequence is required:

- Set the JCOMP signal to the JTAGC enable value, thereby enabling the JTAGC TAP controller

- 2. Load the appropriate instruction for the test or action to be performed

20/32

Access to the JTAGC data registers is achieved by loading the instruction register with any of the JTAGC block instructions while the JTAGC is enabled. Instructions are shifted in via the Select-IR- Scan path and loaded in the Update-IR state. At this point, all data register access is performed via the Select-DR-Scan path.

The Select-DR-Scan path is used to read or write the register data by shifting the data in and out (LSB first) during the Shift-DR state. When reading a register, the register value is loaded into the IEEE 1149.1-2001 shifter during the Capture-DR state. When writing a register, the

DocID025201 Rev 3

AN4353 JTAG Traffic Generation

value is loaded from the IEEE 1149.1-2001 shifter to the register during the Update-DR state. When reading a register, there is no requirement to shift out the entire register contents. Shifting may be terminated once the required number of bits has been acquired.

The JTAGC block implements the IEEE 1149.1-2001 defined instructions listed Table 4.

This section gives an overview of each instruction; refer to the IEEE 1149.1-2001 standard for more details. All undefined opcodes are reserved.

Table 4. 6-bit JTAG Instructions for SPC57xx

| DCODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Instruction            | Code[5:0]     | Instruction Summary                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------|---------------------------------------------------|

| and preloading without disturbing functional operation.  SAMPLE  000011  Selects boundary scan register for shifting and sampling without disturbing functional operation.  Selects boundary scan register while applying preloaded values to output pins and asserting functional reset.  Factory debug reserved  000101  Intended for factory debug only.  Factory debug reserved  000110  Intended for factory debug only.  Selects JTAG_PASSWORD register.  HIGHZ  001001  Selects JTAG_PASSWORD register.  Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved  001010  Intended for factory debug only.  Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved  001100  Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR  001110  Enables access to DCI CR register.  ENABLED_DCI_PINCR  001111  Enables access to DCI PINCR register.  ACCESS_AUX_X  100000-111110  Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  ACCESS_AUX_NR_PD  100010  Reserved  Reserved  100010  Reserved  Reserved  100010  Reserved  Reserved  100010  Reserved  Reserved  100010  Reserved  Factory test reserved  100101  Intended for factory test only.  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to the Enables access to E200 Core 0  ACCESS_AUX_CORE_0  101001  Enables access to E200 Core 0                                                                                                                                                                                                                                                                                                                                                                                                          | IDCODE                 | 000001        | Selects device identification register for shift. |

| SAMPILE  Sampling without disturbing functional operation.  EXTEST  D00100  Selects boundary scan register while applying preloaded values to output pins and asserting functional reset.  Factory debug reserved  D00101  Intended for factory debug only.  ENABLED_JTAG_PASSWORD  D00111  Selects JTAG_PASSWORD register.  HIGHZ  D01001  Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved  D01010  Intended for factory debug only.  Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved  D01010  CLAMP  D01100  Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR  D01110  Enables access to DCI CR register.  ENABLED_DCI_PINCR  D01111  Enables access to DCI PINCR register.  ACCESS_AUX_X  D0000-111110  Reserved  ACCESS_AUX_NR_PD  D0000  Reserved  ACCESS_AUX_NR_PD  D0001  Reserved  Reserved  D0010  Reserved  Reserved  D01010  Reserved  Reser | SAMPLE/PRELOAD         | 000010        |                                                   |

| EXTEST 000100 preloaded values to output pins and asserting functional reset.  Factory debug reserved 000101 Intended for factory debug only.  Factory debug reserved 000110 Intended for factory debug only.  ENABLED_JTAG_PASSWORD 000111 Selects JTAG_PASSWORD register.  HIGHZ 001001 Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved 001010 Intended for factory debug only.  CLAMP 001100 Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR 001110 Enables access to DCI CR register.  ENABLED_DCI_PINCR 001111 Enables access to DCI PINCR register.  ACCESS_AUX_X 100000-111110 Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved 100000 Reserved  ACCESS_AUX_NR_PD 100001 Enables access to the NAR TAP controller on PD.  Reserved 100010 Reserved  Reserved 100101 Reserved  Factory test reserved 100101 Intended for factory test only.  ACCESS_AUX_JDC 100110 Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM 100111 Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0 101000 Enables access to E200 Core 0  ACCESS_AUX_CORE_1 101001 Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SAMPLE                 | 000011        |                                                   |

| Factory debug reserved 000110 Intended for factory debug only.  ENABLED_JTAG_PASSWORD 000111 Selects JTAG_PASSWORD register.  HIGHZ 001001 Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved 001010 Intended for factory debug only.  CLAMP 001100 Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR 001110 Enables access to DCI CR register.  ENABLED_DCI_PINCR 001111 Enables access to DCI PINCR register.  ACCESS_AUX_x 100000-111110 Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved 100000 Reserved  ACCESS_AUX_NR_PD 100001 Enables access to the NAR TAP controller on PD.  Reserved 100010 Reserved  Reserved 100101 Reserved  Factory test reserved 100101 Intended for factory test only.  ACCESS_AUX_JDC 100110 Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM 100111 Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0 101000 Enables access to E200 Core 0  ACCESS_AUX_CORE_1 101001 Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EXTEST                 | 000100        | preloaded values to output pins and asserting     |

| ENABLED_JTAG_PASSWORD  001111  Selects JTAG_PASSWORD register.  Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved  001010  Intended for factory debug only.  CLAMP  001100  Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR  001110  Enables access to DCI CR register.  ENABLED_DCI_PINCR  001111  Enables access to DCI PINCR register.  ACCESS_AUX_X  100000-111110  Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  100000  Reserved  ACCESS_AUX_NR_PD  100010  Reserved  Reserved  100010  Reserved  Reserved  100101  Reserved  Factory test reserved  100101  Intended for factory test only.  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to the HSM core TAP controller.  Enables access to the HSM core TAP controller.  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Factory debug reserved | 000101        | Intended for factory debug only.                  |

| HIGHZ  Donoton Selects bypass register while tree-stating all output pins and asserting functional reset.  Factory debug reserved  Donoton Intended for factory debug only.  Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR  Donoton Donoton Enables access to DCI CR register.  ENABLED_DCI_PINCR  Donoton Donoton Enables access to DCI PINCR register.  ACCESS_AUX_X  Donoton Intended for factory debug only.  Selects bypass register while applying preloaded values to output pins and asserting functional reset.  Enables access to DCI CR register.  Enables access to DCI PINCR register.  ACCESS_AUX_X  Donoton Intended some the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  ACCESS_AUX_NR_PD  Donoton Enables access to the NAR TAP controller on PD.  Reserved  Reserved  Donoton Reserved  Reserved  Donoton Reserved  Reserved  Donoton Reserved  Factory test reserved  Donoton Reserved  Factory test reserved  Donoton Reserved  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_JDC  Donoton Enables access to the HSM core TAP controller.  Enables access to E200 Core 0  ACCESS_AUX_CORE_0  Donoton Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Factory debug reserved | 000110        | Intended for factory debug only.                  |

| Factory debug reserved  O01010  Intended for factory debug only.  Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR  O01110  Enables access to DCI CR register.  ENABLED_DCI_PINCR  O01111  Enables access to DCI PINCR register.  ACCESS_AUX_X  100000-111110  Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  100000  Reserved  ACCESS_AUX_NR_PD  100001  Enables access to the NAR TAP controller on PD.  Reserved  100010  Reserved  Reserved  100011  Reserved  Factory test reserved  100100  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101001  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ENABLED_JTAG_PASSWORD  | 000111        | Selects JTAG_PASSWORD register.                   |

| CLAMP  O01100  Selects bypass register while applying preloaded values to output pins and asserting functional reset.  ENABLED_DCI_CR  O01110  Enables access to DCI CR register.  ENABLED_DCI_PINCR  O01111  Enables access to DCI PINCR register.  ACCESS_AUX_x  100000-111110  Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  100000  Reserved  ACCESS_AUX_NR_PD  100001  Reserved  Reserved  100010  Reserved  Reserved  100011  Reserved  Reserved  100100  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  ACCESS_AUX_CORE_0  101001  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | HIGHZ                  | 001001        |                                                   |

| Values to output pins and asserting functional reset.  ENABLED_DCI_CR  ENABLED_DCI_PINCR  001111  Enables access to DCI CR register.  ENABLED_DCI_PINCR  001111  Enables access to DCI PINCR register.  ACCESS_AUX_X  100000-111110  Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  100000  Reserved  ACCESS_AUX_NR_PD  100001  Enables access to the NAR TAP controller on PD.  Reserved  100010  Reserved  Reserved  100011  Reserved  Reserved  100100  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Factory debug reserved | 001010        | Intended for factory debug only.                  |

| ENABLED_DCI_PINCR  001111  Enables access to DCI PINCR register.  ACCESS_AUX_X  100000-111110  Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  100000  Reserved  ACCESS_AUX_NR_PD  100001  Enables access to the NAR TAP controller on PD.  Reserved  100010  Reserved  Reserved  100011  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CLAMP                  | 001100        |                                                   |

| ACCESS_AUX_X  100000-111110  Grants one the auxiliary TAP controllers ownership of the TAP as shown in the cells below.  Reserved  100000  Reserved  ACCESS_AUX_NR_PD  100001  Enables access to the NAR TAP controller on PD.  Reserved  100010  Reserved  Reserved  100011  Reserved  Reserved  100100  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ENABLED_DCI_CR         | 001110        | Enables access to DCI CR register.                |

| the TAP as shown in the cells below.  Reserved  100000  Reserved  ACCESS_AUX_NR_PD  100001  Enables access to the NAR TAP controller on PD.  Reserved  100010  Reserved  Reserved  100011  Reserved  Reserved  100100  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ENABLED_DCI_PINCR      | 001111        | Enables access to DCI PINCR register.             |

| ACCESS_AUX_NR_PD  100001 Enables access to the NAR TAP controller on PD.  Reserved  100010 Reserved  Reserved  100011 Reserved  Reserved  100100 Reserved  Factory test reserved  100101 Intended for factory test only.  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111 Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000 Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001 Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ACCESS_AUX_x           | 100000-111110 |                                                   |

| Reserved  Reserved  Reserved  100010  Reserved  Reserved  100100  Reserved  100100  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reserved               | 100000        | Reserved                                          |

| Reserved  Reserved  Reserved  100100  Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ACCESS_AUX_NR_PD       | 100001        | Enables access to the NAR TAP controller on PD.   |

| Reserved  Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Reserved               | 100010        | Reserved                                          |

| Factory test reserved  100101  Intended for factory test only.  ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reserved               | 100011        | Reserved                                          |

| ACCESS_AUX_JDC  100110  Enables access to the JDC TAP controller to access the HSM challenge and response registers.  ACCESS_AUX_HSM  100111  Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0  101000  Enables access to E200 Core 0  ACCESS_AUX_CORE_1  101001  Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reserved               | 100100        | Reserved                                          |

| ACCESS_AUX_JDC the HSM challenge and response registers.  ACCESS_AUX_HSM 100111 Enables access to the HSM core TAP controller.  ACCESS_AUX_CORE_0 101000 Enables access to E200 Core 0  ACCESS_AUX_CORE_1 101001 Enables access to E200 Core 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Factory test reserved  | 100101        | Intended for factory test only.                   |