# AN4437 Application note

# L9678 user configurable airbag

### Introduction

This document explains the features and benefits of the L9678 device, target for entry level airbag system, with flexible configuration for power supply and management.

The configuration of the device depends on the specific application.

Guidelines for different operating modes of the device are provided.

Meaning features are the flexible configuration, availability of different voltage regulators, two PSI-5 sensor interfaces, four DC sensors interface, two GPOs, high or low level diagnostic test, arming managed following both internal or external safing engine, deployment profile selectable, 32 bit SPI communication.

Note:

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

September 2016 DocID025845 Rev 3 1/198

# **Contents**

| 1 | Des | ription          |                                |

|---|-----|------------------|--------------------------------|

|   | 1.1 | Main features    | g                              |

|   | 1.2 | Application ov   | erview                         |

| 2 | Pow | erup             |                                |

|   | 2.1 | Power off        |                                |

|   |     | 2.1.1 From       | power off to sleep mode        |

|   | 2.2 | Sleep mode       |                                |

|   |     | 2.2.1 From       | sleep to active mode           |

|   |     | 2.2.2 From       | active back to sleep mode14    |

|   | 2.3 | Active mode      |                                |

|   |     | 2.3.1 From       | active to passive mode         |

|   |     | 2.3.2 From       | active back to sleep mode16    |

|   | 2.4 | Passive mode     |                                |

|   |     | 2.4.1 COVE       | RACT17                         |

|   |     | 2.4.2 From       | passive back to active mode19  |

|   |     | 2.4.3 From       | passive back to sleep mode19   |

|   |     | 2.4.4 From       | passive back to power off mode |

| 3 | Pow | er up and pow    | ver down                       |

|   | 3.1 | Power up seq     | uence 21                       |

|   | 3.2 | Power down s     | sequence                       |

| 4 | Ope | ative state .    |                                |

|   | 4.1 | Initialization - | Watchdog function              |

|   |     | 4.1.1 WATO       | CHDOG INITIAL                  |

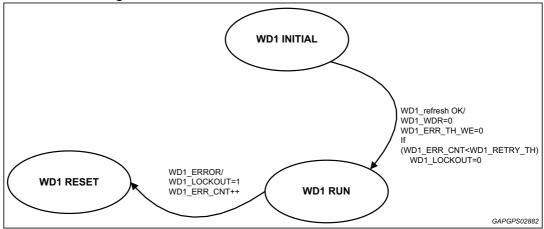

|   |     | 4.1.2 WD1        | INITIAL - WD1 RESET28          |

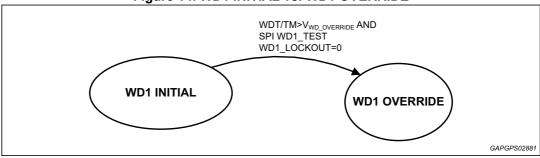

|   |     | 4.1.3 WD1        | INITIAL - WD1 OVERRIDE         |

|   |     | 4.1.4 WD1        | INITIAL - WD1 RUN30            |

|   |     | 4.1.5 WD1        | RUN - WD1 TEST                 |

|   | 4.2 | Diagnostic       |                                |

|   | 4.3 | SAFING           |                                |

|   | 4.4 | SCRAP            |                                |

AN4437 Contents

|             | 4.5   | ARMIN    | IG                                                      | 34       |

|-------------|-------|----------|---------------------------------------------------------|----------|

| 5           | Volta | age regi | ılators                                                 | 35       |

|             | 5.1   | Interna  | ıl voltage regulators                                   | 35       |

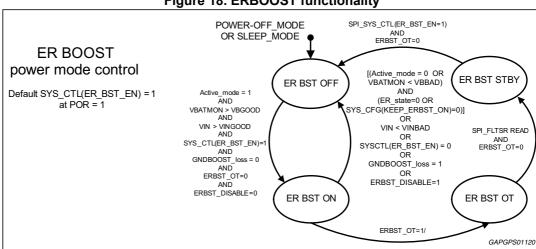

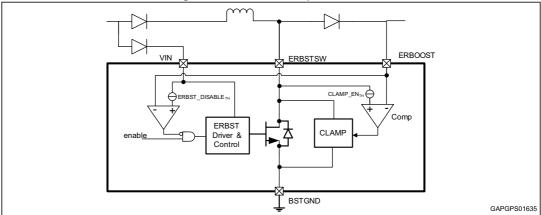

|             | 5.2   | ERBO     | OST                                                     | 35       |

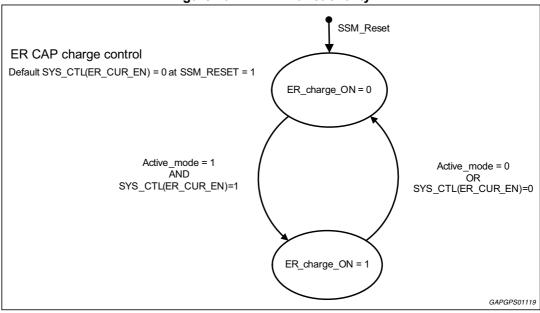

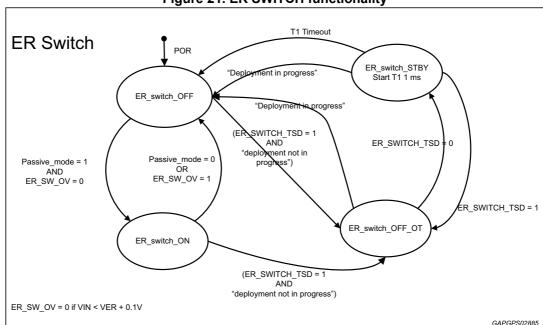

|             | 5.3   | ER CH    | IARGE - ER SWITCH                                       | 38       |

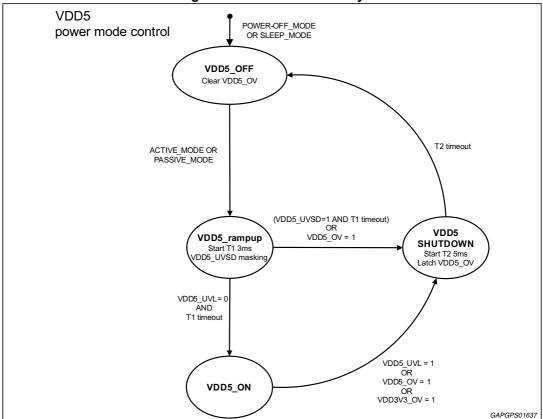

|             | 5.4   | VDD5     | linear regulator                                        | 41       |

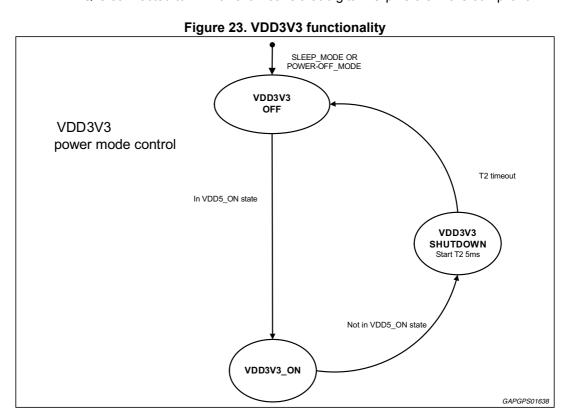

|             | 5.5   | VDD3\    | /3 linear regulator                                     | 43       |

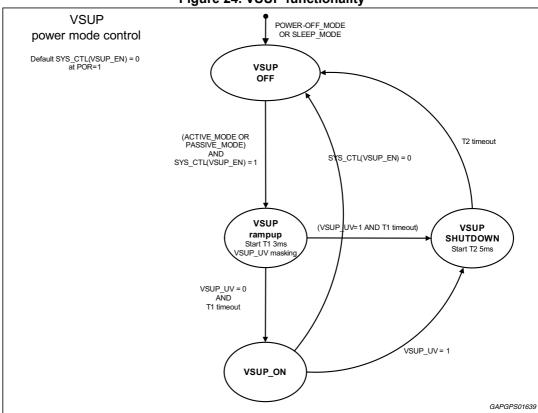

|             | 5.6   | VSUP     | Linear regulator (available for L9678S version)         | 45       |

|             | 5.7   |          | near regulator                                          |          |

|             | 5.8   |          | Г                                                       |          |

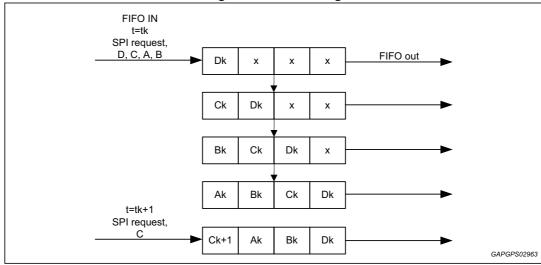

| 6           | SPI   |          |                                                         | 51       |

| 7           | SAF   | ING      |                                                         | 64       |

|             | 7.1   | SPI se   | nsor data decoding - Configuration                      | 65       |

|             | 7.2   | SPI se   | nsor data decoding - MASK                               | 73       |

|             | 7.3   | SPI se   | nsor data decoding - Example arming without on board se | ensor 78 |

|             | 7.4   | Additio  | nal communication line (ACL)                            | 81       |

| 8           | Dep   | loyment  |                                                         | 82       |

|             | 8.1   | Deploy   | ment requirement                                        | 82       |

|             |       | 8.1.1    | ARMING state                                            | 85       |

|             |       | 8.1.2    | DIAGNOSTIC state                                        | 86       |

|             |       | 8.1.3    | SAFING state                                            | 87       |

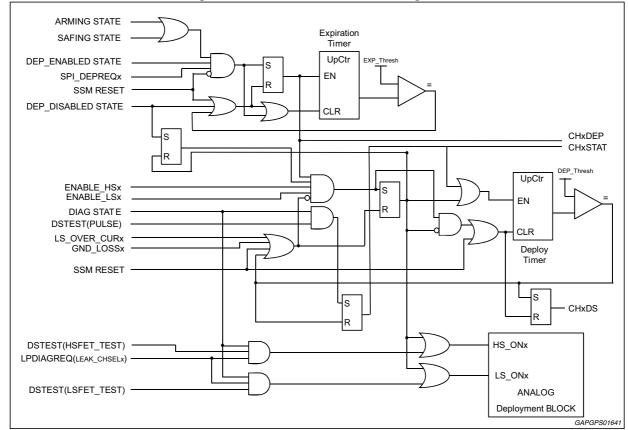

|             |       | 8.1.4    | DEPLOYMENT driver                                       |          |

|             | 8.2   | Deploy   | ment driver protection                                  | 92       |

|             | 8.3   | Deploy   | ment driver example                                     | 93       |

| 9           | Diag  | nostic   |                                                         | 98       |

|             | 9.1   | Low le   | vel                                                     | 100      |

|             |       | 9.1.1    | High voltage leak test, oxide isolation IC-car chassis  | 101      |

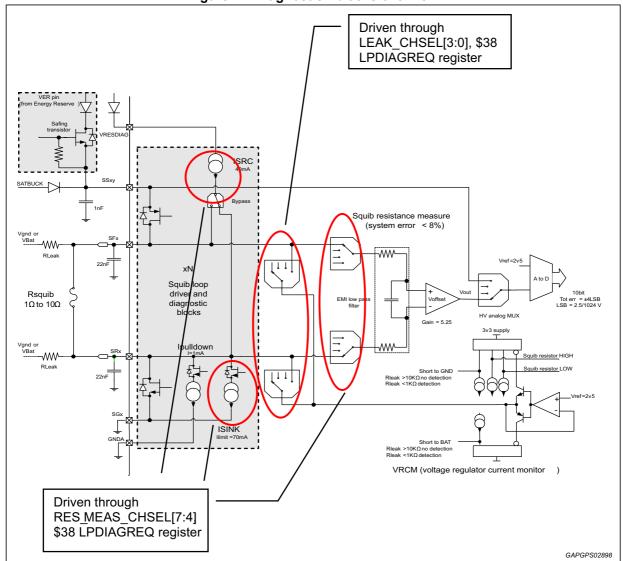

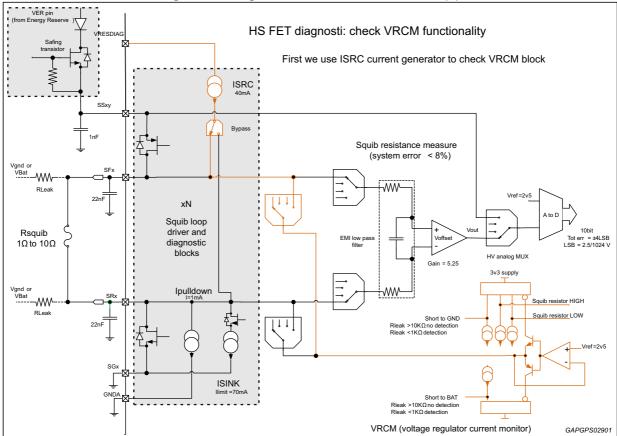

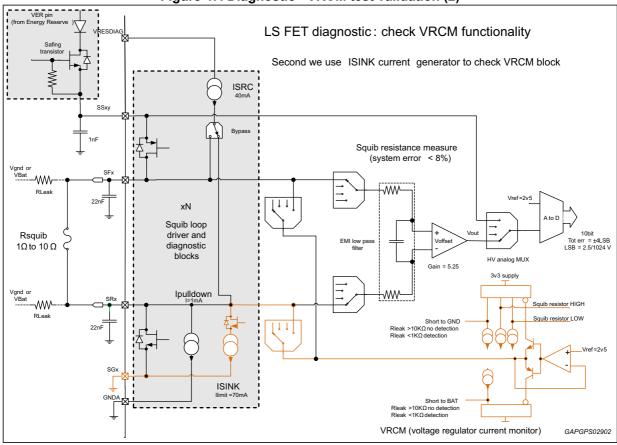

|             |       | 9.1.2    | VRCM test validation                                    |          |

|             |       | 9.1.3    | Leakage test - High side                                |          |

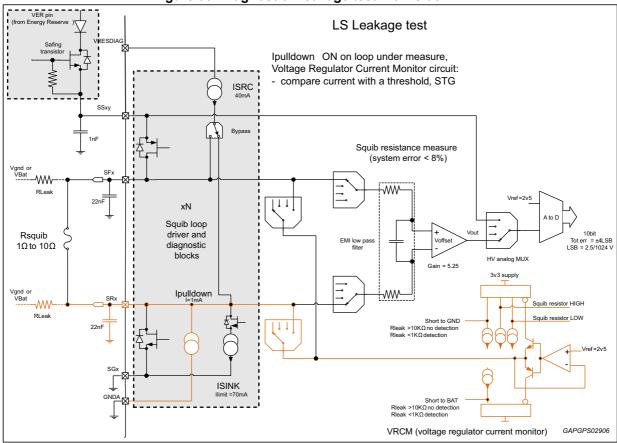

|             |       | 9.1.4    | Leakage test - low side                                 |          |

|             |       | 9.1.5    | Leakage test - low side IPD                             | 111      |

| <b>5</b> // |       |          | DocID025845 Rev 3                                       | 3/198    |

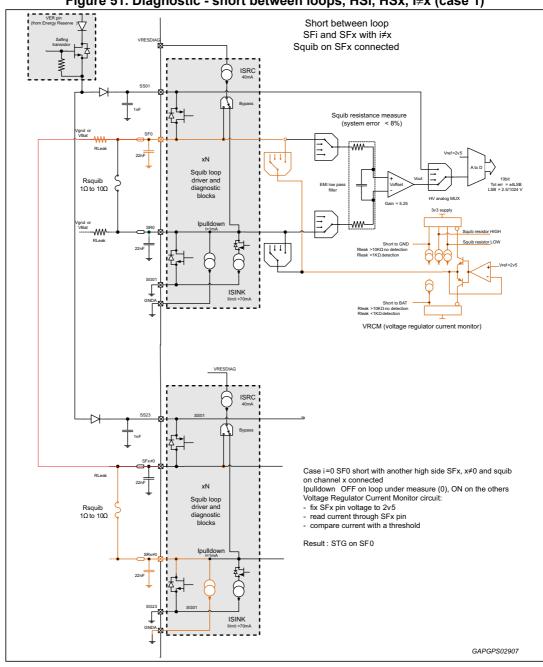

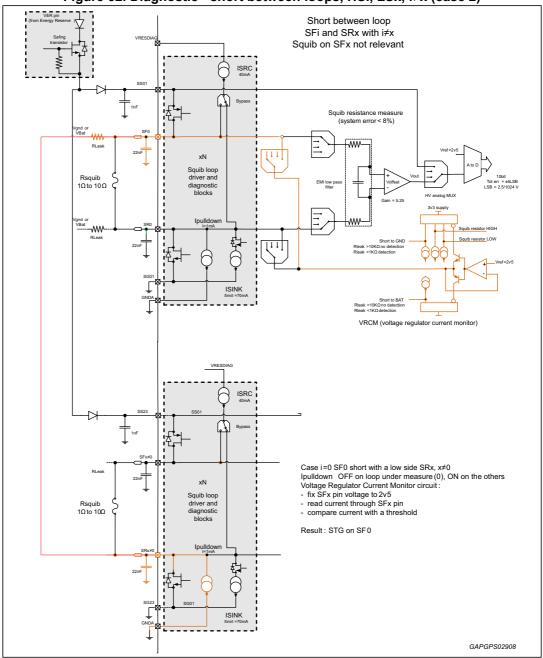

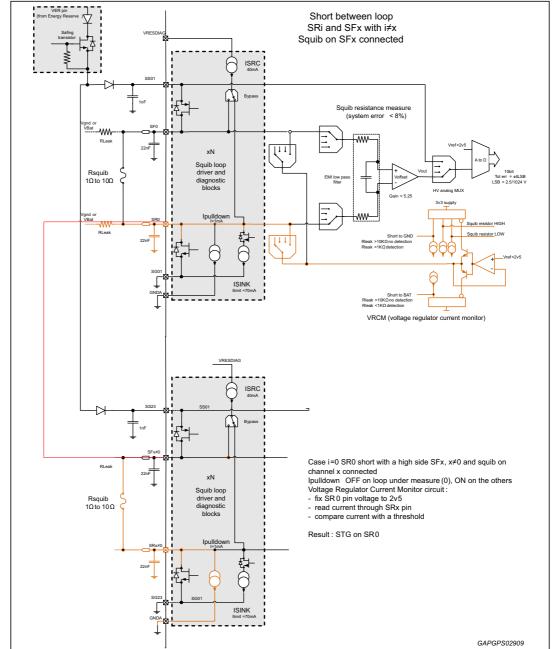

|    |       | 9.1.6    | Short between loops                     | . 113 |

|----|-------|----------|-----------------------------------------|-------|

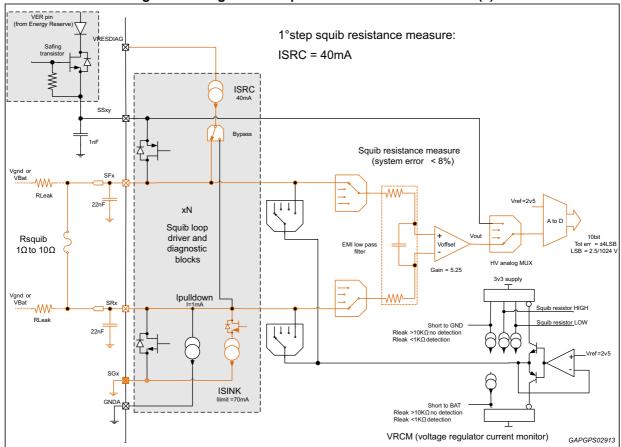

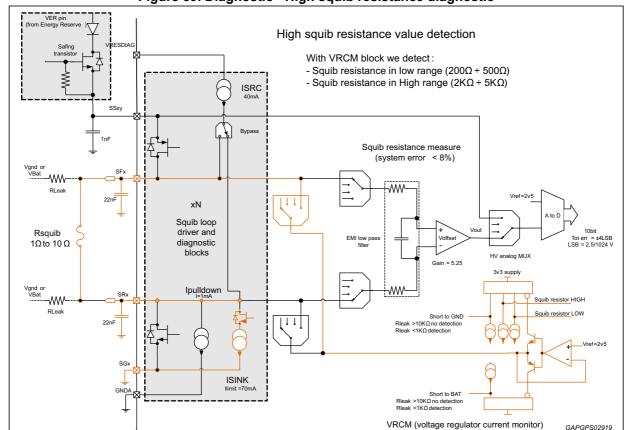

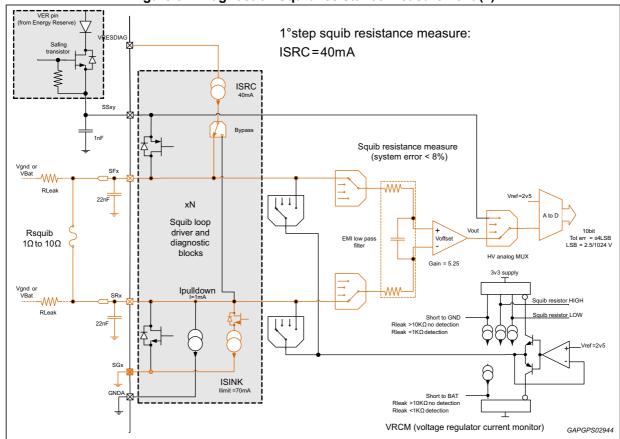

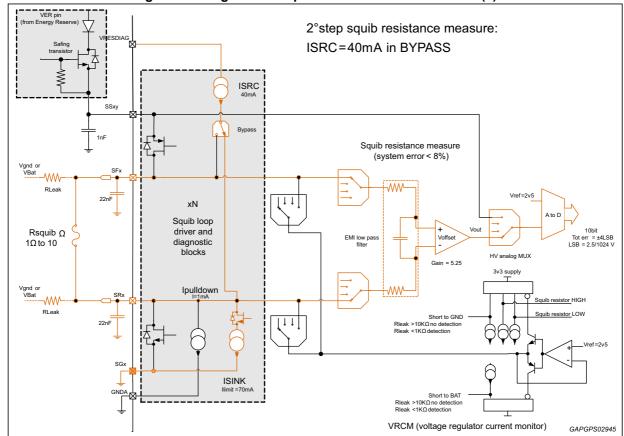

|    |       | 9.1.7    | Squib resistance measurement            | . 120 |

|    |       | 9.1.8    | High squib resistance diagnostic        | . 125 |

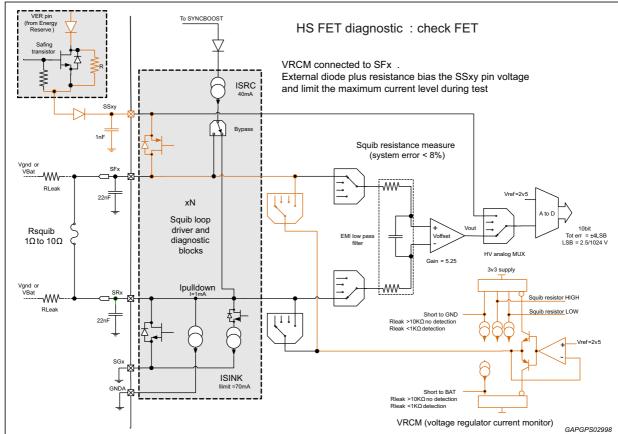

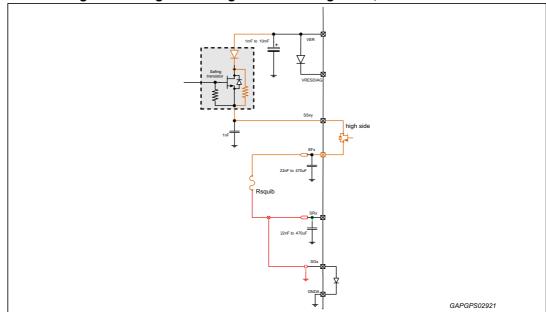

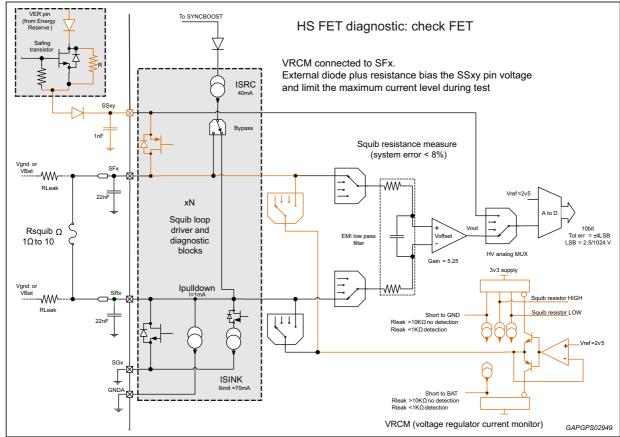

|    |       | 9.1.9    | High side FET diagnostic                | . 128 |

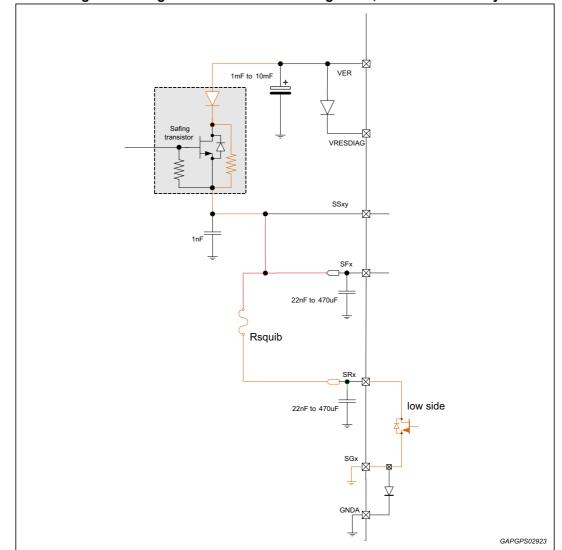

|    |       | 9.1.10   | Low side FET diagnostic                 | . 131 |

|    |       | 9.1.11   | LOSS of Ground                          | . 135 |

|    |       | 9.1.12   | Safing FET diagnostic                   | . 136 |

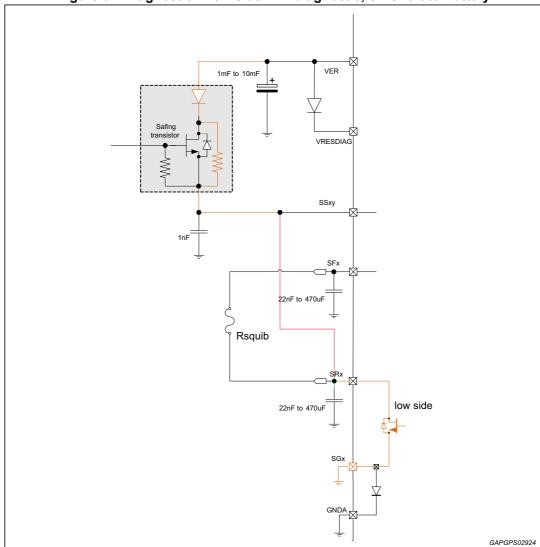

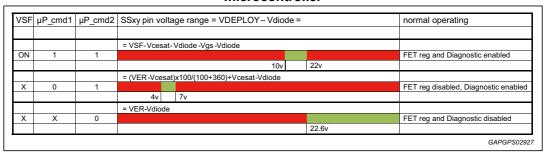

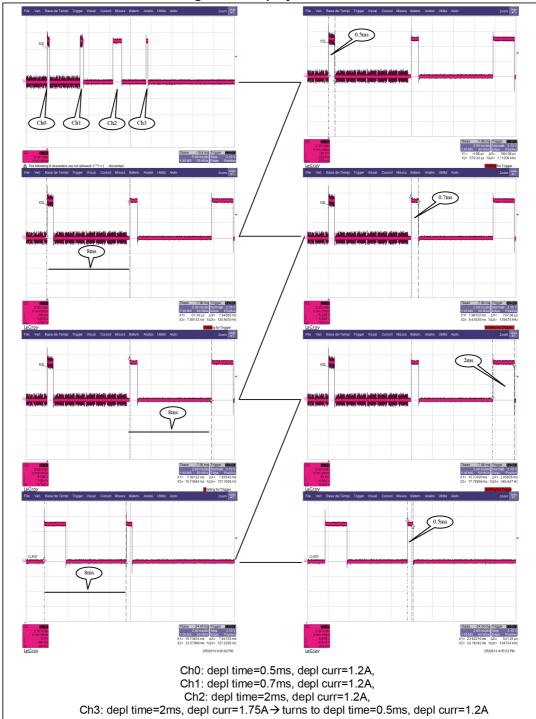

|    |       | 9.1.13   | Deployment time diagnostic              | . 139 |

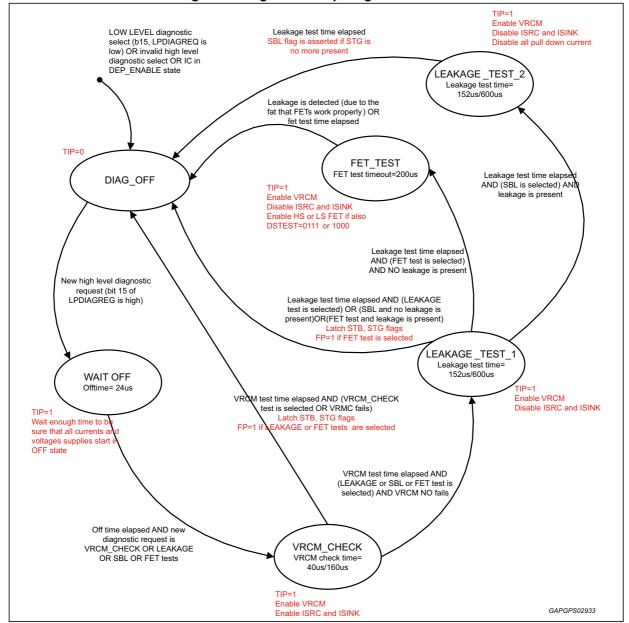

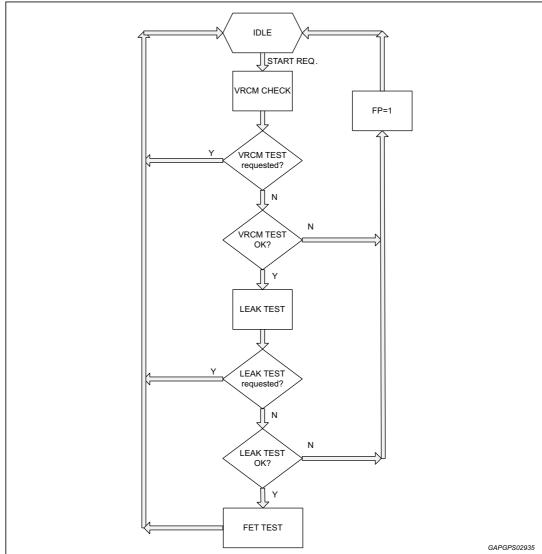

|    | 9.2   | High le  | evel                                    | 142   |

|    |       | 9.2.1    | VRCM check - High side                  | . 146 |

|    |       | 9.2.2    | VRCM check - Low side                   | . 148 |

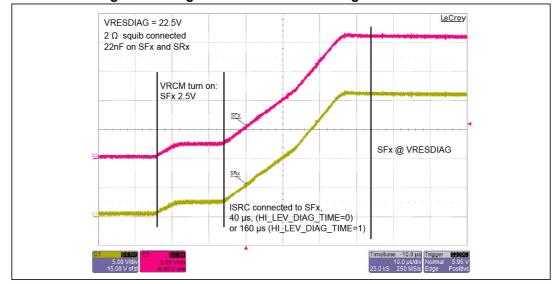

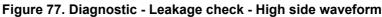

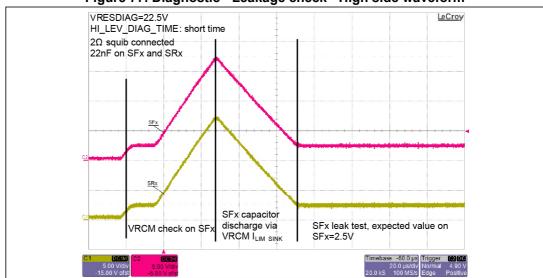

|    |       | 9.2.3    | Leakage check - High side               | . 150 |

|    |       | 9.2.4    | Leakage check - Low side                | . 153 |

|    |       | 9.2.5    | Short between loops                     | . 154 |

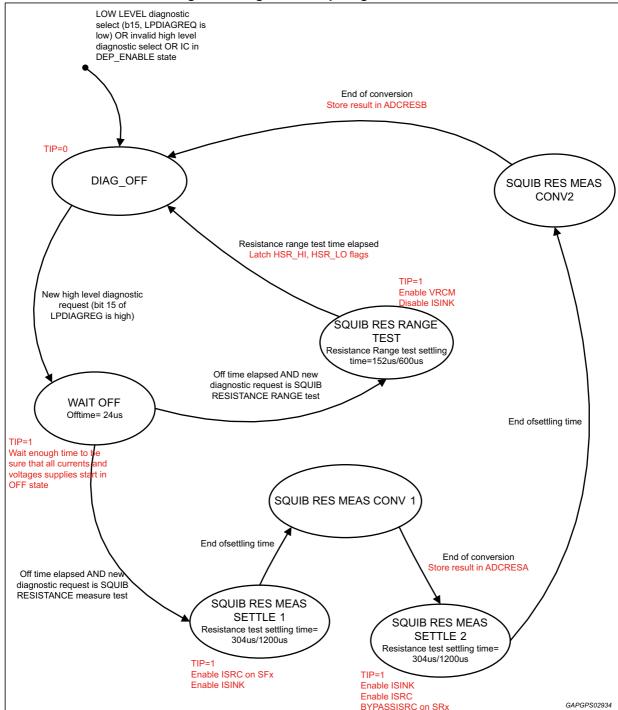

|    |       | 9.2.6    | Squib resistance range                  | . 155 |

|    |       | 9.2.7    | Squib resistance measurement            | . 157 |

|    |       | 9.2.8    | High side FET diagnostic                | . 161 |

|    |       | 9.2.9    | Low side FET diagnostic                 | . 163 |

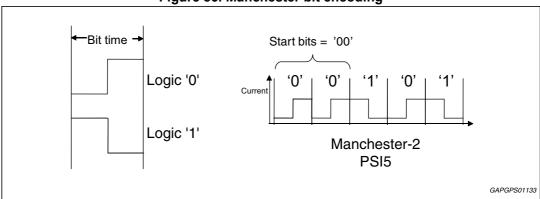

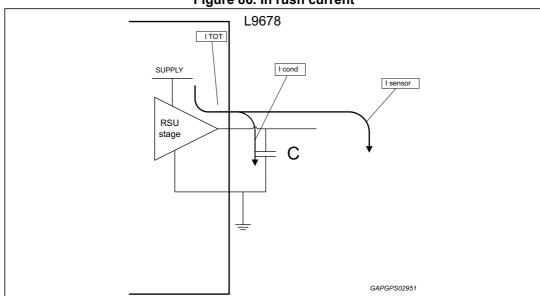

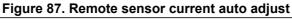

| 10 | Rem   | ote sen  | sor interface - L9678-S only            | 166   |

|    | 10.1  | Fault p  | protection, short to GND, current limit | 170   |

|    | 10.2  | Fault p  | protection, short to battery            | 170   |

|    | 10.3  | -        | link                                    |       |

|    | 10.4  |          | ge to battery / open condition          |       |

|    | 10.5  | •        | ge to ground                            |       |

|    | 10.6  | •        | al shut-down                            |       |

|    | 10.7  |          | ester decoding                          |       |

|    | 10.7  |          | rrent auto adjust                       |       |

|    | 10.0  | mp cu    | ineni auto aujust                       | 173   |

| 11 | DC s  | ensor i  | nterface                                | 175   |

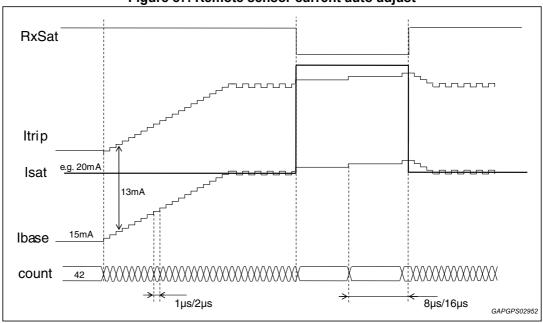

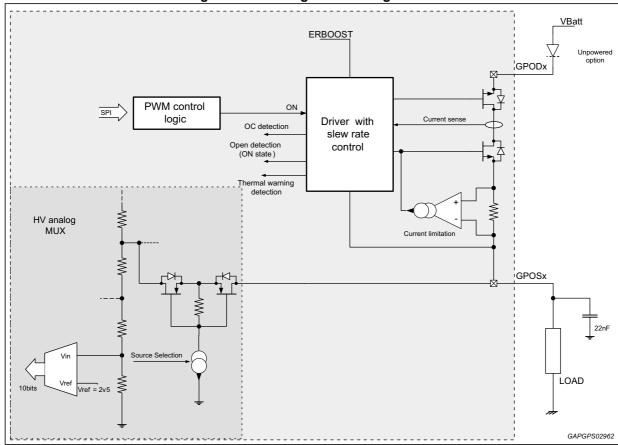

| 12 | GPO   | drivers  | ·                                       | 182   |

| 13 | ISO9  | 141 traı | nsceiver                                | 186   |

| 14 | Sunt  | om volt  | age diagnostic                          | 107   |

| 14 | Syste | em volt  | aye ulayılusılu                         | 10/   |

| AN4437  |                                | Contents |

|---------|--------------------------------|----------|

|         | 14.1 ADC algorithm             |          |

| 15      | Temperature sensor             |          |

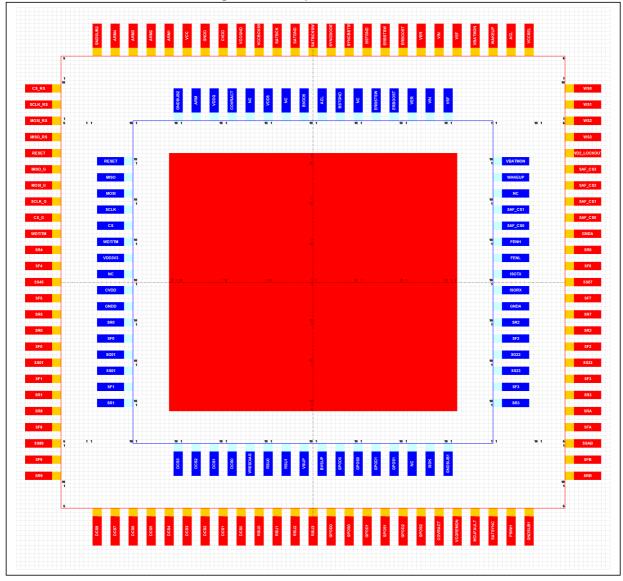

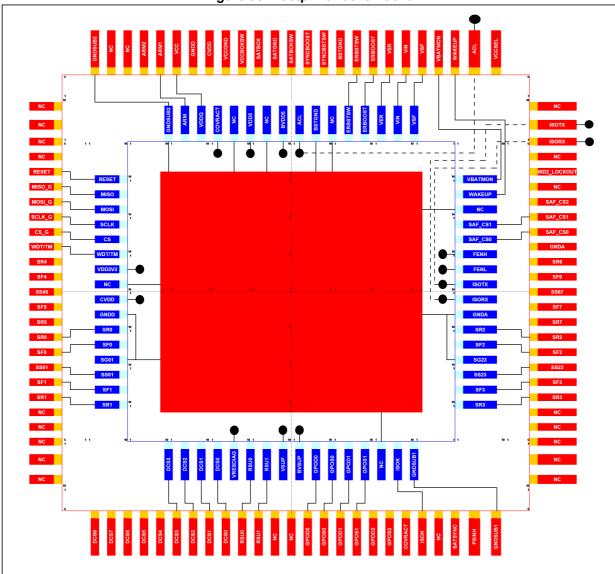

| 16      | Footprint                      | 191      |

| Append  | dix A Energy reserve capacitor | 193      |

| Revisio | on history                     |          |

List of tables AN4437

# List of tables

| Table 1.  | VER measurement of the value ratio ADC                | 15    |

|-----------|-------------------------------------------------------|-------|

| Table 2.  | Blocks disabled in each IC state                      | 19    |

| Table 3.  | Global SPI register map                               | 51    |

| Table 4.  | Deployment driver example                             |       |

| Table 5.  | VRESDIAG and SFx measurement of the value ratio ADC   |       |

| Table 6.  | Squib x resistance measurement of the value ratio ADC | . 121 |

| Table 7.  | VSF and SS measurement of the value ratio ADC         | . 137 |

| Table 8.  | Resistance measurement of the value ratio ADC         | . 159 |

| Table 9.  | RSUx measurement to obtain the voltage value          | . 171 |

| Table 10. | GPODx and GPOSx measurement of the value ratio ADC    | . 185 |

| Table 11. | Voltage measurements                                  | . 188 |

| Table 12  | Document revision history                             |       |

AN4437 List of figures

# List of figures

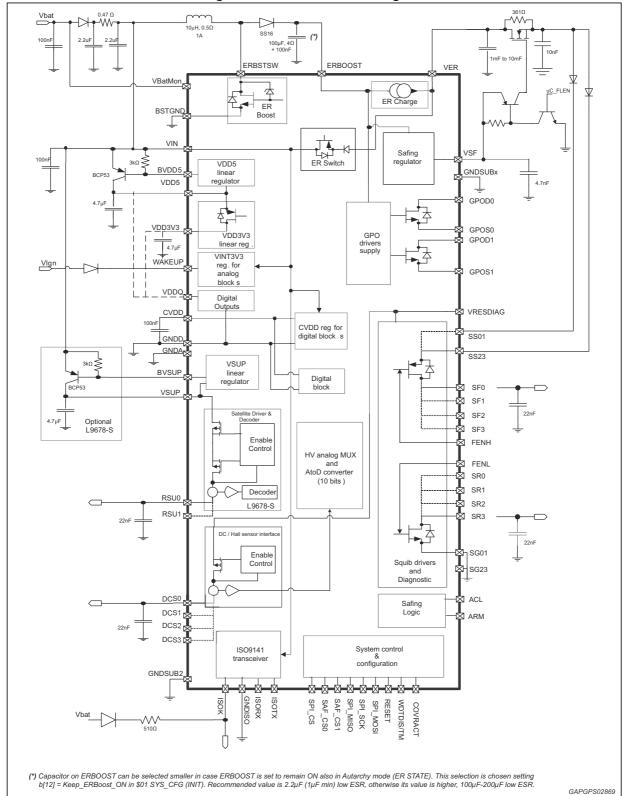

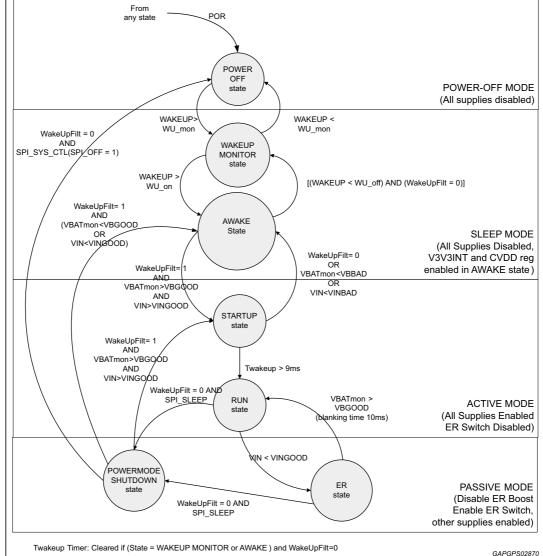

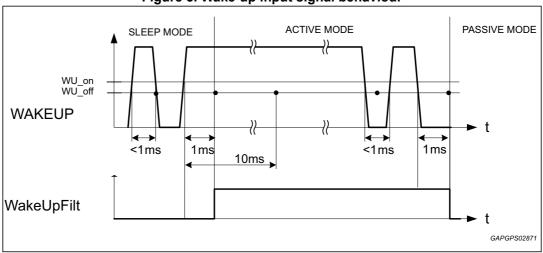

| Figure 2.         Device states         12           Figure 3.         Wake-up input signal behaviour         15           Figure 5.         WAKEUP filter time         17           Figure 5.         COVRACT external components usage         18           Figure 7.         Example of power up sequence - WAKEUP then WAKEUP         21           Figure 7.         Example of power up sequence - WAKEUP then VBAT         22           Figure 8.         Microcontroller drives the power shutdown.         23           Figure 9.         Device functionality.         24           Figure 10.         Device functionality.         25           Figure 11.         Watchdog functionality.         26           Figure 12.         WD1 INITIAL.         28           Figure 13.         WD1 INITIAL vs. WD1 POYERRIDE         29           Figure 15.         WD1 INITIAL vs. WD1 POYERRIDE         29           Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 20.         ER CAP functionality         39           Figure 21.         ER SWITCH functionality         40           Figure 22.         VD55 f                                                                                     | Figure 1.  | Functional block diagram                        | . 11 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|------|

| Figure 4.         WAKEUP filter time.         17           Figure 5.         COVRACT external components usage         18           Figure 6.         Example of power up sequence - VBAT then WAKEUP         21           Figure 7.         Example of power up sequence - WAKEUP then VBAT         22           Figure 8.         Microcontroller drives the power shutdown.         23           Figure 9.         Power shutdown due to low or lost battery.         24           Figure 10.         Device functionality.         26           Figure 12.         WD1 INITIAL.         25           Figure 13.         WD1 INITIAL - WD1 RESET.         28           Figure 14.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET.         28           Figure 15.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET.         30           Figure 16.         WATCHDOG service.         31           Figure 17.         WD1 RESET - WD1 TEST.         32           Figure 19.         ERBOOST functionality.         36           Figure 20.         ER CAP functionality.         36           Figure 21.         ER SWITCH functionality.         40           Figure 23.         VDD3V3 functionality.         42           Figure 24.         VSUP functionality.         46                                                                              | Figure 2.  | Device states                                   | . 12 |

| Figure 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 3.  | Wake-up input signal behaviour                  | . 15 |

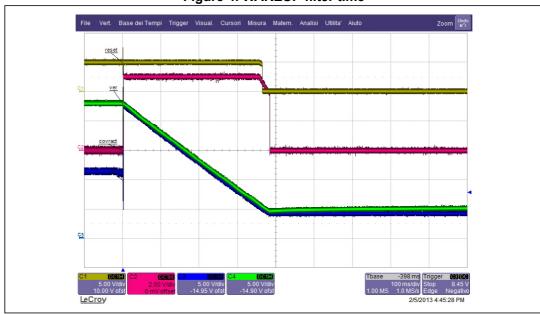

| Figure 6.         Example of power up sequence - WAKEUP then WAKEUP         21           Figure 7.         Example of power up sequence - WAKEUP then VBAT         22           Figure 8.         Microcontroller drives the power shutdown.         23           Figure 9.         Power shutdown due to low or lost battery.         24           Figure 10.         Device functionality.         25           Figure 11.         Watchdog functionality.         25           Figure 12.         WD1 INITIAL - WD1 RESET.         28           Figure 13.         WD1 INITIAL - WD1 RESET.         28           Figure 14.         WD1 INITIAL vs. WD1 VS. WD1 RESET.         30           Figure 15.         WD1 INITIAL vs. WD1 RESET.         30           Figure 17.         WD1 RESET - WD1 TEST.         32           Figure 18.         ERBOOST functionality.         36           Figure 29.         ER CAP functionality.         39           Figure 20.         ER CAP functionality.         40           Figure 21.         ER SWITCH functionality.         40           Figure 22.         VDD5 functionality.         42           Figure 23.         VD303 functionality.         42           Figure 24.         VSIP enable.         47           Figur                                                                            | Figure 4.  |                                                 |      |

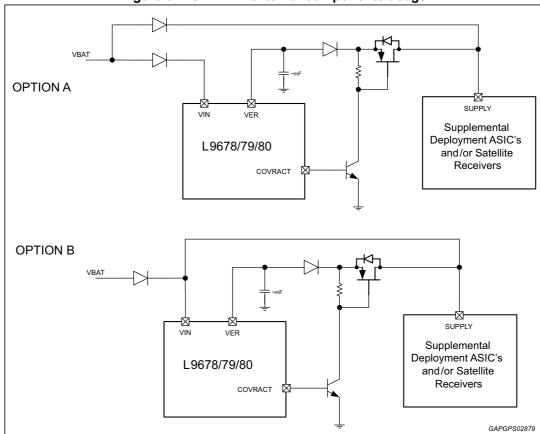

| Figure 7.         Example of power up sequence - WAKEUP then VBAT         22           Figure 8.         Microcontroller drives the power shutdown.         23           Figure 9.         Power shutdown due to low or lost battery.         24           Figure 10.         Device functionality.         25           Figure 11.         Watchdog functionality.         26           Figure 12.         WD1 INITIAL.         28           Figure 13.         WD1 INITIAL vs. WD1 RESET.         28           Figure 14.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET         30           Figure 15.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET         30           Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 19.         ERBOST protection         37           Figure 20.         ER CAP functionality         40           Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD3 functionality         42           Figure 23.         FR Egulators diagnostic errors         48           Figure 24.         VSUP functionality         46           Figure 27. <t< td=""><td>Figure 5.</td><td>COVRACT external components usage</td><td>. 18</td></t<>   | Figure 5.  | COVRACT external components usage               | . 18 |

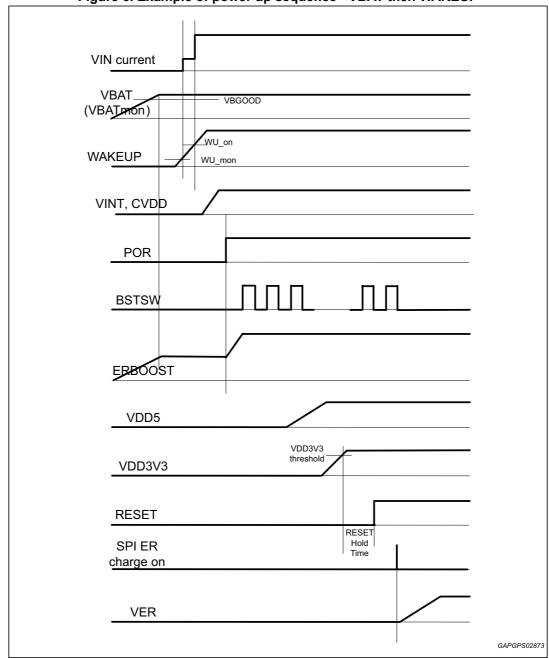

| Figure 8         Microcontroller drives the power shutdown.         23           Figure 9         Power shutdown due to low or lost battery.         24           Figure 10         Device functionality.         25           Figure 11         Watchdog functionality.         26           Figure 12         WD1 INITIAL - WD1 RESET.         28           Figure 14         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET.         29           Figure 15         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET.         30           Figure 17         WD1 RESET - WD1 TEST         30           Figure 18         ERBOOST functionality         36           Figure 19         ERBOOST functionality         36           Figure 20         ER CAP functionality         39           Figure 21         ER SWITCH functionality         40           Figure 23         VDD3V3 functionality         42           Figure 24         VSUP functionality         44           Figure 25         VSF enable.         47           Figure 27         Resulators diagnostic errors.         48           Figure 28         SPI signals         62           Figure 29         Internal ARIMNG signals         64           Figure 30         ARMING organization         67 </td <td>Figure 6.</td> <td>Example of power up sequence - VBAT then WAKEUP</td> <td>. 21</td> | Figure 6.  | Example of power up sequence - VBAT then WAKEUP | . 21 |

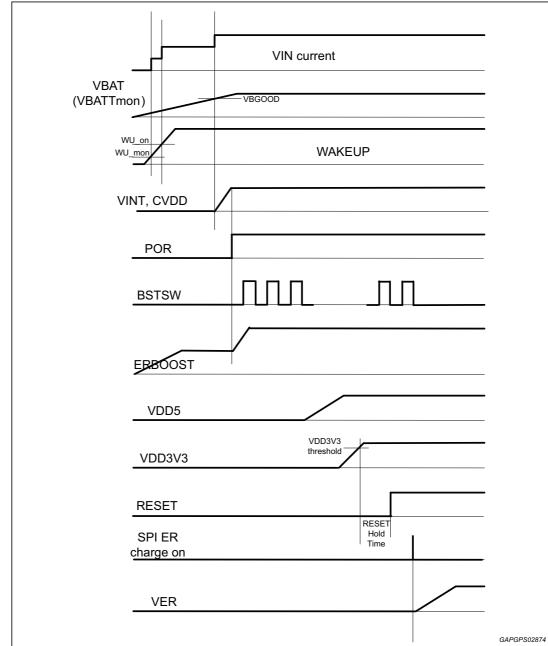

| Figure 9.         Power shutdown due to low or lost battery.         24           Figure 10.         Device functionality.         25           Figure 12.         WD1 INITIAL.         28           Figure 13.         WD1 INITIAL vs. WD1 RESET.         28           Figure 14.         WD1 INITIAL vs. WD1 OVERRIDE         29           Figure 15.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET         30           Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 19.         ER CAP functionality         36           Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD5 functionality         40           Figure 23.         VDD55 functionality         42           Figure 24.         VSUP functionality         44           Figure 25.         VSF enable.         47           Figure 26.         Regulators diagnostic errors.         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64                                                                                                                               | Figure 7.  | Example of power up sequence - WAKEUP then VBAT | . 22 |

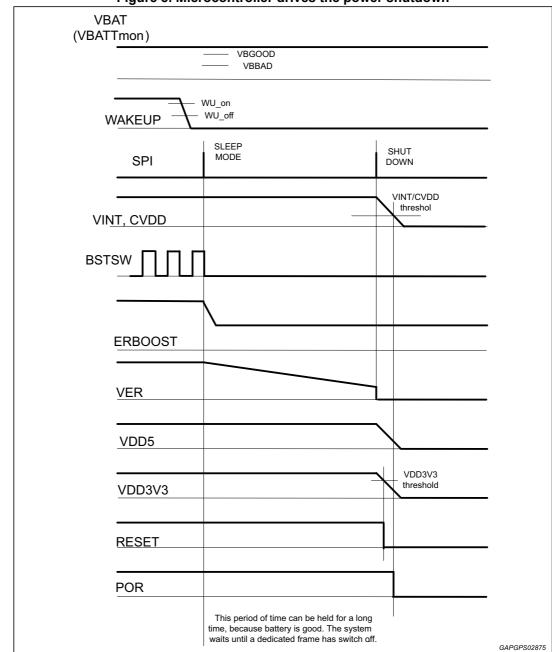

| Figure 10.         Device functionality         25           Figure 11.         Watchdog functionality         26           Figure 13.         WD1 INITIAL         28           Figure 13.         WD1 INITIAL - WD1 RESET         28           Figure 14.         WD1 INITIAL vs. WD1 OVERRIDE         29           Figure 16.         WD1 INITIAL vs. WD1 RESET         30           Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 19.         ERBOOST functionality         36           Figure 19.         ERBOOST protection         37           Figure 20.         ER CAP functionality         49           Figure 21.         ER SWITCH functionality         49           Figure 22.         VDD5 functionality         42           Figure 23.         VDD30/3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 30.         ARMING or                                                                                                                                 | Figure 8.  | Microcontroller drives the power shutdown       | . 23 |

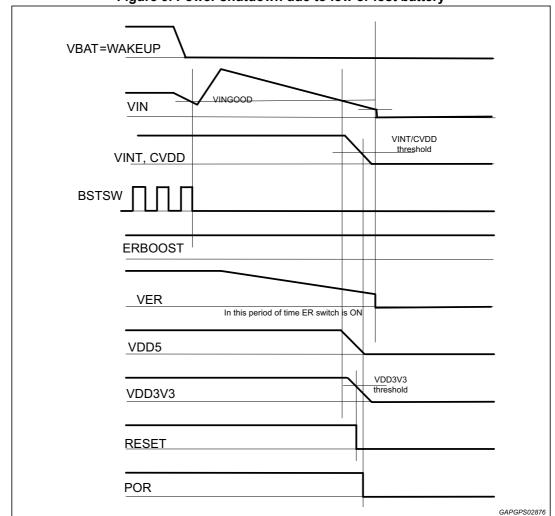

| Figure 11.         Watchdog functionality         26           Figure 12.         WD1 INITIAL         28           Figure 14.         WD1 INITIAL vs. WD1 RESET.         28           Figure 15.         WD1 INITIAL vs. WD1 RESET         30           Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 19.         ERBOOST frotection         37           Figure 21.         ER CAP functionality         40           Figure 22.         VDD5 functionality         40           Figure 23.         VDD3V3 functionality         42           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors.         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67                                                                                                                               | Figure 9.  | Power shutdown due to low or lost battery       | . 24 |

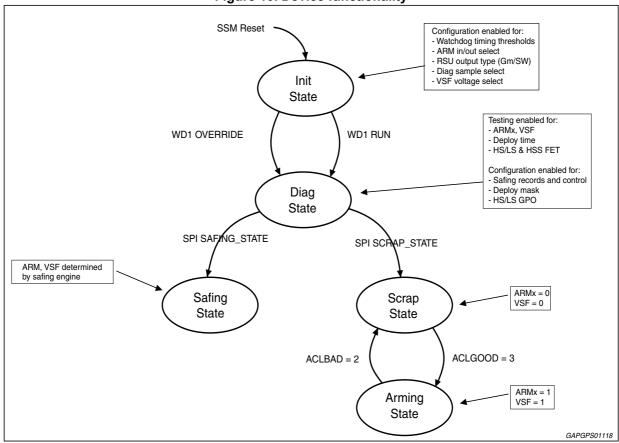

| Figure 12.         WD1 INITIAL         28           Figure 13.         WD1 INITIAL vs. WD1 RESET.         29           Figure 15.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET         30           Figure 16.         WATCHDOG service         31           Figure 18.         ERBOOST functionality         36           Figure 18.         ERBOOST protection         37           Figure 20.         ER CAP functionality         39           Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD5 functionality         40           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors.         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68                                                                                                           | Figure 10. | Device functionality                            | . 25 |

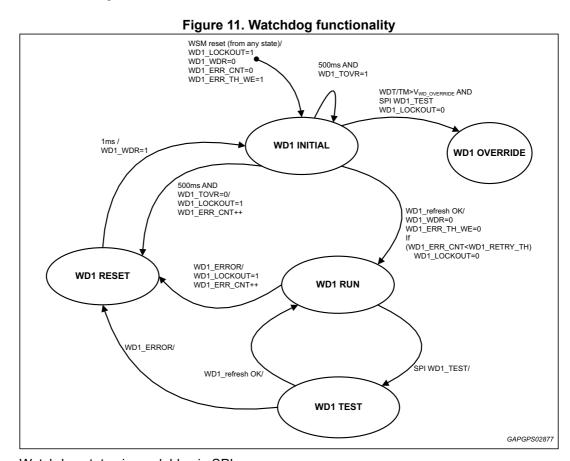

| Figure 13.         WD1 INITIAL - WD1 RESET.         28           Figure 14.         WD1 INITIAL vs. WD1 OVERRIDE         29           Figure 15.         WD1 INITIAL vs. WD1 OVERRIDE         30           Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 29.         ER CAP functionality         36           Figure 20.         ER CAP functionality         40           Figure 21.         ER SWITCH functionality         40           Figure 23.         VDD5 functionality         42           Figure 24.         VSUP functionality         44           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         ARMING organization         64           Figure 30.         ARMING signals         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67 <tr< td=""><td>Figure 11.</td><td>Watchdog functionality</td><td>. 26</td></tr<>                                    | Figure 11. | Watchdog functionality                          | . 26 |

| Figure 14.         WD1 INITIAL vs. WD1 OVERRIDE         29           Figure 15.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET         30           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 19.         ERBOOST protection         37           Figure 21.         ER CAP functionality         39           Figure 22.         VDD5 functionality         40           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CSI, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization                                                                                                   | Figure 12. | WD1 INITIAL                                     | . 28 |

| Figure 15.         WD1 INITIAL vs. WD1 RUN vs. WD1 RESET         30           Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 20.         ER CAP functionality         39           Figure 21.         ER CAP functionality         40           Figure 22.         VDD3V3 functionality         42           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CSI, SCLK         65           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CSI, SCLK         75 <td>Figure 13.</td> <td>WD1 INITIAL - WD1 RESET</td> <td>. 28</td>                               | Figure 13. | WD1 INITIAL - WD1 RESET                         | . 28 |

| Figure 16.         WATCHDOG service         31           Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 19.         ERBOOST protection         37           Figure 20.         ER CAP functionality         39           Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD5 functionality         42           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         62           Figure 30.         ARMING organization.         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70                                                                                                                 | Figure 14. | WD1 INITIAL vs. WD1 OVERRIDE                    | . 29 |

| Figure 17.         WD1 RESET - WD1 TEST         32           Figure 18.         ERBOOST functionality         36           Figure 19.         ERBOOST protection         37           Figure 20.         ER CAP functionality         39           Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD3 functionality         42           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CSI, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CSI, SCLK                                                                                                   | Figure 15. | WD1 INITIAL vs. WD1 RUN vs. WD1 RESET           | . 30 |

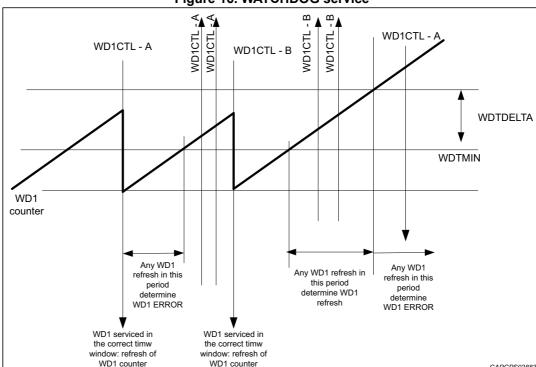

| Figure 18.         ERBOOST functionality         36           Figure 20.         ER CAP functionality         39           Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD5 functionality         42           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable.         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84<                                                                                              | Figure 16. | WATCHDOG service                                | . 31 |

| Figure 19.         ERBOOST protection         37           Figure 20.         ER CAP functionality         39           Figure 21.         ER SWITCH functionality         42           Figure 22.         VDD5 functionality         44           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable.         47           Figure 26.         Regulators diagnostic errors.         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         High side and low side squib enable in ARMI                                                                                     | Figure 17. | WD1 RESET - WD1 TEST                            | . 32 |

| Figure 20.         ER CAP functionality.         39           Figure 21.         ER SWITCH functionality.         40           Figure 22.         VDD5 functionality.         42           Figure 23.         VDD3V3 functionality.         44           Figure 24.         VSUP functionality.         46           Figure 25.         VSF enable.         47           Figure 26.         Regulators diagnostic errors.         48           Figure 27.         RESET organization.         49           Figure 28.         SPI signals.         62           Figure 29.         Internal ARIMNG signals.         64           Figure 29.         Internal ARIMNG signals.         64           Figure 30.         ARMING organization.         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CS1, SCLK.         65           Figure 32.         Sensor's axis and vehicle's axis correlation.         67           Figure 33.         ARMING enable pulse stretch.         68           Figure 34.         SPI sensor frame organization.         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK.         75           Figure 36.         ACL signal.         81           Figure 37.         Device functionality.<                                                                                     | Figure 18. | ERBOOST functionality                           | . 36 |

| Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD5 functionality         42           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors.         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84           Figure 38.         High side and low side squib enable in ARMING state.         85           Figure 49.         High side                                                                                      | Figure 19. | ERBOOST protection                              | . 37 |

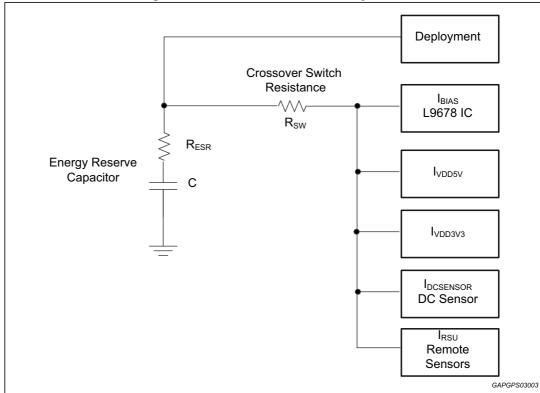

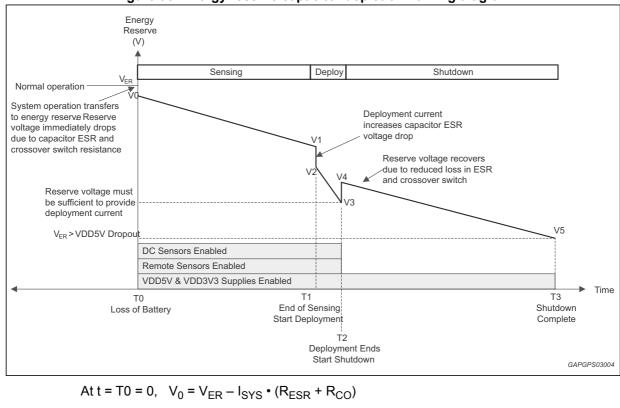

| Figure 21.         ER SWITCH functionality         40           Figure 22.         VDD5 functionality         42           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors.         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84           Figure 38.         High side and low side squib enable in ARMING state.         85           Figure 49.         High side                                                                                      | -          | ER CAP functionality                            | . 39 |

| Figure 22.         VDD5 functionality         42           Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84           Figure 38.         High side and low side squib enable in ARMING state         85           Figure 40.         High side and low side squib enable in DIAG state         86           Figure 41. <td>-</td> <td></td> <td></td>                                                 | -          |                                                 |      |

| Figure 23.         VDD3V3 functionality         44           Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality.         84           Figure 38.         High side and low side squib enable.         84           Figure 39.         High side and low side squib enable in ARMING state.         85           Figure 40.         High side and low side squib enable with ARMING signal         87                                                                            |            | •                                               |      |

| Figure 24.         VSUP functionality         46           Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CSO, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84           Figure 38.         High side and low side squib enable         84           Figure 40.         High side and low side squib enable in ARMING state         85           Figure 41.         High side and low side squib enable with ARMING signal         87           Figure 42.         Driver's DEPLOYMENT enable/disable         89                                                                 |            | · · · · · · · · · · · · · · · · · · ·           |      |

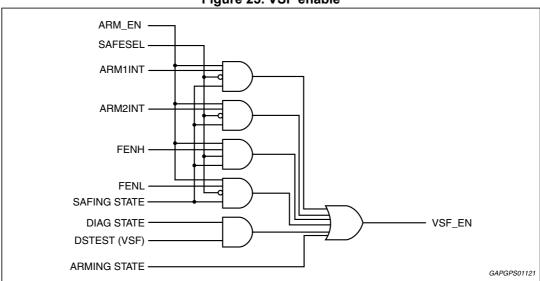

| Figure 25.         VSF enable         47           Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84           Figure 38.         High side and low side squib enable         84           Figure 39.         High side and low side squib enable in ARMING state         85           Figure 40.         High side and low side squib enable in DIAG state         86           Figure 41.         High side and low side squib enable with ARMING signal         87           Figure 42.         Driver's DEPLOYMENT signals                                                    |            | · · · · · · · · · · · · · · · · · · ·           |      |

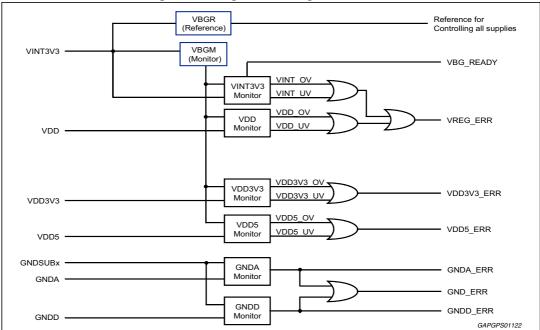

| Figure 26.         Regulators diagnostic errors         48           Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84           Figure 38.         High side and low side squib enable         84           Figure 39.         High side and low side squib enable in ARMING state         85           Figure 40.         High side and low side squib enable with ARMING signal         87           Figure 41.         High side and low side squib enable with ARMING signal         87           Figure 42.         Driver's DEPLOYMENT signals         88           Figure 43.         DEPLOYMENT enabl                                         |            | ·                                               |      |

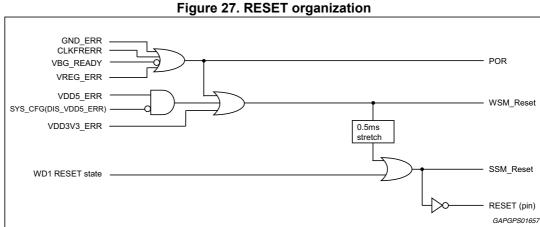

| Figure 27.         RESET organization         49           Figure 28.         SPI signals         62           Figure 29.         Internal ARIMNG signals         64           Figure 30.         ARMING organization         64           Figure 31.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         65           Figure 32.         Sensor's axis and vehicle's axis correlation         67           Figure 33.         ARMING enable pulse stretch         68           Figure 34.         SPI sensor frame organization         70           Figure 35.         MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK         75           Figure 36.         ACL signal         81           Figure 37.         Device functionality         84           Figure 38.         High side and low side squib enable         84           Figure 39.         High side and low side squib enable in ARMING state         85           Figure 40.         High side and low side squib enable with ARMING signal         87           Figure 41.         High side and low side squib enable with ARMING signal         87           Figure 42.         Driver's DEPLOYMENT signals         88           Figure 43.         DEPLOYMENT enable/disable         89           Figure 44.         Diagnostic - blocks                                         | -          |                                                 |      |

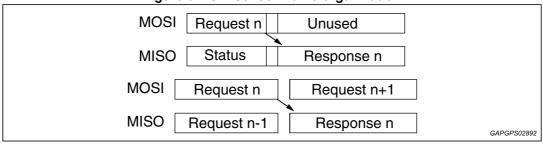

| Figure 28.SPI signals62Figure 29.Internal ARIMNG signals64Figure 30.ARMING organization64Figure 31.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK65Figure 32.Sensor's axis and vehicle's axis correlation67Figure 33.ARMING enable pulse stretch68Figure 34.SPI sensor frame organization70Figure 35.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK75Figure 36.ACL signal81Figure 37.Device functionality84Figure 38.High side and low side squib enable84Figure 40.High side and low side squib enable in ARMING state85Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -          |                                                 |      |

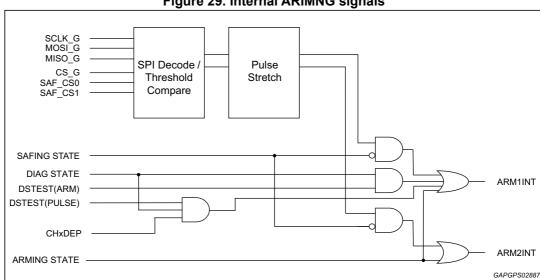

| Figure 29.Internal ARIMNG signals64Figure 30.ARMING organization64Figure 31.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK65Figure 32.Sensor's axis and vehicle's axis correlation67Figure 33.ARMING enable pulse stretch68Figure 34.SPI sensor frame organization70Figure 35.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK75Figure 36.ACL signal81Figure 37.Device functionality84Figure 38.High side and low side squib enable.84Figure 39.High side and low side squib enable in ARMING state.85Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview.99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1).104Figure 47.Diagnostic - VRCM test validation (2).105                                                                                                                                                                                                                                                                                                                                                                                                                                  | -          |                                                 |      |

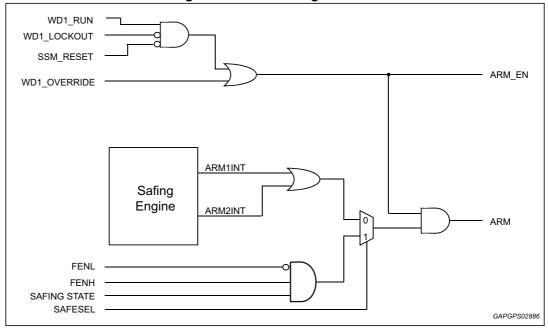

| Figure 30.ARMING organization.64Figure 31.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK65Figure 32.Sensor's axis and vehicle's axis correlation67Figure 33.ARMING enable pulse stretch68Figure 34.SPI sensor frame organization70Figure 35.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK75Figure 36.ACL signal81Figure 37.Device functionality84Figure 38.High side and low side squib enable.84Figure 39.High side and low side squib enable in ARMING state.85Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview.99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -          |                                                 |      |

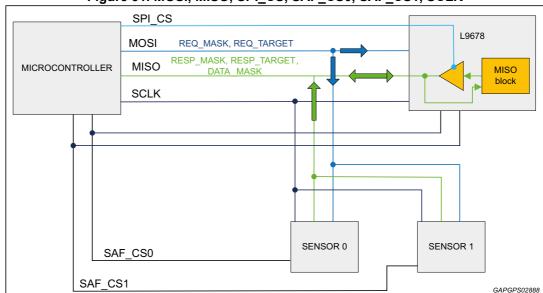

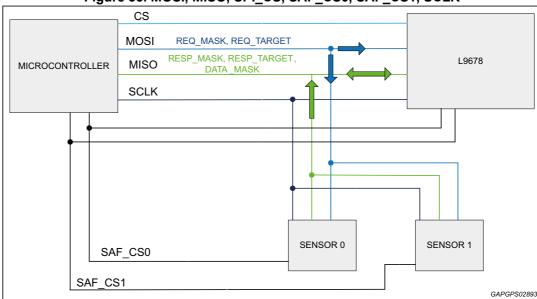

| Figure 31. MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK. 65 Figure 32. Sensor's axis and vehicle's axis correlation 67 Figure 33. ARMING enable pulse stretch 68 Figure 34. SPI sensor frame organization 70 Figure 35. MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK 75 Figure 36. ACL signal 81 Figure 37. Device functionality 84 Figure 38. High side and low side squib enable. 84 Figure 39. High side and low side squib enable in ARMING state 85 Figure 40. High side and low side squib enable in DIAG state 86 Figure 41. High side and low side squib enable with ARMING signal 87 Figure 42. Driver's DEPLOYMENT signals 88 Figure 43. DEPLOYMENT enable/disable 89 Figure 44. Diagnostic - blocks overview 99 Figure 45. High voltage leak test, oxide isolation IC-car chassis 101 Figure 47. Diagnostic - VRCM test validation (2) 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -          |                                                 |      |

| Figure 32.Sensor's axis and vehicle's axis correlation67Figure 33.ARMING enable pulse stretch68Figure 34.SPI sensor frame organization70Figure 35.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK75Figure 36.ACL signal81Figure 37.Device functionality84Figure 38.High side and low side squib enable84Figure 39.High side and low side squib enable in ARMING state85Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -          |                                                 |      |

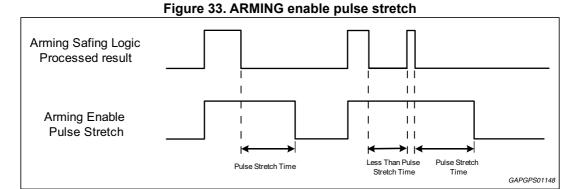

| Figure 33.ARMING enable pulse stretch68Figure 34.SPI sensor frame organization70Figure 35.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK75Figure 36.ACL signal81Figure 37.Device functionality84Figure 38.High side and low side squib enable84Figure 39.High side and low side squib enable in ARMING state85Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -          |                                                 |      |

| Figure 34. SPI sensor frame organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -          |                                                 |      |

| Figure 35.MOSI, MISO, SPI_CS, SAF_CS0, SAF_CS1, SCLK75Figure 36.ACL signal81Figure 37.Device functionality84Figure 38.High side and low side squib enable84Figure 39.High side and low side squib enable in ARMING state85Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -          |                                                 |      |

| Figure 36.ACL signal81Figure 37.Device functionality84Figure 38.High side and low side squib enable84Figure 39.High side and low side squib enable in ARMING state85Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -          |                                                 |      |

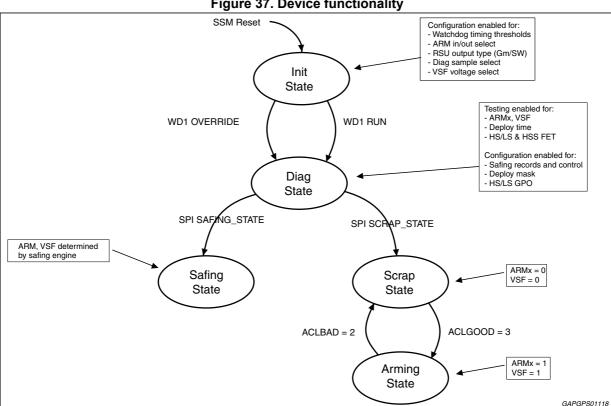

| Figure 37.Device functionality.84Figure 38.High side and low side squib enable.84Figure 39.High side and low side squib enable in ARMING state.85Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview.99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -          |                                                 |      |

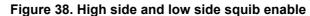

| Figure 38.High side and low side squib enable.84Figure 39.High side and low side squib enable in ARMING state.85Figure 40.High side and low side squib enable in DIAG state.86Figure 41.High side and low side squib enable with ARMING signal.87Figure 42.Driver's DEPLOYMENT signals.88Figure 43.DEPLOYMENT enable/disable.89Figure 44.Diagnostic - blocks overview.99Figure 45.High voltage leak test, oxide isolation IC-car chassis.101Figure 46.Diagnostic - VRCM test validation (1).104Figure 47.Diagnostic - VRCM test validation (2).105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •          |                                                 |      |

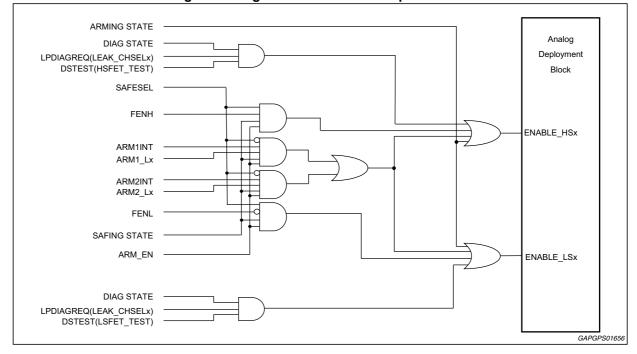

| Figure 39.High side and low side squib enable in ARMING state.85Figure 40.High side and low side squib enable in DIAG state.86Figure 41.High side and low side squib enable with ARMING signal.87Figure 42.Driver's DEPLOYMENT signals.88Figure 43.DEPLOYMENT enable/disable.89Figure 44.Diagnostic - blocks overview.99Figure 45.High voltage leak test, oxide isolation IC-car chassis.101Figure 46.Diagnostic - VRCM test validation (1).104Figure 47.Diagnostic - VRCM test validation (2).105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •          |                                                 |      |

| Figure 40.High side and low side squib enable in DIAG state86Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -          |                                                 |      |

| Figure 41.High side and low side squib enable with ARMING signal87Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                 |      |

| Figure 42.Driver's DEPLOYMENT signals88Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •          |                                                 |      |

| Figure 43.DEPLOYMENT enable/disable89Figure 44.Diagnostic - blocks overview99Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •          |                                                 |      |

| Figure 44.Diagnostic - blocks overview.99Figure 45.High voltage leak test, oxide isolation IC-car chassis.101Figure 46.Diagnostic - VRCM test validation (1).104Figure 47.Diagnostic - VRCM test validation (2).105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •          |                                                 |      |

| Figure 45.High voltage leak test, oxide isolation IC-car chassis101Figure 46.Diagnostic - VRCM test validation (1)104Figure 47.Diagnostic - VRCM test validation (2)105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •          |                                                 |      |

| Figure 46. Diagnostic - VRCM test validation (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •          |                                                 |      |

| Figure 47. Diagnostic - VRCM test validation (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •          |                                                 |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •          |                                                 |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 48. | Diagnostic - leakage test - high side           |      |

List of figures AN4437

| Figure 49. | Diagnostic - leakage test - low side                                                | 109 |

|------------|-------------------------------------------------------------------------------------|-----|

| Figure 50. | Diagnostic - leakage test - low side IPD                                            |     |

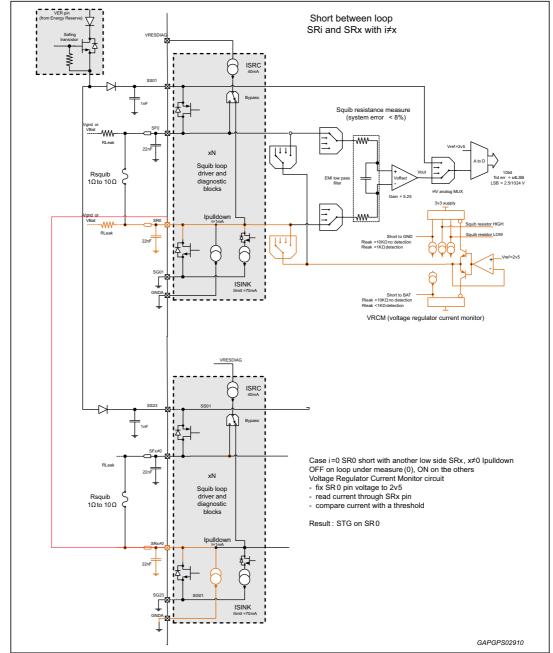

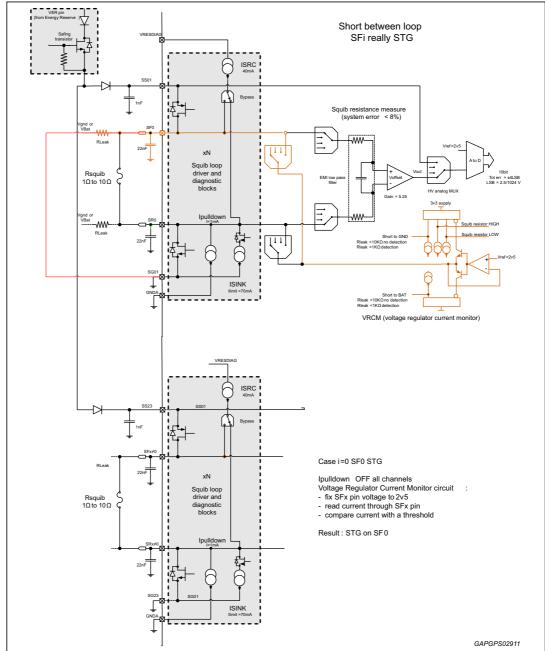

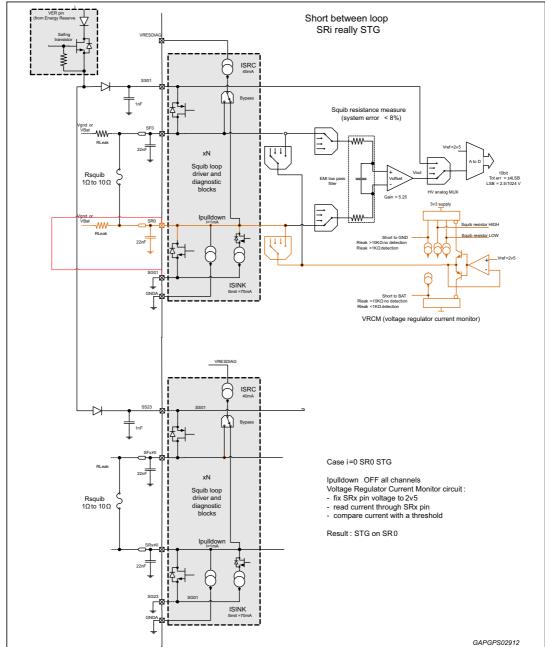

| Figure 51. | Diagnostic - short between loops, HSi, HSx, i≠x (case 1)                            | 113 |

| Figure 52. | Diagnostic - short between loops, HSi, LSx, i≠x (case 2)                            |     |

| Figure 53. | Diagnostic - short between loops, LSi, HSx, i≠x (case 3)                            |     |

| Figure 54. | Diagnostic - short between loops, LSi, LSx, i≠x (case 4)                            |     |