# Introduction to using the hardware real-time clock (RTC) and the tamper management unit (TAMP) with STM32 MCUs

## Introduction

A real-time clock (RTC) is a computer clock that tracks the current time. Although the RTCs are often used in personal computers, servers and embedded systems, they are also present in almost any electronic device that requires an accurate time keeping. The microcontrollers supporting the RTC can be used for chronometers, alarm clocks, watches, small electronic agendas, and many other devices.

This application note describes the RTC features and how to configure it to implement several use cases such as calendar, alarm, wakeup, timestamp, tamper detection, or calibration.

Depending on the RTC type, the product documentation may refer to an independent TAMP that is also detailed in this application note.

Software examples are then detailed in this document to show how to use the RTC in the low-power modes, and how to ensure the tamper detection and timestamp while the main supply is switched off and the MCU is supplied by an alternate battery. Other examples are also presented to illustrate the following features: smooth calibration, synchronization, reference clock detection and internal tamper.

The dedicated software is provided through the X-CUBE-RTC Expansion Package delivered with this application note. This software contains the source code of these examples and all the embedded software modules required to run the examples.

In this document, the STM32 microcontroller terminology applies to the products listed in the table below.

Table 1. Applicable products

| Туре              | Products                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Expansion Package | X-CUBE-RTC                                                                                                                                                                                                                                                                                                                                                                       |

| Microcontrollers  | STM32C0 series, STM32F0 series, STM32F2 series, STM32F3 series, STM32F4 series, STM32F7 series, STM32G0 series, STM32G4 series, STM32H5 series, STM32H7 series, STM32L0 series, STM32L1 series, STM32L4 series, STM32L4 series, STM32L5 series, STM32N6 series, STM32U0 series, STM32U3 series, STM32U5 series, STM32WB series, STM32WB0 series, STM32WBA series, STM32WL series |

## 1 Overview of the STM32 MCUs advanced RTC

The RTC is embedded in STM32 Arm® Cortex®-based MCUs.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

The RTC provides a full-featured calendar, alarm, periodic wakeup unit, digital calibration, synchronization, timestamp, and advanced tamper detection.

The RTC features and their implementation can be significantly different (regarding the registers map for example) depending on the product. Two RTC types, RTC2 and RTC3, are distinguished and characterized in the table below. These types affect the information presented in the rest of this application note.

Table 2. RTC/TAMP types

|                               | Fea                       | tures                                                                                            | RTC2 | RTC3 |

|-------------------------------|---------------------------|--------------------------------------------------------------------------------------------------|------|------|

| RTC clock source (LSE, LSI, F | ISE with prescal          | er)                                                                                              | Х    | Х    |

| Binary mode                   |                           |                                                                                                  | -    | Х    |

| Mixed mode (BCD and binary)   |                           |                                                                                                  | -    | Х    |

| Prescalers                    | Asynchronous              |                                                                                                  | Х    | X    |

| Frescalers                    | Synchronous               |                                                                                                  | X    | Х    |

|                               |                           | 12 h/24 h format                                                                                 | Χ    | X    |

|                               | Time                      | Hour, minute, second                                                                             | Χ    | X    |

|                               |                           | Subsecond                                                                                        | Χ    | X    |

| Calendar                      | Date                      |                                                                                                  | Χ    | X    |

|                               | Daylight opera            | tion                                                                                             | Χ    | X    |

|                               | Bypass the sh             | adow registers                                                                                   | Χ    | X    |

|                               | Power optimiz             | ation mode                                                                                       | -    | X    |

|                               | Alarms                    | Alarm A                                                                                          | Χ    | X    |

|                               | available                 | Alarm B                                                                                          | Χ    | X    |

|                               |                           | 12 h/24 h format                                                                                 | Х    | X    |

| Alarm                         | Time                      | Hour, minutes, seconds                                                                           | Χ    | X    |

|                               |                           | Subseconds                                                                                       | Χ    | X    |

|                               | Date or week              | day                                                                                              | Χ    | X    |

|                               | Binary mode a             | larm                                                                                             | -    | X    |

|                               |                           | Backup registers erase <sup>(1)</sup>                                                            | Х    | Х    |

|                               | Tamper<br>effects         | Interruption                                                                                     | Х    | Х    |

|                               |                           | Trigger for low-power timer                                                                      | Х    | X    |

|                               | Configurable e            | edge detection                                                                                   | Х    | Х    |

| Tamper detection              | Configurable le           | Configurable level detection (filtering, sampling and precharge configuration, internal pull-up) |      | ×    |

|                               | Internal tampe            | r events                                                                                         | -    | Х    |

|                               | External tampe            | er inputs                                                                                        | Х    | Х    |

|                               | V <sub>BAT</sub> mode pir | ns                                                                                               | Х    | Х    |

|                               | NOERASE mo                | ode                                                                                              | Х    | Х    |

AN4759 - Rev 10 page 2/61

|                              | Fea                            | tures                                                   | RTC2 | RTC3 |  |  |

|------------------------------|--------------------------------|---------------------------------------------------------|------|------|--|--|

|                              | Independent v                  | vatchdog linked to an internal tamper for ction timeout | -    | Х    |  |  |

|                              | Active tamper                  |                                                         | -    | X    |  |  |

| Tamper detection             | Monotonic cou                  | ınter                                                   | -    | Х    |  |  |

|                              | SAES key stor                  | rage                                                    | -    | Х    |  |  |

|                              | Secure protec                  | tion modes                                              | -    | Х    |  |  |

|                              | Privileged prof                | ection mode                                             | -    | Х    |  |  |

|                              | Configurable i                 | nput mapping                                            | Х    | Х    |  |  |

|                              | Time                           | Hour, minute, second                                    | X    | Х    |  |  |

| Time and a man               | Tillle                         | Subsecond                                               | X    | X    |  |  |

| Timestamp                    | Date (day, mo                  | nth)                                                    | Х    | X    |  |  |

|                              | Timestamp on                   | tamper detection event                                  | Х    | Х    |  |  |

|                              | Timestamp on                   | switch to V <sub>BAT</sub> mode                         | X    | X    |  |  |

| \A/=1                        | Clock source a                 | available                                               | X    | Х    |  |  |

| Wakeup unit                  | Hardware auto                  | omatic flag clearance                                   | X    | Х    |  |  |

|                              |                                | Alarm event                                             | X    | Х    |  |  |

|                              | TAMPALRM                       | Wakeup event                                            | X    | Х    |  |  |

| RTC outputs                  |                                | Tamper event                                            | -    | Х    |  |  |

|                              | CALIB                          | 512 Hz                                                  | Х    | Х    |  |  |

|                              | CALIB                          | 1 Hz                                                    | X    | Х    |  |  |

| Smooth digital calibration   | Smooth calibra                 | ation                                                   | X    | Х    |  |  |

| Smooth digital calibration   | Power optimiz                  | ation mode                                              | -    | Х    |  |  |

| RTC synchronization          | ·                              |                                                         | X    | X    |  |  |

| Reference clock detection    |                                |                                                         | X    | Х    |  |  |

| Packup registers             | Reset on a tamper detection    |                                                         |      |      |  |  |

| Dackup registers             | Reset when F                   | lash memory readout protection is disabled              | Х    | Х    |  |  |

| RTC secure protection mode   |                                |                                                         | -    | Х    |  |  |

| RTC privileged protection mo | RTC privileged protection mode |                                                         |      |      |  |  |

<sup>1.</sup> Depending on devices, other resources can also be erased.

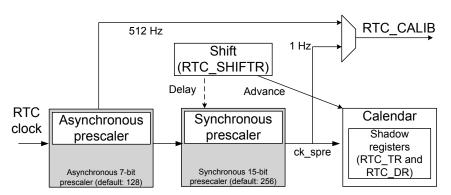

The RTC acts as an independent binary-coded decimal (BCD) timer/counter. For the RTC3 type, a binary and a mixed (both binary and BCD) modes are available.

A given feature can be available for a RTC type but not implemented on all products (see Table 4 and Table 5 for more details).

The table below specifies which RTC type is implemented on which product.

Table 3. RTC type on STM32 MCUs

| RTC type | STM32 MCUs                                                                                                                                                                                                                                                  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTC2     | STM32F0 series, STM32F2 series, STM32F3 series, STM32F4 series, STM32F7 series, STM32H72/H73/H74/H75xxx, STM32L0 series, STM32L1 series, STM32L4R5/Q5 line, STM32L4R7/S7 line, STM32L4R9/S9 line, STM32WB series, STM32WB0 series                           |

| RTC3     | STM32C0 series, STM32G0 series, STM32G4 series, STM32H5 series, STM32H7A3/7B3 line, STM32H7Rx/7Sx line, STM32L41/L42xxx, STM32L4P5/Q5 line, STM32L5 series, STM32N6 series, STM32U0 series, STM32U3 series, STM32U5 series, STM32WL series, STM32WBA series |

AN4759 - Rev 10 page 3/61

## 2 Advanced RTC features

The following tables summarize the RTC features available on each STM32 MCU.

Table 4. Advanced features for RTC2 type

|             |                                     |                                                                                                 |                         |           |           |           |           |                  | STM       | 32L1                                                |                          |           |                  |        |

|-------------|-------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------|-----------|-----------|-----------|-----------|------------------|-----------|-----------------------------------------------------|--------------------------|-----------|------------------|--------|

|             | Feature                             | STM32F0                                                                                         | STM32F2                 | STM32F3   | STM32F4   | STM32F7   | STM32L0   | Cat. 2/3/4/5/6   | Cat. 1    | STM32L4 <sup>(1)</sup> -<br>STM32L4+ <sup>(2)</sup> | STM32H72/H73/<br>H74/H75 | STM32WB   | STM32WB0         |        |

| RTC o       | clock source (LSE, LS<br>aler)      | SI, HSE with                                                                                    | Х                       | X         | X         | X         | X         | X                | х         | х                                                   | X                        | X         | х                | Х      |

| ers         | Asynchronous                        | (number of bits)                                                                                | X (7)                   | X (7)     | X (7)     | X (7)     | X (7)     | X (7)            | X (7)     | X (7)                                               | X (7)                    | X (7)     | X (7)            | X (7)  |

| Prescalers  | Synchronous                         | (number of bits)                                                                                | X<br>(15)               | X<br>(13) | X<br>(15) | X<br>(15) | X<br>(15) | X<br>(15)        | X<br>(15) | X<br>(13)                                           | X<br>(15)                | X<br>(15) | X<br>(15)        | X (15) |

|             |                                     | 12 h/24 h format                                                                                | Х                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | Х      |

|             | Time                                | Hour, minute, second                                                                            | Х                       | X         | Х         | Х         | X         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | Х      |

| dar         |                                     | Subsecond                                                                                       | Х                       | N/A       | Х         | Х         | Х         | Х                | Х         | N/A                                                 | Х                        | Х         | Х                | Х      |

| Calendar    | Date                                |                                                                                                 | Х                       | X         | Х         | Х         | Х         | Х                | Х         | Х                                                   | X                        | Х         | X                | X      |

|             | Daylight operation                  |                                                                                                 | X                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | X      |

|             | Bypass shadow reg                   | gisters                                                                                         | Х                       | N/A       | Х         | Х         | Х         | Х                | Х         | N/A                                                 | Х                        | Х         | Х                | X      |

|             | V <sub>BAT</sub> mode               |                                                                                                 | X                       | Х         | Х         | Х         | Х         | N/A              | N/A       | N/A                                                 | Х                        | Х         | Х                | X      |

|             | Alarms available                    | Alarm A                                                                                         | X                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | X      |

|             | 7 II ATTIO AVAILABIO                | Alarm B                                                                                         | N/A                     | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | N/A    |

| Ę           |                                     | 12 h/24 h format                                                                                | Х                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | X      |

| Alarm       | Time                                | Hour, minute, second                                                                            | Х                       | X         | X         | X         | Х         | X                | Х         | Х                                                   | X                        | X         | х                | Х      |

|             |                                     | Subsecond                                                                                       | X                       | N/A       | Х         | Х         | Х         | Х                | Х         | N/A                                                 | Х                        | Х         | Х                | X      |

|             | Date or week day                    |                                                                                                 | X                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | X      |

|             | Configurable input                  | mapping                                                                                         | X                       | Х         | Х         | Х         | Х         | Х                | N/A       | N/A                                                 | Х                        | Х         | Х                | X      |

| _           | Configurable edge                   | detection                                                                                       | X                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | N/A    |

| r detection | _                                   | Configurable level detection (filtering, sampling, and precharge configuration on tamper input) |                         | N/A       | X         | x         | X         | X                | Х         | N/A                                                 | X                        | X         | Х                | N/A    |

| Tamper      | Number of tamper i                  | nputs                                                                                           | <b>2</b> <sup>(3)</sup> | 2         | 2         | 2         | 3         | 3                | 3         | 1                                                   | 3                        | 3         | 3                | N/A    |

| <u> </u>    | Number of tamper                    | events                                                                                          | 0                       | 1         | 2         | 2         | 3         | 3                | 3         | 1                                                   | 3                        | 3         | 3                | N/A    |

|             | V <sub>BAT</sub> mode pins (inputs) |                                                                                                 | 1                       | 1         | 1         | 2         | 2         | N/A              | N/A       | N/A                                                 | 3                        | 3         | 3                | N/A    |

|             | Configurable input mapping          |                                                                                                 | Х                       | Х         | Х         | Х         | Х         | X <sup>(4)</sup> | N/A       | N/A                                                 | X <sup>(4)</sup>         | Х         | X <sup>(4)</sup> | N/A    |

| Timestamp   | Time Hour, minute second            |                                                                                                 | Х                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | N/A    |

| mest        |                                     | Subseconds                                                                                      | X                       | N/A       | Х         | Х         | Х         | Х                | Х         | N/A                                                 | Х                        | Х         | Х                | N/A    |

| =           | Date (day, month)                   |                                                                                                 | X                       | Х         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | N/A    |

|             | Timestamp on tamp                   | per detection event                                                                             | Х                       | X         | Х         | Х         | Х         | Х                | Х         | Х                                                   | Х                        | Х         | Х                | N/A    |

AN4759 - Rev 10 page 4/61

|             |                    |                             |         |         |         |         |         | STM     | 32L1           |        | 11                                                  |                          |         |          |

|-------------|--------------------|-----------------------------|---------|---------|---------|---------|---------|---------|----------------|--------|-----------------------------------------------------|--------------------------|---------|----------|

|             | Feature            | 9 <b>S</b>                  | STM32F0 | STM32F2 | STM32F3 | STM32F4 | STM32F7 | STM32L0 | Cat. 2/3/4/5/6 | Cat. 1 | STM32L4 <sup>(1)</sup> -<br>STM32L4+ <sup>(2)</sup> | STM32H72/H73/<br>H74/H75 | STM32WB | STM32WB0 |

| Timestamp   | Timestamp on swite | ch to V <sub>BAT</sub> mode | N/A     | N/A     | N/A     | N/A     | х       | N/A     | N/A            | N/A    | х                                                   | х                        | Х       | N/A      |

| ts          | RTC_ALARM          | Alarm event                 | Х       | Х       | Х       | Х       | Х       | Х       | Х              | Х      | Х                                                   | Х                        | Х       | Х        |

| RTC outputs | Wakeup ever        |                             | Х       | Х       | Х       | Х       | Х       | Х       | Х              | Х      | Х                                                   | Х                        | Х       | X        |

| TC 0        | RTC_CALIB          | 512 Hz                      | Х       | Х       | Х       | Х       | Х       | Х       | Х              | Х      | Х                                                   | Х                        | Х       | Х        |

| Ľ.          | KTC_CALIB          | 1 Hz                        | Х       | N/A     | Х       | Х       | Х       | Х       | Х              | N/A    | Х                                                   | Х                        | Х       | Х        |

AN4759 - Rev 10 page 5/61

|                            |                                                        |                    |         |                    |         |                    |                    | STM            | 32L1   |                                                     | _                        |                    |                    |

|----------------------------|--------------------------------------------------------|--------------------|---------|--------------------|---------|--------------------|--------------------|----------------|--------|-----------------------------------------------------|--------------------------|--------------------|--------------------|

|                            | Features                                               | STM32F0            | STM32F2 | STM32F3            | STM32F4 | STM32F7            | STM32L0            | Cat. 2/3/4/5/6 | Cat. 1 | STM32L4 <sup>(1)</sup> -<br>STM32L4+ <sup>(2)</sup> | STM32H72/H73/<br>H74/H75 | STM32WB            | STM32WB0           |

| tion                       | Coarse calibration                                     | N/A <sup>(5)</sup> | Х       | N/A <sup>(5)</sup> | Х       | N/A <sup>(5)</sup> | N/A <sup>(5)</sup> | Х              | Х      | N/A <sup>(5)</sup>                                  | N/A <sup>(5)</sup>       | N/A <sup>(5)</sup> | N/A <sup>(5)</sup> |

| RTC calibration            | Smooth calibration                                     | Х                  | N/A     | Х                  | Х       | Х                  | Х                  | X              | N/A    | х                                                   | X                        | X                  | Х                  |

| Synch                      | ronizing the RTC                                       | X                  | N/A     | Х                  | Х       | Х                  | Х                  | Х              | N/A    | Х                                                   | Х                        | Х                  | X                  |

| Refere                     | ence clock detection                                   | Х                  | Х       | Х                  | Х       | Х                  | Х                  | Х              | Х      | Х                                                   | Х                        | Х                  | Х                  |

| စ္                         | Powered-on V <sub>BAT</sub>                            | Х                  | Х       | Х                  | Х       | Х                  | N/A                | N/A            | N/A    | Х                                                   | Х                        | Х                  | VDD12              |

| giste                      | Reset on a tamper detection                            | Х                  | Х       | Х                  | Х       | Х                  | Х                  | Х              | Х      | Х                                                   | Х                        | Х                  | N/A                |

| Backup registers           | Reset when flash memory readout protection is disabled | х                  | N/A     | х                  | N/A     | х                  | х                  | Х              | Х      | х                                                   | х                        | Х                  | N/A                |

| Number of backup registers |                                                        | 5                  | 20      | 16                 | 20      | 32                 | 5                  | 32(6)          | 20     | 20(7)                                               | 32                       | 20                 | 5                  |

- 1. Except STM32L41/42xxx.

- 2. Except STM32L4P5/Q5 line.

- 3. 3 inputs for STM32F07/F09x.

- 4. Thanks to timestamp on tamper event.

- 5. Obsolete, replaced by smooth calibration.

- 6. Only 20 for Cat 2.

- 7. 32 for STM32L4R/4S line.

AN4759 - Rev 10 page 6/61

Table 5. Advanced features of RTC3 type

| No.   No.  |          | Feature             | es                   | STM32C0 | STM32G0 | STM32G4 | STM32H5                                            | STM32H7A3/7B3       | STM32L41/42/4P<br>5/4Q5                                                                             | STM32L5                       | STM32N6                                                              | STM32U5                                           | STM32U3               | STM32WL          | STM32U0          | STM32H7Rx/7Sx                              | STM32WBA         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|----------------------|---------|---------|---------|----------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------|---------------------------------------------------|-----------------------|------------------|------------------|--------------------------------------------|------------------|

| Martin     |          |                     |                      | х       | х       | х       | х                                                  | х                   | x                                                                                                   | х                             | х                                                                    | x                                                 | x                     | х                | x                | x                                          | Х                |

| March   Mar  |          | Binary m            | ode                  | N/A     | N/A     | N/A     | Х                                                  | N/A                 | N/A                                                                                                 | N/A                           | х                                                                    | х                                                 | х                     | Х                | х                | N/A                                        | Х                |

| March   Marc | N        |                     |                      | N/A     | N/A     | N/A     | x                                                  | N/A                 | N/A                                                                                                 | N/A                           | х                                                                    | х                                                 | х                     | x                | х                | N/A                                        | х                |

| March   Mar  | calers   | Asynch<br>(numbe    | ronous<br>r of bits) | X (7)   | X (7)   | X (7)   | X (7)                                              | X (7)               | X (7)                                                                                               | X (7)                         | X (7)                                                                | X (7)                                             | X (7)                 | X (7)            | X (7)            | X (7)                                      | X (7)            |

| Fig.    | Pres     |                     |                      | X (15)  | X (15)  | X (15)  | X (15)                                             | X (15)              | X (15)                                                                                              | X (15)                        | X (15)                                                               | X (15)                                            | X (15)                | X (15)           | X (15)           | X (15)                                     | X (15)           |

| Time   minuse, a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                     |                      | Х       | х       | х       | х                                                  | х                   | Х                                                                                                   | х                             | х                                                                    | Х                                                 | Х                     | х                | Х                | Х                                          | Х                |

| Barrian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Time                | minute,              | Х       | Х       | х       | х                                                  | х                   | x                                                                                                   | х                             | Х                                                                    | x                                                 | x                     | x                | x                | x                                          | х                |

| Description    | ndar     |                     |                      | Х       | Х       | Х       | х                                                  | Х                   | х                                                                                                   | х                             | Х                                                                    | X                                                 | X                     | х                | x                | X                                          | Х                |

| Bypess the shadow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cale     | Da                  | ate                  | Х       | Х       | Х       | X                                                  | Х                   | X                                                                                                   | Х                             | Х                                                                    | X                                                 | X                     | Х                | Х                | Х                                          | Х                |

| Power control   Power contro |          | Daylight            | operation            | Х       | Х       | Х       | Х                                                  | Х                   | х                                                                                                   | Х                             | Х                                                                    | Х                                                 | Х                     | Х                | х                | х                                          | X                |

| Alarm A   Alarm A   X   X   X   X   X   X   X   X   X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                     |                      | х       | Х       | Х       | х                                                  | Х                   | х                                                                                                   | х                             | Х                                                                    | х                                                 | х                     | х                | X                | х                                          | Х                |

| Alarm B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                     |                      | N/A     | N/A     | N/A     | х                                                  | N/A                 | х                                                                                                   | х                             | х                                                                    | х                                                 | х                     | х                | х                | х                                          | Х                |

| Figure   F |          |                     | Alarm A              | Х       | Х       | Х       | X                                                  | Х                   | X                                                                                                   | Х                             | Х                                                                    | X                                                 | X                     | Х                | Х                | Х                                          | Х                |

| Figure   F |          | available           | Alarm B              | N/A     | Х       | Х       | Х                                                  | Х                   | Х                                                                                                   | Х                             | Х                                                                    | Х                                                 | Х                     | Х                | Х                | Х                                          | Х                |

| Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                     | format               | Х       | Х       | Х       | х                                                  | Х                   | х                                                                                                   | Х                             | Х                                                                    | х                                                 | х                     | х                | х                | Х                                          | Х                |

| Date or week day                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Alarm    | Time                | minute,              | х       | Х       | Х       | х                                                  | Х                   | x                                                                                                   | х                             | Х                                                                    | х                                                 | х                     | х                | х                | х                                          | х                |

| Binary mode alarm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                     |                      |         |         | Х       |                                                    |                     | Х                                                                                                   |                               |                                                                      | х                                                 |                       |                  | х                |                                            | Х                |

| Tamper   T |          |                     | -                    |         |         |         |                                                    |                     |                                                                                                     |                               |                                                                      |                                                   |                       |                  |                  |                                            |                  |

| Tamper reactions   Tamper reac |          | Binary me           |                      | N/A     | N/A     | N/A     | X                                                  | N/A                 | N/A                                                                                                 | N/A                           | Х                                                                    | X                                                 | X                     | X                | Х                | Х                                          | X                |

| Trigger for low-power limber   N/A   X   X   X   X   X   X   X   X   X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                     | registers            | N/A     | Х       | х       | X <sup>(2)</sup>                                   | X <sup>(1)</sup>    | х                                                                                                   | X <sup>(1)</sup>              | X <sup>(2)</sup>                                                     | X <sup>(2)</sup>                                  | X <sup>(2)</sup>      | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup>                           | X <sup>(2)</sup> |

| Tamper inputs   N/A    |          |                     |                      | N/A     | х       | х       | х                                                  | х                   | х                                                                                                   | х                             | х                                                                    | x                                                 | x                     | х                | х                | х                                          | Х                |

| Defigurable level detection   N/A   X   X   X   X   X   X   X   X   X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                     | for low-<br>power    | N/A     | x       | ×       | х                                                  | ×                   | x                                                                                                   | x                             | ×                                                                    | x                                                 | x                     | X                | x                | x                                          | x                |

| Number of internal tamper events   N/A   A   A   A   A   A   A   A   A   A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                     |                      | N/A     | Х       | Х       | x                                                  | Х                   | X                                                                                                   | х                             | Х                                                                    | X                                                 | X                     | X                | X                | х                                          | х                |

| V <sub>BAT</sub> mode pins N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tion     |                     |                      | N/A     | х       | х       | х                                                  | х                   | х                                                                                                   | х                             | х                                                                    | х                                                 | х                     | x                | х                | х                                          | х                |

| V <sub>BAT</sub> mode pins N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | er detec |                     |                      | N/A     | 4       | 4       | 13                                                 | 7                   | N/A                                                                                                 | 5                             | 10                                                                   | 11                                                | 9                     | 4                | 4                | 11                                         | 9                |

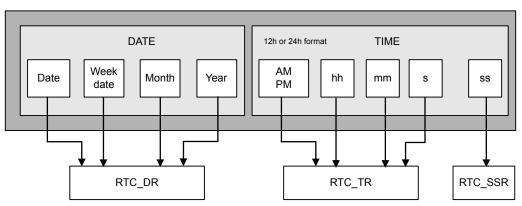

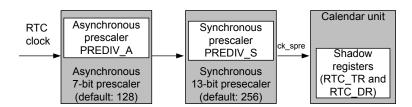

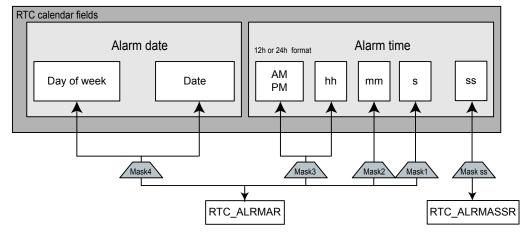

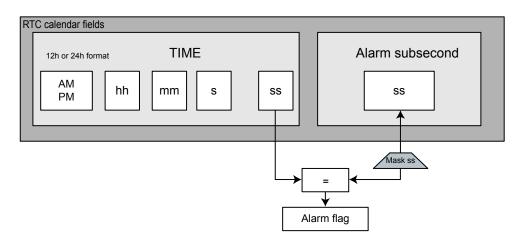

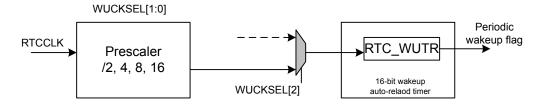

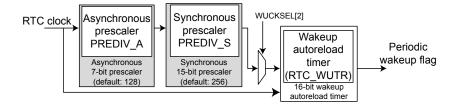

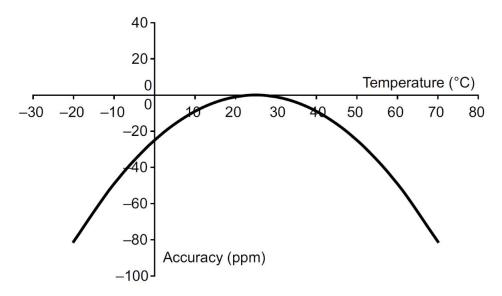

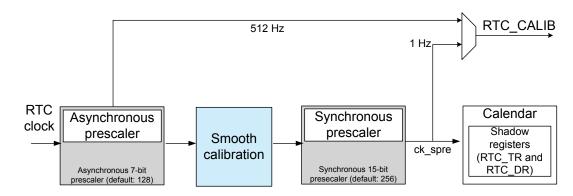

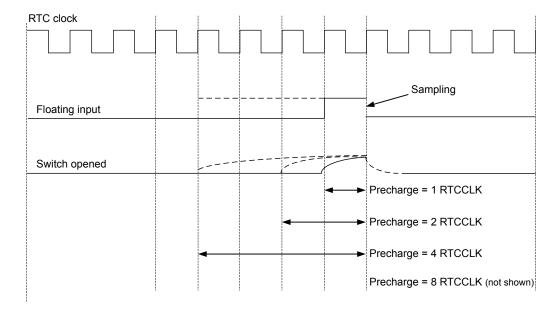

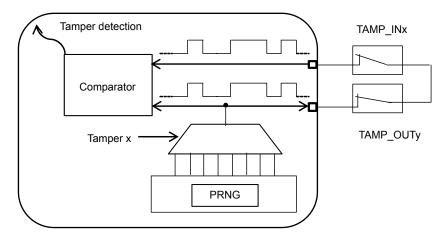

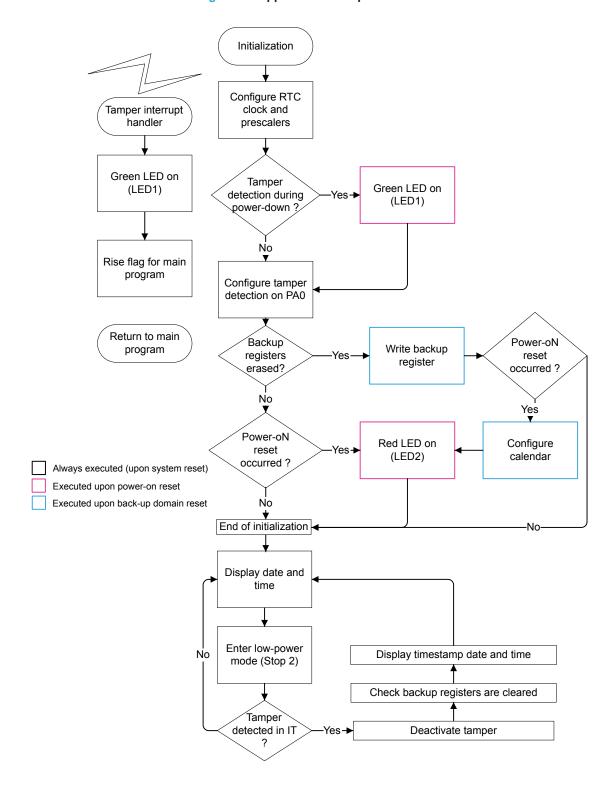

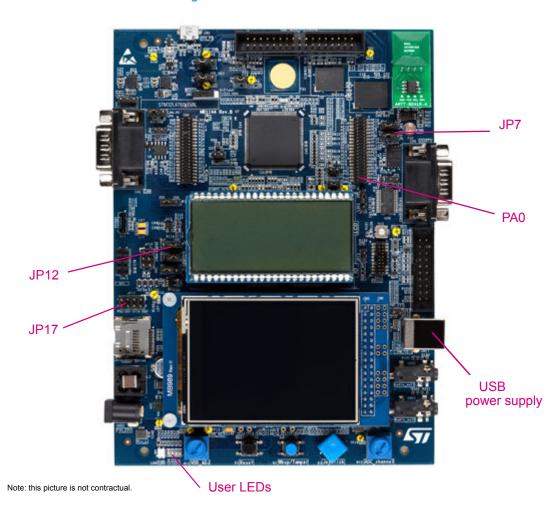

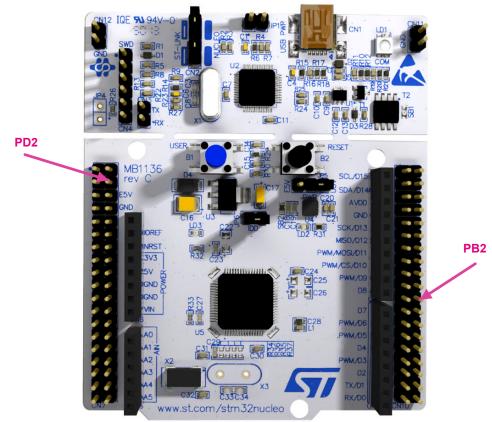

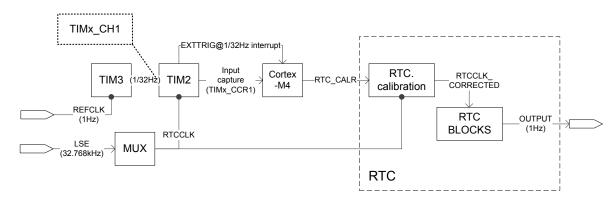

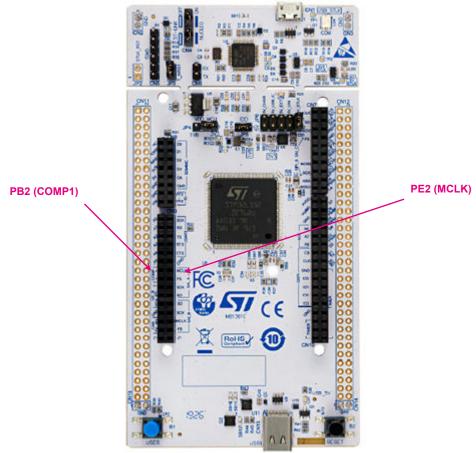

| V <sub>BAT</sub> mode pins N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Tamp     |                     |                      | N/A     | 2       | 3       |                                                    | 3                   | 3 (4)                                                                                               | 8                             | 7                                                                    | 8                                                 | 5                     | 3                | 5                | 8                                          | 6 (6 pins)       |