# AN4904 Application note

Migration of microcontroller applications from STM32F1 Series to STM32F4 Access lines

#### Introduction

For more and more applications using STM32 products, it is important to migrate a project easily to a different microcontroller in the same product family.

Migrating an application to a different microcontroller is often needed when product requirements grow, putting extra demands on memory size, or increasing the number of I/Os. On the other hand, cost reduction objectives may force you to switch to smaller components and shrink the PCB area.

This application note is intended to help analyze the steps you need to migrate from an existing STM32F1 Series based design to STM32F4 Access lines. It groups together all the most important information and lists the vital aspects that you need to address.

The current document lists the 'full set' of features for STM32F1 and the equivalent features of STM32F401/410/411/412/413/423 (Access lines) products when available. To fully benefit from this application note, you should be familiar with the STM32 microcontroller documentation available from <a href="https://www.st.com">www.st.com</a> with a particular focus on the documents listed below.

#### STM32F401/410/411/412/413/423 lines:

- STM32F401xB/C and STM32F401xD/E reference manual (RM0368)

- STM32F410 reference manual (RM0401)

- STM32F412 reference manual (RM0402)

- STM32F411xC/E reference manual (RM0383)

- STM32F413/423 reference manual(RM0430)

- All the STM32F401/410/411/412/413/423 lines' datasheets.

#### STM32F1 Series:

- STM32F1xx reference manual (RM0008)

- STM32F1xx reference manual (RM0041)

- STM32F1xx datasheets

- STM32F1 Flash and EEPROM programming manuals (PM0068, PM0056, PM0075).

Table 1. Applicable products

| Туре             | Product Series / line                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------|

| Microcontrollers | STM32F1 Series<br>STM32F401 line<br>STM32F410 line<br>STM32F411 line<br>STM32F412 line<br>STM32F413/423 line |

December 2016 DocID029695 Rev 2 1/38

Contents AN4904

### **Contents**

| 1 | Hard  | lware migration                                       | 5  |

|---|-------|-------------------------------------------------------|----|

| 2 | Boot  | mode selection                                        | 8  |

| 3 | Perip | oheral migration                                      | 11 |

|   | 3.1   | STM32 product cross-compatibility                     | 11 |

|   | 3.2   | Memory mapping                                        | 14 |

|   | 3.3   | DMA                                                   | 16 |

|   | 3.4   | Interrupts                                            | 22 |

|   | 3.5   | RCC                                                   | 26 |

|   |       | 3.5.1 Maximum clock frequency versus Flash wait state | 28 |

|   |       | 3.5.2 Peripheral access configuration                 | 30 |

|   |       | 3.5.3 Peripheral clock configuration                  | 31 |

|   | 3.6   | PWR                                                   | 32 |

|   | 3.7   | RTC                                                   | 33 |

|   | 3.8   | GPIO                                                  | 34 |

|   | 3.9   | EXTI                                                  | 34 |

|   | 3.10  | Flash                                                 | 35 |

|   | 3.11  | ADC                                                   | 36 |

| 4 | Revi  | sion history                                          | 37 |

AN4904 List of figures

# List of figures

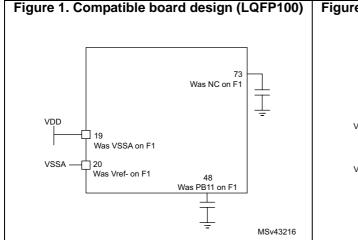

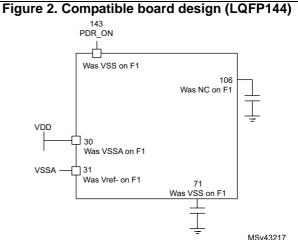

| Figure 1. | Compatible board design (LQFP100) | 7 |

|-----------|-----------------------------------|---|

| Figure 2. | Compatible board design (LQFP144) | 7 |

List of tables AN4904

### List of tables

| Table 1.  | Applicable products                                                              | 1      |

|-----------|----------------------------------------------------------------------------------|--------|

| Table 2.  | Package availability                                                             |        |

| Table 3.  | STM32F1 Series and STM32F401/410/411/412/413/423 lines pin out differences (QFP  | ) 6    |

| Table 4.  | STM32F1 Series and STM32F401/410/411/412/413/423 lines ball out differences (BGA | ۱) . 6 |

| Table 5.  | Boot modes                                                                       | 8      |

| Table 6.  | Bootloader interfaces                                                            | 9      |

| Table 7.  | STM32 peripheral compatibility between STM32F1 Series and                        |        |

|           | STM32F401/410/411/412/413/423 lines                                              | . 12   |

| Table 8.  | Bus mapping differences between STM32F1 Series and                               |        |

|           | STM32F401/410/411/412/413/423 lines                                              | . 14   |

| Table 9.  | DMA request differences migrating from STM32F1 Series to                         |        |

|           | STM32F401/410/411/412/413/423 lines                                              | . 17   |

| Table 10. | Interrupt vector differences between STM32F401/410/411/412/413/423 lines and     |        |

|           | STM32F1 Series                                                                   | . 22   |

| Table 11. | RCC differences between STM32F401/410/411/412/413/423 lines and                  |        |

|           | STM32F1 Series                                                                   | . 26   |

| Table 12. | Number of wait states according to CPU clock (HCLK) frequency for                |        |

|           | STM32F401 line                                                                   | . 28   |

| Table 13. | Number of wait states according to CPU clock (HCLK) frequency                    |        |

|           | for STM32F410/411/412 lines                                                      | . 28   |

| Table 14. | Number of wait states according to CPU clock (HCLK) frequency                    |        |

|           | for STM32F413/423 line                                                           |        |

| Table 15. | RCC registers used for peripheral access configuration                           |        |

| Table 16. | Peripheral clock configuration                                                   | . 31   |

| Table 17. | PWR differences between STM32F401/410/411/412/413/423 lines and                  |        |

|           | STM32F1 Series                                                                   | . 32   |

| Table 18. | RTC differences between STM32F401/410/411/412/413/423 lines and                  |        |

|           | STM32F1 Series                                                                   | . 33   |

| Table 19. | EXTI differences between STM32F1 Series and                                      |        |

|           | STM32F401/410/411/412/413/423 lines                                              | . 34   |

| Table 20. | Flash differences between STM32F1 Series and                                     |        |

| T 11 04   | STM32F401/410/411/412/413/423 lines                                              | . 35   |

| Table 21. | Differences between the ADC peripheral of STM32F1 Series and                     | 0.0    |

| T 11 00   | STM32F401/410/411/412/413/423 lines                                              |        |

| Table 22  | Document revision history                                                        | 37     |

AN4904 Hardware migration

## 1 Hardware migration

The available packages for the STM32F1 Series and STM32F401/410/411/412/413/423 lines are listed in *Table 2*.

Table 2. Package availability<sup>(1)</sup>

|          |                       | STI  | M32F1 Se | ries |              | STM32F401/410/411/412/413/423 lines |      |      |      |              |

|----------|-----------------------|------|----------|------|--------------|-------------------------------------|------|------|------|--------------|

| Package  | F100<br>value<br>line | F101 | F102     | F103 | F105<br>/107 | F401                                | F410 | F411 | F412 | F413<br>/423 |

| LQFP144  | Х                     | Х    | -        | Х    | -            | -                                   | -    | -    | Х    | Х            |

| LQFP100  | Х                     | Х    | -        | Х    | Х            | Х                                   | -    | Х    | Х    | Х            |

| LQFP64   | Х                     | Х    | Х        | Х    | Х            | Х                                   | Х    | Х    | Х    | Х            |

| LQFP48   | Х                     | Х    | Х        | Х    | -            | -                                   | Х    | -    | -    | -            |

| UFBGA144 | -                     | -    | -        | -    | -            | -                                   | -    | -    | Х    | Х            |

| UFBGA100 | -                     | -    | -        | Х    | _            | Х                                   | -    | Х    | Х    | Х            |

| UFBGA64  | -                     | -    | -        | -    | -            | -                                   | Х    | -    | -    | -            |

| LFBGA144 | -                     | -    | -        | Х    | -            | -                                   | -    | -    | -    | -            |

| LFBGA100 | -                     | -    | -        | Х    | Х            | -                                   | -    | -    | -    | -            |

| TFBGA64  | Х                     | -    | -        | Х    | -            | -                                   | -    | -    | -    | -            |

| WLCSP81  | -                     | -    | -        | -    | -            | -                                   | -    | -    | -    | Х            |

| WLCSP64  | -                     | -    | -        | Х    | -            | -                                   | -    | -    | Х    | -            |

| WLCSP49  | -                     | -    | -        | -    | -            | Х                                   | -    | Х    | -    | -            |

| WLCSP36  | -                     | -    | -        | -    | -            | -                                   | Х    | -    | -    | -            |

| UFQFPN48 | -                     | -    | -        | -    | -            | Х                                   | Х    | Х    | Х    | Х            |

| VFQFPN36 | -                     | Х    | -        | Х    | -            | -                                   | -    | -    | -    | -            |

<sup>1. &#</sup>x27;X' denotes available package.

Hardware migration AN4904

The STM32F401/410/411/412/413/423 lines and STM32F1 Series present a high level of pin compatibility. Most peripherals share the same pins in the two families.

The transition from the STM32F1 Series to the STM32F401/410/411/412/413/423 lines is easy since only a few pins are impacted (refer to *Table 3* and *Table 4*).

Table 3. STM32F1 Series and STM32F401/410/411/412/413/423 lines pin out differences (QFP)<sup>(1)</sup>

|       | Package / | pin number |        | Signal / supply name |                                        |  |  |

|-------|-----------|------------|--------|----------------------|----------------------------------------|--|--|

| QFP48 | QFP64     | QFP100     | QFP144 | STM32F1 Series       | STM32F401/410/411/412/413/423<br>lines |  |  |

| 5     | 5         | 12         | 23     | PD0-OSC_IN           | PH0-OSC_IN                             |  |  |

| 6     | 6         | 13         | 24     | PD1-OSC_OUT          | PH1-OSC_OUT                            |  |  |

| -     | -         | 19         | 30     | VSSA                 | VDD                                    |  |  |

| -     | -         | 20         | 31     | VREF-                | VSSA                                   |  |  |

| 22    | 30        | 48         | -      | PB11                 | VCAP_1                                 |  |  |

| -     | -         | -          | 71     | VSS                  | VCAP_1                                 |  |  |

| -     | -         | 73         | 106    | NC                   | VCAP_2                                 |  |  |

| -     | -         | -          | 143    | VSS                  | PDR_ON                                 |  |  |

| -     | -         | -          | 95     | VDD                  | VDDUSB                                 |  |  |

<sup>1.</sup> Dependence on product package availability.

Table 4. STM32F1 Series and STM32F401/410/411/412/413/423 lines ball out differences (BGA)<sup>(1)</sup>

| Package / k | oall location | Signa          | I / supply name                        |

|-------------|---------------|----------------|----------------------------------------|

| UFBGA100    | LFBGA144      | STM32F1 Series | STM32F401/410/411/412/413/423<br>lines |

| -           | C11           | NC             | VDDUSB                                 |

| -           | H7            | VSS            | VCAP_1                                 |

| -           | G9            | VSS            | VCAP_2                                 |

| НЗ          | -             | VDD            | PDR_ON                                 |

| -           | E5            | VSS            | PDR_ON                                 |

| E3          | H5            | VSS            | BYPASS_REG                             |

| C11         | -             | NC             | VCAP_2                                 |

| L11         | -             | PB11           | VCAP_1                                 |

<sup>1.</sup> Dependence on product package availability.

Note:

The STM32F1 Series proposes an LFBGA100 package that has a different ball out and size than the UFBGA100. It is not compatible with the STM32F401/410/411/412/413/423 lines' UFBGA100 package.

The STM32F103 is proposed in a WLCSP64 package, which is not compatible with that of the STM32F412.

6/38 DocID029695 Rev 2

AN4904 Hardware migration

# Recommendations for migration from an STM32F1 Series board to an STM32F401/410/411/412/413/423 line board

The VSSA pin (pin 19 on QFP100) is now used as VDD in the STM32F401/410/411/412/413/423 lines.

For STM32F410 LQFP64 package, there is no PD2 pin, it is replaced by PB11.

On STM32F401/410/411/412/413/423 lines there are no PD0 and PD1 pins; they are replaced by PH0 and PH1 respectively.

*Figure 1* and *Figure 2* show examples of board designs that are compatible with both the STM32F1 Series and STM32F401/410/411/412/413/423 lines.

Boot mode selection AN4904

### 2 Boot mode selection

Both the STM32F401/410/411/412/413/423 lines and the STM32F1 Series can select between 3 boot-mode options:

- boot from main Flash memory

- boot from SRAM

- boot from system memory.

*Table 5* summarizes the different configurations available for selecting the boot mode.

Table 5. Boot modes

|       | STM32F401/410/411/412/413/423/F1<br>boot mode selection |                      | Aliasing                                        |

|-------|---------------------------------------------------------|----------------------|-------------------------------------------------|

| BOOT1 | воото                                                   |                      | _                                               |

| Х     | 0                                                       | Main Flash<br>memory | Main Flash memory is selected as the boot space |

| 0     | 1                                                       | System memory        | System memory is selected as the boot space     |

| 1     | 1                                                       | Embedded SRAM        | Embedded SRAM is selected as the boot space     |

AN4904 Boot mode selection

#### **Embedded boot loader**

The embedded boot loader is located in the system memory, programmed by ST during production. It is used to reprogram the Flash memory using one of the serial interfaces shown in *Table 6*.

Table 6. Bootloader interfaces<sup>(1)</sup>

|            |                                                                         | s <sup>-</sup>  | TM32F1 Se                  | eries                                            |                        | STM32F4 lines    |               |                        |  |  |

|------------|-------------------------------------------------------------------------|-----------------|----------------------------|--------------------------------------------------|------------------------|------------------|---------------|------------------------|--|--|

| Peripheral | Pin                                                                     | STM32<br>F10xxx | STM32<br>F105xx/<br>F107xx | STM32<br>F10xxx<br>XL-<br>density <sup>(2)</sup> | STM32<br>F401/<br>F411 | STM32<br>F410    | STM32<br>F412 | STM32<br>F413/<br>F423 |  |  |

| DFU        | USB_DM (PA11)<br>USB_DP (PA12)                                          | Х               | Х                          | Х                                                | Х                      | -                | Х             | Х                      |  |  |

| CAN2       | CAN2_RX (PB5)<br>CAN2_TX (PB6)                                          | -               | X                          | -                                                | -                      | -                | -             | -                      |  |  |

| CANZ       | CAN2_RX (PB5)<br>CAN2_TX (PB13)                                         | -               | -                          | -                                                | -                      | _                | х             | Х                      |  |  |

| USART1     | USART1_TX (PA9)<br>USART1_RX (PA10)                                     | Х               | Х                          | Х                                                | Х                      | Х                | Х             | х                      |  |  |

| USART2     | USART2_TX (PD5)<br>USART2_RX (PD6)                                      | -               | Х                          | Х                                                | Х                      | -                | Х             | х                      |  |  |

| USARIZ     | USART2_TX (PA2)<br>USART2_RX (PA3)                                      | -               | -                          | -                                                | -                      | Х                | -             | -                      |  |  |

| USART3     | USART3_TX (PB10)<br>USART3_RX (PB11)                                    | -               | -                          | -                                                | -                      | -                | х             | х                      |  |  |

| I2C1       | I2C1_SCL (PB6)<br>I2C1_SDA (PB7)                                        | -               | -                          | -                                                | Х                      | Х                | х             | Х                      |  |  |

| I2C2       | I2C2_SCL (PB10)<br>I2C2_SDA (PB11)                                      | -               | -                          | -                                                | Х                      | Х                | -             | -                      |  |  |

| 1202       | I2C2_SCL (PF0)<br>I2C2_SDA (PF1)                                        | -               | -                          | -                                                | -                      | -                | х             | х                      |  |  |

| I2C3       | I2C3_SCL (PA8)<br>I2C3_SDA (PB4)                                        | -               | -                          | -                                                | Х                      | -                | х             | Х                      |  |  |

| 1204       | I2C2_SCL (PB10)<br>I2C2_SDA(PB3)                                        | -               | -                          | -                                                | -                      | X <sup>(3)</sup> | -             | -                      |  |  |

| I2C4       | I2C2_SCL (PB15)<br>I2C2_SDA(PB14)                                       | -               | -                          | -                                                | -                      | X <sup>(4)</sup> | х             | Х                      |  |  |

| SDI4       | SPI1_NSS (PA4)<br>SPI1_SCK (PA5)<br>SPI1_MISO (PA6)<br>SPI1_MOSI (PA7)  | -               | -                          | -                                                | х                      | X <sup>(4)</sup> | х             | х                      |  |  |

| SPI1       | SPI1_NSS (PA15)<br>SPI1_SCK (PA5)<br>SPI1_MISO (PB4)<br>SPI1_MOSI (PB5) | -               | -                          | -                                                | -                      | X <sup>(3)</sup> | -             | -                      |  |  |

Boot mode selection AN4904

Table 6. Bootloader interfaces<sup>(1)</sup> (continued)

|            |                                                                            | S <sup>-</sup>  | ГМ32F1 Se                  | eries                                            | STM32F4 lines          |               |               |                        |

|------------|----------------------------------------------------------------------------|-----------------|----------------------------|--------------------------------------------------|------------------------|---------------|---------------|------------------------|

| Peripheral | Pin                                                                        | STM32<br>F10xxx | STM32<br>F105xx/<br>F107xx | STM32<br>F10xxx<br>XL-<br>density <sup>(2)</sup> | STM32<br>F401/<br>F411 | STM32<br>F410 | STM32<br>F412 | STM32<br>F413/<br>F423 |

| SPI2       | SPI2_NSS (PB12)<br>SPI2_SCK (PB13)<br>SPI2_MISO (PB14)<br>SPI2_MOSI (PB15) | -               | -                          | -                                                | ×                      | -             | -             | -                      |

| 3712       | SPI2_NSS (PB12)<br>SPI2_SCK (PB13)<br>SPI2_MISO (PC2)<br>SPI2_MOSI (PC3)   | -               | -                          | -                                                | -                      | X             | -             | -                      |

| SPI3       | SPI3_NSS (PA15)<br>SPI3_SCK (PC10)<br>SPI3_MISO (PC11)<br>SPI3_MOSI (PC12) | -               | -                          | -                                                | X                      | -             | х             | х                      |

| SPI4       | SPI3_NSS (PE11)<br>SPI3_SCK (PE12)<br>SPI3_MISO (PE13)<br>SPI3_MOSI (PE14) | -               | -                          | -                                                | -                      | -             | -             | Х                      |

<sup>1.</sup> For smaller packages please verify pin and peripheral availability.

- 3. For STM32F410Tx devices.

- 4. For STM32F410Cx/Rx devices.

Note: Please refer to AN2606 for more details of the bootloader.

<sup>2.</sup> STM32F101xx and STM32F103xx microcontrollers where the Flash memory density ranges between 768 Kbytes and 1 Mbyte.

### 3.1 STM32 product cross-compatibility

The STM32 Series embeds a set of peripherals which can be classified in three categories:

- Peripherals that are common to all products. These peripherals are identical on all

products, so they have the same structure, registers and control bits. There is no need

to perform any firmware change to keep the same functionality at the application level

after migration. All the features and behavior remain the same.

- Peripherals that present minor differences from one product to another (usually

differences due to the support of new features). Migrating from one product to another

is very easy and does not require any significant new development effort.

- Peripherals which have been considerably modified from one product to another (new architecture, new features and so on). For this category of peripherals, migration requires new development at application level.

Table 7 gives a general overview of this classification.

Table 7. STM32 peripheral compatibility between STM32F1 Series and STM32F401/410/411/412/413/423 lines

|                          |            |                       | Numb                            | er of inst            | ances                 |                                | Compatibility         |                       |                                                                                                                                                                                                       |

|--------------------------|------------|-----------------------|---------------------------------|-----------------------|-----------------------|--------------------------------|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peripherals              |            | STM32<br>F1<br>Series | STM32<br>F401/<br>F411<br>lines | STM32<br>F410<br>line | STM32<br>F412<br>line | STM32<br>F413/<br>F423<br>line | Software              | Pinout                | Comments                                                                                                                                                                                              |

|                          | QuadSPI    | 0                     | 0                               | 0                     | 1                     | 1                              | NA                    | NA                    | New QuadSPI added for<br>STM32F412/413/423 lines                                                                                                                                                      |

|                          | SPI/I2S    | 3/2                   | 4/2<br>5/2                      | 3/3                   | 5/5                   | 5/5                            | Full<br>Compatibility | Partial compatibility | Full compatibility for the same feature.  Some alternate functions are not mapped on the same GPIO.                                                                                                   |

| Communication interfaces | 12C        | 2                     | 3                               | 3                     | 4                     | 4                              | Full<br>Compatibility | Partial compatibility | Full compatibility for the same feature.  Some alternate functions are not mapped on the same GPIO.  For STM32F410/412/413/423 lines the new I2C interface supports the Fast-mode plus (up to 1 MHz). |

|                          | USART      | 5                     | 3                               | 3                     | 4                     | 10                             | Full<br>Compatibility | Full<br>Compatibility | Full compatibility for the same feature                                                                                                                                                               |

|                          | USB OTG FS | 1                     | 1                               | 0                     | 1                     | 1                              | Full compatibility    | Full compatibility    | Separate power rail for<br>STM32F412/413/423 lines                                                                                                                                                    |

|                          | SDIO       | 1                     | 1                               | 1                     | 1                     | 1                              | Full<br>Compatibility | Partial compatibility | SDIO only available for STM32F103 in STM32F1 Series                                                                                                                                                   |

|                          | CAN        | 2                     | 0                               | 0                     | 2                     | 3                              | Full compatibility    | Full compatibility    | Full compatibility for the same feature                                                                                                                                                               |

|                          | SAI        | 0                     | 0                               | 0                     | 0                     | 1                              | NA                    | NA                    | New SAI added for<br>STM32F413/423 line                                                                                                                                                               |

Table 7. STM32 peripheral compatibility between STM32F1 Series and STM32F401/410/411/412/413/423 lines (continued)

|                     |           | Numb                  | er of inst                      | ances                 |                       | Compatibility                  |                          |                                                           |                                                                   |

|---------------------|-----------|-----------------------|---------------------------------|-----------------------|-----------------------|--------------------------------|--------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|

| Pe                  | ripherals | STM32<br>F1<br>Series | STM32<br>F401/<br>F411<br>lines | STM32<br>F410<br>line | STM32<br>F412<br>line | STM32<br>F413/<br>F423<br>line | Software                 | Software Pinout Comments                                  |                                                                   |

|                     | GP        | 10                    | 7                               | 3                     | 10                    | 10                             |                          |                                                           |                                                                   |

| Timers              | Advanced  | 2                     | 1                               | 1                     | 2                     | 2                              | Full                     | Partial                                                   | Internal connections may differ.  Some pins are not mapped on the |

| Timers              | Basic     | 2                     | 0                               | 1                     | 2                     | 1                              | compatibility            | compatibility                                             | same GPIO.                                                        |

|                     | Low Power | 0                     | 0                               | 1                     | 0                     | 1                              |                          |                                                           |                                                                   |

| Ethernet            |           | 1                     | 0                               | 0                     | 0                     | 0                              | NA                       | NA                                                        | Ethernet peripheral not available on STM32F401/410/411/412 lines  |

| WWDG                |           | 1                     | 1                               | 1                     | 1                     | 1                              | Full<br>Compatibility    | NA                                                        | -                                                                 |

| IWDG                |           | 1                     | 1                               | 1                     | 1                     | 1                              | Full<br>Compatibility    | NA                                                        | -                                                                 |

| GPIO <sup>(1)</sup> |           | Up to<br>142 IOs      | Up to<br>81 IOs                 | Up to<br>50 IOs       | Up to<br>114 IOs      | Up to<br>114 IOs               | Full compatibility       | Full compatibility                                        | Full compatibility for the same feature                           |

| ADC                 |           | 3                     | 1                               | 1                     | 1                     | 1                              | Full compatibility       | NA                                                        | Full compatibility for the same feature                           |

| DAC                 |           | 2                     | 0                               | 1                     | 0                     | 2                              | Full compatibility       | NA                                                        | Full compatibility for the same feature                           |

| RCC                 |           | 1                     | 1                               | 1                     | 1                     | 1                              | Partial<br>Compatibility | NA                                                        | -                                                                 |

| PWR                 |           | 1                     | 1                               | 1                     | 1                     | 1                              | Full compatibility       | NA                                                        | Full compatibility for the same feature                           |

| DFSDM               |           | 0                     | 0                               | 0                     | 1                     | 2                              | NA                       | NA New DFSDM 4 channels / 8 filter for STM32F413/423 line |                                                                   |

| AES                 |           | 0                     | 0                               | 0                     | 0                     | 1                              | NA                       | NA                                                        | New AES 256 bits only for the STM32F423 device                    |

<sup>1.</sup> Maximum number of instances.

### 3.2 Memory mapping

The peripheral address mapping of the STM32F401/410/411/412/413/423 lines is different to that of the STM32F1 Series.

*Table 8* provides the peripheral address mapping correspondence between F1 and STM32F401/410/411/412/413/423 lines.

Table 8. Bus mapping differences between STM32F1 Series and STM32F401/410/411/412/413/423 lines

| Davimhaval             | S     | TM32F1 Series    | STM32F401/4 | 10/411/412/413/423 lines   |

|------------------------|-------|------------------|-------------|----------------------------|

| Peripheral             | Bus   | Bus Base address |             | Base address               |

| Backup registers (BKP) | APB1  | 0x4000 6C00      | NA          |                            |

| I2S2ext                |       |                  |             | 0x4000 3400                |

| I2S3ext                | ]<br> |                  |             | 0x4000 4000                |

| UART8                  | - NA  | IVA              |             | 0x4000 7C00 <sup>(1)</sup> |

| UART7                  |       |                  |             | 0x4000 7800 <sup>(1)</sup> |

| UART4                  |       | 0x4000 4C00      | APB1        | 0x4000 4C00 <sup>(1)</sup> |

| UART5                  | A DD4 | 0x4000 5000      |             | 0x4000 5000 <sup>(1)</sup> |

| CAN1                   | APB1  | 0x4000 6400      |             | 0x4000 6400 <sup>(2)</sup> |

| CAN2                   |       | 0x4000 6800      |             | 0x4000 6800 <sup>(2)</sup> |

| CAN3                   | NA    | 1                |             | 0x4000 6C00 <sup>(1)</sup> |

| I2C2                   | APB1  | 0x4000 5C00      |             | 0x4000 5800                |

| I2C3                   | NIA   | ,                | APB1        | 0x4000 5C00                |

| I2CFMP1                | - NA  |                  |             | 0x4000 6000                |

| DAC                    | APB1  | 0x4000 7400      | ADD4        | 0x4000 7400 <sup>(3)</sup> |

| LPTIM1                 | NA    | -                | APB1        | 0x4000 2400 <sup>(3)</sup> |

| TIM1                   | APB2  | 0x4001 2C00      |             | 0x4001 0000                |

| TIM8                   | NA    | ,                |             | 0x4001 0400                |

| USART1                 | APB2  | 0x4001 3800      |             | 0x4001 1000                |

| USART6                 | NA    | ,                |             | 0x4001 1400                |

| ADC1                   | APB2  | 0x4001 2400      | ADDO        | 0x4001 2000                |

| SPI4                   | NIA   | •                | — APB2      | 0x4001 3400                |

| SYSCFG                 | - NA  |                  |             | 0x4001 3800                |

| TIM9                   |       | 0x4001 4C00      |             | 0x4001 4000                |

| TIM10                  | APB2  | 0x4001 5000      |             | 0x4001 4400                |

| TIM11                  |       | 0x4001 5400      |             | 0x4001 4800                |

AN4904 Peripheral migration

Table 8. Bus mapping differences between STM32F1 Series and STM32F401/410/411/412/413/423 lines (continued)

| Davimbanal | S    | TM32F1 Series    | STM32F401/4 | STM32F401/410/411/412/413/423 lines |  |

|------------|------|------------------|-------------|-------------------------------------|--|

| Peripheral | Bus  | Bus Base address |             | Base address                        |  |

| SPI5       |      | _                |             | 0x4001 5000                         |  |

| DFSDM1     |      |                  |             | 0x4001 6000 <sup>(2)</sup>          |  |

| DFSDM2     | NIA  |                  | ADDO        | 0x4001 6400 <sup>(1)</sup>          |  |

| SAI1       | NA   |                  | APB2        | 0x4001 5800 <sup>(1)</sup>          |  |

| UART10     |      |                  |             | 0x4001 1C00 <sup>(1)</sup>          |  |

| UART9      |      |                  |             | 0x4001 1800 <sup>(1)</sup>          |  |

| ADC3       |      | 0x4001 3C00      | NA          |                                     |  |

| ADC2       |      | 0x4001 2800      | → NA        |                                     |  |

| GPIOA      |      | 0x4001 0800      |             | 0x4002 0000                         |  |

| GPIOB      |      | 0x4001 0C00      |             | 0x4002 0400                         |  |

| GPIOC      | APB2 | 0x4001 1000      |             | 0x4002 0800                         |  |

| GPIOD      |      | 0x4001 1400      | ALID4       | 0x4002 0C00                         |  |

| GPIOE      |      | 0x4001 1800      | — AHB1      | 0x4002 1000                         |  |

| GPIOF      |      | 0x4001 1C00      |             | 0x4002 1400                         |  |

| GPIOG      |      | 0x4001 2000      |             | 0x4002 1800                         |  |

| GPIOH      |      |                  |             | 0x4002 1C00                         |  |

| AES        | NA   |                  | ALIDO       | 0x5006 0000 <sup>(4)</sup>          |  |

| RNG        |      |                  | AHB2        | 0x5006 0800 <sup>(5)</sup>          |  |

| SDIO/SDMMC | AHB  | 0x4001 8000      | APB2        | 0x4001 2C00                         |  |

- 1. Only available in STM32F413/423 line.

- 2. Only available in STM32F412/413/423 lines.

- 3. Only available in STM32F410/413/423 lines.

- 4. Only available in the STM32F423 device.

- 5. Only available in STM32F410/412/413/423 lines.

Note: For more details about the system memory mapping please refer to reference manual or datasheet.

### 3.3 DMA

The STM32F401/410/411/412/413/423 lines implement an 'enhanced' DMA compared to the STM32F1 Series:

The STM32F1 Series embeds two DMA controllers, each controller has up to 7 channels. Each channel is dedicated to managing memory access requests from one or more peripherals. It has an arbiter for handling the priority between DMA requests.

The STM32F401/410/411/412/413/423 lines embed two DMA controllers, each

controller has 8 streams, and each stream is dedicated to managing memory access

requests from one or more peripherals. Each stream can have up to 8 channels

(requests) in total. Each has an arbiter for handling the priority between DMA requests.

AN4904 Peripheral migration

*Table 9* presents the correspondence between the peripheral DMA requests in the STM32F401/410/411/412/413/423 lines and in the STM32F1 Series.

Table 9. DMA request differences migrating from STM32F1 Series to STM32F401/410/411/412/413/423 lines

| Peripheral          | DMA request | STM32F1 Series                                                                                                                                                                                           | STM32F401/410/411/412/413/423<br>lines                                              |

|---------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| ADC1                | ADC1        | DMA1_Channel1                                                                                                                                                                                            | DMA2_Stream0<br>DMA2_Stream4                                                        |

| ADC3                | ADC3        | DMA2_Channel5                                                                                                                                                                                            | NA                                                                                  |

| DAG                 | DAC1        | DMA2_Channel3                                                                                                                                                                                            | DMA1_Stream5 <sup>(1)(2)</sup>                                                      |

| DAC                 | DAC2        | DMA2_Channel4                                                                                                                                                                                            | DMA1_Stream6 <sup>(2)</sup>                                                         |

|                     | SPI1_Rx     | DMA1_Channel2                                                                                                                                                                                            | DMA2_Stream0<br>DMA2_Stream2                                                        |

| SPI1                | SPI1_Tx     | DMA1_Channel3                                                                                                                                                                                            | DMA2_Stream3 DMA2_Stream5 DMA2_Stream2 <sup>(2)</sup>                               |

| enia.               | SPI2_Rx     | DMA1_Channel4                                                                                                                                                                                            | DMA1_Stream3                                                                        |

| SPI2                | SPI2_Tx     | DMA1_Channel5                                                                                                                                                                                            | DMA1_Stream4                                                                        |

| ODIO.               | SPI3_Rx     | DMA2_Channel1                                                                                                                                                                                            | DMA1_Stream0<br>DMA1_Stream2                                                        |

| SPI3                | SPI3_Tx     | DMA2_Channel1 [  DMA2_Channel2 [                                                                                                                                                                         | DMA1_Stream5<br>DMA1_Stream7                                                        |

| SPI4                | SPI4_Rx     | DMA2_Channel3  DMA2_Channel4  DMA1_Channel3  DMA1_Channel4  DMA1_Channel5  DMA2_Channel1  DMA2_Channel1  DMA2_Channel2  DMA2_Channel2  DMA2_Channel2  DMA2_Channel2  DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD | DMA2_Stream0 <sup>(3)</sup> DMA2_Stream3 <sup>(3)</sup> DMA2_Stream4 <sup>(2)</sup> |

|                     | SPI4_Tx     |                                                                                                                                                                                                          | DMA2_Stream1 <sup>(3)</sup><br>DMA2_Stream4 <sup>(3)</sup>                          |

|                     | SPI5_Rx     |                                                                                                                                                                                                          | DMA2_Stream5 <sup>(4)</sup><br>DMA2_Stream3 <sup>(5)</sup>                          |

| SPI5                | SPI5_Tx     | NA                                                                                                                                                                                                       | DMA2_Stream5 <sup>(4)</sup> DMA2_Stream6 <sup>(4)</sup> DMA2_Stream4 <sup>(5)</sup> |

| USART1              | USART1_Rx   | DMA1_Channel5                                                                                                                                                                                            | DMA2_Stream2<br>DMA2_Stream5                                                        |

|                     | USART1_Tx   | DMA1_Channel4                                                                                                                                                                                            | DMA2_ Stream7                                                                       |

| USART2              | USART2_Rx   | DMA1_Channel6                                                                                                                                                                                            | DMA1_Stream5 DMA1_ Stream7                                                          |

| USART2_RX USART2_TX | USART2_Tx   | DMA1_Channel7                                                                                                                                                                                            | DMA1_Stream6                                                                        |

|                     | USART3_Rx   | DMA1_Channel3                                                                                                                                                                                            | DMA1_Stream1                                                                        |

| USART3              | USART3_Tx   | DMA1_Channel2                                                                                                                                                                                            | DMA1_Stream3<br>DMA1_Stream4 <sup>(2)</sup>                                         |

Table 9. DMA request differences migrating from STM32F1 Series to STM32F401/410/411/412/413/423 lines (continued)

| Peripheral | DMA request | STM32F1 Series                 | STM32F401/410/411/412/413/423<br>lines                         |

|------------|-------------|--------------------------------|----------------------------------------------------------------|

| UART4      | UART4_Rx    | DMA2_Channel3                  | DMA1_Stream2 <sup>(2)</sup>                                    |

| UAR14      | UART4_Tx    | DMA2_Channel5                  | DMA1_Stream4 <sup>(2)</sup>                                    |

| USART6     | USART6_Rx   |                                | DMA2_Stream1<br>DMA2_Stream2                                   |

| UUARTU     | USART6_Tx   | - NA                           | DMA2_ Stream6<br>DMA2_ Stream7                                 |

|            | I2C1_Rx     | DMA1_Channel7                  | DMA1_Stream0<br>DMA1_Stream5                                   |

| 12C1       | I2C1_Tx     | DMA1_Channel6                  | DMA1_Stream6<br>DMA1_Stream7<br>DMA1_Stream1 <sup>(2)(5)</sup> |

| I2C2       | I2C2_Rx     | DMA1_Channel5                  | DMA1_Stream2<br>DMA1_Stream3                                   |

|            | I2C2_Tx     | DMA1_Channel5  DMA1_Channel4   | DMA1_Stream7                                                   |

| I2C3       | I2C3_Rx     | - NA                           | DMA1_Stream1<br>DMA1_Stream2                                   |

| 1203       | I2C3_Tx     |                                | DMA1_Stream4<br>DMA1_Stream5                                   |

| SDIO       | SDIO        | DMA2_Channel4                  | DMA2_Stream3<br>DMA2_Stream6                                   |

|            | TIM1_UP     | DMA1_Channel5                  | DMA2_Stream5                                                   |

|            | TIM1_TRIG   | DMA1_Channel4                  | DMA2_Stream0<br>DMA2_Stream4                                   |

|            | TIM1_COM    | DMA1_Channel4                  | DMA2_Stream4                                                   |

| TIM1       | TIM1_CH1    | DMA1_Channel2<br>DMA1_Channel6 | DMA2_Stream1 DMA2_Stream3 DMA2_Stream6                         |

|            | TIM1_CH2    | DMA1_Channel6                  | DMA2_Stream2<br>DMA2_Stream6                                   |

|            | TIM1_CH3    | DMA1_Channel6                  | DMA2_Stream6                                                   |

|            | TIM1_CH4    | DMA1_Channel4                  | DMA2_Stream4                                                   |

AN4904 Peripheral migration

Table 9. DMA request differences migrating from STM32F1 Series to STM32F401/410/411/412/413/423 lines (continued)

| Peripheral | DMA request | STM32F1 Series | STM32F401/410/411/412/413/423<br>lines                           |

|------------|-------------|----------------|------------------------------------------------------------------|

|            | TIM2_UP     | DMA1_Channel2  | DMA1_Stream1<br>DMA1_Stream7                                     |

|            | TIM2_CH1    | DMA1_Channel5  | DMA1_Stream5                                                     |

| TIM2       | TIM2_CH2    | DMA1_Channel7  | DMA1_Stream6                                                     |

|            | TIM2_CH3    | DMA1_Channel1  | DMA1_Stream1                                                     |

|            | TIM2_CH4    | DMA1_Channel7  | DMA1_Stream6<br>DMA1_Stream7                                     |

|            | TIM3_UP     | DMA1_Channel3  | DMA1_Stream2                                                     |

|            | TIM3_TRIG   | DMA1_Channel6  | DMA1_Stream4                                                     |

| TIM3       | TIM3_CH1    | DMA1_Channel6  | DMA1_Stream4                                                     |

| TINIS      | TIM3_CH2    | NA             | DMA1_Stream5                                                     |

|            | TIM3_CH3    | DMA1_Channel2  | DMA1_Stream7                                                     |

|            | TIM3_CH4    | DMA1_Channel3  | DMA1_Stream2                                                     |

|            | TIM4_UP     | DMA1_Channel7  | DMA1_Stream6                                                     |

| TIM4       | TIM4_CH1    | DMA1_Channel1  | DMA1_Stream0                                                     |

| 1 11014    | TIM4_CH2    | DMA1_Channel4  | DMA1_Stream3                                                     |

|            | TIM4_CH3    | DMA1_Channel5  | DMA1_Stream7                                                     |

|            | TIM5_UP     | DMA2_Channel2  | DMA1_Stream0<br>DMA1_Stream6                                     |

|            | TIM5_TRIG   | DMA2_Channel1  | DMA1_Stream1<br>DMA1_Stream3                                     |

| TIM5       | TIM5_CH1    | DMA2_Channel5  | DMA1_Stream2                                                     |

|            | TIM5_CH2    | DMA2_Channel4  | DMA1_Stream4                                                     |

|            | TIM5_CH3    | DMA2_Channel2  | DMA1_Stream0                                                     |

|            | TIM5_CH4    | DMA2_Channel1  | DMA1_Stream1<br>DMA1_Stream3                                     |

| TIM6       | TIM6_UP     | DMA2_Channel3  | DMA1_Stream1 <sup>(2)(5)</sup>                                   |

| TIM7       | TIM7_UP     | DMA2_Channel4  | DMA1_Stream2 <sup>(2)(5)</sup><br>DMA1_Stream4 <sup>(2)(5)</sup> |

Table 9. DMA request differences migrating from STM32F1 Series to STM32F401/410/411/412/413/423 lines (continued)

| Peripheral                | DMA request | STM32F1 Series | STM32F401/410/411/412/413/423<br>lines |

|---------------------------|-------------|----------------|----------------------------------------|

|                           | TIM8_UP     | DMA2_Channel1  | DMA2_Stream1                           |

|                           | TIM8_COM    | DMA2_Channel2  | DMA2_Stream7                           |

|                           | TIM8_TRIG   | DMA2_Channel2  | DMA2_Stream7                           |

|                           | TIM8_CH1    | DMA2_Channel3  | DMA2_Stream2                           |

| TIM8                      | TIM8_CH2    | DMA2_Channel5  | DMA2_Stream2<br>DMA2_Stream3           |

|                           | TIM8_CH3    | DMA2_Channel1  | DMA2_Stream2<br>DMA2_Stream4           |

|                           | TIM8_CH4    | DMA2_Channel2  | DMA2_Stream7                           |

| QUADSPI <sup>(2)(5)</sup> | QUADSPI     | NA             | DMA2_Stream7                           |

| DFSDM <sup>(2)(5)</sup>   | DFSDM1_FLT0 | NA             | DMA2_Stream0<br>DMA2_Stream6           |

| DESDIME ACT               | DFSDM1_FLT1 | NA D           | DMA2_Stream1<br>DMA2_Stream4           |

|                           | DFSDM2_FLT0 |                | DMA2_Stream0<br>DMA2_Stream4           |

| DEODMO(2)                 | DFSDM2_FLT1 | Ī              | DMA2_Stream1<br>DMA2_Stream5           |

| DFSDM2 <sup>(2)</sup>     | DFSDM2_FLT2 | - NA           | DMA2_Stream2<br>DMA2_Stream6           |

|                           | DFSDM2_FLT3 |                | DMA2_Stream3<br>DMA2_Stream7           |

| (2)                       | UART5_Rx    |                | DMA1_Stream0                           |

| UART5 <sup>(2)</sup>      | UART5_Tx    | - NA           | DMA1_Stream7                           |

| UART7 <sup>(2)</sup>      | UART7_Rx    | - NA           | DMA1_Stream3                           |

| O/MCT/                    | UART7_Tx    |                | DMA1_Stream1                           |

| UART8 <sup>(2)</sup>      | UART8_Rx    | - NA           | DMA1_Stream6                           |

| OAKTO                     | UART8_Tx    | INA            | DMA1_Stream0                           |

| UART9 <sup>(2)</sup>      | UART9_Rx    | - NA           | DMA2_Stream7                           |

| OAICI                     | UART9_Tx    |                | DMA2_Stream0                           |

| LICADT40(2)               | USART10_RX  | NA             | DMA2_Stream3<br>DMA2_Stream0           |

| USART10 <sup>(2)</sup>    | USART10_TX  | - NA           | DMA2_Stream5<br>DMA2_Stream7           |

Table 9. DMA request differences migrating from STM32F1 Series to STM32F401/410/411/412/413/423 lines (continued)

| Peripheral          | DMA request | STM32F1 Series | STM32F401/410/411/412/413/423 lines |

|---------------------|-------------|----------------|-------------------------------------|

| SAI1 <sup>(2)</sup> | SAI1_A      | NA             | DMA2_Stream1<br>DMA2_Stream3        |

| SAIT                | SAI1_B      |                | DMA2_Stream4<br>DMA2_Stream5        |

| AES <sup>(6)</sup>  | AES_IN      | NA             | DMA2_Stream6                        |

| ALG.                | AES_OUT     | 1 IVA          | DMA2_Stream5                        |

- 1. Only available in STM32F410 line.

- 2. Only available in STM32F413/423 line.

- 3. Not applicable for STM32F410 line.

- 4. Not applicable for STM32F401/410 lines.

- 5. Only available in STM32F412 line.

- 6. Only available in the STM32F423 device.

### 3.4 Interrupts

*Table 10* presents the interrupt vectors in the STM32F401/410/411/412/413/423 lines versus the STM32F1 Series.

Table 10. Interrupt vector differences between STM32F401/410/411/412/413/423 lines and STM32F1 Series

| Position | STM32F1 Series                                   | STM32F401/410/411/412/413/423<br>lines |

|----------|--------------------------------------------------|----------------------------------------|

| 0        | WWDG                                             | WWDG                                   |

| 1        | PVD                                              | PVD                                    |

| 2        | TAMPER                                           | TAMP_STAMP                             |

| 3        | RTC                                              | RTC_WKUP                               |

| 4        | FLASH                                            | FLASH                                  |

| 5        | RCC                                              | RCC                                    |

| 6        | EXTI0                                            | EXTI0                                  |

| 7        | EXTI1                                            | EXTI1                                  |

| 8        | EXTI2                                            | EXTI2                                  |

| 9        | EXTI3                                            | EXTI3                                  |

| 10       | EXTI4                                            | EXTI4                                  |

| 11       | DMA1_Channel1                                    | DMA1_Stream0                           |

| 12       | DMA1_Channel2                                    | DMA1_Stream1                           |

| 13       | DMA1_Channel3                                    | DMA1_Stream2                           |

| 14       | DMA1_Channel4                                    | DMA1_Stream3                           |

| 15       | DMA1_Channel5                                    | DMA1_Stream4                           |

| 16       | DMA1_Channel6                                    | DMA1_Stream5                           |

| 17       | DMA1_Channel7                                    | DMA1_Stream6                           |

| 18       | ADC1_2                                           | ADC                                    |

| 19       | CAN1_TX / USB_HP_CAN_TX                          | CAN1_TX                                |

| 20       | CAN1_RX0 / USB_LP_CAN_RX0                        | CAN1_RX0                               |

| 21       | CAN1_RX1                                         | CAN1_RX1                               |

| 22       | CAN1_SCE                                         | CAN1_SCE                               |

| 23       | EXTI9_5                                          | EXTI9_5                                |

| 24       | TIM1_BRK / TIM1_BRK _TIM9 (1)                    | TIM1_BRK / TIM9                        |

| 25       | TIM1_UP / TIM1_UP_TIM10 <sup>(1)</sup>           | TIM1_UP / TIM10                        |

| 26       | TIM1_TRG_COM / TIM1_TRG_COM_TIM11 <sup>(1)</sup> | TIM1_TRG_COM / TIM11                   |

| 27       | TIM1_CC                                          | TIM1_CC                                |

| 28       | TIM2                                             | TIM2                                   |

| 29       | TIM3                                             | TIM3                                   |

Table 10. Interrupt vector differences between STM32F401/410/411/412/413/423 lines and STM32F1 Series (continued)

| Position | STM32F1 Series (CORUM                               | STM32F401/410/411/412/413/423<br>lines |

|----------|-----------------------------------------------------|----------------------------------------|

| 30       | TIM4                                                | TIM4                                   |

| 31       | I2C1_EV                                             | I2C1_EV                                |

| 32       | I2C1_ER                                             | I2C1_ER                                |

| 33       | I2C2_EV                                             | I2C2_EV                                |

| 34       | I2C2_ER                                             | I2C2_ER                                |

| 35       | SPI1                                                | SPI1                                   |

| 36       | SPI2                                                | SPI2                                   |

| 37       | USART1                                              | USART1                                 |

| 38       | USART2                                              | USART2                                 |

| 39       | USART 3                                             | USART 3                                |

| 40       | EXTI15_10                                           | EXTI15_10                              |

| 41       | RTC_Alarm                                           | EXTI17 / RTC Alarm                     |

| 42       | OTG_FS_WKUP / USBWakeUp                             | EXTI18 / OTG_FS WKUP                   |

| 43       | TIM8_BRK / TIM8_BRK_TIM12 <sup>(1)</sup>            | TIM8_BRK_TIM12                         |

| 44       | TIM8_UP / TIM8_UP_TIM13 <sup>(1)</sup>              | TIM8_UP_TIM13                          |

| 45       | TIM8_TRG_COM /<br>TIM8_TRG_COM_TIM14 <sup>(1)</sup> | TIM8_TRG_COM_TIM14                     |

| 46       | TIM8_CC                                             | TIM8_CC                                |

| 47       | ADC3                                                | DMA1_Stream7                           |

| 48       | FSMC                                                | FSMC                                   |

| 49       | SDIO                                                | SDIO                                   |

| 50       | TIM5                                                | TIM5                                   |

| 51       | SPI3                                                | SPI3                                   |

| 52       | UART4                                               | UART4                                  |

| 53       | UART5                                               | UART5                                  |

| 54       | TIM6 / TIM6_DAC <sup>(1)</sup>                      | TIM6_GLB_IT/DAC1/DAC2 <sup>(1)</sup>   |

| 55       | TIM7                                                | TIM7                                   |

| 56       | DMA2_Channel1                                       | DMA2_Stream0                           |

| 57       | DMA2_Channel2                                       | DMA2_Stream1                           |

| 58       | DMA2_Channel3                                       | DMA2_Stream2                           |

| 59       | DMA2_Channel4 / DMA2_Channel4_5 <sup>(1)</sup>      | DMA2_Stream3                           |

| 60       | DMA2_Channel5                                       | DMA2_Stream4                           |

| 61       | ETH                                                 | DFSDM1_FLT0                            |

| 62       | ETH_WKUP                                            | DFSDM1_FLT1/ EXTI19(1)                 |

|          |                                                     |                                        |

Table 10. Interrupt vector differences between STM32F401/410/411/412/413/423 lines and STM32F1 Series (continued)

| Position | STM32F1 Series | STM32F401/410/411/412/413/423<br>lines |

|----------|----------------|----------------------------------------|

| 63       | CAN2_TX        | CAN2_TX                                |

| 64       | CAN2_RX0       | CAN2_RX0                               |

| 65       | CAN2_RX1       | CAN2_RX1                               |

| 66       | CAN2_SCE       | CAN2_SCE                               |

| 67       | OTG_FS         | OTG_FS                                 |

| 68       |                | DMA2_Stream5                           |

| 69       |                | DMA2_Stream6                           |

| 70       |                | DMA2_Stream7                           |

| 71       |                | USART6                                 |

| 72       |                | I2C3_EV                                |

| 73       |                | I2C3_ER                                |

| 74       |                | CAN3_TX                                |

| 75       |                | CAN3_RX0                               |

| 76       |                | CAN3_RX1                               |

| 77       |                | CAN3_SCE                               |

| 78       | NA.            | N/A                                    |

| 79       | - NA           | CRYPTO                                 |

| 80       |                | RNG                                    |

| 81       |                | FPU                                    |

| 82       |                | UART7                                  |

| 83       |                | UART8                                  |

| 84       |                | SPI4                                   |

| 85       |                | SPI5                                   |

| 87       |                | SAI1                                   |

| 88       |                | UART9                                  |

| 89       |                | UART10                                 |

| 92       |                | Quad-SPI                               |

Table 10. Interrupt vector differences between STM32F401/410/411/412/413/423 lines and STM32F1 Series (continued)

| Position  | STM32F1 Series                                        | STM32F401/410/411/412/413/423<br>lines |  |

|-----------|-------------------------------------------------------|----------------------------------------|--|

| 95        |                                                       | I2CFMP1 event/ I2C4_EV <sup>(1)</sup>  |  |

| 96        |                                                       | I2CFMP1 error/ I2C4_ER <sup>(1)</sup>  |  |

| 97        |                                                       | LPTIM1/EXTI23                          |  |

| 98        | NA                                                    | DFSDM2_FLT0                            |  |

| 99        |                                                       | DFSDM2_FLT1                            |  |

| 100       |                                                       | DFSDM2_FLT2                            |  |

| 101       |                                                       | DFSDM2_FLT3                            |  |

| Color key |                                                       |                                        |  |

|           | Same feature, but specification change or enhancement |                                        |  |

|           | Only in STM32F412/413/423 lines                       |                                        |  |

|           | Different Interrupt vector                            |                                        |  |

|           | Only in STM32F410/413/423 lines                       |                                        |  |

|           | Only in STM32F410/413/423 lines                       |                                        |  |

|           | Only in STM32F410/412/413/423 lines                   |                                        |  |

|           | Only in STM32F413/F423 line                           |                                        |  |

|           | Only in STM32F423 device                              |                                        |  |

<sup>1.</sup> Depending on the product line used.

### 3.5 RCC

The main differences related to the RCC (reset and clock controller), between the STM32F1 Series and the STM32F401/410/411/412/413/423 lines, are presented in *Table 11* below.

Table 11. RCC differences between STM32F401/410/411/412/413/423 lines and STM32F1 Series

| RCC                    | STM32F1 Series                                                                                                                                                                                 | STM32F401/410/411/412/413/423<br>lines                                                                         |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| HSI                    | 8 MHz RC factory and user trimmed                                                                                                                                                              | 16 MHz RC factory and user trimmed                                                                             |

| LSI                    | 40 kHz RC                                                                                                                                                                                      | 32 kHz                                                                                                         |

| HSE                    | Connectivity line: (1) 3 - 25 MHz Other lines: 4 - 16 MHz (up to 25 MHz in bypass mode)                                                                                                        | 4 - 26 MHz                                                                                                     |

| LSE                    | 32.768 kHz (up to 1 MHz in bypass mode) Available in backup domain (VBAT)                                                                                                                      | 32.768 kHz. Configurable drive/consumption (not in STM32F401 lines). Available in backup domain (VBAT).        |

| PLL                    | Connectivity line <sup>(1)</sup> :  3 PLLs Main PLL sources: HSI/2, HSE, PLL2 (through divider)  PLL2, PLL3 clocked by HSE through divider  Other lines:  1 PLL  The PLL sources are HSI, HSE. | Main PLL for system 1 PLL (PLLI2S) for I2S The PLL sources are HSI, HSE                                        |

| System clock source    | HSI, HSE or PLL                                                                                                                                                                                | HSI, HSE or PLL                                                                                                |

| System clock frequency | Up to 72 MHz 8 MHz after reset using HSI                                                                                                                                                       | Up to 84 MHz (STM32F401 line),<br>100 MHz<br>(STM32F410/411/412/413/423 lines)<br>16 MHz after reset using HSI |

| AHB frequency          | Up to 72 MHz                                                                                                                                                                                   | Up to 84 MHz (STM32F401 line),<br>100 MHz<br>(STM32F410/411/412/413/423 lines)                                 |

| APB1 frequency         | Up to 36 MHz                                                                                                                                                                                   | Up to 42 MHz (STM32F401 line),<br>50 MHz (STM32F410/411/412 lines)                                             |

| APB2 frequency         | Up to 72 MHz                                                                                                                                                                                   | Up to 84 MHz (STM32F401 line),<br>100 MHz (STM32F411 line)                                                     |

| RTC clock source       | LSI, LSE or HSE/128                                                                                                                                                                            | LSI, LSE or HSE (1 MHz) using 1/2, 1/3, 1/4 clock pre-divider                                                  |

AN4904 Peripheral migration

Table 11. RCC differences between STM32F401/410/411/412/413/423 lines and STM32F1 Series (continued)

| RCC                                           | STM32F1 Series                                                                                                                                                                                                                                                                                     | STM32F401/410/411/412/413/423<br>lines                                                                                                        |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| MCO clock source                              | MCO1 pin (PA8): (max 50 MHz) Connectivity line <sup>(1)</sup> : HSI, HSE, SYSCLK, PLLCLK/2, PLL2CLK, PLL3CLK/2, XT1 ext 3-25 MHz (OSC_IN), PLL3CLK Other lines: HSI, HSE, SYSCLK, PLLCLK/2                                                                                                         | MCO1 pin (PA8): HSI, LSE, HSE, PLLCLK MCO2 pin (PC9): HSE, PLLCLK, SYSCLK, PLLI2S With configurable prescaler, 1, 2, 3, 4, 5 for each output. |