# VIPower M0-7 H-Bridges for Automotive DC Motor Control

## Introduction

The VIPower M0-7 H-bridge family of fully integrated and protected H-bridges are designed to drive low or medium power automotive DC motors.

Each device in the family contains the monolithic double high side driver and two low side chips.

The following features render these devices ideal for numerous DC motor applications (e.g., door locks, washer pumps, fans, mirrors, etc.) in the rigorous automotive environment:

- · integrated logic for driving each MOS according to clockwise or anticlockwise motor rotation and braking

- possibility to employ PWM at 20 kHz for speed control

- · embedded protections against electrical or thermal stress

- · state of the art "MultiSense" diagnostic in ON and OFF state.

The purpose of this hardware design guide is to provide a comprehensive tool kit for design engineers to better understand M0-7 H-bridge behavior and the application usage context, as well as to facilitate embedding the design.

## 1 General items

The VIPower M0-7 H-bridges are built with same technology blocks featuring common functionality and a unique analogue diagnostic feedback pin. The individual devices, featuring specific  $R_{ds(on)}$  ( $R_{ONHS} + R_{ONLS}$ ) values for different load ranges, are listed below:

- VNH7040AY: 40 mΩ typical in a PowerSSO-36 TP package

- VNH7070AS / VNH7070BAS: 70 mΩ typical in a SO-16L package

- VNH7100AS / VNH7100BAS: 100 mΩ typical in a SO-16L package

## 1.1 Pin description

The M0-7 H-bridges are designed to be housed in the tiny 16-lead S0-16 plastic package and the 36-lead PowerSSO-36 package with three additional exposed pads on the surface for high thermal conductivity to the PCB, significantly increasing the power that can be managed by the device.

## 1.2 Common pins for all VNH7XXX devices

- INA, INB: voltage controlled input pin with hysteresis, compatible with 3 V and 5 V CMOS outputs. A logic high level on INA turns high side A (HSA) on; logic high level on INB turns high side B (HSB) on

- **PWM**: voltage controlled input pin with hysteresis, compatible with 3 V and 5 V CMOS outputs. A logic high level turns one or both the low side drivers on, depending on the state of INA, INB pins. A square wave signal up to 20 kHz can be used on this pin for motor speed control.

- Vcc: power leads are connected internally to the two HS drains and must be connected to the battery track

of the application.

- GNDA, GNDB: connected internally to the LSA, LSB sources and also represent the ground reference of the

device logic.

## 1.3 Additional pins for devices in SO-16N package

- OUTA, OUTB: these output power pins are connected to the external load. The OUTA leads are internally shorted to the sources of the HSA PowerMOS and the drains of the LSA PowerMOS; likewise for OUTB, HSB and LSB. All OUTA and OUTB leads must be connected to corresponding leads to ensure uniform distribution of the load current in the device.

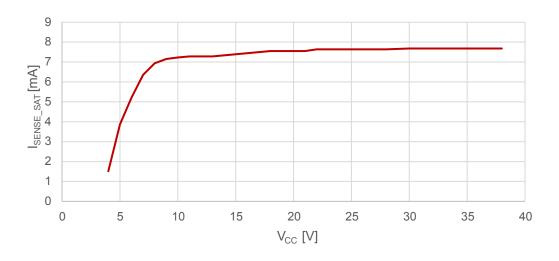

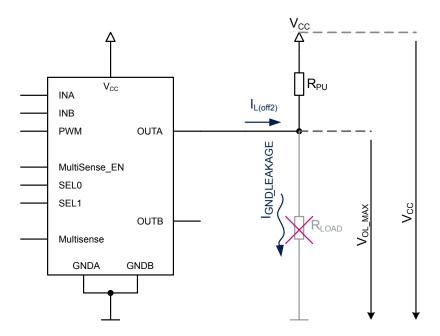

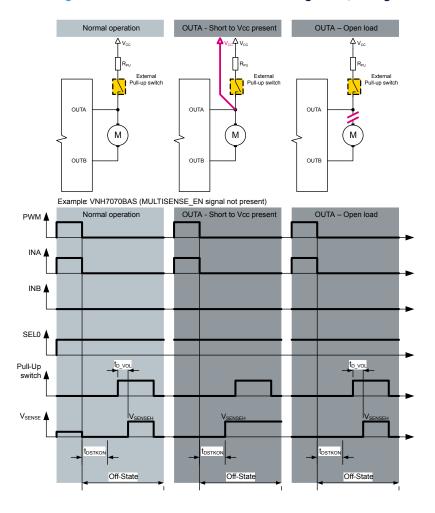

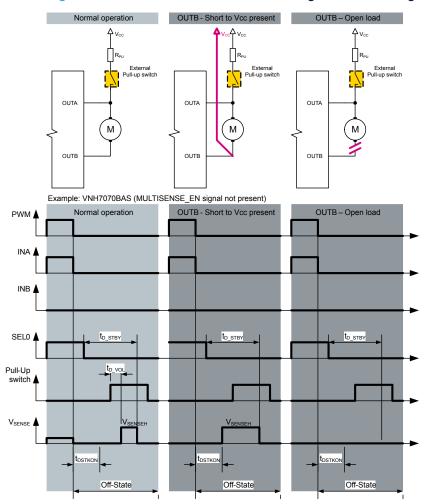

- **SEL0**: voltage controlled input pin with hysteresis, compatible with 3 V and 5 V CMOS outputs. A logic high level lets the device sense, through the CS output, the current flowing in the HSA or a fault relevant to the Output A; likewise for logic low, HSB and Output B. This pin also allows the CS to signal an open load or stuck to battery.

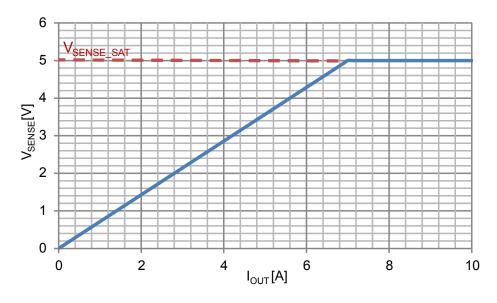

- CS: the multiplexed analog sense output pin:

- delivers a current proportional to the HSA output current if SEL0 is set high; likewise for HSB if SEL0 is set low

- develops a voltage flag for a failure on the relevant output in the ON state as well as the OFF state

## 1.4 Additional pins for devices in PowerSSO-36 TP package

- DRAIN\_LSA, SOURCE\_HSA and DRAIN\_LSB, SOURCE\_HSB: output power pins which must be shorted to corresponding pins on the PCB and connected to an external load terminal. This connection is the clockwise terminal and counter-clockwise of the bi-directional DC Motor for the A side and B side, respectively. Alternatively, if the device implements a two half H-bridge topology, the positive terminal of the mono-directional motor placed on branch A or branch B.

- MultiSense: the multiplexed analog sense output pin:

- delivers a current proportional to the HSA or HSB output current according to the settings SEL0 = high or low and SEL1= low

- in combination with SEL1 = low and SEL0 = high or low settings, it develops a voltage flag in case of failure on the relevant output in the ON state as well as the OFF state

- In combination with SEL1= high and SEL= high or low settings, it develops a voltage signal proportional to the high side chip temperature or Vcc voltage

AN5026 - Rev 2.0 page 2/109

- **SEL0, SEL1**: voltage controlled input pins with hysteresis, compatible with 3 V and 5 V CMOS outputs. They act as Multiplexer input pins thus:

- In the ON state: when SEL1 is low and SEL0 is high, they allow sensing the current flowing in the HSA

or a fault relevant to the Output A through the MultiSense output; likewise for SEL0 low, HSB and

Output B.

- In the OFF state: When SEL1 is low and SEL0 is high, they allow monitoring of the voltage level of DRAIN\_LS<sub>A</sub>, SOURCE\_HS<sub>A</sub> to detect and signal an open load or an output stuck to Vcc through the MultiSense output; likewise for SEL0 low, DRAIN\_LS<sub>B</sub>, SOURCE\_HS<sub>B</sub>

- Both in ON or OFF state: two combinations allow the MultiSense pin to develop a signal proportional to the high side driver chip temperature (SEL0=low, SEL1=high) or to the Vcc voltage (SEL0=SEL1=high)

- MultiSense\_EN: voltage controlled input pin with hysteresis, compatible with 3 V and 5 V CMOS outputs. A

logic high level enables the MultiSense output reading. A logic low level sets the MultiSense output to high

impedance.

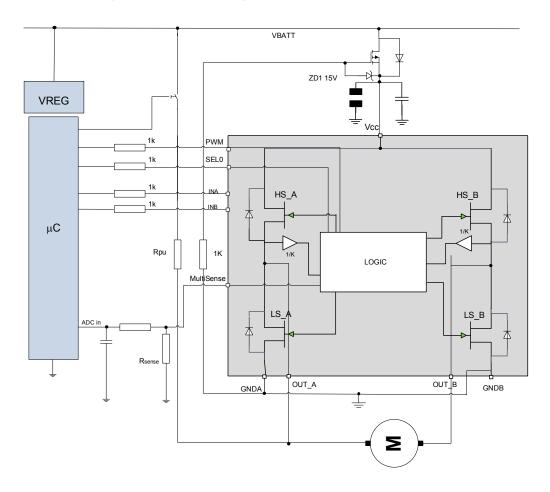

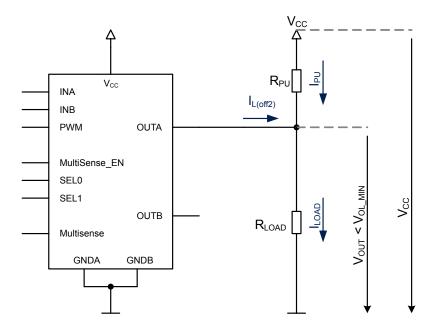

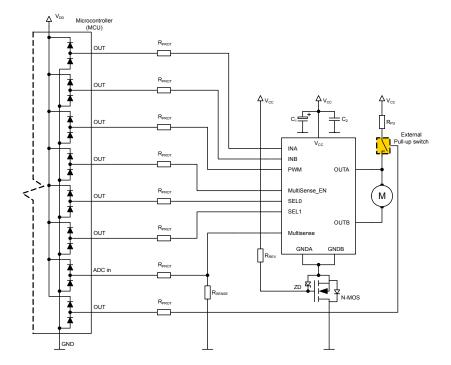

## 1.5 Basic application schematic

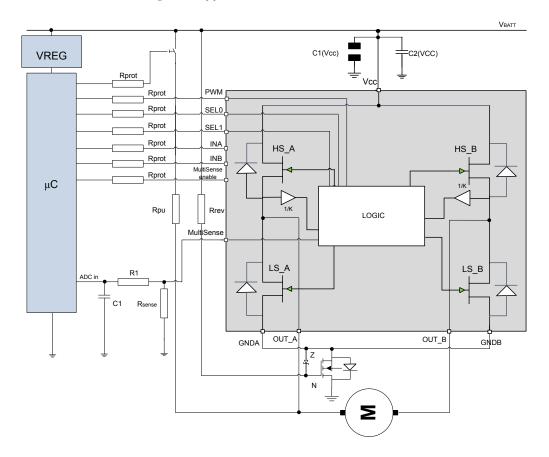

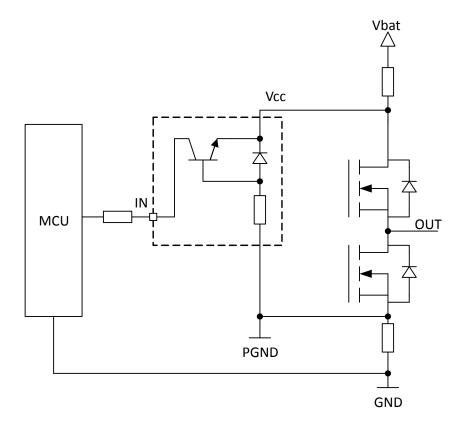

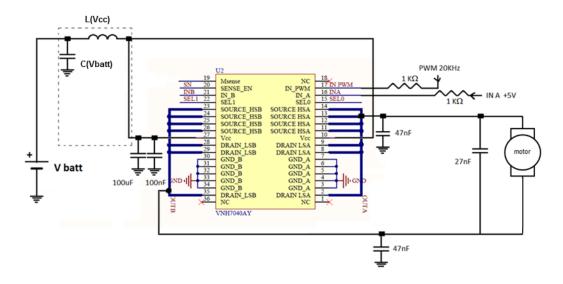

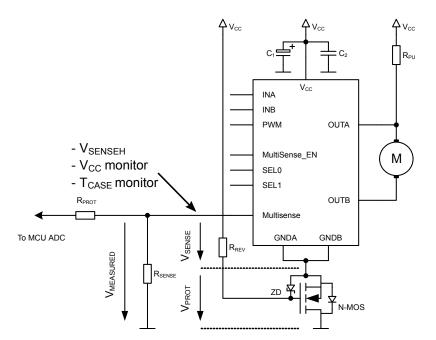

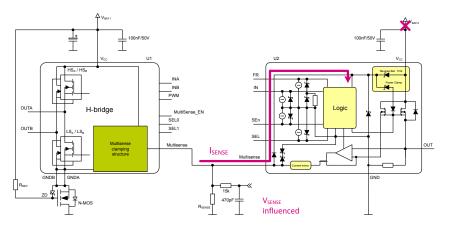

Figure 1. application schematic of VNH7040AY

- Rprot: resistors are placed in series with digital inputs (INA, INB, SEL0, SEL1, PWM, and MultiSense\_EN)

to limit the current in the input structures and in the microcontroller output structures to a safe value during

transient and reverse battery conditions. An appropriate value is 1k.

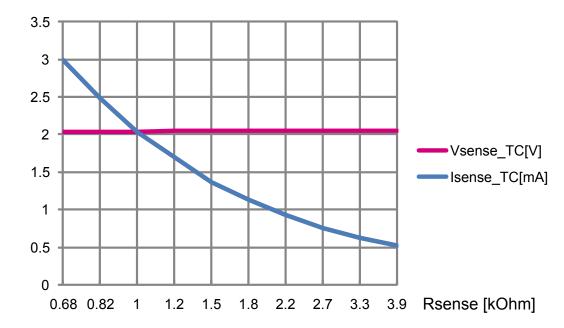

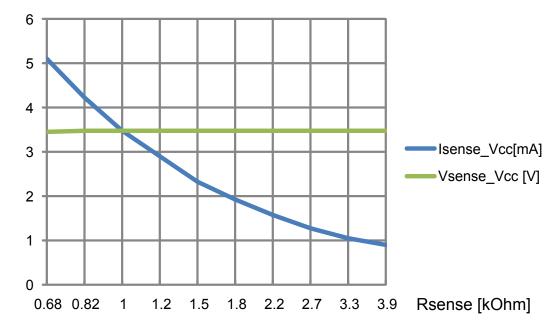

- Rsense: converts the current sense output current, which is proportional to the load current, into a voltage which can be read by the A/D converter of the microcontroller. The magnitude of Rsense should ensure an appropriate resolution range and granularity to monitor nominal current as well as detecting open load and overload events. A typical value is around 1 k $\Omega$  (see Section 5.1.4 Dimensioning the Rsense resistor). Rsense should not be lower than 765  $\Omega$  in order to sustain reverse battery polarity.

- R1, C1: an RC low pass-filter placed across the Rsense resistor to suppress HF noise. The time constant of this filter (RxC) should be long enough to suppress noise and short enough to allow MultiSense signal

AN5026 - Rev 2.0 page 3/109

- stabilization taking into account multiplexer delay and settling times in case of a shared microcontroller A/D port. C1 should be placed close to the MCU A/D input and its ground connection should be at the same potential as the ground of the A/D reference. R1 should be 10 k $\Omega$  and also limits the A/D input pin current.

- **C1(Vcc)**: this capacitor is used to suppress high energetic voltage transients developed, for instance, when the motor rotates and the OUTPUTs enter tristate conditions due to a battery line cut-off (see Section 3.2.2.1 C1(Vcc) capacitive filter on the supply line).

- **C2** (Vcc): the C2 capacitor helps suppress voltage transients that originate from other actuators connected in parallel and sharing the same battery line. This capacitor is only able to suppress low energetic short transient pulses and HF noise at the Vcc pin (see Section 3.2.2.2 C2(Vcc) capacitive filter on the IC supply line).

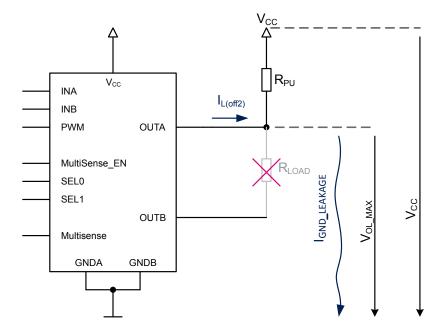

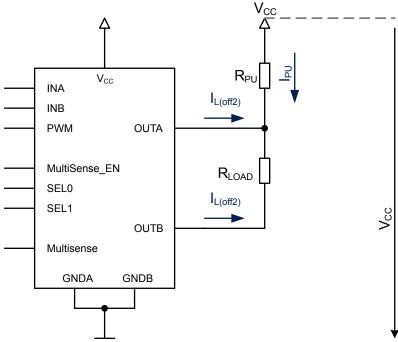

- **Rpu**: The pull up resistor is used for the open load detection of the OFF state (see Section 5.1.11 Open load detection in off-state). One Rpu is sufficient for a full H-bridge configuration. Two Rpu are required for a two half (one for each half) H-bridge configuration

- N, Rrev and Z: represent the reverse battery network. The N-MOS with source connected to the ground pins

of VNH7XXX and drain on Power GND provides reverse battery and battery negative fast transient

protection. Its gate needs to be connected through Rrev = 100 kΩ resistor to the battery track and a Zener

diode Z is required between its gate and source to clamp the gate voltage during positive transients on the

battery track (see Section 3.2.2 Design verification checks and Section 3.2.3 Overview of capacitor C1(Vcc)

assessment).

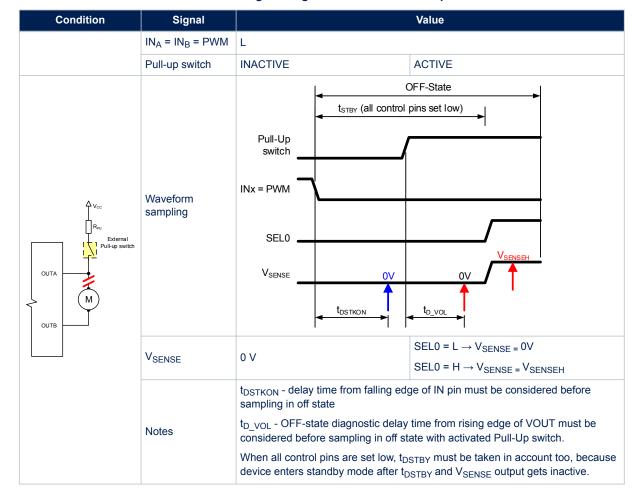

## 1.6 Operating modes

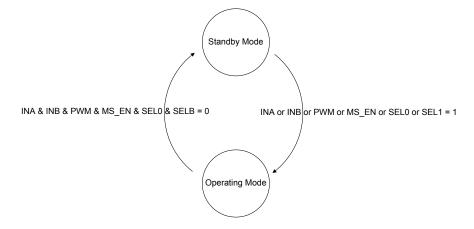

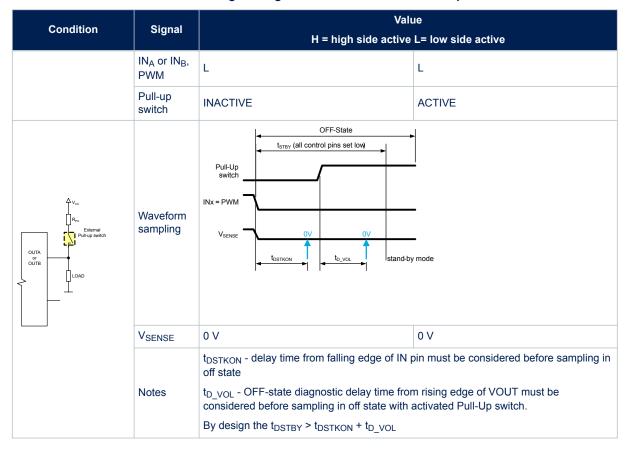

The VNH7XXX H-bridges have the following main states (see Figure 2. H-bridge operating modes):

- Operating mode: occurs when at least one of the input signals is set to logic level high. This condition

includes the OFF state of both low side and high side MOSFETs (i.e., INA = INB = PWM = 0 V). The device

current consumption from the Vcc pin in the OFF state is a few mA (indicated as I<sub>S</sub> "off state-no-stanby" in

the datasheet).

- 2. Standby Mode: occurs when all input signals pins (INA, INB, PWM, SEL0, SEL1, MultiSense\_EN) are set to low. The current drawn by the bridge is 1μA max. from -40 °C to 85 °C in this mode. After the last input pin has been set to zero, the H-bridge only enters standby mode after a t<sub>D\_stby</sub> delay given in the datasheets (see Section 5.1.8 Entering standby-mode after an OVL event) to avoid triggering accidental standby due to the rapid commutation of all input pins to zero level. The device exits the standby condition when any of the IN, PWM, MultiSense\_EN or SELx pins is set high.

Figure 2. H-bridge operating modes

AN5026 - Rev 2.0 page 4/109

# 2 Embedded protections

VIPower M0-7 H-bridge drivers integrate advanced protection functions to protect both the power stage and the load. A Power MOSFET must be protected against overvoltage, overcurrent and over temperature events outside the safe operating area.

Typical overvoltage protection involves a clamp that allows switching on the PowerMOS during exposure to the stress. The Power MOSFET is current protected by a current limiter block or current latch circuitry. The Power MOSFET is protected against high temperature events both by thermal shut down and by a power limitation block that limits the junction temperature gradient with the time.

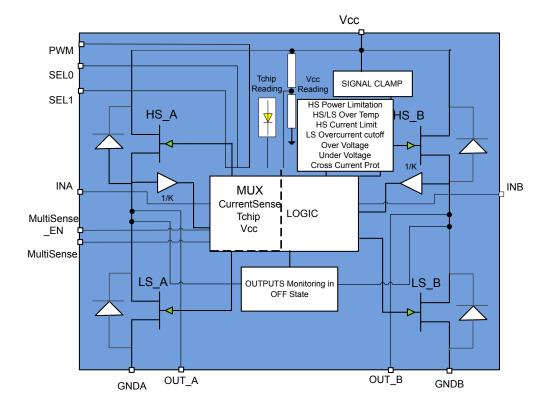

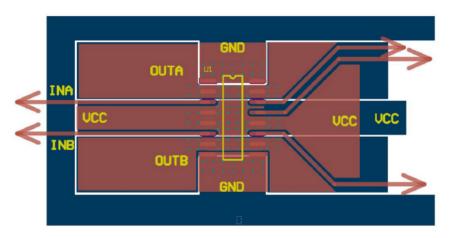

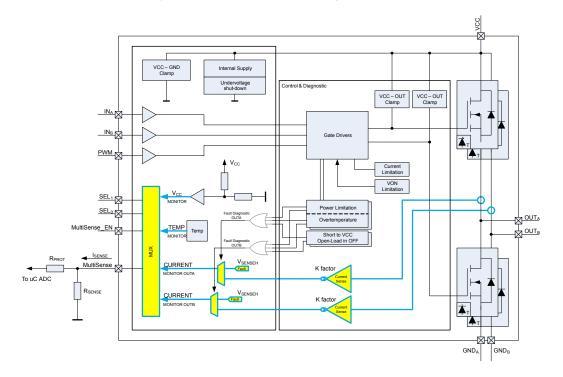

Figure 3. simplified internal blocks of a H-Bridge in PowerSSO-36 package

## 2.1 Protection against overvoltage

## 2.1.1 Overvoltage clamp

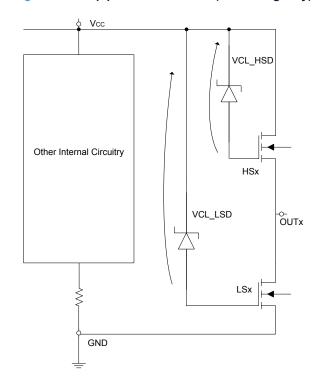

The device is protected against voltage transients on  $V_{CC}$  (e.g., ISO7637/2 transients) via the combination of the HS and LS power clamps (indicated in the datasheet as  $V_{CL\_HS}$  and  $V_{CL\_LS}$  respectively). As soon as a voltage transient higher than  $V_{CL\_HS} = V_{CL\_LS}$  occurs on  $V_{CC}$ , the LS is forced to work in the ohmic region while the HS is forced to work in the linear region. Therefore, the component subjected to the highest dissipation is the HSx. For negative transients applied across the device supply pin terminals, most of the current flows through the PowerMOS body diodes. It is not limited by anything other than the pulse generator intrinsic resistance. External circuitry is normally used to protect the device against such events.

AN5026 - Rev 2.0 page 5/109

Figure 4. Clamp protection circuits (for one leg only)

## 2.1.2 Device behavior with respect to ISO7637/2-2:2011(E) and ISO16750 standards

The table below describes the device performance with tests applied to VNH7XXX only, without components and accessed through  $V_{CC}$  and GND terminals only.

Status II is defined in ISO 7637-1 Function Performance Status Classification (FPSC) as: "The function does not perform as designed during the test but returns automatically to normal operation after the test".

During negative pulses (1 and 3a) the energy is transmitted through the series of body diodes of the HS and LS and the clamp signal circuit.

| Test Pulse<br>2011(E)                   | Test pulse severity level with<br>Status II functional<br>performance status |         | Minimum number of pulses or test | Burst cycle / pulse repetition time |        | Pulse duration and pulse<br>generator internal |  |  |

|-----------------------------------------|------------------------------------------------------------------------------|---------|----------------------------------|-------------------------------------|--------|------------------------------------------------|--|--|

|                                         | Level                                                                        | U s (1) | time                             | min                                 | max    | impedance                                      |  |  |

| 1                                       | III                                                                          | -112 V  | 500 pulses                       | 0.5 s                               |        | 2 ms, 10 Ω                                     |  |  |

| 2a                                      | III                                                                          | +55 V   | 500 pulses                       | 0.2 s                               | 5 s    | 50 μs, 2 Ω                                     |  |  |

| 3a                                      | IV                                                                           | -220 V  | 1h                               | 90 ms                               | 100 ms | 0.1 μs, 50 Ω                                   |  |  |

| 3b                                      | IV                                                                           | +150 V  | 1h                               | 90 ms                               | 100 ms | 0.1 μs, 50 Ω                                   |  |  |

| 4 (2)                                   | IV                                                                           | -7 V    | 1 pulse                          |                                     |        | 100 ms, 0.01 Ω                                 |  |  |

| Load dump according to ISO 16750-2:2010 |                                                                              |         |                                  |                                     |        |                                                |  |  |

| Test B - (3)                            |                                                                              | 40 V    | 5 pulse                          | 1 min                               |        | 400 ms, 2 Ω                                    |  |  |

Table 1. ISO 7637-2 - electrical transient conduction along supply line

- 1. U<sub>S</sub> is the peak amplitude as defined for each test pulse in ISO 7637-2:2011(E), chapter 5.6.

- 2. Test pulse from ISO 7637-2:2004(E).

- 3. With 40 V external suppressor referred to ground (-40°C <  $T_j$  < 150 °C).

AN5026 - Rev 2.0 page 6/109

#### 2.1.3 Device behavior after a load dump

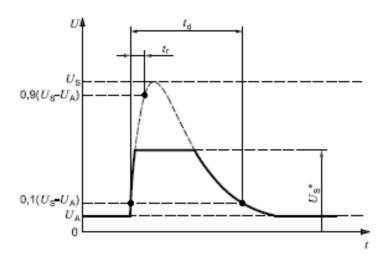

Load dump refers to the disconnection of the vehicle battery from the alternator while the battery is being charged. The bridges are subjected to pulses simulating this condition, according to ISO165750-2 (see Figure 6. Examples of waveforms relevant to ISO pulse 5b (load dump) applied to a VNH7XXX, where I<sub>MOV</sub> is the current flowing in the external transil during the pulse).

Figure 6. Examples of waveforms relevant to ISO pulse 5b (load dump) applied to a VNH7XXX

- Pulse condition: 400ms / 4Ω Voltage applied: +87V

- Temperature: +25°C

I<sub>MOV</sub> 10A/div

The PowerMOS energy of the LS and HS is not given in the datasheet since the device is intended to be used in H-bridge driver configuration. The inductive energy of the load in fact normally re-circulates in the PowerMOS body diodes.

External components like filtering capacitors on Vcc are necessary when the battery transients exceed those listed in the tables for ISO7637-2 and ISO 16750-2 (see Section 3 External protections).

AN5026 - Rev 2.0 page 7/109

## 2.2 Undervoltage protection

This function shuts down the device when battery voltage  $V_{BAT}$  is lower than  $V_{USD}$  (given in the datasheet) with an active high signal acting directly on the LS and HS gates, turning them off.

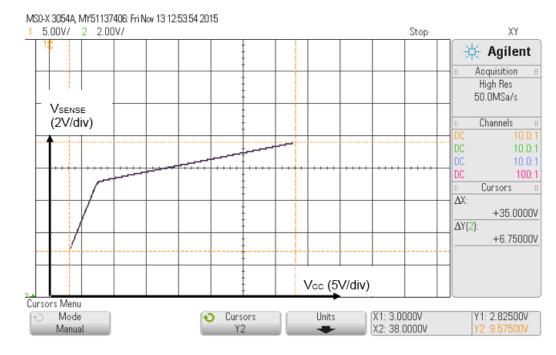

This protection validates the internal supply as soon as it is able to supply all logic blocks appropriately:

- For V<sub>CC</sub> decreasing from 13.5 V, the device is turned off at about 2.5 V; current sense is disabled from about 2.9 V V<sub>CC</sub>.

- Normal behavior resumes when V<sub>BAT</sub> reaches V<sub>USD</sub> + V<sub>USDhyst</sub>.

Note:

The undervoltage condition is not considered a fault condition so it is not reported by the diagnostic.

- As V<sub>CC</sub> rises, the device is typically turned on at 2.8 V.

- Current sense starts to operate at about 3 V.

Parameters which represent undervoltage behavior are given in the datasheet:

- V<sub>USD</sub> is the maximum shutdown voltage when V<sub>CC</sub> is decreasing

- V<sub>USD reset</sub> is the level which turns on the bridge when V<sub>CC</sub> is increasing3

- V<sub>USD hvst</sub> is the typical hysteresis of the two voltages.

### 2.3 Loss of VCC and loss of GND

#### 2.3.1 GND disconnection

Following GND disconnection, the device can stop normal operation (motor rotation control) but it must end up in a safe operating state with no motor activation.

## 2.3.1.1 Device GND pin disconnection

This can occur due to physical defects in PCB soldering.

Any H-bridge in an SO-16N package has four different GND pins, or 10 GND pins in a PowerSSO-36 TP package. These are split in two pairs, where each is connected to the relevant LS source.

A soldering issue causing all GND pins to be disconnected from the PCB is quite unlikely and, even if does occur, all four PowerMOS are switched off.

The device resumes normal operation once GND is reconnected.

#### 2.3.1.2 Disconnection of the module GND line

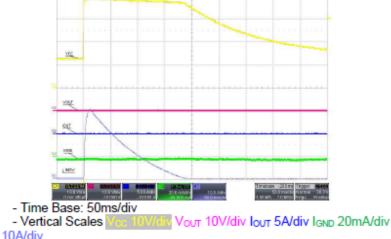

If the module GND line that supplies the VNH7xxx is disconnected, the device switches off immediately, as shown in the following figure.

As the H-bridge Power elements are OFF, any residual motor energy is dissipated in the external IC components, especially the capacitor on the V<sub>CC</sub> pin. This is charged and must be properly dimensioned (see Section 3.2.5.2 Capacitors on VNH7XXX Outputs (C(OUT)) and on Vcc (C2(Vcc))).

AN5026 - Rev 2.0 page 8/109

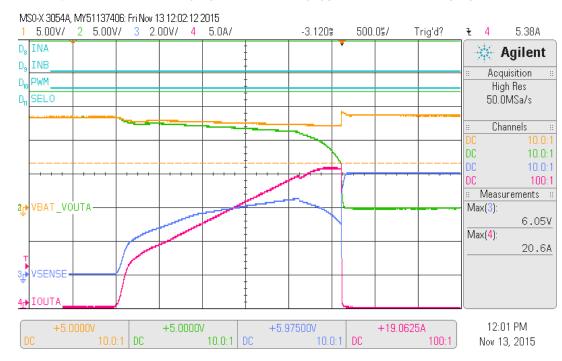

Figure 7. GND loss (INA, lout, Vbatt, Vsense)

In the figure above, where the device is alternatively driven clockwise and counter-clockwise:

- · red arrow: the device stops operation immediately after GND disconnection

- · white arrow: device restarts normal operation as the GND line is reconnected

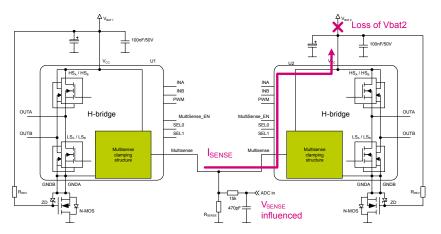

## 2.3.2 Loss of battery connection

Similar considerations are applicable to the battery where multiple pins (exposed pad included for PowerSSO-36 TP) are connected to the  $V_{CC}$  signal.

## 2.3.2.1 Battery line disconnection

When battery disconnection occurs, the device  $V_{CC}$  voltage starts to decrease since the bulk capacitor energy is used to supply the motor.

AN5026 - Rev 2.0 page 9/109

Figure 8. Battery loss (INA, lout, Vbatt, Vsense)

- red arrow: motor operation stops as the V<sub>CC</sub> undervoltage threshold is reached

- white arrow: operation restarts once battery is reconnected

Note: External precautions are necessary to avoid the load energy increasing voltage  $V_{CC}$  above  $V_{CLAMP}$ , which may damage the device.

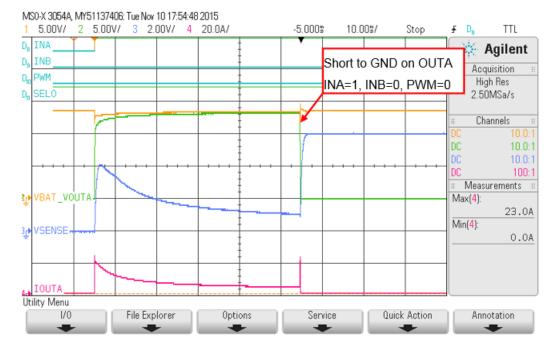

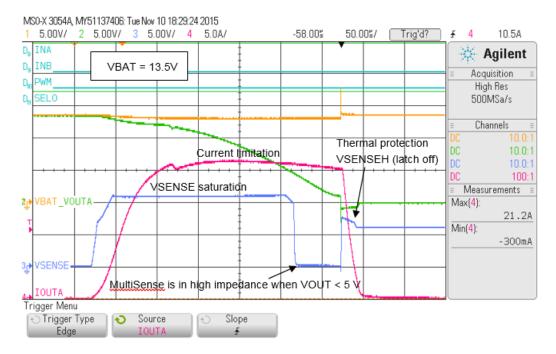

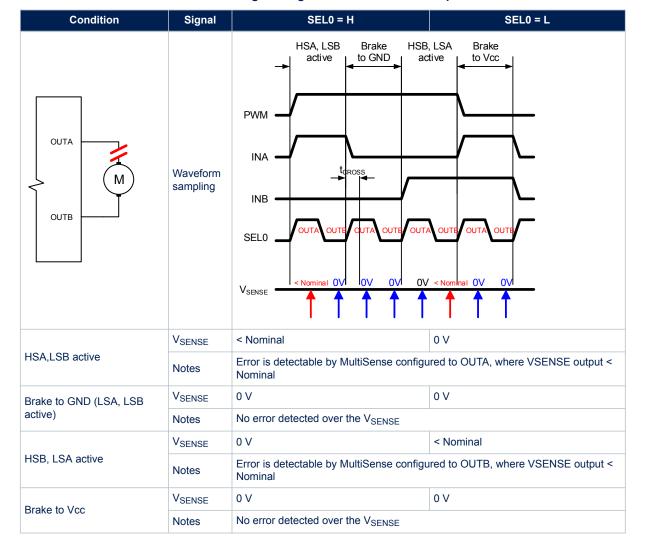

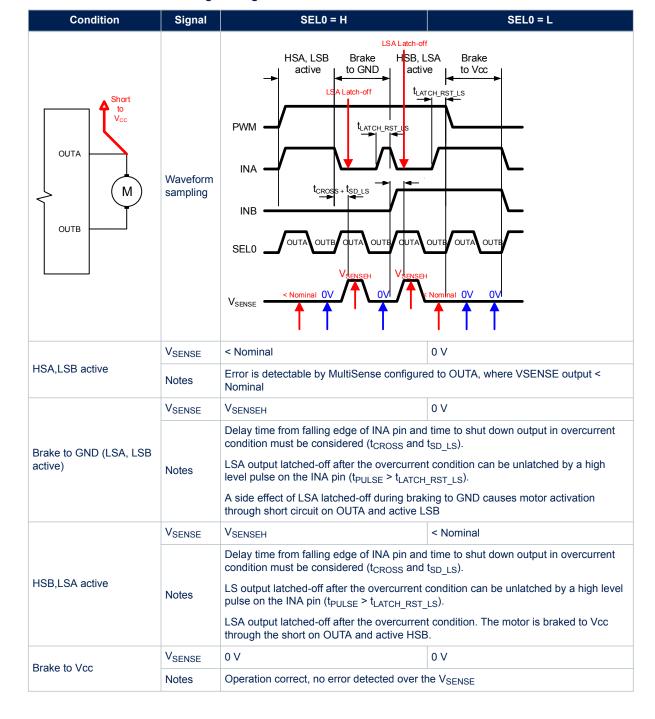

## 2.4 Short-circuit protection

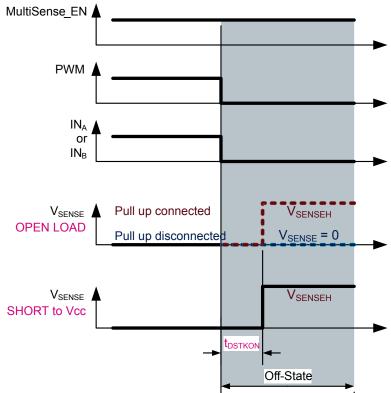

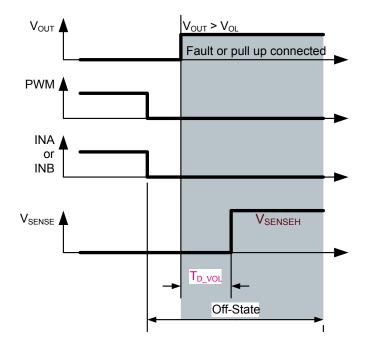

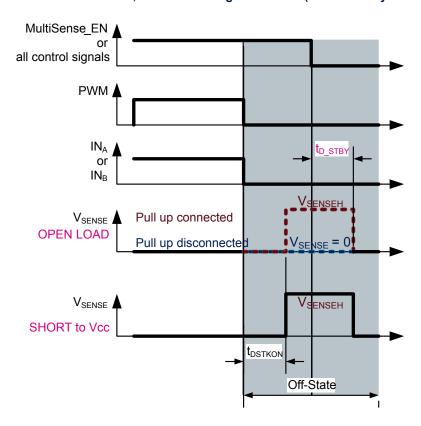

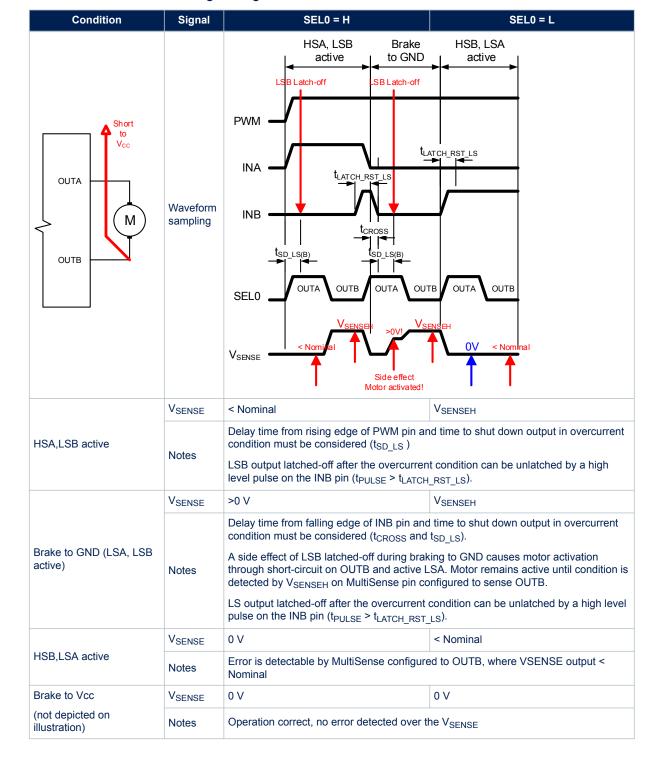

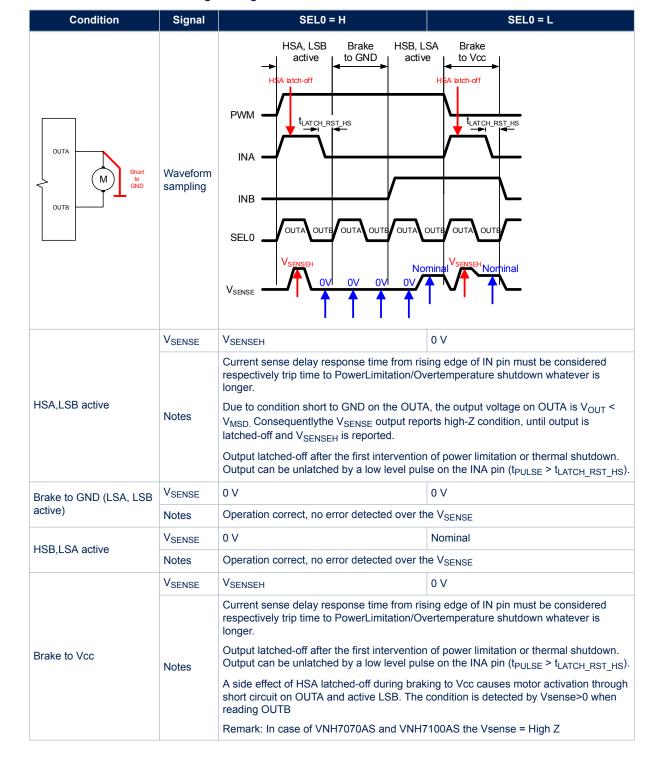

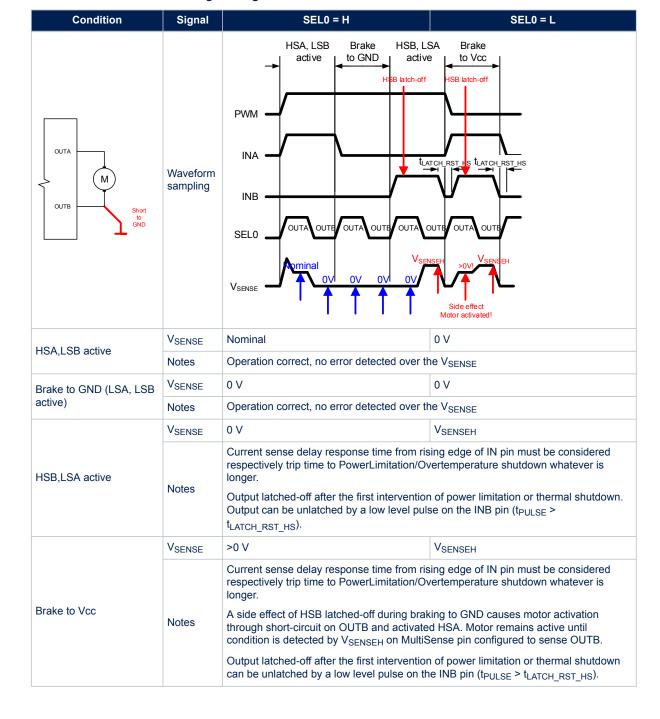

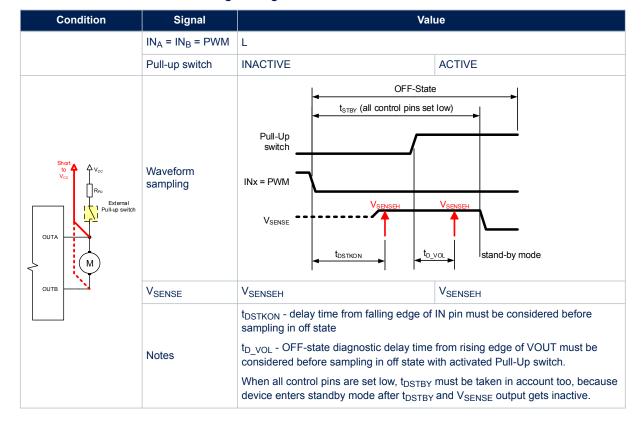

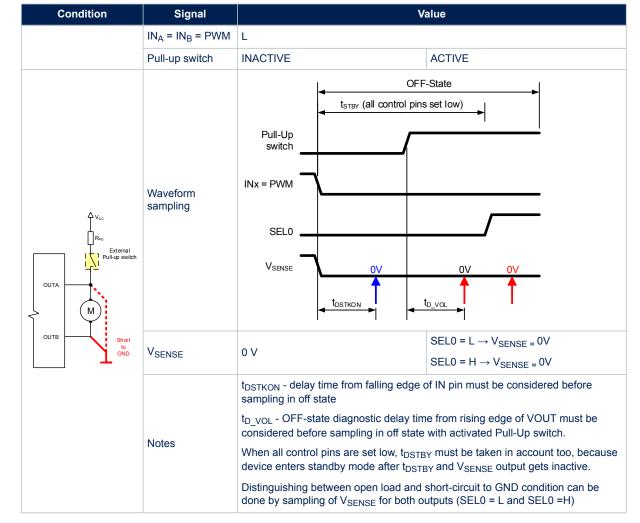

Short-circuit events are signaled by the diagnostic CS pin (MultiSense in VNH7040AY). In fault conditions, Vsense is pulled high to VsenseH on the selected leg (through SEL0 input signal).

## 2.4.1 Short-circuit on device outputs to car ground

For output shorted to GND, the High Side in the ON state is the stressed element in the VNH7XXX and the drain current rises well above nominal levels.

When the I<sub>LIMH</sub> threshold is reached, an embedded current limiter intervenes to protect the HS PowerMOS against dangerous current density. In this condition, the High Side PowerMOS works in the saturation region and dissipates high power due to simultaneous high voltage and high current.

At this point, the power limitation block circuit, designed to limit the fast thermal transients in the device to improve device lifetime, intervenes. It monitors the difference between the temperature read by a case temperature sensor embedded in the logic and the junction temperature measured by a sensor in the PowerMOS.

If the HS PowerMOS junction temperature exceeds the case temperature by about 60°C, the HS latches itself off.

The HS is protected against absolute maximum junction temperature (datasheet symbol  $T_{TSD\_HS}$ ) by the overtemperature thermal shutdown block.

In summary, the HS has the following protection circuits:

- Current Limiter: triggering of this protection is not signaled by CS (MultiSense) and does not cause device latch off

- Power Limitation circuit: triggering of this protection is signaled by CS (MultiSense) and causes device latch off

- Overtemperature shutdown circuit: triggering of this protection is signaled by CS (MultiSense) and causes

device latch off

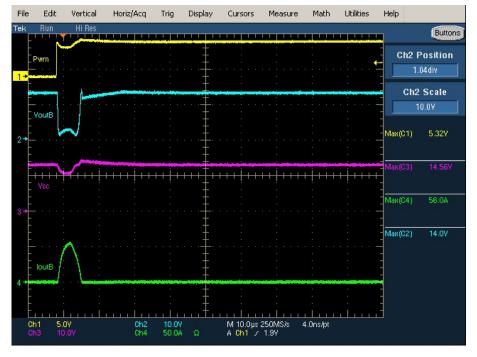

In the figure below, the device terminal A is shorted to GND and then switched on.

AN5026 - Rev 2.0 page 10/109

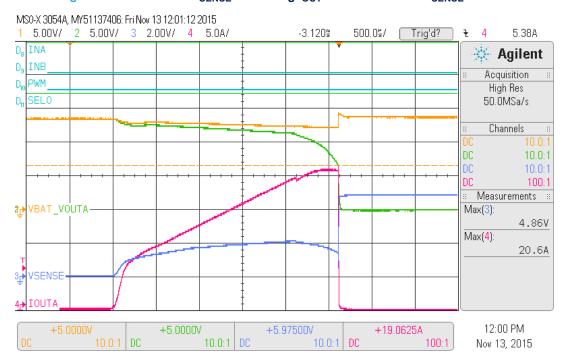

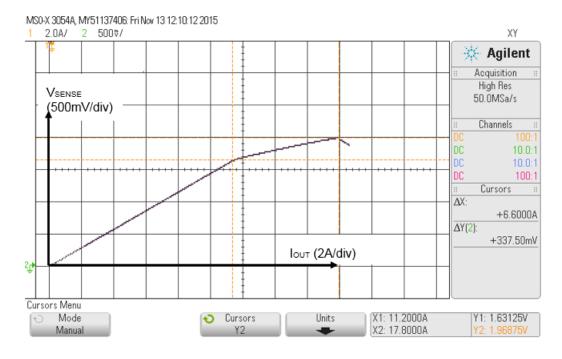

Figure 9. Power Limitation event (VINA, VoutA, Vsense(SEL0=1), lout=lhsd)

## 2.4.2 Short to Vcc protection

For output shorted to  $V_{CC}$ , the Low Side in the ON state is the stressed element in the VNH7XXX and the drain current rises well above nominal levels in the device. In this case, the LS has a double protection depending on whether the short-circuit is hard or resistive.

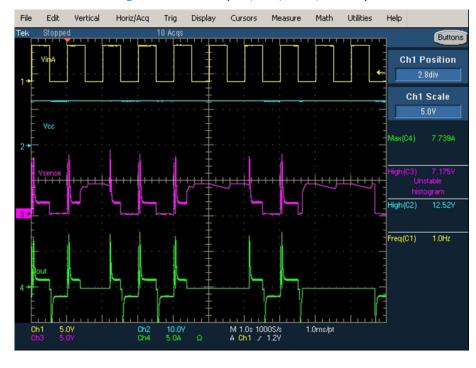

#### 2.4.2.1 Hard short-circuit

In a hard short-circuit (few m $\Omega$  resistance), as soon as the current through the low side MOSFET exceeds the I<sub>SD\_LS</sub> shutdown current, the device is switched off after a certain filtering time (indicated as t<sub>SD\_LS</sub> in the datasheets) and it latches. The fault condition is then detected by the diagnostic.

AN5026 - Rev 2.0 page 11/109

File Edit Vertical Horiz/Acq Trig Display Cursors Measure Math Utilities Help Buttons **Ch2** Position 1.04 div Ch2 Scale Max/C1) 117.6A Max(C4) Max(C2) M 10.0μs 250MS/s A Ch1 / 1.9Y 4.0ns/pt 5.0Y 10.0\ 5.0Y 50.0A Ch2 Ch4

Figure 10. VNH7070BAS short to Vcc event (CH1=VPWM, CH2=Vsense(SEL0=0), CH3=Vcc, CH4=Ivcc, INA=1, INB=0

A filtering time (datasheet symbol T<sub>SD\_LSD</sub>) after the LS current reaches its threshold helps avoid unwanted Low Side latching at switch-on when, for example, filtering capacitors are placed on the VNH7XXX OUTPUTs.

Just before LSx switch-on, the corresponding OUTx is at battery voltage. When the LSx is switched on, the output filtering capacitor is subjected to rapid voltage variation and a consequent current spike.

Depending on capacitor size and LS switch-on time ( $t_f$  in datasheet), this current spike can reach  $I_{SD\_LS}$ , which is why this protection needs to be filtered out.

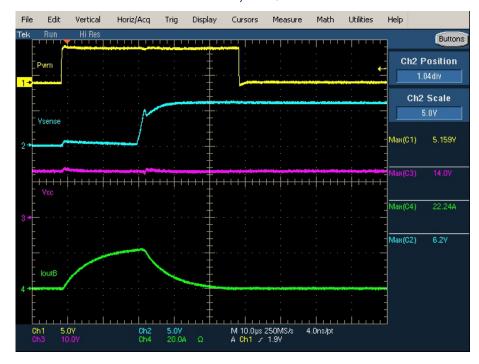

## 2.4.2.2 Resistive (soft) short-circuit - overload

In a resistive short-circuit, the current through the low side MOSFET doesn't reach I<sub>SD\_LS</sub>, but the temperature rises to the LS thermal shutdown level, causing the device to switch off and latch; this fault is detected by the diagnostic.

In the figure below, the device terminal A is before shorted to  $V_{BAT}$  and then the LSA is switched on.

AN5026 - Rev 2.0 page 12/109

Note:

Figure 11. VNH7070BAS short to Vcc event (CH1=VPWM, CH2=Vsense(SEL0=0), CH3=Vcc, CH4=Ivcc INA=1, INB=0

In summary, the Low Side has the following protection circuits:

- Shutdown low side current: triggering of this protection is signaled by CS (MultiSense) and causes device latch off

- Overtemperature shutdown circuit: triggering of this protection is signaled by CS (MultiSense) and causes device latch off

Note: The VNH7XXX enters standby mode if all logic pins (INA, INB, SEL0 and PWM) are at low logic level. The aim of standby is to minimize  $I_S$  device current consumption while the module is idle.

At device power on from standby mode, it is recommended to toggle either INA, INB, SEL0, SEL1 or MultiSense EN out of STBY mode and then toggle PWM with a delay of at least 20 µs. This avoids overly stressing the LS in case of permanent short-to-battery.

The device behavior in case of short-circuit to V<sub>BAT</sub> is influenced by the initial state:

- starting from the STBY condition, the internal logic needs around 20 µs to detect the short to V<sub>BAT</sub> and turn off the LS, during which time the device operating current is well above I<sub>SD\_LS</sub>. The characteristics of the short-circuit (stray inductance and resistance) play a key role in limiting the current slope and following the max. peak current because of the 20 µs delay time.

- starting from a condition other than STBY, the internal logic detects the fault immediately after the built-in filtering time ( $t_{SD\ LS}$ ), turning off the LS at a lower peak current.

## 2.4.3 Short-circuit across the load

A hard short-circuit across the load latches due to the triggering of the overload current shutdown protection of the PowerMOS with the lowest value. The VNH7XXX bridges are designed with the High Side current limitation  $(I_{\text{LIM\_H}})$  lower than the Low Side shutdown current  $(I_{\text{SD\_LS}})$ .

## 2.4.3.1 Short-circuit is applied so that HSA is switched on while the LSB is already on

In the following figure, at the HS switch on  $V_{DS}$ , HS =  $V_{CC} - V_{outA} \sim V_{BAT}$ , meaning that the whole battery voltage is across the HS terminals. In this condition, the HS dissipates a lot of power deriving from  $I_{LIMH} \times V_{BAT}$ , while the power dissipation inside the LS is much less as the LS  $V_{DS}$  is well below 1 V.

As the HS is in high dissipation, either power limitation or thermal shut down circuit will latch the device off.

AN5026 - Rev 2.0 page 13/109

Figure 12. VNH7040AY short across load event (HSA switched on while LSB is already ON)

2.4.3.2 Short-circuit is applied so that LSB is switched on while the HSA is already on In this second case, the device latches due to LS protection triggering (I<sub>SD LS</sub> reached).

Figure 13. VNH7040AY short across the load event (LSB switched on while HSA is ON)

### 2.4.3.3 Short circuit occurs when HSA and LSB are both on

In this third case, the overshoot of the HSA current limiter lets the LSB reach its shutdown current protection  $I_{SD\ LSD}$  and cuts off of the short-circuit current by latching the device off.

AN5026 - Rev 2.0 page 14/109

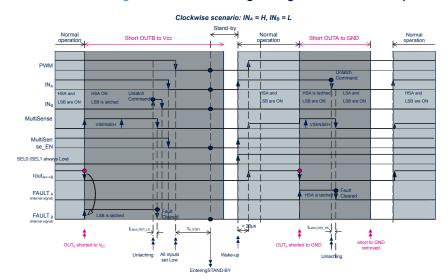

## 2.5 Cross conduction suppression

In normal operation, an H-bridge drives a motor in two directions: clockwise (HSB on, LSA on) and counter clockwise (HSA on, LSB on). It cannot switch both PowerMOS of the same leg on at the same time as this causes a short to GND battery event (cross conduction event).

To avoid this behavior, the VNH7XXX ICs implement specific logic:

- when INA is toggled high, the complemented signal immediately turns off the LSA MOSFET before the

charge pump circuitry has had time to switch on the HS MOSFET; likewise for INB and LSB. This protection

takes advantage of the switching time difference between the Low Side MOSFET and the High Side

MOSFET; due to the charge pump circuitry, the HS switch has slower turn-on/turn-off times compared to the

LS MOSFET.

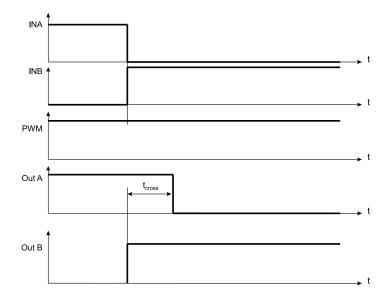

- when INA is toggled low, HSA switch off is slower than LSA switch on, so a delay (t<sub>cross</sub> of about 150 µs) is added to ensure LSA switch on after HSA switch off; likewise for INB, HSB and LSB. Therefore, t<sub>cross</sub> is longer than the HS switch off time (t<sub>d(off)</sub>).

The figure below shows a change of direction from HSA and LSB in on state to HSB and LSA in on state, and indicates the  $t_{CROSS}$  delay before the LSA is turned on (delay time for turning on of HSB is not shown)

Figure 14. cross current delay

The M0-7 H-bridge drivers are designed to avoid shoot-through during operation in PWM, even in adverse ambient conditions.

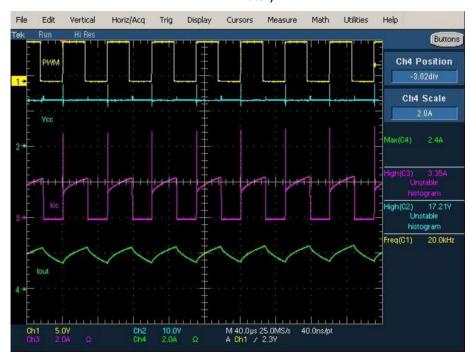

In the figure below, the High Side is in the DC condition (HSA is on, HSB is off), while the Low Side is toggling as per the PWM signal.

AN5026 - Rev 2.0 page 15/109

Figure 15. Vbatt=13.5V, TJ=25°C, Duty Cycle 50%, DC MOTOR (CH1=VPWM, CH2=Vcc, CH3=I(Vcc), CH4=Imotor)

The current peaks on V<sub>CC</sub> are due to the intrinsic HS diode recovery time.

The VNH7XXX devices are immune to shoot-through, a typical dynamic issue in bridge topology. As soon as any LS is switched on by a PWM signal, a negative dv/dt is applied to the High Side of the same leg output.

Potentially, this dv/dt is coupled through the High Side  $C_{GS}$  capacitance to its gate ( $C_{GD}$  and  $C_{GS}$ ). Depending on the HS gate-source pull down impedance, current may flow from battery to ground, resulting in extra power dissipation (the impact of which can be significant at high frequencies) and hazardous conditions for the device. This problem is avoided by design in the VNH7XXX bridge.

AN5026 - Rev 2.0 page 16/109

# 3 External protections

## 3.1 Reverse polarity protection

A common problem in the automotive environment is damage when car battery terminals are connected incorrectly.

H-bridge ICs in VIPower technology include two parasitic p-n diodes from GND to the supply voltage pin  $V_{CC}$  (2 x  $V_f \sim 1.5$  V). An inverse supply voltage would allow high current to flow through these diodes and damage the device.

Electronic safeguards involving passive or active reverse polarity protection need to ensure that any reverse current flow and reverse bias voltage is low enough to prevent damage to internal electronics.

Reverse polarity protection strategies can be:

- · active or passive

- on battery line (V<sub>CC</sub> terminal) or on GND line (GND terminal)

Four possible reverse battery protection solutions are summarized in the following table.

Reverse battery protection design

Protection type

Connection

Schottky Diode

Passive

Vcc

P-channel MOSFET

Active

Vcc

Reverse FET

Active

Vcc

N-channel MOSFET

Active

GND

Table 2. Reverse battery protection designs

## 3.1.1 Diode in series with battery line

## 3.1.1.1 Protection behavior

## Normal operation (positive battery voltage)

All load current flows through the diode, which must be chosen so as not to allow the junction temperature to exceed the maximum. Here it is the formula to apply:

## **Equation 1**

$$DT_{j} = T_{j(D)max} - T_{amb, max} \& lt; P \cdot R_{thj} - amb$$

(1)

Where:

- T<sub>amb,max</sub> is the maximum module temperature

- · R<sub>thi-amb</sub> is the thermal resistance (junction to ambient) for the device and mounting use

Power dissipation is given by:

## **Equation 2**

$$P = V_{TO} * I_{F(AV)} + rd \cdot I_{F(RMS)}^{2}$$

(2)

Where:

- I<sub>F(AV)</sub> = maximum average forward current

- I<sub>F(RMS)</sub> = RMS forward current

AN5026 - Rev 2.0 page 17/109

rd (small signal diode resistance) and V<sub>TO</sub> depend on the special characteristics of the diode and can be extracted from the diode datasheet.

### Behavior during reverse battery polarity

The diode is off once polarity is inverted; no current can flow in this state other than the rated leakage reverse current.

The diode breakdown voltage  $V_z$  must be higher than the reverse battery voltage value (typ.: 16 V). An important aspect is the peak reverse voltage limit of the Schottky diode. If we consider the maximum repetitive reverse voltage of the diode:

- V<sub>RRM</sub> > 100V for "ISO 7637-2:2004(E)" pulse 1 Test level IV

- V<sub>RRM</sub> > 150V for "ISO 7637-2:2011(E)" pulse 1 Test level IV.

During the negative ISO7637-2 transients, the motor is supplied by the electrolytic filtering capacitor on  $V_{CC}$ .

The advantage of a Schottky diode over a standard diode is a very low voltage drop in the forward direction, hence power dissipation is reduced. This solution can be used for low current motors.

## 3.1.2 P-channel MOSFET in the Vcc line

Figure 16. Reverse battery protection with P-channel MOSFET

#### 3.1.2.1 Protection behavior

#### Normal operation (positive battery voltage)

After the power-up phase when the P channel MOSFET body diode is forward-biased, a negative gate-source voltage switches on the P channel MOSFET.

Behavior during reverse battery polarity

AN5026 - Rev 2.0 page 18/109

The P channel MOSFET is switched off since its gate-source voltage is positive (voltage drop over the Zener diode); no current can flow in this state.

#### 3.1.2.2 External component selection

Zener diode ZD1 is dimensioned on the basis of:

- Vz above the nominal battery voltage to avoid high module standby current;

- Vz must be below the P- Ch PowerMOS gate-source voltage absolute maximum rating;

- Power rating enough to handle the current in case of load dump event.

The resistor between gate and GND limits the current through the Zener diode at supply voltages higher than the Zener voltage and limits the charging or discharging current of the gate.

This resistor, together with the gate capacitance of the P-channel MOSFET, also determines the turn-off time when exposed to fast negative transients or abrupt reverse polarity according to LV 124: 2013-06 standard.

$1~k\Omega$  appears to be a good compromise between minimizing the charging/discharging current and ensuring a fast turn-off time.

As the P-channel MOSFET also carries the load current, it needs to be properly dimensioned to handle the whole load current.

A capacitor could be placed between Gate and Source of the P-channel MOSFET.

The RC filter composed of the 1 k $\Omega$  resistor and the capacitor can be dimensioned to be transparent against the fast negative pulses ISO 7637-2:2004(E) pulse 1 test level IV, keeping the reverse polarity protection circuitry switched ON.

Main PowerMOS parameters ( $R_{ds(on)}$ ,  $V_{(BR)DSS}$ ,  $V_{gs\_th}$ ):

The maximum P-channel  $V_{qs}$  th is given at the minimum battery voltage.

The P channel  $R_{ds(on)}$  must be such that power dissipation is kept low enough to keep the junction temperature below the rated maximum (150 °C).

### **Equation 3**

$$DTj = Tj_{Pch\_max} - T_{amb\_max} = R_{ds(0N)max} * l_{motor\_RMS\_max}^{2}$$

(3)

#### Where:

- T<sub>amb,max</sub> is the maximum module temperature

- I<sub>motoravg max</sub> is average motor current calculated at the maximum battery voltage.

The P channel MOSFET breakdown voltage ( $V_{(BR)DSS}$ ) must be higher than the reverse battery voltage value (typ. 16 V).

If no low pass filter is placed on the P channel gate, any negative ISO transient opens the P channel MOSFET. The motor is then supplied by the electrolytic filtering capacitor on  $V_{CC}$ .

A standard logic MOSFET is normally recommended for noise immunity issue.

The Zener diode clamps the Gate of the MOSFET to its Zener voltage and protects it against overvoltage.

The same reverse battery protection can be shared among several bridges connected to the battery.

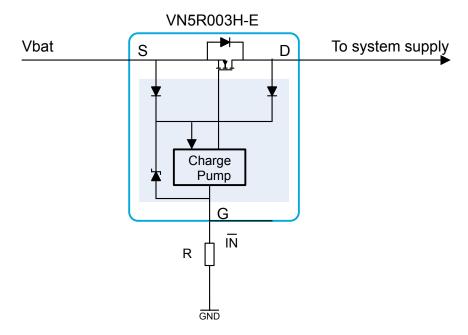

#### 3.1.3 Dedicated ST Reverse FET solution

The VN5R003H-E device uses VIPower<sup>™</sup> technology by ST to provide reverse battery protection for an electronic module. It consists of an N-channel MOSFET and driver circuit, two power pins (Drain and Source) and a control pin (IN\_NOT).

AN5026 - Rev 2.0 page 19/109

Figure 17. Reverse polarity protection – Reverse FET protection

Once the IN\_NOT voltage is pulled low, the device is turned ON. The internal charge pump allows the PowerMOS gate to rise above the battery voltage to make it function in ohmic region. When IN\_NOT is left open, device is in the OFF state and behaves like a power diode between the source and drain pins.

During a reverse battery polarity event, the charge pump stops operation, causing the PowerMOS to switch off. In normal operation, the VN5R005 dissipates power given by the battery current multiplied by its  $R_{ds(on)}$ .

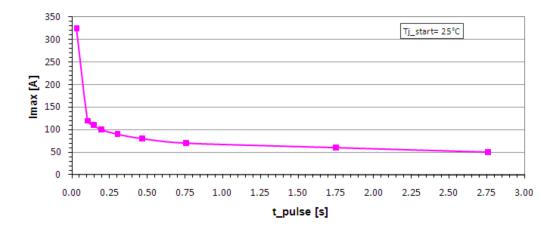

The figure below shows the safe operating area and the maximum pulsed drain current the device is able to manage during normal operation (PCB FR4 area =  $58 \text{ mm} \times 58 \text{ mm}$ , PCB thickness = 2 mm, Cu thickness = 35 mm, Copper areas: minimum pad lay-out and  $2 \text{ cm}^2$ )

Figure 18. Maximum current versus duration time of VN5R003H-E

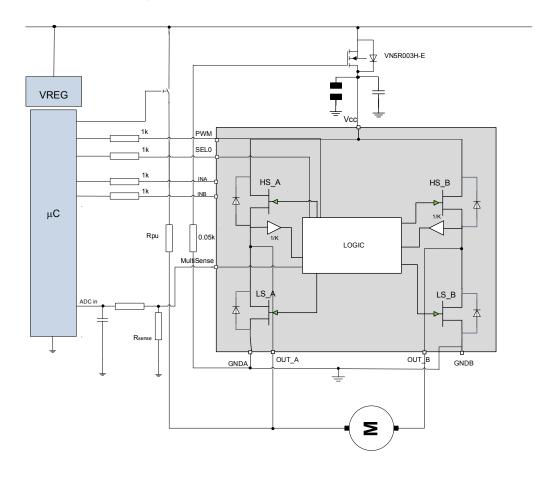

The VN5R003H-E is able to handle ISO 7637-2 2004 pulses with R (IN\_NOT) > 5  $\Omega$ . Its performance was evaluated using the circuit schematic below.

AN5026 - Rev 2.0 page 20/109

Figure 19. Application schematic with VN5R003H-E

AN5026 - Rev 2.0 page 21/109

## 3.1.4 N-channel MOSFET connected to module ground

VREG PWM SEL0 1k HS A HS B 1k μС Rpu 100 LOGIC MultiSe LS LS B GNDB OUT\_A

Figure 20. Reverse battery protection with N-channel MOSFET

### 3.1.4.1 Protection behavior

#### Normal operation (positive battery voltage)

After the power-up phase ,when the N channel MOSFET body diode provides the GND to the motor control IC, the zener diode DZ plus the resistor generate enough gate-source voltage to switch on the N-MOSFET.

#### Reverse battery polarity condition

The N-Channel is switched off since its gate voltage is low; no current can flow in this state.

The series resistor  $R_g$  between  $V_{CC}$  and N channel MOSFET gate limits the current through the Zener diode at supply voltages higher than the Zener voltage and limits the charging/discharging current of the gate.

This resistor, together with the gate capacitance of the N channel Power MOSFET, determines the turn-off time when the module is exposed to fast negative transients or abrupt reverse polarity according to the LV 124: 2009-10 standards.

A good tentative value for  $R_g$  could be a few tens of kilohms, considering that a long turn-off time could cause high power dissipation for both the LS and this N-channel Power MOSFET used as reverse battery.

A capacitor,  $C_g$ , might be placed between Gate and Source of the N channel Power MOSFET. The RC filter formed by  $R_g$  and  $C_g$  can be dimensioned to be transparent against the fast negative pulses ISO 7637-2:2011(E) 3a, keeping the reverse polarity protection circuitry switched on.

The time constant ( $R_g x C_g$ ) must be longer than the pulse 3a length (0.1 µs) but smaller than the pulse 1 length (2 ms).

#### 3.1.4.2 External component selection

The zener diode must be dimensioned based on the following considerations:

- V<sub>Z</sub> above the nominal battery voltage to avoid high module standby current;

- V<sub>Z</sub> must be below the N-Ch PowerMOS gate-source voltage absolute maximum rating;

- Power rating enough to handle the current in case of load dump event.

AN5026 - Rev 2.0 page 22/109

Main PowerMOS parameters (R<sub>ds(on)</sub>, V<sub>(BR)DSS</sub>, V<sub>th</sub>):

The N-Ch  $R_{ds(on)}$  must be such that power dissipation is kept low enough to ensure that the junction temperature remains below the rated maximum (150 °C).

## **Equation 4**

$$DTj = Tj_{Nch \ max} - T_{amb \ max} = R_{ds(0N)max} * I_{motor \ RMS \ max}^{2}$$

(4)

#### Where:

- T<sub>amb,max</sub> is the maximum module temperature

- I<sub>motor RMS max</sub> is average motor current calculated at the maximum battery voltage.

The N-channel PowerMOS breakdown voltage ( $V_{(BR)DSS}$ ) should be higher than the maximum negative transient peak voltage of ISO 7637:2-2011(E) or its energy capability in avalanche must be high enough to handle the transient pulse energy.

The N-channel PowerMOS must be large enough to handle ISO7637/2 pulse 1 level IV energy.

A standard logic MOSFET is normally recommended for noise immunity issue.

## 3.2 DC motor control application considerations

The typical application schematic of a M0-7 H-bridge is given below.

Figure 21. Typical application schematic of a VNH7XXX

AN5026 - Rev 2.0 page 23/109

## 3.2.1 H-bridge device application considerations

Mechanically commutated motors with brushes (DC motors) are driven by half bridge or by full-bridge (H-bridge) power switch configurations.

High-current and high frequency applications like motor control need to address the effect of parasitic inductors. Inappropriate handling of these inductors can lead to EMC issues (conducted and radiated high RF noise emission), erratic behavior and IC device failure.

Any interconnection inside the device (wire bonding) of the car wiring and in the module (vias, PCB traces) introduces stray inductances. Switching of inductive current causes overvoltages across its terminals as per the formula:

#### **Equation 5**

$$V_L = -L \cdot dI_L/dt \tag{5}$$

#### Where:

- V<sub>I</sub> is the voltage across the inductor

- L the inductor itself

- I<sub>L</sub> is the current flowing through

Any high current variation leads to an overvoltage.

Moreover, according to the formula:

#### **Equation 6**

$$E_L = 0.5L \cdot I^2 \tag{6}$$

Any inductor stores some energy that, when inductor current is stopped, is discharged or transferred to the structures connected to the inductor terminals. This energy must be managed to avoid unexpected failure of the structures connected to the inductor.

## 3.2.2 Design verification checks

#### 3.2.2.1 C1(Vcc) capacitive filter on the supply line

This electrolytic capacitor keeps the voltage ripple at the  $V_{CC}$  pin of the IC below a predefined value during operation in PWM at high frequency. This ripple should be kept below 3 V peak to peak.

The capacitive value of an electrolytic capacitor depends on the  $V_{CC}$  DC voltage and the module ambient temperature.

Capacitor selection must involve consideration of the ESR value, which can degrade the filtering capability of the capacitor if too high. This capacitor must be placed as close as possible to the device  $V_{CC}$  and GND pins to minimize trace inductance.

#### 3.2.2.2 C2(Vcc) capacitive filter on the IC supply line

This ceramic capacitor must absorb all fast transients between the  $V_{CC}$  pin and GND pin. The value can be determined from CISPR25 conducted emission measurements on the battery line.

This capacitor must be placed as close as possible to the IC supply pin  $(V_{CC})$  and ground terminals with minimal PCB trace length to minimize the trace inductance.

#### 3.2.2.3 Ripple on Vcc caused by motor inductance

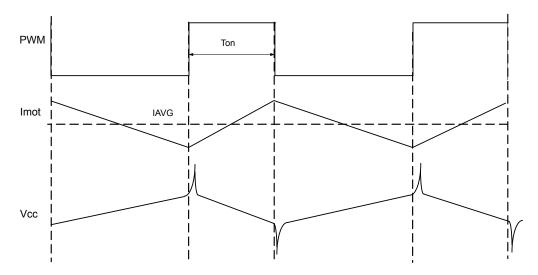

In the steady state with the motor driven by PWM, the motor current is the sum of:

- 1. an average value (I<sub>MAVG</sub>) provided by the car battery

- 2. a ripple current (I<sub>Mripple</sub> peak-to-peak) provided by the bulk capacitor(s) placed across the motor control IC

The battery provides energy to the motor when either HSA /LSB or HSB /LSA are on (Ton, on phase of the whole PWM period).

Below are the typical waveforms:

AN5026 - Rev 2.0 page 24/109

Figure 22. Voltage and current ripple during PWM application

In the following considerations, it is assumed that the motor average current is provided by the battery, whilst the ripple current is provided by the bulk capacitor.

In the worst case assumption that the system formed by the H-bridge IC and the bulk capacitor is decoupled from the battery by the wire stray inductance, the energy provided by the supply bulk capacitors during T<sub>on</sub> is identical to the power provided to the DC motor.

The characteristic equation of a DC motor is:

## **Equation 7**

$$V_{batt} = R_{motor} \cdot I_{motor} + L_{motor} \cdot \frac{dI_{motor}}{dt} + BEMF = V_{motor,avg} + V_{motor,ripple} \tag{7}$$

Where:

## **Equation 8**

$$V_{motor, avg} = R_{motor} \cdot I_{avg} + BEMF \tag{8}$$

If we neglect the drop on the motor resistance  $R_{motor}$  in the above equation, we derive the following formula:

## **Equation 9**

$$Vmotor, ripple \cong Lmotor^* \frac{dImotor}{dt}$$

$$\tag{9}$$

Therefore the current ripple during t<sub>ON</sub> can be simplified according to the following equation:

#### **Equation 10**

$$I_{motor, ripple} = \frac{\left(V_{batt} - V_{motor, avg}\right)}{L_{motor}} \cdot T_{on} \tag{10}$$

Where:

#### **Equation 11**

$$V_{motor, avg} = \frac{T_{on}}{T} \cdot V_{batt} \tag{11}$$

If we consider a linear increase of the motor current, the charge required by the bulk capacitor to supply the motor is:

AN5026 - Rev 2.0 page 25/109

#### **Equation 12**

$$DQ = 0.5 \cdot T_{on} \cdot I_{motor, ripple} \tag{12}$$

At this point, the C<sub>(Vcc)</sub> must be:

#### **Equation 13**

$$C1_{(Vcc)}$$

>  $\frac{DQ}{DVcc}$  (13)

This equation helps to define the right  $C1_{(Vcc)}$  capacitor for the chosen ripple allowed on  $V_{CC}$ . By applying the previous four formulas, we finally derive:

#### **Equation 14**

$$C1_{(Vcc)} \& gt; \frac{0.5 \cdot T_{on}^2 \cdot V_{batt} \cdot \left(1 - \frac{T_{on}}{T}\right)}{L_{motor} \cdot DV_{CC}}$$

(14)

The maximum pulse length  $(t_{on})$  is determined by the PWM frequency and duty cycle (in Equation 14, the maximum C1(V<sub>CC</sub>) is obtained at 67% duty cycle. The capacitor value in case of loads which require 20 kHz PWM is relatively low in comparison to the value needed to face other possible applicative conditions described below.

## 3.2.2.4 Ripple on Vcc caused by stray wiring inductance during sudden current variation

During motor operation in PWM, the battery current is continuously stopped and restarted.

The ripple on V<sub>CC</sub> depends on:

- the stray inductance between the IC V<sub>CC</sub> and the battery itself

- · the maximum speed at which the LS is switched on and off

- the maximum motor load current in the worst case environmental conditions.

The voltage variation across the stray inductance is:

#### **Equation 15**

$$DV_{CC} = -L_{stray} \left( \frac{dI_{motor}}{dt} \right)$$

(15)

Where  $L_{stray}$  is the stray inductance between  $V_{batt}$  and device  $V_{CC}$  and dt is either the  $t_{fall}$  or the  $t_{rise}$  of the LS working in PWM.

The filtering capacitor on  $V_{CC}$  must be dimensioned by taking in account the balance of energy between the one stored in the  $L_{stray}$  and the one stored in the  $C_{(VCC)}$ .

If we consider that the stray inductance energy is transferred instantaneously to the bulk capacitor (thus neglecting the LS switching times), the following equation applies:

#### **Equation 16**

$$0.5 \cdot L_{stray} \cdot I_{motor}^2 = 0.5 \cdot C1_{(Vcc)} \cdot DV_{CC}^2$$

$$\tag{16}$$

Assuming:

### **Equation 17**

$$DV_{CC, max} = V_{CC\_AMR} - V_{batt\_max}$$

(17)

Where V<sub>CC AMR</sub> is given in the datasheet Absolute Maximum Rating table.

This yields:

AN5026 - Rev 2.0 page 26/109

#### **Equation 18**

$$C1_{(VCC)}$$

>  $\frac{L_{stray} \cdot I_{motor}^2}{DV_{CC\ max}^2}$  (18)

#### 3.2.2.5 Ripple on Vcc in current switch off due to short to battery and short to ground

All VIPower H-bridges have the Low Side shut-down current ( $I_{LS\_SD}$  in datasheets), so in short-circuits to battery, the LS switches off as soon as the LS current reaches the current cut-off value.

Depending on the stray inductance of the short-circuit, the energy stored in it must be dissipated in the structures connected to the stray inductor terminals.

Because of the H-bridge structure, a positive pulse on the LS drain is transferred to the IC supply pin (V<sub>CC</sub>).

The capacitive filtering on V<sub>CC</sub> helps to absorb this inductive energy.

Even here, we must balance the energy thus:

#### **Equation 19**

$$0.5 \cdot L_{stray\_sc} \cdot I_{SD\_LS, max}^{2} = 0.5 \cdot C1_{(VCC)} \cdot DV_{CC, max}^{2}$$

$$\tag{19}$$

## Where:

- L<sub>stray</sub> sc is the short-circuit stray inductance

- I<sub>SD LS,max</sub> is the Low Side shut-down current

- DV<sub>CC,max</sub> = V<sub>CC,max</sub> V<sub>CC,initial</sub> with V<sub>CC,max</sub> representing the Absolute Maximum Rating of the device.

By imposing that  $DV_{CC,max} = V_{CC\_AMR} - V_{batt\_max}$  ( where the  $V_{CC\_AMR}$  is given in the datasheet Absolute Maximum rating table), this yields:

#### **Equation 20**

$$C1_{(VCC)}$$

>

$$\frac{L_{Stray\_sc} \cdot I_{SD\_LS,max}^2}{DV_{CC,max}^2}$$

(20)

The same considerations can be applied in case of short-circuits to ground. In the H-bridge IC, the High Side has both current limitation and thermal shut down features. The worst case energy discharge event is the one that occurs at the maximum current limitation value ( $I_{lim h}$ ). The formula is:

## **Equation 21**

$$0.5 \cdot L_{stray} \cdot I_{limh}^2 = 0.5 \cdot C1_{(Vcc)} \cdot DV_{CC, max}^2$$

$$\tag{21}$$

By imposing that  $DV_{cc,max} = V_{cc\_AMR} - V_{batt\_max}$  ( $V_{cc\_AMR}$  from the datasheet Absolute Maximum rating table), we derive:

## **Equation 22**

$$C1_{(Vcc)}$$

>  $\frac{L_{stray} \cdot I_{limh}^2}{DV_{CC,max}^2}$  (22)

## 3.2.2.6 Ripple on Vcc due to sudden battery disconnection with motor fully energized

In this condition, the motor energy must be absorbed by the bulk capacitors to avoid reaching the H-bridge IC breakdown voltage and consequent failure due to excessive energy levels. The applicable formula is:

### **Equation 23**

$$E_{motor} = 0.5 \cdot C1_{(Vcc)} \cdot DV_{CC, max}^{2}$$

(23)

AN5026 - Rev 2.0 page 27/109

By imposing that  $DV_{cc,max} = V_{cc\_AMR} - V_{batt\_max}$  ( $V_{cc\_AMR}$  from the datasheet Absolute Maximum Rating table), we derive:

#### **Equation 24**

$$C1_{(Vcc)}$$

>

$$\frac{E_{motor}}{0.5 \cdot DV_{CC,max}^2}$$

(24)

#### 3.2.2.7 Vcc drop with risk of undervoltage event at motor current in-rush

Device V<sub>CC</sub> is normally inductively decoupled from the car battery positive due to:

- 1. battery cable with stray inductance powering the IC

- inductance of the Pi filter if present

The motor start current is much higher than nominal current to overcome mechanical inertia (in-rush current) and generate movement.

C1<sub>(Vcc)</sub> must be large enough to provide at least part of the energy required by the motor in order to avoid unwanted undervoltage events.

### **Equation 25**

$$dI_{motor,inrush} = C1_{(Vcc)} \cdot \frac{DV_{CC}}{dt}$$

(25)

Given  $DV_{CC} = V_{batt.min} - V_{USD max}$ , then:

#### **Equation 26**

$$C1_{(Vcc)}$$

>

$$\frac{dI_{motor,inrush} \cdot dt}{V_{batt,min} - V_{USD\_max}}$$

(26)

All of the above formulas set the conditions that C1<sub>(Vcc)</sub> must fulfil to guarantee proper device operation.

## 3.2.2.8 Vcc variation because of fast ISO7637/2 ISO transients (pulses 3a, 3b)

Some reverse battery protection topologies allow transfer of voltage transients directly to device V<sub>CC</sub>.

The fast transients according to ISO7637/2 are:

- 1. 3a, level IV, max. negative voltage = -220 V, pulse length= 0.1  $\mu$ s, series resistance= 50  $\Omega$ ; this pulse causes sudden V<sub>CC</sub> voltage drop of roughly 100 ns

- 2. 3b, level IV, max. positive voltage = +150 V, pulse length= 0.1  $\mu$ s, series resistance = 50  $\Omega$ ; This pulse causes a sudden overvoltage that could trigger the H-bridge IC Power clamp in case of no filtering capacitor on the  $V_{CC}$  line.

A filtering capacitor  $C2_{(Vcc)}$  of a few tens of nF is enough to smooth the effect of the above pulses and avoid triggering any protections as well as device malfunction.

## 3.2.3 Overview of capacitor C1(Vcc) assessment

Table 3. Overview of capacitor C1(Vcc) assessment

| Applicative condition                                                         | Formula to apply to get C1 <sub>(Vcc)</sub> | Applied criteria                                                                                                   |

|-------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Section 3.2.2.3 Ripple on Vcc caused by motor inductance                      | Equation 14                                 | DV <sub>CC</sub> = maximum allowed peak to peak voltage (e.g., 3 V)                                                |

| Section 3.2.2.4 Ripple on Vcc caused by stray wiring inductance during sudden | Equation 18                                 | $L_{\text{stray}}$ is the stray inductance from battery to device (included any eventual inductance of Pi-filter); |

| current variation                                                             |                                             | $DV_{cc,max} = V_{cc\_AMR} - V_{batt\_max}$ (1)                                                                    |

AN5026 - Rev 2.0 page 28/109

| Applicative condition                                                                        | Formula to apply to get C1 <sub>(Vcc)</sub> | Applied criteria                                                                                                                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                              | Equation 20                                 | L <sub>stray_sc</sub> is the stray inductance of the short-circuit path; I <sub>SD_LS,max</sub> is the maximum low side cutoff current (given in the datasheet);                                                                                   |  |

| Section 3.2.2.5 Ripple on Vcc in current                                                     |                                             | $DV_{cc,max} = V_{cc\_AMR} - V_{batt\_max}$ (1)                                                                                                                                                                                                    |  |

| switch off due to short to battery and short to ground                                       | Equation 22                                 | $L_{stray}$ is the stray inductance from battery to device (included any eventual inductance of Pi-filter); $I_{LIM\_H}$ is the maximum high side current limitation (given in the datasheet); $DV_{cc,max} = V_{cc\_AMR} - V_{batt\_max}  ^{(1)}$ |  |

| Section 3.2.2.6 Ripple on Vcc due to sudden battery disconnection with motor fully energized | Equation 24                                 | $E_{motor}$ is the total energy of the motor (kinetic and inductive).<br>$DV_{cc,max} = V_{cc\_AMR} - V_{batt\_max}$ (1)                                                                                                                           |  |

| Section 3.2.2.7 Vcc drop with risk of undervoltage event at motor current in-rush            | Equation 26                                 | Dt <sub>motor_inrush</sub> is the rise time of the motor in-rush current; V <sub>USD_max</sub> is the maximum undervoltage shutdown threshold (given in the datasheet)                                                                             |  |

<sup>1.</sup> Vcc\_AMR is given in the datasheet Absolute Maximum Rating table

To prevent dangerous overvoltages or undervotages on the battery connection for the H-Bridge, all the above conditions should be fulfilled.

#### Example: Dual washer pump motor driven by VNH7040AY

During ON state, PWM 20 kHz is applied.

The following VNH7040AY parameters are applied:

- V<sub>CC AMR</sub> = 38 V

- I<sub>LIM HSD</sub> = 70A Maximum

- I<sub>SD LS</sub> = 84 A Maximum

- V<sub>USD</sub> = 4 V Maximum

- $T_{ON}/T=0.67$ ;  $T_{ON}=33.5 \mu s$

The following DC motor parameters are applied:

- L<sub>motor</sub> = 100 μH

- I<sub>motor</sub> = 10 A Maximum

- DI<sub>motor,inrush</sub> = 26 A Maximum

- Dt<sub>motor,inrush</sub> = 1 μs

- E<sub>motor</sub> = 33.5 mJ (Energy of the motor before battery disconnection)

The following application parameters are applied:

- V<sub>batt,min</sub> = 7 V

- V<sub>batt,max</sub> = 26 V (for example jump start)

- DV<sub>CC</sub> = 3 V (max peak to peak voltage)

- L<sub>stray</sub> = 5 μH

- $L_{stray\_sc} = 3 \mu H$

The limitation of  $V_{CC}$  ripple during PWM caused by motor inductance (Equation 14) yields:

$$C1(Vcc) \& gt; \frac{0.5*Ton^2*Vbatt, max*\left(1 - \frac{Ton}{T}\right)}{Lmotor*DVcc} = 16.05 \,\mu F \tag{27}$$

Limitation of V<sub>CC</sub> ripple caused by wiring stray inductance due to sudden current variation (Equation 18) yields:

$$C1(Vcc)$$

>  $\frac{Lstray*Imotor^2}{DVcc, max^2} = 3.47 \,\mu F$  (28)

AN5026 - Rev 2.0 page 29/109

Limitation of V<sub>CC</sub> peak at LS switch off in the event of short of OUT to battery (Equation 20), yields:

$$C1(Vcc) \& gt; \frac{Lstray\_sc*I_{SD\_LS,max}^2}{DVcc,max^2} = 147 \,\mu F$$

(29)

Limitation of V<sub>CC</sub> peak at HS switch off in the event of short of OUT to ground (Equation 22), yields:

$$C1(Vcc) \& gt; \frac{Lstray*I_{SLIM\_HSD,max}^2}{DVcc,max^2} = 170 \ \mu F \eqno(30)$$

Limitation of Vcc peak during sudden battery disconnection with energized motor (Equation 24), yields:

$$C1(Vcc) \& gt; \frac{Emotor}{0.5*DVcc, max^2} = 470 \ \mu F$$

(31)

Limitation of V<sub>CC</sub> drop at motor inrush (Equation 26), yields:

C1(Vcc) >

$$\frac{dImotor, inrush*dt}{Vbatt, min - V_{USD\_max}} = 8.7 \ \mu F \tag{32}$$

The worst case condition in this example is the battery disconnection with energized motor, since all other applicative events require a smaller  $C1(V_{CC})$ . Every applicative condition, DC motor type and VNH7XX choice should take into account the above-mentioned conditions.

## 3.2.4 Protection resistors (INA, INB, PWM and SEL0)

When negative transients are applied to  $V_{CC}$ , the control pins are pulled negative to approximately -2 x Vf  $\sim$  -1.5 V where this latter is the voltage drop across the PowerMOS antiparallel intrinsic diodes.

During such an event, the npn parasitic bipolar transistor present in each logic pin enters saturation mode (see the following figure).

Figure 23. simplified internal schematic in negative battery transients

AN5026 - Rev 2.0 page 30/109

This bipolar saturation current may rise higher than the maximum MCU I/O current and cause MCU failure (latch-up event).

VNH7XXX digital input protection resistors (typ. 1 K $\Omega$ ) are therefore mandatory.

The value of these resistors is a compromise between the current absorbed by the HS I/Os in high logic state and the latch-up limit of microcontroller I/Os:

## **Equation 27**

$$\frac{1.5\,V}{I_{\rm latchup}} \le R_{prot} \le \frac{{\rm V_{OH}\mu C, min^{\,-\,V_{\rm IH,\,min}}}}{I_{\rm INHmax}} \tag{33}$$

Where:

- I<sub>latchup</sub> is the maximum latch-up current of the microcontroller

- V<sub>OHuC.min</sub> is the minimum high state voltage of the microcontroller output

- V<sub>IH.min</sub> is the minimum input high level voltage of the VNH7XXX (given in the datasheet)

- I<sub>INH.max</sub> is the maximum input current of VNH71XXX (given in the datasheet)

In summary, the above protection resistors are recommended in case of VNH7XXX failure with potential high voltage in the digital inputs; negative ISO transients (worst case based on the ISO7637/2, ed. 2011 is -150 V) applied to the Vcc pin.

This event is heavily influenced by the reverse battery protection topology and is only applicable when the reverse battery network is connected to the device ground.

## 3.2.5 Rejection of conducted and radiated electromagnetic emissions

A device or system generates noise which is injected into connection lines or radiated, potentially affecting the performance of other devices or systems connected to the same lines and placed close to it.

To limit the effect of this noise, its amplitude must be lower than EMC limits contained in specific technical reference documentation:

- Standard reference CISPR25 (conducted emissions on V<sub>batt</sub>, radiated emissions at system level)

- Standard reference IEC 61967/4 (conducted emissions on Outputs using 1 Ω/150 Ω method)

- Standard reference IEC 61967/2 (radiated emissions using TEM-Cell method and wideband TEM-cell method -150 KHz to 8 GHz).

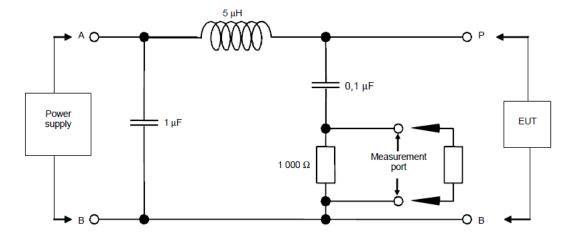

**For conducted emissions on Vbatt**, a specific artificial network (AN) called line impedance stabilizing network (LISN), is used to couple the measurement instrument (spectrum analyzer) with the V<sub>batt</sub> line. The figure below shows the LISN schematic for the CISPR25 standard.

Figure 24. LISN setup - CISPR25

AN5026 - Rev 2.0 page 31/109

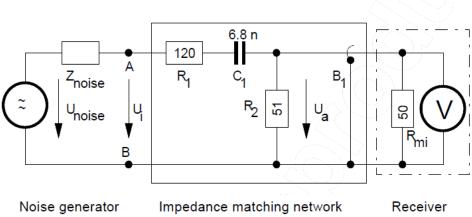

For conducted emissions on system outputs (e.g.,  $V_{CC}$  line or VNH7XX outputs), the 150  $\Omega$  measurement method (IEC 61967/4) is commonly used. To perform measurements, the impedance matching network figured below is required.

Figure 25. Impedance matching network (IEC 61000-4)

One or multiple configurations can be chosen for input signals, PWM frequency, duty cycle percentage and output loads. The final configuration is usually the one closer to the common operating condition of the DUT. The type (shielded or unshielded) and length of wire may affect performance of the DUT either with respect to the CISPR25/IEC 61967/4 standard (conducted emissions) or the IEC 61967/2 standard (radiated emissions).

#### 3.2.5.1 Pi-filter dimensioning

Conducted emission measurements may reveal levels of RF noise injected into the battery line above the required limits. The best solution in this case is to add a Pi filter in series with the dedicated battery line.

C1<sub>(Vcc)</sub> can be considered as part of the normally used Pi filter and its capacitance is calculated with formulas explained in previous chapters.

The resonance frequency of the  $L_{(Vcc)}$  and  $C_{(Vbatt)}$  filter is:

## **Equation 28**

$$fr = \frac{1}{2 \cdot \pi \cdot \sqrt{L(Vcc) \cdot C(Vbatt)}}$$

(34)

The equation for the L<sub>(Vcc)</sub>, C(Vbatt) filter transfer function Vout/Vin:

## **Equation 29**

$$\frac{V_{out}}{V_{in}} = \frac{\frac{1}{j\omega C_{(Vbatt)}}}{j\omega L_{(Vcc)} + \frac{1}{j\omega C_{(Vbatt)}}}$$

(35)

Where  $V_{in}$  is the device  $V_{CC_i}$  while  $V_{out}$  is the  $V_{batt}$  as the filter is intended to cut the noise generated by the Hbridge while operating in PWM. Artificial network (LISN to couple spectrum analyzer with DUT) impedance and internal resistance of V<sub>batt</sub> are considered negligible.

According to transfer function given above, L<sub>(Vcc)</sub> C<sub>(Vbatt)</sub> filter attenuation in dB can be expressed as:

AN5026 - Rev 2.0 page 32/109

#### **Equation 30**

$$Att._{dB} = 20*log \left| \frac{Vout}{Vin} \right| = 20*log \left| \frac{\frac{1}{j\omega C(Vbatt)}}{j\omega L(Vcc) + \frac{1}{j\omega C(Vbatt)}} \right| = 20*log$$

$$\left| \frac{1}{1 - 4*\pi^2 * f^2 * L(Vcc) * C(Vbatt)} \right| \approx 20*log \left| \frac{1}{4*\pi^2 * f^2 * L(Vcc) * C(Vbatt)} \right|$$

(36)

Where, considering frequencies whose attenuation values, in absolute value, are generally higher or equal to 40dB, we can suppose:

$$1 \ll 4*\pi^2 f^2 L(Vcc) C(Vbatt)$$

(37)

Selection criteria for the input power inductor  $L_{(Vcc)}$  include inductance value, rated current, series resistance, power rating (internal temperature rise) and size.

The power dissipated inside the inductor depends on the typical DC resistance R<sub>DCR</sub> and worst case input RMS current:

#### **Equation 31**

$$P_{L(Vcc)} = R_{DCR} \cdot I_{(vcc)}^{2} \tag{38}$$

Taking the criteria into account,  $L_{(Vcc)}$  is generally in the range of 1  $\mu H$  to 30  $\mu H$ .

According to general conducted EMC rules or specific customer requirements, minimum noise attenuation in dB can be chosen at a given frequency (generally the lower value in the measurement frequency range). Starting from the selected  $L_{(Vcc)}$  value and required noise attenuation level, we can express  $C_{(Vbatt)}$  as:

#### **Equation 32**

$$C_{(Vbatt)} = \frac{1}{L_{(Vcc)}} \cdot \left( \frac{10 - \frac{Att \cdot dB}{40}}{2 \cdot \pi \cdot f} \right)^2 = \frac{1}{L_{(Vcc)}} \cdot \left( \frac{10 \frac{|Att \cdot dB|}{40}}{2 \cdot \pi \cdot f} \right)^2$$

(39)

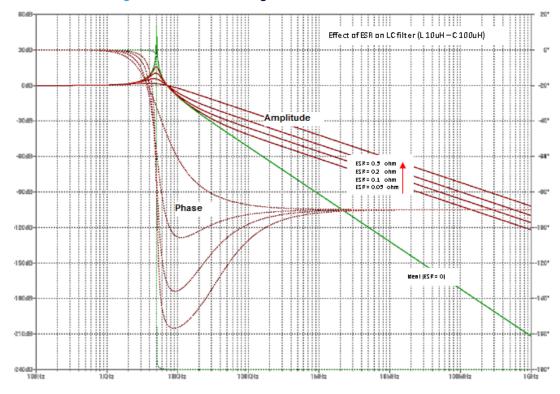

The real attenuation of the PI filter made of the  $L_{(Vcc)}$  and  $C_{(Vbatt)}$  components just dimensioned is actually lower than the value calculated in Equation 30. This mainly due to the equivalent series resistance (ESR) of  $C_{(Vbatt)}$ , called FSR.

To determine the attenuation of the real filter, given that

$$1 \ll 4*\pi^2 f^2 L(Vcc) C(Vbatt)$$

$$\tag{40}$$

we use the formula:

#### **Equation 33**

$$Att._{dB} = 20 \cdot log \sqrt{\frac{1}{1 + w^2 \cdot L \cdot C \cdot \frac{w^2 \cdot L \cdot C - 2}{1 + w^2 \cdot ESR^2 \cdot C^2}}}$$

$$\tag{41}$$

Where:

- ω=2.π.f

- L=L(Vcc)

- C=C<sub>(Vbatt)</sub>

- ESR=ESR<sub>C(Vbatt)</sub>

The figure below illustrates the effect of rising ESR and compares the ideal and real cases for a filter where  $L_{(Vcc)}$  = 10  $\mu$ H and  $C_{(Vbatt)}$  = 100  $\mu$ F. The ESR acts as a damping resistor which partially compensates the resonance effect.

AN5026 - Rev 2.0 page 33/109

Figure 26. Attenuation diagram of Pi-filter with different ESR

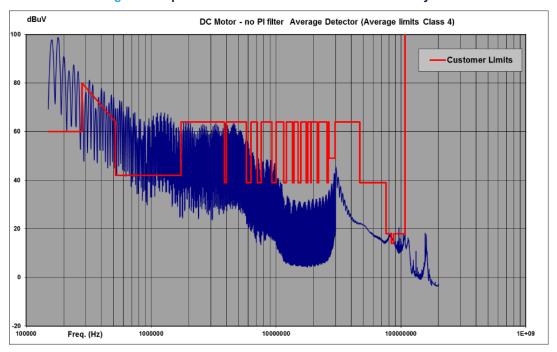

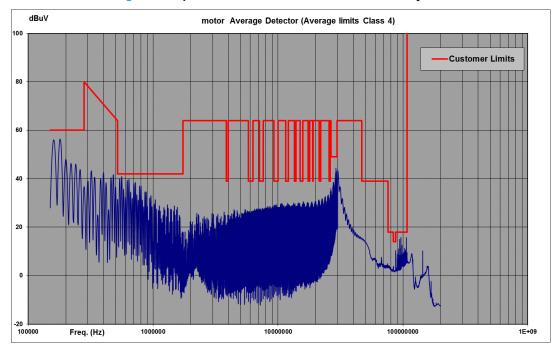

Below we can see an example regarding the benefit we can obtain introducing PI filter on the Vbatt line. Without a filter the CISPR25 spectrum (compared to customer limits TL965EN VW) is above class4 limit mask in almost all frequency ranges; by adding a PI filter, dimensioned as written in Equation 32, emissions on battery line decrease significantly.

The filter is dimensioned considering that a real attenuation of -50dB minimum at 150 kHz frequency is required, bearing in mind that the theoretical and real attenuation are different because of the ESR.

A simplified schematic and component values are shown in Figure 27. Simplified schematic and component values.

By setting for example  $L_{(Vcc)}$  = 6µH inductance and taking into account Equation 32 where we considered the theoretical Attenuation of -70dB, we calculated a capacitance value of 593 µF for  $C_{(Vbat)}$  capacitor. Using a commercial capacitor with a capacitance of 470 µF, we obtain through Equation 30 about -68 dB theoretical attenuation instead of -70 dB.

AN5026 - Rev 2.0 page 34/109

Figure 27. Simplified schematic and component values

The above figure shows the spectrum measured without putting the filter on battery line, while the figure below shows the spectrum with a PI filter on the battery line.

We can see emissions are about 50 dB lower in low frequency range. This allows the spectrum to be below the class4 limit mask.

AN5026 - Rev 2.0 page 35/109

Figure 29. Spectrum measured with PI filter on battery line

As shown in the two figures, the real attenuation as the absolute value, is 20 dB lower than the theoretical one due to ESR of  $C_{(Vhat)}$ , about 50 m $\Omega$  in this case.

In case the real filter does not fulfill the attenuation specification, we can dimension the filter by assigning a higher theoretical attenuation in Equation 32, in order to compensate the ESR value and repeating the verification through Equation 33.

## 3.2.5.2 Capacitors on VNH7XXX Outputs (C(OUT)) and on Vcc (C2(Vcc))

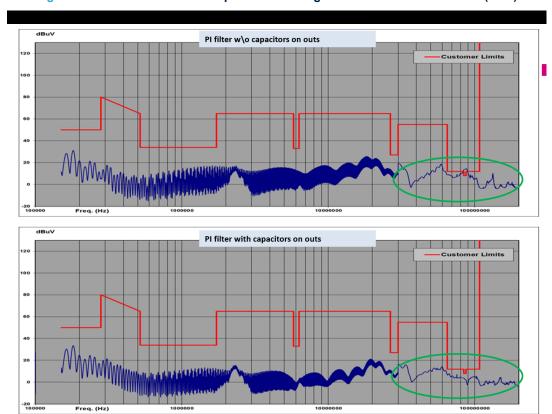

Ceramic capacitors on the VNH7XXX outputs help improve application EMI and ESD performance. Their values depend on the PWM frequency, on the inductive energy in place and on the motor wires.

During motor control in PWM, EM disturbance is injected into the VNH7XXX output pins either due to the antenna effect in car wiring or due to motor brushes. Capacitors on outputs create a path to GND for those disturbances, thus avoiding their return to  $V_{\text{batt}}$ .

They also smooth falling and rising edges of output waveforms, which benefits emissions at high frequencies (reducing emissions conducted on batt).

Capacitor values between 47 nF and 100 nF are recommended: values below this have little effect and values above don't provide any further benefits and may negatively affect output waveforms and increase switching losses.

C2<sub>(Vcc)</sub> values between 47 nF and 100 nF are also recommended for similar reasons.

The following VNH7040AY spectra with and without  $C_{(OUT)}$  highlights the beneficial effect of the output capacitor at high frequencies.

AN5026 - Rev 2.0 page 36/109

Figure 30. Conducted emission spectra according CISPR25 with and without C(OUT)

# 3.2.6 PCB layout considerations

In an H-bridge driver, high current paths and low current paths are all near each other. Alternating current (ac) paths carry spikes and noise, high direct current (dc) produces significant voltage drops and low current paths are sensitive to noise.

We can group the signals thus:

- High frequency and high current (i.e., H-bridge outputs)

- · Digital at low frequency (Like INX signals)

- Digital at high frequency (like PWM signals)

A PCB floor plan is important to minimize current loop areas and arrange the power components so that the current flows smoothly, avoiding sharp corners and narrow paths. This helps reduce parasitic capacitance and inductance, therefore, eliminating ground bounce.

The best performance in terms of parasitic inductance and EMC can be reached with a 3- or 4-layer PCB with a dedicated GND plane that improves filtering efficiency.

All filtering capacitors (mainly  $C1_{(Vcc)}$  and  $C2_{(Vcc)}$ ) must be placed as close as possible to the device terminals to keep the parasitic inductors of the PCB-wires as low as possible.

To keep the RF noise from the DC motor low and reach good immunity from ESD, the  $C_{(OUT)}$  and  $C_{(Vbatt)}$  capacitors must be placed on the board connector and directly soldered to the module GND usually in star connection with all possible ground signals (Digital GND, Analog GND and Power GND).

The best ESD performance can be achieved by putting an ESD filtering component like a transil or ceramic capacitor as close as possible to the connector pin and well-grounded by via to the ground plane.

A multilayer PCB is better than a 2-layer PCB for heat dissipation. For improved thermal and electrical conduction, a 2-ounce-or-higher copper thickness may be used in place of the standard 1 ounce. Several PGND planes connected together with vias also help.

AN5026 - Rev 2.0 page 37/109

Figure 31. Optimized connection between Drain LS and Source HS and  $GND_B$  connection (symmetrical connection)

GAPG0210151549CFT

AN5026 - Rev 2.0 page 38/109

# 4 Load and device compatibility

Matching the right motor driver device with the motor influences the operational behavior and lifetime of the device.

Embedded protections like current limitation, current shutdown, power limitation and over temperature shutdown never intervene during normal device operation, only during anomalous, transitory fault conditions.

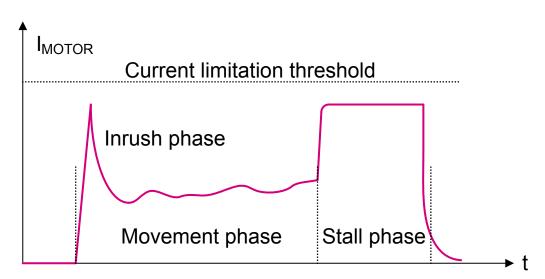

In general we can recognize three phases of motor current demand.

- Inrush phase: the motor drive device can deliver above-nominal current for a short time to provide peak torque to start the motor; the peak torque of the starting motor determines peak current inrush current of the starting motor

- Movement phase: a moving motor draws less current; it is generally the desired motor operation phase

- **Stall phase**: the motor loses its movement speed and current becomes maximal. The current is limited by the armature winding resistance only

Figure 32. Generic motor current profile

# 4.1 Protections summary

# 4.1.1 PowerMOS High Side protections

- Current limitation (ILIMH) this protection limits the maximum current flowing over the activated Power MOS

- Power limitation when the monitored difference between junction and case temperature rises above the threshold, Power MOS is shut down.

- Junction overtemperature when the junction temperature (sensor is positioned close to Power MOS)

threshold is breached, the Power MOS is shut down.

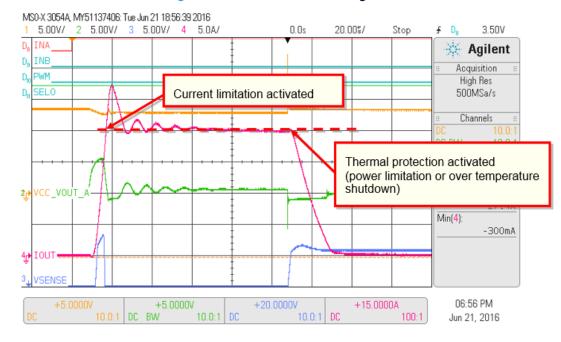

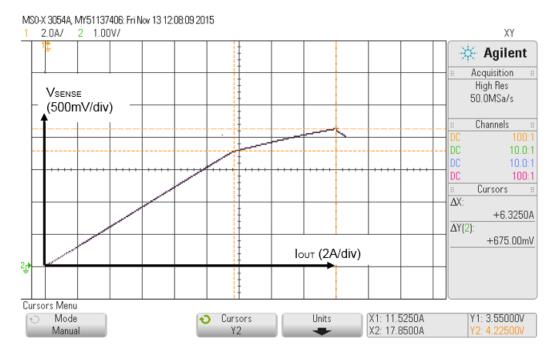

The following example depicts motor load switching on the VNH7070AS high side:

- 1. the motor inrush current exceeds the threshold limit

- 2. the high side Power MOS limits the current supplied to the load

- 3. the high (limited) current flowing though the Power MOS increases its temperature to above the threshold

- 4. a further power limitation or overtemperature protection is triggered

- 5. the Power MOS is deactivated, signaled by the VSENSE H level on the MultiSense output

AN5026 - Rev 2.0 page 39/109

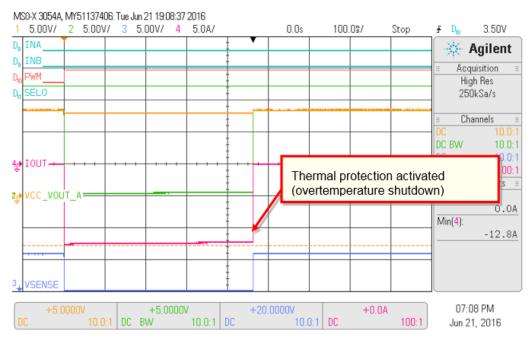

Figure 33. Current limitation on high side

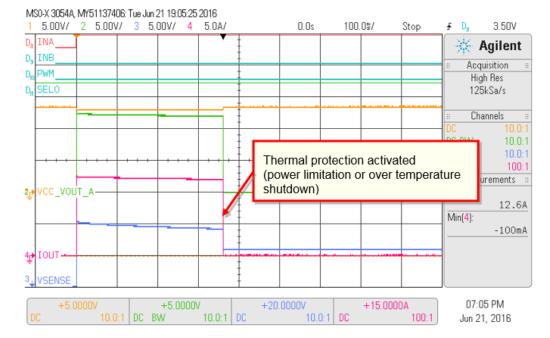

#### The next example shows:

- 1. the current threshold on the high side Power MOS is not reached

- 2. power dissipation on the high side still triggers the thermal protection triggering

- 3. output is deactivated and fault state is signaled by VSENSE\_H

Figure 34. Thermal protection on high side

### 4.1.2 PowerMOS Low Side protections

Junction over temperature – exceeding absolute threshold on junction temperature sensor (positioned close to Power MOS) causes Low Side Power MOS latch off.

AN5026 - Rev 2.0 page 40/109

Overcurrent detector – exceeding the shutdown current (I<sub>LS\_SD</sub>) flowing through low side Power MOS causes its latch off.

The following example shows:

- 1. an overload on the low side that exceeds the maximum current threshold

- 2. the Power MOS is shut down

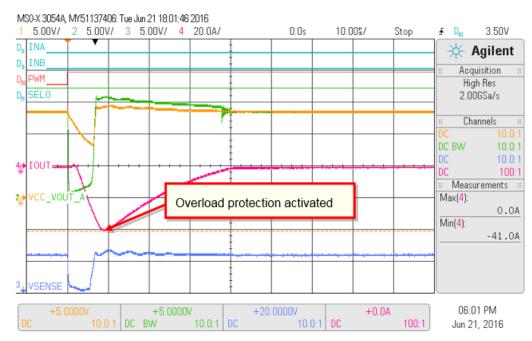

Figure 35. Overload on low side

Figure 36. Thermal protection on low side

AN5026 - Rev 2.0 page 41/109

During the motor inrush and movement phases, none of the protections should be activated. If motor parameters are not compatible with the device and one or more protections are triggered, device control will be interrupted.

### 4.1.3 Motor phases and protections

#### 4.1.3.1 Inrush phase

During the inrush phase (where the main parameters are the inrush current and time) the current peak should not activate **any of** the low side overcurrent protections, high side power limitations or high side and low side over temperature triggers.

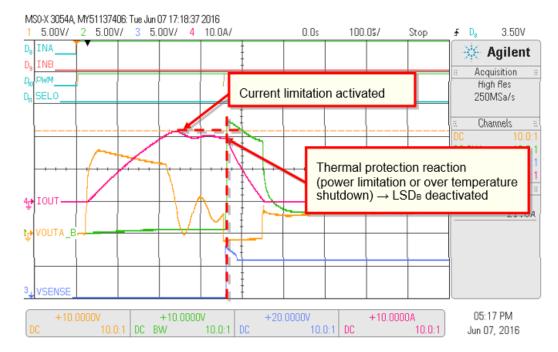

The figure below shows an example of underestimated motor load driven by a VNH7070BAS:

- HS<sub>A</sub> and LS<sub>B</sub> are active

- 2. the current flowing through the load rises to the current limitation threshold

- 3. the current is limited to the threshold level

- 4. before the inrush phase has elapsed, the thermal protection deactivates the LS<sub>B</sub>

- 5. the error is signaled by the MultiSense output by VSENSE H level

Figure 37. Inrush phase

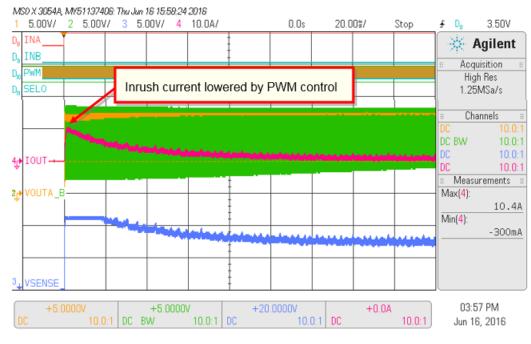

To achieve a smooth motor start during the inrush phase (by limiting inrush current), PWM control can be applied over the H-bridge PWM pin.

The figure below shows motor activation with PWM mode control (duty cycle 50%):

- 1. the maximum current over the motor load during the inrush phase gets limited

- 2. the motor activation phase is accordingly prolonged

- 3. none of the protections are activated and motor is started successfully

AN5026 - Rev 2.0 page 42/109

Figure 38. Motor activation with PWM

### 4.1.3.2 Movement phase

When the motor reaches the movement phase, it typically draws less current than the inrush current. The duration of the movement phase is important because energy dissipated in the high and low side Power MOS increases overall temperature, which may trigger temperature protections (power limitation or over temperature shutdown). If speed reduction or regulation is required, PWM control can also be applied (all protections are active during this type of control).

The approximate dissipated energy in the H-bridge can be estimated thus (assuming motor current is more or less constant):

#### Equation 34: Power dissipation on activated high side

$$P_{ONHS}[W] = R_{ONHS} * I_{RMS\_MOT}^2$$

(42)

# Where:

- R<sub>ONHS</sub> = static resistance on high side

- I<sub>MOT</sub> = steady current of activated load (motor)

### Equation 35: Power dissipation on activated low side (active state only while output driven in PWM mode)

$$P_{ONLS}[W] = R_{ONLS}*I_{RMS\_MOT}^2*DutyCycle$$

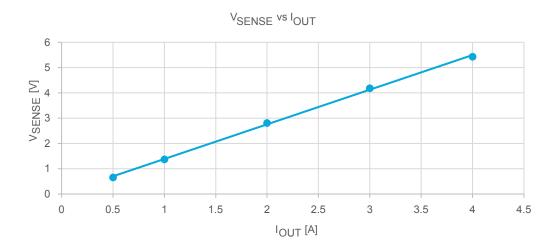

(43)

### Where: