### Automotive 3-Phase motor gate driver unit

#### TQFP48 (exposed pad down)

## **Features**

- Full ISO26262 compliant, ASIL-D systems ready

- VDH motor supply voltage range from 4.5 V to 75 V for working in single (12 V systems), double (24 V systems) and 48 V battery applications

- 3.3 V internal supply voltage generated from 5 V on VDD pin

- Digital I/O compatible to 3.3 V/5 V logics

- 6 separate N-channel FET pre-drivers:

- dedicated source connection to each FET

- the device can withstand -14 V to 95 V on motor connection pins

- 0% to 100% duty cycle operation support

- dedicated PWM input pin for each gate driver

- 3 differential high accuracy current monitors for ground referred current measurements:

- ADC/DAC architecture

- SPI adjustable Gain Factor and Output Offset

- built-in error calibration

- the device can withstand -14 V to 6 V on input sensing pins

- SPI readable current measurement

- 0 to 4.6 V DAC output dynamic range

- 3 real time phase voltage monitor channels:

- SPI programmable phase voltage feedback;

- SPI readable phase duty cycle measurement;

- 32-bits 10 MHz SPI interface with 5-bit CRC and 1bit frame counter for internal setting, self-test and full diagnostics

- Protection and diagnostic:

- SPI programmable VDS diagnostic and protection in on state

- SPI programmable Dead Time protection

- SPI programmable Shoot-trough diagnostic and protection

- Open load, short to GND and short to battery diagnostic in off state

- Over-temperature diagnostic and protection with SPI programmable warning flag

- SPI readable Tj measurement

- Ground loss diagnostic

- System clock monitoring

- Power supply pins VDD, VDH, VBP over-voltage and under-voltage diagnostic

- FET driver supply VPRE and VCP under-voltage and over-voltage diagnostic

- SPI Window Watchdog

- Fault status flag output

| Product summary |                        |           |

|-----------------|------------------------|-----------|

| Order<br>code   | Package                | Packing   |

| L9908           | TQFP48 (exp. pad down) | Tray      |

| L9908-TR        |                        | Tape&Reel |

#### **Application**

- EPS Electronic Power Steering

- HVAC Blowers Heating, ventilation, and air conditioning

- · Engine Cooling Fans

- · Electronic Brake Booster

- EWP, EFP, EOP

#### **Description**

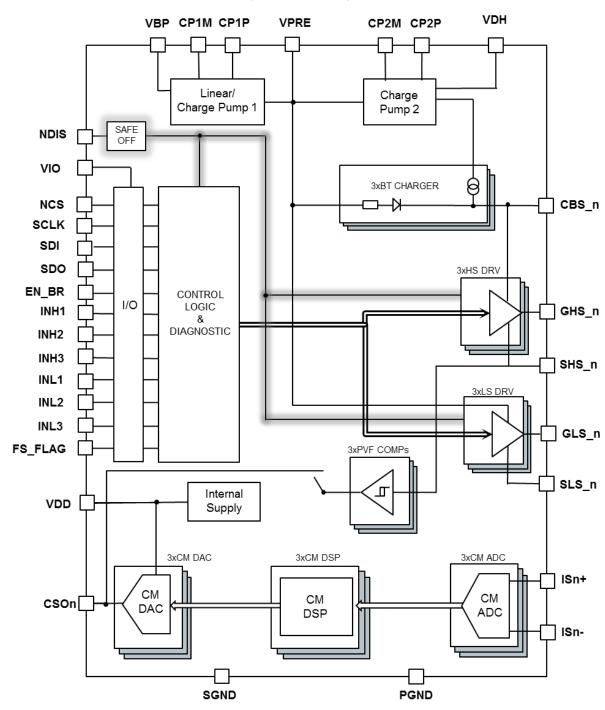

L9908 is a gate driver unit (GDU) for controlling 6 N-channel FETs for brushless motors in automotive applications.

Each one of the 3 half bridge drivers channels (HS/LS couples) can be independently configured allowing different load driving and is able to withstand -14 V to 95 V excursion on motor's pins.

Through 6 dedicated parallel input the pre-driver stages can be controlled independently supporting duty cycle operations from 0% to 100% and allowing to implement all kinds of electric motor control strategy. A dedicated combination of regulators, charge pumps and bootstrap circuits allows L9908 to be suitable to operate in passenger, commercial or hybrid vehicles.

Safe operation of half bridges is ensured by shoot-trough diagnosis, dead-time, short to battery, short to ground and open load detection plus a real time phase voltage monitoring.

L9908 is equipped with 3 independent high accuracy current monitor channels with SPI-configurable input differential voltage ranges for ground referenced current measurements, with 5 V/3.3 V output dynamic range compatibility.

L9908 implements diagnostics on external and internal supply, ground level, internal temperature.

A 32-bit out of frame SPI-slave interface is implemented for communication up to 10 MHz between L9908 and uC. SPI communication is safe-guarded by 5-bit CRC, 1bit frame counter, frame length check and an SPI-configurable Window Watchdog.

DB4343 - Rev 1 page 2/12

## 1 Block diagram and pin description

Figure 1. Block diagram

DB4343 - Rev 1 page 3/12

FS\_FLAG INH2 INH3 INL2 NL3 INH1 N VPRE VBP 48 47 46 45 44 43 42 41 40 39 38 37 1 36 NCS CP2M 2 35 SCLK CP2P 3 SDI 34 VDH 4 33 SHS\_1 SDO 5 VIO 32 GHS\_1 6 CSO3/PVF 31 CBS\_1 7 30 CSO2 SHS\_2 CSO1 8 29 GHS\_2 9 28 VDD CBS\_2 10 27 SGND SHS\_3 11 26 EN\_BR GHS\_3 12 25 NDIS CBS\_3 13 16 18 19 20 21 22 23 24 14 15 17 GLS\_2 GLS\_1 S2+ 83 151+GLS <u>83</u> <u>S1</u>-52 SIS SIS

Figure 2. Pin connection diagram (top view)

Legenda: I = Input, O = Output, P = Power Supply, G = Ground, I/O = Input/Output

Table 1. Pin list description

| Pin# | Pin name | Description                                                                         | Pin type | Class |

|------|----------|-------------------------------------------------------------------------------------|----------|-------|

| 1    | NCS      | SPI Chip Select Input (Active LOW)                                                  | I        | Local |

| 2    | SCLK     | SPI Serial Clock Input                                                              | I        | Local |

| 3    | SDI      | SPI Serial Data Input                                                               | I        | Local |

| 4    | SDO      | SPI Serial Data Output                                                              | 0        | Local |

| 5    | VIO      | Power supply for digital output                                                     | Р        | Local |

| 6    | CSO3/PVM | Current monitor 3 analog output. Phase voltage feedback output                      | 0        | Local |

| 7    | CSO2     | Current monitor 2 analog output                                                     | 0        | Local |

| 8    | CSO1     | Current monitor 1 analog output                                                     | 0        | Local |

| 9    | VDD      | Power supply input for internal circuitry and current monitors analog output (CSOn) | Р        | Local |

| 10   | SGND     | Signal Ground (Analog, Digital, Reference)                                          | G        | Local |

DB4343 - Rev 1 page 4/12

| Pin# | Pin name | Description                                     | Pin type | Class  |

|------|----------|-------------------------------------------------|----------|--------|

| 11   | EN_BR    | Bridge Enable Input (Active HIGH)               | I        | Local  |

| 12   | NDIS     | Safe switch-off activation Input (Active LOW)   | I        | Local  |

| 13   | IS3-     | Current monitor 3 negative input                | I        | Local  |

| 14   | IS3+     | Current monitor 3 positive input                | I        | Local  |

| 15   | IS2-     | Current monitor 2 negative input                | I        | Local  |

| 16   | IS2+     | Current monitor 2 positive input                | I        | Local  |

| 17   | IS1-     | Current monitor 1 negative input                | I        | Local  |

| 18   | IS1+     | Current monitor 1 positive input                | I        | Local  |

| 19   | SLS_3    | Source connection of LS FET, phase 3            | I/O      | Local  |

| 20   | GLS_3    | Gate connection of LS FET, phase 3              | I/O      | Local  |

| 21   | SLS_2    | Source connection of LS FET, phase 2            | I/O      | Local  |

| 22   | GLS_2    | Gate connection of LS FET, phase 2              | I/O      | Local  |

| 23   | SLS_1    | Source connection of LS FET, phase 1            | I/O      | Local  |

| 24   | GLS_1    | Gate connection of LS FET, phase 1              | I/O      | Local  |

| 25   | CBS_3    | Bootstrap capacitor of HS, phase 3              | I/O      | Local  |

| 26   | GHS_3    | Gate connection of HS FET, phase 3              | I/O      | Local  |

| 27   | SHS_3    | Source connection of HS FET, phase 3            | I/O      | Global |

| 28   | CBS_2    | Bootstrap capacitor of HS, phase 2              | I/O      | Local  |

| 29   | GHS_2    | Gate connection of HS FET, phase 2              | I/O      | Local  |

| 30   | SHS_2    | Source connection of HS FET, phase 2            | I/O      | Global |

| 31   | CBS_1    | Bootstrap capacitor of HS, phase 1              | I/O      | Local  |

| 32   | GHS_1    | Gate connection of HS FET, phase 1              | I/O      | Local  |

| 33   | SHS_1    | Source connection of HS FET, phase 1            | I/O      | Global |

| 34   | VDH      | Drain connection of HS FETs                     | Р        | Global |

| 35   | CP2P     | Charge Pump 2 positive input of fly capacitance | I/O      | Local  |

| 36   | CP2M     | Charge Pump 2 negative input of fly capacitance | I/O      | Local  |

| 37   | VBP      | Pre-regulation stage power supply               | Р        | Global |

| 38   | CP1M     | Charge Pump 1 negative input of fly capacitance | I/O      | Local  |

| 39   | PGND     | Power Ground (Charge Pump 1 and 2)              | G        | Local  |

| 40   | CP1P     | Charge Pump 1 positive input of fly capacitance | I/O      | Local  |

| 41   | VPRE     | Pre-regulated voltage for HS/LS Vgs driving     | I/O      | Local  |

| 42   | INH3     | PWM command for HS, phase 3 (Active HIGH)       | I        | Local  |

| 43   | INH2     | PWM command for HS, phase 2 (Active HIGH)       | I        | Local  |

| 44   | INH1     | PWM command for HS, phase 1 (Active HIGH)       | I        | Local  |

| 45   | INL3     | PWM command for LS, phase 3 (Active HIGH)       | I        | Local  |

| 46   | INL2     | PWM command for LS, phase 2 (Active HIGH)       | I        | Local  |

| 47   | INL1     | PWM command for LS, phase 1 (Active HIGH)       | I        | Local  |

| 48   | FS_FLAG  | Fault status flag output (Active LOW)           | 0        | Local  |

|      | Exp. PAD | Cooling slug to be connected to GND plane       |          |        |

DB4343 - Rev 1 page 5/12

## Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

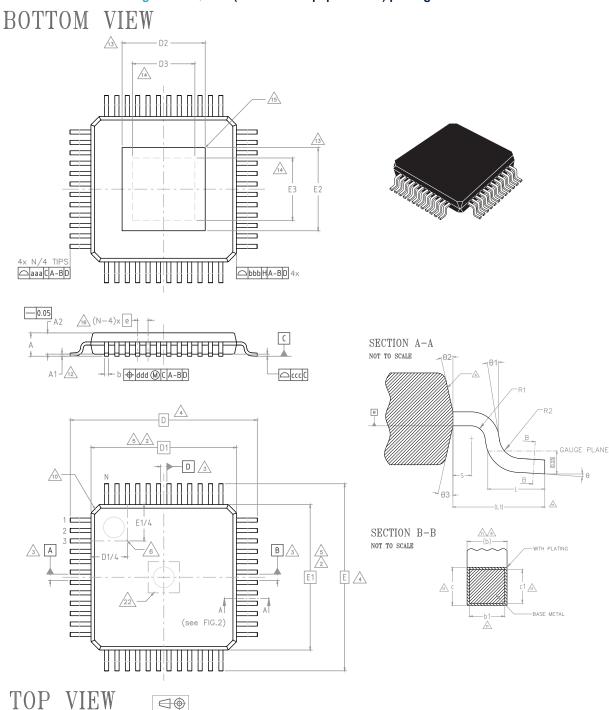

#### 2.1 TQFP48 (7x7x1 mm exp. pad down) package information

Figure 3. TQFP48 (7x7x1 mm exp. pad down) package outline

DB4343 - Rev 1 page 6/12

Table 2. LQFP64 (10x10x1.4 mm exp. pad up) package mechanical data

| Symbol - | Dimensions in mm |                 |      |  |

|----------|------------------|-----------------|------|--|

|          | Min.             | Тур.            | Max. |  |

| Α        | -                | -               | 1.2  |  |

| A1       | 0.04             | -               | 0.15 |  |

| A2       | 0.95             | 1.00            | 1.05 |  |

| b        | 0.17             | 0.22            | 0.27 |  |

| С        | 0.09             | -               | 0.20 |  |

| D        |                  | 9.00            |      |  |

| D1       |                  | 7.00            |      |  |

| D2       | -                | -               | 4.15 |  |

| D3       | 3.89             | -               | -    |  |

| е        | -                | 0.50            | -    |  |

| Е        |                  | 9.00            |      |  |

| E1       |                  | 7.00            |      |  |

| E2       | -                | -               | 4.15 |  |

| E3       | 3.89             | -               | -    |  |

| L        | 0.45             | 0.60            | 0.75 |  |

| L1       | 1.00             |                 |      |  |

| N        | 48               |                 |      |  |

| R1       | 0.08             | -               | -    |  |

| R2       | 0.08             | -               | 0.2  |  |

| S        | 0.2              | -               | -    |  |

|          | Tolerance of fo  | rm and position |      |  |

| aaa      | -                | 0.2             | -    |  |

| bbb      | -                | 0.2             | -    |  |

| ccc      | -                | 0.08            | -    |  |

| ddd      | -                | 0.08            | -    |  |

DB4343 - Rev 1 page 7/12

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 03-Nov-2020 | 1       | Initial release. |

DB4343 - Rev 1 page 8/12

## **Contents**

| 1                     | Block diagram and pin description |                                                     |     |

|-----------------------|-----------------------------------|-----------------------------------------------------|-----|

| 2 Package information |                                   | kage information                                    | . 6 |

|                       | 2.1                               | TQFP48 (7x7x1 mm exp. pad down) package information | . 6 |

| Rev                   | ision                             | history                                             | . 8 |

## **List of tables**

| Table 1. | Pin list description                                      | 4 |

|----------|-----------------------------------------------------------|---|

| Table 2. | LQFP64 (10x10x1.4 mm exp. pad up) package mechanical data | 7 |

| Table 3. | Document revision history                                 | 8 |

DB4343 - Rev 1 page 10/12

# **List of figures**

| Figure 1. | Block diagram                                   | 3 |

|-----------|-------------------------------------------------|---|

| Figure 2. | Pin connection diagram (top view)               | 4 |

| Figure 3. | TQFP48 (7x7x1 mm exp. pad down) package outline | 6 |

DB4343 - Rev 1 page 11/12

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics - All rights reserved

DB4343 - Rev 1 page 12/12