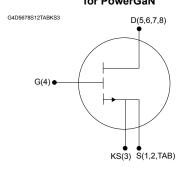

## 700 V, 74 m $\Omega$ typ., 21 A, e-mode PowerGaN transistor

PowerFLAT 5x6 HV for PowerGaN

#### **Features**

| Order code   | V <sub>DS</sub> | R <sub>DS(on)</sub> max. | I <sub>D</sub> | Series |

|--------------|-----------------|--------------------------|----------------|--------|

| SGT100R70FDC | 700 V           | 100 mΩ                   | 21 A           | G-HEMT |

- · Enhancement mode normally off transistor

- Very high switching speed

- · High power management capability

- Extremely low capacitances

- Zero reverse recovery charge

- ESD safeguard

### **Applications**

- AC-DC converters

- DC-DC converters

- USB type-C PD adapters and quick chargers

- · Wireless charging

### **Description**

The SGT100R70FDC is a 700 V, 21 A e-mode PowerGaN transistor. The resulting device provides extremely low conduction losses, high current capability and ultrafast switching operation to enable high power density and unbeatable efficiency performances.

#### **Product status link**

SGT100R70FDC

| Product summary         |                                  |  |  |

|-------------------------|----------------------------------|--|--|

| Order code SGT100R70FDC |                                  |  |  |

| Marking                 | 100R70F                          |  |  |

| Package                 | PowerFLAT 5x6 HV for<br>PowerGaN |  |  |

| Packing                 | Tape and reel                    |  |  |

# 1 Electrical ratings

$T_C$  = 25 °C unless otherwise specified.

Table 1. Absolute maximum ratings

| Symbol           | Parameter                                                 | Value              | Unit |

|------------------|-----------------------------------------------------------|--------------------|------|

| \/               | Drain-source voltage                                      | 700 <sup>(1)</sup> | V    |

| $V_{DS}$         | Drain-source voltage (transient, t <sub>p</sub> < 200 μs) | 800                | _ v  |

| V <sub>GS</sub>  | Gate-source voltage                                       | -6 to 7            | V    |

| I <sub>D</sub>   | Drain current (continuous)                                | 21                 | Α    |

| I <sub>DM</sub>  | Pulse drain current (t <sub>p</sub> = 10 μs)              | 41                 | Α    |

| P <sub>TOT</sub> | Total power dissipation at T <sub>C</sub> = 25 °C         | 107                | W    |

| T <sub>stg</sub> | Storage temperature range                                 | FF to 150          | °C   |

| TJ               | Operating junction temperature range                      | -55 to 150         | °C   |

<sup>1.</sup> Recommended continuous maximum bus voltage during switching operations should not exceed 450 V.

Table 2. Thermal data

| Symbol                           | Parameter                               | Value | Unit |

|----------------------------------|-----------------------------------------|-------|------|

| R <sub>thJC</sub>                | Thermal resistance, junction-to-case    | 1.16  | °C/W |

| R <sub>thJA</sub> <sup>(1)</sup> | Thermal resistance, junction-to-ambient | 69.94 | °C/W |

1. When mounted on a standard 1 inch² area of FR-4 PCB with 2-oz copper.

DB5666 - Rev 1 page 2/5

## 2 Electrical characteristics

$T_C$  = 25 °C unless otherwise specified.

Table 3. Static

| Symbol                     | Parameter                         | Test conditions                                                         | Min. | Тур. | Max. | Unit  |

|----------------------------|-----------------------------------|-------------------------------------------------------------------------|------|------|------|-------|

| I <sub>DSS</sub> Drain-sou | Desire assumed to the second      | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 700 V                          |      | 0.8  |      | μА    |

|                            | Drain-source leakage current      | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 700 V, T <sub>J</sub> = 125 °C |      | 9    |      |       |

| I <sub>GSS</sub>           | Gate-source leakage current       | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = 6 V                            |      | 90   |      | μΑ    |

| V <sub>GS(th)</sub>        | Gate threshold voltage            | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 18.3 mA            | 1.2  | 1.7  | 2.5  | V     |

| В                          | Static drain-source on-resistance | V <sub>GS</sub> = 6 V, I <sub>D</sub> = 0.5 A                           |      | 74   | 100  | mΩ    |

| R <sub>DS(on)</sub>        |                                   | V <sub>GS</sub> = 6 V, I <sub>D</sub> = 6 A, T <sub>J</sub> = 125 °C    |      | 148  |      | 11122 |

Table 4. Dynamic

| Symbol                            | Parameter                                    | Test conditions                                             | Min. | Тур. | Max. | Unit |

|-----------------------------------|----------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| C <sub>iss</sub>                  | Input capacitance                            |                                                             | -    | 130  | -    | pF   |

| C <sub>oss</sub>                  | Output capacitance                           | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 400 V, f = 100 kHz | -    | 47   | -    | pF   |

| C <sub>rss</sub>                  | Reverse transfer capacitance                 |                                                             | -    | 0.5  | -    | pF   |

| C <sub>o(er)</sub> <sup>(1)</sup> | Equivalent output capacitance energy related | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 0 to 400 V         | -    | 62.9 | -    | pF   |

| C <sub>o(tr)</sub> <sup>(2)</sup> | Equivalent output capacitance time related   | VGS - 0 V, VDS - 0 to 400 V                                 | -    | 83.4 | -    | pF   |

| $R_g$                             | Intrinsic gate resistance                    | f = 5 MHz, I <sub>D</sub> = 0 A                             | -    | 7    | -    | Ω    |

| V <sub>plat</sub>                 | Gate plateau voltage                         | V <sub>DS</sub> = 400 V, I <sub>D</sub> = 6 A               | -    | 2.1  | -    | V    |

| Qg                                | Total gate charge                            |                                                             | -    | 3.4  | -    | nC   |

| Q <sub>gs</sub>                   | Gate-source charge                           | $V_{GS} = 0$ to 6 V, $V_{DS} = 400$ V, $I_{D} = 6$ A        | -    | 0.3  | -    | nC   |

| Q <sub>gd</sub>                   | Gate-drain charge                            |                                                             | -    | 1.3  | -    | nC   |

| Q <sub>rr</sub>                   | Reverse recovery charge                      | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 400 V              | -    | 0    | -    | nC   |

| Q <sub>oss</sub>                  | Output charge                                | VGS - 0 V, VDS - 400 V                                      | -    | 32.7 | -    | nC   |

C<sub>o(er)</sub> is a constant capacitance value that gives the same stored energy as C<sub>oss</sub> while V<sub>DS</sub> is rising from 0 to the stated value

Table 5. Reverse conduction

| Symbol          | Parameter                    | Test conditions                              | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>SD</sub> | Source-drain reverse voltage | $V_{GS} = 0 \text{ V}, I_{SD} = 6 \text{ A}$ | -    | 2.4  | -    | V    |

DB5666 - Rev 1 page 3/5

<sup>2.</sup>  $C_{O(tr)}$  is a constant capacitance value that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to the stated value.

# **Revision history**

Table 6. Document revision history

| Date        | Revision | Changes        |

|-------------|----------|----------------|

| 08-Oct-2025 | 1        | First release. |

DB5666 - Rev 1 page 4/5

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

DB5666 - Rev 1 page 5/5