## Power-line communication, analog front-end

Datasheet - production data

#### **Features**

- Integrated, analog power-line driver and receiver

- EN 50065-1 CENELEC, European bands A, B, C, and D

- Supports FSK, S-FSK, and OFDM

- Supports PRIME, G3, and IEC 61334

- · Half-duplex mode

- Thermal protection

- Programmable overcurrent protection

- 10 V p-p single-ended output range

- 20 V p-p differential-ended output range

- Programmable transmitter chain (Tx) and receiver chain (Rx) filters

- · Programmable Rx and Tx gain control

- 7 V to 14 V line driver supply

- Low power consumption: 10 mW (receive mode)

- Reverse sensitivity 20 µVrms typical

- Four-wire, serial peripheral interface

- Two integrated zero cross detectors

- Temperature range: -40 °C to 125 °C

### **Applications**

- E-metering

- · Smart grid applications

- Smart light control

- Solar energy management

- Building automation

- Remote monitoring and control

#### **Description**

The ST-PLC-AFE is a power-line communication, analog front-end device capable of capacitive or transformer-coupled connections to the power line while under the control of a microcontroller or a DSP.

The line driver is able to drive low-impedance lines, requiring up to 1.65 A, into reactive loads. It can also work in differential mode for high performance, as well as single-ended mode for a low-cost bill of materials (BOM). The integrated receiver is able to detect signals down to 20  $\mu Vrms$ . The system works in half-duplex mode.

The AFE is protected against over temperature and short-circuit conditions. It also provides four adjustable current limits through an internal register. Through the four-wire serial peripheral interface, or SPI, each functional block can be enabled or disabled to optimize power consumption.

Contents ST-PLC-AFE

# **Contents**

| 1 | Pacl | kage pin description and connections                                 | 4  |

|---|------|----------------------------------------------------------------------|----|

| 2 | Gen  | eral description                                                     | 7  |

|   | 2.1  | PA block                                                             | 9  |

|   |      | 2.1.1 Typical connections to the PA                                  | 9  |

|   |      | 2.1.2 Power amplifier power management                               | 10 |

|   | 2.2  | Tx block                                                             | 11 |

|   |      | 2.2.1 Internal DAC driving mode                                      |    |

|   |      | 2.2.2 External driving mode, differential-ended power amplifier mode |    |

|   | 2.3  | Rx block                                                             | 13 |

| 3 | Abs  | olute maximum ratings and operating conditions                       | 15 |

| 4 | Elec | trical characteristics                                               | 16 |

| 5 | Reg  | isters                                                               | 24 |

| 6 | SPI  | interfaces                                                           | 28 |

|   | 6.1  | SPI timing                                                           | 28 |

|   | 6.2  | Read/write figures in SPI mode 0.0                                   | 30 |

| 7 | Pow  | vering the device and resetting the SPI and registers                | 31 |

|   | 7.1  | Turning the device on and off                                        | 31 |

|   | 7.2  | Resetting the internal registers                                     | 31 |

|   | 7.3  | Resetting the SPI                                                    | 31 |

|   | 7.4  | Use of an external DAC                                               | 32 |

| 8 | Турі | cal characteristics                                                  | 33 |

| 9 | Syst | tem timings and interruptions                                        | 37 |

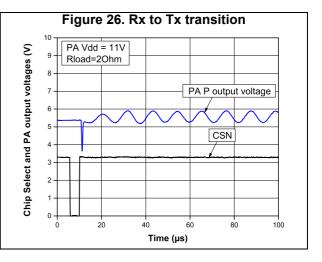

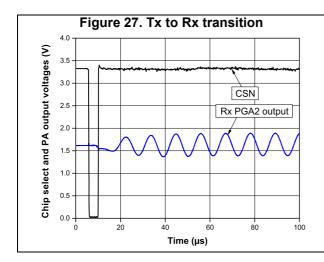

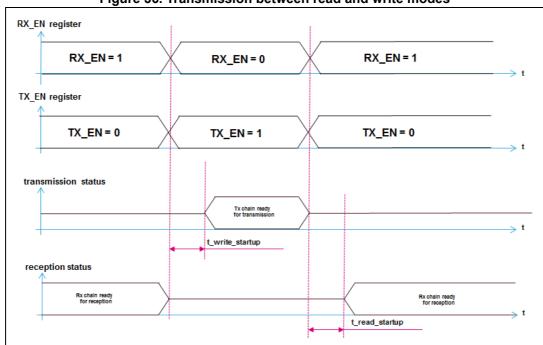

|   | 9.1  | Rx - Tx - Rx transitions                                             | 37 |

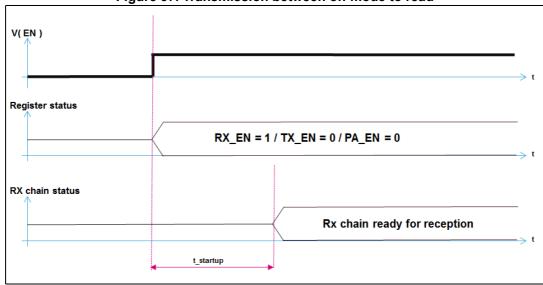

|   | 9.2  | Power-down to Rx                                                     | 37 |

|   | 9.3  | Interruptions                                                        | 38 |

|   |      | 9.3.1 Overcurrent condition                                          | 38 |

|   |      |                                                                      |    |

|    |       | 9.3.2     | Over temperature condition                                        | . 39 |

|----|-------|-----------|-------------------------------------------------------------------|------|

| 10 | Appli | cation i  | information                                                       | 40   |

|    | 10.1  | Therma    | al sensor                                                         | 40   |

|    | 10.2  | Therma    | al considerations                                                 | . 41 |

|    |       | 10.2.1    | Maximizing the heat flow from the junction temperature to the PCB | . 41 |

|    |       | 10.2.2    | Reducing the PCB thermal resistance                               | . 41 |

|    |       | 10.2.3    | Reducing supply voltage from the power amplifier                  | . 42 |

|    | 10.3  | Moving    | from differential mode to single-ended mode                       | 43   |

|    | 10.4  | Circuit   | protection                                                        | . 44 |

|    | 10.5  | Applica   | tion schematics                                                   | . 47 |

|    | 10.6  | Bill of n | naterials (BOM)                                                   | . 49 |

|    | 10.7  | ST-PLC    | C-AFE consumption (no load)                                       | . 51 |

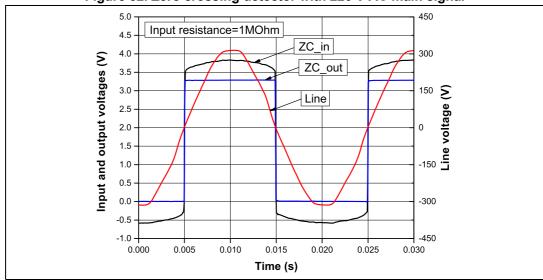

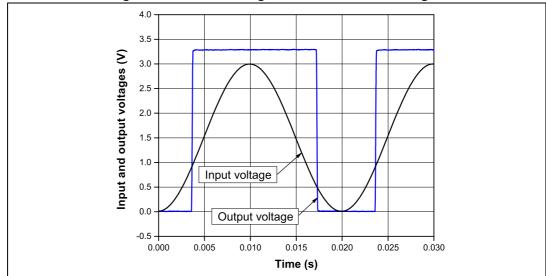

|    | 10.8  | Zero cr   | ossing detector                                                   | . 51 |

|    | 10.9  | PCB la    | yout recommendations                                              | . 52 |

|    | 10.10 | Power-    | line demonstration and development kit                            | . 52 |

| 11 | Packa | age info  | ormation                                                          | . 53 |

|    | 11.1  | QFN48     | package information                                               | 54   |

| 12 | Orde  | ring info | ormation                                                          | . 56 |

| 13 | Revis | ion his   | tory                                                              | . 57 |

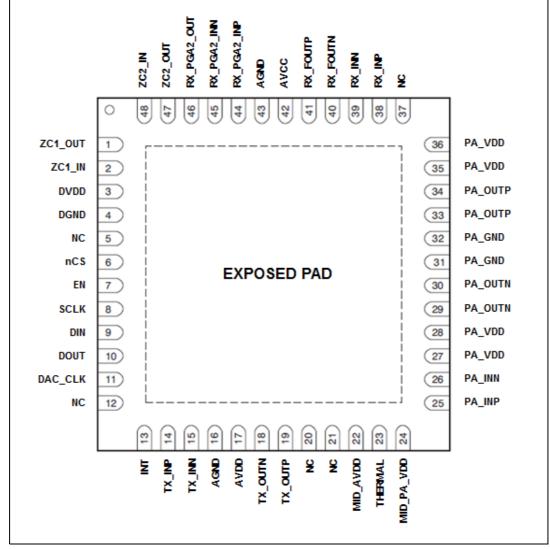

# 1 Package pin description and connections

Table 1. QFN48 pin description

| Pin no. | Name       | Туре          | Description                                                                                |

|---------|------------|---------------|--------------------------------------------------------------------------------------------|

| 1       | ZC1_OUT    | OUT ANALOG    | Zero cross detector 1 output node                                                          |

| 2       | ZC1_IN     | IN ANALOG     | Zero cross detector 1 input node                                                           |

| 3       | DVDD       | DOWED DICITAL | Digital positive supply                                                                    |

| 4       | DGND       | POWER DIGITAL | Digital ground                                                                             |

| 5       | NC1        | NC            | Not connected to the Silicon                                                               |

| 6       | nCS        |               | SPI digital select                                                                         |

| 7       | EN         | IN DIGITAL    | System enable                                                                              |

| 8       | SCLK       | - IN DIGITAL  | SPI serial clock                                                                           |

| 9       | DIN        |               | SPI digital input                                                                          |

| 10      | DOUT       | OUT           | SPI digital output                                                                         |

| 11      | DAC_CLK    | IN DIGITAL    | DAC input frequency                                                                        |

| 12      | NC2        | NC            | Not connected to the Silicon                                                               |

| 13      | INT        | OUT DIGITAL   | Interrupt on overcurrent or thermal limit                                                  |

| 14      | TX_INP     | - IN ANALOG   | DAC output (positive side)                                                                 |

| 15      | TX_INN     | IN ANALOG     | DAC output (negative side)                                                                 |

| 16      | AGND       | POWER ANALOG  | Analog ground                                                                              |

| 17      | AVDD       | POWER ANALOG  | Analog positive supply                                                                     |

| 18      | TX_OUTN    | OLIT ANIAL OC | Tx LPF output (negative side)                                                              |

| 19      | TX_OUTP    | OUT ANALOG    | Tx LPF output (positive side)                                                              |

| 20      | NC3        | - NC          | Not connected to the Cilians                                                               |

| 21      | NC4        |               | Not connected to the Silicon                                                               |

| 22      | MID_AVDD   |               | Rx common mode voltage, AVDD/2 to be connected to 150 nF capacitor                         |

| 23      | THERMAL    | OUT ANALOG    | Thermal sensor output voltage, to be connected to an ADC                                   |

| 24      | MID_PA_VDD |               | PA common mode voltage, PA supply voltage divided by 2, to be connected to 10 nF capacitor |

| 25      | PA_INP     | INI ANIAL OG  | PA non inverting input                                                                     |

| 26      | PA_INN     | IN ANALOG     | PA inverting input                                                                         |

| 27      | PA_VDD     | DOMED DA      |                                                                                            |

| 28      | PA_VDD     | POWER PA      | Power amplifier positive supply                                                            |

| 29      | PA_OUTN    | OUT DA        | Daniel de la constantina                                                                   |

| 30      | PA_OUTN    | OUT PA        | PA output inverting side                                                                   |

4/58 DocID028727 Rev 1

Table 1. QFN48 pin description (continued)

| Pin no. | Name        | Туре         | Description                                      |  |  |  |

|---------|-------------|--------------|--------------------------------------------------|--|--|--|

| 31      | PA_GND      | POWER PA     | Power amplifier ground                           |  |  |  |

| 32      | PA_GND      | FOWERFA      | Power amplifier ground                           |  |  |  |

| 33      | PA_OUTP     | OUT PA       | PA output non inverting side                     |  |  |  |

| 34      | PA_OUTP     | TOOTPA       | PA output non inverting side                     |  |  |  |

| 35      | PA_VDD      | POWER PA     | Power amplifier positive supply                  |  |  |  |

| 36      | PA_VDD      | FOWERFA      | Power amplifier positive suppry                  |  |  |  |

| 37      | NC5         | NC           | Not connected to the Silicon                     |  |  |  |

| 38      | RX_INP      | IN ANALOG    | Rx chain input pin, non-inverting input          |  |  |  |

| 39      | RX_INN      | IN ANALOG    | Rx chain input pin, inverting input              |  |  |  |

| 40      | RX_FOUTN    | OUT ANALOG   | Rx output after LPF filter, inverting output     |  |  |  |

| 41      | RX_FOUTP    | TOOT ANALOG  | Rx output after LPF filter, non-inverting output |  |  |  |

| 42      | AVDD        | POWER ANALOG | Analog positive supply                           |  |  |  |

| 43      | AGND        | POWER ANALOG | Analog ground                                    |  |  |  |

| 44      | RX_PGA2_INP | IN ANALOG    | Rx PGA2 input pin, non-inverting input           |  |  |  |

| 45      | RX_PGA2_INN | IN ANALUG    | Rx PGA2 input pin, inverting input               |  |  |  |

| 46      | RX PGA2_OUT | OUT ANALOG   | Rx PGA2 output pin, single mode                  |  |  |  |

| 47      | ZC2_OUT     | TOOT ANALOG  | Zero cross detector 2 output node                |  |  |  |

| 48      | ZC2_IN      | IN ANALOG    | Zero cross detector 2 input node                 |  |  |  |

Figure 1. QFN48 pin connections (top view)

1. The exposed pad must be connected to ground

577

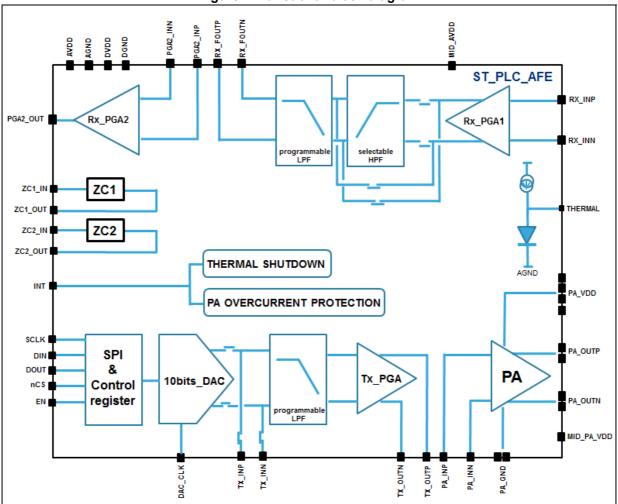

## 2 General description

The ST-PLC-AFE combines a digital-to-analog converter (DAC), an adaptive gain control (AGC), programmable filters, and a line driver on a single chip. The architecture is divided into three primary functional blocks:

Power amplifier (PA)

The PA is characterized by the following features:

- Differential or single-ended output architecture

- 1.65 A drive capability @ 14 Vpp

- Gain of 6.9 V/V

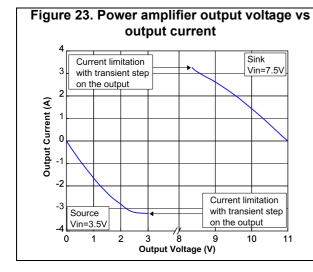

- PA current limiter with four programmable limits: 0.5 A, 1 A, 1.5 A, and 2.1 A

- Integrated thermometer placed closed to the PA

- Transmitter chain (Tx)

The Tx is characterized by the following features:

- Can work with a 10-bit internal DAC

- Can be driven with an external DAC through the TX\_INP input pin

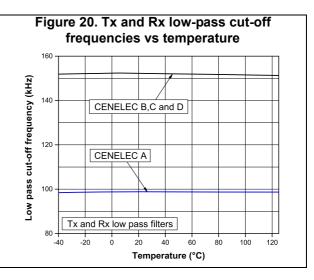

- Programmable unity-gain fourth-order low-pass filter, following CENELEC bands A, B, C, and D.

- PGA with gains of 6 dB, 0 dB, -18 dB, and -36 dB

- Receiver chain (Rx)

The Rx is characterized by the following features:

- PGA1 with gains of -3 dB, 3 dB, 9 dB, and 15 dB

- Sensitivity of 20 μVrms typical

- Can be connected in differential or single-input mode

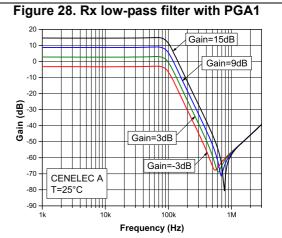

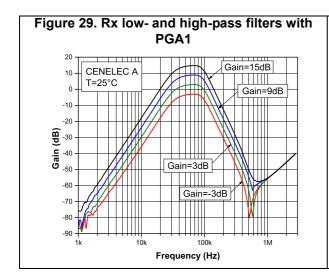

- Programmable unity-gain fourth-order low-pass filter, following CENELEC bands A, B, C, and D.

- Selectable high-pass filter with a 35 kHz cutoff frequency)

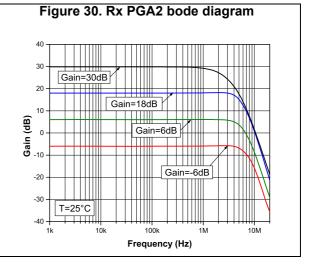

- PGA2 with gains of -6 dB, 6 dB, 18 dB, and 30 dB

The ST-PLC-AFE supports other circuitry blocks, such as:

- SPI interface for the microcontroller

- Thermal shutdown

- Two zero crossing detectors

General description ST-PLC-AFE

Figure 2. Functional block diagram

ST-PLC-AFE General description

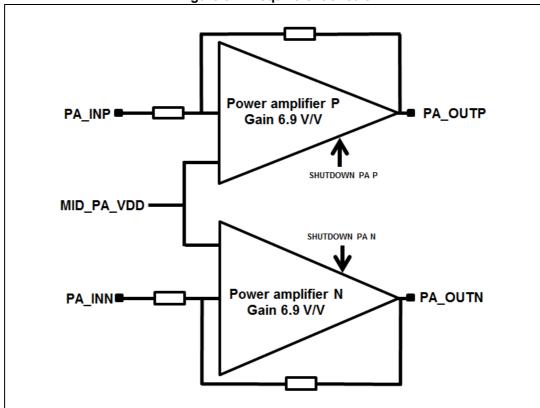

#### 2.1 PA block

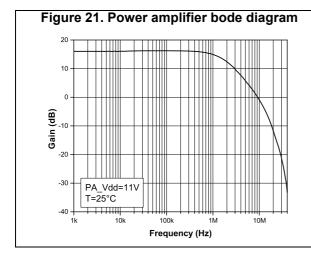

The PA block has a low-pass filter response when configured with a gain of 6.9 V/V. The PA is specified to operate from 7 V to 14 V and can deliver up to 1.65 A of continuous output current over the specified junction temperature range of -40 °C to 125 °C.

In differential mode, both PAs are turned on (see Figure 3).

In single-ended configuration, the N side of the PA is turned off and its output is placed into high impedance. This is achieved by setting the PA2\_EN bit in the Enable register to 0 (see *Figure 3*).

Figure 3. PA equivalent circuit

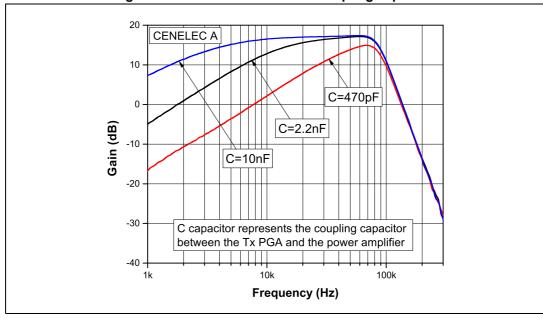

#### 2.1.1 Typical connections to the PA

Connecting the PA in a typical PLC application requires an input AC coupling capacitor, C\_IN\_PA (see *Figure 5* and *Figure 7*). This capacitor introduces a single-pole, high-pass characteristic to the PA transfer function; combined with the inherent low-pass transfer function, this characteristic results in a pass band response.

Figure 4 shows the impact of this coupling capacitor.

General description ST-PLC-AFE

Figure 4. Tx chain with different coupling capacitor

If using CENELEC band A, it is recommended to use a 2.2 nF capacitor. For CENELEC bands B, C, and D, a 1 nF can be used.

#### 2.1.2 Power amplifier power management

When the transmitter is not in use, the outputs can be disabled and placed into a high-impedance state. This is achieved by setting the PA\_EN bit in the Enable register to 0. A description of energy consumption following sub-block activation through the internal registers is given in Section 10.7: ST-PLC-AFE consumption (no load).

The PA integrates a current limiter that is programmable by an internal register thanks to the SPI communication. The current limit is set by the CL bits in the Gain register. Four limits are available: 0.5 A, 1 A, 1.5 A, and 2.1 A. See Section 9.3.1: Overcurrent condition for overcurrent protection.

10/58 DocID028727 Rev 1

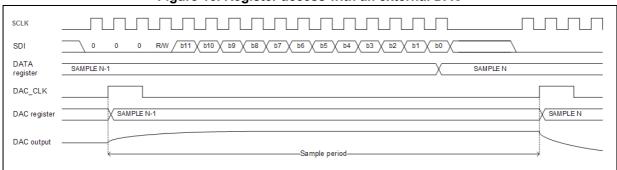

#### 2.2 Tx block

The Tx block is divided into an internal DAC, an internal fourth-order filter, a programmable amplifier, and a power liner driver. There are two ways to drive this transmission line:

- The internal DAC driving mode, achieved through the SPI interface and the internal 10-bit DAC.

- 2. Using an external driving mode where the signal received by the ST-PLC-AFE is purely analog, coming from an external MCU DAC. This signal is applied on the TX\_INP input pin.

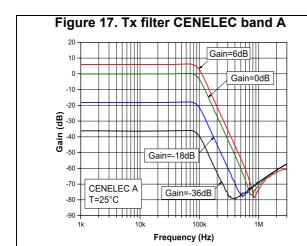

**Tx PGA** can be configured through the SPI to operate as an attenuator or to work in follower. The gain steps of the Tx PGA are 6 dB, 0 dB, -18 dB, and -36 dB. The gain can be programmed through the TX\_PGA1<1:0> bits in the Gain register.

The **Tx\_filter** is a unity-gain, fourth-order, low-pass filter. Its cutoff frequency is selectable between CENELEC A or CENELEC B, C, or D modes. The selection of the band is achieved through the BAND SEL bit in the Enable register.

#### 2.2.1 Internal DAC driving mode

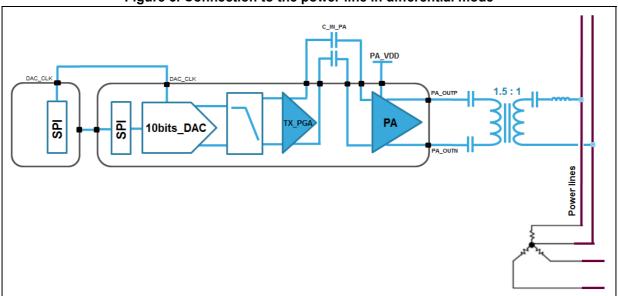

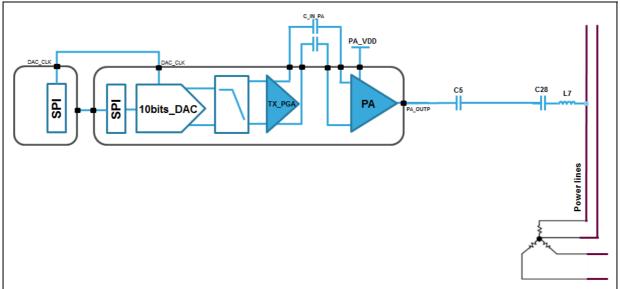

The ST-PLC-AFE accepts serial data from the microprocessor and writes the data to the internal DAC registers. Operating in DAC mode results in the lowest distortion signal injected onto the AC mains. DAC mode is selected by setting the DAC\_EN bit in the Enable register to 1. *Figure 5* and *Figure 6* show the connection to the power line while using the internal DAC in differential mode and in single-ended mode respectively.

Figure 5. Connection to the power line in differential mode

General description ST-PLC-AFE

Figure 6. Connection to the power line in single-ended mode

This mode requests an external clock generator from the MCU. See *Section 6* for the constraints related to this conduction mode.

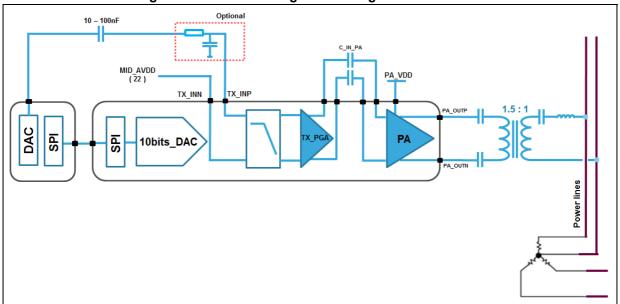

#### 2.2.2 External driving mode, differential-ended power amplifier mode

*Figure 7* shows the differential coupling with the power line. The input signal is driven with an external DAC.

When in external driving mode, the ST-PLC-AFE accepts being driven by analog through the TX\_INP input pin. In this case, TX\_INN has to be connected to the pin MID\_AVDD (pin 22). External drive mode is selected by setting the DAC EN bit in the Enable register to 0.

Figure 7. External driving mode using an external DAC

57

ST-PLC-AFE General description

Single to differential gain through the filter is equal to 1. If the single-ended input voltage amplitude is 1 Vpp, then the output voltage in differential mode is also equal to 1 Vpp. *Figure 8* shows the single-ended to differential gain conversion.

Figure 8. PGA filter connection

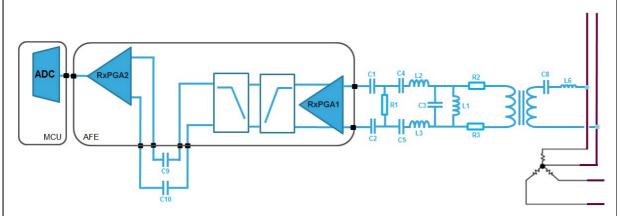

#### 2.3 Rx block

The Rx block consists of:

- Two programmable gain amplifiers (Rx PGA1 and Rx PGA2)

- A fourth-order, low-pass filter

- · A selectable high-pass filter

The input sensing mode can be differential mode for better noise immunity or single mode for the lowest BOM.

The **Rx PGA1** can be configured through the SPI to operate as either an attenuator or an amplifier. The gain steps of the Rx PGA1 are -3 dB, 3 dB, 9dB, and 15 dB. The gain can be programmed through the RX\_PGA1<1:0> bits in the Gain register. Configuring the Rx PGA1 as an attenuator (at gains less than 0 dB) is useful for applications where large interference signals are present within the signal band. Attenuating large interference allows these signals to pass through the analog Rx signal chain without causing an overload; the interference signal can then be processed and removed within the microprocessor as necessary. The gain steps of the **Rx PGA2** are -6 dB, 6 dB, 18 dB, and 30 dB. The gain can be programmed through the RX\_PGA2<1:0> bits in the Gain register.

The **Rx filter** is a very low-noise, unity-gain, fourth-order low-pass filter. Its cutoff frequency is selectable between CENELEC A or CENELEC B, C, or D bands. The selection of the band is achieved through the BAND\_SEL bit in the Enable register.

The 35 kHz **high-pass filter** is activated by the HP\_EN bit in the Enable register.

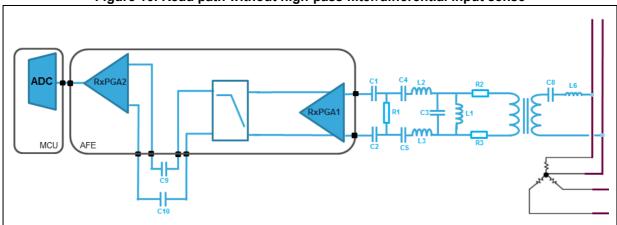

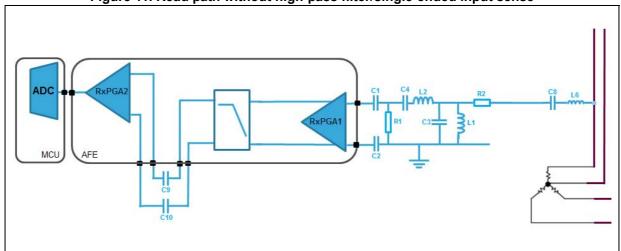

Recommended connections for the Rx signal chain are shown in *Figure 9*, *Figure 10*, and *Figure 11*.

**General description** ST-PLC-AFE

Figure 9. Read path with high-pass filter/differential input sense

Figure 10. Read path without high-pass filter/differential input sense

Figure 11. Read path without high-pass filter/single-ended input sense

5// 14/58 DocID028727 Rev 1

# 3 Absolute maximum ratings and operating conditions

Table 2. Absolute maximum ratings

| Symbol | Parameter                                              | Value | Unit |

|--------|--------------------------------------------------------|-------|------|

| PA_VDD |                                                        | 15    |      |

| AVDD   | Supply voltage                                         | 4.8   | V    |

| DVDD   |                                                        | 4.8   |      |

| TOP    | Operating temperature, TA <sup>(1)</sup> -40 to 150    |       | °C   |

| TSRT   | Storage temperature, TA -55 to 150                     |       | C    |

| Rthja  | Thermal resistance junction-to-ambient QFN48 power PAD | 30    | °C/W |

| Rthjc  | Thermal resistance junction-to-case QFN48 power PAD    | 4     | C/VV |

| HBM    | Human body model ESD                                   | 2000  |      |

| MM     | Machine model ESD                                      | 200   | V    |

| CDM    | Charged device model ESD                               | 500   |      |

<sup>1.</sup> The device automatically shuts down above 160°C

**Table 3. Operating conditions**

| Symbol | Parameter Value                          |            | Unit |

|--------|------------------------------------------|------------|------|

| PA_VDD | Power amplifier supply voltage           | 7 to 14    |      |

| DVDD   | Digital supply voltage                   | 3 to 3.6   | V    |

| AVDD   | Analog supply voltage                    | 3 to 3.6   |      |

| TOPER  | Operating free air temperature range (1) | -40 to 125 | °C   |

<sup>1.</sup> The device automatically shuts down above 160°C

## 4 Electrical characteristics

Unless otherwise specified, the test conditions are TJ = 25  $^{\circ}$ C, PA\_VDD = 11 V, AVDD = DVDD = 3.3 V.

Table 4. Power supply

|             |                                | Table 411 eller cappiy                                                       |      |      |      |      |  |  |  |

|-------------|--------------------------------|------------------------------------------------------------------------------|------|------|------|------|--|--|--|

| Symbol      | Parameter                      | Conditions                                                                   | Min. | Тур. | Max. | Unit |  |  |  |

| Current cor | Current consumptions           |                                                                              |      |      |      |      |  |  |  |

| IQPA_vs     | Power amplifier current        | lout = 0, PAs P and N on                                                     | 50   | 60   | 80   | mA   |  |  |  |

| IQDVDD      | Digital aupply aurrent         | Tx configuration (1)                                                         |      | 130  | 175  |      |  |  |  |

| IQUVUU      | Digital supply current         | Rx configuration (2)                                                         |      | 180  | 200  | μA   |  |  |  |

|             |                                | Tx configuration (1)                                                         | 2.6  | 2.9  | 3.5  | mA   |  |  |  |

|             | Analog supply                  | Rx configuration (2)                                                         | 2.5  | 2.8  | 3.1  | IIIA |  |  |  |

| IQAVDD      | current                        | Zero-cross detectors on, Rx<br>and Tx off, for both zero-<br>cross detectors |      | 60   |      | μΑ   |  |  |  |

| Power-dow   | n (EN = 0)                     |                                                                              |      |      |      |      |  |  |  |

| PA_VS       | Power amplifier supply voltage |                                                                              |      |      | 35   |      |  |  |  |

| DVDD        | Digital supply voltage         | EN pin is low                                                                |      |      | 150  | μΑ   |  |  |  |

| AVDD        | Analog supply voltage          |                                                                              |      |      | 50   |      |  |  |  |

| Temperatur  | е                              |                                                                              |      |      |      |      |  |  |  |

| Tj          | Junction temperature           |                                                                              | -40  |      | 125  | °C   |  |  |  |

<sup>1.</sup> In Tx configuration, the following blocks are enabled: DAC, Tx, and PA. All other blocks are disabled.

<sup>2.</sup> In Rx configuration, the Rx block is enabled. All other blocks are disabled.

Table 5. Power amplifier

| Symbol                  | Parameter                       | Conditions                                                                         | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------------------|------------------------------------------------------------------------------------|------|------|------|------|

| Frequency               | response                        |                                                                                    |      |      |      | ı    |

| D)4/ D4                 | D 1 110                         | RLOAD = 5 Ω                                                                        | 600  | 790  |      |      |

| BW_PA                   | Bandwidth                       | RLOAD = 50 Ω                                                                       | 1200 | 1600 |      | kHz  |

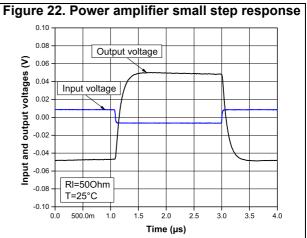

|                         |                                 | Single-ended mode, 2 V input step and 50 Ω load                                    | 20   | 27   |      |      |

| SR_PA                   | Slow rate                       | Single-ended mode, 2 V input step and 2 Ω load                                     |      | 10   |      | V/uo |

| SK_PA                   | Slew rate                       | Differential mode, 2 V input step and 100 Ω load                                   | 40   | 54   |      | V/µs |

|                         |                                 | Differential mode, 2 V input step and 4.5 Ω load                                   |      | 20   |      |      |

| FPBW_PA                 | Full-power<br>bandwidth         | Single-ended mode,<br>VPA_OUTP = 5 VPP, 50 Ω load<br>and 100 pF output capacitance |      | 1700 |      | kHz  |

| Output                  |                                 |                                                                                    |      |      | •    |      |

| V                       | Voltage output swing            | lo = 300 mA, sourcing                                                              |      | 0.2  | 0.6  |      |

| $V_{OH\_PA}$            | from PA_Vs                      | Io = 1.6 A, sourcing                                                               |      | 1.3  | 2    | V    |

| V.                      | Voltage output swing from PA_Vs | Io = 300 mA, sink                                                                  |      | 0.2  | 0.6  | ]    |

| V <sub>OL_PA</sub>      |                                 | Io = 1.6 A, sink                                                                   |      | 1.3  | 2    |      |

| I <sub>OUT_PA_DC</sub>  | Maximum DC output current       | CL0 = CL1 = 11                                                                     | 1.65 | 2.1  |      |      |

| I <sub>OUT_PA_AC</sub>  | Maximum peak current, AC        | TJ = -40 °C to 125°C,<br>f = 50 kHz                                                |      | 2.3  |      |      |

|                         |                                 | [CL1; CL0] = 00                                                                    | 0.3  | 0.5  |      | Α    |

|                         | DA ourrent limitation           | [CL1; CL0] = 10                                                                    | 0.75 | 1    |      |      |

| I <sub>LIM_PA</sub>     | PA current limitation           | [CL1; CL0] = 01                                                                    | 1.2  | 1.5  |      |      |

|                         |                                 | [CL1; CL0] = 11                                                                    | 1.65 | 2.1  |      |      |

| Z <sub>OUT_PA_off</sub> | Output impedance when PA off    | limII                                                                              | 100  | 150  |      | kΩ   |

| Ro                      | Output resistance               | Io = 1 A, f = 60 kHz                                                               |      | 0.2  |      | Ω    |

| Gain                    |                                 |                                                                                    |      |      |      |      |

| G                       | Nominal gain                    | RLOAD = 50 Ω                                                                       | 6.8  | 6.9  |      | V/V  |

| _                       | Gain error                      |                                                                                    | 3    | 0.1  | 3    | - %  |

| _                       | Gain drift                      | Tj = -40 °C to 125 °C                                                              | 0.5  |      | 0.5  | 70   |

| Input                   |                                 | <u> </u>                                                                           |      |      | •    | •    |

| Z <sub>IN_PA</sub>      | Input impedance                 |                                                                                    |      | 20   |      | kΩ   |

|                         | •                               |                                                                                    |      | •    | •    |      |

Table 5. Power amplifier (continued)

| Symbol            | Parameter                              | Conditions | Min. | Тур. | Max. | Unit |  |

|-------------------|----------------------------------------|------------|------|------|------|------|--|

| Thermal shu       | Thermal shutdown                       |            |      |      |      |      |  |

| T <sub>J_SD</sub> | Junction<br>temperature at<br>shutdown |            |      | 160  |      |      |  |

| T <sub>hyst</sub> | Hysteresis                             |            |      | 15   |      | °C   |  |

| _                 | Return to normal operation             |            |      | 145  |      |      |  |

**Table 6. Transmitter**

| Symbol                      | Parameter                  | Conditions                              | Min.      | Тур. | Max.         | Unit     |

|-----------------------------|----------------------------|-----------------------------------------|-----------|------|--------------|----------|

| Tx_DAC                      |                            |                                         |           |      |              |          |

| _                           | DAC resolution             |                                         |           | 10   |              | Bits     |

| INL                         | INL                        |                                         |           | 0.5  | ±1           | LCD      |

| DNL                         | DNL                        |                                         |           | 0.25 | ±0.5         | LSB      |

| f <sub>S_DAC</sub>          | Sampling frequency         |                                         |           | 1    | 1.6          | MHz      |

| SINAD                       | SINAD                      | Between 0 to 1.6 MHz sampling frequency | 47        | 55   |              | dB       |

| 1                           | DAC maximum output voltage | Differential output VAVDD = 3.3 V       | 2         | 2.1  |              | VPP      |

| Tx_filter (fo               | ourth-order, Butterw       | orth, low-pass filter) CENELEC A        |           |      |              |          |

| V <sub>IN_Tx</sub>          | Input voltage range        |                                         | GND - 0.1 |      | AVDD+<br>0.1 | <b>V</b> |

| Z <sub>IN_Tx</sub>          | Input impedance            |                                         |           | 65   |              | kΩ       |

| f <sub>C_Tx</sub>           | Cut-off frequency          |                                         | 95        | 100  | 105          | kHz      |

| ٨                           | Stop-band attenuation      | @ 400 kHz                               | 45        | 48   |              | dB       |

| A <sub>tt_Tx</sub>          |                            | @ 700 kHz                               |           | 75   |              | uВ       |

| Tx_filter (fo               | ourth-order, Butterw       | orth, low-pass filter) CENELEC B, C, a  | nd D      |      | _            |          |

| V <sub>IN_Tx</sub>          | Input voltage range        |                                         | GND - 0.1 |      | AVDD + 0.1   | V        |

| Z <sub>IN_Tx</sub>          | Input impedance            |                                         |           | 65   |              | kΩ       |

| f <sub>C_Tx</sub>           | Cut-off frequency          |                                         | 145       | 152  | 160          | kHz      |

| $A_{tt\_Tx}$                | Stop-band                  | @ 400 kHz                               | 30        | 33   |              | dB       |

| ' 'π_1x                     | attenuation                | @ 700 kHz                               |           | 59   |              | ub.      |

| Tx_PGA                      |                            |                                         |           |      | _            |          |

|                             | Gain                       | [TX_PGA1; TX_PGA0] = 00, 2V/V           |           | + 6  |              |          |

| G <sub>Tx_PGA</sub>         |                            | [TX_PGA1; TX_PGA0] = 01, 1 V/V          |           | 0    |              | dB       |

| 17_1 3/1                    |                            | [TX_PGA1; TX_PGA0] = 10, 1/8 V/V        |           | 18   |              |          |

|                             |                            | [TX_PGA1; TX_PGA0] = 11, 1/64 V/V       |           | 36   |              |          |

| I <sub>OUT_Tx_</sub><br>PGA | Output current             |                                         |           |      | 1            | mA       |

| Z <sub>OUT_Tx_</sub><br>PGA | Output impedance           |                                         |           | 1    |              | Ω        |

Table 6. Transmitter (continued)

| Symbol             | Parameter                    | Conditions                                                                               | Min.      | Тур.   | Max.       | Unit   |  |  |  |

|--------------------|------------------------------|------------------------------------------------------------------------------------------|-----------|--------|------------|--------|--|--|--|

| Global Tx c        | Global Tx chain              |                                                                                          |           |        |            |        |  |  |  |

| V <sub>in_Tx</sub> | Input voltage range          |                                                                                          | GND – 0.1 |        | AVDD + 0.1 | V      |  |  |  |

| t <sub>WK_Tx</sub> | Wake-up time                 | All blocks disabled to "ready to transmit"                                               |           |        | 100        | μs     |  |  |  |

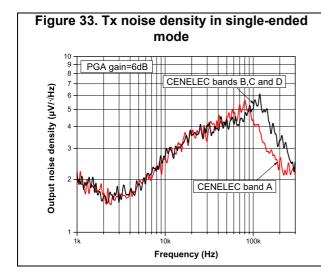

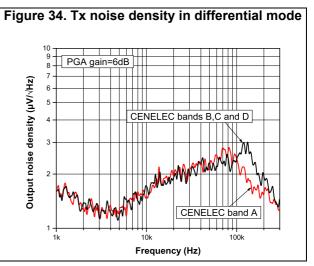

| Α -                | Differential noise           | V(PA_OUTP) – V(PA_OUTN),<br>CENELEC A,<br>Tx PGA gain = 6 dB/PA gain = 6.9 V/V           |           | 660    |            | u)/rmc |  |  |  |

| e <sub>n_Tx</sub>  | Differential noise           | V(PA_OUTP) – V(PA_OUTN),<br>CENELEC B, C, and D,<br>Tx PGA gain = 6 dB/PA gain = 6.9 V/V |           | 670    |            | μVrms  |  |  |  |

| _                  | Filter and PGA gain accuracy |                                                                                          |           | 0.5    | 4          | %      |  |  |  |

| Thermometer ladder |                              |                                                                                          |           |        |            |        |  |  |  |

| _                  |                              | Referenced to AVDD/2                                                                     |           | 4      |            | mV/°C  |  |  |  |

| _                  |                              | Output voltage @ temp = 25 °C                                                            |           | AVDD/2 |            | V      |  |  |  |

| _                  |                              | Precision                                                                                | -5        |        | 5          | °C     |  |  |  |

Table 7. Receiver

| Symbol                     | Parameter                          | Conditions                     | Min.      | Тур. | Max.          | Unit |

|----------------------------|------------------------------------|--------------------------------|-----------|------|---------------|------|

| Rx PGA1                    |                                    |                                |           |      |               |      |

| V <sub>IN_PGA1</sub>       | DC input level                     |                                | GND - 0.1 |      | AVDD<br>+ 0.1 | ٧    |

|                            |                                    | [PGA1_G1; PGA1_G0] = 00        |           | -3   |               |      |

| 0                          | Cain                               | [PGA1_G1; PGA1_G0] = 01        |           | 3    |               | ٩D   |

| G <sub>Rx_PGA1</sub>       | Gain                               | [PGA1_G1 ; PGA1_G0] = 10       |           | 9    |               | dB   |

|                            |                                    | [ PGA1_G1 ; PGA1_G0 ] = 11     |           | 15   |               |      |

| _                          | Gain accuracy                      |                                |           | 0.5  | 4             | %    |

|                            |                                    | [PGA1_G1; PGA1_G0] = 00        |           | 35   |               |      |

| 7                          | land income days                   | [PGA1_G1; PGA1_G0] = 01        |           | 25   |               | 1.0  |

| Z <sub>IN_Rx_PGA1</sub>    | Input impedance                    | [PGA1_G1; PGA1_G0] = 10        |           | 16   |               | kΩ   |

|                            |                                    | [PGA1_G1; PGA1_G0] = 11        |           | 9    |               |      |

|                            |                                    | G = -3 dB, 0.707 V/V           |           | 10   |               |      |

| D)44                       | 5                                  | G = 3 dB, 1.414 V/V            |           | 8    |               | MHz  |

| BW_ <sub>Rx_PGA1</sub>     | Bandwidth                          | G = 9 dB, 2.83 V/V             |           | 8    |               |      |

|                            |                                    | G = 15 dB, 5.66 V/V            |           | 4.5  |               |      |

| Rx filter                  |                                    |                                |           |      |               |      |

| V <sub>IN_Rx</sub>         | Input voltage range                |                                | GND - 0.1 |      | AVDD<br>+ 0.1 | ٧    |

| Rx, third-ord              | er, Butterworth, high-pa           | ass filter                     | <u> </u>  |      |               |      |

| f <sub>C_Rx_HPF</sub>      | Cut-off frequency                  |                                | 33        | 35   | 37            | kHz  |

| A <sub>tt_Rx_HPF</sub>     | Stop band attenuation              | @ 7 kHz                        | 37        | 40   |               | dB   |

| Rx_filter (fou             | rth-order, Butterworth,            | low-pass filter) CENELEC A     | -1        |      |               |      |

| I <sub>OUT_Rx_filter</sub> | Output maximum, continuous current | Sourcing, sinking              |           | 1    | 5             | mA   |

| f <sub>C_Rx_LPF</sub>      | Cut-off frequency                  |                                | 95        | 100  | 105           | kHz  |

| _                          | Otan bandattanation                | @ 400 kHz                      | 45        | 48   |               | -ID  |

| $A_{tt\_Rx\_LPF}$          | Stop-band attenuation              | @ 700 kHz                      |           | 68   |               | dB   |

| Rx_filter (fou             | rth-order, Butterworth,            | low-pass filter) CENELEC B, C, | and D     |      |               |      |

| I <sub>OUT_Rx_filter</sub> | Output maximum, continuous current | Sourcing, sinking              |           | 1    | 5             | mA   |

| f <sub>C_Rx_LPF</sub>      | Cut-off frequency                  |                                | 145       | 152  | 160           | kHz  |

| ۸                          | Stop-band attenuation              | @ 400 kHz                      | 30        | 33   |               | dB   |

| $A_{tt\_Rx\_LPF}$          | Stop-parid attenuation             | @ 700 kHz                      |           | 63   |               |      |

Table 7. Receiver (continued)

| Symbol                  | Parameter                                      | Conditions                                                                   | Min.      | Тур.  | Max.          | Unit                        |

|-------------------------|------------------------------------------------|------------------------------------------------------------------------------|-----------|-------|---------------|-----------------------------|

| Rx PGA2                 |                                                |                                                                              |           |       | 1             | •                           |

| V <sub>IN_Rx_PGA2</sub> | Input voltage range                            |                                                                              | GND - 0.1 |       | AVDD<br>+ 0.1 | V                           |

|                         |                                                | [PGA2_G1; PGA2_G0] = 00                                                      |           | - 6   |               |                             |

| 0                       | Gain                                           | [PGA2_G1; PGA2_G0] = 01                                                      |           | 6     |               | dB                          |

| G <sub>Rx_PGA2</sub>    | Gairi                                          | [PGA2_G1; PGA2_G0] = 10                                                      |           | 18    |               | uБ                          |

|                         |                                                | [PGA2_G1; PGA2_G0] = 11                                                      |           | 30    |               | %<br>— MHz<br>— kHz<br>— kΩ |

| _                       | Gain accuracy                                  |                                                                              |           | 0.5   | 4             | %                           |

| BW <sub>Rx_PGA2</sub>   |                                                | [PGA2_G1; PGA2_G0] = 00                                                      |           | 5     |               | MUz                         |

|                         | Eroguanay roonana                              | [PGA2_G1; PGA2_G0] = 01                                                      |           | 4     |               | IVITZ                       |

|                         | Frequency response                             | [PGA2_G1; PGA2_G0] = 10                                                      |           | 3     |               | l/∐-z                       |

|                         |                                                | [PGA2_G1; PGA2_G0] = 11                                                      |           | 1.5   |               | KI IZ                       |

|                         |                                                | [PGA2_G1; PGA2_G0] = 00                                                      |           | 45    |               |                             |

| 7                       | lanut inon o don o o                           | [PGA2_G1; PGA2_G0] = 01                                                      |           | 18 κΩ |               |                             |

| Z <sub>IN_Rx_PGA2</sub> | Input impedance                                | [PGA2_G1; PGA2_G0] = 10                                                      |           | 18    |               | KΩ                          |

|                         |                                                | [PGA2_G1; PGA2_G0] = 11                                                      |           | 10    |               |                             |

| Rx chain                |                                                |                                                                              |           |       |               |                             |

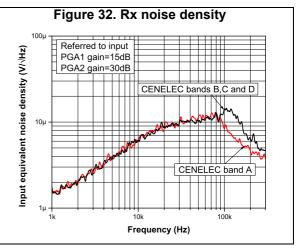

|                         | Integrated noise that                          | CENELEC Band A<br>μV <sub>RMS</sub> (40 kHz to 95 kHz)<br>Gain = 45 dB       |           | 8     |               | μV <sub>RMS</sub>           |

| e <sub>n_Rx</sub>       | includes whole Rx line (referred to the input) | CENELEC Bands B/C/D<br>μV <sub>RMS</sub> (95 kHz to 140 kHz)<br>Gain = 45 dB |           | 8     |               | μV <sub>RMS</sub>           |

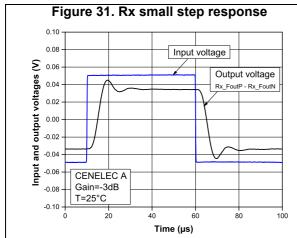

| t_startup               | Wake up time                                   | From all devices powered down to Rx ready for operations                     |           |       | 500           | ue                          |

| t_read_start<br>up      | Rx power-up time                               | Tx to Rx transition time, coupling capacitors of 3.3 nF                      |           | 10    |               | μs                          |

| Rx out                  |                                                |                                                                              |           |       |               |                             |

| V <sub>OUT_Rx</sub>     | Output voltage range                           | Vcc = 3.3 V, single ended output                                             | 0.1       |       | 3.2           | V                           |

| C <sub>OUT_Rx</sub>     | Output capacitance                             |                                                                              |           |       | 50            | pF                          |

| Z <sub>OUT_Rx</sub>     | Output impedance                               |                                                                              |           | 1     |               | Ω                           |

## Table 8. Digital domain

| Symbol                                           | Parameter Conditions      |                            | Min.            | Тур.             | Max.       | Unit |  |  |  |

|--------------------------------------------------|---------------------------|----------------------------|-----------------|------------------|------------|------|--|--|--|

| Digital inputs (nCS, EN, SCLK, DIN, and DAC_CLK) |                           |                            |                 |                  |            |      |  |  |  |

| V <sub>IH</sub>                                  | High-level input voltage  |                            | 0.25 x<br>VDVDD |                  |            | V    |  |  |  |

| V <sub>IL</sub>                                  | Low-level input voltage   |                            |                 | 0.75 x.<br>VDVDD |            | V    |  |  |  |

| Digital outpu                                    | uts (DOUT and INT)        |                            |                 |                  |            |      |  |  |  |

| V <sub>OH</sub>                                  | High-level output voltage | Source current, IOH = 2 mA | VDVDD –<br>0.45 |                  | VDVDD      | V    |  |  |  |

| V <sub>OL</sub>                                  | Low-level output voltage  | Sink current, IOL = - 2 mA | GND             |                  | GND + 0.45 | V    |  |  |  |

## Table 9. Zero crossing detector

| Symbol               | Parameter                          | Conditions   | Min.       | Тур. | Max.       | Unit     |

|----------------------|------------------------------------|--------------|------------|------|------------|----------|

| V <sub>IN_ZCR</sub>  | DC input,<br>ZC1_IN; ZC2_IN        |              | AGND – 0.3 |      | AVDD + 0.3 |          |

| V <sub>THR_ZCR</sub> | Rising threshold                   |              | 0.9        |      | 1          | V        |

| V <sub>THF_ZCR</sub> | Falling threshold                  |              | 0.45       |      | 0.55       |          |

| C <sub>IN_ZCR</sub>  | Input capacitance                  |              |            | 3    |            | pF       |

| V <sub>OH_ZCR</sub>  | High-level output ZC1_OUT; ZC2_OUT | IOL = 3 mA   | DVDD - 0.3 |      | DVDD       | <b>V</b> |

| V <sub>OL_ZCR</sub>  | Low-level output ZC1_OUT; ZC2_OUT  | IOH = - 3 mA | DGND       |      | DGND + 0.3 | V        |

Registers ST-PLC-AFE

# 5 Registers

Table 10. Main register table

| Register    | Address | Default | Function                                     |  |

|-------------|---------|---------|----------------------------------------------|--|

| Data        | 0x00h   | 000h    | Data register                                |  |

| Status/Flag | 0x01h   | 000h    | Status register                              |  |

| Gain        | 0x02h   | 003h    | Tx, Rx gain and current limitation selection |  |

| Enable      | 0x03h   | 12Ch    | Block enable or disable                      |  |

| ID          | 0x04h   | 069h    | Die name and revision                        |  |

Each register is 12 bits in width.

The registers are described in more detail in the tables below. Note in the column "Location", 0 = LSB and 11 = MSB.

Table 11. Data register

| Bit name | Location | Function        |

|----------|----------|-----------------|

| DATA0    | 0        | LSB of SPI DATA |

| DATA1    | 1        |                 |

| DATA2    | 2        |                 |

| DATA3    | 3        |                 |

| DATA4    | 4        | SPI DATA        |

| DATA5    | 5        | SFIDATA         |

| DATA6    | 6        |                 |

| DATA7    | 7        |                 |

| DATA8    | 8        |                 |

| DATA9    | 9        | MSB of SPI DATA |

ST-PLC-AFE Registers

Table 12. Status register

| Bit name | Location | Default | R/W | Function                                                                                                                                                                  |

|----------|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OVC_FLAG | 2        | 0       | R/W | Overcurrent condition Read 1: over current condition Read 0: no over current Write 0: reset the bit See Section 9.3: Interruptions for further information                |

| T_FLAG   | 1        | 0       | R/W | Thermal temperature shutdown Read 1: thermal shutdown activated Read 0: no thermal shutdown Write 0: reset the bit See Section 9.3: Interruptions for further information |

Table 13. Gain register

| Bit name     | Location | Default | R/W | Function                                                                                |

|--------------|----------|---------|-----|-----------------------------------------------------------------------------------------|

| RX_PGA2<1:0> | 7-6      | 00      | R/W | Select gain of Rx PGA2<br>00: - 6 dB<br>01: 6 dB<br>10: 18 dB<br>11: 30 dB              |

| RX_PGA1<1:0> | 5-4      | 00      | R/W | Select gain of Rx PGA1<br>00: -3 dB<br>01: 3 dB<br>10: 9 dB<br>11: 15 dB                |

| TX_PGA1<1:0> | 3-2      | 00      | R/W | Select gain of Tx PGA<br>00: + 6 dB<br>01: 0 dB<br>10: - 18 dB<br>11: - 36 dB           |

| CL<1:0>      | 1-0      | 00      | R/W | PA current limitation<br>00: 0.5 A typ<br>01: 1.5 A typ<br>10: 1 A typ<br>11: 2.1 A typ |

Registers ST-PLC-AFE

Table 14. Enable register

| Bit name | Location | Default | R/W | Function                                                                                                  |

|----------|----------|---------|-----|-----------------------------------------------------------------------------------------------------------|

| ZCR_EN   | 9        | 0       | R/W | Zero crossing detector enable<br>0: ZC1 and ZC2 off<br>1: ZC1 and ZC2 on                                  |

| BAND_SEL | 8        | 1       | R/W | Select CENELEC bandwidth 1: 100 kHz CENELEC band A 0: 150 kHz CENELEC band B, C, and D                    |

| PA_EN    | 7        | 0       | R/W | Enable power amplifier<br>0: PAs P and N off<br>1: PAs P and N on                                         |

| TX_EN    | 6        | 0       | R/W | Enable Tx channel<br>0: Tx off<br>1: Tx on                                                                |

| RX_EN    | 5        | 1       | R/W | Enable Rx channel<br>0: Rx off<br>1: Rx on                                                                |

| DAC_EN   | 4        | 0       | R/W | Enable internal DAC  0: DAC off and Tx path driven by external DAC  1: Tx path driven by the internal DAC |

| PA2_EN   | 3        | 1       | R/W | Enable power amplifier N<br>0: PA N side off<br>1: PA N side on                                           |

| HP_EN    | 2        | 1       | R/W | Enable high-pass filter<br>0: high-pass filter off<br>1: high-pass filter on                              |

| RST_SPI  | 1        | 0       | R/W | Reset all registers <sup>(1)</sup> 0: normal mode 1: reset all the registers to their default value       |

| PD_SPI   | 0        | 0       | R/W | Power-down all devices <sup>(2)</sup> 0: all devices on 1: all devices off                                |

<sup>1.</sup> The HP\_EN bit is self-resetting.

<sup>2.</sup> A reset cancels this command to its "0" default value.

ST-PLC-AFE Registers

## Table 15. ID register

| Bit name | Location | Default | R/W | Function  |

|----------|----------|---------|-----|-----------|

| ID       | 7-3      | 01101   | R   | ID number |

| REV      | 2-0      | 001     | R   | revision  |

SPI interfaces ST-PLC-AFE

#### 6 SPI interfaces

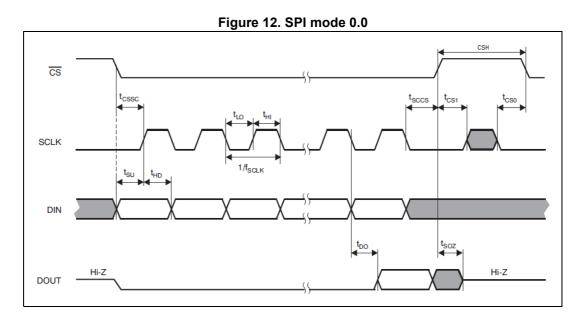

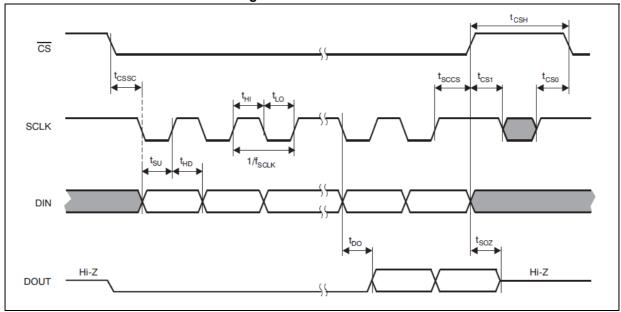

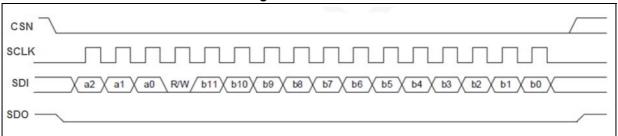

The ST-PLC-AFE interface supports SPI mode 0.0 and 1.1. A host SPI frame consists of a read/write bit, a 3-bit register address, and a 12-data bit register. Data are shifted out on the falling edge of the SCLK and latched on the rising edge of the SCLK. Refer to *Section 6.1: SPI timing* for a valid host and SPI communication protocol.

When nCS = 1, the state machine is reset asynchronously to the R/W state. The nCS does not need to go high between transfers but, it must be low during the entire transfer. Address bits identify target registers for writing data. There are three address bits which allow 8 x 12 bit registers, including the DAC register. Received data are stored in the target register on the  $16^{th}$  edge of the SCLK, if R/W is low.

## 6.1 SPI timing

28/58 DocID028727 Rev 1

ST-PLC-AFE SPI interfaces

Table 16. Timing table, DVDD from 3 V to 3.6 V, temperature between -40 °C to 125 °C, CLOAD on SDOUT =  $10~\rm pF$

| Symbol | Parameter                              | Condition      | Min | Тур | Max | Unit |

|--------|----------------------------------------|----------------|-----|-----|-----|------|

| _      | Input capacitance                      |                |     |     | 1   | pF   |

| tRFI   | Input rise/fall time                   | nCS, DIN, SCLK |     |     | 2   |      |

| tRFO   | Output rise/fall time                  | SDOUT          |     |     | 10  |      |

| tCSH   | nCS high time                          |                | 20  |     |     | ns   |

| tCSO   | SCLK edge to nCS fall setup time       |                | 10  |     |     |      |

| tCSSC  | nCS fall to first SCLK edge setup time |                | 10  |     |     |      |

| fSCLK  | SCLK frequency                         |                |     |     | 30  | MHz  |

| tHI    | SCLK high time                         |                | 12  |     |     |      |

| tLO    | SCLK low time                          |                | 12  |     |     |      |

| tSCCS  | SCLK last edge to nCS rise time        |                | 10  |     |     |      |

| tSU    | DIN setup time                         |                | 5   |     |     | ns   |

| tHD    | DIN hold time                          |                | 5   |     |     |      |

| tDO    | SCLK to DOUT valid propagation delay   |                |     |     | 12  |      |

| tSOZ   | nCS rise to DOUT forced to Hi-Z        |                |     |     | 20  |      |

Figure 13. SPI mode 1.1

SPI interfaces ST-PLC-AFE

## 6.2 Read/write figures in SPI mode 0.0

Figure 14. SPI write

Figure 15. SPI read

30/58 DocID028727 Rev 1

# 7 Powering the device and resetting the SPI and registers

## 7.1 Turning the device on and off

The ENABLE input pin (EN) allows the device to be turned on and off.

When EN is set to zero, all internal consumptions are reduced to a minimum, the SPI interface is ready to receive messages from the microcontroller, and all internal registers keep their value. Consequently, EN does not reset the IC. Using the SPI interface when the IC is powered down, allows the system to be preprogrammed.

When the EN pin is high (1), the ST-PLC-AFE device operates normally.

By default, the PD\_SPI bit is set to 0 (which means that all internal blocks of the device are activated). To turn off the device using the registers, the PD\_SPI must be set to 1. Then, all internal blocks are turned off. The SPI interface is still active for microcontroller communication and all registers keep their value without any resets.

## 7.2 Resetting the internal registers

The internal registers are reset by setting the RST\_SPI bit in the Enable register to 1. By doing this, all internal registers are set to their default values and the SPI interface performs an auto-reset.

When the analog power supply, AVDD, increases from zero to its final value, an internal power-on-reset (POR) occurs. All digital registers are reset when AVDD crosses the voltage window 1.6 V to 2.4 V.

## 7.3 Resetting the SPI

The SPI is reset using the high state of the input pin nCS.

#### 7.4 Use of an external DAC

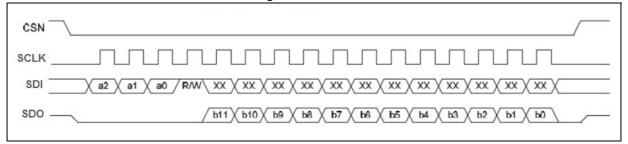

Figure 16. Register access with an external DAC

The Data register is used to update the DAC output. It is programmed directly by the SPI at address 000h. Data are transferred to the DAC at the rising edge of DAC\_CLK pin which triggers the start of a conversion.

The DAC\_CLK pin must be supplied with a stable, low-jitter, clock signal at the required sample frequency.

The SCLK and DAC\_CLK pins can be completely asynchronous, but SCLK must be more than 16 times the frequency of the DAC\_CLK pin to ensure that the Data register is updated with a new sample between each DAC\_CLK pulse.

32/58 DocID028727 Rev 1

# 8 Typical characteristics

Figure 18. Tx filter CENELEC band B, C, and D

20

10

Gain=6dB

Gain=6dB

Gain=0dB

Gain=-18dB

Gain=-18dB

Frequency (Hz)

Figure 19. Tx filter small step 0.10 0.08 Input voltage Output voltage Input and output voltages 0.04 Tx\_outP - Tx\_outN 0.02 -0.02 -0.04 CENELEC A Gain=6dB -0.08 T=25°C -0.10 100 Time (µs)

Figure 24. Power amplifier large step response

Output voltage

Input voltage

Input voltage

A RI=500hm

T=25°C

Output voltage

Input voltage

Input voltage

Input voltage

Input voltage

Input voltage

Input voltage

Figure 25. Power amplifier output impedance

**577**

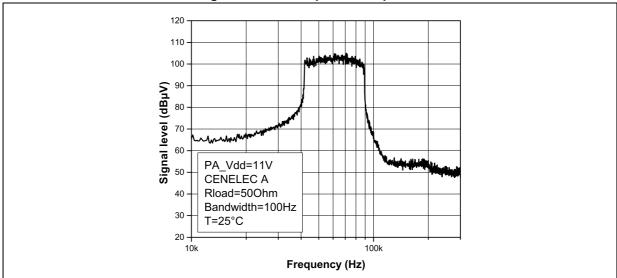

Figure 35. OFDM spectral response

# 9 System timings and interruptions

#### 9.1 Rx - Tx - Rx transitions

Figure 36. Transmission between read and write modes

### 9.2 Power-down to Rx

Figure 37. Transmission between off mode to read

The analog front end needs t\_startup to bias the external capacitors correctly. This period of time lasts 50 µs, but it can vary depending on external capacitors values.

### 9.3 Interruptions

The interrupt pin (INT) can be used to warn the microprocessor/DSP of unusual operating conditions. The INT pin can be triggered by two external circuit conditions, depending on the enable register settings. The ST-PLC-AFE can be programmed to issue an interrupt on current or thermal overload.

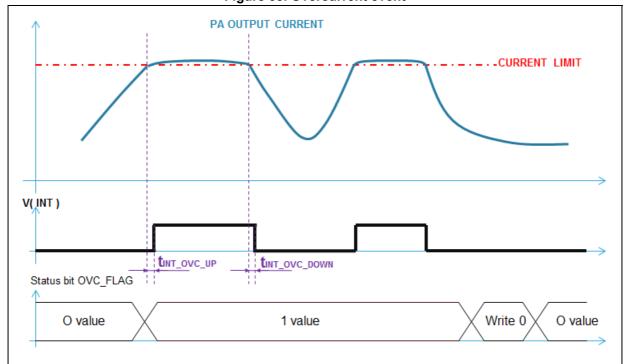

#### 9.3.1 Overcurrent condition

The maximum output current allowed from the PA can be programmed using the SPI communication system (CL<1:0> bit in the Gain register). If a FAULT condition occurs and causes an overcurrent, the PA goes into current limitation and the OVC\_FLAG bit (in the Status register) changes to 1.

The OVC\_FLAG bit remains set to 1 even after the device returns to normal operation. It can be reset when the microprocessor writes 0 inside the Status register. It can also be set back to 0 through a system reset using the RST\_SPI bit in the Enable register.

This configuration results in the presence of an interrupt signal at the INT pin. The INT signal returns to 0 when the device returns to normal operation. The latency time between the interrupt and the INT change of state  $t_{\text{INT}}$  OVC UP and  $t_{\text{INT}}$  OVC DOWN is 1  $\mu$ s.

Figure 38. Overcurrent event

38/58 DocID028727 Rev 1

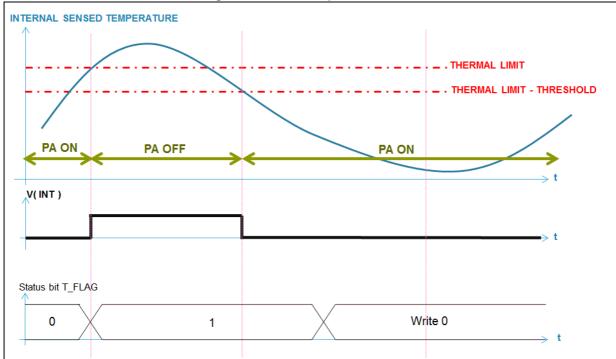

#### 9.3.2 Over temperature condition

The ST-PLC-AFE contains protective, internal circuitry that automatically disables the PA output stage if the junction temperature exceeds 160 °C. The device also includes a thermal hysteresis which allows the PA to resume normal operation when the junction temperature falls to 145 °C.

If a fault condition occurs that causes a thermal overload, the T\_FLAG bit switches from 0 to 1. This configuration results in an interrupt signal at the INT pin. The T\_FLAG bit remains set to 1 even after the device returns to normal operation. The T\_FLAG bit remains 1 until it is reset by the microprocessor (when 0 is written inside the T\_FLAG bit of the Status register). Another way to reset the T\_FLAG bit is to use the RST\_SPI system reset operation.

Figure 39. Over temperature event

#### 10 **Application information**

#### 10.1 Thermal sensor

2.5 Temperature sensor voltage (V) 2.0 1.5 1.0 Hysteresis 0.5 Thermal shutdown -20 20 40 60 80 100 Temperature (°C)

Figure 40. Thermal ladder characteristic

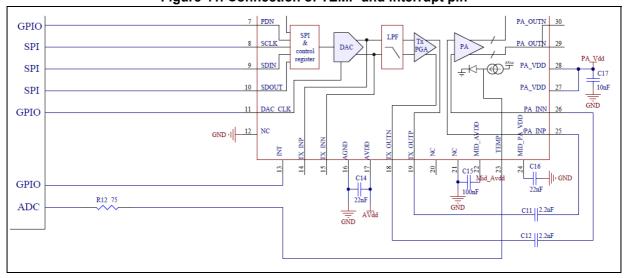

The THERMAL pin can be connected to a microcontroller GPIO pin which allows the internal temperature to be directly measured. The thermal sensor is physically placed close to the PAs to give the highest temperature indication inside the silicon.

Figure 41. Connection of TEMP and interrupt pin

#### 10.2 Thermal considerations

When the ST-PLC-AFE transmits information on low-impedance, power-line domains, more power is dissipated which leads to junction temperature increase. If the junction temperature reaches 160 °C, the thermal protection latches to freeze the transmission. This is why good PCB design and correct management of the heat flow from the ST-PLC-AFE is necessary to minimize losses and decrease system temperature, extend device operating life, and maximize performance.

### 10.2.1 Maximizing the heat flow from the junction temperature to the PCB

The package of the ST-PLC-AFE is a QFN48-pin with an exposed PAD. The majority of heat is evacuated through the exposed PAD, on the underside of the package, which is why the package must be soldered to the PCB thermal pad with the lowest resistivity possible. The thermal pad should be the same size as the exposed pad and multiple vias.

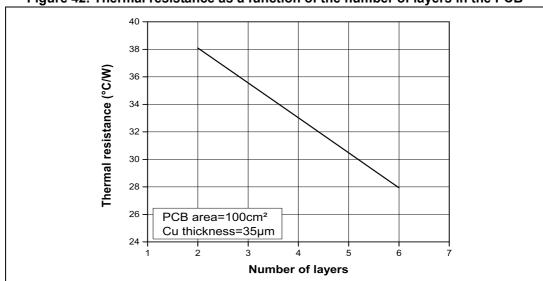

### 10.2.2 Reducing the PCB thermal resistance

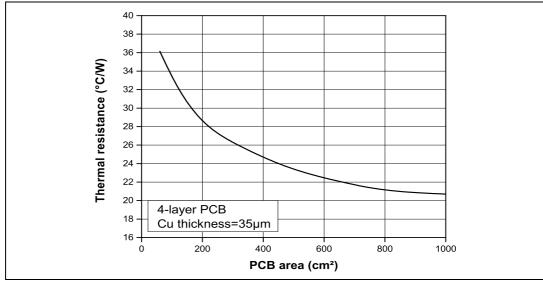

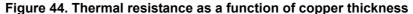

This can be done by increasing the number of layers, using thicker copper, and/or increasing the PCB area. The figures below show PCB examples of thermal resistance as a function of the number of PCB layers, PCB area, and copper thickness.

Figure 42. Thermal resistance as a function of the number of layers in the PCB

Figure 43. Thermal resistance as a function of PCB area

#### 10.2.3 Reducing supply voltage from the power amplifier

The system architecture has to take into account that power dissipated in transmission is strongly linked to the supply voltage level of the PA. For example, in differential mode with a 50 % Tx duty cycle, the power dissipated with 2  $\Omega$  load is 2.28 W when PA VDD = 11 V and 1.66 W when PA VDD = 8 V.

Note that this power corresponds to the current being drawn out of the PA power supply voltage multiplied by its supply voltage.

42/58 DocID028727 Rev 1

## 10.3 Moving from differential mode to single-ended mode

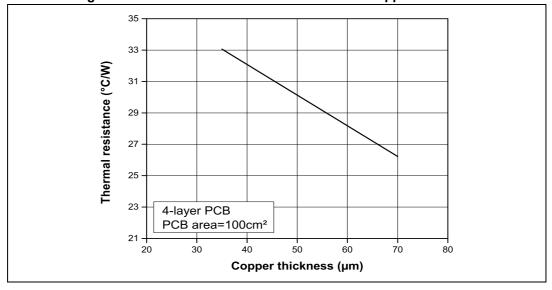

Differential mode can drive extremely low impedances, even at low supply voltage. However, differential mode also activates two PAs at the same time which increases the internal temperature (see *Figure 45*).

105 Differential mode With 1.5:1 transformer Temperature elevation (°C) 60 45 Single ended mode Vload=120dBµV Direct coupling Rload=20hm Ta=25°C 15 G3 OFDM frame Tx ratio=50% 12 Power supply voltage (V)

Figure 45. Temperature elevation in differential-ended and single-ended modes vs power supply voltage

To minimize the dissipated power and thus the temperature elevation, it is recommended to use the minimum power supply voltage.

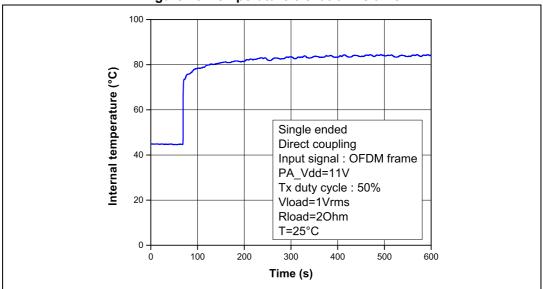

In *Figure 45*, the temperature elevation was monitored after a "waiting" time to achieve a stable temperature. Such "waiting" time and the temperature elevation depends on the number of PCB layers, copper thickness, PCB area, and PCB layout. *Figure 46* is an example of temperature elevation over time for the following board features:  $24 \text{ cm}^2$ , 4-layer PCB, and  $35 \mu m$  copper thickness.

Figure 46. Temperature elevation vs time

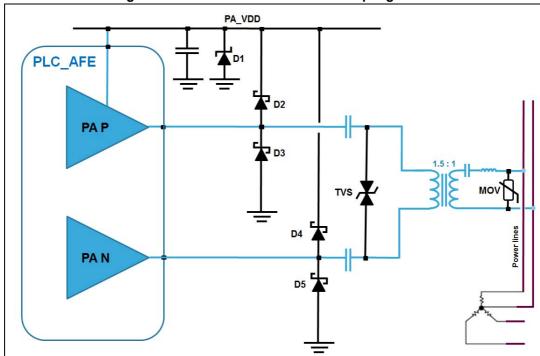

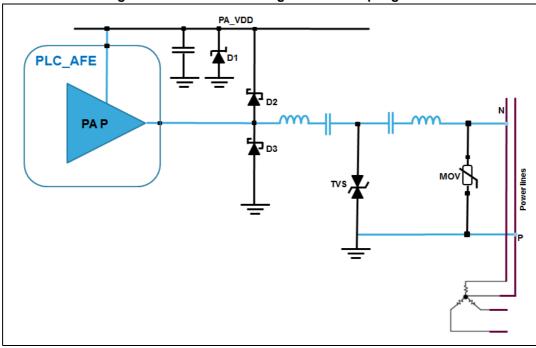

## 10.4 Circuit protection

Electrical perturbations may happen on the power lines, such as capacitor bank switching, inductive switching, lighting, and other grid fault conditions. Consequently, it is recommended to protect the ST-PLC-AFE in differential mode using the schematic shown in *Figure 47* and in single-ended, direct coupling mode using the schematic shown in *Figure 48*.

Figure 47. Protection in differential coupling mode

57

Figure 48. Protection in single-ended coupling mode

*Table 17* gives a list transient, protective devices which are recommended for use with the ST-PLC-AFE.

| rabio 111 Elot of rocommonaca, transland, protoctivo acvicco |                                |                    |             |  |

|--------------------------------------------------------------|--------------------------------|--------------------|-------------|--|

| Component                                                    | Description                    | Manufacturer       | P/N         |  |

| D1                                                           | Zener diode                    | _                  | _           |  |

| D2, D3, D4, D5                                               | Schottky diode                 |                    | STPS3L40S   |  |

| TVS, single-ended configuration                              | - Transient voltage suppressor | STMicroelectronics | SM6T6V8CA   |  |

| TVS, differential-<br>ended configuration                    | Transient voltage suppressor   |                    | SM6T12CA    |  |

| MOV                                                          | Metal oxyde varistor           | Bourns             | MOV-20D431K |  |

Table 17. List of recommended, transient, protective devices

In addition to external, protective circuits, the PAs integrate robust ESD diodes at their output which help to protect the ST-PLC-AFE against over-voltages (*Figure 48*).

Figure 49. ESD diode characteristics at the PA output

- 1. Diode high P: diode between  $PA_{DD}$  and positive PA output

- 2. Diode high N: diode between  $PA_V_{DD}$  and negative PA output

- 3. Diode low P: diode between GND and positive PA output

- 4. Diode low N: diode between GND and negative PA output

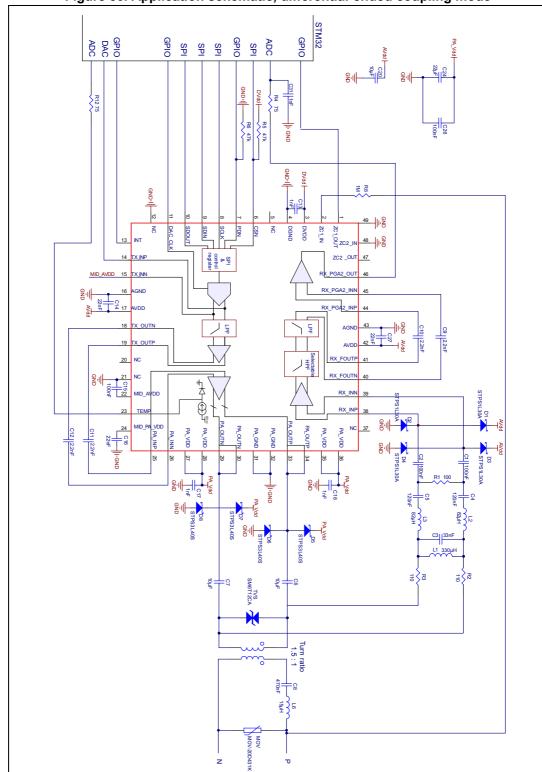

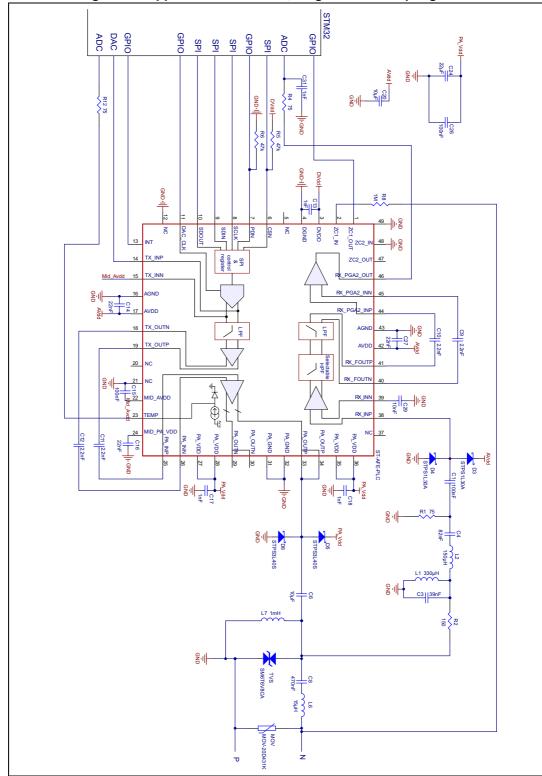

## 10.5 Application schematics

Figure 50. Application schematic, differential-ended coupling mode

Figure 51. Application schematic, single-ended coupling mode

**5**//

# 10.6 Bill of materials (BOM)

Table 18. BOM for differential-ended mode configuration

| Description                  | Designator         | Quantity | Value/PN   | Comment                            |

|------------------------------|--------------------|----------|------------|------------------------------------|

| AFE smart metering           | ST-AFE-PLCTR       | 1        | ST_PLC_AFE | QFN48 package                      |

|                              | C1, C2, C15, C26   | 4        | 100 nF     |                                    |

|                              | C3                 | 1        | 33 nF      |                                    |

|                              | C4, C5             | 2        | 120 nF     |                                    |

| Canacitar                    | C6, C7, C20        | 3        | 10 μF      |                                    |

| Capacitor                    | C9, C10, C11, C12  | 4        | 2.2 nF     |                                    |

|                              | C13, C17, C18, C31 | 4        | 1 nF       |                                    |

|                              | C14, C16, C27      | 3        | 22 nF      |                                    |

|                              | C24                | 1        | 22 µF      |                                    |

| Schottky diode               | D1, D2, D3, D4     | 4        | STPS1L30A  | STMicroelectronics,                |

| Scholiky diode               | D5, D6, D7, D8     | 4        | STPS3L40S  | SMA package                        |

|                              | L1                 | 1        | 330 µH     |                                    |

| Inductance                   | L2, L3             | 2        | 82 µH      |                                    |

| Transformer                  |                    | 1        |            | Turn ratio 1.5:1                   |

|                              | R1                 | 1        | 100        |                                    |

|                              | R2, R3             | 2        | 110        |                                    |

| Resistor                     | R4, R12            | 2        | 75         |                                    |

|                              | R5, R6             | 2        | 47 kΩ      |                                    |

|                              | R8                 | 1        | 1 ΜΩ       |                                    |

| Transient voltage suppressor | TVS                | 1        | SM6T12CA   | STMicroelectronics,<br>SMB package |

|                              |                    |          |            |                                    |

| Metal oxyde varistor         | MOV                | 1        |            |                                    |

| Capacitor                    | itor C8            |          | 470 nF     | Coupling to the main               |

| Inductance                   | L6                 | 1        | 15 µH      |                                    |

Table 19. BOM for single-ended mode configuration

| Description                  | Designator         | Quantity | Value/PN   | Comment                            |

|------------------------------|--------------------|----------|------------|------------------------------------|

| AFE smart metering           | ST-AFE-PLCTR       | 1        | ST_PLC_AFE | QFN48 package                      |

|                              | C1, C15, C26       | 3        | 100 nF     |                                    |

|                              | C3                 | 1        | 39 nF      |                                    |

|                              | C4                 | 1        | 82 nF      |                                    |

|                              | C6, C20            | 2        | 10 μF      |                                    |

| Capacitor                    | C9, C10, C11, C12  | 4        | 2.2 nF     |                                    |

|                              | C13, C17, C18, C31 | 4        | 1 nF       |                                    |

|                              | C14, C16, C27      | 3        | 22 nF      |                                    |

|                              | C24                | 1        | 22 µF      |                                    |

|                              | C29                | 1        | 10 nF      |                                    |

| Cobottly, diada              | D3, D4             | 2        | STPS1L30A  | STMicroelectronics,                |

| Schottky diode               | D5, D6             | 2        | STPS3L40S  | SMA package                        |

|                              | L1                 | 1        | 330µH      |                                    |

| Inductance                   | L2                 | 1        | 150 µH     |                                    |

|                              | L7                 | 1        | 1 mH       |                                    |

| Resistor                     | R1, R4, R12        | 3        | 75         |                                    |

|                              | R2                 | 1        | 150        |                                    |

|                              | R5, R6             | 2        | 47 kΩ      |                                    |

|                              | R8                 | 1        | 1 ΜΩ       |                                    |

| Transient voltage suppressor | TVS                | 1        | SM6T6V8CA  | STMicroelectronics,<br>SMB package |

| Metal oxyde varistor         | MOV                | 1        |            |                                    |

| Capacitor                    | C8                 | 1        | 470 nF     | Coupling to the main               |

| Inductance                   | L6                 | 1        | 15 µH      |                                    |

## 10.7 ST-PLC-AFE consumption (no load)

Register bits **AVDD DVDD** TX\_EN RX\_EN PA\_EN PA2\_EN DAC\_EN **HP\_filter EN** PA\_VDD 1 2.9 mA 60 mA 130 µA 1 1 2.1 mA 130 µA 60 mA 0 1 0 2.1 mA 130 µA 31 mA 1.8 mA 130 µA 23 µA 0 130 µA 0 2.8 mA 23 µA 0 1 0 1 3.4 mA 130 µA 23 µA 0 0 590 µA 130 µA 23 µA