# 36 V 3 A synchronous step-down converter in SOT23-6L

## **Features**

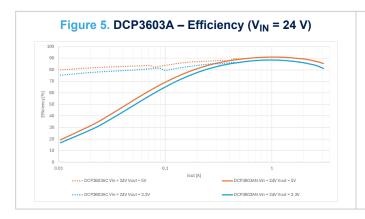

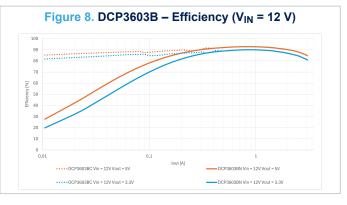

- 89% typical efficiency at 1000 mA load (V<sub>IN</sub> = 24 V, V<sub>OUT</sub> = 5 V)

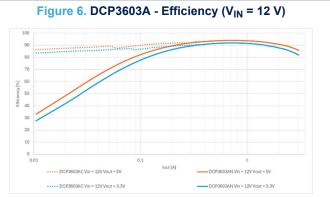

- 93% typical efficiency at 1000 mA load (V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 5 V)

- 3.3 V to 36 V input operating voltage range

- Up to 3 A output current capability

- 85 μA operating quiescent current

- 500 kHz or 1.0 MHz fixed switching frequency

- Synchronous rectification

- Internal compensation network

- Peak current mode control

- Two different versions: LCM for high efficiency at light loads and LNM for noise-sensitive applications

- Output overvoltage protection

- Thermal shutdown

- · Precision enable

- Switching frequency dithering

- Available in SOT23-6L package

# **Applications**

- Major appliances

- Smart metering

- Industrial 12/24 V bus conversion

## **Description**

The DCP3603 is a wide-input voltage, easy-to-use synchronous buck converter capable of driving up to 3 A load current.

The extended input range from 3.3 V to 36 V makes the device suitable for a wide range of industrial applications.

The DCP3603 operates at 500 kHz or 1.0 MHz fixed switching frequency allowing the use of small inductors for an optimized solution size.

Optional switching frequency dithering is implemented to improve EMI performances.

It is based on a peak current mode architecture, including soft-start circuit, overcurrent protection circuit, overtemperature protection and output overvoltage protection, and is packaged in a SOT23-6L package.

# Maturity status link

DCP3603

# 1 Application schematic

VIN VIN SW VEN O EN GND FB

Figure 1. DCP3603 typical application schematic

**Table 1. Typical external components**

| VOUT    | Switching frequency | L                          | CIN <sup>(1)</sup>  | COUT (1)                    | CBOOT (1)                                     | R1    | R2       |

|---------|---------------------|----------------------------|---------------------|-----------------------------|-----------------------------------------------|-------|----------|

|         |                     | 3.3 µH                     |                     | 22 μF / 25 V                | 100 nF / 50 V                                 |       |          |

| 5.0 V   | 1 MHz               | XGL5050-332<br>- Coilcraft |                     | C2012X5R1E226M125A<br>- TDK | -TDK<br>885012206095 - Wurth<br>100 nF / 50 V |       |          |

|         |                     | 744393305033<br>- Wurth    |                     | 885012107018 - Wurth        |                                               |       | 15<br>kΩ |

|         | 500 kHz             | 6.8 µH                     |                     | 2 x 22 µF / 25 V            |                                               |       |          |

|         |                     | XGL5050-682<br>- Coilcraft |                     | C2012X5R1E226M125A<br>- TDK |                                               |       |          |

|         |                     | 2.2 µH                     |                     | 22 μF / 25 V                |                                               |       |          |

| 3.3 V - | 1 MHz               | XGL5050-222<br>- Coilcraft | C2012X7R1H225K125AC | C2012X5R1E226M125A<br>- TDK | 100 nF / 50 V                                 | kΩ kΩ | 30       |

|         |                     | 5.6 µH                     | - TDK               | 2 x 22 µF / 25 V            | 04000\/754114041/00044                        |       | kΩ       |

|         | 500 kHz             | XGL5050-562<br>- Coilcraft |                     | C2012X5R1E226M125A<br>- TDK | C1608X7R1H104K080AA<br>-TDK                   |       |          |

<sup>1.</sup> Ceramic capacitor

DS15056 - Rev 1 page 2/26

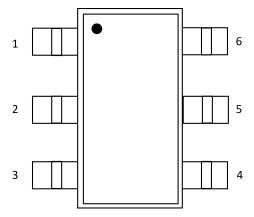

# 2 Pin connections

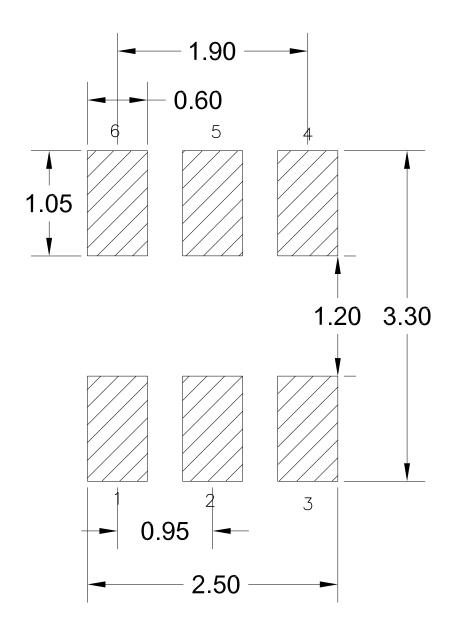

Figure 2. Pin configuration (top view)

Table 2. Pin description

| Name | Pin # | Description                                                                                                                                                                                                                                                                                                          |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| воот | 1     | <b>Bootstrap.</b> Connect a capacitor between SW and BOOT to form a floating supply across the high-side switch driver. A 100 nF low ESR ceramic capacitor is recommended.                                                                                                                                           |

| GND  | 2     | <b>System ground.</b> GND is the reference ground of the regulated output voltage. Therefore, care must be taken during PCB layout. Use wide PCB traces to make the connection.                                                                                                                                      |

| FB   | 3     | <b>Feedback.</b> An external resistor divider from the output to GND, tapped to FB, sets the output voltage. It is recommended to place the resistor divider as close as possible to the FB pin.                                                                                                                     |

| EN   | 4     | <b>Enable.</b> Precision enable pin. If the EN voltage is below 0.95 V, the converter is in shutdown mode with all functions disabled. (cannot be left floating).                                                                                                                                                    |

| VIN  | 5     | <b>Input voltage.</b> V <sub>IN</sub> supplies power for the internal MOSFET, regulator, and the embedded analog circuitry. Input capacitors are needed to decouple the input rail. Use wide PCB traces to make the connection.                                                                                      |

| SW   | 6     | $\label{eq:Switch output.} \textbf{Switch output.} \ \ \text{Connect SW to the inductor and bootstrap capacitor. SW is driven up to $V_{IN}$ by the high-side switch during the on-time of the PWM duty cycle. The inductor current drives SW low during the off-time. Use wide PCB traces to make the connection.}$ |

DS15056 - Rev 1 page 3/26

# 3 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol               | Parameter                       | Value                         | Unit |

|----------------------|---------------------------------|-------------------------------|------|

| $V_{IN}$             | Power supply voltage            | - 0.3 to + 38                 | V    |

| V <sub>EN</sub>      | Enable input voltage            | - 0.3 to V <sub>IN</sub> +0.3 | V    |

| $V_{FB}$             | Feedback pin voltage            | - 0.3 to + 1.5                | V    |

| V <sub>BOOT-SW</sub> | Boot to SW differential voltage | - 0.3 to + 5.5                | V    |

| SW                   | Switching node voltage DC       | - 0.3 to V <sub>IN</sub> +0.3 | V    |

| TJ                   | Operating junction temperature  | - 40 to 150                   | °C   |

| T <sub>STG</sub>     | Storage temperature             | - 55 to 150                   | °C   |

Note: Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not guaranteed.

Table 4. Thermal data

| Symbol                | Parameter                                    | SOT23-6L | Unit |

|-----------------------|----------------------------------------------|----------|------|

| R <sub>thJA</sub>     | Thermal resistance junction-ambient          | 117      |      |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 117      |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 32       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 13       |      |

| ΨЈВ                   | Junction-to-board characterization parameter | 32       |      |

Note: These values were calculated in accordance with JESD specification and simulated on a 4-layer JEDEC board.

Table 5. Recommended operating conditions

| Symbol           | Parameter                 | Min. | Тур. | Max.            | Unit |

|------------------|---------------------------|------|------|-----------------|------|

| V <sub>IN</sub>  | Input supply voltage      | 3.3  |      | 36              | V    |

| V <sub>EN</sub>  | Enable supply voltage (1) | 0    |      | V <sub>IN</sub> | V    |

| I <sub>OUT</sub> | Output current            | 0    |      | 3               | А    |

<sup>1.</sup> The voltage on this pin must not exceed the voltage on the  $V_{\text{IN}}$  pin by more than 0.3 V.

Table 6. ESD ratings

| Symbol           | Parameter                  | Value | Unit |

|------------------|----------------------------|-------|------|

| V <sub>ESD</sub> | Human body model (HBM)     | ±2000 | V    |

|                  | Charged device model (CDM) | ±500  | V    |

DS15056 - Rev 1 page 4/26

# 4 Electrical characteristics

$T_J$  = 25 °C,  $V_{\mbox{\footnotesize{IN}}}$  = 24 V, unless otherwise specified.

**Table 7. Electrical characteristics**

| Symbol                | Parameter                                                  | Test conditions                                             | Min   | Тур   | Max   | Unit |

|-----------------------|------------------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|------|

| V <sub>FB</sub>       | Feedback voltage                                           |                                                             | 0.833 | 0.850 | 0.867 | ٧    |

| la la                 | Quiocont gurrent                                           | $V_{EN}$ = 3.3 V, $V_{FB}$ = 0.9 (no switching), LCM device |       | 85    | 120   | μA   |

| IQ                    | Quiescent current                                          | $V_{EN}$ = 3.3 V, $V_{FB}$ = 0.9 (no switching), LNM device |       | 1.4   |       | mA   |

| I <sub>SD</sub>       | Shutdown current                                           | V <sub>EN</sub> = 0 V                                       |       | 4.5   | 8     | μA   |

| I <sub>SKIP</sub>     | Skip current limit                                         |                                                             |       | 0.8   |       | Α    |

| I <sub>VY_SINK</sub>  | Reverse current limit                                      | LNM or V <sub>OUT</sub> overvoltage                         | 1.2   | 1.5   | 1.75  | Α    |

| V <sub>UVLO</sub>     | Lindon soltage legicust throughold                         | V <sub>IN</sub> rising                                      | 2.85  |       | 3.2   | ٧    |

| VUVLO                 | Undervoltage lockout threshold                             | V <sub>IN</sub> falling                                     | 2.6   |       | 2.9   | V    |

| .,                    | Cushis three-hald                                          | V <sub>EN</sub> rising                                      | 1.1   | 1.23  | 1.35  | V    |

| V <sub>EN</sub>       | Enable threshold                                           | V <sub>EN</sub> falling                                     | 0.95  | 1.1   | 1.22  | V    |

|                       | Enghla innut la alcana aumant                              | V <sub>EN</sub> = 3.3 V                                     |       | 10    | 100   | nA   |

| I <sub>LKG_EN</sub>   | Enable input leakage current                               | $V_{IN} = V_{EN} = 36 \text{ V}$                            |       | 20    |       |      |

| I <sub>LKG_FB</sub>   | Feedback input leakage current                             | V <sub>FB</sub> = 1.2 V                                     |       | 0.2   |       | nA   |

| R <sub>DS_ON_HS</sub> | High-side MOSFET on-resistance                             | I <sub>SW</sub> = 0.1 A                                     |       | 0.14  | 0.21  |      |

| R <sub>DS_ON_LS</sub> | Low-side MOSFET on-resistance                              | I <sub>SW</sub> = 0.1 A                                     |       | 0.08  | 0.14  | Ω    |

| I <sub>LIM_HS</sub>   | High-side MOSFET switch current limit                      | V <sub>IN</sub> = 24 V                                      | 4.0   | 5.1   | 6.3   | А    |

| I <sub>LIM_LS</sub>   | Low-side MOSFET switch current limit                       | V <sub>IN</sub> = 24 V                                      | 3.2   | 3.8   | 4.5   | Α    |

| t <sub>ON_MIN</sub>   | Minimum switch-on time                                     | on SW pin                                                   |       | 90    |       | ns   |

| t <sub>OFF_MIN</sub>  | Minimum switch-off time                                    | on SW pin                                                   |       | 135   |       | ns   |

| t <sub>SS</sub>       | Internal soft-start time                                   |                                                             |       | 1.3   |       | ms   |

| F <sub>SW</sub>       | Switshing fraguency                                        | DCP3603Ax                                                   | 400   | 500   | 600   | kHz  |

| ' SW                  | Switching frequency                                        | DCP3603Bx                                                   | 0.8   | 1.0   | 1.2   | MHz  |

| T <sub>SD</sub>       | Thermal shutdown threshold                                 |                                                             |       | 175   |       | °C   |

| T <sub>SD_REC</sub>   | Thermal recovery threshold                                 |                                                             |       | 155   |       | °C   |

| V <sub>OVP</sub>      | Overvoltage threshold (V <sub>OVP</sub> /V <sub>FB</sub> ) |                                                             |       | 120   |       | %    |

| V <sub>OVP_HYST</sub> | Overvoltage hysteresis                                     |                                                             |       | 8     |       | %    |

DS15056 - Rev 1 page 5/26

# 5 Block diagram

VIN Reference UVLO Internal EN 🗀 Regulator ф воот OVP\_th Control FB 🖒 🗋 sw Comp Logic SS 0.85V GND ่ LIM\_LS\_COMP Thermal Shutdown CLK Soft-Start Oscillator

Figure 3. Simplified block diagram

DS15056 - Rev 1 page 6/26

# 6 Functional description

The DCP3603 device is based on a "peak current mode" architecture with constant frequency control. Therefore, the intersection between the error amplifier output and the sensed inductor current generates the PWM control signal to drive the power switch.

The device features LNM (low noise mode) that is forced PWM control, or LCM (low consumption mode) to increase the efficiency at light load, depending on the selected part number.

The main internal blocks shown in the block diagram are:

- · Embedded power elements

- A fully integrated sawtooth oscillator with ramp for slope compensation, avoiding subharmonic instability

- The transconductance error amplifier with integrated compensation network

- The high-side current sense amplifier to sense the inductor current

- A "pulse width modulator" (PWM) comparator and the driving circuitry of the embedded power elements

- The soft-start blocks to ramp the error amplifier reference voltage and reduce the inrush current at powerup. The EN pin inhibits the device when driven low

- The EN pin switches the device on and off

- The current limitation circuit to implement constant current protection, sensing pulse-by-pulse the highside / low-side switch current

- A circuit to implement the thermal protection function

- Dithering

- The OVP circuitry to discharge the output capacitor in case of an overvoltage event

#### 6.1 EN

The EN pin controls the ON/OFF operation of the buck converter. If the voltage is less than 0.95 V, it shuts down the device, while a voltage of greater than 1.36 V is required to start the converter.

The EN pin is an input and cannot be left open or floating. The simplest way to enable the operation of the DCP3603 is to connect the EN to  $V_{IN}$ . This allows self-startup when  $V_{IN}$  is within the operating range.

#### 6.2 Soft-start

The soft-start (SS) limits the inrush current surge and makes the output voltage increase monotonically. The device implements the soft-start phase ramping the internal reference with very small steps. Once the SS ends, the error amplifier reference is switched to the internal value of 0.85 V coming directly from the bandgap cell.

During normal operation, a new soft-start cycle takes place in case of:

- 1. Thermal shutdown event

- 2. UVLO event

- 3. EN pin rising over the V<sub>EN</sub> threshold.

## 6.3 Light-load operation

The DCP3603 implements two different light-load strategies:

- 1. Low consumption mode (LCM)

- 2. Low noise mode (LNM)

Refer to Table 9 to select the part number with the preferred light-load strategy.

DS15056 - Rev 1 page 7/26

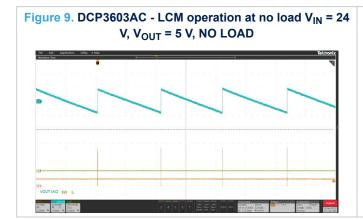

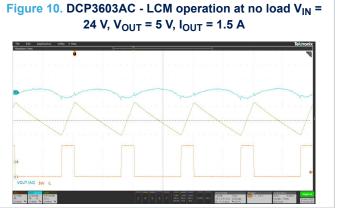

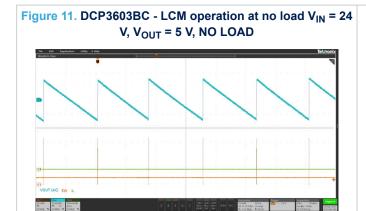

#### 6.3.1 Low consumption mode (LCM)

The Low Consumption Mode (LCM) is an advanced feature that enhances efficiency under light-load conditions.

When the switch peak current request is lower than the  $I_{SKIP}$  threshold (see Table 7), the device regulates  $V_{OUT}$  by the Skip threshold, generating pulses at a variable frequency that is inversely proportional to the load. The duty cycle of the pulses may remain relatively constant, but the interval between pulses increases as the load decreases.

The device interrupts the switching activities when two conditions occur simultaneously:

- The peak inductor current required is lower than I<sub>SKIP</sub>.

- The voltage on the FB pin is higher than the internal reference voltage.

A new switching cycle takes place once the voltage on the FB pins becomes lower than the internal reference voltage. The HS switch is kept on until the inductor current reaches  $I_{SKIP}$ . The amount of inductor peak current is defined by the required conversion and components selection.

Once the current on the HS reaches the defined value, the device turns the HS off and turns the LS on. The LS is kept enabled until one of the following conditions is met:

- 1. The inductor current sensed by the LS becomes equal to zero

- The switching period has expired

If, at the end of the switching cycle, the voltage on the FB pin is still above the reference voltage, the LS

remains enabled until the inductor current becomes equal to zero. Otherwise, the device turns on the HS

again and starts a new switching pulse.

During the burst pulse, if the energy transferred to  $C_{OUT}$  increases the  $V_{FB}$  level above the threshold defined in Eq. (1), the device interrupts the switching activities. The new cycle takes place only when  $V_{FB}$  becomes lower than the defined threshold. Otherwise, as soon as the LS is turned off, the HS is turned on. Given the energy stored in the inductor during a burst, the voltage ripple depends on the capacitor value:

$$V_{OUT\_RIPPLE} = \frac{\Delta Q_{IL}}{C_{OUT}} = \frac{\int_0^T BURST(I_L(t))dt}{C_{OUT}}$$

(1)

In case of a very light-load condition in LCM, the device can enter into sleep mode with minimized input current absorption.

#### 6.3.2 Low noise mode (LNM)

Low noise mode implements a forced PWM operation over different loading conditions. The LNM features a constant switching frequency to minimize the noise in the final application and a constant voltage ripple at fixed  $V_{\rm IN}$ .

The regulator, in steady loading condition, operates in continuous conduction mode (CCM) over the different loading conditions.

The triangular-shaped current ripple (with zero average value) flowing into the output capacitor generates the output voltage ripple, which depends on the capacitor value and the equivalent resistive component (ESR). Consequently, the output capacitor must be selected to ensure that the voltage ripple is compliant with the application requirements.

$$V_{OUT\,RIPPLE} = ESR \cdot \Delta I_{LMAX} + \frac{\Delta I_{LMAX}}{8 \cdot C_{OUT} \cdot f_{SW}} \tag{2}$$

Usually, the resistive component of the ripple can be neglected if the selected output capacitor is a multilayer ceramic capacitor (MLCC).

DS15056 - Rev 1 page 8/26

## 6.4 Dithering

The internal dithering circuit changes the switching frequency in a range of ± 50 kHz.

$$\Delta F_{SW} = 50 \, kHz \tag{3}$$

The device updates the frequency every clock period by fixed steps:

- Ramps up in 63 steps from minimum to maximum F<sub>SW</sub>

- Ramps down in 63 steps from maximum to minimum F<sub>SW</sub>

The modulation shape is almost triangular with a frequency of:

$$F_{Dithering} = F_{SW}/126 \tag{4}$$

## 6.5 Duty cycle range

Minimum ON-time ( $t_{ON\_MIN}$ ) is the shortest duration of time that the high-side switch can be turned on.  $t_{ON\_MIN}$  is typically 90 ns.

Minimum OFF-time ( $t_{OFF\_MIN}$ ) is the shortest duration of time that the high-side switch can be off.  $t_{OFF\_MIN}$  is typically 135 ns. In CCM operation,  $t_{ON\_MIN}$  and  $t_{OFF\_MIN}$  limit the voltage conversion range without switching frequency foldback.

The minimum duty cycle without frequency foldback allowed is:

$$D_{MIN} = t_{ON \ min} \cdot F_{SW} \tag{5}$$

The maximum duty cycle without frequency foldback allowed is:

$$D_{MAX} = 1 - (t_{OFF \ min} \cdot F_{SW}) \tag{6}$$

Given a required output voltage, the maximum V<sub>IN</sub> can be found by:

$$V_{IN\ MAX} = V_{OUT}/t_{ON\ min} \cdot F_{SW} \tag{7}$$

### 6.6 Overcurrent protection

The current protection circuitry features a constant current protection, so the device limits the maximum peak current (please refer to Table 7) in overcurrent condition.

The DCP3603 device implements a pulse-by-pulse current sensing on both power elements (high-side and low-side switches) for effective current protection over the duty cycle range. The high-side current sensing is called "peak", while the low-side sensing is called "valley".

The internal noise generated during the switching activity makes the current sensing circuitry ineffective for a minimum conduction time of the power element. This time is called "masking time" because the information from the analog circuitry is masked by the logic to prevent erroneous detection of an overcurrent event. Therefore, the peak current protection is disabled for a masking time after the high-side switch is turned on. The masking time for the valley sensing is activated after the low-side switch is turned on. In other words, the peak current protection can be ineffective at extremely low duty cycles, while the valley current protection can be ineffective at extremely high duty cycles.

The DCP3603 device assures an effective overcurrent protection sensing the current flowing in both power elements. If one of the two current sensing circuits is ineffective because of masking time, the device is protected by sensing the current on the opposite switch. Thus, the combination of the "peak" and "valley" current limits assures the effectiveness of the overcurrent protection even in extreme duty cycle conditions.

If the current diverges because of the high-side masking time, the low-side power element is turned on until the switch current level drops below the valley current sense threshold. The low-side operation is able to prevent the high-side turn-on, so the device can skip pulses, decreasing the switching frequency.

DS15056 - Rev 1 page 9/26

### 6.7 Overvoltage protection

The overvoltage protection monitors the FB pin and enables the low-side MOSFET to discharge the output capacitor if the output voltage exceeds 20% above the nominal value.

This is a second-level protection and should never be triggered in normal operating conditions if the system is properly dimensioned. In other words, the selection of the external power components and the dynamic performance determined by the compensation network should guarantee output voltage regulation within the overvoltage threshold, even under worst-case load transition conditions.

The protection is reliable and able to operate even during normal load transitions in a system whose dynamic performance is not in line with the load dynamic request. Consequently, the output voltage regulation would be affected.

The DCP3603 device implements a negative current limitation (I<sub>VY\_SINK</sub>, refer to Table 7) to limit the maximum reversed switch current during overvoltage operation.

### 6.8 Thermal shutdown

The shutdown block disables the switching activity if the junction temperature is higher than a fixed internal threshold (TSH refer to Table 7). The thermal sensing element is close to the power elements, ensuring fast and accurate temperature detection. A hysteresis of approximately 20 °C prevents the device from turning ON and OFF too fast. After a thermal protection event is expired, the DCP3603 restarts with a new soft-start.

DS15056 - Rev 1 page 10/26

# 7 Application information

The DCP3603 is a buck DC-to-DC converter. It is typically used to convert a higher input voltage to a lower output DC voltage with a maximum output current of 3 A. The following design procedure can be used to select components for the DCP3603.

## 7.1 Typical application

The device only requires a few external components to convert from a wide voltage range supply to a fixed output voltage. The figure below shows a basic schematic.

VIN BOOT VOUT

VIN SW

VEN O

EN FB

GND

R<sub>1</sub>

R<sub>2</sub>

R<sub>2</sub>

Figure 4. DCP3603 application schematic

# 7.2 Output voltage setting

The error amplifier reference voltage is typically 0.85 V (refer to Table 7). The output voltage is adjusted accordingly with the following equation:

$$V_{OUT} = V_{FB} \cdot \left(1 + \frac{R_1}{R_2}\right) \tag{8}$$

## 7.3 Input capacitor selection

The input capacitor voltage rating must be higher than the maximum input operating voltage of the application. During the switching activity, a pulsed current flows into the input capacitor; therefore, its RMS current capability must be selected according to the application conditions. Internal losses of the input filter depend on the ESR value, thus low ESR capacitors (such as multilayer ceramic capacitors) usually have a higher RMS current capability. On the other hand, given the RMS current value, a lower ESR input filter has lower losses and thus contributes to higher conversion efficiency.

The maximum RMS input current, flowing through the capacitor, can be calculated as follows:

$$I_{RMS} = I_{OUT} \cdot \sqrt{\left(\left(1 - \frac{D}{\eta}\right)\frac{D}{\eta}\right)} \tag{9}$$

Where  $I_{OUT}$  is the maximum DC output current, D is the duty cycle, and  $\eta$  is the efficiency. This function has a maximum at D = 0.5 and, considering  $\eta$  = 1, it is equal to  $I_{OUT}/2$ . In a specific application, the range of possible duty cycles has to be considered to determine the maximum RMS input current. The maximum and minimum duty cycles can be calculated as:

$$D_{MAX} = \frac{V_{OUT} + \Delta V_{LOW\_side}}{V_{IN\_min} + \Delta V_{LOW\_side} - \Delta V_{HIGH\_side}}$$

(10)

$$D_{MIN} = \frac{V_{OUT} + \Delta V_{LOW\_side}}{V_{IN\_max} + \Delta V_{LOW\_side} - \Delta V_{HIGH\_side}}$$

(11)

DS15056 - Rev 1 page 11/26

Where  $\Delta V_{HIGHSIDE}$  and  $\Delta V_{LOWSIDE}$  are the voltage drops across the embedded switches. The peak-to-peak voltage across the input filter can be calculated as the equation below:

$$V_{PP} = \frac{I_{OUT}}{C_{IN} \cdot F_{SW}} \cdot \left(1 - \frac{D}{\eta}\right) \frac{D}{\eta} + ESR \cdot \left(I_{OUT} + \Delta I_L\right)$$

(12)

In case of negligible ESR (MLCC capacitor), the equation of  $C_{IN}$  as a function of the target  $V_{PP}$  can be written as follows:

$$C_{IN} = \frac{I_{OUT}}{(V_{PP} \cdot F_{SW})} \cdot \left(1 - \frac{D}{\eta}\right) \frac{D}{\eta} \tag{13}$$

Considering  $\eta = 1$ , this function has its maximum at D = 0.5:

$$C_{IN\_min} = \frac{I_{OUT}}{\left(4 \cdot V_{PP\_max} \cdot F_{SW}\right)} \tag{14}$$

Typically,  $C_{IN}$  is dimensioned to keep the maximum peak-to-peak voltage across the input filter within the order of  $5\% V_{INMAX}$ .

### 7.4 Inductor selection

The inductor current ripple flowing into the output capacitor determines the output voltage ripple. The inductor value is usually selected to keep the current ripple lower than 20% - 40% of the output current over the input voltage range. The inductance value can be calculated by the following equation:

$$\Delta I_L = \frac{V_{IN} - V_{OUT}}{L} \cdot t_{ON} = \frac{V_{OUT}}{L} \cdot t_{OFF}$$

(15)

Where  $T_{ON}$  and  $T_{OFF}$  are the on- and off-time of the internal power switch. The maximum current ripple at fixed  $V_{OUT}$  is obtained at maximum  $T_{OFF}$ , which is at minimum duty cycle. So fixing  $\Delta I_L = 20\%$  to 40% of the maximum output current, the minimum inductance value can be calculated:

$$L_{min} = \frac{V_{OUT}}{\Delta I_{L \ max}} \cdot \frac{1 - D_{min}}{F_{SW}} \tag{16}$$

The peak current through the inductor is given by:

$$I_{L\_peak} = I_{OUT} + \frac{\Delta I_L}{2} \tag{17}$$

So if the inductor value decreases, the peak current (that has to be lower than the current limit of the device) increases. The higher the inductor value, the higher the average output current that can be delivered, without reaching the current limit.

DS15056 - Rev 1 page 12/26

## 7.5 Output capacitor selection

The triangular-shaped current ripple (with zero average value) flowing into the output capacitor generates the output voltage ripple, which depends on the capacitor value and the equivalent resistive component (ESR). Therefore, the output capacitor has to be selected to ensure that the voltage ripple is compliant with the application requirements.

The voltage ripple equation can be calculated as:

$$\Delta V_{OUT} = ESR \cdot \Delta I_{L\_max} + \frac{\Delta I_{L\_max}}{(8 \cdot C_{OUT} \cdot F_{SW})}$$

(18)

For a ceramic (MLCC) capacitor, the capacitive component of the ripple dominates the resistive one. For an electrolytic capacitor, the opposite is true. Neglecting the ESR contribution, the minimum value of the output capacitor is given by:

$$C_{OUT\_min\_RIPPLE} = \frac{\Delta I_{L\_max}}{(8 \cdot \Delta V_{OUT} \cdot F_{SW})}$$

(19)

As the compensation network is internal, the output capacitor should be selected to provide a proper phase margin and ensure a stable control loop.

## 7.6 Board layout guidelines

The DC-DC converter area is very sensitive, and it is necessary to pay attention to the layout of this part. The DC-DC converter generates GND noise that can get coupled on the surrounding ground, reducing the sensitivity, and high-frequency components can be coupled onto the RF part. Therefore, to ensure a correct layout, it is necessary to:

- · Provide efficient filtering by placing capacitors as close as possible

- Reduce parasitic, ensuring wide and short connections.

A two-layer or a four-layer board is strongly recommended. Put the ground layer very close to the top layer to obtain a good ground plane reference. A minimum copper thickness for each layer of 0.07 mm (2 oz) is suggested.

Put a ground plane internally to reduce the coupling between the traces. If it is not possible to use a four-layer board, it is necessary to fill the area under the phase node of the board with ground metal to reduce or eliminate radiation emissions.

#### **Ground plane**

Any switch-mode power supply requires a good PCB layout to achieve the maximum performance.

Component placement, GND trace routing and width, are the major issues. Basic rules commonly used for DC-DC converters for good PCB layout should be followed. All traces carrying current should be drawn on the PCB as short and as thick as possible. This should be done to minimize resistive and inductive parasitic effects and to increase system efficiency.

Connect all the ground metallization and/or layers with as many vias as possible. Ground vias between layers should be added liberally throughout the RF portion of the PCB. This helps prevent the accrual of parasitic ground inductance due to ground-current return paths. The vias also help to prevent cross-coupling from the RF and other signal lines across the PCB.

#### **Capacitor placing**

Particular care has to be taken in the placement of the supply voltage filtering capacitors. It is, in fact, important to ensure efficient filtering by placing these capacitors as close as possible to their dedicated pins.

The layout of decoupling capacitors is extremely important to minimize the induction loop formed between the capacitor and the IC power and ground. The vias should be placed on the side of the capacitor lands, not the ends. The vias should be located at the minimum keep-out distance and connected to the capacitor lands with a wide trace - at least as wide as the via pad. Vias of opposite polarity should be placed as close together as possible (minimum keep-out distance), and vias of the same polarity should be kept separated as much as possible. If space allows, a second pair of vias on the opposite side of the capacitor may be added to reduce the inductance further.

#### Inductor placing

The DC-DC converter inductor has to be placed as close as possible, with traces as short and as thick as possible. This should be done to minimize resistive parasitic effects and increase system efficiency.

DS15056 - Rev 1 page 13/26

#### Feedback resistor placing

It is important to place the resistor divider close to the FB pin to reduce noise sensitivity of the output voltage feedback path. Route the V<sub>OUT</sub> sense path away from noisy nodes and preferably through a layer on the opposite side of a shielded layer.

#### Thermal aspects

The device power dissipation inside the IC is mainly due to the DC-DC integrated MOSFET power loss. The heat generated by this power dissipation level requires a suitable heat sink to keep the junction temperature below the overtemperature protection threshold (Thermal shutdown) at the rated ambient temperature. Try, where possible, to increase the number of power planes connected to improve the heat dissipation.

However, different layouts are also possible. Basic principles suggest keeping the IC in the middle of the dissipating area; providing as many vias as possible; designing a dissipating area with a square shape; and avoiding interruption of this area by other copper traces.

DS15056 - Rev 1 page 14/26

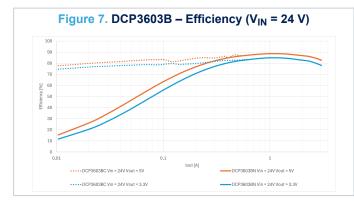

# Typical performance characteristics

DS15056 - Rev 1 page 15/26

Figure 12. DCP3603BC - LCM operation at no load V<sub>IN</sub> = 24 V, V<sub>OUT</sub> = 5 V, I<sub>OUT</sub> = 1.5 A

DS15056 - Rev 1 page 16/26

# 9 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

# 9.1 SOT23-6L package information

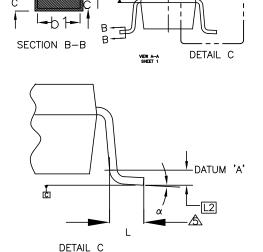

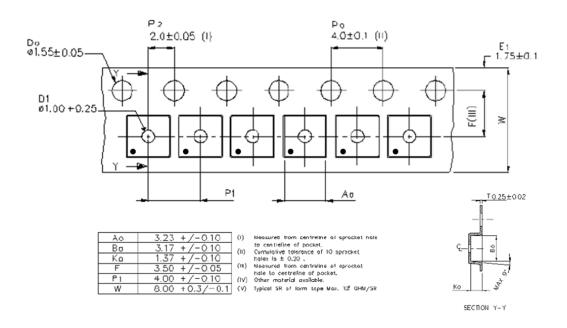

Figure 15. SOT23-6L package outline

DS15056 - Rev 1 page 17/26

Table 8. SOT23-6L mechanical data

| Dimensions |      |             |      |  |  |  |

|------------|------|-------------|------|--|--|--|

| Complete   |      | Millimeters |      |  |  |  |

| Symbol     | Min. | Тур.        | Max. |  |  |  |

| A          | 0.90 |             | 1.25 |  |  |  |

| A1         | 0.0  |             | 0.10 |  |  |  |

| A2         | 0.9  |             | 1.30 |  |  |  |

| b          | 0.30 |             | 0.50 |  |  |  |

| b1         | 0.30 |             | 0.45 |  |  |  |

| С          | 0.14 |             | 0.20 |  |  |  |

| c1         | 0.14 | 0.15        | 0.16 |  |  |  |

| D          |      | 2.90 BSC    |      |  |  |  |

| E          |      | 2.80 BSC    |      |  |  |  |

| E1         |      | 1.60 BSC    |      |  |  |  |

| е          |      | 0.95 BSC    |      |  |  |  |

| e1         |      | 1.90 BSC    |      |  |  |  |

| L          | 0.30 |             | 0.55 |  |  |  |

| L2         |      | 0.25        |      |  |  |  |

| N          |      | 5           |      |  |  |  |

| α          | 0°   |             | 8°   |  |  |  |

| Symbol     |      | Tolerance   |      |  |  |  |

| aaa        |      | 0.15        |      |  |  |  |

| bbb        |      | 0.20        |      |  |  |  |

| ccc        |      | 0.10        |      |  |  |  |

| ddd        |      | 0.20        |      |  |  |  |

| eee        |      | 0.08        |      |  |  |  |

DS15056 - Rev 1 page 18/26

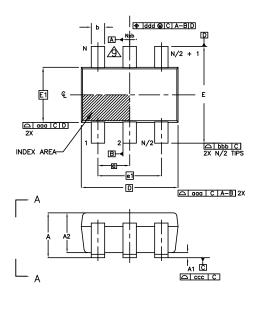

Figure 16. SOT23-6L recommended footprint

# FOOTPRINT SUGGESTED

PLANT CODE: 9992 SOT 23 6 LEADS

DS15056 - Rev 1 page 19/26

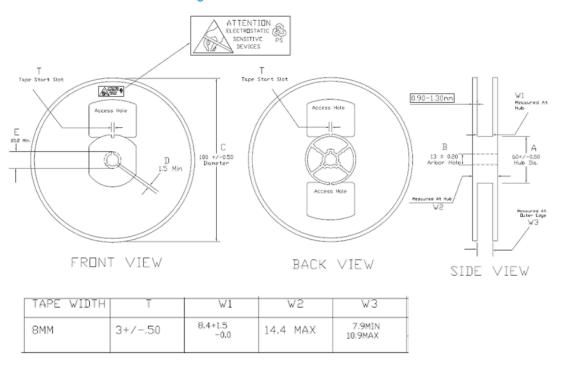

# 9.2 SOT23-6L package information

Figure 17. SOT23-6L carrier tape outline

Figure 18. SOT23-6L reel outline

DS15056 - Rev 1 page 20/26

# 10 Ordering information

Table 9. Ordering information

| Order codes  | Marking | Switching frequency | Dithering | Light load behavior        | Package  | Packing       |

|--------------|---------|---------------------|-----------|----------------------------|----------|---------------|

| DCP3603ACMR  | 03AC    | 500 kHz             | OFF       |                            |          |               |

| DCP3603BCMR  | 03BC    | 1.0 MHz             |           | LCM (Low consumption mode) |          |               |

| DCP3603ACDMR | 3ACD    | 500 kHz             | ON        |                            |          |               |

| DCP3603BCDMR | 3BCD    | 1.0 MHz             |           |                            | SOT23-6L | Tape and reel |

| DCP3603ANMR  | 03AN    | 500 kHz             | OFF       | LNM (Low noise mode)       | 30123-0L | Tape and Teel |

| DCP3603BNMR  | 03BN    | 1.0 MHz             |           |                            |          |               |

| DCP3603ANDMR | 3ACD    | 500 kHz             | ON        |                            |          |               |

| DCP3603BNDMR | 3BCD    | 1.0 MHz             | ON        |                            |          |               |

DS15056 - Rev 1 page 21/26

# **Revision history**

Table 10. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 12-Nov-2025 | 1        | Initial release. |

DS15056 - Rev 1 page 22/26

# **Contents**

| 1   | App    | Application schematic             |    |  |  |  |  |  |

|-----|--------|-----------------------------------|----|--|--|--|--|--|

| 2   | Pin    | connections                       |    |  |  |  |  |  |

| 3   | Max    | ximum ratings                     |    |  |  |  |  |  |

| 4   |        | ctrical characteristics           |    |  |  |  |  |  |

| 5   | Bloc   | ock diagram                       |    |  |  |  |  |  |

| 6   |        | nctional description              |    |  |  |  |  |  |

|     | 6.1    | EN                                |    |  |  |  |  |  |

|     | 6.2    | Soft-start                        |    |  |  |  |  |  |

|     | 6.3    | Light-load operation              |    |  |  |  |  |  |

|     |        | 6.3.1 Low consumption mode (LCM)  |    |  |  |  |  |  |

|     |        | <b>6.3.2</b> Low noise mode (LNM) |    |  |  |  |  |  |

|     | 6.4    | Dithering                         |    |  |  |  |  |  |

|     | 6.5    | Duty cycle range                  |    |  |  |  |  |  |

|     | 6.6    | Overcurrent protection            |    |  |  |  |  |  |

|     | 6.7    | Overvoltage protection            |    |  |  |  |  |  |

|     | 6.8    | Thermal shutdown                  |    |  |  |  |  |  |

| 7   | Арр    | plication information             |    |  |  |  |  |  |

|     | 7.1    | Typical application               |    |  |  |  |  |  |

|     | 7.2    | Output voltage setting            |    |  |  |  |  |  |

|     | 7.3    | Input capacitor selection         |    |  |  |  |  |  |

|     | 7.4    | Inductor selection                |    |  |  |  |  |  |

|     | 7.5    | Output capacitor selection        |    |  |  |  |  |  |

|     | 7.6    | Board layout guidelines           |    |  |  |  |  |  |

| 8   | Турі   | pical performance characteristics |    |  |  |  |  |  |

| 9   | Pac    | ckage information                 |    |  |  |  |  |  |

|     | 9.1    | SOT23-6L package information      |    |  |  |  |  |  |

|     | 9.2    | SOT23-6L package information      | 20 |  |  |  |  |  |

| 10  | Ord    | dering information                |    |  |  |  |  |  |

| Rev | /ision | n history                         | 22 |  |  |  |  |  |

# **List of tables**

| Table 1.  | Typical external components      |   |

|-----------|----------------------------------|---|

| Table 2.  | Pin description                  | j |

| Table 3.  | Absolute maximum ratings         | , |

| Table 4.  | Thermal data4                    |   |

| Table 5.  | Recommended operating conditions |   |

| Table 6.  | ESD ratings                      |   |

| Table 7.  | Electrical characteristics       | i |

| Table 8.  | SOT23-6L mechanical data         | , |

| Table 9.  | Ordering information             |   |

| Table 10. | Document revision history        |   |

# **List of figures**

| Figure 1.  | DCP3603 typical application schematic                                                                         | . 2 |

|------------|---------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin configuration (top view)                                                                                  | . 3 |

| Figure 3.  | Simplified block diagram                                                                                      | . 6 |

| Figure 4.  | DCP3603 application schematic                                                                                 | 11  |

| Figure 5.  | DCP3603A – Efficiency (V <sub>IN</sub> = 24 V)                                                                | 15  |

| Figure 6.  | DCP3603A - Efficiency (V <sub>IN</sub> = 12 V)                                                                | 15  |

| Figure 7.  | DCP3603B – Efficiency (V <sub>IN</sub> = 24 V)                                                                | 15  |

| Figure 8.  | DCP3603B – Efficiency (V <sub>IN</sub> = 12 V)                                                                | 15  |

| Figure 9.  | DCP3603AC - LCM operation at no load V <sub>IN</sub> = 24 V, V <sub>OUT</sub> = 5 V, NO LOAD                  | 15  |

| Figure 10. | DCP3603AC - LCM operation at no load V <sub>IN</sub> = 24 V, V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 1.5 A | 15  |

| Figure 11. | DCP3603BC - LCM operation at no load V <sub>IN</sub> = 24 V, V <sub>OUT</sub> = 5 V, NO LOAD                  | 16  |

| Figure 12. | DCP3603BC - LCM operation at no load V <sub>IN</sub> = 24 V, V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 1.5 A | 16  |

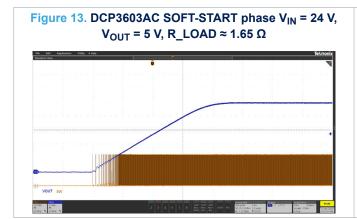

| Figure 13. | DCP3603AC SOFT-START phase $V_{IN}$ = 24 V, $V_{OUT}$ = 5 V, $R_LOAD \approx 1.65 \Omega$                     | 16  |

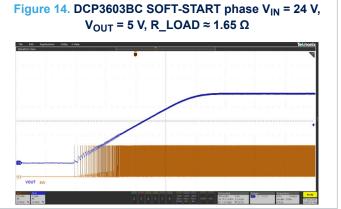

| Figure 14. | DCP3603BC SOFT-START phase $V_{IN}$ = 24 V, $V_{OUT}$ = 5 V, $R_LOAD \approx 1.65 \Omega$                     | 16  |

| Figure 15. | SOT23-6L package outline                                                                                      | 17  |

| Figure 16. | SOT23-6L recommended footprint                                                                                | 19  |

| Figure 17. | SOT23-6L carrier tape outline                                                                                 | 20  |

| Figure 18. | SOT23-6L reel outline                                                                                         | 20  |

DS15056 - Rev 1 page 25/26

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics - All rights reserved

DS15056 - Rev 1 page 26/26