## Automotive SPI to isolated SPI transceiver

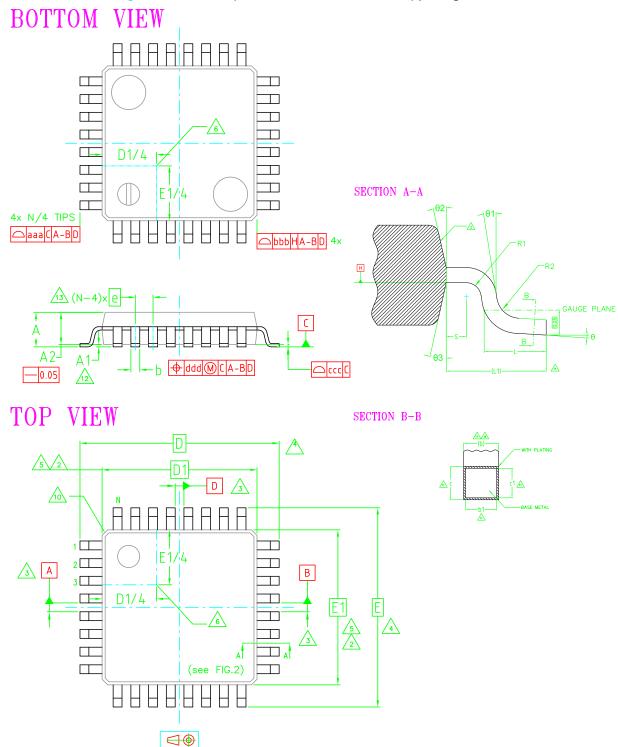

LQFP32L 7x7x1.4 mm

#### **Product status link**

L9965T, L9965TS

| Product summary |                    |               |  |  |  |

|-----------------|--------------------|---------------|--|--|--|

| Order code      | de Package Packing |               |  |  |  |

| L9965T-TR       | LQFP32L            | Tape and reel |  |  |  |

| L9965TS-TR      | LQFF32L            | rape and reer |  |  |  |

#### **Features**

- AEC-Q100 qualified

- Temperature grade 1: -40°C to +125°C operating temperature range

- HBM ESD classification level 2

- CDM ESD classification level C4B

- Full ISO26262 compliant, ASIL-D systems ready, documentation available

- Automatic wake-up of BMS/BMU MCU and PMIC from SHUTDOWN/SLEEP in case of fault detected in the chain

- Single or dual channel p/n in the same package for ring connection

- · Supports up to 59 devices in chain

- Cable lengths verified up to 10 meters

- 10 MHz 4-wire SPI interface

- 4 Mbps 2-wire vertical interface (VIF)

- · Supports both transformer and capacitive isolation

- Compressed burst data read for enhanced communication speed over the whole chain

- Broadcast write command to configure and control all devices in the chain (or a subset)

- Very low EMI susceptibility and emissions

- Compatible with 3.3 V and 5 V logics

- Supply voltage from 6 V to 24 V

## **Application**

- Automotive battery monitoring systems

- · Energy storage systems

- UPS

## **Description**

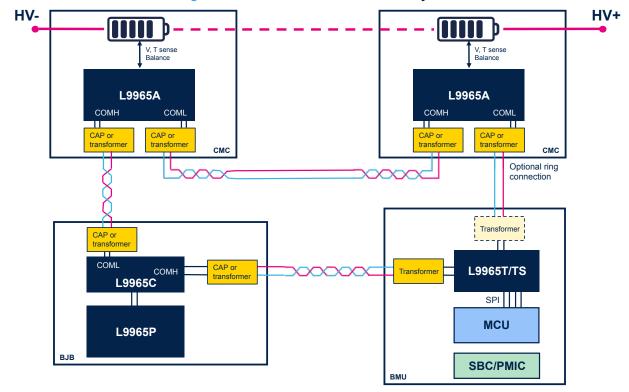

In BMS systems, the L9965T and L9965TS bidirectional SPI transceivers allow communication between isolated devices in different voltage domains through a twisted-pair connection.

The devices belong to the L9965 chipset family for the monitoring and control of high-voltage battery management systems.

## 1 Overview

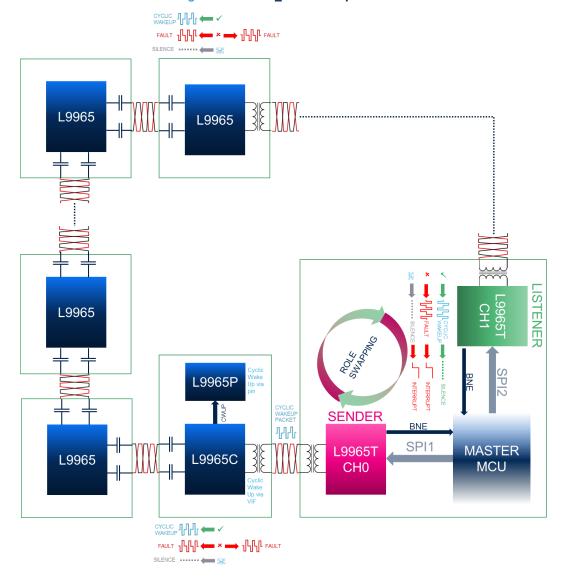

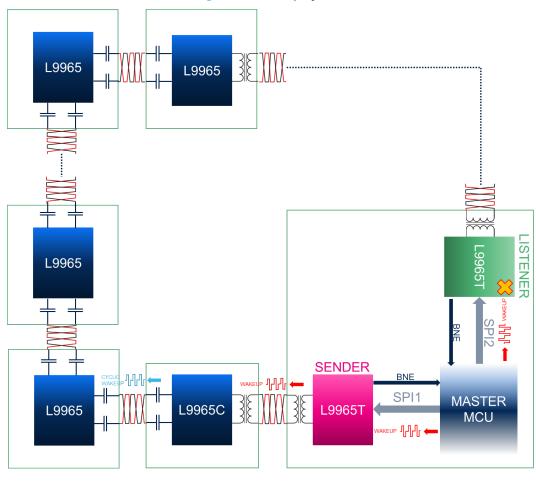

In a high voltage battery management system, the master microcontroller accesses the cells monitor and the pack current monitor devices for diagnostics and control purposes. Since the different BMS ICs are located into different voltage domains, it is required isolated communication between each other.

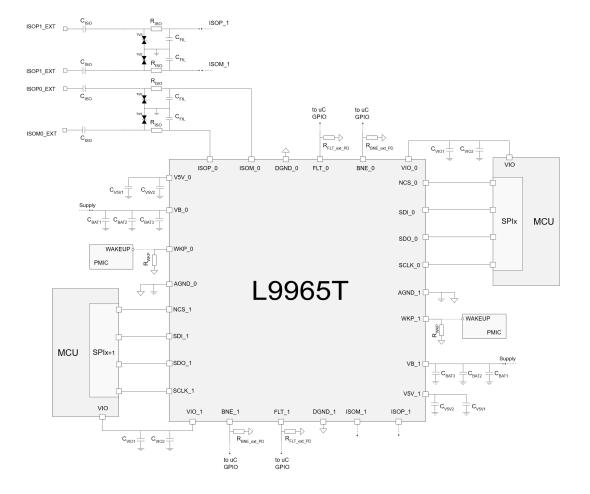

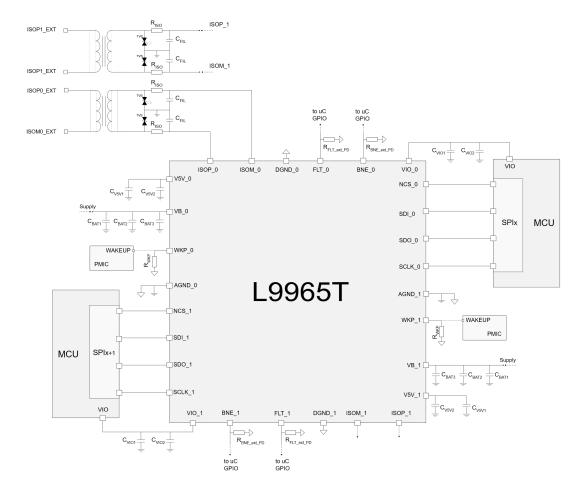

The L9965T/TS allows isolated daisy chain connection through a simple two-wire protocol in L9965x-based HV BMS applications. It converts data from a standard 4-wire SPI protocol to a 2-wire proprietary protocol (and vice versa), supporting the signals isolation by capacitors or transformers.

All the devices in the daisy chain recognize the protocol and can be addressed in read-write mode by a single transceiver. Ring connection can be implemented by the dual channel device L9965T.

L9965T/L9965TS implements two physical communication interfaces.

- SPI Target Interface: this interface is used by the controller MCU to configure and send commands to L9965T/TS and, through it, to all the devices in the chain.

- Isolated Vertical Interface (VIF): this interface is typically used to connect BMS daisy-chained devices L9965A/C to L9965T/TS and to each other on the VIF bus.

Figure 1. L9965T in a L9965x-based BMS system

The L9965T/TS manages periodic wakeup of the devices in the chain for diagnostic purposes and it is sensitive to fault tones from the devices in the chain when in low power mode. It implements a set of commands to optimize the communication over the chain:

- Broadcast command, to write and configure all devices in the chain (or a subset)

- Burst and compressed burst read, to enable high data rate transmission from all devices in the chain with negligible impact on the power consumption

- Go-to-sleep command, to set all the devices in the chain to low power mode

- FAULT/WAKEUP tone, to wake-up the chain for normal operation or faults signaling

- CYCLIC\_WAKEUP tone, to trigger periodic diagnostic execution in the chained devices.

These functionalities are implemented using different functional states, to optimize system power consumption:

NORMAL: full operation mode

DS14987 - Rev 1 page 2/62

- CYCLIC\_WAKEUP/CYCLIC\_COUNT: low power modes to send a periodic tone and trigger cyclic

diagnostics in the chained devices during low power operation. In these states the device is sensitive to

wakeup tones both from the VIF in case of fault and from the SPI by the MCU

- DEEPSLEEP: Ultralow power state for managing long inactivity periods. In this state the device is sensitive

to wakeup tones both from the VIF in case of fault and from the SPI by the MCU.

DS14987 - Rev 1 page 3/62

# Block diagram and pin description

# 2.1 Block diagram

Figure 2. Single die block diagram V5V THERMAL SHUTDOWN 8 V5V LDO VIF I/F V3V3 MAIN (ISO SPI) LDO SLEEP BANDGAP (MONITOR) MAIN BANDGAP V3V3 MAIN V3V3 MAIN NCS MAIN OSCILLATOR OSCILLATOR MONITOR SLEEP OSCILLATOR SCLK VIO SPI SLAVE I/F BNE DRIVING S MONITOR SLEEP/MAIN VIO SDO **LOGIC** DRIVING FL MONITOR **DRIVING** NVM WKP **STATUS** DGND AGND

DS14987 - Rev 1 page 4/62

## 2.2 Pin description

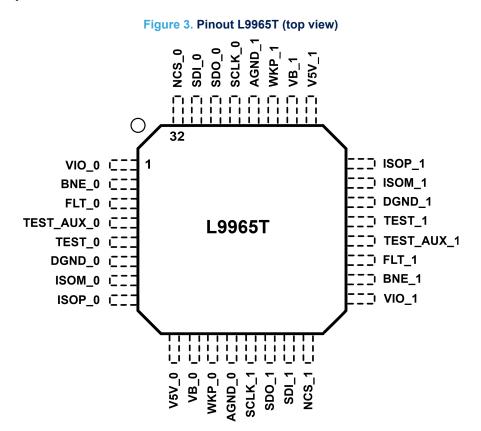

Figure 4. Pinout L9965T (top view)

DS14987 - Rev 1 page 5/62

Table 1. L9965T pin function

| Pin# | Pin name   | Description                               | Pin type                     |

|------|------------|-------------------------------------------|------------------------------|

| 1    | VIO_0      | Digital Output Buffer Supply channel 0    | Supply                       |

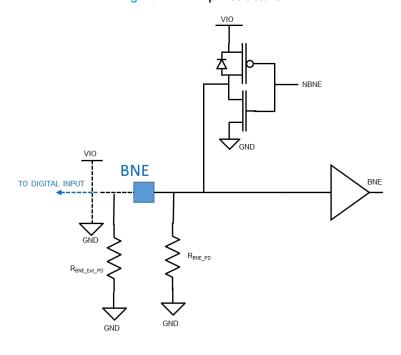

| 2    | BNE_0      | Buffer Not Empty flag channel 0           | Digital I/O                  |

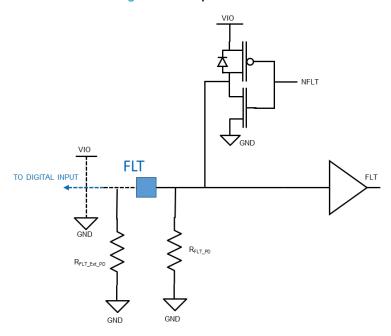

| 3    | FLT_0      | Fault interrupt out channel 0             | Digital I/O                  |

| 4    | TEST_AUX_0 | Test Mode AUX 0                           | Reserved <sup>(1)</sup>      |

| 5    | TEST_0     | Test Mode 0                               | Reserved <sup>(1)</sup>      |

| 6    | DGND_0     | Digital Ground channel 0                  | GND                          |

| 7    | ISOM_0     | VIF Port channel 0 (Negative)             | Analog I/O                   |

| 8    | ISOP_0     | VIF Port channel 0 (Positive)             | Analog I/O                   |

| 9    | V5V_0      | Internal 5 V supply channel 0             | Regulator Out <sup>(2)</sup> |

| 10   | VB_0       | Supply input battery compatible channel 0 | Supply                       |

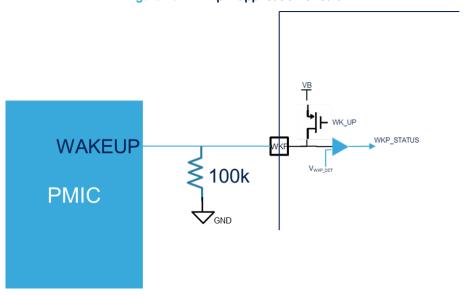

| 11   | WKP_0      | Wakeup pin channel 0                      | Analog I/O                   |

| 12   | AGND_0     | Analog Ground channel 0                   | GND                          |

| 13   | SCLK_1     | SPI Serial clock channel 1                | Digital In                   |

| 14   | SDO_1      | SPI Serial Data output channel 1          | Digital Out                  |

| 15   | SDI_1      | SPI Serial Data Input channel 1           | Digital In                   |

| 16   | NCS_1      | SPI Chip Select channel 1                 | Digital In                   |

| 17   | VIO_1      | Digital Output Buffer Supply channel 1    | Supply                       |

| 18   | BNE_1      | Buffer Not Empty flag channel 1           | Digital I/O                  |

| 19   | FLT_1      | Fault interrupt out channel 1             | Digital I/O                  |

| 20   | TEST_AUX_1 | Test Mode AUX 1                           | Reserved <sup>(1)</sup>      |

| 21   | TEST_1     | Test Mode 1                               | Reserved <sup>(1)</sup>      |

| 22   | DGND_1     | Digital Ground channel 1                  | GND                          |

| 23   | ISOM_1     | VIF Port channel 1 (Negative)             | Analog I/O                   |

| 24   | ISOP_1     | VIF Port channel 1 (Positive)             | Analog I/O                   |

| 25   | V5V_1      | Internal 5 V supply channel 1             | Regulator Out <sup>(2)</sup> |

| 26   | VB_1       | Supply input battery compatible channel 1 | Supply                       |

| 27   | WKP_1      | Wakeup pin channel 1                      | Analog I/O                   |

| 28   | AGND_1     | Analog Ground channel 1                   | GND                          |

| 29   | SCLK_0     | SPI Serial clock channel 0                | Digital In                   |

| 30   | SDO_0      | SPI Serial Data output channel 0          | Digital Out                  |

| 31   | SDI_0      | SPI Serial Data Input channel 0           | Digital In                   |

| 32   | NCS_0      | SPI Chip Select channel 0                 | Digital In                   |

<sup>1.</sup> To be tied to GND

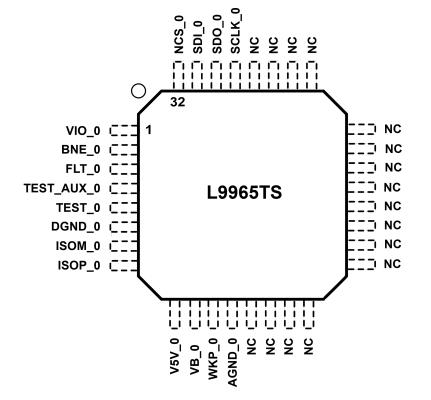

Table 2. L9965TS pin function

| Pin# | Pin name | Description                            | Pin type    |

|------|----------|----------------------------------------|-------------|

| 1    | VIO_0    | Digital Output Buffer Supply channel 0 | Supply      |

| 2    | BNE_0    | Buffer Not Empty flag channel 0        | Digital I/O |

| 3    | FLT_0    | Fault interrupt out channel 0          | Digital I/O |

DS14987 - Rev 1 page 6/62

<sup>2.</sup> To be connected to an external filtering capacitor only.

| Pin# | Pin name   | Description                               | Pin type                     |

|------|------------|-------------------------------------------|------------------------------|

| 4    | TEST_AUX_0 | Test Mode AUX 0                           | Reserved <sup>(1)</sup>      |

| 5    | TEST_0     | Test Mode 0                               | Reserved <sup>(1)</sup>      |

| 6    | DGND_0     | Digital Ground channel 0                  | GND                          |

| 7    | ISOM_0     | VIF Port channel 0 (Negative)             | Analog I/O                   |

| 8    | ISOP_0     | VIF Port channel 0 (Positive)             | Analog I/O                   |

| 9    | V5V_0      | Internal 5 V supply channel 0             | Regulator Out <sup>(2)</sup> |

| 10   | VB_0       | Supply input battery compatible channel 0 | Supply                       |

| 11   | WKP_0      | Wakeup pin channel 0                      | Analog I/O                   |

| 12   | AGND_0     | Analog Ground channel 0                   | GND                          |

| 13   | NC         | Not connected                             | -                            |

| 14   | NC         | Not connected                             | -                            |

| 15   | NC         | Not connected                             | -                            |

| 16   | NC         | Not connected                             | -                            |

| 17   | NC         | Not connected                             | -                            |

| 18   | NC         | Not connected                             | -                            |

| 19   | NC         | Not connected                             | -                            |

| 20   | NC         | Not connected                             | -                            |

| 21   | NC         | Not connected                             | -                            |

| 22   | NC         | Not connected                             | -                            |

| 23   | NC         | Not connected                             | -                            |

| 24   | NC         | Not connected                             | -                            |

| 25   | NC         | Not connected                             | -                            |

| 26   | NC         | Not connected                             | -                            |

| 27   | NC         | Not connected                             | -                            |

| 28   | NC         | Not connected                             | -                            |

| 29   | SCLK_0     | SPI Serial clock channel 0                | Digital In                   |

| 30   | SDO_0      | SPI Serial Data output channel 0          | Digital Out                  |

| 31   | SDI_0      | SPI Serial Data Input channel 0           | Digital In                   |

| 32   | NCS_0      | SPI Chip Select channel 0                 | Digital In                   |

<sup>1.</sup> To be tied to GND

DS14987 - Rev 1 page 7/62

<sup>2.</sup> To be connected to an external filtering capacitor only.

# 3 Device ratings

## 3.1 Electrical ratings

The following section describes the different operational ranges.

For each device pin:

- Operating Range (OR): within this range functions operate as specified and without parameter deviations.

All the device's electrical parameters are tested and guaranteed in this range and are valid over the whole junction temperature operating range, unless otherwise specified.

- **Absolute Maximum Rating range (AMR)**: within this range functions may not operate properly. However, the IC will not be damaged. Exposure to AMR conditions for extended periods may affect device reliability. Exceeding any AMR may cause permanent damage to the integrated circuit.

Note: Currents are noted with a positive sign when flowing into a pin.

Note: Integrated protections and diagnostics are designed to prevent device destruction under the fault conditions described in the specification. Fault conditions are considered to be out of normal operating range. Protection functions are not designed for continuous repetitive operation.

All device electrical parameters in this document are tested and guaranteed in the operating conditions specified in Table 3 below, unless otherwise noted.

DS14987 - Rev 1 page 8/62

Table 3. Absolute maximum ratings

| Param                                                     | Description                 | Test<br>cond | AMR<br>min | OR min | OR<br>typ | OR max           | AMR max                | Unit | Notes                                                                                                      |

|-----------------------------------------------------------|-----------------------------|--------------|------------|--------|-----------|------------------|------------------------|------|------------------------------------------------------------------------------------------------------------|

| Power supp                                                | olies                       |              |            |        |           |                  |                        |      |                                                                                                            |

| $V_{VB}$                                                  | VB_x voltage range          | vs. GND      | -0.3       | 6      |           | 24               | 40                     | V    |                                                                                                            |

| V <sub>VIO</sub>                                          | VIO_x voltage range         |              | 3          | 3      |           | 5.5              | 7                      | ٧    |                                                                                                            |

| V <sub>V5V</sub>                                          | V5V: voltage range          | vs. GND      | -0.3       |        | 5         |                  | 7                      | V    | Regulated supply to<br>be used only for<br>internal use (needed<br>external capacitor)                     |

|                                                           |                             |              |            |        |           |                  |                        |      | C=1µF + 1µF                                                                                                |

| Ground                                                    |                             |              |            |        |           |                  |                        |      |                                                                                                            |

| AGND                                                      | Ground                      |              | -0.3       | -0.1   |           | 0.1              | 0.3                    | V    |                                                                                                            |

| DGND                                                      | Ground                      |              | -0.3       | -0.1   |           | 0.1              | 0.3                    | V    |                                                                                                            |

| VIF                                                       |                             |              |            |        |           |                  |                        |      |                                                                                                            |

| V <sub>ISOx</sub> <sup>(1)</sup>                          | ISOM_x ISOP_x voltage range | vs. GND      | -9         | 0      |           | V <sub>V5V</sub> | 18                     | V    | AMR account for the maximum voltage that can be withstood during hotplug, BCI, and system level ESD trials |

| SPI                                                       |                             |              |            |        |           |                  |                        |      |                                                                                                            |

| V <sub>NCS</sub> , V <sub>SDI</sub> ,<br>V <sub>SCK</sub> | NCS, SDI, SCK voltage range |              | -0.3       | 0      |           | 5.5              | 7                      | V    |                                                                                                            |

| V <sub>SDO</sub>                                          | SDO voltage range           |              | -0.3       | 0      |           | V <sub>VIO</sub> | V <sub>VIO</sub> + 0,3 | V    | fed by VIO (Output)                                                                                        |

| Digital pins                                              |                             |              |            |        |           |                  |                        |      |                                                                                                            |

| BNE                                                       | BNE: voltage range          |              | -0.3       | 0      |           | V <sub>VIO</sub> | V <sub>VIO</sub> + 0,3 | V    | active High, fed by VIO (Output)                                                                           |

| FLT                                                       | FLT Voltage Range           |              | -0.3       | 0      |           | V <sub>VIO</sub> | V <sub>VIO</sub> + 0,3 | V    | active High, fed by VIO (Output)                                                                           |

| Others                                                    |                             |              |            |        |           |                  |                        |      |                                                                                                            |

| WKP                                                       | WKP Voltage Range           |              | -0.3       | 0      |           | V <sub>VB</sub>  | V <sub>VB</sub> + 0.3  | ٧    | PMOS open drain                                                                                            |

<sup>1.</sup> This limit is intended to guarantee DPI EMC, BCI EMC, Hotplug, and ESD 4kV HBM on ISOx pins

# 3.2 ESD ratings

**Table 4. ESD protection**

| Test Type               | Pin                  | Value | Unit |

|-------------------------|----------------------|-------|------|

| HBM <sup>(1)</sup>      | All pins             | ±2    | kV   |

| HBM <sup>(1)(2)</sup>   | ISOPx , ISOMx , VB_x | ±4    | kV   |

| CDM <sup>(3)</sup>      | All pins             | ±500  | V    |

| CDM <sup>(3)</sup>      | Corner pins          | ±750  | V    |

| Latch-up <sup>(4)</sup> | All pins             | ±100  | mA   |

- 1. HBM (human body model) test according to AEC-Q100-002

- 2. Each pin is tested versus GND. GND pins connected together

- 3. CDM (Charged Device Model) test according to AEC-Q100-011

- 4. Latch-up test according to AEC-Q100-004 Class-2, Level-A

DS14987 - Rev 1 page 9/62

# 3.3 Thermal ratings

All device electrical parameters are tested and guaranteed in the temperature operating conditions reported in Table 5 below, unless otherwise noted.

Table 5. Temperature ranges and thermal data

| Symbol              | Parameter                                                 | Min | Тур | Max | Unit |

|---------------------|-----------------------------------------------------------|-----|-----|-----|------|

| T <sub>amb</sub>    | Operating temperature (ECU environment)                   | -40 |     | 125 | °C   |

| Тj                  | Operating junction temperature                            | -40 |     | 150 | °C   |

| T stg               | Storage temperature                                       | -65 |     | 150 | °C   |

| R <sub>Th j-a</sub> | Thermal resistance junction-to-ambient <sup>(1)</sup> (2) |     | 54  |     | °C/W |

<sup>1.</sup> For each die

DS14987 - Rev 1 page 10/62

<sup>2.</sup> Evaluated according to Jedec JESD51-2, -5, -7 guideline with a 2s2p thermally enhanced PC

# 4 Current consumption

L9965T/TS are supplied by VBx pins, which are used to generate all the regulated supplies of related transceiver die

When used in BEV/PHEV systems, the IC is usually placed in the LV battery junction box, where it is usually supplied by the 12 V battery supply.

Current consumption is reported in different operating modes. Refer to Section 5.1 for functional state definitions.

Table 6. Current consumption for each die

| Symbol                       | Parameter                                           | Test condition                         | Min | Тур | Max | Unit | Pin |

|------------------------------|-----------------------------------------------------|----------------------------------------|-----|-----|-----|------|-----|

| I <sub>VB</sub> (DEEPSLEEP)  | Supply Current                                      | DEEPSLEEP                              |     | 4   | 10  | μA   | VB  |

| IVB(DEEL OFFEL )             | Supply Culterit                                     | -40°C ≤ Tamb ≤ +85°C                   |     | 4   | 10  | μΑ   | VD  |

| I <sub>VB</sub> (DEEPSLEEP)  | Supply Current                                      | DEEPSLEEP                              |     | 10  | 15  | μA   | VB  |

| IVB(DEEL OFFEL )             | Supply Culterit                                     | +85°C ≤ Tamb ≤+125°C                   |     | 10  | 13  | μΛ   | VD  |

| I <sub>VB</sub> (CYCLIC)     | Consumption from VB pin when wakeup timer is active | CYCLIC_COUNT Mode -40°C ≤ Tamb ≤ +85°C |     | 30  | 37  | μΑ   | VB  |

| I <sub>VB</sub> (CYCLIC)     |                                                     | CYCLIC_COUNT Mode +85°C ≤ Tamb ≤+125°C |     | 40  | 45  | μA   | VB  |

| I <sub>VB</sub> (NORMAL)     | Supply Current                                      | NORMAL no current on WKP pin           |     | 1.6 | 2   | mA   | VB  |

| I <sub>VIO</sub> (DEEPSLEEP, | VIO Supply Current                                  | DEEPSLEEP                              |     |     | 1   |      | VIO |

| CYCLIC_COUNT)                | VIO Supply Current                                  | CYCLIC_COUNT                           |     |     |     | μA   | VIO |

| I <sub>VIO</sub> (NORMAL)    | VIO Supply Current                                  | NORMAL state, BNE and FLT pins idle    |     | 490 | 600 | μΑ   | VIO |

DS14987 - Rev 1 page 11/62

# 5 Functional description

## 5.1 Device functional states

The following figure shows all possible L9965T and L9965TS states.

VB < VB por 25/11/2022 OFF VB >= VB por+hyst VB < VB por **DEEP SLEEP** FAULT/WAKEUP tone received from VIF or WAKEUP sequence received from SPI or CYCLIC WAKEP tone received

\*1 VB < VB por **CYCLIC** T\_cyclic expired (listener) or FAULT/WAKEUP tone received from VIF or WAKEUP sequence received from SPI \*1 COUNT Cyclic wakeup routine T\_cyclic expired (sender) \*1 finished without internal fault detected VB < VB por **CYCLIC** WAKEUP Internal fault detected or FAULT/WAKEUP tone received from VIF or WAKEUP sequence received from SPI VB < VB por NORMAL GO2SLP and GO2SLP and \*1 Subject to T<sub>WAKEUP\_TIMEOUT</sub> CYCLIC WAKE enabled CYCLIC WAKE not enabled

Figure 5. L9965T/TS functional state mode (FSM)

Table 7. Device functional states

| State        | Purpose                                                            | Reached<br>from   | Condition                                                                                                                    | Active resources                                             |  |

|--------------|--------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| OFF          | Device OFF                                                         | Any state         | When VB voltage falls below the POR threshold                                                                                | None                                                         |  |

| DEEPSLEEP    | Ultra-low power<br>state for<br>managing long<br>inactivity        | NORMAL            | GO2SLP command received AND no CYCLIC_WAKEUP timer enabled (GEN_CFG5.WAKEUP_CYCLIC_ENB=0) OSC STUCK detected V5V_OT detected | Wake up Via VIF<br>Wake up via SPI<br>Target                 |  |

|              | periods                                                            | CYCLIC_<br>WAKEUP | OSC STUCK detected     V5V_OT detected                                                                                       |                                                              |  |

|              |                                                                    | OFF               | VB > POR threshold + hysteresis                                                                                              |                                                              |  |

|              |                                                                    |                   | CYCLIC_WAKEUP routine finished without internal fault detected                                                               | Wake up Via VIF Wake up via SPI                              |  |

| CYCLIC_COUNT | Performs count<br>in order to<br>cyclically wake-<br>up the system | NORMAL            | GO2SLP command validated AND CYCLIC_WAKEUP timer enabled (GEN_CFG5.WAKEUP_CYCLIC_ENB=1)                                      | Target  Cyclic wakeup timer as configured during NORMAL mode |  |

DS14987 - Rev 1 page 12/62

| State         | Purpose                                                  | Reached from     | Condition                                                                                                                                                    | Active resources                                 |

|---------------|----------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| CYCLIC_WAKEUP | To perform cyclic diagnostics during low power operation | CYCLIC_<br>COUNT | CYCLIC_WAKEUP timer expired (in sender mode)                                                                                                                 | Wake up Via VIF Cyclic wakeup diagnostic routine |

| NORMAL        | Full operation  CYCLIC_COUNT  CYCLIC_WAKEUP              |                  | <ul> <li>FAULT/WAKEUP tone received from VIF</li> <li>CYCLIC_WAKEUP tone received from VIF</li> <li>WAKEUP command received from SPI</li> </ul>              |                                                  |

|               |                                                          | _                | <ul> <li>FAULT/WAKEUP tone received from VIF</li> <li>WAKEUP command received from SPI</li> <li>CYCLIC_WAKEUP timeout expired (in listener mode)</li> </ul>  | All resources fully operative                    |

|               |                                                          | _                | <ul> <li>Internal fault detected during diagnostic routine</li> <li>FAULT/WAKEUP tone received from VIF</li> <li>WAKEUP command received from SPI</li> </ul> |                                                  |

For the special frames VIF FAULT/WAKEUP tone, VIF CYCLIC\_WAKEUP tone and SPI WAKEUP sequence, refer to Section 5.8.3.

#### 5.1.1 NORMAL State and wakeup sources

In NORMAL mode all resources are fully available.

#### 5.1.1.1 Wakeup Sources

The L9965T/TS responds to three wakeup sources:

- Wakeup via VIF

- The IC is daisy-chained on the VIF bus along with other companion chips, and can be woken up by VIF special frames (CYCLIC WAKEUP or FAULT/WAKEUP frames) sent from another device (see Section 5.8.3)

- Wakeup via SPI

- The IC can be woken up by any dummy frame received on the SPI

- Self-Wakeup

- A wakeup trigger is internally generated when the device is in CYCLIC\_WAKEUP mode (see Section 5.1.2).

The device can reach NORMAL state from low power states by the wakeup via SPI and via VIF sources, described below.

Whenever a wakeup source is validated, the wakeup sequence is initiated and shall successfully end within  $T_{WAKEUP\ TIMEOUT}$ . Otherwise, the IC returns to DEEPSLEEP state

## 5.1.1.1.1 Wakeup via VIF

When in DEEPSLEEP, CYCLIC\_WAKEUP or CYCLIC\_COUNT the IC is sensitive to wakeup signals incoming on VIF port (see Section 5.8.3).

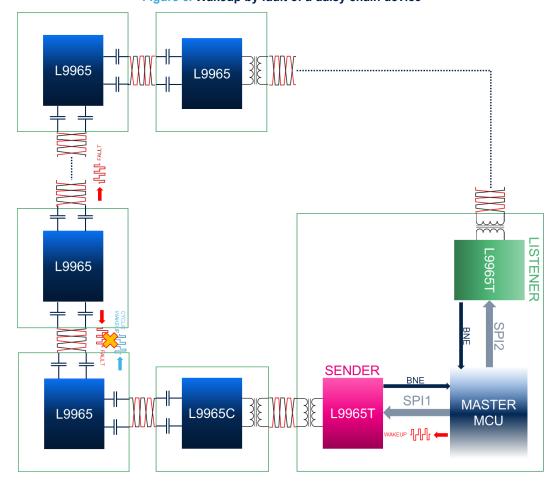

Figure 6 shows a typical application scenario where some L9965x in the chain has self-detected a fault and wakes up the daisy-chain sending the FAULT/WAKEUP tone on both VIF ports.

The wakeup by fault of a VIF daisy chain device is an asynchronous event with respect to the CYCLIC\_WAKEUP thread managed in background by the L9965T/TS. Fault notification mechanism guarantees that the FAULT/WAKEUP tone is correctly propagated at least in one direction, even in case of conflict with the CYCLIC\_WAKEUP tone.

Depending on the position of the sending L9965x in the daisy chain, the wakeup interrupt reaches the MCU in approximately less than:

1/2\*NVIF STACK\*TVIF WAKEUP TIME ≤ t ≤ NVIF STACK\*TVIF WAKEUP TIME.

DS14987 - Rev 1 page 13/62

In a ring topology, a FLT pin interrupt is generated from both channels of L9965T within  $N_{VIF\_STACK}^*T_{VIF\_WAKEUP\_TIME}$  timeout.

When the MCU is woken up by one channel of L9965T, it is supposed to wait also for the other channel to generate the FLT pin interrupt to confirm the daisy-chain wakeup. If such event does not occur within the  $N_{VIF\_STACK}^{*T}_{VIF\_WAKEUP\_TIME}$  timeout, the MCU shall run the VIF chain wakeup by MCU procedure.

Figure 6. Wakeup by fault of a daisy chain device

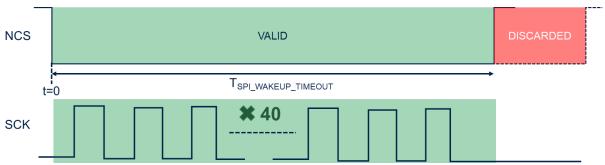

#### **5.1.1.1.2** Wake-up via SPI

L9965T/TS can be woken up in DEEPSLEEP, CYCLIC\_COUNT and CYCLIC\_WAKEUP state by any valid SPI frame issued by MCU on the SPI Target. A wakeup condition is acknowledged when the following pattern is received:

- 1. A NCS high to low transition

- 2. 40 SCK pulses

- 3. A NCS low to high transition

The T<sub>SPI\_WAKEUP\_TIMEOUT</sub> is started upon every NCS assertion, and the wakeup pattern shall end before timeout expiration, otherwise it is discarded.

DS14987 - Rev 1 page 14/62

Wakeup frames are not decoded: their content may be arbitrary. However, it is strongly recommended to send READ commands to avoid inadvertent write operations in case the device is already awake.

### 5.1.1.2 NORMAL State diagnostics

In this state several diagnostic functions are available:

- 1. NVM data integrity check

- 2. Periodic check of registers data integrity, if configured by GENERAL REG.CYC CRC DIS

- 3. Oscillator fail

- Oscillator stuck: if detected, logic block is immediately put under reset and the device moves to DEEPSLEEP state (immediate reaction)

- 5. Oscillators monitor BIST

- 6. VB undervoltage

- 7. V3V3 overvoltage

- 8. V5V overvoltage

- 9. V5V undervoltage

- 10. V5V overcurrent

- 11. GND loss if configured by the GEN CFG4.EN GND LOSS bit

- 12. Analog comparators BIST if configured by the GEN CFG5.BIST ANA ENB = 1

- a. VB undervoltage comparator analog BIST

- b. V3V3 overvoltage comparator analog BIST

- c. V5V undervoltage comparator analog BIST

- d. V5V overvoltage comparator analog BIST

- 13. WKP, FLT and BNE pins diagnostics

- 14. Thermal-shutdown monitoring

- 15. VIF communication monitoring

- 16. SPI communication monitoring.

All the fault and events detected by L9965T/TS are latched in a corresponding status bits and can be read by the BMS MCU through SPI communication.

The most relevant faults and events are reported, according to fault detection mask registers, in the internal GSW (Global Status Word). The OR combination of all the bits in the GSW is signaled by the FAULT bit of the SPI MISO frame shown in Table 26 and notified by the FLT pin (HIGH if at least one of the bits in the GSW is set) to trigger an MCU interrupt.

Assert condition and behavior of each fault are described in detail in the related section.

### 5.1.2 CYCLIC WAKEUP State

When all the BMS system is in low power mode, the L9965T/TS can be configured to automatically trigger chain monitoring, according to the system topology (single access or ring), alternating CYCLIC\_COUNT and CYCLIC\_WAKEUP states.

DS14987 - Rev 1 page 15/62

#### 5.1.2.1 CYCLIC\_WAKEUP State operation

To configure CYCLIC\_WAKEUP state the following procedure must be followed.

## Procedure 1: Set up of CYCLIC\_WAKEUP state

- 1. Program the proper  $T_{CYCLIC}$  WAKEUP in GEN\_CFG5.WAKEUP\_CYCLIC\_TIMEOUT\_SENDER\_SEL register

- 2. Enable the CYCLIC\_WAKEUP by setting the GEN\_CFG5.WAKEUP\_CYCLIC\_ENB bit in GEN\_CFG5 register

- 3. Send a global broadcast GO2SLP command (Section 5.8.3.3) to move all the ICs in low power mode

- 4. L9965T/TS moves to CYCLIC\_COUNT state. The value of the cyclic counter during CYCLIC\_COUNT state is stored in GEN\_STATUS2.WAKEUP\_CYCLIC\_TRX\_COUNTER. The LSB of this register is 4.096e-3 seconds.

Step 1, 2 and 3 of the above procedure must be applied on both channels of the L9965T if configured in ring topology.

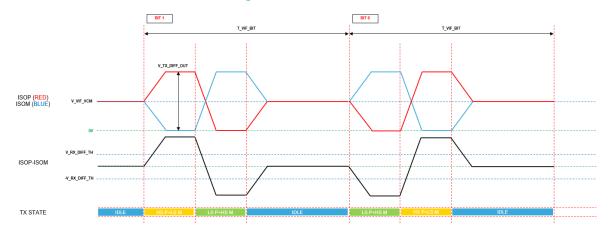

The system operates as shown in Figure 8 according to the daisy-chain topology.

#### Ring topology:

- Dual transceiver scenario: the two L9965T channels should be configured by the MCU in sender (setting GEN\_CFG5.WAKEUP\_CYCLIC\_SENDER bit) and listener (setting CFG5.WAKEUP\_CYCLIC\_LISTENER bit) modes.

- Single transceiver scenario: If the devices are connected in single access daisy chain, the last L9965A

device in the chain can be configured to propagate backward the CYCLIC\_WAKEUP tone. In this case the

single transceiver channel should be configured by the MCU in sender (setting

GEN CFG5.WAKEUP CYCLIC SENDER bit).

- As sender, the transceiver has the VIF RX and VIF TX both enabled. After T<sub>CYCLIC\_WAKEUP</sub> the sender moves from CYCLIC\_COUNT to CYCLIC\_WAKEUP state, performs the internal diagnosis (see Section 5.1.2.2) and, if no faults are present, it sends a CYCLIC\_WAKEUP tone on the VIF to wake up one by one the devices on the daisy chain, then changes his role to listener, set the timer threshold at T<sub>CYCLIC\_WAKEUP\_TIMEOUT</sub>, and moves again to CYCLIC\_COUNT state.

- The listener (can be either the The transceiver channel on the opposite end of the ring, or the single transceiver switched from sender in the previous step) has the VIF RX enabled and VIF TX disabled. If the CYCLIC\_WAKEUP tone arrives within T<sub>CYCLIC\_WAKEUP\_TIMEOUT</sub>, the "no fault" condition is acknowledged, the listener changes his role to sender, the timer is reset to count until T<sub>CYCLIC\_WAKEUP</sub> and the cycle starts again in the opposite direction

- If the CYCLIC\_WAKEUP tone is not received within T<sub>CYCLIC\_WAKEUP\_TIMEOUT</sub> when transceiver is listener, it moves to NORMAL state and asserts the WKP and FLT pins (to wake up the MCU) and set GEN\_STATUS2.WAKEUP\_CYCLIC\_TRX\_TIMEOUT bit.

- If during the internal diagnosis phase a fault is asserted, the device moves to NORMAL state. According to fault detection mask registers GEN\_CFG2 and GEN\_CFG3, fault detection is notified by the FLT pin (asserted HIGH) and reported on the FAULT bit of the SPI MISO frame shown in Table 26. Depending on its configuration (see Section 5.9.3) also WKP pin may be asserted HIGH in case of faults. In this case no CYCLIC WAKEUP tone is generated.

**Single access**: L9965TS channel moves to CYCLIC\_WAKEUP state, performs the diagnostics in Section 5.1.2.2 and generates a CYCLIC\_WAKEUP tone every T<sub>CYCLIC\_WAKEUP</sub> period. The transceiver is sensitive to fault wakeup from VIF and wakeup by MCU.

DS14987 - Rev 1 page 16/62

Figure 8. CYCLIC WAKEUP operation

The CYCLIC WAKEUP state can be divided in three phases:

- 1. Transition phase from CYCLIC\_COUNT to CYCLIC\_WAKEUP state.

- 2. Diagnostic phase

- 3. CYCLIC\_WAKEUP tone generation (see Section 5.8.3.7). CYCLIC\_WAKEUP tone is generated only if there aren't fault recorded during diagnostic phase.

During CYCLIC\_WAKEUP state every VIF data frame is not recognized by the device, and only FAULT/WAKEUP tones (see Section 5.8.3.8) and SPI wakeup commands (see Section 5.8.3.2) are accepted.

Device reaction to incoming wake-up tones from VIF or from SPI Target are the following:

- During transition phase from CYCLIC\_COUNT to CYCLIC\_WAKEUP state: IC moves to NORMAL and sets FLT and WKP outputs (depending on the setting of WKP pin, see Section 5.9.3). Device never completes the CYCLIC\_WAKEUP phase.

- During diagnostic phase: IC moves to NORMAL state (it becomes again sensitive to VIF communication) and sets FLT and WKP outputs (depending on the setting of WKP pin, see Section 5.9.3); diagnostic routine continues until completion.

- During CYCLIC WAKEUP tone generation device moves to NORMAL state.

## 5.1.2.2 CYCLIC\_WAKEUP State diagnostics

During the CYCLIC WAKEUP state the following diagnostics are automatically performed:

DS14987 - Rev 1 page 17/62

- 1. NVM trimming data CRC

- 2. NVM configuration data CRC

- 3. Oscillator fail

- 4. Oscillator stuck: if detected, logic block is immediately put under reset and the device moves to DEEPSLEEP state (immediate reaction)

- 5. Oscillators Monitor BIST

- 6. V3V3 overvoltage

- 7. V5V overvoltage

- 8. V5V undervoltage

- 9. V5V overcurrent

- 10. GND loss (In CYCLIC\_WAKEUP this diagnosis is executed automatically independently by the value of GND LOSS ENABLE bit)

- 11. Analog BIST:

- a. V3V3 overvoltage comparator analog BIST

- b. V5V overvoltage comparator analog BIST

- c. V5V undervoltage comparator analog BIST

- d. GND loss comparator BIST

- 12. Thermal-shutdown monitoring

If at least one of the above faults is verified, the device moves to NORMAL state and the fault detection is latched in the corresponding bit of the status registers GEN\_STATUS1 and GEN\_STATUS3. Faults that may happen within VIF tone generation time will not cause a transition to NORMAL state.

According to fault detection mask registers GEN\_CFG2 and GEN\_CFG3, fault detection is notified by the FLT pin (asserted HIGH) and reported on the FAULT bit of the SPI MISO frame shown in Table 26. Depending on its configuration (see Section 5.9.3), the WKP pin may also be asserted HIGH in case of faults. In this case, no CYCLIC WAKEUP tone is generated.

Assert condition and behavior of each fault are described in detail in the related section.

In addition to the above faults monitoring, a timeout counter ( $T_{CW\_diag\_timeout}$ ) is running in background during diagnostic phase to monitor its duration.

Table 8. CYCLIC\_WAKEUP timeout diagnostic

| Fault type                        | Assertion condition                                                      | IC reaction to assertion                                                                                                                                                                       | Release condition | Maskable        |

|-----------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|

| CYCLIC_WAKEUP<br>Duration Timeout | Diagnostic time in CYCLIC_WAKEUP t > T <sub>CW_diag_timeout</sub>        | <ul> <li>Diagnostic routine is interrupted</li> <li>Device moves to NORMAL</li> <li>GEN_CFG5.WAKEUP_CYCLIC_END = 1</li> <li>The FLT pin, the WKP pin and the SPI FAULT are asserted</li> </ul> | Clear on read     | Non<br>maskable |

| CYCLIC_WAKEUP                     | Tone not received in TCYCLIC_WAKEUP_TIMEOUT when transceiver is listener | <ul> <li>Device moves to NORMAL</li> <li>GEN_CFG5.WAKEUP_CYCLIC_TRX_TIMEOUT = 1</li> <li>The FLT pin, the WKP pin and the SPI FAULT are asserted</li> </ul>                                    | Clear on read     | Non<br>maskable |

### 5.1.3 Electrical parameters

Table 9. FSM and Wakeup electrical parameters

| Symbol                     | Parameter                                                                  | Test conditions | Min | Тур | Max | Unit |

|----------------------------|----------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| T <sub>FIRST_POWERUP</sub> | Time needed to perform first power-up sequence (to reach DEEP_SLEEP state) |                 |     |     | 1   | ms   |

DS14987 - Rev 1 page 18/62

| Symbol                                  | Parameter                                                       | Test conditions                                                                        | Min   | Тур   | Max   | Unit |

|-----------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|------|

| T <sub>WAKEUP</sub>                     | Time from wakeup<br>detection to ISOL-ISOP<br>ready to transmit |                                                                                        |       |       | 3     | ms   |

| T <sub>VIF_WAKEUP_TIME</sub>            | Duration of wakeup from VIF detection                           |                                                                                        |       |       | 2     | ms   |

| T <sub>SPI_WAKEUP_TIME</sub>            | Duration of wakeup from SPI detection                           | From the NCS low to high transition to the IC in NORMAL state and ready to communicate |       |       | 2     | ms   |

| T <sub>SELF_WAKEUP</sub>                | Self-wakeup latency                                             | From the assertion of a fault in CYCLIC_WAKEUP to the complete transition in NORMAL    |       |       | 2     | ms   |

| T <sub>SPI_WAKEUP_TIMEOUT</sub>         | Timeout for receipt of wakeup frame                             |                                                                                        | 0.4   |       | 2     | ms   |

| T <sub>CW_diag_timeout</sub>            | Diagnostics timeout                                             |                                                                                        | 55    |       | 75    | ms   |

| T <sub>WAKEUP_TIMEOUT</sub>             | Timeout for completing the wakeup sequence                      |                                                                                        | 17    | 20    | 33    | ms   |

| T <sub>CYCLIC_</sub> WAKEUP_000         |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=000                                      | 0.96  | 1.06  | 1.15  |      |

| T <sub>CYCLIC_WAKEUP_001</sub>          |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=001                                      | 1.90  | 2.10  | 2.30  |      |

| T <sub>CYCLIC_</sub> WAKEUP_010         |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=010                                      | .90   | 3.20  | 3.50  |      |

| T <sub>CYCLIC_</sub> WAKEUP_011         | Transceiver                                                     | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=011                                      | 3.80  | 4.20  | 4.60  |      |

| T <sub>CYCLIC_WAKEUP_100</sub>          | CYCLIC_WAKEUP tone generation period                            | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=100                                      | 4.802 | 5.30  | 5.80  | S    |

| T <sub>CYCLIC_WAKEUP_101</sub>          |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=101                                      | 5.80  | 6.35  | 6.90  |      |

| T <sub>CYCLIC_</sub> WAKEUP_110         |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=110                                      | 6.70  | 7.45  | 8.20  |      |

| T <sub>CYCLIC_WAKEUP_111</sub>          |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_SENDER_SEL=111                                      | 7.70  | 8.45  | 9.20  | -    |

| T <sub>CYCLIC_WAKEUP_TIMEOUT_000</sub>  |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_LISTENER_SEL=000                                    | 2.70  | 3.00  | 3.30  |      |

| TCYCLIC_WAKEUP_TIMEOUT_001              |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_LISTENER_SEL=001                                    | 4.37  | 4.86  | 5.34  |      |

| TCYCLIC_WAKEUP_TIMEOUT_010              |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_LISTENER_SEL=010                                    | 6.04  | 6.71  | 7.39  |      |

| TCYCLIC_WAKEUP_TIMEOUT_011              | Transceiver CYCLIC_WAKEUP timeout                               | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_LISTENER_SEL=011                                    | 7.71  | 8.57  | 9.43  | s    |

| T <sub>CYCLIC_WAKEUP_TIMEOUT_100</sub>  |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_LISTENER_SEL=100                                    | 9.39  | 10.43 | 11.47 | -    |

| T <sub>CYCLIC_</sub> WAKEUP_TIMEOUT_101 |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_LISTENER_SEL=101                                    | 11.06 | 12.29 | 13.51 |      |

| T <sub>CYCLIC_</sub> WAKEUP_TIMEOUT_110 |                                                                 | GEN_CFG5.WAKEUP_CYCLIC_ TIMEOUT_LISTENER_SEL=110                                       | 12.73 | 14.14 | 15.56 | -    |

DS14987 - Rev 1 page 19/62

| Symbol                                 | Symbol Parameter Test conditions    |                                                                                     | Min   | Тур   | Max   | Unit |

|----------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|------|

| T <sub>CYCLIC_WAKEUP_TIMEOUT_111</sub> | Transceiver CYCLIC_WAKEUP timeout   | GEN_CFG5.WAKEUP_CYCLIC_<br>TIMEOUT_LISTENER_SEL=111                                 | 14.40 | 16.00 | 17.60 | S    |

| T <sub>SELF_WAKEUP</sub>               | Self-wakeup latency                 | From the assertion of a fault in CYCLIC_WAKEUP to the complete transition in NORMAL |       |       | 2     | ms   |

| T <sub>SPI_WAKEUP_TIMEOUT</sub>        | Timeout for receipt of wakeup frame |                                                                                     | 0.4   |       | 2     | ms   |

## 5.2 Power supply section

The VB pin is the main supply:

- It feeds the 5V LDO (V5V)

- It feeds the 3V3 Internal LDO (V3V3)

- It is directly connected to WKP pin

## 5.2.1 V<sub>B</sub> battery supply

#### 5.2.1.1 Diagnostic functions

Table 10. Power supply diagnostics

| Fault<br>type | Assertion condition                        | IC reaction to assertion                                                                                                              | Release condition                                                                   | Maskable                                                                                  |

|---------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| VB UV         | V <sub>VB</sub> <<br>V <sub>VB_UV_TH</sub> | <ul> <li>VB_UV = 1 in GEN_STATUS1</li> <li>The FLT pin and the SPI FAULT are asserted in NORMAL if MSK_VB_UV=0 in GEN_CFG3</li> </ul> | Clear on read if  V <sub>VB</sub> > V <sub>VB_UV_TH</sub> +  V <sub>VB_UV_HYS</sub> | VB_UV status bit non maskable FLT pin and SPI FAULT maskable by bit MSK_VB_UV in GEN_CFG3 |

#### 5.2.1.2 Electrical parameters

Table 11. Power supply electrical parameters

| Symbol                 | Parameter                   | Test condition       | Min  | Тур | Max  | Unit |

|------------------------|-----------------------------|----------------------|------|-----|------|------|

| V <sub>VB_UV_TH</sub>  | VB Undervoltage Threshold   | Tested in production | 4.75 | 5   | 5.25 | V    |

| V <sub>VB_UV_HYS</sub> | VB Undervoltage hysteresis  | Tested in production | 85   |     | 185  | mV   |

| T <sub>VB_UV_FIL</sub> | VB Undervoltage filter time | Tested by SCAN       |      | 20  |      | μs   |

## 5.2.2 VIO output buffer supply

This supply must be powered externally by a regulated 3.3V or 5V voltage (could be from MCU PMIC). It powers SDO, FLT, and BNE interface pins.

## 5.2.3 V3V3 internal LDO

This is the internal 3.3V LDO:

- It is fed by the VB main supply

- It is used for supplying internal circuitry

When in undervoltage, it determines the POR\_MAIN assertion.

The bit GEN\_CFG5.POR\_SLEEP\_ASSERTED indicates that a transition to OFF state has occurred or that an oscillator stuck condition has been previously detected. At the first power-up, this bit is normally asserted.

DS14987 - Rev 1 page 20/62

#### 5.2.3.1 Diagnostics functions

Table 12. Power supply diagnostics

| Fault<br>type | Assertion condition                                                             | IC reaction to assertion | Release condition                                                                                 | Maskable                                                                                               |

|---------------|---------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| V3V3<br>OV    | V <sub>3V3</sub> ><br>V3V3 <sub>OV_TH</sub> for t<br>> T <sub>V3V3_OV_FIL</sub> | MSK V3V3 INT OV=0 in     | Clear on read if $V_{3V3} < V_{3V3}\_OV\_TH$ + $V_{3V3}\_OV\_HYS$ for t>T <sub>V3V3</sub> _OV_FIL | V3V3_INT_OV status bit non maskable  FLT pin and SPI FAULT maskable by bit MSK_V3V3_INT_OV in GEN_CFG3 |

### 5.2.3.2 Electrical parameters

Table 13. Power supply electrical parameters

| Symbol                  | Parameter               | Test condition | Min  | Тур  | Max  | Unit |

|-------------------------|-------------------------|----------------|------|------|------|------|

| V3V3 <sub>OV_TH</sub>   | Overvoltage threshold   |                | 3.45 | 3.71 | 3.97 | V    |

| V3V3 <sub>OV_HYS</sub>  | Undervoltage hysteresis |                | 10   |      | 60   | mV   |

| T <sub>3V3_OV_FIL</sub> | OV filter time          | Tested by SCAN | 17   |      | 23   | μs   |

## 5.2.4 5V LDO (V5V)

This is the 5V LDO:

- It is fed by VB main supply

- It feeds the Isolated Vertical Interface (VIF)

## 5.2.4.1 Diagnostic functions

The undervoltage, overvoltage (caused by external load on V5V pin) and overcurrent (short-to-GND scenario) conditions are covered by dedicated diagnostics.

The V5V pin is protected by a thermal sensor and shut-down comparator. For this diagnostic, refer to Section 5.4. All V5V monitoring features are available in NORMAL and CYCLIC\_WAKEUP states.

Table 14. V5V LDO diagnostics

| Fault<br>type | Assertion condition                                                         | IC reaction to assertion                                                                                                                                                       | Release condition                                                                                                       | Maskable                                                                                                                 |

|---------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| V5V<br>UV     | $V_{V5V} < V_{V5V\_UV\_TH}$ for t > $T_{V5V\_UV\_OV\_FIL}$                  | <ul> <li>V5V_UV = 1 in<br/>GEN_STATUS1</li> <li>The FLT pin and the SPI<br/>FAULT is asserted in<br/>NORMAL if<br/>MSK_V5V_UV=0 in<br/>GEN_CFG3</li> </ul>                     | Clear on read if  V <sub>V5V</sub> > V <sub>V5V_UV_TH</sub> +  V <sub>V5V_UV_HYS</sub> for t>T <sub>V5V_UV_OV_FIL</sub> | <ul> <li>V5V_UV status bit non maskable</li> <li>FLT pin and SPI FAULT maskable by bit MSK_V5V_UV in GEN_CFG3</li> </ul> |

| V5V<br>OV     | V <sub>V5V</sub> > V <sub>V5V_OV_TH</sub> for t> T <sub>V5V_UV_OV_FIL</sub> | <ul> <li>V5V_OV = 1 in         GEN_STATUS1</li> <li>The FLT pin and the SPI         FAULT is asserted in         NORMAL if         MSK_V5V_OV=0 in         GEN_CFG3</li> </ul> | Clear on read if  V <sub>V5V</sub> < V <sub>V5V_OV_TH</sub> -  V <sub>V5V_OV_HYS</sub> for t>T <sub>V5V_UV_OV_FIL</sub> | V5V_OV status bit non maskable FLT pin and SPI FAULT maskable by bit MSK_V5V_OV in GEN_CFG3                              |

| V5V<br>OC     | I <sub>V5V</sub> > I <sub>TH_OC_V5V</sub> for t> t <sub>FLT_OC_V5V</sub>    | V5V_OC = 1 in     GEN_STATUS3                                                                                                                                                  | Clear on read if  I <sub>V5V</sub> < V <sub>V5V_OV_TH</sub> -  V <sub>V5V_OV_HYS</sub>                                  | V5V_OC status bit non maskable                                                                                           |

DS14987 - Rev 1 page 21/62

| Fault<br>type | Assertion condition | IC reaction to assertion Release condition                                      |                                   | Maskable                                                              |

|---------------|---------------------|---------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------|

|               |                     | The FLT pin and the SPI FAULT is asserted in NORMAL if MSK_V5V_OC=0 in GEN_CFG3 | for t>T <sub>V5V_UV</sub> _oV_FIL | FLT pin and SPI FAULT<br>maskable by bit<br>MSK_V5V_OC in<br>GEN_CFG3 |

### 5.2.4.2 Electrical parameters

Table 15. V5V electrical parameters

| Symbol                               | Parameter                                      | Test conditions                                                                                | Min  | Тур  | Max  | Unit |

|--------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>V5V</sub> Regulated voltage N |                                                | NORMAL, All operating lines and loads                                                          |      | 5    | +2%  | V    |

| I <sub>V5V_LIM</sub>                 | Current limitation                             | NORMAL, V <sub>V5V</sub> = 0V Tested in production                                             | -220 |      | -80  | mA   |

| C <sub>V5V</sub>                     | External LDO capacitance                       | Application info. Electrical parameters guaranteed from 1.6μF to 2.64μF. Stability down 0.8μF. |      | 2    | 2.64 | μF   |

| T <sub>V5V_SOFT_START</sub>          | Soft start timing                              | From 10% to 90% of V <sub>V5V,</sub> Guaranteed by design                                      |      |      | 200  | μs   |

| V <sub>V5V_UV_TH</sub>               | V5V Undervoltage Threshold                     | Tested in production                                                                           |      |      | 4.75 | V    |

| V <sub>V5V_UV_HYS</sub>              | V5V Undervoltage hysteresis                    | Tested in production                                                                           | 50   |      | 150  | mV   |

| V <sub>V5V_OV_TH</sub>               | V5V Overvoltage Threshold                      | Tested in production                                                                           | 5.4  |      | 6    | V    |

| V <sub>V5V_OV_HYS</sub>              | V5V Overvoltage hysteresis                     | Tested in production                                                                           | 50   |      | 150  | mV   |

| T <sub>V5V_UV_OV_FIL</sub>           | UV/OV filter time                              | Tested by SCAN                                                                                 | 17   |      | 23   | μs   |

| I <sub>TH_OC_V5V</sub>               | V5V overcurrent monitor, threshold current     |                                                                                                | -185 | -145 | -85  | mA   |

| t <sub>FLT_OC_V5V</sub>              | V5V overcurrent monitor, detection filter time | Digital filter                                                                                 | 17   | 20   | 23   | μs   |

## 5.3 Analog BIST

The IC embeds an analog built-in self-test (BIST) to prevent latent failures affecting safety relevant comparators. In CYCLIC\_WAKEUP state the BIST procedure is executed automatically within the diagnostic routine and it covers the following comparators:

- V3V3 OV

- V5V UV

- V5V OV

- GND LOSS

The BIST procedure can be started in NORMAL state by setting GEN\_CFG5.BIST\_ANA\_ENB = 1 in and covers the following comparators:

- VB UV

- V3V3 OV

- V5V UV

- V5V OV

The bit GEN\_STATUS3.BIST\_ANA\_DONE= 1 confirms the correct execution of the BIST procedure.

DS14987 - Rev 1 page 22/62

## 5.3.1 Diagnostic functions

Table 16. Analog BIST diagnostics

| Fault<br>type             | Assertion condition                                                                                                                      | IC reaction to assertion                                                                                                                                                   | Release condition | Maskable                                                                                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog<br>BIST<br>failure | VB_UV or V3V3 OV or V5V UV or V5V OV comparator fail in NORMAL. V3V3 OV or V5V UV or V5V OV or GND LOSS comparator FAIL in CYCLIC_WAKEUP | <ul> <li>BIST_ANA_FAIL = 1 in<br/>GEN_STATUS3</li> <li>The FLT pin and the SPI<br/>FAULT is asserted in<br/>NORMAL if<br/>MSK_BIST_ANA_FAIL = 0 in<br/>GEN_CFG3</li> </ul> | Clear on read     | BIST_ANA_FAIL status bit non maskable FLT pin and SPI FAULT maskable by bit MSK_BIST_ANA_FAIL in GEN_CFG3  BIST_ANA_FAIL status bit non maskable systems. |

### 5.4 Thermal shutdown

The device embeds a thermal sensor and shut-down comparator to protect, in case of short to GND, the following pins:

- V5V pin (see Section 5.2.4)

- WKP driver circuit (see Section 5.9.3).

Thermal shutdown feature is enabled only after V5V regulator has completed the power-up phase.

## **5.4.1** Diagnostic functions

When both thermal shutdown and V5V overcurrent are detected concurrently, V5V regulator is immediately disabled and IC moves to DEEPSLEEP state; after a new successful power-up, the V5V\_OT flag set is still readable to the user, as this bit only is not cleared in DEEPSLEEP mode.

When thermal shutdown is detected concurrently to WKP\_ERR detection (see Section 5.9), a fault is detected and WKP driver is immediately disabled, it can be re-engaged if the fault condition is removed.

Table 17. Thermal shutdown diagnostics

| Fault<br>type | Assertion condition                                                     | IC reaction to assertion                                                                                                             | Release condition                                                                                                      | IC reaction<br>to status<br>bit clear | Maskable                                                                              |

|---------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------|

| TSD           | T <sub>J</sub> >T <sub>TH_TSD_V5V</sub> for t> t <sub>FLT_TSD_V5V</sub> | TSD = 1 in GEN_STATUS3 The FLT pin and the SPI FAULT is asserted in NORMAL if MSK_TSD=0 in GEN_CFG3                                  | Clear on read if T <sub>J</sub> <t<sub>TH_TSD_V5V- T<sub>TH_HYS_TSD_V5V</sub> for t&gt;t<sub>FLT_TSD_V5V</sub></t<sub> |                                       | TSD status bit non maskable FLT pin and SPI FAULT maskable by bit MSK_TSD in GEN_CFG3 |

| V5V OT        | V5V_OC = 1 and<br>TSD = 1                                               | <ul> <li>V5V_OT = 1 in<br/>GEN_STATUS1</li> <li>V5V regulator is<br/>disabled</li> <li>Transition to DEEP<br/>SLEEP state</li> </ul> | Clear on read after successful power-up                                                                                |                                       | Non maskable                                                                          |

DS14987 - Rev 1 page 23/62

| Fault<br>type | Assertion condition        | IC reaction to assertion                                                                                                                                                                    | Release condition                           | IC reaction<br>to status<br>bit clear | Maskable                                                                                 |

|---------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------|

| WKP_OT        | WKP_ERR = 1<br>and TSD = 1 | <ul> <li>WKP driver is disabled</li> <li>WKP_OT = 1 in<br/>GEN_STATUS1</li> <li>The FLT pin and the<br/>SPI FAULT is asserted<br/>in NORMAL if<br/>MSK_WKP_OT =0 in<br/>GEN_CFG3</li> </ul> | Clear on read if fault condition is removed | The driver is reengaged               | TSD status bit non maskable FLT pin and SPI FAULT maskable by bit MSK_WKP_OT in GEN_CFG3 |

### 5.4.2 Electrical parameters

Table 18. Thermal shutdown electrical parameters

| Symbol                       | Parameter                                               | Test conditions      | Min | Тур | Max | Unit |

|------------------------------|---------------------------------------------------------|----------------------|-----|-----|-----|------|

| T <sub>TH_TSD_V5V</sub>      | V5V thermal shut-down, threshold equivalent temperature | Guaranteed by design |     | 165 |     | deg  |

| T <sub>TH_ HYS_TSD_V5V</sub> |                                                         | Guaranteed by design |     | 10  |     | deg  |

| t <sub>FLT_TSD_V5V</sub>     | V5V thermal shut-down, detection filter time            | Digital filter       | 17  | 20  | 23  | μs   |

## 5.5 Ground loss monitor

To detect failures in grounding, the IC integrates a ground loss monitor. Such diagnostic is available on-demand in NORMAL state to cover latent failures. Diagnostic execution is enabled programming GEN\_CGF\_4.EN\_GND\_LOSS = 1.

## 5.5.1 Diagnostic functions

Table 19. Ground loss monitor diagnostics

| Fault<br>type         | Assertion condition                                  | IC reaction to assertion                                                                                                   | Release condition                                                                              | Maskable                                                                                                 |

|-----------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| AGND,<br>DGND<br>LOSS | •  AGND - DGND  > VGND_LOSS_TH for t > TGND_LOSS_FIL | GND_LOSS = 1 in GEN_STATUS1  The FLT pin and the SPI FAULT are asserted in NORMAL if MSK_GND_LOSS = 0 in register GEN_CFG3 | Clear on read if   AGND - DGND  <  V <sub>GND_LOSS_TH</sub> for t  > T <sub>GND_LOSS_FIL</sub> | GND_LOSS status bit non maskable FLT pin and SPI FAULT maskable by bit MSK_GND_LOSS in GEN_CFG3 GND_CFG3 |

## 5.5.2 Electrical parameters

Table 20. Ground loss monitor characteristics

| Symbol                    | Parameter                         | Test conditions      | Min | Тур | Max | Unit | Pin        |

|---------------------------|-----------------------------------|----------------------|-----|-----|-----|------|------------|

| V <sub>GND_LOSS_TH</sub>  | Ground loss detection threshold   | Tested in production | 100 | 200 | 300 | mV   | AGND, DGND |

| T <sub>GND_LOSS_FIL</sub> | Ground loss detection filter time | Tested by SCAN       |     | 300 |     | μs   | AGND, DGND |

## 5.6 Oscillators

Each transceiver channel embeds two oscillators.

A low frequency oscillator operates at  $f_{OSCI\_SLEEP}$  in the following states:

In DEEPSLEEP state it is the time base for wakeup source detection (SPI, VIF)

DS14987 - Rev 1 page 24/62

- In CYCLIC COUNT it is used to feed the CYCLIC WAKEUP timer

- In NORMAL it is used for clock monitoring functionality. A high frequency oscillator operates at f<sub>MAIN\_OSC</sub> and it is active in NORMAL and CYCLIC\_WAKEUP states

## 5.6.1 Diagnostic functions

When in NORMAL or in CYCLIC\_WAKEUP state, the two oscillators monitor each-other to ensure that the frequency is in the allowed range. If the oscillator frequency is not in the correct operating range, the power up and down transitions and related timing may be affected. Any frequency drift can be detected by the oscillator monitor.

The oscillator monitor is covered, for latent fault detection, by BIST at each transition from low power states to NORMAL and CYCLIC\_WAKEUP modes.

| Fault<br>type      | Assertion condition                                                                                | IC reaction to assertion                                                                                                   | Release condition            | Maskable                                                                                                  |

|--------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|

| OSC<br>FAIL        | fosci_sleep -<br>fmain_osc /32  ><br>fosc_mon_err                                                  | OSC_FAIL = 1 in GEN_STATUS1     The FLT pin and the SPI FAULT is asserted in NORMAL if MSK_OSC_FAIL =0 in GEN_CFG3         | Clear on read                | MSK_OSC_FAIL status bit non maskable     FLT pin and SPI FAULT maskable by bit MSK_OSC_FAIL in GEN_CFG3   |

| OSC<br>STUCK       | Tosc_stuck > Tosci_stuck_timeout                                                                   | The device moves in DEEPSLEEP state POR_SLEEP_ASSERTED =1 in GEN_CFG5 Device configurations are restored to default values | -                            | Non maskable                                                                                              |

| OSC<br>MON<br>BIST | During transition to<br>NORMAL and<br>CYCLIC_WAKEUP,<br>if oscillator monitor logic<br>check fails | BIST_OSC_FAIL=1 in GEN_STATUS3 The FLT pin and the SPI FAULT is asserted in NORMAL if MSK_BIST_OSC_FAIL=0 in GEN_CFG3      | Clear on read <sup>(1)</sup> | BIST_OSC_FAIL status bit non maskable FLT pin and SPI FAULT maskable by bit MSK_BIST_OSC_FAIL in GEN_CFG3 |

**Table 21. Oscillator Monitor diagnostics**

#### 5.6.2 Electrical parameters

Table 22. V5V electrical parameters

| Symbol                          | Parameter                            | Test conditions      | Min | Тур | Max | Unit |

|---------------------------------|--------------------------------------|----------------------|-----|-----|-----|------|

| f <sub>OSCI_SLEEP</sub>         | Stand-by oscillator frequency        | Tested in production | -8% | 500 | +8% | kHz  |

| f <sub>MAIN_OSC</sub>           | Oscillator frequency                 | Tested in production | -5% | 16  | +5% | MHz  |

| fosc_mon_err                    | Oscillator delta frequency threshold | Guaranteed by SCAN   | 25  |     | 36  | %    |

| T <sub>OSCI_STUCK_TIMEOUT</sub> | Oscillator stuck detection timeout   | Guaranteed by SCAN   |     | 2   |     | ms   |

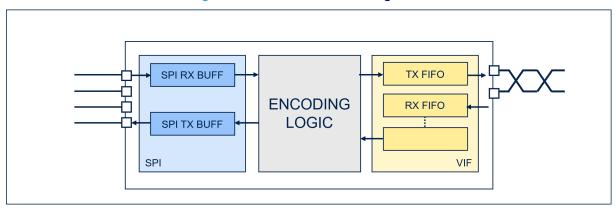

### 5.7 Communication interfaces

The L9965T/TS implements two communication interfaces allowing BMS microcontroller access to internal registers and interaction with all the L9965x chained devices:

- SPI Target, described in Section 5.7.1: used by the controller MCU to access the L9965T/TS device.

- Isolated Vertical Interface (VIF), described in Section 5.7.2: used by L9965T/TS device to communicate with the L9965x devices connected in daisy chain on the VIF bus.

DS14987 - Rev 1 page 25/62

<sup>1.</sup> This flag must be checked at least 12 ms after the power-up.

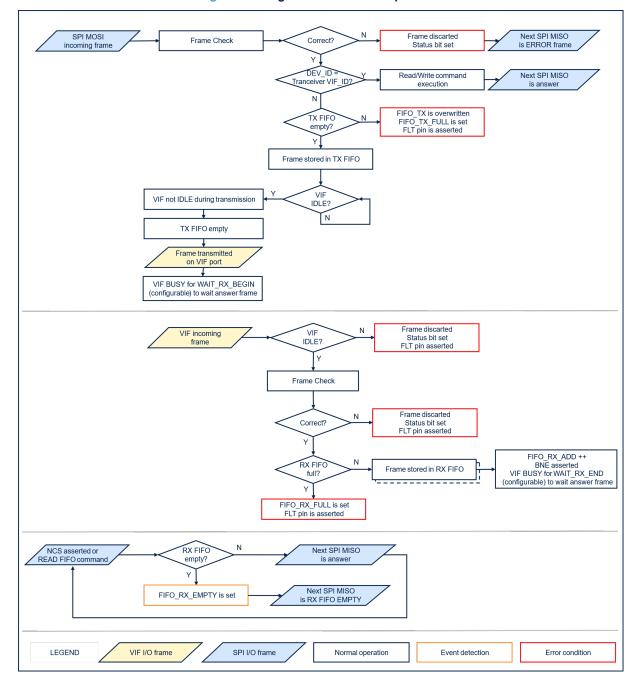

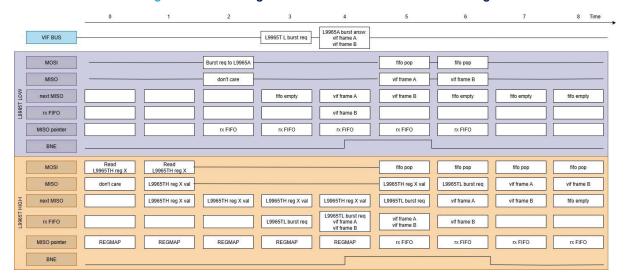

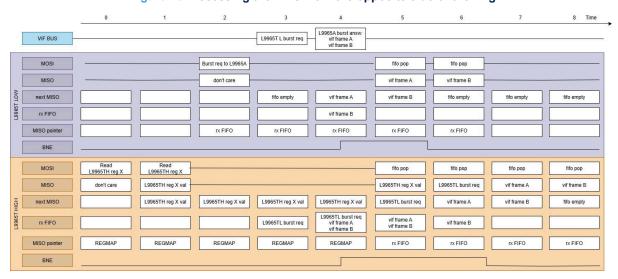

As shown in Figure 9 below, the SPI frame from MCU is temporarily stored in the VIF port TX FIFO (depth 1) to be transmitted to the chained device, while the incoming frames from VIF are stored in the RX FIFO (depth 32), where they can be read by the MCU. For the communication protocol details, see Section 5.8.

Figure 9. SPI - VIF interface management

## 5.7.1 SPI target

The registers of both the L9965T/TS and all the L9965x devices connected by VIF on the daisy chain can be accessed by MCU when devices are in NORMAL state, performing read/write operations on the transceiver through SPI.

SPI port is available for communication only in NORMAL functional state. In DEEPSLEEP, CYCLIC\_COUNT and CYCLIC WAKEUP states only NCS and SCLK pins are active to recognize the wake-up sequence.

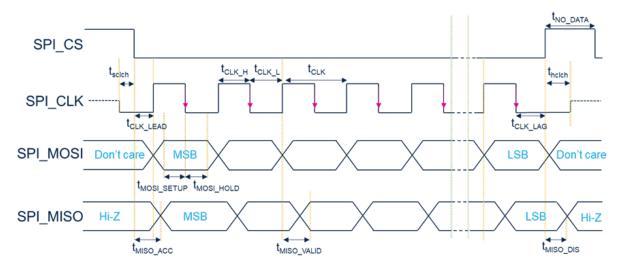

### 5.7.1.1 Physical layer

The SPI target peripheral pins and settings are described below.

Table 23. SPI pins description

| PIN  | Function           | I/O type    | Notes                                           | Active states                                                                          |

|------|--------------------|-------------|-------------------------------------------------|----------------------------------------------------------------------------------------|

| NCS  | Chip Select        | Digital In  | weak pullup R <sub>IN_PU</sub>                  | DEEPSLEEP, CYCLIC_COUNT and CYCLIC_WAKEUP (to recognize the wake-up sequence)  NORMAL  |

| SDI  | Serial Data Input  | Digital In  | weak pulldown R <sub>IN_PD</sub> <sup>(1)</sup> | NORMAL                                                                                 |

| SDO  | Serial Data Output | Digital Out | The output buffer is connected to VIO           | NORMAL                                                                                 |

| SCLK | Serial Clock       | Digital In  | weak pulldown R <sub>IN_PD</sub> a              | DEEP_SLEEP, CYCLIC_COUNT and CYCLIC_WAKEUP (to recognize the wake-up sequence)  NORMAL |

<sup>1.</sup> Weak pull-down resistors on SDI and SCLK pins and weak pull-up on NCS pin are always enabled to address open failures.

Table 24. SPI overview

| Parameter           | Description  |

|---------------------|--------------|

| Protocol            | Out of frame |

| Single frame length | 40 bits      |

| Frame protection    | 6-bit CRC    |

| Max. Frequency      | 10 MHz       |

| CPOL                | 0            |

DS14987 - Rev 1 page 26/62

| Parameter | Description |

|-----------|-------------|

| СРНА      | 1           |

### 5.7.1.2 SPI frame composition

The frame format to send read/write commands to L9965T/TS is shown in the table below.

Table 25. Single Read/Write frame format

|      | 39     | 38         | 37 | 36 | 35  | 34  | 33 | 3, 2 | - c | 2 6  | 28    | 27   | 26   | 25 | 24    | 23 | 22 | 21 | 20 | 19 | 9 | 17 | 16 | 15  | 4   | 13 | 12 | Ξ | 10 | တ | ∞ | 7 | 9 | 2 | 4 | က  | 7 | ~ | 0 |

|------|--------|------------|----|----|-----|-----|----|------|-----|------|-------|------|------|----|-------|----|----|----|----|----|---|----|----|-----|-----|----|----|---|----|---|---|---|---|---|---|----|---|---|---|

| MOSI | PA = 1 | RW         |    | D  | )EV | _ID |    |      |     | ,    | Addr  | ess  |      |    | RSVD  |    |    |    |    |    |   |    | D  | ata | wri | te |    |   |    |   |   |   |   |   |   | CR | С |   |   |

| MISO | PA = 0 | Compressed |    | D  | EV  | _ID |    |      | Ad  | ddre | ess f | eedl | oack | (  | FAULT |    |    |    |    |    |   |    | D  | ata | rea | ad |    |   |    |   |   |   |   |   |   | CR | С |   |   |