## Triple half-bridge gate driver with programmable currents and SPI configuration

## Features

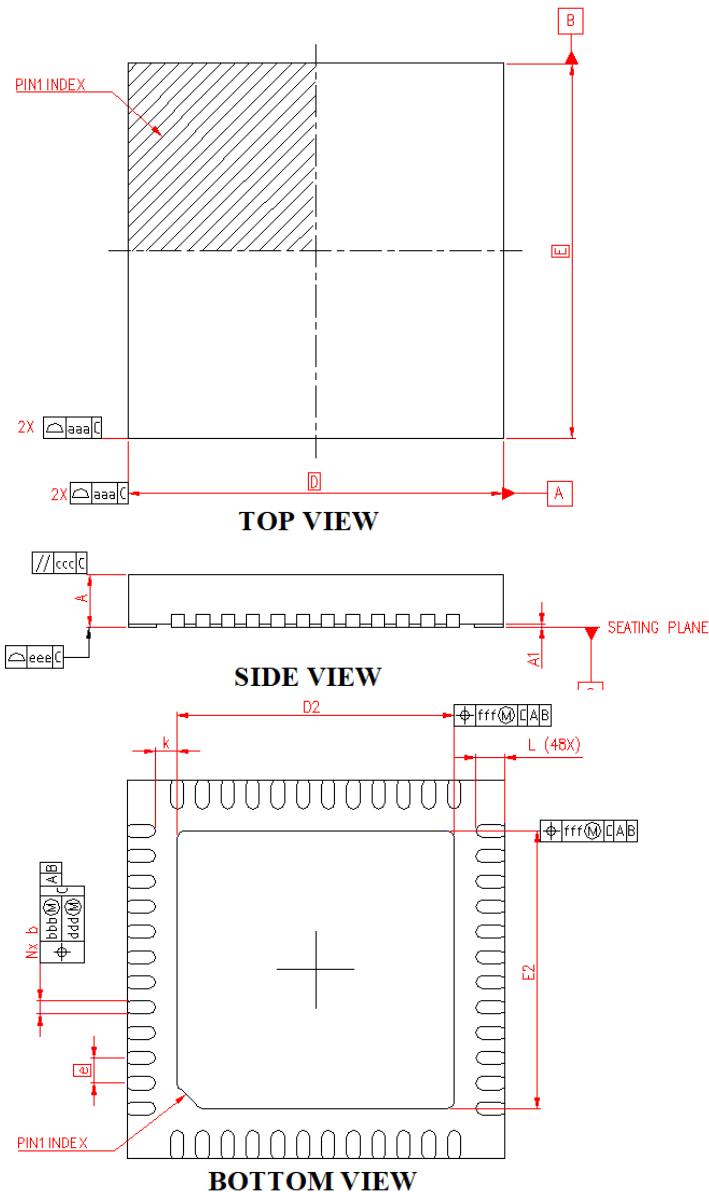

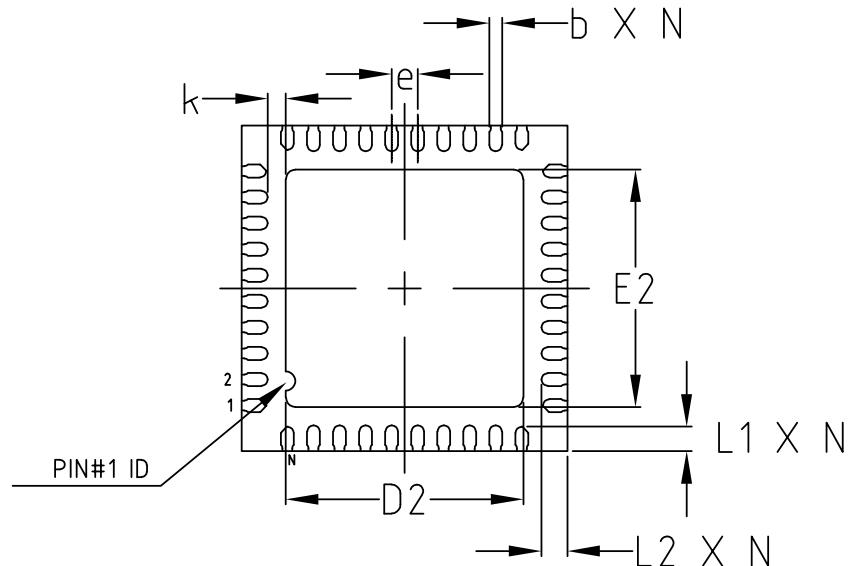

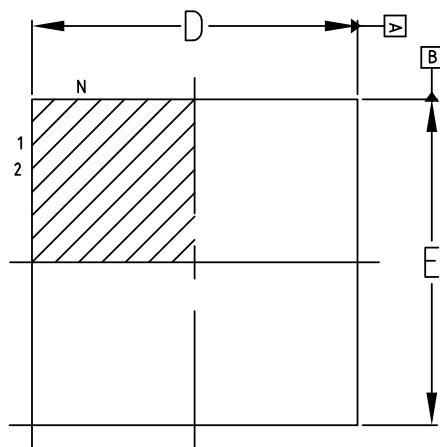

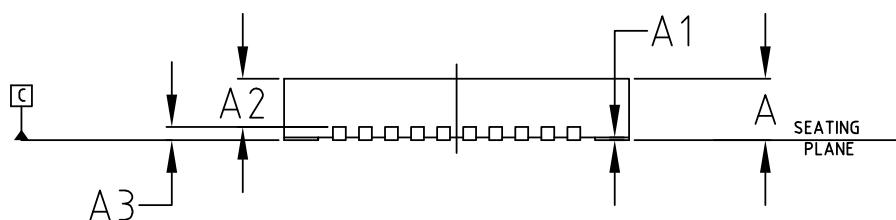

VFQFPN 48L, 6x6x1 mm

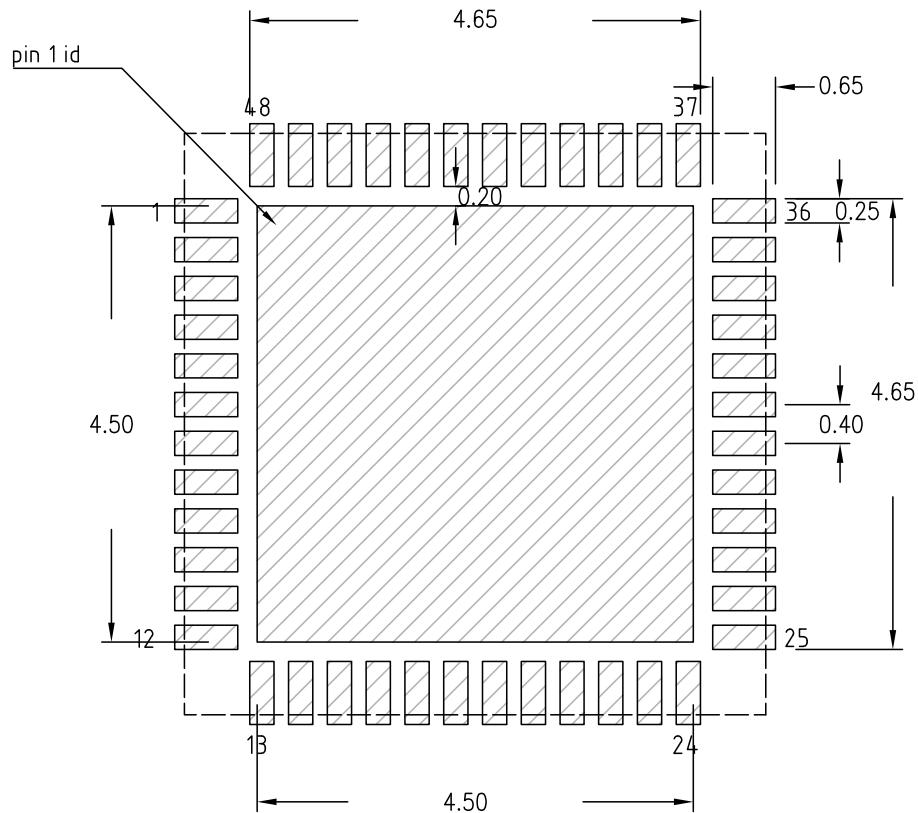

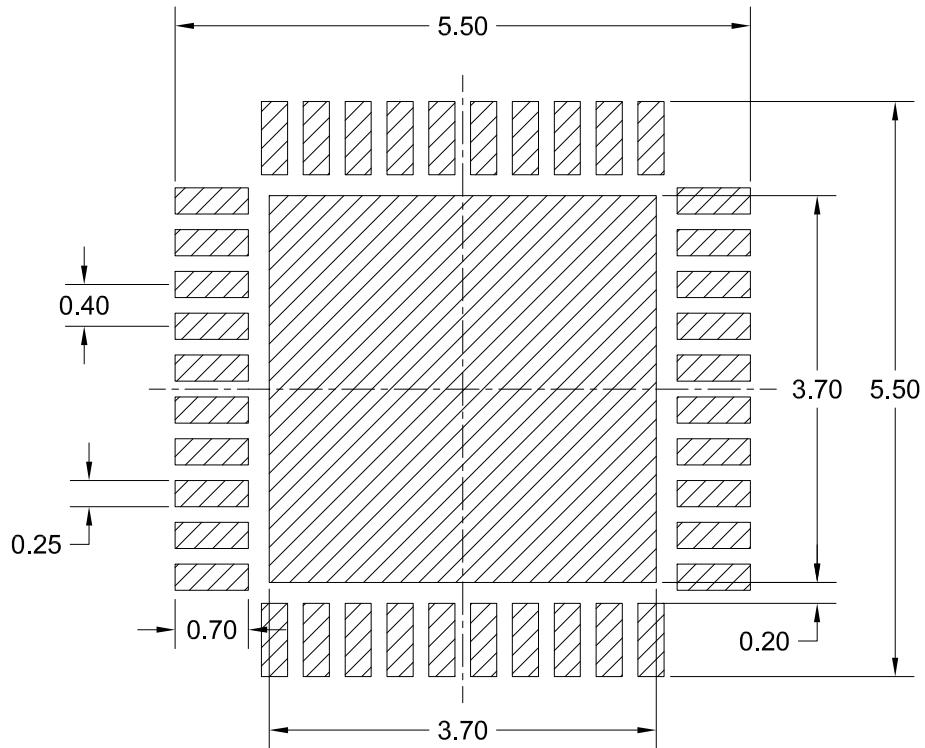

VFQFPN 40L, 5x5x1 mm

- Operating voltage from 6 to 50 V

- Gate drivers with programmable current capability up to:

- 1 A source current

- 2 A sink current

- High robustness against below-ground and overshoot

- Charge pump for 100 % duty cycle operation with dedicated undervoltage lockout protection

- Flexible power management:

- 12 V LDO linear regulator with dedicated undervoltage lockout protection

- 3.3 V LDO linear regulator with dedicated undervoltage lockout protection

- Standby mode for low consumption (less than 50 nA)

- Thermal shutdown protection

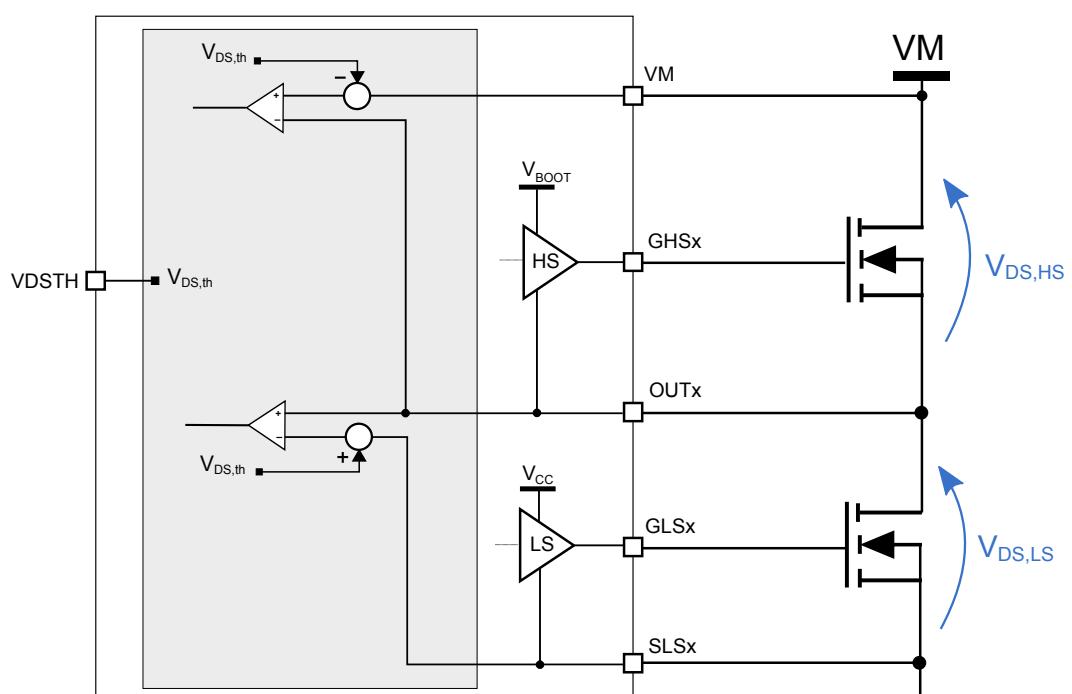

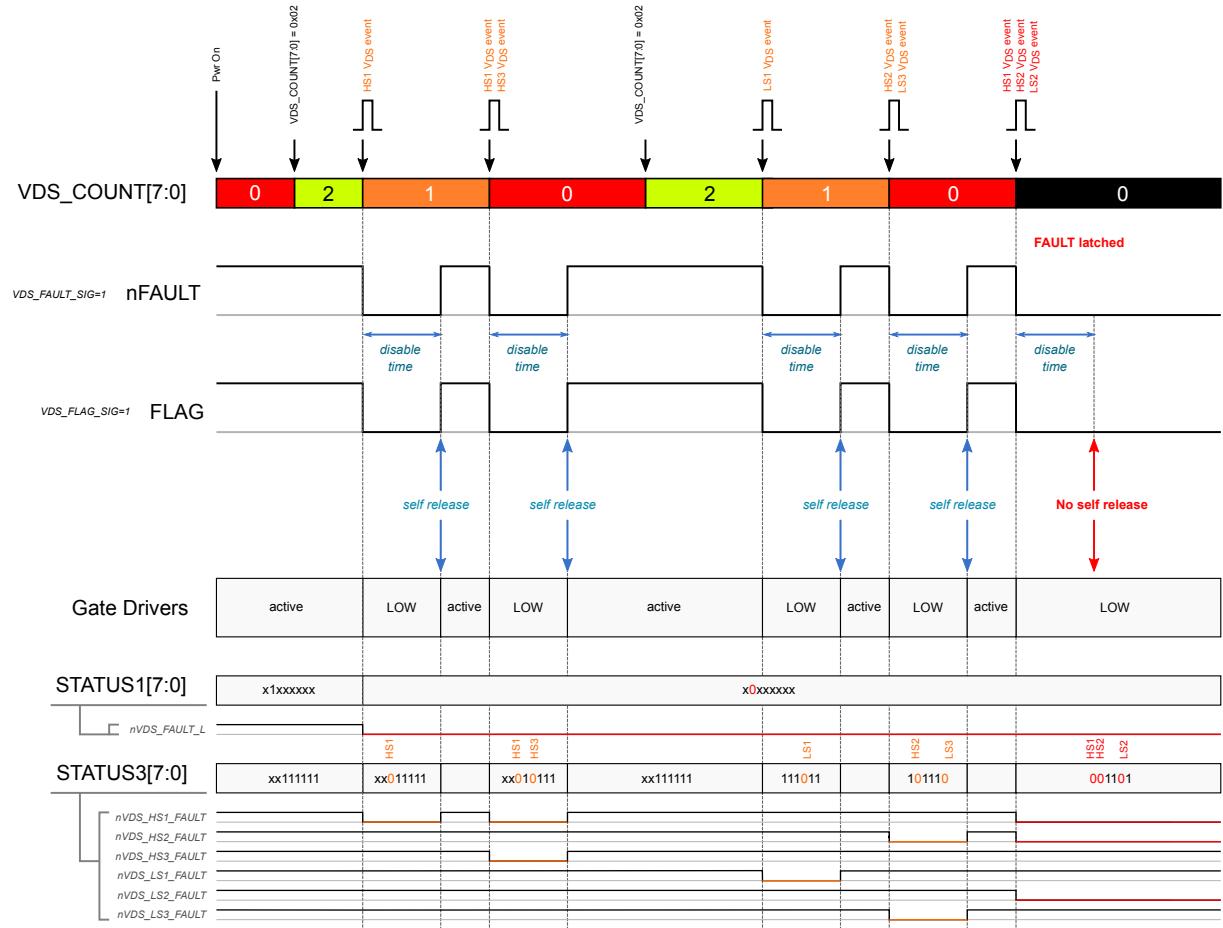

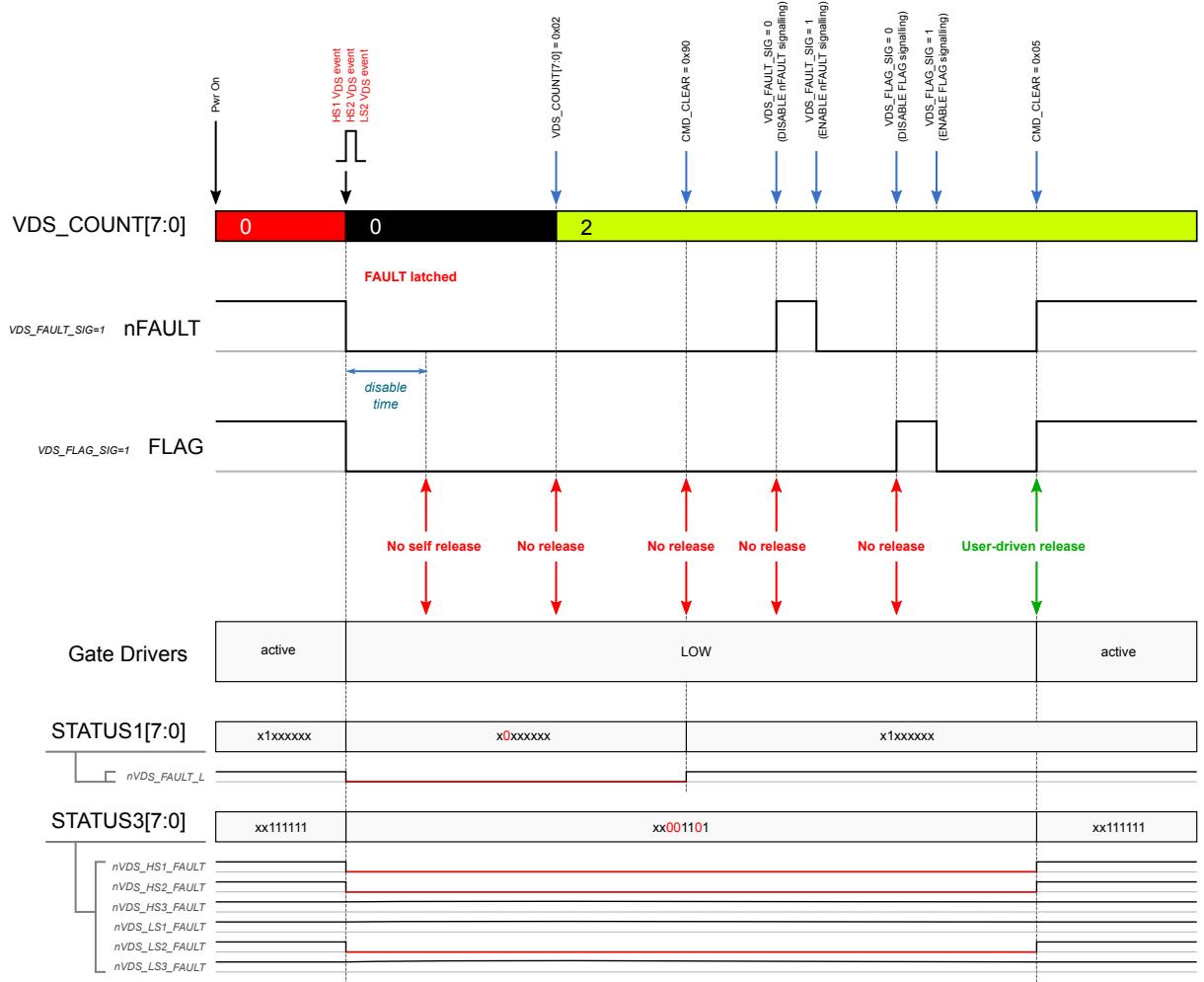

- $V_{DS}$  monitoring for safe driving operation of the power MOSFETs

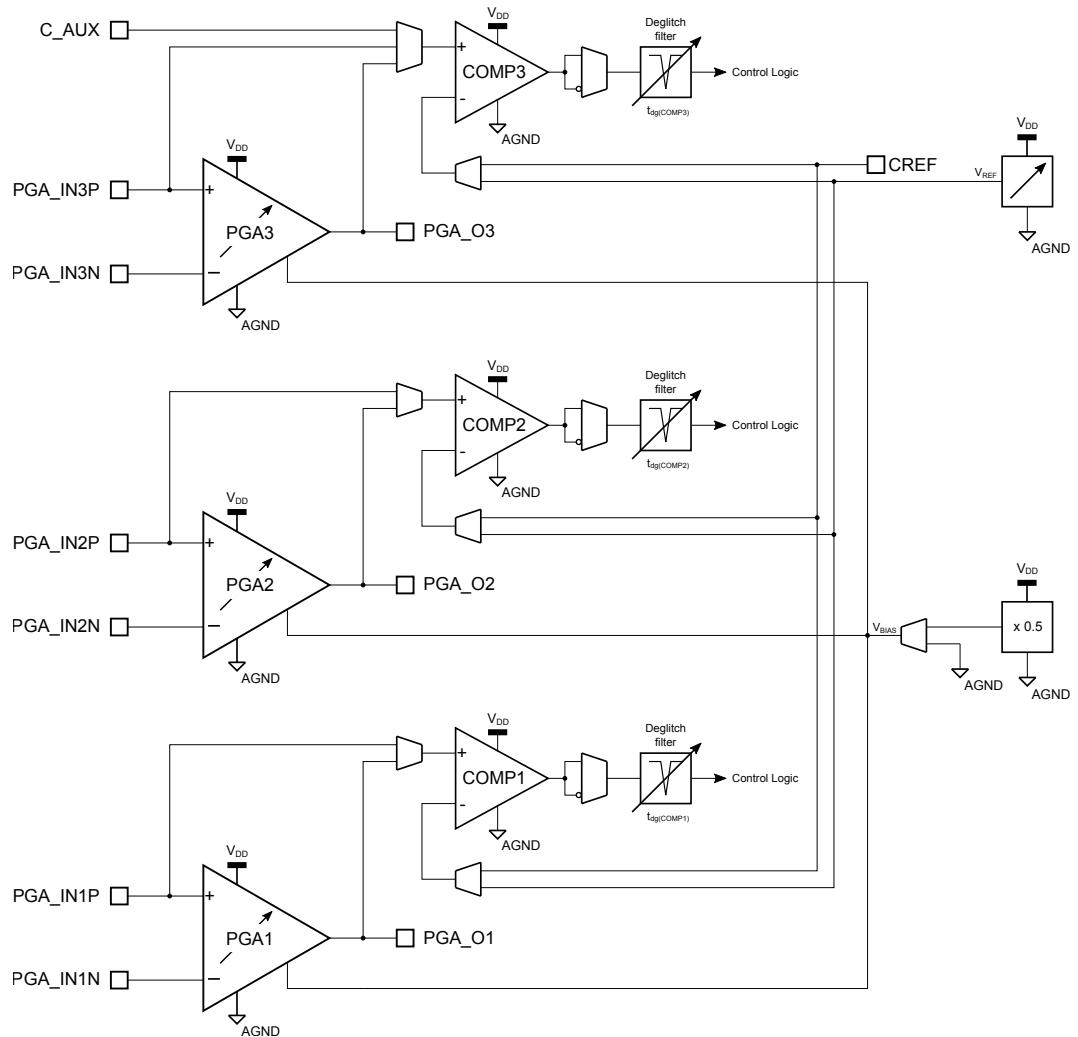

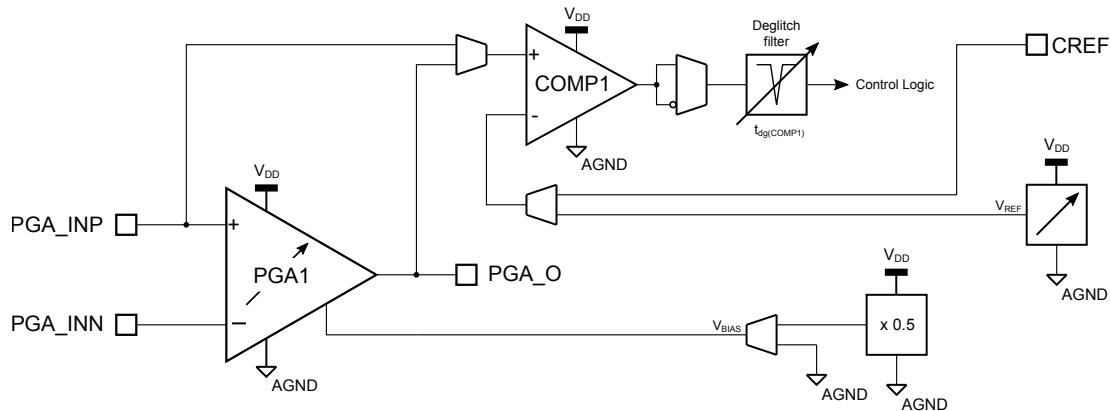

- Flexible analog front-end:

- Up to three programmable-gain amplifiers

- Up to three high-speed comparators

- Dual control modes:

- $ENx/INx$

- $INHx/INLx$  with interlocking

- Matched propagation delay for all channels

- Logic inputs up to 5 V, TTL compatible

- Configurability and diagnostics through SPI

## Product status link

[STDRIVE102BP](#)[STDRIVE102P](#)

## Applications

- Battery-supplied power tools

- Portable vacuum cleaners

- E-bikes

- Industrial automation

- Robotics

- Pumps and fans

## Product label

## Description

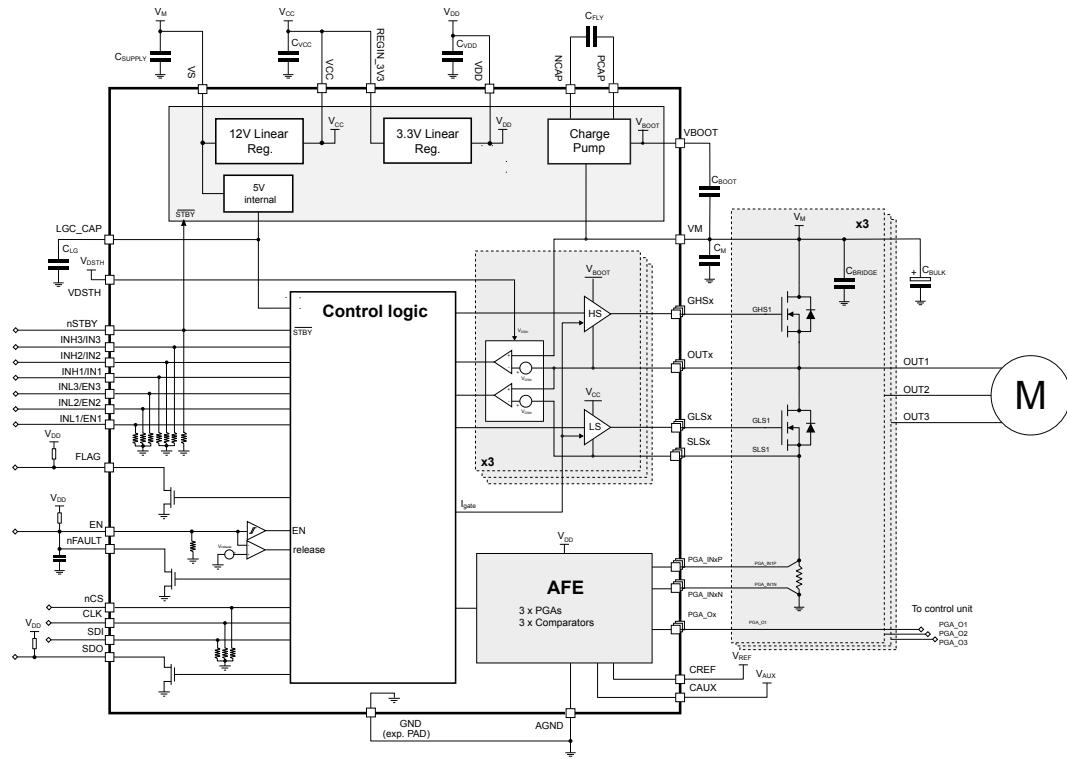

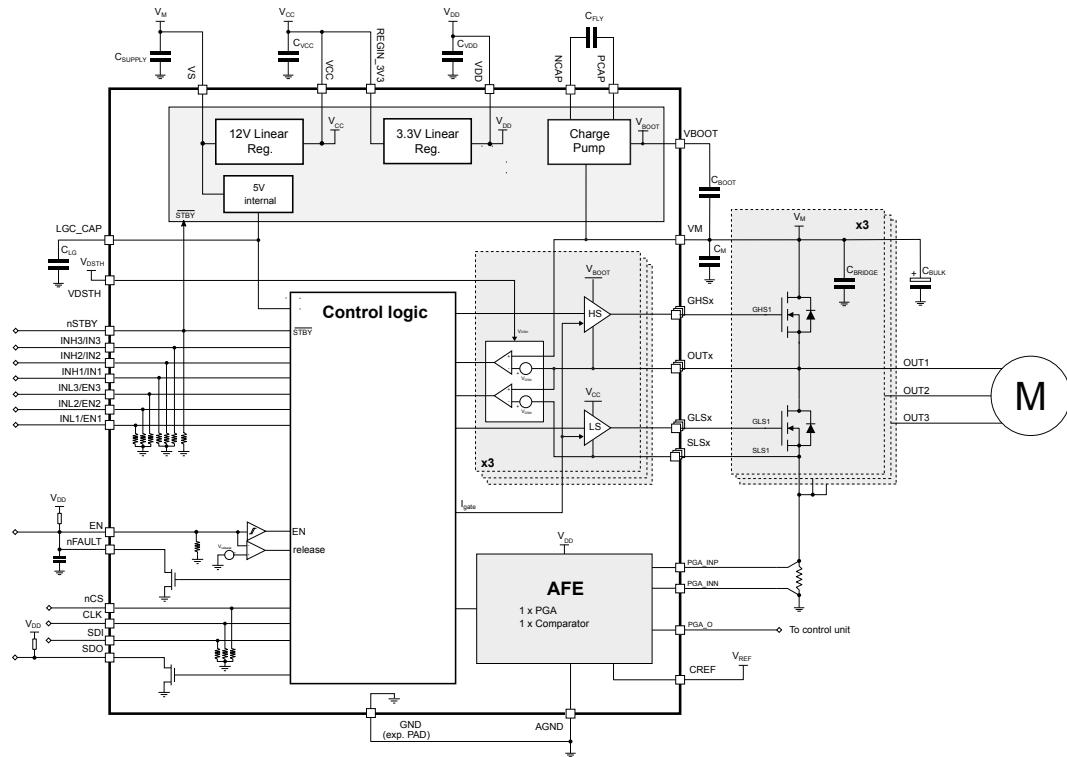

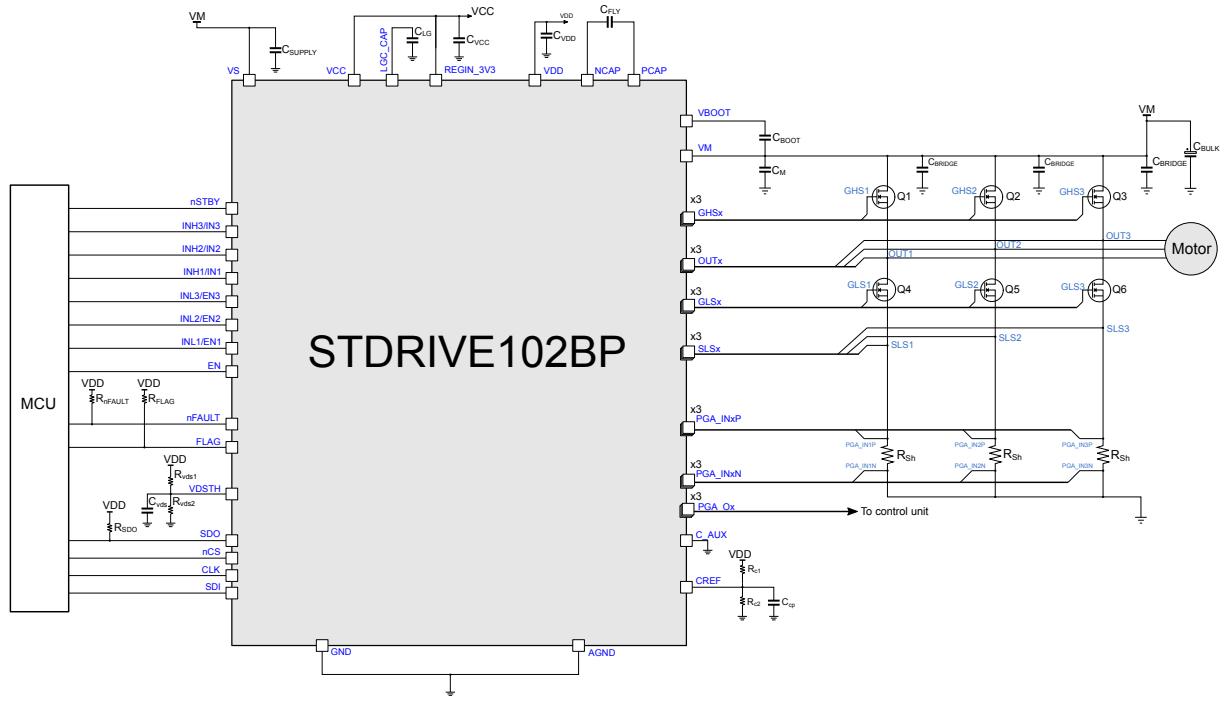

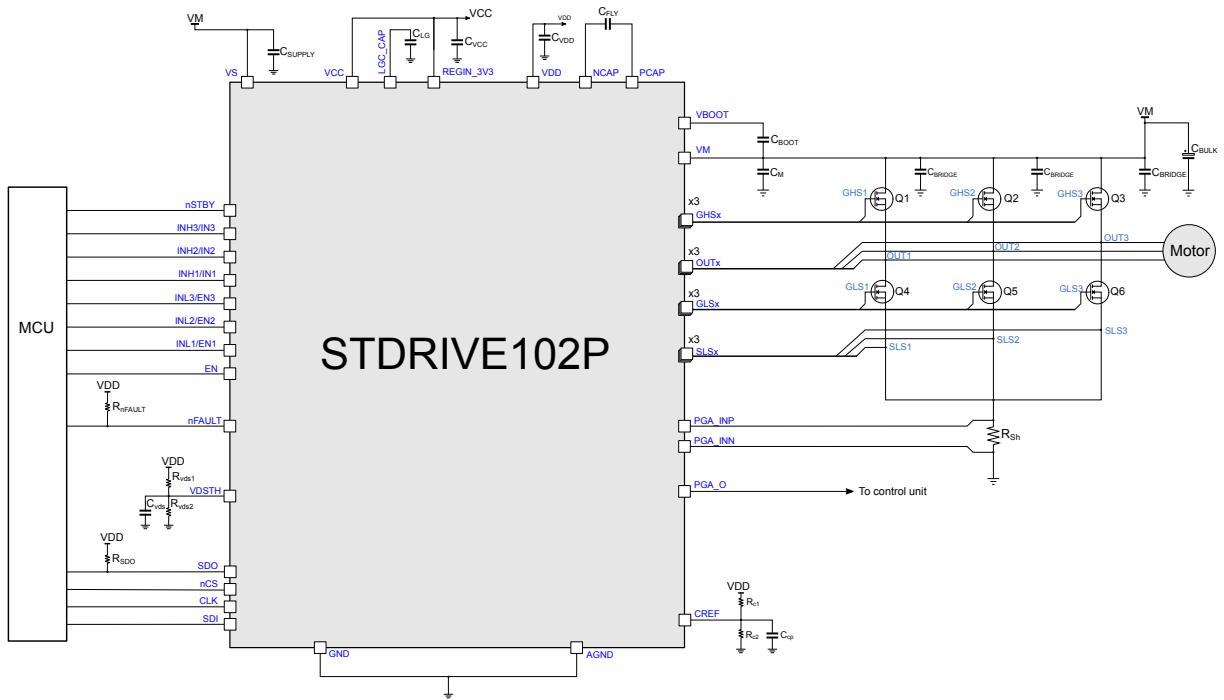

The STDRIVE102BP and the STDRIVE102P are triple half-bridge gate drivers suitable for 3-phase brushless motor driving.

The STDRIVE102BP/P is the optimal solution for battery-supplied motor driver applications such as power tools, vacuum cleaners and small appliances thanks to its very efficient standby mode, which strongly reduces the current consumption when the device is not active.

The gate drivers are designed to drive, with a programmable gate current, six external N-channel power MOSFETs, allowing a superior performance of the power stage and regulating the slew rate of power outputs without the need for external gate resistors. The gate current and the other configurations of the drivers are set through the SPI interface.

An integrated charge pump supplies the three high-side drivers, enabling unlimited on-time of the high-side MOSFETs.

An embedded 12 V LDO linear regulator provides the supply of the three low-side drivers and its output is available on the VCC pin, to also supply external loads.

Another LDO linear regulator provides a 3.3 V on the VDD pin to supply external low-voltage components and the embedded analog front end (AFE), which has a different configuration, depending on the device part number. The STDRIVE102BP integrates three programmable-gain amplifiers (PGAs) and three comparators, while the STDRIVE102P integrates one programmable-gain amplifier and one comparator. In a typical application, the PGAs can be used to amplify the current in each phase of the motor by monitoring the voltage across the shunt resistors on each low-side MOSFET. Concurrently, the comparators can be used to detect dangerous overcurrent conditions.

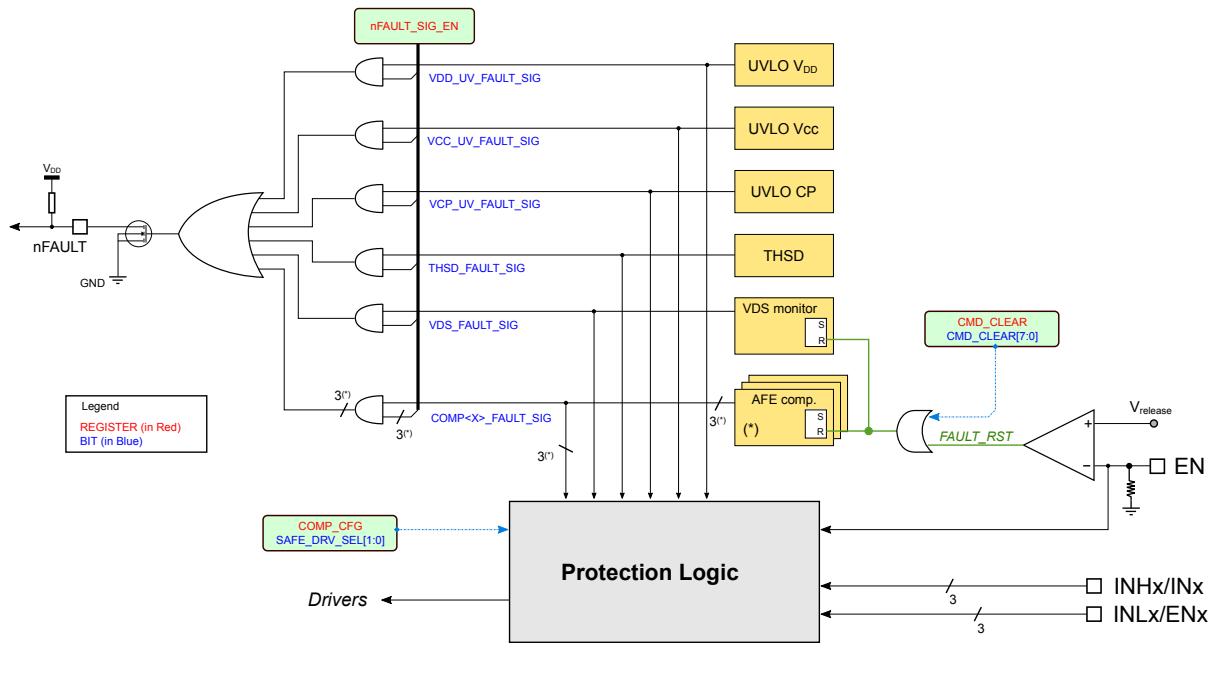

A full set of embedded protections is present to increase the overall application robustness: undervoltage lockout (UVLO) on each supply (VCC, VDD, and charge pump voltage), thermal shutdown, and the  $V_{DS}$  monitoring on both high-side and low-side MOSFETs.

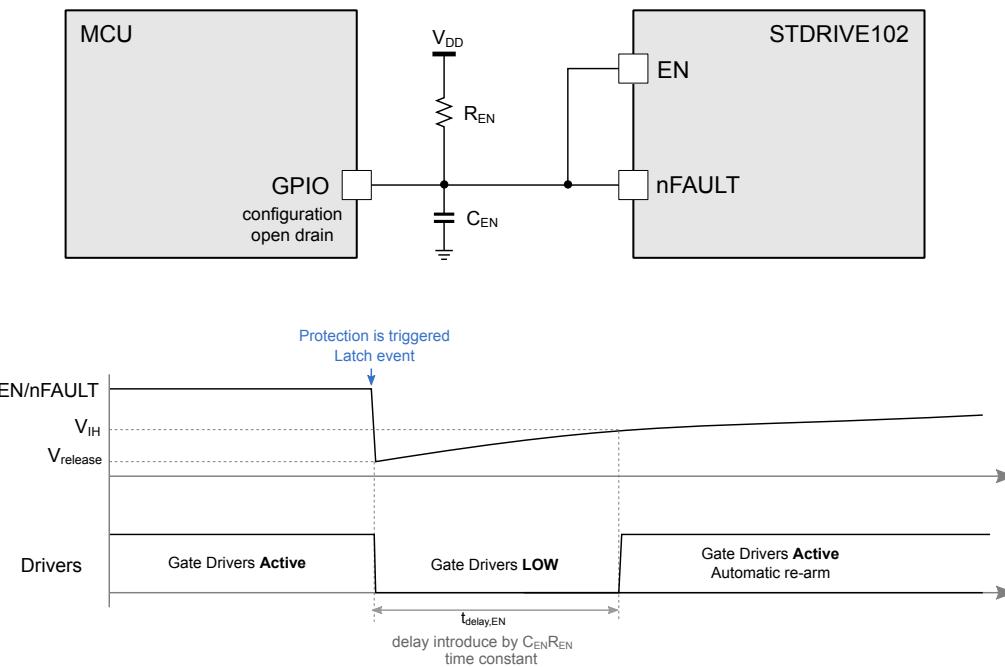

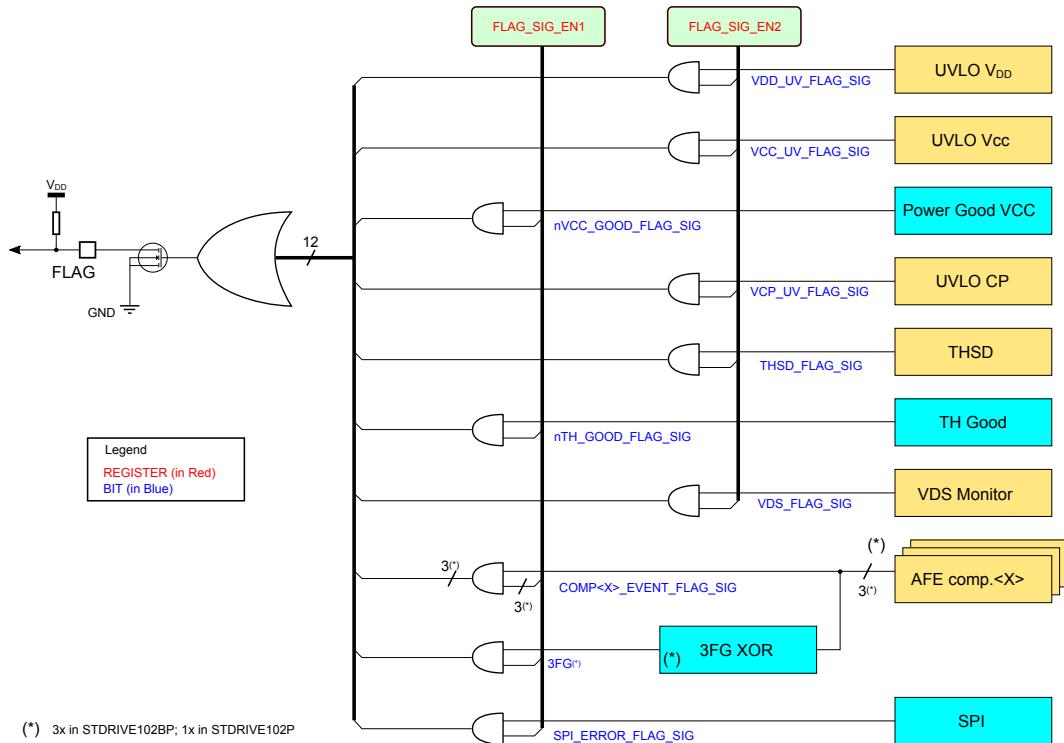

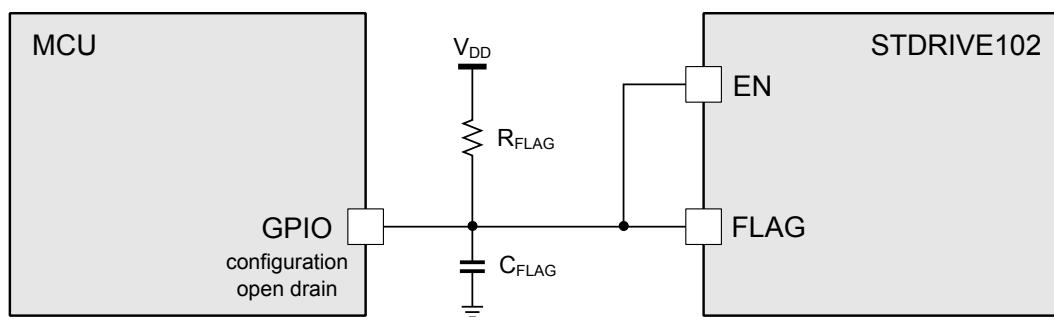

In case a protection is triggered, the nFAULT and FLAG (STDRIVE102PB only) open-drain pins can be configured to signal which specific protection event has been triggered. Both the nFAULT and FLAG pins can be used in combination with the EN pin to implement an automatic rearm after a protection event.

In addition to the main supply pin (VS), the STDRIVE102BP/P has a dedicated pin VM, which should be connected to the motor supply voltage, in correspondence with the drains of the high side N-channel MOSFETs. The VM pin is used for the integrated  $V_{DS}$  monitoring as well as a reference voltage for the charge pump. To increase the device's flexibility, the VS and VM pin can operate at different voltages.

Both STDRIVE102BP and STDRIVE102P provide full configuration and diagnostics through a set of internal registers (accessible via the SPI interface).

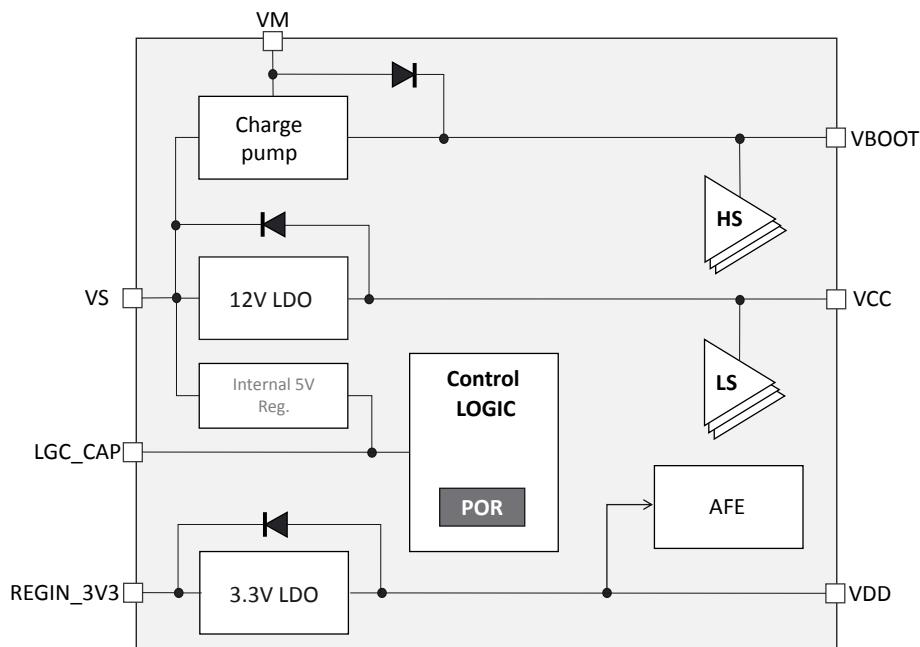

## 1 Block diagram

**Figure 1. STDRIVE102BP block diagram**

**Figure 2. STDRIVE102P block diagram**

## 2 Device ratings

### 2.1 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in [Table 1](#) may cause permanent damage to the device. Exposure to maximum rating conditions for extended periods may affect device reliability.

Two separate reference grounds are present in the device: GND and AGND. All voltages reported in [Table 1](#) are considered with AGND and GND pins shorted, unless otherwise specified.

**Table 1. Absolute maximum ratings**

| Symbol              | Parameter                                                                                                 | Test condition                                                                       | Value                            | Unit |

|---------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|------|

| <b>Power supply</b> |                                                                                                           |                                                                                      |                                  |      |

| $V_M$               | Motor supply voltage                                                                                      |                                                                                      | -0.3 to 55                       | V    |

| $V_S$               | 12 V LDO linear regulator input and main supply                                                           |                                                                                      | -0.3 to 55                       | V    |

| $V_{CC}$            | 12 V LDO linear regulator output and gate drivers supply voltage                                          |                                                                                      | -0.3 to 18                       | V    |

| $V_{REGIN\_3V3}$    | 3.3 V LDO linear regulator input                                                                          |                                                                                      | -0.3 to 18                       | V    |

| $V_{DD}$            | 3.3 V LDO linear regulator output and analog front end supply                                             |                                                                                      | -0.3 to 4                        | V    |

| $V_{NCAP}$          | Charge pump switching capacitor negative side                                                             |                                                                                      | -0.3 to $V_S+0.3$                | V    |

| $V_{PCAP}$          | Charge pump switching capacitor positive side                                                             |                                                                                      | $V_M-0.3$ to $V_{BOOT}+0.3$      | V    |

|                     |                                                                                                           |                                                                                      | 65                               | V    |

| $V_{BOOT}$          | Charge pump output/ high-side boot supply                                                                 |                                                                                      | $V_M-0.3$ to $V_M+18$            | V    |

|                     |                                                                                                           |                                                                                      | 65                               | V    |

| <b>Gate drivers</b> |                                                                                                           |                                                                                      |                                  |      |

| $V_{SLSx}$          | Low-side reference pin voltage                                                                            | DC                                                                                   | -2 to +2                         | V    |

|                     |                                                                                                           | Transient pulse duration 200 ns<br>Repetition frequency 20 kHz <sup>(1)</sup>        | -8 to +8                         | V    |

| $V_{GLSx}$          | Low-side driver output voltage                                                                            |                                                                                      | $V_{SLSx}-0.3$ to $V_{CC}+0.3$   | V    |

| $V_{GS\_LSx}$       | Differential voltage between low-side driver output and its reference ( $V_{GLSx}$ - $V_{SLSx}$ )         |                                                                                      | -0.3 to 18                       | V    |

| $V_{supply\_LS}$    | Supply rail of the low-side driver ( $V_{CC}$ - $V_{SLSx}$ )                                              |                                                                                      | -0.3 to 18                       | V    |

| $V_{OUTx}$          | OUTx pin voltage                                                                                          | DC                                                                                   | -4 to $V_M+4$                    | V    |

|                     |                                                                                                           | Transient pulse duration between 200 ns and 5 $\mu$ s<br>Repetition frequency 20 kHz | -8 to $V_M+8$                    | V    |

|                     |                                                                                                           | Transient pulse duration 200 ns<br>Repetition frequency 20 kHz                       | -10 to $V_M+10$                  | V    |

| $V_{GHSx}$          | High-side driver output                                                                                   |                                                                                      | $V_{OUTx}-0.3$ to $V_{BOOT}+0.3$ | V    |

| $V_{GO\_HSx}$       | Differential voltage between high-side gate driver's output and its reference ( $V_{GHSx}$ - $V_{OUTx}$ ) | (2)                                                                                  | -0.3 to 16                       | V    |

| Symbol                             | Parameter                                                             | Test condition                                                 | Value                  | Unit |

|------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|------------------------|------|

| $V_{BO,x}$                         | Supply rail of the high-side driver ( $V_{BOOT} - V_{OUTx}$ )         |                                                                | -0.3 to 65             | V    |

| <b>Analog pins and digital I/O</b> |                                                                       |                                                                |                        |      |

| $V_{IO}$                           | Logic I/O voltage (INHx/INx, INLx/ENx, nSTBY, EN, SDI, nCS, CLK pins) |                                                                | -0.3 to 5.5            | V    |

| $V_{DSTH}$                         | VDSTH analog input pin voltage                                        |                                                                | -0.3 to 5.5            | V    |

| $V_{OD}$                           | Open-drain pins voltage (nFAULT, FLAG, SDO)                           |                                                                | -0.3 to 5.5            | V    |

| $V_{C\_AUX}$                       | C_AUX input                                                           |                                                                | -0.3 to $V_{DD} + 0.3$ | V    |

| $V_{CREF}$                         | CREF input                                                            |                                                                | -0.3 to $V_{DD} + 0.3$ | V    |

| $V_{PGA\_INxP}$                    | PGAs positive inputs                                                  | DC                                                             | -2 to $V_{DD} + 0.3$   | V    |

|                                    |                                                                       | Transient pulse duration 200 ns<br>Repetition frequency 20 kHz | -8 to 8                | V    |

| $V_{PGA\_INxN}$                    | PGAs negative inputs                                                  | DC                                                             | -0.4 to $V_{DD} + 0.3$ | V    |

|                                    |                                                                       | Transient pulse duration 200 ns<br>Repetition frequency 20 kHz | -2 to $V_{DD} + 0.3$   |      |

| $V_{PGA\_Ox}$                      | PGAs outputs                                                          |                                                                | -0.3 to $V_{DD} + 0.3$ | V    |

| <b>Temperature</b>                 |                                                                       |                                                                |                        |      |

| $T_{stg}$                          | Storage temperature                                                   |                                                                | -55 to 150             | °C   |

| $T_j$                              | Junction temperature                                                  |                                                                | -40 to 150             | °C   |

| <b>Reference grounds</b>           |                                                                       |                                                                |                        |      |

| $\Delta V_{GND}$                   | GND misalignment                                                      | AGND with respect to GND (exposed pad)                         | -0.3 to 0.3            | V    |

1.  $V_{supply\_LS}$  AMR must be also considered.

2. Limit to avoid  $V_{GS}$  clamp turn-on.

## 2.2

### Recommended operating conditions

All voltages must be considered with AGND and GND pins shorted.

**Table 2. Recommended operating conditions**

| Symbol     | Parameter                                  | Test condition                            | Min.           | Typ. | Max. | Unit |

|------------|--------------------------------------------|-------------------------------------------|----------------|------|------|------|

| $V_M$      | Motor supply voltage                       |                                           | 6              |      | 50   | V    |

| $V_S$      | 12 V LDO linear regulator input            | (1)                                       | $V_{CC}$       |      | 50   | V    |

| $V_{CC}$   | VCC gate driver supply voltage             | VCC supplied by internal linear regulator |                | 12   |      | V    |

|            |                                            | VS shorted to VCC and externally supplied | 6              |      | 15   | V    |

| $I_{CC}$   | 12 V linear regulator output current       | (1) (2)                                   |                |      | 50   | mA   |

| $C_{VCC}$  | 12 V LDO linear regulator output capacitor | (3)                                       |                | 4.7  |      | μF   |

| $V_{BOOT}$ | Charge pump output voltage                 |                                           | $V_M + V_{CC}$ |      |      | V    |

| $I_{BOOT}$ | Charge pump current                        | (2)                                       |                |      | 35   | mA   |

| Symbol           | Parameter                                                               | Test condition                                   | Min.     | Typ. | Max.     | Unit      |

|------------------|-------------------------------------------------------------------------|--------------------------------------------------|----------|------|----------|-----------|

| $V_{REGIN\_3V3}$ | 3.3 V LDO linear regulator input                                        |                                                  | $V_{DD}$ |      | 15       | V         |

| $V_{DD}$         | 3.3 V LDO linear regulator output                                       | VDD supplied by internal linear regulator        |          | 3.3  |          | V         |

|                  |                                                                         | REGIN_3V3 shorted to VDD and externally supplied | 3.1      | 3.3  | 3.6      | V         |

| $I_{DD}$         | 3.3 V LDO linear regulator output current                               | (1) (2)                                          |          |      | 30       | mA        |

| $C_{VDD}$        | 3.3 V output capacitor                                                  | (3)                                              |          | 4.7  |          | $\mu$ F   |

| $C_{LG}$         | Output capacitor for internal logic supply regulator (LGC_CAP pin)      | (3)                                              |          | 4.7  |          | $\mu$ F   |

| $dV_{OUTx}/dt$   | OUTx slew rate                                                          |                                                  |          |      | 2.5      | V/ns      |

| $V_{IN,logic}$   | Logic input voltage (INHx/INx, INLx/ENx, nSTBY, EN, SDI, nCS, CLK pins) | (4)                                              | 0        |      | 5        | V         |

| $V_{OD}$         | nFAULT, FLAG, SDO pins pull-up voltage                                  | (4)                                              | 0        |      | 5        | V         |

| $I_{OD}$         | nFAULT, FLAG, SDO pins sink current                                     |                                                  |          |      | 8        | mA        |

| $V_{DSTH}$       | $V_{DS}$ monitoring reference voltage                                   | Protection enabled                               | 0.05     |      | 2        | V         |

|                  |                                                                         | Protection disabled                              | 3        |      | 3.3      | V         |

| $V_{SLSx}$       | LSx driver sense pin                                                    |                                                  | -1       |      | +1       | V         |

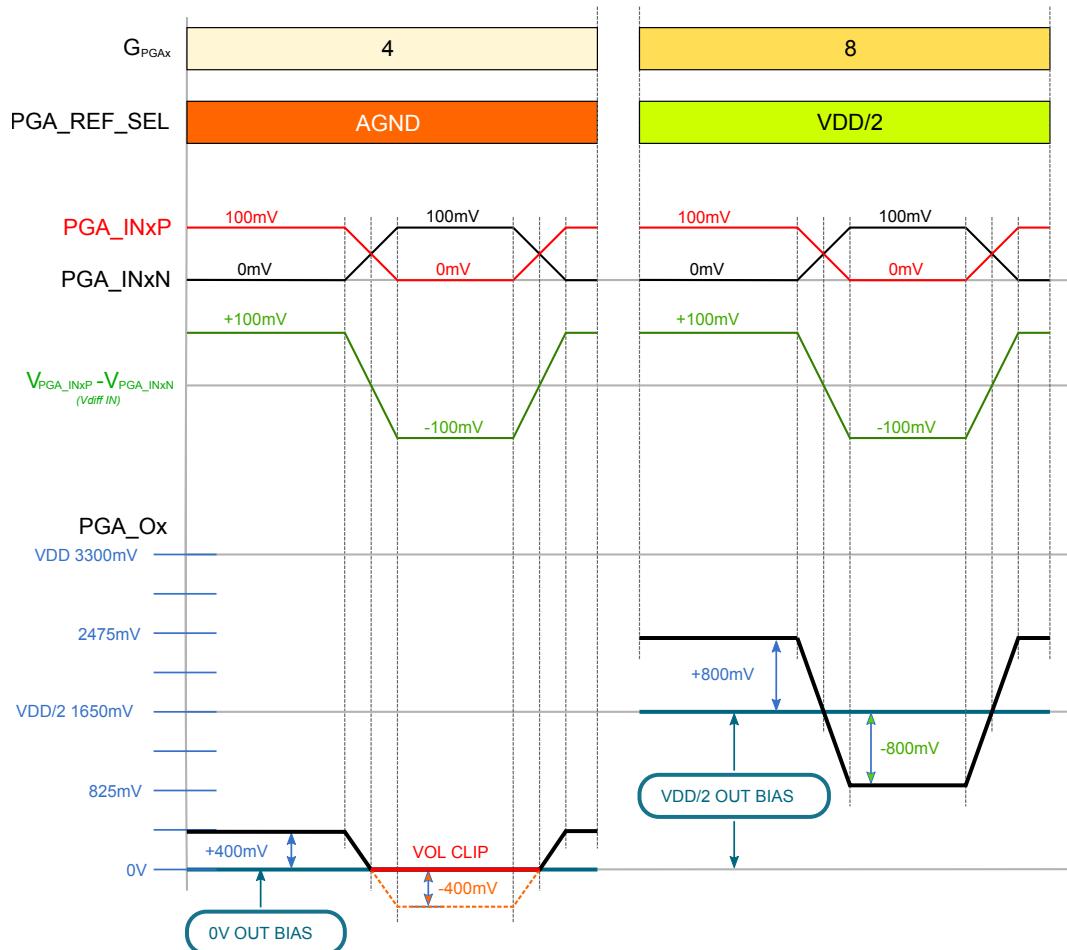

| $V_{PGA\_INxP}$  | PGAs positive inputs                                                    | PGAx_GAIN[1:0] = 00 ( $G_{PGA} = 4$ )            | -0.66    |      | $V_{DD}$ | V         |

|                  |                                                                         | PGAx_GAIN[1:0] = 01 ( $G_{PGA} = 8$ )            | -0.43    |      | $V_{DD}$ | V         |

|                  |                                                                         | PGAx_GAIN[1:0] = 10 ( $G_{PGA} = 16$ )           | -0.31    |      | $V_{DD}$ | V         |

|                  |                                                                         | PGAx_GAIN[1:0] = 11 ( $G_{PGA} = 32$ )           | -0.245   |      | $V_{DD}$ | V         |

| $V_{PGA\_INxN}$  | PGAs negative inputs                                                    | PGAx_GAIN[1:0] = 00 ( $G_{PGA} = 4$ )            | -0.3     |      | $V_{DD}$ | V         |

|                  |                                                                         | PGAx_GAIN[1:0] = 01 ( $G_{PGA} = 8$ )            | -0.25    |      | $V_{DD}$ | V         |

|                  |                                                                         | PGAx_GAIN[1:0] = 10 ( $G_{PGA} = 16$ )           | -0.22    |      | $V_{DD}$ | V         |

|                  |                                                                         | PGAx_GAIN[1:0] = 11 ( $G_{PGA} = 32$ )           | -0.2     |      | $V_{DD}$ | V         |

| $R_{eqL,out}$    | Equivalent load resistor connected to the PGA output (PGA_Ox)           | Resistor to AGND or to VDD                       | 1        |      |          | $k\Omega$ |

| $V_{C\_AUX}$     | Comparator 3 auxiliary input (C_AUX pin)                                |                                                  | 0        |      | $V_{DD}$ | V         |

| $V_{CREF}$       | CREF input                                                              |                                                  | 0        |      | $V_{DD}$ | V         |

| $T_{amb}$        | Operative ambient temperature                                           | (1)                                              | -40      |      | 85       | °C        |

1. Actual operative range can be limited by thermal shutdown.

2. Consumption of internal circuitry included.

3. An additional 100 nF low-ESR bypass capacitor could be added to improve the noise immunity.

4. All digital inputs are compliant with TTL/CMOS thresholds and 5 V tolerant. They can be biased within the respective AMR whatever the supply condition of the device (supplied, floating, or shorted to ground) without damaging the device.

## 2.3 Thermal data

Thermal values are calculated by simulation.

**Table 3. STDRIVE102BP thermal data (VFQFPN 48L, 6x6x1 mm)**

| Symbol        | Parameter                                         | Test condition                                    | Value | Unit |

|---------------|---------------------------------------------------|---------------------------------------------------|-------|------|

| $R_{thJA}$    | Junction-to-ambient thermal resistance            | Natural convection according to JESD51-2a         | 32.1  | °C/W |

| $R_{thJCTop}$ | Junction-to-case thermal resistance (top side)    | Cold plate on top, according to JESD51-12         | 15.8  | °C/W |

| $R_{thJCbot}$ | Junction-to-case thermal resistance (bottom side) | Cold plate on exposed pad, according to JESD51-12 | 3.4   | °C/W |

| $R_{thJB}$    | Junction-to-board thermal resistance              | According to JESD51-8                             | 15.3  | °C/W |

| $\Psi_{JT}$   | Junction-to-top characterization parameter        | According to JESD51-2a                            | 0.1   | °C/W |

| $\Psi_{JB}$   | Junction-to-board characterization parameter      | According to JESD51-2a                            | 15    | °C/W |

**Table 4. STDRIVE102P thermal data (VFQFPN 40L, 5x5x1 mm)**

| Symbol        | Parameter                                         | Test condition                                    | Value | Unit |

|---------------|---------------------------------------------------|---------------------------------------------------|-------|------|

| $R_{thJA}$    | Junction-to-ambient thermal resistance            | Natural convection according to JESD51-2a         | 36.3  | °C/W |

| $R_{thJCTop}$ | Junction-to-case thermal resistance (top side)    | Cold plate on top, according to JESD51-12         | 19.5  | °C/W |

| $R_{thJCbot}$ | Junction-to-case thermal resistance (bottom side) | Cold plate on exposed pad, according to JESD51-12 | 4.0   | °C/W |

| $R_{thJB}$    | Junction-to-board thermal resistance              | According to JESD51-8                             | 18.0  | °C/W |

| $\Psi_{JT}$   | Junction-to-top characterization parameter        | According to JESD51-2a                            | 0.1   | °C/W |

| $\Psi_{JB}$   | Junction-to-board characterization parameter      | According to JESD51-2a                            | 17.7  | °C/W |

## 2.4 Electrical sensitivity characteristics

**Table 5. ESD protection ratings**

| Symbol | Parameter           | Test condition                            | Class | Value | Unit |

|--------|---------------------|-------------------------------------------|-------|-------|------|

| HBM    | Human Body Model    | Conforming to ANSI/ESDA/JEDEC JS-001-2017 | 2     | 2000  | V    |

| CDM    | Charge Device Model | Conforming to ANSI/ESDA/JEDEC JS-002-2018 | C3    | 1000  | V    |

### 3 Electrical characteristics

Testing conditions:  $V_M = 24$  V,  $V_S = 12$  V,  $V_{CC} = 12$  V,  $V_{REGIN\_3V3} = 3.3$  V,  $V_{DD} = 3.3$  V,  $V_{DSTH} = 3.3$  V. All gate drivers LOW (sinking current) unless otherwise specified.

Typical values are tested at  $T_j = 25^\circ\text{C}$ . Minimum and maximum values are guaranteed by thermal characterization over the temperature range of -40 to  $125^\circ\text{C}$ , unless otherwise specified.

**Table 6. Electrical characteristics**

| Symbol                            | Parameter                                     | Test condition                              | Min.  | Typ. | Max.  | Unit |

|-----------------------------------|-----------------------------------------------|---------------------------------------------|-------|------|-------|------|

| <b>Supply and UVLO protection</b> |                                               |                                             |       |      |       |      |

| $V_{CC(On)}$                      | $V_{CC}$ UVLO turn-on threshold               | $V_{CC}$ rising, UV_SEL = 1                 |       | 7.8  | 8.1   | V    |

|                                   |                                               | $V_{CC}$ rising, UV_SEL = 0                 |       | 5.5  | 5.8   | V    |

| $V_{CC(Hyst)}$                    | $V_{CC}$ UVLO hysteresis                      | $V_{CC}$ falling, UV_SEL = 1                |       | 0.25 |       | V    |

|                                   |                                               | $V_{CC}$ falling, UV_SEL = 0                |       | 0.25 |       | V    |

| $V_{CC(Off)}$                     | $V_{CC}$ UVLO turn-off threshold              | $V_{CC}$ falling, UV_SEL = 1                | 7.2   | 7.55 |       | V    |

|                                   |                                               | $V_{CC}$ falling, UV_SEL = 0                | 5.0   | 5.25 |       | V    |

| $V_{P\_GOOD(On)}$                 | $V_{CC}$ power-good warning release threshold | $V_{CC}$ rising, VCC_GOOD_SEL = 1           |       | 9.65 |       | V    |

|                                   |                                               | $V_{CC}$ rising, VCC_GOOD_SEL = 0           |       | 7.75 |       | V    |

| $V_{P\_GOOD(Hyst)}$               | $V_{CC}$ power-good warning hysteresis        | $V_{CC}$ falling, VCC_GOOD_SEL = 1          |       | 0.35 |       | V    |

|                                   |                                               | $V_{CC}$ falling, VCC_GOOD_SEL = 0          |       | 0.25 |       | V    |

| $V_{P\_GOOD(Off)}$                | $V_{CC}$ power-good warning threshold         | $V_{CC}$ falling, VCC_GOOD_SEL = 1          |       | 9.3  |       | V    |

|                                   |                                               | $V_{CC}$ falling, VCC_GOOD_SEL = 0          |       | 7.5  |       | V    |

| $V_{CPump(On)}$                   | $V_{BOOT} - V_M$ UVLO turn-on threshold       | ' $V_{BOOT} - V_M$ ' rising, UV_SEL = 1     |       | 7.3  | 8.5   | V    |

|                                   |                                               | ' $V_{BOOT} - V_M$ ' rising, UV_SEL = 0     |       | 4.5  | 5.2   | V    |

| $V_{CPump(Hyst)}$                 | $V_{BOOT} - V_M$ UVLO hysteresis              | ' $V_{BOOT} - V_M$ ' falling, UV_SEL = 1    |       | 0.3  |       | V    |

|                                   |                                               | ' $V_{BOOT} - V_M$ ' falling, UV_SEL = 0    |       | 0.2  |       | V    |

| $V_{CPump(Off)}$                  | $V_{BOOT} - V_M$ UVLO turn-off threshold      | ' $V_{BOOT} - V_M$ ' falling, UV_SEL = 1    | 5.9   | 7    |       | V    |

|                                   |                                               | ' $V_{BOOT} - V_M$ ' falling, UV_SEL = 0    | 3.6   | 4.3  |       | V    |

| $V_{DD(On)}$                      | $V_{DD}$ UVLO turn-on threshold               | $V_{DD}$ rising                             |       | 2.6  | 2.9   | V    |

| $V_{DD(Hyst)}$                    | $V_{DD}$ UVLO hysteresis                      | $V_{DD}$ falling                            |       | 0.2  |       | V    |

| $V_{DD(Off)}$                     | $V_{DD}$ UVLO turn-off threshold              | $V_{DD}$ falling                            | 2.2   | 2.4  |       | V    |

| $I_{STBY}$                        | Standby current consumption                   | $V_S = 50$ V, $T_j = 25^\circ\text{C}$      |       |      | 50    | nA   |

| <b>12 V LDO linear regulator</b>  |                                               |                                             |       |      |       |      |

| $V_{CC}$                          | 12 V linear regulator output                  | $V_S = 15$ V, $I_{CC} = 40$ mA              | 11.45 | 12   | 12.55 | V    |

| $I_{CC,lim}$                      | 12 V linear regulator current limiter         | $V_{CC}$ shorted to AGND                    | 55    | 85   | 115   | mA   |

| <b>3.3 V LDO linear regulator</b> |                                               |                                             |       |      |       |      |

| $V_{DD}$                          | 3.3 V linear regulator output                 | $V_{REGIN\_3V3} = 12$ V<br>$I_{DD} = 25$ mA | 3.13  | 3.3  | 3.47  | V    |

| $I_{DD,lim}$                      | 3.3 V linear regulator current limiter        | $V_{DD}$ shorted to AGND                    | 36    | 45   | 65    | mA   |

| <b>Charge pump</b>                |                                               |                                             |       |      |       |      |

| $f_{SW,CP}$                       | charge pump switching frequency               |                                             |       | 90   |       | kHz  |

| Symbol                                           | Parameter                                                         | Test condition                                                         | Min.  | Typ.  | Max.  | Unit |

|--------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------|-------|-------|-------|------|

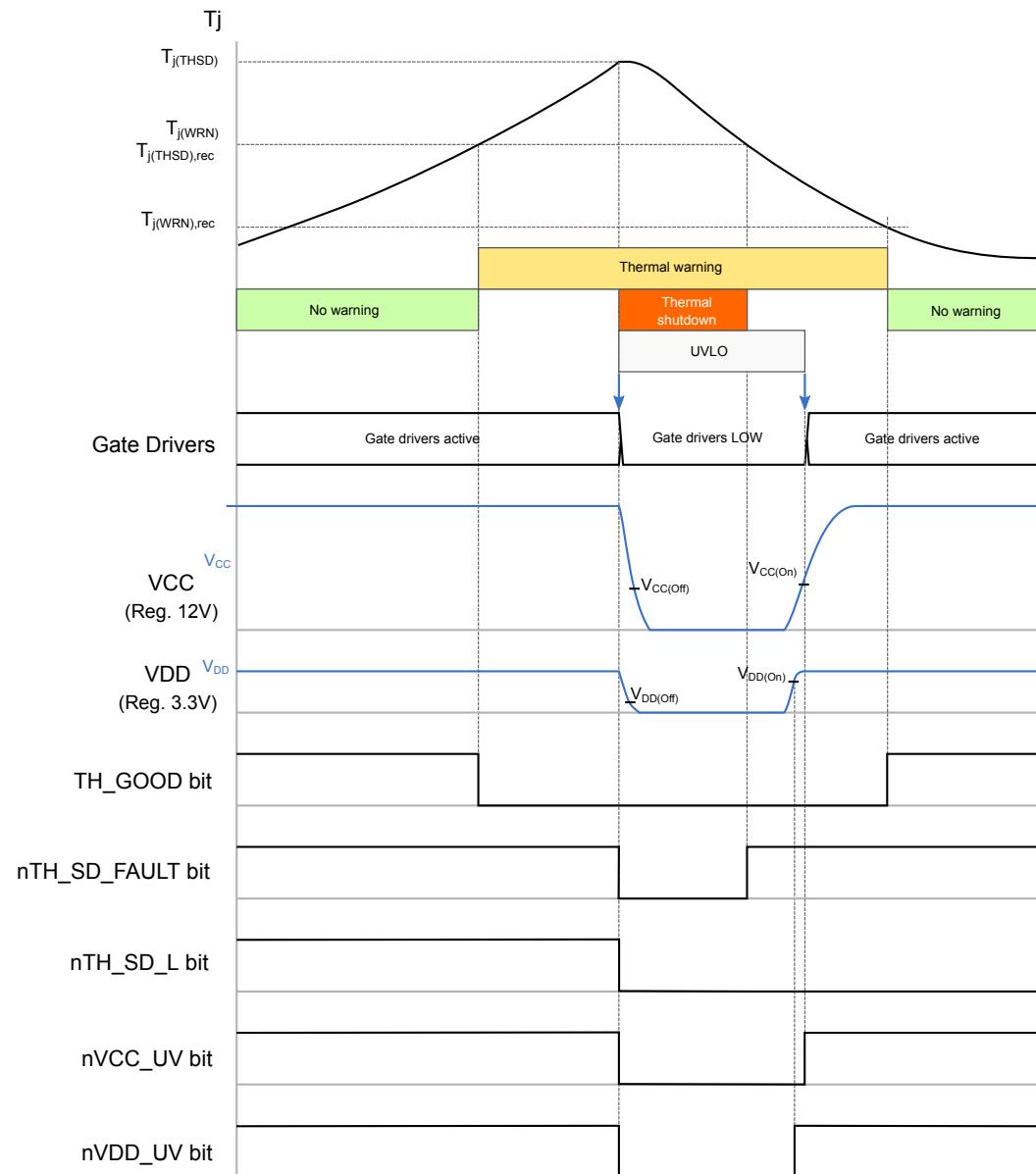

| <b>Thermal shutdown and thermal warning</b>      |                                                                   |                                                                        |       |       |       |      |

| $T_{j(THSD),rec}$                                | Thermal shutdown recovery temperature                             |                                                                        |       | 135   |       | °C   |

| $T_{j(THSD)}$                                    | Thermal shutdown temperature                                      |                                                                        |       | 150   |       | °C   |

| $T_{j(WRN),rec}$                                 | Thermal warning recovery temperature                              |                                                                        |       | 125   |       | °C   |

| $T_{j(WRN)}$                                     | Thermal warning temperature                                       |                                                                        |       | 135   |       | °C   |

| <b>Gate drivers</b>                              |                                                                   |                                                                        |       |       |       |      |

| $I_{GATE,on}$                                    | Gate driver source current capability                             | $IGATE[3:0] = 1111$ , see <a href="#">Table 32</a>                     |       | 1000  |       | mA   |

| $I_{GATE,off}$                                   | Gate driver sink current capability                               | $IGATE[3:0] = 1111$ , see <a href="#">Table 32</a><br>$DRV_EQ_SEL = 0$ |       | 2000  |       | mA   |

| $I_{hold,on}$                                    | Gate driver hold current (source)                                 |                                                                        |       | 25    |       | mA   |

| $I_{hold,off}$                                   | Gate driver hold current (sink)                                   | $DRV_EQ_SEL = 0$                                                       |       | 50    |       | mA   |

| $I_{clamp}$                                      | Gate driver clamp current                                         | $DRV_EQ_SEL = 0$                                                       |       | 2140  |       | mA   |

| $t_{cc,on}$                                      | Constant source current time                                      | $DRV_EQ_SEL = 0$<br>$TCC[3:0] = 0000$ , see <a href="#">Table 31</a>   |       | 280   |       | ns   |

|                                                  |                                                                   | $DRV_EQ_SEL = 0$<br>$TCC[3:0] = 1111$ , see <a href="#">Table 31</a>   |       | 5400  |       | ns   |

| $t_{cc,off}$                                     | Constant sink current time                                        | $DRV_EQ_SEL = 0$<br>$TCC[3:0] = 0000$ , see <a href="#">Table 31</a>   |       | 140   |       | ns   |

|                                                  |                                                                   | $DRV_EQ_SEL = 0$<br>$TCC[3:0] = 1111$ , see <a href="#">Table 31</a>   |       | 2700  |       | ns   |

| $V_{GS, clamp}$                                  | Clamping voltage protection on the high-side driver output        | $I_{GS,clamp} = 25$ mA                                                 |       | 17.5  |       | V    |

| $I_{OUTx,bias}$                                  | OUTx bias current                                                 | $V_{OUTx} = V_M = 40$ V<br>$IGATE[3:0] = 1111$                         |       | 300   |       | μA   |

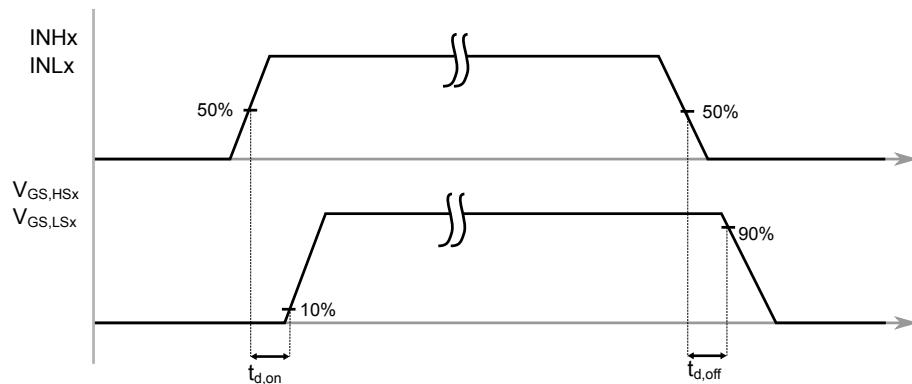

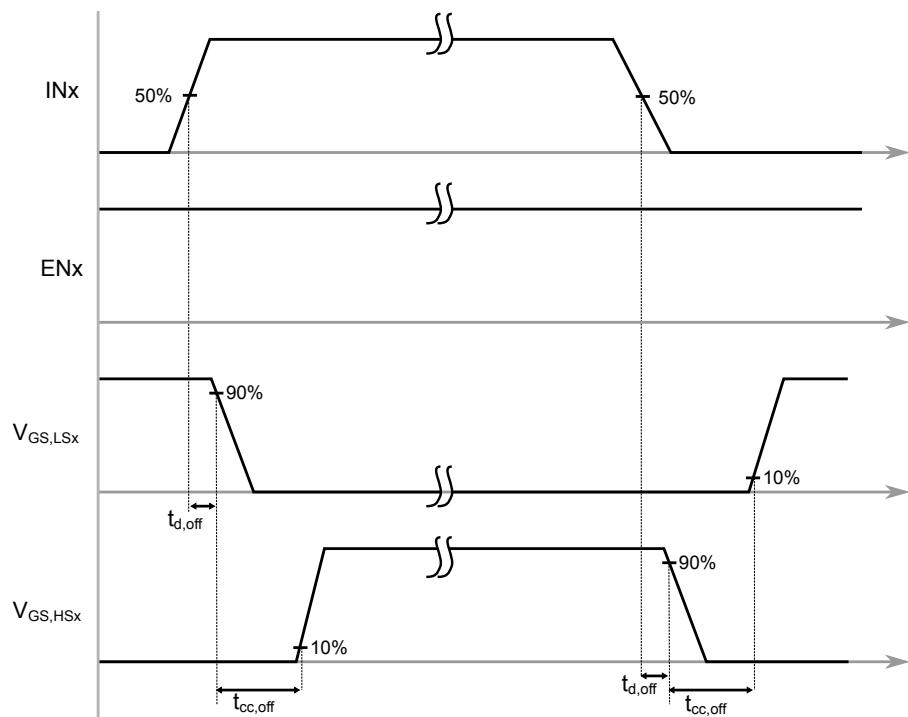

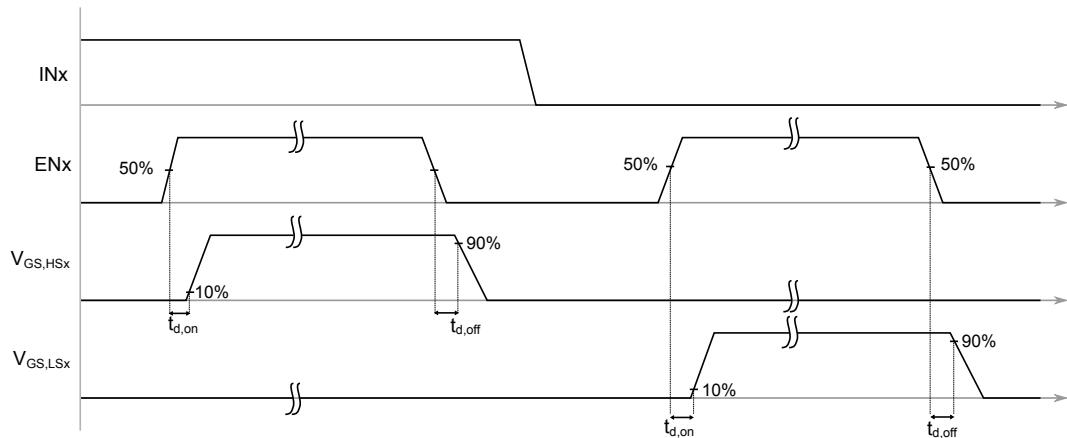

| $t_{d,on}$                                       | Turn-on propagation delay (input to output) <sup>(1)</sup>        | $C_{LOAD} = 1$ nF<br>$IGATE[3:0] = 1111$                               |       | 50    |       | ns   |

| $t_{d,off}$                                      | Turn-off propagation delay (input to output) <sup>(1)</sup>       | $C_{LOAD} = 1$ nF<br>$IGATE[3:0] = 1111$                               |       | 45    |       | ns   |

| $MT_{on-off}$                                    | Propagation delay matching between turn-on and off <sup>(2)</sup> | $C_{LOAD} = 1$ nF<br>$IGATE[3:0] = 1111$                               |       | 5     |       | ns   |

| $MT_{HL}$                                        | Propagation delay matching between HS and LS <sup>(3)</sup>       | $C_{LOAD} = 1$ nF<br>$IGATE[3:0] = 1111$                               |       | 7     |       | ns   |

| $MT_{CH}$                                        | Propagation delay matching between channels <sup>(4)</sup>        | $C_{LOAD} = 1$ nF<br>$IGATE[3:0] = 1111$                               |       | 0     |       | ns   |

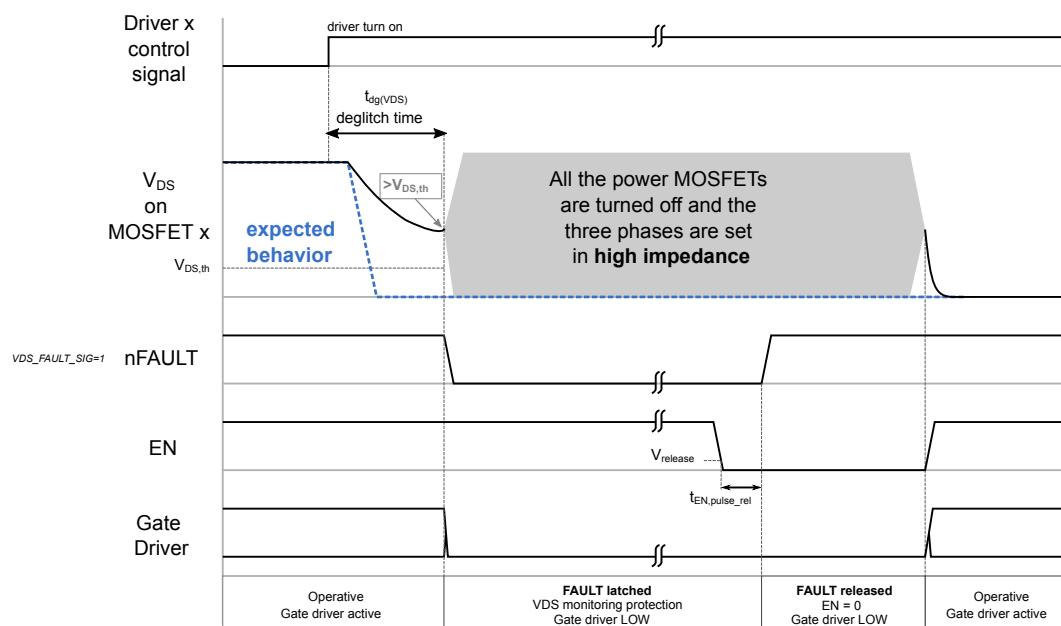

| <b><math>V_{DS}</math> monitoring protection</b> |                                                                   |                                                                        |       |       |       |      |

| $V_{DS,th}$                                      | $V_{DS}$ monitor protection threshold                             | $VDSTH = 0.05$ V                                                       | 0.020 | 0.050 | 0.083 | V    |

|                                                  |                                                                   | $VDSTH = 2$ V                                                          | 1.8   | 2     | 2.2   | V    |

| $V_{DSTH,en}$                                    | $V_{DS}$ monitor protection enable voltage                        |                                                                        |       |       | 2.4   | V    |

| $V_{DSTH,dis}$                                   | $V_{DS}$ monitor protection disable voltage                       |                                                                        | 3     |       |       | V    |

| $R_{PD,VDSTH}$                                   | VDSTH pin pull-down resistor                                      |                                                                        |       | 450   |       | kΩ   |

| Symbol                          | Parameter                                                           | Test condition                                                                      | Min. | Typ. | Max. | Unit |

|---------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| <b>PGA</b>                      |                                                                     |                                                                                     |      |      |      |      |

| G <sub>PGA</sub>                | Programmable gain amplifiers differential gain                      | PGAx_GAIN[1:0] = 00, (G <sub>PGA</sub> = 4)                                         |      | 4    |      | V/V  |

|                                 |                                                                     | PGAx_GAIN[1:0] = 01, (G <sub>PGA</sub> = 8)                                         |      | 8    |      | V/V  |

|                                 |                                                                     | PGAx_GAIN[1:0] = 10, (G <sub>PGA</sub> = 16)                                        |      | 16   |      | V/V  |

|                                 |                                                                     | PGAx_GAIN[1:0] = 11, (G <sub>PGA</sub> = 32)                                        |      | 32   |      | V/V  |

| V <sub>PGA,io</sub>             | PGA input offset voltage                                            | PGAx_GAIN[1:0] = 11, (G <sub>PGA</sub> = 32)                                        | -6   | 0    | 6    | mV   |

| V <sub>PGA_OH</sub>             | High level output voltage (V <sub>DD</sub> - V <sub>PGA_Ox</sub> )  | Output source current I <sub>PGA_Ox</sub> = +1 mA                                   |      | 30   | 100  | mV   |

| V <sub>PGA_OL</sub>             | Low level output voltage                                            | Output sink current I <sub>PGA_Ox</sub> = -1 mA                                     |      | 30   | 100  | mV   |

| BW <sub>PGA</sub>               | PGA bandwidth at -3 dB                                              | G <sub>PGA</sub> = 4, C <sub>L</sub> = 1 nF, R <sub>L</sub> = 10 kΩ <sup>(5)</sup>  |      | 3.6  |      | MHz  |

|                                 |                                                                     | G <sub>PGA</sub> = 8, C <sub>L</sub> = 1 nF, R <sub>L</sub> = 10 kΩ <sup>(5)</sup>  |      | 2    |      | MHz  |

|                                 |                                                                     | G <sub>PGA</sub> = 16, C <sub>L</sub> = 1 nF, R <sub>L</sub> = 10 kΩ <sup>(5)</sup> |      | 1.1  |      | MHz  |

|                                 |                                                                     | G <sub>PGA</sub> = 32<br>C <sub>L</sub> = 1 nF, R <sub>L</sub> = 10 kΩ              |      | 0.6  |      | MHz  |

| SR                              | Slew rate                                                           | G <sub>PGA</sub> = 4<br>C <sub>L</sub> = 1 nF, R <sub>L</sub> = 10 kΩ               |      | 12   |      | V/μs |

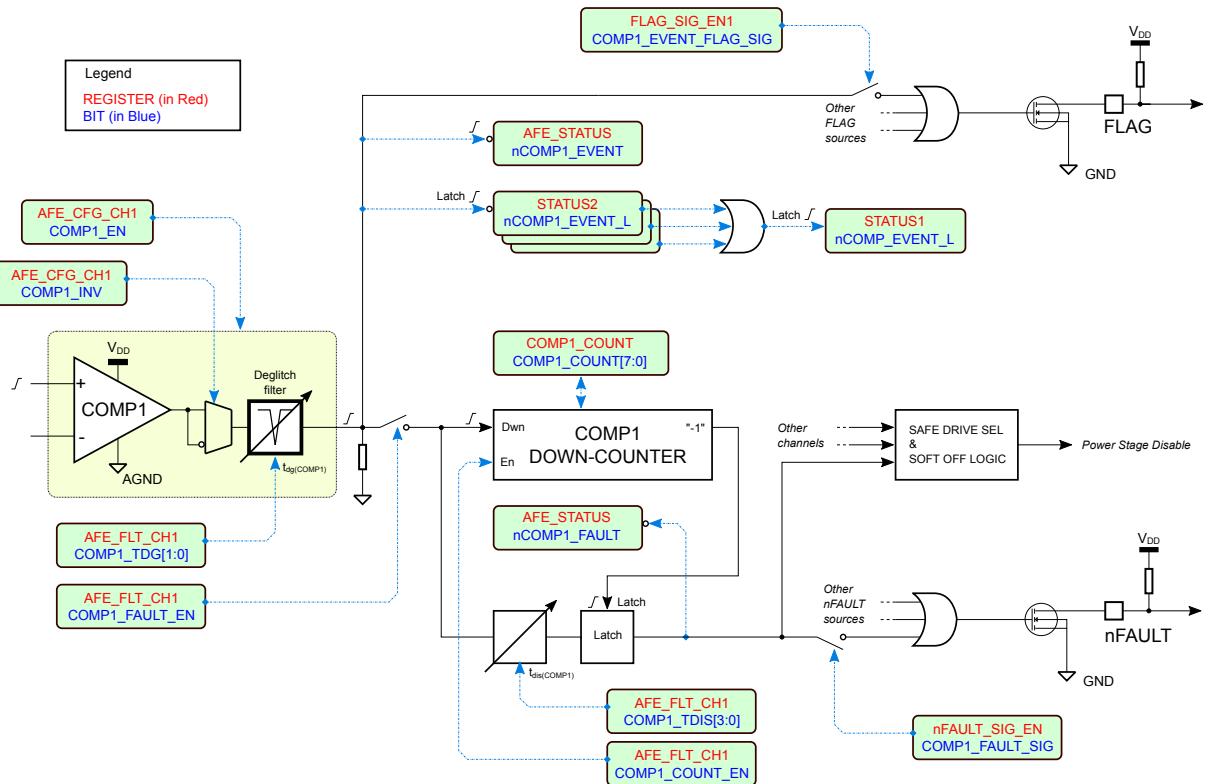

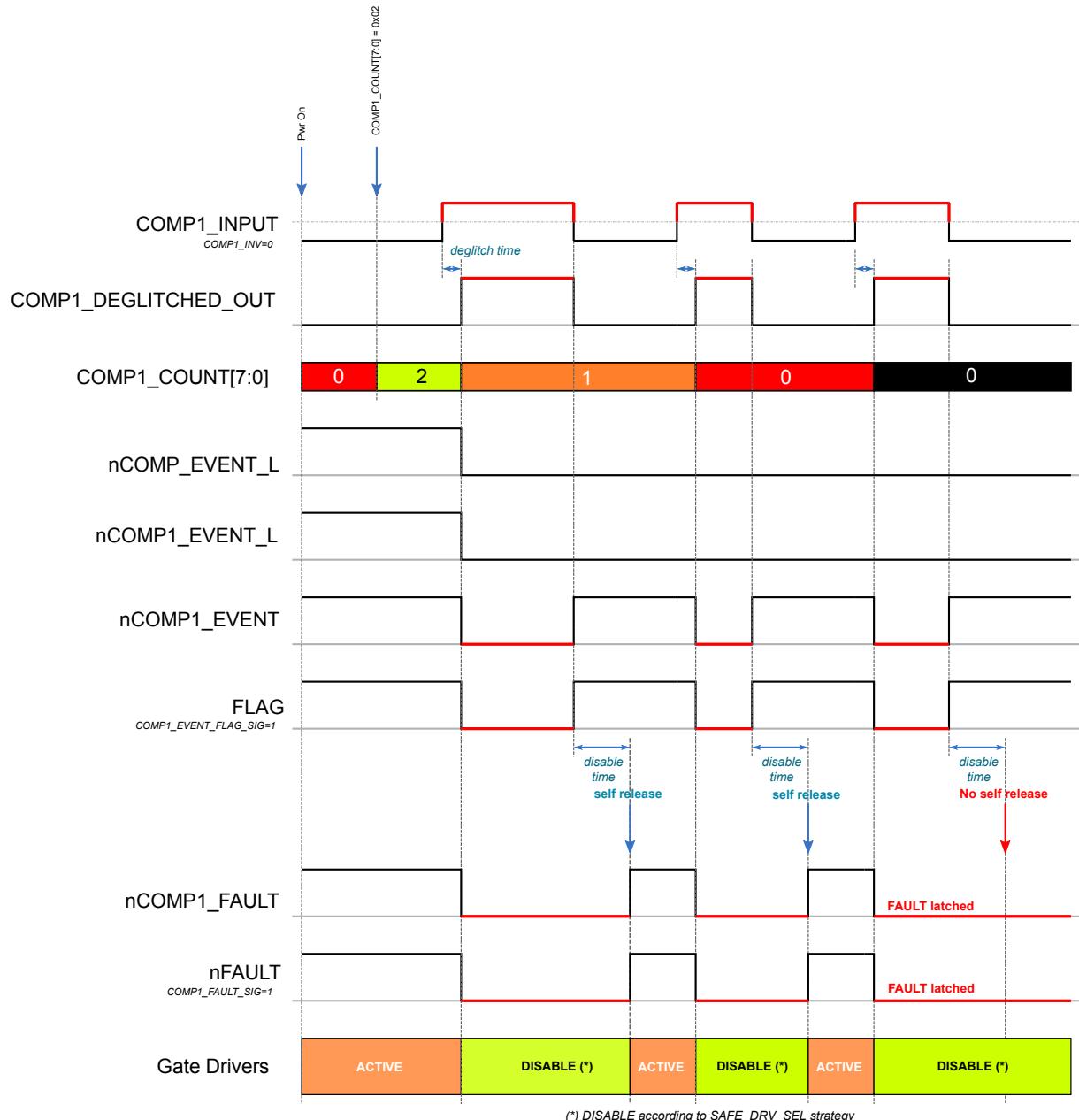

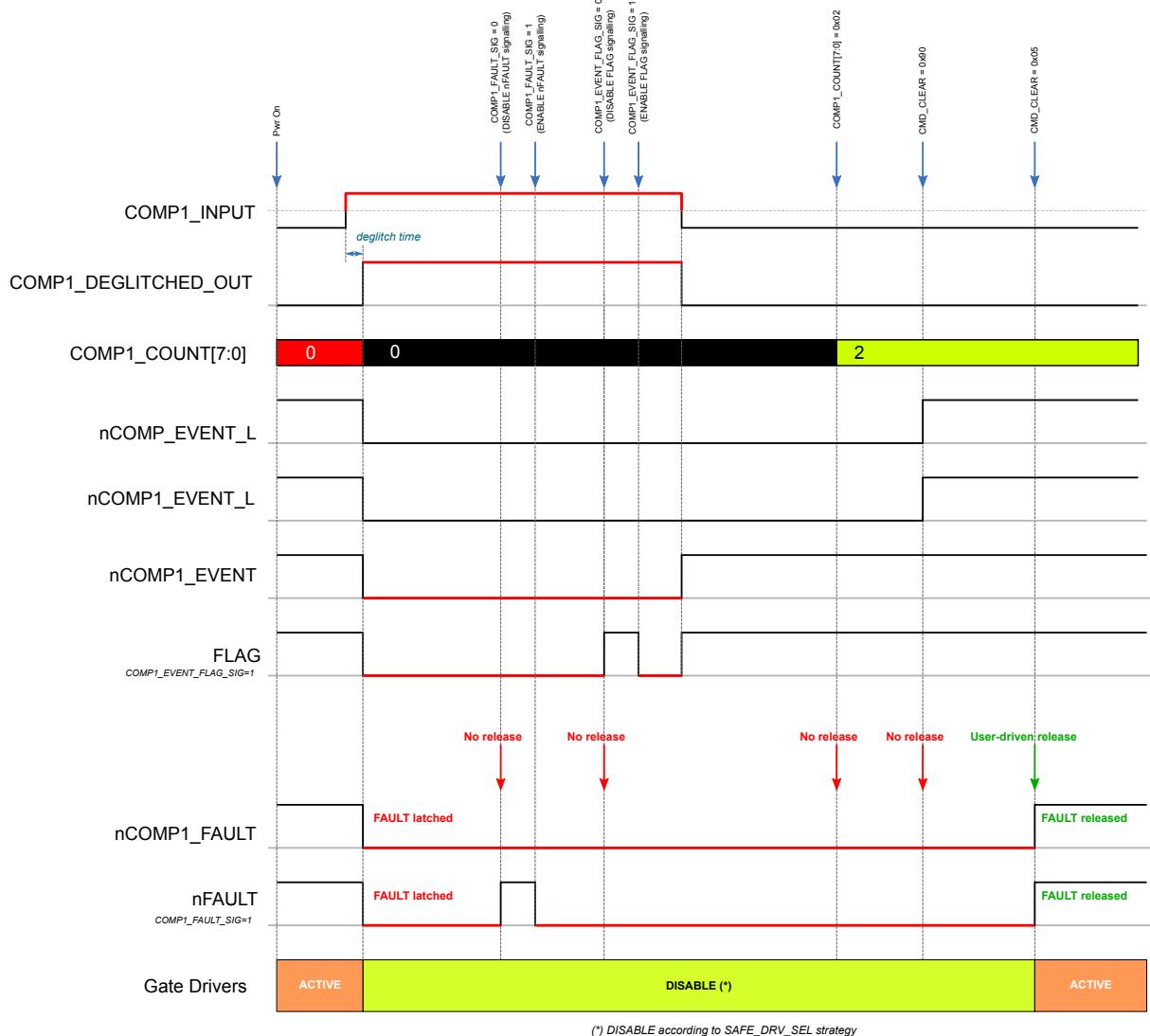

| <b>Comparators</b>              |                                                                     |                                                                                     |      |      |      |      |

| V <sub>COMP,io</sub>            | Input offset voltage                                                | CREF = 1.65 V                                                                       | -16  | 0    | 16   | mV   |

| V <sub>Hyst(COMP)</sub>         | Comparator hysteresis high-to-low transition                        | T <sub>j</sub> = 25°C                                                               |      | 20   |      | mV   |

| I <sub>CREF</sub>               | CREF pin input current                                              | T <sub>j</sub> = 25°C <sup>(5)</sup>                                                |      |      | 1    | nA   |

| I <sub>C_AUX</sub>              | C_AUX pin input current                                             | T <sub>j</sub> = 25°C <sup>(5)</sup>                                                |      |      | 1    | nA   |

| t <sub>pd(COMP)</sub>           | Comparator propagation delay                                        | CREF = 1.65 V<br>COMP<x> DEG = 00                                                   |      | 200  |      | ns   |

| <b>Logic inputs and outputs</b> |                                                                     |                                                                                     |      |      |      |      |

| V <sub>IL</sub>                 | Low logic input voltage                                             |                                                                                     |      |      | 0.8  | V    |

| V <sub>IH</sub>                 | High logic input voltage                                            |                                                                                     | 2    |      |      | V    |

| V <sub>IL,stby</sub>            | nSTBY pin low logic input voltage                                   |                                                                                     |      |      | 0.6  | V    |

| V <sub>IH,stby</sub>            | nSTBY pin high logic input voltage                                  |                                                                                     | 2    |      |      | V    |

| R <sub>PD,in</sub>              | Pull-down resistor on input lines INHx/INx, INLx/ENx, nCS, CLK, SDI |                                                                                     |      | 220  |      | kΩ   |

| R <sub>PD,STBY</sub>            | nSTBY pin pull-down resistor                                        |                                                                                     |      | 440  |      | kΩ   |

| R <sub>PD,EN</sub>              | EN pin pull-down resistor                                           |                                                                                     |      | 440  |      | kΩ   |

| V <sub>OD,L</sub>               | Open-drain output low voltage (nFAULT, FLAG, SDO)                   | I <sub>OD</sub> = 8 mA                                                              |      |      | 0.35 | V    |

| V <sub>release</sub>            | EN pin latch release threshold                                      |                                                                                     | 0.37 |      |      | V    |

| t <sub>EN,pulse_rel</sub>       | Latch release time                                                  |                                                                                     | 400  |      |      | ns   |

| Symbol     | Parameter    | Test condition          | Min. | Typ. | Max. | Unit    |

|------------|--------------|-------------------------|------|------|------|---------|

| $t_{STBY}$ | Standby time | From nSTBY falling edge |      |      | 100  | $\mu$ s |

1. See Figure 20, Figure 21, Figure 22.

2. The matching time, on the same driver, between the on and off transition is defined as  $|t_{d,on} - t_{d,off}|$ .

3. The matching of the same parameter ( $t_{d,on}$  or  $t_{d,off}$ ) between the two drivers (HS and LS) of the same half bridge is defined as  $|t_{d,on,HS} - t_{d,on,LS}|$  or  $|t_{d,off,HS} - t_{d,off,LS}|$ .

4. The matching of the same parameter ( $t_{d,on}$  or  $t_{d,off}$ ) between the two drivers (HS and LS) of two different half-bridges (channels) "x" and "y" is defined as  $|t_{d,on,HSx} - t_{d,on,HSy}|$ ,  $|t_{d,off,HSx} - t_{d,off,HSy}|$ ,  $|t_{d,on,LSx} - t_{d,on,LSy}|$ ,  $|t_{d,off,LSx} - t_{d,off,LSy}|$ .

5. Guaranteed by design.

## 4 Pin description

### 4.1 STDRIVE102BP pin description

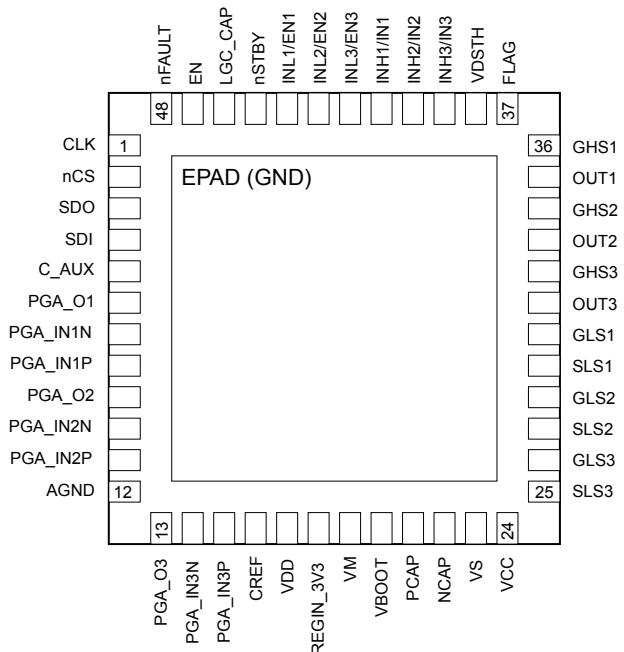

**Figure 3. STDRIVE102BP pin description**

**Table 7. STDRIVE102BP pin list**

| Pin N. | Name     | Type        | Function                                                                                     |

|--------|----------|-------------|----------------------------------------------------------------------------------------------|

| 1      | CLK      | Digital In  | Serial clock of the SPI. Internal pull-down.                                                 |

| 2      | nCS      | Digital In  | Chip-select of the SPI (active low). Internal pull-down.                                     |

| 3      | SDO      | Digital Out | Serial data output of the SPI (open-drain).                                                  |

| 4      | SDI      | Digital In  | Serial data input of the SPI. Internal pull-down.                                            |

| 5      | C_AUX    | Analog In   | Auxiliary non-inverting input of the comparator 3.                                           |

| 6      | PGA_O1   | Analog Out  | Output of the PGA 1.                                                                         |

| 7      | PGA_IN1N | Analog In   | Inverting input of the PGA 1.                                                                |

| 8      | PGA_IN1P | Analog In   | Non-inverting input of the PGA 1.                                                            |

| 9      | PGA_O2   | Analog Out  | Output of the PGA 2.                                                                         |

| 10     | PGA_IN2N | Analog In   | Inverting input of the PGA 2.                                                                |

| 11     | PGA_IN2P | Analog In   | Non-inverting input of the PGA 2.                                                            |

| 12     | AGND     | Power       | Analog ground of the device. Connect this pin to the EPAD or a suitable reference GND point. |

| 13     | PGA_O3   | Analog Out  | Output of the PGA 3.                                                                         |

| 14     | PGA_IN3N | Analog In   | Inverting input of the PGA 3.                                                                |

| 15     | PGA_IN3P | Analog In   | Non-inverting input of the PGA 3.                                                            |

| Pin N. | Name      | Type        | Function                                                                                                             |

|--------|-----------|-------------|----------------------------------------------------------------------------------------------------------------------|

| 16     | CREF      | Analog In   | Common reference voltage for the three comparators (inverting input).                                                |

| 17     | VDD       | Power       | 3.3 V LDO linear regulator output and supply voltage of the Analog front end (AFE).                                  |

| 18     | REGIN_3V3 | Power       | 3.3 V LDO linear regulator input.                                                                                    |

| 19     | VM        | Power       | Motor supply voltage: reference for the internal charge pump and $V_{DS}$ monitoring protection.                     |

| 20     | VBOOT     | Power       | Charge pump output voltage: high-side drivers supply.                                                                |

| 21     | PCAP      | Power       | Charge pump fly capacitor positive pin.                                                                              |

| 22     | NCAP      | Power       | Charge pump fly capacitor negative pin.                                                                              |

| 23     | VS        | Power       | Device power supply and 12 V LDO linear regulator input.                                                             |

| 24     | VCC       | Power       | 12 V LDO linear regulator output and supply voltage of the low-side drivers.                                         |

| 25     | SLS3      | Analog      | Phase 3 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 3).                    |

| 26     | GLS3      | Analog      | Phase 3 low-side driver output.                                                                                      |

| 27     | SLS2      | Analog      | Phase 2 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 2).                    |

| 28     | GLS2      | Analog      | Phase 2 low-side driver output.                                                                                      |

| 29     | SLS1      | Analog      | Phase 1 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 1).                    |

| 30     | GLS1      | Analog      | Phase 1 low-side driver output.                                                                                      |

| 31     | OUT3      | Analog      | Phase 3 high-side reference voltage (external half-bridge 3 output).                                                 |

| 32     | GHS3      | Analog      | Phase 3 high-side driver output.                                                                                     |

| 33     | OUT2      | Analog      | Phase 2 high-side reference voltage (external half-bridge 2 output).                                                 |

| 34     | GHS2      | Analog      | Phase 2 high-side driver output.                                                                                     |

| 35     | OUT1      | Analog      | Phase 1 high-side reference voltage (external half-bridge 1 output).                                                 |

| 36     | GHS1      | Analog      | Phase 1 high-side driver output.                                                                                     |

| 37     | FLAG      | Digital Out | Open-drain pin for event signaling (configurable).                                                                   |

| 38     | VDSTH     | Analog In   | $V_{DS}$ monitoring threshold. Internal pull-down.                                                                   |

| 39     | INH3/IN3  | Digital In  | Digital control signal for the high-side of the phase 3 or control of the OUT3 voltage level. Internal pull-down.    |

| 40     | INH2/IN2  | Digital In  | Digital control signal for the high-side of the phase 2 or control of the OUT2 voltage level. Internal pull-down.    |

| 41     | INH1/IN1  | Digital In  | Digital control signal for the high-side of the phase 1 or control of the OUT1 voltage level. Internal pull-down.    |

| 42     | INL3/EN3  | Digital In  | Digital control signal for the low-side of the phase 3 or enable of the half-bridge on OUT3. Internal pull-down.     |

| 43     | INL2/EN2  | Digital In  | Digital control signal for the low-side of the phase 2 or enable of the half-bridge on OUT2. Internal pull-down.     |

| 44     | INL1/EN1  | Digital In  | Digital control signal for the low-side of the phase 1 or enable of the half-bridge on OUT1. Internal pull-down.     |

| 45     | nSTBY     | Digital In  | Digital control for the standby mode (active low). Internal pull-down.                                               |

| 46     | LGC_CAP   | Power       | Pin for external bypass capacitor – internal logic supply stabilization (not intended for external supply purposes). |

| 47     | EN        | Digital In  | Drivers enable with “FAULT release” feature. Internal pull-down.                                                     |

| 48     | nFAULT    | Digital Out | Open-drain pin for failure/protection events signaling (configurable).                                               |

| EPAD   | GND       | Power       | Ground.                                                                                                              |

## 4.2 STDRIVE102P pin description

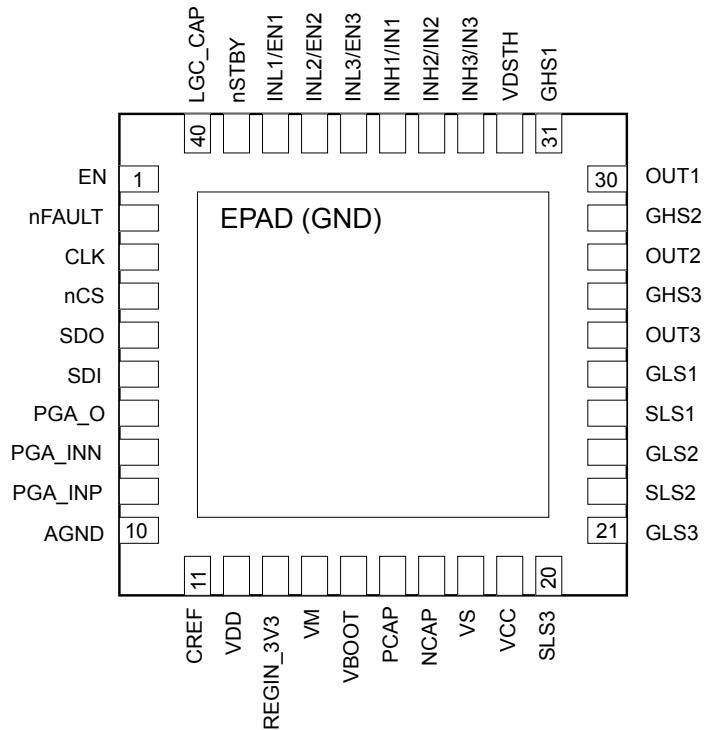

**Figure 4.** STDRIVE102P pin description

**Table 8.** STDRIVE102P pin list

| Pin N. | Name      | Type        | Function                                                                                         |

|--------|-----------|-------------|--------------------------------------------------------------------------------------------------|

| 1      | EN        | Digital In  | Drivers enable with “FAULT release” feature. Internal pull-down.                                 |

| 2      | nFAULT    | Digital Out | Open-drain pin for failure/protection events signaling (configurable).                           |

| 3      | CLK       | Digital In  | Serial clock of the SPI. Internal pull-down.                                                     |

| 4      | nCS       | Digital In  | Chip-select of the SPI (active low). Internal pull-down.                                         |

| 5      | SDO       | Digital Out | Serial data output of the SPI (open-drain).                                                      |

| 6      | SDI       | Digital In  | Serial data input of the SPI. Internal pull-down.                                                |

| 7      | PGA_O     | Analog Out  | Output of the PGA.                                                                               |

| 8      | PGA_INN   | Analog In   | Inverting input of the PGA.                                                                      |

| 9      | PGA_INP   | Analog In   | Non-inverting input of the PGA.                                                                  |

| 10     | AGND      | Power       | Analog ground of the device. Connect this pin to the EPAD or a suitable reference GND point.     |

| 11     | CREF      | Analog In   | Common reference voltage for the comparator (inverting input).                                   |

| 12     | VDD       | Power       | 3.3 V LDO linear regulator output and supply voltage of the Analog Front-End (AFE).              |

| 13     | REGIN_3V3 | Power       | 3.3 V LDO linear regulator input.                                                                |

| 14     | VM        | Power       | Motor supply voltage: reference for the internal charge pump and $V_{DS}$ monitoring protection. |

| 15     | VBOOT     | Power       | Charge pump output voltage: high-side drivers supply.                                            |

| 16     | PCAP      | Power       | Charge pump fly capacitor positive pin.                                                          |

| Pin N. | Name     | Type       | Function                                                                                                             |

|--------|----------|------------|----------------------------------------------------------------------------------------------------------------------|

| 17     | NCAP     | Power      | Charge pump fly capacitor negative pin.                                                                              |

| 18     | VS       | Power      | Device power supply and 12 V LDO linear regulator input.                                                             |

| 19     | VCC      | Power      | 12 V LDO linear regulator output and supply voltage of the low-side drivers.                                         |

| 20     | SLS3     | Analog     | Phase 3 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 3).                    |

| 21     | GLS3     | Analog     | Phase 3 low-side driver output.                                                                                      |

| 22     | SLS2     | Analog     | Phase 2 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 2).                    |

| 23     | GLS2     | Analog     | Phase 2 low-side driver output.                                                                                      |

| 24     | SLS1     | Analog     | Phase 1 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 1).                    |

| 25     | GLS1     | Analog     | Phase 1 low-side driver output.                                                                                      |

| 26     | OUT3     | Analog     | Phase 3 high-side reference voltage (external half-bridge 3 output).                                                 |

| 27     | GHS3     | Analog     | Phase 3 high-side driver output.                                                                                     |

| 28     | OUT2     | Analog     | Phase 2 high-side reference voltage (external half-bridge 2 output).                                                 |

| 29     | GHS2     | Analog     | Phase 2 high-side driver output.                                                                                     |

| 30     | OUT1     | Analog     | Phase 1 high-side reference voltage (external half-bridge 1 output).                                                 |

| 31     | GHS1     | Analog     | Phase 1 high-side driver output.                                                                                     |

| 32     | VDSTH    | Analog In  | $V_{DS}$ monitoring threshold. Internal pull-down.                                                                   |

| 33     | INH3/IN3 | Digital In | Digital control signal for the high-side of the phase 3 or control of the OUT3 voltage level. Internal pull-down.    |

| 34     | INH2/IN2 | Digital In | Digital control signal for the high-side of the phase 2 or control of the OUT2 voltage level. Internal pull-down.    |

| 35     | INH1/IN1 | Digital In | Digital control signal for the high-side of the phase 1 or control of the OUT1 voltage level. Internal pull-down.    |

| 36     | INL3/EN3 | Digital In | Digital control signal for the low-side of the phase 3 or enable of the half-bridge on OUT3. Internal pull-down.     |

| 37     | INL2/EN2 | Digital In | Digital control signal for the low-side of the phase 2 or enable of the half-bridge on OUT2. Internal pull-down.     |

| 38     | INL1/EN1 | Digital In | Digital control signal for the low-side of the phase 1 or enable of the half-bridge on OUT1. Internal pull-down.     |

| 39     | nSTBY    | Digital In | Digital control for the standby mode (active low). Internal pull-down.                                               |

| 40     | LGC_CAP  | Power      | Pin for external bypass capacitor – internal logic supply stabilization (not intended for external supply purposes). |

| EPAD   | GND      | Power      | Ground.                                                                                                              |

## 5 Device description

The STDRIVE102BP and the STDRIVE102P are triple half-bridge gate drivers suitable for 3-phase brushless motor driving. From now on, the naming convention STDRIVE102BP/P will be used to refer to either one indistinctly.

### 5.1 Power management section

The power management section of the STDRIVE102BP/P (Figure 5) is composed of:

- One LDO linear regulator with 12 V output; it is used to generate the VCC for the gate drivers' supply. Its input VS can be connected to the VM or to an external voltage (up to 50 V operative).

- One LDO linear regulator, which generates the 3.3 V supply (VDD). Its input REGIN\_3V3 ranges between 3.6 V and 15 V. It can also be connected to the VCC or be fed by an external supply.

- One internal regulator, which supplies the STDRIVE102BP/P control logic at 5 V. This voltage is for internal use only. No external load or circuitry can be connected to the LGC\_CAP pin, which must only be used to connect an external decoupling capacitor (low-ESR ceramic, 4.7  $\mu$ F / 16 V). This capacitor stabilizes all the internal control circuits, including the power-on reset (POR).

- A charge pump, supplied by VS and referenced to VM, which generates the VBOOT supply rail for the high-side gate drivers.

Figure 5. Power management block diagram

## 5.1.1

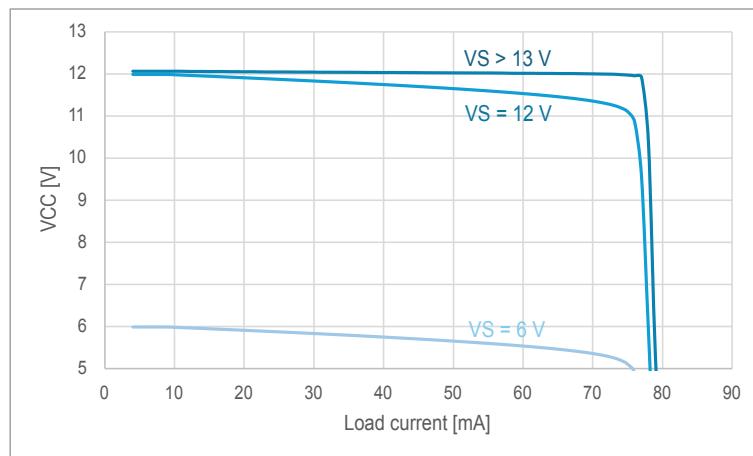

## 12 V LDO linear regulator

This regulator generates the voltage on the VCC pin, which is the supply for the low-side gate drivers and the set point for the ' $V_{BOOT} - V_M$ ' voltage provided by the charge pump (refer to Section 5.1.3). A low ESR ceramic capacitor of 4.7  $\mu$ F, 25 V must be placed as close as possible to the VCC pin, to ensure the stability of the VCC and support the currents required by the low-side gate drivers.

In addition, external loads can be connected to the VCC pin, provided they stay within the operating range. The output current of the regulator is limited at  $I_{CC,lim}$  protecting it against short circuit and overload. The overall consumption of the external loads plus the drivers must be smaller than this current limitation.

Figure 6. 12 V LDO output according to the current load at different VS input

The linear regulator input is connected to the main supply VS. The regulator can be bypassed by connecting the VCC and the VS together and forcing an external voltage equal to the target VCC value, which must always be within the operative range of the VCC pin.

The regulator is disabled in standby mode in order to reduce the current consumption.

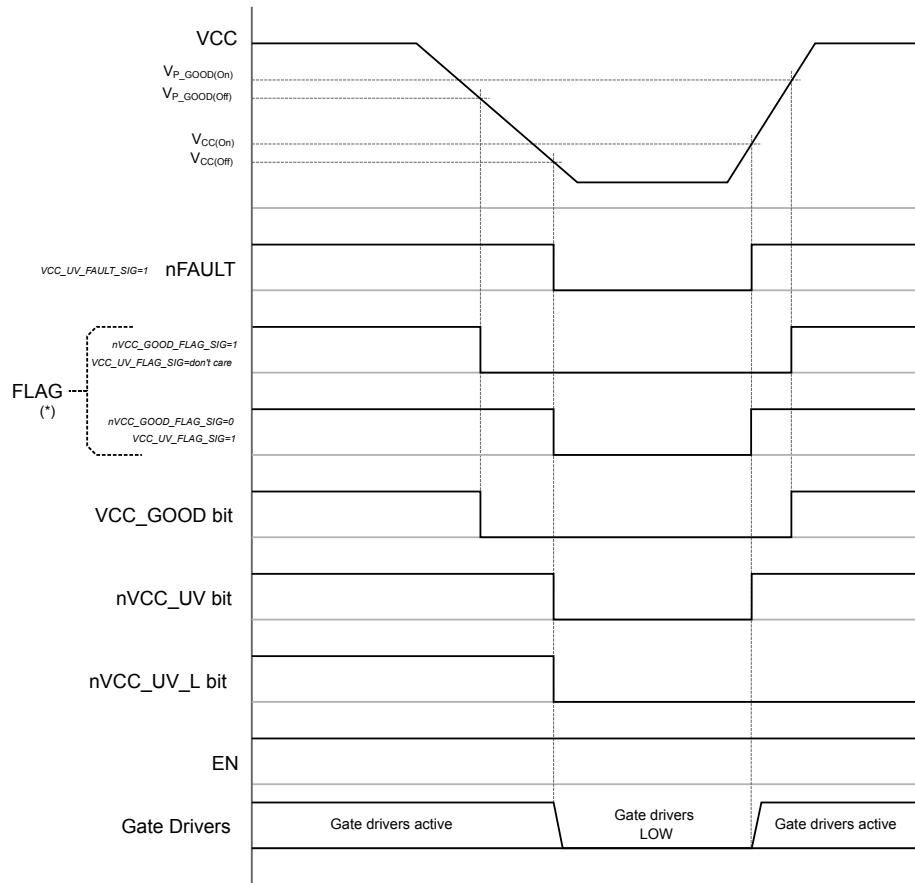

The output of the regulator VCC has two different thresholds: the "power-good" threshold and the undervoltage lockout (UVLO) threshold. Both thresholds have a hysteresis as shown in Figure 7.

The VCC good thresholds values can be selected using VCC\_GOOD\_SEL bit (refer to Section 5.12.4.6).

The VCC undervoltage lockout (UVLO) thresholds are selectable as well using UV\_SEL bit (refer to Section 5.12.4.6). This bit also affects the undervoltage thresholds on the charge pump voltage (refer to Section 5.1.3).

In case the VCC voltage falls below the UVLO threshold ( $V_{CC(off)}$ ), the gate drivers turn off all the external MOSFETs, forcing the power stage into a safe condition. As soon as the VCC voltage rises above the  $V_{CC(On)}$  threshold, the nFAULT is released and the drivers return to an active condition, according to the status of the digital inputs.

It is possible to report the UVLO condition on the nFAULT pin, by setting the VCC\_UV\_FAULT\_SIG at 1 (see Section 5.12.4.9). In this case the nFAULT pin is kept low during the UVLO condition, and then released when VCC rises above the  $V_{CC(On)}$  threshold. In case the VCC\_UV\_FAULT\_SIG = 0, the UVLO condition is not reported on nFAULT pin, but the UVLO protection is still active.

In case the VCC voltage falls below the "power-good" threshold ( $V_{P\_GOOD(off)}$ ), but stays above the UVLO threshold ( $V_{CC(off)}$ ), there are no other effects on the functional blocks of the devices. The gate drivers stay active according to the status of the digital inputs.

If  $nVCC\_GOOD\_FLAG\_SIG = 1$  (see Section 5.12.4.10), when the VCC voltage falls below the "power-good" threshold ( $V_{P\_GOOD(off)}$ ), the FLAG open-drain pin is forced low. The FLAG pin is then released as soon as the VCC voltage rises above the  $V_{P\_GOOD(On)}$  threshold. This situation is represented in Figure 7 on the upper instance of FLAG signal.

In case  $VCC\_UV\_FLAG\_SIG = 1$  (see Section 5.12.4.11) and  $nVCC\_GOOD\_FLAG\_SIG = 0$ , the FLAG pin reports the UVLO condition. This situation is represented in Figure 7 on the lower instance of FLAG signal.

The status bits related to the power-good and VCC UVLO conditions are also shown in Figure 7. The actual meaning of each bit (VCC\_GOOD, nVCC\_UV and nVCC\_UV\_L) is reported in Section 5.12.4.1 and Section 5.12.4.2.

Figure 7. V<sub>CC</sub> thresholds (power-good and UVLO)

Note: (\*) The FLAG pin is available only on the STDRIVE102BP.

## 5.1.2

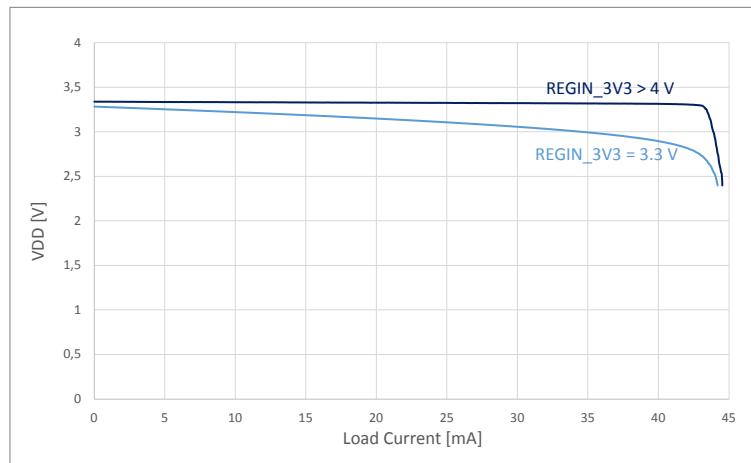

## 3.3 V LDO linear regulator

The device integrates a 3.3 V regulator, which supplies the embedded analog front end (AFE). In addition, external loads can be connected to the VDD pin, provided they stay within the operating range. It is recommended to place a low ESR ceramic capacitor of 4.7  $\mu$ F 16 V as close as possible to the VDD pin, to ensure the stability of the VDD voltage.

The output current of the regulator is limited at  $I_{DD,lim}$ , protecting it against short-circuit and overload. The overall consumption of the external loads plus the AFE must be smaller than this current limitation.

Figure 8. 3.3 V LDO output according to the current load at different REGIN\_3V3 input

The regulator is disabled in standby mode in order to reduce the current consumption.

The regulator can be bypassed by connecting the VDD and the REGIN\_3V3 pins together and forcing externally a voltage equal to the target VDD value, which must always be within the operative range of the VDD pin.

The 3.3 V regulator has a dedicated UVLO protection. The UVLO helps to avoid unexpected behavior related to all the circuitries supplied by the VDD. In particular, it avoids spurious events coming from the AFE comparators.

In case of UVLO condition (VDD falls below the  $V_{DD(off)}$  threshold), the drivers turn off all the external MOSFETs, forcing the power stage into a safe condition. As soon as the VDD voltage rises above the  $V_{DD(On)}$  threshold, the drivers return to an active condition, depending on the status of the digital inputs.

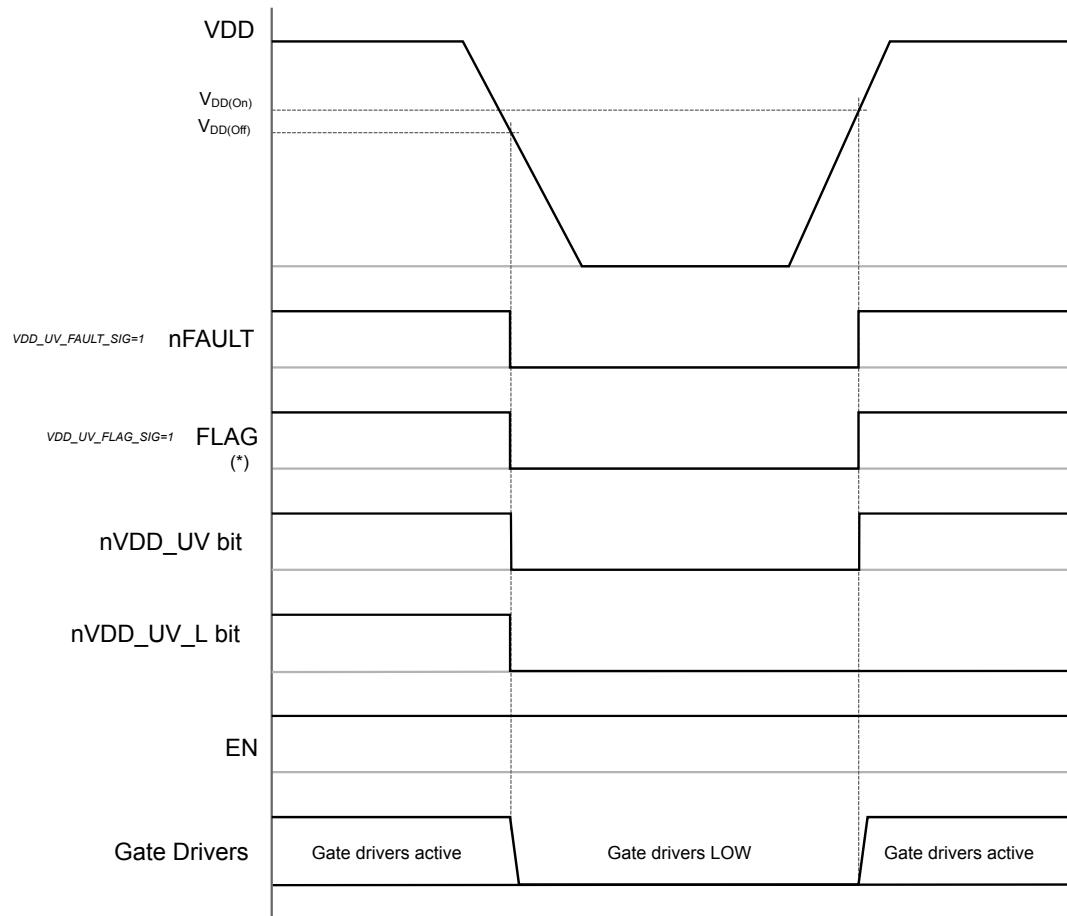

It is possible to report the UVLO condition on the nFAULT pin, by setting the VDD\_UV\_FAULT\_SIG at 1 (see [Section 5.12.4.9](#)). In this case, the nFAULT pin is kept low during the UVLO condition, and then released when VDD rises above the  $V_{DD(On)}$  threshold. In case the VDD\_UV\_FAULT\_SIG = 0, the UVLO condition is not reported on nFAULT pin, but the UVLO protection is still active.

It is also possible to report the UVLO condition on the FLAG pin, by setting the VDD\_UV\_FLAG\_SIG at 1 (see [Section 5.12.4.11](#)). In this case the FLAG pin is kept low during the UVLO condition, and then released when VDD rises above the  $V_{DD(On)}$  threshold. In case the VDD\_UV\_FLAG\_SIG = 0, the UVLO condition is not reported on the FLAG pin, but the UVLO protection is still active.

The status bits related to the VDD UVLO condition are also shown in [Figure 9](#). The actual meaning of each bit (nVDD\_UV\_L and nVDD\_UV) is reported in [Section 5.12.4.1](#) and [Section 5.12.4.3](#).

Figure 9. VDD thresholds (UVLO)

Note: (\*) The FLAG pin is available only on the STDRIVE102BP.

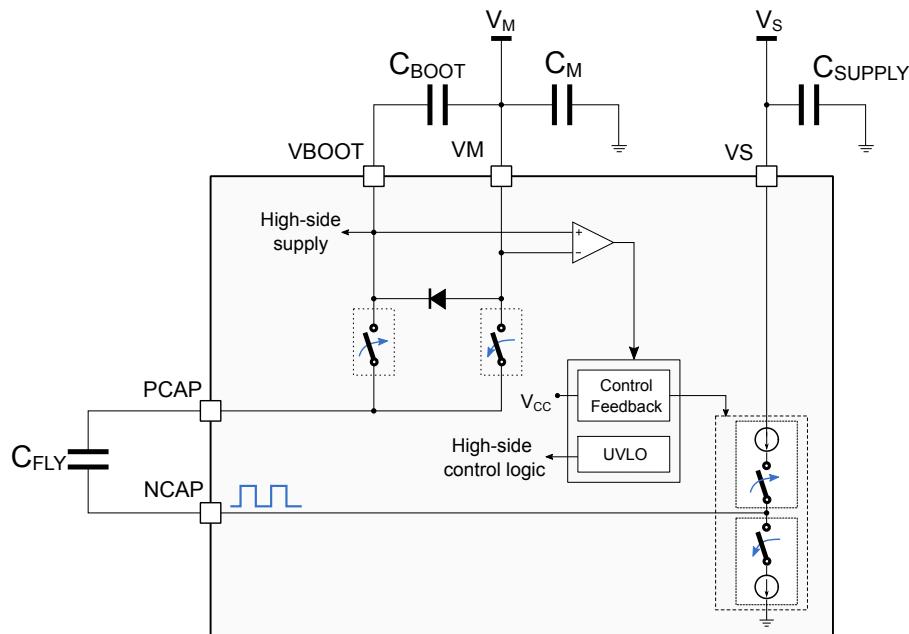

### 5.1.3 Charge pump

The embedded charge pump supplies the high-side gate drivers and ensures an unlimited on-time of the high-side MOSFETs with a PWM duty cycle of 100%.

**Figure 10. Charge pump simplified block diagram**

The charge pump is supplied directly by the VS pin and generates the voltage  $V_{BOOT}$  referenced to the motor supply  $V_M$ . The  $V_{BOOT}$  is the supply of the three high-side gate drivers and it must be greater than  $V_M$  to properly turn on the high-side MOSFETs. The internal feedback circuit of the charge pump tracks the value of the voltage on the VCC pin and regulates the  $V_{BOOT}$  to be equal to ' $V_M + V_{CC}$ '. In this way, both the low-side and the high-side MOSFETs are driven with the same  $V_{GS}$ , thus ensuring a more balanced behavior of the power stage.

The circuit on the NCAP pin charges the capacitor  $C_{FLY}$ . The charge is then transferred to the  $C_{BOOT}$  capacitor through the PCAP pin. The amount of charge stored in the  $C_{FLY}$  capacitor is controlled by the internal feedback, in order to meet the target voltage on  $V_{BOOT}$  pin.

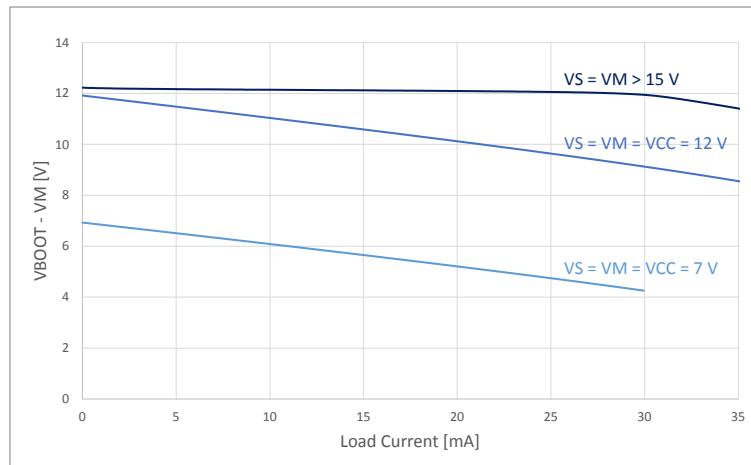

The drop between the target value of  $V_{BOOT}$  and its actual value depends on the voltage on the VS pin and the average load current required by the high-side drivers. The drop increases for lower  $V_S$  and higher current load. Figure 11 shows the charge pump output voltage with respect to the load current at  $T_{amb} = 25^\circ\text{C}$ , using the recommended values for  $C_{FLY} = 220 \text{ nF}$  and  $C_{BOOT} = 1 \mu\text{F}$ .

The pulsed current required by the high-side drivers is provided by the  $C_{BOOT}$  capacitor. This capacitor should be sized according to the maximum allowed ripple and total gate charge of the external MOSFETs. A ceramic low ESR capacitor of the same value of  $C_{BOOT}$  must be placed close to the VM pin and the exposed pad (GND) of the STDRIVE102BP/P.

The high-side drivers are connected to  $V_{BOOT}$  by an internal connection. Under no circumstances should other external loads be connected to the  $V_{BOOT}$  pin. The  $V_{BOOT}$  pin is referred to the VM pin. Any external event forcing a ' $V_{BOOT} - V_M$ ' voltage below the limit reported in Table 1 results in device breakdown.

The charge pump is disabled in standby mode in order to reduce the current consumption.

**Figure 11. Charge pump output voltage with respect to the load current**

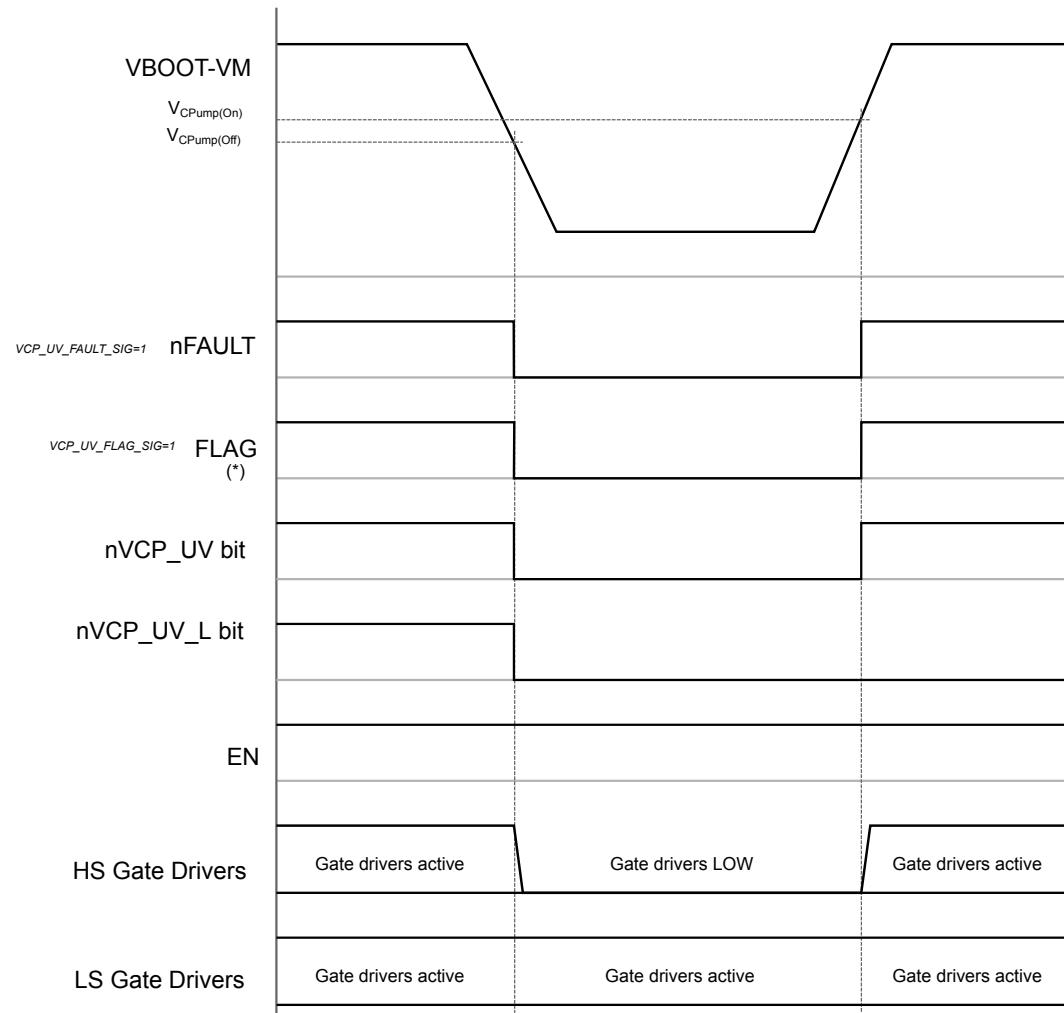

In case of undervoltage (' $V_{BOOT} - V_M < V_{CPump(Off)}$ '), the UVLO protection turns off the high-side MOSFETs, while the low-side drivers keep operating. The high-side drivers resume operation when ' $V_{BOOT} - V_M > V_{CPump(On)}$ '.

The charge pump undervoltage thresholds can be selected using the bit UV\_SEL bit in the SYS\_CFG register (see [Section 5.12.4.6](#)). This bit also affects the undervoltage thresholds on the VCC (see [Section 5.1.1](#)).

It is possible to report the UVLO condition on the nFAULT pin, by setting the VCP\_UV\_FAULT\_SIG at 1 ([Section 5.12.4.9](#)). In this case, the nFAULT pin is kept low during the UVLO condition, and then released when ' $V_{BOOT} - V_M$ ' rises above the  $V_{CPump(On)}$  threshold. In case the VCP\_UV\_FAULT\_SIG = 0, the UVLO condition is not reported on nFAULT pin, but the UVLO protection is still active.

The status bits related to the charge pump UVLO condition are also shown in [Figure 12](#). The actual meaning of each bit (nVCP\_UV\_L and nVCP\_UV) is reported in [Section 5.12.4.1](#) and [Section 5.12.4.2](#).

Figure 12. Charge pump thresholds (UVLO)

Note: (\*) The FLAG pin is available only on the STDRIVE102BP.

## 5.2 Gate drivers

The gate drivers use a constant-current approach, enabling the following advantages:

- No external components are required between the MOSFETs' gates and the drivers.

- The slew rate of the half-bridge outputs is better controlled.

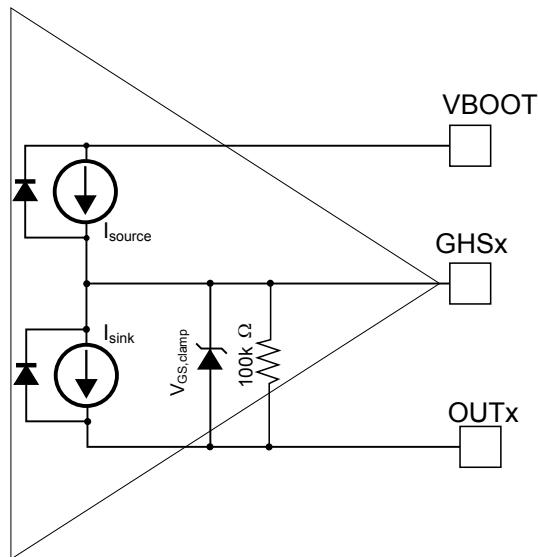

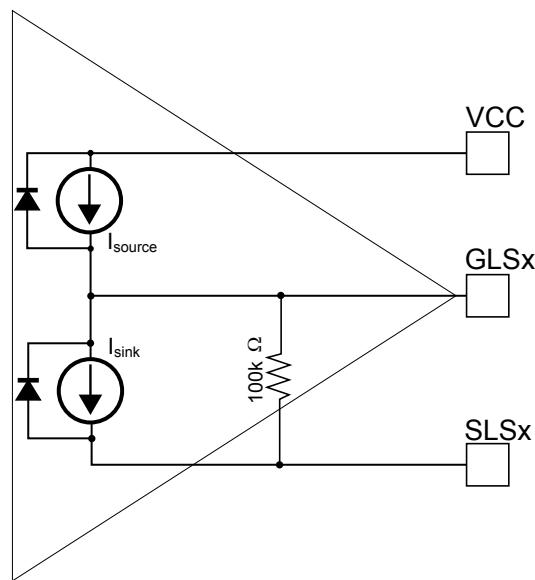

The high-side drivers (Figure 13) and the low-side drivers (Figure 14) have a similar structure:

- A reference pin for the low level (OUTx for the high-side and SLSx for the low-side).

- The output pin (GHSx for the high-side or GLSx for the low-side), which directly drives the external MOSFET's gate.

- The supply pins (VBOOT shared by the three high side drivers and VCC shared by the three low side drivers).

When the driver is not operative (for example, in standby mode or for very low supply), an equivalent 100 kΩ resistor keeps the external MOSFETs off. Under normal conditions, the gate driver must force a voltage on the gate of its respective MOSFET, in order to keep it in a well-defined state. This datasheet uses the following definitions:

- Setting the gate driver to HIGH means that the driver sources a controlled current to increase the  $V_{GS}$  of the MOSFET and turn it on. The gate current comes from the supply VCC for the low-side driver, or from VBOOT for the high-side driver.

- Setting the gate driver to LOW means that the driver sinks a controlled current from the gate of the MOSFET to turn it off. The sink circuitry of the driver is referred to the OUTx pin for the high-side, and to the SLSx pin for the low-side. This approach ensures that the MOSFET is kept off, even in the presence of below-GND transients.

In normal mode operation, when a high-side driver is set HIGH, the voltage on the GHSx pin increases up to its target level  $V_{BOOT}$ . At the same time, the OUTx voltage increases up to  $V_M$ , so that the  $V_{GS}$  of the external MOSFET is kept under control (less or equal to  $V_{CC}$ ). In case the OUTx pin cannot follow the GHSx pin, the gate driver protects the gate of the external MOSFET from breakdown by clamping the  $V_{GS}$  at  $V_{GS}$ , clamp.

The six gate drivers (three low-side and three high-side) are controlled by six digital inputs, INH1/IN1, INH2/IN2, INH3/IN3, INL1/EN1, INL2/EN2, INL3/EN3. Each digital input has an internal pull-down resistor  $R_{PD,in}$ . Each half-bridge (driven by a low-side driver and a high-side driver) is controlled by a couple of inputs. For example, INH1/IN1 and INL1/EN1 refer to half-bridge 1. The label INHx/INx or INLx/ENx can be used to indicate one of the three half-bridges, with no specific reference to a particular channel. Note that the terms "channel" or "phase" may be used interchangeably to refer to the half-bridge output.

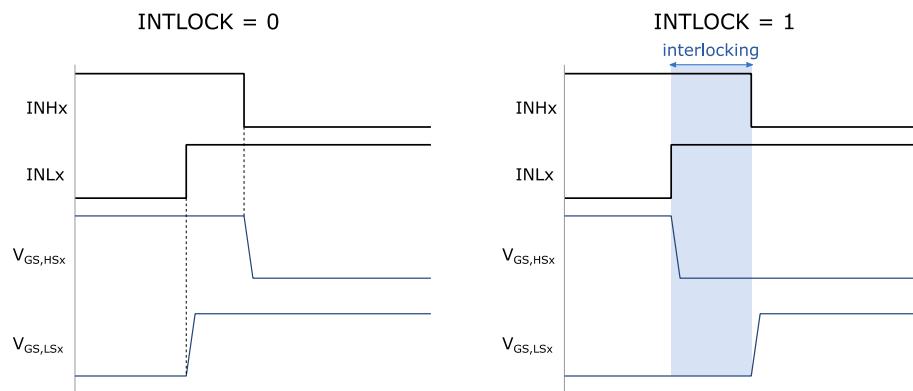

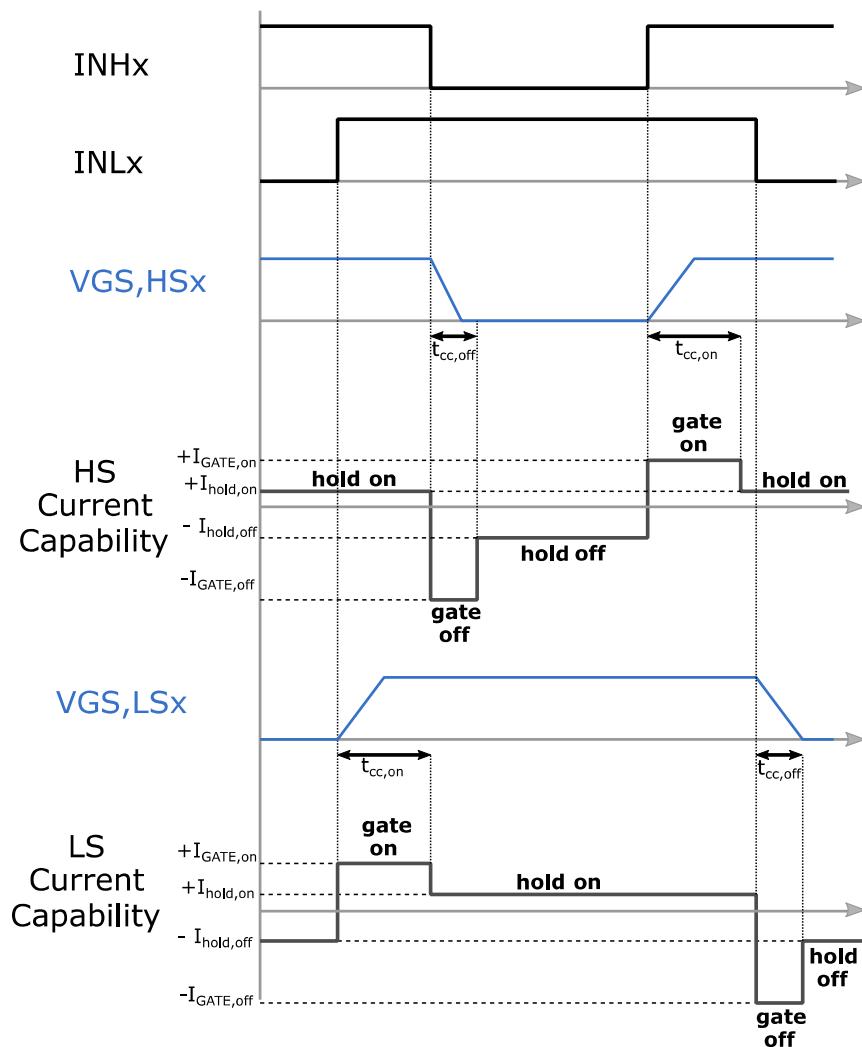

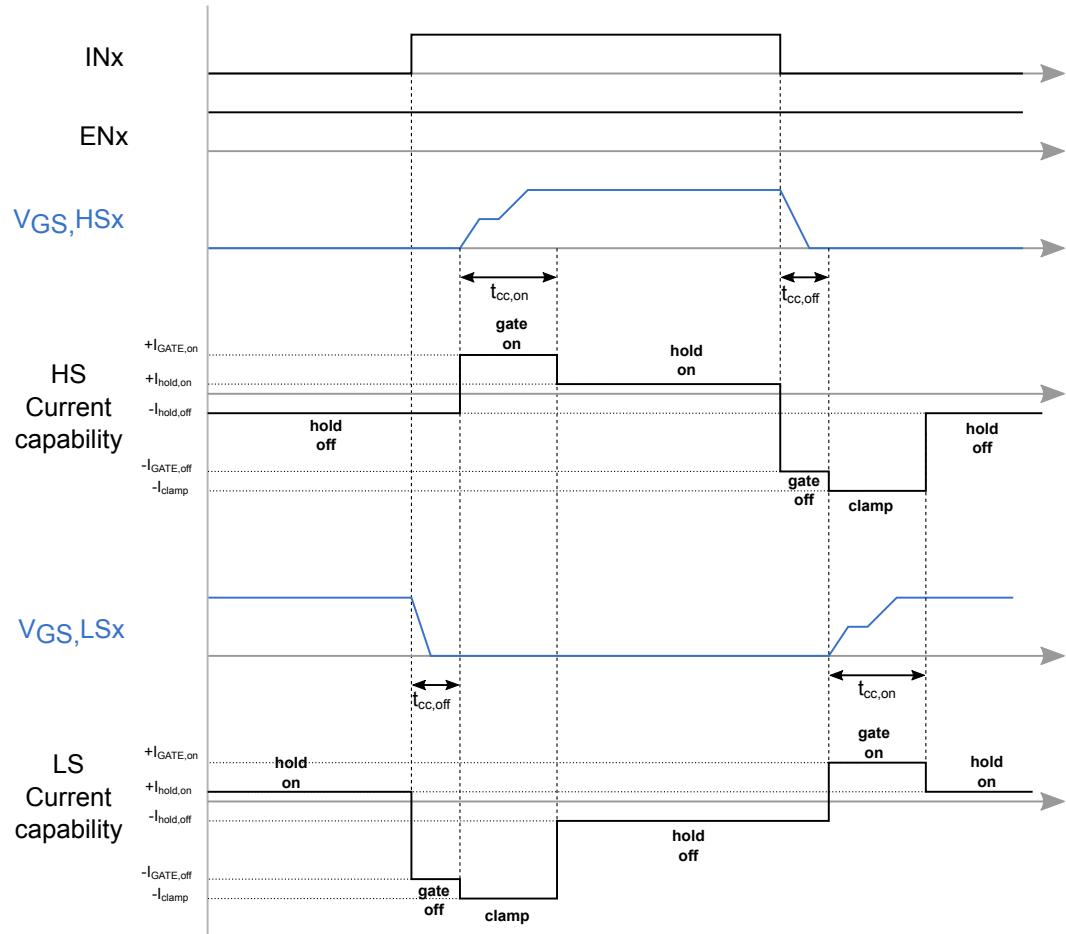

The STDRIVE102BP/P implements two control modes: the enable/input mode (EN/IN) or the direct mode (INH/INL), respectively explained in Section 5.2.3 and Section 5.2.2. The digital inputs assume a different function according to the input mode selected:

- In case the device is configured in Enable/Input mode:

- INHx/INx → INx

- INLx/ENx → ENx

- In case the device is configured in Direct mode:

- INHx/INx → INHx

- INLx/ENx → INLx

In addition to the six digital inputs mentioned above, another digital input named EN (pin 47 for the STDRIVE102BP and pin 1 for the STDRIVE102P) is used as general enable. In case it is forced to 0, all the six gate drivers are set to LOW, turning off all the external power MOSFETs. Setting EN to 1 activates the gate drivers, which behave according to their related digital inputs. The EN pin also integrates an analog threshold  $V_{release}$ , to release the latched condition after a FAULT event (refer to Section 5.8.1).

Figure 13. High-side driver simplified block diagram

Figure 14. Low-side driver simplified block diagram

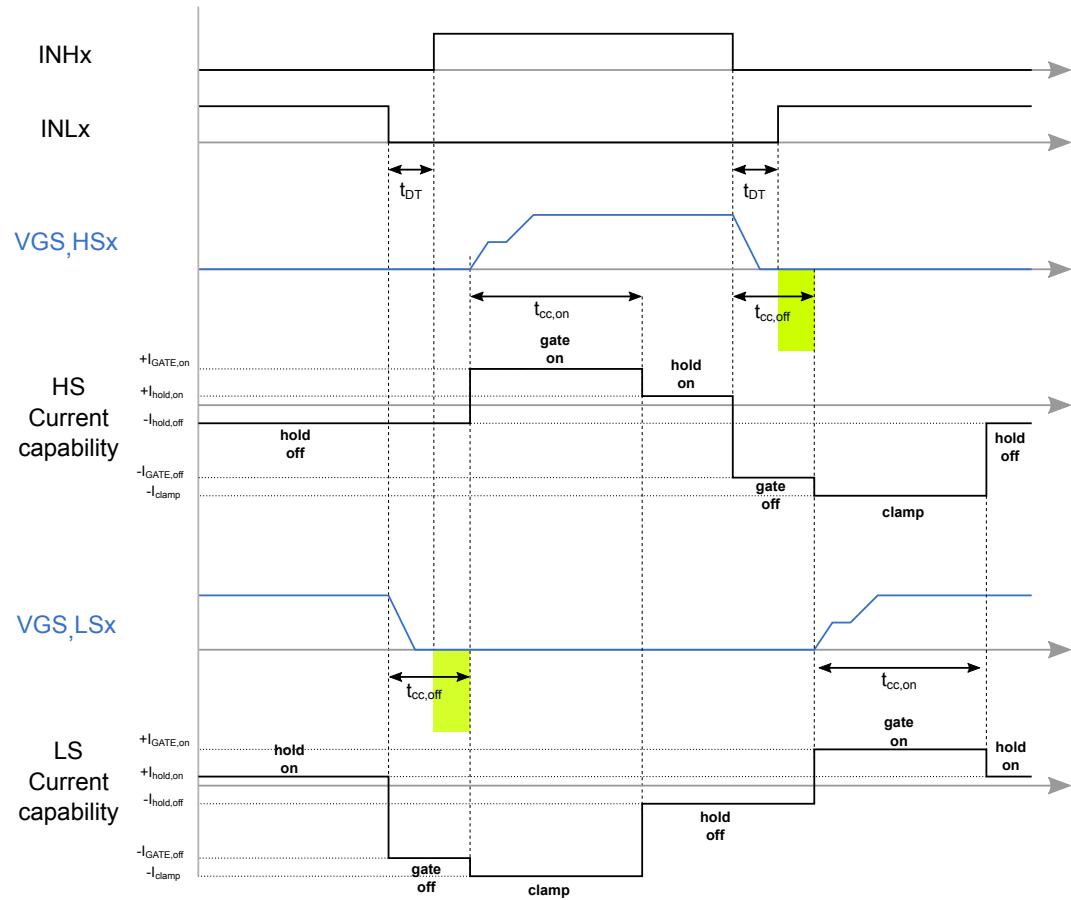

### 5.2.1 Driving current management

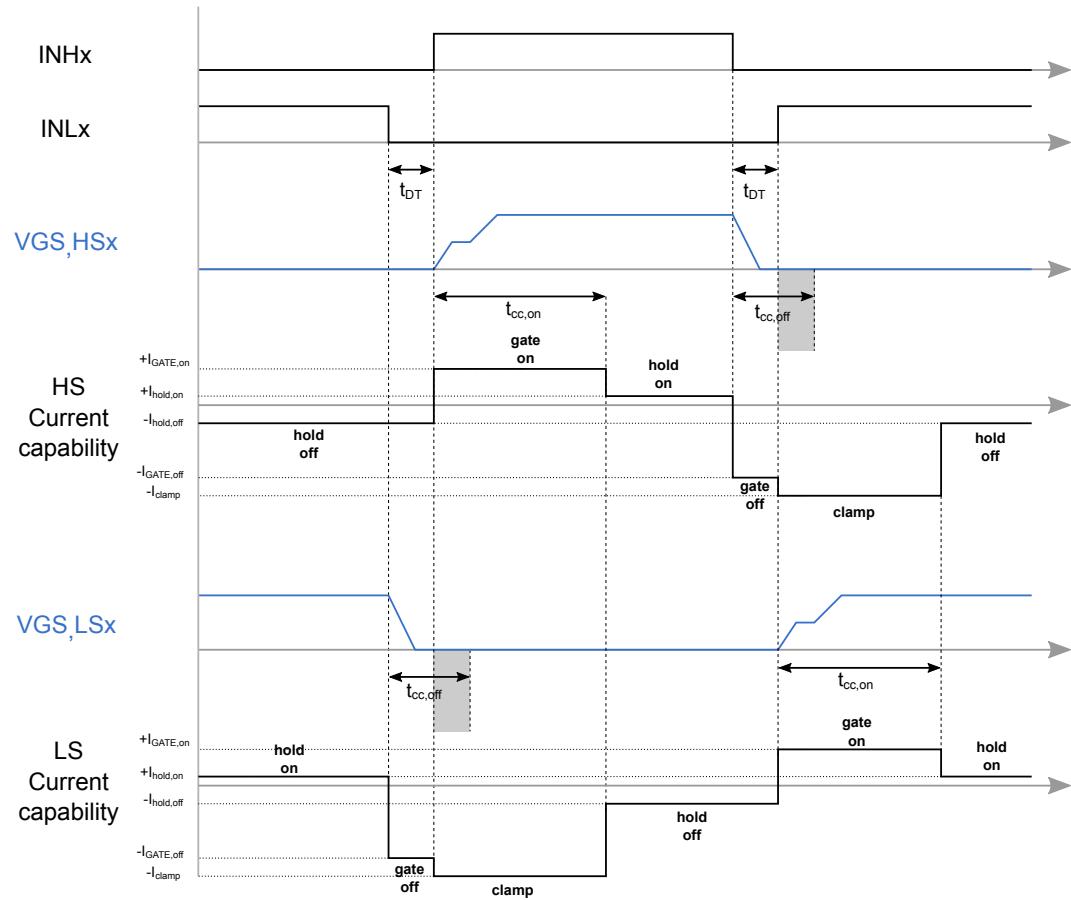

The gate driver turns on the respective MOSFET by sourcing the programmed current  $I_{GATE,ON}$  for a time equal to the programmed  $t_{cc,ON}$  time. After this time, the MOSFET's gate should be fully charged, so the driver reduces the source current to a hold value  $I_{hold,ON}$ .

The gate driver turns off the respective MOSFET by sinking the programmed current  $I_{GATE,OFF}$  for a time equal to the programmed  $t_{cc,OFF}$  time. After this time, the MOSFET's gate should be fully discharged, so the driver reduces the sink current to a hold value  $I_{hold,OFF}$ .

To avoid induced turn-on effects, during the turn-on phase of a MOSFET (that is, when a driver is forcing  $I_{GATE,ON}$ ) the complementary driver sinks the maximum available current  $I_{clamp}$  for the entire  $t_{cc,ON}$  duration.

In case the interlocking protection is disabled (see Section 5.2.3), the  $I_{clamp}$  is not used.

The relation between currents and timings as a function of the programmed configuration can be summarized as:

- The value of the source current and the sink current is programmed with the bits IGATE[3:0] in the DRV\_CFG register (see [Section 5.12.4.5](#)) and the relation between them depends on the DRV\_EQ\_SEL bit in the SYS\_CFG register (see [Section 5.12.4.6](#)):

- DRV\_EQ\_SEL = 0:  $I_{GATE,off} = 2 \times I_{GATE,on}$ , ensuring a turn-off faster than the turn-on.

- DRV\_EQ\_SEL = 1:  $I_{GATE,off} = I_{GATE,on}$ .

- According to the setting of DRV\_EQ\_SEL, the relation between the timing programmed using the TCC[3:0] bits in the DRV\_CFG register (see [Table 31](#)) is:

- DRV\_EQ\_SEL = 0:  $t_{cc,off} = 0.5 \times t_{cc,on}$ .

- DRV\_EQ\_SEL = 1:  $t_{cc,off} = t_{cc,on}$ .

In this case, it is also possible to select the  $t_{cc}$  value among two sets of values, using the TCC\_EQ\_SEL bit. The TCC\_EQ\_SEL bit has no effect when DRV\_EQ\_SEL = 0.

- The  $I_{hold,on}$  cannot be programmed and corresponds to the minimum source current that is 25 mA.