# Automotive-grade 650 V, 200 A trench gate field-stop M series low-loss IGBT die in D11 packing

#### **Features**

- AEC-Q101 qualified

- Low-loss series IGBT

- Low  $V_{CE(sat)} = 1.55 \text{ V (typ.)}$  at  $I_C = 200 \text{ A}$

- Positive V<sub>CE(sat)</sub> temperature coefficient

- Tight parameter distribution

- Maximum junction temperature: T<sub>J</sub> = 175 °C

- 6  $\mu$ s minimum short-circuit withstanding time at T<sub>J</sub> = 150 °C

#### **Applications**

Main inverter (electric traction)

### Description

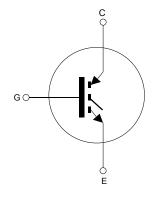

EGCD

This device is an IGBT developed using an advanced proprietary trench gate field-stop structure. The device is part of the M series IGBTs, which represent an optimal balance between inverter system performance and efficiency where the low-loss and the short-circuit functionality is essential. Furthermore, the positive  $V_{\text{CE(sat)}}$  temperature coefficient and the tight parameter distribution result in safer paralleling operation.

**Product status link**

STG200M65F2D11AG

| Product summary       |                  |  |

|-----------------------|------------------|--|

| Order code            | STG200M65F2D11AG |  |

| V <sub>CE</sub>       | 650 V            |  |

| I <sub>CN</sub> 200 A |                  |  |

| Die size              | 9.73 x 10.23 mm  |  |

| Packing D11           |                  |  |

# **Mechanical parameters**

**Table 1. Mechanical parameters**

| Parameter                      |                         | Value                   | Unit                   |

|--------------------------------|-------------------------|-------------------------|------------------------|

| Die size including scribe line | )                       | 9.73 x 10.23            | mm                     |

| Die thickness                  |                         | 70                      | μm                     |

| Front side passivation         |                         | Silicon                 | nitride                |

| Emitter pad size               | x4                      | 4.26 x 1.94             | mm                     |

| Emilier pau size               | including gate pad (x4) | 4.26 x 2.18             | mm                     |

| Gate pad size                  |                         | 1.66 x 0.83             | mm                     |

| Front side metallization       | Composition             | Al                      | Cu                     |

| Tront side metalization        | Thickness               | 4.5                     | μm                     |

| Back side metallization        | Composition             | AI/Ti/N                 | NiV/Ag                 |

| Back Side Metallization        | Thickness               | 0.80                    | μm                     |

| Die bond                       |                         | Electrically conductive | ve glue or soft solder |

| Recommended wire bonding       |                         | ≤ 500                   | μm                     |

DS14547 - Rev 1 page 2/11

# 2 Electrical ratings

Table 2. Absolute maximum ratings

| Symbol                            | Parameter                                                                                                      | Value      | Unit |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------|------------|------|

| V <sub>CES</sub>                  | Collector-emitter voltage (V <sub>GE</sub> = 0 V)                                                              | 650        | V    |

| V <sub>GE</sub>                   | Gate-emitter voltage                                                                                           | ±20        | V    |

| I <sub>CN</sub>                   | Continuous collector current at T = 100 °C                                                                     | 200        | Α    |

| I <sub>CP</sub> <sup>(1)(2)</sup> | Pulsed collector current                                                                                       | 600        | Α    |

| t <sub>sc</sub> (3)               | Short-circuit withstand time $V_{CC}$ = 360 V, $V_{GE}$ = 15 V, $V_{CE}$ (peak) ≤ 650 V, $T_{Jstart}$ ≤ 150 °C | 6          | μs   |

| TJ                                | Operating junction temperature range                                                                           | -40 to 175 | °C   |

- 1. Depending on thermal properties of assembly.

- 2. Pulse width limited by maximum junction temperature.

- 3. Not tested at chip level, verified by design/characterization. Allowed number of short-circuits < 1000; time between short-circuits > 1 s.

DS14547 - Rev 1 page 3/11

### 3 Electrical characteristics

$T_J$  = 25 °C unless otherwise specified.

Table 3. Static characteristics (tested on wafer unless otherwise specified)

| Symbol               | Parameter                            | Test conditions                                | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|------------------------------------------------|------|------|------|------|

| V <sub>BR(CES)</sub> | Collector-emitter breakdown voltage  | I <sub>C</sub> = 250 μA, V <sub>GE</sub> = 0 V | 650  |      |      | V    |

| V <sub>CE(sat)</sub> | Collector-emitter saturation voltage | V <sub>GE</sub> = 15 V, I <sub>C</sub> = 200 A |      | 1.55 |      | V    |

| V <sub>GE(th)</sub>  | Gate threshold voltage               | $V_{CE} = V_{GE}$ , $I_C = 3 \text{ mA}$       | 5    | 6    | 7    | V    |

| I <sub>CES</sub>     | Collector cut-off current            | V <sub>CE</sub> = 650 V, V <sub>GE</sub> = 0 V |      |      | 100  | μA   |

| I <sub>GES</sub>     | Gate-emitter leakage current         | V <sub>GE</sub> = ±20 V, V <sub>CE</sub> = 0 V |      |      | ±600 | nA   |

| R <sub>G</sub>       | Intrinsic gate resistance            | f = 1 MHz                                      |      | 2.5  |      | Ω    |

Table 4. Electrical characteristics (specified by design and evaluated by characterization, not tested in production)

| Symbol               | Parameter                                                                           | Test conditions                                                        | Min. | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| $V_{\text{CE(sat)}}$ | Collector-emitter saturation voltage                                                | V <sub>GE</sub> = 15 V, I <sub>C</sub> = 200 A                         | -    | 1.55 | 2.3  | V    |

|                      |                                                                                     | V <sub>GE</sub> = 15 V, I <sub>C</sub> = 200 A T <sub>J</sub> = 175 °C | -    | 1.95 |      | V    |

| C <sub>ies</sub>     | Input capacitance                                                                   |                                                                        | -    | 17.8 |      | nF   |

| C <sub>oes</sub>     | Output capacitance $V_{CE} = 25 \text{ V}, f = 1 \text{ MHz } V_{GE} = 0 \text{ V}$ |                                                                        | -    | 0.7  |      | nF   |

| C <sub>res</sub>     | Reverse transfer capacitance                                                        |                                                                        | -    | 0.37 |      | nF   |

| Qg                   | Total gate charge                                                                   |                                                                        | -    | 650  |      | nC   |

| Q <sub>ge</sub>      | Gate-emitter charge                                                                 | $V_{CC}$ = 400 V, $I_{C}$ = 200 A, $V_{GE}$ = 0 to 15 V                | -    | 130  |      | nC   |

| Q <sub>gc</sub>      | Gate collector charge                                                               |                                                                        | -    | 240  |      | nC   |

DS14547 - Rev 1 page 4/11

Table 5. Switching characteristics on inductive load (specified by design and evaluated by characterization, not tested in production)

| Symbol               | Parameter                 | Test conditions                                                                                            | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>d(on)</sub>   | Turn-on delay time        |                                                                                                            | -    | 134  | -    | ns   |

| t <sub>r</sub>       | Current rise time         | $V_{CC} = 300 \text{ V}, I_{C} = 200 \text{ A},$ $V_{GF} = -15 \text{ to } 15 \text{ V}, R_{G} = 2 \Omega$ | -    | 41   | -    | ns   |

| t <sub>d(off)</sub>  | Turn-off delay time       |                                                                                                            | -    | 151  | _    | ns   |

| t <sub>f</sub>       | Current fall time         | VGE13 to 13 V, NG - 2 M                                                                                    | -    | 88   | -    | ns   |

| E <sub>off</sub> (1) | Turn-off switching energy |                                                                                                            | -    | 5.5  | -    | mJ   |

| t <sub>d(on)</sub>   | Turn-on delay time        |                                                                                                            | -    | 173  | _    | ns   |

| t <sub>f</sub>       | Current rise time         | V = 200 V L = 200 A                                                                                        | -    | 32   | -    | ns   |

| t <sub>d(off)</sub>  | Turn-off delay time       | $V_{CC}$ = 300 V, $I_{C}$ = 200 A,<br>$V_{GE}$ = -15 to 15 V, $R_{G}$ = 2 $\Omega$ , $T_{J}$ = 175 °C      | -    | 58   | -    | ns   |

| t <sub>f</sub>       | Current fall time         |                                                                                                            | -    | 110  | -    | ns   |

| E <sub>off</sub> (1) | Turn-off switching energy |                                                                                                            | -    | 7.0  | -    | mJ   |

<sup>1.</sup> Including the tail of the collector current.

Note:

Switching characteristics and thermal properties are strongly dependent on module design and mounting technology. These results are obtained using an ST custom package.

DS14547 - Rev 1 page 5/11

# 4 Die layout

9.73

4.26

1.94

1.59

2.18

0.40

0.40

10.23

Folitter

Figure 1. Die drawing (dimensions are in mm)

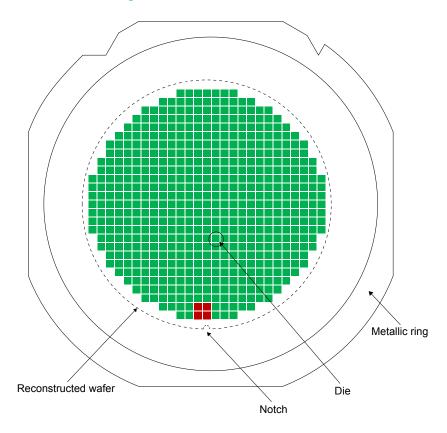

### 4.1 Packing information

Table 6. Die delivery

| Package option | Description                                                                                                                                                                                                                                                                                                                                 | Picture |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| D11            | Known good dice (KGD) 100% tested in UV cured reconstructed wafer, supported by metallic ring frame.  Reconstructed wafers are packed into a black box sealed under vacuum in a moisture barrier bag, with oxygen absorber, oxygen indicator, desiccant dry and HIC card.  Some inked dice can be present after final QA visual inspection. |         |

The wafers on frames are shipped inside a black box containing 25 wafers maximum.

DS14547 - Rev 1 page 6/11

Figure 2. Black box wafers

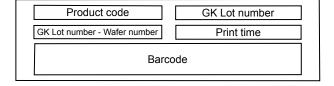

Figure 3. Notch orientation and label

#### Label

Picture not in scale, used for demonstration purposes only.

GADG051220231242GT

DS14547 - Rev 1 page 7/11

### 5 Additional information

### 5.1 Handling

- Products should only be handled in ESD-safe workstations. Standard ESD precautions and safe work environments are defined in MIL-HDBK-263.

- Products must be handled in a class 1000 clean room or higher.

- The single die should not be handled with tweezers. A vacuum wand with a non-metallic tip protected against electrostatic discharge must be used.

### 5.2 Wafer storage

To avoid contamination and/or degradation of the product after shipment, proper storage conditions are required.

- The recommended storage temperature is between 15 °C and 35 °C maximum.

- The recommended ambient humidity is between 10% and 70% maximum.

- The maximum storage time after the date of shipment from ST is 6 months.

DS14547 - Rev 1 page 8/11

### **Revision history**

Table 7. Document revision history

| Date        | Revision | Changes        |

|-------------|----------|----------------|

| 07-Dec-2023 | 1        | First release. |

DS14547 - Rev 1 page 9/11

### **Contents**

| 2 Electrical ratings 3 Electrical characteristics. 4 Die layout                                                            | 1   | Mech    | nanical parameters  | . 2 |

|----------------------------------------------------------------------------------------------------------------------------|-----|---------|---------------------|-----|

| 3 Electrical characteristics. 4 Die layout 4.1 Packing information 5 Additional information 5.1 Handling 5.2 Wafer storage | 2   | Elect   | rical ratings       | .3  |

| 4.1 Packing information  5 Additional information  5.1 Handling  5.2 Wafer storage                                         | 3   |         | -                   |     |

| 5 Additional information                                                                                                   | 4   | Die la  | ayout               | . 6 |

| <ul><li>5.1 Handling</li></ul>                                                                                             |     | 4.1     | Packing information | . 6 |

| 5.2 Wafer storage                                                                                                          | 5   | Addi    | tional information  | . 8 |

| -                                                                                                                          |     | 5.1     | Handling            | . 8 |

| Revision history                                                                                                           |     | 5.2     | Wafer storage       | . 8 |

|                                                                                                                            | Rev | ision l | history             | .9  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

DS14547 - Rev 1 page 11/11