#### Resonant half bridge controller

# STIPLES OF

#### **Features**

- Phase shift control (PSC) of resonant half-bridge for enhanced dynamic performance and wide input voltage range operation

- Up to 750 kHz maximum frequency with self-adjusting dead-time

- Burst mode operation enables very low open-load input power consumption

- Full protection set: Overcurrent, overpower, DC brown-OUT/IN, hard-switch prevention (HSP) function for anti-capacitive protection and safe startup

- 600 V rail compatible high-side gate driver with integrated bootstrap diode and high dV/dt immunity

- High-voltage startup

- X-capacitor discharge (STNRG599A)

- -300/800 mA high-side and low-side gate drivers with UVLO pull-down

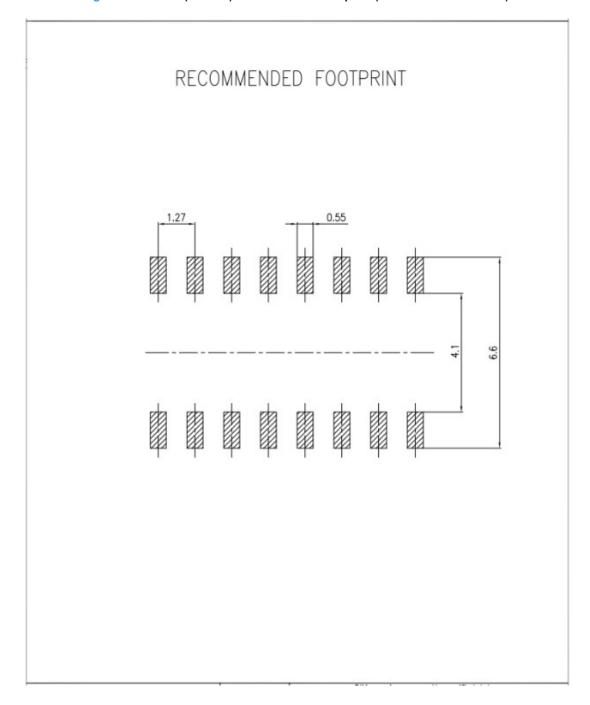

- SO16N package

#### Product status link

STNRG599

#### Product label

#### **Application**

- SMPS for led TV, desktop, and all-in-one PC

- High-power LED lighting modules

- Consumer and industrial SMPS

- High-end AC-DC adapter, open frame SMPS

#### **Description**

The STNRG599 is a double-ended controller designed for series-resonant topologies, supporting both LLC and LCC configurations.

The IC provides two complementary outputs that drive the high-side and low-side MOSFET 180° out of phase. The dead time inserted between the turn-off of one switch and the turn-on of the other is automatically adjusted to fit the transition times of the half-bridge midpoint, ensuring zero voltage switching across the entire operating range.

Output voltage (or current) regulation is obtained by directly controlling the phase shift between the half-bridge voltage and the resonant tank current. This proprietary control method, called phase shift control (PSC), enhances dynamic behavior and input voltage ripple rejection. Additionally, it makes the control loop with small sensitivity to component tolerance in the LLC / LCC resonant tank.

At light load, STNRG599 enters a controlled burst-mode operation, enabling intermittent converter operation. This reduces the average switching frequency and minimize the open-load input power.

STNRG599 is equipped with a full set of protection features: hard-switch prevention and anti-capacitive protection, 1<sup>st</sup> and 2<sup>nd</sup> level overcurrent protection, delayed shutdown and restart function based on pin DELAY (for user-programmable delayed shutdown upon overload with automatic restart). On the whole, OCP1, OCP2, and functions based on pin DELAY provide reliable and robust management of conditions such as short-time overcurrent, continuous overload, and severe output short-circuit.

DC brown-out/in protection is not latched. It is implemented at the input pin LINE, with constant hysteresis between brown-out and brown-in thresholds. The function prevents converter operation outside the selected DC input voltage range.

## Device and system block diagrams

AC mains HVVCC HV STARTUP POWER MANAGEMENT UVLO CBOOT STBY HVG ADAPTIVE DEAD TIME & GATE DRIVERS OUT LVG HS ZCD LS CONTROL LOGIC & PROTECTIONS DELAY ISEN\_DIS-T OSC OCP VIN LLC osc LINE

Figure 1. Device block diagram

**Table 1. Device information**

| Order code | XCAP discharge function | Package marking |

|------------|-------------------------|-----------------|

| STNRG599A  | Enabled                 | STNRG599A       |

| STNRG599B  | Disabled                | STNRG599B       |

DS15052 - Rev 3 page 2/49

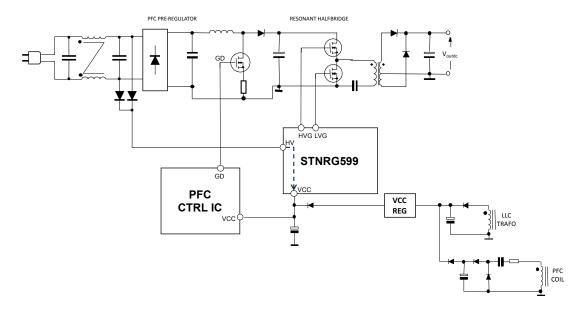

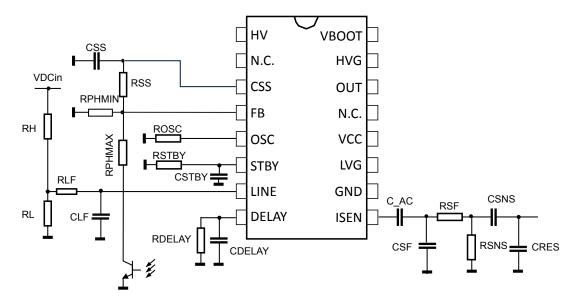

Figure 2. Typical system diagram

DS15052 - Rev 3 page 3/49

## Device pinout and pin description

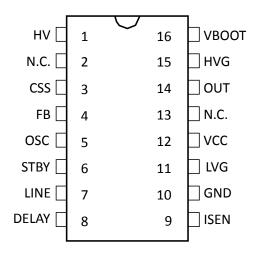

Figure 3. Device pinout (top view)

Table 2. Pin description

| N. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      | High-voltage start-up generator and AC voltage sensing input for X-capacitor discharge. The pin can withstand 800 V and must be connected to the AC side of the input rectifier bridge, via a pair of diodes (1N400x type) with common cathode, to sense the AC input voltage.                                                                                                                                                                                                                                                                                                        |

|    |      | If the pin voltage is higher than 30 V (max), then an internal circuit charges the external capacitor connected between the pin VCC and ground. The first charging period is done at low current (1 mA, typ) to guarantee IC safety, in case the pin VCC is shorted to ground. When VCC > 1.2 V (typ), the charging current increases to about 9 mA, and VCC is brought to VCCon (16.5 V, typ), at which point the control IC operation can start. After VCCon has been triggered, the HVSU generator is kept on for about 80 ms, then it is turned off.                              |

| 1  | HV   | In relation to fault management, each time a fault is released, if no other valid faults are present, the HVSU generator is turned on to charge VCC to VCCon. The purpose of the HVSU turn-on at fault release is twofold: one, it guarantees the necessary condition (VCC ≥ VCCon) for restarting the switching activity; two, it ensures that the restart of the switching activity, happening when VCC is close to VCCoff, cannot turn off the IC.                                                                                                                                 |

|    |      | X-capacitor discharge function (STNRG599A): when mains voltage disconnection is detected by the dedicated internal circuitry, the HVSU generator is activated to discharge the X-capacitors of the EMI filter to a safe level. In this way, the converter can meet safety regulations without using the traditional discharge resistor in parallel to the X-capacitor that is between the phase conductor and the neutral conductor, thus enabling low-power consumption in open load according to efficiency standards. X-capacitor discharge function is disabled in the STNRG599B. |

| 2  | N.C. | High-voltage spacer not internally connected. Purpose: to isolate high-voltage section and foster compliance with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    |      | Half-bridge soft-start.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3  | CSS  | The soft-start function is implemented by connecting a capacitor, $C_{SS}$ , from the pin CSS to ground, and a resistor, $R_{SS}$ , from the pin CSS to the pin FB. $R_{SS}$ and $C_{SS}$ set both the initial phase and the time constant of the soft start procedure.                                                                                                                                                                                                                                                                                                               |

|    |      | An internal switch (120 $\Omega$ , typ) fully discharges C <sub>SS</sub> each time the IC is turned off (that is, when VCC < VCCoff, ISEN > 1.5 V, LINE < 1.75 V, LINE > 3.1 V, DELAY > 1 V). In this way, a complete soft start occurs when the IC turns on again.                                                                                                                                                                                                                                                                                                                   |

DS15052 - Rev 3 page 4/49

| N. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      | For the sake of precision, after a fault, the restart of the switching activity is allowed only after $C_{SS}$ has been discharged to less than 100 mV (necessary condition for the restart of the switching activity).                                                                                                                                                                                                                                                                                   |

|    |      | The internal switch is also shortly activated (5 us, typ) when ISEN > 0.87 V (OCP1 event). In this way, the operating phase is temporarily increased and the power transfer is limited.                                                                                                                                                                                                                                                                                                                   |

|    |      | CSS > 1 V: STBY enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    |      | CSS > 300 mV: OCP1 and OCP2 enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    |      | The enable of STBY, OCP1, and OCP2 by CSS is reset by any fault (= event stops switching, apart from burst mode operation). In detail, the reset conditions are:  • DELAY = 1.75 V                                                                                                                                                                                                                                                                                                                        |

|    |      | VCC = VCCon after that VCC = VCCoff (while VCC is toggling and DELAY = GND)                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |      | LINE = 2.4 V after that LINE = 1.75 V (in case DELAY = GND and VCC > VCCon)                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |      | Feedback pin and min/max phase shift setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |      | The pin, which provides an accurate 2 V voltage reference, is connected to the collector of the optocoupler that sustains the feedback loop. The current sunk by the optocoupler, i.e. sourced by the pin, is mirrored inside the IC to build the feedback signal.                                                                                                                                                                                                                                        |

| 4  | FB   | A resistor, R <sub>PHMIN</sub> , between pin FB and ground defines the minimum feedback current mirrored into the IC and, therefore, the minimum phase shift the control loop can set. In this way, the maximum power that can be transferred is set.                                                                                                                                                                                                                                                     |

|    |      | A resistor, R <sub>PHMAX</sub> , in series between pin FB and the collector of the optocoupler, is necessary to limit the current sourced by the pin itself. The typical maximum sourced current is 500 uA, so the typical value of the resistor is 4 k $\Omega$ . This resistor also defines the maximum phase shift the control loop can set (the maximum phase shift defined by R <sub>PHMAX</sub> is usually overwritten by the burst mode threshold that is programmed at pin STBY). Max C = 100 pF. |

|    |      | Internal oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5  | osc  | The current source for the internal oscillator is programmed by the resistor, $R_{OSC}$ , connected between the pin and ground. A capacitor in parallel may be required for filtering purposes.  Max C = 100 pF. Max sourced current = 500 uA.                                                                                                                                                                                                                                                            |

|    |      | Burst mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

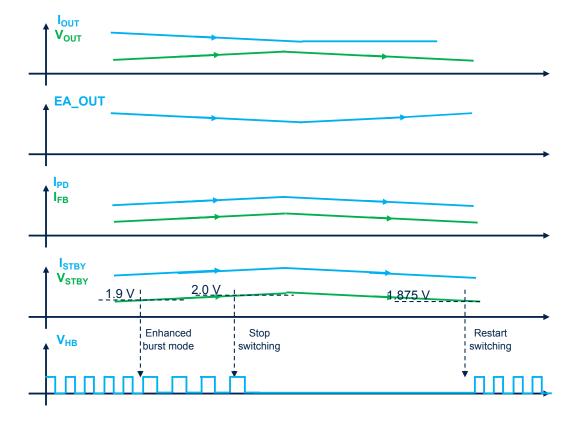

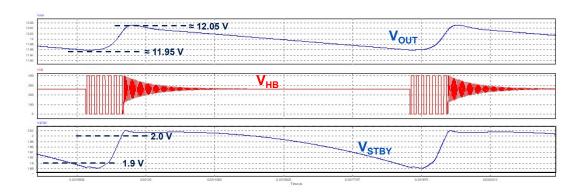

|    |      | A resistor, $R_{STBY}$ , between pin STBY and ground, defines the feedback current and the corresponding phase shift at which burst mode operation starts. When $V_{STBY}$ goes above 2 V, the switching activity is stopped. The voltage hysteresis on pin STBY is 125 mV: the switching activity is restarted when $V_{STBY}$ goes below 1.875 V.                                                                                                                                                       |

| 6  | STBY | Enhanced burst mode: as the voltage on pin STBY rises across 1.9 V, the feedback current mirrored into the IC is reduced by 30% to reduce the phase shift between the half-bridge voltage and the resonant tank current, during the switching packet, thus increasing the energy transferred by each switching cycle.                                                                                                                                                                                     |

|    |      | The 30% reduction of the feedback current mirrored into the IC is removed when $V_{STBY}$ goes above 2.0 V, that is, the threshold at which the switching activity is stopped.                                                                                                                                                                                                                                                                                                                            |

|    |      | Burst mode operation is disabled as long as $V_{CSS} < 1 \text{ V. STBY}$ is enabled when $V_{CSS}$ goes above 1 V (reset by DELAY = 1.75 V). Internal replica of $V_{STBY}$ is bottom clamped. The external effect is that, when VCC reaches 6 V during turn-on, $V_{STBY}$ rises to about 1.5 V · $R_{STBY}/(R_{STBY}+R_{INT})$ with $R_{INT}$ = 102 k $\Omega$ (typ).                                                                                                                                  |

| 7  | LINE | Line sensing input: DC brown-out/in + OVP protection + Feedback failure disconnection                                                                                                                                                                                                                                                                                                                                                                                                                     |

DS15052 - Rev 3 page 5/49

| N. | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |       | The pin monitors the input voltage of the half-bridge by means of an external resistive divider. The IC is enabled when $V_{LINE} > 2.4 \text{ V}$ (typ) and disabled when $V_{LINE} < 1.75 \text{ V}$ (typ). The soft-start capacitor $C_{SS}$ is completely discharged when $V_{LINE} < 1.75 \text{ V}$ , so that the whole soft-start process can take place when $V_{LINE} > 2.4 \text{ V}$ . A small RC filter (R up to 100 $\Omega$ , C up to 10 nF) from pin LINE to ground might be needed to filter noise.                                                                              |

|    |       | If the pin is pulled to 3.1 V (typ, 200 mV hysteresis), then the turn-off procedure based on pin DELAY is activated: the switching activity is immediately stopped, the soft-start capacitor $C_{SS}$ is completely discharged, and the internal 250 uA current source is kept on until $V_{DELAY}=1.75\ V$ . As the voltage on the pin exceeds 1.75 V, the internal 250 uA current source is turned off. The voltage on the pin then decays because of $R_{DELAY}$ and, also in this case, the IC is restarted, following the complete soft-start process, when $V_{DELAY}$ falls below 0.24 V. |

|    |       | In both cases:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    |       | <ul> <li>when the fault is triggered (LINE falling below 1.75 V or LINE rising above 3.1 V), the switching activity is stopped after the running LVG / HVG pulse pair is completed by the control loop</li> <li>when the fault is released (LINE rising above 2.4 V or LINE falling below 2.9</li> </ul>                                                                                                                                                                                                                                                                                         |

|    |       | V), the HVSU can be turned on to bring VCC to VCCon. At this point, the switching activity can restart (provided there is no other active fault).                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    |       | The pin is internally clamped to 3.4 V, typ, to manage feedback failure disconnection of the low-side resistor of the external divider on the input voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    |       | Delayed shutdown and restart upon overload.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    |       | A capacitor, C <sub>DELAY</sub> , and a resistor, R <sub>DELAY</sub> , are connected from this pin to ground to set:                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|    |       | the maximum duration of an overcurrent condition before the IC stops switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    |       | and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |       | the delay after which the IC restarts switching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

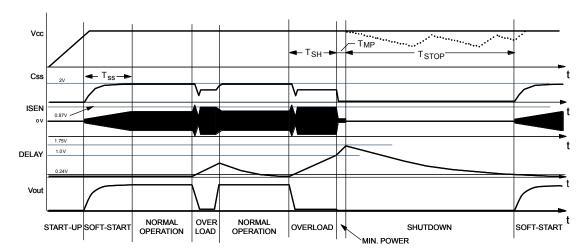

|    |       | Each time $V_{ISEN}$ > 0.87 V, which is an OCP1 event, $C_{DELAY}$ is charged by an internal 250 $\mu$ A current source for 5 us (typ.) and then it is slowly discharged by $R_{DELAY}$ .                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |       | When the voltage on the pin reaches 1 V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |       | + the soft-start capacitor $C_{SS}$ is completely discharged (internal switch, 120 $\Omega$ , typ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |       | and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |       | • the internal 250 $\mu$ A current source is kept on until V <sub>DELAY</sub> = 1.75 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8  | DELAY | As the voltage on the pin exceeds 1.75 V, the IC stops switching (after the running LVG / HVG has elapsed) and the internal 250 uA current source is turned off. The voltage on the pin then decays because of $R_{DELAY}$ . When $V_{DELAY}$ reaches 0.24 V, the IC is restarted following the complete soft-start process. In this way, under short-circuit conditions, the converter works intermittently with very low input average power. The switching activity is inhibited when $V_{DELAY}$ is falling from 1.75 V to 0.24 V.                                                           |

|    |       | If the function is not used, then DELAY can be connected to ground. In this case (DELAY = GND), the DELAY procedure cannot take place when the switching activity is stopped by an OCP2 event (ISEN = 1.5 V) and/or an OVP event (LINE = 3.1 V). Two events can set the HVSU generator:                                                                                                                                                                                                                                                                                                          |

|    |       | <ul> <li>VCC = VCCoff (occurring when VCC is sustained by the switching activity of the converter, because such switching activity has been stopped by the fault event),</li> <li>LINE toggling below 1.75 V and above 2.4 V (to be done at application level, to solve the latch that occurs in case VCC cannot reach VCCoff).</li> </ul>                                                                                                                                                                                                                                                       |

|    |       | When DELAY = GND, the internal 250 uA current source that is activated by OCP2 or OVP is turned off at VCC = VCCon, after the activation of the HVSU generator when VCC has reached VCCoff.                                                                                                                                                                                                                                                                                                                                                                                                      |

DS15052 - Rev 3 page 6/49

| N. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      | If DELAY = GND and VCC cannot reach VCCoff, then any fault entailing DELAY would latch the converter. The latch can be solved by sensing the fault release at application level and setting a low / high transition to the pin LINE.                                                                                                                                                                             |

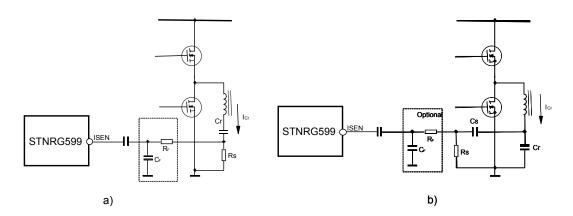

|    |      | Voltage sensing input of resonant tank current.                                                                                                                                                                                                                                                                                                                                                                  |

|    |      | The resonant tank current can be sensed through a series resistor (lossy sensing) or through a capacitive shunt (lossless sensing). The signal is used to implement the phase-shift control methodology and some protection features. It must sense the resonant current tank: it cannot be shorted to ground or left open. It must be AC coupled by means of a ceramic capacitor around 10 nF.                  |

|    |      | If the voltage at the input terminal of the AC coupling capacitor exceeds 0.87 V (corresponding to OCP1 fault), then two actions take place:                                                                                                                                                                                                                                                                     |

|    |      | • the soft-start capacitor $C_{SS}$ is discharged by the internal switch (120 $\Omega$ ) at pin CSS for 5 us (typ), and then it is recharged by $R_{SS}$ .                                                                                                                                                                                                                                                       |

|    |      | • the capacitor $C_{DELAY}$ is charged by an internal 250 $\mu$ A current source for 5 us (typ.), and then it is slowly discharged by $R_{DELAY}$ .                                                                                                                                                                                                                                                              |

|    |      | The $C_{SS}$ discharge temporarily increases the current mirrored into the pin FB, so that the phase shift slightly increases, thus limiting the transferred power. Under output short-circuit conditions, the resulting operation of the converter is a nearly constant peak primary current. This condition is allowed for a maximum time set by the delayed shutdown function (see description of pin DELAY). |

|    |      | Second-level overcurrent protection, OCP2, is also implemented: if the current keeps building up despite OCP1 protection, or if a large current spike is observed, a comparator referenced to 1.5 V can be triggered (voltage at the input of the AC coupling capacitor). In this case, the following actions take place:                                                                                        |

| 9  | ISEN | <ul> <li>switching is immediately stopped, and a restart procedure based on pin DELAY is activated (HVG pulse reset by OCP2, not by control loop)</li> <li>the soft-start capacitor C<sub>SS</sub> is completely discharged, and the internal 250 uA current source is kept on until V<sub>DELAY</sub> = 1.75 V.</li> </ul>                                                                                      |

|    |      | As the voltage on the pin exceeds 1.75 V, the internal 250 uA current source is turned off. The voltage on the pin then decays because of $R_{DELAY}$ and, the IC is restarted, following the complete soft-start process, when $V_{DELAY}$ falls below 0.24 V. The switching activity is also conditioned by CSS: it is not allowed when CSS < 0.1 V.                                                           |

|    |      | OCP1 and OCP2 are disabled when voltage at pin CSS is less than 300 mV.                                                                                                                                                                                                                                                                                                                                          |

|    |      | An OCP1 fault is not latched (event not stored in a flip-flop) within the IC: each time the voltage at the input of the AC coupling capacitor at pin ISEN reaches 0.87 V, an internal pulse lasting 5 us is generated to perform the actions described above ( $C_{SS}$ discharge and $C_{DELAY}$ charge, for 5 us).                                                                                             |

|    |      | An OCP2 fault is latched (event stored in a flip-flop) within the IC: when the voltage at the input of the AC coupling capacitor at pin ISEN reaches 1.5 V, an internal flip-flop is set; such flip-flop is usually reset by DELAY = 1.75 V.                                                                                                                                                                     |

|    |      | In case DELAY = GND, the flip-flip is reset when VCC = VCCon, after the HVSU has been turned on at VCC = VCCoff.                                                                                                                                                                                                                                                                                                 |

|    |      | If DELAY = GND and VCC cannot reach VCCoff, then the reset must be forced at application level with a low / high transition at pin LINE.                                                                                                                                                                                                                                                                         |

|    |      | VCC = VCCon after VCC = VCCoff and LINE toggling low /high are mechanisms to turn off the internal 250 uA current source (DELAY = GND and/or VCC > VCCoff).                                                                                                                                                                                                                                                      |

|    |      | The signal at pin is also used to implement the Hard Switch Prevention (HSP) / Anti-Capacitive Protection (ACP) function.                                                                                                                                                                                                                                                                                        |

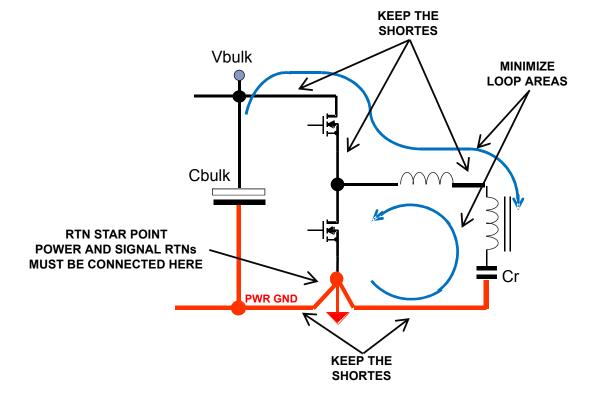

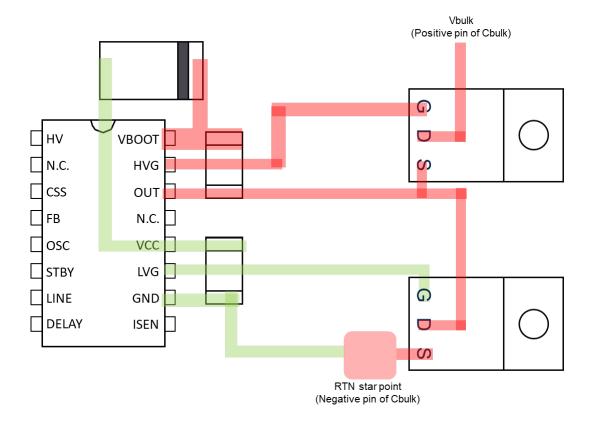

| 10 | GND  | IC ground. The pin collects both the return currents of the low side gate driver (pin LVG) and of all the IC biasing circuitry. External biasing components that are referenced to ground must be directly connected to pin GND and the PCB trace(s) must be kept separated from any PCB traces carrying pulsed return currents.                                                                                 |

| 11 | LVG  | Output of the low side gate driver.                                                                                                                                                                                                                                                                                                                                                                              |

DS15052 - Rev 3 page 7/49

| N. | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                        |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |       | The driver is capable of 0.3 A source and 0.8 A sink peak current (minimum values, including temperature variation) to drive the low side MOSFET of the half-bridge leg. The pin is actively pulled to ground during UVLO. There is no timeout on the pulse length. The LVG pulse is reset by the control loop.                                                                                 |

|    |       | IC supply voltage.                                                                                                                                                                                                                                                                                                                                                                              |

|    |       | The pin feeds both the signal and biasing part of the IC and the low side gate driver (pin LVG). A bypass ceramic capacitor (100 nF, typ.), from the pin to ground is recommended, while an electrolytic capacitor is necessary to collect the charge from the HVSU generator and to sustain IC operation.                                                                                      |

| 12 | VCC   | At VCC = VCCon (and during normal operation), the switching activity is conditioned by the state of the pins LINE, DELAY, ISEN, CSS according to the following (see corresponding pin description for details):  LINE < 1.75 V or > 3.10 V: no switch  DELAY falling from 1.75 V to 0.24 V: no switch  ISEN > 1.5 V (& CSS > 300 mV): no switch  CSS < 0.1 V: necessary condition for switching |

|    |       | During a fault condition, in which VCC is charged / discharged between VCCon and VCCoff, when VCCoff is triggered, CSS is discharged.                                                                                                                                                                                                                                                           |

|    |       | At VCC = VCCoff, the HVSU generator is turned on.                                                                                                                                                                                                                                                                                                                                               |

|    |       | At VCC = VCCon, the internal state is reset. The pins LINE, DELAY, ISEN, CSS are internally polled before the pin VCC reaches VCCon.                                                                                                                                                                                                                                                            |

| 13 | N.C.  | High-voltage spacer not internally connected. Purpose: to isolate high-voltage section and foster compliance with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                            |

| 14 | OUT   | Floating ground of the high side gate driver. The pin collects the return current of the high side gate driver. Careful layout of the PCB trace is necessary to avoid large negative spikes that can damage the IC, considering that the pin is subject to the full voltage swing of the half-bridge leg.                                                                                       |

|    |       | Output of the high side gate driver.                                                                                                                                                                                                                                                                                                                                                            |

| 15 | HVG   | The driver is capable of a 0.3 A source and a 0.8 A sink peak current (minimum values, including temperature variation) to drive the high side MOSFET of the half-bridge leg. An internal resistor connected to pin OUT guarantees that the pin is not floating during UVLO. There is no timeout on the pulse length. The HVG pulse is reset by the control loop or by OCP2.                    |

| 16 | VBOOT | Floating supply voltage of the high side gate driver. The external bootstrap capacitor connected between this pin and pin OUT must be fed by an external bootstrap diode.                                                                                                                                                                                                                       |

DS15052 - Rev 3 page 8/49

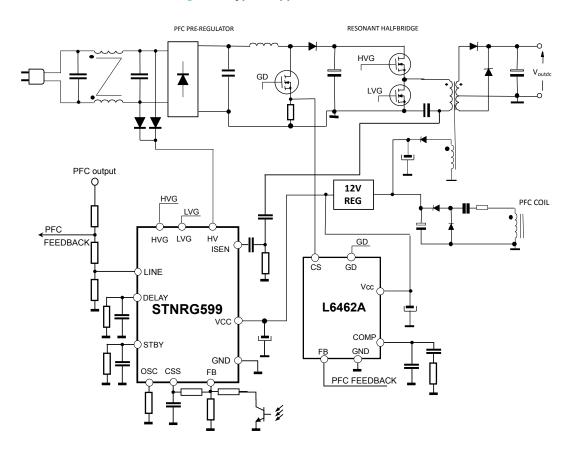

## Typical application schematic

Figure 4. Typical application schematic

Note: At both pins LINE and ISEN, an RC filter can be added to suppress high frequency noise usually generated by the switching activity of the power stages. For pin ISEN, RC filter must be placed between the current sensing resistor and the AC coupling capacitor (that is, it must not be directly connected to the pin itself), and its time constant not exceed about 200 nsec, to avoid impacting the control loop. There are no special requirements for the time constant of the RC filter at pin LINE.

DS15052 - Rev 3 page 9/49

## 4 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol                                                                   | Pin                                              | Parameter                                           | AMR         | Unit |  |

|--------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-------------|------|--|

| V <sub>HV</sub>                                                          | 1                                                | Voltage range                                       | -1 to 800   | V    |  |

| V <sub>VBOOT</sub> 16                                                    |                                                  | Floating supply voltage (referred to GND)           | -1 to 620   | V    |  |

| V <sub>HVG</sub> 15                                                      | High side gate driver                            | V <sub>OUT</sub> -0.3 to<br>V <sub>VBOOT</sub> +0.3 | V           |      |  |

| VOUT         14           dVOUT /dt         14           VVCC         11 | OUT 14 Floating ground voltage (referred to GND) |                                                     | -3 to 600   | V    |  |

|                                                                          | 14                                               | Floating ground max. slew rate                      | 50          | V/ns |  |

|                                                                          | 11                                               | IC Supply voltage                                   | -0.3 to 20  | V    |  |

| $V_{LVG}$                                                                | 12                                               | Low side gate driver                                | -0.3 to Vcc | V    |  |

| V <sub>ISEN</sub>                                                        | 9                                                | Current sense voltage                               | -3 to 5.5   | V    |  |

| V <sub>LINE</sub>                                                        | 7                                                | Voltage range                                       | -0.3 to 3.6 | V    |  |

| I <sub>FB</sub> 4                                                        |                                                  | Maximum source current                              | 2           | mA   |  |

| Other pins                                                               | 3, 4, 5, 6, 8                                    | Analog inputs & outputs voltage range               | -0.3 to 3.6 | V    |  |

| ESD HBM                                                                  | 14-15                                            | According to ANSI/ESDA/JEDEC                        | ±900        | V    |  |

| LOD HOW                                                                  | 1, 3 to 12, 16                                   | JS-001-2014                                         | ±2000       | V    |  |

Stressing the device above the AMR may cause permanent damage of the device. Device operation at the AMR may affect the device reliability.

DS15052 - Rev 3 page 10/49

## 5 Thermal data

Table 4. Thermal data

| Symbol                | Parameter                                                                     | Value      | Unit |

|-----------------------|-------------------------------------------------------------------------------|------------|------|

| R <sub>th j-amb</sub> | R <sub>th j-amb</sub> Max. thermal resistance, junction-to-ambient (SO16) 120 |            | °C/W |

| P <sub>tot</sub>      | Power dissipation @Tamb = 50°C (SO16)                                         | 0.83       | W    |

| Tj                    | Junction temperature operating range                                          | -40 to 150 | °C   |

| T <sub>stg</sub>      | Storage temperature                                                           | -55 to 150 | °C   |

DS15052 - Rev 3 page 11/49

## 6 Electrical characteristics

$(T_j$  = -40 to +125 °C,  $V_{HV}$  > 25 V,  $V_{VCC}$  =  $V_{VBOOT}$  = 15 V,  $C_{HVG}$  =  $C_{LVG}$  = 1 nF; unless otherwise specified)

**Table 5. Electrical characteristics**

| Symbol                  | Parameter                                                                                                                | Test condition                                                    | Min. | Тур.     | Max.     | Unit |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|----------|----------|------|

| IC SUPPLY VOLTAGE       |                                                                                                                          | 1                                                                 |      | <u> </u> | <u> </u> |      |

| V <sub>VCC</sub>        | Operating range                                                                                                          | After turn-on                                                     | 10   |          | 19       | V    |

| V <sub>VCCOn</sub>      | Turn-on threshold                                                                                                        | Voltage rising <sup>(1)</sup>                                     | 15.5 | 16.5     | 17.5     | V    |

| V <sub>VCCOff</sub>     | Turn-off threshold                                                                                                       | Voltage falling <sup>(1)</sup>                                    | 9    | 9.5      | 10       | V    |

| SUPPLY CURRENT          | <u>'</u>                                                                                                                 |                                                                   | '    |          |          |      |

| I <sub>op</sub>         | Operating supply current                                                                                                 | LVG and HVG unloaded                                              |      | 1.5      |          | mA   |

| I <sub>FAULT</sub>      | Residual consumption                                                                                                     | V <sub>DELAY</sub> > 1.75 V or<br>V <sub>LINE</sub> < 1.75 V      |      | 800      |          | μA   |

| Iq                      | Quiescent current (excluding I <sub>OSC</sub> , I <sub>FB</sub> )                                                        | Idle during burst mode T <sub>j</sub> = 27 °C                     |      | 1        |          | mA   |

| HIGH VOLTAGE START-UP   | CURRENT GENERATO                                                                                                         | DR .                                                              |      |          | -        |      |

| V <sub>HV_BD</sub>      | Breakdown voltage                                                                                                        | I <sub>HV</sub> < 100 μA                                          | 800  |          |          | V    |

| Vvcc_so                 | V <sub>VCC</sub> switch<br>overvoltage: V <sub>VCC</sub><br>at which I <sub>HV_ON</sub><br>changes from 1<br>mA to 10 mA |                                                                   |      | 1.1      |          | V    |

| I <sub>HV_ON</sub>      | Current sunk by                                                                                                          | V <sub>HV</sub> >= 30 V<br>V <sub>VCC</sub> < V <sub>VCC_SO</sub> | 0.4  | 1        | 1.7      | mA   |

| ·nv_on                  | pin HV to charge<br>pin VCC                                                                                              | V <sub>HV</sub> >= 30 V<br>16.5 V < V <sub>VCC</sub> < 17.5 V     | 5    | 9.3      | 14       | mA   |

| I <sub>HV_OFF</sub>     | Off-state leakage current                                                                                                | V <sub>HV</sub> = 400 V                                           |      | 20       | 40       | μA   |

| Т <sub>тоит</sub>       | Generator shutdown timeout                                                                                               | After V <sub>VCC</sub> > V <sub>VCC_ON</sub>                      | 60   | 80       | 100      | ms   |

| X-CAPACITORS DISCHARG   | E (STNRG599A)                                                                                                            |                                                                   |      |          |          |      |

| $V_{HVmin}$             | Peak residual voltage (application parameter: V <sub>HVmax</sub> after 1 s from mains disconnection)                     | I <sub>HV, DIS</sub> > 4.2 mA                                     |      |          | 40       | V    |

| I <sub>HV, DIS</sub>    | Discharge current                                                                                                        | V <sub>HV</sub> = 45 V                                            | 4.2  |          |          | mA   |

| T <sub>DET</sub>        | Detection time (no XCAP if V <sub>HV</sub> missing for less than T <sub>DET</sub> )                                      |                                                                   | 48   | 64       |          | ms   |

| LINE - HB INPUT VOLTAGE | SENSING                                                                                                                  |                                                                   |      |          |          |      |

| V <sub>LINE_E</sub>     | Enable voltage                                                                                                           | Voltage rising <sup>(2)</sup>                                     | 2.33 | 2.4      | 2.47     | V    |

| V <sub>LINE_D</sub>     | Disable voltage                                                                                                          | Voltage falling <sup>(2)</sup>                                    | 1.7  | 1.75     | 1.8      | V    |

DS15052 - Rev 3 page 12/49

| Symbol                                  | Parameter                                                        | Test condition                                                                      | Min. | Тур. | Max. | Unit |

|-----------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>LINE_PROT</sub>                  | Protection threshold                                             | Voltage rising <sup>(2)</sup>                                                       | 3.01 | 3.1  | 3.19 | V    |

| V <sub>LINE_PROT_DIS</sub>              | Disable of protection threshold                                  | Voltage falling <sup>(2)</sup>                                                      | 2.81 | 2.9  | 2.99 | V    |

| V <sub>LINE_CLAMP</sub>                 | Protection clamp                                                 | Voltage rising <sup>(2)</sup>                                                       | 3.2  | 3.4  | 3.6  | V    |

| ILINE_CLAMP                             | Clamp current                                                    |                                                                                     |      | 0.5  |      | mA   |

| ADAPTIVE DEAD-TIME                      |                                                                  |                                                                                     |      |      |      | ı    |

|                                         | Maximum dead-<br>time, HB rising                                 |                                                                                     | 700  |      |      | ns   |

| T <sub>D_max</sub>                      | Max variation<br>between DT on<br>rising and DT on<br>falling    | DT on falling copied from<br>measured DT on rising.<br>DT on falling > DT on rising |      |      | 10   | %    |

|                                         | Minimum dead-<br>time,<br>HB rising                              | Assuming gate fall time +<br>MOSFET off time + HB<br>transition time ≈ 170 ns       |      | 270  | 300  | ns   |

| $T_{D\_min}$                            | Max variation<br>between DT on<br>rising and DT on<br>falling    | DT on falling copied from<br>measured DT on rising.<br>DT on falling > DT on rising |      |      | 20   | %    |

| T <sub>D_out</sub>                      | Watch dog on dead-time                                           | No HSP / ACP                                                                        |      | 1.2  |      | us   |

| FEEDBACK INPUT (pin FB)                 |                                                                  |                                                                                     |      |      |      |      |

| $V_REF$                                 | Voltage                                                          |                                                                                     | 1.93 | 2    | 2.07 | V    |

| * REF                                   | reference <sup>(3)</sup>                                         | I <sub>REF</sub> = -500 uA                                                          | 1.93 | 2    | 2.07 | V    |

| I <sub>FBmax</sub>                      |                                                                  |                                                                                     | 500  |      |      | uA   |

| STBY FUNCTION                           |                                                                  |                                                                                     |      |      |      |      |

| K <sub>STBY</sub>                       | Mirroring ratio I <sub>STBY</sub> /I <sub>FB</sub>               | I <sub>FB</sub> > 50 uA                                                             |      | 0.5  |      |      |

| V <sub>STBY_2V0</sub> <sup>(4)</sup>    | Stop switching threshold V <sub>CSS</sub> > V <sub>CSS_BME</sub> | Voltage rising <sup>(5)</sup>                                                       | 1.93 | 2.00 | 2.07 | V    |

| V <sub>STBY_2V0_LH</sub> <sup>(4)</sup> | Local hysteresis of burst mode comparator                        |                                                                                     | 10   | 25   | 45   | mV   |

| V <sub>STBY_1V9</sub> <sup>(4)</sup>    | Enhanced burst mode comparator                                   | Voltage rising <sup>(5)</sup>                                                       | 1.83 | 1.90 | 1.97 | V    |

| V <sub>STBY_1V9_LH</sub> <sup>(4)</sup> | Local hysteresis of burst mode comparator                        |                                                                                     | 10   | 25   | 40   | mV   |

| %I <sub>FB_RED</sub>                    | % I <sub>FB</sub> reduction                                      | By design (not tested)                                                              |      | 30   |      | %    |

| V <sub>CSS_BME</sub>                    | V <sub>CSS</sub> above which BM is enabled                       | Voltage rising                                                                      | 09   | 1    | 1.1  | V    |

| COSC MANAGEMENT AT T                    | URN OFF                                                          |                                                                                     |      |      |      |      |

| T <sub>VTIME_RESET</sub>                | Time V <sub>TIME</sub> kept<br>zero after turn-off<br>of LVG/HVG |                                                                                     |      | 50   |      | ns   |

| PIN OSC                                 |                                                                  |                                                                                     | 1    | 1    | 1    | 1    |

DS15052 - Rev 3 page 13/49

| Symbol                        | Parameter                                                 | Test condition                                                             | Min.         | Тур.          | Max.  | Unit |

|-------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------|--------------|---------------|-------|------|

| V <sub>REF_OSC</sub>          | Reference voltage <sup>(3)</sup>                          |                                                                            | 1.85         | 2.00          | 2.15  | V    |

| CSS - SOFT START              | '                                                         |                                                                            |              |               |       |      |

| I <sub>LEAK</sub>             | Open state current                                        | V <sub>CSS</sub> = 2 V                                                     |              |               | 1     | μA   |

| R <sub>D_CSS</sub>            | Soft-start internal discharge resistor                    |                                                                            |              | 120           |       | Ω    |

| T <sub>DISCH</sub>            | C <sub>SS</sub> discharge duration                        | V <sub>ISEN</sub> > V <sub>ISEN_OCP1</sub>                                 |              | 5             |       | μs   |

| ISEN – ZERO CURRENT CO        | MPARATOR                                                  |                                                                            |              |               |       |      |

| V <sub>ISENth_PS</sub>        | Zero-current<br>threshold for phase<br>shift control loop | AC value.<br>Internal DC value ≈ 1.65 V                                    | -2           | 0             | 2     | mV   |

| Note: specified voltage value | s are referred to the inp                                 | out of the series capacitance at                                           | pin ISEN, no | ot to the pii | 7.    |      |

| ISEN - PROTECTION COMP        | PARATORS                                                  |                                                                            |              |               |       |      |

| I <sub>SEN</sub>              | Input impedance                                           |                                                                            |              | 100           |       | kΩ   |

| V <sub>ISEN_OCP1</sub>        | OCP1 threshold                                            | Voltage rising <sup>(6)</sup>                                              | 0.820        | 0.870         | 0.920 | V    |

| V <sub>ISEN_OCP2</sub>        | OCP2 threshold                                            | Voltage rising <sup>(6)</sup>                                              | 1.4          | 1.5           | 1.6   | V    |

| V <sub>CSS_EN_OCP</sub>       | OCP1,2 enable                                             |                                                                            |              | 300           |       | mV   |

| V <sub>pos</sub>              | Zero current for ACP/HSP                                  |                                                                            | 20           | 40            | 60    | mV   |

| V <sub>neg</sub>              | Zero current for ACP/HSP                                  |                                                                            | -60          | -40           | -20   | mV   |

| Note: specified voltage value | s are referred to the inp                                 | out of the series capacitance at                                           | pin ISEN, no | ot to the pii | า     |      |

| DELAY – DELAYED SHUT D        | OWN FUNCTION                                              |                                                                            |              |               |       |      |

| I <sub>LEAK</sub>             | Open-state current                                        | V <sub>DELAY</sub> = 1.8 V                                                 |              |               | -0.5  | μA   |

| I <sub>CHARGE</sub>           | Charge current                                            | V <sub>DELAY</sub> = 1 V,<br>V <sub>ISEN</sub> = 0.85 V                    | 180          | 250           | 320   | μA   |

| V <sub>TH1</sub>              | Threshold at which DELAY procedure is no more reversible  | Voltage rising (7)                                                         | 0.95         | 1.0           | 1.05  | V    |

| V <sub>TH2</sub>              | Threshold at which switching activity is stopped          | Voltage rising <sup>(7)</sup>                                              | 1.65         | 1.75          | 1.85  | V    |

| V <sub>TH3</sub>              | Restart threshold                                         | Voltage falling <sup>(7)</sup>                                             | 0.14         | 0.24          | 0.34  | V    |

| LOW-SIDE GATE DRIVER (v       | oltages referred to GN                                    | D)                                                                         | 1            | 1             | 1     | 1    |

| V <sub>LVGL</sub>             | Output low voltage                                        | I <sub>sink</sub> = 100 mA                                                 |              | 0.7           | 1.5   | V    |

| V <sub>LVGH</sub>             | Output high voltage                                       | I <sub>source</sub> = 10 mA<br>V <sub>VCC</sub> = 15 V                     | 14.0         | 14.9          |       | V    |

| t <sub>f</sub>                | Voltage fall time                                         | From 13.5 V to 1.5 V                                                       |              | 25            | 50    | ns   |

| t <sub>r</sub>                | Voltage rise time                                         | From 1.5 V to 13.5 V                                                       | 30           | 43            | 75    | ns   |

|                               | UVLO saturation <sup>(8)</sup>                            | V <sub>VCC</sub> = 0.5 V, I <sub>sink</sub> = 1 mA                         |              | 1             | 1.5   | V    |

| HIGH-SIDE GATE DRIVER (       | voltages referred to OU                                   | IT)                                                                        | I            |               |       |      |

| V <sub>HVGL</sub>             | Output low voltage                                        | I <sub>sink</sub> = 100 mA<br>V <sub>VBOOT</sub> - V <sub>OUT</sub> = 15 V |              | 0.7           | 1.5   | V    |

DS15052 - Rev 3 page 14/49

| Symbol             | Parameter             | Test condition                                                              | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------|-----------------------------------------------------------------------------|------|------|------|------|

| $V_{HVGH}$         | Output high voltage   | I <sub>source</sub> = 10 mA<br>V <sub>VBOOT</sub> - V <sub>OUT</sub> = 15 V | 14.0 | 14.9 |      | V    |

| t <sub>f</sub>     | Voltage fall time     | From 13.5 V to 1.5 V                                                        |      | 25   | 50   | ns   |

| t <sub>r</sub>     | Voltage rise time     | From 1.5 V to 13.5 V                                                        | 30   | 43   | 75   | ns   |

| R <sub>PD_HO</sub> | HVG-OUT pull-<br>down |                                                                             | 8    | 25   | 35   | kΩ   |

- 1. Values tracking each other

- 2. Values tracking each other

- 3. Matched voltage references

- 4.  $V_{STBY\_STOP} = V_{STBY\_2V0}$

$V_{STBY\_REST} = V_{STBY\_1V9} - V_{STBY\_1V9\_LH}$

$V_{STBY\_EBM\_ON} = V_{STBY\_1V9}$

$V_{STBY\_EBM\_OFF} = V_{STBY\_2V0}$

- 5. Values tracking each other

- 6. Values tracking each other

- 7. Values tracking each other

- 8. In case of V<sub>VCC</sub> < V<sub>VCCOn</sub>, if external current is forced into pin LVG, then an internal clamp is activated to avoid external MOSFET turn-on (pin LVG can rise above V<sub>GSth</sub> because of the external injection). V<sub>VCC</sub> = 0 → 0.3 V, the UVLO saturation is bypassed by internal parasitic diode and V<sub>LVG</sub> = 0.6 V typ. V<sub>VCC</sub>: 0.3 V → 1.1 V, the UVLO saturation is active. V<sub>VCC</sub> > 1.1 V, the internal LS MOSFET is turned on and pin LVG is kept to ground. Test of UVLO saturation must be done with V<sub>VCC</sub> around 0.5 V.

DS15052 - Rev 3 page 15/49

#### Description of operation

#### 7.1 Application information

The STNRG599 is an advanced double-ended controller specific for the resonant half-bridge topology. In these converters, the MOSFETs of the half-bridge leg are alternately switched on and off (180° out-of-phase) to generate a high-voltage square wave that is applied to a resonant tank circuit. This is commonly referred to as operation at "50% duty cycle", although the real duty cycle, i.e. the ratio of the on-time of either switch to the switching period, is less than 50% because of the dead time between complementary gate drive pulses. Dead time is inserted between the turning off of one MOSFET and the turning on of the other MOSFET. During such dead time, both MOSFETs are off. Dead time is necessary for the correct operation of the resonant tank converter: it enables soft switching of the MOSFETs and, therefore, high-frequency operation with high efficiency and low EMI emissions. In brief, during dead time, the half-bridge node voltage moves between from the high level to ground and vice versa, pushed by the switched current (that is, the resonant tank current flowing at the time the MOSFET is turned off). It successively discharges and charges the equivalent capacitance of the halfridge node. When the half-bridge node voltage has reached the ground or the high level, the corresponding MOSFET (low side or high side) can be turned on. The transition time of the half-bridge node depends on the switched current that, in turn, depends on the output load. A useful feature offered by STNRG599 is the adaptive dead time function: the controller can set a dead time value, within a certain range, according to the half-bridge node transition time. The benefits and operation of the adaptive dead time function are described in the dedicated section. In brief, it allows optimization of the resonant tank design so that soft switching can be achieved with a lower level of magnetizing current in the transformer; in this way, the converter efficiency can be optimized over a broad load range.

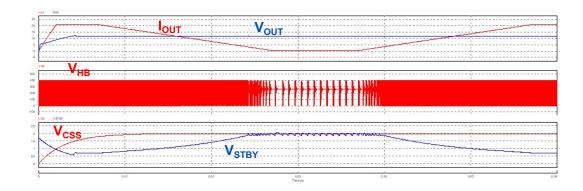

Normal operation of the resonant tank converter is such that the frequency (of the 50% duty cycle square wave feeding the resonant tank) increases when the load is reduced. This operating mode is called continuous switching. In general, at some light load, the switching losses become relevant and dominant, so it is no longer possible to regulate the output load in continuous switching operation while keeping good efficiency and being compliant with energy-saving regulations.

Output regulation at light load with limited switching frequency increase is allowed by burst mode operation: rather than continuously switching, the converter starts operating in a controlled intermittent way in which packets of a limited number of switching cycles are spaced by idle periods characterized by both MOSFETs in the off state. Details of the burst mode function of STNR599, in relationship with phase shift control methodology, are given in the dedicated section.

#### 7.2 Phase shift control (PSC) methodology

The controlled variable in the phase shift control methodology is the phase between the half-bridge edge (rising or falling) and the zero crossing (ascending or descending) of the resonant tank current. The phase is defined as the ratio between the time from the half-bridge edge to the resonant current zero crossing and the time the half bridge stays high or low. In other words, the phase is the displacement angle between the input voltage and the input current of the resonant tank. Since the power transferred across the resonant tank in a switching cycle (disregarding the losses) is proportional to the input voltage by the input current and by the cosine of the displacement angle (i.e., the phase), controlling the latter make it possible to control the output power. The phase approaches zero at full load, while it approaches 0.5 at light load (0.5 corresponds to  $\pi$  / 2 rad, given that  $T_{SW}$  corresponds to  $2 \cdot \pi$  rad).

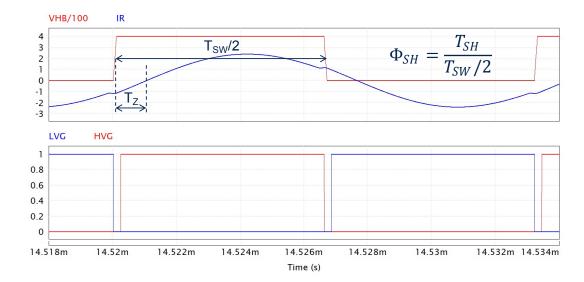

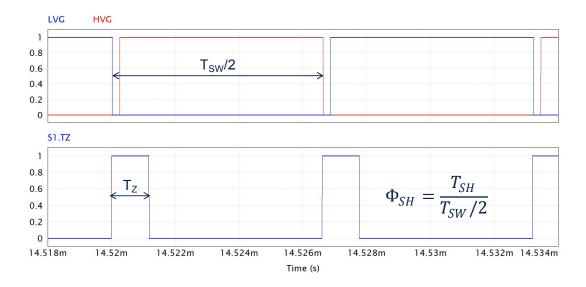

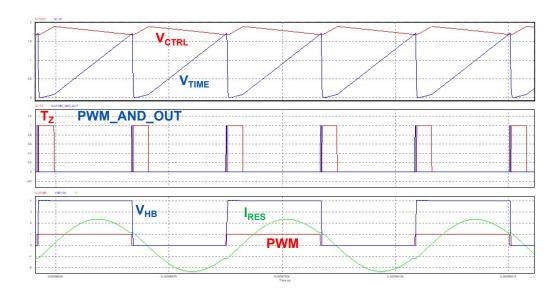

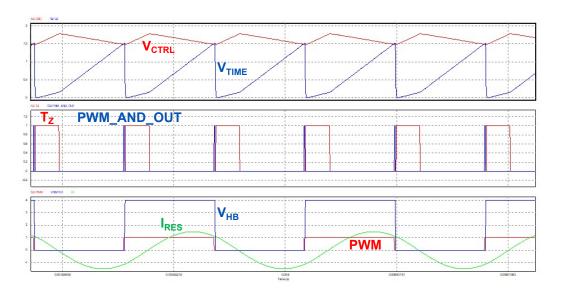

Inside STNRG599, the phase shift,  $\Phi_{SH}$ , is measured as the ratio between the time from one MOSFET turn-off to the corresponding zero crossing of the sensed resonant current, and the time from the MOSFET turn-off to the complementary MOSFET turn-off. Figure 5 shows the phase shift between the half-bridge voltage and the resonant tank current, while Figure 6 shows the way the phase shift is measured inside STNRG599. The control law resulting from the implementation of the phase shift control methodology is:

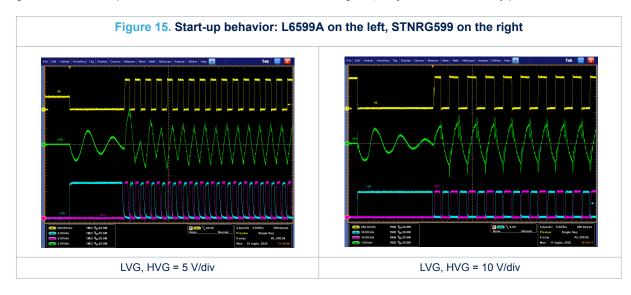

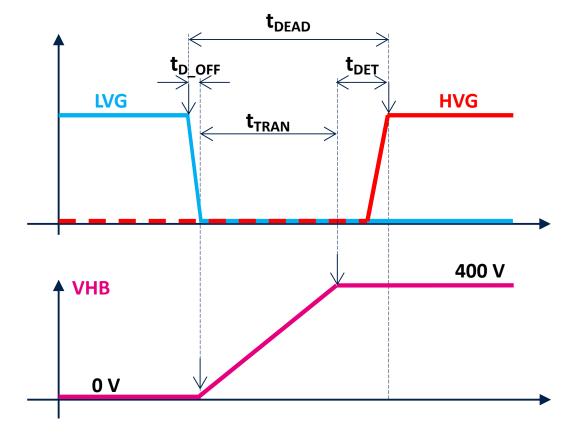

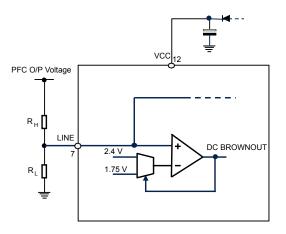

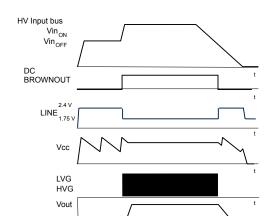

$$\Phi_{SH} = \frac{T_Z}{T_{EW}/2} = 0.25 \cdot \frac{I_{FB}}{I_{OSC}} \tag{1}$$