### Rad-Hard 100 V, 6 A, N-channel Power MOSFET

SMD.5

Product status link

STRH8N10

#### **Features**

| V <sub>DS</sub> | I <sub>D</sub> | R <sub>DS(on)</sub> typ. | Q <sub>g</sub> typ. |

|-----------------|----------------|--------------------------|---------------------|

| 100 V           | 6 A            | 0.27 Ω                   | 18.5 nC             |

- Fast switching

- 100 % avalanche tested

- · Hermetic package

- 50 krad TID

- SEE radiation hardened

### **Description**

The STRH8N10 is a N-channel Power MOSFET able to operate under severe environment conditions and radiation exposure. It provides high reliability performance and immunity to the total ionizing dose (TID) and single event effects (SEE).

Qualified as per ESCC detail specification No. 5205/023 and available in SMD.5 hermetic package it is specifically recommended for space and harsh environment applications and suitable for in-Satellite power conversion, motor control and power switch circuits.

In case of discrepancies between this datasheet and the relevant agency specification, the latter takes precedence.

#### **Device summary**

| Product summary |                   |                        |         |                |                    |

|-----------------|-------------------|------------------------|---------|----------------|--------------------|

| Part<br>numbers | Quality<br>level  | ESCC<br>Part<br>number | Package | Lead<br>finish | Radiation<br>level |

| STRH8N10S1      | Engineering model | 5205/022               | CMD 5   | Gold           | -                  |

| STRH8N10SG      | ESCC              | 5205/023               | SMD.5   |                | 50 krad            |

| STRH8N10ST      | flight            |                        |         | Solder-dip     | JU KIAU            |

Note: See Table 8 for ordering information.

# 1 Electrical ratings

Table 1. Absolute maximum ratings

| Symbol                         | Parameter                                               | Value      | Unit |

|--------------------------------|---------------------------------------------------------|------------|------|

| V <sub>DS</sub> <sup>(1)</sup> | Drain-source voltage (V <sub>GS</sub> = 0)              | 100        | V    |

| V <sub>GS</sub> <sup>(2)</sup> | Gate-source voltage                                     | ±20        | V    |

| I <sub>D</sub> (3)             | Drain current (continuous)                              | 6          | А    |

| I <sub>D</sub>                 | Drain current (continuous) at T <sub>amb</sub> = 100 °C | 4.1        | Α    |

| I <sub>DM</sub> <sup>(4)</sup> | Drain current (pulsed)                                  | 24         | А    |

| P <sub>TOT</sub>               | Total dissipation at T <sub>C</sub> = 25 °C             | 62.5       | W    |

| P <sub>TOT</sub>               | Total dissipation at T <sub>a</sub> = 25 °C             | 2.4        | W    |

| dv/dt <sup>(5)</sup>           | Peak diode recovery voltage slope                       |            | V/ns |

| T <sub>op</sub>                | Operating temperature range                             | -55 to 150 | °C   |

| Tj                             | Max. operating junction temperature range               | 150        | °C   |

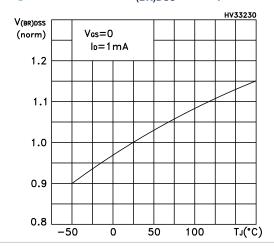

- 1. This rating is guaranteed at  $T_J \ge 25$  °C (see Figure 9. Normalized  $V_{(BR)DSS}$  vs temperature ).

- 2. This value is guaranteed over the full range of temperature.

- 3. Rated according to the  $R_{thj\text{-case}} + R_{thc\text{-s.}}$

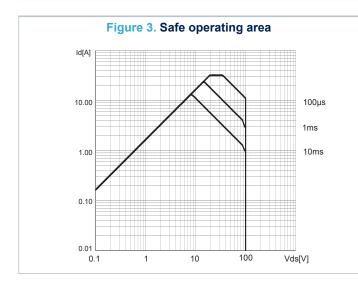

- 4. Pulse width limited by safe operating area.

- 5.  $I_{SD} \le 6 \text{ A}$ ,  $di/dt \le 1060 \text{ A/}\mu\text{s}$ ,  $V_{DD} = 80 \text{ %}V_{(BR)DSS}$

Table 2. Thermal data

| Symbol            | Parameter                               | Value | Unit |

|-------------------|-----------------------------------------|-------|------|

| R <sub>thJC</sub> | Thermal resistance, junction-to-case    | 2     | °C/W |

| R <sub>thJA</sub> | Thermal resistance, junction-to-ambient | 52    | °C/W |

DS7120 - Rev 13 page 2/14

# 2 Avalanche data

Table 3. Avalanche data

| Symbol                         | Parameter                                                                                                                                              | Value | Unit |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| I <sub>AR</sub>                | Avalanche current, repetitive or not-repetitive $ (\text{pulse width limited by } T_j \text{ max.}) $                                                  | 4     | Α    |

| E <sub>AS</sub> <sup>(1)</sup> | Single pulse avalanche energy (starting $T_j = 25$ °C, $I_D = I_{AR}$ , $V_{DD} = 50$ V)                                                               | 457   | mJ   |

| E <sub>AS</sub>                | Single pulse avalanche energy (starting $T_j$ = 110 °C, $I_D$ = $I_{AR}$ , $V_{DD}$ = 50 V)                                                            | 134   | IIIJ |

| E <sub>AR</sub>                | Repetitive avalanche $(V_{DD} = 50 \text{ V}, I_{AR} = 4 \text{ A}, f = 100 \text{ KHz},$ $T_{J} = 25  ^{\circ}\text{C}, \text{ duty cycle} = 10  \%)$ | 4.3   |      |

| LAR                            | Repetitive avalanche $(V_{DD} = 50 \text{ V}, I_{AR} = 4 \text{ A}, f = 100 \text{ KHz},$ $T_{J} = 110 \text{ °C}, \text{ duty cycle} = 10 \text{ %})$ | 1.4   | mJ   |

<sup>1.</sup> Maximum rating value.

DS7120 - Rev 13 page 3/14

## 3 Electrical characteristics

Table 4. Electrical characteristics (T<sub>amb</sub> = 25 °C unless otherwise specified)

| Symbol               | Parameter                         | Test conditions                                                                         | Min. | Max.  | Unit |

|----------------------|-----------------------------------|-----------------------------------------------------------------------------------------|------|-------|------|

| BV <sub>DSS</sub>    | Drain-source breakdwon voltage    | I <sub>D</sub> = 1 mA                                                                   | 100  |       | V    |

|                      | Zero gate voltage drain current   | BV <sub>DSS</sub> = 80 V                                                                |      | 10    | μΑ   |

| I <sub>DSS</sub>     | (V <sub>GS</sub> = 0)             | BV <sub>DSS</sub> = 80 V, T <sub>C</sub> = 125 °C                                       |      | 100   | μΑ   |

|                      | V <sub>GS</sub> = 20 V            |                                                                                         |      | 100   |      |

| 1                    | Gate body leakage current,        | V <sub>GS</sub> = -20 V                                                                 | -100 |       | nA   |

| I <sub>GSS</sub>     | (V <sub>DS</sub> = 0)             | V <sub>GS</sub> = 20 V, T <sub>C</sub> = 125 °C                                         |      | 200   | IIA  |

|                      |                                   | V <sub>GS</sub> = -20 V, T <sub>C</sub> = 125 °C                                        | -200 |       |      |

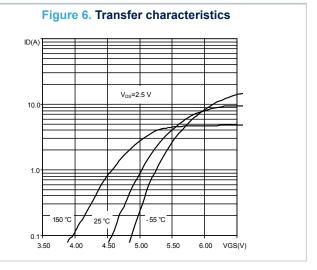

|                      |                                   | $V_{DS} = V_{GS}$ , $I_D = 1$ mA                                                        | 2    | 4.7   |      |

| $V_{GS(th)}$         | Gate threshold voltage            | $V_{DS} = V_{GS}$ , $I_D = 1$ mA, $T_C = 125$ °C                                        | 1.5  | 4.1   | V    |

|                      |                                   | $V_{DS} = V_{GS}$ , $I_D = 1$ mA, $T_C = -55$ °C                                        | 2.1  | 5.5   |      |

| В                    |                                   | V <sub>GS</sub> = 12 V, I <sub>D</sub> = 4 A                                            |      | 0.3   |      |

| R <sub>DS(on)</sub>  | Static drain-source on resistance | V <sub>GS</sub> = 12 V, I <sub>D</sub> = 4 A, T <sub>a</sub> = 125 °C                   |      | 0.72  | Ω    |

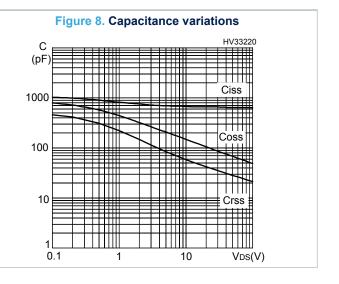

| C <sub>iss</sub>     | Input capacitance                 |                                                                                         |      | 791   | pF   |

| C <sub>oss</sub> (1) | Output capacitance                | $V_{DS}$ = 25 V, f = 1 MHz, $V_{GS}$ = 0 V                                              | 76   | 114   | pF   |

| C <sub>rss</sub>     | Reverse transfer capacitance      | _                                                                                       | 31   | 47    | pF   |

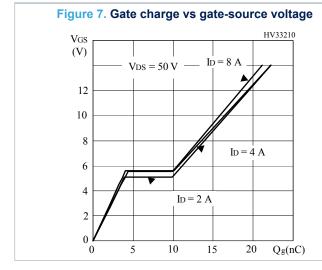

| Qg                   | Total gate charge                 |                                                                                         | 15   | 22    | nC   |

| Q <sub>gs</sub>      | Gate-to-source charge             | V <sub>DD</sub> = 50 V, I <sub>D</sub> = 4 A, V <sub>GS</sub> = 12 V                    | 2.5  | 4.5   | nC   |

| $Q_{gd}$             | Gate-to-drain ("Miller") charge   |                                                                                         | 4.3  | 6.5   | nC   |

| t <sub>d(on)</sub>   | Turn-on delay time                |                                                                                         | 5    | 10    |      |

| t <sub>r</sub>       | Rise time                         | V = 50 V L = 4 A D = 4 7 O V = 12 V                                                     | 2    | 9     |      |

| t <sub>d(off)</sub>  | Turn-off delay time               | $V_{DD}$ = 50 V, $I_{D}$ = 4 A, $R_{G}$ = 4.7 $\Omega$ , $V_{GS}$ = 12 V                | 13   | 30    | ns   |

| t <sub>f</sub>       | Fall time                         | -                                                                                       |      | 7.5   |      |

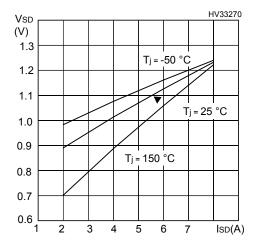

| .,                   | Diada famuand valtage             | I <sub>SD</sub> = 8 A, V <sub>GS</sub> = 0 V                                            |      | 1.5   | .,   |

| $V_{SD}$             | Diode forward voltage             | I <sub>SD</sub> = 8 A, V <sub>GS</sub> = 0 V, T <sub>a</sub> = 125 °C                   |      | 1.275 | V    |

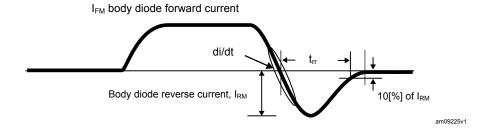

| t <sub>rr</sub> (1)  | Reverse recovery time             | I <sub>SD</sub> = 8 A, di/dt = 100 A/μs, V <sub>DD</sub> = 50 V, T <sub>j</sub> = 25 °C | 196  | 294   | ns   |

<sup>1.</sup> Not tested in production, garanteed by process.

DS7120 - Rev 13 page 4/14

### 4 Radiation characteristics

This products is guaranteed in radiation as per ESCC 5205/023 and ESCC 22900 specification at 50 krad. Each lot tested in radiation is accepted according to the characteristics as per Table 5.

### 4.1 Total dose radiation (TID) testing

The bias with  $V_{GS}$  = + 15 V and  $V_{DS}$  = 0 V is applied during irradiation exposure.

The parameters listed in Table 5 are measured:

- · Before irradiation

- After irradiation

- After 24 hrs at room temperature

- after 168 hrs at 100 °C anneal

Table 5. Post-irradiation electrical characteristics (T<sub>amb</sub> = 25 °C unless otherwise specified)

| Symbol                         | Parameter                                             | Test conditions                              | Min. | Max. | Unit |

|--------------------------------|-------------------------------------------------------|----------------------------------------------|------|------|------|

| I <sub>DSS</sub>               | Zero gate voltage drain current (V <sub>GS</sub> = 0) | V <sub>DS</sub> = 80 V                       |      | 10   | μA   |

| lass                           | Gate body leakage current, (V <sub>DS</sub> = 0)      | V <sub>GS</sub> = 20 V                       |      | 100  |      |

| I <sub>GSS</sub>               | Gate body leakage current, (VDS = 0)                  | V <sub>GS</sub> = -20 V                      | 100  |      | nA   |

| V <sub>(BR)DSS</sub>           | Drain-to-source breakdown voltage                     | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 1 mA | 100  |      | V    |

| V <sub>GS(th)</sub>            | Gate threshold voltage                                | $V_{DS} = V_{GS}$ , $I_D = 1 \text{ mA}$     | 2    | 4.7  | V    |

| R <sub>DS(on)</sub>            | Static drain-source on resistance                     | V <sub>GS</sub> = 12 V, I <sub>D</sub> = 4 A |      | 0.3  | Ω    |

| V <sub>SD</sub> <sup>(1)</sup> | Diode forward voltage                                 | I <sub>SD</sub> = 8 A, V <sub>GS</sub> = 0 V |      | 1.5  | V    |

<sup>1.</sup> Pulsed: pulse duration = 300  $\mu$ s, duty cycle  $\leq$  1.5%

DS7120 - Rev 13 page 5/14

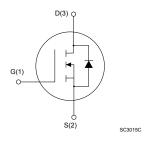

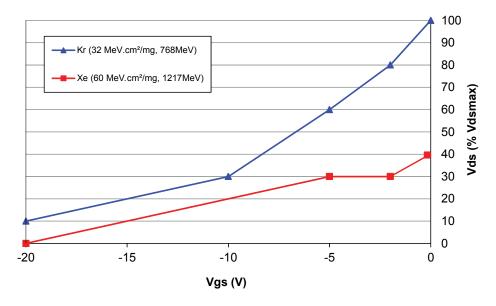

### 4.2 Single event effect RBSOA

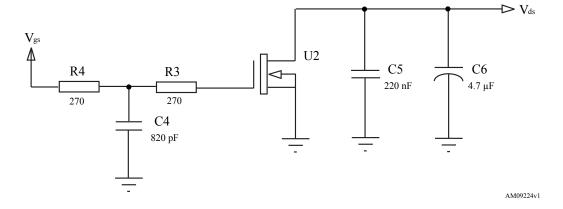

The STRH8N10 is extremely resistant to heavy ions exposure as per MIL-STD-750E, test method 1080, bias circuit of Figure 2.

SEB and SEGR tests are performed with a fluence of 3e+5 ions/cm² with the following acceptance criteria:

- SEB test: drain voltage checked, trigger level is set to VDS = 5 V. Stop condition: as soon as a SEB occurs or if the fluence reaches 3e+5 ions/cm².

- SEGR test: the gate current is monitored every 200 ms. A gate stress is performed before and after irradiation. Stop condition: as soon as the gate current reaches 100 nA (during irradiation or during PIGS test) or if the fluence reaches 3e+5 ions/cm².

Table 6. Single event effect (SEE), reverse biased safe operating area (RBSOA)

| lon | Let (Mev/(mg/cm²) | Energy<br>(MeV) | Range<br>(μm) |

|-----|-------------------|-----------------|---------------|

| Kr  | 32                | 768             | 94            |

| Xe  | 60                | 1217            | 89            |

Figure 1. Single event effect, RBSOA

Figure 2. Single event effect, bias circuit

DS7120 - Rev 13 page 6/14

# Electrical characteristics (curves)

Figure 4. Thermal impedance  $\delta = 0.5$  0.2 0.0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.0

Figure 5. Output characteristics

ID

(A)

VGS = 10 V

25

VGS = 7 V

VGS = 6 V

10

VGS = 5 V

0

10

20

VDS(V)

DS7120 - Rev 13 page 7/14

Figure 9. Normalized V<sub>(BR)DSS</sub> vs temperature

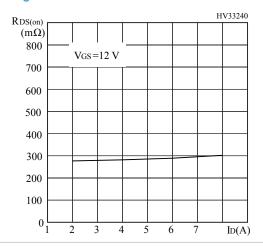

Figure 10. Static drain-source on-resistance

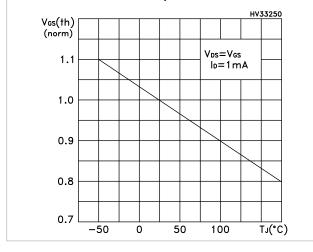

Figure 11. Normalized gate threshold voltage vs temperature

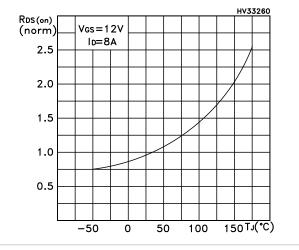

Figure 12. Normalized on-resistance vs temperature

Figure 13. Source drain-diode forward characteristics

DS7120 - Rev 13 page 8/14

# 6 Test circuits

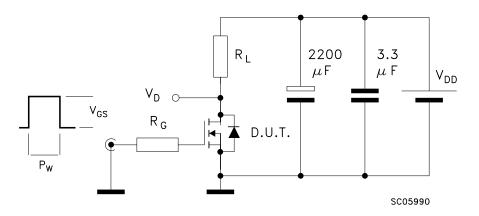

Figure 14. Switching times test circuit for resistive load

Note:  $Max driver V_{GS} slope = 1 V/ns (no DUT)$

Figure 15. Source drain diode waveform

DS7120 - Rev 13 page 9/14

# 7 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

### 7.1 SMD.5 package information

Pin n° 1 identification ⊕ .014 M C A 2 pls b2 2 pls b3 2 pls D1 D b1 □.004 C > ← В ⊕ .014 M C A Bottom view Top view

Figure 16. SMD.5 package outline

7386434\_REV7

Table 7. SMD.5 package mechanical data

| Dim.   | mm        |       |       |  |  |  |

|--------|-----------|-------|-------|--|--|--|

| Dilli. | Min.      | Тур.  | Max.  |  |  |  |

| Α      | 2.84      |       | 3.30  |  |  |  |

| A1     | 0.25      | 0.38  | 0.51  |  |  |  |

| b      | 7.13      | 7.26  | 7.39  |  |  |  |

| b1     | 5.58 5.72 |       | 5.84  |  |  |  |

| b2     | 2.28      | 2.41  | 2.54  |  |  |  |

| b3     | 2.92      | 3.05  | 3.18  |  |  |  |

| D      | 10.03     | 10.16 | 10.28 |  |  |  |

| D1     | 0.76      |       |       |  |  |  |

| E      | 7.39      | 7.52  | 7.64  |  |  |  |

| е      |           | 1.91  |       |  |  |  |

Note: The lid is not connected to any pin.

DS7120 - Rev 13 page 10/14

### 8 Order codes

**Table 8. Ordering information**

| Part number | Agency specification | Quality<br>level  | Radiation<br>level | Package | Weight | Lead<br>finish | Marking <sup>(1)</sup> | Packing    |

|-------------|----------------------|-------------------|--------------------|---------|--------|----------------|------------------------|------------|

| STRH8N10S1  | -                    | Engineering model | -                  | CMD 5   | 4 -    | Gold           | STRH8N10S1             | Chris mank |

| STRH8N10SG  | 5205/023/01          | ESCC              | 50 krad            | SMD.5   | 1 g    |                | 520502301F             | Strip pack |

| STRH8N10ST  | 5205/023/02          | flight            | 50 KIAU            |         |        | Solder-dip     | 520502302F             |            |

Specific marking only. The full marking includes in addition: For the Engineering Models: ST logo, date code; country of origin (FR). For ESCC flight parts: STlogo, date code, country of origin (FR), ESA logo, serial number of the part within the assembly lot.

Contact ST sales office for information about specific conditions for products in die form.

DS7120 - Rev 13 page 11/14

# 9 Other information

Table 9. Traceability and documentation

| Screening type    | Date code <sup>(1)</sup> | Radiation level | Documentation                                                                                                                                              |

|-------------------|--------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Engineering model | 3yywwN                   | -               | Certificate of conformance                                                                                                                                 |

| Flight model      | yywwN                    | 50 krad         | Certificate of conformance ESCC qualification maintenance lot reference Radiation verification test (RVT) report at 10 / 20 / 30 / 50 krad at 0.1 rad / s. |

<sup>1.</sup> yy = year, ww = week number, N = lot index in the week.

DS7120 - Rev 13 page 12/14

## **Revision history**

Table 10. Document revision history

| Date        | Revision | Changes                                                                                                                                      |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 20-May-2011 | 1        | First release.                                                                                                                               |

| 09-Nov-2011 | 2        | Updated dynamic values on Table 6: Dynamic, Table 7: Switching times.                                                                        |

| 03-Jun-2013 | 3        | Added new package and mechanical data: SMD.5  Removed TO-39 package.                                                                         |

| 16-Dec-2013 | 4        | Updated <i>Description</i> Minor text changes                                                                                                |

| 09-Apr-2014 | 5        | Document status promoted from preliminary data to production data  Modified: Figure 2.  Minor text changes.                                  |

| 26-May-2014 | 6        | Updated Figure 1.                                                                                                                            |

| 04-Mar-2016 | 7        | Updated: Features, Table 5, Table 6, Table 9, Table 10, Table 11 and Table 15.  Updated Section 6: Package information.  Minor text changes. |

| 10-Feb-2017 | 8        | Updated Table 6: Dynamic and Table 8: Source drain diode.                                                                                    |

| 04-Oct-2021 | 9        | Updated <i>Description</i> . Minor text changes.                                                                                             |

| 19-May-2022 | 10       | Updated Table 4, Figure 15 and Section 9 Other information.                                                                                  |

| 18-Jan-2024 | 11       | Updated Table 4. Electrical characteristics (Tamb = 25 °C unless otherwise specified).  Minor text changes.                                  |

| 05-Apr-2024 | 12       | Updated Table 4.                                                                                                                             |

| 12-Sep-2024 | 13       | Updated Table 4, and Table 5.                                                                                                                |

DS7120 - Rev 13 page 13/14

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

DS7120 - Rev 13 page 14/14