# Ultra-low power motion sensor for optical finger navigation (OFN)

Datasheet - production data

#### **Features**

- Ultra-low power performance and high speed/high accuracy motion detection (up to 26 in/s @ 3600 f/s)

- Manual or automatic power management options

- Very low quiescent and operating current modes for battery life saving

- Fully integrated solution: internal oscillator and LED driver

- 1<sup>2</sup>C interface with fast polling rates for high-end applications (report rate up to 1 per ms).

- User-selectable I<sup>2</sup>C address (default I<sup>2</sup>C address is 0xA6)

- CPI programmable up to 3,200 CPI

- Fully automatic exposure control (AEC)

## **Applications**

- Smart phones

- Laptop/Netbook PCs

- Media players

- GPS devices

- Remote controls for home entertainment equipment

#### Description

The VD5377 is an ultra-low power, single-chip controller IC containing all the functions necessary for optical joysticks/optical finger navigation modules enabling improved mobile experience and longer battery life. This device is cost and performance optimized for Optical Finger Navigation applications and includes special features to ensure optimum performance even in bright sunlight.

Contents VD5377

# **Contents**

| 1 | Ove   | Overview                         |  |  |  |

|---|-------|----------------------------------|--|--|--|

|   | 1.1   | Technical specification          |  |  |  |

|   | 1.2   | VD5377 enhancements              |  |  |  |

|   | 1.3   | Floor plan changes               |  |  |  |

| 2 | Silic | on specification                 |  |  |  |

|   | 2.1   | Silicon thickness                |  |  |  |

|   | 2.2   | Die size and optical center      |  |  |  |

|   | 2.3   | Pad opening sizes                |  |  |  |

|   | 2.4   | Device pinout                    |  |  |  |

|   | 2.5   | Bond pad coordinates             |  |  |  |

| 3 | Арр   | lication schematic13             |  |  |  |

|   | 3.1   | Signal descriptions              |  |  |  |

|   | 3.2   | Cursor orientation               |  |  |  |

| 4 | Syst  | em overview                      |  |  |  |

|   | 4.1   | Manual power management          |  |  |  |

|   | 4.2   | Automatic power management       |  |  |  |

| 5 | I/O d | lescription                      |  |  |  |

|   | 5.1   | I2C_SEL[2:0]                     |  |  |  |

|   | 5.2   | LED_OUT (tracking LED) and GPIO0 |  |  |  |

|   | 5.3   | MOTION                           |  |  |  |

|   | 5.4   | STANDBY 28                       |  |  |  |

|   | 5.5   | POWERDOWN 29                     |  |  |  |

| 6 | Key   | features                         |  |  |  |

|   | 6.1   | Feature count                    |  |  |  |

|   | 6.2   | Minimum features threshold       |  |  |  |

|   | 6.3   | X/Y scaling 30                   |  |  |  |

|   | 6.4   | Automatic exposure control       |  |  |  |

|    | 6.5                 | 5 x 5 high pass filter                           | 34 |

|----|---------------------|--------------------------------------------------|----|

|    | 6.6                 | Sunlight timing                                  | 35 |

|    | 6.7                 | Automatic/manual frame rate                      | 36 |

| 7  | Addi                | tional features                                  | 38 |

|    | 7.1                 | Auto-movement filter                             | 38 |

|    | 7.2                 | Adaptive CPI                                     | 40 |

| 8  | Basi                | c start-up information                           | 42 |

|    | 8.1                 | Register override                                | 42 |

|    | 8.2                 | Recommended start-up settings                    | 42 |

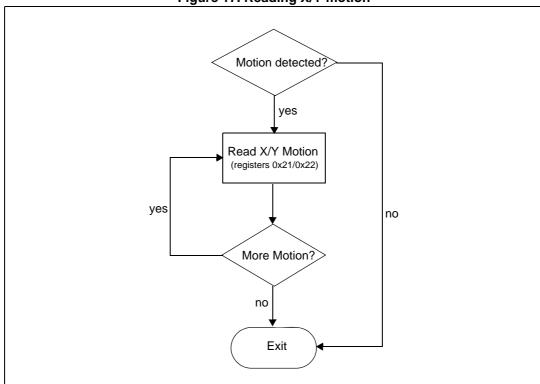

|    | 8.3                 | Reading X/Y motion data                          | 44 |

|    | 8.4                 | Switching between automatic mode and manual mode | 46 |

|    | 8.5                 | Soft reset                                       | 48 |

| 9  | lmag                | e capture                                        | 49 |

|    | 9.1                 | I <sup>2</sup> C image capture                   | 49 |

|    |                     | 9.1.1 Step-by-step procedure                     | 52 |

|    |                     | 9.1.2 Debug mode                                 | 53 |

|    | 9.2                 | Fast capture                                     | 53 |

| 10 | Elect               | rical characteristics                            | 56 |

|    | 10.1                | Operating conditions                             | 56 |

|    | 10.2                | Digital I/O                                      | 57 |

| 11 | l <sup>2</sup> C iı | nterface                                         | 58 |

|    | 11.1                | Protocol                                         | 58 |

|    | 11.2                | Data format                                      | 58 |

|    | 11.3                | Message interpretation                           | 59 |

|    | 11.4                | Type of messages                                 | 59 |

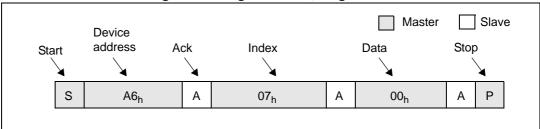

|    |                     | 11.4.1 Single location, single data write        |    |

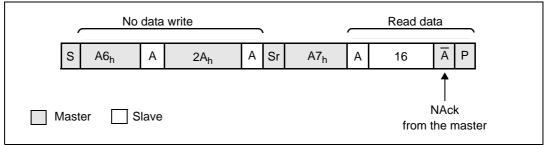

|    |                     | 11.4.2 Single location read                      | 59 |

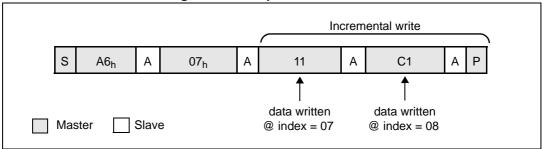

|    |                     | 11.4.3 Multiple location write                   | 60 |

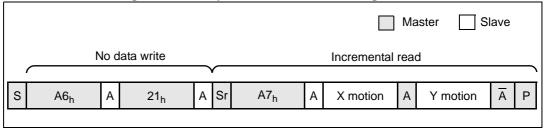

|    |                     | 11.4.4 Multiple location read                    | 60 |

| 12 | I <sup>2</sup> C r  | egister map                                      | 61 |

|    |                     |                                                  |    |

| Contents | VD53                       | 377 |

|----------|----------------------------|-----|

| 13       | Acronyms and abbreviations | 77  |

| 14       | Ordering information       | 78  |

| 15       | Revision history           | 79  |

VD5377 List of tables

# List of tables

| Table 1.  | Technical specification                                                   | . 8 |

|-----------|---------------------------------------------------------------------------|-----|

| Table 2.  | Die size and optical center comparison                                    | . 9 |

| Table 3.  | Die size                                                                  | 10  |

| Table 4.  | Optical center                                                            | 10  |

| Table 5.  | Pad openings                                                              | 10  |

| Table 6.  | Bond pad coordinates                                                      | 12  |

| Table 7.  | Signal descriptions                                                       | 14  |

| Table 8.  | Typical power consumption - Manual mode                                   | 18  |

| Table 9.  | Manual mode timing constraints                                            | 19  |

| Table 10. | Typical power consumption - automatic mode                                | 21  |

| Table 11. | Automatic mode timing constraints                                         | 22  |

| Table 12. | User-selectable I <sup>2</sup> C addresses                                | 23  |

| Table 13. | Control register to dynamically configure device I <sup>2</sup> C address | 23  |

| Table 14. | Control register for LED_OUT and GPIO0                                    | 25  |

| Table 15. | Truth-table                                                               |     |

| Table 16. | Control register for motion pin polarity                                  |     |

| Table 17. | Features and scaling                                                      | 31  |

| Table 18. | Exposure control                                                          |     |

| Table 19. | 5x5 high-pass filter register                                             | 34  |

| Table 20. | Sunlight DMIB timing mode                                                 | 35  |

| Table 21. | Adaptive frame rate control                                               | 36  |

| Table 22. | Modified exposure limits                                                  | 37  |

| Table 23. | Motion threshold                                                          | 37  |

| Table 24. | Auto-movement filter                                                      | 38  |

| Table 25. | Adaptive CPI                                                              | 40  |

| Table 26. | Analog_ctrl2 recommended setting                                          | 42  |

| Table 27. | Start-up settings                                                         | 42  |

| Table 28. | X/Y motion data                                                           | 45  |

| Table 29. | Soft reset                                                                | 48  |

| Table 30. | I2C frame dump registers                                                  | 50  |

| Table 31. | Fast capture                                                              | 54  |

| Table 32. | Operating conditions                                                      |     |

| Table 33. | Digital IO electrical characteristics                                     | 57  |

| Table 34. | Register types                                                            | 61  |

| Table 35. | I <sup>2</sup> C register map                                             | 61  |

| Table 36. | Acronyms and abbreviations                                                | 77  |

| Table 37. | Delivery formats                                                          | 78  |

| Table 38. | Document revision history                                                 | 79  |

List of figures VD5377

# List of figures

| Figure 1.  | VD5377 SIMPIIITIEG SYSTEM DIOCK GIAGRAM                   | /  |

|------------|-----------------------------------------------------------|----|

| Figure 2.  | VD5377 bond pad layout                                    | 11 |

| Figure 3.  | Typical application schematic                             | 13 |

| Figure 4.  | VD5377 default XY orientation                             |    |

| Figure 5.  | VD5377 power management modes                             | 16 |

| Figure 6.  | Manual power mode flow diagram                            | 17 |

| Figure 7.  | Manual power mode timing diagram                          | 18 |

| Figure 8.  | Automatic power mode flow diagram                         | 20 |

| Figure 9.  | Automatic power mode timing diagram (use_standby_pin=1)   | 22 |

| Figure 10. | LED drive options                                         | 24 |

| Figure 11. | LED control                                               | 24 |

| Figure 12. | Typical configuration of GPIO                             | 26 |

| Figure 13. | MOTION behavior at power-up                               | 27 |

| Figure 14. | In AUTOMATIC mode the STANDBY pin functions as I2C enable | 29 |

| Figure 15. | Automatic exposure algorithm                              | 32 |

| Figure 16. | Adaptive CPI algorithm                                    | 40 |

| Figure 17. | Reading X/Y motion                                        | 44 |

| Figure 18. | Accessing low power standby from Automatic power mode     | 46 |

| Figure 19. | Automatic mode to low power standby mode                  | 47 |

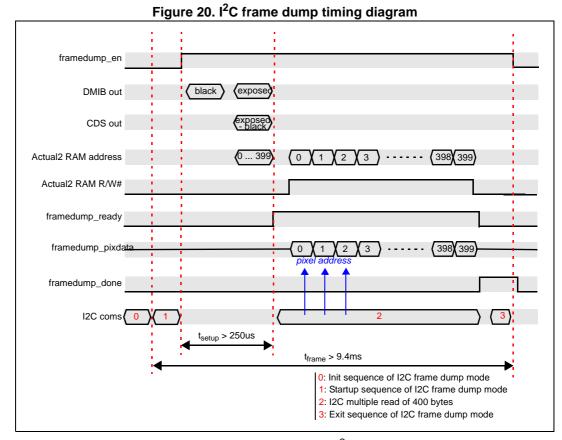

| Figure 20. | I2C frame dump timing diagram                             | 49 |

| Figure 21. | Flow chart procedure for I2C frame dump                   | 52 |

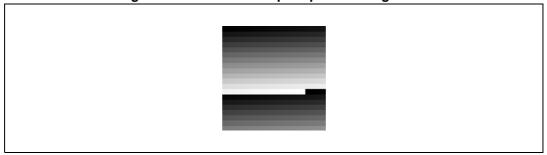

| Figure 22. | I2C frame dump output in debug mode                       | 53 |

| Figure 23. | Fast capture timing diagram                               | 55 |

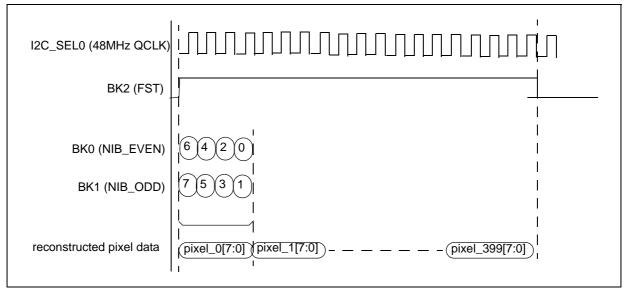

| Figure 24. | Serial interface data transfer protocol                   | 58 |

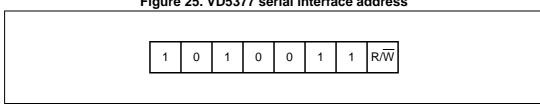

| Figure 25. | VD5377 serial interface address                           | 58 |

| Figure 26. | Single location, single write                             | 59 |

| Figure 27. | Single read                                               | 60 |

| Figure 28. | Multiple location write                                   | 60 |

| Figure 29  | Multiple location read: reading motion                    | 60 |

VD5377 Overview

#### 1 Overview

The VD5377 is an ultra-low power, single-chip controller IC containing all the functions necessary for optical joysticks/optical finger navigation modules. It incorporates a 20 x 20, 30.4  $\mu$ m pixel imaging array supporting frame rates up to 3.6 k frames/s capable of detecting and tracking motion at up to 26 inches/s with high accuracy and low drift. Maximum velocity is calculated as follows:

maximum velocity = (pixel size/lens magnification) x max frame rate x max.displacement per frame

#### For example:

0.5 magnification = (30  $\mu\text{m}/0.5)$  x 3600 f/s x 3 pixels = 0.65 m/s (26 inches/s)

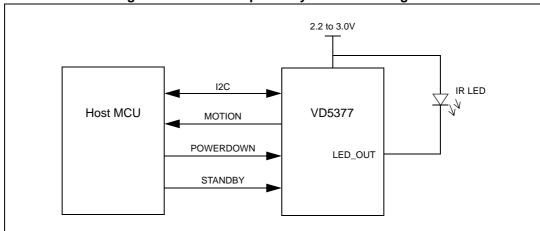

Figure 1 shows a simplified block diagram of a typical optical navigation system. Communication with the device is over a 400 kHz I<sup>2</sup>C serial link (I<sup>2</sup>C address is userselectable). The MOTION signal is asserted when the VD5377 senses motion and motion X/Y data is accessed over the I<sup>2</sup>C link. The user can choose between Automatic power management mode, where the device will automatically go into low power hibernation if no motion is detected or Manual power management mode where there is a choice of two low power states: Standby or Powerdown. The external navigation LED driver is fully integrated in the device, supporting drive currents up to 14 mA. Where higher power is required, an external driver can be used.

Figure 1. VD5377 simplified system block diagram

Overview VD5377

## 1.1 Technical specification

**Table 1. Technical specification**

| Feature               | Detail                                               |  |  |

|-----------------------|------------------------------------------------------|--|--|

| Resolution            | Programmable up to 3200 cpi                          |  |  |

| Pixel size            | 30.4 μm                                              |  |  |

| Array size            | 20 x 20 pixels                                       |  |  |

| Frame rate            | Up to 3.6 kf/s (auto or manual)                      |  |  |

| Tracking performance  | Up to 650 mm/s (26 in/s)<br>low drift, high accuracy |  |  |

| Supply voltage        | 2.2 V to 3.0 V using internal regulator              |  |  |

| Operating temperature | -20°C to 70°C                                        |  |  |

#### 1.2 VD5377 enhancements

The VD5377 has been optimized for optical finger navigation (OFN) applications. For applications migrating from the previous VD5376 device, the following list highlights the key differences:

- optimized floor plan for improved module design

- enhanced automatic power management mode: fully programmable sleep and wakeup intervals

- ultra-low powerdown mode (<1 μA)</li>

- user-selectable I<sup>2</sup>C addresses with the option to create custom start-up configurations

- programmable polarity on external MOTION signal

- power-on reset (POR) function gated on MOTION signal

- · enhanced performance in high ambient light conditions

- new filter added to aid navigation in low contrast images

- increased LED on-time for greater dynamic range

- simplified support circuit: Rbin and Cosc components now integrated

- smaller external capacitor on VREG (220 nF)

- improved I<sup>2</sup>C frame capture

VD5377 Overview

# 1.3 Floor plan changes

Table 2. Die size and optical center comparison

|                | Conditions                       | VD5377 |        | VD5376 |      |

|----------------|----------------------------------|--------|--------|--------|------|

|                | X (μm)                           | Y (µm) | X (µm) | Υ (μm) |      |

|                | Including seal                   | 1794   | 1758   | 1800   | 1832 |

| Die size       | Including scribe (step & repeat) | 1894   | 1858   | 1900   | 1932 |

| Optical center | Relative to die center           | -83    | +447   | -91    | +319 |

Silicon specification VD5377

# 2 Silicon specification

This chapter contains physical die information.

## 2.1 Silicon thickness

Standard silicon thickness is 180 µm (see Table 37: Delivery formats on page 78).

# 2.2 Die size and optical center

All dimensions and all coordinates are referenced to the origin at die center.

Table 3. Die size

| Conditions                         | X size (μm) | Y size (µm) |

|------------------------------------|-------------|-------------|

| Including seal                     | 1794        | 1758        |

| Including scribe (step and repeat) | 1894        | 1858        |

**Table 4. Optical center**

| Parameter    | X (μm) | Υ (μm) |

|--------------|--------|--------|

| Die center   | 0      | 0      |

| Array center | -83    | +447   |

# 2.3 Pad opening sizes

Table 5. Pad openings

|      | X (μm) | Υ (μm) |

|------|--------|--------|

| Size | 86.4   | 86.4   |

Minimum bond pad pitch: 138 µm.

VD5377 Silicon specification

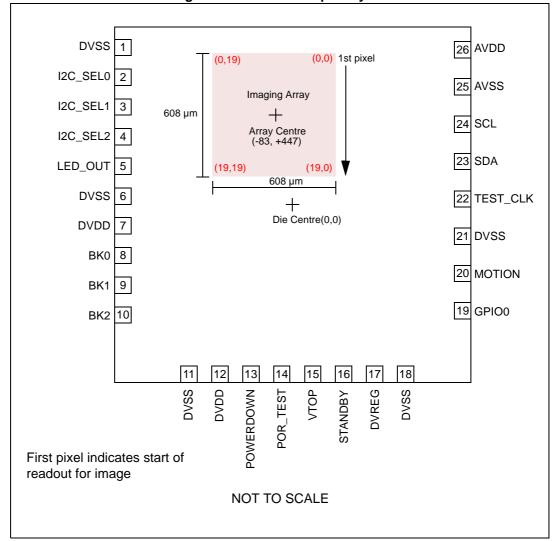

## 2.4 Device pinout

*Figure 2* shows the bond pad layout and *Table 6* provides the bond pad coordinates. All dimensions are in microns.

Figure 2. VD5377 bond pad layout

Silicon specification VD5377

# 2.5 Bond pad coordinates

All dimensions are in microns. Bond pad coordinates correspond to the bond pad centers referenced to the die center.

Table 6. Bond pad coordinates

| Pad # | Pad name  | X co-ordinate | Y co-ordinate |

|-------|-----------|---------------|---------------|

| 1     | DVSS      | -827.6        | 792.7         |

| 2     | I2C_SEL0  | -827.6        | 515.6         |

| 3     | I2C_SEL1  | -827.6        | 378.0         |

| 4     | I2C_SEL2  | -827.6        | 240.3         |

| 5     | LED_OUT   | -827.6        | 102.6         |

| 6     | DVSS      | -827.6        | -35.0         |

| 7     | DVDD      | -827.6        | -218.8        |

| 8     | BK0       | -827.6        | -356.4        |

| 9     | BK1       | -827.6        | -494.1        |

| 10    | BK2       | -827.6        | -631.8        |

| 11    | DVSS      | -649.8        | -810.1        |

| 12    | DVDD      | -511.4        | -810.1        |

| 13    | POWERDOWN | -317.5        | -810.1        |

| 14    | POR_TEST  | -213.8        | -810.1        |

| 15    | VTOP      | -110.1        | -810.1        |

| 16    | STANDBY   | 28.3          | -810.1        |

| 17    | DVREG     | 470.1         | -810.1        |

| 18    | DVSS      | 649.6         | -810.1        |

| 19    | GPIO0     | 827.6         | -632.3        |

| 20    | MOTION    | 827.6         | -484.3        |

| 21    | DVSS      | 827.6         | -336.1        |

| 22    | TEST_CLK  | 827.6         | -187.5        |

| 23    | SDA       | 827.6         | -10.3         |

| 24    | SCL       | 827.6         | 145.4         |

| 25    | AVSS      | 827.6         | 556.0         |

| 26    | AVDD      | 827.6         | 733.4         |

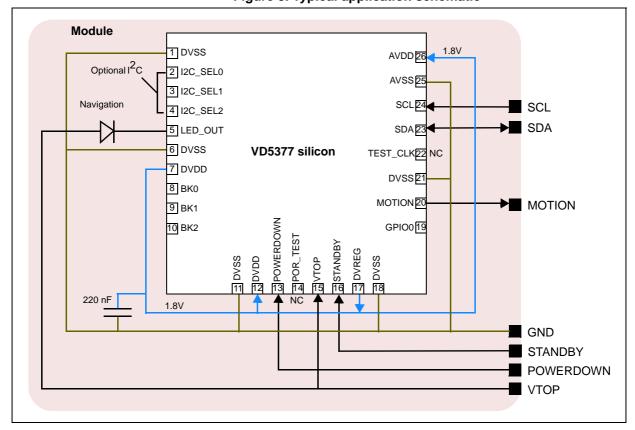

# 3 Application schematic

The VD5377 requires a 2.2 V to 3.0 V external supply. The circuit embeds an internal regulator (DVREG) capable of providing the 1V8 supply for the analog and digital cores.

External wiring is required (at module level for instance) to connect the DVREG 1V8 output to the AVDD/DVDD pins. A typical application schematic is shown in *Figure 3*.

The internal 1.8 V core regulator requires a minimum 220 nF decoupling capacitor. Larger values may increase the minimum power down time which is required to guarantee a proper reset of the device.

Figure 3. Typical application schematic

# 3.1 Signal descriptions

Table 7. Signal descriptions

| Pad # | Signal name                   | Туре                | Description                                                                                                                                                                                                                                             |  |

|-------|-------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | DVSS                          | Supply              | Digital ground                                                                                                                                                                                                                                          |  |

| 2     | I2C_SEL0                      | 1.8V digital input  | I <sup>2</sup> C address select input.                                                                                                                                                                                                                  |  |

| 3     | I2C_SEL1                      | 1.8V digital input  | 5 V tolerant inputs with integrated pull-down resistor. If unconnected default address is 0xA6.                                                                                                                                                         |  |

| 4     | I2C_SEL2                      | 1.8V digital input  | (Pads have internal 35 kOhm pull-down resistors. If connected to VDD, the pull-down resistor is disconnected after the intern micro-controller boot sequence is completed to reduce powe consumption).                                                  |  |

| 5     | LED_OUT                       | Current DAC output  | Navigation LED drive pad. Constant current sink set by internal DAC. Maximum setting 14 mA. For external LED driver use GPIO0.                                                                                                                          |  |

| 6     | DVSS                          | Supply              | Digital ground                                                                                                                                                                                                                                          |  |

| 7     | DVDD                          | Supply              | 1.8 V digital supply                                                                                                                                                                                                                                    |  |

| 8     | BK0                           | -                   | Used in fast capture test mode only                                                                                                                                                                                                                     |  |

| 9     | BK1                           | -                   | Used in fast capture test mode only                                                                                                                                                                                                                     |  |

| 10    | BK2                           | -                   | Used in fast capture test mode only                                                                                                                                                                                                                     |  |

| 11    | DVSS                          | Supply              | Digital ground                                                                                                                                                                                                                                          |  |

| 12    | DVDD                          | Supply              | 1.8 V digital supply                                                                                                                                                                                                                                    |  |

| 13    | POWERDOWN                     | Analog input        | Active high. This disables the internal 1.8 V core regulator. Input switching level is 0.8 V to be compatible with 1.8 V or 2.8 V signal.                                                                                                               |  |

| 14    | POR_TEST                      | -                   | No connect                                                                                                                                                                                                                                              |  |

| 15    | VTOP                          | Supply              | Internal 1.8 V regulator supply input:  – 2.2 to 3.0 V for internal regulator configuration                                                                                                                                                             |  |

| 16    | 16 STANDBY 1.8V digital input |                     | If use_standby_pin register is selected (register 0x5 bit 4):  - In manual mode STANDBY = 1 puts the device in low power mode  - In auto mode STANDBY = 1 disables I <sup>2</sup> C  Otherwise, connect to DVSS if not used.  This pad is 5 V tolerant. |  |

| 17    | DVREG                         | Supply              | 1.8V internal regulator output. Connect to DVDD and AVDD supplies. Requires a 220 nF capacitor to DVSS.                                                                                                                                                 |  |

| 18    | DVSS                          | Supply              | Digital ground                                                                                                                                                                                                                                          |  |

| 19    | GPIO0                         | 3.0V digital I/O    | External LED drive control signal or general purpose I/O. Referenced to Vtop. This pad is 5 V tolerant.                                                                                                                                                 |  |

| 20    | MOTION                        | 3.0V digital output | Motion detection flag. Configurable as Push/Pull or open-drain. Active high or low (programmable polarity). Referenced to Vtop. This pad is 5 V tolerant.                                                                                               |  |

| Pad # | Signal name | Туре               | Description                                                                 |  |  |  |

|-------|-------------|--------------------|-----------------------------------------------------------------------------|--|--|--|

| 21    | DVSS        | Supply             | Digital ground                                                              |  |  |  |

| 22    | TEST_CLK    | -                  | No connect                                                                  |  |  |  |

| 23    | SDA         | 1.8V digital I/O   | I <sup>2</sup> C bidirectional data (open-drain). This pad is 5 V tolerant. |  |  |  |

| 24    | SCL         | 1.8V digital input | I <sup>2</sup> C clock.<br>This pad is 5 V tolerant.                        |  |  |  |

| 25    | AVSS        | Supply             | Analog ground                                                               |  |  |  |

| 26    | AVDD        | Supply             | 1.8 V analog supply                                                         |  |  |  |

Table 7. Signal descriptions (continued)

#### 3.2 Cursor orientation

Figure 4 shows the direction of positive motion vectors relative to silicon orientation with the default power-up register settings: parameters\_2 (0x27) = 0x08 that is, invert\_x = 0, invert\_y = 0 and swap\_xy = 1. An imaging lens is assumed but not shown. The direction of X/Y motion can be reversed or swapped by writing to register 0x27 allowing preferred cursor movement from any die orientation.

Pad 1

Pixel array

A

Imaging lens not shown

Figure 4. VD5377 default XY orientation

System overview VD5377

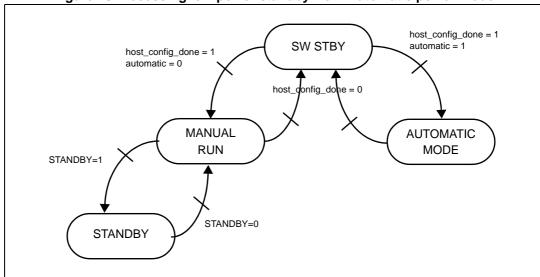

## 4 System overview

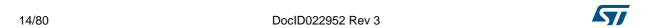

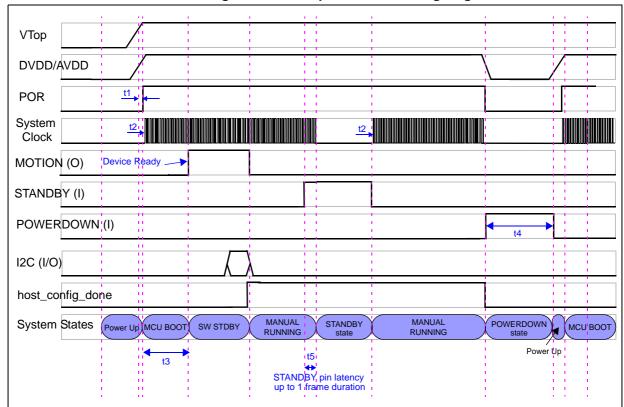

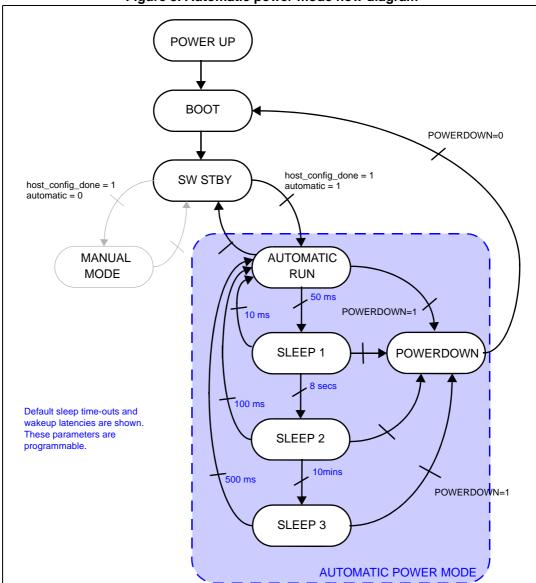

The VD5377 operates in one of two power management modes: MANUAL or AUTOMATIC (see *Figure 5*). After initial MCU BOOT the device enters the SW STBY state and waits for configuration from the host. When configured, the device enters MANUAL RUN or AUTOMATIC RUN mode.

- MANUAL power management mode is the simplest mode where the host initializes the

device which then remains in MANUAL RUN mode until it receives a command to

change mode (either an I<sup>2</sup>C command to return to the SW STBY state or a low power

state using the POWERDOWN or STANDBY pin).

- AUTOMATIC power management mode is an intelligent, power efficient mode where

the device automatically switches to low power mode depending on motion activity.

When initialized, the device will continue to operate autonomously minimizing power

consumption and host CPU overhead.

Figure 5. VD5377 power management modes

VD5377 System overview

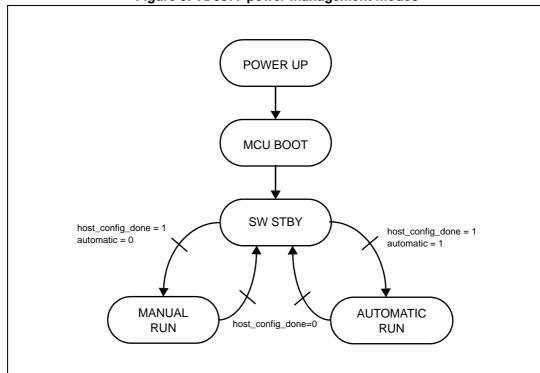

#### 4.1 Manual power management

Manual power mode is the basic mode of the VD5377. After initialization, the sensor remains in MANUAL RUN mode even when no motion activity is detected. The host can use the external POWERDOWN or STANDBY signals to achieve lower current consumption.

- STANDBY pin<sup>(a)</sup> (active high): if set, the system goes into low power STANDBY mode at the end of the current frame. Typical power consumption in STANDBY mode is shown in *Table 8 on page 18*. The internal clock and motion engine are switched off and so the VD5377 does not respond to any I<sup>2</sup>C communication and no motion activity is detected. All register settings are maintained in this state, so when STANDBY is deasserted the system immediately resumes in RUN mode.

- POWERDOWN pin: if set, this signal immediately disables the internal 1.8 V core regulator. After power down, the system needs to be re-initialized. Power consumption is typically <1 µA in this state.</li>

Figure 6. Manual power mode flow diagram

DocID022952 Rev 3

a. During initialization, the user must set the use\_standby\_pin register bit (system\_config 0x05 bit 4) to 1 to enable the STANDBY pin function otherwise it is ignored.

System overview VD5377

*Table 8* summarizes the typical operating current in Manual mode.

Table 8. Typical power consumption<sup>(1)</sup> - Manual mode

|         | Run      |          | Standby | Power down |  |

|---------|----------|----------|---------|------------|--|

| 3 kf/s  | 1.8 kf/s | 0.9 kf/s | Standby |            |  |

| 10.2 mA | 6.9 mA   | 4.5 mA   | 25 μΑ   | <1 µA      |  |

<sup>1.</sup> Includes LED (maximum exposure), led\_dac 14 mA

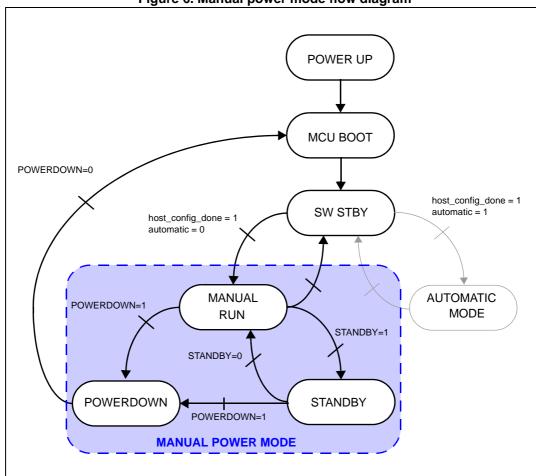

*Figure 7* describes the power-up sequence of the VD5377.

Figure 7. Manual power mode timing diagram

After the MCU boot sequence is completed, the system enters SW STDBY state and the MOTION pin is set to 1 indicating that the device is ready to receive commands from the host. After initialization by the host over I<sup>2</sup>C, the device enters the MANUAL RUN state and the MOTION pin goes low.

Note: The MOTION pin polarity is programmable. If active low polarity is selected during initialization, the MOTION pin will remain high.

If the STANDBY pin is asserted, the system completes the current frame operation before entering the STANDBY state and stopping the internal system clock. When the STANDBY pin is de-asserted, the system clock is restarted and the device resumes in the RUN state (no re-initialization required). If the POWERDOWN pin is asserted (active high), the internal 1.8 V regulator is disabled and the 1.8 V core supply is switched off. When the POWERDOWN pin is de-asserted, the internal 1.8 V regulator is re-enabled triggering a

VD5377 System overview

POR (Power-On Reset) and the MCU re-initializes as at power-up before entering the SW STBY state. The device must be re-configured after POWERDOWN.

Key timing parameters are shown in Table 9.

Table 9. Manual mode timing constraints

| Symbol            | Parameter                                           | Typical    |

|-------------------|-----------------------------------------------------|------------|

| t1                | POR Delay<br>(POR threshold = 1.4 V typ)            | 20 µs      |

| t2                | Clock Startup                                       | 1 µs       |

| t3                | MCU boot time                                       | 450 µs     |

| t4                | Minimum Powerdown time (220 nF regulator capacitor) | 10 ms      |

| t5 <sup>(1)</sup> | Standby pin latency (up to 1 frame at 0.9 kf/s)     | up to 1 ms |

<sup>1.</sup> No  $I^2C$  comms permitted to VD5377 after Standby pin asserted

System overview VD5377

## 4.2 Automatic power management

Automatic power mode is the advanced power saving mode of the VD5377. When this mode is activated, the sensor automatically enters low power modes (called SLEEP states) after a given time if the sensor does not detect any motion.

Figure 8. Automatic power mode flow diagram

A SLEEP state is a low power state where the internal system clock is disabled, the analog block is powered down and only the internal 50 kHz oscillator is running to wake the sensor up periodically. Each time the sensor wakes up, a single frame is captured and the motion versus previous frame is estimated. If motion is detected the system resumes in RUN mode; otherwise if no motion is detected the sensor goes back to SLEEP. Up to three SLEEP states (default) can be selected. The sleep time-out and wake-up latency periods are programmable.

VD5377 System overview

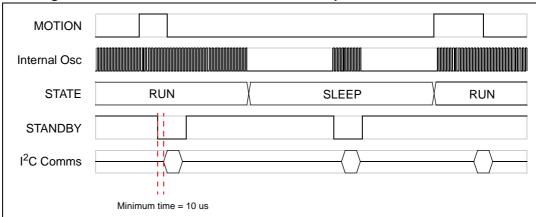

In Automatic power mode, if the use\_standby\_pin register is set, the STANDBY pin is configured as a chip select (active low) to perform I<sup>2</sup>C communications. This allows the host to perform I<sup>2</sup>C communications to the VD5377 at anytime even during SLEEP modes. If the use\_standby\_pin register is not set, the host can only perform I<sup>2</sup>C communications when motion data is pending.

#### Low power states:

- SLEEP states: Typical power consumption in the various sleep states is shown in Table 10.

- POWERDOWN pin: if set, this signal immediately disables the internal 1.8 V core regulator. After power down, the system needs to be re-initialized. Power consumption is typically <1 µA in this state.</li>

|         | rable 10. Typical power consumption - automatic mode |          |        |        |            |            |  |  |

|---------|------------------------------------------------------|----------|--------|--------|------------|------------|--|--|

| Run     |                                                      | Sleep1   | Sleep2 | Sleep3 | Power down |            |  |  |

| 3 kf/s  | 1.8 kf/s                                             | 0.9 kf/s | Sieepi | Sieepz | Sieeps     | rower down |  |  |

| 10.2 mA | 6.9 mA                                               | 4.5 mA   | 350 uA | 60 uA  | 20 uA      | <1 uA      |  |  |

Table 10. Typical power consumption<sup>(1)</sup> - automatic mode

Figure 9 describes the power-up sequence of the VD5377 in AUTOMATIC power management mode. After the MCU boot sequence is completed, the system enters SW STDBY state and the MOTION pin is set to 1 indicating that the device is ready to receive commands from the host. After initialization by the host over I<sup>2</sup>C, the device enters the AUTO RUN state and the MOTION pin will go low.

Note:

The MOTION pin polarity is programmable. If active low polarity is selected during initialization, the MOTION pin will remain high.

After a time, motion is detected and the MOTION PIN goes high. Once motion is detected the device can no longer enter SLEEP until all pending motion data has been read. The host de-asserts the STANDBY pin to enable I<sup>2</sup>C comms (if use\_standby\_pin register was set in initialization routine); motion data is read and the STANDBY pin is re-asserted. After the RunningTimeout period, if no further motion is detected, the device enters the SLEEP1 state. After the Sleep1Latency period, the device wakes up for 1 frame to detect any movement. No motion is detected so the device remains in the SLEEP1 state.

If the POWERDOWN pin is asserted, the internal 1.8 V regulator is disabled and the 1.8 V core supply is switched off. When the POWERDOWN pin is de-asserted, the internal 1.8 V regulator is re-enabled and the MCU re-initializes as at power-up before entering the SW STBY state. The device must be re-configured after POWERDOWN.

<sup>1.</sup> Includes LED (maximum exposure), led\_dac 14 mA

System overview VD5377

VTop DVDD/AVDD POR Osc 44 MHz Osc 50 kHz Device Ready motion detected MOTION (O) motion' read STANDBY (I) through I2C with STANDBY POWERDOWN:(I) as Chip Select I2C (I/O) host\_config\_done AUTO RUNNING System States SLEEP1 POWERDOWN state Power Up MCU BOOT SW STDBY мси воот Power Up RunningTimeout Sleep1Latency 1 frame wake-up duration t3

Figure 9. Automatic power mode timing diagram (use\_standby\_pin=1)

Key timing parameters are shown in *Table 11*.

Table 11. Automatic mode timing constraints

|        | =                                     |         |

|--------|---------------------------------------|---------|

| Symbol | Parameter                             | Typical |

| t1     | POR Delay (POR threshold = 1.4 V typ) | 20 μs   |

| t2     | Clock Startup                         | 1 µs    |

| t3     | MCU boot time                         | 450 µs  |

| t4     | Minimum Powerdown time                | 10 ms   |

VD5377 I/O description

## 5 I/O description

#### 5.1 I2C\_SEL[2:0]

The default I<sup>2</sup>C address is 0xA6. However, in some applications the default address may conflict with other I<sup>2</sup>C devices sharing the bus or it may be necessary to chain multiple OFN devices on the same bus. For that reason, the user can select from one of seven I<sup>2</sup>C addresses as shown in *Table 12*.

| I2CSEL[2:0] | 8-bit I <sup>2</sup> C address |

|-------------|--------------------------------|

| 000         | 0xA6                           |

| 001         | Reserved                       |

| 010         | 0xC6                           |

| 011         | 0xD6                           |

| 100         | 0xE6                           |

| 101         | 0x36                           |

| 110         | 0x46                           |

| 111         | 0x20                           |

Table 12. User-selectable I<sup>2</sup>C addresses

The I2C\_SEL pads have internal pull-down resistors and can be left unconnected for the default address. For any other address, connect pads that require a logic "1" to DVDD (the internal pull-down resistor is automatically disconnected after the internal micro-controller boot sequence is completed to conserve power).

If required, custom configurations can be stored in ROM on the device corresponding to a particular I<sup>2</sup>C address to reduce the number of required register writes by the host. If interested in this feature, please contact STMicroelectronics.

The device  $I^2C$  address can also be configured dynamically by writing to register DEVADDR (0x7c) bits [7:1] (see *Table 13*). This sets the 7-bit base  $I^2C$  address of the device and allows multiple devices with the same default address to be re-mapped dynamically. This operation must be done in 2 steps:

- program register 0x7c using the current device address to program the new one

- access registers with the new device address

Each device must be powered in turn to reconfigure its address and this operation must be repeated each time the system is initialized.

Table 13. Control register to dynamically configure device I<sup>2</sup>C address

| Addr<br>(Hex) | Register name | Signal name            | Bit | Туре | Default<br>(Hex) | Comment                         |

|---------------|---------------|------------------------|-----|------|------------------|---------------------------------|

| 7c            | DEVADDR       | i2cs_index_auto_inc_en | 0   | PRW  | 01               | Auto increment function         |

| 10            | DEVADOR       | i2cs_dev_addr          | 7:1 | PRW  | 53               | I <sup>2</sup> C device address |

I/O description VD5377

## 5.2 LED\_OUT (tracking LED) and GPIO0

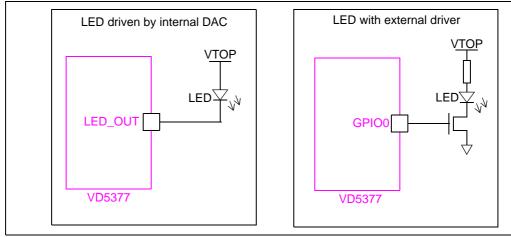

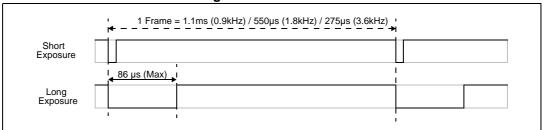

LED\_OUT is controlled by a 3-bit current DAC (0x3 ANALOG\_CTRL2 bits [6:4]) capable of driving up to 14 mA (current sink). Where higher power output is required, an external LED driver can be used controlled by GPIO0 (0x3 ANALOG\_CTRL2 bit7 and 0xd GPIO\_GPIO0 bit 4). *Figure 10* shows the two LED drive options. LED pulse timing is controlled automatically (see *Figure 11*). GPIO0 can also be used as a general purpose I/O and is configured using register 0xd GPIO\_GPIO0 bit 4. A typical configuration of a GPIO is shown in *Figure 12 on page 26*.

Figure 10. LED drive options

Figure 11. LED control

VD5377 I/O description

Table 14. Control register for LED\_OUT and GPIO0

| Addr<br>(Hex) | Register name  | Signal name          | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                                                                                       |

|---------------|----------------|----------------------|-----|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3             | 3 ANALOG_CTRL2 | led_dac_control      | 6:4 | PRW  | 07               | Adjust Led Drive DAC drive output current.  0 = lout = 0 mA  1 = lout = 2.0 mA  2 = lout = 4.0 mA  3 = lout = 6.0 mA  4 = lout = 8.0 mA  5 = lout = 10.0 mA  6 = lout = 12.0 mA  7 = lout = 14.0 mA (default) |

|               |                | led_out_polarity     | 7   | PRW  | 01               | LED_OUT_EN polarity  0 = High when LED must be ON  1 = Low when LED must be ON                                                                                                                                |

|               |                | gpio_gpio0_en        | 0   | PRW  | 00               | GPIO0 output enable (active low) 0 = PAD configured as OUTPUT 1 = PAD configured as INPUT                                                                                                                     |

|               |                | gpio_gpio0_a         | 1   | PRW  | 00               | GPIO0 data output<br>(when _en = 0)                                                                                                                                                                           |

|               |                | gpio_gpio0_zi        | 2   | PR   | 00               | GPIO0 IO value                                                                                                                                                                                                |

| d             | GPIO_GPIO0     | gpio_gpio0_a_ctrl    | 4   | PRW  | 00               | GPIO0 data output select, either as LED_OUT_EN or from register bank.  0 = Output value from HW register  1 = LED_OUT_EN (polarity set in register 0x3 analog_ctrl2 bit 7)                                    |

|               |                | gpio_gpio0_opendrain | 7   | PRW  | 00               | GPIO0 pad open drain control 0 = GPIO0 pad normal config 1 = GPIO0 pad in open drain (A=EN)                                                                                                                   |

I/O description VD5377

Register Bank

gpio\_opendrain

gpio\_en

gpio\_a\_ctrl

gpio\_a

Digital Logic

led\_ctrl

Figure 12. Typical configuration of GPIO

Table 15. Truth-table

| gpio_opendrain | gpio_en | gpio_a or led_ctrl | Condition  | Output    |

|----------------|---------|--------------------|------------|-----------|

| 0              | 0       | 0                  | Output     | 0         |

| 0              | 0       | 1                  | Output     | 1         |

| 0              | 1       | Х                  | Input      | -         |

| 1              | Х       | 0                  | Open-drain | 0         |

| 1              | Х       | 1                  | Open-drain | Tri-state |

VD5377 I/O description

#### 5.3 MOTION

The MOTION pad is a 3.0 V digital I/O pad referenced to VTOP and can be configured either as a push/pull output or open-drain. It combines the functions of motion pending flag and power-on reset indicator (see *Figure 13*). The MOTION signal is driven low at power-up and stays low until the internal MCU boot sequence is completed. Once the boot sequence is completed the MOTION signal goes high and remains high until the device is configured and enters the AUTOMATIC or MANUAL RUN state. Thereafter the level on the MOTION pad depends on the MOTION pin polarity setting (register 0x5 SYSTEM\_CONFIG bit 2).

Note:

In Powerdown, a 35 kOhm pull-down resistor is activated in the Motion pad. This may result in leakage current in the external circuit. Also, in open-drain configuration, careful choice of pull-up resistor is required to ensure the resultant intermediate voltage on the Motion pad does not induce leakage current in the Motion input gate.

POR MOTION

STATE Power Up MCU BOOT SW STDBY AUTO RUN or MANUAL RUN

Table 16. Control register for motion pin polarity

| Addr<br>(Hex) | Register name | Signal name          | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                                                                                                   |

|---------------|---------------|----------------------|-----|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |               | automatic_power_mode | 0   | PRW  | 01               | Power mode scheme 0 = Manual 1 = Automatic                                                                                                                                                                                |

|               |               | motion_pin_polarity  | 2   | PRW  | 00               | MOTION pin polarity (in non IDLE system state)  0 = MOTION pin LOW when motion detected  1 = MOTION pin HIGH when motion detected                                                                                         |

| 5             | SYSTEM_CONFIG | host_config_done     | 3   | PRW  | 00               | Bit needs to be set by host when configured after power up.                                                                                                                                                               |

|               |               | use_standby_pin      | 4   | PRW  | 01               | STANDBY pin is used as chip select to enable I <sup>2</sup> C in AUTO power mode and STANDBY pin is used to wake up the OSC/DVREG (in sleep states in auto power mode).  0 = STANDBY pin not used 1 = STANDBY pin is used |

|               |               | system_state         | 7:5 | RW   | 01               | Legacy register - please use system_state (0x91) instead.                                                                                                                                                                 |

I/O description VD5377

Table 16. Control register for motion pin polarity (continued)

| Addr<br>(Hex) | Register name | Signal name           | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                               |

|---------------|---------------|-----------------------|-----|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|               |               | gpio_motion_en        | 0   | PRW  | 00               | MOTION output enable (active low)  0 = PAD configured as  OUTPUT  1 = PAD configured as INPUT                                         |

|               |               | gpio_motion_a         | 1   | PRW  | 01               | MOTION data output<br>(when _en = 0)                                                                                                  |

|               |               | gpio_motion_zi        | 2   | PR   | 01               | MOTION IO value                                                                                                                       |

| С             | GPIO_MOTION   | gpio_motion_pd        | 3   | PRW  | 01               | MOTION pull-down control<br>(internal 35 kOhms pull-down<br>resistor) - active LOW<br>0 = IO is pulled down<br>1 = IO not pulled down |

|               |               | gpio_motion_a_ctrl    | 4   | PRW  | 00               | MOTION data output origin 0 = Output value from HW register 1 = Output value from motion detect IP                                    |

|               |               | Reserved              | 6:5 | PRW  | 02               | Reserved                                                                                                                              |

|               |               | gpio_motion_opendrain | 7   | PRW  | 00               | MOTION pad open drain control 0 = MOTION pad normal config 1 = MOTION pad in open drain (A = EN)                                      |

#### 5.4 STANDBY

The STANDBY pad is a 1.8 V digital input (active high/ 5 V tolerant). In MANUAL RUN mode, if STANDBY is asserted the device enters a low power STANDBY state **at the end of the current frame** (see *Figure 6: Manual power mode flow diagram on page 17*). When STANDBY is de-asserted the device resumes in RUN mode without requiring reinitialization.

In AUTOMATIC RUN mode, the STANDBY pin acts as a  $I^2C$  enable (see *Figure 14*). When STANDBY = 0,  $I^2C$  is enabled and the VD5377 will respond to  $I^2C$  communication from the host in either RUN or any of the SLEEP states. When STANDBY = 1 the VD5377 consumes less power but will not respond to  $I^2C$  communication. In order to use the STANDBY pin in AUTOMATIC mode the use\_standby\_pin (register 0x5 SYSTEM\_CONFIG bit 4 in *Table 17: Features and scaling on page 31*) must be set during system initialization. If this function is not required, the use\_standby\_pin register should be set to 0 and the STANDBY pad should be connected to either VDD or VSS.

Note: If use\_standby\_pin = 1, the STANDBY pin must be set to 0 before each  $l^2$ C transaction even if motion data is pending.

VD5377 I/O description

Figure 14. In AUTOMATIC mode the STANDBY pin functions as I<sup>2</sup>C enable

## 5.5 POWERDOWN

POWERDOWN is a 3.0 V capable analog input pad referenced to Vtop. The input switching level is 0.8 V and is compatible with 1.8 V and 2.8 V systems. When POWERDOWN is set to 1 the core 1.8 V digital supply is switched off. The device typically consumes <1 μA in this state<sup>(b)</sup>. When POWERDOWN is set to 0, the internal 1.8 V core regulator is enabled and the power-up sequence is initiated (see *Figure 7: Manual power mode timing diagram on page 18*). The device requires full re-initialization after POWERDOWN.

b. See the note in Section 5.3: MOTION on page 27.

Key features VD5377

## 6 Key features

This chapter gives an overview of some of the most important registers and functions.

#### 6.1 Feature count

Feature count is a measure of the useful detail in an image which is used to match successive frames. Generally, the higher the feature count the better the tracking. The FEATURES register (0x31) in *Figure 17* is an 8-bit value representing the 8 MSBs of a 12-bit internal register. A maximum value of 255 represents a feature count of  $16 \times 255 = 4080$ . A reasonable average target feature count is around 2000. Feature counts averaging less than 1000 are likely to result in missing counts and sluggish navigation. This is usually as a result of low contrast in the image or significant vignetting due to the lens.

Note:

On some textured surfaces the feature count may exceed 4080. When this occurs the FEATURES register clips at 255. This is normal and does not affect tracking.

#### 6.2 Minimum features threshold

Without any object on the sensor the feature count will be non-zero, typically around 200. This residual value is usually due to the characteristics of the lens and/or pixel noise but may also be caused by internal or external light reflection which can sometimes result in unintentional cursor movement (or jitter). To prevent this unwanted movement, the motion engine is inhibited until the feature count register exceeds the value in the MIN\_FEATURES register (0x29). Multiply the register value by 16 to get the actual feature count threshold. Default value is  $16d \times 16 = 256$ .

## 6.3 X/Y scaling

The VD5377 outputs a single count for each one pixel displacement of the object. The physical dimension of one pixel is 30  $\mu$ m. The actual displacement depends on the magnification of the lens used. For a lens of magnification M = 0.5 one pixel displacement equates to 60  $\mu$ m physical displacement of the object.

Cursor movement is typically expressed in Counts or Dots per Inch (CPI or DPI). In this case (M = 0.5):

```

Counts per Inch = 25.4mm/60µm = 423 CPI

```

The X/Y scaling registers (*Table 17: Features and scaling on page 31*) can be used to increase or decrease the native CPI according to the following equation:

```

Counts per Inch = register value x M x 100

```

Scale factors can be applied to X and Y independently to compensate for any lens distortion.

VD5377 Key features

Table 17. Features and scaling

| Addr<br>(Hex) | Register name | Signal name      | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                                                                                            |

|---------------|---------------|------------------|-----|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29            | MIN_FEATURES  | min_features     | 7:0 | PRW  | 10               | This register represents the minimum feature count below which motion is inhibited. Multiply by 16 to get the actual feature count threshold. Default is 16d x 16 = 256.                                           |

| 2a            | X_SCALING     | motion_x_scaling | 7:0 | PRW  | 10               | Scaling for X motion vectors. Resolution is calculated as register value x 100 x M, where M is the lens magnification. So, for M = 0.5: 0x08 = 400 CPI that is 8 x 100 x 0.5 0x0c = 600 CPI that is 12 x 100 x 0.5 |

| 2b            | Y_SCALING     | motion_y_scaling | 7:0 | PRW  | 10               | Scaling for Y motion vectors. Resolution is calculated as register value x 100 x M, where M is the lens magnification. So, for M = 0.5: 0x08 = 400 CPI that is 8 x 100 x 0.5 0x0c = 600 CPI that is 12 x 100 x 0.5 |

| 31            | FEATURES      | features_report  | 7:0 | PR   | 00               | Feature count report, as the SUM of absolute differences between pixels and the field average. Bits [11:4] are represented here so x16 to calculate the actual feature count. Maximum value is 4080 = 255 x 16.    |

Key features VD5377

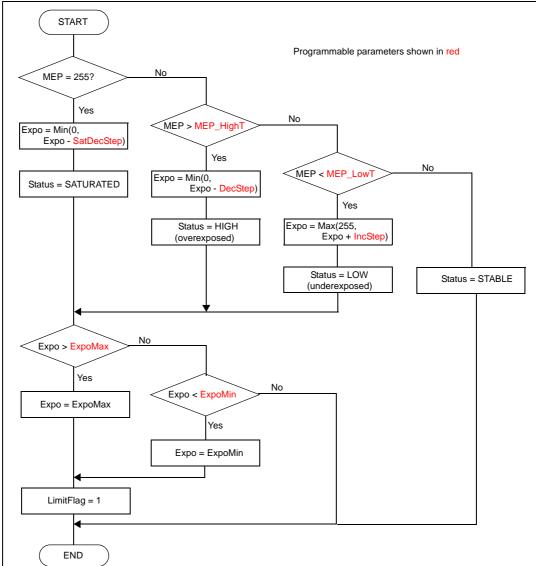

## 6.4 Automatic exposure control

Figure 15 describes the automatic exposure control function. This routine is performed every EXPO\_FRAME\_UPDATE (register 0x4B). The auto-exposure control algorithm works by adjusting exposure until the brightest (max exposed<sup>(c)</sup>) pixel in the frame lies within a specified target range. This is to ensure that no part of the frame is saturated.

Figure 15. Automatic exposure algorithm

Manual or automatic exposure control can be selected. This is controlled using register EXPOSURE\_CONTROL 0x43 bit 0 (see *Table 18*). Bits [6:4] give the exposure status and bit 7 is the exposure limit flag. In automatic exposure control mode, register EXPOTIME

c. In fact the second brightest pixel is used. Note that AEC operates on the exposed frame, that is, before noise cancellation. Processing is done on the CDS frame which is derived from the exposed frame as follows: CDS frame = Exposed frame - Black frame + 8

VD5377 Key features

0x47 gives the current exposure time. This register is also used to enter the required exposure time in manual exposure mode. Register 0x44 is the MAX\_EXPO\_PIX (read-only).

Registers 0x45/0x46 are the upper and lower exposure targets (180 to 240 by default). When the MEP is within this range the exposure is judged to have "converged" and no further exposure updates are required until the MEP moves outside the target range. It is not normally required to adjust the exposure targets.

The default exposure range is 1 to 255. These limits are programmable with registers 0x49/0x4a.

By default, exposure update rate is every two frames. This can be adjusted using register 0x4b. Exposure convergence can be modified by changing the exposure increment/decrement step sizes with registers 0x4e/0x4f/0x50.

Table 18. Exposure control

| Addr<br>(Hex) | Register name                | Signal name                       | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                                                                                            |

|---------------|------------------------------|-----------------------------------|-----|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | EXPOSURE_CONTROL             | autoexpo_en                       | 0   | RW   | 01               | Auto exposure control 0 = Disable 1 = Enable                                                                                                                                                                       |

| 43            |                              | autoexpo_status                   | 6:4 | R    | 00               | Auto exposure status  0 = UNDEF (no AEC performed yet)  1 = LOW (exposure increasing)  2 = STABLE (max exposed pixel within range)  3 = HIGH (exposure decreasing)  4 = SATURATED (exposure saturation decreasing) |

|               |                              | autoexpo_limit_flag               | 7   | R    | 00               | Exposure limit reached flag  0 = Exposure time within range  1 = Exposure time limit reached                                                                                                                       |

| 44            | MAX_EXPO_PIX                 | max_exposed_pixel_v<br>alue       | 7:0 | PR   | 00               | Second maximum pixel value of the current frame (before CDS)                                                                                                                                                       |

| 45            | MAX_EXPO_PIX_THRE<br>SH_HIGH | max_exposed_pixel_t<br>hresh_high | 7:0 | RW   | fO               | High threshold value of max exposed pixel where the AEC is stable.                                                                                                                                                 |

| 46            | MAX_EXPO_PIX_THRE<br>SH_LOW  | max_exposed_pixel_t<br>hresh_low  | 7:0 | RW   | b4               | Low threshold value of max exposed pixel where the AEC is stable.                                                                                                                                                  |

| 47            | EXPOTIME                     | exposure_time                     | 7:0 | PRW  | 40               | Exposure time value in 3 MHz clk period step (333ns)                                                                                                                                                               |

Key features VD5377

**Table 18. Exposure control (continued)**

| Addr<br>(Hex) | Register name             | Signal name               | Bit | Туре | Default<br>(Hex) | Comment                                                                    |

|---------------|---------------------------|---------------------------|-----|------|------------------|----------------------------------------------------------------------------|

| 49            | EXPOTIME_MAX              | exposure_time_max         | 7:0 | RW   | ff               | Maximum exposure time applied by the AEC.                                  |

| 4a            | EXPOTIME_MIN              | exposure_time_min         | 7:0 | RW   | 01               | Minimum exposure time applied by the AEC.                                  |

| 4b            | EXPO_FRAME_UPDAT<br>E     | autoexpo_frame_upda<br>te | 7:0 | RW   | 01               | Exposure update frequency (every N+1 frames). Default is every two frames. |

| 4e            | EXPOTIME_INC_STEP         | expo_inc_step             | 7:0 | RW   | 04               | Exposure increment step (used when below max_expo_pix_thresh_low).         |

| 4f            | EXPOTIME_DEC_STEP         | expo_dec_step             | 7:0 | RW   | 04               | Exposure decrement step (used when above max_expo_pix_thresh_high).        |

| 50            | EXPOTIME_SAT_DEC_<br>STEP | expo_sat_dec_step         | 7:0 | RW   | 10               | Exposure decrement step (used when above max_expo_pix is saturated = 255). |

# 6.5 5 x 5 high pass filter

Before each frame is processed the image data is passed through a high-pass filter to extract edge information. The PARAMETERS\_3 register 0x28 bit 5 (*Table 19*) permits selection between two high pass filter options. 3 x 3 is the default high-pass filter. The alternative 5 x 5 high-pass filter has a lower cut-off frequency and so preserves more information in lower contrast images. This may help improve tracking performance in some situations, although a possible effect is an increase in hover (this can be overcome by increasing min\_features threshold, register 0x29).

Table 19. 5x5 high-pass filter register

| Addr<br>(Hex)   | Register name | Signal name | Bit | Туре | Default<br>(Hex)                                                                                         | Comment  |

|-----------------|---------------|-------------|-----|------|----------------------------------------------------------------------------------------------------------|----------|

| 28 PARAMETERS_3 |               | Reserved    | 3:0 | PRW  | 04                                                                                                       | Reserved |

|                 |               | Reserved    | 4   | PRW  | 01                                                                                                       | Reserved |

|                 | hpf_5x5_sel   | 5           | PRW | 00   | Select between 3 x 3 and 5 x 5 high pass filter.  0 = 3 x 3 high pass filter  1 = 5 x 5 high pass filter |          |

|                 |               | Reserved    | 6   | PRW  | 01                                                                                                       | Reserved |

VD5377 Key features

## 6.6 Sunlight timing

In applications where strong external ambient lighting could interfere with tracking such as direct sunlight, "Sunlight DMIB timing" mode is recommended (0x51 bit 1 = 1). This can either be set to always on, that is 0x51 = 0x2 or set to change automatically when the sensor detects high ambient light conditions (that is, 0x51 = 0x1). See Table 20. The default is "Normal DMIB timing" mode.

Note:

The maximum permitted frame rate in Sunlight timing mode is 3 kf/s (see Section 6.7: Automatic/manual frame rate).

Table 20. Sunlight DMIB timing mode

| Addr<br>(Hex) | Register name | Signal name    | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                                                         |

|---------------|---------------|----------------|-----|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51            | 51 CONTROL    | dmib_ctrl_mode | 0   | RW   | 00               | DMIB controller timing switch mode  0 = Manual (chosen by dmib_timing register)  1 = Automatic (system auto sets the dmib_timing mode, status reported in dmib_timing register) |

|               |               | dmib_timing    | 1   | PRW  | 00               | DMIB controller timing mode 0 = Normal DMIB timing (same as 376 with double expo time possible) 1 = Sunlight DMIB timing                                                        |

|               |               | Reserved       | 7   | PRW  | 00               | Reserved                                                                                                                                                                        |

Key features VD5377

#### 6.7 Automatic/manual frame rate

The VD5377 can operate in either automatic or manual frame rate control mode. The default frame rate control mode is automatic (see *Table 21*, register 0x1c bit 4). This means that the device adjusts frame rate automatically depending on the tracking velocity. By default, frame rate is adjusted in the range 0.9 k to 1.8 k to Max. Because power consumption increases as frame rate increases, automatic frame rate control is the most efficient in terms of power consumption and requires no additional overhead from the host CPU. The maximum frame rate to be applied in auto frame rate mode is set with register 0x1c bits 7:5. The default maximum frame rate is 3 kf/s. Manual frame rate is selected with register 0x1c bits [2:0].

Table 21. Adaptive frame rate control

| Addr<br>(Hex) | Register name          | Signal name             | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                                                                                                                                                                                       |

|---------------|------------------------|-------------------------|-----|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | FRAME_RATE_CONT<br>ROL | frame_rate_sel          | 2:0 | PRW  | 02               | Frame rate selection (value for internal osc running @44MHz)  0 = 0.45 kf/s (2.2 ms period)  1 = 0.9 kf/s (1.1 ms period)  2 = 1.8 kf/s (550 us period)  3 = 2.2 kf/s (450 us period)  4 = 2.6 kf/s (380 us period)  5 = 3.0 kf/s (333 us period)  6 = 3.2 kf/s (310 us period)  7 = 3.6 kf/s (275 us period) |

| 1c            |                        | frame_rate_ctrl         | 4   | RW   | 00               | Frame rate management control 0 = Automatic (0.9 k/1.8 k/Max f/s auto frame rate) 1 = Manual (set with frame_rate_sel reg)                                                                                                                                                                                    |

|               |                        | max_auto_frame_r<br>ate | 7:5 | RW   | 05               | Maximum frame rate to be applied in auto frame rate mode  0 = not allowed  1 = not allowed  2 = 1.8 kf/s (550 us period)  3 = 2.2 kf/s (450 us period)  4 = 2.6 kf/s (380 us period)  5 = 3.0 kf/s (333 us period)  6 = 3.2 kf/s (310 us period)  7 = 3.6 kf/s (275 us period)                                |

Due to CPU bandwidth limitations of the on-board MCU, maximum frame rate is limited to 3kf/s in sunlight timing mode. In Normal DMIB timing mode only (default mode - register 0x51 = 0), the maximum frame rate may be increased up to 3.6 kf/s but in order to meet internal timing constraints, the maximum exposure time (EXPOTIME\_MAX 0x49) needs to be reduced according to *Table 22*. The motion\_threshold\_low\_comp (SPARE 0x32) should also be updated.

VD5377 Key features

### Table 22. Modified exposure limits

|                    | Frame rate control mode |           |          |        |          |          |  |

|--------------------|-------------------------|-----------|----------|--------|----------|----------|--|

|                    |                         | Automatic | Manual   |        |          |          |  |

| Maximum frame rate | 3 kf/s                  | 3.2 kf/s  | 3.6 kf/s | 3 kf/s | 3.2 kf/s | 3.6 kf/s |  |

| Maximum exposure   | 255                     | 232       | 157      | 255    | 249      | 174      |  |

#### Table 23. Motion threshold

| Addr<br>(Hex) | Register name | Signal name                   | Bit | Туре | Default<br>(Hex) | Comment                                                                                                        |

|---------------|---------------|-------------------------------|-----|------|------------------|----------------------------------------------------------------------------------------------------------------|

|               |               | Reserved                      | 0   | RW   | 00               | Reserved                                                                                                       |

|               |               | Reserved                      | 1   | RW   | 00               | Reserved                                                                                                       |

| 32            | SPARE         | motion_threshold_l<br>ow_comp | 7:4 | RW   | 03               | Update motion_threshold_low<br>register for adaptive frame rate:<br>0 = 3.6 kf/s<br>2 = 3.2 kf/s<br>3 = 3 kf/s |

Additional features VD5377

### 7 Additional features

#### 7.1 Auto-movement filter

An auto-movement filter has been added in VD5377 rev 2.0 to enhance the navigation performance in high ambient light conditions.

The filter can only be enabled in automatic power  $\mathsf{mode}^{(d)}$ . On initial wakeup, after sleep, the filter will hold the sensor in the lowest run state until motion is seen is X times in Y period. Both X and Y are programmable.

With the default settings, the AMF will look for motion in three separate 7 ms periods. Once motion is seen in one 7 ms period, the filter will immediately move onto the next 7 ms period.

| Addr<br>(Hex) | Register name  | Signal name                 | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                        |  |

|---------------|----------------|-----------------------------|-----|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               |                | bAutoMoveFilterEn<br>able   | 0   | RW   | 00               | Auto movement filter enable 0 = Disable 1 = Enable                                                                                             |  |

| 8d            | AUTO_MOVEMENT_ | ucAutoMoveFilterFr<br>ameNb | 6:1 | RW   | 07               | Number of frames on which the auto movement filter is applied (must be greater than 1).                                                        |  |

|               | CTRL1          | bAutoMoveSaturate<br>dExpo  | 7   | RW   | 00               | When image in high light and exposure (reg 0x47) is set to 1, flag used by engine to discard motion in this condition.  0 = Disable 1 = Enable |  |

Table 24. Auto-movement filter

38/80 DocID022952 Rev 3

d. Automatic power mode without standby (SYSTEM\_CONFIG 0x5 = 0x09) does not function correctly when the auto-movement filter is enabled. Suggested workaround is to use automatic power mode with use\_standby\_pin enabled. Alternatively, there is a firmware patch available which can be requested from STMicroelectronics.

VD5377 Additional features

Table 24. Auto-movement filter (continued)

| Addr<br>(Hex) | Register name           | Signal name                 | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                                                                                                                                    |

|---------------|-------------------------|-----------------------------|-----|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8e            | AUTO_MOVEMENT_<br>CTRL2 | ucAutoMoveFilterL<br>atency | 3:0 | RW   | 01               | Latency between frames on which the auto movement filter is applied.  0 = 400 us 1 = 1 ms 2 = 1.4 ms 3 = 2 ms 4 = 4 ms 5 = 10 ms 6 = 20 ms 7 = 50 ms 8 = 100 ms 9 = 150 ms 10 = 200 ms 11 = 500 ms 12 = 1 s 13 = 1.5 s 14 = 2 s 15 = 2.6 s |

|               |                         | ucAutoMoveFilterL<br>oop    | 7:4 | RW   | 03               | Set the number of sequences to detect motion to grant motion in sleep mode.                                                                                                                                                                |

Additional features VD5377

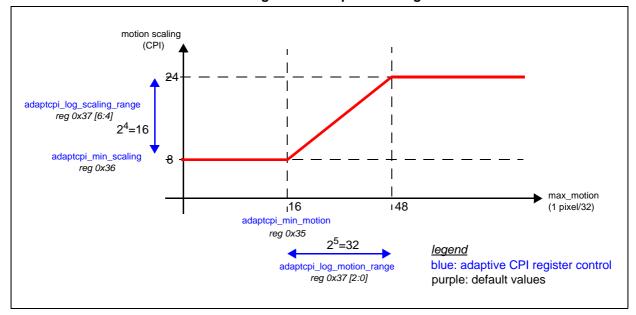

## 7.2 Adaptive CPI

To be able to cope with large screen resolution an adaptive CPI functionality has been implemented in VD5377, where the motion scaling can be adjusted depending on the speed of the detected motion.

The algorithm is shown in *Figure 16* where maximum motion is max\_abs\_motion (register 0x2f).

Figure 16. Adaptive CPI algorithm

Table 25. Adaptive CPI

| Addr<br>(Hex) | Register name            | Signal name              | Bit | Туре | Default<br>(Hex) | Comment                                                                                                                         |

|---------------|--------------------------|--------------------------|-----|------|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 23            | OVERFLOW                 | adapt_cpi_en             | 6   | PRW  | 00               | If set, the CPI is function of the detected motion.  0 = No adaptive CPI  1 = Enable adaptive CPI                               |

| 2f            | MAX_ABS_MOTION           | max_abs_motion           | 6:0 | PR   | 00               | Max(ABS(X motion), ABS(Y motion)) either from integrated or instant motion                                                      |

| 35            | ADAPTCPI_MIN_<br>MOTION  | adaptcpi_min_<br>motion  | 7:0 | PRW  | 10               | Minimum value of max( X frame motion ,  Y frame motion ) from which the CPI is adaptive (if feature enabled) - multiply by 1/32 |

| 36            | ADAPTCPI_MIN_<br>SCALING | adaptcpi_min_<br>scaling | 7:0 | PRW  | 08               | Minimum motion scaling value when adaptive CPI feature is enabled.                                                              |

VD5377 Additional features

Table 25. Adaptive CPI (continued)