## ST25DV04K, ST25DV16K and ST25DV64K device limitations

### Silicon identification

The ST25DV-I2C series is a dynamic NFC/RFID tag ICs with 4, 16 or 64-Kbit EEPROM and Fast transfer mode capability.

Table 1 shows the full list of impacted part numbers (hereinafter referred to as ST25DVxxK). These parts are identified physically by their marking or directly in the application by reading the I<sup>2</sup>C product revision byte.

**Table 1. Device summary**

| References | Package      | Ordering code     | IC reference      | Product code |  |

|------------|--------------|-------------------|-------------------|--------------|--|

|            | SO8N         | ST25DV04K-IER6S3  | 24h               | 24h          |  |

|            |              | ST25DV04K-IER8S3  |                   |              |  |

|            | TSS0P8       | ST25DV04K-IER6T3  |                   |              |  |

|            |              | ST25DV04K-IER8T3  |                   |              |  |

| ST25DV04K  | UFDFPN8      | ST25DV04K-IER6C3  |                   |              |  |

| 5125DV04K  | UFDFPNo      | ST25DV04K-IER8C3  |                   |              |  |

|            | UFDFPN12     | ST25DV04K-JFR6D3  |                   |              |  |

|            | UFDFPN12     | ST25DV04K-JFR8D3  |                   | 0Eh          |  |

|            | Unsawn wafer | ST25DV04K-JFR6U3  |                   | 25h          |  |

|            | WLCSP        | ST25DV04K-JFR6L3  |                   |              |  |

|            | SO8N         | ST25DV16K-IER6S3  |                   |              |  |

|            |              | ST25DV16K-IER8S3  |                   | 26h          |  |

| ST25DV16K  | TSS0P8       | ST25DV16K-IER6T3  | 26h               | 2011         |  |

| 3123DV 10K | 1330F6       | ST25DV16K-IER8T3  |                   |              |  |

|            | UFDFPN12     | ST25DV16K-JFR6D3  |                   | 27h          |  |

|            | OFDFFN12     | ST25DV16KC-JFR8D3 |                   |              |  |

|            | SO8N         | ST25DV64K-IER6S3  |                   |              |  |

| ST25DV64K  |              | ST25DV64K-IER8S3  | 26h<br>26h<br>27h | 26h          |  |

|            | TSS0P8       | ST25DV64KC-IER6T3 |                   |              |  |

|            |              | ST25DV64KC-IER8T3 |                   |              |  |

|            | UFDFPN12     | ST25DV64K-JFR6D3  |                   | 27h          |  |

|            |              | ST25DV64K-JFR8D3  |                   | 2/11         |  |

The IC reference (IC\_REF register) is read from  $I^2C$  at address 0017h (device select code E2 = 1) or from RF by issuing a *Get System Information* or an *Extended Get System Information* command.

The product code is read from I<sup>2</sup>C at address 001Dh or from RF by issuing an *Inventory*, a *Get System Information* or an *Extended Get System Information* command and is the third byte of the UID (after E0h 02h).

The product revision (IC\_REV register) is read from I<sup>2</sup>C at address 0020h (device select code E2 = 1).

## 1 Limitations

Table 2 gives quick references to all documented device limitations of ST25DVxxK and their status:

- A = workaround available

- N = no workaround available

- P = partial workaround available

- '-' = fixed

Applicability of a workaround depends on specific conditions of the target application. Adoption of a workaround may cause restrictions to the target application. Workaround for a limitation is deemed partial if it only reduces the rate of occurrence and/or consequences of the limitation, or if it is fully effective for only a subset of instances on the device or in only a subset of operating modes, of the concerned function.

ES0616 - Rev 1 page 2/17

Table 2. Summary of silicon limitations

| Links to silicon limitations                |                                                                                                                                                                 | Workaround <sup>(1)</sup> | Workaround <sup>(2)</sup> |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|

|                                             | Fast extended read single<br>block RF command not<br>functional for block addresses<br>above 255 (00FFh)                                                        | А                         | А                         |

|                                             | Manage GPO command can<br>affect GPO pin state of all<br>ST25DV-I2C tags present in<br>the RF field                                                             | А                         | A                         |

| RF commands limitations                     | Write message and fast write<br>message commands can<br>affect GPO pin state of other<br>ST25DV-I2C tags present in<br>the RF field when<br>address_flag is set | А                         | Α                         |

|                                             | Write message and fast write<br>message commands can<br>overwrite mailbox content of<br>ST25DV-I2C tags present in<br>the RF field                              | А                         | А                         |

|                                             | Wrong memory address potentially overwritten after tearing during an RF write in EEPROM when V <sub>CC</sub> is present                                         | Α                         | -                         |

|                                             | Wrong memory address potentially overwritten after V <sub>CC</sub> off during an I <sup>2</sup> C write in EEPROM when RF field is present                      | N                         | -                         |

| Tearing robustness limitations              | Potential communication lock after tearing during an RF write in EEPROM when V <sub>CC</sub> is present                                                         | N                         | -                         |

|                                             | Potential communication lock after $V_{CC}$ off during an $I^2C$ write in EEPROM when RF field is present                                                       | N                         | -                         |

|                                             | RF access to EEPROM potentially locked after tearing during an RF read in EEPROM when V <sub>CC</sub> is present                                                | А                         | -                         |

|                                             | I <sup>2</sup> C busy state not released after an I <sup>2</sup> C error                                                                                        | Α                         | -                         |

| I <sup>2</sup> C RF arbitration limitations | RF response corrupted during I <sup>2</sup> C programming cycle when I <sup>2</sup> C is busy                                                                   | N                         | -                         |

| Power supply                                | Potential RF and I²C lock if V <sub>CC</sub> gets disconnected then reconnected when RF field is present                                                        | А                         | А                         |

| Communication limitation                    | Communication limitation on<br>a marginal portion of<br>production parts (sub-carrier<br>frequency drift)                                                       | А                         | А                         |

ES0616 - Rev 1 page 3/17

| Links to silicon limitations  |                                                                                                                | Workaround <sup>(1)</sup> | Workaround <sup>(2)</sup> |

|-------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|

| Fast transfer mode limitation | Fast transfer mode watchdog not started correctly after an I <sup>2</sup> C write message in mailbox           | А                         | А                         |

|                               | RF_PUT_MSG bit wrongly<br>cleared after I <sup>2</sup> C reading<br>MB_LEN_Dyn if message is<br>256 bytes long | А                         | A                         |

- 1. For product code 25h and 27h

- 2. For product code 24h and 26h

#### 1.1 RF commands limitations

## 1.1.1 Fast extended read single block RF command not functional for block addresses above 255 (00FFh)

Impacetd devices: All ST25DVxxK with IC Reference 26h

#### **Description**

When a fast extended read single block RF command is received with a Block Number field value above 255 (00FFh), the ST25DV16K and ST25DV64K return a wrong block value.

The most significant byte of the requested block number of the fast extended read single block command is ignored, and the ST25DV16K and ST25DV64K return the value of the block number pointed by the least significant byte of the requested block number.

#### Workaround

The same functionality of the fast extended read single block command can be achieved using the fast extended read multiple block command and requesting only one block. To achieve this, set the number of blocks field of the fast extended read multiple block command to 0000h.

## 1.1.2 Manage GPO command can affect GPO pin state of all ST25DV-I2C tags present in the RF field Impacetd devices: All ST25DVxxK

#### Description

The Manage GPO command received by a tag, if correctly formatted, is always executed by the tag.

This means that the command can be executed (but is not answered) in the following incorrect cases:

- When command is sent in addressed mode and UID in the command does not match

- When command is sent in selected mode and tag is not in selected state

- When tag is in quiet state

As a consequence, if RF\_GPO\_USER or RF\_GPO\_INTERRUPT interrupts are enabled and if GPO output is enabled too (GPO\_EN bit set to 1), the GPO pin state of the tag can be affected by any correctly formatted Manage GPO command destined to another tag.

### Workaround

To avoid undesired state change on GPO pin, the reader can enable GPO output per tag, only on demand. For this, the GPO\_EN bit can be used. The tag must have the GPO output disabled by default (GPO\_EN set to 0). The reader enables GPO output (GPO\_EN set to 1) before sending a Manage GPO command to this tag. After Manage GPO command is sent, the GPO output is disabled again to avoid any undesired GPO state change due to any Manage GPO commands sent to another tag.

To change value of the GPO\_EN bit, reader must first open the configuration security session by presenting the password 0, and then use the Write Configuration command to write in the GPO system register.

### Workaround for ST25DV-I2C devices with CMOS GPO pin only (product codes 25h and 27h)

For product versions with CMOS GPO pin, it is possible to use energy harvesting to control the GPO output of the tag, by controlling its power supply (VDCG pin).

For this, the VDCG pin is connected to the V\_EH pin. GPO output can then be controlled by enabling or disabling energy harvesting (by writing EH EN bit in EH CTRL Dyn register).

The EH\_EN bit of EH\_CTRL\_Dyn register then acts as output enable/disable bit, just like the GPO\_EN bit would do, but with the advantage of not having to present the configuration password before updating it.

ES0616 - Rev 1 page 4/17

## 1.1.3 Write message and fast write message commands can affect GPO pin state of other ST25DV-I2C tags present in the RF field when address flag is set

Impacetd devices: All ST25DVxxK

#### **Description**

A write message, or fast write message command received by a tag, if correctly formatted, is always executed by the tag and can affect the GPO pin state if the address flag set to 1, even if the UID does not match.

The GPO pin state of the tag can be affected by a correctly formatted write message or fast write message command destined to another tag if the following conditions are met:

- Write message or fast write message is sent with address\_flag set to 1 and non-matching UID

- RF\_PUT\_MSG interruption is enabled

- GPO output is enabled (GPO EN bit set to 1)

- mailbox is enabled (MB MODE set to 1 and MB EN set to 1)

#### Workaround

To avoid undesired state change on GPO pin when receiving the write message command, the reader can enable mailbox only on demand. It is the recommended way of using fast transfer mode.

For this, the MB\_EN bit (bit 0 of MB\_CRTL\_Dyn register) can be used. The tag must have the mailbox disabled by default (MB\_EN set to 0), and enabled only when fast transfer mode exchange session is ongoing between this tag and the reader.

If this method cannot be put in place, then the reader can temporarily enable/disable the GPO output, as described in the workaround of Section 1.1.2 Manage GPO command can affect GPO pin state of all ST25DV-I2C tags present in the RF field.

## 1.1.4 Write message and fast write message commands can overwrite mailbox content of ST25DV-I2C tags present in the RF field

Impacetd devices: All ST25DVxxK

### Description

A write message, or fast write message command received by a tag, if correctly formatted is always executed by the tag. This means that the command can be executed (but not answered) in the following incorrect cases:

- When command is sent in address mode and UID in the command does not match

- · When command is sent in selected mode and tag is not in selected state

- When tag is in quiet state

As a consequence, content of the mailbox can be overwritten by a correctly formatted write message or fast write message command destined to another tag if the following conditions are met:

- mailbox is enabled (MB\_MODE set to 1 and MB\_EN set to 1)

- a message from RF is already present in the mailbox

If mailbox is enabled and no message is present, or if message present is from I<sup>2</sup>C host, the content of mailbox is not modified.

#### Workaround

To avoid undesired corruption of the mailbox content when receiving the write message command, the reader can enable mailbox only on demand. It is the recommended way of using fast transfer mode.

For this, the MB\_EN bit (bit 0 of MB\_CRTL\_Dyn register) can be use. The tag must have the mailbox disabled by default (MB\_EN set to 0), and enabled only when fast transfer mode exchange session is ongoing between this tag and the reader.

## 1.2 Tearing robustness limitations

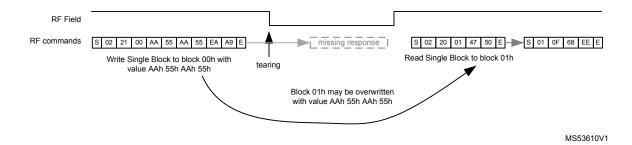

# 1.2.1 Wrong memory address potentially overwritten after tearing during an RF write in EEPROM when V<sub>CC</sub> is present

Impacted devices: All ST25DVxxK devices with product code 25h and 27h

**Description**

ES0616 - Rev 1 page 5/17

If the following conditions are met:

- V<sub>CC</sub> is powered during the complete operation

- RF field is lost during the EEPROM programming phase of any RF write command to EEPROM

- next RF command is any command that reads data from the EEPROM

Then, depending on the tearing timing in the programming phase, the memory content can potentially be overwritten at block address pointed by the RF read command that follows the tearing.

Any memory address can be overwritten, including read-only addresses.

There is no risk for write and read commands that do not access the EEPROM.

RF commands that write into EEPROM are:

- Write single block

- Lock block

- Write multiple blocks

- Write AFI

- Lock AFI

- Write DSFID

- Lock DSFID

- Extended write single block

- Extended lock block

- Extended write multiple blocks

- · Write configuration

- Write password

Figure 1. Wrong memory address potentially overwritten after tearing during an RF write in EEPROM when V<sub>CC</sub> is present

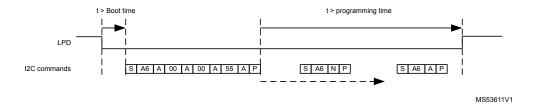

#### Workaround

This limitation has been fixed in devices with product codes 24h and 26h in revision 13h.

For devices with product codes 25h and 27h the following workaround can be used.

The LPD pin must be permanently kept at high level when  $V_{CC}$  is present, and must be pulled to low level only during transmission of  $I^2C$  commands to the ST25DV-I2C.

To allow ST25DV-I2C to execute properly the I<sup>2</sup>C command, the I<sup>2</sup>C master must:

- wait for internal regulator turn on time

- wait for internal LPD boot time after pulling LPD from high to low level, before starting to send I<sup>2</sup>C commands

For more details about turning on time of internal regulator and LPD boot time, refer to Dynamic NFC/RFID tag IC with 4-Kbit, 16-Kbit or 64-Kbit EEPROM, and fast transfer mode capability (DS10925) datasheet.

ES0616 - Rev 1 page 6/17

To allow ST25DV-I2C to program correctly EEPROM after a valid  $I^2C$  write command in EEPROM, the  $I^2C$  master must wait the end of programming time before rising LPD from low to high level. For programming time tw definition refer to Dynamic NFC/RFID tag IC with 4-Kbit, 16-Kbit or 64-Kbit EEPROM, and fast transfer mode capability (DS10925) datasheet

Figure 2. Workaround of wrong memory address potentially overwritten after tearing during an RF write in EEPROM when V<sub>CC</sub> is present (product codes 25h and 27h in rev 12h)

# 1.2.2 Wrong memory address potentially overwritten after V<sub>CC</sub> off during an I<sup>2</sup>C write in EEPROM when RF field is present

Impacted devices: All ST25DVxxK devices with product code 25h and 27h

#### **Description**

If the following conditions are met:

- RF field is powering the tag during the complete operation

- V<sub>CC</sub> is lost during the EEPROM programming phase of any I<sup>2</sup>C write command to EEPROM

- next I<sup>2</sup>C command is a read that accesses data from the EEPROM

Then, depending on the tearing timing in the programming phase, the memory content can potentially be overwritten at memory address pointed by the I<sup>2</sup>C read command that follows the tearing.

Any memory address can be overwritten, including read-only addresses.

There is no risk for write and read commands that do not access the EEPROM.

#### Workaround

There is no workaround for product with product code 25h and 27h.

This limitation has been fixed in product with product code 24h and 26h in revision 13h.

### 1.2.3 Potential communication lock after tearing during an RF write in EEPROM when V<sub>CC</sub> is present

Impacted devices: All ST25DVxxK devices with product code 25h and 27h.

## **Description**

If the following conditions are met:

- V<sub>CC</sub> is powered during the complete operation

- RF field is lost during the EEPROM programming phase of any RF write command to EEPROM

- next RF command is a command that writes data to the EEPROM.

Then, depending on the tearing timing in the programming phase, both RF and I<sup>2</sup>C communication to the device can potentially get blocked.

No overwrite of memory occurs in this case, and data from the last write command is not programmed into memory.

In order to recover communication with the device, a complete power-off/power-on cycle must be performed (with both RF field and  $V_{CC}$  removed from the device).

There is no risk of blocking if at least one of the two write commands does not access the EEPROM.

ES0616 - Rev 1 page 7/17

RF commands that write into the EEPROM are:

- Write single block

- Lock block

- Write multiple blocks

- Write AFI

- Lock AFI

- Write DSFID

- Lock DSFID

- Extended write single block

- Extended lock block

- Extended write multiple blocks

- Write configuration

- · Write password

#### Workaround

There is no workaround for product with product code 25h and 27h.

This limitation has been fixed in product with product code 24h and 26h and revision 13h.

# 1.2.4 Potential communication lock after V<sub>CC</sub> off during an I<sup>2</sup>C write in EEPROM when RF field is present

Impacted devices: All ST25DVxxK devices with product code 25h and 27h.

#### **Description**

If the following conditions are met:

- RF field is powering the tag during the complete operation

- V<sub>CC</sub> is lost during the EEPROM programming phase of any I<sup>2</sup>C write command to EEPROM

- next I<sup>2</sup>C command is a read that accesses data from the EEPROM

Then, depending on the tearing timing in the programming phase, both RF and I<sup>2</sup>C communication with the device can potentially get blocked.

No overwrite of memory occurs in this case, and data from the last write command is not programmed into memory.

In order to recover communication with the device, a complete power-off/power-on cycle must be performed (with both RF field and  $V_{CC}$  removed from the device).

There is no risk of blocking if at least one of the two write commands does not access the EEPROM.

### Workaround

There is no workaround for product with product code 25h and 27h.

This limitation has been fixed in product with product code 24h and 26h and revision 13h.

## 1.2.5 RF access to EEPROM potentially locked after tearing during an RF read in EEPROM when V<sub>CC</sub> is present

Impacted devices: All ST25DVxxK devices with product code 25h and 27h.

## **Description**

If the following conditions are met:

- V<sub>CC</sub> is powered during the complete operation

- RF field is lost during the EEPROM read phase of any RF read command to EEPROM (EEPROM is read during RF response)

- RF field lost is immediately followed by an I<sup>2</sup>C command with a device slave address different from A6h/A7h or AEh/AFh (I<sup>2</sup>C commands for another slave device).

Then, depending on the tearing timing in the EEPROM reading phase, the access to EEPROM from RF can be blocked: any RF command that reads data into EEPROM is answered with all data values to 0.

ES0616 - Rev 1 page 8/17

RF commands that read into EEPROM are:

- Inventory

- Read single block

- · Read multiple blocks

- Extended read single block

- Extended read multiple blocks

- Get system info

- Extended get system info

- Get multiple block security status

- Extended get multiple block security status

- Read configuration

- Present password

- · Fast read single block

- Fast read multiple block

- Fast extended read single block

- Fast extended read multiple block

#### Workaround

This limitation has been fixed in product with product codes 24h and 26h in revision 13h.

For product with product codes 25h and 27h, the following workaround can be used.

The LPD pin must be permanently kept at high level when  $V_{CC}$  is present, and must be pulled to low level only during transmission of  $I^2C$  commands to the ST25DV-I2C.

To allow ST25DV-I2C to execute properly the I<sup>2</sup>C command, the I<sup>2</sup>C master must:

- wait for internal regulator turn on time

- wait for internal LPD boot time after pulling LPD from high to low level, before starting to send an I<sup>2</sup>C command.

For more details about turning on time of internal regulator and LPD boot time, refer to Dynamic NFC/RFID tag IC with 4-Kbit, 16-Kbit or 64-Kbit EEPROM, and fast transfer mode capability (DS10925) datasheet.

To allow ST25DV-I2C to program correctly EEPROM after a valid I<sup>2</sup>C write command in EEPROM, the I<sup>2</sup>C master must wait the end of programming time before rising LPD from low to high level. For programming time tw definition refer to Dynamic NFC/RFID tag IC with 4-Kbit, 16-Kbit or 64-Kbit EEPROM, and fast transfer mode capability (DS10925) datasheet.

### 1.3 I<sup>2</sup>C RF arbitration limitations

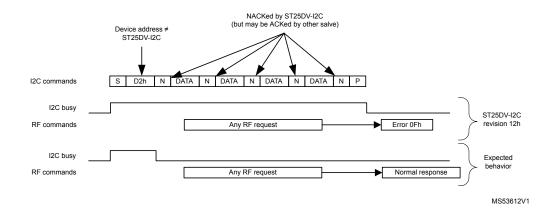

### 1.3.1 I<sup>2</sup>C busy state not released after an I<sup>2</sup>C error

Impacted devices: All ST25DVxxK devices with product code 25h and 27h.

#### **Description**

When an error occurs in any I<sup>2</sup>C frame (implying the return of a no ACK bit by the ST25DV-I2C), the arbitration does not release the exclusive access and stays in I<sup>2</sup>C busy state until the stop condition (or the I<sup>2</sup>C timeout condition) is reached.

As a consequence, any RF command received after a no ACK condition and before the I<sup>2</sup>C stop condition (or I<sup>2</sup>C timeout), is not answered or answered with error 0Fh.

ES0616 - Rev 1 page 9/17

In case of intense traffic on the  $I^2C$  bus (i.e. multiple slave devices with several frequent accesses), this limitation can create latency or difficult communication from RF.

Figure 3. I<sup>2</sup>C busy state not released after an I<sup>2</sup>C error

#### Workaround

This limitation has been fixed in devices with product codes 24h and 26h in revision 13h.

For devices with product codes 25h and 27h, the following workaround can be used.

The LPD pin must be permanently kept at high level when VCC is present, and must be pulled to low level only during transmission of I<sup>2</sup>C commands to the ST25DV-I2C.

To allow ST25DV-I2C to execute properly the I<sup>2</sup>C command, the I<sup>2</sup>C master must:

- · wait for internal regulator turn on time

- wait for internal LPD boot time after pulling LPD from high to low level, before starting to send I<sup>2</sup>C command

For more details about turning on time of internal regulator and LPD boot time, refer to *Dynamic NFC/RFID tag IC* with 4-Kbit, 16-Kbit or 64-Kbit EEPROM, and fast transfer mode capability (DS10925) datasheet.

To allow ST25DV-I2C to program correctly EEPROM after a valid I<sup>2</sup>C write command in EEPROM, the I<sup>2</sup>C master must wait the end of programming time before rising LPD from low to high level. For programming time tw definition refer to *Dynamic NFC/RFID tag IC with 4-Kbit, 16-Kbit or 64-Kbit EEPROM, and fast transfer mode capability* (DS10925) datasheet.

### 1.3.2 RF response corrupted during I<sup>2</sup>C programming cycle when I<sup>2</sup>C is busy

Impacted devices: All ST25DVxxK devices with product code 25h and 27h.

### **Description**

If an RF command is received during an I<sup>2</sup>C write command to EEPROM (when I<sup>2</sup>C is busy), and if the RF response occurs during the programing phase following the I<sup>2</sup>C write command (right after the STOP bit condition), then the RF response gets corrupted after the I<sup>2</sup>C STOP condition and returns random values instead of the expected values (01h, 0Fh, 68h, FEh).

This does not lock access to the device, neither RF nor I<sup>2</sup>C and does not corrupt any data.

#### Workaround

There is no workaround for product with product code 25h and 27h.

This limitation has been fixed in product with product code 24h and 26h in revision 13h.

## 1.4 Power supply limitations

## 1.4.1 Potential RF and I<sup>2</sup>C lock if V<sub>CC</sub> gets disconnected then reconnected when RF field is present

Impacted devices: All ST25DVxxK devices.

Description

ES0616 - Rev 1 page 10/17

When the device is powered both by  $V_{CC}$  and RF field, if  $V_{CC}$  pin gets disconnected and left floating (i.e.  $V_{CC}$  is connected to a microcontroller GPIO, and the GPIO configuration is changed from output to HiZ), the ST25DVxxK enter an unexpected state where approximately 1.4 V is present on the floating  $V_{CC}$  pin.

Once the unexpected  $V_{CC}$  at 1.4 V state is reached, the ST25DV-I2C returns to its normal state in the following conditions:

- If RF field disappears (the ST25DV-I2C goes completely off and restarts in normal state when either RF field or V<sub>CC</sub> power come back)

- If any RF command is received (V<sub>CC</sub> then goes to 0 V)

- If V<sub>CC</sub> rises again to its nominal value (>1.8 V).

Nevertheless, if during this unexpected  $V_{CC}$  at 1.4 V state, the  $V_{CC}$  is pulled down to 0 V and then to its nominal value (1.4 V, then 0 V, then above 1.8 V), the ST25DV-I2C can enter a deadlock state where all I<sup>2</sup>C accesses are not acknowledged and any RF command is answered with error 0Fh.

The trigger of the deadlock is dependent upon the duration of the negative pulse on V<sub>CC</sub>.

The negative pulse is acting as a discharge of internal capacitors of the ST25DV-I2C. If the pulse is shorter than 1 ms, the capacitors are not fully discharged and correct internal reset is not occurring, setting the ST25DV-I2C in deadlock state.

#### Workaround

Several workarounds are available:

- Proper reset is done on V<sub>CC</sub> side before disconnecting V<sub>CC</sub> (before configuring the GPIO that controls V<sub>CC</sub> to HiZ), with duration >1 ms

- Proper reset is done on V<sub>CC</sub> side before connecting again V<sub>CC</sub> (before configuring the GPIO that controls V<sub>CC</sub> from HiZ to its nominal value), with duration >1 ms

- If the glitch to 0 V on V<sub>CC</sub> that triggers the deadlock state is short enough, an additional capacitor on V<sub>CC</sub> with time constant longer than the glitch can filter it

- On ST25DV-I2C versions with product codes 51h and 53h, it is possible to properly reset the device by setting the LPD pin high

### 1.5 Communication limitation

## 1.5.1 Communication limitation on a marginal portion of production parts (sub-carrier frequency drift)

Impacted device: All ST25DVxxK devices.

### **Description**

In a limited portion of the reading range, and on marginal portion of production parts, communications between some NFC readers and the ST25 products listed above may be lost (communication hole). The communication loss is more likely to occur as the ambient temperature decreases.

The reader and the tag antennas dimensions are impacting the distance where the communication hole happens. The failure mechanism is a loss of clock cycles during the tag back-scattering under some field conditions. Therefore, the tag response may be transmitted with a sub-carrier frequency drift and not be decoded properly by some readers.

#### Workarounds

- As the communication hole happens only at certain field strength, moving the tag closer or farther to the

reader can allow communication with the tag. Applications where the ST25DV is in movement ("tap"

gesture, moving parts in production line,...) are less likely to experience the communication loss, as the

communication protocol includes retries

- As the temperature has an impact on the issue, using the tag in higher temperature can allow communication with the tag

- Replacing device with a ST25DVxxKC revision 13h (please contact your local ST sales office for availability on specific options).

- Some RF readers are not sensitive to a sub-carrier frequency drift. Reading hole is not seen when using those readers. Recommended readers: ST25R3916, ST25R3916B, ST25R3917, ST25R3917B, ST25R3918, ST25R3919B, ST25R3911B, ST25R3912, ST25R3914, ST25R3915, ST25R3920, and ST25R3920B

ES0616 - Rev 1 page 11/17

#### 1.6 Fast transfer mode limitation

# 1.6.1 Fast transfer mode watchdog not started correctly after an I<sup>2</sup>C write message in mailbox Impacted devices: All ST25DVxxK devices.

#### **Description**

At the end of a valid RF write message command in mailbox, the RF\_PUT\_MSG flag is set in MB\_CTRL\_Dyn register. This flag must be cleared only if the mailbox is deactivated or if the I<sup>2</sup>C has read the complete message, or if the watchdog is triggered. But if the message is 256 bytes long, and if the first I<sup>2</sup>C command after the RF has written the message is a read of MB\_LEN\_Dyn register (user address 2007h), the RF\_PUT\_MSG flag is wrongly cleared.

#### Workaround

After the RF has written a message in the mailbox, it is recommended to check the MB\_CTRL\_Dyn register to verify if a message is present, before reading MB\_LEN\_Dyn to check its size. Therefore, it is recommended for the I2C host to read first MB\_CTRL\_Dyn, then MB\_LEN\_dyn, then the message in mailbox. This can be done in a single read sequential command, starting at address 2006h (MB\_CTRL\_Dyn) and ending at end of the mailbox (258 bytes are read). This sequentially reads the MB\_CTRL\_Dyn register, the MB\_LEN\_Dyn register and the full mailbox content.

## 1.6.2 RF\_PUT\_MSG bit wrongly cleared after I<sup>2</sup>C reading MB\_LEN\_Dyn if message is 256 bytes long Impacted devices: All ST25DVxxK devices.

#### **Description**

At the end of a valid RF Write Message command in mailbox, the RF\_PUT\_MSG flag is set in MB\_CTRL\_Dyn register. This flag must be cleared only if the mailbox is deactivated or if the I²C has read the complete message, or if the watchdog is triggered. But if the message is 256 bytes long, and if the first I²C command after the RF has written the message is a read of MB\_LEN\_Dyn register (user address 2007h), the RF\_PUT\_MSG flag is wrongly cleared.

#### Workaround

After the RF has written a message in the mailbox, it is recommended to check the MB\_CTRL\_Dyn register to verify if a message is present, before reading MB\_LEN\_Dyn to check its size. Therefore, it is recommended for the I²C host to read first MB\_CTRL\_Dyn, then MB\_LEN\_dyn, then the message in mailbox. This can be done in a single read sequential command, starting at address 2006h (MB\_CTRL\_Dyn) and ending at end of the mailbox (258 bytes are read). This sequentially reads the MB\_CTRL\_Dyn register, the MB\_LEN\_Dyn register and the full mailbox content.

ES0616 - Rev 1 page 12/17

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 07-Jul-2023 | 1       | Initial release. |

ES0616 - Rev 1 page 13/17

## **Contents**

| 1    | Limi   | tations             |                                                                                                                                                  | .2  |

|------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 1.1    | RF con              | nmands limitations                                                                                                                               | . 4 |

|      |        | 1.1.1               | Fast extended read single block RF command not functional for block addresses above 255 (00FFh)                                                  | . 4 |

|      |        | 1.1.2               | Manage GPO command can affect GPO pin state of all ST25DV-I2C tags present in the RF field                                                       | . 4 |

|      |        | 1.1.3               | Write message and fast write message commands can affect GPO pin state of other ST25DV-I2C tags present in the RF field when address_flag is set | . 5 |

|      |        | 1.1.4               | Write message and fast write message commands can overwrite mailbox content of ST25DV-I2C tags present in the RF field                           | . 5 |

|      | 1.2    | Tearing             | g robustness limitations                                                                                                                         | . 5 |

|      |        | 1.2.1               | Wrong memory address potentially overwritten after tearing during an RF write in EEPROM when $V_{CC}$ is present                                 | . 5 |

|      |        | 1.2.2               | Wrong memory address potentially overwritten after $V_{CC}$ off during an $I^2C$ write in EEPROM when RF field is present                        | . 7 |

|      |        | 1.2.3               | Potential communication lock after tearing during an RF write in EEPROM when V <sub>CC</sub> is present                                          | . 7 |

|      |        | 1.2.4               | Potential communication lock after V <sub>CC</sub> off during an I <sup>2</sup> C write in EEPROM when RF field is present                       | . 8 |

|      |        | 1.2.5               | RF access to EEPROM potentially locked after tearing during an RF read in EEPROM when $V_{CC}$ is present                                        | . 8 |

|      | 1.3    | I <sup>2</sup> C RF | arbitration limitations                                                                                                                          | . 9 |

|      |        | 1.3.1               | I <sup>2</sup> C busy state not released after an I <sup>2</sup> C error                                                                         | . 9 |

|      |        | 1.3.2               | RF response corrupted during I <sup>2</sup> C programming cycle when I <sup>2</sup> C is busy                                                    | 10  |

|      | 1.4    | Power               | supply limitations                                                                                                                               | 10  |

|      |        | 1.4.1               | Potential RF and I <sup>2</sup> C lock if V <sub>CC</sub> gets disconnected then reconnected when RF field is present                            | 10  |

|      | 1.5    | Comm                | unication limitation                                                                                                                             | 11  |

|      |        | 1.5.1               | Communication limitation on a marginal portion of production parts (sub-carrier frequency drift)                                                 | 11  |

|      | 1.6    | Fast tra            | ansfer mode limitation                                                                                                                           | 12  |

|      |        | 1.6.1               | Fast transfer mode watchdog not started correctly after an I <sup>2</sup> C write message in mailbox                                             | 12  |

|      |        | 1.6.2               | RF_PUT_MSG bit wrongly cleared after I <sup>2</sup> C reading MB_LEN_Dyn if message is 256 bytes long                                            | 12  |

| Rev  | ision  | history             |                                                                                                                                                  | 13  |

| List | of tak | oles                |                                                                                                                                                  | 15  |

| List | of fig | ures                |                                                                                                                                                  | 16  |

ES0616 - Rev 1 page 14/17

## **List of tables**

| Table 1. | Device summary                 |

|----------|--------------------------------|

| Table 2. | Summary of silicon limitations |

| Table 3. | Document revision history      |

ES0616 - Rev 1 page 15/17

## **List of figures**

| Figure 1. | Wrong memory address potentially overwritten after tearing during an RF write in EEPROM when V <sub>CC</sub> is present 6 |

|-----------|---------------------------------------------------------------------------------------------------------------------------|

|           | Workaround of wrong memory address potentially overwritten after tearing during an RF write in EEPROM when                |

|           | V <sub>CC</sub> is present (product codes 25h and 27h in rev 12h)                                                         |

| Figure 3. | I <sup>2</sup> C busy state not released after an I <sup>2</sup> C error                                                  |

ES0616 - Rev 1 page 16/17

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

ES0616 - Rev 1 page 17/17