# STM32L4 - PWR

パワーコントロール

Revision 1

|               |                       |                            |

|---------------|-----------------------|----------------------------|

| Wake-up<br>時間 | RUN (Range1) (80 MHz) | 120 $\mu$ A / MHz**        |

|               | RUN (Range2) (26 MHz) | 100 $\mu$ A / MHz**        |

|               | LPRUN (2 MHz)         | 112 $\mu$ A / MHz**        |

|               | SLEEP (26 MHz)        | 35 $\mu$ A / MHz           |

|               | LPSLEEP (2 MHz)       | 48 $\mu$ A / MHz           |

|               | STOP 1 (full に保持)     | 6.6 $\mu$ A / 6.9 $\mu$ A* |

|               | STOP 2 (full に保持)     | 1.1 $\mu$ A / 1.4 $\mu$ A* |

|               | STANDBY + 32 KB RAM   | 350 nA / 650 nA*           |

|               | STANDBY               | 115 nA / 415 nA*           |

|               | SHUTDOWN              | 30 nA / 330 nA*            |

|               | VBAT                  | 4 nA / 300 nA*             |

Typ @ VDD = 1.8 V @ 25 °C

\* : with RTC

\*\* : from SRAM1

## FlexPowerControl

- 効率的な実行

- 7つのlow-power モード、いくつかのサブモード

- 高い柔軟性

## Application の利点

- ハイパフォーマンス

→ CoreMark スコア = 273

- 高い電力効率

→ ULPBbench スコア = 150

- 高速ウェイクアップをサポートした7つの low-power モード

- I/Oからのウェイクアップ時 30 nA 以下

- 32 KB RAM 保持時 350 nA 以下

- 多数のペリフェラルからウェイクアップ

- Runモードで 100  $\mu$ A/ MHz 以下

- バッテリーバックアップモード(RTC含む) およびバックアップレジスタサポート

- 独立した電源

## Application の利点

- アクティブなペリフェラル、必要なパフォーマンスと必要なウェイクアップソースに応じて、低消費電力化への高い柔軟性

- バッテリー寿命の増加

- 外部シフターを除去することによって、BOMコストの節約

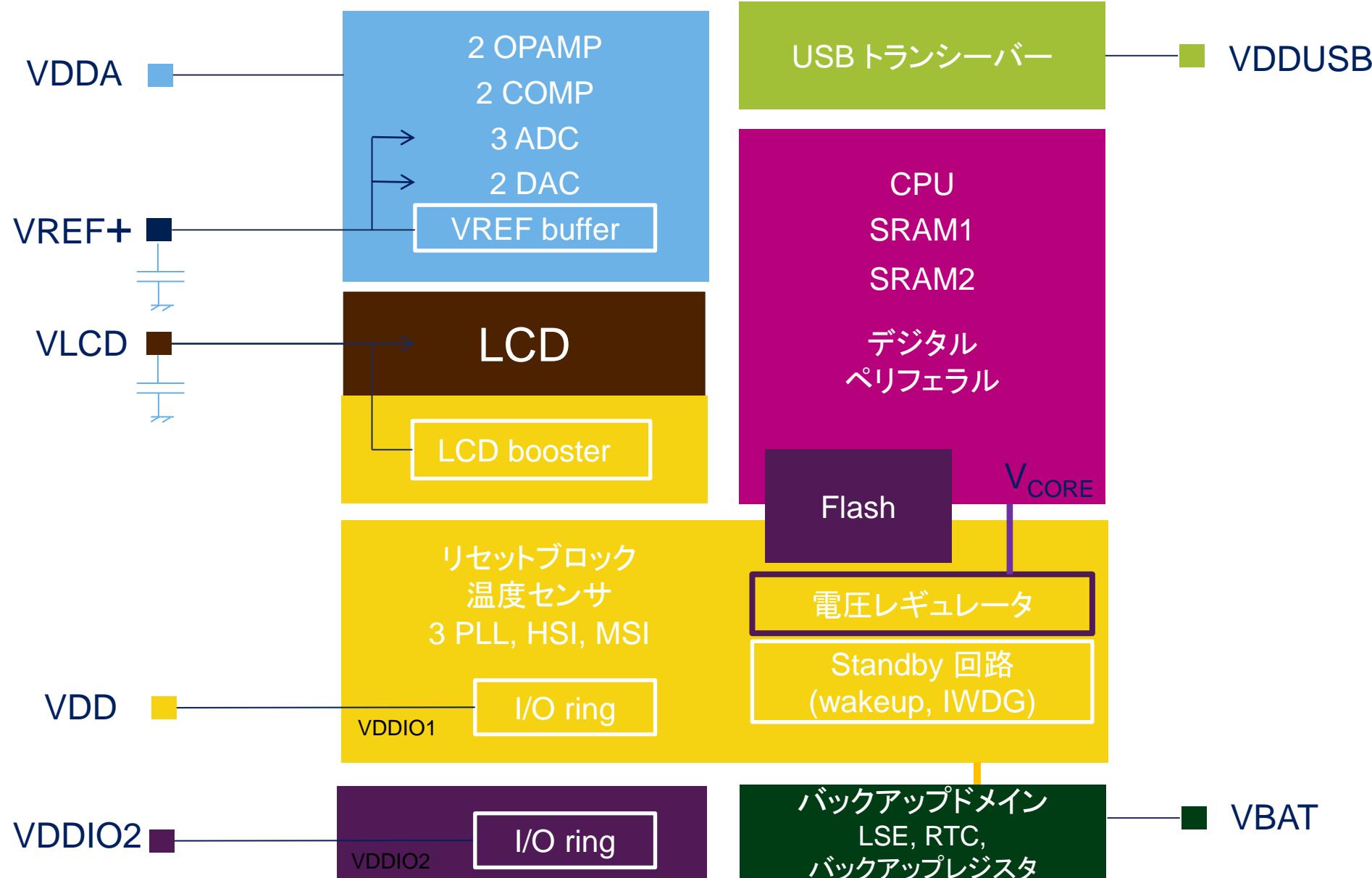

## 独立した電源による最適化された消費電力とパフォーマンス

- $V_{DD}$  は 1.71 から 3.6 V (パワーダウン時は 1.6 V まで下げられる)

- $V_{DDA}$  は 1.62 から 3.6 V

- ADC と COMP 使用時、最小 1.62 V

- DAC と OPAMP 使用時、最小 1.8 V

- VREFBUF を使用時、最小 2.4 V

- USB トランシーバーのための  $V_{DDUSB}$  は 3 から 3.6 V

- 以下の機能用の PG[15:2] のための  $V_{DDIO2}$  は 1.08 から 3.6 V:

- 2 I2C – 2 SPI – 1 SAI – 2 UARTs – 2 Timers

- LQFP144 と BGA132のみ。CSP72 と CSP81 では 6 つの I/O のみ

- $V_{BAT}$  は 1.55 から 3.6 V。これは RTC と 128 バイトのバックアップレジスタを含む

## LCDコントラストとアナログのパフォーマンスのため 独立したリファレンス電源

- LCDのためのリファレンス電源  $V_{LCD}$  は2.5から3.6V:

- これは、独立したVDDの電圧を、外部電源電圧によって、または内蔵された昇圧コンバータのいずれかによって提供することができる。

- VLCDは、LCDを使用しない場合GPIOとして使用することができるPC3と多重化されています。

- ADCとDACのためのリファレンス電源  $V_{REF+}$ :

- これは、外部リファレンス電圧、または内部リファレンス電圧バッファのいずれかを提供することができる。

- $V_{REF+}$ ピン、および内部電圧リファレンスは、64ピンパッケージでは使用できない。このパッケージでは、このピンはVDDAが外部リファレンスと接続している。64ピンでは内部電圧リファレンスバッファが使用できないため、無効にしなければならない。

# ペリフェラル電圧モニター

7

- VDDA, VDDUSB, VDDIO2 のためのペリフェラル電圧モニターは選択された電源がスレッショルドを下回ったときにStopモードからウェイクアップさせる機能をもつ

| PVM  | Power supply | PVM threshold |

|------|--------------|---------------|

| PVM1 | $V_{DDUSB}$  | VPVM1: 1.22 V |

| PVM2 | $V_{DDIO2}$  | VPVM2: 0.96 V |

| PVM3 | $V_{DDA}$    | VPVM3: 1.65 V |

| PVM4 | $V_{DDA}$    | VPVM4: 1.82 V |

- リセット時は、それぞれの独立した電源は、電気的にopenになっていて、ペリフェラルとI/Oは電源が供給されていない。PVMにより電源が供給されているのを確認してから、ソフトウェアによってopenを解除し、ペリフェラルに電源を供給する。

## 安全で超低消費電力なリセット管理

- Brown-out reset は Shutdown モードを除き、常に有効

- MCU は VDD スロープにかかわらず、選択されたしきい値を下回るとすぐにリセットする。

- 5 つのスレッショルドがオプションバイトで選択できる。 **BOR\_LEV[2:0]**,  $V_{BOR0} = 1.7 \text{ V}$  から  $V_{BOR4} = 2.95 \text{ V}$  まで。

- 電源電圧検出器は Standby と Shutdown モードを除き、有効

- 7 つのスレッショルド + 外部ピン。これはソフトウェアで選択可能

- BOR0 の消費電力はデータシートに記載

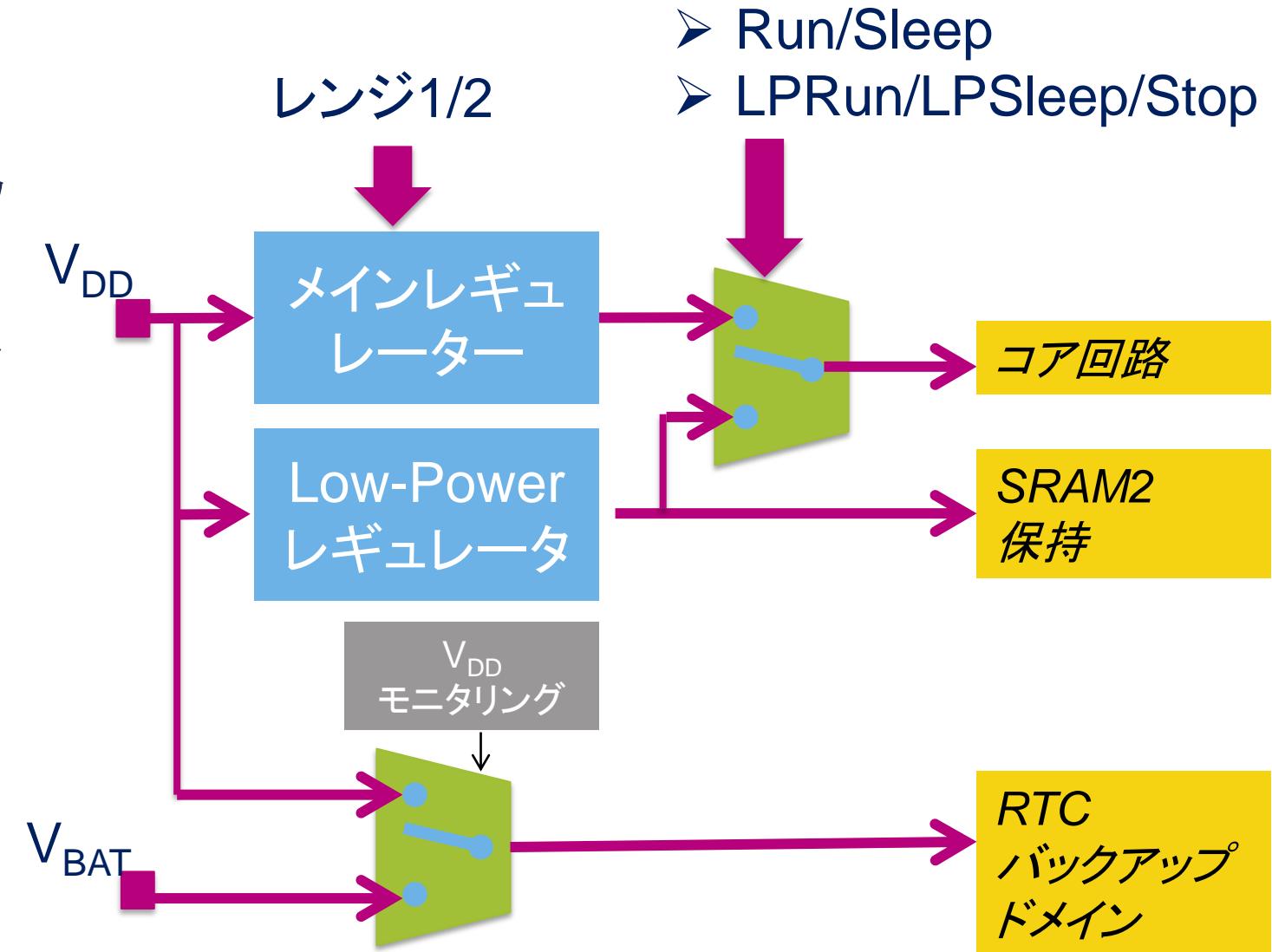

# 電圧レギュレーター

9

- 2つの電圧レギュレーター

- メインレギュレーターはダイナミック電圧スケーリングするための2つの電圧レンジを持つ; それらは RunとSleepモードで使用される

- Low-power レギュレーターは Low-power run, Low-power sleep, Stop 1, Stop 2 モード用で、Standby時のRAMの保持にも使われる

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QUADSPI       |

| BOR           |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPPI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| IWDG          |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

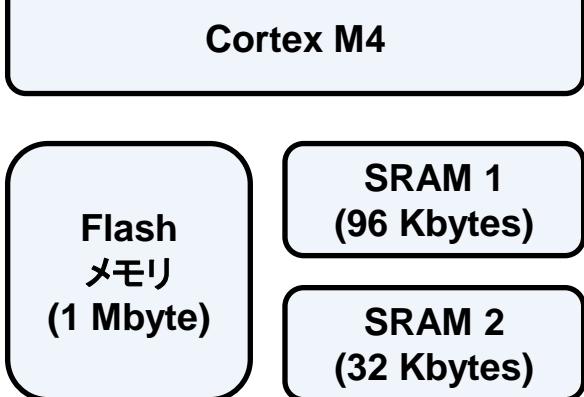

# Run モード: レンジ 1

Ex: Flashメモリからの実行

Cortex M4

Flash

メモリ

(1 Mbyte)

SRAM 1

(96 Kbytes)

SRAM 2

(32 Kbytes)

メインレギュレーター (MR)

レンジ 1 (最大 80 MHZ)

レンジ 2 (最大 26 MHZ)

Low-power

レギュレーター (LPR)

最大 2 MHz

レンジ 1

131  $\mu$ A/MHz @ 80 MHz

(10.5 mA)

レンジ 2

112  $\mu$ A/MHz @ 26 MHz

(2.9 mA)

有効な

クロック

|     |

|-----|

| HSI |

| HSE |

| LSI |

| LSE |

| MSI |

アクティブ

クロックオフ

パワーダウン

有効なクロック

とペリフェラル

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QUADSPI       |

| <b>BOR</b>    |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPPI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| IWDG          |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

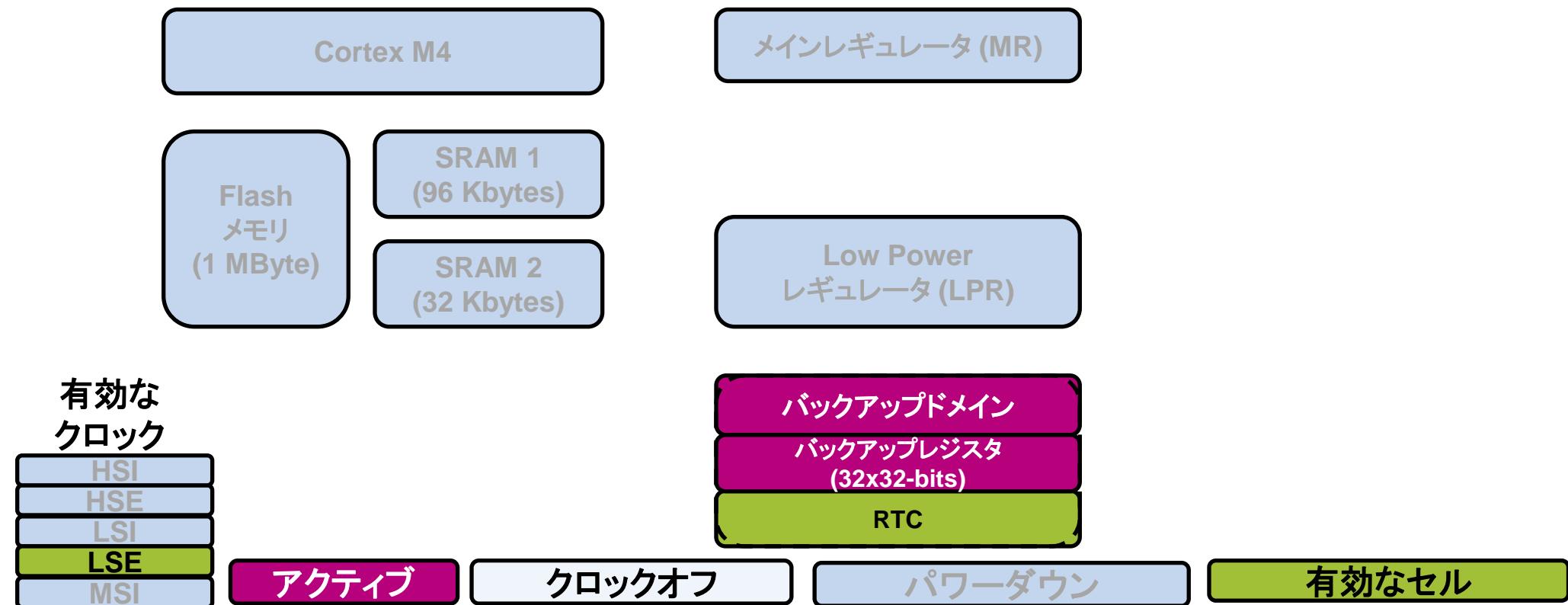

# Run モード: レンジ 2

## Ex: SRAMからの実行

Cortex M4

Flash

メモリ

(1 Mbyte)SRAM 1

(96 Kbytes)SRAM 2

(32 Kbytes)

メインレギュレータ (MR)

レンジ 1 (最大 80 MHz)

レンジ 2 (最大 26 MHz)

Low-power

レギュレータ (LPR)

最大 2 MHz有効な

クロック

HSI

HSE

LSI

LSE

MSI

アクティブ

クロックオフ

パワーダウン

有効なクロック

ペリフェラルレンジ 1 SRAM1 実行

120  $\mu$ A/MHz @ 80 MHz

(9.6 mA)レンジ 2 SRAM1 実行

110  $\mu$ A/MHz @ 26 MHz

(2.6 mA)

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QUADSPI       |

| <b>BOR</b>    |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPPI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| IWDG          |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

# Low-power run モード

## Ex: Flashメモリからの実行

Cortex M4

Flash

メモリ

(1 Mbyte)SRAM 1

(96 Kbytes)SRAM 2

(32 Kbytes)

メインレギュレータ (MR)

レンジ 1 (最大 80 MHZ)

レンジ 2 (最大 26 MHZ)

Low-power

レギュレータ (LPR)

最大 2 MHzFlash実行

135  $\mu$ A/MHz @ 2 MHz

(269  $\mu$ A)SRAM1実行

112  $\mu$ A/MHz @ 2 MHz

(225  $\mu$ A)有効な

クロック

HSI

HSE

LSI

LSE

MSI

アクティブ

クロックオフ

パワーダウン

有効なクロック

とペリフェラル

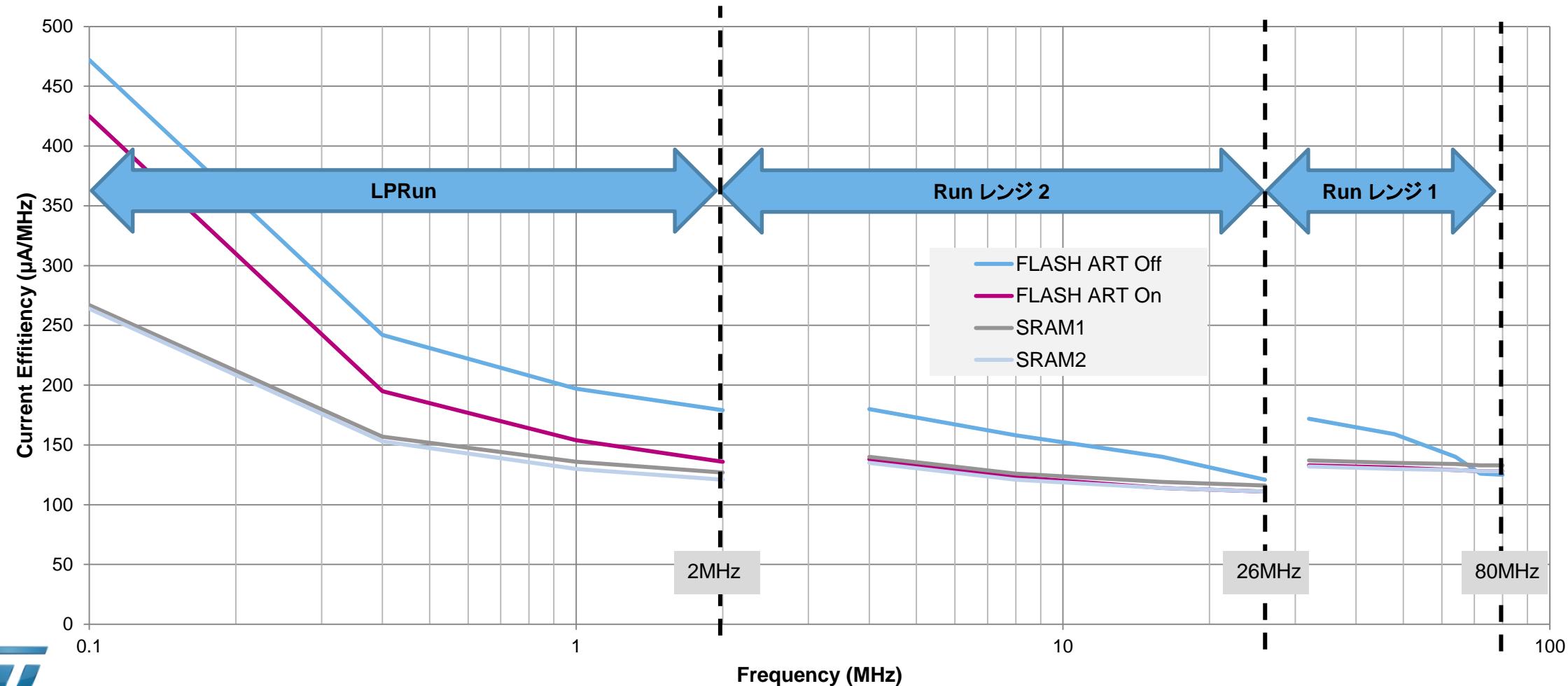

# Run と Low-power run モード

13

要求されるパフォーマンスと消費電力の間での柔軟性

| 電圧レンジ         | SYSCLK   | MSI        | HSI    | HSE           | PLL                       |

|---------------|----------|------------|--------|---------------|---------------------------|

| レンジ 1         | 最大80 MHz | 48 MHz レンジ | 16 MHz | 48 MHz        | 80 MHz<br>最大VCO = 344 MHz |

| レンジ 2         | 最大26 MHz | 24 MHz レンジ | 16 MHz | 26 MHz        | 26 MHz<br>最大VCO = 128 MHz |

| Low-power run | 最大2 MHz  | 2 MHz レンジ  | 許される   | 分周つきで<br>許される | 禁止                        |

# Run と Low-power run モード

14

- それぞれのペリフェラルクロックはON/OFFの設定可能

- リセット後、FLASHクロックを除き、全てのペリフェラルのクロックはOFF

- Runモードのとき、SRAM1とSRAM2のクロックは常にON

- SRAM1、SRAM2から実行している時 (Run または Low-power run):

- Flash はパワーダウンモードにできる

- Flash クロックはOFFにできる

- 割り込みベクタテーブルは必ずSRAMにリマップする！

# RunとLow-power runモード

15

- Run モードでの消費電力はいくつかのパラメータに依存する:

- 実行バイナリコード(プログラム自体+コンパイラの影響)

- メモリ内のプログラムの位置(実行コードのアドレスに依存)

- デバイスのソフトウェア設定(アプリケーション依存)

- I/Oピン負荷およびスイッチング頻度

- 温度

- FlashからかSRAMからの実行

- Flashからの実行時: ART アクセラレータの設定(キャッシュ, プリフェッチ)

=> エネルギー効率は ART ONがいい

- SRAMからの実行時: SRAM1 または SRAM2

=> エネルギー効率はSRAM2がいい

Run の消費電力は低い周波数におとすと最適化できる

Small Flash の動的消費電力: FWが限られたキャッシングを使用する場合に利点

# Sleep と Low-power sleep モード

17

全てのペリフェラルは利用可能そしてwakeup時間は最速

- コアは停止。各ペリフェラルクロックはON/OFFできる。

- **WFI** (Wait For Interrupt) または **WFE** (Wait For Event)の実行によりこのモードになる

- このモードになるのに2つのメカニズムがある:

- **Sleep Now**: MCUは、WFI/WFE命令が実行されると、すぐにSleepモードに入る

- **Sleep on Exit**: 最も低い優先度のISRを出るときに、MCUはすぐにSleepモードに入る

- スタックは、スリープモードに入る前に、ポップされない。それは次の割り込みが発生したときに、実行時間を節約するためにプッシュしないことでつじつまを合わせる。

- 制御はCortex-M4の **System Control Register [SLEEPONEXIT]**で行う

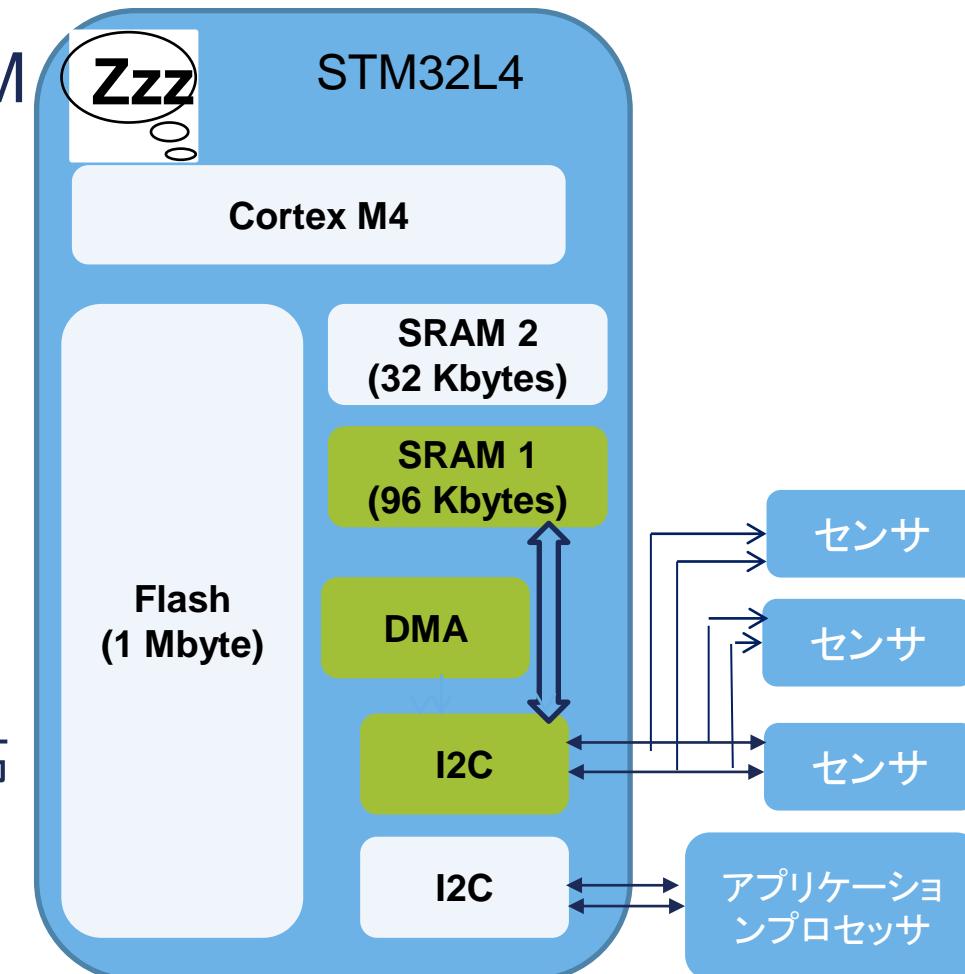

# バッチ アクイジション(取得)モード (BAM)

18

通信するペリフェラルとの間でデータを転送するモードを最適化し、

その間、デバイスをLow-powerモードにする

- 必要なものは、通信ペリフェラル、DMA、SRAMのみ。これらはSleepモードでクロックが有効

- Flashメモリは、パワーダウンモードにされ、Flashクロックは、Sleepモード時にOFF

- Sleep または Low-power sleep モードのどちらかになる

- 注意: I2Cクロックは、Low-power sleepモードで1MHzの高速モードプラスのサポートするため、16MHzを使える。

- U(S)ART/ LPUARTクロックもHSIが使える。

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QUADSPI       |

| <b>BOR</b>    |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPPI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| IWDG          |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

# Sleep モード: レンジ 1

Ex: Flash メモリ ON

Zzz

Cortex M4

Flash

メモリ

(1 Mbyte)

SRAM 1

(96 Kbytes)

SRAM 2

(32 Kbytes)

メインレギュレータ (MR)

レンジ 1 (最大 80 MHz)

レンジ 2 (最大 26 MHz)

Low Power

レギュレータ (LPR)

最大 2 MHz

レンジ 1

37  $\mu$ A/MHz @ 80 MHz

(2.96 mA)

レンジ 2

35  $\mu$ A/MHz @ 26 MHz

(0.92 mA)

有効な

クロック

HSI

HSE

LSI

LSE

MSI

アクティブ

クロックオフ

パワーダウン

有効なクロック

ペリフェラル

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QUADSPI       |

| <b>BOR</b>    |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPPI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| IWDG          |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

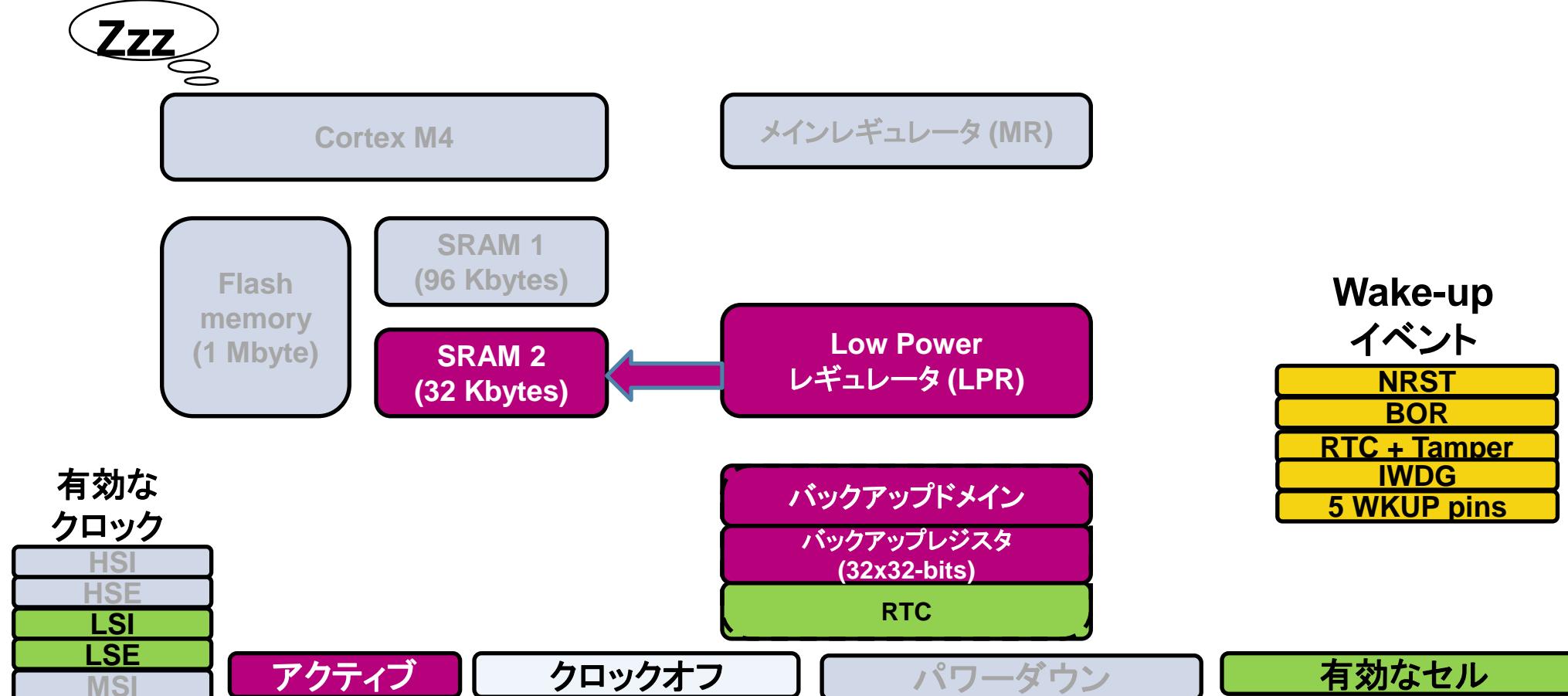

# Low-power sleep モード

Ex: Flash メモリ OFF

Zzz

Cortex M4

Flash

メモリ

(1 Mbyte)

SRAM 1

(96 Kbytes)

SRAM 2

(32 Kbytes)

メインレギュレータ (MR)

レンジ 1 (最大 80 MHz)

レンジ 2 (最大 26 MHz)

Low Power

レギュレータ (LPR)

最大 2 MHz

Flash ON, SRAM OFF

48  $\mu$ A/MHz @ 2 MHz

(96  $\mu$ A)

Flash OFF, SRAM OFF

40.5  $\mu$ A/MHz @ 2 MHz

(81  $\mu$ A)

有効な

クロック

HSI

HSE

LSI

LSE

MSI

アクティブ

クロックオフ

パワーダウン

有効なクロック

ペリフェラル

# Stop 1 と Stop 2 モード

21

全体を保持するモードで最も低消費電力なモード。4  $\mu$ s wakeup @ 48 MHz

- SRAM1, SRAM2 および全てのペリフェラルレジスタは保持される

- 全ての高速クロックは停止する

- LSE (32.768 kHz 外部発信子) and LSI (32 kHz 内部発信子) は有効にできる。

- いくつかのペリフェラルはアクティブにできて、またStopモードからのWakeupも可能

- Wakeup時のシステムクロックは **HSI** または **MSI** で最大48 MHz (4  $\mu$ s wakeup 時間)

Stop 2 の消費電力のほうが低い、Stop 1 は少しサポートしてるペリフェラルが多い

life.augmented

21

## 有効なペリフェラル

|                |

|----------------|

| GPIO           |

| DMA            |

| FSMC           |

| QSPI           |

| <b>BOR</b>     |

| PVD, PVM       |

| LCD            |

| USB OTG        |

| USART          |

| LP UART        |

| I2C 1 / I2C 2  |

| <b>I2C 3</b>   |

| SPI            |

| CAN            |

| SDMMC          |

| SWPMI          |

| SAI            |

| DFSDM          |

| ADC            |

| <b>DAC</b>     |

| OPAMP          |

| <b>COMP</b>    |

| Temp Sensor    |

| Timers         |

| LPTIM 1        |

| <b>LPTIM 2</b> |

| IWDG           |

| WWDG           |

| Systick Timer  |

| Touch Sens     |

| RNG            |

| AES            |

| CRC            |

I/Oはそのまま。かつ設定可能

# Stop 1 モード

22

w/o RTC: 6.6  $\mu$ A @ 3.0 V

w/ RTC: 7.1  $\mu$ A @ 3.0 V

Wakeup 時間 @48 MHz:

SRAM起動: 4  $\mu$ s

Flash起動: 6  $\mu$ s

ZZZ

Cortex M4

メインレギュレータ (MR)

Flash

メモリ

(1 Mbyte)

SRAM 1

(96 Kbytes)

SRAM 2

(32 Kbytes)

Low Power

レギュレータ (LPR)

有効な

クロック

HSI

HSE

LSI

LSE

MSI

アクティブ

クロックオフ

パワーダウン

有効なセル

NRST

BOR

PVD

PVM

RTC + Tamper

LCD

USB OTG

USART

LP UART

I2C 1 / I2C 2

I2C 3

SWPMI

COMP

LPTIM 1

LPTIM 2

IWDG

GPIOs

|                |

|----------------|

| GPIO           |

| DMA            |

| FSMC           |

| QSPI           |

| <b>BOR</b>     |

| PVD, PVM       |

| LCD            |

| USB OTG        |

| USART          |

| LP UART        |

| I2C 1 / I2C 2  |

| <b>I2C 3</b>   |

| SPI            |

| CAN            |

| SDMMC          |

| SWPPI          |

| SAI            |

| DFSDM          |

| ADC            |

| DAC            |

| OPAMP          |

| <b>COMP</b>    |

| Temp Sensor    |

| Timers         |

| <b>LPTIM 1</b> |

| LPTIM 2        |

| <b>IWDG</b>    |

| WWDG           |

| Systick Timer  |

| Touch Sens     |

| RNG            |

| AES            |

| CRC            |

I/Oはそのまま。かつ設定可能

w/o RTC: 1.2  $\mu$ A @ 3.0 V

w/ RTC: 1.7  $\mu$ A @ 3.0 V

ZZZ

有効なクロック

|            |

|------------|

| <b>HSI</b> |

| HSE        |

| <b>LSI</b> |

| <b>LSE</b> |

| MSI        |

アクティブ

クロックオフ

パワーダウン

有効なセル

# Stop 2 モード

Wakeup 時間 @ 48 MHz:

SRAM起動: 5  $\mu$ s

Flash 起動: 8  $\mu$ s

メインレギュレータ (MR)

Low Power

レギュレータ (LPR)

バックアップドメイン

バックアップレジスタ

(32x32-bits)

RTC

Wake-up

イベント

|              |

|--------------|

| NRST         |

| BOR          |

| PVD          |

| PVM          |

| RTC + Tamper |

| LCD          |

|         |

|---------|

| LP UART |

|---------|

|       |

|-------|

| I2C 3 |

|-------|

|         |

|---------|

| COMP    |

| LPTIM 1 |

|       |

|-------|

| IWDG  |

| GPIOs |

# Stop 1 と Stop 2 の比較

24

|                    | Stop 1 モード                                                                                                                                                                                         | Stop 2 モード                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 消費電力               | 25 °C, 3 V<br>6.6 µA w/o RTC                                                                                                                                                                       | 25 °C, 3 V<br>1.2 µA w/o RTC                                                    |

| Wakeup 時間 @ 48 MHz | Flash起動: 6 µs<br>SRAM起動: 4 µs                                                                                                                                                                      | Flash起動: 8 µs<br>SRAM起動: 5 µs                                                   |

| Wakeup クロック        | MSI 最大 48 MHz または HSI @ 16 MHz                                                                                                                                                                     |                                                                                 |

| レギュレータ             | メインレギュレータ (+100 µA, 1 µs wakeup time)<br>または Low power レギュレータ                                                                                                                                      | Low power レギュレータ                                                                |

| Peripherals        | LCD, RTC, I/O, BOR, PVD, PVM, COMP, IWDG<br><br>USB (suspend, 握入検出)<br>2 LP TIMER<br>1 LP UART (スタート、アドレスマッチ、バイト受信)<br>5 UARTx (スタート、アドレスマッチ、バイト受信)<br>3 I2C (アドレスマッチ)<br>SWPMI (suspendからのresume) | 1 LP TIMER (LPTIM1)<br>1 LP UART (スタート、アドレスマッチ、バイト受信)<br>1 I2C (I2C3) (アドレスマッチ) |

## 最小の電力モード。SRAM2の保持とVBATへのスイッチとI/O制御

- デフォルト: SRAMやレジスタの保持は無し(パワーダウンでの電圧レギュレータ)。128バイトのバッカアップレジスタは常に保持。

- 32 KのSRAM2は保持可能

- 超低消費電力 BOR は常に ON: VDDスロープにかかわらず安全なリセット

- pull-up または pull-down または無しをそれぞれの I/O に設定可能

PWR\_CR3レジスタにAPCがセットされているとき、PWR\_PUCRx / PWR\_PDCRx registers (x = A,B,...H)が適応

=>外部コンポーネント入力状態を制御することができる

- 5つのwakeupピン: それぞれの5つのwakeupピンについて極性を設定可能

- Wakeup クロックは MSI で1 から 8 MHzで設定可能

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QSPI          |

| <b>BOR</b>    |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPMI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| <b>IWDG</b>   |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

I/Oは設定可能

pull-upありなし

pull-downありなし

# Standby モード SRAM2保持

RTCなし: 390 nA @ 3.0 V

RTCあり: 890 nA @ 3.0 V

Wakeup 時間 @ 8 MHz:

Flash 起動: 14  $\mu$ s

ZZZ

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QSPI          |

| <b>BOR</b>    |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPPI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| <b>IWDG</b>   |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

I/Oは設定可能

pull-upありなし

pull-downありなし

# Standby モード

27

RTCなし: 150 nA @ 3.0 V

RTCあり: 650 nA @ 3.0 V

Wakeup 時間 @ 8 MHz:

Flash 起動: 14  $\mu$ s

Zzz

Cortex M4

メインレギュレータ (MR)

Flash

メモリ

(1 Mbyte)

SRAM 1

(96 Kbytes)

SRAM 2

(32 Kbytes)

Low Power

レギュレータ (LPR)

有効な

クロック

HSI

HSE

LSI

LSE

MSI

アクティブ

クロックオフ

パワーダウン

有効なセル

Wake-up

イベント

|              |

|--------------|

| NRST         |

| BOR          |

| RTC + Tamper |

| IWDG         |

| 5 WKUP pins  |

バックアップドメイン

バックアップレジスタ

(32x32-bits)

RTC

## 最小のパワーモード: 30 nA !!

- Standby に似ているが

- NO パワーモニタリング: BOR無し, VBATへのスイッチ無し

- NO LSI, IWDG無し

- BOR reset がShutdownモードから抜けるときに発生

- ⇒ バックアップドメインを除く全てのレジスタがリセット

- ⇒ PADにリセット信号生成

- 128バイトの バックアップレジスタ

- Wakeup ソース: 5つの **wakeup** ピン, RTC

- Wakeup クロックは MSI 4 MHz.

# Shutdown モード

29

## 有効な ペリフェラル

|               |                             |

|---------------|-----------------------------|

| GPIO          | I/Oは設定可能                    |

| DMA           | pull-upありなし                 |

| FSMC          | pull-downありなし               |

| QSPI          | しかしShutdownから抜けたときはFloating |

| BOR           |                             |

| PVD, PVM      |                             |

| LCD           |                             |

| USB OTG       |                             |

| USART         |                             |

| LP UART       |                             |

| I2C 1 / I2C 2 |                             |

| I2C 3         |                             |

| SPI           |                             |

| CAN           |                             |

| SDMMC         |                             |

| SWPPI         |                             |

| SAI           |                             |

| DFSDM         |                             |

| ADC           |                             |

| DAC           |                             |

| OPAMP         |                             |

| COMP          |                             |

| Temp Sensor   |                             |

| Timers        |                             |

| LPTIM 1       |                             |

| LPTIM 2       |                             |

| IWDG          |                             |

| WWDG          |                             |

| Systick Timer |                             |

| Touch Sens    |                             |

| RNG           |                             |

| AES           |                             |

| CRC           |                             |

ZZZ

RTC無し: 60 nA @ 3.0 V

RTCあり: 550 nA @ 3.0 V

Wakeup 時間 @ 4 MHz:

Flash 起動: 250 μs

Cortex M4

メインレギュレータ (MR)

Flash

メモリ

(1 Mbyte)

SRAM 1

(96 Kbytes)

SRAM 2

(32 Kbytes)

Low Power

レギュレータ (LPR)

Wake-up

イベント

NRST

RTC + Tamper

5 WKUP pins

有効な

クロック

HSI

HSE

LSI

LSE

MSI

アクティブ

クロックオフ

パワーダウン

有効なセル

バックアップドメイン

バックアップレジスタ

(32x32-bits)

RTC

# 低消費電力モード一覧

30

| モード      | レギュレータ         | CPU  | Flash             | SRAM              | クロック         | ペリフェラル                                                                                                        | 消費電力<br>@ 1.8V                         | Wakeup 時間                            |

|----------|----------------|------|-------------------|-------------------|--------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------|

| Run      | R1             | Yes  | ON <sup>(1)</sup> | ON                | 何でも          | すべて                                                                                                           | 127 $\mu$ A/MHz                        | N/A                                  |

|          | R2             |      |                   |                   |              | OTG, RNG以外                                                                                                    | 111 $\mu$ A/MHz                        |                                      |

| LPRun    | LPR            | Yes  | ON <sup>(1)</sup> | ON                | PLL以外<br>何でも | OTG, RNG以外                                                                                                    | 136 $\mu$ A/MHz                        |                                      |

| Sleep    | R1             | No   | ON <sup>(1)</sup> | ON <sup>(2)</sup> | 何でも          | すべて<br>全てのIT または event                                                                                        | 37 $\mu$ A/MHz                         | 6 サイクル                               |

|          | R2             |      |                   |                   |              |                                                                                                               | 35 $\mu$ A/MHz                         |                                      |

| LPSleep  | LPR            | No   | ON <sup>(1)</sup> | ON <sup>(2)</sup> | PLL以外<br>何でも | OTG, RNG以外<br>全てのIT または event                                                                                 | 40 $\mu$ A/MHz                         | 6 サイクル                               |

| Stop 1   | LPR<br>(or MR) | No   | OFF               | ON                | LSE/LSI      | Reset ピン, 全てのI/O<br>BOR,PVD,PVM,RTC,LCD,IWDG,<br>COMPx,DACx,OPAMPx,USARTx,<br>LPUART,I2Cx,LPTIMx,OTG_FS,SWPMI | 6.6 $\mu$ A RTCなし<br>6.9 $\mu$ A RTCあり | 4 $\mu$ A RAM<br>6 $\mu$ A Flash メモリ |

| Stop 2   | LPR            | No   | OFF               | ON                | LSE/LSI      | Reset ピン, 全てのI/O<br>BOR,PVD,PVM,RTC,LCD,IWDG,<br>COMPx,LPUART,I2C3,LPTIM1                                     | 1.1 $\mu$ A RTCなし<br>1.4 $\mu$ A RTCあり | 5 $\mu$ A RAM<br>7 $\mu$ A Flash メモリ |

| Standby  | LPR            | DOWN | OFF               | SRAM2 ON          | LSE/LSI      | Reset ピン, 5つのWKUPx ピン<br>BOR, RTC, IWDG                                                                       | + 235 nA                               | 14 $\mu$ s                           |

|          | OFF            |      |                   | DOWN              |              |                                                                                                               | 115 nA RTCなし<br>415 nA RTCあり           |                                      |

| Shutdown | OFF            | DOWN | OFF               | DOWN              | LSE          | Reset ピン, 5つのWKUPx ピン<br>RTC                                                                                  | 30 nA RTCなし<br>330 nA RTCあり            | 250 $\mu$ s                          |

- パワーダウン、クロックOFF可能

- SRAM1 と SRAM2 それぞれクロックOFF可能

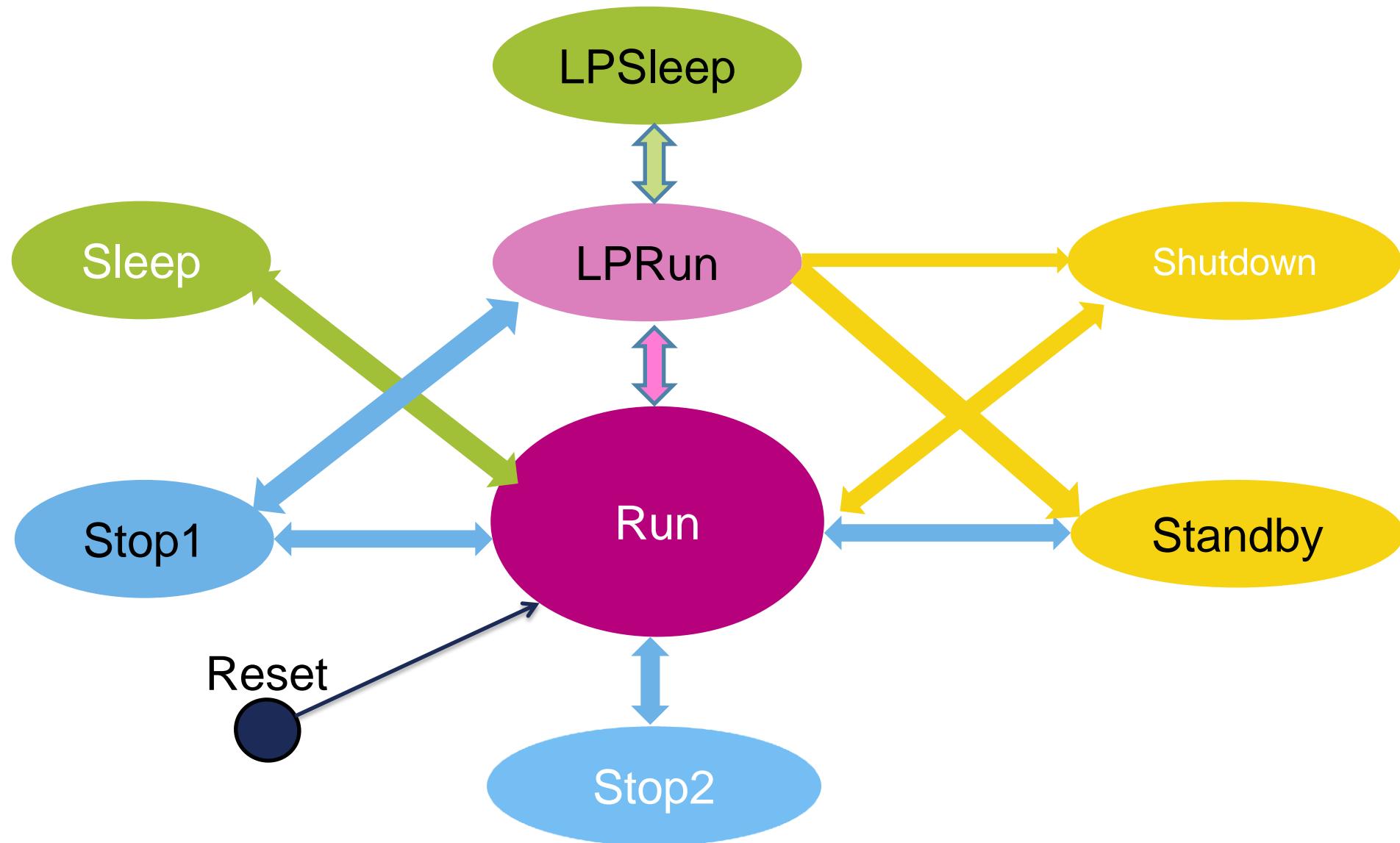

# Low-power モード遷移図

31

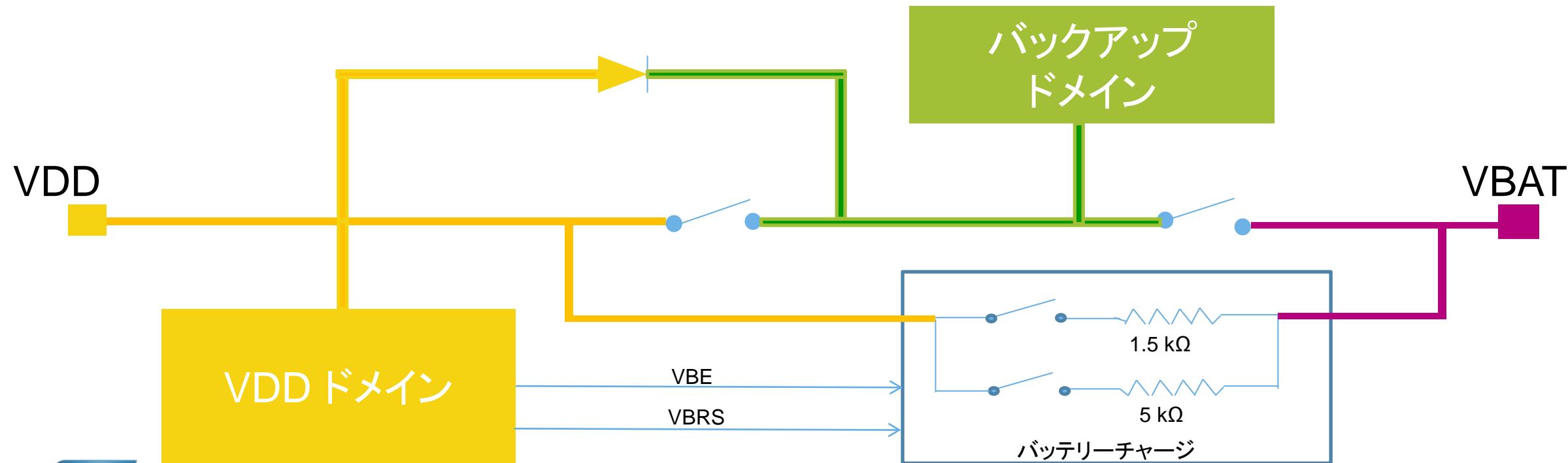

VDDの損失の場合に、RTCは継続して実行しバックアップレジスタは保存

- バックアップドメインは以下を含む:

- LSE 32.768 kHz でクロックされるRTC、3つの **tamper** ピンを含む

- 128 バイトのバックアップレジスタ

- RCC\_BDCR レジスタ

- VDDがパワーダウンまたはパワーオンしたときに、自動的にVBATとVDDを内部でスイッチする

- 電圧モニタリング(VBAT/3)のための、ADCへの内部接続

- VBAT 充電機能

# VBAT バックアップドメイン

33

- VBAT 充電機能: VDDが存在する場合に、内部抵抗を介してVBATのスーパー キャパシタンスを充電することができる

|               |

|---------------|

| GPIO          |

| DMA           |

| FSMC          |

| QSPI          |

| BOR           |

| PVD, PVM      |

| LCD           |

| USB OTG       |

| USART         |

| LP UART       |

| I2C 1 / I2C 2 |

| I2C 3         |

| SPI           |

| CAN           |

| SDMMC         |

| SWPPI         |

| SAI           |

| DFSDM         |

| ADC           |

| DAC           |

| OPAMP         |

| COMP          |

| Temp Sensor   |

| Timers        |

| LPTIM 1       |

| LPTIM 2       |

| IWDG          |

| WWDG          |

| Systick Timer |

| Touch Sens    |

| RNG           |

| AES           |

| CRC           |

# VBAT モード

RTC無し: 6.2 nA @ 3.0 V

RTCあり: 494 nA @ 3.0 V

- フラッシュオプションバイトの3つのオプションビットでは、low powerモードの禁止を設定することができる:

- nRST\_SHDWN: クリアのとき、シャットダウンモードに入ると、リセットが生成される

- nRST\_STDBY: クリアのとき、スタンバイモードに入ると、リセットが生成される

- nRST\_STOP: クリアのとき、ストップ1またはストップ2モードに入ると、リセットが生成される

- DBGMCU\_CR レジスタの3ビットの設定で Sleep, Stop, Standby, Shutdown モード中のデバッグが可能になる:

- DBG\_STANDBY:セットのとき、デジタル部は、スタンバイおよびシャットダウンモードでは電源 OFFにならず、HCLKとFCLKは内部RCが提供してオンのまま。また、スタンバイ/シャットダウン時にMCUはシステムリセットされている。

- DBG\_STOP:セットのとき、Stop 1とStop 2のモードでHCLKとFCLKは内部RCが提供してオンのまま。

- DBG\_SLEEP:セットのとき、SleepとLow power sleepモードでHCLKとFCLKはオンのまま。

- これらのビットが設定されると、デバッガとの接続は、低電力モード中でも維持される。ウェイクアップ後、デバッグは可能。

- 電力モードとその依存関係の詳細については、ペリフェラルのトレーニングの次のリストを参照のこと：

- Reset and clock control (RCC)

- Interrupts (NVIC-EXTI)

- Digital-to-analog converter (DAC)

- Comparator (COMP)

- Liquid crystal display controller (LCD)

- Low-power timer (LPTIM)

- Independent watchdog (IWDG)

- Real-time clock (RTC)

- Inter-integrated circuit (I2C) interface

- Universal synchronous asynchronous receiver transmitter (USART)

- Low-power universal asynchronous receiver transmitter (LPUART)

- Single Wire Protocol Master Interface (SWPPI)

- USB On-The-Go Full-Speed (OTG\_FS)

- 詳細については、以下を参照のこと。

- AN4621: STM32L4xx ultra-low-power features overview