# STM32L4 – LPUART

低電力ユニバーサル非同期レシーバ・トランスマッタ

Low Power Universal Asynchronous Receiver /Transmitter

Revision 1

Jan - 2016

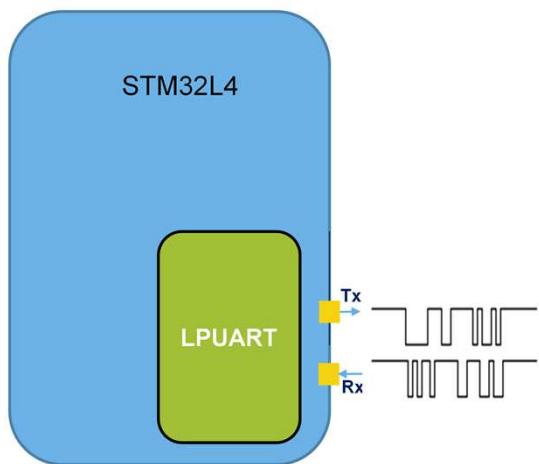

こんにちは。こちらでは、低電力ユニバーサル非同期レシーバ・トランスマッタ(LPUART)をご紹介します。

- **LPUART (Low Power Universal Asynchronous Receiver /Transmitter)**

- ストップモード機能からのウェイクアップ、32.768 kHzの低速外部発振器(LSE)を用いて9600ボーレートフルUART通信。

- より高いボーレートは、他のクロック・ソースで使用可能。

### Application の利点

- デバイス間の安価な通信リンク

- HWはシンプル。いくつかのピンのみ必要

- low-power stop モードから起動可能

**Low Power Universal Synchronous Asynchronous Receiver (LPUART、発音は“L” “P” “U”-“Art”)** は9600bpsでのUART(発音は“U”-“Art”)通信機能で、LPUARTが32.768kHzのLSEでクロックされているときに動作する。より高いボーレートを使用するときはLSE以外のクロックソースを使用する。アプリケーションは、ごく少数のピンを必要とし、デバイス間の簡単で安価な接続の利点がある。また、LPUARTペリフェラルはLow-powerモードで機能します。

## 主な機能

3

- 完全にプログラム可能なシリアル・インターフェース

- データは 7、8、9bit

- パリティは Even、odd、no-parity

- 1、2 ストップビット

- プログラマブルなデータ並び MSB、LSB first

- 送信も受信もプログラマブルな信号極性

- プログラマブルなボーレート生成

- RS-232 と RS-485 hardware flow 制御をサポート

LPUARTは、データ長、自動的に生成され、チェックされているパリティ、ストップビット数、データの順序、送信と受信のための信号極性、およびボーレートジェネレータとして設定可能な機能と完全にプログラム可能なシリアルインタフェースである。

これは、RS-232とRS-485ハードウェアフロー制御オプションをサポートしている。

## 主な機能 (続き) ■ 4

- デュアルなクロックドメイン:

- ストップ・モードからウェイクアップするため

- ボーレートのプログラミングがPCLKに依存しないため

- マルチプロセッサ通信

- シングルワイヤの半二重通信

LPUARTは、Stopモードからウェイクアップを可能にするため、

とペリフェラルクロックから独立したボーレートプログラミング

のための、デュアルクロックドメインをサポートしている。

マルチプロセッサモードでは、アドレス指定されていない時に

USARTがアイドル状態のままにできる。

全二重通信に加えて、それは、シングルワイヤでの半二重

モードをサポートする。

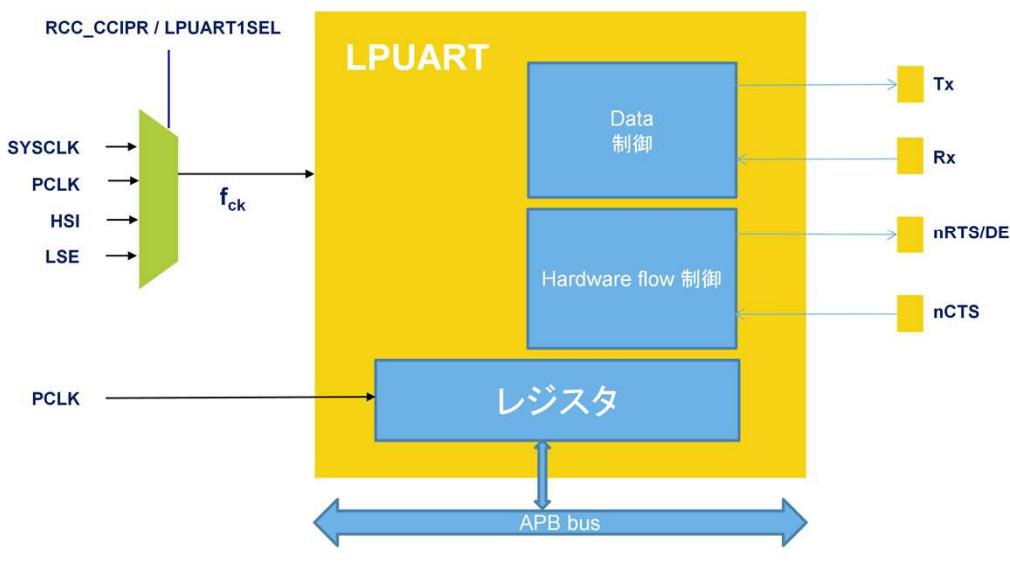

## ブロック図

5

これはLPUARTブロック図。LPUARTクロック(FCK)がいくつ

かのクロックの中から選択することができ、システムクロック、

APBクロック、高速内蔵16 MHzのRCオシレータ(HSI)また

は低速外部32.768kHz水晶発振器(LSE)。

TxとRxは、データの送受信のために使用される。

nCTSとnRTSは、RS-232ハードウェアフロー制御のために

使用される。

nRTSと同じI/Oで提供されているドライババイナブル(DE)

信号は、RS-485モードで使用される。

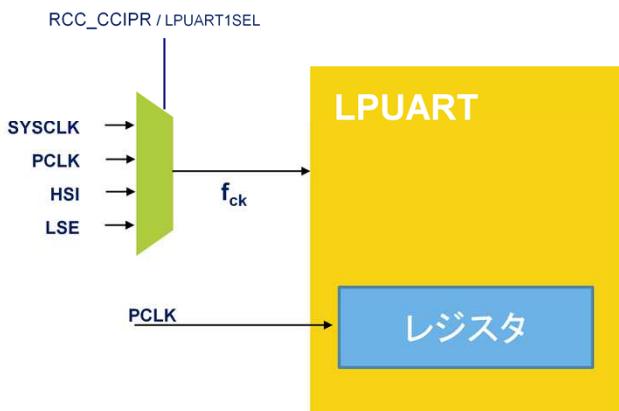

# デュアルクロックドメイン

6

## PCLKの再プログラミングから独立したボーレートのプログラミング

- 選択可能なクロック・ソースを介する、フレキシブルなクロッキング方式

- PCLK (デフォルト)

- HSI クロック

- LSE クロック

- システムクロック (SYSCLK)

- 最大ボーレートは:

- 9600 baud (fck が LSE 32.768 KHz)

- 26 Mbaud (fck が 80MHz)

LPUARTは、柔軟なクロッキング方式を持つ。そのクロックソースは、RCCで選択することができ、デフォルトのクロックソースであるPCLK、またはHSI、LSEまたはシステムクロックのいずれかである。

レジスタは、APBバスを介してアクセスされ、モジュールはAPBクロックから独立しているFCKでクロックされる。

クロックソースがLSEのとき、最大ボーレートは9600ボーです。

クロックソースが80 MHzであるとき、26メガボー(発音は「ボー」、「メガ」)です。

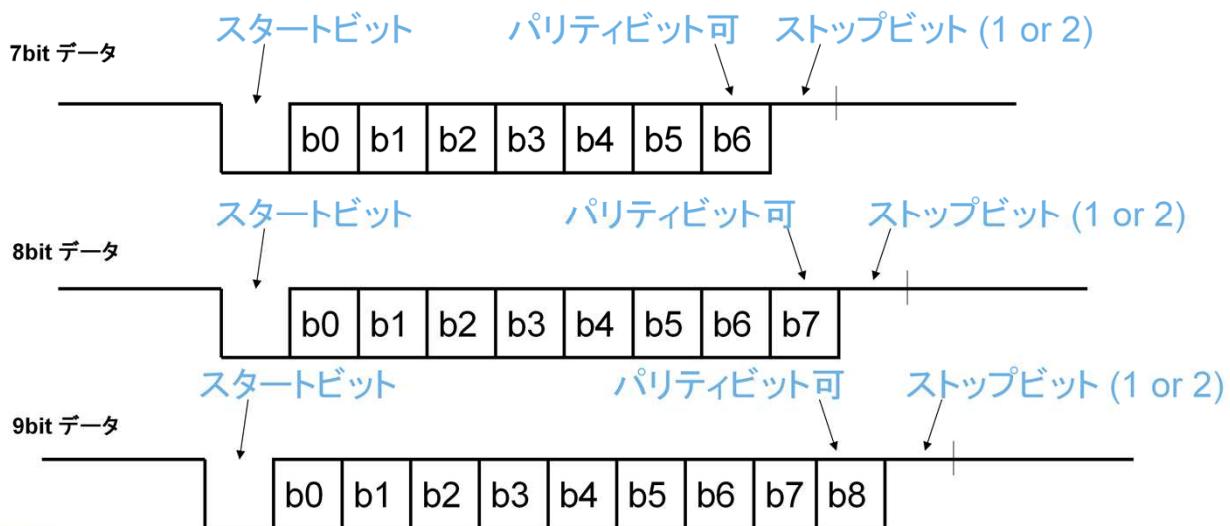

# データ・フォーマット

7

サポートしているデータ長: 7、8、9bit

フレームフォーマットは、同期および必要に応じてエラーチェック用のパリティビットのためのビットに加えて、データビットのセットで構成される。フレームは、ラインが1ビット周期にローに駆動される、1スタートビット(S)、で始まる。これは、フレームの開始を通知し、同期のために使用される。パリティ・ビットも数えて、データ長が9、8、7ビットであることができる。最後に、1または2ストップビットは、これはラインがハイに駆動される、フレームの終了を示す。

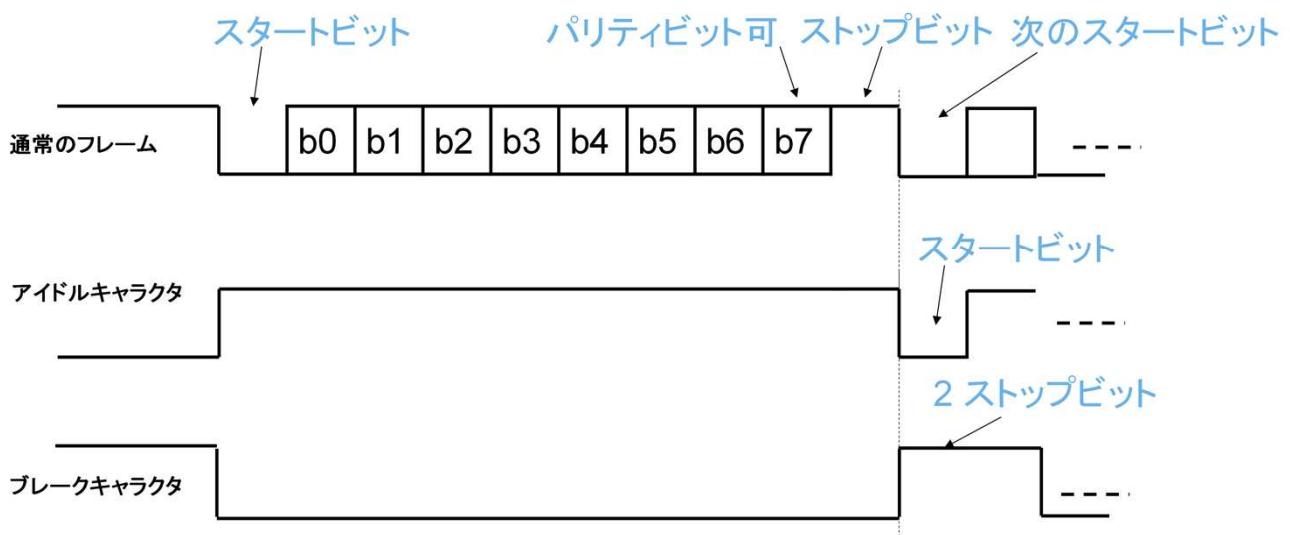

## アイドル / ブレークキャラクタ

8

前のスライドは、標準的なフレームを説明した。このスライドは、1ストップビットで構成された8ビットのデータフレームの一例を示す図である。

アイドルキャラクタは「1」の列がフレーム全体として解釈される。「1」の数は、同様に、ストップビットの数を含む。

ブレークキャラクタは、フレーム期間のすべてが「0」を受信したと解釈される。ブレークフレームの終了時に、2ストップビットが挿入される。

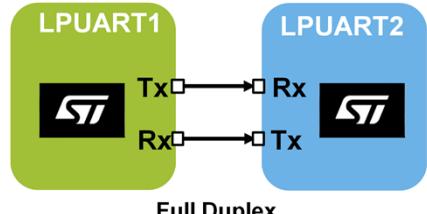

# 全二重/半二重モード

9

全二重: 2 ワイヤ

半二重: 1 ワイヤ

- LPUART 全二重通信:

- TxとRxラインは、それぞれ他のインターフェースのRxおよびTxラインに接続されている。

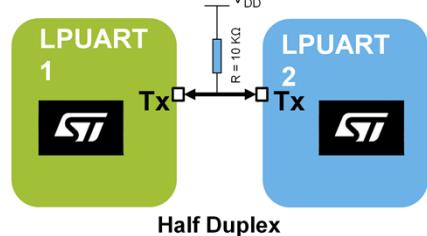

- LPUART 半二重通信:

- TxとRxラインは内部で接続されている。

- Txピンは送信と受信の両方に使用される。

LPUARTはTxとRxラインがそれぞれ他のインターフェースのRxおよびTxラインに接続されている全二重通信をサポートしています。

LPUARTはまたTxとRxラインが内部で接続されている単線半二重プロトコル用に設定することができる。この通信モードでは、TXピンだけが送信と受信の両方のために使用される。何もデータが送信されないときのTxピンが常にリリースされる。このように、アイドル状態または受信状態での標準I/Oとして機能する。この使用方法については、I/Oが、外部プルアップ抵抗を持つオルタネート機能オープンドレインモードでのTxピンで設定する必要がある。

# RS-232 ハードウェアフロー制御

10

## データアンダーラン/オーバーランを避けるためのハードウェアハンドシェイク

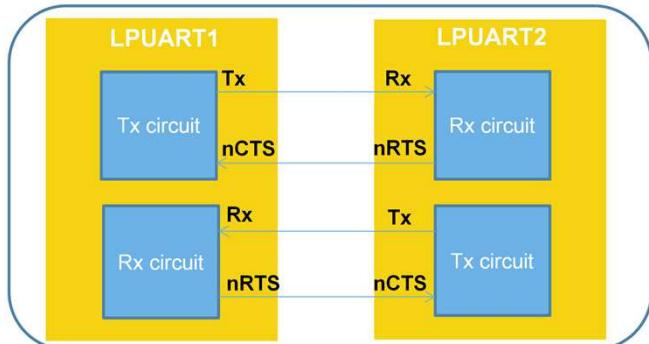

- RS-232 ハードウェアフロー制御

- nRTS (Request to Send) 出力は受信がデータを受け取るのにREADYな場合アサートされる

- nCTS (Clear to Send) 入力は転送が引き続き通信可能なときにアサートされる

- 半二重システムに特に有用

RS-232規格では、nCTS入力とnRTS出力を使用して、2つのデバイス間のシリアルデータのフローを制御することが可能。この2ラインは、受信機と送信機は、それらのお互いの状態を警告することができる。このスライドは、このモードでは、二つのデバイスを接続する方法を示している。このアイデアは、半二重通信の場合にバイト落ちまたは衝突を防止する。両方の信号はアクティブ・ローである。

# RS-485 ハードウェアフロー制御

11

## ハードウェアハンドシェイク

- マスターがトランシーバ(物理層(PHY))を制御するための方向信号を生成する必要がある、半二重システムで有用。この信号は、送信か受信モードとして動作しなければならない場合に、物理層に通知する。

- それは外部のRS-485バスドライバーを活性化するために、DE(ドライバインペーブル)ピンを使用している。

- DEとnRTS信号は同じピン。

RS-485のようなシリアル半二重通信プロトコルは、マスターは、トランシーバ(物理層)を制御するための方向信号を生成する必要があります。この信号は、送信か受信モードとして動作しなければならない場合に、物理層に通知します。

RS-485モードでは、制御ライン「ドライバインペーブル」は外部トランシーバ制御を活性化するために使用される。DEとnRTSでピンを共有している。

# マルチプロセッサ通信

12

## いくつかのデバイスの間での通信

- マルチプロセッサ通信では、意図されたメッセージの唯一の受信者は、積極的にメッセージを受信することが望ましい

- アドレス指定されないデバイスはミュートモードにことができる

- ミュートモードは2つのメソッドで制御できる:

- アイドルライン検知

- アドレスマーク検知

複数のプロセッサ間の通信を簡素化するために、LPUARTは、特別なマルチプロセッサモードをサポートしている。マルチプロセッサ通信では、意図されたメッセージの唯一の受信者は、積極的にメッセージを受信することが望ましい。アイドルラインまたはアドレスマーク:アドレス指定されないデバイスは、2つの方法を使用してミュート・モードに入れることができる。

LPUARTはミュートモードに入る、から出るに、2つの方法のいずれかを使用することができる。

- アイドルライン検出

- アドレスマーク検出

## STOPモードからのwakeup

13

- LPUARTは、LPUARTクロックが以下の場合、StopモードからMCUをwakeupすることが可能:

- HSI or

- LSE

- wakeup ソースは:

- 通常の RXNE 割込みまたは

- 特定のwakeup イベント:

- スタートビット

- アドレスマッチ

- 受信データ

LPUARTは、LPUARTクロックがHSIまたはLSEの場合、StopモードからMCUをwakeupすることが可能。

ウェイクアップのソースは、標準RXNE割込み、または特定のイベントの、スタートビット検出、アドレス一致、任意のデータを受信する、です。

| 割込みイベント                         | 説明                                |

|---------------------------------|-----------------------------------|

| Transmit Data register empty    | 送信データレジスタが空のときセット                 |

| Transmit complete               | データ送信が終了し、データレジスタもシフトレジスタも空のときセット |

| CTS                             | nCTS入力がトグルしたときセット                 |

| Receive data register Not Empty | 受信データレジスタにデータがあるときセット             |

| Idle line                       | アイドルライン検知のときセット                   |

| Character match                 | 受信データが対応するアドレスのときセット              |

| Wakeup from stop mode           | Stopモードからwakeupしたときセット            |

## いくつかの LPUART イベントは割込みを起こす

送信データレジスタが空で書かれる準備ができるとき、送信データレジスタエンプティフラグがセットされる。

データ送信が完了し、データレジスタとシフトレジスタの両方が空のときに送信完了フラグがセットされる。

nCTS入力がトグルされるときにCTSフラグがセットされる。

受信データレジスタに読み込み可能な状態のデータが含まれている場合に受信データレジスタが空ではないフラグがセットされる。

アイドルラインが検出されたときにアイドルラインフラグがセットされる。

受信したデータがプログラムされたアドレスに対応するときにキャラクタマッチフラグがセットされる。

ウェイクアップイベント(スタートビットやアドレス一致または任意のデータを受信)が確認されたときストップモードからのウェイクアップフラグがセットされる。

## エラー割込みおよび DMA

15

| 割込みイベント       | 説明                        |

|---------------|---------------------------|

| Overrun error | オーバーランエラーのときセット           |

| Parity error  | パリティエラーのときセット             |

| Framing error | 同期はずれ、過剰なノイズのときセット        |

| Noise error   | フレームのスタートビット受信時にノイズ検知でセット |

- DMA リクエストは送信データレジスタエンプティと受信データレジスタフルで発生する

表のように、いくつかのエラーフラグはまたLPUARTによって生成される。

オーバーラン、パリティ、フレーミングエラーはそれぞれのエラーが発生したのに対応してエラーフラグがセットされる。ノイズエラーは受信フレームのスタートビットでノイズを見つけたときに発生する。

DMA リクエストは送信データレジスタエンプティと受信データレジスタフルで発生する

# Low-power モード

16

| モード             | 説明                                                                                                                                            |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Run             | アクティブ                                                                                                                                         |

| Sleep           | アクティブ。ペリフェラル割込みはデバイスがsleepモードから抜けたときに発生                                                                                                       |

| Low-power run   | アクティブ                                                                                                                                         |

| Low-power sleep | アクティブ。ペリフェラル割込みはデバイスがlow-power sleepモードから抜けたときに発生                                                                                             |

| Stop 1          | LPUARTは、LPUARTクロックがHSI16またはLSEに設定されている場合、Stop 1またはStop 2からMCUを起動することができる。Stop 1およびStop 2モードからMCUのウェイクアップは、標準RXNE割込みやWUFイベントのいずれかを使用して行うことができる |

| Stop 2          |                                                                                                                                               |

| Standby         | パワーダウン。ペリフェラルはStandbyモード復帰後、再初期化が必要                                                                                                           |

| Shutdown        | パワーダウン。ペリフェラルはShutdownモード復帰後、再初期化が必要                                                                                                          |

LPUARTペリフェラルはRun、Low-power run、sleep、Low-power sleepでアクティブ。LPUART割込みは、デバイスがSleepまたはLow-power sleepモードを終了する、原因となる。LPUARTは、LPUARTクロックがHSI16またはLSEに設定されている場合、Stop 1とStop 2からMCUを起動することができる。Stop 1およびStop 2モードからMCUのウェイクアップは、標準RXNE割込みやWUFイベントのいずれかを使用して行うことができる。

StandbyとShutdownモードでは、ペリフェラルはパワーダウンになり、それらのモードを抜けた後、初期化をしなければならない

# STM32L4 LPUART 機能一覧

17

| U(S)ART/LPUART 機能             | USART | LPUART |

|-------------------------------|-------|--------|

| モデムのためのハードウェアフロー制御            | X     | X      |

| マルチプロセッサ通信                    | X     | X      |

| 同期モード                         | X     | -      |

| スマートカードモード                    | X     | -      |

| 単線半二重通信                       | X     | X      |

| IrDA SIR ENDEC                | X     | -      |

| LINモード                        | X     | -      |

| 2つのクロックドメインとstopモードからの wakeup | X     | X      |

| 受信タイムアウト                      | X     | -      |

| Modbus 通信                     | X     | -      |

| オートボーレート検出                    | X     | -      |

| Driver enable                 | X     | X      |

STM32L4デバイスは1つのLPUARTを内蔵している。

USART (発音は “U”-“Sart”)と比べて、LPUART は同期をサポートしない、スマートカードをサポートしない、IrDAとLINをサポートしない。さらに、受信タイムアウト、modbus、オートボーレート検出もサポートしない。

## 関連ペリフェラル

18

- LPUARTに関する以下のペリフェラル・トレーニングを参照してください。

- GPIO (alternate function configurations)

- Reset and Clock Controller (RCC)

- Power controller (PWR)

- Interrupts (NVIC and EXTI)

- Direct memory access controller (DMA)

これはLPUARTに関するペリフェラルのリスト。必要な場合、これらのペリフェラルのトレーニングを参照のこと。

- General-purpose input/output

- Reset and clock controller

- Power controller

- Interrupts controller

- Direct memory access controller