Hello, and welcome to this overview of the hardware architecture of the STM32MP1 series.

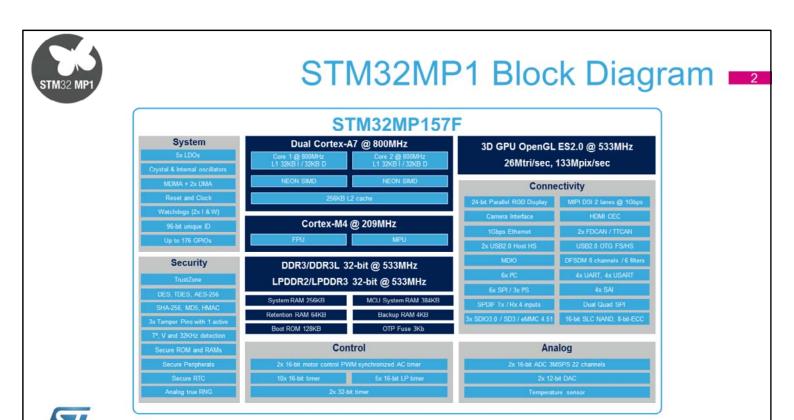

This block diagram summarizes the key features of the STM32MP157F which is part of the high-end line of the STM32MP1 Series.

The STM32MP157F microprocessor integrates Dual Cortex®-A7 32-bit core with single- and double-precision floating point units, plus the Arm® NEON™ Advanced SIMD instruction set and can run up to 800MHz. Each core has a 32 Kbytes level 1 Instruction Cache and a 32 Kbytes level 1 Data Cache, plus 256 Kbytes of level 2 cache shared between the two cores.

In addition to this powerful application core, it also embeds a Cortex®-M4 32-bit RISC core (with single-precision floating point unit) running at up to 209 MHz.

Finally, a powerful 3D GPU is available supporting Open GL ES 2.0 and running at up to 533 MHz.

The internal SRAM memory size is 708 Kbytes with a scattered architecture split into:

256 Kbytes of AXI System RAM

- plus 384 Kbytes of AHB MCU Subsystem RAM

- plus 64 Kbytes of AHB MCU subsystem retention RAM in backup domain

- and 4 Kbytes of SRAM in backup domain to keep data in the lowest power modes.

This line also includes up to 37 communication peripherals in addition to an LCD-TFT controller interface which can feed pixel to a parallel or Display Serial Interface (DSI) having two data lanes up to 1 Gbit/s each.

The STM32MP157 line embeds also low-power 16-bit ADCs running at up to 3 Msamples/s, 12-bit DACs, as well as 29 timers.

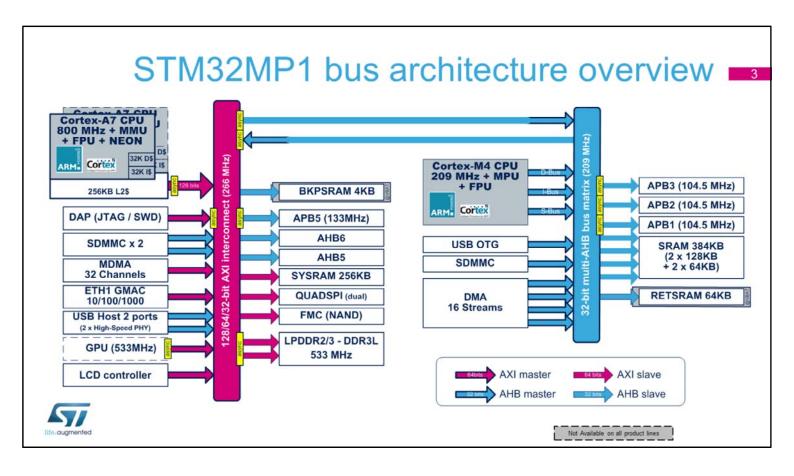

The STM32MP1 bus architecture is split in two interconnect matrix (Arm Cortex-A7 and Arm Cortex-M4) operating in different frequency domains, which can be set in low power modes independently.

• One high-speed Arm CoreLink NIC-400 network interconnect AXI-based performing interconnection between master and slaves on Arm Cortex-A7 side (called MPU-side), operating at 266 MHz (ck\_aclk) and allowing an internal bandwidth up to 2 Gbytes/s between each master and slave. This matrix is optimized for low latency and very high bandwidth master transfers to/from external DDR as well as internal SRAMs. An external DDR memory provides a raw bandwidth up to 4 GBytes/s. Peripherals belonging to the AXI domain are connected to AHB5, AHB6, APB4 (thru AHB6) and APB5 buses.

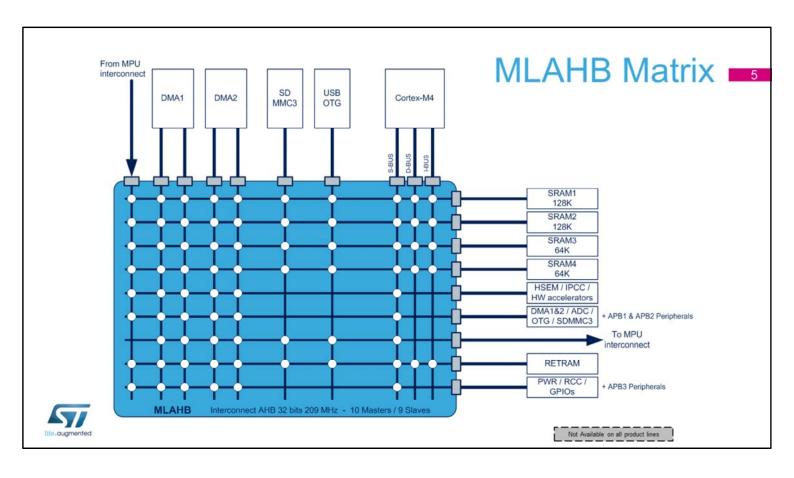

One multi-layer AHB interconnect (MLAHB) performing interconnection between master and slaves on Arm Cortex-M4 side (called MCU-side) with an architecture inherited from former MCU and operating at 209 MHz (ck\_mcu).

AXI interconnect matrix (AXIM) and Multi-layer AHB (ML-AHB) are connected together to enable the sharing of any peripheral by any master.

Blocks with dashed lines are not available on all product lines.

Security is not shown in this overview.

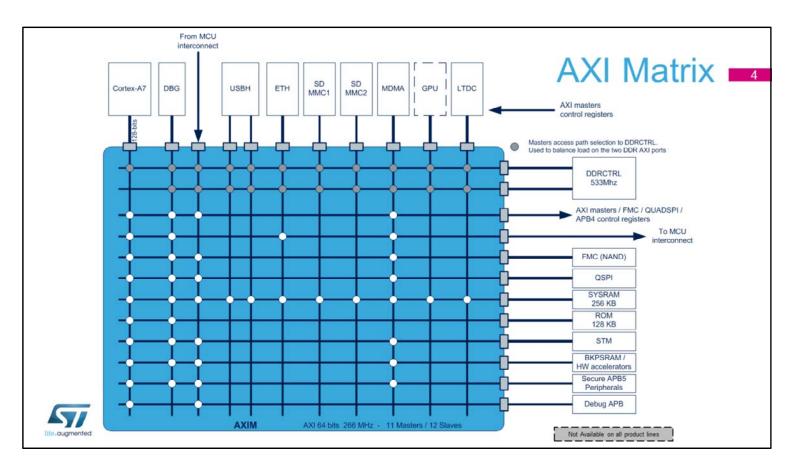

The AXI Matrix is enabling the interconnection between up to 11 masters and 12 slaves peripherals.

AHB Matrix is enabling the interconnection between up to 10 masters and 9 slaves peripherals.

# Memories Summary

#### Cortex-A7 TrustZone Cortex-M4 Memory Type **Access Control** BOOTROM ROM 128 KB SRAM SRAM 384 KB SYSRAM SRAM 256 KB RETRAM SRAM (On VBAT) 64 KB **BKPSRAM** SRAM (On VBAT) DDR3, DDR3L, DDR SDRAM Up to 1 GB LPDDR2, LPDDR3 SDMMC SD-Card, e-MMC (SDMMC3 only) Up to 512 MB (1) QUADSPI SPI Flash Up to 4 GB (2) FMC NOR NOR Flash, SRAM Up to 256 MB •

Up to 256 MB

(1) Memory-mapped mode (2) Indirect-mode

life.augmented

FMC NAND

NAND Flash

Some memories are dedicated to Cortex-A7 core access (e.g. BootROM, DDR), and benefit from the optional access control using the Arm TrustZone technology.

|                    |                             |                                                              | APB5 Secure commit(s): 172C / 12PC 0x5C00 0000 0x5C00 0000                                     | Memory Map                                          |

|--------------------|-----------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| OMFFFF FFFF        | DDR extension<br>(CA7 only) | OxFFFF FFF  OxCOO DOFF  Oystem debug IPs  Oystem debug IPs   | APB4 DORC / DORPHY / DORPERFM / LTDC / DSHOST / LSBPHYC 0x5A00 0000                            | overview                                            |

| 0xE000 0000        | or Debug                    | OxE004 4000 CM4 debug IPs 0xE004 0000                        | AHB6<br>USBH/ETH/<br>SDMMC/MDMA/<br>GPU                                                        |                                                     |

| 0xC000 0000        | CA7                         | OXOSFFFFFF<br>GLACOSFFFF                                     | 0x5600 0000<br>0x570F FFFF<br>0x5700 0000<br>0x5400 43FF                                       | <ul> <li>Uniform memory map</li> </ul>              |

| 0xA000 0000        | STM                         | GIC 0xA002 1000<br>0xA000 0000<br>STM 16 MB                  | AHB5 Backup RAM / HW accelerators 0x5000 DFFF  APB-DBG                                         | <ul> <li>All peripherals visible at same</li> </ul> |

| 0x9000 0000        | FMC NAND                    | 019000 0000<br>DMFFF FFFF<br>DM8000 0000                     | Coresight IPs 0+5008 0000 0+5008 0000 APB3 0+5002 A3FF                                         | address of every masters                            |

| 0x7000 0000        | FMC NOR                     | QUADSPI 256 MB 0x7000 0000                                   | SYSCFG / LPTIM /<br>BAI / PMB / HDP<br>0x5002 0000<br>AHB4<br>PWR / RCC / GPIOs<br>0x5001 FFFF | <ul> <li>No Remap</li> </ul>                        |

| 0x6000 0000        | Peripherals 2               |                                                              | 0.4000.4075                                                                                    |                                                     |

| 0x5000 0000        | Peripherals 1               |                                                              | HSEM / IPCC /<br>HW accelerators 0x4C00 0000                                                   |                                                     |

| 0x4000 0000        | RAM aliases                 |                                                              | AHB2 DM / ADC / SDMMC2 0x4800 0000 0x4401 37FF                                                 |                                                     |

| 0x3000 0000        |                             | SYSRAM 256 KB 0x2FFF FFFF 0x2FFC 0000                        | CAN / SAI / TIM / USART 0x4400 0000 0x4001 C3FF                                                |                                                     |

| 0x2000 0000        | SYSRAM                      | 0x2000 0000<br>0x1006 0000                                   | 12C / DAC / TIM /<br>UART / USART                                                              |                                                     |

| 0x1000 0000        | SRAMs                       | SRAM3 128 KB 0x1004 0000 0x1002 0000 0x1002 0000 0x1002 0000 | 0x3FFF FFFF                                                                                    |                                                     |

|                    | BOOT                        | ROM 126 KB                                                   | RETRAM 64 KB 0x3800 0000  SRAM3 128 KB 0x3004 0000  SRAM2 136 KB 0x3004 0000                   |                                                     |

| life.augment Resen | ved                         | CHICAGO CUAD                                                 | SRAM1 128 KB 0x3002 0000                                                                       |                                                     |

The memory map addressed by any masters is the same, all peripherals are visible at the same address, simplifying the development and debug.

There is no dynamic memory remapping, only part of the MCU SRAM and RETRAM memories are aliased on two locations to allow Cortex-M4 access optimizations.

# Reset and Clocking (RCC)

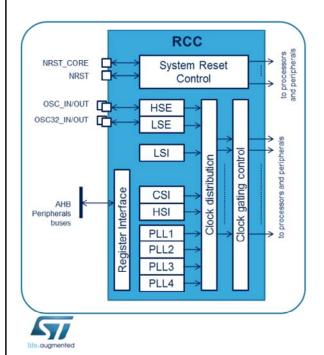

- The Reset and Clock Controller (RCC) manages:

- The generation of all the clocks,

- 4xPLLs, RC oscillators, Crystal oscillators...

- The gating of all the clocks

- · Possibility to enable/disable clocks for each peripheral

- The control of all the system and peripheral resets.

#### Application benefits

- High flexibility regarding the clock sources to meet consumption and accuracy requirements.

- Safe and flexible reset management

The reset and clock controller (RCC) manages the system reset and the peripherals clock generation. STM32MP15x microprocessor embeds 3 internal oscillators, 2 oscillators for an external crystal or resonator, and 4 phase-locked loops (PLL) managed by the RCC.

Outside the RCC, there is also one dedicated PLL for the High-Speed USB. For STM32MP15x lines with a Display Serial Interface (DSI), one additional PLL is dedicated to the clocking of this interface.

Many peripherals have their own clock, independent of the system clock to allow maximum flexibility.

The RCC provides high flexibility in the choice of the clock sources. This enables the system designer to meet both power consumption and accuracy requirements. The numerous independent peripheral clocks allow a

designer to adjust the system power consumption without impacting the communication baud rates, and also keep some peripherals active in low-power mode.

#### Power Supplies

| Name                  | Typical or Range     | Description                                                                                    |  |

|-----------------------|----------------------|------------------------------------------------------------------------------------------------|--|

| VDD                   | 1.7V – 3.6V          | Power supply input for I/Os                                                                    |  |

| VDD_ANA               |                      | Power supply input for system analog like RCC, PWR. To be connected to VDD                     |  |

| VDD_DSI**             |                      | Power supply input for DSI regulator. To be connected to VDD                                   |  |

| VDD_PLL               |                      | Power supply input for PLLs. To be connected to VDD                                            |  |

| VDD_CORE 1.2V         |                      | Power supply input for Digital Core domain                                                     |  |

| VDDA                  | 1.7V – 3.6V          | Analog Power supply input for ADCs, DACs and voltage reference buffers                         |  |

| VDDQ_DDR              | 1.2V / 1.35V / 1.5V° | Power supply input for DDR Physical Interface (PHY) and IOs                                    |  |

| VDD3V3_USBHS/FS       | 3.3V                 | Power supply input for USB Physical Interface (PHY) and IOs                                    |  |

| Internally generated  | Power Supplies       |                                                                                                |  |

| VDDA1V8_REG           | 1.8V                 | Analog Power Supply input or output, used internally for USB Physical Interface (PHY)          |  |

| VDDA1V8_DSI**         |                      | Analog Power supply input for DSI Physical Interface (PHY), to be connected to VDDA1V8_REG     |  |

| VDDA1V2_DSI_REG" 1.2V |                      | Analog Power supply output, used internally for DSI PLL                                        |  |

| VDDA1V2_DSI_PHY"      |                      | Analog Power supply input for DSI Physical Interface (PHY), to be connected to VDDA1V2_DSI_REG |  |

| VDDA1V1_REG 1.1V      |                      | Analog Power supply output for USB Physical Interface (PHY)                                    |  |

(\*) LPDDR2/LPDDR3, DDR3L and DDR3 respectively

\*) only on STM32MP157 line

The STM32MP15x microprocessor requires various dedicated power supplies to work.

- VDD has a wide range and is mostly used to supply the IOs.

- VDDCORE is the main supply for the internal logic.

- VDDA is used for the analog parts of the chip.

- VDDQ\_DDR is the IO voltage for the DDR interface. This voltage depends on the selected memory type and is 1.2V for LPDDR2 or LPDDR3, 1.35V for DDR3L and 1.5V for DDR3 memories.

- VDD3V3 USBHS and USB3V3 USBFS are used to supply the embedded USB physical interface for respectively high-speed and full-speed ports.

The STM32MP15x also embeds some internal regulators to supply the USB and DSI physical interfaces.

# Power Controller (PWR) 10

| Cortex-M4<br>or -A7 mode | Description                                                                                                                         | Wakeup                                                      |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| CRun                     | CPU Active → CPU, CPU-sub system bus matrix(s), CPU enabled peripheral clock(s) active.                                             | -                                                           |

| CSleep                   | CPU Sleep → CPU clock stopped, CPU-sub system bus matrix(s), CPU sleep enabled peripheral clock(s) active.                          | Any CPU Interrupt                                           |

| CStop                    | CPU Deepsleep → CPU, CPU-sub system bus matrix(s), CPU peripheral clock(s) stopped.                                                 | Depend on System mode                                       |

| System mode              | Description                                                                                                                         | Wakeup                                                      |

| Run                      | Clocks are active and forwarded to the system                                                                                       |                                                             |

| Stop / Lp-Stop           | Clocks are stopped. Some platform supplies are powered down (Lp-Stop). Some peripherals could request clock while in Stop / Lp-Stop | RTC/TAMP, EXTI, some peripherals, WKUP pins                 |

| LpLv-Stop                | Clocks are stopped. Some platform supplies are powered down. Core voltage could be reduced                                          | RTC/TAMP, EXTI, WKUP pins                                   |

| Standby                  | Most platform supplies are powered down. Core supply is powered down. Backup domain may be active                                   | RTC/TAMP, WKUP pins                                         |

| Off                      | All Platform, Core and IOs supplies are powered down. Backup domain may be active                                                   | RTC/TAMP event could request PMIC to restore power supplies |

The Core entering low power mode is controlled by software. When one Core enters CStop mode, the domain and system operating mode depend on the other Core mode.

Lp-Stop system mode could be used to control external supplies to reduce the system power.

LpLv-Stop system mode could be used to control external supplies as well as reducing the VDDCORE voltage to reduce the system power.

External power supplies are controlled using dedicated PWR ON or PWR LP signals in addition to some external software settings when an external Power Management IC (PMIC) is used.

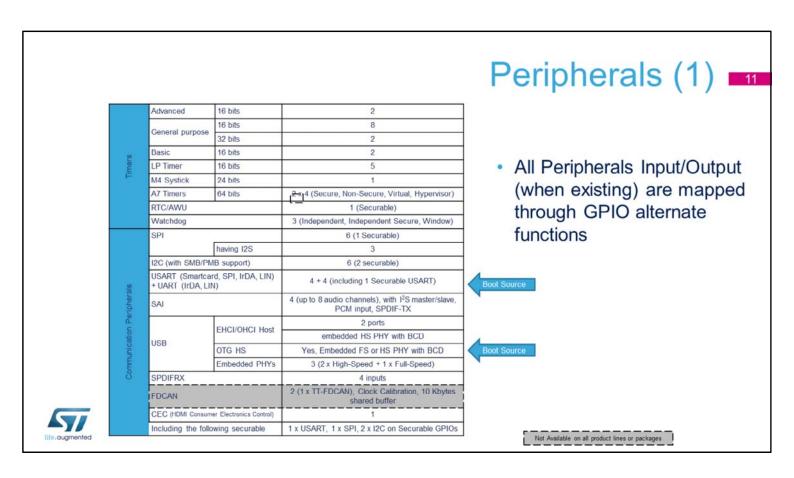

Peripherals with IOs are mapped on GPIO alternate functions (AFMUX).

Some peripherals are managed by BOOTROM and can be used as system control or program download during the initialization phase.

UART and USB are used to setup the system and/or download code into the external Flash memory.

Note that FDCAN is not available on STM32MP151 line.

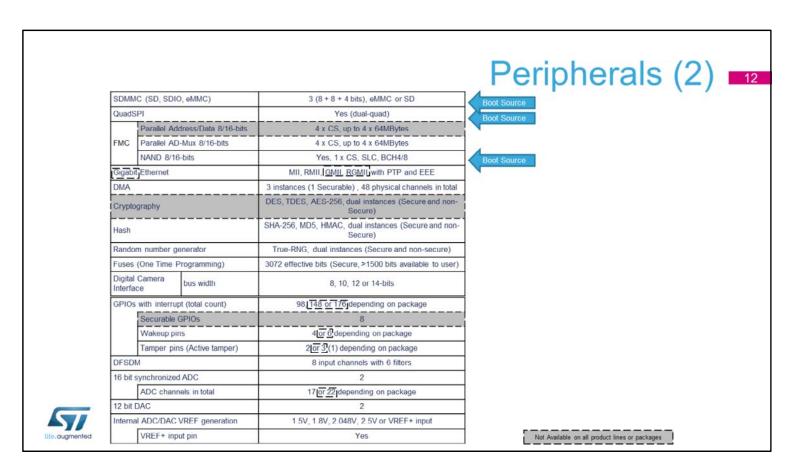

SDMMC can be a boot source by using either SD-Card (SDMMC1) or eMMC (SDMMC2) memory cards. QUADSPI bank1 can be a boot source for Serial-NOR or Serial-NAND Flash memories.

FMC could be a boot source for SLC parallel-NAND Flash memories.

Cryptography is not available on STM32MP15xA devices. Securable GPIOs are only available on STM32MP15xxAA (LFBGA448 18x18) and STM32MP15xxAC (TFBGA361 12x12) devices.

### Graphic and Display

- LCD-TFT controller, up to 24-bit // RGB888

- up to WXGA (1366 × 768) @60 fps

- · Two layers with programmable colour LUT

- 3D GPU: Vivante® OpenGL® ES 2.0

- · 533 MHz, up to 26 Mtriangle/s, 133 Mpixel/s

- MIPI<sup>®</sup> DSI 2 data lanes up to 1 GHz each

- up to WXGA (1366 × 768) @60 fps

Not Available on all product lines or packages

The LCD controller can provide up to WXGA @60fps (63Mpixels/s). Higher resolution are possible with reduced frame rate assuming the pixel clock remains in the allowed range.

A 3D GPU is available on STM32MP157 line and can process up to 26 Mtriangles/s or 133 Mpixels/s. A Display Serial Interface (MIPI DSI) is available on STM32MP157 line and can provide up to WXGA @60fps (63Mpixels/s). Higher resolution are possible with reduced frame rate assuming the LTDC pixel clock and the data lane rate remain in the allowed range.

#### OTP Fuses 14

- OTP Fuses are One Time Programming memory

- · Initial bits are '0' and are irreversibly programmed to '1'

- Incremental programing of bits in a 32-bit word is possible

- Handled thru BSEC controller IP

- Programming, reading, status and locking handled by BSEC

- Lock mechanism to avoid read and/or program (32-bits granularity)

- OTP Content

- Product configuration and Trimming values set by ST during production

- Secrets and unique identification numbers set by ST during production

- Device configuration set by OEM (e.g. MAC address, boot source, security mode, etc...)

- Secrets set by OEM (e.g. for secure boot)

- Up to 1184 bits available for other OEM purposes

OTP fuses are memory fields which could be programmed once and then cannot be altered anymore.

The BSEC IP manages the control of the OTP fuses, including reading, programming and secure accesses.

The OTP content includes product configuration and unique numbers.

The OTP could contains OEM information such as the MAC address, secret keys or any relevant data.

Up to 1184 bits are fully available for OEM various purposes.

## System control & Security 15

- System control

- RCC

- Reset and Clock Controller

- **PWR**

- · Power modes Controller

- EXTI

- External Interrupt management

- SYSCFG

- · Various system level configuration

- MDMA, DMA1/2, DMAMux

- Direct Memory Access

- MDMA chained to DMA1/2

- · DMAMux used for requestor flexibility

#### Security

- ETZPC

- · Control security level of some peripherals as well as SYSRAM and BKPSRAM

- Isolation of M4 resources from MPU subsystem

- TZC

- · Security firewall for DDR data accesses

- BSEC

- · Global security settings and OTP fuses control

- · Contains Device Electronic Signature registers

- TAMP

- · Tamper pins and backup registers management

- BKPSRAM

- · securable memory, Tamper protected

- CRYP, HASH, RNG and CRC

- · Secure and non-secure instances

Various blocks are managing the transversal system control. The major ones are the Reset and Clock Controller (RCC), the power manager (PWR) which controls the system power modes.

Security is controlled by Trustzone inside the Cortex-A7 core as well as various blocks. The Enhanced TrustZone Protection Controller (ETZPC) defines which peripherals are secure or not, isolated or not.

The TrustZone Address Space Controller for DDR (TZC) blocks unwanted access to DDR data.

#### Annex 16

- Keys points

- Cortex-A7 MPU subsystem can run powerful open operating systems like Linux or Android

- · Cortex-M4 MCU subsystem benefits from the rich STM32 MCUs family heritage

- · can be seen as a real time coprocessor for MPU

- · Large external DDR memory

- · Graphic Processing Unit

- Hardware architecture reference documents

- DS12505 STM32MP157C/F DataSheet

- RM0436 STM32MP157xxx Reference Manual

- Additional available documents

AN5031 - Getting started with STM32MP1 Series hardware development

The main points to be noted from this presentation are:

- The STM32MP15x embeds a Cortex-A7 core able to run powerful operating systems like Linux or Android.

- The STM32MP15x embed as well a Cortex-M4 core able to run real time tasks or act as a coprocessor to reduce the Cortex-A7 load or power.

- The STM32MP15x always need an external DDR memory to run the operating system.

- The STM32MP157 Line includes a GPU which provides rich graphic capabilities for operating system.