# **ST7 FAMILY**

# FLASH Programming

# REFERENCE MANUAL

Rev. 2

May 2005

USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED. STMicroelectronics PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF STMicroelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# ST7 FAMILY

# FLASH PROGRAMMING REFERENCE MANUAL

#### INTRODUCTION

This manual describes how to program FLASH memory of an ST72Fxxx microcontroller. For implementation details such as register or stack top address, refer to the product datasheet.

Three FLASH technologies are available in the ST7 family with different programming methods. Each ST7 FLASH microcontroller is associated with one of these three technologies as shown in the Flash Technology Types table in the Flash Programming Quick Reference Manual.

- XFlash (Extended): FLASH memory based on a EEPROM technology (see Section 2)

- HDFlash (High Density): FLASH memory based on FLASH technology (see Section 3)

- CFlash (ST72Cxxx): FLASH memory based on a EEPROM technology and not described in this document (see AN1179 for more details)

The In-Circuit Programming (ICP) method is used to update the entire contents of the FLASH memory (including option bytes) while the user application is not running. It uses In-Circuit Communication (ICC) protocol which enables an ST7 microcontroller to communicate with an external controller such as a PC with only 4 wires including V<sub>SS</sub> (see "ICC Protocol" reference manual for more details).

For ST72Cxxx devices, the In-Situ programming (ISP) method is used instead of ICP one. ISP is not described in this document (see AN1179 for more details).

In contrast to the ICP method, In-Application programming (IAP) uses any communication interface supported by the microcontroller (I/Os, SPI, SCI, USB, CAN...). IAP has been implemented for users who want their application software to update itself by re-programming the FLASH memory during execution. The main advantage of IAP is its ability to re-program the FLASH memory when the chip has already been soldered on the application board and while the user application is running. Nevertheless, part of the FLASH memory has to be previously programmed using ICP.

#### **Related Documentation**

- ICC Protocol Reference Manual

- Flash Programming Quick Reference Manual<sup>1</sup>

- Debug Module Reference Manual

<sup>1</sup>The Quick Reference manual provides device-specific tables included in the previous revision of the Flash Progamming and ICC reference manuals.

3/68 May 2005

Rev. 2

# **Table of Contents**

| INTRO | DDUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| N GLC | SSARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                       |

| 1 MEN | IORY PROTECTION STRATEGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8                       |

| 1.1   | READ-OUT PROTECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8                       |

| 1.2   | RECOVERY PROTECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                       |

| 1.3   | REGISTER ACCESS SECURITY SYSTEM (RASS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                       |

| 2 PRO | GRAMMING XFLASH MCUS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                       |

| 2.1   | INTRODUCTION1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                       |

| 2.3   | XFLASH PROGRAMMING  2.2.1 XFlash Programming Organization 2.2.1.1 XFlash Option Byte Programming 2.2.1.2 XFlash Protection Option Bits 2.2.1.3 Readout Protection Recovery 2.2.1.4 XFlash and RASS Protection 2.2.1.5 XFlash Control/Status Register (FCSR)  10  XFLASH PROGRAMMING TIME  11  XFLASH IN-CIRCUIT PROGRAMMING 12  2.4.1 ICP Method 13  2.4.2 ICP Example 2.4.2.1 ICP_Prog_Drv Example Program 2.4.2.2 ICP_Verif_Drv Example Program 2.4.2.3 ICP_Verif_Drv Example Program 2.4.2.3 ICP_Verif_Drv Example Program 2.4.2.3 ICP_Verif_Drv Example Program 2.4.2.3 ICP_Verif_Drv Example Program 2.4.2.4 ICP_Verif_Drv Example Program 2.4.2.5 ICP_Verif_Drv Example Program 3.5 ICP_Verif_Drv Example Program 3.6 ICP_Verif_Drv Example Program 3.7 ICP_Verif_Drv Example Program 3. | 145667<br><b>78</b> 889 |

| 2.5   | XFLASH IN-APPLICATION PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                       |

|       | 2.5.1 IAP Method       2.5.2 IAP Example         2.5.2 IAP Example       2.5.2 IAP Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |

| 3 PRO | GRAMMING HDFLASH MCUS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                       |

| 3.1   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                       |

| 3.2   | HDFLASH PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

|       | 3.2.1 HDFlash Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3<br>5                  |

|       | 3.2.4 Command Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | o                       |

# **Table of Contents**

|              | command Descriptions and Examples                             |    |

|--------------|---------------------------------------------------------------|----|

|              | .2.5.1 Commands and HDFlash Protections                       |    |

|              | .2.5.2 RASS Key Entry                                         |    |

|              | .2.5.3 Byte Programming (00h)                                 |    |

|              | .2.5.4 Block Programming (01h)                                |    |

|              | .2.5.5 Option Byte Programming (02h)                          |    |

|              | .2.5.6 Sector Erasing (03h)                                   |    |

|              | .2.5.7 All Programming (04h)                                  |    |

|              | .2.5.8 Option Byte Read (05h)                                 |    |

|              | .2.5.9 Checksum Computation (06h)                             |    |

|              | efining the Programming/Erasing Pulse Length (FREQ Parameter) |    |

|              | Programming the HDFLASH                                       |    |

|              | .2.7.1 Method when fCPU is unknown                            |    |

|              | .2.7.2 Method when fCPU is known                              |    |

|              | .2.7.3 Other method when fCPU is known                        |    |

|              | rasing the HDFLASH                                            |    |

|              | .2.8.1 Method when fCPU is known                              |    |

|              | .2.8.2 Method when fCPU is unknown                            |    |

|              | rasing the option bytes                                       |    |

|              | .2.9.1 Method when fCPU is unknown                            |    |

|              | .2.9.2 Method when fCPU is known                              |    |

| 3.           | .2.9.3 Other method when fCPU is known                        | 35 |

| 3.2.10G      | ieneral Rule                                                  | 35 |

| 3.2.11Ti     | ime-out                                                       | 35 |

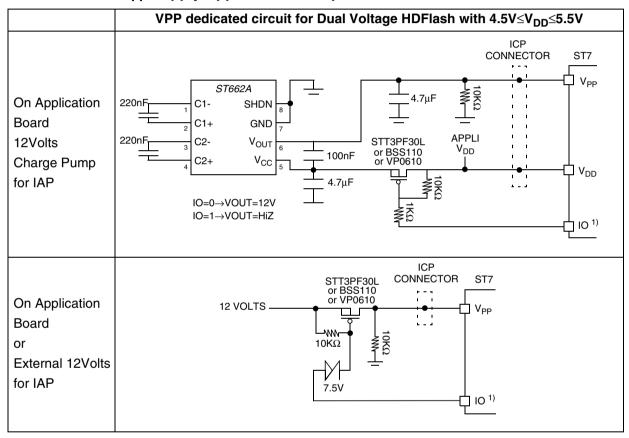

| 3.3 VPP FC   | OR DUAL VOLTAGE HDFLASH DEVICES                               | 36 |

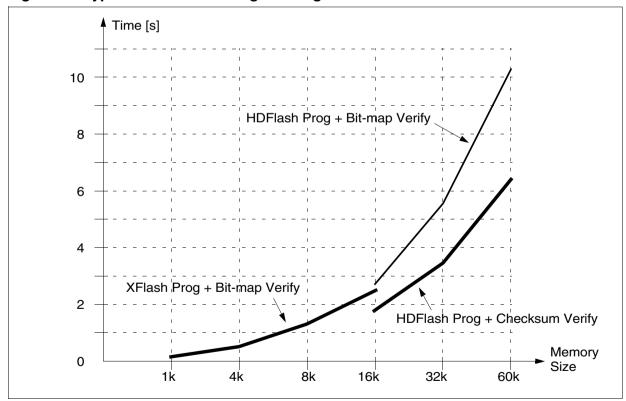

| 3.4 HDFLA    | ASH PROGRAMMING TIME                                          | 37 |

| 3.5 HDFLA    | ASH IN-CIRCUIT PROGRAMMING                                    | 38 |

| 351 IC       | CP Method                                                     | 38 |

|              | CP Example Program                                            |    |

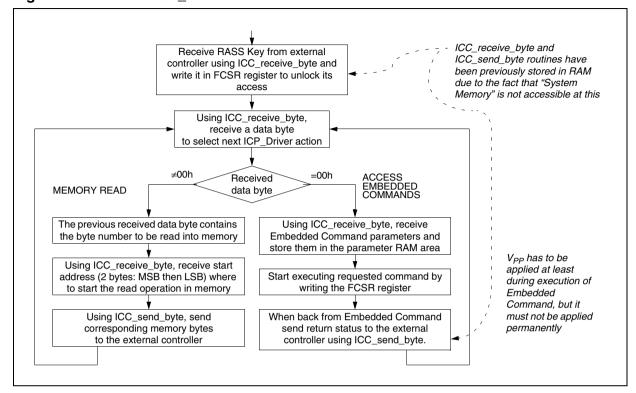

|              | ASH IN-APPLICATION PROGRAMMING                                |    |

|              |                                                               |    |

| APPENDIX 1 ( | (XFLASH AND HDFLASH PROGRAMMING TIMES)                        | 41 |

| APPENDIX 2 ( | (XFLASH PROGRAMMING SOURCE CODE EXAMPLE)                      | 44 |

| APPENDIX 3 ( | (HDFLASH PROGRAMMING SOURCE CODE EXAMPLE)                     | 50 |

| APPENDIX 4 ( | (EMULATED DATA EEPROM WITH XFLASH MEMORY)                     | 53 |

| APPENDIX 5 ( | (XFLASH ICP DRIVER SOFTWARE EXAMPLE)                          | 56 |

| APPENDIX 6 ( | (EMULATED DATA EEPROM WITH HDFLASH MEMORY)                    | 60 |

|              |                                                               |    |

|                     | Table of Contents |   |   |

|---------------------|-------------------|---|---|

| CHAMA DV OF CHANCES |                   | G | - |

# **GLOSSARY**

This chapter gives a brief definition of all new acronyms and names linked to the ICP and IAP methods as a quick reference:

- XFlash (Extended): Extended FLASH memory is based on EEPROM technology. The XFlash provides extended features such as byte per byte re-programming (by means of the byte erasing) and data EEPROM capability. The XFlash devices are available between 1k and 16kbytes.

- HDFlash (High Density): High density FLASH memory is based on FLASH technology. The high density of the HDFlash cell is used for devices with 4k up to 60kbytes FLASH memory. This HDFlash is programmed byte per byte but erased by sector.

- CFlash: CFlash memory is based on EEPROM technology and is implemented in ST72Cxx devices. CFlash programming is not described in this manual but in the AN1179 application note.

- IAP (In-Application Programming): The IAP is the ability to re-program the FLASH memory of a microcontroller while the device is already plugged-in to the application and the application is running.

- ICC Mode/Protocol (In-Circuit Communication): The ICC is either an ST7 mode or a software protocol stored by ST7 microcontrollers in the System Memory. The ICC software is used to download programs into RAM and execute them. It can also write (registers or RAM) or read any part of the memory space and jump to any memory address. The ICC protocol is used for ICP. It is accessed by entering ICC mode after a dedicated reset sequence.

- ICP (In-Circuit Programming): The ICP is the ability to program the FLASH memory of a microcontroller using ICC protocol while the device is plugged-in to the application.

- **Driver:** A driver is a control program defined by the application developer. A driver is used to manage the allocation of system resources to start application programs. In this document two drivers are described: ICP driver and IAP driver.

- ICC Monitor: The ICC monitor is the ST7 embedded software which manages the ICC protocol. It is located in System Memory.

- **USER Mode:** The USER mode is the standard user application running mode in the ST7. It is entered by means of the RESET pin and without any specific reset sequence.

- Embedded Commands: The Embedded Commands are the software drivers used by the USER application to program or erase HDFlash devices.

- System Memory: The System Memory is a write-protected part of the memory which contains the ICC monitor. The HDFlash System Memory also contains the Embedded Command software. The XFlash System Memory is accessible when the USER application is executed however this is not the case for HDFlash System Memory.

# 1 MEMORY PROTECTION STRATEGY

The ST7 FLASH protection strategy is based on 3 different types of protection:

- **Read-out Protection:** The user is able to protect the program and data stored in the FLASH memory from being read. To do so, the corresponding option bit must be programmed in the option byte using the ICP method.

- **Recovery Protection:** During the programming phase, the device can always recover in a stable and known state by executing a reset sequence. During ICP or IAP, this is guaranteed by the fact that the programming software driver is always write protected.

- Programming Mode Access Protection: This feature is used to protect the application against unwanted re-programming of the FLASH memory, disabling the FLASH Control/Status Register (FCSR). Access to the FCSR is enabled by writing a specific key sequence (see Section 1.3 REGISTER ACCESS SECURITY SYSTEM (RASS)). For HDFlash memories (which are dual voltage), the Programming Mode Access Protection is also guaranteed by the fact that an external V<sub>PP</sub> supply is needed to write or erase memory.

#### 1.1 READ-OUT PROTECTION

The read-out protection can be removed only if the entire FLASH memory is programmed or erased. Readout protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Even though no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller. Of course a user application that permits the user to dump the FLASH memory contents will render this read-out protection useless. Table 1 describes the capability of the FLASH memory sectors versus the ST7 modes and read-out protection settings.

| Caution: | When the read-out protection is set, STMicroelectronics is not able to |

|----------|------------------------------------------------------------------------|

|          | disable this option without erasing the FLASH content.                 |

Table 1. ST7 FLASH Memory Read-out Protection Summary

| ST7 Modes $ ightarrow$                 | USER mode (including IAP) |  | ICC I          | mode             |

|----------------------------------------|---------------------------|--|----------------|------------------|

| FLASH read-out protection $ ightarrow$ | Disabled Enabled          |  | Disabled       | Enabled          |

| FLASH Sector 0                         | Read / Execute            |  | Read / Write / | Protected        |

| FLASH Sector 1 or 2                    | Read / Write / Execute    |  | Execute        | (not accessible) |

8/68

# 1.2 RECOVERY PROTECTION

During either ICP or IAP sessions, the programming software driver is always write/erase protected. When entering ICC mode for ICP, the System Memory area, which contains the ICC monitor, cannot be modified. For IAP, sector 0 (where the IAP driver must be implemented) is write/erase protected.

- In ICC mode, this protection guarantees the ability to restart the ICP phase from the beginning by a device reset after an undesired programming or program counter corruption.

- Using IAP, the application RESET vector and the IAP driver software are in the write/erase protected sector 0. Thanks to these conditions, the USER application is able to manage the recovery protection in sector 0.

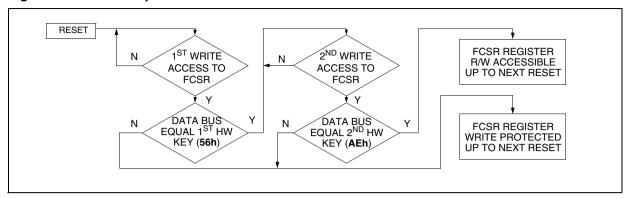

# 1.3 REGISTER ACCESS SECURITY SYSTEM (RASS)

The purpose of the RASS is to prevent the application from unintentionally accessing the FLASH control register which could cause involuntary re-programming of the FLASH memory. Even if the ICP or IAP is suddenly activated, no programming can be done unless the RASS procedure is completed.

After a device reset, the FLASH Control/Status Register (FCSR) is available only in Read mode. To be able to write to this register, a sequence of two hardware keys fixed by STMicroelectronics must be sequentially written to the FCSR address. If a write command that is other than the correct hardware key sequence is attempted, the FCSR register cannot be written to until the next device reset.

- When the FCSR register is written to for the first time after a reset, the data bus content is not latched into the FCSR register, but compared to the first hardware key value (56h).

- If the key available on the data bus is incorrect, then the FCSR register will remain locked until the next reset. Any new write commands sent to this address will be discarded.

- If the first hardware key is correct when the FCSR register is written to for the second time, the data bus content is still not latched into the FCSR register, but compared to the second hardware key value (AEh).

- If the key available on the data bus is incorrect, then the FCSR register will remain locked until the next reset. Any new write commands sent to this address will be discarded.

- If the second hardware key is correct, the FLASH register access is unlocked until the next reset. This means that the next write command sent to the FLASH register will be taken into account.

- There are two different ways of checking if the FCSR register is locked or unlocked, depending on whether the register is associated with XFlash (see Section 2.2.1.4) or HD-Flash (see Section 3.2.5.2) memory.

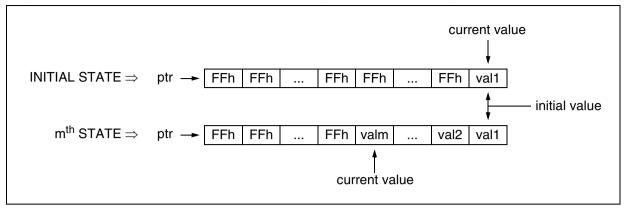

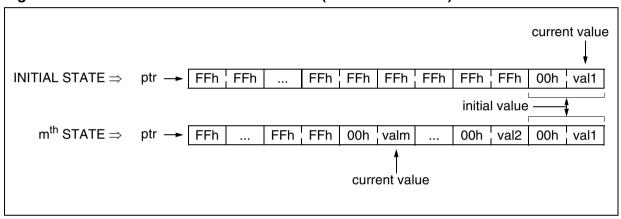

The serial RASS Principle is shown in Figure 1.

Figure 1. RASS Principle

To increase the reliability of the system, the software sequence which writes the hardware keys must not be stored in the program memory. Both hardware keys must always be loaded externally (via I/O ports, SCI, etc...). This security feature prevents any wrongful access after a program counter corruption.

**Note**: The hardware key values are atypical values of the FCSR register to ensure that the RASS sequence is not in the memory area.

# 2 PROGRAMMING XFlash MCUS

#### 2.1 INTRODUCTION

This section describes how to program the ST7 Single-Voltage XFlash microcontrollers (MCUs). See ST7 device list in section on page 3.

#### 2.2 XFlash PROGRAMMING

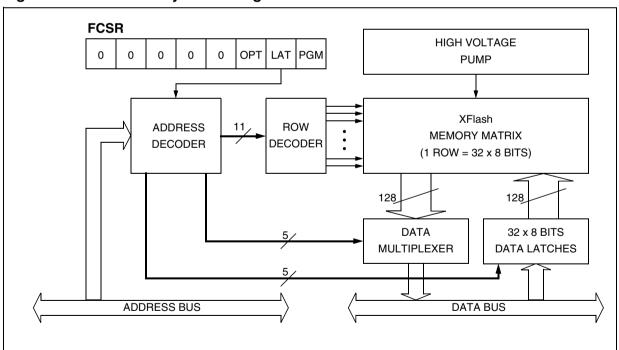

# 2.2.1 XFlash Programming Organization

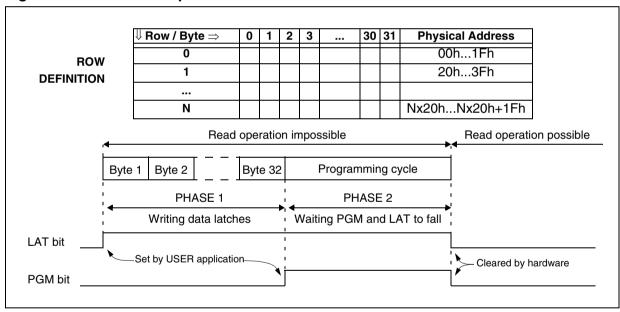

The XFlash program memory is organized in 8-bit wide memory cells which can be used for storing both code and data constants. It is mapped in the upper part of the ST7 addressing space and includes the reset and user interrupt vector area. The XFlash memory can be erased and programmed byte per byte. Up to 32 bytes can be programmed in the same erase and programming cycle. The Data EEPROM (featured on some devices) can be programmed the same way as the XFlash memory using either ICP or IAP sequences. The XFlash sector 0 and option bytes can be modified using ICP only.

XFlash programming is controlled by a single FLASH Control/Status Register (FCSR) described in Section 2.2.1.5.

Figure 1. XFlash Memory Block Diagram

**Note:** When the data EEPROM is not available in a ST7 device, it can be emulated by the XFlash memory with some restrictions (see APPENDIX 4 on page 53 for more details).

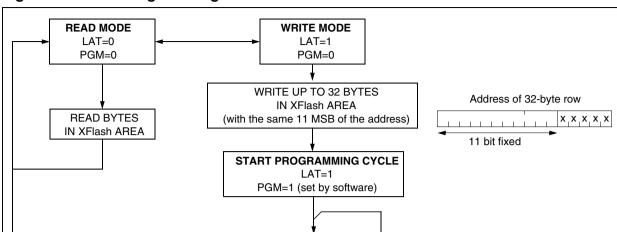

XFlash memory Read/Write access modes are controlled by the LAT bit in the FCSR register as shown in Figure 2.

- Read Operation (LAT=0): The XFlash memory program can be read as a normal ROM location when the LAT bit of the FCSR register is cleared.

- Write Operation (LAT=1): To enter Write mode, the LAT bit must be set by software (the PGM bit remains cleared). When a Write access to the XFlash area occurs, the value is latched by the 32 data latches.

When the PGM bit is set by software, all the bytes previously written in the data latches (up to 32) are programmed in the XFlash cells. The 11 most significant bits of the address (row) are given by the last data latch write sequence. This means that the selected row is defined by the last latched byte address, previous latched data bytes are taken into account within this row. Therefore, to prevent incorrect programming, the user must verify that all the bytes written between two programming sequences have the same high address: only the five least significant bits (LSBs) of the address can change.

At the end of the programming cycle, the PGM and LAT bits are cleared simultaneously by hardware.

This write operation sequence is illustrated in Figure 3. A source code example is given in AP-PENDIX 2 on page 44.

| Caution: | As soon as the LAT bit is set and up to the end of programming, the |

|----------|---------------------------------------------------------------------|

|          | XFlash contents cannot be executed. So the programming sequence     |

|          | has to be executed from another memory (RAM, Data EEPROM).          |

#### Notes:

- 1. Care should be taken during the programming cycle. Writing to the same memory location will over-program the memory (logical AND between the two write accesses) because the data latches are only cleared at the end of the programming cycle or when LAT bit is cleared. Latched data cannot be read. This note is illustrated in Figure 2.

- 2. If the LAT bit is not set, then the PGM bit can not be set (it is kept cleared).

Figure 2. XFlash Programming Flowchart

Figure 3. XFlash Write Operation

CLEARED BY HARDWARE-

**Note:** If a programming cycle is interrupted (by software or a reset action), the integrity of the data in memory is not guaranteed.

# 2.2.1.1 XFlash Option Byte Programming

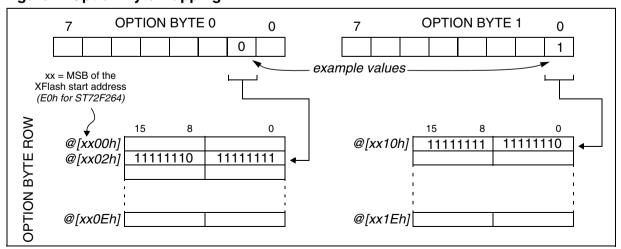

For security, each one of the 16 option bits is physically stored as two bytes (where only bit 0 of each byte is significant). Consequently, the 2 option bytes used to configure the MCU are mapped to 32 bytes of FLASH memory known as the Option Byte R21 row (see Figure 4). To access the Option byte row for programming, the OPT bit must be set in the FCSR register.

To program an Option Bit, write bit 0 of the corresponding byte pair to the opposite value you want to program and write bit 8 of the byte pair to the value (see Figure 4). Then, for each byte pair, the value can be set to FFFEh (option is set) or FEFFh (option is cleared).

The option bits are taken into account immediately after they are programmed, and not after the next reset as is the case with HDFlash.

At the end of Option Byte programming, the OPT bit must be cleared by software.

A source code example is given in APPENDIX 2 on page 44.

#### Important note:

To avoid static power consumption, it is mandatory to program ALL THE OPTIONS (and, consequently, all the 32 bytes in the option byte row), respecting the rule that the LSBit of each byte in the byte pair must be programmed with opposite values (all other bits must be kept set). If this rule is not respected, static consumption will occur and the option byte will be undefined. Moreover, a parasitic write protection could be set making the XFlash not reprogrammed.

# **Caution:**

As soon as the LAT bit is set and up to the end of programming, the XFlash contents cannot be executed. So the option byte programming sequence has to be executed from another memory (RAM, Data  $E^2$ ...).

Figure 4. Option Byte Mapping

# 2.2.1.2 XFlash Protection Option Bits

XFlash systematically includes two option bits dedicated to memory protection. One of these two bits (bit 0) is used to protect the XFlash content from being read (see section 1 on page 8 for more details), while the second one (bit 1) can be used to write protect the device (FLASH ROM capability).

- Read-out protection bit: as soon as this option bit is set, it is not possible to read-out the XFlash content as shown in Table 2. If this option bit is erased in order to re-program the XFlash that has been read-out protected, the whole XFlash memory is erased first. Note that even though no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

- Write protection bit: as soon as this option bit is set, it is not possible to re-write the XFlash memory, it behaves like a ROM (see Table 2).

| Caution: | When the write protection is set, STMicroelectronics is not able to |

|----------|---------------------------------------------------------------------|

|          | disable this option without erasing the entire XFlash memory.       |

**Table 2. ST7 XFlash Memory Protections**

|                                         | ST7 Modes $ ightarrow$              | USER mode (including IAP)  |     |             |       |             |

|-----------------------------------------|-------------------------------------|----------------------------|-----|-------------|-------|-------------|

| FLASH write protection bit $ ightarrow$ |                                     | 0                          | 1   | 0           | 1     | Х           |

| FLASH re                                | ead-out protection bit $ ightarrow$ | X                          | X   | 0           | 0     | 1           |

| DATA EEPROM when available              |                                     | R/W/E                      |     | R/W/E       |       | Protected   |

| XFlash                                  | Sector 0                            | R                          | / E | R/W/E       | R/E   | (not        |

| Ariasii                                 | Sector 1                            | R/W/E R/E                  |     | 11 / VV / L | 11/ 🗅 | accessible) |

| Write protection                        |                                     | -                          |     | R / W once  |       | R / W once  |

| Option bytes                            | Read-out protection                 | Protected (not accessible) |     | R/W         | R     | R/W         |

| Bytoo                                   | Others                              |                            |     | IT / VV     |       | R           |

**Notes:** the following abbreviations are used in the previous table.

R / W / E: read, write and execute capabilities

R / W: read and write capabilities

R / W once: read capability and write once capabilities

R / E: read and execute capabilities

R: read capability

# 2.2.1.3 Readout Protection Recovery

Removal of readout protection causes loss of RC calibration values in devices supporting this feature. When implementing your own programmer, these values should be restored when readout protection is removed using the following procedure:

- 1. Enter ICC mode with external clock. In this mode, option bytes configuration is ignored. (Refer Table 1)

- 2. Remove readout protection.

- 3. Refer to the RC calibration value table in the Flash Programming Quick Reference Manual and read off the correct RC calibration address values according appropriate device.

- 4. Rewrite the values in FLASH (0xFFDE and 0xFFDF) and/or EEPROM (0x1000 and 0x1001).

A user may want to either use a particular address as standard memory or store the RC calibration values in it. In order to provide this flexibility, it is suggested to prompt the user for restoration of each RCCRx location in FLASH and EEPROM. In case the user chooses to use these addresses as standard memory, the programmer must never write into these addresses and in case the user wants to use them to store RC calibration values, the programmer must give a warning in case of any attempt of violation.

#### 2.2.1.4 XFlash and RASS Protection

To protect the XFlash memory against involuntary re-programming, before programming the XFlash for the first time after a device reset, the RASS key sequence has to be written in the FLASH Control/Status Register (FCSR). If the access to the FCSR is write-protected by the RASS (wrong keys have been previously written in FCSR), a device reset has to be performed to unlock the RASS protection:

```

.RASS_Disable

LD A,#$56 ; 1st hardware key to unlock FCSR

LD FCSR,A

LD A,#$AE ; 2nd hardware key to unlock FCSR

LD FCSR,A

RET

```

#### Caution:

This example is intentionally simplified. For reliability reasons, keys should not be stored in the program memory. See Section 1.3 for more details.

To check if the FCSR register is locked or not by the RASS, set the LAT bit and read it again to verify if the bit has been written. If yes, the FCSR is unlocked, otherwise it is locked and a reset sequence has to be generated in order to unlock it.

47/

# 2.2.1.5 XFlash Control/Status Register (FCSR)

Read/Write

Reset Value: 0000 0000 (00h) 1<sup>ST</sup> RASS Key: 0101 0110 (56h) 2<sup>ND</sup> RASS Key: 1010 1110 (AEh)

| 7 |   |   |   |   |     |     | 0   |

|---|---|---|---|---|-----|-----|-----|

| 0 | 0 | 0 | 0 | 0 | OPT | LAT | PGM |

Bits 7:3 = Reserved, must be always kept cleared.

Bit 2 = **OPT**: Option byte Programming Mode.

This bit is set and cleared by software to select Program memory or Option byte access in ICP mode. When the LAT bit is set, the OPT bit can not be modified. So the OPT and the LAT bits cannot be set together, this operation must be done in two steps (example: BSET FCSR,#OPT then BSET FCSR,#LAT).

0: Program memory access

1: Option byte access

Bit 1 = **LAT**: Read/Write bit.

This bit is set by software. It is cleared by hardware at the end of the programming cycle. It can only be cleared by software if the PGM bit is cleared. While LAT bit is set the XFlash cannot be executed.

0: Read mode (32-byte latches are not accessible and are all set to FFh)

1: Write mode (32-byte latches are accessible)

Bit 0 = **PGM**: Program Bit

This bit is set by software to begin the programming cycle. At the end of the programming cycle, this bit is cleared by hardware.

0: Programming finished or not yet started

1: Programming cycle is in progress

Note: If the PGM bit is cleared during the programming cycle, the memory data is not guaranteed

#### 2.3 XFlash PROGRAMMING TIME

| Description                  |          | Conditions               | Max.     | Unit |

|------------------------------|----------|--------------------------|----------|------|

| Erase/Programming pulse time | е        | up to 32 bytes at a time | 5        |      |

| Erase/programming time       | 1 kbyte  | by block of 32 bytes     | 160      | ms   |

| Erase/programming time       | nb kbyte | by block of 32 bytes     | nb x 160 |      |

**Note**: The programming time is proportional to the number of bytes to be programmed but independent from  $f_{CPU}$ . The XFlash latch loading and the communication time for getting the data to be programmed depend on the application (including  $f_{CPU}$ ) and have to be added to this erase/programming time. For more details on programming time refer to APPENDIX 1 on page 41.

#### 2.4 XFlash IN-CIRCUIT PROGRAMMING

#### 2.4.1 ICP Method

ICP uses a protocol called ICC (In-Circuit Communication) to communicate with an external programming device connected via cable. See "ICC Protocol" reference manual for more details on ICC mode entry and the ICC protocol. ICP is performed in three steps:

- Switch the ST7 to ICC mode (In-Circuit Communications). When the ST7 enters ICC mode, it fetches a specific RESET vector which points to the ST7 System Memory containing the ICC protocol routine. This routine enables the ST7 to download the ICP driver into RAM.

- Download the ICP driver software into the RAM of the ST7 microcontroller using ICC.

- Using the ICC <go> command, jump to the ICP driver start address to start the XFlash programming sequence (this software may use the ICC protocol to transfer the data to be written in XFlash memory or another protocol).

The ST7 exits ICC mode by being reset.

Refer to the device datasheet for the hardware interface on the application board.

# 2.4.2 ICP Example

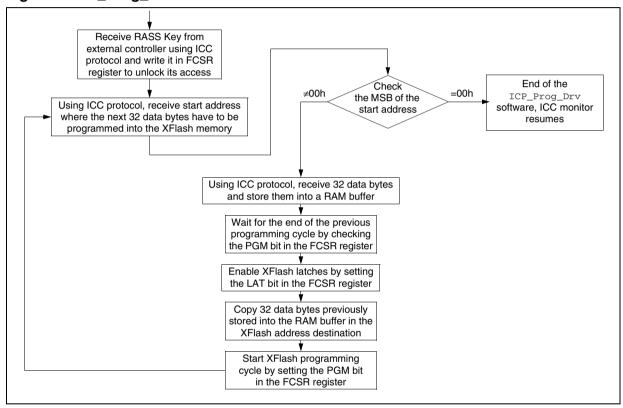

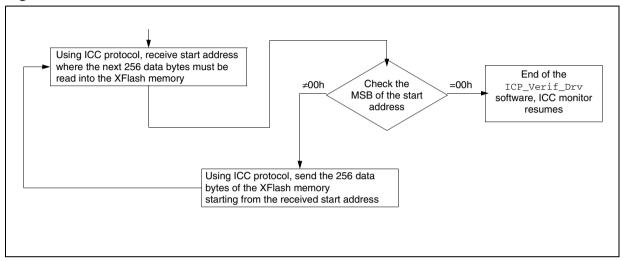

In this ICP driver example, the programmed device receives the data bytes using the ICC protocol while a programming cycle is in progress. This process can be used to optimize the global programming time. The programming and verify phases have been split to fit in a small RAM memory space. When a large RAM memory is available the programming and verify drivers can be downloaded at the same time. The verify procedure is needed to check if the XFlash has been correctly programmed. The ICP\_Prog\_Drv and ICP\_Verif\_Drv programs are described in Figure 5 and Figure 6 respectively. They are also described in AP-PENDIX 5 on page 56.

The programming procedure is summarized with the following steps:

- Enter ICC mode using the specific reset sequence (ICC monitor is then executed).

- Using the ICC <Write memory> command, download the programming ICP\_Prog\_Drv program into RAM. The purpose of the ICP\_Prog\_Drv program is to receive data bytes while a programming cycle is in progress and to program these data bytes without any verification. The data bytes are received by calling the ICC\_receive\_byte subroutine stored in the System Memory.

- Using the ICC <Go> command, jump to ICP\_Prog\_Drv to launch the programming phase.

At the end of the ICP\_Prog\_Drv program, the program jumps back to the ICC monitor to be ready for the next download to RAM.

- Using the ICC <Write memory> command, download the ICP\_Verif\_Drv program into the RAM. The purpose of the ICP\_Verif\_Drv program is to check that the programming has been correctly completed by reading the entire XFlash memory. This check is done by calling

47/

the ICC\_receive\_byte subroutine stored in the System Memory and the ICC\_send\_byte subroutine downloaded in the RAM. At the end of the ICP\_Verif\_Drv program, ICC mode recovers control.

**Note:** For the address of the <code>ICC\_receive\_byte</code> subroutine refer to "ICC Protocol" reference manual.

# 2.4.2.1 ICP\_Prog\_Drv Example Program

The ICP\_Prog\_Drv example program is described in Figure 5. The assembler software is shown in APPENDIX 5 on page 56.

Figure 5. ICP\_Prog\_Drv Flowchart

# 2.4.2.2 ICP Verif Drv Example Program

The ICP\_Verif\_Drv example program is described in Figure 6. The assembler software is shown in APPENDIX 5 on page 56.

Figure 6. ICP\_Verif\_Drv Flowchart

**Note:** To speed-up the verify procedure after the XFlash programming, a simple checksum can be computed by the ST7. In this case, only the checksum result is sent to the controller reducing to the minimum the time spent for communication.

#### 2.5 XFlash IN-APPLICATION PROGRAMMING

#### 2.5.1 IAP Method

In-Application Programming (IAP) enables the user to re-program the contents of the XFlash memory while executing the user application software. IAP has been implemented for users who want their application software to update itself by re-programming the XFlash memory during execution.

Sector 0 of the XFlash memory is write-protected in USER mode. To use IAP, this sector must contain the software driver (called IAP driver) to be able to re-program XFlash Sector 1. The IAP driver must be programmed by the user in Sector 0 using ICP. Sector 0 size is configurable by option byte so it can be adapted to different applications (see product datasheet for more details).

If a problem occurs during IAP, its execution can be recovered due to the fact that the IAP driver is always write/erase protected. This IAP driver can be programmed using ICP. This gives the user complete flexibility when integrating the IAP function in the application (mode of entry, choice of communication interface used to download the data to be programmed, etc...).

47/

# 2.5.2 IAP Example

The implementation of IAP depends on the user application software. In the following example (described in Figure 7), the data to be programmed into the XFlash memory is read from an external controller using a communication method called "user protocol". This user protocol depends on the application and can use, for example, an SPI, SCI, CAN or USB interface.

USER application User User No Yes Return from RAM Application decides Nο Application decides execution to to enter IAP to continue IAP the XFlash IAP driver Receive RASS Key from external controller Using user protocol, receive 32 data bytes using user protocol and write it and store them into a RAM buffer in FCSR register to unlock access Wait for the end of the previous programming cycle by checking Copy into RAM the software which will the PGM bit in the FCSR register program the XFlash memory (this software is the one surrounded with dot line) and call it Enable XFlash latches by setting the LAT bit in the FCSR register During an XFlash End of the IAP. Copy 32 data bytes previously programming cycle, the XFlash stored into the RAM buffer in the **USER** application cells can not be read or XFlash address destination recovers control executed, so this programming phase must be controlled from Start XFlash programming If the RASS keys have been locked previously outside XFlash (RAM or Data cycle by setting the PGM bit for security reasons, the USER application has EEPROM for example) in the FCSR register first to generate a device reset

Figure 7. XFlash IAP Driver Example Flowchart

Caution:

During XFlash memory programming cycles, all interrupts MUST be disabled to prevent unexpected Fetch commands from being sent to XFlash memory (not accessible at that time).

### 3 PROGRAMMING HDFLASH MCUS

#### 3.1 INTRODUCTION

This section describes how to program the ST7 Dual-Voltage HDFlash microcontrollers (MCUs). See ST7 device list on Page 3.

# 3.2 HDFlash PROGRAMMING

# 3.2.1 HDFlash Memory Organization

The ST7 DV (Dual Voltage) HDFlash is a non-volatile memory that may be electrically erased (by sector or completely at a time) and programmed in the application board on a byte-by-byte basis using an external  $V_{PP}$  supply. Since the external  $V_{PP}$  supply must not be permanently supplied, it has to be present only when a write or erase action is in progress. Nevertheless it is still possible to execute the HDFlash memory when the programming voltage is supplied to the  $V_{PP}$  pin as  $V_{PP}$  is not directly connected to the HDFlash cell but goes through an internal switch controlled by the Embedded Commands. The array matrix organization enables each sector to be erased and reprogrammed without affecting other sectors.

In the ST7 HDFlash memory, each sector can be erased and programmed only a few hundred cycles. It is organized in 8-bit wide sectors that can be used for both code and data storage.

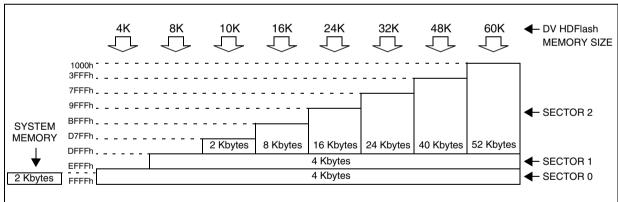

Figure 8. Memory Map and Sector Addresses

The DV HDFlash memory contains one, two or three user sectors depending on its size and one system sector called System Memory (see Figure 8). Each of the user sectors can be erased independently (filled with FFh). This prevents the unnecessary erasing of the entire HDFlash memory when only a partial erasing is required. The two first user sectors are set to 4 Kbytes for all memory sizes. They are mapped in the upper part of the ST7 addressing space and the reset and interrupt vectors are contained in Sector 0 (F000h-FFFFh). The size of the third user sector depends on the size of the total HDFlash memory and is not present if it is lower than or equal to 8 Kbytes.

**577**

The System Memory sector is located in a separate memory page that cannot be accessed by the user application. The System Memory contains the ICC monitor and the Embedded Command software that are used for programming and erasing the HDFlash memory.

#### 3.2.2 Embedded Command Use

The HDFlash memory is programmed by executing the Embedded Commands located in System Memory as described in the following procedure.

- 1. Write the Embedded Command parameters in the specified RAM addresses (see Table 3).

- 2. Ensure that at least 124 bytes are available in the stack.

- 3. Unlock access to the FLASH Control/Status Register (FCSR) by writing the two RASS hardware keys.

- 4. If available, disable the top level interrupt (TLI). This precaution must be taken to avoid a ST7 program counter corruption when a TLI occurs while the ST7 is programming the HDFlash. Consequently, HDFlash programming cannot be started during TLI routine execution.

- 5. Write a random value in the FLASH Control/Status Register (FCSR). This causes the ST7 to generate a non-maskable interrupt and execute the selected Embedded Command in System Memory. The user application execution is stopped, but all hardware peripherals remain active. All interrupts (except TLI) remain pending until the Embedded Command has finished execution.

- 6. When the Embedded Command is finished, an IRET instruction is generated and the user application program resumes. A status code is returned in the "ECMD" RAM location (address 00FFh, see Table 4).

# 3.2.3 RAM Memory Management

# 3.2.3.1 Parameter Passing

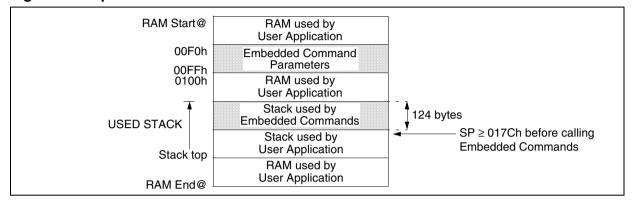

The Embedded Command parameters are exchanged through a RAM area located from 00F8h to 00FFh on page zero (see Figure 9). Table 3 lists the commands and parameters that must be specified by the user.

This RAM area as well as 00F0h to 00F7h is also used by the Embedded Command to store local variables and must not be written by the user application until the Embedded Command has completed execution as indicated by the return status code (see Table 4). When Embedded Commands are not used, the 00F0h..00FFh area is available for the application.

**Table 3. Embedded Command Description**

| Embedded Comman                               | Embedded Command Parameters |                               |                  |                               |                                 |                                 |                                     |                 |

|-----------------------------------------------|-----------------------------|-------------------------------|------------------|-------------------------------|---------------------------------|---------------------------------|-------------------------------------|-----------------|

| Name                                          | ECMD<br>(00FFh)             | SECT<br>(00FEh)               | PTRL<br>(00FDh)  | PTRH<br>(00FCh)               | ENDL<br>(00FBh)                 | ENDH<br>(00FAh)                 | DATA<br>(00F9h)                     | FREQ<br>(00F8h) |

| Byte programming                              | 00h                         |                               | @ Low            | @ High                        |                                 |                                 | Data                                | [18] 1)         |

| Block programming                             | 01h                         | Byte<br>Number                | Flash<br>Start@L | Flash<br>Start@H              | Buffer <sup>2)</sup><br>Start@L | Buffer <sup>2)</sup><br>Start@H |                                     | [18] 1)         |

| Option byte programming 3)                    | 02h                         |                               | 20h              |                               | 38h                             | Opt1                            | Opt0 4)                             | [18] 1)         |

| Sector and option erase (erased value is FFh) | 03h                         | Flash<br>Sector <sup>5)</sup> | 03h              | Flash<br>Sector <sup>5)</sup> |                                 |                                 |                                     | [18] 1)         |

| All programming 6)                            | 04h                         |                               | 00h              | 04h                           | FFh                             | FFh                             | 00h                                 | [18] 1)         |

| Option byte read                              | 05h                         |                               |                  |                               |                                 | Returne<br>dOpt1                | Re-<br>turned<br>Opt0 <sup>4)</sup> | [18] 7)         |

| Checksum computation (256 bytes)              | 06h                         |                               | Start@L          | Start@H                       | Re-<br>turned<br>CSL            | Re-<br>turned<br>CSH            |                                     | [18] 7)         |

#### Notes:

- 1. For recommendations on using the FREQ parameter, refer to section 3.2.6 on page 33. FREQ must be set for all commands and its value must never exceed f<sub>CPU</sub>, or 8 if f<sub>CPU</sub> is greater than 8MHz.

- 2. The data buffer to be programmed can be either in the RAM area or in the hardware register area.

- 3. A new option byte configuration becomes valid only after next device RESET. Nevertheless, the <Option byte read> command returns new option byte value. To program option bytes correctly, an erase must always be performed before programming an option byte, even if the value is FFh. Even if the device uses only one option byte for user settings, both option bytes have to be read and the second one reprogrammed with the value previously read. The same applies to reserved option bits, they must be programmed with the same value got from the read operation.

- 4. The Opt0 option byte includes the read-out protection bit (see Section 3.2.5.1 for more details).

- 5. To erase option bytes, the <Sector Erase> command must be called with Sector 0Fh as parameter (see Section 3.2.5.6 for more details).

- 6. This command can only be used to program the entire FLASH memory to 00h. In USER mode, this command must not be used when the watchdog is activated because this command has no timeout (see Section 3.2.4). If this command is used in USER mode, it returns a fail status after programming Sector 2 and 1 due to the fact that Sector 0 is write protected. The <All Programming> command must be called before erasing the option byte when the read out protection is activated.

- 7. FREQ parameter value is not used for the command computation but must be set between 1 and 8.

#### Caution:

The returned status code, ECMD, MUST ALWAYS be checked after each Embedded Command (see Section 3.2.3.3). After an Embedded Command has been executed, not only is the ECMD location modified but all the reserved area (from 00F0h to 00FFh) can be corrupted by the execution. Consequently, after each call, all command parameters have to be re-initialized.

24/68

# 3.2.3.2 Stack Usage

At least 124 bytes of the stack are required to execute the Embedded Commands (see Figure 9). This is due to the fact that during the programming phase, the DV HDFlash memory cannot be read or executed, so execution is done from RAM.

Figure 9. Required RAM area for Embedded Commands

#### 3.2.3.3 Returned Status Codes

A status code is returned by each Embedded Command in the ECMD RAM location, to report if the operation was performed successfully (see Table 4). This status code is only given in the 4 most significant bits of the ECMD RAM location.

#### Caution: