# PM0020 Programming manual

## STR91xFA Flash programming manual

#### Introduction

This manual describes how to configure, program, erase and protect access to the Flash memory of the STR91xFA microcontroller family.

The STR91xFA embedded Flash memory can be programmed using In-Circuit Programming or In-Application programming.

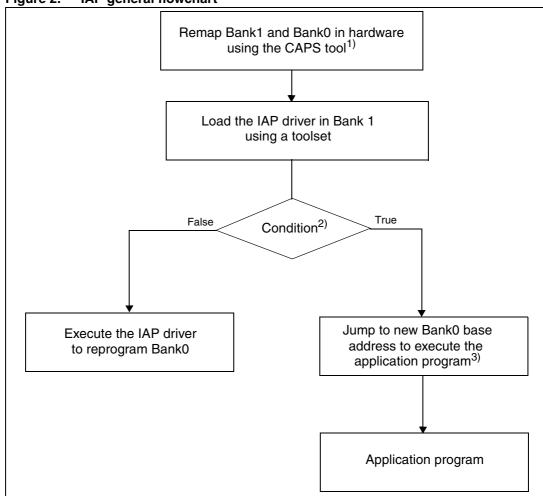

The In-Circuit programming (ICP) method is used to update the entire contents of the Flash memory, using the JTAG protocol to load the user application into the microcontroller. ICP offers quick and efficient design iterations and eliminates unnecessary package handling or socketing of devices.

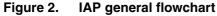

In contrast to the ICP method, In-Application Programming (IAP) can use any communication interface supported by the microcontroller (I/Os, USB, CAN, UART...) to download the data to be programmed in memory. IAP allows you to re-program the Flash memory while the application is executing. Nevertheless, part of the application has to have been previously programmed in one of the Flash banks using ICP.

## **Glossary**

This section gives a brief definition of acronyms and abbreviations used in this document:

CUI (Command User Interface): is the software interface of the FPEC.

**FPEC (Flash Program/Erase controller)**: The write operations to the 2 banks are managed by an embedded FPEC.

**IAP (In-Application Programming)**: IAP is the ability to program a bank of Flash memory from the user application residing in another bank.

**ICP (In-Circuit Programming)**: ICP is the ability to program the Flash memory of a microcontroller using JTAG protocol.

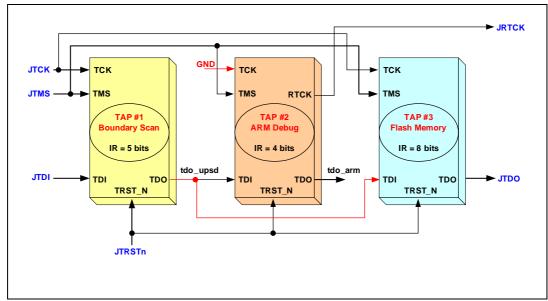

**JTAG (Joint Test Action Group)**: The debug interface of the ARM966E-S core is based on the Joint Test Action Group (JTAG) protocol.

Word address: Address that aligns to a word boundary (address lines A[1:0]=00).

Contents PM00020

# **Contents**

| 1 | STR  | 1xFA FI    | ash memory                                                           | 9    |

|---|------|------------|----------------------------------------------------------------------|------|

|   | 1.1  | Feature    | s                                                                    | 9    |

|   | 1.2  | Memory     | organization                                                         | . 10 |

|   | 1.3  | Initializa | ition                                                                | . 15 |

|   | 1.4  | Boot co    | nfiguration                                                          | . 16 |

|   | 1.5  | Electror   | nic signature                                                        | . 16 |

|   | 1.6  | OTP se     | ctor                                                                 | . 16 |

|   | 1.7  | Power d    | lown mode                                                            | . 16 |

|   | 1.8  | JTAG in    | terface                                                              | . 16 |

|   |      | 1.8.1      | JTAG access protection                                               | 17   |

|   | 1.9  | Sector v   | vrite protection                                                     | . 17 |

|   | 1.10 | Comma      | nd user interface (CUI)                                              | . 17 |

|   |      | 1.10.1     | Memory bank concurrency                                              | 19   |

|   | 1.11 | Read or    | perations                                                            | . 20 |

|   |      | 1.11.1     | RSR read bank status register (70h)                                  | 20   |

|   |      | 1.11.2     | RSIG read electronic signature (90h)                                 | 20   |

|   |      | 1.11.3     | ROTP read OTP sector (98h)                                           | 21   |

|   |      | 1.11.4     | RD read array (FFh)                                                  | 21   |

|   | 1.12 | Write op   | perations                                                            | . 22 |

|   |      | 1.12.1     | SE sector erase setup (20h)                                          | 22   |

|   |      | 1.12.2     | PG program setup (40h)                                               | 22   |

|   |      | 1.12.3     | CLSR clear status register (50h)                                     | 23   |

|   |      | 1.12.4     | CR write Flash configuration register (60h)+(03h)                    | 23   |

|   |      | 1.12.5     | PRP program protection level 1 register (60h)+(01h) or (D0h) $\dots$ | 24   |

|   |      | 1.12.6     | BE bank erase setup (80h)                                            | 24   |

|   |      | 1.12.7     | PES program/erase suspend (B0h)                                      | 24   |

|   |      | 1.12.8     | LOTP lock OTP sector (C0h)                                           | 25   |

|   |      | 1.12.9     | WOTP write OTP sector (C0h)                                          | 25   |

|   |      | 1.12.10    | PER program/erase resume (D0h)                                       | 26   |

|   | 1.13 | CUI reg    | isters                                                               | . 27 |

|   |      | 1.13.1     | Bank status register                                                 | 27   |

|   |      | 1.13.2     | Protection level 2 register (STR91xFAxx2 and STR91xFAxx4)            | 28   |

|   |      | 1.13.3     | Protection level 2 register (STR91xFAxx6 and STR91xFAxx7)            | 29   |

PM00020 Contents

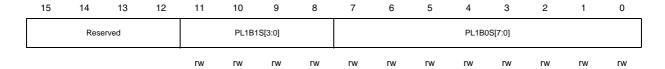

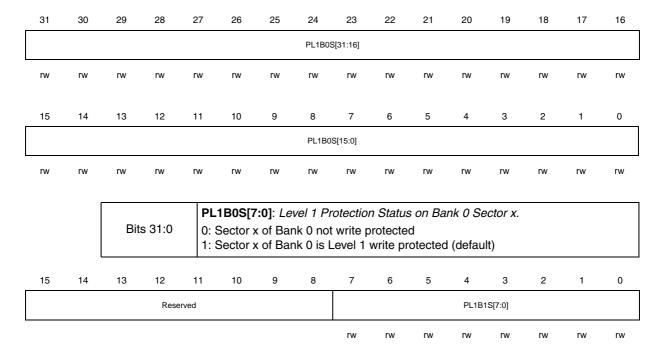

|   |                                                                                     | 1.13.4                                                                                                                                             | Protection level 1 register (STR91xFAxx2 and STR91xFAxx4)                                                      | 30                                                       |

|---|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   |                                                                                     | 1.13.5                                                                                                                                             | Protection level 1 register (STR91xFAxx6 and STR91xFAxx7)                                                      | 31                                                       |

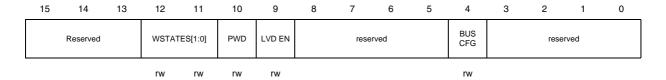

|   |                                                                                     | 1.13.6                                                                                                                                             | Flash configuration register                                                                                   | 32                                                       |

|   | 1.14                                                                                | CUI con                                                                                                                                            | nmand summary                                                                                                  | 33                                                       |

|   | 1.15                                                                                | FMI reg                                                                                                                                            | ister description                                                                                              | 35                                                       |

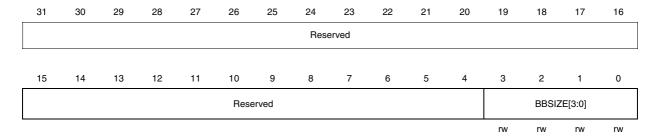

|   |                                                                                     | 1.15.1                                                                                                                                             | Boot bank size register (FMI_BBSR)                                                                             | 35                                                       |

|   |                                                                                     | 1.15.2                                                                                                                                             | Non-boot bank size register (FMI_NBBSR)                                                                        | 36                                                       |

|   |                                                                                     | 1.15.3                                                                                                                                             | Boot bank base address register (FMI_BBADR)                                                                    |                                                          |

|   |                                                                                     | 1.15.4                                                                                                                                             | Non-boot bank base address register (FMI_NBBADR)                                                               |                                                          |

|   |                                                                                     | 1.15.5                                                                                                                                             | FMI control register (FMI_CR)                                                                                  |                                                          |

|   |                                                                                     | 1.15.6                                                                                                                                             | FMI status register (FMI_SR)                                                                                   |                                                          |

|   |                                                                                     | 1.15.7                                                                                                                                             | BC fifth entry target address register (FMI_BCE5ADDR)                                                          |                                                          |

|   | 1.16                                                                                | STR91x                                                                                                                                             | in-application programming (IAP)                                                                               | 40                                                       |

| 2 | JTAG                                                                                | interfac                                                                                                                                           | ce                                                                                                             | 41                                                       |

|   |                                                                                     |                                                                                                                                                    |                                                                                                                |                                                          |

| 3 | Secu                                                                                | rity stat                                                                                                                                          | us                                                                                                             | 43                                                       |

| 4 | Chec                                                                                | ksum ca                                                                                                                                            | alculation                                                                                                     | 43                                                       |

|   |                                                                                     |                                                                                                                                                    |                                                                                                                |                                                          |

|   |                                                                                     |                                                                                                                                                    |                                                                                                                |                                                          |

| 5 | JTAG                                                                                | i sequen                                                                                                                                           | ıce                                                                                                            | 44                                                       |

| 5 | <b>JTAG</b><br>5.1                                                                  | -                                                                                                                                                  | nce                                                                                                            |                                                          |

| 5 |                                                                                     | JTAG tir                                                                                                                                           |                                                                                                                | 45                                                       |

| 5 | 5.1                                                                                 | JTAG tir                                                                                                                                           | ming specification                                                                                             | 45<br>46                                                 |

| 5 | 5.1<br>5.2                                                                          | JTAG tir<br>TURBO                                                                                                                                  | ming specification                                                                                             | 45<br>46<br>46                                           |

| 5 | 5.1<br>5.2<br>5.3                                                                   | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO                                                                                                              | ming specification                                                                                             | 45<br>46<br>46                                           |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                            | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO                                                                                                              | ming specification                                                                                             | 45<br>46<br>46<br>47                                     |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                     | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN                                                                                                    | ming specification                                                                                             | 45<br>46<br>46<br>47<br>47                               |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                              | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN<br>ISC-DIS                                                                                         | ming specification                                                                                             | 45<br>46<br>46<br>47<br>47                               |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                       | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN<br>ISC-DIS<br>ISC-ADI                                                                              | ming specification -PROG-ENABLE E NFIGURATION ABLE GABLE DRESS-SHIFT                                           | 45<br>46<br>46<br>47<br>47<br>48                         |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN.<br>ISC-DIS<br>ISC-ADI<br>ISC-CLI<br>ISC-PRO                                                       | ming specificationPROG-ENABLE E NFIGURATION ABLE SABLE DRESS-SHIFT R-STATUS                                    | 45<br>46<br>46<br>47<br>47<br>48<br>48                   |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                         | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN.<br>ISC-DIS<br>ISC-ADI<br>ISC-CLI<br>ISC-PRO<br>ISC-PRO                                            | ming specification -PROG-ENABLE ENFIGURATION ABLE CABLE DRESS-SHIFT R-STATUS OGRAM OGRAM-UC                    | 45<br>46<br>46<br>47<br>47<br>47<br>48<br>48             |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11         | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN.<br>ISC-DIS<br>ISC-AD<br>ISC-CLI<br>ISC-PRO<br>ISC-PRO<br>ISC-PRO                                  | ming specification -PROG-ENABLE E NFIGURATION ABLE SABLE DRESS-SHIFT R-STATUS OGRAM OGRAM-UC OGRAM-SECURITY    | 45 46 46 47 47 47 48 48 49                               |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12 | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN.<br>ISC-DIS<br>ISC-AD<br>ISC-CLI<br>ISC-PRO<br>ISC-PRO<br>ISC-PRO<br>ISC-PRO<br>ISC-PRO<br>ISC-REA | ming specification -PROG-ENABLE E NFIGURATION ABLE SABLE DRESS-SHIFT R-STATUS OGRAM OGRAM-UC OGRAM-SECURITY AD | 45<br>46<br>46<br>47<br>47<br>47<br>48<br>48<br>49<br>50 |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11         | JTAG tir<br>TURBO<br>IDCODE<br>ISC-CO<br>ISC-EN.<br>ISC-DIS<br>ISC-AD<br>ISC-CLI<br>ISC-PRO<br>ISC-PRO<br>ISC-PRO<br>ISC-PRO<br>ISC-REA<br>ISC-ER. | ming specification -PROG-ENABLE E NFIGURATION ABLE SABLE DRESS-SHIFT R-STATUS OGRAM OGRAM-UC OGRAM-SECURITY    | 45 46 46 47 47 47 48 49 50 51                            |

Contents PM00020

| 6  | Full c | Full chip erase operation 52 |                        |      |

|----|--------|------------------------------|------------------------|------|

| 7  | Erase  | e and pr                     | ogram operation        | 53   |

| 8  | Verify | / operat                     | ion                    | 55   |

| 9  | Blank  | k-check                      | operation              | 56   |

| 10 | Uploa  | ad opera                     | ation                  | 57   |

| 11 | Know   | n limita                     | tions                  | 58   |

| 12 | ISC Id | ogic des                     | scription              | 59   |

|    | 12.1   | Prelimin                     | nary concepts          | 59   |

|    | 12.2   | Instructi                    | on set                 | 61   |

|    | 12.3   | Configu                      | ration bits            | 62   |

|    | 12.4   | Registe                      | r description          | 63   |

|    |        | 12.4.1                       | Instruction Register   |      |

|    |        | 12.4.2                       | ISC default register   |      |

|    |        | 12.4.3                       | IDcode register        | . 65 |

|    |        | 12.4.4                       | Usercode register      | . 65 |

|    |        | 12.4.5                       | MFG register           | . 65 |

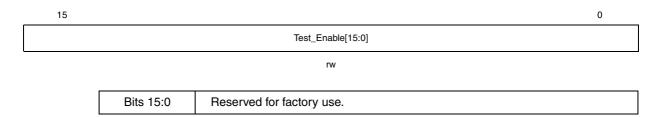

|    |        | 12.4.6                       | Test enable register   | . 66 |

|    |        | 12.4.7                       | ISC enable register    | . 66 |

|    |        | 12.4.8                       | ISC address register   | . 67 |

|    |        | 12.4.9                       | ISC sector register    |      |

|    |        | 12.4.10                      | Configuration register | . 68 |

|    | 12.5   | Instructi                    | on description & flows | 69   |

|    |        | 12.5.1                       | Bypass                 | . 69 |

|    |        | 12.5.2                       | Sample/preload         | . 69 |

|    |        | 12.5.3                       | Clamp                  | . 69 |

|    |        | 12.5.4                       | HIGHZ                  | . 69 |

|    |        | 12.5.5                       | EXTEST                 |      |

|    |        | 12.5.6                       | INTEST                 |      |

|    |        | 12.5.7                       | IDCODE                 |      |

|    |        | 12.5.8                       | MFG_READ               |      |

|    |        | 12.5.9                       | USERCODE               | . 71 |

|    |        |                              |                        |      |

PM00020 Contents

|      | 12.5.10       | ISC CONFIGURATION                       | 72 |

|------|---------------|-----------------------------------------|----|

|      | 12.5.11       | ISC_ENABLE                              | 73 |

|      | 12.5.12       | ISC_DISABLE                             | 74 |

|      | 12.5.13       | ISC_NOOP                                | 75 |

|      | 12.5.14       | ISC_ADDRESS_SHIFT                       | 75 |

|      | 12.5.15       | ISC_CLR_STATUS                          | 76 |

|      | 12.5.16       | ISC PROGRAM                             | 76 |

|      | 12.5.17       | ISC_PROGRAM_UC                          | 79 |

|      | 12.5.18       | ISC_PROGRAM_SECURITY                    | 79 |

|      | 12.5.19       | ISC_READ                                | 81 |

|      | 12.5.20       | ISC_ERASE                               | 82 |

|      | 12.5.21       | ISC_BLANK_CHECK                         | 83 |

|      | 12.5.22       | ISC_TEST_ENABLE                         | 83 |

|      | 12.5.23       | TRST, LVD_RESET_ON and TEST-LOGIC-RESET | 83 |

|      | 12.5.24       | Abort handling                          | 84 |

|      | 12.5.25       | Register table or reset                 | 85 |

| 13 F | Revision hist | torv                                    | 86 |

List of tables PM00020

# List of tables

| Table 1.  | STR91xFAxx2 Flash module organization                                                 | . 10 |

|-----------|---------------------------------------------------------------------------------------|------|

| Table 2.  | STR91xFAxx4 Flash module organization                                                 | . 10 |

| Table 3.  | STR91xFAxx6 Flash module organization                                                 |      |

| Table 4.  | STR91xFAxx7 Flash module organization                                                 | . 13 |

| Table 5.  | CUI commands                                                                          | . 18 |

| Table 6.  | Rules for dual bank operations                                                        |      |

| Table 7.  | RSIG electronic signature data for STR91xFAxx2 and STR91xFAxx4                        | . 20 |

| Table 8.  | RSIG electronic signature data for STR91xFAxx6 and STR91xFAxx7                        |      |

| Table 9.  | OTP word addressing                                                                   | . 21 |

| Table 10. | Command summary                                                                       | . 34 |

| Table 11. | Power up mode                                                                         | . 45 |

| Table 12. | Turbo mode                                                                            | . 45 |

| Table 13. | TURBO-PROG-ENABLE sequence                                                            | . 46 |

| Table 14. | IDCODE sequence                                                                       | . 46 |

| Table 15. | ISC-CONFIGURATION sequence                                                            | . 46 |

| Table 16. | ISC-ENABLE sequence                                                                   | . 47 |

| Table 17. | ISC-DISABLE sequence                                                                  | . 47 |

| Table 18. | ISC-ADDRESS-SHIFT sequence                                                            | . 47 |

| Table 19. | ISC-CLR-STATUS sequence                                                               | . 48 |

| Table 20. | ISC-PROGRAM sequence                                                                  | . 48 |

| Table 21. | ISC-PROGRAM-SECURITY sequence                                                         | . 49 |

| Table 22. | ISC-READ sequence                                                                     | . 50 |

| Table 23. | ISC-ERASE sequence                                                                    | . 51 |

| Table 24. | ISC-BLANK-CHECK sequence                                                              | . 51 |

| Table 25. | Full chip erase                                                                       | . 52 |

| Table 26. | Erase and program operation description                                               | . 53 |

| Table 27. | Verify operation description                                                          | . 55 |

| Table 28. | Blank check operation description                                                     | . 56 |

| Table 29. | Upload operation description                                                          | . 57 |

| Table 30. | Instruction set                                                                       | . 61 |

| Table 31. | Sector addresses                                                                      | . 67 |

| Table 32. | IDCODE sequence                                                                       | . 70 |

| Table 33. | MFG_READ sequence                                                                     |      |

| Table 34. | USERCODE sequence                                                                     | . 71 |

| Table 35. | ISC CONFIGURATION sequence                                                            |      |

| Table 36. | ISC_ENABLE sequence                                                                   | . 73 |

| Table 37. | ISC_DISABLE sequence                                                                  |      |

| Table 38. | ISC_NOOP sequence                                                                     | . 75 |

| Table 39. | ISC_ADDRESS_SHIFT sequence                                                            |      |

| Table 40. | ISC_CLR_STATUS sequence                                                               |      |

| Table 41. | Main and Secondary Flash sectors program flow                                         |      |

| Table 42. | OTP program flow (Lock bit: blocked)                                                  |      |

| Table 43. | OTP Lock Bit program flow                                                             |      |

| Table 44. | Configuration (sector protect, CSx mapping and LVD configuration bits) program flow . |      |

| Table 45. | ISC_PROGRAM_UC sequence                                                               |      |

| Table 46. | ISC_PROGRAM_SECURITY sequence                                                         |      |

| Table 47. | ISC_READ sequence                                                                     |      |

| Table 18  | ISC_ERASE seguence                                                                    | 22   |

| PM00020   | List of tables             |

|-----------|----------------------------|

| Table 49. | ISC_BLANK_CHECK sequence83 |

| Table 50. | Abort handling summary84   |

|           | Register table or reset    |

| Table 52. | Document revision history  |

List of figures PM00020

# **List of figures**

| Figure 1. | Typical memory map with device configured to boot from Bank 0 | 15 |

|-----------|---------------------------------------------------------------|----|

| Figure 2. | IAP general flowchart                                         | 40 |

| Figure 3. | JTAG chaining inside the STR91xFA, normal mode                | 42 |

| Figure 4. | JTAG chaining inside the STR91xFA, turbo programming mode     | 42 |

| Figure 5. | JTAG sequence flowchart                                       | 44 |

| Figure 6. | ISC-PROGRAM-UC sequence                                       | 49 |

| Figure 7. | JTAG state machine                                            | 60 |

## 1 STR91xFA Flash memory

#### 1.1 Features

- Two Flash memory banks with a total capacity up to 2048+128 Kbytes

- 32-bit burst read access, 16-bit write access

- Sequential Burst read up to 96 MHz

- I-TCM (Instruction Tightly Coupled Memory) interface to ARM966-ES core

- Branch Cache (BC) and Instruction prefetch queue (PFQ)

- AHB Interface to FMI registers

- Erasing on a sector or bank basis, and programming on a 16-bit halfword basis

- Each bank can be programmed and erased over 100,000 cycles

- 20-year data retention

- Each sector can be separately protected and unprotected against program and erase

- Electronic Signature memory

- 256 bits of OTP data memory

- Read-While-Write (RWW) Dual Bank operations

- Security protection bit to lock JTAG access or readout

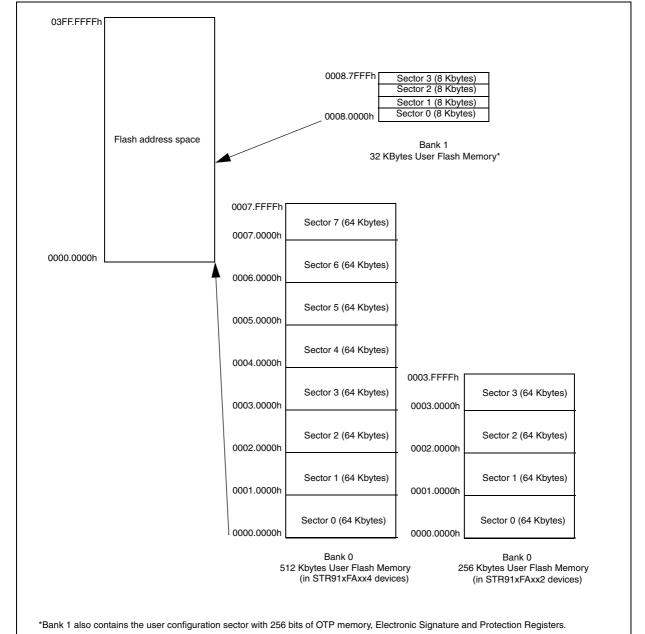

## 1.2 Memory organization

The Flash program memory is organized in 32-bit wide memory cells which can be used for storing both code and data constants.

You can Program Bank 0 and Bank 1 independently, i.e. you can read from one bank while writing to the other.

The on-chip Flash is divided in 2 banks that can mapped independently in the 64 MByte address space 0x0000-0000 - 0x03FF.FFF by programming the FMI registers.

The STR91xFAxx2 embedded Flash Module is organized as shown in *Table 1*.

Table 1. STR91xFAxx2 Flash module organization

| Bank                                                                                                                                                             | Sector                                                                                           | Address Offset            | Size (bytes) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|--------------|

| Bank 0 Bank 0 Sector 1 0x0001.0000 - 0x000 256 Kbytes Bank 0 Sector 2 0x0002.0000 - 0x000 Bank 0 Sector 3 0x0003.0000 - 0x000 Bank 1 Sector 0 0x0000.0000 - 0x00 | Bank 0 Sector 0                                                                                  | 0x0000.0000 - 0x0000.FFFF | 64K          |

|                                                                                                                                                                  | 0x0001.0000 - 0x0001.FFFF                                                                        | 64K                       |              |

| 256 Kbytes                                                                                                                                                       | Bank 0 Sector 2                                                                                  | 0x0002.0000 - 0x0002.FFFF | 64K          |

|                                                                                                                                                                  | Bank 0 Sector 3                                                                                  | 0x0003.0000 - 0x0003.FFFF | 64K          |

|                                                                                                                                                                  | Bank 1 Sector 0                                                                                  | 0x0000.0000 - 0x0000.1FFF | 8K           |

| Bank 1                                                                                                                                                           | Bank 1 Sector 1                                                                                  | 0x0000.2000 - 0x0000.3FFF | 8K           |

| 32 Kbytes                                                                                                                                                        | Bank 1 Sector 2                                                                                  | 0x0000.4000 - 0x0000.5FFF | 8K           |

|                                                                                                                                                                  | Bank 1 Sector 3                                                                                  | 0x0000.6000 - 0x0000.7FFF | 8K           |

| Bank 1                                                                                                                                                           | User Configuration Sector (OTP and Electronic Signature, Configuration and Protection Registers) | Access via CUI or JTAG    | 32           |

The STR91xFAxx4 embedded Flash Module is organized as shown in Table 2.

Table 2. STR91xFAxx4 Flash module organization

| Bank       | Sector          | Address Offset            | Size (bytes) |

|------------|-----------------|---------------------------|--------------|

|            | Bank 0 Sector 0 | 0x0000.0000 - 0x0000.FFFF | 64K          |

|            | Bank 0 Sector 1 | 7.00.000                  | 64K          |

|            | Bank 0 Sector 2 | 0x0002.0000 - 0x0002.FFFF | 64K          |

| Bank 0     | Bank 0 Sector 3 | 0x0003.0000 - 0x0003.FFFF | 64K          |

| 512 Kbytes | Bank 0 Sector 4 | 0x0004.0000 - 0x0004.FFFF | 64K          |

|            | Bank 0 Sector 5 | 0x0005.0000 - 0x0005.FFFF | 64K          |

|            | Bank 0 Sector 6 | 0x0006.0000 - 0x0006.FFFF | 64K          |

|            | Bank 0 Sector 7 | 0x0007.0000 - 0x0007.FFFF | 64K          |

Table 2. STR91xFAxx4 Flash module organization

| Bank      | Sector                                                                                           | Address Offset            | Size (bytes) |

|-----------|--------------------------------------------------------------------------------------------------|---------------------------|--------------|

| Bank 1    | Bank 1 Sector 0                                                                                  | 0x0000.0000 - 0x0000.1FFF | 8K           |

|           | Bank 1 Sector 1                                                                                  | 0x0000.2000 - 0x0000.3FFF | 8K           |

| 32 Kbytes | Bank 1 Sector 2                                                                                  | 0x0000.4000 - 0x0000.5FFF | 8K           |

|           | Bank 1 Sector 3                                                                                  | 0x0000.6000 - 0x0000.7FFF | 8K           |

| Bank 1    | User Configuration Sector (OTP and Electronic Signature, Configuration and Protection Registers) | Access via CUI or JTAG    | 32           |

The STR91xFAxx6 embedded Flash Module is organized as shown in *Table 3*

Table 3. STR91xFAxx6 Flash module organization

| Bank       | Sector           | Address Offset            | Size (bytes) |

|------------|------------------|---------------------------|--------------|

|            | Bank 0 Sector 0  | 0x0000.0000 - 0x0000.FFFF | 64K          |

|            | Bank 0 Sector 1  | 0x0001.0000 - 0x0001.FFFF | 64K          |

|            | Bank 0 Sector 2  | 0x0002.0000 - 0x0002.FFFF | 64K          |

|            | Bank 0 Sector 3  | 0x0003.0000 - 0x0003.FFFF | 64K          |

|            | Bank 0 Sector 4  | 0x0004.0000 - 0x0004.FFFF | 64K          |

|            | Bank 0 Sector 5  | 0x0005.0000 - 0x0005.FFFF | 64K          |

|            | Bank 0 Sector 6  | 0x0006.0000 - 0x0006.FFFF | 64K          |

| Bank 0     | Bank 0 Sector 7  | 0x0007.0000 - 0x0007.FFFF | 64K          |

| 1024Kbytes | Bank 0 Sector 8  | 0x0008.0000 - 0x0008.FFFF | 64K          |

|            | Bank 0 Sector 9  | 0x0009.0000 - 0x0009.FFFF | 64K          |

|            | Bank 0 Sector 10 | 0x000A.0000 - 0x000A.FFFF | 64K          |

|            | Bank 0 Sector 11 | 0x000B.0000 - 0x000B.FFFF | 64K          |

|            | Bank 0 Sector 12 | 0x000C.0000 - 0x000C.FFFF | 64K          |

|            | Bank 0 Sector 13 | 0x000D.0000 - 0x000D.FFFF | 64K          |

|            | Bank 0 Sector 14 | 0x000E.0000 - 0x000E.FFFF | 64K          |

|            | Bank 0 Sector 15 | 0x000F.0000 - 0x000F.FFFF | 64K          |

Table 3. STR91xFAxx6 Flash module organization (continued)

| Bank      | Sector                                                                                           | Address Offset            | Size (bytes) |

|-----------|--------------------------------------------------------------------------------------------------|---------------------------|--------------|

|           | Bank 1 Sector 0                                                                                  | 0x0000.0000 - 0x0000.3FFF | 16K          |

|           | Bank 1 Sector 1                                                                                  | 0x0000.4000 - 0x0000.7FFF | 16K          |

|           | Bank 1 Sector 2                                                                                  | 0x0000.8000 - 0x0000.BFFF | 16K          |

| Bank 1    | Bank 1 Sector 3                                                                                  | 0x0000.C000 - 0x0000.FFFF | 16K          |

| 128Kbytes | Bank 1 Sector 4                                                                                  | 0x0001.0000 - 0x0001.3FFF | 16K          |

|           | Bank 1 Sector 5                                                                                  | 0x0001.4000 - 0x0001.7FFF | 16K          |

|           | Bank 1 Sector 6                                                                                  | 0x0001.8000 - 0x0001.BFFF | 16K          |

|           | Bank 1 Sector 7                                                                                  | 0x0001.C000 - 0x0001.FFFF | 16K          |

| Bank 1    | User Configuration Sector (OTP and Electronic Signature, Configuration and Protection Registers) | Access via CUI or JTAG    | 32           |

The STR91xFAxx7 embedded Flash Module is organized as shown in *Table 4*.

Table 4. STR91xFAxx7 Flash module organization

| Bank       | Sector           | Address Offset            | Size (bytes) |

|------------|------------------|---------------------------|--------------|

|            | Bank 0 Sector 0  | 0x0000.0000 - 0x0000.FFFF | 64K          |

|            | Bank 0 Sector 1  | 0x0001.0000 - 0x0001.FFFF | 64K          |

|            | Bank 0 Sector 2  | 0x0002.0000 - 0x0002.FFFF | 64K          |

|            | Bank 0 Sector 3  | 0x0003.0000 - 0x0003.FFFF | 64K          |

|            | Bank 0 Sector 4  | 0x0004.0000 - 0x0004.FFFF | 64K          |

|            | Bank 0 Sector 5  | 0x0005.0000 - 0x0005.FFFF | 64K          |

|            | Bank 0 Sector 6  | 0x0006.0000 - 0x0006.FFFF | 64K          |

|            | Bank 0 Sector 7  | 0x0007.0000 - 0x0007.FFFF | 64K          |

|            | Bank 0 Sector 8  | 0x0008.0000 - 0x0008.FFFF | 64K          |

|            | Bank 0 Sector 9  | 0x0009.0000 - 0x0009.FFFF | 64K          |

|            | Bank 0 Sector 10 | 0x000A.0000 - 0x000A.FFFF | 64K          |

|            | Bank 0 Sector 11 | 0x000B.0000 - 0x000B.FFFF | 64K          |

|            | Bank 0 Sector 12 | 0x000C.0000 - 0x000C.FFFF | 64K          |

|            | Bank 0 Sector 13 | 0x000D.0000 - 0x000D.FFFF | 64K          |

|            | Bank 0 Sector 14 | 0x000E.0000 - 0x000E.FFFF | 64K          |

| Bank 0     | Bank 0 Sector 15 | 0x000F.0000 - 0x000F.FFFF | 64K          |

| 2048Kbytes | Bank 0 Sector 16 | 0x0010.0000 - 0x0010.FFFF | 64K          |

|            | Bank 0 Sector 17 | 0x0011.0000 - 0x0011.FFFF | 64K          |

|            | Bank 0 Sector 18 | 0x0012.0000 - 0x0012.FFFF | 64K          |

|            | Bank 0 Sector 19 | 0x0013.0000 - 0x0013.FFFF | 64K          |

|            | Bank 0 Sector 20 | 0x0014.0000 - 0x0014.FFFF | 64K          |

|            | Bank 0 Sector 21 | 0x0015.0000 - 0x0015.FFFF | 64K          |

|            | Bank 0 Sector 22 | 0x0016.0000 - 0x0016.FFFF | 64K          |

|            | Bank 0 Sector 23 | 0x0017.0000 - 0x0017.FFFF | 64K          |

|            | Bank 0 Sector 24 | 0x0018.0000 - 0x0018.FFFF | 64K          |

|            | Bank 0 Sector 25 | 0x0019.0000 - 0x0019.FFFF | 64K          |

|            | Bank 0 Sector 26 | 0x001A.0000 - 0x001A.FFFF | 64K          |

|            | Bank 0 Sector 27 | 0x001B.0000 - 0x001B.FFFF | 64K          |

|            | Bank 0 Sector 28 | 0x001C.0000 - 0x001C.FFFF | 64K          |

|            | Bank 0 Sector 29 | 0x001D.0000 - 0x001D.FFFF | 64K          |

|            | Bank 0 Sector 30 | 0x001E.0000 - 0x001E.FFFF | 64K          |

|            | Bank 0 Sector 31 | 0x001F.0000 - 0x001F.FFFF | 64K          |

Table 4. STR91xFAxx7 Flash module organization (continued)

| Bank      | Sector                                                                                           | Address Offset            | Size (bytes) |

|-----------|--------------------------------------------------------------------------------------------------|---------------------------|--------------|

|           | Bank 1 Sector 0                                                                                  | 0x0000.0000 - 0x0000.3FFF | 16K          |

|           | Bank 1 Sector 1                                                                                  | 0x0000.4000 - 0x0000.7FFF | 16K          |

|           | Bank 1 Sector 2                                                                                  | 0x0000.8000 - 0x0000.BFFF | 16K          |

| Bank 1    | Bank 1 Sector 3                                                                                  | 0x0000.C000 - 0x0000.FFFF | 16K          |

| 128Kbytes | Bank 1 Sector 4                                                                                  | 0x0001.0000 - 0x0001.3FFF | 16K          |

|           | Bank 1 Sector 5                                                                                  | 0x0001.4000 - 0x0001.7FFF | 16K          |

|           | Bank 1 Sector 6                                                                                  | 0x0001.8000 - 0x0001.BFFF | 16K          |

|           | Bank 1 Sector 7                                                                                  | 0x0001.C000 - 0x0001.FFFF | 16K          |

| Bank 1    | User Configuration Sector (OTP and Electronic Signature, Configuration and Protection Registers) | Access via CUI or JTAG    | 32           |

The write operations of the two banks are managed by an embedded Flash Program/Erase Controller (FPEC). The high voltage needed for Program/Erase operations is internally generated.

Figure 1. Typical memory map with device configured to boot from Bank 0

#### 1.3 Initialization

After reset, to define the mapping of the Flash memory banks, the user firmware has to write the start address and memory size of Bank 0 and Bank 1 in the FMI registers (see *Section 1.15*).

You must write the start address and the memory size of the bank configured as boot memory first and then the start address and the memory size of the other (non-boot) bank.

## 1.4 Boot configuration

In the default configuration, after reset the first sector of Bank 0 is enabled and resides at 0x0000.0000h so that the device boots from Bank 0, and Bank 1 is disabled.

Using the JTAG interface, you can configure the device to boot from Bank 1. The selection of which Flash memory is at the boot location is programmed in a non-volatile Flash-based configuration bit. The firmware cannot change this configuration bit, only the JTAG interface has access.

## 1.5 Electronic signature

The electronic signature can be read via JTAG or from the application using the RSIG command (*Section 1.11.2*).

The ISC IDCODE assigned to the Flash memory die is 04570041h.

Note:

The electronic signature read by the RSIG command contains the JTAG ID code of the Flash memory die. To get the STR91xFA product ID and revision level, read the last two bytes of the OTP sector.

#### 1.6 OTP sector

The device provides 240 bits of user OTP memory. The last 16 bits in the 256-bit sector are reserved for the STR91xFA product ID and revision level and programmed by ST. You can read all these bits, and program any unprogrammed bits via JTAG or from the application using the ROTP and WOTP commands (see *Section 1.11.3* and *Section 1.12.8*. The OTP sector can be locked via JTAG or CUI command to prevent any modification. The OTP lock status bit is stored in the Protection Level 2 register which can be read by the application. Refer to *Section 1.13.2*).

#### 1.7 Power down mode

In STR91xFA low power modes, the Flash automatically reduces its power consumption and can be read immediately after wake-up.

When the STR91xFA is in low power mode, you can put the Flash in Power Down mode as well for lower power consumption. You do this by programming the PWD bit in the Flash Configuration register (see *Section 1.13.6*). The consumption is drastically reduced, but after wake-up from low power, a delay is inserted automatically to ensure the Flash is operational before the CPU starts execution.

#### 1.8 JTAG interface

The device can be erased and programmed by sending commands to the command interface described in *Table* .

The device can also be programmed through the 4 pin JTAG port which is 1532 standard compliant and supports standard ISC (In System Configuration) programming instructions.

#### 1.8.1 JTAG access protection

You can protect the entire STR91xFA device from read or debug access through the JTAG port by setting the SECURITY bit in the Protection Level 2 register (see *Section 1.13.2.*). Once SECURITY is set, the Flash content cannot be read by JTAG. Only a full chip erase via JTAG can erase the SECURITY bit.

A secured device will not respond to JTAG program or erase commands other than Full Chip Erase, Read User Code and Read ID Code commands. The SECURITY bit has no impact on CUI commands.

## 1.9 Sector write protection

Sector write protection is managed on 2 levels:

- Protection Level 1

- Level 1 protection is controlled by the volatile Protection Level 1 register.

- Each sector has a level 1 write protection bit (see Section 1.13.4). After a device reset, all sectors are protected.

- You are free to modify the protection status of any sectors that are not protected by the Protection Level 2. This can be done from the application using a CUI Program Protection Level 1 command, see Section 1.12.5.

- Protection Level 2

- Level 2 protection is controlled by the non-volatile Protection Level 2 register

- Each sector has a Level 2 write protection bit (see Section 1.13.4). When the bit is set through the JTAG, the sector is always write protected. It can be unprotected only by erasing the bit via JTAG.

## 1.10 Command user interface (CUI)

Program and Erase commands are written to the Command User Interface. An on-chip Program/Erase Controller simplifies the process of programming or erasing the memory by taking care of all of the special operations that are required to update the memory contents. The end of a Program or Erase operation can be detected and any error conditions identified in the Bank Status Registers. The command set required to control the memory is consistent with JEDEC standards.

Erase can be suspended in order to perform either read or program in another sector and then resumed. Program can be suspended to read data in any other sector and then resumed. The two banks are protected during power-up.

The device features 2 different levels of protection to avoid unwanted program/erase operations. The sectors can be protected at Level 1 by the Sector Protect command or by the Protection Level 2 Register programmed via JTAG. All Program or Erase operations are aborted when the device is reset or powered off.

When the application accesses an address in Flash memory, the Command User Interface (CUI) decodes it as an instruction to the Program/Erase Controller (FPEC). The Bank Status Registers indicate the status resulting from the command. They can be read at any time during programming or erase to monitor the progress of the operation and to verify its successful completion.

The reset state of the CUI is Read Array. The command sequence must be followed exactly. Any invalid combination of commands will reset the device to Read Array mode.

Table 5. CUI commands

| Hex<br>Code | Command                                                              |

|-------------|----------------------------------------------------------------------|

| 00h         | Invalid Reset                                                        |

| 01h         | Protect Level 1 Confirm                                              |

| 03h         | Write Flash Configuration Register Confirm                           |

| 10h         | Alternative Program Set-up                                           |

| 20h         | Sector Erase Set-up                                                  |

| 40h         | Program Set-up                                                       |

| 50h         | Clear Status Register                                                |

| 60h         | Protect Level 1 Set-up and Write Flash Configuration Register Set-up |

| 70h         | Read Status Register                                                 |

| 80h         | Bank Erase Set-up                                                    |

| 90h         | Read Electronic Signature                                            |

| 98h         | Read OTP sector                                                      |

| B0h         | Program/Erase Suspend                                                |

| C0h         | Write (program) OTP or program OTP Lock bit                          |

| D0h         | Program/Erase Resume, Erase Confirm or Unprotect Level 1 Confirm     |

| FFh         | Read Array                                                           |

## 1.10.1 Memory bank concurrency

While one bank is in read mode, the other bank can be programmed or erased. The two Flash banks do not support programming or erasing in parallel.

A bank can always be read while erasure is in progress in the other bank.

Flash sector erasure may be suspended while data is read from other sectors of the same Flash memory bank and then resumed after reading.

*Table 6* lists the allowed dual operations in both banks and on the same bank.

Table 6. Rules for dual bank operations

|                          | Commands allowed in other bank                                   |         |              |                          |                         |

|--------------------------|------------------------------------------------------------------|---------|--------------|--------------------------|-------------------------|

| Bank Status              | Read Array/<br>Read Status Reg./<br>Read Electronic<br>Signature | Program | Sector Erase | Program/Erase<br>Suspend | Program/Erase<br>Resume |

| Idle                     | Yes                                                              | Yes     | Yes          | Yes                      | Yes                     |

| Programming              | Yes                                                              | -       | -            | Yes                      | -                       |

| Erasing                  | Yes                                                              | -       | -            | Yes                      | -                       |

| Programming<br>Suspended | Yes                                                              | -       | -            | -                        | Yes                     |

| Erase Suspended          | Yes                                                              | Yes     | -            | -                        | Yes                     |

## 1.11 Read operations

## 1.11.1 RSR read bank status register (70h)

Each bank has a Bank Status Register which indicates when a program or erase operation is completed and the success or error status. Refer to *Section 1.13.1* for the register description.

To read the Bank Status Register:

- Write a Read Status Register command (70h) to any word address in the bank. The status of the other bank is not affected by the command. You can write a Read Status Register command at any time, even while a Program/Erase operation is ongoing.

- Read any address in the bank to obtain the content of the Status Register.

See also Section 1.12.3: CLSR clear status register (50h).

#### 1.11.2 RSIG read electronic signature (90h)

The Electronic Signature is stored in the user configuration sector of Bank 1 which you can read using the RSIG command. It contains factory-programmed identification data that is useful to allow other devices to automatically match their interface to the characteristics of the microcontroller. The RSIG sector also contains Sector protection and Flash Configuration registers.

To read the Electronic Signature content:

- 1. Write a Read Electronic Signature command (90h) to any word address in Bank 1.

- 2. Read any of the RSIG registers shown in *Table 7* Reading the RSIG locations can be non-sequential. To access the RSIG registers, read from any address in Bank 1, using the low byte of the address to select the register.

- To exit RSIG mode, write a Read Array command (FFh) to any word address in Bank 1 to return it to Read Array mode.

Table 7. RSIG electronic signature data for STR91xFAxx2 and STR91xFAxx4

| Code or register             | Bank 1 word address LSB | Data D[31:0] |

|------------------------------|-------------------------|--------------|

| Manufacturer Code            | 00h                     | 20h          |

| Device Code                  | 01h                     | 04570041h    |

| Die Revision Code            | 02h                     | xxxx0000h    |

| Protection Level 2 Register  | 03h                     | xxxxxxxxh    |

| Protection Level 1 Register  | 04h                     | xxxxxxxxh    |

| Flash Configuration Register | 05h                     | xxxxxxxxh    |

Table 8. RSIG electronic signature data for STR91xFAxx6 and STR91xFAxx7

| Code or register                   | Bank 1 word address LSB | Data D[31:0] |

|------------------------------------|-------------------------|--------------|

| Manufacturer Code                  | 00h                     | 20h          |

| Device Code                        | 01h                     | 04570041h    |

| Die Revision Code                  | 02h                     | xxxx0000h    |

| Protection Level 2 Register Bank 0 | 03h                     | xxxxxxxxh    |

| Code or register                   | Bank 1 word address LSB | Data D[31:0] |  |

|------------------------------------|-------------------------|--------------|--|

| Protection Level 2 Register Bank 1 | 04h                     | xxxxxxxxh    |  |

| Protection Level 1 Register Bank 0 | 05h                     | xxxxxxxxh    |  |

| Protection Level 1 Register Bank 1 | 06h                     | xxxxxxxxh    |  |

| Flash Configuration Register       | 07h                     | xxxxxxxxh    |  |

Table 8. RSIG electronic signature data for STR91xFAxx6 and STR91xFAxx7

## 1.11.3 ROTP read OTP sector (98h)

The OTP (one-time programmable) sector is the user configuration sector of bank 1 which you can read using the ROTP command. It contains 16 halfwords and 15 are user-programmable.

To read the OTP sector:

- 1. Write a Read OTP sector command (98h) to any word address in Bank 1.

- 2. Read any of the OTP words see Reading the OTP words can be non-sequential. To access the OTP word, read from any address in Bank 1, using the low byte of the address to select the word.

- 3. To exit ROTP mode, write a Read Array command (FFh) to any word address in Bank 1 to return it to Read Array mode.

| OTP word   | Bank 1 word address LSB |

|------------|-------------------------|

| OTP Word 0 | 00h                     |

| OTP Word 1 | 01h                     |

| OTP Word 2 | 02h                     |

| OTP Word 3 | 03h                     |

| OTP Word 4 | 04h                     |

| OTP Word 5 | 05h                     |

| OTP Word 6 | 06h                     |

| OTP Word 7 | 07h                     |

Table 9. OTP word addressing

## 1.11.4 RD read array (FFh)

Read array is the normal operating mode for reading application data or executing code from a Flash bank. When a device reset occurs, the banks are in Read Array mode by default. However when you write some CUI commands to the bank they change the operating mode (for example to Program or Erase mode). When these operations are completed, you use the Read Array command to put the bank back into Read Array mode. A Read Array command will be ignored while a bank is programming or erasing. However in the other bank, a Read Array command will be accepted.

To put the bank in Read Array mode:

Write a Read Array command (FFh) to any word address in the bank. The status of the other bank is not affected by the command.

## 1.12 Write operations

When programming or writing to a Flash Bank, typically a "write" CUI command is issued and followed by a "read" status register command. This "write" then "read" order must be followed to program the Flash properly.

#### Caution:

This requires bit 18 (Instruction TCM order bit) in the Configuration Control Register of the ARM966E-S core to be set. This can be done by the following assembler code:

MOV R0, #0x40000

MCR P15,0x1,R0,C15,C1,0

When set, the write and read to the Flash Bank are performed in the order generated by the ARM966-ES core. This ensures that writes are committed to the Flash memory before any subsequent read.

#### 1.12.1 SE sector erase setup (20h)

Erasing a sector sets all the bits in the selected sector to '1'. You can erase one sector at a time. You do not have to pre-program the sector, this is done automatically before erasing.

To erase a sector:

- 1. Write a Sector Erase Set-up command (20h) to any word address in the sector to be erased.

- 2. Write an Erase Confirm command (D0h) to any word address in the sector to be erased. If the second command given is not an Erase Confirm, the command aborts and the ES and PS error flags in the status register are set.

- 3. After writing the SE command, reading any address within the bank will return the Status Register data.

- While erasure is in progress the PECS bit in the Status Register is '0'. When

erasure is completed the PECS bit is '1'.

- The ES bit in the Status Register returns '1' if there has been an erase failure.

- If the sector is protected, the erase operation aborts and the SP bit in the Status Register returns '1'

- 4. While the sector erase is ongoing, the bank with the sector being erased accepts only Read Status Register (70h) and Program/Erase Suspend (B0h) commands.

- 5. At the end of the sector erase operation:

- Write a Clear Status Register (50h) command to the bank to reset the Status Register.

- The bank will remain in Read Status Register mode until you write a Read Array (FFh) command.

## 1.12.2 PG program setup (40h)

The Program command programs a 16-bit array (halfword). Only one bank can be programmed at a time, the other bank must be in one of the read modes or in program/erase suspend mode (see *Table 6: Rules for dual bank operations*).

To program a halfword:

- 1. Write a Program Set-up command (40h) to any word address in the bank to be programmed.

- 2. Write the data halfword to be programmed to the destination address in the bank. The address must be pointing to the halfword location where the data is programmed.

- 3. After writing the data, reading any address within the bank will return the Bank Status Register data.

- While programming is in progress the PECS bit in the Bank Status Register is '0'.

When programming is completed the PECS bit is '1'.

- The PS bit in the Bank Status Register returns '1' if there has been a programming error.

- If the bank is protected, the program operation aborts and the SP bit in the Status Register returns '1'

- 4. While programming is ongoing, the bank accepts only Read Status Register (70h) and Program/Erase Suspend (B0h) commands.

- At the end of the program operation:

- Write a Clear Status Register (50h) command to the bank to reset the Status Register.

- Write a Read Array (FFh) command to return to normal operations.

Note:

Programming aborts if the MCU is powered down or a reset occurs. As data integrity cannot be guaranteed when the program operation is aborted, the sector containing the memory location must be erased and reprogrammed.

#### 1.12.3 CLSR clear status register (50h)

Each bank has a Status Register which indicates when a program or erase operation is complete and the success or error status. (see also *Section 1.13.1: Bank status register*).

To clear the Status Register:

- 1. Write a Clear Status Register command (50h) to any word address in the bank.

- 2. After the Clear Status Register command is executed, the bank returns automatically to Read Array mode.

#### 1.12.4 CR write Flash configuration register (60h)+(03h)

The Flash Configuration Register is located in the user configuration sector of Bank 1 which you can read using the RSIG command.

To program the Flash Configuration Register:

- 1. Write a Write Flash Configuration Register command (60h) to any word address in Bank 1.

- Write a Write Flash Configuration Register Confirm command (03h) to an address in Bank 1. The A[12:9] and A4 address bit values are written to the Flash Configuration register. However the reserved bit values cannot be changed. Refer to Section 1.13.6.

- At the end of the command, the memory returns to Read mode as if a Read Array command had been issued

#### 1.12.5 PRP program protection level 1 register (60h)+(01h) or (D0h)

The Protection Level 2 Register and Protection Level 1 registers are located in the user configuration sector of bank 1 which you can read using the RSIG command See *Table*. The Protection Level 2 Register can only be programmed via JTAG. Refer to *Section 1.13.2* and *Section 1.13.4* for the register descriptions.

To program the Protection Level 1 Register:

- 1. Write a Program Set-up command (60h) to any word address in the sector you want to protect/unprotect.

- 2. Write a Protect Confirm command (01h) to any word address in the sector you want to protect or Unprotect Confirm (D0h) if you want to unprotect it.

#### 1.12.6 BE bank erase setup (80h)

Bank erasure sets all the bits within the selected bank to '1'. It is not necessary to preprogram the bank as this is done automatically before erasing.

To erase a bank:

- Write a Bank Erase Set-up command (80h) to any word address in the bank to be erased.

- 2. Write an Erase Confirm command (D0h) to any word address in the bank to be erased. If the second command given is not an Erase Confirm, the command aborts and the ES and PS error flags in the status register are set.

- 3. After writing the BE command, reading any address within the bank will return the Status Register data.

- While erasure is in progress the PECS bit in the Status Register is '0'. When erasure is completed the PECS bit is '1'.

- The ES bit in the Status Register returns '1' if there has been an erase error.

- If the bank is protected, the erase operation aborts and the SP bit in the Status Register returns '1'

- 4. While the bank erase is ongoing, the bank accepts only Read Status Register (70h) and Program/Erase Suspend (B0h) commands.

- 5. At the end of the Bank Erase operation:

- Write a Clear Status Register (50h) command to the bank to reset the Status Register.

- The bank will remain in Read Status Register mode until you write a Read Array (FFh) command.

#### 1.12.7 PES program/erase suspend (B0h)

To suspend an ongoing Program or Erase operation:

Write a Program/Erase Suspend command (B0h) to any word address in the bank being programmed or erased.

#### **Erase suspend**

The Erase Suspend command freezes the erase operation (after a latency period of < 25us) and allows you to read or program in either of the two banks.

You can read the Bank Status register after the erase suspend is issued. The PECS and ESS bits in the Bank Status register are set to '1' when the erase operation has been suspended. The ESS bit is cleared if the erase is completed or in progress.

The valid commands while erase is suspended are: Program/Erase Resume, Program, Read Array, Read Status Register, Read Electronic Signature, Sector Protect, and Sector Unprotect. You can protect the sector being erased by issuing the Sector Protect command.

During Erase Suspend, the Flash goes into standby mode which reduces power consumption. Erase is aborted if the device is powered off.

#### Program suspend

The Program Suspend command freezes the ongoing programming operation.

The PSS bit in the Bank Status Register is set to '1' (within 5µs) if the program operation has been suspended. The PSS bit is cleared if the program operation is completed or in progress.

The valid commands while program is suspended are: Program/Erase Resume, Read Array, Read Status Register, Read Electronic Signature. During program suspend mode, the Flash goes into standby mode which reduces power consumption. The Program operation is aborted if the device is powered off.

#### 1.12.8 LOTP lock OTP sector (C0h)

The Lock OTP command allows you to modify the LOCK bit in the Protection Level 2 Register When it is set, the OTP sector is protected from any further write access. Refer to *Section 1.13.2*.

To program the LOCK bit:

- 1. Write a Write OTP command (C0h) to any word address in Bank 1.

- 2. Write the data value 01h to any word address in Bank 1 with 08h in the low byte of the address.

- After writing the data, reading any address within the bank 1 will return the Bank 1 Status Register data.

- While programming is in progress the PECS bit in the Bank 1 Status Register is '0'. When programming is completed the PECS bit is '1'.

- The PS bit in the Bank 1 Status Register returns '1' if there has been a programming error.

- If the OTP sector is already locked, the program operation aborts and the SP bit in the Status Register returns '1'

- 4. While programming is ongoing, Bank 1 accepts only Read Status Register (70h) and Program/Erase Suspend (B0h) commands.

- 5. At the end of the Lock OTP Sector operation:

- Write a Clear Status Register (50h) command to the bank to reset the Status Register.

- Write a Read Array (FFh) command to return to normal operations.

#### 1.12.9 WOTP write OTP sector (C0h)

The Write OTP command programs a halfword in the OTP sector. Once an OTP halfword is written, it cannot be erased. The other "unprogrammed" halfword can still be written at a

later time. If the LOCK bit in the Protection Level 2 Register is set, the OTP sector is protected from any further write access. Refer to *Section 1.13.2*. You can modify the LOCK bit using the LOTP command (see *Section 1.12.8*) or via the JTAG interface.

To program a halfword in the OTP sector:

- 1. Write a Write OTP command (C0h) to any word address in Bank 1.

- 2. Write the low or high halfword to be programmed to any address in Bank 1 using the low byte of the word address to select the OTP word. Refer to Writing the OTP locations can be non-sequential.

- 3. After writing the data, reading any address within the bank 1 will return the Bank 1 Status Register data.

- While programming is in progress the PECS bit in the Bank 1 Status Register is

'0'. When programming is completed the PECS bit is '1'.

- The PS bit in the Bank 1 Status Register returns '1' if there has been a programming error.

- If the OTP sector is protected, the program operation aborts and the SP bit in the Status Register returns '1'

- 4. While programming is ongoing, Bank 1 accepts only Read Status Register (70h) and Program/Erase Suspend (B0h) commands.

- At the end of the program operation:

- Write a Clear Status Register (50h) command to the bank to reset the Status Register.

- Write a Read Array (FFh) command to return to normal operations.

#### 1.12.10 PER program/erase resume (D0h)

#### Erase resume

If an Erase Suspend command was previously executed, the erase operation may be resumed by writing the D0h command to a word address within the suspended bank. When erase resumes:

- The PECS and ESS bits in the Bank Status register are cleared.

- Read operations to the bank being erased will return the Bank Status Register.

Erase cannot resume until program operations initiated during Erase Suspend have completed. You can also nest suspends as follows:

- 1. Suspend erase in the first bank

- 2. Start programming in the second or in the same bank

- 3. Suspend programming

- 4. Then read from the second or the same bank

#### Program resume

If a Program Suspend instruction was previously executed, the Program operation may be resumed by issuing the D0h command using an address within the suspended bank. When programming resumes,

- The PECS and PSS bits in the Bank Status register are cleared.

- Read operations to the bank being programmed will return the Bank Status Register.

# 1.13 CUI registers

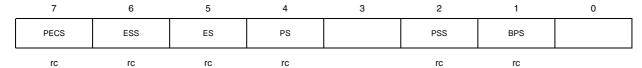

## 1.13.1 Bank status register

This register can be read using the RSR command (see *Section 1.11.1*). It can be cleared using the CLSR command (see *Section 1.12.3*)

|       | PECS: FPEC Status.                                                                                                                                                                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 | This bit indicates the status of the Program/Erase Controller (FPEC). You can poll it to check the progress of FPEC operations. It is set on completion of a Program or Erase operation. The PS and ES bits indicate success or failure.  0: Busy 1: Ready |

|       | ESS: Erase Suspend Status.                                                                                                                                                                                                                                 |

| Bit 6 | This bit is set when you write an Erase Suspend command. It remains set until an Erase Resume command is received.                                                                                                                                         |

|       | Erase in progress or completed     Erase suspended                                                                                                                                                                                                         |

|       | ES: Erase Status.                                                                                                                                                                                                                                          |

| Bit 5 | This bit is set to "1" if the FPEC has applied the max. number of erase pulses to the sector without a successful verify.  0: Erase successful  1: Erase failure                                                                                           |

|       | PS: Program status.                                                                                                                                                                                                                                        |

| Bit 4 | This bit is set to "1" if the FPEC has failed to program a word. 0: Program successful 1: Program failure                                                                                                                                                  |

| Bit 3 | Reserved.                                                                                                                                                                                                                                                  |

|       | PSS: Program suspend status.                                                                                                                                                                                                                               |

| Bit 2 | This bit is set when you write an Program Suspend command. It remains set until an Program Resume command is received.  0: Programming in progress or completed  1: Programming suspended                                                                  |

|       | SP: Sector protection status.                                                                                                                                                                                                                              |

| Bit 1 | This bit is set to "1" if a Program or Erase operation has been attempted on a protected sector 0: No Protection error 1: Program/Erase attempted on protected sector                                                                                      |

| Bit 0 | Reserved.                                                                                                                                                                                                                                                  |

| Dit 0 | rieserved.                                                                                                                                                                                                                                                 |

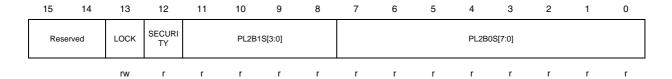

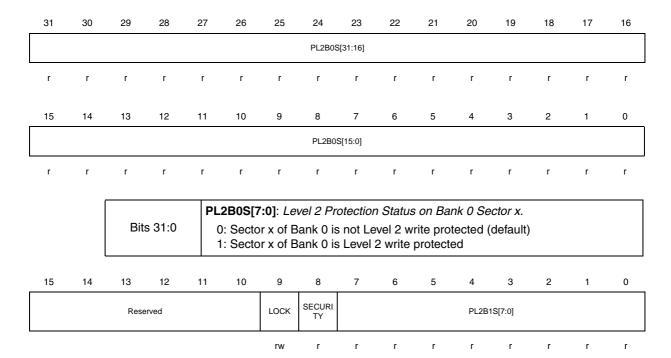

## 1.13.2 Protection level 2 register (STR91xFAxx2 and STR91xFAxx4)

This register can be read using the RSIG command (see *Section 1.11.2*) or by JTAG. The LOCK bit can be written via CUI or JTAG. Other bits can be written only via JTAG. The factory default settings may be modified by the user via JTAG. The register is not cleared by a device reset.