# RM0137 Reference manual

# ST40 core and instruction set architecture

# Introduction

The ST40 is a 32-bit RISC (reduced instruction set computer) microprocessor. It includes separate instruction and operand caches. The operand caches support both copy-back and write-through modes.

The 16-bit fixed-length instruction set gives the architecture extremely good code density.

The ST40 core products are grouped into series. These series can be distinguished by the following features.

- The associativity of the cache architecture.

- The presence of index and RAM modes in the cache architecture.

- The presence of a floating point unit (FPU). This provides hardware support for scalar and vector floating point computation.

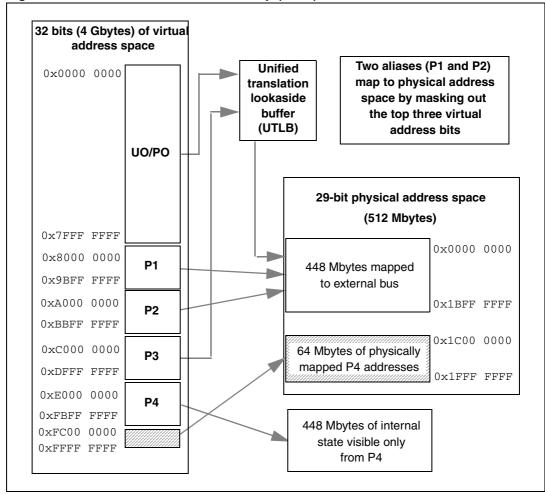

- The presence of a memory management unit (MMU). This provides hardware support for translation and protection of parts of the address space. It incorporates a 64 entry unified translation lookaside buffer (TLB) and a 4 entry instruction TLB which caches entries from the unified TLB without software intervention.

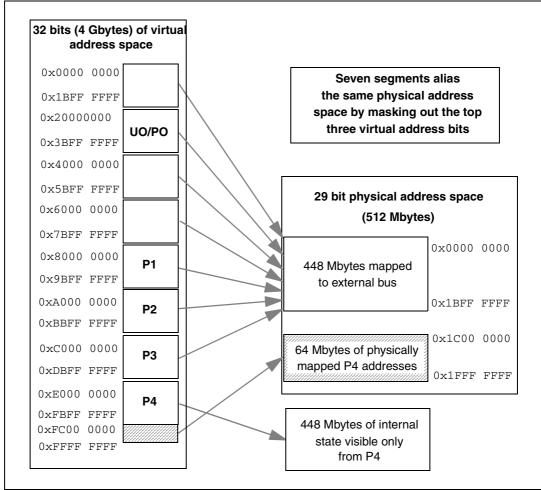

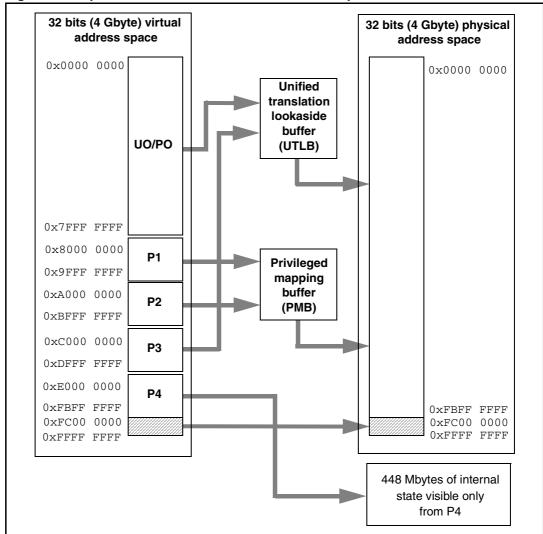

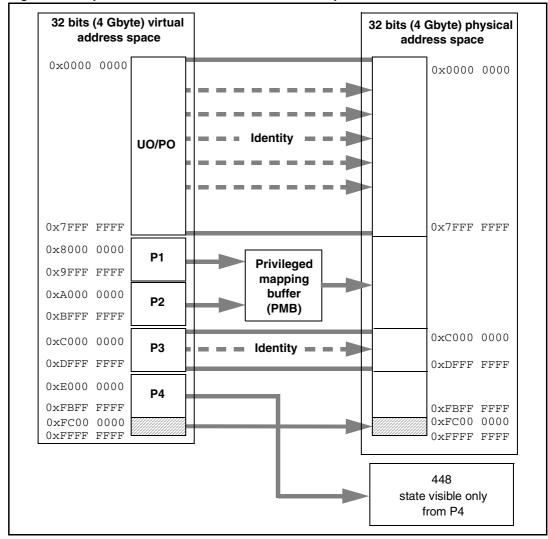

- The width of physical addressing used on the STBus. Earlier ST40 cores support 29-bit physical addressing. Newer ST40 cores can also support 32-bit physical addressing.

#### **Naming conventions**

ST40 for information common to all products.

ST40-100/200 series for series specific features.

ST40-103/202 for variant specific features.

Contents ST40 core

# **Contents**

| Prefac | ce   |            |                                                        | 10 |

|--------|------|------------|--------------------------------------------------------|----|

|        | Docu | ıment ide  | entification and control                               | 10 |

|        | ST40 | ) docume   | entation suite                                         | 10 |

|        | Conv | rentions ι | used in this guide                                     | 11 |

| 1      | Ove  | rview .    |                                                        | 12 |

|        | 1.1  | ST40       | core features                                          | 12 |

|        | 1.2  | Block      | diagram                                                | 17 |

| 2      | Prog | ırammir    | ng model1                                              | 18 |

|        | 2.1  | Gener      | al registers                                           | 19 |

|        | 2.2  | Syster     | m registers                                            | 20 |

|        | 2.3  | Contro     | ol registers                                           | 24 |

|        | 2.4  | Floatin    | ng-point registers                                     | 26 |

|        | 2.5  | Memo       | ry-mapped control registers                            | 28 |

|        | 2.6  | Data fo    | ormat in registers                                     | 28 |

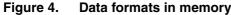

|        | 2.7  | Data fo    | ormats in memory                                       | 28 |

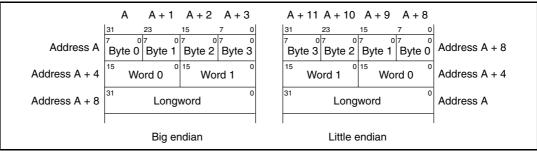

|        | 2.8  | Proces     | ssor states                                            | 29 |

|        |      | 2.8.1      | Reset state                                            | 29 |

|        |      | 2.8.2      | Reset address                                          | 29 |

|        |      | 2.8.3      | Exception-handling state                               | 29 |

|        |      | 2.8.4      | Program execution state                                | 30 |

|        |      | 2.8.5      | Power-down state                                       | 31 |

|        | 2.9  | Proces     | ssor modes                                             | 31 |

| 3      | Mem  | ory ma     | nagement unit (MMU)                                    | 32 |

|        | 3.1  | Termin     | nology 3                                               | 32 |

|        | 3.2  | ST40 I     | MMU variants                                           | 33 |

|        | 3.3  | Role o     | f the MMU                                              | 34 |

|        | 3.4  | Physic     | al address space                                       | 37 |

|        |      | 3.4.1      | 29-bit physical address space                          | 37 |

|        |      | 3.4.2      | 32-bit physical address space (space-enhancement mode) | 38 |

|     | 3.4.3   | Overview of mode switching                                   | 9  |

|-----|---------|--------------------------------------------------------------|----|

|     | 3.4.4   | Switching into space-enhancement mode                        | 0  |

|     | 3.4.5   | Switching out of space-enhancement mode4                     | 0  |

|     | 3.4.6   | Limitations on some ST40-200 series parts4                   | 0  |

|     | 3.4.7   | Effect of mode switching on the UTLB and ITLB4               | Ю  |

|     | 3.4.8   | Effect of mode switching on the instruction cache            | 0  |

|     | 3.4.9   | Effect of mode switching on the operand cache4               | .1 |

|     | 3.4.10  | Effect of mode switching on bus operations                   | ₊1 |

|     | 3.4.11  | Mode switching when the physical address of the PC changes 4 | 2  |

|     | 3.4.12  | Examples of switching into space-enhancement mode 4          | .3 |

|     | 3.4.13  | Example of switching out of space-enhancement mode4          | 4  |

| 3.5 | Virtual | addresses 4                                                  | 5  |

|     | 3.5.1   | MMU operating modes4                                         | -5 |

|     | 3.5.2   | Virtual address regions4                                     | -6 |

|     | 3.5.3   | Virtual to physical address mapping4                         | -6 |

|     | 3.5.4   | Multiple virtual address spaces5                             | 2  |

| 3.6 | Hardwa  | are and software functions                                   | 3  |

|     | 3.6.1   | Hardware functions5                                          | 3  |

|     | 3.6.2   | Software functions 5                                         | 3  |

| 3.7 | P4 add  | ress region                                                  | 4  |

|     | 3.7.1   | Resources accessible only through P45                        | 4  |

|     | 3.7.2   | Resources accessible through P4 and through translations5    | 4  |

|     | 3.7.3   | P4 virtual addressing structure5                             | 5  |

| 3.8 | Registe | er descriptions 5                                            | 7  |

|     | 3.8.1   | Page table entry high register (PTEH)                        | 7  |

|     | 3.8.2   | Page table entry low register (PTEL)                         | 9  |

|     | 3.8.3   | Translation table base register (TTB)                        | i2 |

|     | 3.8.4   | TLB exception address register (TEA) 6                       | 3  |

|     | 3.8.5   | MMU control register (MMUCR)6                                | 3  |

|     | 3.8.6   | Physical address space control register (PASCR) 6            | 6  |

|     | 3.8.7   | Instruction refetch inhibit control (IRMCR) 6                | 8  |

| 3.9 | Unified | TLB (UTLB) 6                                                 | 9  |

|     | 3.9.1   | UTLB operations                                              | 'O |

|     | 3.9.2   | UTLB address array                                           | 2  |

|     | 3.9.3   | UTLB data array                                              | '4 |

|   | 3.10 | Instruc  | tion TLB (ITLB)                                                                   | 79   |

|---|------|----------|-----------------------------------------------------------------------------------|------|

|   |      | 3.10.1   | ITLB operations                                                                   | 79   |

|   |      | 3.10.2   | ITLB LRU state                                                                    | 81   |

|   |      | 3.10.3   | ITLB address array                                                                | 82   |

|   |      | 3.10.4   | ITLB data array                                                                   | 84   |

|   | 3.11 | Privileg | ged mapping buffer (PMB)                                                          | 88   |

|   |      | 3.11.1   | PMB operations                                                                    | 89   |

|   |      | 3.11.2   | PMB address array                                                                 | 89   |

|   |      | 3.11.3   | PMB data array                                                                    | 91   |

|   | 3.12 | Handlir  | ng MMU exceptions                                                                 | 94   |

|   |      | 3.12.1   | ITLBMULTIHIT                                                                      | 95   |

|   |      | 3.12.2   | ITLBMISS                                                                          | 95   |

|   |      | 3.12.3   | EXECPROT                                                                          | 96   |

|   |      | 3.12.4   | OTLBMULTIHIT                                                                      | 96   |

|   |      | 3.12.5   | WTLBMISS/RTLBMISS                                                                 | 96   |

|   |      | 3.12.6   | READPROT/WRITEPROT                                                                | 97   |

|   |      | 3.12.7   | FIRSTWRITE                                                                        | 97   |

|   | 3.13 | Interac  | tion of MMU and cache                                                             | 98   |

|   | 3.14 | Memor    | y coherency                                                                       | 99   |

|   |      | 3.14.1   | Coherency mechanisms on ST40-100, ST40-200, ST40-400 and ST40-500 series cores 99 |      |

|   |      | 3.14.2   | Coherency mechanisms on ST40-300 series cores                                     | 103  |

|   | 3.15 | MMU s    | state coherency                                                                   | 105  |

|   |      | 3.15.1   | Coherency requirements                                                            | 105  |

|   |      | 3.15.2   | Achieving coherency (ST40-100, ST40-200, ST40-400 and ST40-series cores) 106      | -500 |

|   |      | 3.15.3   | Achieving coherency (ST40-300 series cores)                                       | 106  |

|   | 3.16 | Side ef  | fects of instruction pre-fetch                                                    | 107  |

|   |      | 3.16.1   | Inline fetching near ends of memory regions                                       | 107  |

|   |      | 3.16.2   | Branches following exceptions                                                     | 108  |

| 4 | Cach | ies      |                                                                                   | 114  |

|   | 4.1  | Overvi   | ew                                                                                | 114  |

|   |      | 4.1.1    | Features                                                                          | 114  |

|   |      | 4.1.2    | Cache modes                                                                       | 114  |

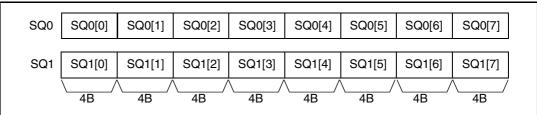

|   |      | 4.1.3    | Store queues                                                                      | 115  |

|   |      |          |                                                                                   |      |

| 4.2 | Regist   | ter descriptions                         | . 116 |

|-----|----------|------------------------------------------|-------|

|     | 4.2.1    | Cache control register (CCR)             | 116   |

|     | 4.2.2    | Queue address control register 0 (QACR0) | 119   |

|     | 4.2.3    | Queue address control register 1 (QACR1) | 120   |

|     | 4.2.4    | On-chip memory control register (RAMCR)  | 120   |

| 4.3 | Opera    | and cache (OC)                           | . 121 |

|     | 4.3.1    | Configuration                            | 121   |

|     | 4.3.2    | Read operation                           | 123   |

|     | 4.3.3    | Write operation                          | 124   |

|     | 4.3.4    | Write-back buffer                        | 125   |

|     | 4.3.5    | Write-through buffer                     | 125   |

|     | 4.3.6    | RAM mode                                 | 125   |

|     | 4.3.7    | OC index mode                            | 127   |

|     | 4.3.8    | Explicit cache controls                  | 127   |

| 4.4 | Instruc  | ction cache (IC)                         | . 128 |

|     | 4.4.1    | Configuration                            | 128   |

|     | 4.4.2    | Read operation                           | 129   |

|     | 4.4.3    | IC index mode                            | 130   |

|     | 4.4.4    | Explicit cache controls                  | 130   |

| 4.5 | Memo     | ory-mapped cache configuration           | . 131 |

|     | 4.5.1    | IC address array                         | 133   |

|     | 4.5.2    | IC data array                            | 135   |

|     | 4.5.3    | OC address array                         | 136   |

|     | 4.5.4    | OC data array                            | 138   |

| 4.6 | Store of | queues (SQs)                             | . 140 |

|     | 4.6.1    | Power-save functions                     | 141   |

|     | 4.6.2    | SQ configuration                         | 141   |

|     | 4.6.3    | SQ writes                                | 141   |

|     | 4.6.4    | SQ reads                                 | 142   |

|     | 4.6.5    | Transfer to external memory              | 142   |

|     | 4.6.6    | Physical address for external transfer   | 143   |

|     | 4.6.7    | Access rights for store queue operations | 144   |

| 4.7 | Cache    | e state coherency                        | . 145 |

| 5 | Exce | eptions |                                         | 146 |

|---|------|---------|-----------------------------------------|-----|

|   | 5.1  | Regist  | ter descriptions                        | 146 |

|   |      | 5.1.1   | Exception event register (EXPEVT)       | 146 |

|   |      | 5.1.2   | Interrupt event register (INTEVT)       | 147 |

|   |      | 5.1.3   | TRAPA exception register (TRA)          | 147 |

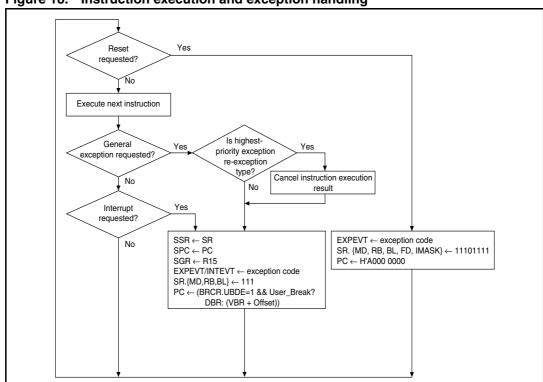

|   | 5.2  | Excep   | tion handling functions                 | 148 |

|   |      | 5.2.1   | Exception handling flow                 | 148 |

|   |      | 5.2.2   | Exception handling vector addresses     | 148 |

|   | 5.3  | Excep   | tion types and priorities               | 149 |

|   | 5.4  | Excep   | tion flow                               | 150 |

|   |      | 5.4.1   | Exception source acceptance             | 151 |

|   |      | 5.4.2   | Exception requests and BL bit           | 152 |

|   |      | 5.4.3   | Return from exception handling          | 153 |

|   | 5.5  | Descri  | iption of exceptions                    | 153 |

|   |      | 5.5.1   | Resets                                  | 153 |

|   |      | 5.5.2   | General exceptions                      | 156 |

|   |      | 5.5.3   | Interrupts                              | 159 |

|   |      | 5.5.4   | Priority order with multiple exceptions | 160 |

|   | 5.6  | Usage   | e notes                                 | 161 |

| 6 | Floa | ting-po | int unit                                | 163 |

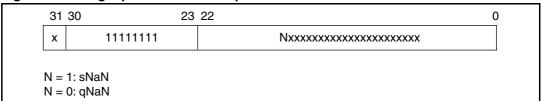

|   | 6.1  | Floatin | ng-point format                         | 163 |

|   |      | 6.1.1   | Non-numbers (NaN)                       | 165 |

|   |      | 6.1.2   | Denormalized numbers                    | 165 |

|   | 6.2  | Round   | ding                                    | 166 |

|   | 6.3  | Floatin | ng-point exceptions                     | 166 |

|   | 6.4  |         | ics support functions                   | 168 |

|   |      | 6.4.1   | Geometric operation instructions        |     |

|   | 6.5  |         | data transfer                           |     |

|   | 0.0  | 6.5.1   | Register-to-register transfers          |     |

|   |      | 6.5.2   | Memory transfers                        |     |

|   |      |         | ,                                       |     |

| 7 | Instr | uction  | set                            | . 172 |

|---|-------|---------|--------------------------------|-------|

|   | 7.1   | Execu   | tion environment               | . 172 |

|   | 7.2   | Addre   | ssing modes                    | . 173 |

|   | 7.3   | Instruc | ction set summary              | . 177 |

| 8 | Instr | uction  | specification                  | . 189 |

|   | 8.1   | Variab  | les and types                  | . 189 |

|   |       | 8.1.1   | Integer                        | 189   |

|   |       | 8.1.2   | Boolean                        | 190   |

|   |       | 8.1.3   | Bit-fields                     | 190   |

|   |       | 8.1.4   | Arrays                         | 190   |

|   |       | 8.1.5   | Floating point values          | 190   |

|   | 8.2   | Expres  | ssions                         | . 191 |

|   |       | 8.2.1   | Integer arithmetic operators   | 191   |

|   |       | 8.2.2   | Integer shift operators        | 192   |

|   |       | 8.2.3   | Integer bitwise operators      | 192   |

|   |       | 8.2.4   | Relational operators           | 193   |

|   |       | 8.2.5   | Boolean operators              | 193   |

|   |       | 8.2.6   | Single-value functions         | 194   |

|   | 8.3   | Staten  | nents                          | . 196 |

|   |       | 8.3.1   | Undefined behavior             | 196   |

|   |       | 8.3.2   | Assignment                     | 196   |

|   |       | 8.3.3   | Conditional                    | 197   |

|   |       | 8.3.4   | Repetition                     | 197   |

|   |       | 8.3.5   | Exceptions                     | 198   |

|   |       | 8.3.6   | Procedures                     | 198   |

|   | 8.4   | Archite | ectural state                  | . 199 |

|   | 8.5   | Memo    | ry model                       | . 200 |

|   |       | 8.5.1   | Support functions              |       |

|   |       | 8.5.2   | Instruction fetch              |       |

|   |       | 8.5.3   | Reading memory                 | 202   |

|   |       | 8.5.4   | Prefetching memory             |       |

|   |       | 8.5.5   | Writing memory                 |       |

|   | 8.6   | Sleep   | and synchronization operations |       |

|   | 8.7   | •       | model                          |       |

|   |       |         |                                |       |

|    | 8.8   | Floating | g-point model                               | 206 |

|----|-------|----------|---------------------------------------------|-----|

|    |       | 8.8.1    | Functions to access SR and FPSCR            |     |

|    |       | 8.8.2    | Functions to model floating-point behavior  |     |

|    |       | 8.8.3    | Floating-point special cases and exceptions |     |

|    | 8.9   | Abstrac  | ct sequential model                         | 209 |

|    | 8.10  |          | le instructions                             |     |

|    |       | 8.10.1   | ADD #imm, Rn                                |     |

|    |       | 8.10.2   | FADD FRm, FRn                               |     |

| 9  | Instr | uction c | descriptions                                | 213 |

|    | 9.1   |          | etical list of instructions                 |     |

| 10 | ST40  | -100, 20 | 00, 400, 500 performance characteristics    | 474 |

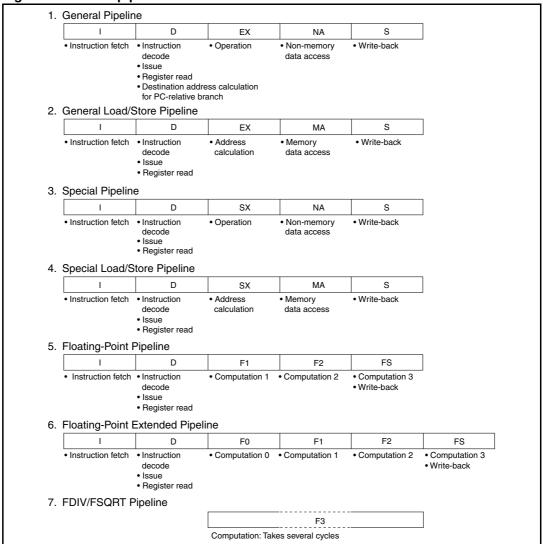

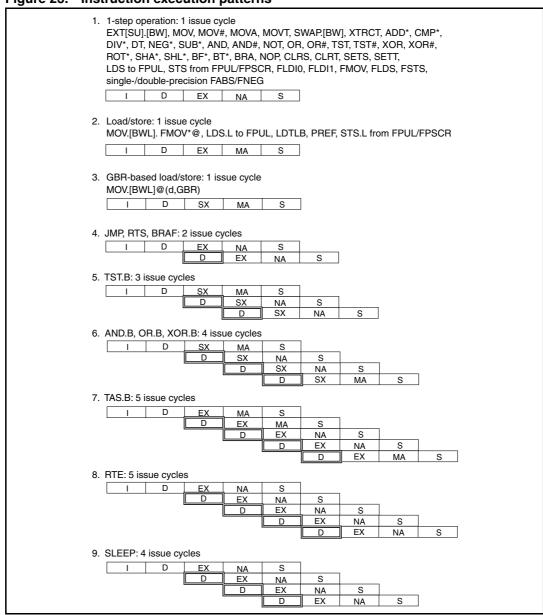

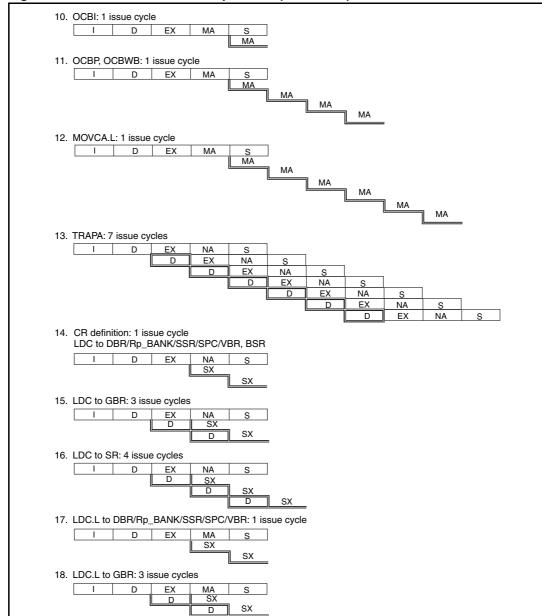

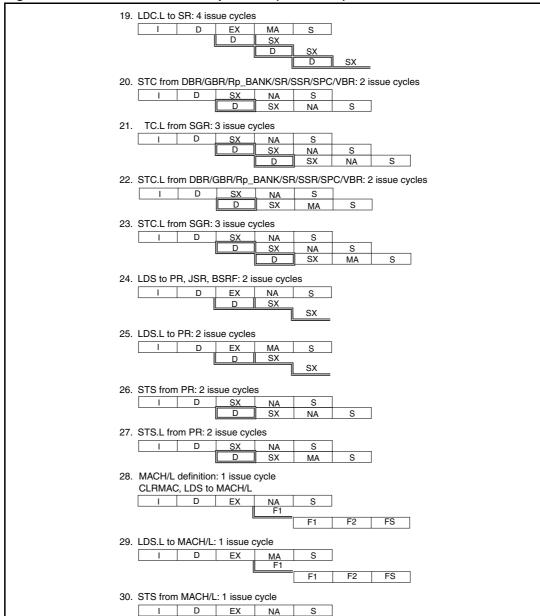

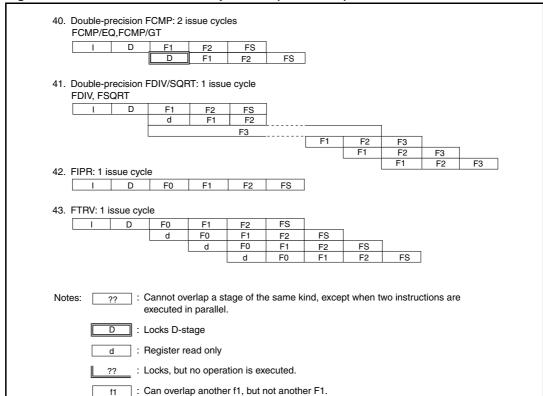

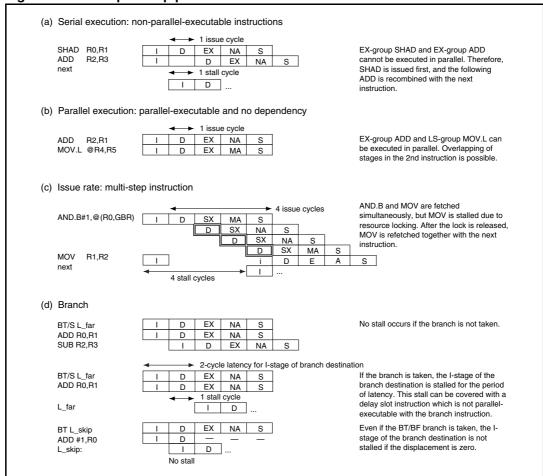

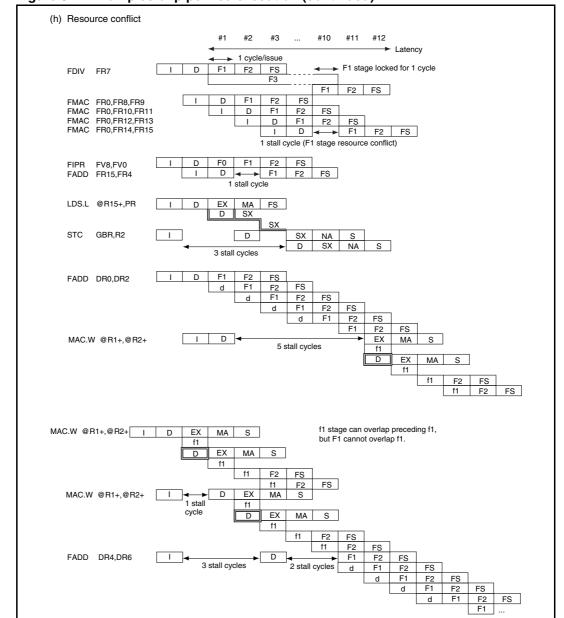

|    | 10.1  | Pipeline | es                                          | 474 |

|    | 10.2  | Parallel | l executables                               | 479 |

|    | 10.3  |          | ion cycles and pipeline stalling            |     |

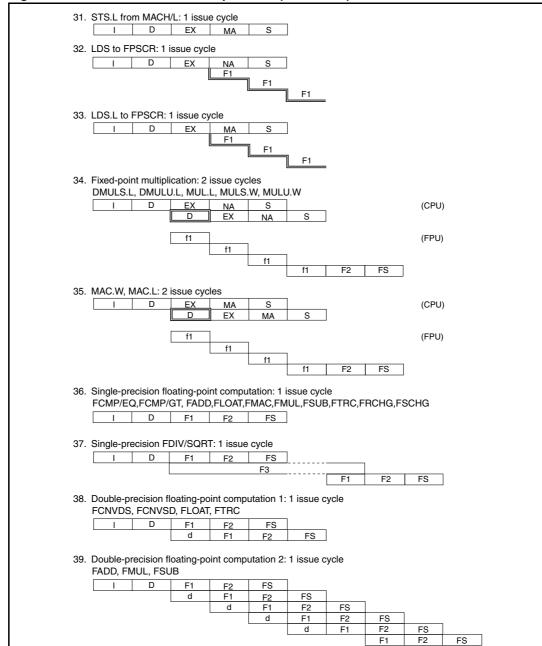

| 11 | ST40  | -300 pe  | erformance characteristics                  | 497 |

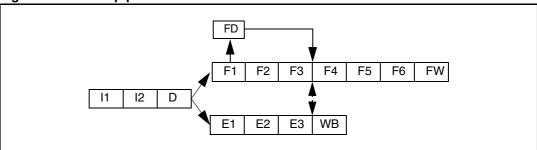

|    | 11.1  |          | oipeline structure                          |     |

|    | 11.2  | Issue c  | constraints                                 | 498 |

|    | 11.3  |          | tion performance characteristics            |     |

|    |       | 11.3.1   | Integer instructions                        |     |

|    |       | 11.3.2   | Floating point instructions                 |     |

|    |       | 11.3.3   | Branching scenarios                         | 508 |

| 12 | User  | break o  | controller (UBC)                            | 510 |

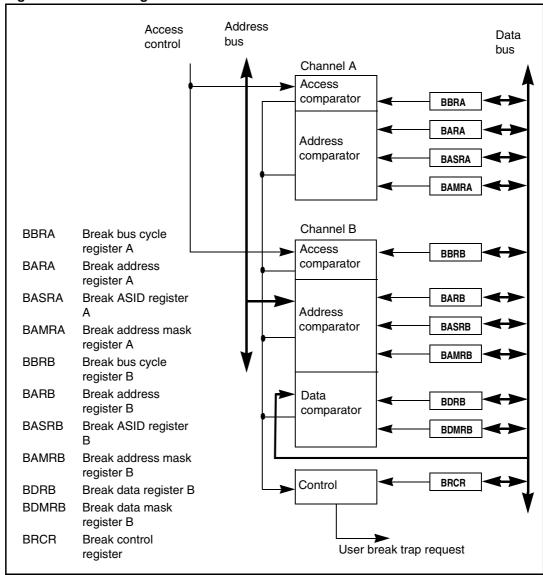

|    | 12.1  | Overvie  | ew                                          | 510 |

|    |       | 12.1.1   | Features                                    | 510 |

|    |       | 12.1.2   | Block diagram                               | 511 |

|    | 12.2  | Registe  | er overview                                 | 512 |

|    | 12.3  | Registe  | er descriptions                             | 513 |

|    |       | 12.3.1   | Access to UBC control registers             | 513 |

|    |       | 12.3.2   | Break address register A (UBC.BARA)         | 513 |

|    |       | 12.3.3   | Break ASID register A (UBC.BASRA)           | 514 |

|    |       | 12.3.4   | Break address mask register A (UBC.BAMRA)   | 514 |

|    |       | 12.3.5   | Break bus cycle register A (UBC.BBRA)       | 516 |

|    |       |          |                                             |     |

|               | 12.3.6    | Break address register B (UBC.BARB)                    | 517 |

|---------------|-----------|--------------------------------------------------------|-----|

|               | 12.3.7    | Break ASID register B (UBC.BASRB)                      | 517 |

|               | 12.3.8    | Break address mask register B (UBC.BAMRB)              | 517 |

|               | 12.3.9    | Break data register B (UBC.BDRB)                       | 517 |

|               | 12.3.10   | Break data mask register B (UBC.BDMRB)                 | 518 |

|               | 12.3.11   | Break bus cycle register B (UBC.BBRB)                  | 518 |

|               | 12.3.12   | Break control register (UBC.BRCR)                      | 518 |

| 12.4          | 4 Operati | on                                                     | 520 |

|               | 12.4.1    | Explanation of terms relating to accesses              | 520 |

|               | 12.4.2    | Explanation of terms relating to instruction intervals | 521 |

|               | 12.4.3    | User break operation sequence                          | 521 |

|               | 12.4.4    | Instruction access cycle break                         | 522 |

|               | 12.4.5    | Operand access cycle break                             | 523 |

|               | 12.4.6    | Condition match flag setting                           | 524 |

|               | 12.4.7    | Program counter (PC) value saved                       | 525 |

|               | 12.4.8    | Contiguous A and B settings for sequential conditions  | 526 |

| 12.5          | 5 Usage   | notes                                                  | 527 |

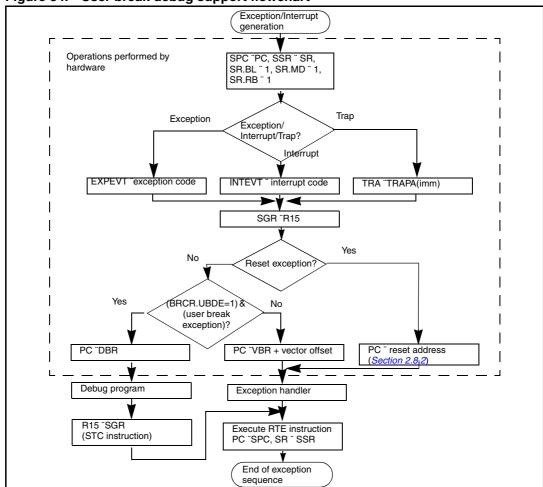

| 12.6          | 6 User br | eak debug function                                     | 529 |

| 12.7          | 7 Exampl  | les of use                                             | 530 |

|               | 12.7.1    | Instruction access cycle break condition settings      | 530 |

|               | 12.7.2    | Operand access cycle break condition settings          | 533 |

|               | 12.7.3    | User break controller stop function                    | 534 |

| Appendix A    | Address   | list                                                   | 535 |

| Revision hist | ory       |                                                        | 536 |

Preface ST40 core

# **Preface**

Comments on this manual should be made by contacting your local STMicroelectronics sales office or distributor.

#### Document identification and control

Each book carries a unique identifier of the form:

nnnnnnn Rev x

where *nnnnnn* is the document number, and *x* is the revision.

Whenever making comments on this document, quote the complete identification nnnnnn Rev x.

### ST40 documentation suite

The ST40 documentation suite comprises the following volumes:

#### 32-Bit RISC Series, ST40 Core Architecture Manual (7182230)

This manual describes the architecture and instruction set of the ST40 (previously known as ST40-C200) core as used by STMicroelectronics.

#### ST40 Core Support Peripherals Manual (7988763)

This manual provides details of the architecture of the ST40 core support peripherals which include: *Clock, power and reset control (CPRC), Real-time clock (RTC), Timer unit (TMU), Serial comms interface with FIFO (SCIF)*, and the *Interrupt controller (INTC)*.

The manual also describes the peripheral bridge that acts as the interface between the peripherals and the STBus. This is achieved by grouping the modules into a single port on the STBus, and handling any data size, data rate and endianness issues transparently.

#### ST40-300 Core Support Peripherals Manual (8011247)

This manual provides details on the architecture of the ST40-300 core support peripherals which includes: *Clock, power and reset control (CPRC), Timer unit (TMU), User debug interface (UDI)* and the *Interrupt controller (INTC)*.

This manual also describes the peripheral bridge that acts as the interface between the peripherals and the STBus.

#### ST40 Micro Toolset User Guide (7379953)

This manual describes the ST40 Micro Toolset and provides an introduction to OS21. It covers the various code and cross development tools that are provided in the toolset, how to boot OS21 applications from ROM and how to port applications which use STMicroelectronics' OS20 operating systems. Information is also given on how to build the open source packages that provide the compiler tools, base run-time libraries and debug tools and how to set up an ST Micro Connect.

ST40 core Preface

## **OS21 User Manual (7358306)**

This manual describes the generic use of OS21 across the supported platforms. It describes all the core features of OS21 and their use and details the OS21 function definitions. It also explains how OS21 differs from OS20, the API targeted at ST20 platforms.

# **OS21 for ST40 User Manual (7358673)**

This manual describes the use of OS21 on ST40 platforms. It describes how specific ST40 facilities are exploited by the OS21 API. It also describes the OS21 board support packages for ST40 platforms.

# Conventions used in this guide

#### **General notation**

The notation in this document uses the following conventions:

- sample code, keyboard input and file names,

- variables, code variables and code comments,

- equations and math,

- screens, windows, dialog boxes and tool names,

- instructions.

#### **Hardware notation**

The following conventions are used for hardware notation:

- REGISTER NAMES and FIELD NAMES,

- PIN NAMES and SIGNAL NAMES.

Overview ST40 core

# 1 Overview

This chapter provides an overview of the ST40.

### 1.1 ST40 core features

This manual describes the architecture of the ST40 core. The core is a highly encapsulated design component that can be integrated into any product. There are therefore no references to clock speeds, system facilities, pin-outs or similar data in this manual. This information is contained in the product's *Datasheet*, *System Architecture Manual* or *Core Support Package Architecture Manual* (where applicable).

Table 1 summarizes the differences between each series.

| Table 1. | Summary of differen | ences betwe | en ST40 pro | duct series |

|----------|---------------------|-------------|-------------|-------------|

|          |                     |             |             |             |

| Series | Cache associativity    | FPU      | MMU | 32-bit physical addressing | Examples |

|--------|------------------------|----------|-----|----------------------------|----------|

| 100    | Direct-mapped          | Yes      | Yes | No                         | ST40-103 |

| 200    | Two-way <sup>(1)</sup> | Yes      | Yes | Some <sup>(2)</sup>        | ST40-202 |

| 300    | Two-way <sup>(3)</sup> | Optional | Yes | Yes                        | ST40-300 |

| 400    | Two-way                | No       | No  | No                         | ST40-400 |

| 500    | Two-way                | No       | Yes | Yes                        |          |

The ST40-202 includes a compatibility mode which halves the sizes of the caches and causes them to operate with direct-mapped associativity.

Most soft core products support configurable cache sizes (in the range 4 Kbytes to 64 Kbytes, with it being possible to set the sizes of the instruction and operand independently). Refer to the product datasheet for further details.

Some differences are specific to particular products. For example, the ST40-202 has a fixed cache configuration (a 16 Kbyte 2-way instruction cache and a 32 Kbyte 2-way operand cache) and has a compatibility mode that causes it to behave as a 16 Kbyte direct mapped operand cache and an 8 Kbyte direct mapped instruction cache (as found in the ST40-103). All such product-specific architectural features are described in this document, and the different variants to which they apply are clearly indicated.

<sup>2.</sup> Depends on how the ST40-202 has been integrated into the specific product.

<sup>3.</sup> Extra option to use four-way on later implementations.

ST40 core Overview

The features of the ST40 CPU core are summarized in the following list.

#### **CPU**

- Original Renesas architecture

- 32-bit internal data bus

- General register file:

- sixteen 32-bit general registers (and eight 32-bit shadow registers)

- seven 32-bit control registers

- four 32-bit system registers

- RISC-type instruction set

- fixed 16-bit instruction length for improved code efficiency

- load-store architecture

- delayed branch instructions

- conditional execution

- Superscalar architecture: parallel execution of two instructions

- Instruction execution time: maximum 2 instructions/cycle

- On-chip multiplier

- Five-stage pipeline (100, 200, 400 and 500 series)

- Seven-stage pipeline (300 series)

- Branch target cache for bubble-free branching along predicted path (300 series)

Overview ST40 core

### **FPU** (if present)

- On-chip floating-point co-processor

- Supports single-precision (32 bits) and double-precision (64 bits)

- Supports IEEE754-compliant data types and exceptions

- Two rounding modes: round to nearest and round to zero

- Handling of denormalized numbers: truncation to zero or interrupt generation for compliance with IEEE754

- Floating-point registers:

- 2 banks of sixteen 32-bit single precision registers or

- 2 banks of eight 64-bit double precision registers or

- 2 banks of four 128-bit vector registers (each vector is 4 single precision elements)

- 32-bit CPU-FPU floating-point communication register (FPUL)

- Supports FMAC (multiply-and-accumulate) instruction

- Supports FDIV (divide) and FSQRT (square root) instructions

- Supports FLDI0/FLDI1 (load constant 0/1) instructions

- Instruction execution times (100 and 200 series):

- latency (FMAC/FADD/FSUB/FMUL): 3 cycles (single-precision), 8 cycles (double-precision)

- pitch (FMAC/FADD/FSUB/FMUL): 1 cycle (single-precision), 6 cycles (double-precision)

- Instruction execution times (300 series):

- FMAC/FADD/FSUB: 1 cycle pitch, 6 cycles latency (single and double precision)

- FMUL (single precision): 1 cycle pitch, 6 cycles latency

- FMUL (double precision): 4 cycles pitch, 10 cycles latency

#### Note: FMAC is supported for single-precision only.

- 3-D graphics instructions (single-precision only):

- 4-dimensional vector conversion and matrix operations (FTRV):

- 4 cycles (pitch), 7 cycles (latency) (100 and 200 series)

- 4 cycles (pitch), 10 cycles (latency) (300 series)

- 4-dimensional vector (FIPR) inner product:

- 1 cycle (pitch), 4 cycles (latency) (100 and 200 series)

- 1 cycle (pitch), 6 cycles (latency) (300 series)

- Five-stage pipeline (100 and 200 series)

- Ten-stage pipeline (300 series)

- Single-precision polynomial approximations to sine, cosine and reciprocal square root

#### Power-down

- Power-down modes:

- sleep mode

- standby mode

- module standby function

ST40 core Overview

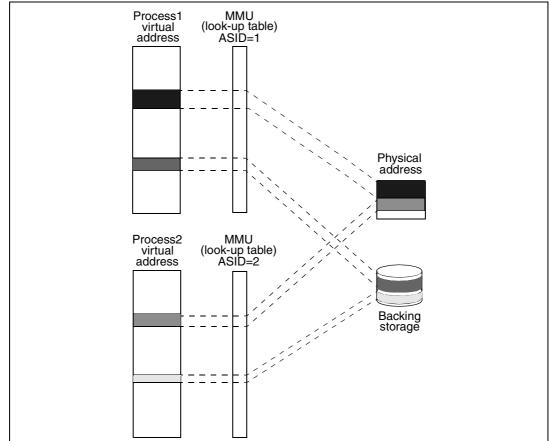

### MMU (if present)

- 4-Gbyte virtual address space, 256 address space identifiers (8-bit ASIDs)

- Single virtual mode and multiple virtual memory mode

- Supports multiple page sizes: 1 Kbyte, 4 Kbytes, 64 Kbytes, 1 Mbyte

- 4-entry fully-associative TLB for instructions

- 64-entry fully-associative TLB for instructions and operands

- Supports software-controlled replacement and random-counter replacement algorithm

- TLB contents can be accessed directly by address mapping

- 29-bit physical addressing (all series)

- 32-bit physical addressing (200, 300 and 500 series)

### **Cache memory**

#### ST40-103

- Instruction cache (IC) features:

- 8 Kbytes, direct mapping

- 256 entries, 32-byte block length

- normal mode (8 Kbyte cache)

- index mode

- Operand cache (OC) features:

- 16 Kbytes, direct mapping

- 512 entries, 32-byte block length

- normal mode (16 Kbyte cache)

- index mode

- RAM mode (8 Kbyte cache + 8 Kbyte RAM)

- choice of write method (copy-back or write-through)

- Single-stage copy-back buffer, single-stage write-through buffer

- Cache memory contents can be accessed directly by address mapping (usable as on-chip memory)

- Store queue (32 bytes x 2 entries)

Overview ST40 core

#### ST40-202

- Instruction cache (IC) features:

- 16 Kbyte, 2-way set associative

- 512 entries, 32-bytes block length

- compatibility mode (8 Kbyte direct mapped)

- index mode

- Operand cache (OC) features:

- 32 Kbyte, 2-way set associative

- 1024 entries, 32 bytes block length

- compatibility mode (16 Kbyte direct mapped)

- index mode

- RAM mode (16 Kbyte cache + 16 Kbyte RAM)

- Single-stage copy-back buffer, single-stage write-through buffer

- Cache memory contents can be accessed directly by address.

mapping (usable as on-chip memory)

- Store queue (32 bytes x 2 entries).

Note:

On the ST40-202 the state of the cache becomes undefined if the OC index mode and OC RAM mode are used together.

#### ST40-200 series (other than the ST40-202), ST40-400 and ST40-500 series

- Instruction cache (IC) features:

- 4, 8, 16, 32 or 64 Kbyte, 2-way set associative cache

- 32 bytes block length

- no compatibility or index mode support

- Operand cache (OC) features:

- 4, 8, 16, 32 or 64 Kbyte, 2-way set associative cache

- 32 bytes block length

- no compatibility mode or index mode support

- RAM mode (half of each way can be reassigned as RAM)

- Single-stage copy-back buffer, single-stage write-through buffer

- Cache memory contents can be accessed directly by address mapping (usable as on-chip memory)

- Store queue (32 bytes x 2 entries)

ST40 core Overview

#### ST40-300 series

- Instruction cache (IC) features:

- 4, 8, 16, 32, 64 or 128 Kbyte, 2-way set associative cache

- option to use 4-way associativity on a future implementation

- 32 bytes block length

- no compatibility or index mode support

- Operand cache (OC) features:

- 4, 8, 16, 32, 64 or 128 Kbyte, 2-way set associative cache

- option to use 4-way associativity on a future implementation

- 32 bytes block length

- no compatibility mode, index mode or RAM mode support

- 8-stage memory store/writeback buffer

- Up to 6 outstanding operand prefetches

- Store queue (32bytes x 2 entries)

# 1.2 Block diagram

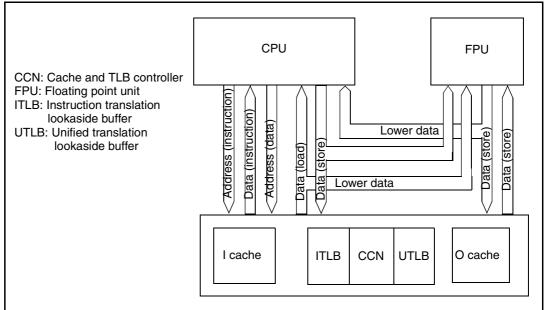

Figure 1 shows an internal block diagram of the ST40 32-bit CPU core.

Figure 1. ST40 32-bit CPU core

# 2 Programming model

The ST40 CPU core has two processor modes, user mode and privileged mode. The ST40 normally operates in user mode, and switches to privileged mode when an exception occurs, or an interrupt is accepted.

There are four kinds of registers.

General registers

There are 16 general registers, R0 to R15. General registers R0 to R7 are banked registers which are switched by a processor mode change.

System registers

Access to these registers does not depend on the processor mode

- Control registers

- Floating-point registers (only present in products with an FPU)

There are thirty two floating point registers, EPO, EP15 and VEO, VE15.

There are thirty two floating point registers.

There are thirty-two floating-point registers, FR0–FR15 and XF0–XF15. FR0–FR15 and XF0–XF15 can be assigned to either of two banks (FPR0\_BANK0–FPR15\_BANK0 or FPR0\_BANK1–FPR15\_BANK1).

The registers that can be accessed differ in the two processor modes.

Register values after a reset are shown in Table 2.

Table 2. Initial register values

| Type Registers           |                                                    | Reset value <sup>(1)</sup>                                                                                 |

|--------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| General registers        | R0_BANK0-R7_BANK0,<br>R0_BANK1-R7_BANK1,<br>R8-R15 | Undefined                                                                                                  |

| Ocated assistant         | SR                                                 | MD=1, RB=1, BL=1, I3-I0=0xF<br>FD=0 - ST40 FPU family), 1 - otherwise<br>reserved bits=0, others undefined |

| Control registers        | GBR, SSR, SPC, SGR,<br>DBR                         | Undefined                                                                                                  |

|                          | VBR                                                | 0x0000 0000                                                                                                |

| System registers         | MACH, MACL, PR, FPUL                               | Undefined                                                                                                  |

| System registers         | PC                                                 | See Section 2.8.2: Reset address on page 29                                                                |

| Floating-point registers | FR0-FR15, XF0-XF15                                 | Undefined                                                                                                  |

| (only if FPU present)    | FPSCR                                              | 0x0004 0001                                                                                                |

<sup>1.</sup> Initial value after power-on or manual reset.

ST40 core Programming model

# 2.1 General registers

Figure 2 shows the relationship between the processor modes and the general registers. The ST40 CPU core has twenty-four 32-bit general registers (R0\_BANK0-R7\_BANK0, R0\_BANK1-R7\_BANK1, and R8-R15). However, only 16 of these can be accessed as general registers, R0-R15, in either processor mode. The assignment of R0-R7, in both modes, is shown below.

- R0\_BANK0-R7\_BANK0:

- in user mode (SR.MD = 0), R0–R7 are always assigned to R0\_BANK0– R7\_BANK0

- in privileged mode (SR.MD = 1), R0–R7 are assigned to R0\_BANK0–R7\_BANK0 only when SR.RB = 0

- R0\_BANK1-R7\_BANK1:

- in user mode, R0\_BANK1-R7\_BANK1 cannot be accessed

- in privileged mode, R0–R7 are assigned to R0\_BANK1–R7\_BANK1 only when SR.RB = 1

Figure 2. General registers

| rigure 2. General registers | ,        |                        |

|-----------------------------|----------|------------------------|

| SR.MD = 0 or                |          | (OD MD                 |

| (SR.MD = 1, SR.RB = 0)      |          | (SR.MD = 1, SR.RB = 1) |

| R0                          | R0_BANK0 | R0_BANK                |

| R1                          | R1_BANK0 | R1_BANK                |

| R2                          | R2_BANK0 | R2_BANK                |

| R3                          | R3_BANK0 | R3_BANK                |

| R4                          | R4_BANK0 | R4_BANK                |

| R5                          | R5_BANK0 | R5_BANK                |

| R6                          | R6_BANK0 | R6_BANK                |

| R7                          | R7_BANK0 | R7_BANK                |

| Do DANK!                    |          | _                      |

| R0_BANK                     | R0_BANK1 | R0                     |

| R1_BANK                     | R1_BANK1 | R1                     |

| R2_BANK                     | R2_BANK1 | R2                     |

| R3_BANK                     | R3_BANK1 | R3                     |

| R4_BANK                     | R4_BANK1 | R4                     |

| R5_BANK                     | R5_BANK1 | R5                     |

| R6_BANK                     | R6_BANK1 | R6                     |

| R7_BANK                     | R7_BANK1 | R7                     |

| Po l                        | R8       | 7 50                   |

| R8                          |          | R8                     |

| R9                          | R9       | R9                     |

| R10                         | R10      | R10                    |

| R11                         | R11      | R11                    |

| R12                         | R12      | R12                    |

| R13                         | R13      | R13                    |

| R14                         | R14      | R14                    |

| R15                         | R15      | R15                    |

## **Programming note**

As the user's R0–R7 are assigned to R0\_BANK0–R7\_BANK0, and after an exception or interrupt R0–R7 are assigned to R0\_BANK1–R7\_BANK1, it is not necessary for the interrupt handler to save and restore the user's R0–R7 (R0\_BANK0–R7\_BANK0).

After a reset, the values of R0\_BANK0-R7\_BANK0, R0\_BANK1-R7\_BANK1, and R8-R15 are undefined.

# 2.2 System registers

Table 3. System registers

| Name           | Size   | Reset value <sup>(1)</sup> | Synopsis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|----------------|--------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                | 32     | Undefined                  | Multiply-and-accumulate register high.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| MACH           | Operat | ion                        | MACH is used for the added value in a MAC instruction, and to store a MAC instruction or MUL instruction operation result.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                | 32     | Undefined                  | Multiply-and-accumulate register low.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| MACL           | Operat | ion                        | MACL is used for the added value in a MAC instruction, and to store a MAC instruction or MUL instruction operation result.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                | 32     | Undefined                  | Procedure register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| PR             | Operat | ion                        | The return address is stored when a subroutine call using a BSR, BSRF or JSR instruction. PR is referenced by the subroutine return instruction (RTS).                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| PC             | 32     | See Section 2.8.2          | Program counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                | Operat | ion                        | PC indicates the executing instruction address.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                | 32     | 0x0004 0001                | Floating-point status/control register.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| FPSCR          | Operat | ion                        | Refer to <i>Table 4: FPSCR register description</i> . This register is only present in products with an FPU.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                | 32     | Undefined                  | Floating-point communication register.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| FPUL Operation |        | ion                        | Data transfer between FPU registers and CPU registers is carried out via the FPUL register. The FPUL register is a system register, and is accessed from the CPU side by means of LDS and STS instructions. For example, to convert the integer stored in general register R1 to a single-precision floating-point number, the processing flow is as follows:  R1 —(LDS instruction) —FPUL —(single-precision FLOAT instruction) —FR1  This register is only present in products with an FPU. |  |  |  |  |

<sup>1.</sup> Initial value after power-on or manual reset.

Table 4. FPSCR register description<sup>(1)</sup>

| FPSCR                  |           |      |                                                                                                     |           |  |  |  |

|------------------------|-----------|------|-----------------------------------------------------------------------------------------------------|-----------|--|--|--|

| Field                  | Bits      | Size | Synopsis                                                                                            | Туре      |  |  |  |

|                        | 0         | 1    | Rounding mode.                                                                                      | RW        |  |  |  |

| RM                     | Operation |      | RM = 0: round to nearest, RM = 1: round to zero. For details see Section 6.2: Rounding on page 166. |           |  |  |  |

|                        | Reset     |      | 1                                                                                                   |           |  |  |  |

|                        | 2         | 1    | FPU inexact exception flag.                                                                         | RW        |  |  |  |

| Flag inexact           | Operation |      | Set to 1 if Inexact exception occurs.                                                               |           |  |  |  |

|                        | Reset     |      | 0                                                                                                   |           |  |  |  |

|                        | 3         | 1    | FPU underflow exception flag.                                                                       | RW        |  |  |  |

| Flag underflow         | Operation |      | Set to 1 if Underflow exception occurs.                                                             |           |  |  |  |

|                        | Reset     |      | 0                                                                                                   |           |  |  |  |

|                        | 4         | 1    | FPU overflow exception flag.                                                                        | RW        |  |  |  |

| Flag overflow          | Operation |      | Set to 1 if overflow exception occurs.                                                              |           |  |  |  |

|                        | Reset     |      | 0                                                                                                   |           |  |  |  |

|                        | 5         | 1    | FPU division by zero exception flag.                                                                | RW        |  |  |  |

| Flag division by zero  | Operation |      | Set to 1 if division by zero exception occurs.                                                      |           |  |  |  |

|                        | Reset     |      | 0                                                                                                   |           |  |  |  |

|                        | 6         | 1    | FPU invalid operation exception flag.                                                               | RW        |  |  |  |

| Flag invalid operation | Operation | •    | Set to 1 if Invalid operation exception occurs.                                                     |           |  |  |  |

| operation              | Reset     |      | 0                                                                                                   |           |  |  |  |

|                        | 7         | 1    | FPU invalid exception enable field.                                                                 | RW        |  |  |  |

| Enable inexact         | Operation |      | Set to 1 to cause a trap when an inexact exception occurs.                                          |           |  |  |  |

|                        | Reset     |      | 0                                                                                                   |           |  |  |  |

|                        | 8         | 1    | FPU underflow exception enable field.                                                               |           |  |  |  |

| Enable underflow       | Operation |      | Set to 1 to cause a trap when an underflow exception occurs.                                        |           |  |  |  |

|                        | Reset     |      | 0                                                                                                   |           |  |  |  |

|                        | 9         | 1    | FPU overflow exception enable field.                                                                | RW        |  |  |  |

| Enable overflow        | Operation |      | Set to 1 to cause a trap when an overflow e occurs.                                                 | exception |  |  |  |

|                        | Reset     |      | 0                                                                                                   |           |  |  |  |

Table 4. FPSCR register description<sup>(1)</sup> (continued)

| FPSCR                   |           |      |                                                                                                  |        |  |  |  |

|-------------------------|-----------|------|--------------------------------------------------------------------------------------------------|--------|--|--|--|

| Field                   | Bits      | Size | Synopsis                                                                                         | Туре   |  |  |  |

|                         | 10        | 1    | FPU division by zero exception enable field.                                                     | RW     |  |  |  |

| Enable division by zero | Operation |      | Set to 1 to cause a trap when a division by zero exception occurs.                               |        |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

|                         | 11        | 1    | FPU invalid exception enable field.                                                              | RW     |  |  |  |

| Enable invalid          | Operation |      | Set to 1 to cause a trap when an Invalid excooccurs.                                             | eption |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

|                         | 12        | 1    | FPU inexact exception cause field.                                                               | RW     |  |  |  |

| Cause inexact           | Operation |      | Set to 0 before an FPU instruction is executed. Set to 1 if an Inexact exception occurs.         |        |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

|                         | 13 1      |      | FPU underflow exception cause field.                                                             | RW     |  |  |  |

| Cause underflow         | Operation |      | Set to 0 before an FPU instruction is executed. Set to 1 if an underflow exception occurs.       |        |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

|                         | 14        | 1    | FPU overflow exception cause field.                                                              | RW     |  |  |  |

| Cause overflow          | Operation |      | Set to 0 before an FPU instruction is executed. Set to 1 if an overflow exception occurs.        |        |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

|                         | 15        | 1    | FPU division by zero exception cause field.                                                      | RW     |  |  |  |

| Cause division by zero  | Operation |      | Set to 0 before an FPU instruction is executed. Set to 1 if a division by zero exception occurs. |        |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

|                         | 16        | 1    | FPU invalid exception cause field.                                                               | RW     |  |  |  |

| Cause invalid           | Operation |      | Set to 0 before an FPU instruction is executed. Set to 1 if an invalid exception occurs.         |        |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

|                         | 17        | 1    | FPU error exception cause field.                                                                 |        |  |  |  |

| Cause FPU error         | Operation |      | Set to 0 before an FPU instruction is executed. Set to 1 if an FPU error exception occurs.       |        |  |  |  |

|                         | Reset     |      | 0                                                                                                |        |  |  |  |

Table 4. FPSCR register description<sup>(1)</sup> (continued)

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| node. RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| alized number is treated as such. alized number is treated as zero. : Denormalized numbers on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PR = 0: floating point instructions are executed as single precision operations.  PR = 1: floating point instructions are executed as double-precision operations (the result of instructions for which double-precision is not supported is undefined).  For 100- and 200- series cores, mode setting [SZ = 1, PR = 1] is reserved. FPU operation results are undefined in this mode.  For the 300- series core, mode setting [SZ=1, PR=1] is well defined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |