# RM0003 Reference manual

# STR750 ARM7TDMI-S®-based microcontroller family

### Introduction

This Reference Manual provides complete information for application developers on how to use the STR750 Microcontroller memory and peripherals.

The STR750 is a family of microcontrollers with different memory sizes, packages and peripherals.

For Ordering Information, Mechanical and Electrical Device Characteristics please refer to the STR750 Datasheet.

For information on programming, erasing and protection of the internal Flash memory please refer to the STR7 Flash Programming Reference Manual

For information on the ARM7TDMI-S core, please refer to the ARM7TDMI-S Technical Reference Manual.

### **Related documents**

Available from www.arm.com:

ARM7TDMI-S Rev. 4 Technical Reference Manual ARM DDI 0234A

Available from www.st.com:

STR750 Datasheet

STR7 Flash Programming Manual

# **Contents**

| 1 | Memo | ory and bus  | architecture                                            | 16   |

|---|------|--------------|---------------------------------------------------------|------|

|   | 1.1  | Multi-Layer  | AHB bus architecture                                    | 16   |

|   | 1.2  | Memory org   | anization                                               | 17   |

|   | 1.3  | Memory ma    | p                                                       | 18   |

|   |      | 1.3.1 Reg    | gister base addresses                                   | . 19 |

|   |      | 1.3.2 Peri   | pheral memory map                                       | . 19 |

|   |      | 1.3.3 Eml    | pedded SRAM                                             | . 21 |

|   |      | 1.3.4 Eml    | oedded Flash                                            | . 22 |

|   | 1.4  | Boot configu | ıration                                                 | 25   |

|   |      | 1.4.1 Eml    | oedded boot loader mode                                 | . 25 |

|   |      | 1.4.2 Exte   | ernal memory (SMI) boot mode                            | . 26 |

|   | 1.5  | Configuratio | n Register (CFG)                                        | 27   |

|   |      | 1.5.1 Glo    | bal Configuration Register (CFG_GLCONF)                 | . 27 |

|   |      | 1.5.2 CFC    | G Register map                                          | . 28 |

| 2 | Powe | r, Reset and | d Clocks                                                | 29   |

|   | 2.1  | Introduction |                                                         | 29   |

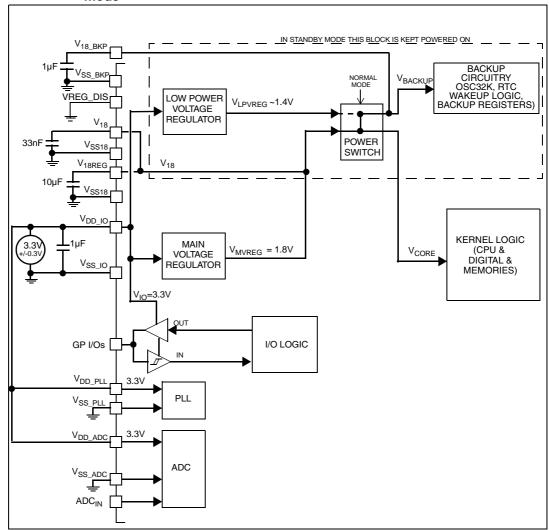

|   | 2.2  | Power suppl  | ies                                                     | 29   |

|   | 2.3  | Power suppl  | y schemes                                               | 30   |

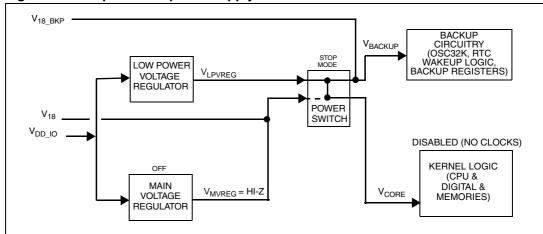

|   |      | 2.3.1 Pow    | ver scheme 1: Single external 3.3V power source         | . 30 |

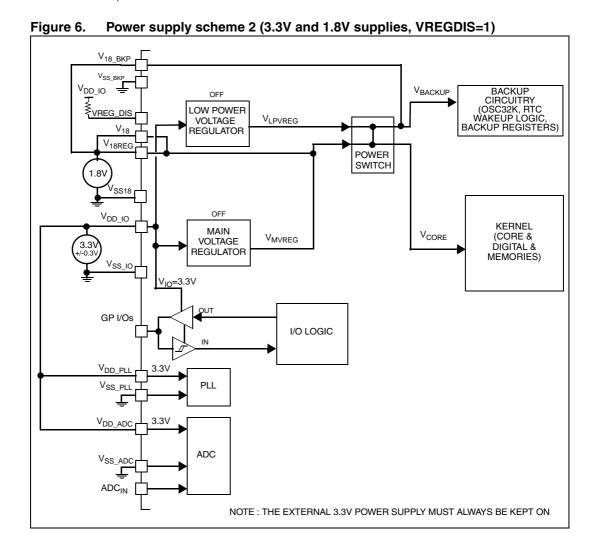

|   |      | 2.3.2 Pow    | ver scheme 2: dual external 3.3V and 1.8V power sources | . 32 |

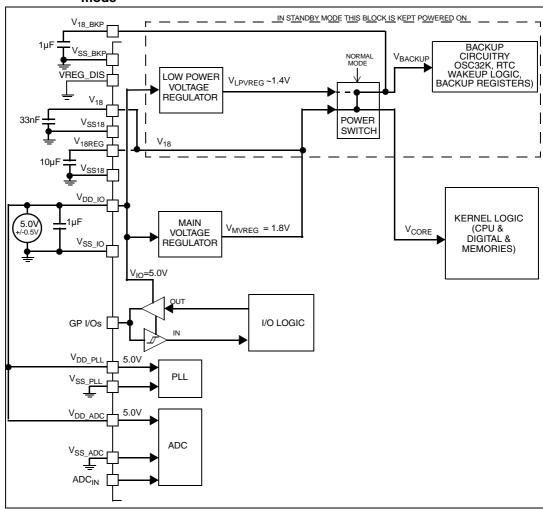

|   |      | 2.3.3 Pow    | ver scheme 3: single external 5.0V power source         | . 33 |

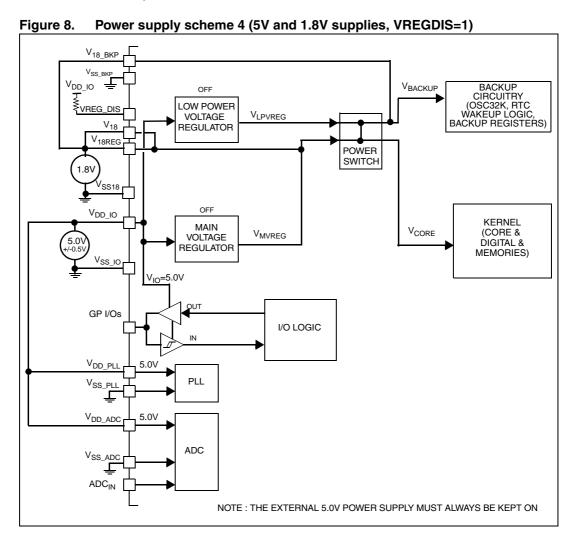

|   |      | 2.3.4 Pow    | ver scheme 4: dual external 5.0V and 1.8V power sources | . 34 |

|   | 2.4  | Main voltage | e regulator                                             | 35   |

|   | 2.5  | Low power v  | oltage regulator                                        | 35   |

|   | 2.6  | Regulator S  | tartup Monitor (RSM)                                    | 35   |

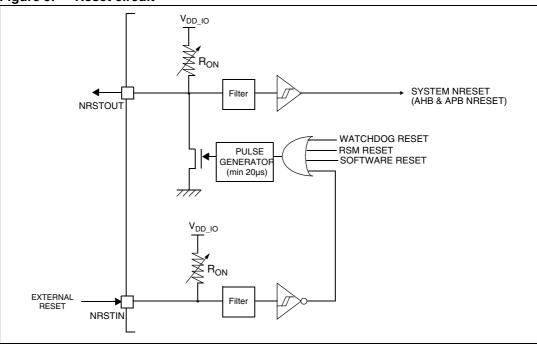

|   | 2.7  | Reset & pov  | ver startup                                             | 36   |

|   |      | •            | er Startup specifications                               |      |

|   |      | 2.7.2 Exte   | ernal Reset Input                                       | . 36 |

|   |      |              | SET sources                                             |      |

|   |      |              | tware Reset                                             |      |

|   |      | 2.7.5 Res    | etting peripherals individually                         | . 38 |

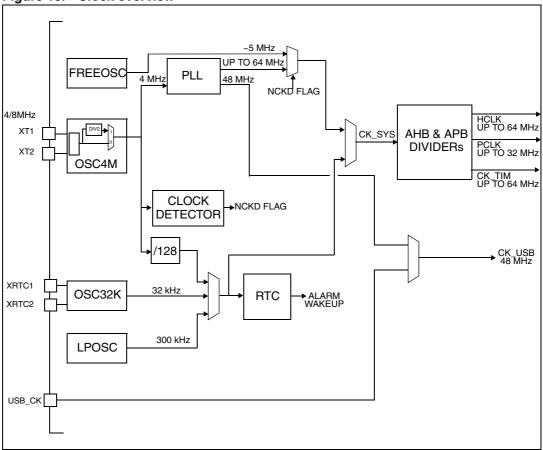

|   | 2.8  | Clocks       |                                                         | 39   |

|   |      |              |                                                         |      |

|      | 2.8.1    | Clock overview                                               |

|------|----------|--------------------------------------------------------------|

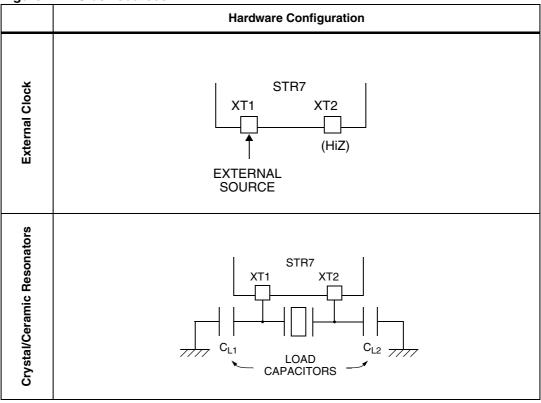

|      | 2.8.2    | Main 4MHz oscillator (OSC4M)                                 |

|      | 2.8.3    | Managing the Oscillator start-up time (builder counter) 42   |

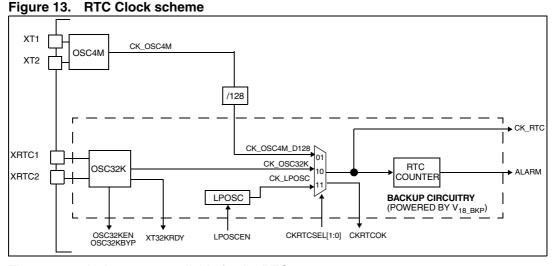

|      | 2.8.4    | RTC Clock Source (LPOSC, OSC32K)43                           |

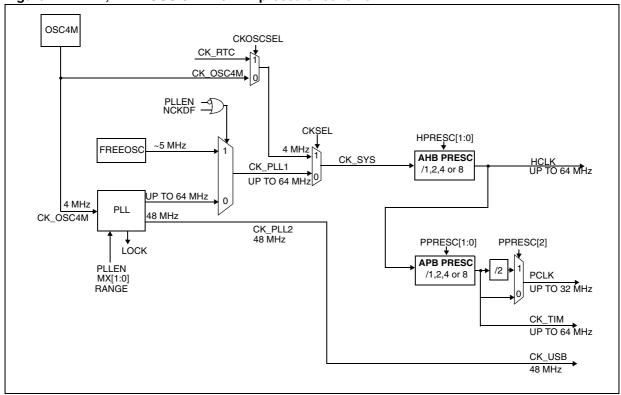

|      | 2.8.5    | PLL, FREEOSC, & AHB/APB prescalers                           |

|      | 2.8.6    | Clock-out capability: MCO (Main Clock Output)                |

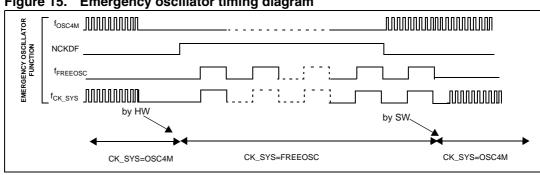

|      | 2.8.7    | Clock Detector (CKD)45                                       |

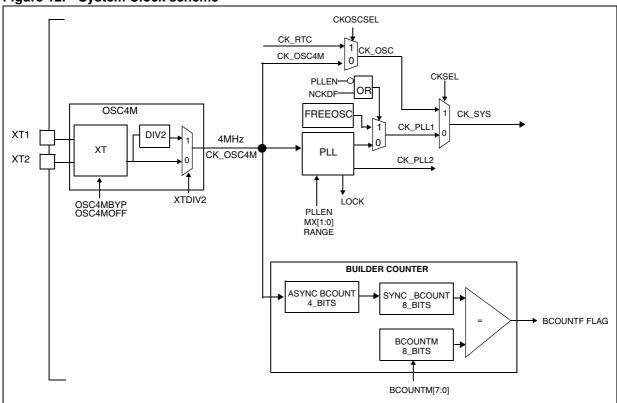

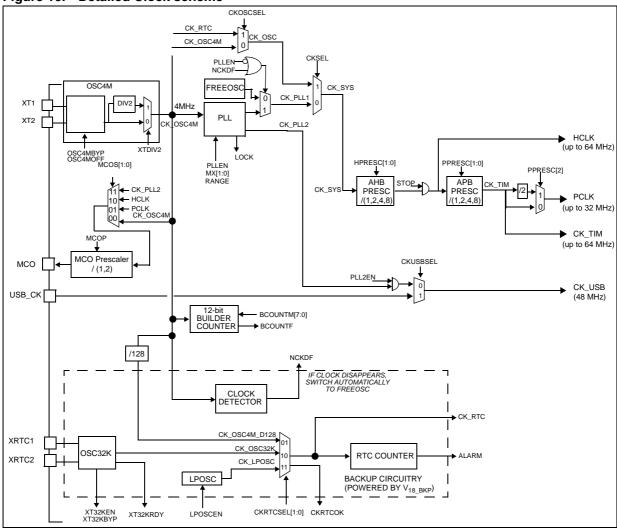

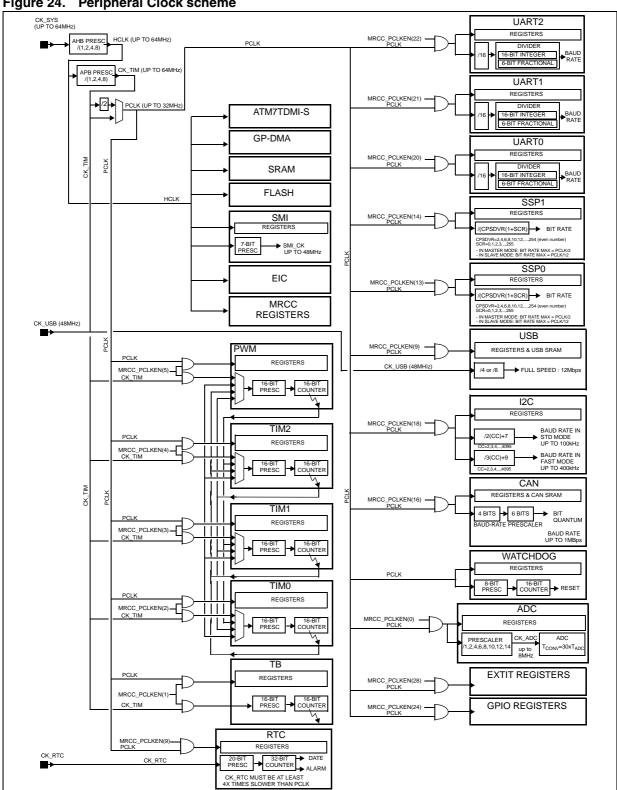

|      | 2.8.8    | Detailed Clock scheme47                                      |

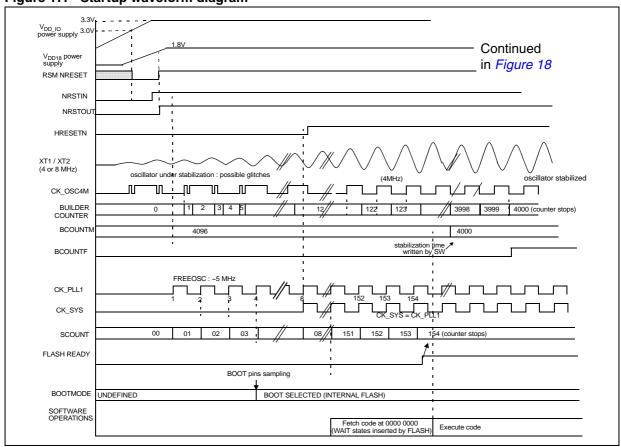

|      | 2.8.9    | System startup                                               |

|      | 2.8.10   | Clock state after Reset49                                    |

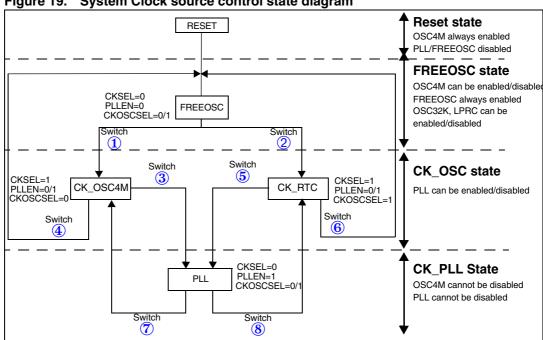

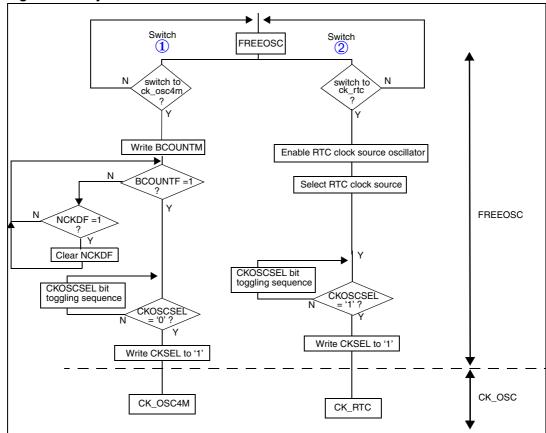

|      | 2.8.11   | Switching CK_SYS from FREEOSC to CK_OSC (CK_OSC4M or CK_RTC) |

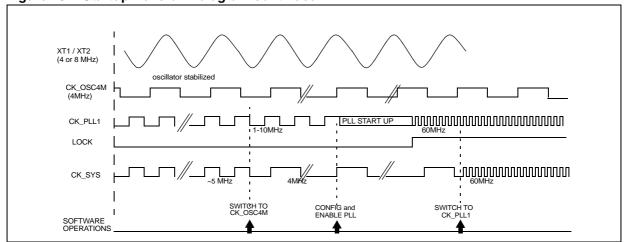

|      | 2.8.12   | Switching CK_SYS from CK_OSC4M to CK_PLL1 (PLL or FREEOSC)52 |

|      | 2.8.13   | Switching CK_SYS from CK_RTC to CK_PLL1 (PLL or FREEOSC) 53  |

|      | 2.8.14   | Switching the CK_SYS from PLL to CK_OSC (CK_OSC4M or CK_RTC) |

|      | 2.8.15   | Peripheral Clock scheme                                      |

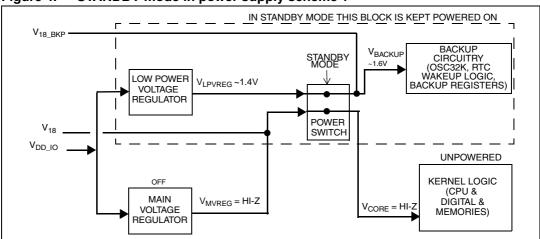

| 2.9  | Low Po   | wer modes 57                                                 |

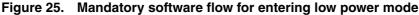

|      | 2.9.1    | Low Power Bit Writing sequence                               |

|      | 2.9.2    | SLOW mode                                                    |

|      | 2.9.3    | PCG mode: Peripherals Clocks Gated mode59                    |

|      | 2.9.4    | WFI mode: Wait For Interrupt mode59                          |

|      | 2.9.5    | STOP mode                                                    |

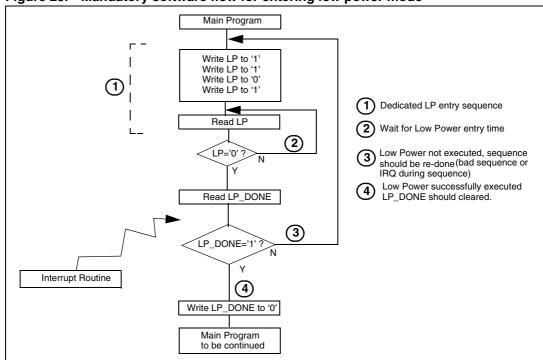

|      | 2.9.6    | STANDBY mode                                                 |

|      | 2.9.7    | Auto-Wake-Up (AWU) from Low Power mode 68                    |

|      | 2.9.8    | LPOSC oscillator calibration                                 |

| 2.10 | Registe  | er description                                               |

|      | 2.10.1   | Clock Control Register (MRCC_CLKCTL)                         |

|      | 2.10.2   | Reset Flag and Status register (MRCC_RFSR)                   |

|      | 2.10.3   | Power Management Control register (MRCC_PWRCTRL)76           |

|      | 2.10.4   | Peripheral Clock Enable register (MRCC_PCLKEN) 80            |

|      | 2.10.5   | Peripheral Software Reset register (MRCC_PSWRES)80           |

|      | 2.10.6   | Backup register 0 (MRCC_BKP0)                                |

|      | 2.10.7   | Backup register 1 (MRCC_BKP1)                                |

|      | 2.10.8   | MRCC Register map82                                          |

| Gene | eral Pur | pose I/O ports (GPIO)83                                      |

|      |          |                                                              |

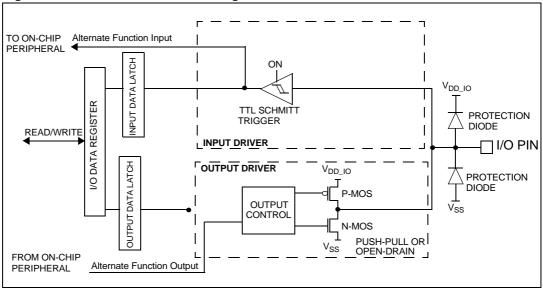

|   | 3.1    | Function | nal description                                         | 83  |

|---|--------|----------|---------------------------------------------------------|-----|

|   |        | 3.1.1    | General Purpose I/O (GPIO)                              | 84  |

|   |        | 3.1.2    | Atomic Bit Set or Bit Reset (Bit-wise write operations) | 85  |

|   |        | 3.1.3    | Alternate Functions (AF)                                | 85  |

|   |        | 3.1.4    | Alternate Functions table                               | 89  |

|   |        | 3.1.5    | External Interrupt / wake-up lines                      | 91  |

|   |        | 3.1.6    | Special case of WKP_STDBY pin (P1.15)                   | 91  |

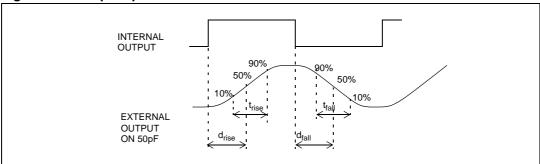

|   |        | 3.1.7    | Output drive & speed                                    | 91  |

|   |        | 3.1.8    | Configuring Outputs for 5V or 3.3V Supply               | 91  |

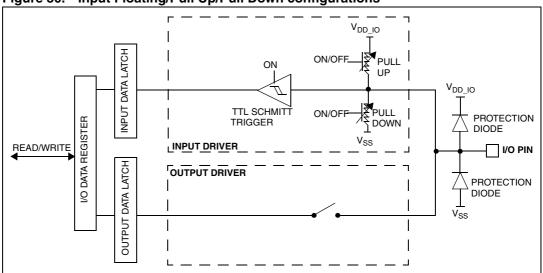

|   |        | 3.1.9    | Input configuration                                     | 92  |

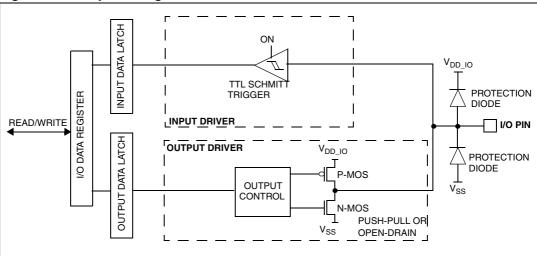

|   |        | 3.1.10   | Output configuration                                    | 92  |

|   |        | 3.1.11   | Alternate Function configuration                        | 93  |

|   |        | 3.1.12   | Analog Input configuration                              | 94  |

|   | 3.2    | Registe  | r description                                           | 95  |

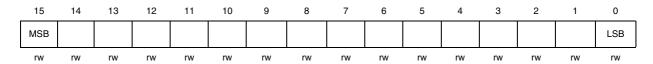

|   |        | 3.2.1    | Port Configuration Register 0 (GPIO_PxC0)               | 95  |

|   |        | 3.2.2    | Port Configuration Register 1 (GPIO_PxC1)               | 96  |

|   |        | 3.2.3    | Port Configuration Register 2 (GPIO_PxC2)               | 96  |

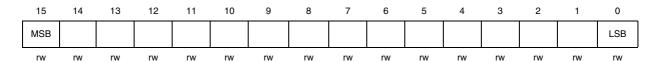

|   |        | 3.2.4    | I/O Data Register (GPIO_PxD)                            | 97  |

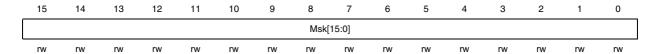

|   |        | 3.2.5    | I/O Mask Register (GPIO_PxM)                            | 97  |

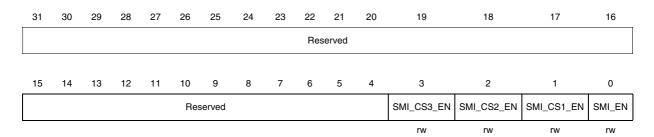

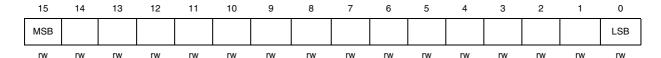

|   |        | 3.2.6    | I/O Remapping Register 0 (GPIO_REMAP0R)                 | 98  |

|   |        | 3.2.7    | I/O Remapping Register 1 (GPIO_REMAP1R)                 | 99  |

|   |        | 3.2.8    | I/O Port Register map                                   | 100 |

| 4 | Interr | upts     |                                                         | 01  |

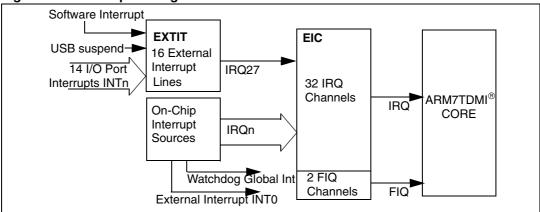

|   | 4.1    | Enhance  | ed Interrupt Controller (EIC)                           | 01  |

|   |        | 4.1.1    | IRQ Interrupt Vector table                              |     |

|   |        | 4.1.2    | FIQ Interrupt Vector table                              |     |

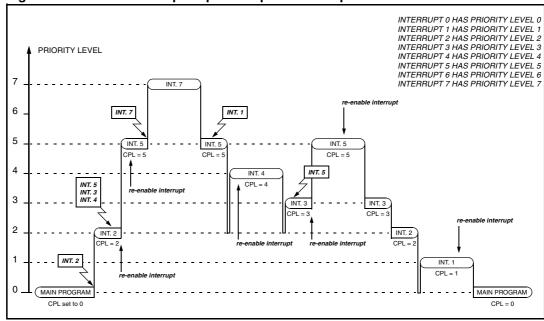

|   |        | 4.1.3    | IRQ Interrupt Structure                                 |     |

|   |        | 4.1.4    | Priority Decoder                                        |     |

|   |        | 4.1.5    | Finite State Machine                                    |     |

|   |        | 4.1.6    | Stack                                                   | 107 |

|   |        | 4.1.7    | EIC Interrupt Vectoring                                 | 108 |

|   |        | 4.1.8    | EIC IRQ notes                                           |     |

|   |        | 4.1.9    | FIQ mechanism                                           | 110 |

|   | 4.2    | Register | r Programming                                           |     |

|   |        | 4.2.1    | IRQ Example                                             |     |

|   |        | 4.2.2    | FIQ Example                                             |     |

|   |        |          |                                                         | • • |

|   | 4.3 | Applicat | ion note                                          | 111   |

|---|-----|----------|---------------------------------------------------|-------|

|   |     | 4.3.1    | Avoiding LR_sys and r5 registers content loss     | . 111 |

|   |     | 4.3.2    | Hints about subroutines used inside ISRs          | . 112 |

|   | 4.4 | Interrup | t latency                                         | 112   |

|   | 4.5 | Registe  | r description                                     | 113   |

|   | 4.6 | Register | r description                                     | 113   |

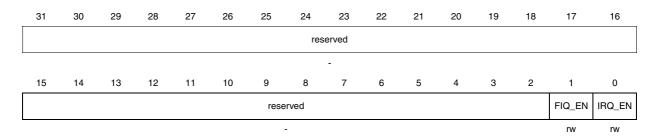

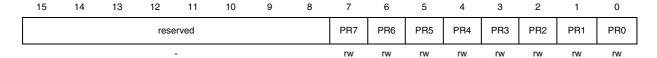

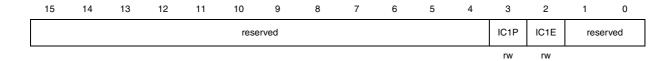

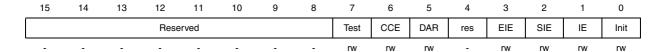

|   |     | 4.6.1    | Interrupt Control Register (EIC_ICR)              |       |

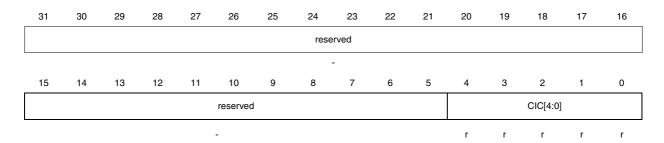

|   |     | 4.6.2    | Current Interrupt Channel Register (EIC_CICR)     | . 114 |

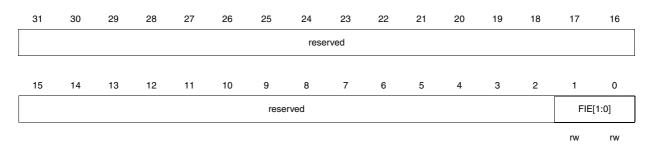

|   |     | 4.6.3    | Current Interrupt Priority Register (EIC_CIPR)    | . 114 |

|   |     | 4.6.4    | Fast Interrupt Enable Register (EIC_FIER)         | . 116 |

|   |     | 4.6.5    | Fast Interrupt Pending Register (EIC_FIPR)        | . 117 |

|   |     | 4.6.6    | Interrupt Vector Register (EIC_IVR)               | . 117 |

|   |     | 4.6.7    | Fast Interrupt Register (EIC_FIR)                 | . 118 |

|   |     | 4.6.8    | Interrupt Enable Register (EIC_IER)               | . 119 |

|   |     | 4.6.9    | Interrupt Pending Register (EIC_IPR)              | . 119 |

|   |     | 4.6.10   | Source Interrupt Registers - Channel n (EIC_SIRn) | . 121 |

|   | 4.7 | EIC Reg  | gister map                                        | 122   |

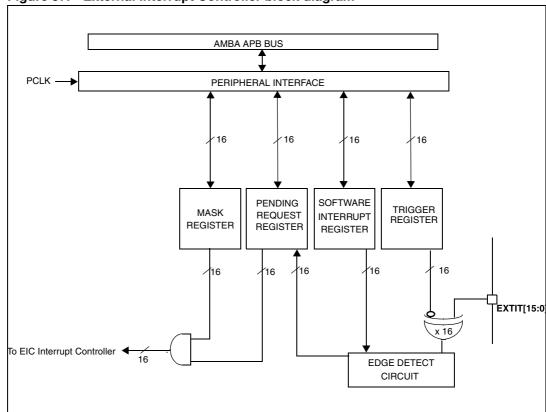

|   | 4.8 | Externa  | Interrupt Controller (EXTIT)                      | 124   |

|   |     | 4.8.1    | Introduction                                      | . 124 |

|   |     | 4.8.2    | Main features                                     | . 124 |

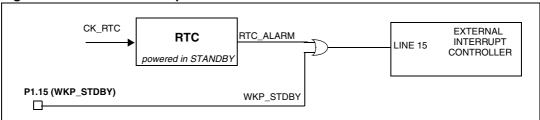

|   |     | 4.8.3    | Block diagram                                     | . 124 |

|   |     | 4.8.4    | Functional description                            | . 125 |

|   |     | 4.8.5    | External interrupt line mapping                   | . 126 |

|   |     | 4.8.6    | Register description                              | . 127 |

|   |     | 4.8.7    | EXTIT Register map                                | . 129 |

| 5 | ВΜΔ | controll | er (DMA)                                          | 130   |

|   | 5.1 |          | tion                                              |       |

|   |     |          |                                                   |       |

|   | 5.2 |          | ntroller priority                                 |       |

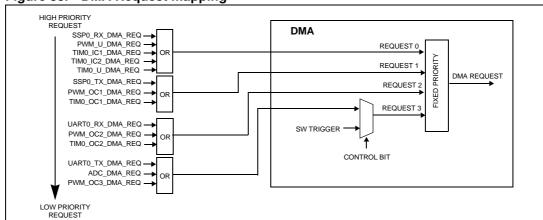

|   | 5.3 |          | equest mapping                                    |       |

|   |     | 5.3.1    | SSP DMA Requests                                  |       |

|   |     | 5.3.2    | UART DMA Requests                                 |       |

|   |     | 5.3.3    | ADC DMA Request                                   |       |

|   |     | 5.3.4    | TIM0 DMA Requests                                 |       |

|   |     | 5.3.5    | PWM Timer DMA Requests                            |       |

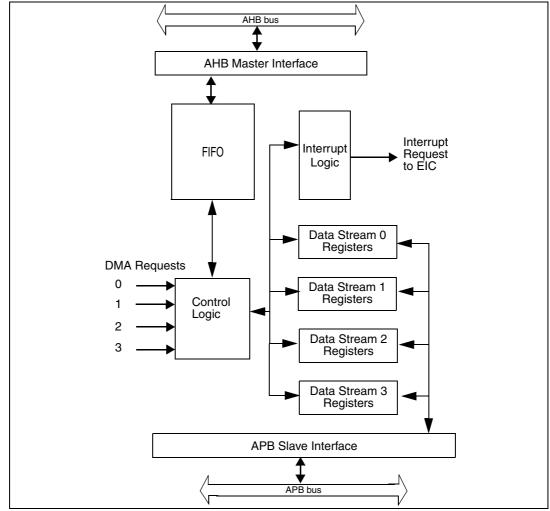

|   | 5.4 | Function | nal description                                   | 132   |

|   |     |          |                                                   |       |

|   | 5.5        | Registe                                                                                              | er description                                                                                                                                                                                                                                       | 136                                                                                |

|---|------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

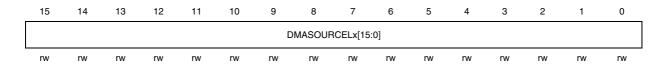

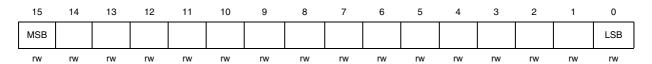

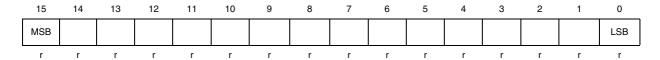

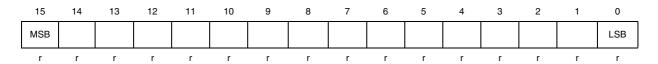

|   |            | 5.5.1                                                                                                | Source Base Address Low (DMA_SOURCELx) (x=0,,3)                                                                                                                                                                                                      |                                                                                    |

|   |            | 5.5.2                                                                                                | Source Base Address High (DMA_SOURCEHx) (x=0,,3)                                                                                                                                                                                                     |                                                                                    |

|   |            | 5.5.3                                                                                                | Destination Base Address Low (DMA_DESTLx) (x=0,,3)                                                                                                                                                                                                   | . 136                                                                              |

|   |            | 5.5.4                                                                                                | Destination Base Address High (DMA_DESTHx) (x=0,,3)                                                                                                                                                                                                  |                                                                                    |

|   |            | 5.5.5                                                                                                | Maximum Count Register (DMA_MAXx) (x=0,,3)                                                                                                                                                                                                           | . 137                                                                              |

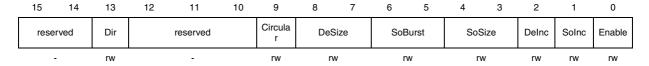

|   |            | 5.5.6                                                                                                | Control Register (DMA_CTRLx) (x=0, 1, 2)                                                                                                                                                                                                             | . 137                                                                              |

|   |            | 5.5.7                                                                                                | Control Register 3 (DMA_CTRL3)                                                                                                                                                                                                                       | . 139                                                                              |

|   |            | 5.5.8                                                                                                | Current Source Address High (DMA_SOCURRHx) (x=0,,3)                                                                                                                                                                                                  | . 140                                                                              |

|   |            | 5.5.9                                                                                                | Current Source Address Low (DMA_SOCURRLx) (x=0,,3)                                                                                                                                                                                                   | . 141                                                                              |

|   |            | 5.5.10                                                                                               | Current Destination Address High (DMA_DECURRHx) (x=0,,3)                                                                                                                                                                                             | . 141                                                                              |

|   |            | 5.5.11                                                                                               | Current Destination Address Low (DMA_DECURRLx) (x=0,,3)                                                                                                                                                                                              | . 142                                                                              |

|   |            | 5.5.12                                                                                               | Terminal Counter Register (DMA_TCNTx) (x=0,,3)                                                                                                                                                                                                       | . 142                                                                              |

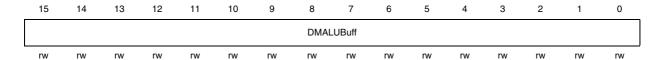

|   |            | 5.5.13                                                                                               | Last Used Buffer location X (DMA_LUBuffX) (X=0,,3)                                                                                                                                                                                                   | . 143                                                                              |

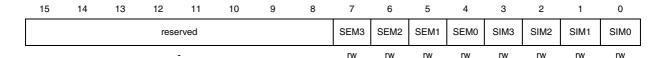

|   |            | 5.5.14                                                                                               | Interrupt Mask Register (DMA_MASK)                                                                                                                                                                                                                   | . 143                                                                              |

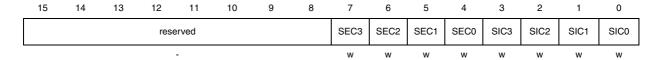

|   |            | 5.5.15                                                                                               | Interrupt Clear Register (DMA_CLR)                                                                                                                                                                                                                   | . 145                                                                              |

|   |            | 5.5.16                                                                                               | Interrupt Status Register (DMA_STATUS)                                                                                                                                                                                                               | . 146                                                                              |

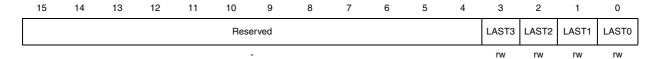

|   |            | 5.5.17                                                                                               | Last Flag Register (DMA_LAST)                                                                                                                                                                                                                        | . 148                                                                              |

|   | 5.6        | DMA R                                                                                                | egister map                                                                                                                                                                                                                                          | 149                                                                                |

| 6 | Seria      | ıl memo                                                                                              | ry interface (SMI)                                                                                                                                                                                                                                   | 151                                                                                |

|   | 6.1        | Introdu                                                                                              | ction                                                                                                                                                                                                                                                | 151                                                                                |

|   | 6.2        |                                                                                                      | eatures                                                                                                                                                                                                                                              |                                                                                    |

|   |            | ıvıaırı ie                                                                                           |                                                                                                                                                                                                                                                      |                                                                                    |

|   | 6.3        |                                                                                                      |                                                                                                                                                                                                                                                      |                                                                                    |

|   | 6.3        | Block d                                                                                              | liagram                                                                                                                                                                                                                                              | 151                                                                                |

|   | 6.3<br>6.4 | Block d                                                                                              | liagram                                                                                                                                                                                                                                              | 151<br>153                                                                         |

|   |            | Block d<br>Functio<br>6.4.1                                                                          | liagram                                                                                                                                                                                                                                              | 151<br>153<br>. 153                                                                |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2                                                                | liagram                                                                                                                                                                                                                                              | 151<br>153<br>. 153<br>. 153                                                       |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3                                                       | liagram  nal description  Clock configuration when using SMI  AHB interface  Memory device compatibility                                                                                                                                             | 151<br>153<br>. 153<br>. 153<br>. 155                                              |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4                                              | liagram  onal description  Clock configuration when using SMI  AHB interface  Memory device compatibility  Hardware mode                                                                                                                             | 151<br>153<br>. 153<br>. 153<br>. 155                                              |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5                                     | liagram  onal description  Clock configuration when using SMI  AHB interface  Memory device compatibility  Hardware mode  Software mode                                                                                                              | 151<br>153<br>. 153<br>. 153<br>. 155<br>. 155                                     |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6                            | liagram  onal description  Clock configuration when using SMI  AHB interface  Memory device compatibility  Hardware mode  Software mode  Booting from external memory                                                                                | 151<br>153<br>. 153<br>. 155<br>. 155<br>. 155                                     |

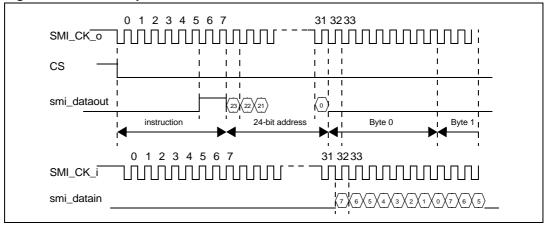

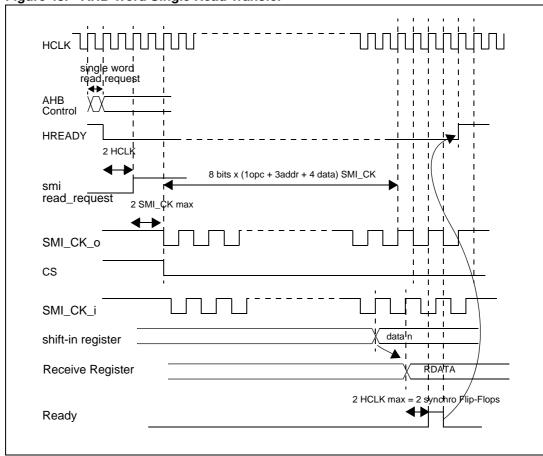

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7                   | liagram  onal description  Clock configuration when using SMI  AHB interface  Memory device compatibility  Hardware mode  Software mode  Booting from external memory  External memory read request                                                  | 151<br>153<br>. 153<br>. 153<br>. 155<br>. 155<br>. 155<br>. 155                   |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8          | liagram                                                                                                                                                                                                                                              | 151<br>153<br>. 153<br>. 153<br>. 155<br>. 155<br>. 155<br>. 156                   |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | liagram  onal description  Clock configuration when using SMI  AHB interface  Memory device compatibility  Hardware mode  Software mode  Booting from external memory  External memory read request  External memory write request  Read while write | 151<br>153<br>. 153<br>. 155<br>. 155<br>. 155<br>. 156<br>. 156<br>. 156          |

|   |            | Block d<br>Function<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8          | liagram                                                                                                                                                                                                                                              | 151<br>153<br>. 153<br>. 155<br>. 155<br>. 155<br>. 156<br>. 156<br>. 156<br>. 157 |

| 6.4.13 Interrupts                                | 160          |

|--------------------------------------------------|--------------|

| 6.5 Register description                         |              |

|                                                  | 161          |

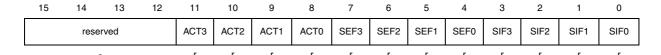

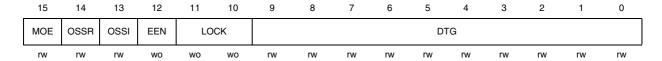

| 6.5.1 SMI control register 1 (SMI_CR1)           |              |

| 6.5.2 SMI control register 2 (SMI_CR2)           | 163          |

| 6.5.3 SMI status register (SMI_SR)               | 164          |

| 6.5.4 SMI transmit register (SMI_TR)             | 165          |

| 6.5.5 SMI receive register (SMI_RR)              |              |

| 6.6 Register map                                 | 166          |

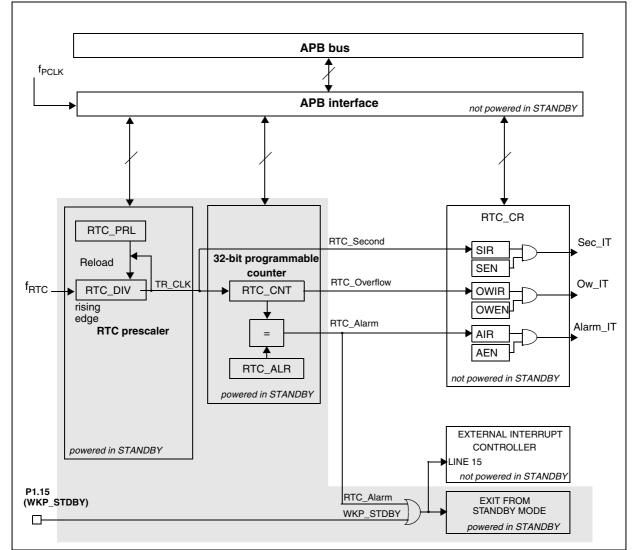

| 7 Real Time Clock (RTC)                          | 167          |

| 7.1 Introduction                                 | 167          |

| 7.2 Main features                                | 167          |

| 7.3 Functional description                       | 167          |

| 7.3.1 Overview                                   |              |

| 7.3.2 Reset procedure                            |              |

| 7.3.3 Reading RTC registers                      | 168          |

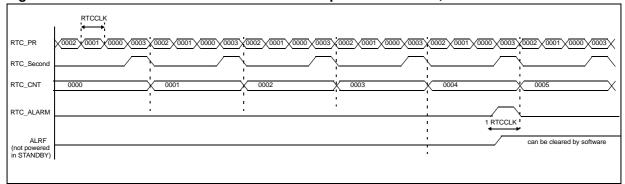

| 7.3.4 Free-running mode                          | 169          |

| 7.3.5 Managing RTC interrupt flags               | 169          |

| 7.3.6 Configuration mode                         | 171          |

| 7.4 Register description                         | 171          |

| 7.4.1 RTC Control Register High (RTC_CRH)        | 171          |

| 7.4.2 RTC Control Register Low (RTC_CRL)         | 172          |

| 7.4.3 RTC Prescaler Load Register (RTC_PRLH / F  | RTC_PRLL)174 |

| 7.4.4 RTC Prescaler Divider Register (RTC_DIVH / | RTC_DIVL)175 |

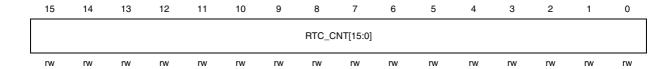

| 7.4.5 RTC Counter Register (RTC_CNTH / RTC_CI    | NTL) 176     |

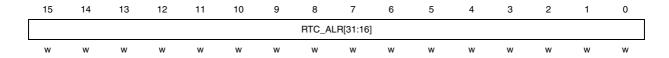

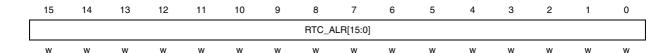

| 7.4.6 RTC Alarm Register High (RTC_ALRH / RTC_   | _ALRL) 177   |

| 7.5 RTC register map                             |              |

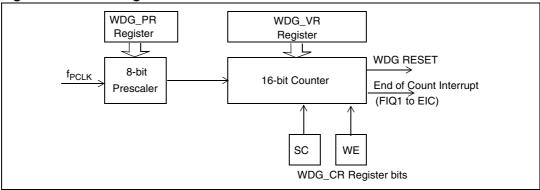

| 8 Watchdog Timer (WDG)                           | 179          |

| 8.1 Introduction                                 | 179          |

| 8.2 Main features                                | 179          |

| 8.3 Functional description                       | 179          |

| 8.3.1 Free-running Timer mode                    | 179          |

| 8.3.2 Watchdog mode                              | 180          |

| 8.4 Register description                         |              |

|    |      | 8.4.1   | WDG Control Register (WDG_CR)                  | 180 |

|----|------|---------|------------------------------------------------|-----|

|    |      | 8.4.2   | WDG Prescaler Register (WDG_PR)                | 181 |

|    |      | 8.4.3   | WDG Preload Value Register (WDG_VR)            | 181 |

|    |      | 8.4.4   | WDG Counter Register (WDG_CNT)                 | 182 |

|    |      | 8.4.5   | WDG Status Register (WDG_SR)                   | 182 |

|    |      | 8.4.6   | WDG Mask Register (WDG_MR)                     | 182 |

|    |      | 8.4.7   | WDG Key Register (WDG_KR)                      | 183 |

|    | 8.5  | WDG F   | Register map                                   | 184 |

| 9  | Time | base Ti | mer (TB)                                       | 185 |

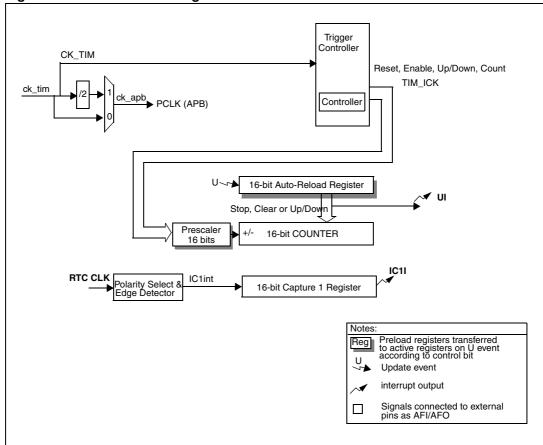

|    | 9.1  | Introdu | ction                                          | 185 |

|    | 9.2  | Synchro | onizable Programmable Timer (SPT) architecture | 185 |

|    | 9.3  | Genera  | ıl block diagram                               | 185 |

|    | 9.4  | Genera  | ıl features                                    | 186 |

|    |      | 9.4.1   | Counter clock selection                        | 186 |

|    | 9.5  | Functio | nal description                                | 187 |

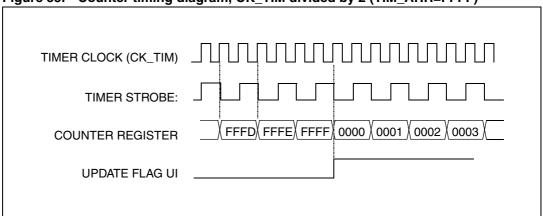

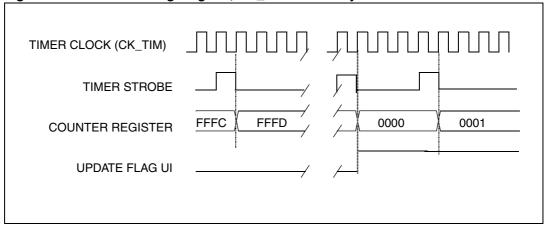

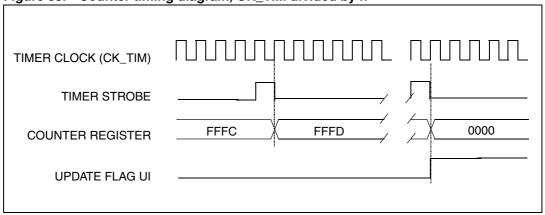

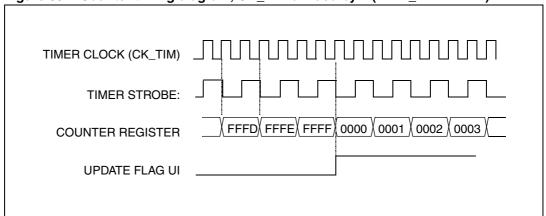

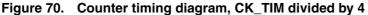

|    |      | 9.5.1   | Counter                                        | 187 |

|    |      | 9.5.2   | Interrupt management                           | 189 |

|    |      | 9.5.3   | Debug mode                                     | 189 |

|    | 9.6  | Registe | er description                                 | 189 |

|    |      | 9.6.1   | Control Register (TB_CR)                       | 190 |

|    |      | 9.6.2   | Synchro Control Register (TB_SCR)              | 191 |

|    |      | 9.6.3   | Input Mode Control Register (TB_IMCR)          | 192 |

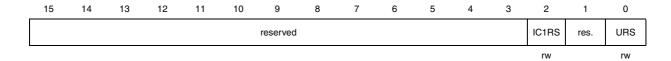

|    |      | 9.6.4   | Request Selection Register (TB_RSR)            | 192 |

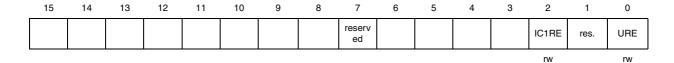

|    |      | 9.6.5   | Request Enable Register (TB_RER)               | 193 |

|    |      | 9.6.6   | Interrupt Status Register (TB_ISR)             | 193 |

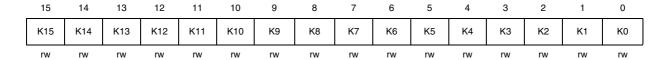

|    |      | 9.6.7   | Counter Register (TB_CNT)                      | 194 |

|    |      | 9.6.8   | Prescaler Register (TB_PSC)                    | 194 |

|    |      | 9.6.9   | Auto-Reload Register (TB_ARR)                  | 195 |

|    |      | 9.6.10  | Input Capture Register 1 (TB_ICR1)             | 195 |

|    | 9.7  | TB Reg  | gister map                                     | 195 |

| 10 | Sync | hroniza | ble Standard Timer (TIM)                       | 197 |

|    | 10.1 | Introdu | ction                                          | 197 |

|    | 10.2 | Synchro | onizable Programmable Timer (SPT) architecture | 197 |

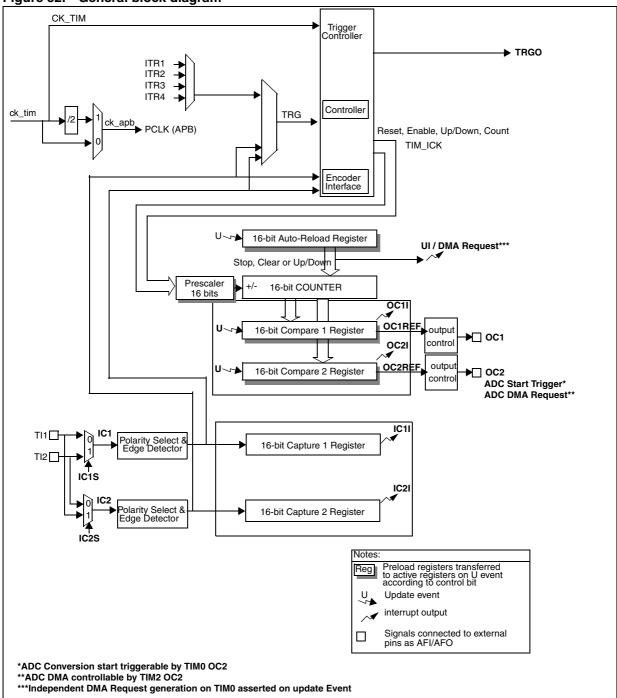

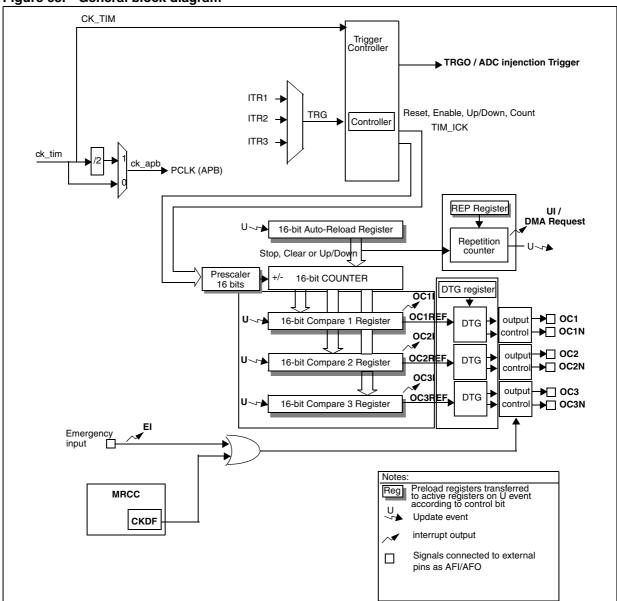

|    | 10.3 | Genera  | ıl block diagram                               | 198 |

| 10.4  | General features |                                         |  |  |  |  |  |

|-------|------------------|-----------------------------------------|--|--|--|--|--|

| 10.5  | Function         | nal description                         |  |  |  |  |  |

|       | 10.5.1           | Counter                                 |  |  |  |  |  |

|       | 10.5.2           | Counter clock selection                 |  |  |  |  |  |

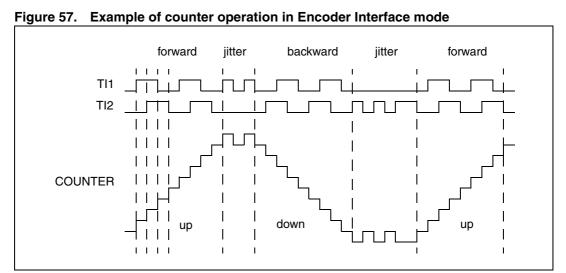

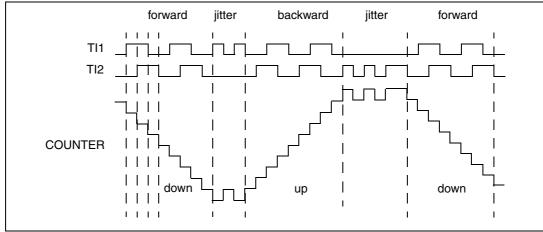

|       | 10.5.3           | Encoder Interface Mode                  |  |  |  |  |  |

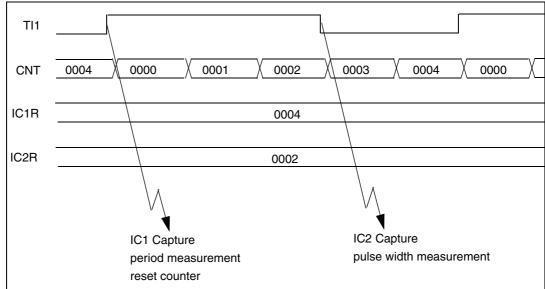

|       | 10.5.4           | Input Capture mode                      |  |  |  |  |  |

|       | 10.5.5           | PWM input mode                          |  |  |  |  |  |

|       | 10.5.6           | Forced output mode                      |  |  |  |  |  |

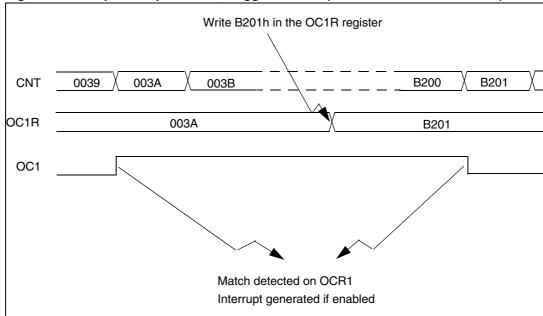

|       | 10.5.7           | Output compare mode                     |  |  |  |  |  |

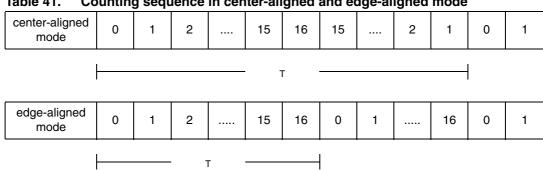

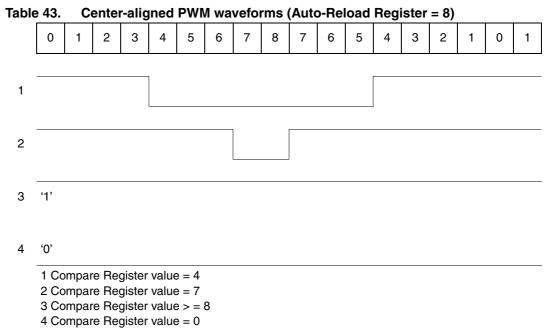

|       | 10.5.8           | PWM mode                                |  |  |  |  |  |

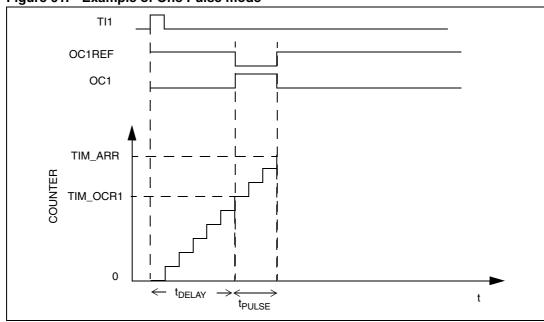

|       | 10.5.9           | One Pulse mode                          |  |  |  |  |  |

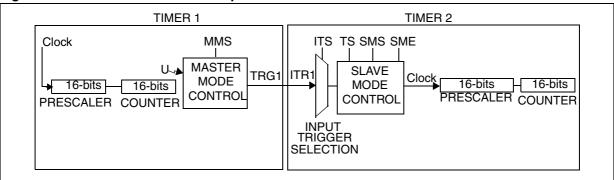

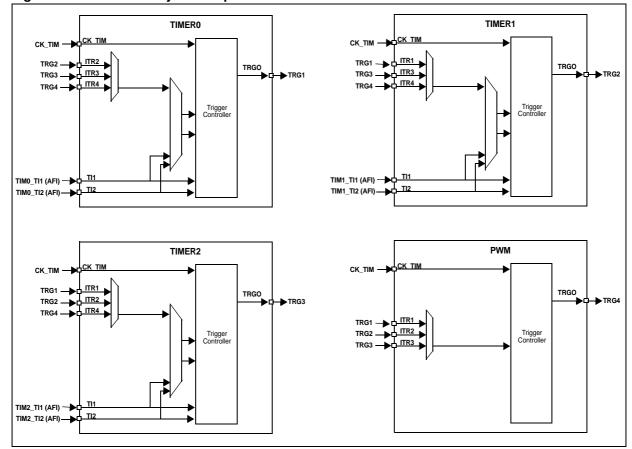

| 10.6  | Timer sy         | ynchronization 213                      |  |  |  |  |  |

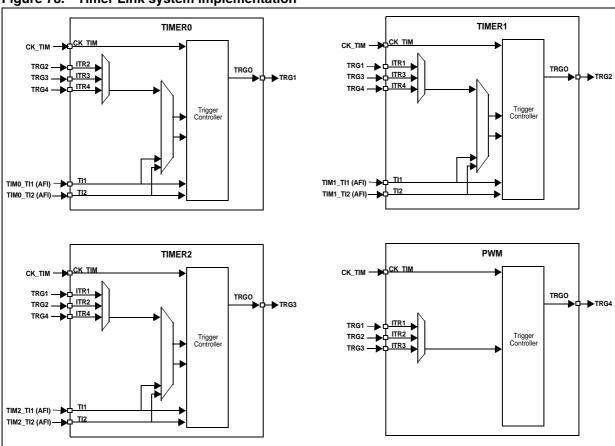

|       | 10.6.1           | Timer Link system                       |  |  |  |  |  |

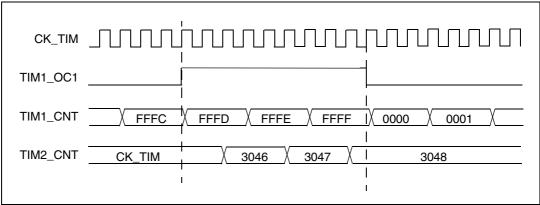

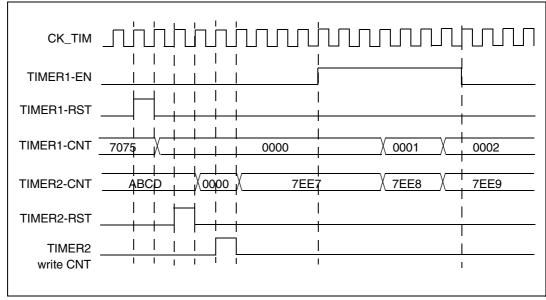

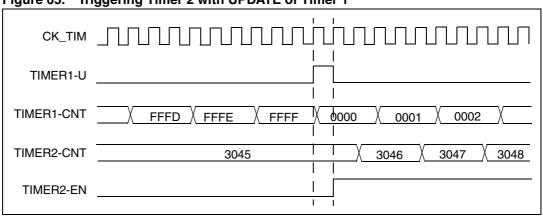

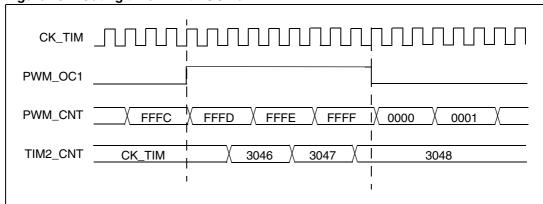

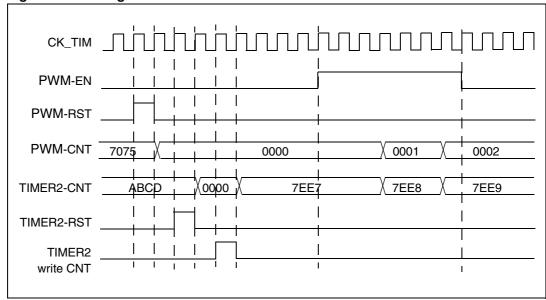

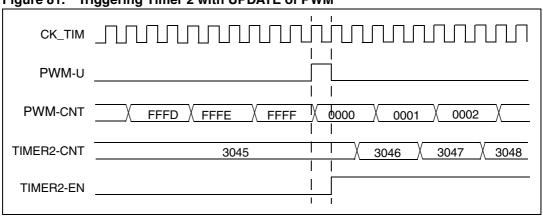

|       | 10.6.2           | Synchronization of 2 Timers             |  |  |  |  |  |

| 10.7  | Interrup         | t management                            |  |  |  |  |  |

| 10.8  | DMA fur          | nction 217                              |  |  |  |  |  |

|       | 10.8.1           | Using the DMA feature                   |  |  |  |  |  |

|       | 10.8.2           | DMA access in burst mode                |  |  |  |  |  |

| 10.9  | Debug r          | mode                                    |  |  |  |  |  |

| 10.10 | Registe          | r description                           |  |  |  |  |  |

|       | 10.10.1          | Control Register (TIM_CR)               |  |  |  |  |  |

|       | 10.10.2          | Synchro Control Register (TIM_SCR)222   |  |  |  |  |  |

|       | 10.10.3          | Input Mode Control Register (TIM_IMCR)  |  |  |  |  |  |

|       | 10.10.4          | Output Mode Register 1 (TIM_OMR1)       |  |  |  |  |  |

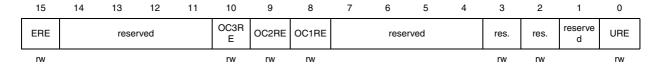

|       | 10.10.5          | Request Selection Register (TIM_RSR)226 |  |  |  |  |  |

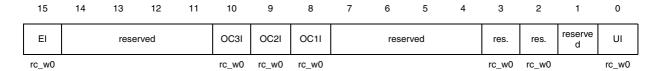

|       | 10.10.6          | Request Enable Register (TIM_RER)227    |  |  |  |  |  |

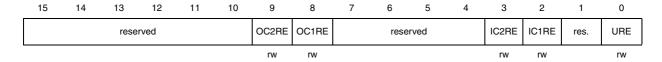

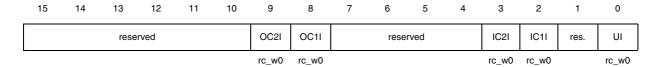

|       | 10.10.7          | Interrupt Status Register (TIM_ISR)228  |  |  |  |  |  |

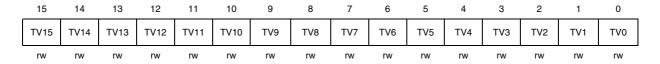

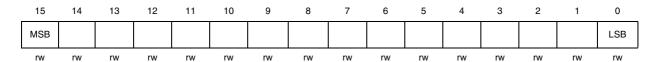

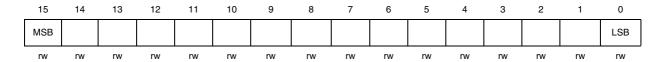

|       | 10.10.8          | Counter Register (TIM_CNT)              |  |  |  |  |  |

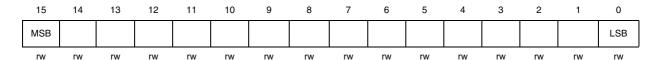

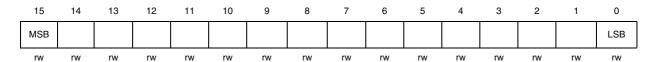

|       | 10.10.9          | Prescaler Register (TIM_PSC)230         |  |  |  |  |  |

|       | 10.10.10         | Auto-Reload Register (TIM_ARR)          |  |  |  |  |  |

|       | 10.10.11         | Output Compare Register 1 (TIM_OCR1)    |  |  |  |  |  |

|       | 10.10.12         | Output Compare Register 2 (TIM_OCR2)    |  |  |  |  |  |

|       | 10.10.13         | Input Capture Register 1 (TIM_ICR1)232  |  |  |  |  |  |

|       |                  | Input Capture Register 2 (TIM_ICR2)232  |  |  |  |  |  |

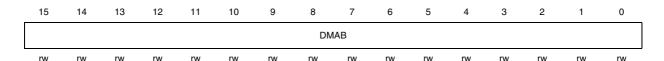

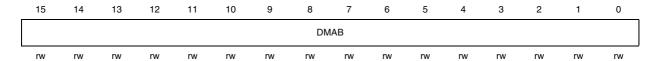

|       | 10.10.15         | DMA Burst Address (TIM_DMAB)            |  |  |  |  |  |

| 10.11 | TIM Red          | pister map                              |  |  |  |  |  |

| 11 | Syncl | hronizal | ble-PWM Timer (PWM)                                    | . 234 |

|----|-------|----------|--------------------------------------------------------|-------|

|    | 11.1  | Introduc | etion                                                  | . 234 |

|    | 11.2  | Synchro  | onizable Programmable Timer (SPT) architecture         | . 234 |

|    | 11.3  | General  | block diagram                                          | . 235 |

|    | 11.4  | General  | l features                                             | . 236 |

|    | 11.5  |          | nal description                                        |       |

|    |       | 11.5.1   | Counter                                                |       |

|    |       | 11.5.2   | Counter clock selection                                |       |

|    |       | 11.5.3   | Forced output mode                                     |       |

|    |       | 11.5.4   | Output compare mode                                    |       |

|    |       | 11.5.5   | PWM mode                                               |       |

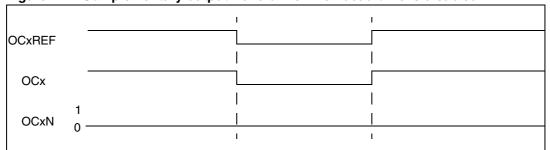

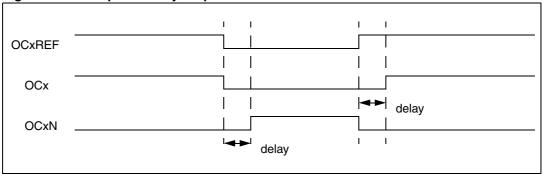

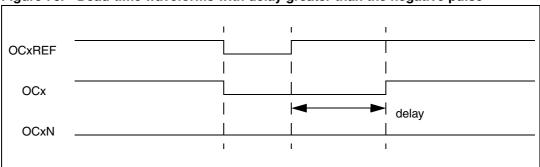

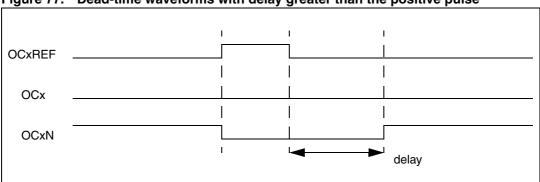

|    |       | 11.5.6   | PWM with Complementary Outputs and Dead-Time Insertion | 245   |

|    |       | 11.5.7   | Re-directing OCxREF to OCx or OCxN                     | 247   |

|    | 11.6  | PWM &    | Timer synchronization                                  | . 248 |

|    |       | 11.6.1   | Timer Link system                                      | 248   |

|    |       | 11.6.2   | Synchronization of Timers and PWM                      | 248   |

|    | 11.7  | Interrup | t management                                           | . 251 |

|    | 11.8  | DMA fu   | nction                                                 | . 251 |

|    |       | 11.8.1   | Using the DMA feature                                  | 251   |

|    |       | 11.8.2   | DMA access in burst mode                               |       |

|    | 11.9  | Debug r  | mode                                                   | . 253 |

|    | 11.10 | _        | r description                                          |       |

|    |       | 11.10.1  | Control Register (PWM_CR)                              |       |

|    |       | 11.10.2  | • • •                                                  |       |

|    |       | 11.10.3  | Output Mode Register 1 (PWM_OMR1)                      |       |

|    |       | 11.10.4  | Output Mode Register 2 (PWM_OMR2)                      | 260   |

|    |       | 11.10.5  | Request Selection Register (PWM_RSR)                   | 263   |

|    |       | 11.10.6  | Request Enable Register (PWM_RER)                      | 264   |

|    |       | 11.10.7  | Interrupt Status Register (PWM_ISR)                    | 265   |

|    |       | 11.10.8  | Counter Register (PWM_CNT)                             | 267   |

|    |       | 11.10.9  | Prescaler Register (PWM_PSC)                           | 268   |

|    |       | 11.10.10 | Repetition Counter Register (PWM_RCR)                  | 268   |

|    |       | 11.10.11 | Auto-Reload Register (PWM_ARR)                         | 269   |

|    |       | 11.10.12 | Output Compare Register 1 (PWM_OCR1)                   | 269   |

|    |       | 11.10.13 | Output Compare Register 2 (PWM_OCR2)                   | 270   |

|    |       | 11.10.14 | Output Compare Register 3 (PWM_OCR3)                   | 270   |

|    |        | 11.10.15 | 5 Dead-Time Register (PWM_DTR)          | 271 |

|----|--------|----------|-----------------------------------------|-----|

|    |        | 11.10.16 | 6 DMA burst address (PWM_DMAB)          | 272 |

|    | 11.11  | PWM R    | legister map                            | 273 |

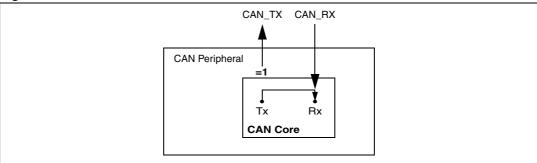

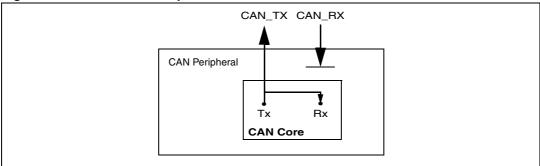

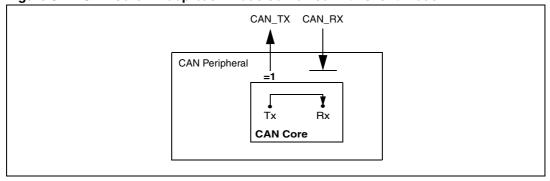

| 12 | Contr  | oller ar | ea network (CAN)                        | 274 |

|    | 12.1   | Introduc | ction                                   | 274 |

|    | 12.2   | Main fe  | atures                                  | 274 |

|    | 12.3   | Block di | iagram                                  | 274 |

|    | 12.4   | Functio  | nal description                         | 275 |

|    |        | 12.4.1   | Software initialization                 |     |

|    |        | 12.4.2   | CAN message transfer                    | 276 |

|    |        | 12.4.3   | Disabled automatic re-transmission mode | 276 |

|    |        | 12.4.4   | Test mode                               | 277 |

|    | 12.5   | Registe  | r description                           | 279 |

|    |        | 12.5.1   | CAN interface reset state               | 281 |

|    |        | 12.5.2   | CAN protocol related registers          | 281 |

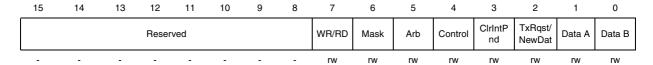

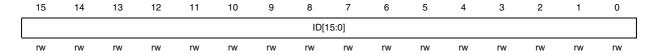

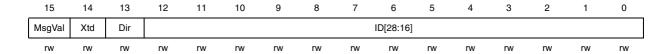

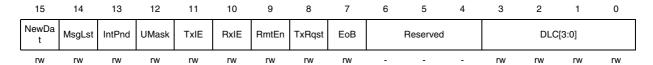

|    |        | 12.5.3   | Message interface register sets         | 286 |

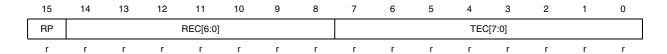

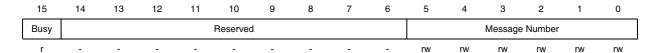

|    |        | 12.5.4   | Message handler registers               | 293 |

|    | 12.6   | Registe  | r map                                   | 297 |

|    | 12.7   | CAN co   | ommunications                           | 298 |

|    |        | 12.7.1   | Managing message objects                | 298 |

|    |        | 12.7.2   | Message handler state machine           | 299 |

|    |        | 12.7.3   | Configuring a transmit object           | 302 |

|    |        | 12.7.4   | Updating a transmit object              | 302 |

|    |        | 12.7.5   | Configuring a receive object            | 303 |

|    |        | 12.7.6   | Handling received messages              | 303 |

|    |        | 12.7.7   | Configuring a FIFO buffer               | 304 |

|    |        | 12.7.8   | Receiving messages with FIFO buffers    | 304 |

|    |        | 12.7.9   | Handling interrupts                     | 305 |

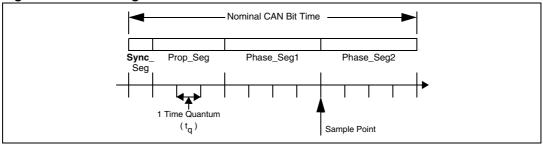

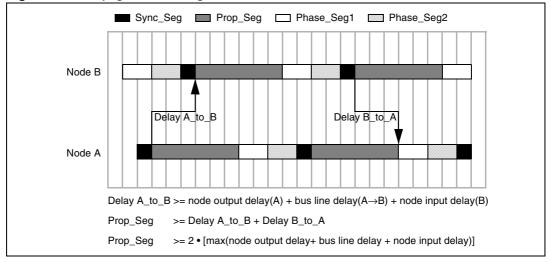

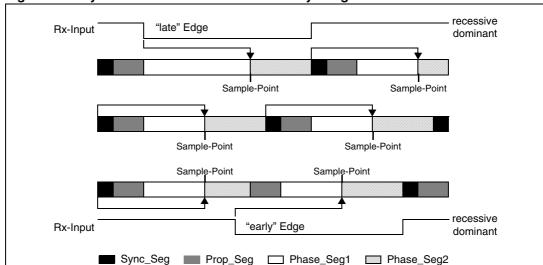

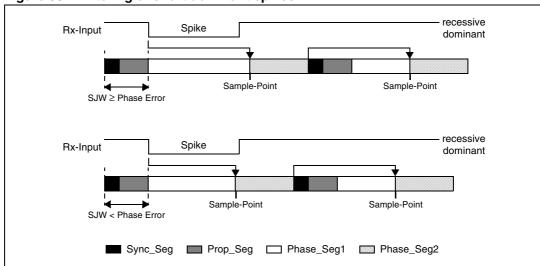

|    |        | 12.7.10  | Configuring the bit timing              | 306 |

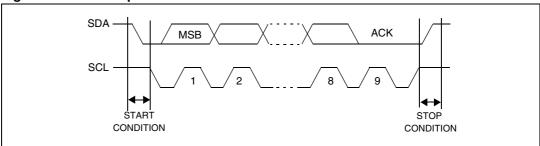

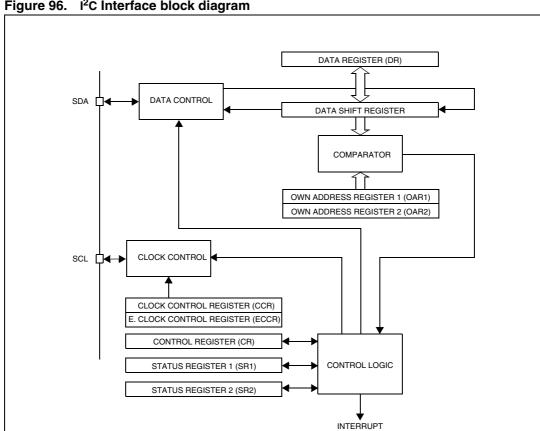

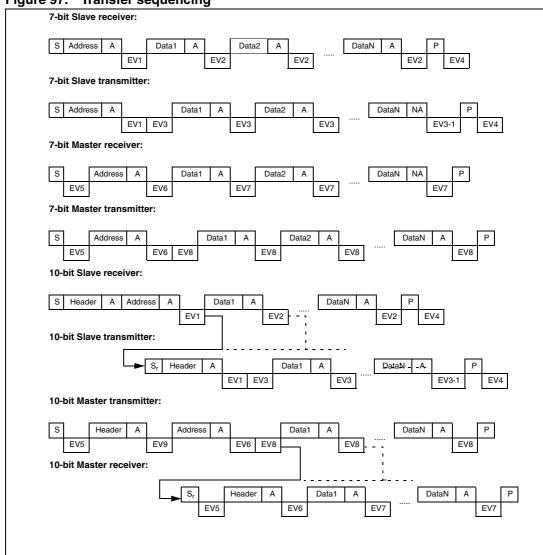

| 13 | I2C In | iterface | Module (I <sup>2</sup> C)               | 315 |

|    | 13.1   | Main fe  | atures                                  | 315 |

|    | 13.2   | Genera   | I description                           | 315 |

|    |        | 13.2.1   | Mode selection                          | 316 |

|    |        | 13.2.2   | Communication flow                      | 316 |

|    |        |          |                                         |     |

|    |      | 13.2.3   | SDA/SCL line control                           | 316   |

|----|------|----------|------------------------------------------------|-------|

|    | 13.3 | Functio  | nal description                                | . 317 |

|    |      | 13.3.1   | Slave mode                                     | 317   |

|    |      | 13.3.2   | Master mode                                    | 319   |

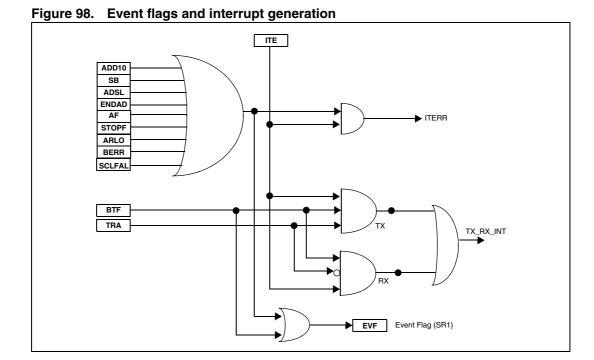

|    | 13.4 | Interrup | ots                                            | . 322 |

|    | 13.5 | Registe  | er description                                 | . 323 |

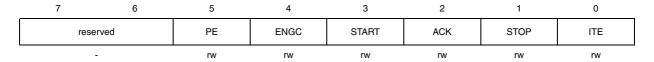

|    |      | 13.5.1   | I2C Control Register (I2C_CR)                  | 323   |

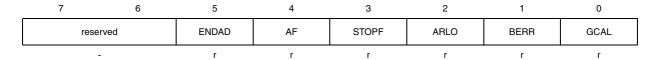

|    |      | 13.5.2   | I2C Status Register 1 (I2C_SR1)                | 324   |

|    |      | 13.5.3   | I2C Status Register 2 (I2C_SR2)                | 326   |

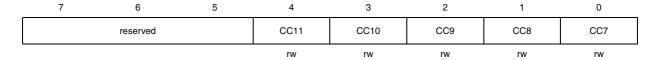

|    |      | 13.5.4   | I2C Clock Control Register (I2C_CCR)           | 327   |

|    |      | 13.5.5   | I2C Extended Clock Control Register (I2C_ECCR) | 328   |

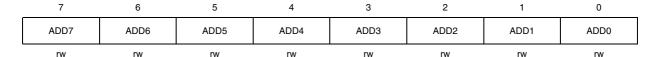

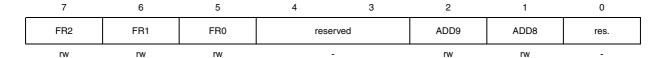

|    |      | 13.5.6   | I2C Own Address Register 1 (I2C_OAR1)          | 328   |

|    |      | 13.5.7   | I2C Own Address Register 2 (I2C_OAR2)          | 329   |

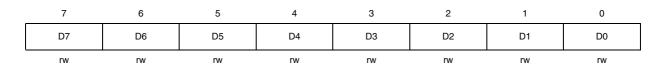

|    |      | 13.5.8   | I2C Data Register (I2C_DR)                     | 329   |

|    | 13.6 | I2C Re   | gister map                                     | . 330 |

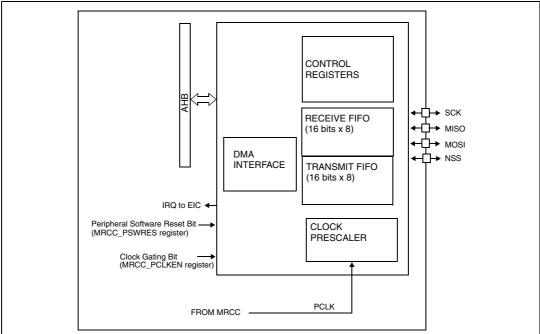

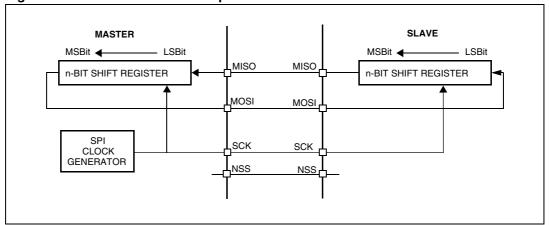

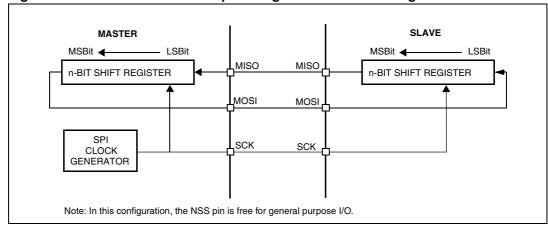

| 14 | Sync | hronou   | s Serial Peripheral (SSP)                      | . 331 |

|    | 14.1 |          | atures                                         |       |

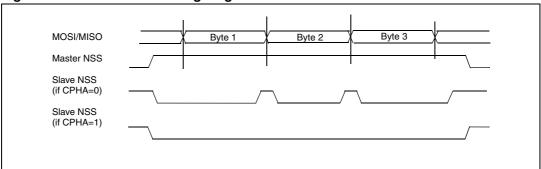

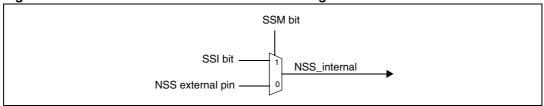

|    | 14.2 |          | nal description                                |       |

|    |      | 14.2.1   | Pin description                                |       |

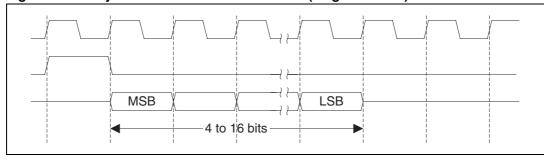

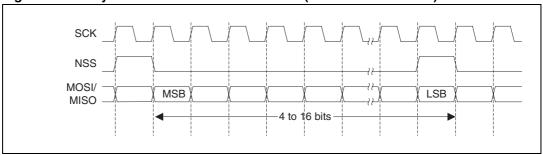

|    |      | 14.2.2   | Master mode                                    |       |

|    |      | 14.2.3   | Slave mode                                     |       |

|    |      | 14.2.4   | Slave Select Management                        |       |

|    |      | 14.2.5   | SSP operation                                  |       |

|    |      | Enabling | g SSP operation                                |       |

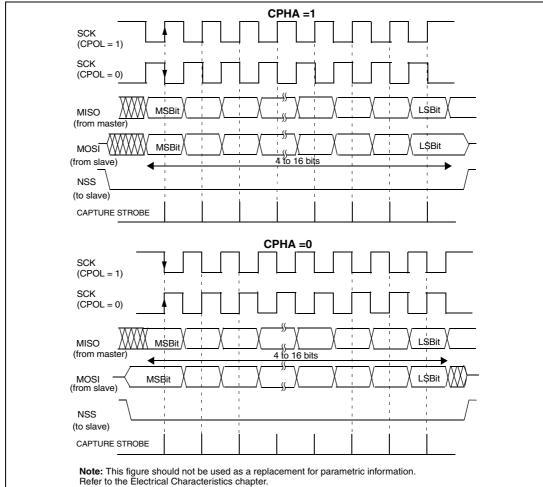

|    |      | Progran  | nming the SSP_CR0 Control Register             | 335   |

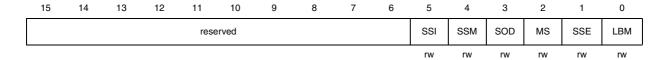

|    |      | _        | nming the SSP_CR1 Control Register             |       |

|    |      | 14.2.6   | Transmit FIFO                                  | 340   |

|    |      | 14.2.7   | Receive FIFO                                   | 340   |

|    |      | 14.2.8   | Interrupt Control                              | 341   |

|    |      | 14.2.9   | SSP0 DMA Interface                             | 341   |

|    | 14.3 | Registe  | er description                                 | . 342 |

|    |      | 14.3.1   | Control Register 0 (SSP_CR0)                   | 342   |

|    |      | 14.3.2   | Control Register 1 (SSP_CR1)                   | 343   |

|    |      | 14.3.3   | Data Register (SSP_DR)                         | 344   |

|    |      | 14.3.4   | Status Register (SSP_SR)                       | 345   |

|    |       | 14.3.5   | Clock Prescaler Register (SSP_PR)                 | 345 |

|----|-------|----------|---------------------------------------------------|-----|

|    |       | 14.3.6   | Interrupt Mask Set and Clear Register (SSP_IMSCR) | 346 |

|    |       | 14.3.7   | Raw Interrupt Status Register (SSP_RISR)          | 346 |

|    |       | 14.3.8   | Masked Interrupt Status Register (SSP_MISR)       | 347 |

|    |       | 14.3.9   | Interrupt Clear Register (SSP_ICR)                | 347 |

|    |       | 14.3.10  | DMA Control Register (SSP_DMACR)                  | 348 |

|    | 14.4  | Registe  | er map                                            | 349 |

| 15 | Unive | ersal As | ynchronous Receiver Transmitter (UART)            | 350 |

|    | 15.1  | Introduc | ction                                             | 350 |

|    | 15.2  | Main fe  | atures                                            | 350 |

|    | 15.3  | Functio  | nal description                                   | 351 |

|    |       | 15.3.1   | Functional block diagram                          |     |

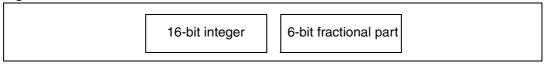

|    |       | 15.3.2   | Fractional baud rate divider                      |     |

|    |       | 15.3.3   | Data transmission or reception                    |     |

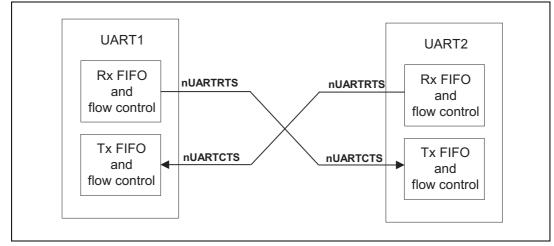

|    |       | 15.3.4   | UART hardware flow control                        |     |

|    |       | 15.3.5   | Interrupts                                        | 358 |

|    |       | 15.3.6   | UARTO DMA Interface                               | 358 |

|    | 15.4  | Registe  | er description                                    | 359 |

|    |       | 15.4.1   | Data Register (UART_DR)                           |     |

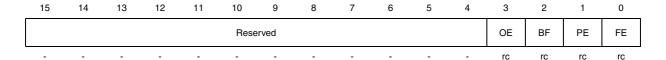

|    |       | 15.4.2   | Receive Status Register (UART_RSR)                |     |

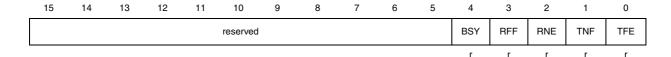

|    |       | 15.4.3   | Flag Register (UART_FR)                           | 362 |

|    |       | 15.4.4   | Break Register (UART_BKR)                         | 363 |

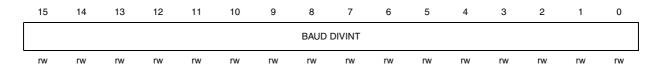

|    |       | 15.4.5   | Integer Baud Rate Register (UART_IBRD)            | 364 |

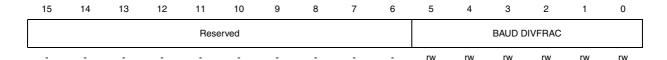

|    |       | 15.4.6   | Fractional Baud Rate Register (UART_FBRD)         | 365 |

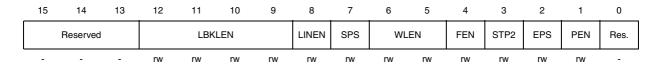

|    |       | 15.4.7   | Line Control Register (UART_LCR)                  | 365 |

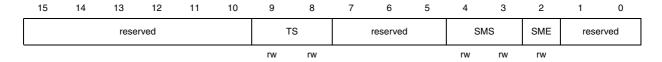

|    |       | 15.4.8   | Control Register (UART_CR)                        | 368 |

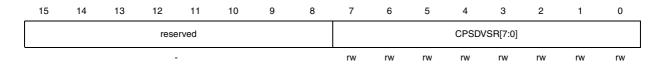

|    |       | 15.4.9   | Interrupt FIFO Level Select Register (UART_IFLS)  | 369 |

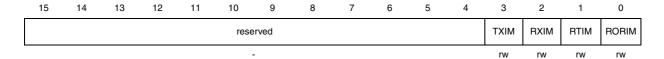

|    |       | 15.4.10  | Interrupt Mask Set/Clear Register (UART_IMSC)     | 370 |

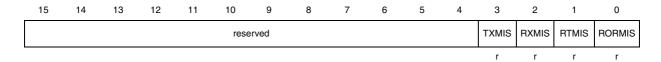

|    |       | 15.4.11  | Raw Interrupt Status Register (UART_RIS)          | 371 |

|    |       | 15.4.12  | Masked Interrupt Status Register (UART_MIS)       | 373 |

|    |       | 15.4.13  | Interrupt Clear Register (UART_ICR)               | 374 |

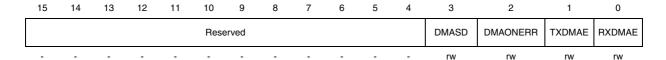

|    |       | 15.4.14  | DMA Control Register (UART_DMACR)                 | 375 |

|    | 15.5  | UART F   | Register map                                      | 376 |

| 16 | USB   | full-spe | ed device interface (USB)                         | 377 |

|     | 16.1 | Introduc | ction                                    | 377 |

|-----|------|----------|------------------------------------------|-----|

|     | 16.2 | Main fe  | atures                                   | 377 |

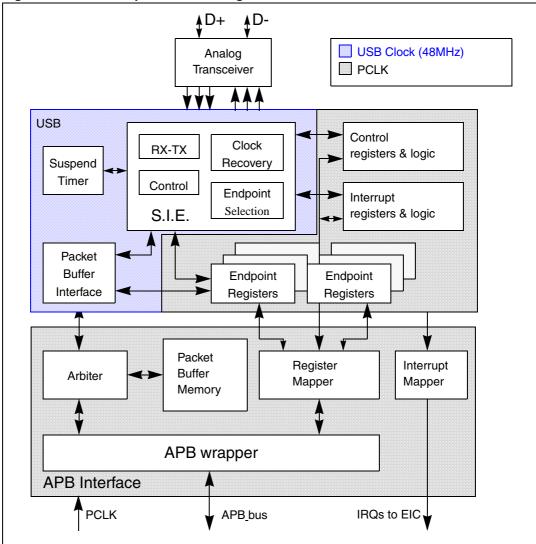

|     | 16.3 | Block d  | iagram                                   | 377 |

|     | 16.4 | Functio  | nal description                          | 378 |

|     |      | 16.4.1   | Description of USB blocks                | 379 |

|     | 16.5 | Progran  | mming considerations                     | 380 |

|     |      | 16.5.1   | Generic USB device programming           | 380 |

|     |      | 16.5.2   | System and power-on reset                | 380 |

|     |      | 16.5.3   | Double-buffered endpoints                | 387 |

|     |      | 16.5.4   | Isochronous transfers                    | 389 |

|     |      | 16.5.5   | Suspend/Resume events                    | 390 |

|     | 16.6 | Registe  | er description                           | 392 |

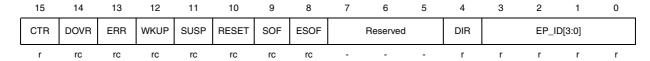

|     |      | 16.6.1   | Common registers                         | 392 |

|     |      | 16.6.2   | Endpoint-specific registers              | 400 |

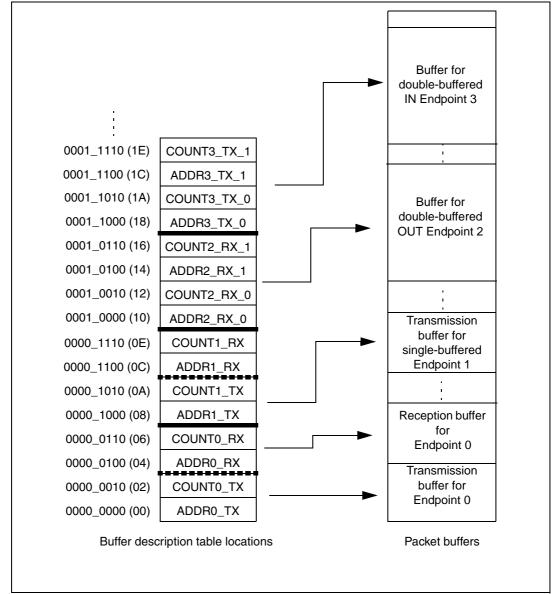

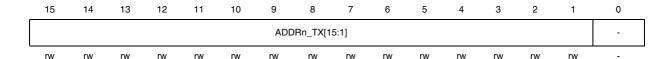

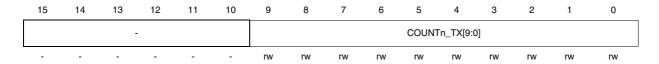

|     |      | 16.6.3   | Buffer descriptor table                  | 405 |

|     | 16.7 | USB Re   | egister map                              | 409 |

| 4-7 | A1   | t. D:    | aital Oamandan (ADO)                     | 440 |

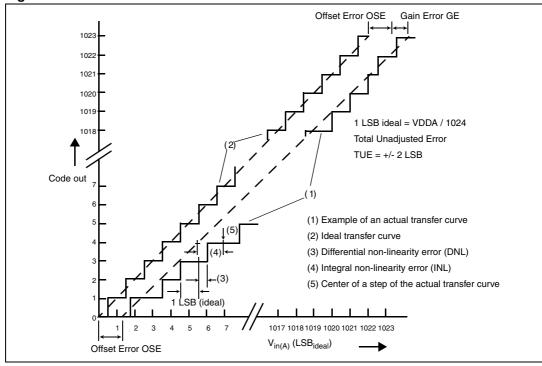

| 17  |      | _        | gital Converter (ADC)                    |     |

|     | 17.1 |          | naracteristics                           |     |

|     | 17.2 |          | ction                                    |     |

|     | 17.3 | Functio  | nal description                          | 411 |

|     |      | 17.3.1   | Start of calibration                     |     |

|     |      | 17.3.2   | Start of conversion                      |     |

|     |      | 17.3.3   | Operating modes                          |     |

|     |      | 17.3.4   | Input channel selection                  |     |

|     |      | 17.3.5   | Timer start of conversion trigger/enable | 413 |

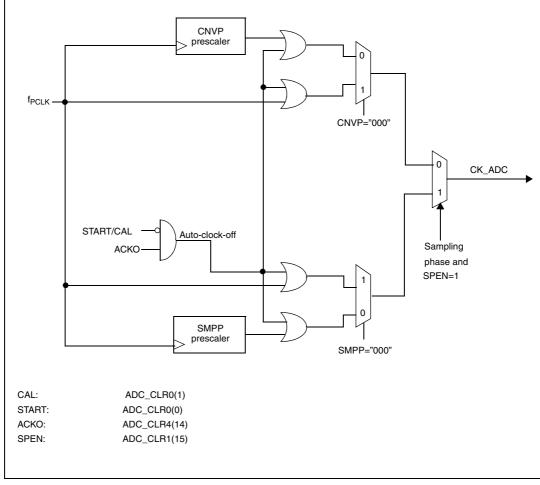

|     |      | 17.3.6   | Analog clock prescaler                   |     |

|     |      | 17.3.7   | Injected conversion chain                |     |

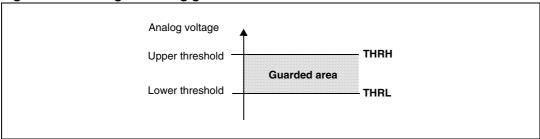

|     |      | 17.3.8   | Analog watchdogs                         |     |

|     |      | 17.3.9   | DMA functionality                        |     |

|     |      | 17.3.10  | Interrupts                               |     |

|     |      | 17.3.11  | Power-down mode                          |     |

|     |      | 17.3.12  | Auto-clock-off mode                      |     |

|     | 17.4 | Registe  | er description                           |     |

|     |      | 17.4.1   | ADC Data Register (ADC_Dx)               |     |

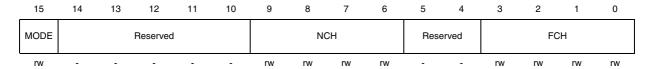

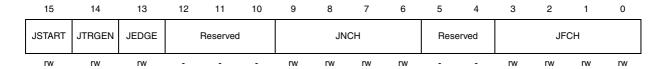

|     |      | 17.4.2   | Control Logic Register 0 (ADC_CLR0)      | 418 |

|    |       | 17.4.3 Control Logic Register 1 (ADC_CLR1)    | 419   |

|----|-------|-----------------------------------------------|-------|

|    |       | 17.4.4 Control Logic Register 2 (ADC_CLR2)    | 420   |

|    |       | 17.4.5 Control Logic Register 3 (ADC_CLR3)    | 421   |

|    |       | 17.4.6 Control Logic Register 4 (ADC_CLR4)    | 422   |

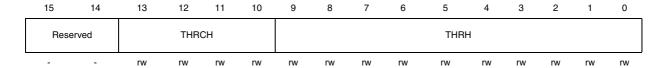

|    |       | 17.4.7 Threshold Registers A (ADC_TRA03)      | 423   |

|    |       | 17.4.8 Threshold Registers B (ADC_TRB03)      | 423   |

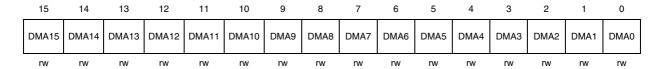

|    |       | 17.4.9 DMA Channel Enable Register (ADC_DMAR) | 424   |

|    |       | 17.4.10 DMA Global Enable Register (ADC_DMAE) | 424   |

|    |       | 17.4.11 Pending Bit Register (ADC_PBR)        | 425   |

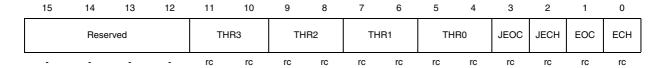

|    |       | 17.4.12 Interrupt Mask Register (ADC_IMR)     | 427   |

|    | 17.5  | ADC register map                              | . 429 |

| 18 | JTAG  | interface & Debug features                    | . 430 |

|    | 18.1  | Overview                                      |       |

|    | 18.2  | Debug system                                  |       |

|    | 18.3  | Debug Host                                    |       |

|    |       | •                                             |       |

|    | 18.4  | Protocol Converter                            |       |

|    | 18.5  | ARM7TDMI-S                                    |       |

|    | 18.6  | ARM7TDMI-S Debug Interface                    | . 431 |

|    | 18.7  | Debugging applications with low power modes   | . 431 |

|    | 18.8  | Debug & Timers                                | . 432 |

|    | 18.9  | JTAG Interface signals                        | . 433 |

|    |       | 18.9.1 JTAG ID Code                           | 434   |

|    |       | 18.9.2 JTAG and GPIO multiplexing             | 434   |

|    |       | 18.9.3 Debug mode entry & restrictions        | 434   |

|    | 18.10 | Using RTCK for Debug mode entry               | . 435 |

| 19 | Revis | sion history                                  | . 436 |

# 1 Memory and bus architecture

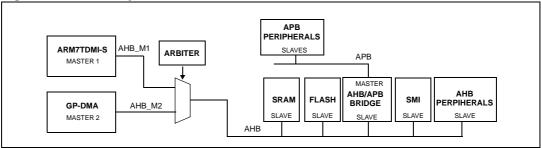

## 1.1 Multi-Layer AHB bus architecture

The main system consists of:

- Two masters:

- ARM7TDMI-S CPU

- GP-DMA (General Purpose DMA)

- Five slaves:

- Internal SRAM

- Internal FLASH

- External SMI (Serial Memory Interface)

- AHB peripheral register interface

- AHB to APB bridge which connects all the APB peripherals

These are interconnected using a Multi-Layer AHB bus architecture as shown in Figure 1:

Figure 1. Multi-Layer AHB bus architecture

The arbitration is implemented in the following way:

- A round robin algorithm is used to arbitrate the two masters

- The arbitration is evaluated after each bus BURST or SEQUENTIAL AHB transfer (a BURST transfer is never cut).

This Bus Matrix achieves "zero idle" cycle access from ARM CPU or DMA to SRAM or FLASH even for nonsequential accesses.

However, the following frequency limitations apply:

- When accessing the flash:

- when not configured in BURST mode, the Flash induces no wait states, but the maximum frequency is limited to 32 MHz

- when configured in BURST mode, the Flash induces 1 wait state for each non sequential access and the maximum frequency is 60 MHz

- The SRAM can be accessed up to 64 MHz with no wait states.

Note: It is up to the user application to ensure that the conditions listed above are respected.

#### **Behavior in ARM DEBUG mode**

When entering DEBUG state (CPU is halted), the Arbiter locks the bus to the ARM7TDMI-S. In the case where the DMA is owner of the bus, then the Arbiter waits for the current transfer before locking the bus to the ARM7TDMI-S.

## 1.2 Memory organization

Program memory, data memory, registers and I/O ports are organized within the same linear address space of 4 GBytes.

The bytes are treated in memory as being in Little Endian format. The lowest numbered byte in a word is considered the word's least significant byte and the highest numbered byte the most significant.

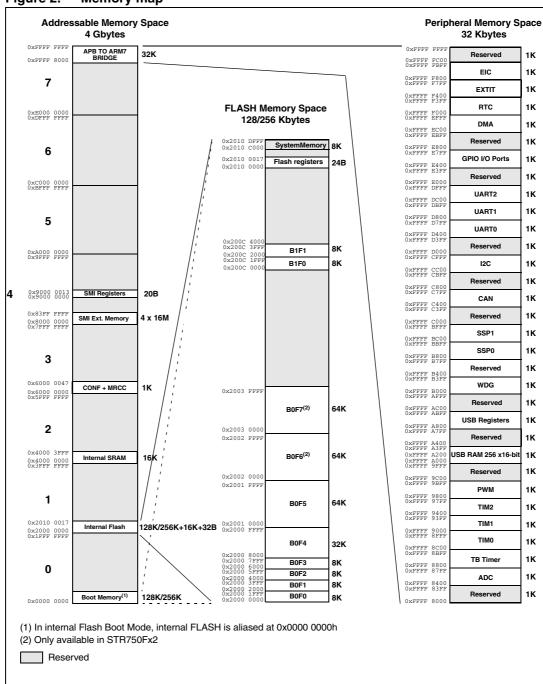

*Figure 2 on page 18* shows the STR750 Memory Map. For the detailed mapping of peripheral registers, please refer to the related chapters.

The addressable memory space is divided into 8 main blocks, selected by the three most significant bits of the memory address bus A[31:0]:

- 000 = Boot Memory: depending on the Boot configuration, it can be aliased to Embedded Flash Memory, embedded Boot loader or Embedded SRAM Memory or External Serial Memory

- 001 = Embedded Flash Memory

- 010 = Embedded SRAM Memory

- 011 = Global Configuration Register and MCU Reset and Clock Control (MRCC)

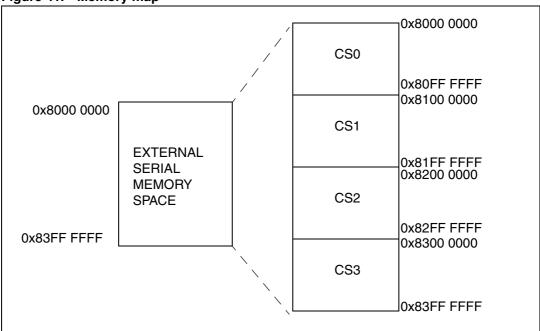

- 100 = External Serial Memory (SMI)

- 101 = Reserved

- 110 = Reserved

- 111 = Peripheral Registers

All memory spaces that are not allocated to on-chip memories and peripherals are considered "reserved" (gray shaded areas in the *Figure 2 on page 18*).

## 1.3 Memory map

Figure 2. Memory map

# 1.3.1 Register base addresses

Table 1. Main Block Register base addresses

| STR750 Main Blocks                      | Bus | Base Address | Block Register Map                                |

|-----------------------------------------|-----|--------------|---------------------------------------------------|

| Flash Registers                         | АНВ | 0x2010 0000  | See STR7 Flash<br>Programming Reference<br>Manual |

| Configuration Register (CFG)            | AHB | 0x6000 0000  | Section 1.5.2                                     |

| MCU Reset and Clock Control (MRCC)      | AHB | 0x6000 0020  | Section 2.10.8                                    |

| Serial Memory Interface Registers (SMI) | AHB | 0x9000 0000  | Section 6.6                                       |

# 1.3.2 Peripheral memory map

Table 2. Peripheral memory map

|             | able 2. Peripheral memory map    |                |     |                                     |                        |               |  |

|-------------|----------------------------------|----------------|-----|-------------------------------------|------------------------|---------------|--|

| Sub<br>Page | SubPage<br>Boundary<br>Addresses | Peripheral     | Bus | Peripheral<br>Boundary<br>Addresses | Bus<br>Access<br>Width | Register Map  |  |

| 0           | 0xFFFF 8000                      | reserved       |     |                                     |                        |               |  |

|             | 0xFFFF 83FF                      | reserved       | -   |                                     |                        |               |  |

| 1           | 0x FFFF 8400                     | ADC            | APB | 0x FFFF 8400                        | - 16-bit               | Section 17.5  |  |

| !           | 0x FFFF 87FF                     | ADC            | AFD | 0xFFFF 848F                         | 16-011                 | Section 17.5  |  |

| 2           | 0x FFFF 8800                     | TB Timer       | APB | 0x FFFF 8800                        | 16-bit                 | Section 9.7   |  |

|             | 0x FFFF 8BFF                     | - 16 Hiller    | APD | 0xFFFF 88BF                         | וט-טונ                 | Section 9.7   |  |

| 0           | 0x FFFF 8C00                     | TIM Time on O  | ADD | 0x FFFF 8C00                        | 10 hit                 | Section 10.11 |  |

| 3           | 0x FFFF 8FFF                     | TIM Timer 0    | APB | 0xFFFF 8C5F                         | 16-bit                 | Section 10.11 |  |

| 4           | 0x FFFF 9000                     | TINA Time and  | APB | 0x FFFF 9000                        | 16-bit                 | Section 10.11 |  |

| 4           | 0x FFFF 93FF                     | TIM Timer 1    |     | 0xFFFF 905F                         |                        | Section 10.11 |  |

| 5           | 0x FFFF 9400                     | TIM Timer 2    | APB | 0x FFFF 9400                        | 16-bit                 | Section 10.11 |  |

| 5           | 0x FFFF 97FF                     | - Hivi Himer 2 |     | 0x FFFF 945F                        | 10-011                 | Section 10.11 |  |

| 6           | 0x FFFF 9800                     | DIAMA ADD      |     | 0x FFFF 9800                        | 16 hit                 | Coation 11 11 |  |

| 6           | 0x FFFF 9BFF                     | PWM            | APB | 0x FFFF 985F                        | - 16-bit               | Section 11.11 |  |

| 7           | 0x FFFF 9C00                     | rocorned       |     |                                     |                        |               |  |

| '           | 0x FFFF 9FFF                     | reserved       | -   |                                     |                        |               |  |

| 8           | 0x FFFF A000                     | USB RAM        | APB |                                     | 16-bit                 |               |  |

| 0           | 0x FFFF A3FF                     | OSD NAIVI      | AFD |                                     | 16-01                  |               |  |

| 9           | 0x FFFF A400                     | reserved       |     |                                     |                        |               |  |

| 9           | 0x FFFF A7FF                     | 16961 Veu      | -   |                                     |                        |               |  |

| 10          | 0x FFFF A800                     | USB            | APB | 0x FFFF A800                        | - 16-bit               | Section 16.7  |  |

| 10          | 0x FFFF ABFF                     | Registers      | ALD | 0x FFFF A853                        | 10-011                 | Section 16.7  |  |

Table 2. Peripheral memory map (continued)

| Sub<br>Page    | SubPage<br>Boundary<br>Addresses | Peripheral | Bus    | Peripheral<br>Boundary<br>Addresses | Bus<br>Access<br>Width | Register Map |

|----------------|----------------------------------|------------|--------|-------------------------------------|------------------------|--------------|

| 11             | 0x FFFF AC00                     | rocomicad  |        | 0x FFFF AC00                        | 16 hit                 |              |

| 11             | 0x FFFF AFFF                     | reserved   | -      | 0x FFFF AFFF                        | - 16-bit               |              |

| 12             | 0x FFFF B000                     | WDG        | APB    | 0x FFFF B000                        | 16-bit                 | Section 8.5  |

| 12             | 0x FFFF B3FF                     | - WDG      | AID    | 0x FFFF B01B                        | 10-51                  | Section 6.5  |

| 13             | 0x FFFF B400                     | reserved   | _      |                                     |                        |              |

| 13             | 0x FFFF B7FF                     | - reserveu | -      |                                     |                        |              |

| 14             | 0x FFFF B800                     | - SSP0     | APB    | 0x FFFF B800                        | 16-bit                 | Section 14.4 |

| 14             | 0x FFFF BBFF                     | 3370       | AFD    | 0x FFFF B827                        | TO-DIL                 | Section 14.4 |

| 15             | 0x FFFF BC00                     | - SSP1     | APB    | 0x FFFF BC00                        | 16-bit                 | Section 14.4 |

| 13             | 0x FFFF BFFF                     | 001 1      | AID    | 0x FFFF BC27                        | 10-51                  | Occilon 14.4 |

| 16             | 0x FFFF C000                     | reserved   | _      |                                     |                        |              |

| 10             | 0x FFFF C3FF                     | - leserveu |        |                                     |                        |              |

| 17             | 0x FFFF C400                     | CAN        | APB    | 0x FFFF C400                        | 16 bit                 | Section 12.6 |

| 17             | 0x FFFF C7FF                     | OAN        |        | 0x FFFF C57F                        | TO Dit                 | Occilor 12.0 |

| 18             | 0x FFFF C800                     | reserved   | _      |                                     |                        |              |

| 10             | 0x FFFF CBFF                     | reserved - |        |                                     |                        |              |

| 19             | 0x FFFF CC00                     | - I2C      | APB    | 0x FFFF CC00                        | 8-bit                  | Section 13.6 |

| 10             | 0x FFFF CFFF                     | 120        | AID    | 0x FFFF C01F                        | O Dit                  | Occilor 10.0 |

| 20             | 0x FFFF D000                     | reserved   | _      |                                     |                        |              |

| 20             | 0x FFFF D3FF                     | 10301 VCG  |        |                                     |                        |              |

| 21             | 0x FFFF D400                     | - UARTO    | APB    | 0x FFFF D400                        | 16 bit                 | Section 15.5 |

|                | 0x FFFF D7FF                     | 0/11110    | 711 15 | 0x FFFF D44B                        | 10 511                 | Coolien 10.0 |

| 22             | 0x FFFF D800                     | - UART1    | APB    | 0x FFFF D800                        | 16 bit                 | Section 15.5 |

|                | 0x FFFF DBFF                     |            | , ,, , | 0x FFFF D84B                        |                        | 200          |

| 23             | 0x FFFF DC00                     | UART2      | APB    | 0x FFFF DC00                        | 16 bit                 | Section 15.5 |

|                | 0x FFFF DFFF                     | 3,         | , ,, , | 0x FFFF DC4B                        |                        | 200          |

| 24             | 0x FFFF E000                     | reserved   | _      |                                     |                        |              |

| 4 <del>4</del> | 0x FFFF E3FF                     | 10001 VGU  | -      |                                     |                        |              |

| Sub<br>Page | SubPage<br>Boundary<br>Addresses | Peripheral    | Bus  | Peripheral<br>Boundary<br>Addresses | Bus<br>Access<br>Width | Register Map  |  |

|-------------|----------------------------------|---------------|------|-------------------------------------|------------------------|---------------|--|

|             |                                  | GP I/O - Port | APB  | 0x FFFF E400                        |                        |               |  |

|             |                                  | 0             | AFD  | 0x FFFF E413                        |                        |               |  |

|             |                                  | GP I/O        | APB  | 0x FFFF E420                        |                        |               |  |

| 25          | 0x FFFF E400                     | Remap         | כו   | 0x FFFF E427                        | 32 bit                 | Section 3.2.8 |  |

| 23          | 0x FFFF E7FF                     | GP I/O - Port | APB  | 0x FFFF E440                        | 32 bit                 |               |  |

|             |                                  | 1             |      | 0x FFFF E453                        |                        |               |  |

|             |                                  | GP I/O - Port | APB  | 0x FFFF E480                        |                        |               |  |

|             |                                  | 2             |      | 0x FFFF E493                        |                        |               |  |

| 26          | 0x FFFF EC00                     | DMA           | AHB  | 0x FFFF EC00                        | 16 bit                 | Section 5.6   |  |

| 20          | 0x FFFF EFFF                     | DIVIA AND     |      | 0x FFFF ECFF                        | TO DIL                 | Section 5.0   |  |

| 27          | 0x FFFF F000                     | RTC           | APB  | 0x FFFF F000                        | 16 bit                 | Section 7.5   |  |

| 21          | 0x FFFF F3FF                     | 1110          | APD  | 0x FFFF F027                        | TO DIL                 | Section 7.5   |  |

| 26          | 0x FFFF F400                     | EXTIT         | APB  | 0x FFFF F400                        | 32 bit                 | Section 4.8.7 |  |

| 20          | 0x FFFF F7FF                     | LAIII         | AFD  | 0x FFFF F40F                        | 32 DIL                 | Section 4.8.7 |  |

| 27          | 0x FFFF F800                     | EIC           | AHB  | 0x FFFF F800                        | 32 bit                 | Section 4.7   |  |

| 21          | 0x FFFF FFFF                     | LIO           | AITD | 0x FFFF F8DF                        | JZ UIL                 | Section 4.7   |  |

Table 2. Peripheral memory map (continued)

### 1.3.3 Embedded SRAM

The STR750 features 16 KBytes of static SRAM. It can be accessed as bytes, half-words (16 bits) or full words (32 bits). The SRAM start address is 0x4000 0000.

You can remap the SRAM on-the-fly to Block 000, using the SW\_BOOT bits in the CFG\_GLCONF register. In SRAM boot mode, the RAM start address is mapped both at 0x0000 0000h and at 0x4000 0000h.

This is particularly useful for managing interrupt vectors and routines, you can copy them to SRAM, modify and access them even when Flash is not available (i.e. during Flash programming or erasing).

#### 1.3.4 Embedded Flash

The high performance Flash Module has the following key features:

- 256 KB Single Voltage Flash Program Memory + 16 KB parameters

- Dual bank architecture for Read-While-Write (RWW) capability

- Bank 0 : up to 256KB organized in 8 sectors for program memory + SystemMemory sector for ICP

- Bank 1:16 KB for parameters (reprogrammable by the software stored in Bank 0)

- Access at up to 32 MHz with zero wait states when burst mode not used

- Access at up to 60 MHz using burst mode (60 MHz with zero wait states for sequential access and with one wait state for random accesses)

- Access up to up 16 MHz for Read While Write (RWW) accesses (when code executed from Bank 0 reprograms Bank 1).

- Readout protection (program code can only be executed but cannot be dumped out)

- Independent Write protection for each sector of the two banks

- In Circuit Programming (ICP) for programming the embedded flash without using JTAG

Debug features. This is performed by using the embedded Boot Loader located in the Flash SystemMemory sector

- In Application Programming for reprogramming any flash sectors except the boot sector by the user program itself.

The embedded Flash Module consists of two banks (Bank 0 and Bank 1) and is organized in sectors as shown in *Table 3*.

Table 3. Flash module organisation

| Bank                       | Sector                       | Addresses               | Size (bytes)       |

|----------------------------|------------------------------|-------------------------|--------------------|

|                            | Bank 0 Flash Sector 0 (B0F0) | 0x00 0000 - 0x00 1FFF   | 8K                 |

|                            | Bank 0 Flash Sector 1 (B0F1) | 0x00 2000 - 0x00 3FFF   | 8K                 |

| Bank 0                     | Bank 0 Flash Sector 2 (B0F2) | 0x00 4000 - 0x00 5FFF   | 8K                 |

| 256 Kbytes                 | Bank 0 Flash Sector 3 (B0F3) | 0x00 6000 - 0x00 7FFF   | 8K                 |

| Program                    | Bank 0 Flash Sector 4 (B0F4) | 0x00 8000 - 0x00 FFFF   | 32K                |

| Memory                     | Bank 0 Flash Sector 5 (B0F5) | 0x01 0000 - 0x01 FFFF   | 64K                |

|                            | Bank 0 Flash Sector 6 (B0F6) | 0x02 0000 - 0x02 FFFF   | 64K <sup>(1)</sup> |

|                            | Bank 0 Flash Sector 7 (B0F7) | 0x03 0000 - 0x03 FFFF   | 64K <sup>(1)</sup> |

| Bank 1                     | Bank 1 Flash Sector 0 (B1F0) | 0x0C 0000 - 0x0C 1FFF   | 8K                 |

| 16 Kbytes<br>Data Memory   | Bank 1 Flash Sector 1 (B1F1) | 0x0C 2000 - 0x0C 3FFF   | 8K                 |

| Flash Control<br>Registers | Flash Control/Data Registers | 0x10 0000 - 0x0010 0017 | 24                 |

| System Flash               | Boot Loader                  | 0x10 C000 - 0x0010 C7FF | 2K                 |

| Memory                     | Reserved                     | 0x10 C800 - 0x0010 DFFF | 6K                 |

<sup>1.</sup> Not available in 128K versions.

#### **RWW** operation

The user must respect the following conditions for proper RWW operation:

The CPU clock frequency is maximum 16 MHz and burst mode must be disabled.

#### Flash programming

You can program Flash memory using In-Circuit Programming (ICP) and In-Application programming (IAP).

ICP can be performed in two ways:

- using the JTAG interface : the debugger tool can re-program the Flash though the JTAG interface by:

- Halting the CPU

- Downloading the SRAM with the flash program/erase routines

- Jump to the SRAM to execute these routines which reprogram the flash.

This can be done whatever the selected Boot mode.

Using a UART: it is possible to re-program the flash using a simple serial interface (UART) when SystemMemory Boot mode is selected.

IAP can be performed directly by the user program: the user is free to choose any protocols using any available communication peripherals to provide the datas to reprogram some sectors of the flash. For this, the flash program/erase routines must be embedded in the user code.

#### Caution:

In IAP mode it is highly recommended to write protect the boot sector (B0F0) to avoid any unrecoverable situations (like erasure of the boot sector)

#### Flash protection

The embedded Flash memory can be protected against unwanted access (read/write/erase).

The protection bits are stored in non-volatile Flash cells.

Two kind of protections are available: sector *Write protection* to prevent unwanted write access and *Readout Protection* to avoid software piracy:

Write protection: Each sectors can be independently write protected by writing the corresponding bit of a non-volatile register (FLASH\_FNVWPAR).

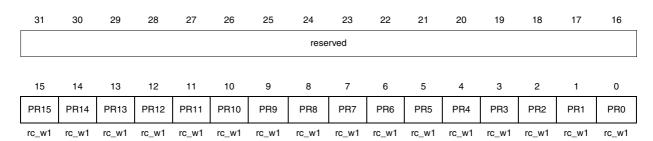

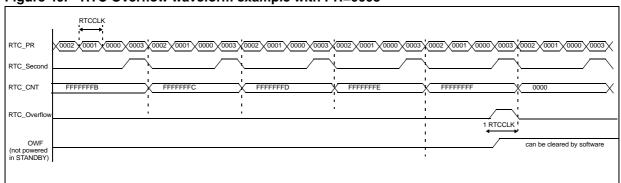

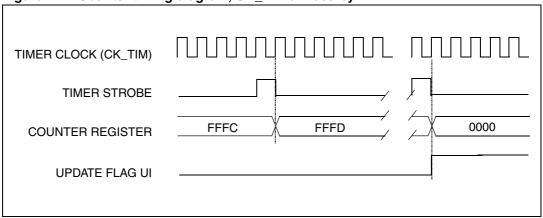

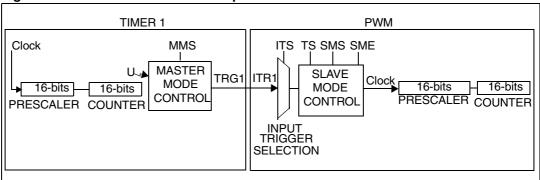

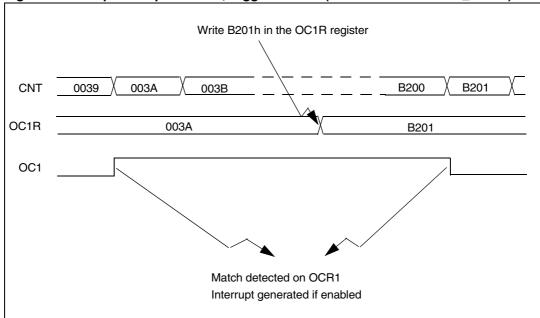

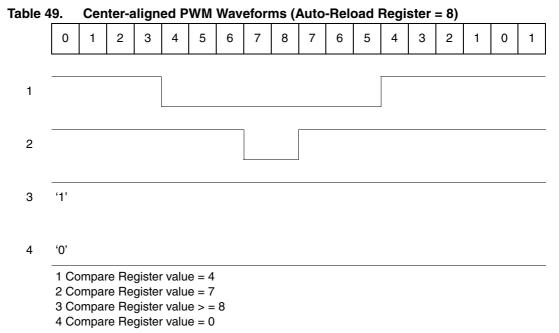

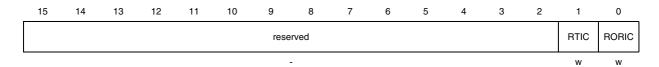

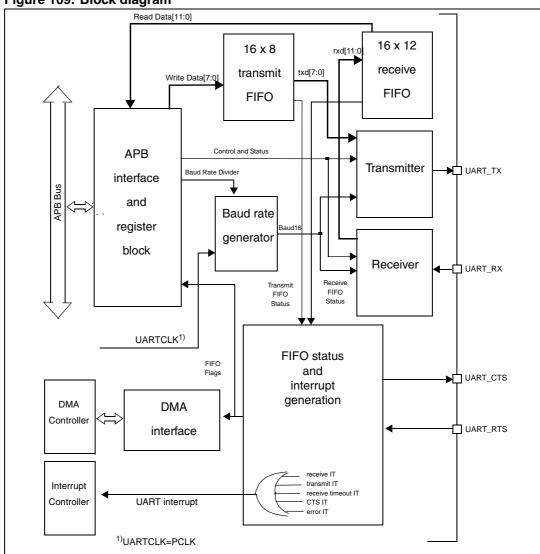

The write protection will be permanent after each Reset, but can be temporarily unprotected by a dedicated sequence.