## 3 V input, 70 V output, fully integrated hybrid charge pump

By Francesco Pulvirenti

#### **Abstract**

A novel integrated-circuit charge pump (CP) voltage multiplier conceived for high multiplying factors is proposed. The solution exploits a mixed architecture, which merges both Cockcroft-Walton and Dickson topologies, by using on-chip 12 V poly-poly capacitors and 3.3 V CMOS transistors, maximizing the output voltage at the minimum silicon size. The proposed CP has been designed to supply a fully integrated driver for miniaturized motors in Micro Electro Mechanical Systems (MEMS) technology. It is conceived to boost the power supply voltage to values higher than those that either Dickson (D), Fibonacci (F), Cockroft-Walton (CW) or Serial-Parallel (SP) fully integrated CPs can generate in the selected technology process. Indeed, the output voltage of the former two CPs is limited by voltage constraints of on-chip capacitors while the multiplication efficiency of the latter two is impacted by high values of on-chip stray capacitors. Specifically, the target > 70 V output voltage has to be internally generated starting from the provided minimum power-supply voltage of 3 V. Furthermore, a mathematical model is proposed to evaluate the open load output voltage and the equivalent output resistance.

#### **Index terms**

Charge Pumps, Voltage Multipliers, Cockcroft-Walton CP, Dickson CP, Fibonacci CP, Serial-Parallel CP.

#### 1 Introduction

The first voltage multiplier was published by Schenkel in 1919 [1.] with discrete capacitors and valve diodes. A few years later, in 1923, Marx filed a patent application [2.] describing a voltage multiplier based on Serial to Parallel architecture implemented with discrete capacitors, very high value resistances and spark gap switches for generating high surge voltages. In 1932, Cockcroft and Walton [3.] proposed a new voltage multiplier for generating voltages greater than those achievable with the Schenkel circuit, up to several million volts, those which could be easily handled by electromagnetic transformers for production of high velocity positive ions, using capacitors with lower operative range.

In this type of application, however, the discrete capacitors can be made sufficiently large for efficient multiplication and adequate current capability while on-chip capacitors have maximum values of a few hundred pF and relatively high stray capacitances; as a result, initially, the mentioned CPs did not have broad application in integrated circuits because they were very sensitive to the stray capacitances. Subsequently, in 1973, a CP based on the Schenkel topology, that is quite insensitive to parasitic capacitances, was patented for the first time in a monolithic form by Luscher [4.] who replaced the valves with MOS diodes. This circuit became very popular with the article published by Dickson in 1976 [5.] and is better known as the Dickson multiplier. Another popular CP using MOS switches was published by Ueno et al. in 1991 [6.], called the Fibonacci multiplier because the generated output voltage is proportional to the Fibonacci sequence.

In the last three decades, on-chip CPs, mainly based on the Dickson architecture insensitive to the bottom stray capacitance, have been widely used in smart power ICs for driving the output power transistors, in non-volatile memory circuits for programming and erasing memory cells, and in low-voltage applications such as energy harvesting [7.] - [10.].

On the other hand, as anticipated, the Cockcroft-Walton multiplier has been used for those applications where high voltages are requested; more specifically, in converters with AC input for low-current applications and when a high-voltage transformer winding is not convenient [11.] - [16.].

TA0363 - Rev 1 page 2/31

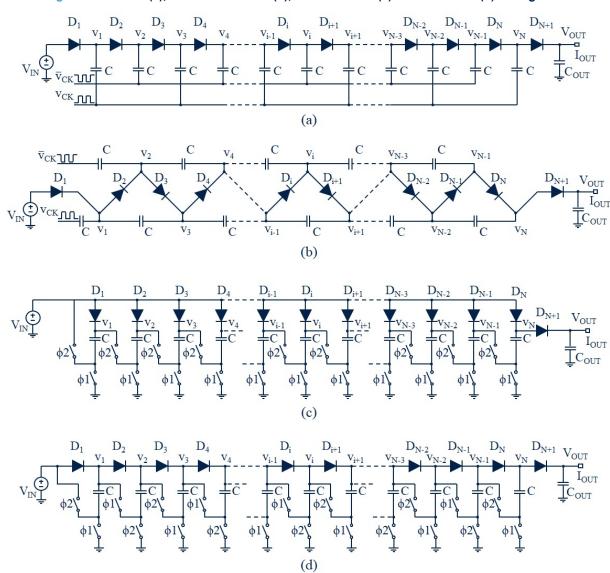

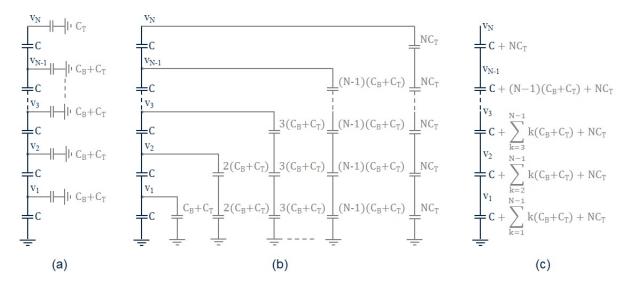

Figure 1. Dickson (a), Cockcroft-Walton (b), Serial-Parallel (c) and Fibonacci (d) N-stage CPs.

More recently, Serial-Parallel [17.] - [19.] and Fibonacci CPs [20.] - [25.] have been employed for lower voltage applications in discrete and monolithic solutions, as well as new Hybrid CPs, based on a combination of Cockcroft-Walton and Dickson architectures, described in [26.] - [28.]. Also notable is the new on-chip Hybrid CP in which a configurable architecture of Cockcroft-Walton and Dickson stages have been devised for extremely low-voltage applications [29.] - [30.].

In this paper, a novel charge pump to supply a fully integrated driver for miniaturized motors in MEMS technology is proposed. In this application, the multiplied voltage gain and the voltage efficiency are key parameters, while the power efficiency is not relevant due to the very low driving current, a few dozen  $\mu$ A, required to drive the motors.

Unlike previous Hybrid CPs [19.], [26.] - [30.], where two different topologies are cascaded in series, the proposed CP merges both Dickson and Cockcroft-Walton topologies and has a completely new arrangement of the pumping capacitors which allows for the uniform distribution of the voltage on them, minimizing the stress and maximizing the multiplication factors, otherwise unfeasible with previous CPs. Indeed, a 24-stage dual branch CP, with each pumping capacitor of 25 pF, was designed and fabricated in 0.35-µm STMicroelectronics BCD process. It was demonstrated that, starting from a 3 V supply, an output voltage higher than 70 V can be achieved by using medium-voltage on-chip capacitors and low-voltage CMOS transistors.

TA0363 - Rev 1 page 3/31

The paper is organized as follows. Section 2 summarizes the most conventional CPs. Section 3 describes the different configurations of the proposed CP, the working principle, and a comparison of the key parameters with the most popular CPs. Section 4 illustrates the proposed CP including stray capacitors and demonstrates the matching of the mathematical model with simulation results. Section 5 describes the physical implementation. Section 6 shows the measurement results comparing the performance with previous works and highlighting the pros and cons. Finally, Section 7 summarizes the author's conclusions and Section Appendix A reports the mathematical analysis.

TA0363 - Rev 1 page 4/31

## 2 Most conventional charge pumps

The most popular CPs [30.] - [39.] with arbitrary N-stage are shown in Figure 1. They consist of N pumping (coupling or flying) capacitors C that pump the charge from the input to the output, one storage capacitor  $C_{OUT}$  that stores the charge and makes stable the voltage at the output node  $V_{OUT}$ , N + 1 diodes and, for the last two CPs, 2N switches properly driven that transfer the charge in only one direction towards the output node.

Even though the Serial-Parallel and Fibonacci CPs are commonly described with switches only, here they are drawn with diodes for uniformity with the other two CPs. The principle of operation, although well known, is summarized below. For the Dickson and Cockcroft-Walton CPs the pumping capacitors, driven by two clocks in anti-phase, are alternatively charged during each half period of the clock cycle. So, charge packets are pumped through the diode chain boosting up the output node. For the Serial-Parallel CP the pumping capacitors are all charged in parallel through the diodes and then connected in serial through the switches to transfer the charge to the output node. For the Fibonacci CP the pumping capacitors are alternatively charged through the diodes and connected among them through the switches to boost up the output node.

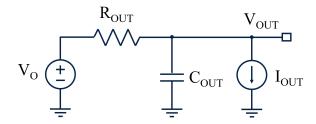

Figure 2 shows the simple equivalent circuit of a CP, where  $V_O$  is the voltage generated in an open load condition, and  $R_{OUT}$  is the equivalent output resistance.

Figure 2. CP equivalent circuit.

From the equivalent circuit, the output voltage  $V_{OUT}$  can be obtained.

$$V_{OUT} = V_O - R_{OUT} \cdot I_{OUT} \tag{1}$$

Parameters of Eq (1) are summarized below for all the above-mentioned CPs, while detailed mathematical analyses are reported in Section Appendix A . Hence, the open load output voltage in ideal operating condition, that happens when parasitic capacitances are negligible, is

$$V_{O, ideal} = \begin{cases} V_{IN} - (N+1)V_D + NV_{CK} & D, CW \\ V_{IN} - (N+1)V_D + NV_{IN} & SP \\ V_{IN} - \left(\sum_{i=1}^{N+1} F_i - 1\right)V_D + \sum_{i=1}^{N} F_i V_{IN} & F \end{cases}$$

(2)

where  $V_{IN}$  is the input voltage of the circuit,

$V_{CK}$  is the swing voltage of the clock signals,

$V_D$  is the forward voltage drop of the diodes,

f is the clock or switching frequency,

$F_i$  is the *i*-th element in the Fibonacci series.

$V_{O,ideal}$  matches with results of Eq (7) reported in [5.] for Dickson CP without top stray capacitor, with results of Eq(11) in [12.] for Serial-Parallel CP replacing diodes with switches, and with results of Eq (2) in [24.] for Fibonacci CP replacing diodes with switches.

The equivalent output resistance calculated in ideal operating conditions and in Slow Switching Limit (SSL), that occurs when the clock period is much longer than the time constant associated with the resistance of the diodes and the capacitance of the pumping capacitors, is

TA0363 - Rev 1 page 5/31

$$R_{OUT,ideal} = \begin{cases} \frac{1}{f \cdot c} N & D, SP \\ \frac{1}{f \cdot c} \cdot 2\sum_{i=1}^{N} i^{2} & CW N even \\ \frac{1}{f \cdot c} \cdot \left[\sum_{i=1}^{N+1} i^{2} + \sum_{i=1}^{N-1} i^{2}\right] CW N odd \\ \frac{1}{f \cdot c} \cdot \sum_{i=1}^{N} F_{i}^{2} & F \end{cases}$$

(3)

$R_{OUT,ideal}$  matches with results of Eq (8) reported in [5.] for Dickson CP without top stray capacitor, with results of Eq(11) in [12.] for Serial-Parallel CP, and with results of Eq(39) in [25.] for Fibonacci CP.

It can be observed that, for  $V_{CK} = V_{IN}$  and N = 2, all CPs have the same  $V_{O,ideal}$  and the same  $R_{OUT,ideal}$ .

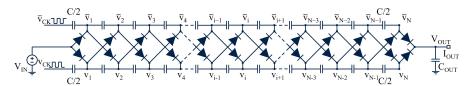

As known, these CPs can be also implemented in a Dual Branch (DB) architecture with the advantage that the voltage ripple on the output node, as well as the current peaks in the capacitors and diodes, are halved. Moreover, if the value of the pumping capacitors is halved with respect to the Single Branch (SB) configuration, the total amount of capacitance does not change since in the dual branch architecture there are  $2N \cdot C/2$  capacitors, while in the single branch there are  $N \cdot C$  capacitors. That said, it is known that for the Dickson, Serial-Parallel and Fibonacci dual branch CPs the open load output voltage and the equivalent output resistance remain the same as those reported in Eq (2) and Eq (3), while, for the dual branch Cockcroft-Walton CP, shown in Figure 3, only  $R_{OUT,ideal}$  changes as given in

$$R_{OUT, ideal} = \frac{1}{f \cdot C} \sum_{i=1}^{N} i^{2} \quad CW DB$$

(4)

In fact, it is worth noting that the dual branch architecture is by construction completely symmetric and for this reason Eq (4) is valid for both N even and odd. Moreover, for a given number N of stages, this architecture has a double number of pumping capacitors per branch with the benefit that the voltage across each pumping capacitor is halved compared to that of the single branch architecture. On the contrary, the equivalent output resistance is much higher because it grows dramatically with the number of stacked pumping capacitors.

Figure 3. Cockcroft-Walton N-stage CP in a DB architecture

As anticipated, on-chip CPs have relatively high values of stray capacitances, which impact the output voltage. More specifically, top plate parasitic capacitors are only considered in the Dickson CP, as bottom plate stray capacitors impact the current consumption only, because they load the clock lines. Instead, in the Cockcroft-Walton, Serial-Parallel and Fibonacci CPs, both bottom plate and top plate parasitic capacitors have to be considered. In his original paper, Dickson wrote that the Cockcroft-Walton CP has two main limitations:

- 1. Efficient multiplication occurs only if the pumping capacitors are much greater than the stray capacitors.

- The output impedance increases rapidly with the number of multiplying stages.

The first limit appears also evident from Eq (A9), where the influence of the top and bottom stray capacitors on the output voltage grows rapidly with the power of *N*. In fact, as the pumping capacitors are connected in series, it is hard to generate significantly high voltages if the number of multiplying stages is increased beyond a critical limit, which typically consists of a few units, heavily dependent on the ratio between the stray and pumping capacitors. The second item, according to Eq (A10), has a direct impact on the silicon size in a monolithic integrated circuit implementation, since the total area of pumping capacitors of the Cockcroft-Walton CP increases dramatically with the number of multiplying stages.

On the contrary, the Dickson CP, when implemented in a monolithic integrated circuit, in some circumstances is not always feasible due to the well-known voltage limitations of on-chip capacitors. In fact, low-voltage MOS capacitors, always available, limit the maximum voltage generated by the CP while high-voltage capacitors like Metal Oxide Metal (MOM) are not so common and, when available, have very low specific value and cannot cover large silicon areas because oxide defects cannot be screened out efficiently [40.].

TA0363 - Rev 1 page 6/31

The Serial-Parallel CP, like the Cockcroft-Walton one, is another architecture sensitive to parasitic capacitances as well as capable of using pumping capacitors with low-voltage stress ratings but both switches and diodes are progressively subjected to high voltages getting closer to the output node.

The Fibonacci CP offers the highest possible boosting ratio for a given *N* and, with an equal area occupation, it has similar performance in many aspects compared to the Dickson one in ideal operating conditions [32.]. However, it has the same limitation in that the voltage stress on pumping capacitors increases progressively getting closer to the output node. Furthermore, like the Serial-Parallel CP, the switches and diodes are progressively subjected to high voltages and the multiplication efficiency is heavily impacted by both top and bottom stray capacitors.

TA0363 - Rev 1 page 7/31

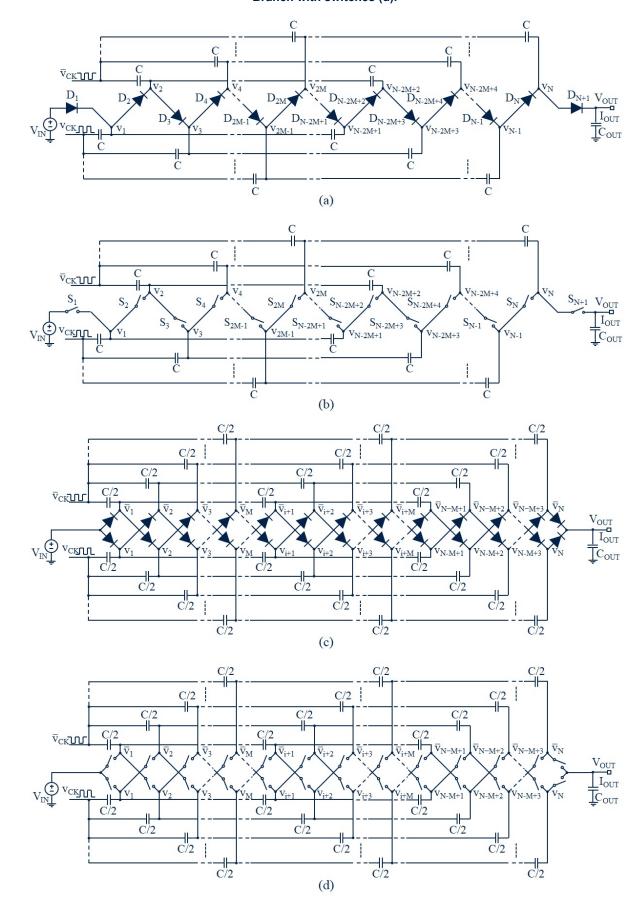

## 3 Proposed charge pump

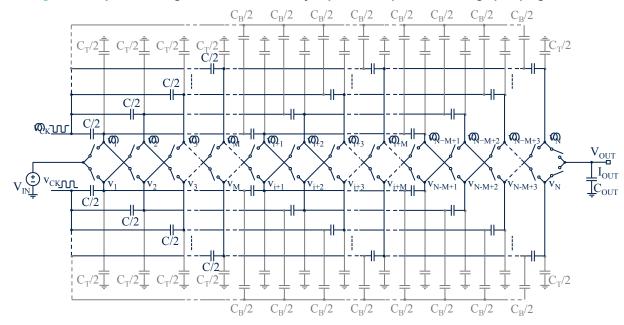

To overcome the above mentioned limitations, a novel hybrid architecture which merges both Cockcroft-Walton and Dickson CPs is proposed. Differently from the other Hybrid CPs, described in [19.] and [26.]-[30.], where two different topologies are cascaded in series, this solution minimizes the stress on the pumping capacitors, thanks to the uniform distribution of the voltage on them. For example, in [29.]-[30.] the voltage on the capacitors of the Dickson stages grows as they get closer to the output node. The mix between the two topologies can be freely chosen in such a way to select any kind of on-chip capacitors exploiting the maximum voltage capability. Indeed, medium voltage on-chip capacitors, like Metal Insulator Metal (MIM) and Poly-Poly (P1P2) capacitors, have very low stray capacitances and are usually present in many technology platforms. Different configurations of the proposed novel architecture are shown in Figure 4.

Referring to the first option, that is, the single branch with diodes of Figure 4, the pumping capacitors are divided into N/M clusters. In the first two clusters, the capacitors connected to the nodes from  $v_1$  to  $v_{2M}$  have the lower terminal connected to the clock signals, like in the Dickson CP, and the higher terminal connected to the diode chain, progressively towards the output. In the intermediate clusters, the pumping capacitors are stacked on the previous ones, like in the Cockcroft-Walton CP; they have the lower terminal connected to the higher terminal of the previous two clusters of capacitors and the higher terminal connected to the diode chain, progressively towards the output. Similarly, in the last two clusters, the pumping capacitors are stacked on the previous ones, having the lower terminal connected to the higher terminal of the previous two clusters of capacitors and the higher terminal connected to the diode chain, progressively towards the output. To summarize, the pumping capacitors belonging to their own cluster are in parallel like in the Dickson CP, while they appear stacked among different clusters like in the Cockcroft-Walton CP.

TA0363 - Rev 1 page 8/31

Figure 4. Proposed N-stage CP with diodes (a), with switches (b), Dual Branch with diodes (c), and Dual Branch with switches (d).

TA0363 - Rev 1 page 9/31

The operation is similar to the other CPs. In the first half clock period, when  $v_{CK}$  is low and  $\bar{v}_{CK}$  is high, the pumping capacitors driven by  $v_{CK}$  are charged to a more positive voltage. They receive the charge packets through the odd diodes from the pumping capacitors driven by  $\bar{v}_{CK}$ , which are contextually discharged. In this phase, the first pumping capacitor is directly charged from the input voltage. In the second half clock period, when  $v_{CK}$  is high and  $\bar{v}_{CK}$  is low, the pumping capacitors driven by  $v_{CK}$  are discharged. They provide the charge packets through the even diodes to the pumping capacitors driven by  $\bar{v}_{CK}$ , which are contextually charged to a more positive voltage.

Referring to the first cluster of pumping capacitors driven by  $v_{CK}$ , it can be observed that the first pumping capacitor is charged to  $V_{IN}$  -  $V_D$ , the third one is charged to  $V_{IN}$  +  $2V_{CK}$  -  $3V_D$ , the fifth one is charged to  $V_{IN}$  +  $4V_{CK}$  -  $5V_D$ , and so on, up to the (2M-1)-th pumping capacitor that is charged to  $V_{IN}$  +  $(2M-2) \cdot V_{CK}$  -  $(2M-1) \cdot V_D$ . Additionally, referring to the second cluster of pumping capacitors driven by  $\bar{v}_CK$ , it happens that the second pumping capacitor is charged to  $V_{IN}$  +  $V_{CK}$  -  $2V_D$ , the fourth one is charged to  $V_{IN}$  +  $3V_{CK}$  -  $4V_D$ , the sixth one is charged to  $V_{IN}$  +  $5V_{CK}$  -  $6V_D$ , and so on, up to the 2M-th pumping capacitor that is charged to  $V_{IN}$  +  $(2M-1) \cdot V_{CK}$  -  $2M \cdot V_D$ . The pumping capacitors from 2M + 1 to N are all charged to  $2M \cdot (V_{CK} - V_D)$ ; this is the voltage across the two terminals of the capacitors. The output capacitor is charged to  $V_{IN}$  +  $N \cdot V_{CK}$  -  $(N+1) \cdot V_D$  as reported in Eq (2) for the Dickson and Cockcroft-Walton CPs.

It is easy to demonstrate that the equivalent output resistance can be obtained as a combination of a 2M-stage Dickson CP and an N/2M-stage Cockcroft-Walton one, as follows

$$R_{OUT,ideal} = \frac{1}{f \cdot C} \cdot 2M \sum_{i=1}^{N/2M} i^2$$

(5)

The proposed CP can be also implemented in a dual branch architecture, as shown in Figure 4c. The operation is similar to that of the single chain architecture with only a difference related to the voltages across the pumping capacitors, which are now halved. This happens because the architecture is, by construction, completely symmetrical and, for a given N-stage, the number of pumping capacitors is doubled. Also, in this configuration  $R_{OUT}$  can be obtained as a combination of an M-stage Dickson CP and an N/M-stage Cockcroft-Walton one, as follows

$$R_{OUT,ideal} = \frac{1}{f \cdot C} \cdot M \sum_{i=1}^{N/M} i^2$$

(6)

Equations Eq(5) and Eq(6) are respectively valid for N multiple of 2M and N multiple of M, and of course in SSL operating condition. Furthermore, it can be noted that for M = N/2 and M = N the proposed CP, respectively in the single and dual branch architectures, becomes the Dickson CP as well as both Eq (5) and Eq (6) corresponding to Eq (3), (D), while for M = 2 and M = 1 it becomes the Cockcroft-Walton one as well as Eq (5) corresponding to Eq (3), (CW N even) and Eq (6) corresponding to Eq (4).

In a fully monolithic approach, CPs are normally implemented with MOS transistors arranged in several different circuit topologies. They can be either n-channel or p-channel MOS transistors as long as they are properly driven. For this reason, the diodes are replaced with switches as shown in Figure 4b and Figure 4d for single and dual branch architectures. In this design, assuming the voltage drop on the switches is negligible, it is easy to demonstrate that  $R_{OUT}$  remains the same as that expressed in Eq (5) and Eq (6), while  $V_O$  simplifies to

$$V_O = V_{IN} + NV_{CK} \tag{7}$$

Table 1. Charge pump key parameters comparison in ideal conditions

|                                                      | Dickson           | Cockcroft-<br>Walton                     | Dual Branch<br>CW                       | Serial-<br>Parallel     | Equal cap<br>Fibonacci                          | Scaled cap<br>Fibona. [32]                  | Sing<br>Branch<br>Proposed<br>CP    | Dual Branch<br>Proposed<br>CP             |

|------------------------------------------------------|-------------------|------------------------------------------|-----------------------------------------|-------------------------|-------------------------------------------------|---------------------------------------------|-------------------------------------|-------------------------------------------|

| Max. voltage on capacitors                           | N·V <sub>IN</sub> | 2V <sub>IN</sub>                         | V <sub>IN</sub>                         | V <sub>IN</sub>         | F <sub>n</sub> ·V <sub>IN</sub>                 | $F_n \cdot V_{IN}$                          | 2M·V <sub>IN</sub>                  | M·V <sub>IN</sub>                         |

| Max. voltage on switches                             | V <sub>IN</sub>   | V <sub>IN</sub>                          | V <sub>IN</sub>                         | V <sub>OUT</sub>        | V <sub>OUT</sub>                                | V <sub>OUT</sub>                            | V <sub>IN</sub>                     | V <sub>IN</sub>                           |

| Ideal voltage gain G=V <sub>O</sub> /V <sub>IN</sub> | N+1<br>25         | N+1<br>25                                | N+1<br>25                               | N+1<br>25               | F <sub>n+2</sub> 21 <sup>(1)</sup>              | F <sub>n+2</sub> 21 <sup>(1)</sup>          | N+1<br>25                           | N+1<br>25                                 |

| Ideal eq. output resistance R <sub>OUT</sub>         | $\frac{N}{fC}$    | $\frac{2\sum_{i=1}^{N/2}i^2}{fC}$ 812 kΩ | $\frac{\sum_{i=1}^{N} i^2}{fC}$ 3062 kΩ | <u>N</u><br>fC<br>15 kΩ | $\frac{\sum_{i=1}^{n} F_i^2}{fC_n}$ 19.5 kΩ (1) | $\frac{\sum_{i=1}^{n} F_i}{fC}$ 12.5 kΩ (1) | $\frac{2M\sum_{i=1}^{N/2M}i^2}{fC}$ | $\frac{M\sum_{i=1}^{N/M} i^2}{fC}$ 228 kΩ |

TA0363 - Rev 1 page 10/31

|                                                      | Dickson | Cockcroft-<br>Walton              | Dual Branch<br>CW                  | Serial-<br>Parallel | Equal cap<br>Fibonacci                                        | Scaled cap<br>Fibona. [32]               | Sing<br>Branch<br>Proposed<br>CP         | Dual Branch<br>Proposed<br>CP          |

|------------------------------------------------------|---------|-----------------------------------|------------------------------------|---------------------|---------------------------------------------------------------|------------------------------------------|------------------------------------------|----------------------------------------|

| Tot. capacitance ratio: $C_{T}/C_{T\text{-DICKSON}}$ | -<br>1  | $\frac{2\sum_{i=1}^{N/2} i^2}{N}$ | $\frac{\sum_{i=1}^{N} i^2}{N}$ 204 | 1                   | $\frac{C\sum_{i=1}^{n} F_{i}^{2}}{N \cdot C_{n}}$ 1.5 (1) (2) | $\frac{\sum_{i=1}^{n} F_i}{N}$ 1 (1) (2) | $\frac{2M\sum_{i=1}^{N/2M} i^2}{N}$ 4.67 | $\frac{M\sum_{i=1}^{N/M} i^2}{N}$ 15.1 |

1.

$$n = 6$$

2. N = 20

Key elements to be considered for proper design of CP architectures, for a given multiplication voltage gain, are the voltage ratings of the pumping capacitors, the output resistance and the silicon area occupation related to the total capacitance. Table 1 summarizes the factors mentioned for the proposed CP in single and dual branch architecture in comparison with the most popular CPs, given the following assumptions:

- All the architectures are designed with ideal switches and ideal capacitors with unlimited voltage breakdown, without diodes and with  $V_{CK} = V_{IN}$ .

- N = 24 stages, except for the Fibonacci CPs. As known, the voltage gain of the Fibonacci CP corresponds

to the Fibonacci sequence and, for a fair comparison, G = 21 has been selected because it is the closest

voltage gain to 25. G = 21 is obtained with n = 6 stages for the Fibonacci CP and N = 20 stages for the other

CPs

- The ideal output resistance is calculated at the clock frequency f = 32 MHz and pumping capacitors C = 50 pF for SB and C = 25 pF for DB, except for Fibonacci CPs where in the first option the pumping capacitors are N/n = 20/6 bigger than the Dickson's and in the second option the pumping capacitors are scaled according to [32] with the last pumping capacitor equal to the Dickson's.

- The total capacitance ratio is calculated assuming the same output resistance and voltage gain *G* = 25, except for the Fibonacci CPs where *G* = 21.

- The parameter M = 4 has been here arbitrarily set; in the next section the setting criteria is explained.

From this comparison it can be observed that the Dickson, Serial-Parallel and Fibonacci CPs have ideally lower output resistance and smaller area occupation than the Cockcroft-Walton and the proposed Hybrid CPs. For instance, assuming unlimited voltage capability of the pumping capacitors, the area occupation of a 24-stage dual branch Cockcroft-Walton CP is 204 times bigger than the Dickson's, as well as the area occupation of a 24-stage proposed dual branch Hybrid CP being 15.1 times bigger than the Dickson's. On the contrary, the Dickson and Fibonacci CPs require high-voltage capacitors, which obviously in a real case, occupy much larger silicon areas and in many technologies are not available, while high-voltage switches in the Fibonacci and Serial-Parallel CPs limit the switching frequency more than one magnitude order. In fact, applying the switching frequency used in [19.] the equivalent output resistance of the Serial-Parallel CP becomes 192 k $\Omega$ , which is higher than that of the proposed Hybrid CP with single branch architecture.

In conclusion, the proposed architecture has the advantage to minimize the silicon area and the equivalent output resistance, thanks to the following characteristics:

- Flexile configuration to adapt the mix of the stages at any capacitor available in technology platforms, exploiting it at the highest voltage capability. No high-voltage capacitors are required unlike in the Dickson and Fibonacci CPs.

- Use of low-voltage CMOS, which are compact and allow for operation at the highest switching frequency. No high-voltage transistors are required unlike in the Serial-Parallel and Fibonacci CPs.

- Lower impact of parasitic capacitances which allow to obtain higher multiplication gain versus the Cockcroft-Walton CP. This point is thoroughly analyzed in the next section.

TA0363 - Rev 1 page 11/31

# 4 Proposed charge pump with stray capacitors

Parasitic capacitances have relevant impact on performance trade-off; for this reason, the proposed architecture with stray capacitors is here analyzed. For the purpose of brevity, only the single branch with switches is shown in Figure 5.

Figure 5. Proposed N-stage CP with stray capacitors

The open load output voltage and the equivalent output resistance for both single branch and dual branch architectures can be obtained as a combination of the Cockcroft-Walton and Dickson CPs and are summarized below, while the detailed mathematical analysis is reported in Section Appendix A .

$$V_{O} = \begin{cases} V_{IN} + 2M\sum_{i=1}^{N/2M} \prod_{j=1}^{i} \frac{1}{1 + \alpha_{SV}(j)} \cdot V_{CK} & SB \\ V_{IN} + M\sum_{i=1}^{N/M} \prod_{j=1}^{i} \frac{1}{1 + \alpha_{SV}(j)} \cdot V_{CK} & DB \end{cases}$$

(8)

$$R_{OUT} = \begin{cases} \frac{1}{f \cdot C} \cdot 2M \sum_{i=1}^{N/2M} \sum_{j=1}^{i} \frac{N/2M - j + 1}{1 + \alpha_{SR}(j)} & SB \\ \frac{1}{f \cdot C} \cdot M \sum_{i=1}^{N/M} \sum_{j=1}^{i} \frac{N/M - j + 1}{1 + \alpha_{SR}(j)} & DB \end{cases}$$

(9)

with  $\alpha_{SV}(j) = C_{SV}(j)/C$ ,  $\alpha_{SR}(j) = C_{SR}(j)/C$ , where  $C_{SV}(j)$  and  $C_{SR}(j)$ , explicated respectively in (A5) and (A6), represent the contribution of top and bottom plate stray capacitors. If stray capacitors are negligible,  $V_O$  and  $R_{OUT}$  are respectively simplified in Eq.(7), Eq.(5) and Eq.(6).

A specific embodiment can be obtained by using the bottom stray capacitors as pumping elements [30.] as shown in Figure 6.

TA0363 - Rev 1 page 12/31

Figure 6. Proposed N-stage CP with bottom stray capacitors exploited as charge-pumping elements

In this implementation, these capacitors realize a Dickson topology, which works in parallel to the main CP, so that the multiplication efficiency is improved. Of course, this solution introduces other parasitic capacitors connected to the bottom terminal of the stray capacitors which, nevertheless, do not have any impact on the output voltage because they only load the clock lines. The open load output voltage is summarized below

$$V_{O} = V_{IN} + M \sum_{i=1}^{N/M} \prod_{j=1}^{i} \frac{1 + B \cdot \sum_{k=j}^{N/M-1} k}{1 + B \cdot \sum_{k=j}^{N/M-1} k + (N/M-j+1)_{T}} \cdot V_{CK}$$

$$\tag{10}$$

It is easy to demonstrate that the equivalent output resistance is the same as Eq (9, DB). Furthermore, it can be observed that setting to zero the top stray capacitor  $C_T$ , which is normally negligible, Eq (10) becomes equal to Eq (7).

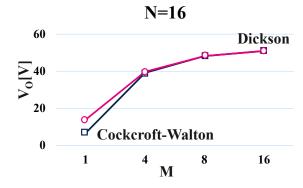

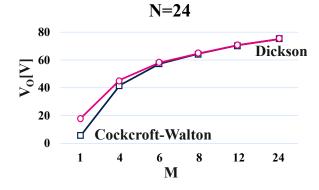

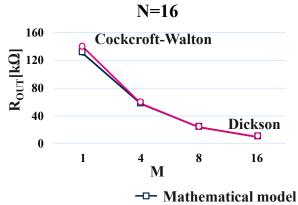

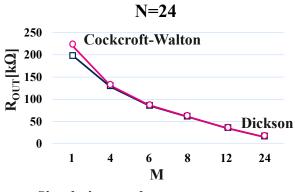

To demonstrate the effectiveness of the mathematical model, the graphs of Figure 7 show the comparison between the theoretical calculation and the simulation results of  $V_O$  in Eq (8, DB) and  $R_{OUT}$  in Eq (9, DB) for the proposed CP in dual branch architecture. The comparison is presented for N = 16 and 24 with different values of M: 1, 4, 6, 8, 12, 16 and 24.

The circuitries have been simulated with ELDO<sup>TM</sup> simulator in CADENCE<sup>TM</sup> framework, with ideal switches,  $V_{IN}$  = 3 V, f = 32 MHz, C = 25 pF,  $_B$  = 6% and  $_T$  = 0.1%. The value of the last two parameters is typical of a P1P2 capacitor.

It can be observed that the open load output voltage increases as M grows, while the equivalent output resistance decreases. This is obvious because, as previously asserted, for M=1 the architecture becomes the Cockcroft-Walton CP, where the parasitic capacitances have an increasing impact on the open load output voltage and N has an increasing impact on the output resistance, while for M=16 (or 24) the architecture becomes the Dickson CP, where  $V_O$  reaches the maximum value and  $R_{OUT}$  reaches the minimum value. In summary, the mathematical model shows a good accuracy and matching with simulation results.

TA0363 - Rev 1 page 13/31

Figure 7. Modeled and simulated VO and ROUT of the proposed CP with 16 and 24 stages for different M

TA0363 - Rev 1 page 14/31

## Implementation of the proposed charge pump

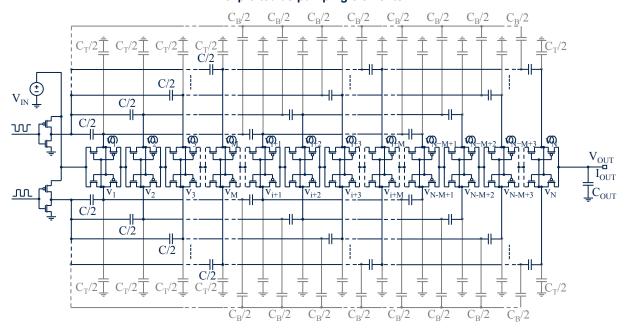

A specific embodiment of the proposed CP in dual branch architecture using MOS transistors in latched configuration and bottom stray capacitors as pumping elements is shown in Figure 8.

Figure 8. Proposed 24-stage CP with MOS transistors in latched topology and bottom stray capacitors exploited as pumping elements

The use of four MOS transistors in latched configuration per each multiplying stage was filed as a patent application by Pulvirenti and Gariboldi in August 1994 [41.] and then published in [42.] and [43.]. This embodiment was later diffused in the literature under the name "latched charge pump". As the operation is well described in the above documents and also in many other papers [8.]-[10.], [34.] it is not further explained here.

As anticipated in the abstract, the proposed CP has been designed to supply a fully integrated driver for miniaturized motors in MEMS technology, where the required 70 V voltage must be internally generated starting from the provided power supply of 3 V. Considering the ratio between the output and input voltages 23.3, the CP is expected to have almost 24 stages. The technology chosen for this project is the STMicroelectronics BCD in 0.35  $\mu$ m lithography with 3.3 V CMOS transistors and 12 V P1P2 capacitor. In this work, M has been set to 4; it is obtained by dividing the maximum voltage capability of the P1P2 capacitor by the power supply voltage, that is 12/3, so that the maximum voltage on the pumping capacitors (that is 4·3 V) never exceeds the operating value, that is 12 V.

To target the specified output resistance of  $130 \text{ k}\Omega$ , each pumping capacitor has the value of C = 25 pF. Furthermore, as in this technology the bottom stray capacitors are isolated from the substrate, hence they have been used as pumping elements, contributing to pumping the charge. Their value is 6% of the 12 V poly-poly capacitance.

To verify the functionality and the simulation results, a test chip has been fabricated as shown in Figure 9.

TA0363 - Rev 1 page 15/31

pumping

(Ck buffer

ESD

prot GND

Figure 9. Layout and die photograph of the proposed Charge Pump with N=24 stages and M=4

To better recognize the blocks, which in the silicon are covered by the metal layers, the layout image has been also enclosed. It consists of the following 3 blocks, the charge pump with 24 latch cells in the middle, 24 pumping capacitors on the left and 24 pumping capacitors on the right, the buffer stage in the bottom-center, which drives the pumping capacitors, and the ESD protection in the bottom-right, which protects the output voltage rail. Furthermore, it is possible to distinguish four pads, from left to right: Clock, IN, Ground and OUT. The die size is  $1.3 \times 1.6 \text{ mm}^2$ .

TA0363 - Rev 1 page 16/31

## 6 Experimental results

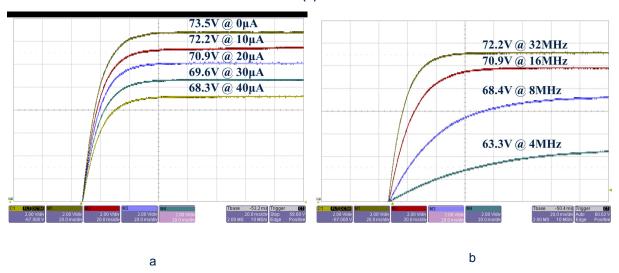

A first set of measurements has been performed applying a variable current sink to the output node with a power-supply voltage of 3.0 V and clock frequency of 32 MHz. The waveforms of the output voltage versus time for different load current values up to 40 µA are shown in Figure 10a.

A specific setting has been arranged to measure the open load output voltage as the probe used in the measurement has an impedance of 10 M $\Omega$ ; this would have charged the output node with a current of 7.3  $\mu$ A. Therefore, a voltage generator and an amperemeter, connected between the output of the CP and the power supply, have been used. Consequently, the open load output voltage has been acquired increasing the voltage on the generator until the amperemeter has indicated zero current.

A second set of measurements has been performed changing the clock frequency from 4 to 32 MHz with a power-supply of 3.0 V and a load current of 10  $\mu$ A. The waveforms of the output voltage versus time for different clock frequency values are shown in Figure 10b. Although the circuit has been dimensioned for a power-supply of 3.0 V and a clock frequency of 32 MHz, it was observed to start operating at the minimum power-supply voltage of 1.1 V, generating a multiplied voltage of nearly 26 V; furthermore, the full operation was verified up to 64 MHz. It was not possible to test the multiplier at higher frequency, because of test bench limitations.

Figure 10. Output voltage for different output load current values (a) and different clock frequency values (b)

From these curves  $V_O$  and  $R_{OUT}$  can be extracted; their value, respectively 73.5 V and 130 k $\Omega$ , is very close to that obtained with the mathematical model 74.3 V and 128 k $\Omega$ . The small discrepancy is due to the fact that, in addition to the approximation described in the Appendix, the intrinsic current consumption generated by the cross conduction of the MOS switches is not considered.

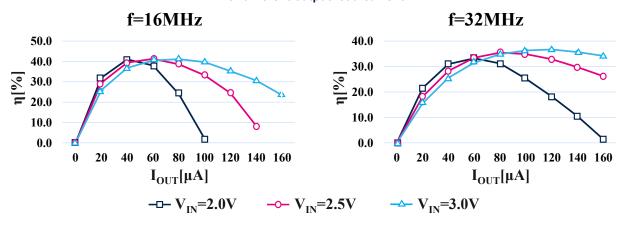

The measured 10%–90% rise time from zero to the open load multiplied voltage, with a 1.5 nF capacitive load, is approximately 800  $\mu$ s, while the voltage ripple in steady-state condition is around 1 mV at 10  $\mu$ A load current. Figure 11 shows the power efficiency measured at a switching frequency of 16 MHz and 32 MHz, at an input voltage of 2.0 V, 2.5 V and 3.0 V, and for different load current up to 160  $\mu$ A. It also includes the driver losses. It can be observed that the maximum efficiency of 42% is obtained at  $V_{IN}$  = 3 V, f = 16 MHz and  $I_{OUT}$  = 80  $\mu$ A.

TA0363 - Rev 1 page 17/31

Figure 11. Measured conversion efficiency of the proposed CP at 16 MHz and 32 MHz switching frequency for different output load current

A comparison of the main parameters among the known CPs is shown in Table 2. The maximum output voltage varies significantly for the different architectures, according to the number of stages, mainly due to technology limitations or application requirements. In comparison to other implementations, the proposed CP shows a better performance trade-off. More specifically, it offers the best voltage conversion efficiency and, considering the very high gain, a good power efficiency and a good output resistance, for a given silicon area.

Table 2. Charge pump key parameters comparison in real implementations

|                                                                          | Pelliconi et al. [8] | Lin et al.<br>[21] | Abaravicius et al.<br>[19]            | Tsai et al. [30]                    | This work                           |

|--------------------------------------------------------------------------|----------------------|--------------------|---------------------------------------|-------------------------------------|-------------------------------------|

| Topology                                                                 | 5-Dickson            | 5-Fibonacci        | Cross-Coupled x 4-<br>Serial Parallel | 3-Dickson + 3-<br>Cockcroft -Walton | 4-Dickson x 6-<br>Cockcroft -Walton |

| Tech lithography                                                         | 0.18 μm              | 0.11 µm            | 0.13 μm                               | 0.18 μm                             | 0.35 μm                             |

| Ideal gain                                                               | 6                    | 13                 | 9                                     | 7                                   | 25                                  |

| Input voltage V <sub>IN</sub>                                            | 1.8 V                | 2.4 V              | 3.1 V                                 | 1.0 V                               | 3.0 V                               |

| Dominion and attended                                                    | MOM                  | Discrete           | 5 V MIM                               | MIM+MOS                             | 12 V P1P2                           |

| Pumping capacitors C                                                     | 2.5 pF               | 47 nF              | 30/15 pF                              | 6/12 pF                             | 25 pF                               |

| Switching frequency f                                                    | 100 MHz              | 50 kHz             | 20/2.5 MHz                            | 20 MHz                              | 32 MHz                              |

| Open load output voltage V <sub>O</sub>                                  | 10.1 V               | 30 V               | 26 V                                  | 6.5 V                               | 73.5 V                              |

| Equivalent output resistance R <sub>OUT</sub>                            | 8.9 kΩ               | 5.3 kΩ             | 120 kΩ                                | 2.9 kΩ                              | 130 kΩ                              |

| Voltage conversion efficiency V <sub>O-real</sub> / V <sub>O-ideal</sub> | 93.5%                | 96.1%              | 93.1%                                 | 92.8%                               | 98.0%                               |

| Max. power conversion efficiency $P_{OUT}$ / $P_{IN}$                    | 50%                  | 83.4%              | 42%                                   | 58%                                 | 42%                                 |

| CP total silicon net area                                                | -                    | -                  | 0.086 mm <sup>2</sup>                 | 0.5 mm <sup>2</sup>                 | 1.4 mm <sup>2</sup>                 |

TA0363 - Rev 1 page 18/31

#### 7 Conclusion

A novel integrated-circuit charge pump conceived to supply drivers for miniaturized motors in MEMS technology has been presented. This charge pump is intended for high multiplying factors and is based on a mixed architecture, which merges both Dickson and Cockcroft-Walton topologies, exploiting medium voltage on-chip capacitors and low-voltage CMOS transistors.

The experimental results have shown that a 24-stage dual branch CP, with each pumping capacitor of 25 pF, can generate an output voltage higher than 70 V starting from a power supply of 3.0 V. In comparison to other implementations known in the literature, the proposed CP shows a better performance trade-off, such as the best voltage conversion efficiency and, considering the very high gain, a good power efficiency and a good output resistance, for a given silicon area. Furthermore, it allows a reduction of the equivalent output resistance maintaining the same area occupation or, alternatively, an area reduction for the same equivalent output resistance, as compared to a conventional Cockcroft-Walton charge pump.

Theoretical analysis of different configurations, with either diodes or MOS transistors, in single and dual branch architectures, also including stray capacitors, has been developed and described, which closely agrees with simulation and measurement results. The test chip has been fabricated in the STMicroelectronics BCD technology, with 0.35 µm lithography, 3.3 V CMOS transistors and a 12 V poly-poly capacitor.

TA0363 - Rev 1 page 19/31

#### 8 References

- 1. M. Schenkel, "Eine neue schaltung fur die erzeugung holder gleichspannungen", *Elektrotechnische Zeitschrift*, vol. 40, no. 28, pp. 333-335, July 1919.

- 2. Verfahren zur Schlagpr üfung von Isolatoren und anderen elektrischen Vorrich- tungen, by E. Marx. (1928, Feb. 13). DE patent 455 933.

- 3. J. D. Cockcroft and E. T. Walton, "Experiments with high velocity positive ions", *Proc. Roy. Soc., A*, vol. 136, pp. 619-630, 1932.

- 4. Arrangements for biasing the substrate of an integrated circuit, by J. Luscher. (1974, Oct. 29). U.S. Patent 3 845 331.

- 5. J. F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique", *IEEE J. Solid-State Circuits*, vol. SC-11, pp. 374-378, June 1976.

- 6. F. Ueno, T. Inoue, I. Oota, and I. Harada, "Emergency power supply for small computer systems", in *Proc. IEEE Int. Conf. Circuits and Systems*, June 1991, pp. 1065–1068.

- 7. J. S. Witters, G. Groeseneken and H. E. Maes, "Analysis and modeling of on-chip high voltage generator circuits for use in EEPROM circuits", *IEEE J. Solid-State Circuits*, vol. 24, no. 5, pp. 1372-1380, Oct. 1989.

- 8. R. Pelliconi, D. Iezzi, A. Baroni, M. Pasotti, and P. L. Rolandi, "Power efficient charge pump in deep submicron standard CMOS technology", *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 1068–1071, Jun. 2003

- M.-D. Ker, S.-L. Chen, and C.-S. Tsai, "Design of charge pump circuit with consideration of gate-oxide reliability in low-voltage CMOS processes", *IEEE J. Solid-State Circuits*, vol. 41, no. 5, pp. 1100–1107, May 2006.

- H. Peng, N. Tang, Y. Yang, and D. Heo, "CMOS Startup Charge Pump with Body Bias and Backward Control for Energy Harvesting Step-Up Converters", *IEEE Trans. Circuits Syst. Regul. Pap.*, vol. 61, no. 6, pp. 1618– 1628, Jun. 2014.

- 11. M. M. Weiner, "Analysis of Cockcroft-Walton voltage multipliers with an arbitrary number of stages", *The Review of Scientific Instruments*, vol. 40, no. 2, pp. 330-333, Feb. 1969.

- 12. J. S. Brugler, "Theoretical performance of voltage multiplier circuits", *IEEE J. Solid-State Circuits*, vol 6, no. 3, pp. 132-135, June 1971.

- 13. P. M. Lin and L. O. Chua, "Topological generation and analysis of voltage multipliers circuits", *IEEE Trans. Circuits Syst.*, vol. cas-24, no. 10, pp. 517-530, Oct. 1977.

- M. S. Bhaskar, P. Sanjeevikumar, F. Blaabjerg, V. Fedák, M. Cernat, and R M. Kulkarni, "Non Isolated and Non-Inverting Cockcroft-Walton Multiplier Based Hybrid 2Nx Interleaved Boost Converter for Renewable Energy Applications", in *Proc. IEEE Int. Power Electronics and Motion Control Conf. (PEMC)*, Varna, Bulgaria, Sep. 2016, pp. 146-151.

- 15. S. Mao, J. Popovic´, and J. A. Ferreira, "Diode Reverse Recovery Process and Reduction of a Half-Wave Series Cockcroft–Walton Voltage Multiplier for High-Frequency High-Voltage Generator Applications", *IEEE J. Solid-State Circuits*, vol. 34, no. 2, pp. 1492-1499, Feb. 2019.

- N. Ellis and R. Amirtharajah, "A Resonant Cockcroft-Walton Switched-Capacitor Converter Achieving Full ZCS and >10kW/inch3 Power Density", in *Proc. IEEE Energy Conversion Congress and Exposition (ECCE*), Baltimore, MD, USA, Oct. 2019, pp. 4378-4384.

- 17. Y.-H. Chang and S.-Y. Kuo "A Gain/Efficiency-Improved Serial-Parallel Switched-Capacitor Step-Up DC–DC Converter", *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 60, no. 10, pp. 2799–2809, Oct. 2013.

- 18. B. Abaravicius, S. Cochran, and S. Mitra "An area-efficient hybrid high-voltage charge pump design for IoT applications", in *Proc. 30th Int. Conf. on Microelectronics (ICM)*, Sousse, Tunisia, Dec. 2018, pp. 36-39.

- 19. B. Abaravicius, S. Cochran, and S. Mitra, "High-Efficiency High Voltage Hybrid Charge Pump Design with an Improved Chip Area", *IEEE Access*, vol. 9, pp. 94386-94397, June 2021.

- A. Cabrini, L. Gobbi, and G. Torelli, "Voltage Gain Analysis of Integrated Fibonacci-Like Charge Pumps for Low Power Applications", *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 54, no. 11, pp. 929–933, Nov. 2007.

- 21. H. Lin, W. C. Chan, W. K. Lee, Z. Chen, M. Chan, and M. Zhang, "High-Current Drivability Fibonacci Charge Pump with Connect–Point–Shift Enhancement", *IEEE Trans. Very Large Scale Integration (VLSI) Systemsc*, vol. 25, no. 7, pp. 2164-2173, July 2017.

- 22. D. Matoušek, O. Šubrt, and J. Hospodka, "Fibonacci Charge Pump Design, Test and Measurement", in *Proc.* 11th Int. Conf. on Measurement, Smolenice, Slovakia, May 2017, pp. 135-138.

TA0363 - Rev 1 page 20/31

- 23. K. Eguchi, S. Pongwatd, F. Asadi, and H. Fujisaki, "A High Voltage Gain SC DC-DC Converter Based on Cross-Connected Fibonacci-Type Converter", in *Proc. Int. Conf. on Engineering, Applied Sciences, and Technology (ICEAST)*, Phuket, Thailand, Aug. 2018.

- 24. D. Matoušek and B. Brtník, "Rationalisation of the Fibonacci Charge Pump", in *Proc. Int. Conf. on Applied Electronics (AE)*, Pilsen, Czech Republic, Sep. 2019.

- 25. A. Oliva and J. H. Lang, "General Analysis of Fibonacci Charge Pump SSL Output Characteristics with Parasitic Capacitances", *IEEE Trans. Power Electronics*, vol. 34, no. 9, pp. 8274-8278, Sep. 2019.

- 26. S. Park, J. Yang, and J. Rivas-Davila, "A Hybrid Cockcroft–Walton/Dickson Multiplier for High Voltage Generation", *IEEE Trans. Power Electronics*, vol. 35, no. 3, pp. 2714-2723, Mar. 2020.

- 27. K. Eguchi, A. Shibata, T. Ishibashi, and F. Asadi, "Design of a Single Inductor LED Sink Driver Employing a Negative Hybrid Cockcroft Walton/Dickson Multiplier", in *Proc. IEEE 4th Int. Conf. on Power and Energy Applications (ICPEA)*, Busan, Korea, Oct. 2021, pp. 24-28.

- 28. K. Eguchi, A. Shibata, T. Ishibashi, and F. Asadi, "Vibration Energy Harvesting Using a MISO Converter Employing Hybrid CockcroftWalton/Dickson Multiplier", in *Proc. IEEE 4th Int. Conf. on Power and Energy Applications (ICPEA)*, Busan, Korea, Oct. 2021, pp. 65-68.

- 29. J.-H. Tsai, S.-A. Ko, H.-H. Wang, C.-W. Wang, H. Chen, and P.-C. Huang, "A 1 V input, 3-to-6v output, integrated 58%-efficient charge pump with hybrid topology and parasitic energy collection for 66% area reduction and 11% efficiency improvement", in *IEEE Asian Solid State Circuits Conf. (A-SSCC)*, Kao Hsiung, Taiwan, Nov. 2014, pp. 61–64.

- 30. J.-H. Tsai, S.-A. Ko, C.-W. Wang, Y.-C. Yen, H.-H. Wang, P.-C. Huang, P.-H. Lan, and M.-H. She, "A 1 V Input, 3 V-to-6 V Output, 58%-Efficient Integrated Charge Pump with a Hybrid Topology for Area Reduction and an Improved Efficiency by Using Parasitics", *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2533–2548, Nov. 2015.

- 31. M. D. Seeman and S. R. Sanders, "Analysis and Optimization of Switched-Capacitor DC–DC Converters", *IEEE Trans. Power Electronics*, vol. 23, no. 2, pp. 841-851, Mar. 2008.

- 32. Y. Allasasmeh and S. Gregori, "A Performance Comparison of Dickson and Fibonacci Charge Pumps", in *Proc. European Conf. on Circuit Theory and Design*, Antalya, Turkey, Aug. 2009, pp. 599-602.

- 33. T. Tanzawa, "On Two-Phase Switched-Capacitor Multipliers With Minimum Circuit Area", *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 57, no. 10, pp. 2602–2608, Oct. 2010.

- 34. G. Palumbo and D. Pappalardo, "Charge Pump Circuits: An Overview on Design Strategies and Topologies", *IEEE Circuits Syst. Mag.*, vol. 10, no. 1, pp. 31–45, First Quarter 2010.

- 35. W-H Ki, Y. Lu, F. Su, and C.-Y. Tsui, "Design and Analysis of On-Chip Charge Pumps for Micro-Power Energy Harvesting Applications", in *Proc. IEEE/IFIP 19th Int. Conf. on VLSI and System-on-Chip*, Hong Kong, China, Oct. 2011, pp. 374-379.

- 36. O.-Y. Wong, H. Wong, W.-S. Tam, and C.-W. Kok, "Dynamic Analysis of Two-Phase Switched-Capacitor DC–DC Converters", *IEEE Trans. Power Electronics*, vol. 29, no. 1, pp. 302-317, Jan. 2014.

- 37. E. Ferro, V. M. Brea, P. López, and D. Cabello, "Dynamic Model of Switched-Capacitor DC–DC Converters in the Slow-Switching Limit Including Charge Reusing", *IEEE Trans. Power Electronics*, vol. 32, no. 7, pp. 5293-5311, July 2017.

- 38. D. Matoušek and L. Beran, "Comparison of Positive and Negative Dickson Charge Pump and Fibonacci Charge Pump", in *Proc. Int. Conf. on Applied Electronics (AE)*, Pilsen, Czech Republic, Sep. 2017.

- 39. A. Ballo, A. D. Grasso, G. Giustolisi, and G. Palumbo, "Optimized Charge Pump with Clock Booster for Reduced Rise Time or Silicon Area", *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 66, no. 12, pp. 1977–1981, Dec. 2019.

- 40. V. Malandruccolo, M. Ciappa, H. Rothleitner, M. Hommel, and W. Fichtner, "A new built-in screening methodology for Successive Approximation Register Analog to Digital Converters", *Microelectronics Reliability*, pp. 1750-1757, Aug. 2010.

- 41. Voltage elevator on the charge pump type, by F. Pulvirenti and R. Gariboldi. (1998, Feb. 25). EP Patent 0 696 839.

- 42. R. Gariboldi and F. Pulvirenti, "A 70 mΩ intelligent high side switch with full diagnostics", in *Proc. ESSCIRC '95: Twenty-first European Solid-State Circuits Conference*, Lille, France, Sep. 1995, pp. 262-265.

- 43. R. Gariboldi and F. Pulvirenti, "A 70 mΩ intelligent high side switch with full diagnostics", *IEEE J. Solid-State Circuits*, vol. 31, no. 7, pp. 915-923, July 1996.

TA0363 - Rev 1 page 21/31

**Francesco Pulvirenti** was born in Acitrezza, Catania, Italy, in 1964. He received a doctorate degree in Electronic Engineering from University of Pisa, Italy, in 1989. In 1991, after military service, he joined Co.Ri.M.Me. Catania, Italy, and in 1996 transferred to STMicroelectronics where he is currently working as the Design Director of the Industrial and Power Conversion Division with the mission to develop new products for Motion Control, Industrial Automation, Battery Charging and Lighting Applications.

He started as a design engineer spending around ten years developing Smart Power ICs, Linear Regulators, Switch Mode Power Supply and Power Management respectively for Industrial, Mobile Phone and Computer Applications. In 2001, he moved to the Display segment to lead the design of Display Drivers for portable equipment. In 2007, he was appointed as Director of the Photovoltaic Business Unit with the task to define and develop new application specific devices for the Photovoltaic Market.

Dr. Pulvirenti holds more than 50 international patents on Analog and Smart Power ICs, he is also co-author of 22 papers published in international conferences/magazines and co-author of the book "Liquid Crystal Display Drivers" edited by Springer in 2009.

TA0363 - Rev 1 page 22/31

## **Appendix A**

Referring to the voltage multipliers described in Sec. II, the multiplied output voltage  $V_{OUT}$  can be computed assuming the pumping capacitors and the diodes are ideally all equal. Also,  $C_{OUT}$  is assumed to be much bigger than the pumping capacitors, hence in steady-state condition  $V_{OUT}$  can be considered a constant DC voltage with small superimposed voltage ripple. Furthermore, the calculation is done in SSL.

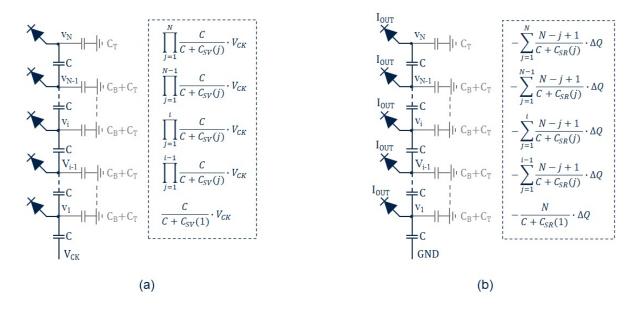

For an arbitrary N-stage Dickson Multiplier the voltages at the intermediate nodes in steady-state condition are reported below. They have three contributions: the first one is the voltage level to which the pumping capacitors are charged when the clock signal is low; the second one, proportional to the clock amplitude  $V_{CK}$ , is the voltage step to which the pumping capacitors are boosted when the clock signal is switched high; while the last contribution is the voltage drop caused by the output load current  $I_{OUT}$ .

$$\begin{cases} v_{1} = V_{IN} - V_{D} + \frac{C}{C + C_{T}} V_{CK} - \frac{\Delta Q}{C + C_{T}} \\ \vdots \\ v_{i} = v_{i-1} - V_{D} + \frac{C}{C + C_{T}} V_{CK} - \frac{\Delta Q}{C + C_{T}} \ i = 2,3,...N \\ \vdots \\ V_{OUT} = v_{N} - V_{D} \end{cases}$$

(A1)

where  $V_{IN}$  is the input voltage of the circuit,

$V_{CK}$  is the swing voltage of the clock signals,

$V_D$  is the forward voltage drop of the diodes,

$\Delta Q$  is the charge transferred in a clock period,

$C_T$  is the top plate stray capacitance.

The multiplied output voltage  $V_{OUT}$  can be easily obtained by solving the equations set (A1) and is given by

$$V_{OUT} = V_{IN} - \left(N+1\right)V_D + \frac{C}{C+C_T}NV_{CK} - \frac{\Delta Q}{C+C_T}N$$

(A2)

where the first three addends represent the open load output voltage, while the last one represents the voltage drop on the equivalent output resistance.

The charge transferred  $\Delta Q$  is directly proportional to the clock period or inversely proportional to the clock frequency f; hence, it can be written as  $\Delta Q = I_{OUT}/f$ . Moreover, the top plate stray capacitor  $C_T$  can be specified as a fraction of the pumping capacitor  $C_T = \alpha_T \cdot C$ . So, Eq (A2) can be rewritten as follows

$$V_O = V_{IN} - \left(N+1\right)V_D + \frac{C}{1+\alpha T}NV_{CK} \tag{A3}$$

$$R_{OUT} = \frac{1}{f \cdot C} \cdot \frac{1}{1 + \alpha r} N \tag{A4}$$

Unlike the Dickson multiplier, the computation for an arbitrary N-stage Cockcroft-Walton multiplier gives different results depending on whether the architecture is single or dual. For this purpose, the following calculations are focused on the dual branch configuration and then extended to the single one. Thus, the value of pumping capacitors is halved with respect to the single branch configuration so that the total amount of capacitance does not change. Furthermore, the precise computation including both bottom and top plate stray capacitors is complex, for this reason the following simplifications are applied.

The first simplification comes from the fact that generally the parasitic capacitors are much smaller than the pumping ones, so that each pumping capacitor in series with the stray capacitor can be approximated as a short. Consequently, the equivalent parasitic capacitance loading the i-th node can be calculated by making the parallel of the cascading N - i + 1 stray capacitors. Hence, the voltage at the i-th node is obtained from the voltage at the previous node with a capacitive partitioning between the i-th pumping capacitor and the corresponding stray capacitor defined as follows:

$$C_{SV}(j) = (N - j) \cdot (C_B + C_T) + C_T \tag{A5}$$

TA0363 - Rev 1 page 23/31

Figure 12. Parasitic capacitors in an N-stage Cockroft-Walton CP basic configuration (a) rearranged in a linearly growing series (b) and connected in parallel (c)

Regarding the second approximation, looking at Figure 12, the parasitic capacitors of circuit (a) can be arranged in a linearly growing series having same capacitive value (b) and then connected in parallel with the pumping capacitors (c).

Of course, the voltage distribution across the intermediate nodes of the stray and pumping capacitors series is not equal and the discrepancy grows with their ratio. Hence, the charge delivered from the *i*-th node is provided by the parallel of the *i*-th pumping capacitor and the corresponding stray capacitors defined in Eq (A6), while the voltage at the related node is obtained from the voltage at the previous node subtracting the drop caused by the charge transferred.

$$C_{SR}(j) = (C_B + C_T) \cdot \sum_{k=j}^{N-1} k + N \cdot C_T \tag{A6}$$

Figure 13(a) shows the clock signal attenuation caused by the stray capacitors. It can be observed that the voltage attenuation grows with the value of these capacitors, therefore they have a detrimental impact on it. Figure 13(b) shows the voltage drop caused by the output load current. In this case it can be noted that the stray capacitors have a positive effect on the voltage drop because they provide part of the charge delivered to the output.

TA0363 - Rev 1 page 24/31

Figure 13. Clock signal attenuation caused by stray capacitors (a) and voltage drop caused by the output load current (b) in a Cockcroft-Walton CP

The voltages at the intermediate nodes in steady-state condition have the same three contributions described for the previous CP

$$\text{A7} \begin{cases} v_1 = V_{IN} - V_D + \frac{C}{C + C_{SV}(1)} V_{CK} - \frac{N \cdot \Delta Q}{C + C_{SR}(1)} \\ \vdots \\ v_i = v_{i-1} - V_D + \prod_j^i = 1 \frac{C}{C + C_{SV}(j)} V_{CK} - \sum_j^i = 1 \frac{(N-j+1) \cdot \Delta Q}{C + C_{SR}(j)} \\ \vdots \\ V_{OUT} = v_N - V_D \end{cases}$$

In this case, bottom and top plate stray capacitors have been considered because both impact the output voltage, which can be obtained by solving the equations set Eq (A7).

$$\begin{split} V_{OUT} &= V_{IN} - (N+1)V_D + \ \Sigma_{i}^{N} = 1 \prod_{j=1}^{i} \frac{C}{C + C_{SV}(j)} \cdot V_{CK} \\ &- \Sigma_{i=1}^{N} \Sigma_{j=1}^{i} \frac{N-j+1}{C + C_{SR}(j)} \cdot \Delta \, Q \end{split} \tag{A8}$$

where the first three addends represent the open load output voltage, while the last one represents the voltage drop on the equivalent output resistance. Then, specifying the charge transferred as  $\Delta Q = I_{OUT}/f$  and the stray capacitors as a fraction of the pumping capacitor Eq (A8) can be rewritten as follows

$$V_{O} = V_{IN} - (N+1)V_{D} + \sum_{i=1}^{N} \prod_{j=1}^{i} \frac{1}{1 + \alpha_{SV}(j)} \cdot V_{CK}$$

(A9)

$$R_{OUT} = \frac{1}{f \cdot C} \sum_{i=1}^{N} \sum_{j=1}^{i} \frac{N-j+1}{1+\alpha_{SR}(j)}$$

(A10)

with  $\alpha_{SV}(j) = C_{SV}(j)/C$  and  $\alpha_{SR}(j) = C_{SR}(j)/C$ ; they are zero if stray capacitors are negligible.

As anticipated, in a Cockcroft-Walton dual branch architecture, there are N pumping capacitors in series on both branches. Differently, in the single branch architecture, with N even, the pumping capacitors in series are N/2 on both sides, while, with N odd, the pumping capacitors in series are (N + 1)/2 on one side and (N - 1)/2 on the opposite side. Hence, for a single chain configuration  $V_O$  and  $R_{OUT}$  become

TA0363 - Rev 1 page 25/31

$$V_{O} = \begin{cases} V_{IN} - (N+1)V_{D} + 2\sum_{i=1}^{N} \Pi_{j}^{i} = 1 \frac{1}{1 + \alpha_{SV}(j)} V_{CK} \\ N \ even \end{cases}$$

$$V_{O} = \begin{cases} V_{IN} - (N+1)V_{D} + \left[ \sum_{i=1}^{\frac{N+1}{2}} \Pi_{j}^{i} = 1 \frac{1}{1 + \alpha_{SV}(j)} \right] \\ + \sum_{i=1}^{\frac{N-1}{2}} \Pi_{j}^{i} = 1 \frac{1}{1 + \alpha_{SV}(j)} \right] \cdot V_{CK} \qquad N \ odd \end{cases}$$

(A11)

$$R_{OUT} = \begin{cases} \frac{1}{f \cdot C} \cdot 2\sum_{i=1}^{N} \sum_{j=1}^{i} \sum_{j=1}^{i} \frac{N-j+1}{1+\alpha_{SR}(j)} & N \text{ even} \end{cases}$$

$$R_{OUT} = \begin{cases} \frac{1}{f \cdot C} \left[ \sum_{i=1}^{N+1} \sum_{j=1}^{i} \frac{N-j+1}{1+\alpha_{SR}(j)} + \sum_{i=1}^{N-1} \sum_{j=1}^{i} \sum_{j=1}^{i} \frac{N-j+1}{1+\alpha_{SR}(j)} \right] & N \text{ odd} \end{cases}$$

$$(A12)$$

Assuming  $V_{CK} = V_{IN}$ , it can be noted that, in a single branch architecture, the pumping capacitors are charged to  $2(V_{IN} - V_D)$ , except for the first one which is charged up to  $V_{IN} - V_D$ , while in a dual branch architecture, as the number of stacked capacitors is doubled, they are charged up to  $V_{IN} - V_D$ . A drawback of this is that, for a given N-stage, the equivalent output resistance is much higher than that of a single branch configuration.

In those designs where the bottom stray capacitors are used as charge pumping elements, like the architecture of Figure 6, they realize a Dickson topology which works in parallel to the main CP. Following the same reasoning of Figure 12, the bottom stray capacitors can be connected in parallel with the pumping capacitors. Of course, this also is an approximation because the voltage distribution across the intermediate nodes of the stray and pumping capacitors series is not perfectly equal since the capacitors in the two series are differently distributed.

$$\begin{cases} v_{1} = V_{IN} - V_{D} + \frac{C + C_{B} \cdot \sum_{k=1}^{N-1} k}{C + C_{B} \cdot \sum_{k=1}^{N-1} k + N \cdot C_{T}} V_{CK} - \frac{N \cdot \Delta Q}{C + C_{SR}(1)} \\ \vdots \\ v_{i} = v_{i} - 1 - V_{D} + \prod_{j=1}^{i} \frac{C + C_{B} \cdot \sum_{k=j}^{N-1} k}{C + C_{B} \cdot \sum_{k=j}^{N-1} k + (N-j+1) \cdot C_{T}} \cdot V_{CK} \\ - \sum_{j=1}^{i} \frac{(N-j+1) \cdot \Delta Q}{C + C_{SR}(j)} \\ \vdots \\ V_{OUT} = v_{N} - V_{D} \end{cases}$$

(A13)

The voltages at the intermediate nodes in steady-state condition are here calculated considering that the bottom stray capacitors, properly distributed, go in parallel with the pumping capacitors. Then,  $V_{OUT}$  can be easily obtained by resolving the equations set Eq (A13)

$$V_{OUT} = V_{IN} - (N+1)V_D$$

$$+ \sum_{i=1}^{N} \prod_{j=1}^{i} \frac{C + C_B \cdot \sum_{k=j}^{N-1} k}{C + C_B \cdot \sum_{k=j}^{N-1} k + (N-j+1) \cdot C_T} V_{CK}$$

(A14)

Finally, specifying the charge transferred as  $\Delta Q = I_{OUT}/f$  and the stray capacitors as a fraction of the pumping capacitor Eq (A14) can be rewritten as follows

$$V_{O} = V_{IN} - (N+1)V_{D}$$

$$+ \sum_{i=1}^{N} \prod_{j=1}^{i} \frac{1 + B \cdot \sum_{k=j}^{N-1} k}{1 + B \cdot \sum_{k=j}^{N-1} k + (N-j+1)T} V_{CK}$$

(A15)

It is easy to demonstrate that the equivalent output resistance is the same as Eq (A10).

TA0363 - Rev 1 page 26/31

# **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 26-Sep-2022 | 1       | Initial release. |

TA0363 - Rev 1 page 27/31

# **Contents**

| 1   | Introduction                               | 2  |

|-----|--------------------------------------------|----|

| 2   | Most conventional charge pumps             | 5  |

| 3   | Proposed charge pump                       | 8  |

| 4   | Proposed charge pump with stray capacitors | 12 |

| 5   | Implementation of the proposed charge pump | 15 |

| 6   | Experimental results                       | 17 |

| 7   | Conclusion                                 | 19 |

| 8   | References                                 | 20 |

| Αp  | pendix A                                   | 23 |

| Rev | vision history                             | 27 |

| Lis | t of tables                                | 29 |

| Lis | t of figures                               | 30 |

# **List of tables**

| Table 1. | Charge pump key parameters comparison in ideal conditions     | 10 |

|----------|---------------------------------------------------------------|----|

| Table 2. | Charge pump key parameters comparison in real implementations | 18 |

| Table 3. | Document revision history                                     | 27 |

TA0363 - Rev 1 page 29/31

# **List of figures**

| Figure 1.  | Dickson (a), Cockcroft-Walton (b), Serial-Parallel (c) and Fibonacci (d) N-stage CPs                                                                    | . 3 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | CP equivalent circuit                                                                                                                                   | . 5 |

| Figure 3.  | Cockcroft-Walton N-stage CP in a DB architecture                                                                                                        | . 6 |

| Figure 4.  | Proposed N-stage CP with diodes (a), with switches (b), Dual Branch with diodes (c), and Dual Branch with switches (d)                                  | . 9 |

| Figure 5.  | Proposed N-stage CP with stray capacitors                                                                                                               | 12  |

| Figure 6.  | Proposed N-stage CP with bottom stray capacitors exploited as charge-pumping elements                                                                   | 13  |

| Figure 7.  | Modeled and simulated VO and ROUT of the proposed CP with 16 and 24 stages for different M                                                              | 14  |

| Figure 8.  | Proposed 24-stage CP with MOS transistors in latched topology and bottom stray capacitors exploited as pumping elements.                                | 15  |

| Figure 9.  | Layout and die photograph of the proposed Charge Pump with N=24 stages and M=4                                                                          | 16  |

| Figure 10. | Output voltage for different output load current values (a) and different clock frequency values (b)                                                    | 17  |

| Figure 11. | Measured conversion efficiency of the proposed CP at 16 MHz and 32 MHz switching frequency for different output load current                            | 18  |

| Figure 12. | Parasitic capacitors in an N-stage Cockroft-Walton CP basic configuration (a) rearranged in a linearly growing series (b) and connected in parallel (c) | 24  |

| Figure 13. | Clock signal attenuation caused by stray capacitors (a) and voltage drop caused by the output load current (b) is a Cockcroft-Walton CP                 |     |

|            |                                                                                                                                                         |     |

TA0363 - Rev 1 page 30/31

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

TA0363 - Rev 1 page 31/31