## Mode transition blocking by internal IPs clock busy signal

#### Introduction

This document presents a possible mode transition stuck in mode entry module (MC\_ME) for SPC58xx devices.

The relationship between mode transition command and internal clock busy signal assertion will be discussed and in order to report a way to avoid the hang.

The phenomenon is generic to all IP auxiliary clock dividers. In this document, for describing the scenario, CAN\_0 auxiliary clock is reported, also SPC58xC device is used for showing relevant signals and schematics.

## 1 Overview

Application software could observe a mode transition getting stuck, after several mode transitions requests. This behavior is not systematic it happens only under specific conditions, here described.

TN1434 - Rev 1 page 2/14

#### Steps for reproducing the phenomenon

#### 2.1 Software

The phenomenon, described in this application note, can occur when the user's application attempts to switch from one running mode with clocks enabled to another in which clocks, are disabled after peripherals have been disabled via their PCTLx in mode entry (ME).

The following steps help for understanding the sequence.

- A mode transition is performed for disabling the peripherals (ME.PCTLx -> 0)

- No clock disabled instruction is programmed

- CAN auxiliary clock gets disabled (CGM.AC8\_DC0 = 0x0)

- A mode transition is performed for disabling the clock sources (PLLx, XOSC)

#### 2.2 CAN clock tree

The following figure shows an example of the peripheral clock tree (SPC58xC) with the dependence of PLL0:PHI (green) or XOSC (red) based on source clock selection in the CGM\_AC8\_SC.SELCTL register.

The full clock diagram can be found in the device's proper reference manual.

CAN\_Subsystem 0 Jitter Enable

CGM\_AC8\_SC.SELCTL

CGM\_AC8\_DC0

DIV 1..64

MCAN Subsys 0)

Figure 1. CAN clock tree on SPC58xC device

#### 2.3 Block diagram

PLL0\_status

The following figure shows the block diagram of interconnection between mode entry (MC\_ME) and clock generation module (MC\_CGM) that are involved in completing a mode transition. PLL0 drives auxiliary AC8 clock divider here.

MC\_ME

Sync1 Sync2

CAN\_clk\_en

ME.S\_MTRANS

MC\_CGM

Sync1 Sync2

Busy

Figure 2. Block diagram when performing a transition

TN1434 - Rev 1 page 3/14

Diagram logical steps are described below:

- 1. PCTL\_CAN: for enabling/disabling the peripheral.

- 2. CAN\_clk\_en: this is the signal used for evaluating if the peripheral is enabled or disabled.

- 3. MC\_CGM.AC8\_DC0: the auxiliary clock divider is used for configuring the peripheral, driven by PLL0:PHI.

- 4. PLL0\_status: this is the signal used for evaluating if the PLL0 is switched on or off.

- 5. MC\_ME.S\_MTRANS: this is the mode transition status bit.

TN1434 - Rev 1 page 4/14

#### 3 Expected behavior

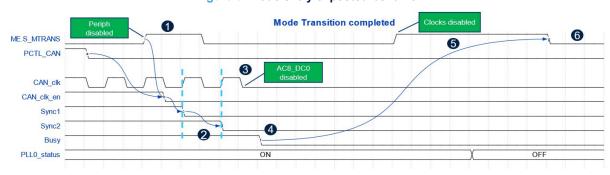

The following figure shows the working scenario on which a transition for disabling the peripheral, the next peripheral clock disable and the final mode transition for disabling all the clocks in the current user mode are successfully completed.

Figure 3. Mode entry expected behavior

The steps to be described are summarized here below (details are in the following sections):

- 1. First mode transition to disable CAN PCTL.

- 2. CAN clock propagation and synchronization.

- 3. CAN clock disabled via auxiliary clock divider.

- 4. Busy signal released.

- 5. Second mode transition for disabling clock sources (PLLx, XOSC).

- Mode transition finished.

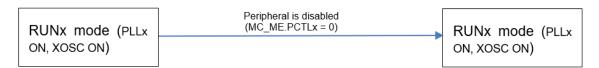

#### 3.1 Peripheral disabling (1)

In this step, the MC\_ME.PCTL related to CAN is set to zero for allowing the device to disable the peripheral and a mode transition is performed for activating the peripheral disabling.

Mode transition ends with success, mode entry does not check the clock sources because they are not poweredoff in the current mode.

Figure 4. Transition clock status when disabling peripheral

#### 3.2 CAN clock propagation (2) and busy signal (4)

CAN\_clk\_en signal is propagated through CAN\_clk until the busy signal goes low (point 4).

This is because the synchronization steps complete before point (3).

#### 3.3 Auxiliary CAN clock disabling (3)

CAN\_clk is driven by the MC\_CGM.AUX8\_DC0 auxiliary clock register and, based on the frequency of the IP, it remains in synch with the synchronization signals and allows the busy signal to go low.

# 3.4 Second mode transition, clocks disabling (5) and mode transition completion (6)

When the second mode transition is performed, for disabling the clocks in the final run mode, the busy signal is already low and so no problem to complete the transition, MC\_ME.S\_MTRANS goes low accordingly.

TN1434 - Rev 1 page 5/14

Figure 5. Mode transition for disabling the clocks

TN1434 - Rev 1 page 6/14

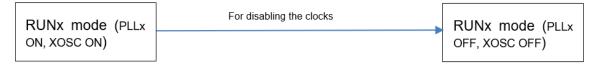

#### 4 Mode transition stuck behavior

The following figure shows the scenario on which the final transition for disabling the clocks hangs.

Figure 6. Mode entry stuck behavior

The steps to be described are summarized here below:

- 1. First mode transition to disable CAN\_PCTL.

- 2. CAN clock propagation and synchronization.

- 3. Slow CAN clock disable via auxiliary clock divider-during synchronization process.

- 4. Busy signal not released.

- 5. Second mode transition for disabling clock sources (PLLx, XOSC).

- 6. Mode transition pending–waiting for the busy signal release. It is not possible to disable clock source (PLL\_0) to a periphery, which is using the clock source–signaled by the busy signal here. Similarly: XOSC cannot be disabled when used for PLL\_0 as a source clock.

#### 4.1 Differences across good behavior

The wrong behavior is due to the CAN\_clk, which is disabled via MC\_CGM.AC8\_DC0 (3) during the synchronization process. At this point, the busy signal (4) does not go low and the second transition (5) loops indefinitely, because (6) the PLL0 clock is expected to be switched off while busy signal is active.

TN1434 - Rev 1 page 7/14

#### 5 Workarounds

Two workarounds can be put in place for avoiding the reported phenomenon, see them in details.

#### 5.1 Disable auxiliary clock

Disabling the AC8\_DC0 auxiliary clock divider at the beginning of the application completely avoid the phenomenon. No clocks remain active and the busy signal works properly.

#### 5.2 Use the right divider for the auxiliary clock

Using a proper value in auxiliary clock dividers is the first mandatory step for avoiding the phenomenon. For each SPC58xx device there is a proper RM paragraph in the clocking chapter reporting the maximum auxiliary level clock frequencies.

Please refer to the relative chapter for every detailed information (see Reference documents).

TN1434 - Rev 1 page 8/14

## **Appendix A Reference documents**

| Doc Name | Title                                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| RM0403   | SPC58 2B Line - 32 bit Power Architecture automotive MCU z2 core 80 MHz, 1 MByte Flash, ASIL-B.                                |

| RM0449   | SPC58 4B Line - 32 bit Power Architecture automotive MCU z4 core 120 MHz, 2 MBytes Flash, HSM, ASIL-B.                         |

| RM0407   | SPC58 C Line - 32 bit Power Architecture automotive MCU Dual z4 cores 180 MHz, 4 MBytes Flash, HSM, ASIL-B – Reference Manual. |

| RM0391   | SPC58 E/G Line - 32 bit Power Architecture automotive MCU Triple z4 cores 180 MHz, 6 MBytes Flash, HSM, ASIL-D.                |

| RM0452   | SPC58 H Line - 32 bit Power Architecture automotive MCU Triple z4 cores 200 MHz, 10 MBytes Flash, HSM, ASIL-D.                 |

| RM0421   | SPC58xNx 32-bit Power Architecture microcontroller for automotive ASILD applications.                                          |

TN1434 - Rev 1 page 9/14

## **Revision history**

Table 1. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 12-Dec-2022 | 1       | Initial release. |

TN1434 - Rev 1 page 10/14

## **Contents**

| 1  | Ove                                  | rview                                                                           | 2  |

|----|--------------------------------------|---------------------------------------------------------------------------------|----|

| 2  | Steps for reproducing the phenomenon |                                                                                 |    |

|    | 2.1                                  | Software                                                                        | 3  |

|    | 2.2                                  | CAN clock tree                                                                  | 3  |

|    | 2.3                                  | Block diagram                                                                   | 3  |

| 3  | Expected behavior                    |                                                                                 |    |

|    | 3.1                                  | Peripheral disabling (1)                                                        | 5  |

|    | 3.2                                  | CAN clock propagation (2) and busy signal (4)                                   | 5  |

|    | 3.3                                  | Auxiliary CAN clock disabling (3)                                               | 5  |

|    | 3.4                                  | Second mode transition, clocks disabling (5) and mode transition completion (6) | 5  |

| 4  | Mod                                  | le transition stuck behavior                                                    | 7  |

|    | 4.1                                  | Differences across good behavior                                                | 7  |

| 5  | Workarounds                          |                                                                                 |    |

|    | 5.1                                  | Disable auxiliary clock                                                         | 8  |

|    | 5.2                                  | Use the right divider for the auxiliary clock                                   | 8  |

| Ap | pendi                                | A Reference documents                                                           | 9  |

| Re | vision                               | history                                                                         | 10 |

| List of tables | List | of | ta | b | les |

|----------------|------|----|----|---|-----|

|----------------|------|----|----|---|-----|

| able 1. | ocument revision history       | 1/ | n |

|---------|--------------------------------|----|---|

| able I. | 0641116111 164131011 1113101 4 |    | J |

TN1434 - Rev 1 page 12/14

## **List of figures**

| Figure 1. | CAN clock tree on SPC58xC device                  | 3 |

|-----------|---------------------------------------------------|---|

| Figure 2. | Block diagram when performing a transition        | 3 |

| Figure 3. | Mode entry expected behavior                      | 5 |

| Figure 4. | Transition clock status when disabling peripheral | 5 |

| Figure 5. | Mode transition for disabling the clocks          | 6 |

| Figure 6. | Mode entry stuck behavior                         | 7 |

TN1434 - Rev 1 page 13/14

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

TN1434 - Rev 1 page 14/14