# UM2262 User manual

# Getting started with the X-CUBE-SBSFU STM32Cube Expansion Package

# Introduction

This user manual describes how to get started with the X-CUBE-SBSFU STM32Cube Expansion Package.

The X-CUBE-SBSFU secure boot and secure firmware update solution allows the update of the STM32 microcontroller built-in program with new firmware versions, adding new features and correcting potential issues. The update process is performed in a secure way to prevent unauthorized updates and access to confidential on-device data.

The secure boot (Root of Trust services) is an immutable code, always executed after a system reset, that checks STM32 static protections, activates STM32 runtime protections, and then verifies the authenticity and integrity of user application code before every execution to ensure that invalid or malicious code cannot be run.

The secure firmware update application receives the firmware image via a UART interface with the YMODEM protocol, checks its authenticity, and checks the integrity of the code before installing it. The firmware update is done on the complete firmware image, or only on a portion of the firmware image. Examples are provided for single-slot configuration to maximize firmware image size, and for dual-slot configuration to ensure safe image installation and enable over-the-air firmware update capability commonly used in IoT devices. For a complex system, the firmware image configuration can be extended up to three images. Examples can be configured to use asymmetric or symmetric cryptographic schemes with or without firmware encryption.

The secure key management services provide cryptographic services to the user application through the PKCS #11 APIs (KEY ID-based APIs) that are executed inside a protected and isolated environment. User application keys are stored in the protected and isolated environment for their secured update: authenticity check, data decryption, and data integrity check.

STSAFE-A110 is a tamper-resistant secure element (Hardware Common Criteria EAL5+ certified) used to host X509 certificates and keys and perform verifications that are used for firmware image authentication during secure boot and secure firmware update procedures.

X-CUBE-SBSFU is built on top of STM32Cube software technology, making the portability across different STM32 microcontrollers easy. It is provided as a reference code to demonstrate the best use of STM32 security protections.

X-CUBE-SBSFU is classified ECCN 5D002.

December 2025 UM2262 Rev 11 1/109

Contents UM2262

# **Contents**

| 1 | Gen  | ral information                                                     | 9  |

|---|------|---------------------------------------------------------------------|----|

|   | 1.1  | Terms and definitions                                               | 9  |

|   | 1.2  | References                                                          | 11 |

| 2 | STM  | 2Cube overview                                                      | 12 |

| 3 | Seci | e boot and secure firmware update (SBSFU)                           | 14 |

|   | 3.1  | Product security introduction                                       | 14 |

|   | 3.2  | Secure boot                                                         | 14 |

|   | 3.3  | Secure firmware update                                              | 15 |

|   | 3.4  | Cryptography operations                                             | 16 |

| 4 | Key  | nanagement services                                                 | 18 |

| 5 | Prot | ction measures and security strategy                                | 20 |

|   | 5.1  | STM32L4 series, STM32L4+ series, and STM32L0 series                 | 22 |

|   | 5.2  | STM32F4 series, STM32F7 series, and STM32L1 series                  | 24 |

|   | 5.3  | STM32G0 series, STM32G4 series, and STM32H7 series                  | 26 |

|   | 5.4  | STM32WB series                                                      | 30 |

|   | 5.5  | STM32L4+ series combined with STSAFE-A110                           | 32 |

| 6 | Pacl | age description                                                     | 35 |

|   | 6.1  | General description                                                 | 35 |

|   | 6.2  | Architecture                                                        | 37 |

|   |      | 6.2.1 STM32CubeHAL                                                  | 37 |

|   |      | 6.2.2 Board support package (BSP)                                   | 37 |

|   |      | 6.2.3 Cryptographic Library                                         | 38 |

|   |      | 6.2.4 Secure engine (SE) middleware                                 | 38 |

|   |      | 6.2.5 Key management services (KMS) middleware                      | 38 |

|   |      | 6.2.6 STSAFE-A middleware                                           | 38 |

|   |      | 6.2.7 Secure boot and secure firmware upgrade (SBSFU) application . |    |

|   |      | 6.2.8 User application                                              | 40 |

|   | 6.3  | Folder structure                                                    | 41 |

|        | 6.4     |         |                                                                   |    |

|--------|---------|---------|-------------------------------------------------------------------|----|

|        | 6.5     | Applic  | ation compilation process with IAR Systems <sup>®</sup> toolchain | 43 |

| 7      | Hard    | lware a | nd software environment setup                                     | 45 |

|        | 7.1     | Hardw   | /are setup                                                        | 45 |

|        | 7.2     | Softwa  | are setup                                                         | 45 |

|        |         | 7.2.1   | Development toolchains and compilers                              | 45 |

|        |         | 7.2.2   | Software tools for programming STM32 microcontrollers             | 45 |

|        |         | 7.2.3   | Terminal emulator                                                 | 46 |

|        |         | 7.2.4   | X-CUBE-SBSFU firmware image preparation tool                      | 46 |

| 8      | Step    | -by-ste | p execution                                                       | 47 |

|        | 8.1     | STM3    | 2 board preparation                                               | 48 |

|        | 8.2     | Applic  | ation compilation                                                 | 51 |

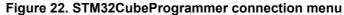

|        | 8.3     | Tera T  | erm connection                                                    | 52 |

|        |         | 8.3.1   | ST-LINK disable                                                   | 52 |

|        |         | 8.3.2   | Tera Term launch                                                  | 52 |

|        |         | 8.3.3   | Tera Term configuration                                           | 52 |

|        |         | 8.3.4   | Welcome screen display                                            | 54 |

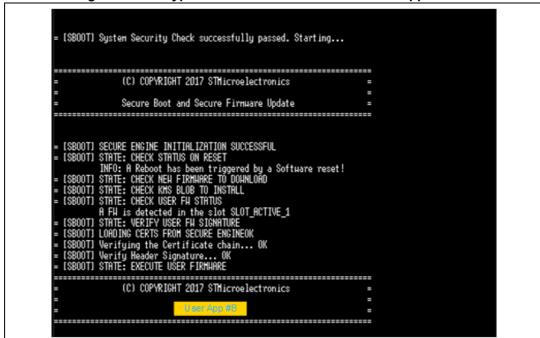

|        | 8.4     | SBSF    | U application execution                                           | 54 |

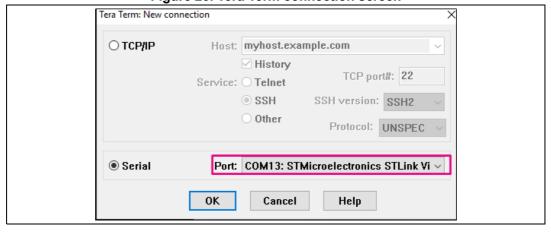

|        |         | 8.4.1   | Download request                                                  | 54 |

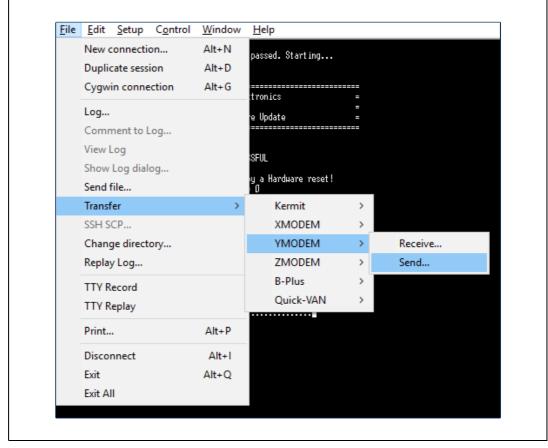

|        |         | 8.4.2   | Send firmware                                                     | 54 |

|        |         | 8.4.3   | File transfer completion                                          | 56 |

|        |         | 8.4.4   | System restart                                                    | 56 |

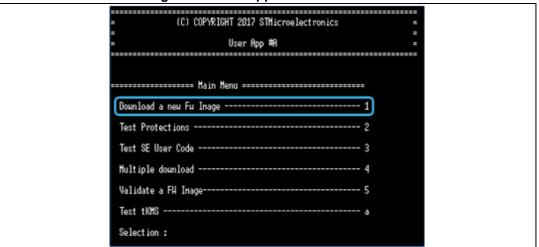

|        | 8.5     | User a  | application execution                                             | 57 |

|        |         | 8.5.1   | Download a new firmware image                                     | 58 |

|        |         | 8.5.2   | Test protections                                                  | 59 |

|        |         | 8.5.3   | Test secure engine user code                                      | 59 |

|        |         | 8.5.4   | Multiple downloads                                                | 60 |

|        |         | 8.5.5   | Firmware image validation                                         | 60 |

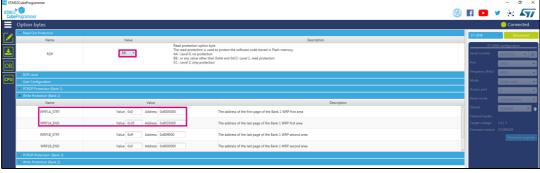

|        | 8.6     | Progra  | amming a new software when the securities are activated           | 61 |

| 9      | Unde    | erstand | ling the last execution status message at boot-up                 | 62 |

| Append | dix A S | Secure- | engine protected environment                                      | 64 |

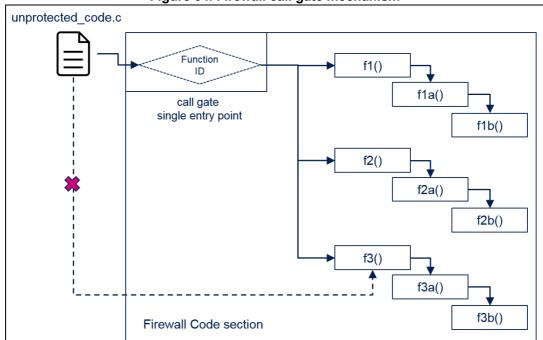

|        | A.1     | Firewa  | all-based secure engine isolation                                 | 65 |

|        |         |         |                                                                   |    |

|          |     |            | SE core call gate mechanism                                   |      |

|----------|-----|------------|---------------------------------------------------------------|------|

|          |     | A.1.2      | SE interface                                                  | . 66 |

|          | A.2 | MPU-bas    | sed secure engine isolation                                   | 67   |

|          |     |            | Principle                                                     |      |

|          |     | A.2.2      | Constraints                                                   | . 70 |

| Appendix | B D | ual-slot   | configuration                                                 | 71   |

|          | B.1 | Elements   | s and roles                                                   | 71   |

|          | B.2 | Mapping    | definition                                                    | 73   |

| Appendix | C S | ingle-slo  | t configuration                                               | 74   |

|          | C.1 | Elements   | s and roles                                                   | 74   |

|          | C.2 | Mapping    | definition                                                    | 74   |

| Appendix | D C | ryptogra   | phic schemes handling                                         | 75   |

|          | D.1 | Cryptogr   | aphic schemes contained in this package                       | 75   |

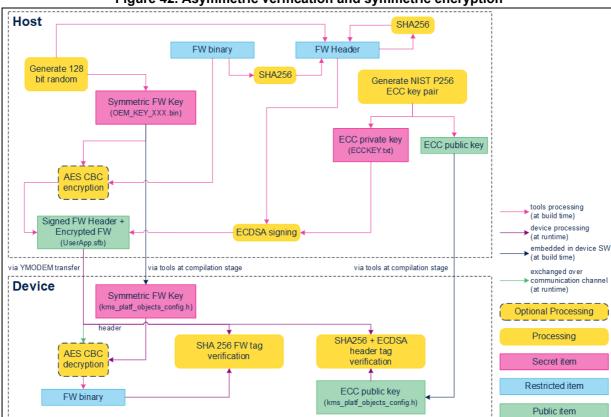

|          | D.2 | Asymme     | tric verification and symmetric encryption schemes            | 76   |

|          |     | D.2.1      | Cryptographic schemes with full software implementation       | . 76 |

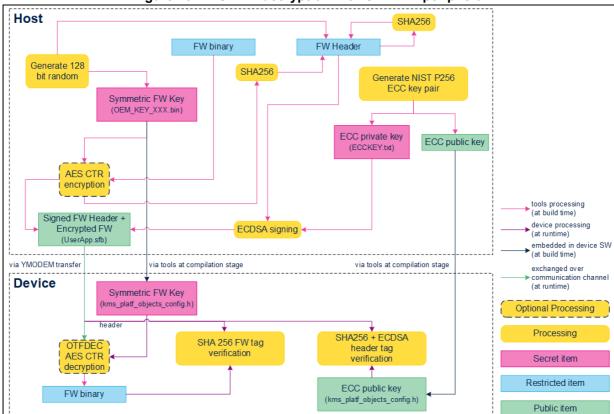

|          |     | D.2.2      | AES CTR decryption with OTFDEC peripheral                     | . 77 |

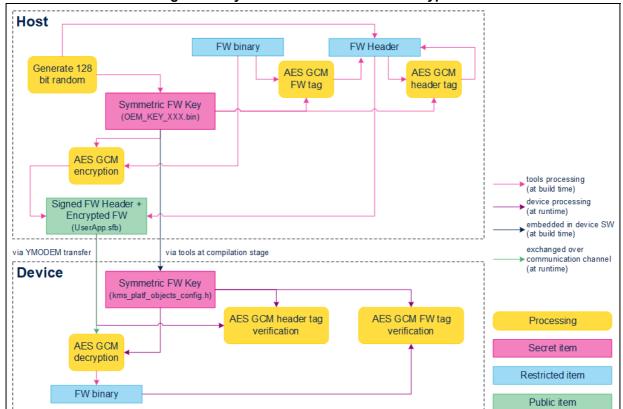

|          | D.3 | Symmetr    | ric verification and encryption scheme                        | 78   |

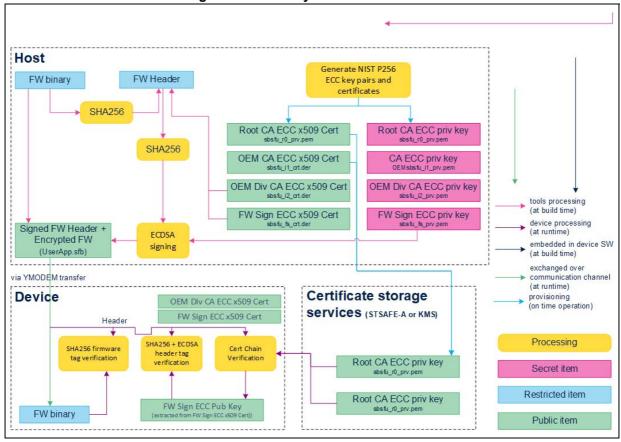

|          | D.4 | X509 cer   | tificate-based asymmetric scheme without firmware encryption. | 79   |

|          | D.5 | Asymme     | tric verification and symmetric encryption schemes            | 80   |

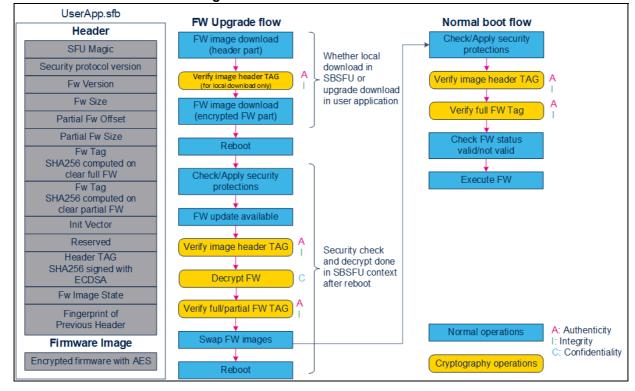

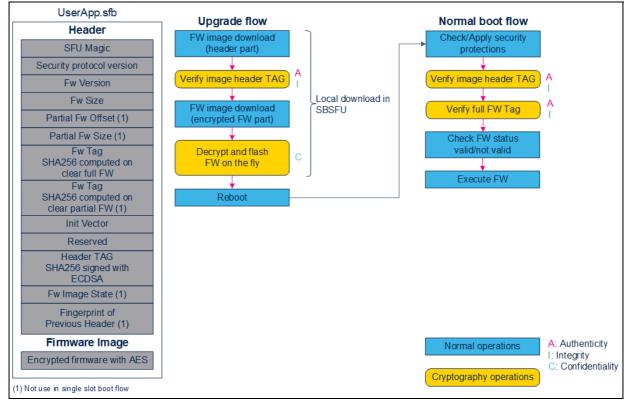

|          | D.6 | Secure b   | oot and secure firmware update flow                           | 81   |

| Appendix | E F | irmware    | image preparation tool                                        | 83   |

|          | E.1 | Tool loca  | tion                                                          | 83   |

|          | E.2 | Inputs .   |                                                               | 83   |

|          | E.3 | Outputs    |                                                               | 84   |

|          | E.4 | IDE integ  | gration                                                       | 84   |

|          | E.5 | Partial In | nage                                                          | 85   |

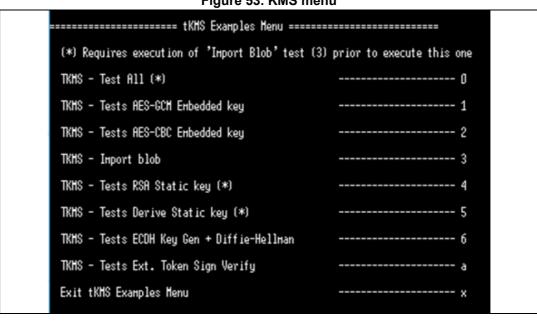

| Appendix | FK  | MS         |                                                               | 86   |

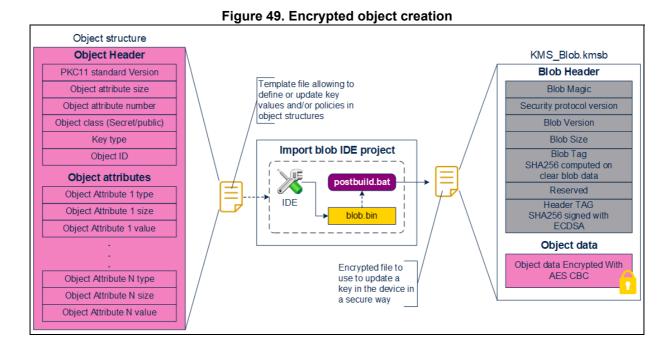

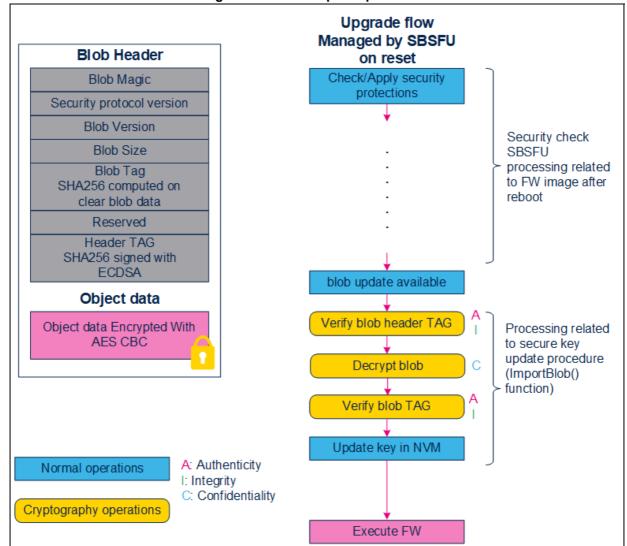

|          | F.1 | Key upda   | ate process description                                       | 86   |

|          | F.2 | SBSFU s    | static keys generation                                        | 87   |

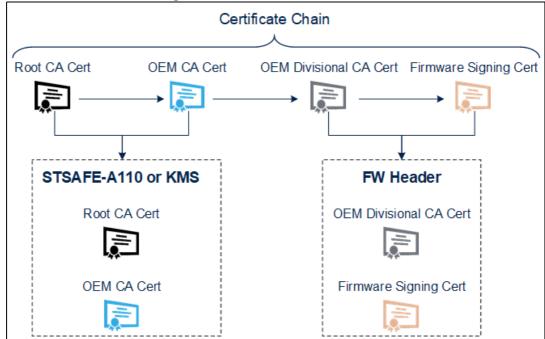

|          | F.3 | Using KN   | AS & X509 cryptographic scheme                                | 88   |

|          |     |            |                                                               |      |

| F.4           | UserApp menu                                                |

|---------------|-------------------------------------------------------------|

| Appendix G    |                                                             |

| G.1           | Introduction to STSAFE-A110                                 |

| G.2           | Certificate generation                                      |

| G.3           | STSAFE-A110 provisioning93                                  |

| G.4           | STM32 and firmware image provisioning                       |

| G.5           | STSAFE-A110 ordering94                                      |

| Appendix H    | STM32WB series specificities                                |

| H.1           | Compilation process                                         |

| H.2           | Key provisioning                                            |

| H.3           | Wireless stack/FUS update                                   |

| Appendix I    | STM32H7 series specificities                                |

| I.1           | JTAG connection capability with configured secure memory 99 |

| 1.2           | External flash memory on STM32H7B3xx devices                |

| 1.3           | STM32H750Bxx devices specificities                          |

| Appendix J    | Validation of the new firmware image                        |

| Revision hist | ory                                                         |

List of tables UM2262

# List of tables

| Table 1. | List of acronyms                                                      | . 9 |

|----------|-----------------------------------------------------------------------|-----|

| Table 2. | List of terms                                                         | 10  |

| Table 3. | Cryptographic scheme comparison                                       | 17  |

| Table 4. | MPU regions in the STM32F4 series, STM32F7 series, and STM32L1 series | 26  |

| Table 5. | MPU regions in the STM32G0 series, STM32G4 series, and STM32H7 series | 28  |

| Table 6. | Error messages at boot-up                                             | 62  |

| Table 7. | MPU regions for secure engine isolation                               | 68  |

| Table 8. | Cryptographic scheme list                                             | 75  |

| Table 9. | Document revision history                                             | 106 |

UM2262 List of figures

# List of figures

| Figure 1.                | Secure boot Root of Trust                                                              | . 15 |

|--------------------------|----------------------------------------------------------------------------------------|------|

| Figure 2.                | Typical in-field device update scenario                                                | . 15 |

| Figure 3.                | KMS functions overview                                                                 |      |

| Figure 4.                | SBSFU security IPs vs. STM32 series (1 of 2)                                           |      |

| Figure 5.                | SBSFU security IPs vs. STM32 series (2 of 2)                                           |      |

| Figure 6.                | STM32L4, STM32L4+, and STM32L0 protection overview during SBSFU execution              |      |

| Figure 7.                | STM32F4, STM32F7, and STM32L1 protection overview during SBSFU execution               |      |

| Figure 8.                | STM32G0, STM32G4, and STM32H7 protection overview during SBSFU execution               |      |

| Figure 9.                | STM32G0, STM32G4, and STM32H7 protection overview                                      |      |

| ga. o o.                 | during user application execution                                                      | 29   |

| Figure 10.               | STM32WB protection overview during SBSFU execution                                     |      |

| Figure 11.               | STM32L4+ with STSAFE-A110 protection overview during SBSFU execution                   |      |

| Figure 12.               | Software architecture overview                                                         |      |

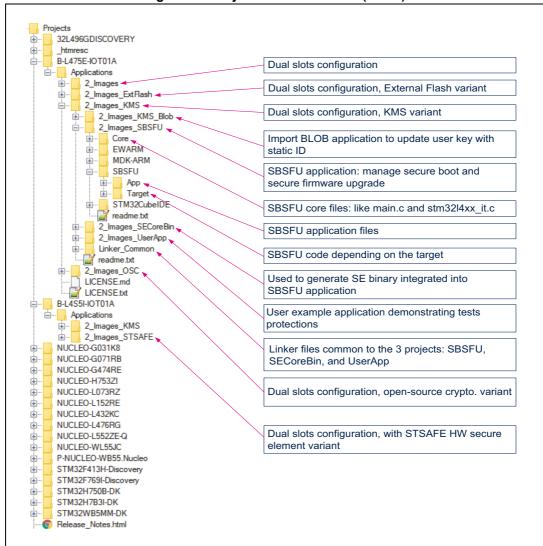

| Figure 13.               | Project folder structure (1 of 2)                                                      |      |

| Figure 14.               | Project folder structure (2 of 2)                                                      |      |

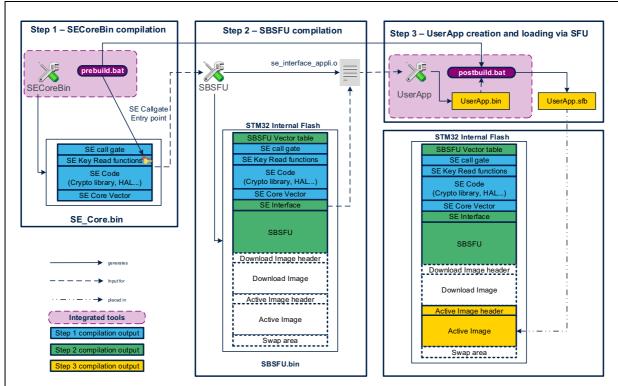

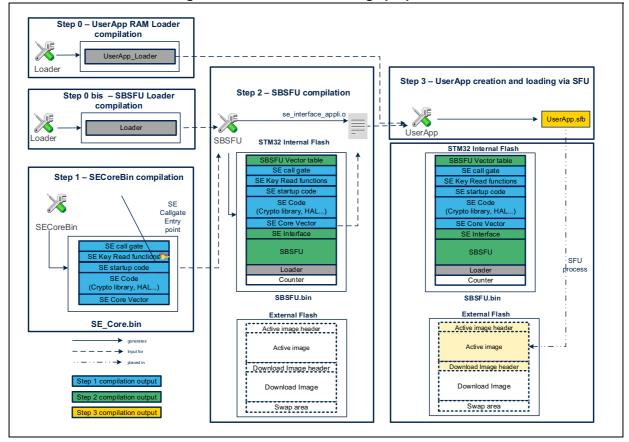

| Figure 15.               | Application compilation steps                                                          |      |

| Figure 16.               | Firmware image preparation tool IDE integration                                        |      |

| Figure 17.               | Step-by-step execution                                                                 |      |

| Figure 18.               | STM32 board preparation                                                                |      |

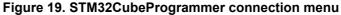

| Figure 19.               | STM32CubeProgrammer connection menu                                                    |      |

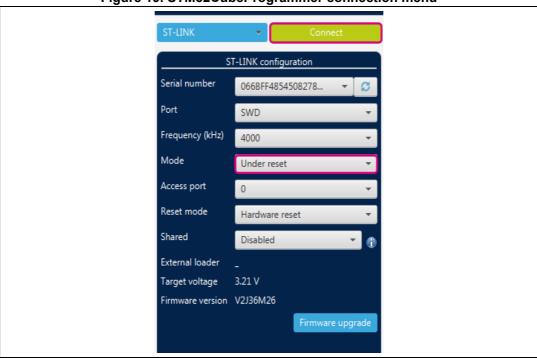

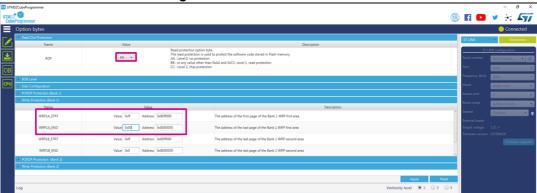

| Figure 20.               | STM32CubeProgrammer Option bytes screen                                                |      |

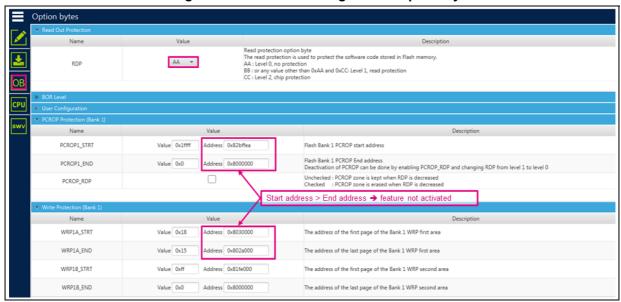

| Figure 21.               | STM32CubeProgrammer erasing                                                            |      |

| Figure 21.               | STM32CubeProgrammer connection menu                                                    |      |

| Figure 23.               | Tera Term connection screen                                                            |      |

| Figure 24.               | Tera Term setup screen                                                                 |      |

| Figure 25.               | SBSFU welcome screen display.                                                          |      |

| Figure 26.               | SBSFU encrypted firmware transfer start                                                |      |

| Figure 20.               |                                                                                        |      |

| -                        | SBSFU encrypted firmware transfer in progress                                          |      |

| Figure 28.<br>Figure 29. | SBSFU reboot after encrypted firmware transfer                                         |      |

| -                        |                                                                                        |      |

| Figure 30.               | Encrypted firmware download via a user application                                     |      |

| Figure 31.               | User application test protection menu                                                  |      |

| Figure 32.               | Option Bytes menu                                                                      |      |

| Figure 33.               | FLASH mass deletion                                                                    |      |

| Figure 34.               | Firewall call gate mechanism                                                           |      |

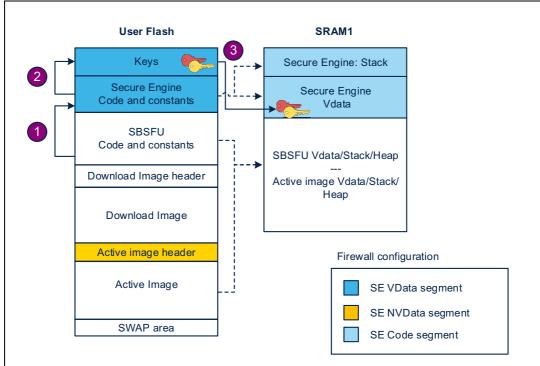

| Figure 35.               | Secure engine call-gate mechanism                                                      |      |

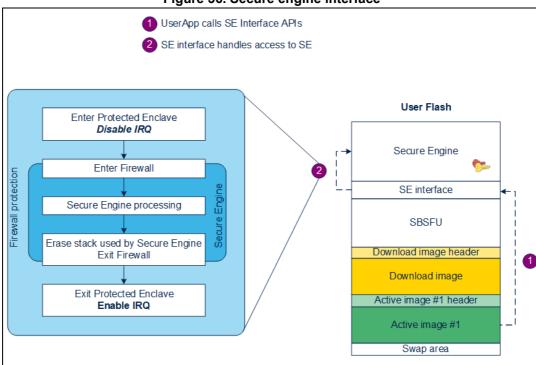

| Figure 36.               | Secure engine interface                                                                |      |

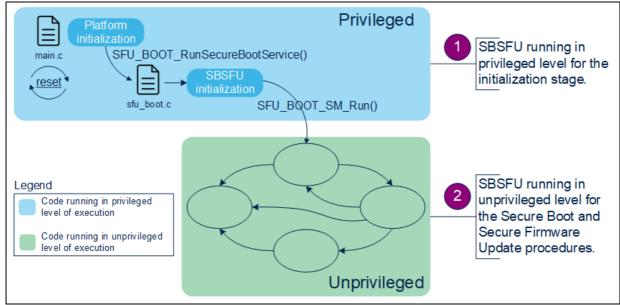

| Figure 37.               | SBSFU running in the unprivileged level of software execution for standard operations. |      |

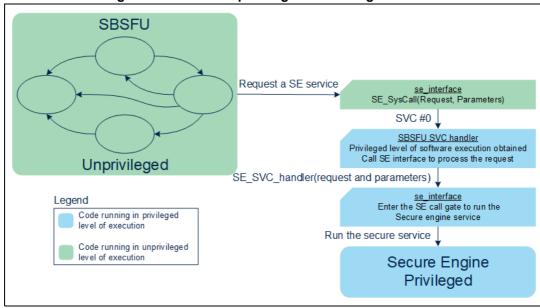

| Figure 38.               | SBSFU requesting a secure engine service                                               |      |

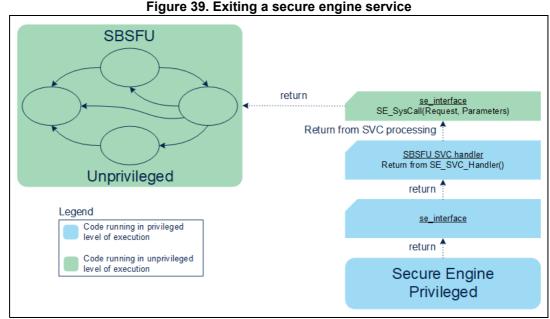

| Figure 39.               | Exiting a secure engine service                                                        | . 69 |

| Figure 40.               | Internal user flash memory mapping:                                                    | 70   |

| E!                       | Example of the NUCLEO-L476RG with 512-byte headers                                     |      |

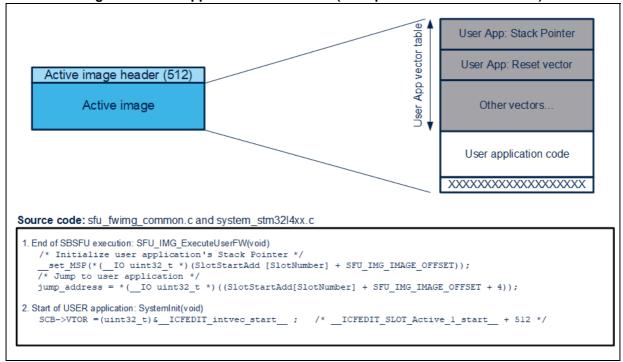

| Figure 41.               | User application vector table (example of the STM32L4 series)                          |      |

| Figure 42.               | Asymmetric verification and symmetric encryption                                       |      |

| Figure 43.               | AES CTR decryption with OTFDEC peripheral                                              |      |

| Figure 44.               | Symmetric verification and encryption                                                  |      |

| Figure 45.               | X509 asymmetric verification                                                           |      |

| Figure 46.               | Certificate chain                                                                      | . 80 |

UM2262 Rev 11 7/109

List of figures UM2262

| Figure 47. | SBSFU dual-slot boot flows                                                       |

|------------|----------------------------------------------------------------------------------|

| Figure 48. | SBSFU single-slot boot flows                                                     |

| Figure 49. | Encrypted object creation                                                        |

| Figure 50. | Secure update procedure                                                          |

| Figure 51. | KMS key storage                                                                  |

| Figure 52. | Certificate chain overview89                                                     |

| Figure 53. | KMS menu                                                                         |

| Figure 54. | Certificate chain overview90                                                     |

| Figure 55. | Pairing key and certificate provisioning overview                                |

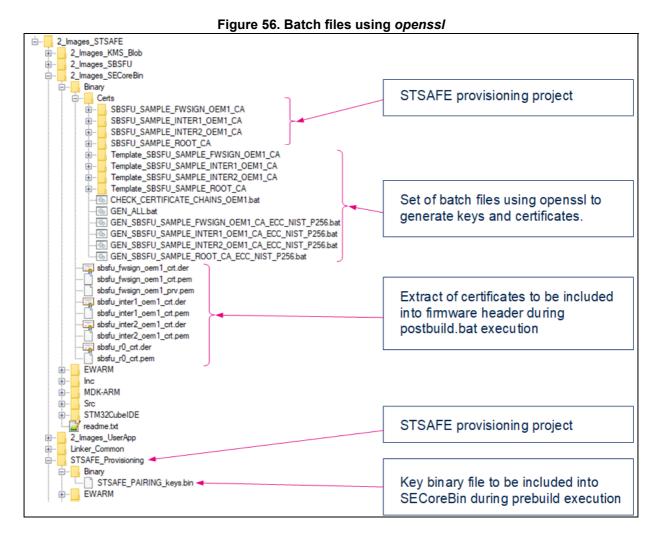

| Figure 56. | Batch files using openssl                                                        |

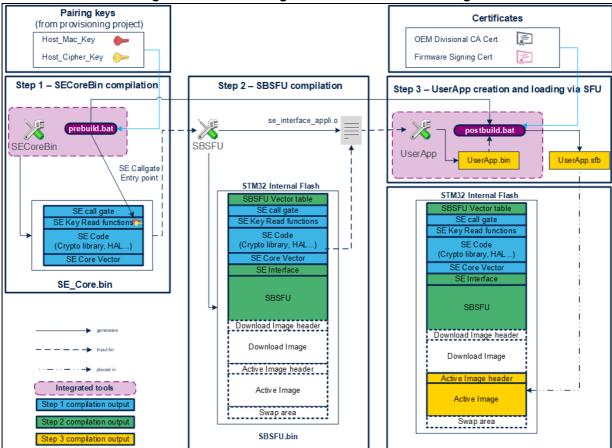

| Figure 57. | Provisioning in STM32 and firmware image                                         |

| Figure 58. | Compile with loader integration (NUCLEO-WB55RG Nucleo mapping) 95                |

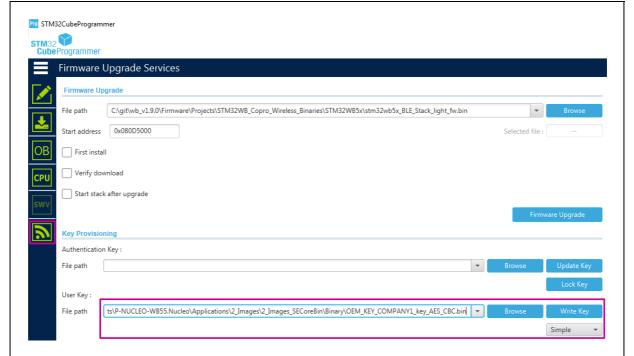

| Figure 59. | Firmware upgrade services panel96                                                |

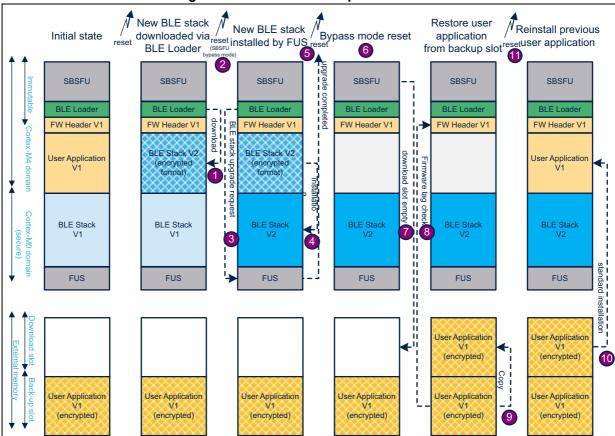

| Figure 60. | Wireless stack update scenario                                                   |

| Figure 61. | JTAG connection capability on STM32H7B3xx MCUs and STM32H753xx MCUs 99           |

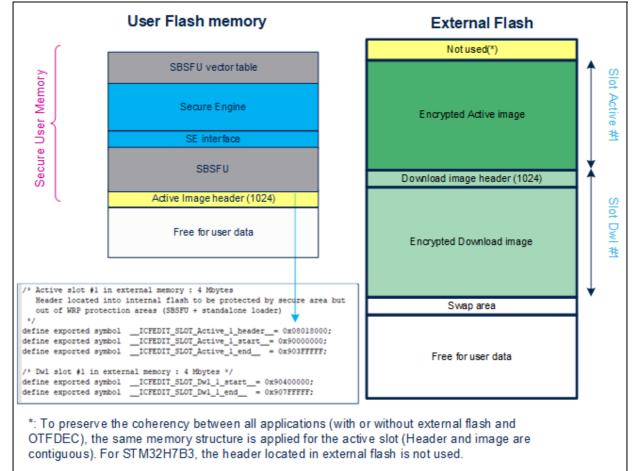

| Figure 62. | STM32H7B3xx: MPU isolation and secure user memory with external flash memory 100 |

| Figure 63. | Memory mapping for STM32H7B3xx devices with external flash memory 101            |

| Figure 64. | STM32H750xx - MPU isolation                                                      |

| Figure 65. | STM32H750xx - Image preparation                                                  |

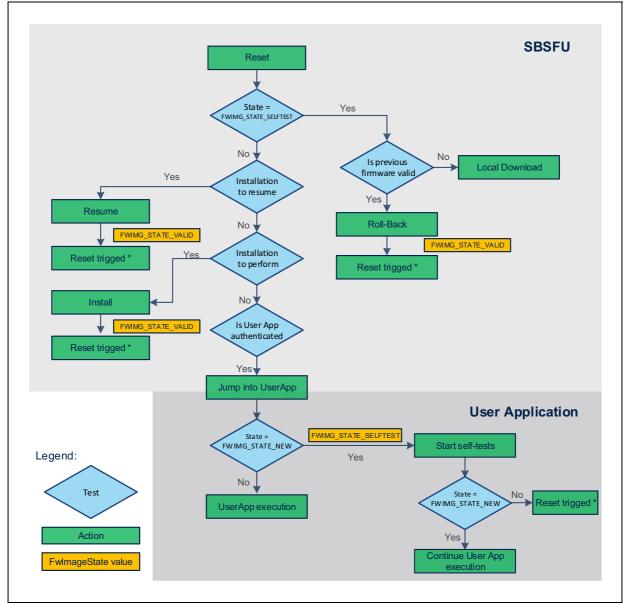

| Figure 66. | Image state handling                                                             |

UM2262 General information

# 1 General information

The X-CUBE-SBSFU Expansion Package comes with examples running on the STM32F4 series, STM32F7 series, STM32G0 series, STM32G4 series, STM32H7 series, STM32L0 series, STM32L1 series, STM32L4 series, STM32L4+ series, and STM32WB series. An example combining STM32 microcontroller and STSAFE-A110 is also provided for the STM32L4+ series.

X-CUBE-SBSFU is provided as a reference code for standalone STM32 system solution examples demonstrating the best use of STM32 protections to protect assets against unauthorized external and internal access. X-CUBE-SBSFU proposes also a system solution example combining STM32 and STSAFE-A110, which demonstrates hardware secure element protections for secure authentication services and secure data storage.

X-CUBE-SBSFU is a starting point for OEMs to develop their SBSFU as a function of their product security requirement levels.

The X-CUBE-SBSFU secure boot and secure firmware update Expansion Package runs on STM32 32-bit microcontrollers based on the Arm<sup>®(a)</sup> Cortex<sup>®</sup>-M processor.

9/109

# 1.1 Terms and definitions

Table 1 presents the definition of acronyms that are relevant for a better understanding of this document.

Table 1. List of acronyms

| Acronym | Description                                |  |  |

|---------|--------------------------------------------|--|--|

| AAD     | Additional authenticated data              |  |  |

| AES     | Advanced encryption standard               |  |  |

| CBC     | AES cipher block chaining                  |  |  |

| CKS     | Customer key storage                       |  |  |

| CTR     | AES counter-based cipher mode              |  |  |

| DMA     | Direct memory access                       |  |  |

| DSA     | Digital signature algorithm                |  |  |

| ECC     | Elliptic curve cryptography                |  |  |

| ECCN    | Export control classification number       |  |  |

| ECDSA   | Elliptic curve digital signature algorithm |  |  |

| FSM     | Finite-state machine                       |  |  |

| GCM     | AES Galois/counter mode                    |  |  |

| GUI     | Graphical user interface                   |  |  |

a. Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

UM2262 Rev 11

General information UM2262

Table 1. List of acronyms (continued)

| Acronym | Description                                         |  |  |

|---------|-----------------------------------------------------|--|--|

| HAL     | Hardware abstraction layer                          |  |  |

| HDP     | Hide protect memory (also named secure user memory) |  |  |

| IDE     | Integrated development environment                  |  |  |

| IV      | Initialization vector                               |  |  |

| IWDG    | Independent watchdog                                |  |  |

| FW      | Firmware                                            |  |  |

| FWALL   | Firewall                                            |  |  |

| KMS     | Key management services                             |  |  |

| MAC     | Message authentication code                         |  |  |

| MCU     | Microcontroller unit                                |  |  |

| MPU     | Memory protection unit                              |  |  |

| NONCE   | Number used only once                               |  |  |

| OTFDEC  | On-the-fly decryption                               |  |  |

| PCROP   | Proprietary code read-out protection                |  |  |

| PEM     | Privacy enhanced mail                               |  |  |

| RDP     | Read protection                                     |  |  |

| SB      | Secure boot                                         |  |  |

| SE      | Secure engine                                       |  |  |

| SFU     | Secure firmware update                              |  |  |

| SM      | State machine                                       |  |  |

| UART    | Universal asynchronous receiver/transmitter         |  |  |

| UUID    | Universally unique identifier                       |  |  |

| WRP     | Write protection                                    |  |  |

*Table 2* presents the definition of terms that are relevant for a better understanding of this document.

Table 2. List of terms

| Term            | Description                                                                                                                               |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Firmware image  | A binary image (executable) is run by the device as a user application.                                                                   |  |

| Firmware header | header Bundle of meta-data describing the firmware image to be installed. It contains firmware information and cryptographic information. |  |

| mbedTLS         | mbed implementation of the TLS and SSL protocols and the respective cryptographic algorithms.                                             |  |

| sfb file        | Binary file packing the firmware header and the firmware image.                                                                           |  |

UM2262 General information

# 1.2 References

### STMicroelectronics related documents

Public documents are available online from the STMicroelectronics website at *www.st.com*. Contact STMicroelectronics when more information is needed.

- 1. Application note *How to integrate the X-CUBE-SBSFU STM32Cube Expansion Package* (AN5056)

- 2. Application note *Introduction to security for STM32 MCUs* (AN5156)

- 3. User manual STM32CubeProgrammer software description (UM2237)

- 4. Datasheet Authentication, state-of-the-art security for peripherals and IoT devices (DS12911)

### Other documents

5. PKCS #11 Cryptographic Token Interface Current Mechanisms Specification Version 2.40

https://docs.oasis-open.org/pkcs11/pkcs11-curr/v2.40/os/pkcs11-curr-v2.40-os.html(a)

4

UM2262 Rev 11 11/109

a. The URL belongs to a third-party. It might be moved, modified, and/or inactivated by them at any time. STMicroelectronics is not responsible for the content of the referenced website.

STM32Cube overview UM2262

# 2 STM32Cube overview

#### What is STM32Cube?

STM32Cube is an STMicroelectronics original initiative to improve designer productivity significantly by reducing development effort, time, and cost. STM32Cube covers the whole STM32 portfolio.

#### STM32Cube includes:

- A set of user-friendly software development tools to cover project development from conception to realization, among which are:

- STM32CubeMX, a graphical software configuration tool that allows the automatic generation of C initialization code using graphical wizards

- STM32CubeIDE, an Eclipse<sup>®</sup>-based IDE, providing code edition, compilation, programming, and debugging capabilities

- STM32CubeCLT, an all-in-one command-line development toolset with code compilation, board programming, and debug features

- STM32CubeIDE for Visual Studio Code (STM32VSCode), a complete IDE based on VS Code<sup>®</sup> platform

- STM32CubeProgrammer (STM32CubeProg), a programming tool available in graphical and command-line versions

- STM32CubeMonitor (STM32CubeMonitor, STM32CubeMonPwr, STM32CubeMonRF, STM32CubeMonUCPD) powerful monitoring tools to finetune the behavior and performance of STM32 applications in real time

- STM32CubeWiSE (STM32CubeWiSEcg, STM32CubeWiSEre), graphical tools designed to evaluate and test the capabilities of sub-GHz radios and protocols

- STM32Cube MCU and MPU Packages, comprehensive embedded-software platforms specific to each microcontroller and microprocessor series (such as STM32CubeL4 for the STM32L4 series and STM32L4+ series), which include:

- STM32Cube hardware abstraction layer (HAL), ensuring maximized portability across the STM32 portfolio

- STM32Cube low-layer APIs, ensuring the best performance and footprints with a high degree of user control over hardware

- A consistent set of middleware components such as FAT file system, RTOS, USB Host and Device, touch library, and graphics

- All embedded software utilities with full sets of peripheral and applicative examples

- STM32Cube Expansion Packages, which contain embedded software components that complement the functionalities of the STM32Cube MCU and MPU Packages with:

- Middleware extensions and applicative layers

- Examples running on some specific STMicroelectronics development boards

UM2262 STM32Cube overview

# How does this software complement STM32Cube?

The proposed software is based on the STM32CubeHAL, the hardware abstraction layer for the STM32 microcontroller. The package extends STM32Cube by providing middleware components:

- Secure engine for managing all critical data and operations, such as cryptography operations accessing the firmware encryption keys and others

- Key management services offering cryptographic services via PKCS #11 APIs

- STSAFE-A for managing hardware secure element features

The package includes different sample applications to provide a complete SBSFU solution:

- SE\_CoreBin application: provides a binary including all the 'trusted' code.

- Secure boot and secure firmware upgrade (SBSFU) application:

- Secure boot (Root of Trust)

- Local download via UART Virtual COM

- Firmware installation management

- User application:

- Downloads a new firmware in the dual-slot mode of operation

- Provides examples of testing protection mechanisms

- Provides examples using KMS APIs

The sample applications are delivered in dual-slot and single-slot modes of operation and can be configured in different cryptographic schemes.

Note: The single-slot configuration is demonstrated in examples named 1\_Image.

The dual-slot configuration is demonstrated in examples named 2\_Images.

This user manual describes the typical use of the package:

- Based on the NUCLEO-L476RG board

- With sample applications operating in dual-slot mode and configured with asymmetric authentication and symmetric firmware encryption

More information about the configuration options and the single-slot mode of operation are provided in the appendices of this document.

Note: The KMS feature is available on the STM32L4 series and STM32L4+ series with the example provided on the B-L475E-IOT01A and B-L4S5I-IOT01A boards.

Note: The STSAFE-A110 feature is available on the STM32L4+ series with an example provided on the B-L4S5I-IOT01A board.

47/

UM2262 Rev 11 13/109

#### Secure boot and secure firmware update (SBSFU) 3

#### 3.1 **Product security introduction**

A device deployed in the field operates in an untrusted environment and it is therefore subject to threats and attacks. To mitigate the risk of attack, the goal is to allow only authentic firmware to run on the device. Allowing the update of firmware images to fix bugs, or introduce new features or countermeasures, is commonplace for connected devices, but it is prone to attacks if not executed securely.

Consequences may be damaging such as firmware cloning, malicious software download, or device corruption. Security solutions have to be designed to protect sensitive data (potentially even the firmware itself) and critical operations.

Typical countermeasures are based on cryptography (with an associated secret key) and memory protections:

- Cryptography ensures integrity (the assurance that data has not been corrupted), authentication (the assurance that a certain entity is who it claims to be) and confidentiality (the assurance that only authorized users can read sensitive data) during firmware transfer.

- Memory protection mechanisms prevent external attacks (for example by accessing the device physically through JTAG) and internal attacks from other embedded processes.

The following chapters describe solutions implementing confidentiality, integrity, and authentication services to address the most common threats for an IoT end-node device.

#### 3.2 Secure boot

Secure boot (SB) asserts the integrity and authenticity of the user application image that is executed: cryptographic checks are used to prevent any unauthorized or maliciously modified software from running. The secure boot process implements a Root of Trust (refer to Figure 1): starting from this trusted component (1), every other component is authenticated (2) before its execution (3).

The **integrity** is verified to be sure that the image that is going to be executed has not been corrupted or maliciously modified.

An authenticity check aims to verify that the firmware image is coming from a trusted and known source to prevent unauthorized entities to install and execute code.

Reset Code **Application** Code **Authenticates** Secure Boot Trusted

Figure 1. Secure boot Root of Trust

#### 3.3 Secure firmware update

Secure firmware update (SFU) provides a secure implementation of in-field firmware updates, enabling the download of new firmware images to a device in a secure way.

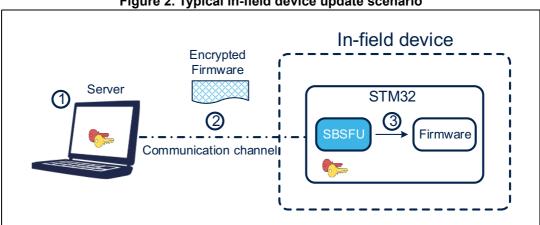

As shown in Figure 2, two entities are typically involved in a firmware update process:

- Server

- OEM manufacturer server/web service

- Stores the new version of device firmware

- Communicates with the device and sends the new image version in an encrypted form if it is available

- Device

- Deployed in the field

- Embeds a code running firmware update process.

- Communicates with the server and receives a new firmware image.

- Authenticates decrypts and installs the new firmware image then executes it.

Figure 2. Typical in-field device update scenario

(7)

UM2262 Rev 11 15/109 Firmware update runs through the following steps:

- 1. If a firmware update is needed, a new encrypted firmware image is created and stored in the server.

- 2. The new encrypted firmware image is sent to the device deployed in the field through an untrusted channel.

- 3. The new image is downloaded, checked, and installed.

The firmware update can be done on the complete firmware image, or only on a portion of the firmware image (only for dual-slot configuration).

The firmware update is vulnerable to the threats presented in *Section 3.1: Product security introduction*: cryptography is used to ensure confidentiality, integrity, and authentication.

**Confidentiality** is implemented to protect the firmware image, which may be a key asset for the manufacturer. The firmware image sent over the untrusted channel is encrypted so that only devices having access to the encryption key can decrypt the firmware package.

The **integrity** is verified to be sure that the received image is not corrupted.

The **authenticity** check aims to verify that the firmware image is coming from a trusted and known source, to prevent unauthorized entities to install and execute code.

# 3.4 Cryptography operations

The X-CUBE-SBSFU STM32Cube Expansion Package is delivered with four cryptographic schemes using both asymmetric and symmetric cryptography.

The default cryptographic scheme demonstrates ECDSA asymmetric cryptography for firmware verification and AES-CBC symmetric cryptography for firmware decryption. Thanks to asymmetric cryptography, firmware verification can be performed with public-key operations so that no secret information is required in the device.

The alternative cryptographic schemes provided in the X-CUBE-SBSFU Expansion Package are:

- ECDSA asymmetric cryptography for firmware verification with AES-CBC or AES-CTR symmetric cryptography for firmware encryption

- ECDSA asymmetric cryptography for firmware verification without firmware encryption

- X509 certificate-based ECDSA asymmetric cryptography for firmware verification without firmware encryption

- AES-GCM symmetric cryptography for both firmware verification and encryption.

*Table 3* presents the various security features associated with each of the cryptographic schemes.

Table 3. Cryptographic scheme comparison

| Features                     | Asymmetric with AES encryption                                                                                         | Asymmetric without encryption                                                                             | X509 certificate-based asymmetric without encryption                            | Symmetric<br>(AES-GCM) <sup>(1)</sup> |

|------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------|

| Confidentiality              | AES-CBC encryption,<br>or AES-CTR<br>encryption for STM32<br>MCUs supporting<br>OTFDEC processing<br>(firmware binary) | No, the user firmware is in a clear format.                                                               |                                                                                 | AES-GCM encryption (firmware binary)  |

| Integrity                    | SHA256 (Firmware head                                                                                                  | ·)                                                                                                        | AES-GCM Tag                                                                     |                                       |

| Authentication               |                                                                                                                        | SHA256 of the firmware header is ECDSA signed SHA256 of the firmware binary stored in the firmware header |                                                                                 |                                       |

| Cryptographic keys in device | Private AES-CBC/<br>ES-CTR key (secret)<br>Public ECDSA key                                                            | Public ECDSA key                                                                                          | Public ECDSA key in<br>X509 certificate chain<br>(stored in STSAFE-A or<br>KMS) | Private AES-GCM<br>key (secret)       |

<sup>1.</sup> For the symmetric cryptographic scheme, it is highly recommended to configure a unique symmetric key for each product.

UM2262 Rev 11 17/109

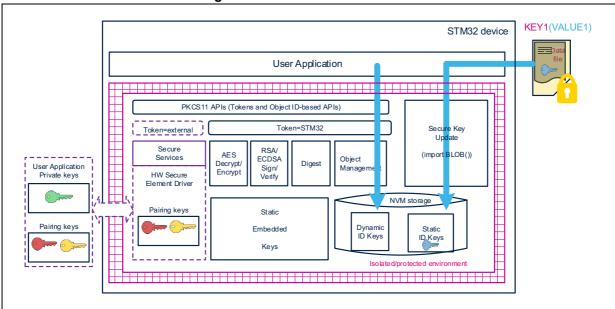

# 4 Key management services

Key management services (KMS) middleware provides cryptographic services through the standard PKCS #11 APIs (specified by OASIS) allowing to abstract the key value to the caller (using object ID and not directly the key-value). KMS is executed inside a protected/isolated environment to ensure that the key value cannot be accessed by an unauthorized code running outside the protected/isolated environment.

KMS also offers the possibility to use cryptographic services with keys that are managed securely outside the STM32 microcontroller, such as by an STSAFE-A110 secure element for example (rooting based on token ID).

KMS only supports a subset of PKCS #11 APIs:

- Object management functions: creation/update/deletion

- AES encryption functions

- AES decryption functions

- Digesting functions

- RSA and ECDSA Signing/Verifying functions

- Key management functions: key generation/derivation

KMS manages three types of keys:

- Static Embedded keys:

- Predefined keys are embedded within the code. Such keys cannot be modified.

- Updatable keys with Static ID:

- Keys IDs are predefined in the system

- The key value can be updated in an NVM storage via a secure procedure using static embedded root keys (authenticity check, data integrity check, and data decryption)

- Key cannot be deleted

- Updatable keys with dynamic ID:

- Key IDs are defined when creating the keys

- The key value is created using internal functions. Typically, the DeriveKey() function creates dynamic objects.

- Key can be deleted

Figure 3. KMS functions overview

For more details regarding the OASIS PKCS #11 standard, refer to [5].

UM2262 Rev 11 19/109

# 5 Protection measures and security strategy

Cryptography ensures integrity, authentication, and confidentiality. However, the use of cryptography alone is not enough: a set of measures and system-level strategies are needed for protecting critical operations and sensitive data (such as a secret key), and the execution flow, to resist possible attacks.

Secure software coding techniques such as doubling critical tests, doubling critical actions, checking parameter values, and testing a flow control mechanism, are implemented to resist basic fault-injection attacks.

The security strategy is based on the following concepts:

- Ensure single entry point at reset: Force code execution to start with secure boot code

- Make SBSFU code and SBSFU secrets immutable: No possibility to modify or alter them once security is fully activated

- Create a protected enclave isolated from SBSFU application and user applications to store secrets such as keys, and to run critical operations such as cryptographic algorithms

- Limit surface execution to SBSFU code during SBSFU application execution

- Remove JTAG access to the device

- Monitor the system: intrusion detection and SBSFU execution time

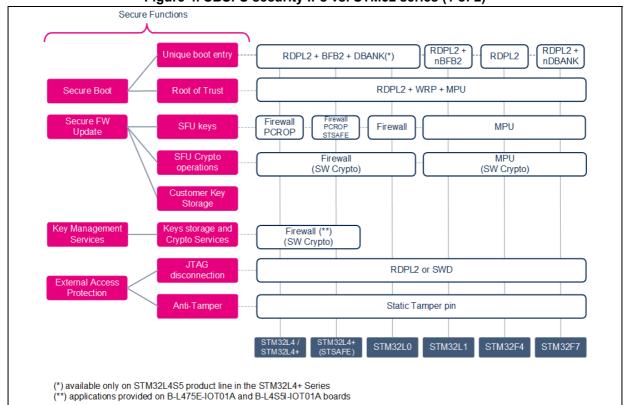

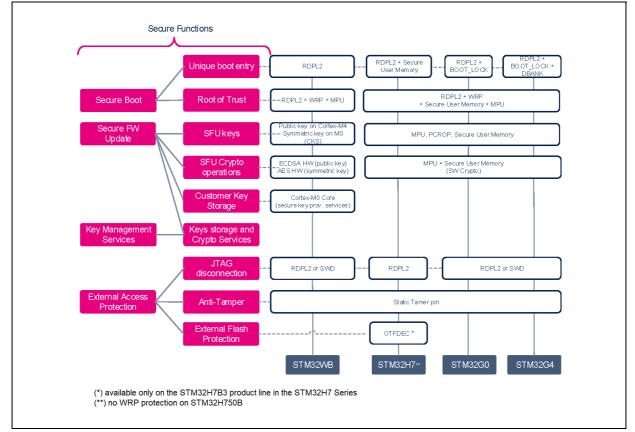

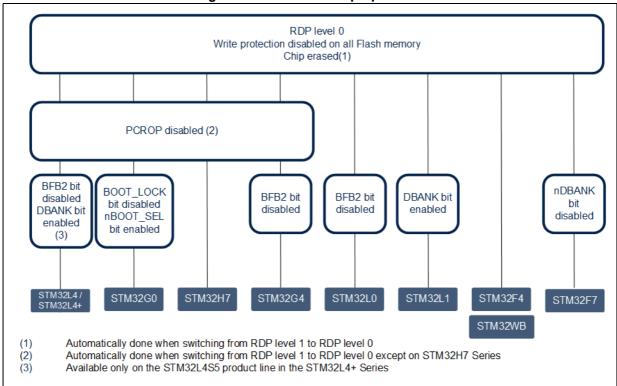

*Figure 4* and *Figure 5* give a high-level view of the security mechanisms activated on each STM32 series.

Figure 4. SBSFU security IPs vs. STM32 series (1 of 2)

4

Figure 5. SBSFU security IPs vs. STM32 series (2 of 2)

UM2262 Rev 11 21/109

# 5.1 STM32L4 series, STM32L4+ series, and STM32L0 series

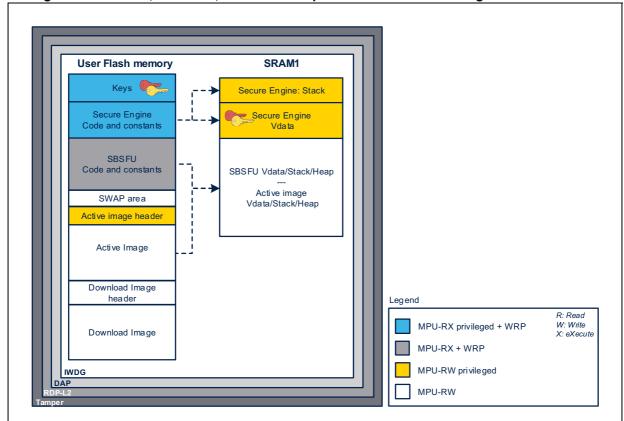

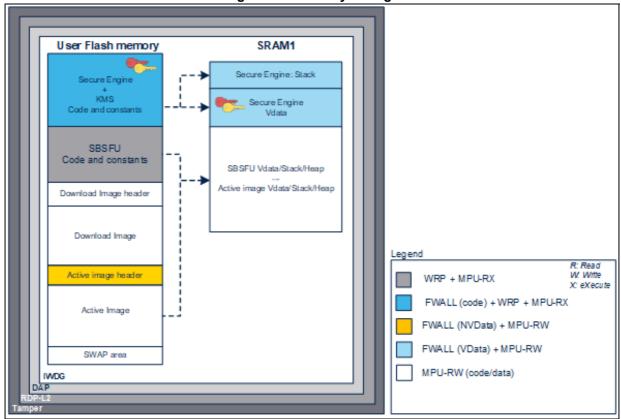

*Figure 6* illustrates how the system, the code, and the data are protected in the X-CUBE-SBSFU application example for the STM32L4 series, STM32L4+ series, and STM32L0 series.

Figure 6. STM32L4, STM32L4+, and STM32L0 protection overview during SBSFU execution **User Flash memory** SRAM1 Keys 🔮 Secure Engine: Stack Secure Engine Secure Engine Code and constants Vdata SBSFU Code and constants SBSFU Vdata/Stack/Heap Active image Download Image header Vdata/Stack/Heap Download Image Legend R: Read Active image header WRP + MPU-RX X: eXecute FWALL (code) + WRP + MPU-RX Active Image FWALL (code) + WRP + PCROP + MPU-RX FWALL (NVData) + MPU-RW SWAP area FWALL (VData) + MPU-RW IWDG MPU-RW (code/data)

# Protections against outer attacks

Outer attacks refer to attacks triggered by external tools such as debuggers or probes, trying to access the device. In the SBSFU application example, RDP, tamper, DAP, and IWDG protections are used to protect the product against outer attacks:

- **RDP** (Read Protection): Read Protection Level 2 is mandatory to achieve the highest level of protection and to implement a Root of Trust:

- External access via the JTAG hardware interface to RAM and flash memory is forbidden. This prevents attacks aiming to change SBSFU code and therefore mining the Root of Trust.

- Option bytes cannot be changed. This means that other protections such as WRP and PCROP cannot be changed anymore.

Caution - RDP level 1 is not proposed for the following reasons:

- 1. Secure boot/Root of Trust (single entry point and immutable code) cannot be ensured, because Option bytes (WRP) can be modified in RDP L1.

- 2. Device internal flash memory can be fully reprogrammed (after flash memory mass erasure via RDP L0 regression) with a new firmware without any security.

- 3. Secrets in RAM protected by the firewall can be accessed by attaching the debugger via the JTAG hardware interface on a system reset.

In case JTAG hardware interface access is not possible at customer product, and in case the customer uses a trusted and reliable user application code, then the above highlighted risks are not valid.

- **Tamper**: the anti-tamper protection is used to detect physical tampering actions on the device and to take related countermeasures. In the case of tampering detection, the SBSFU application example forces a reboot.

- DAP (Debug Access Port): the DAP protection consists of de-activating the DAP (Debug Access Port). Once de-activated, JTAG pins are no longer connected to the STM32 internal bus. DAP is automatically disabled with RDP Level 2.

- **IWDG** (Independent Watchdog): IWDG is a free-running down-counter. Once running, it cannot be stopped. It must be refreshed periodically before it causes a reset. This mechanism allows the control of SBSFU execution duration.

### **Protections against inner attacks**

Inner attacks refer to attacks triggered by code running in the STM32. Attacks may be due to either malicious firmware exploiting bugs or security breaches, or unwanted operations. In the SBSFU application example, WRP, firewall, PCROP, and MPU protections preserve the product from inner attacks:

- **FWALL** (firewall): the firewall is configured to protect the code, volatile and non-volatile data. Protected code is accessible through a single entry point (the call gate mechanism is described in *Appendix A*). Any attempt to jump and try to execute any of the functions included in the code section without passing through the entry point generates a system reset.

- In the KMS example, keys and cryptographic services are executed inside the isolated environment under firewall protection.

UM2262 Rev 11 23/109

- **PCROP**<sup>(1)</sup> (proprietary code readout protection): a section of flash memory is defined as execute-only through PCROP protection. It is not possible to access this section in reading or writing. Being an execute-only area, a key is protected with PCROP only if it is 'embedded' in a piece of code: executing this code moves the key to a specific pointer in RAM. Placed behind the firewall, its execution is impossible from the outside.

- **WRP** (write protection): write protection is used to protect trusted code from external attacks or even internal modifications such as unwanted writings/erase operations on critical code/data.

- MPU (memory protection unit): the MPU is used to make an embedded system more

robust by splitting the memory map for flash memory and SRAMs into regions having

their access rights. In the SBSFU application example, MPU is configured to ensure

that no other code is executed from any memories during SBSFU code execution.

When leaving the SBSFU application, the MPU configuration is updated to authorize

also the execution of the user application code.

- Read protection is tightly coupled with write protection for the STM32L0 series: when activated, any readprotected sector is also write-protected. For this reason, read protection cannot be activated.

# 5.2 STM32F4 series, STM32F7 series, and STM32L1 series

*Figure* 7 illustrates how the system, the code, and the data are protected in the X-CUBE-SBSFU application example for the STM32F4 series, STM32F7 series, and STM32L1 series.

Figure 7. STM32F4, STM32F7, and STM32L1 protection overview during SBSFU execution

# Protections against outer attacks

Outer attacks refer to attacks triggered by external tools such as debuggers or probes, trying to access the device. In the SBSFU application example, RDP, tamper, DAP, and IWDG protections are used to protect the product against outer attacks:

- **RDP** (Read Protection): Read Protection Level 2 is mandatory to achieve the highest level of protection and to implement a Root of Trust:

- External access via the JTAG hardware interface to RAM and flash memory is forbidden. This prevents attacks aiming to change SBSFU code and therefore mining the Root of Trust.

- Option bytes cannot be changed. This means that other protections such as WRP and PCROP cannot be changed anymore.

Caution - RDP level 1 is not proposed for the following reasons:

- 1. Secure boot/Root of Trust (single entry point and immutable code) cannot be ensured, because Option bytes (WRP) can be modified in RDP L1.

- 2. Device internal flash memory can be fully reprogrammed (after flash memory mass erasure via RDP L0 regression) with a new firmware without any security.

- 3. Secrets in RAM protected by the firewall can be accessed by attaching the debugger via the JTAG hardware interface on a system reset.

In case JTAG hardware interface access is not possible at customer product, and in case the customer uses a trusted and reliable user application code, then the above highlighted risks are not valid.

- **Tamper**: the anti-tamper protection is used to detect physical tampering actions on the device and to take related countermeasures. In the case of tampering detection, the SBSFU application example forces a reboot.

- DAP (Debug Access Port): the DAP protection consists of de-activating the DAP (Debug Access Port). Once de-activated, JTAG pins are no longer connected to the STM32 internal bus. DAP is automatically disabled with RDP Level 2.

- **IWDG** (Independent Watchdog): IWDG is a free-running down-counter. Once running, it cannot be stopped. It must be refreshed periodically before it causes a reset. This mechanism allows the control of SBSFU execution duration.

# Protections against inner attacks

Inner attacks refer to attacks triggered by code running in the STM32. Attacks may be due to either malicious firmware exploiting bugs or security breaches, or unwanted operations. In the SBSFU application example, WRP and MPU protections preserve the product from inner attacks:

- **WRP** (write protection): write protection is used to protect trusted code from external attacks or even internal modifications such as unwanted writing or erase operations on critical code or data.

- **MPU** (memory protection unit): the protected environment managing all critical data and operations (secure engine) is isolated from the other software components by leveraging the MPU. The secure engine code and data can be accessed only through a privileged level of software execution. Therefore, software running at a non-privileged level cannot call secure engine services or access critical data. This strict access control to secure engine services and resources is implemented by defining specific MPU regions as described in *Table 4*.

UM2262 Rev 11 25/109

Table 4. MPU regions in the STM32F4 series, STM32F7 series, and STM32L1 series

| Region content                   | Privileged permission         | Unprivileged permission |

|----------------------------------|-------------------------------|-------------------------|

| Secure engine code and constants | Read-only (execution allowed) | No access               |

| Secure engine stack and VDATA    | Read/write (not executable)   | No access               |

Besides, the MPU also ensures that only authorized code is granted execution permission when the secure boot and secure firmware update processes are running. This is the reason why the MPU configuration is updated before launching the user application to authorize its execution. Nevertheless, the secure engine isolation settings and supervisor call mechanisms still apply when running the user application (not only when running the SBSFU code).

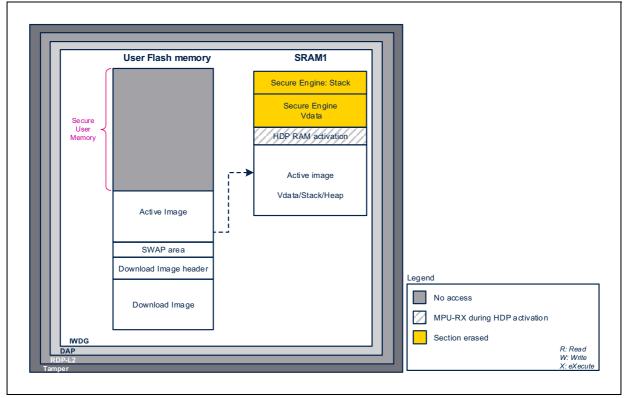

# 5.3 STM32G0 series, STM32G4 series, and STM32H7 series

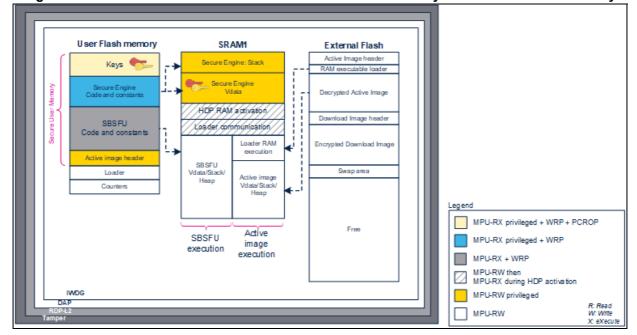

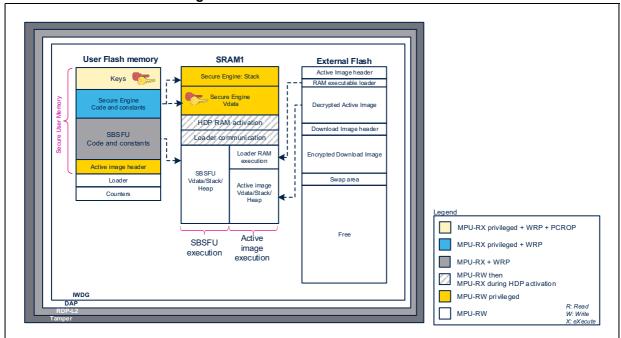

*Figure 8* illustrates how the system, the code, and the data are protected in the X-CUBE-SBSFU application example for the STM32G0 series, STM32G4 series, and STM32H7 series<sup>(a)</sup>.

For the specificities of STM32H7B3xx devices, refer to appendix *I.2: External flash memory on STM32H7B3xx devices*.

For the specificities of STM32H750xx devices, refer to appendix *I.3:* STM32H750Bxx devices specificities.

**User Flash memory** SRAM1 Keys Secure Engine: Stack Secure Engine Code and constants Use HDP RAM activation SBSFU Code and constants SBSFU Vdata/Stack/Heap Active image Vdata/Stack/Heap Active Image SWAP area MPU-RX privileged + WRP + PCROP Download Image header MPU-RX privileged + WRP MPU-RX + WRP Download Image MPU-RW then MPU-RX during HDP activation MPU-RW privile ged R: Read W: Write MPU-RW

Figure 8. STM32G0, STM32G4, and STM32H7 protection overview during SBSFU execution

a. X-CUBE-SBSFU complements the STM32CubeH7 MCU Package, which applies to the STM32H7 series but the STM32H7Rx/Sx MCUs. Similarly, the X-CUBE-SBSFU application note (AN5056) and user manual (UM2262) do not apply to the STM32H7Rx/Sx MCUs.

# Protections against outer attacks

Outer attacks refer to attacks triggered by external tools such as debuggers or probes, trying to access the device. In the SBSFU application example, RDP, tamper, DAP, and IWDG protections are used to protect the product against outer attacks:

#### RDP (Read Protection):

- Read Protection Level 2 allows achieving the highest level of protection and to implement a Root of Trust.

- External access via the JTAG HW interface to RAM and flash memory is forbidden. This prevents attacks aiming to change SBSFU code and therefore mining the Root of Trust.

- Option bytes cannot be changed. This means that other protections such as WRP and PCROP cannot be changed anymore.

- Read Protection level 1 allows achieving a lower level of protection than RDP level 2 for the following reasons:

- Code/Data stored in internal flash memory can be modified (removing immutability), once Option bytes (WRP) is reset (not possible in RDP Level 2).

- Device internal flash memory can be fully reprogrammed in RDP level 1 (after flash memory massive erasure via RDP L0 regression) with a new firmware without any security.

- Secrets in RAM can be accessed by attaching the debugger via the JTAG HW interface on a system reset<sup>(1)</sup>.

- Read Protection Level 0 does not support any protection and full product access is allowed.

**Secure boot/Root of Trust:** After reset, that part of the customer code is forced to run first using the *BOOT\_Lock* configuration. It is isolated from the rest of the runtime firmware using the Securable memory area protection.

**Tamper:** The anti-tamper protection is used to detect physical tampering actions on the device and to take related countermeasures. In the case of tampering detection, the SBSFU application example forces a reboot.

**DAP (Debug Access Port):** The DAP protection consists of de-activating the DAP (Debug Access Port). Once de-activated, JTAG pins are no longer connected to the STM32 internal bus. DAP is automatically disabled with RDP Level 2.

**IWDG (Independent Watchdog):** IWDG is a free-running down-counter. Once running, it cannot be stopped. It must be refreshed periodically before it causes a reset. This mechanism allows the control of SBSFU execution duration.

1. Not possible on the STM32H7 series. Refer to *Appendix I* for more details.

UM2262 Rev 11 27/109

# Protections against inner attacks

Inner attacks refer to attacks triggered by code running in the STM32. Attacks may be due to either malicious firmware exploiting bugs or security breaches, or unwanted operations.

In the SBSFU application example, PCROP, WRP, and MPU protections preserve the product from inner attacks:

- **PCROP** (proprietary code readout protection): a section of flash memory is defined as execute-only through PCROP protection. It is not possible to access this section in reading or writing. Being an execute-only area, a key is protected with PCROP only if it is 'embedded' in a piece of code: executing this code moves the key to a specific pointer in RAM. Placed behind the firewall, its execution is impossible from the outside.

- WRP (write protection): write protection is used to protect trusted code from external attacks or even internal modifications such as unwanted writings/erase operations on critical code/data.

- **MPU** (memory protection unit): the protected environment managing all critical data and operations (secure engine) is isolated from the other software components by leveraging the Memory Protection Unit (MPU). The secure engine code and data can be accessed only through a privileged level of software execution. Therefore, software running at a non-privileged level cannot call secure engine services or access critical data. This strict access control to secure engine services and resources is implemented by defining specific MPU regions described in *Table 5*.

Table 5. MPU regions in the STM32G0 series, STM32G4 series, and STM32H7 series

| Region content                   | Privileged permission          | Unprivileged permission |

|----------------------------------|--------------------------------|-------------------------|

| Secure engine code and constants | Read-only (execution allowed)  | No access               |

| Secure engine stack and VDATA    | Read/write<br>(not executable) | No access               |

Besides, the MPU also ensures that only authorized code is granted execution permission when the secure boot and secure firmware update processes are running. Before launching the user application, the MPU protection is disabled but the secure user memory protection is activated.

• Secure user memory: when the secure user memory protection is activated, any access to the securable memory area (fetch, read, programming, erase) is rejected, generating a bus error. All the code and secrets located inside the secure user memory (a protected environment) are fully hidden. Secure engine stack and data are cleared when launching the user application as not under secure user memory protection.

The code executed to activate the secure user memory must be located outside the protected memory. In SBSFU, this code is located in RAM.

Figure 9 illustrates the closure of secure user memory when starting the user application.

Figure 9. STM32G0, STM32G4, and STM32H7 protection overview during user application execution

UM2262 Rev 11 29/109

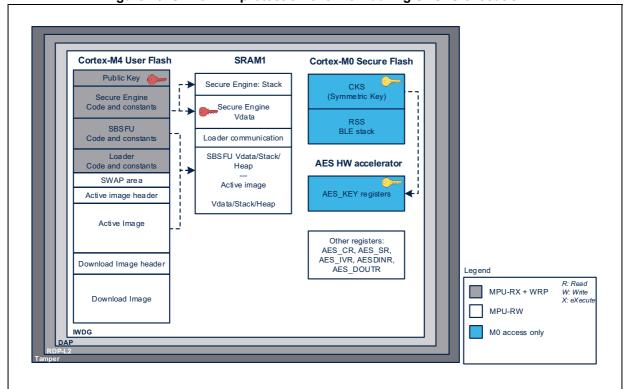

# 5.4 STM32WB series

*Figure 10* illustrates how the system, the code, and the data are protected in the X-CUBE-SBSFU application example for the STM32WB series.

Figure 10. STM32WB protection overview during SBSFU execution

# Protections against outer attacks

Outer attacks refer to attacks triggered by external tools such as debuggers or probes, trying to access the device. In the SBSFU application example, RDP, tamper, DAP, and IWDG protections are used to protect the product against outer attacks:

- **RDP** (Read Protection): Read Protection Level 2 is mandatory to achieve the highest level of protection and to implement a Root of Trust:

- External access via the JTAG hardware interface to RAM and flash memory is forbidden. This prevents attacks aiming to change SBSFU code and therefore mining the Root of Trust.

- Option bytes cannot be changed. This means that other protections such as WRP and PCROP cannot be changed anymore.

Caution - RDP level 1 is not proposed for the following reasons:

- 1. Secure boot/Root of Trust (single entry point and immutable code) cannot be ensured, because Option bytes (WRP) can be modified in RDP L1.

- 2. Device internal flash memory can be fully reprogrammed (after flash memory mass erase via RDP L0 regression) with a new firmware without any security.

- 3. Secrets in RAM protected by the firewall can be accessed by attaching the debugger via the JTAG hardware interface on a system reset.

In case JTAG hardware interface access is not possible at customer product, and in case the customer uses a trusted and reliable user application code, then the above highlighted risks are not valid.

- **Tamper**: the anti-tamper protection is used to detect physical tampering actions on the device and to take related countermeasures. In the case of tampering detection, the SBSFU application example forces a reboot.

- DAP (Debug Access Port): the DAP protection consists of de-activating the DAP (Debug Access Port). Once de-activated, JTAG pins are no longer connected to the STM32 internal bus. DAP is automatically disabled with RDP Level 2.

- **IWDG** (Independent Watchdog): IWDG is a free-running down-counter. Once running, it cannot be stopped. It must be refreshed periodically before it causes a reset. This mechanism allows the control of SBSFU execution duration.

### **Protections against inner attacks**

Inner attacks refer to attacks triggered by code running in the STM32. Attacks may be due to either malicious firmware exploiting bugs or security breaches, or unwanted operations. In the SBSFU application example, CKS, WRP, and MPU protections preserve the product from inner attacks:

- **CKS** (customer key storage): the SBSFU symmetric key is isolated in the Cortex<sup>®</sup>-M0+ core secure flash memory and therefore cannot be accessed from the Cortex<sup>®</sup>-M4 core. Before each AES cryptographic decryption/encryption, the Cortex<sup>®</sup>-M4 core requests the Cortex<sup>®</sup>-M0+ code to load the key into the AES hardware accelerator key register (only accessible from the Cortex<sup>®</sup>-M0+ core).

- **WRP** (write protection): write protection is used to protect trusted code from external attacks or even internal modifications such as unwanted writings/erase operations on critical code/data. Moreover, WRP allows protecting the SBSFU public key.

- MPU (memory protection unit): the MPU is used to make an embedded system more

robust by splitting the memory map for flash memory and SRAMs into regions having

their access rights. In the SBSFU application example, the MPU is configured to

ensure that no other code is executed from any memory during SBSFU code

UM2262 Rev 11 31/109

execution. When leaving the SBSFU application, the MPU configuration is updated to authorize also the execution of the user application code.

# 5.5 STM32L4+ series combined with STSAFE-A110

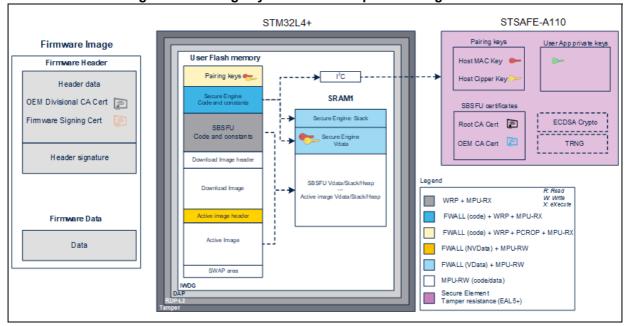

*Figure 11* illustrates how the system, the code, and the data are protected in the X-CUBE-SBSFU application example featuring the STM32L4+ series combined with STSAFE-A110.

STM32L4+ STSAFE-A110 Pairing keys User App private keys User Flash memory Host MAC Key Pairing keys Host Cipper Key Secure Engine SRAM1 Code and constants SBS FU certificates Secure Engine: Stack ECDSA Crypto Root CA Cert SBSFU -------Code and constants Secure Engine OEM CA Cert TRNG Download Image header SBSFU Vdata/Stack/Heap Legend Download Image Active image Vdata/Stack/Heap R: Read W Write WRP + MPU-RX Active image header FWALL (code) + WRP + MPU-RX FWALL (code) + WRP + PCROP + MPU-RX Active Image FWALL (NVData) + MPU-RW FWALL (VData) + MPU-RW SWAP area MPU-RW (code/data) IWDG Secure Element Tamper resistance (EAL5+)

Figure 11. STM32L4+ with STSAFE-A110 protection overview during SBSFU execution

# STM32 microcontroller protections against outer attacks

Outer attacks refer to attacks triggered by external tools such as debuggers or probes, trying to access the device. In the SBSFU application example, RDP, tamper, DAP, and IWDG protections are used to protect the product against outer attacks:

- **RDP** (Read Protection): Read Protection Level 2 is mandatory to achieve the highest level of protection and to implement a Root of Trust:

- External access via the JTAG hardware interface to RAM and flash memory is forbidden. This prevents attacks aiming to change SBSFU code and therefore mining the Root of Trust.

- Option bytes cannot be changed. This means that other protections such as WRP and PCROP cannot be changed anymore.

**Caution** - RDP level 1 is not proposed for the following reasons:

- 1. Secure boot/Root of Trust (single entry point and immutable code) cannot be ensured, because Option bytes (WRP) can be modified in RDP L1.

- 2. Device internal flash memory can be fully reprogrammed (after flash memory mass erase via RDP L0 regression) with a new firmware without any security.

- 3. Secrets in RAM protected by the firewall can be accessed by attaching the debugger via the JTAG hardware interface on a system reset.

In case JTAG hardware interface access is not possible at customer product, and in case the customer uses a trusted and reliable user application code, then the above highlighted risks are not valid.

- **Tamper**: the anti-tamper protection is used to detect physical tampering actions on the device and to take related countermeasures. In the case of tampering detection, the SBSFU application example forces a reboot.

- DAP (Debug Access Port): the DAP protection consists of de-activating the DAP (Debug Access Port). Once de-activated, JTAG pins are no longer connected to the STM32 internal bus. DAP is automatically disabled with RDP Level 2.

- **IWDG** (Independent Watchdog): IWDG is a free-running down-counter. Once running, it cannot be stopped. It must be refreshed periodically before it causes a reset. This mechanism allows the control of SBSFU execution duration.

### STM32 microcontroller protections against inner attacks

Inner attacks refer to attacks triggered by code running in the STM32. Attacks may be due to either malicious firmware exploiting bugs or security breaches, or unwanted operations. In the SBSFU application example, WRP, firewall, PCROP, and MPU protections preserve the product from inner attacks:

• **FWALL** (firewall): the firewall is configured to protect the code, volatile and non-volatile data. Protected code is accessible through a single entry point (the call gate mechanism is described in *Appendix A*). Any attempt to jump and try to execute any of the functions included in the code section without passing through the entry point generates a system reset.

UM2262 Rev 11 33/109

- PCROP (proprietary code readout protection): a section of flash memory is defined as execute-only through PCROP protection. It is not possible to access this section in reading or writing. Being an execute-only area, a key is protected with PCROP only if it is 'embedded' in a piece of code: executing this code moves the key to a specific pointer in RAM. Placed behind the firewall, its execution is impossible from the outside.

- WRP (write protection): write protection is used to protect trusted code from external attacks or even internal modifications such as unwanted writings/erase operations on critical code/data.

- MPU (memory protection unit): the MPU is used to make an embedded system more robust by splitting the memory map for flash memory and SRAMs into regions having their access rights. In the SBSFU application example, MPU is configured to ensure that no other code is executed from any memories during SBSFU code execution. When leaving the SBSFU application, the MPU configuration is updated to authorize also the execution of the user application code.

### **STSAFE-A** secure element protections

The STSAFE-A110 is a highly secure solution with a secure operating system running on the latest generation of secure microcontrollers:

- Security features: The chip is CC EAL5+ AVA VAN5 Common Criteria certified and provides the following protections.

- Active shield

- Monitoring of environmental parameters

- Protection mechanism against faults

- Unique serial number on each die

- Protection against side-channel attacks

- Secure operating system: STSAFE-A110 runs a secure operating system offering protection against logical and physical attacks.

- Secure channel and device binding: STSAFE-A110 allows a secure channel to be set up with the STM32 to prevent eavesdropping of sensitive information on the I2C line and to ensure pairing of a specific STM32 with a specific STSAFE-A110 (to prevent cloning).

The secure channel is based on symmetric cryptography: two AES 128-bit keys (the socalled host pairing keys) are used to implement services such as command authorization. command data encryption, response data encryption, and response authentication.

# 6 Package description

This section details the X-CUBE-SBSFU package content and the way to use it.

# 6.1 General description

X-CUBE-SBSFU is a software package for STM32 microcontrollers.

It provides a complete solution to build secure boot and secure firmware update applications:

- Support of symmetric and asymmetric cryptography approaches with the AES-GCM, AES-CBC, and ECDSA algorithms for decryption, verification, or both with the use of X-CUBE-CRYPTOLIB

- Support of X509 certificate chain verification of firmware image and firmware updates<sup>(a)</sup>

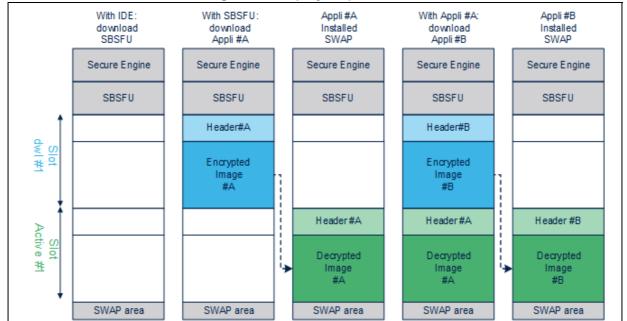

- Two modes of operation:

- The dual-slot configuration with one active slot and one download slot, which enables safe image programming, with resume capability in the case of an interruption of the installation procedure

- The single-slot configuration with one active slot, which maximizes the user application size

- Integration of security peripherals and mechanisms to implement an SBSFU Root of Trust. RDP, WRP, PCROP, firewall, MPU, secure user memory, tamper, and IWDG are combined to achieve the highest security level<sup>(b)</sup>.

- Use of a secure engine (SE) module as part of the middleware to provide a protected environment managing all critical data and operations such as secure key storage, cryptographic operations, and others

- Integration of secure key management services (KMS) offering symmetric and asymmetric cryptographic services via the PKCS #11 APIs and offering secure key storage, update services

- Integration of the STSAFE-A110 secure element to provide the system with a tamper-resistant Root of Trust (CC EAL5+ AVA\_VAN5 Common Criteria certified), to

b. The availability of security IPs depends on the STM32 series.

UM2262 Rev 11 35/109

a. Specific to the STSAFE-A110.

Package description UM2262

offload the host MCU of ECDSA cryptographic operations. More information about STSAFE-A110 can be found at www.st.com/stsafe-a110.

- Availability of the user application example source code.

- The firmware image configuration can be extended up to three images for a complex system with multiple firmware (such as protocol stack, middleware, and user application.)

- User application can validate the installation of the new active image(s) in case of successful validation of new image through "self-test".

- Management of interruption during code execution inside the firewall is now supported for applications requiring low latency on interruption handling.

- Availability of the firmware image preparation tool provided both as executable and source code.

X-CUBE-SBSFU is ported on the STM32F4 series, STM32F7 series, STM32G0 series, STM32G4 series, STM32H7 series, STM32L0 series, STM32L1 series, STM32L4 series, STM32L4+ series, and STM32WB series. X-CUBE-SBSFU is also ported on the STM32L4+ series combined with STSAFE-A110 mounted on the B-L4S5I-IOT01A board.

The package includes sample applications that the developer can use to start experimenting with the code.

The package is provided as a zip archive containing the source code.

The following integrated development environments are supported:

- IAR Systems<sup>®</sup> IAR Embedded Workbench<sup>®(a)</sup>

- Keil<sup>®</sup> MDK-ARM<sup>(a)</sup>

- STMicroelectronics STM32CubeIDE

Note:

The KMS feature is available on the STM32L4 series and STM32L4+ series with an example provided on the B-L475E-IOT01A and B-L4S5I-IOT01A boards. The STSAFE-A110 feature is available on the STM32L4+ series with an example provided on the B-L4S5I-IOT01A board.

a. On Windows  $^{\circledR}$  only.

UM2262 Package description

# 6.2 Architecture

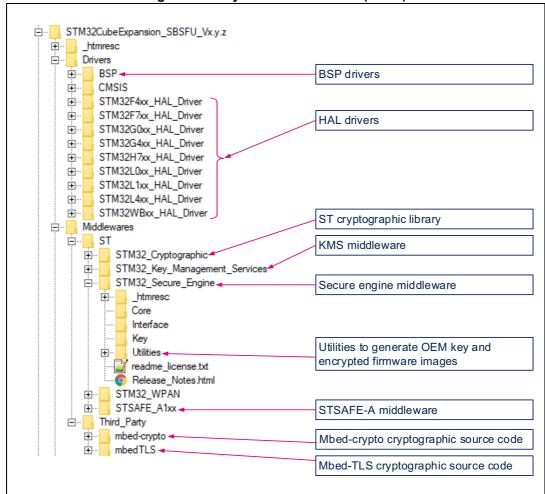

This section describes the software components of the X-CUBE-SBSFU package illustrated in *Figure 12*.

SBSFU sample application PC Secure Boot Secure firmware User application Safe firmware software **Root of Trust** loader programming Application level Secure Engine Cryptography Key management services **STSAFE** Utilities Middleware level Board support package (BSP) Hardware abstraction layer (HAL) **CMSIS Drivers**

Figure 12. Software architecture overview

#### 6.2.1 STM32CubeHAL

The HAL driver layer provides a generic multi-instance simple set of APIs (application programming interfaces) to interact with the upper layers (application, libraries and stacks). It is composed of generic and extension APIs. It is directly built around a generic architecture and allows the layers that are built upon, such as the middleware layer, implementing their functionalities without dependencies on the specific hardware configuration for a given microcontroller unit (MCU).

This structure improves the library code re-usability and guarantees an easy portability onto other devices.

# 6.2.2 Board support package (BSP)

The software package needs to support the peripherals on the STM32 boards apart from the MCU. This software is included in the board support package (BSP). This is a limited set of APIs which provides a programming interface for certain board-specific peripherals such as the LED and the User button.

57

UM2262 Rev 11 37/109

Package description UM2262

# 6.2.3 Cryptographic Library

Three different cryptographic middleware are supported:

X-CUBE-CRYPTOLIB supports symmetric and asymmetric key approaches (AES-GCM, AES-CBC, ECDSA) as well as hash computation (SHA256) for decryption and verification. Software cryptographic functions are used to avoid storing secret keys in hardware cryptography peripheral registers that are not protected.

- mbedTLS: cryptographic services delivered as open-source code. Similarly as for X-CUBE-CRYPTOLIB, the symmetric and asymmetric key approaches (AES-GCM, AES-CBC, ECDSA), as well as hash computation (SHA256) for decryption and verification, are supported. Examples are provided for the 32L496GDISCOVERY, B-L475E-IOT01A, STM32F413HDISCOVERY, STM32F769IDISCOVERY, NUCLEO-WB55RG<sup>(a)</sup>, and NUCLEO-H753ZI boards under the folder 2 images OSC.

- mbed-crypto: cryptographic services delivered as open-source code. This middleware provides a PSA cryptography API implementation. Examples are provided for B-L4S5I-IOT01A board, under the folders 2 Images KMS and 2 Images STSAFE.

# 6.2.4 Secure engine (SE) middleware