## Discovery kits with STM32U5x9NJ MCUs

#### Introduction

The STM32U5x9J-DKx Discovery kits (order codes STM32U5A9J-DK and STM32U5G9J-DK1) are complete demonstration and development platforms for the STM32U5x9NJH6Q microcontrollers, featuring an Arm<sup>®</sup> Cortex<sup>®</sup>-M33 core with Arm<sup>®</sup> TrustZone<sup>®</sup>.

Leveraging the innovative ultra-low-power oriented features, 3 Mbytes of embedded SRAM for STM32U5G9NJH6Q or 2.5 Mbytes for STM32U5A9NJH6Q, 4 Mbytes of embedded flash memory, and rich graphics features, the STM32U5x9J-DKx Discovery kits enable users to easily prototype applications with state-of-the-art energy efficiency, as well as provide stunning and optimized graphics rendering with the support of specific graphic features associated with each microcontroller.

The full range of hardware features available on the board helps users to enhance their application development by an evaluation of all the peripherals such as a 2.47-inch RGB  $480 \times 480$  pixels TFT round LCD module with MIPI DSI<sup>®</sup> interface and capacitive touch panel, USB Type-C<sup>®</sup> HS, Octo-SPI flash memory device, Hexadeca-SPI PSRAM memory device, eMMC flash memory device, Time-of-Flight and gesture detection sensor, temperature sensor, 20-pin audio MEMS connector (for STM32U5G9J-DK1), and two 2.54 mm pitch double-row flexible expansion connectors for easy prototyping with daughterboards for specific applications (USART, LPUART, two SPIs, SAI, three I<sup>2</sup>C, SDMMC, ADCs, timers, and GPIOs).

The STM32U5x9J-DKx Discovery kits integrate an STLINK-V3E embedded in-circuit debugger and programmer for the STM32 microcontroller with a USB Virtual COM port bridge and comes with the STM32CubeU5 MCU Package, which provides an STM32 comprehensive software HAL library as well as various software examples.

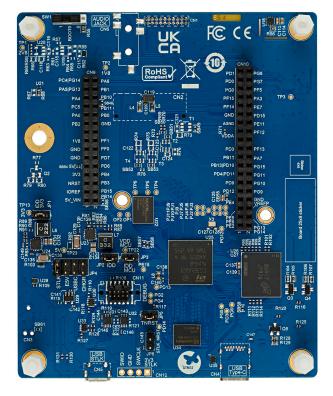

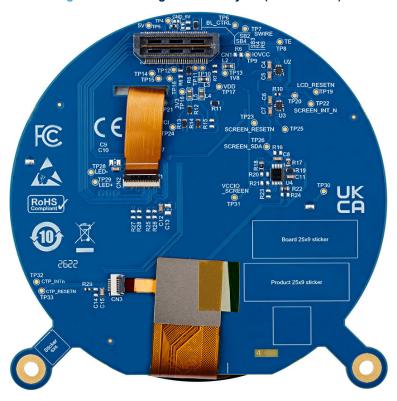

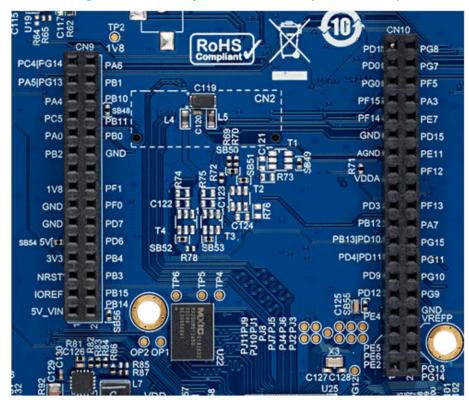

Figure 1. STM32U5G9J-DK1 top view

Figure 2. STM32U5G9J-DK1 bottom view

Pictures are not contractual.

## 1 Features

- Ultra-low-power STM32U5x9NJH6Q microcontroller based on the Arm<sup>®</sup> Cortex<sup>®</sup>-M33 core with Arm<sup>®</sup>

TrustZone<sup>®</sup>, featuring 4 Mbytes of flash memory, 3 Mbytes of SRAM for STM32U5G9NJH6Q or 2.5 Mbytes

for STM32U5A9NJH6Q, and SMPS in a TFBGA216 package

- 2.47" RGB 480 × 480 pixels TFT round LCD module with 16.7M color depth, with MIPI DSI<sup>®</sup> 2-data lane

interface and capacitive touch panel

- USB Type-C<sup>®</sup> with USB 2.0 HS interface, sink only

- Low-power system designed for VDD at 1.8 V only

- · MEMS sensors from STMicroelectronics

- Time-of-Flight and gesture-detection sensor

- Temperature sensor

- 512-Mbit Octo-SPI NOR flash memory

- 512-Mbit Hexadeca-SPI PSRAM

- 4-Gbyte eMMC flash memory

- Two user LEDs

- User and reset push-buttons

- Board connectors:

- USB ST-LINK Micro-B

- USB Type-C<sup>®</sup>

- Two double-row 2.54 mm pitch expansion connectors for additional peripherals prototyping

- Audio MEMS daughterboard expansion (for STM32U5G9J-DK1)

- MIPI10

- Tag-Connect<sup>™</sup> 10-pin footprint

- Flexible power-supply options: ST-LINK USB V<sub>BUS</sub>, USB connector, or external sources

- On-board STLINK-V3E debugger/programmer with USB re-enumeration capability: mass storage, Virtual COM port, and debug port

- Comprehensive free software libraries and examples available with the STM32CubeU5 MCU Package

- Support of a wide choice of Integrated Development Environments (IDEs) including IAR Embedded Workbench®, MDK-ARM, and STM32CubeIDE

Note: Arm and TrustZone are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

UM2967 - Rev 5 page 2/70

# 2 Ordering information

To order the STM32U5x9J-DKx Discovery kits, refer to Table 1. Additional information is available from the datasheet and reference manual of the target STM32.

Table 1. List of available products

| Order code     | Board reference                                    | Target STM32   | Differentiating feature                    |

|----------------|----------------------------------------------------|----------------|--------------------------------------------|

| STM32U5A9J-DK  |                                                    | STM32U5A9NJH6Q | -                                          |

| STM32U5G9J-DK1 | • MB1829 <sup>(1)</sup><br>• MB1835 <sup>(2)</sup> | STM32U5G9NJH6Q | Audio MEMS     daughterboard     expansion |

- 1. Main board

- 2. LCD daughterboard

## 2.1 Codification

The meaning of the codification is explained in Table 2.

**Table 2. Codification explanation**

| STM32XXYYZ-DKT | Description                                | Example: STM32U5G9J-DK1     |

|----------------|--------------------------------------------|-----------------------------|

| XX             | MCU series in STM32 32-bit Arm Cortex MCUs | STM32U5 series              |

| YY             | MCU product line in the series             | STM32U5F9/5G9 product line  |

| Z              | STM32 flash memory size:  J for 4 Mbytes   | 4 Mbytes                    |

| DK             | Discovery kit                              | Discovery kit               |

| Т              | Sequential number                          | First Discovery kit version |

UM2967 - Rev 5 page 3/70

## 3 Development environment

## 3.1 System requirements

- Multi-OS support: Windows® 10, Linux® 64-bit, or macOS®

- USB Type-A or USB Type-C<sup>®</sup> to USB Type-C<sup>®</sup> cable

- USB Type-A or USB Type-C<sup>®</sup> to Micro-B cable

Note: macOS<sup>®</sup> is a trademark of Apple Inc., registered in the U.S. and other countries and regions.

Linux<sup>®</sup> is a registered trademark of Linus Torvalds.

Windows is a trademark of the Microsoft group of companies.

## 3.2 Development toolchains

- IAR Systems® IAR Embedded Workbench®(1)

- Keil® MDK-ARM<sup>(1)</sup>

- STMicroelectronics STM32CubeIDE

- 1. On Windows® only.

## 3.3 Demonstration software

The demonstration software, included in the STM32Cube MCU Package corresponding to the on-board microcontroller, is preloaded in the STM32 flash memory for easy demonstration of the device peripherals in standalone mode. The latest versions of the demonstration source code and associated documentation can be downloaded from <a href="https://www.st.com">www.st.com</a>.

UM2967 - Rev 5 page 4/70

## 4 Laser consideration

The Time-of-Flight and gesture-detection sensor contains a laser emitter and the corresponding drive circuitry. The laser output is designed to remain within Class 1 laser safety limits under all reasonably foreseeable conditions including single faults in compliance with IEC 60825-1:2014 (third edition). The laser output remains within Class 1 limits as long as the STMicroelectronics recommended device settings are used and the operating conditions specified in the datasheets are respected. The laser output power must not be increased by any means and no optics are used to focus the laser beam. Figure 3 shows the warning label for Class 1 laser products.

Figure 3. Class 1 laser product label

UM2967 - Rev 5 page 5/70

# 5 Conventions

Table 3 provides the conventions used for the ON and OFF settings in the present document.

Table 3. ON/OFF convention

| Convention            | Definition                                    |

|-----------------------|-----------------------------------------------|

| Jumper JPx ON         | Jumper fitted                                 |

| Jumper JPx OFF        | Jumper not fitted                             |

| Jumper JPx [1-2]      | Jumper fitted between Pin 1 and Pin 2         |

| Solder bridge SBx ON  | SBx connections closed by 0 $\Omega$ resistor |

| Solder bridge SBx OFF | SBx connections left open                     |

| Resistor Rx ON        | Resistor soldered                             |

| Resistor Rx OFF       | Resistor not soldered                         |

| Capacitor Cx ON       | Capacitor soldered                            |

| Capacitor Cx OFF      | Capacitor not soldered                        |

UM2967 - Rev 5 page 6/70

## 6 Quick start

Before installing and using the product, accept the Evaluation Product License Agreement from the www.st.com/epla webpage.

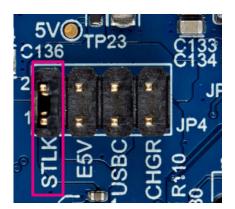

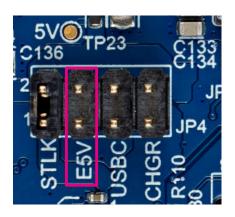

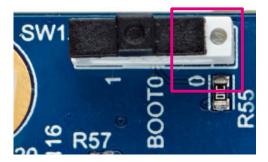

Follow the sequence below to configure the STM32U5x9J-DKx Discovery kit and launch the demonstration application (refer to Figure 5 and Figure 6 for component location):

- 1. For the correct identification of all the device interfaces from the host PC and before connecting the kit, install the STLINK-V3 USB driver as described in the technical note *Overview of ST-LINK derivatives* (TN1235).

- 2. Check that jumpers JP1, JP2, JP3, and JP5 are ON, that JP4 is set on STLK, and SW1 white side switch is set to 0.

- 3. Connect the STM32U5x9J-DKx Discovery kit to a PC with a USB cable (USB Type-A or USB Type-C<sup>®</sup> to Micro-B) through the STLINK-V3E USB connector (CN5) to power the kit.

- 4. The 5V green LED (LD2) and the COM LED (LD6) light up.

- 5. The LCD module displays a menu with icons, indicating the demonstration application software startup.

- 6. The demonstration application software and its user manual, as well as other software examples for exploring STM32U5x9J-DKx features are available on the STM32CubeU5 webpage.

- 7. Proceed to the STLINK-V3 firmware upgrade and configuration as described in TN1235.

- 8. Develop your application using the available examples.

UM2967 - Rev 5 page 7/70

## 7 Hardware layout and configuration

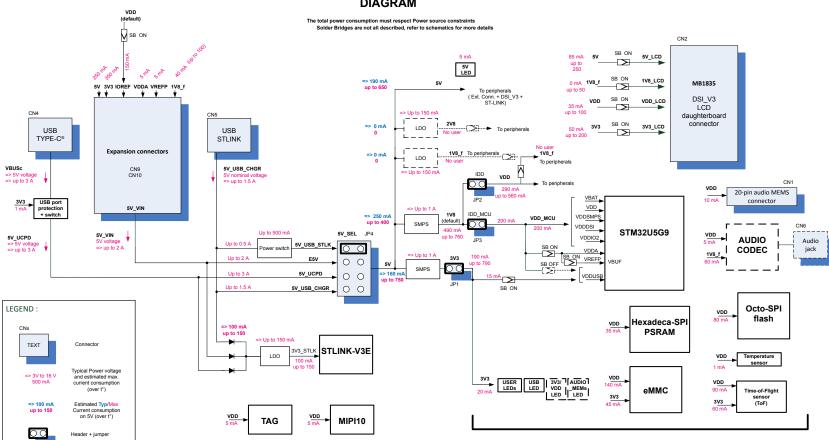

## 7.1 Hardware block diagram

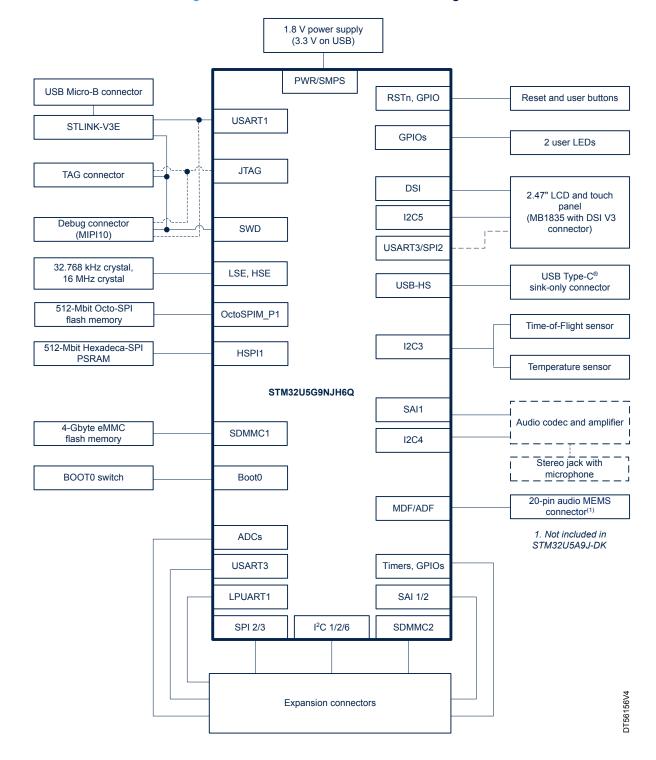

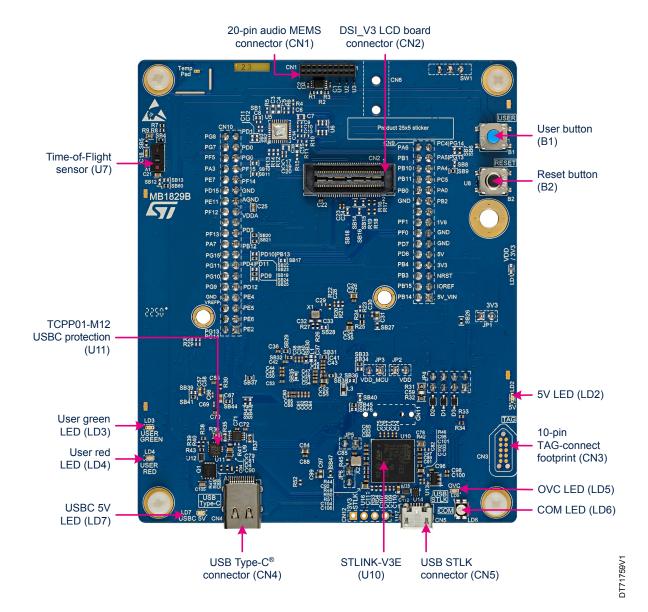

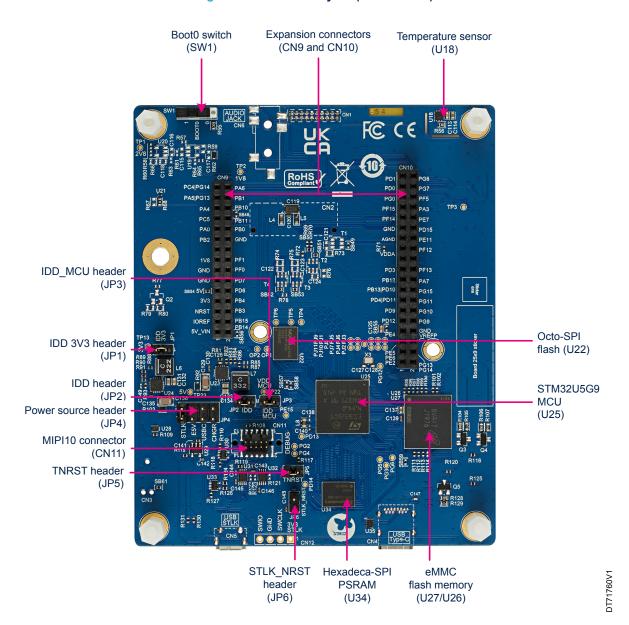

The STM32U5x9J-DKx Discovery kits are designed with the STM32U5x9NJH6Q microcontrollers, in a TFBGA216 package. The hardware block diagram in Figure 4 illustrates the connection between the microcontroller and the peripherals. Figure 5 and Figure 6 help to locate these features on the STM32U5G9J-DK1 Discovery main board.

Figure 4. STM32U5G9J-DK1 hardware block diagram

UM2967 - Rev 5 page 8/70

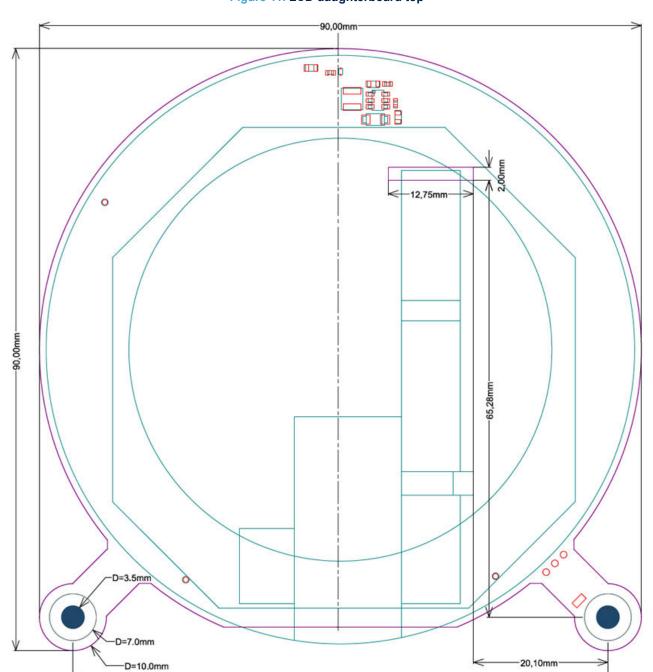

## 7.2 Main board layout

Figure 5. Main board layout (top view)

UM2967 - Rev 5 page 9/70

Figure 6. Main board layout (bottom view)

UM2967 - Rev 5 page 10/70

Figure 7. LCD daughterboard layout (top view)

Figure 8. LCD daughterboard layout (bottom view)

UM2967 - Rev 5 page 11/70

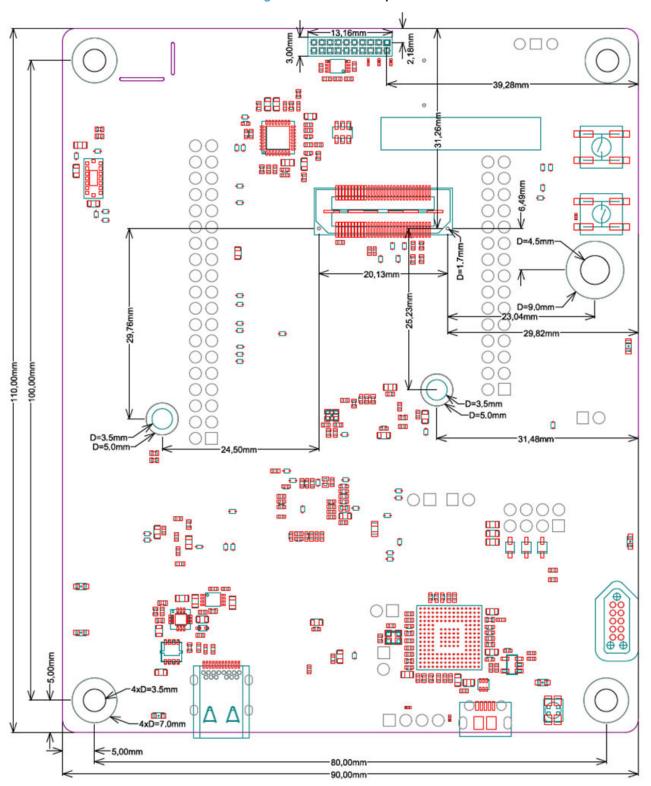

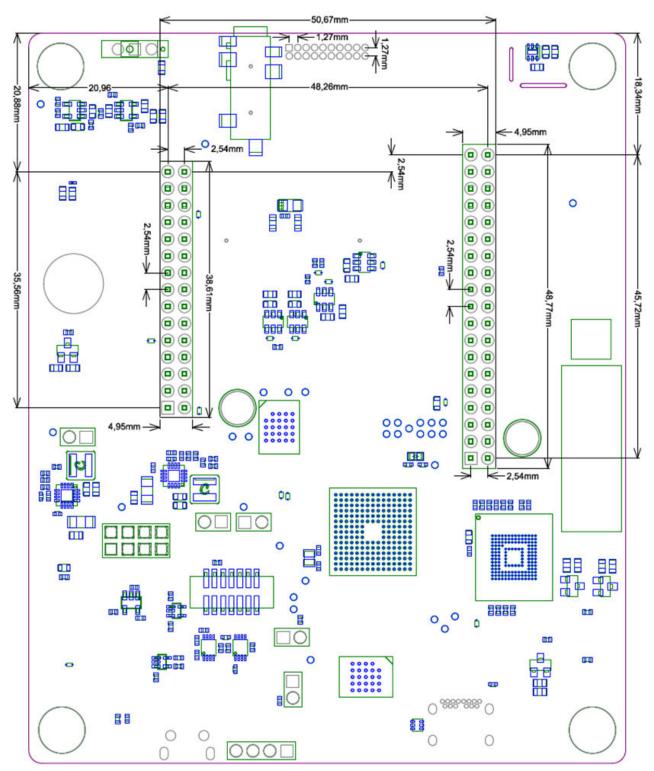

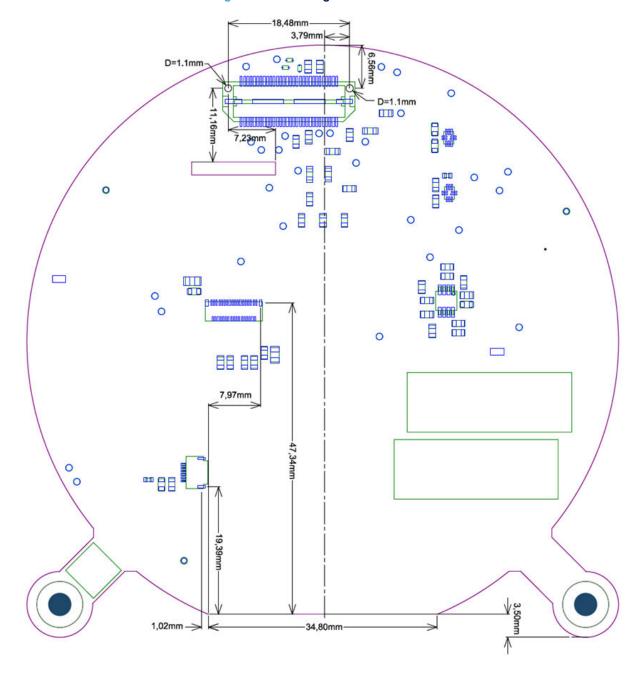

## 7.3 Mechanical drawings

All measurements are in millimeters.

Figure 9. Main board top

UM2967 - Rev 5 page 12/70

Figure 10. Main board bottom

UM2967 - Rev 5 page 13/70

80,00mm

Figure 11. LCD daughterboard top

UM2967 - Rev 5 page 14/70

Figure 12. LCD daughterboard bottom

UM2967 - Rev 5 page 15/70

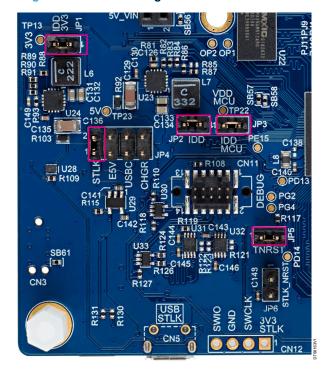

#### 7.4 Embedded STLINK-V3E

The chapter below gives some information about the implementation of the STLINK-V3E on this board.

Attention:

Before using STLINK-V3E, check your default configuration is the same as explained below. Then, ensure your complete system is well configured and up-to-date versus the STLINK-V3E function. For detailed information about the STLINK-V3E features such as drivers, firmware upgrade, USB interface selection, and LED management, refer to the technical note Overview of ST-LINK derivatives (TN1235).

Ensure that the following default configuration is set on the main board (refer to Figure 13):

- The JP1, JP2, and JP3 jumpers must be ON to power STM32U5x9NJ and peripherals.

- The JP4 jumper must be ON (STLK power source selected) and the relevant power input connected as described in Section 7.5.2.1: STLK (for compatibility with USB Host port legacy).

- The JP5 jumper must be ON to connect the output reset from STLINK-V3E to the TNRST reset input of STM32U5x9NJH6Q.

- The JP6 jumper must be OFF to set STLINK-V3E in Active mode. The debug connector (CN11) and the TAG connector (CN3) are not used by default.

Figure 13. Default configuration to use STLINK-V3E

Note:

STLINK-V3E can also be functional with other JP4 settings. Refer to Section 7.5.2: Power source selection for detailed configurations.

UM2967 - Rev 5 page 16/70

#### 7.4.1 Description

There are two different ways to program and debug the onboard STM32 MCU:

- Using the embedded STLINK-V3E, adapted to MCU 1.8V signaling (embedded level shifters)

- Using an external debug tool compatible with 1.8 V signaling, to be connected to the MIPI10 connector (CN11) or the Tag-Connect<sup>™</sup> footprint (CN3). Refer to Section 7.4.6.

Features supported in STLINK-V3E:

- 5 V/500 mA self-power supply by the USB Micro-B connector (CN5), with JP4 on STLK

- USB 2.0 high-speed-compatible interface

- Serial Wire Debug (SWD) and Serial Wire Viewer as option (SWV, on SWO output)

- Virtual COM port (VCP) on USB through USART1 interface

- COM status LED (LD6) and OVC overcurrent detection LED (LD5)

- Device firmware upgrade support (DFU)

Note: For a summary of all debug/program/trace or other interface capabilities, refer to Section 7.4.5.

Note: Always ensure your STLINK-V3E is up-to-date referring to the technical note Overview of ST-LINK derivatives (TN1235).

#### 7.4.2 STLINK-V3E active mode

The STM32U5x9J-DKx products can be powered from the ST-LINK USB connector (CN5), but the host PC might provide only 100 mA to the ST-LINK circuit until the end of the USB enumeration. The 3V3\_STLK LDO (U13) supplies 3.3 V to STLINK-V3E with up to 5.5 V recommended input voltage respecting these 100 mA consumption during enumeration. Then, STLINK-V3E requires a 500 mA current from the host PC.

If the host PC can provide the required power, the enumeration finishes, and then, the 5V\_STLK power switch (U29) is turned ON, after which the STM32U5x9J-DKx products can drive a 500 mA current. At this step, the PC can rely on the overcurrent protection of this power switch. In case of overcurrent detection, the FAULT pin is asserted and the OVC overcurrent detection red LED (LD5) turns ON.

If the host PC is not able to provide the requested current, the enumeration fails. Therefore, the power switch remains OFF and the 5 V power reference of the board is OFF. The 5V green LED (LD2) is turned OFF.

The green LED (LD2) is turned ON when the STM32U5x9J-DKx product is correctly powered by 5V. The COM LED (LD6) indicates the STLINK-V3E communication status with the host (refer to the technical note Overview of ST-LINK derivatives (TN1235).

Note: In case the board is powered by a USB wall charger on CN5 with JP4 on STLK, there is no USB enumeration, but the power switch is activated and the board is powered up, with an 800 mA current protection.

UM2967 - Rev 5 page 17/70

#### 7.4.3 STLINK-V3E deactivation (Reset mode)

It is simple to deactivate the STLINK-V3E function by moving the JP5 jumper on the JP6 header, to connect STLK\_NRST to GND (refer to Figure 14 and Table 4). Programming, debugging, and monitoring through STLINK are impossible in this Reset state, where all STLINK-V3E PIOs are in high impedance.

#### Attention:

The Reset mode is useful to connect an external probe to MIPI10/STDC14 debug (CN11) or TAG (CN3) connector for the embedded STM32U5x9NJ debug (refer to Section 7.4.5).

In this Reset mode, when JP6 is ON, 5V selection JP4 STLK is not functional, but any other 5V selection on JP4 might be used to power the board from other sources without overcurrent onboard protection.

Figure 14. STLK\_NRST default configuration (JP6)

Table 4. STLK\_NRST configuration (JP6)

| Reference          | Jumper <sup>(1)</sup> | Function               | Comment                                                                                     |

|--------------------|-----------------------|------------------------|---------------------------------------------------------------------------------------------|

|                    | OFF                   | STLINK-V3E active      | STLINK-V3E detects a USB ST-LINK plug on CN5.                                               |

| JP6 <sup>(2)</sup> | ON                    | STLINK-V3E Reset state | Set STLINK-V3E in Reset mode (all I/Os in high impedance). There is no power from JP4 STLK. |

- 1. The default setting is in bold.

- 2. In case JP6 is ON, JP5 must be OFF.

## 7.4.4 STLINK-V3E TNRST disconnection

It is possible to isolate physically the STLINK-V3E output reset (T\_NRST signal function) from the main STM32U5x9NJ NRST function by disconnecting JP5 (refer to Figure 15 and Table 5).

Figure 15. TNRST default configuration (JP5)

Table 5. TNRST configuration (JP5)

| Reference          | Jumper <sup>(1)</sup> | Function                                                          | Comment |

|--------------------|-----------------------|-------------------------------------------------------------------|---------|

| ON                 |                       | STLINK-V3E T_NRST output reset connected to NRST of STM32U5x9NJ.  |         |

| JP5 <sup>(2)</sup> | OFF S                 | STLINK-V3E T_NRST output reset isolated from NRST of STM32U5x9NJ. |         |

- 1. The default setting is in bold.

- 2. In case JP5 is ON, JP6 must be OFF.

UM2967 - Rev 5 page 18/70

## 7.4.5 SWD debug/program/trace and JTAG/USART

Attention:

Before using CN3 or CN11, also check the specific constraints detailed in Section 7.4.6: Using an external debug tool to program and debug the on-board STM32.

The SWD debug/program/trace interface is accessible through the STLINK-V3E USB connector (CN5) by default, and the debug connector (CN11) or Tag-Connect<sup>™</sup> 10-pin footprint (CN3) are other options.

By default, access to SWO trace and JTAG is not functional and needs hardware modification.

The USART1 bootloader is accessible through STLINK-V3E by default.

To debug/program/trace, first, choose any of the exclusive following connectors and consider Table 6 to summarize STM32U5x9J-DKx capabilities:

Table 6. Debug/program/trace and JTAG/USART interface overview

| Connector                               | SWD debug/program | SWO trace <sup>(1)</sup> | JTAG <sup>(1)(2)(3)</sup> | USART1 bootloader |

|-----------------------------------------|-------------------|--------------------------|---------------------------|-------------------|

| USB STLINK-V3E CN5                      | Yes               | Yes, as an option        | No                        | Yes               |

| MIPI10 debug CN11 (STDC14 as an option) | Yes               | Yes, as an option        | Yes, as an option         | No <sup>(4)</sup> |

| TAG footprint CN3                       | Yes               | Yes, as an option        | Yes, as an option         | No                |

- 1. SWO/JTDO (PB3) can be used by moving SB33 on SB34 (exclusive with SDMMC2.D2).

- 2. NJTRST(PB4) is not connected to connectors but is accessible on CN9 (exclusive with SDMMC2.D3).

- 3. JTDI is connected by default, and cannot be used when UCPD.CC1 is used.

- 4. The USART1 bootloader interface is only accessible on the CN11 footprint (pins 13 and 14): USART1\_RX (PA10) and USART1\_TX (PA9).

Refer to Section 9.2 and Section 9.3 for CN11 and CN3 pin assignment details.

When using STLINK-V3E USB CN5 by default, refer to the software tool description for any specific constraints or capabilities.

Here are the interface signals between STM32U5x9NJ MCU and STLINK-V3E or the external probes:

Table 7. Default STM32U5x9NJ interface to STLINK-V3E and external debug tools

| STM32U5x9NJ PIO | Configuration                                    |

|-----------------|--------------------------------------------------|

| PA14            | SWCLK (T.SWCLK/T.JTCK)                           |

| PA13            | SWDIO (T.SWDIO/T.JTMS)                           |

| PB3             | SWO (T.SWO/T.JTDO)                               |

| PA15            | JTDI (T.JTDI) -not available for STLINK-V3E      |

| PB4             | NJTRST -not used                                 |

| NRST            | NRST (NRST)                                      |

| PA9             | VCP_TX (T.VCP_TX)-USART1_TX -only for STLINK-V3E |

| PA10            | VCP_RX (T.VCP_RX)-USART1_RX -only for STLINK-V3E |

| PH0             | MCO (T.MCO) -not used                            |

For details about relevant connector pin assignments, refer to Section 9.

UM2967 - Rev 5 page 19/70

Note:

#### 7.4.6 Using an external debug tool to program and debug the on-board STM32

Warning: Take care MIPI10 debug and TAG connectors are 1.8 V signaling interface by default. Use

only adequate/compatible tools to connect.

**Warning:** Some TAG connector tools connect a 5 V external power on pin 5 of the CN3 footprint,

which can create a short circuit. Pay attention to using the right tool combination of adapter/cable not to bring 5 V on pin 5, or simply remove the dedicated solder bridge from the PCB,

or find a way to disconnect the 5 V signal from your tool.

Warning: The CN11 and CN3 connectors are exclusives, use only one at the same time to avoid

conflict.

Before using any external debug tool, read carefully its user manual, to check if specific constraints apply.

The following page details the list of things to consider and configure when using the CN11 or the CN3 connector.

- 1. Put the embedded STLINK-V3E in Reset mode: Move the TRNST jumper (JP5) on the STLK\_NRST header (JP6), no data transfer is possible from USB ST-LINK. This allows the use of either CN11 or CN3 without the risk of signal conflict with STLINK-V3E on any interface.

- 2. Because STLINK-V3E is in Reset mode, you have also to remove the jumper (JP4) from the STLK position and put it in any other position according to your required configuration (refer to Section 7.5.2: Power source selection and Section 7.5.1: Power diagram).

- 3. If you use the SWD interface in 2-wire mode (without SWO), there is no need for further modifications.

- 4. If you use the SWD interface in 3-wire mode (with SWO), or the JTAG interface (with JTDO), disconnect SB33 and connect it to SB34.

Note: JTDI can be used by default as UCPD.CC1 is not used.

CN11 and CN3 connectors provide access to the NRST pin of the STM32U5x9NJH6Q microcontroller, but do not offer access to the NJRST function. NJRST function is only accessible on PB4 on CN9 pin 8, and it is exclusive to SDMMC2\_D3.

- 5. If you want to use the USART1 bootloader interface from CN11: Connect your tool to RX/TX on pin 13/14 of CN11 (it must be 1.8V compatible). (Or, if STDC14 is used as CN11, just connect the MIPI14 cable to your 1.8V compatible tool).

- 6. Power up the board: Connect your power source to the board.

- 7. Use any of the debug (CN11) or TAG (CN3) connectors for the STM32U5x9NJH6Q connection: Use a MIPI10 or MIPI14 cable to connect to the debug connector (CN11) or use a TAG connect cable to connect to the TAG footprint (CN3). Reminder: The board is 1.8 V by default, so only use adequate/compatible tools to connect.

UM2967 - Rev 5 page 20/70

## 7.5 Power supply

#### 7.5.1 Power diagram

Warning: This Discovery kit is a low-power system designed for VDD and VDD\_MCU at 1.8 V only.

Attention: Do not remove JP3 when the board is powered up, or do not start the board with JP3 OFF, for this might have

an impact on the long-term reliability of the MCU in specific temperature conditions. Use preferably JP4 OFF,

Reset button, or power source removal to restart the board.

Attention: Do not remove the JP2 header when the board is powered up, for it might have an impact on the long-term

reliability of the peripherals.

Attention: This Discovery kit uses a power scheme that might be different from standard application notes. Refer to the

relevant application notes for your design.

Figure 16 describes the power architecture and the maximum voltage and current limits, under which functions can be safely used on the STM32U5x9J-DKx product. In any case, ensure the total power budget of the application always conforms to the selected 5 V power source mode, if not, malfunction can occur. For detailed configuration, refer to the relevant function description and technical application notes.

Note: When using expansion connectors, it might be necessary to use one of the three following power sources, depending on the application power budget:

• 5V VIN, up to 2 A: Expansion connectors power the STM32U5x9J-DKx application

- 5V\_USB\_CHGR, up to 1.5 A: Power the board from a 1.5 A compatible USB Host port or USB charger

- 5V\_UCPD, up to 3.0 A: Power the board from a 1.5 or 3.0 A compatible USB Host port or USB charger and check the 5 V power supply voltage tolerance fits with the application.

UM2967 - Rev 5 page 21/70

## Figure 16. Power diagram

# POWER DIAGRAM

Main peripherals have also solder bridges to allow individual current consumption measurement

$\square$

20 pin Audio Connector SB (Solder Bridge)

Dots (not populated

included on the expansion add-on board)

#### 7.5.2 Power source selection

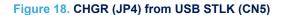

The STM32U5x9J-DKx Discovery kits are designed to be powered by a 5V DC power supply. It is possible to configure the Discovery main board with JP4 header to use any of the four sources described in Table 8 for the 5V DC power supply.

Reference Jumper (1) **Function** Comment 5 V (+10%/-5%) 5 V is supplied by USB STLK **STLK** 800 mA typ. embedded overcurrent protection (CN5). Up to 500 mA capable 5 V (+10%/-5%) 5 V is supplied by USB STLK **CHGR** No embedded current protection (CN5). Up to 1.5 A current 5 V (+10%/-5% at current < 500 mA) JP4 5 V (+/-10% at current < 1.5 A) 5 V is supplied by the USB Type-**USBC** No embedded current protection C® connector (CN4). Up to 3 A (check USB Type-C® VBUS constraints in that case) 5 V is supplied by 5V\_VIN and 5 V (+/-5%), up to 2 A E5V GND pins on the expansion No embedded current protection (can be

Table 8. 5V selection configuration jumper (JP4)

In all the above four power source configurations, the LED 5V (LD2) must be lit when the Discovery main board is correctly powered by the 5V supply.

The recommended maximum voltage applied on 5 V in continuous mode must be 5.5 V in standard use cases.

connector (CN9).

## 7.5.2.1 STLK (for compatibility with USB Host port legacy)

Figure 17 shows the selection of 5V from STLK on JP4, with a power source connected to USB ST-LINK (CN5). It is the default setting.

The USB ST-LINK CN5 connector can power the STM32U5x9J-DKx Discovery kits, but the host PC only provides 100 mA to the ST-LINK circuit until the end of USB enumeration. At the end of the USB enumeration, the STM32U5x9J-DKx Discovery kits require a 500 mA current from the host PC.

If the USB enumeration succeeds, a power switch supplies the board with up to 500 mA current. This power switch also features a current limitation to protect the PC in case of overcurrent on the board.

Note:

In this mode, in case a wall charger powers the board, there is no USB enumeration but the overcurrent protection is still active on the powered board.

Figure 17. STLK (JP4) from USB STLK (CN5)

JT56167V1

UM2967 - Rev 5 page 23/70

<sup>1.</sup> The default setting is in bold.

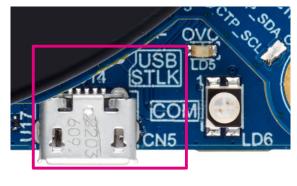

#### 7.5.2.2 CHGR

Figure 18 shows 5 V DC power from CHGR on JP4, with a power source connected to USB ST-LINK (CN5) and without any current protection. Thus, if the Discovery kit is powered by a USB PC port, debug features are available, but with the risk of damaging the PC. If a simple USB wall charger powers the Discovery kit, the debug/monitor features through STLINK-V3E are not available. In that configuration, the board can draw up to 1.5 A

maximum recommended current. Prefer using USB ports showing charging port marking in that case ( ) or using a USB Type-C<sup>®</sup> port with a USB Micro-B cable adapter, they enable up to 1.5 A current capability including data communication. CHGR position can be used when using MIPI10 or Tag-Connect<sup>™</sup> footprint.

200

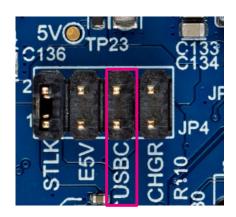

#### 7.5.2.3 USBC

Figure 19 shows the selection of 5 V DC power from USBC on JP4, with a power source connected to the USB Type- $C^{\$}$  connector (CN4). A USB Type- $C^{\$}$  port protection device with a power switch protects the STM32U5x9J-DKx Discovery kits from overvoltage on V<sub>BUS</sub>. USB Type- $C^{\$}$  V<sub>BUS</sub> nominal voltage must be in the 5 V +10%/-5% voltage range. The following constraints apply to USB Type- $C^{\$}$  host types to use:

- Low-power USB hosts are not supported, and permanent damage might occur (100 mA is not enough to start).

- USB 2.0 or USB 3.x host ports might be used if they can provide 500 mA without data communication.

Prefer using USB ports showing charging port marking in that case (\*) or using a USB Type-C® port, they can provide a higher current.

- Any other USB Type-C<sup>®</sup> source type can supply and start up the STM32U5x9J-DKx Discovery kits.

Figure 19. USBC (JP4) from USB Type-C® (CN4)

JT56170V1

UM2967 - Rev 5 page 24/70

#### 7.5.2.4 E5V

Figure 20 shows the selection of 5 V DC power from E5V on JP4, with a power source connected to external 5V\_VIN pin 1 (CN9) and GND pin 11 or 13 (CN9). Note that GND pins are also available on other pins of expansion connectors (CN9 and CN10). Refer to Section 9.7: Expansion connectors (CN9 and CN10) for details. In this case, a power supply unit or auxiliary equipment complying with standard EN 60950-1: 2006+A11/2009+A12/2011+A2/2013 or EN 62368-1 (2014+A11/2017) must power the STM32U5x9J-DKx Discovery kits and must be safety extra low voltage (SELV/ES1) with limited power capability (LPS/PS2).

Note:

There is no input current protection on MB1829 in this configuration. The recommended maximum current to be drawn from this E5V pin is 1.5 A, but 2 A must also be functional in practice (current protection might be placed on the expansion board).

Figure 20. E5V (JP4) from 5V IN/GND (CN9)

56171V1

#### 7.5.3 Microcontroller power

Warning: The STM32U5x9J-DKx Discovery kits are low-power systems designed for VDD and

VDD\_MCU at 1.8 V only.

Attention: Do not remove the JP3 header when the board is powered up, or do not start the board with JP3 OFF, this might

have an impact on the long-term reliability of the MCU in specific temperature conditions. Use preferably JP4

removal or the reset button or power source removal to restart the board.

**Attention:** Do not remove the JP2 header when the board is powered up, it might have an impact on the long-term

reliability of the peripherals.

**Attention:** The STM32U5x9J-DKx Discovery kits use a power scheme that might be different from standard application notes. Refer to the relevant application notes for your design.

By default, the STM32U5x9NJH6Q microcontroller power supply pins are connected to the VDD\_MCU power supply (1.8 V) and the 3V3 power supply (3.3 V). In case the user wants to test any other power supply configuration, a few solder bridges can be modified (refer to Section 10.2: Solder bridges).

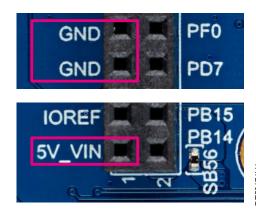

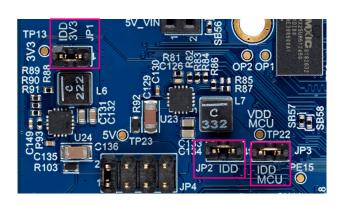

Two SMPS devices supply the 1.8 V and the 3.3 V power supplies of the board (going to the microcontroller and peripherals). Both SMPS outputs can supply a current of 1 A. The three headers (JP1, JP2, and JP3) allow measuring the currents going respectively to:

- IDD 3V3 (JP1): Current from 3V3\_SMPS to 3V3 power supply (VDDUSB of MCU and 3V3 of peripherals)

- IDD (JP2): Current from VDDMCU\_SMPS to VDD peripheral power supply (VDD is going only to peripherals)

- IDD MCU (JP3): Current from VDDMCU\_SMPS to VDD\_MCU (only to the MCU)

UM2967 - Rev 5 page 25/70

A jumper is fitted on each header, but an ammeter can replace any jumper for easy IDD measurement. Refer to Figure 21 and Table 9.

Figure 21. Jumpers default configuration (JP1, JP2, and JP3)

JT56172V1

Some solder bridges or serial resistors are available on boards to measure the current of some microcontroller and peripheral supply rails (refer to schematics for detailed possibilities).

Table 9. IDD configuration (JP1, JP2, and JP3)

| Reference | Jumper <sup>(1)</sup> | Function                             | Comment                                                                                      |

|-----------|-----------------------|--------------------------------------|----------------------------------------------------------------------------------------------|

|           | ON                    | 3V3 connected to SMPS output         | SMPS powers 3V3. No current measurement.                                                     |

| JP1       | OFF                   | 3V3 not connected to SMPS output     | 3V3 is not powered. Add an ammeter to power the MCU and peripherals and measure the current. |

| ON        |                       | VDD connected to SMPS output         | SMPS powers VDD for peripherals. No current measurement.                                     |

| JP2       | OFF                   | VDD not connected to SMPS output     | VDD is not powered. Add an ammeter to power the peripherals and measure the current.         |

| ON<br>JP3 |                       | VDD_MCU connected to SMPS output     | SMPS powers VDD_MCU. No current measurement.                                                 |

| JP3       | OFF                   | VDD_MCU not connected to SMPS output | VDD_MCU is not powered. Add an ammeter to power the MCU and measure the current.             |

<sup>1.</sup> The default setting is in bold.

#### 7.5.3.1 VDD MCU

By default, the SMPS output to VDD\_MCU is set to 1.8 V, to be compatible with the current design and peripherals.

VDDIO2 is a power rail dedicated to a few GPIOs (PG2 to PG15) and is independent of other GPIO power rails in the microcontroller. VDDIO2 is set at 1.8 V by default (connected to VDD\_MCU).

VBAT is connected to VDD\_MCU by default (for voltage measurement capability). Thus, VDD\_MCU can be monitored through the internal ADC channel on ADC1/2/4 (VBAT/4).

#### 7.5.3.2 Internal SMPS

An internal SMPS can supply power to a few IPs of the microcontroller. This internal SMPS is supplied by VDD\_MCU and enables very low power consumption figures in some power modes of the STM32U5x9NJH6Q microcontroller.

#### 7.5.3.3 Analog power supplies

VDDA is the external analog power supply for ADC converters, DAC converters, voltage reference buffers, operational amplifiers, and comparators. It is connected to VDD\_MCU by default, through a ferrite bead.

UM2967 - Rev 5 page 26/70

VSSA/VREF- are connected to general ground VSS in one point of the design, thanks to a solder bridge. Other options are available.

VREF+ is the STM32U5x9NJH6Q input reference voltage for ADCs and DACs. It is connected to VDDA (default setting). Because VDDA is 1.8 V, VREFBUF cannot be used to power VREF+.

VDD USB is fixed at 3.3 V (supplied by an SMPS as explained below) to enable USB Type-C<sup>®</sup> use.

#### 7.5.4 Other peripheral power

The 1.8 V power rail supplies most of the board peripherals, through a dedicated jumper. The power rail is named VDD to differentiate with VDD MCU, dedicated to the microcontroller.

Some components/peripherals need a 3.3 V supply: MCU, expansion connectors, MB1835 LCD daughterboard, ToF sensor, eMMC, and LEDs. A dedicated SMPS provides the 3.3 V power rail, to be compatible with the current design and peripherals.

STLINK-V3E is powered by the 3V3\_STLK supply (LDO) from different 5 V sources. 5.5 V is the maximum recommended continuous input voltage, with at least 6.5 V peak AMR.

#### 7.6 Clock sources

The STM32U5x9J-DKx Discovery kits rely on an HSE oscillator (16 MHz crystal) and an LSE oscillator (32.768 kHz crystal) as clock references.

Using the HSE (instead of HSI) is mandatory to manage the DSI interface for the LCD module and the USB high-speed interface.

Any other internal clock reference might be used, but the clock tree might be adapted, and some features might be unavailable.

HSE oscillator crystal might be replaced by an external clock reference thanks to a solder bridge (MCO clock source coming from STLINK-V3E, but the clock tree might be adapted, and some features might be unavailable).

The LSE might be replaced by internal LSI use, but the clock tree might be adapted, and some features might be unavailable.

## 7.7 Boot options

#### Attention:

The white side of the SW1 switch indicates the Boot0 value setting (default position white switch at the right indicates BOOT0 = 0), refer to Figure 22.

By default, the boot procedure is managed through the PH3/BOOT0 pin of the MCU (center pin of the BOOT0 SW1 switch). The PH3/BOOT0 pin is connected either to a 10 k $\Omega$  pull-down (position 0) or to a 10 k $\Omega$  pull-up (position 1).

As the nSWBOOT0 option bit of STM32U5x9NJH6Q is set to 1, STM32U5x9J-DKx boot on internal flash memory, thanks to the SW1 switch default position (BOOT0 = 0).

SW1 is located on the bottom side of the board due to mechanical constraints. For specific purposes, the switch might be moved on top when CN1 is not used or replaced with a standard 3-pole header with a jumper.

Figure 22. BOOT0 default configuration, set on "0" (SW1)

561737/1

## 8 Board functions

This section explains all the functions, peripherals, and interfaces of the board. Refer to Features, Hardware layout and configuration, Figure 5, and Figure 6 STM32U5x9J-DKx top and bottom layout views.

## 8.1 2.47" round TFT DSI LCD daughterboard and DSI\_V3 connector

Caution:

- To peel off the LCD protective liner, do it slowly and carefully.

- If fixed patterns are displayed for a long time, a remnant image is likely to occur.

Note:

The microcontroller software system must invert DSI.CK\_N and DSI.CK\_P lines together to align with DSI\_V3 add-on boards. The DSI clock differential signals (\_N and \_P) are inverted on CN2 for layout reasons (refer to the DSI\_V3 connector standard pinning in Section 9.4: DSI\_V3 display board connector (CN2)).

Note:

The MB1835 display module board is designed to be compatible with a VDD setting of 1.8 V. Refer to the MB1835 schematics for more detailed constraints and options.

The LCD daughterboard is a 2.47" TFT round display,  $480 \times 480$  resolution, 16.7 million color depth with a MIPI DSI<sup>®</sup> 2-lane interface and a capacitive multi-touch panel. The STM32U5x9J-DKx Discovery kits integrate two DSI\_V3 compatible connectors (refer to Section 9.4: DSI\_V3 display board connector (CN2) for details) to interface the main and LCD boards. The height between both boards is 8 mm.

#### 8.1.1 Display management

The display uses a bidirectional two-data-lane DSI interface with one clock lane to interface with the MB1829 main board. The DSI interface is used to transfer display and command data to the display controller (including power-saving modes and synchronization to avoid the tearing effect).

The MB1829 main board provides four power supplies to the MB1835 LCD module board. These power supplies respect a power-up and power-down sequence following these timeframes:

- Power-up order (on 5V source activation): 5V LCD -> 1V8 LCD -> VDD LCD -> 3V3 LCD

- Power-down order (on 5V source removal): 5V LCD -> 3V3 LCD -> 1V8 LCD -> VDD LCD

Note:

By default, 1V8\_LCD is not used by MB1835. VDD\_LCD is used instead of 1V8\_LCD.

By default, the four power supplies are not switchable (power switches are replaced by 0  $\Omega$  solder bridges on the MB1829 main board).

The PIO list description of the DSI\_V3 connector and the default PIO configuration is defined in Section 8.1.3: 2.47" display and DSI\_V3 I/O interface. Many PIOs are not used by default. Refer to the I/O interface table.

Some PIOs are used by default to manage the LCD screen display (for dedicated touch-panel PIOs, refer to Section 8.1.2: Touch-panel management):

- DSI RESETn (PD5, active Low), to control the hardware RESET (common control with the touch panel)

- DSI BL CTRL (PI6, active high), to control the backlight (PIO, PWM, or SWIRE modes are possible)

Refer to the "Reset timing" and "Power on/off sequence and timing" sections of the display controller datasheet or touch-panel datasheet for further DSI RESETn management details.

DSI\_TE PIO (PF11) is not used by default. It might be used with other LCD module boards to manage the tearing effect function and synchronize host frame writing with the display controller.

#### 8.1.2 Touch-panel management

The capacitive touch panel is driven through the I2C5 microcontroller interface.

The DSI\_RESETn PIO (PD5, active low) controls the touch-panel controller hardware reset, at the same time as the display reset, but each reset signal is adapted to the peripheral (thanks to level shifters on MB1835). Pay attention to respect hardware reset timings depending on the used LCD module board.

The DSI\_TOUCH\_INT PIO (PE8, active low) manages the touchscreen interrupt function, to synchronize touch-panel activation with the host. It might also wake up the MCU from standby/shutdown modes.

UM2967 - Rev 5 page 28/70

## 8.1.3 2.47" display and DSI\_V3 I/O interface

Table 10. 2.47" display and DSI\_V3 I/O interface

| PIO     | Configuration                                                        |

|---------|----------------------------------------------------------------------|

| PI6     | BL_CTRL (DSI_BL_CTRL)                                                |

| PD5     | DSI_RESETn (DSI_RESETn)                                              |

| PE8     | TOUCH_INT (DSI_TOUCH_INT)                                            |

| DSI_CKN | CK_P (DSI.CK_P)-Polarity inversion on CN2 needs SW inversion on MCU. |

| DSI_CKP | CK_N (DSI.CK_N)-Polarity inversion on CN2 needs SW inversion on MCU. |

| DSI_D0N | D0_N (DSI.D0_N)                                                      |

| DSI_D0P | D0_P (DSI.D0_P)                                                      |

| DSI_D1N | D1_N (DSI.D1_N)                                                      |

| DSI_D1P | D1_P (DSI.D1_P)                                                      |

| PH4     | SDA (I2C5.SDA)                                                       |

| PH5     | SCL (I2C5.SCL)                                                       |

| PI5     | DSI_PWR_ON (DSI_PWR_ON) -not used                                    |

| PD8     | DSI_SPI_CS (DSI_SPI_USART_CS) –not used                              |

| PB13    | DSI_SPI_CK (DSI_SPI_CLK) –not used                                   |

| PD4     | DSI_SPI_MOSI (DSI_SPI_MOSI) -not used                                |

| PD11    | DSI_SPI_DCX (DSI_SPI_D/CX) –not used                                 |

| PB10    | USART3_TX (DSI_USART_TX) -not used                                   |

| PD10    | USART3_CK (DSI_USART_CK) -not used                                   |

| PI7     | SWIRE (DSI_SWIRE) -not used                                          |

| PF11    | TE (DSI_TE) –not used                                                |

## 8.1.4 Other DSI\_V3 compatible peripherals

The MB1829 main board allows supporting the following peripherals (non-exhaustive list): MB1835B-01, MB1232A-01. Some peripherals require hardware adaptation (DSI\_PWR\_ON is not active by default):

- MB1829B-01 with MB1835B-01 (2.47" round LCD) uses the default hardware configuration.

- MB1829B-01 with MB1232A-01 (HDMI board) needs hardware changes.

#### Updates with MB1232A-01 HDMI board:

- Remove R72 from the MB1829 (PIO is 5V-tolerant. Ok to tie it to 3V3 on the MB1232A side).

- Check that SB53 is fitted on the MB1829 (or put a shunt on SB53, in case SB53 is formerly removed for development purposes).

- Remove SB50 from MB1829 (to use pull-ups values on the MB1232A side).

- Add 2.2 kΩ resistors on R8 and R9 of MB1232A.

- Add a 2.7 kΩ resistor on R5 of MB1232A.

- Use the free spacer/screw and pillar to attach MB1232A onto MB1829 for strong mechanical plugging.

Note: MB1232A-01 is part of B-LCDAD-HDMI1 product version 1.

UM2967 - Rev 5 page 29/70

## 8.2 USB Type-C® (High Speed, sink only)

The STM32U5x9J-DKx products support a USB HS 2.0 interface on the USB Type-C<sup>®</sup> receptacle connector (CN4). The STM32U5x9J-DKx products offer compatibility with USB Type-C<sup>®</sup> rev 1.3 and are configured by default to behave as self-powered USB devices (when JP4 is on STLK).

#### Caution:

As required by the USB Type-C<sup>®</sup> specification, the STM32U5x9J-DKx products can interface on CN4 with USB2.0 and USB3.x legacy hosts supporting the USB high-speed data link but with these restrictions:

- JP4 must not be set on USBC (to respect the 100 mA maximum current before enumeration), or

- JP4 might be set on USBC, but the source must be 500 mA current capable (USB2.0 charging port for example)

#### Caution:

The total drawn current on CN4 USB Type- $C^{\circledR}$  V<sub>BUS</sub> must not exceed 3 A in any application. When using CN4 to power the STM32U5x9J-DKx, check that the USB V<sub>BUS</sub> voltage constraints are compatible with your 5 V-powered application on expansion connector CN9 (refer to the USB Type- $C^{\circledR}$  current load line).

Warning

The STM32U5x9J-DKx supports only a 5 V nominal voltage  $V_{BUS}$  on the USB Type-C<sup>®</sup> CN4 connector. Do not set  $V_{BUS}$  at higher or lower nominal voltages than 5 V. Using out-of-range nominal voltage  $V_{BUS}$  might result in board malfunction.

The USB Type-C<sup>®</sup> connector (CN4) can be used to demonstrate different features of STM32U5x9J-DKx.

- 1. Power the Discovery main board with a 5 V V<sub>BUS</sub> with a current of up to 3 A

- 2. High-speed data transfers with any USB Host

## 8.2.1 USB Type-C® sink only

Even if the Discovery kit is configured by default to behave as a self-powered USB device powered by USB ST-LINK connector CN5, the CN4 USB Type-C® connector can power the Discovery main board with a 5 V power coming from any USB Type-C® connected source (refer to Section 7.5.1: Power diagram) with the following constraints:

- A jumper must be set on the USBC position of the JP4 header (5 V source selection, to behave as a USB powered device).

- As per the USB Type-C<sup>®</sup> specification, V<sub>BUS</sub> is in the range of 5 V +10%/-5% and the default sourcing current is 500 mA minimum while the UCPD.DBn control pin (PE9) is an input (default state).

- Sinking up to 1.5 A or up to 3 A from a USB Type-C<sup>®</sup> source requires:

- To set the UCPD.DBn control pin (PE9) at a high level to be able to monitor CCx lines on UCPD.ADC1 (PG0)/UCPD.ADC2 (PF15) for host capability identification

- To check whether V<sub>BUS</sub> voltage constraints are compatible with any 5 V-powered application on the expansion connector (CN9). Refer to USB Type-C<sup>®</sup> current load lines and check that the 7 V maximum overvoltage V<sub>BUS</sub> protection fits your needs.

A USB Type-C<sup>®</sup> port protection device, associated with a power switch, is used to protect STM32U5x9J-DKx from ESD and USB V<sub>BUS</sub> overvoltage (6.5 V typical, up to 7 V). The USB Type-C<sup>®</sup> port protection device (U11) is called "USB Type-C<sup>®</sup> protection device" hereafter to simplify wording.

UM2967 - Rev 5 page 30/70

Five I/Os are used to manage the USB Type-C<sup>®</sup> connection: two configuration channels (CCx) connected on ADC inputs, a VBUS SENSE on ADC input, a dead battery (UCPD.DBn), and a fault (UCPD.FLT) on GPIOs.

Configuration Channel I/O (UCPD.ADCx): These signals are connected to the associated CCx line of the USB Type- $C^{\otimes}$  connector through the USB Type- $C^{\otimes}$  protection device. These lines are used for the configuration channel lines (CCx) to sense the cable orientation and identify power source capability. The Discovery kit supports only sink current mode with the default 5V power supply with up to 3 A current. To be compatible with the 1.8 V ADC voltage range, a resistor bridge is present between CCx lines and UCPD.ADCx inputs: It presents a total 5.1 k $\Omega$  pull-down on the USB connector and adapts the voltages from CCx lines to the maximum 1.8 V range of MCU inputs. According to the USB Type- $C^{\otimes}$  specification, the following thresholds must be used in the context of MB1829 to identify the host source capability:

| Source advertisement       | Minimum voltage on<br>UCPD.ADCx | Maximum voltage on UCPD.ADCx | Threshold between modes |

|----------------------------|---------------------------------|------------------------------|-------------------------|

| Default USB power (500 mA) | 0.24 V                          | 0.44 V                       | 0.54 V                  |

| 1.5 A @ 5 V                | 0.63 V                          | 0.84 V                       | 1 V                     |

| 3 A @ 5 V                  | 1 16 V                          | 1 49 V                       | _                       |

Table 11. UCPD.ADCx voltage range and threshold according to power source capability

To measure UCPD.ADCx inputs, UCPD.DBn must be set high before. See below.

- Dead battery I/O (UCPD.DBn, PE9): This signal is connected to the associated DBn line of the USB Type-C® protection device. When UCPD.DBn is low, the USB Type-C® protection device manages internally the dead battery resistors on CCx lines that enable 5V, and at least 500 mA default mode. When going High, UCPD.DBn connects ADCx lines of the microcontroller to the connector and enables it to sink more current than 500 mA (in the limit of 3 A). Thus, if UCPD.DBn is not set to the high level, STM32U5x9J-DKx must not consume or activate used cases requiring more than 500 mA.

- $V_{BUS}$  fault detection: UCPD.FLT (PE12, interrupt active low). This signal is provided by the USB Type-C<sup>®</sup> protection device. It is used as fault reporting to MCU after a bad  $V_{BUS}$  level detection. By design, the OVP  $V_{BUS}$  protection is set to 6.5 V nominal (7 V max) which is compatible with the absolute maximum ratings of the design. OVP  $V_{BUS}$  = 1.25 x (10 k $\Omega$  + 2.4 k $\Omega$ ) / 2.4 k $\Omega$ .

- VBUS\_SENSE ADC input (PG1) is used to detect attachment and detachment and to measure accurate VBUS voltage at the JP4 header (5V UCPD).

During startup, the DBn pin is tied to GND, and the USB Type- $C^{\$}$  protection device manages directly the CC lines: It enables the host source to power the 5 V  $V_{BUS}$  by default. A green LED (LD2) is lit when 5V is present. The USB Type- $C^{\$}$  protection device controls a FET switch and protects the Discovery kits against  $V_{BUS}$  overvoltage. Moreover, in any case, to ensure the functional behavior of the kit, the maximum recommended voltage applied on USB  $V_{BUS}$  is 5.5 V in continuous mode.

Note:

UCPD.ADC1 and UCPD.ADC2 functions are exclusive with respectively the ADC4\_IN6 and ADC4\_IN7 functions of the expansion connector (CN10). Solder bridges can handle it. Refer to Table 32. Solder bridge configuration.

## 8.2.2 USB 2.0 high-speed interface

STM32U5x9J-DKx supports a USB 2.0 high-speed interface on CN4 for compatibility with up to 480 Mbit/s. This allows limited time to transfer data into the embedded 4-Gbyte eMMC flash memory for example.

UM2967 - Rev 5 page 31/70

# 8.2.3 USB Type-C® function interface

Table 12. USB Type-C® function interface

| PIO  | Configuration                     |

|------|-----------------------------------|

| PE12 | FLT (UCPD.FLT)                    |

| PE9  | DBn (UCPD.DBn)                    |

| PG0  | ADC1 (UCPD.ADC1) -optionally used |

| PF15 | ADC2 (UCPD.ADC2) -optionally used |

| PA12 | HS_P (USBC.HS_P)                  |

| PA11 | HS_N (USBC.HS_N)                  |

| PG1  | VBUS_SENSE (VBUS_SENSE)           |

| PA15 | CC1 (UCPD.CC1) -not used          |

| PB15 | CC2 (UCPD.CC2) -not used          |

## 8.3 Hexadeca-SPI PSRAM memory

The 512-Mbit PSRAM is managed through the Hexadeca-SPI interface.

Table 13. Hexadeca-SPI PSRAM I/O interface

| PIO  | Configuration                 |

|------|-------------------------------|

| PH9  | NCS (HEXASPI1.NCS)            |

| PI3  | CLK (HEXASPI1.CLK)            |

| PI2  | DQS0 (HEXASPI1.DQS0)          |

| PH10 | IO0 (HEXASPI1.IO0)            |

| PH11 | IO1 (HEXASPI1.IO1)            |

| PH12 | IO2 (HEXASPI1.IO2)            |

| PH13 | IO3 (HEXASPI1.IO3)            |

| PH14 | IO4 (HEXASPI1.IO4)            |

| PH15 | IO5 (HEXASPI1.IO5)            |

| PI0  | IO6 (HEXASPI1.IO6)            |

| PI1  | IO7 (HEXASPI1.IO7)            |

| PI4  | NCLK -not used/not accessible |

| PI8  | DQS1 (HEXASPI1.DQS1)          |

| PI9  | IO8 (HEXASPI1.IO8)            |

| PI10 | IO9 (HEXASPI1.IO9)            |

| PI11 | IO10 (HEXASPI1.IO10)          |

| PI12 | IO11 (HEXASPI1.IO11)          |

| PI13 | IO12 (HEXASPI1.IO12)          |

| PI14 | IO13 (HEXASPI1.IO13)          |

| PI15 | IO14 (HEXASPI1.IO14)          |

| PJ0  | IO15 (HEXASPI1.IO15)          |

UM2967 - Rev 5 page 32/70

## 8.4 Octo-SPI flash memory

The 512-Mbit NOR flash memory is managed through the Octo-SPI interface.

The NRST reset pin from the microcontroller manages the Octo-SPI flash memory RESET function.

Table 14. Octo-SPI flash memory I/O interface

| PIO  | Configuration         |

|------|-----------------------|

| PA2  | NCS (OCTOSPIM_P1.NCS) |

| PA1  | DQS (OCTOSPIM_P1.DQS) |

| PF10 | CLK (OCTOSPIM_P1.CLK) |

| PF8  | IO0 (OCTOSPIM_P1.IO0) |

| PF9  | IO1 (OCTOSPIM_P1.IO1) |

| PF7  | IO2 (OCTOSPIM_P1.IO2) |

| PF6  | IO3 (OCTOSPIM_P1.IO3) |

| PC1  | IO4 (OCTOSPIM_P1.IO4) |

| PC2  | IO5 (OCTOSPIM_P1.IO5) |

| PC3  | IO6 (OCTOSPIM_P1.IO6) |

| PC0  | IO7 (OCTOSPIM_P1.IO7) |

| NRST | NRESET (NRESET)       |

## 8.5 eMMC flash memory

The 4-Gbyte eMMC flash memory is compatible with eMMC V5.0.

The eMMC\_RSTn (PH6, active low) is the reset for eMMC.

The embedded footprint is also compatible with other eMMC references in the 153-ball package. Check the compatibility of the memory datasheet versus the MB1829 schematics.

Table 15. eMMC flash memory I/O interface

| PIO  | Configuration         |

|------|-----------------------|

| PD2  | CMD (SDMMC1.CMD)      |

| PC12 | CLK (SDMMC1.CK)       |

| PC8  | D0 (SDMMC1.D0)        |

| PC9  | D1 (SDMMC1.D1)        |

| PC10 | D2 (SDMMC1.D2)        |

| PC11 | D3 (SDMMC1.D3)        |

| PB8  | D4 (SDMMC1.D4)        |

| PB9  | D5 (SDMMC1.D5)        |

| PC6  | D6 (SDMMC1.D6)        |

| PC7  | D7 (SDMMC1.D7)        |

| PH6  | eMMC_RSTn (eMMC.RSTn) |

UM2967 - Rev 5 page 33/70

## 8.6 Audio codec (not used)

Note:

SAI audio codec (U5) and audio jack (CN6) functions are not populated by default.

The Discovery kit features an audio codec with an SAI interface and a 3.5 mm audio jack connector (for stereo output and analog microphone). For the audio jack description, refer to the connector section.

The audio codec is driven through the I2C4 interface. An SAI 5-wire interface transfers audio PCM data. A dedicated GPIO (Audio\_RSTn, PH2, active low) is used to reset the audio codec.

Table 16. Audio codec I/O interface

| PIO | Configuration        |

|-----|----------------------|

| PB7 | SDA (I2C4.SDA)       |

| PB6 | SCL (I2C4.SCL)       |

| PE5 | SCK_A (SAI1.SCK_A)   |

| PE4 | FS_A (SAI1.FS_A)     |

| PE6 | SD_A (SAI1.SD_A)     |

| PE3 | SD_B (SAI1.SD_B)     |

| PE2 | MCLK_A (SAI1.MCLK_A) |

| PH2 | Audio_RSTn (RESETN)  |

## 8.7 20-pin audio MEMS connector

Note:

The 20-pin audio MEMS connector function is a differentiating feature, refer to Section 2: Ordering information. The Discovery kit features a 20-pin audio MEMS connector (CN1) to interface audio MEMS microphones on add-on boards. MDF and ADF interfaces are available through one clock and two data wires. PE10, PF4, and PF3 PIOs can manage up to four MEMS microphones. PE13 (Audio\_MEMS\_LED) is a control PIO to light a LED. For details about CN1 pinning, refer to the Connectors section.

Table 17. 20-pin audio MEMS connector function I/O interface

| PIO  | Configuration             |

|------|---------------------------|

| PE10 | SDIN4 (MIC.SDIN4)         |

| PF4  | SDIN0 (MIC.SDIN0)         |

| PF3  | CCK0 (MIC.CCK0)           |

| PE13 | Audio_MEMs_LED (MEMS_LED) |

UM2967 - Rev 5 page 34/70

## 8.8 Time-of-Flight sensor

Warning: Refer to Section 4 for a detailed explanation.

The Time-of-Flight (ToF) sensor is a laser-ranging sensor. It can be used for gesture control as well as for accurate distance measurements.

The device uses an analog power supply of 3.3 V, which starts after the 1.8 V digital supply. The ToF sensor (U7) is managed with an I<sup>2</sup>C bus shared with a temperature sensor, an LPN control line, and an interrupt line. The I<sup>2</sup>C can be accessed only if the LPN is high. The interrupt line is mapped on a WKUP PIO.

The Time-of-Flight sensor (U7) is subject to Class 1 laser product identification, refer to its datasheet for technical details, and refer to Figure 5 to identify its location on board.

Figure 23. Class 1 laser product label

Table 18. ToF sensor I/O interface

| PIO  | Configuration       |

|------|---------------------|

| PH8  | SDA (I2C3.SDA)      |

| PH7  | SCL (I2C3.SCL)      |

| PE14 | TOF_LPN (ToF_LPN)   |

| PB5  | TOF_INTN (ToF_INTN) |

## 8.9 Temperature sensor

The temperature sensor is managed with an  $I^2C$  shared with a ToF sensor, and an interrupt line. The interrupt line is mapped on a WKUP GPIO.

Table 19. Temperature sensor I/O interface

| PIO | Configuration         |

|-----|-----------------------|

| PH8 | SDA (I2C3.SDA)        |

| PH7 | SCL (I2C3.SCL)        |

| PF2 | TEMP_INTN (TEMP_INTN) |

UM2967 - Rev 5 page 35/70

Note:

Note:

## 8.10 Expansion connectors

**Warning:** The standard way to power the STM32U5x9J-DKx Discovery kits from expansion

connectors is to use the 5V\_VIN input power pin and GND pins from CN9.

By default, pin 5V of CN9 is an output power to expansion connectors. Do not use it to power MB1829 to avoid conflict with the 5V source selection jumper (JP4). For development purposes, the 5V pin of CN9 might be used as 5V input to the MB1829, provided the jumper is removed from the JP4 header.

The two connectors (CN9 and CN10) provide access to many ports: 4-bit SDMMC, two SAI, three  $I^2$ C, a USART, an LPUART, two SPI, ADCs, timers, and GPIOs. They include four spare pins to connect any other PIOs from the design. They also provide access to power supplies from MB1829.

Some interfaces are not available by default, and others are exclusive to other onboard functions. Refer to Section 9.7: Expansion connectors (CN9 and CN10) for pin assignment details and limitations.

Note: ADC4\_IN6 and ADC4\_IN7 functions of the expansion connector (CN10) are not connected by default because they are exclusive to UCPD.ADC1 and UCPD.ADC2 functions of USBC. If two additional ADCs are necessary for user application, it is recommended to use ADC4\_IN15 and ADC4\_IN16 from PD11/PD12 providing SAI2 is not used on expansion connectors (solder bridges can handle it, refer to the solder bridge table).

Note: SDMMC2\_D1 and SDMMC2\_D2 functions of expansion connector CN9 are connected by default and are exclusive with respectively UCPD.CC1 and T.SWO (JTDO) functions (solder bridges can handle it, refer to the solder bridge table).

Note: The SAI1 function of the expansion connector (CN10) is shared with the audio codec function, which is not populated on-board (the audio codec can support a high impedance state on this bus).

Note: Some USART3 signals of expansion connectors might be connected to the DSI\_V3 connector (solder bridges can handle it, refer to the solder bridge table).

SPI2 signals of expansion connectors might be connected to the DSI\_V3 connector (solder bridges can handle it, refer to the solder bridge table).

#### 8.11 User button function

**Warning:** Debounce filter, serial protection, and external pull-down are not present on the user button function.

The user button schematics have been optimized, so it is up to the user to manage the internal pull-down and debounce filtering by software. If the user wants to use PC13 as an output, it is recommended to disconnect the serial resistor (or change it to 220  $\Omega$  for example) to protect it from unwanted short circuits to VDD through the button.

The user button (B1) is a way to interact with software. This is a selection key, active high, which is mapped on a WKUP PIO (PC13).

A touch panel is also available on the display, and a ToF sensor is on the main board to interact with software.

#### 8.12 Reset button and reset function

The B2 reset button can activate the NRST reset function for all connected onboard devices.

The hardware system reset is managed by the STM32U5x9NJH6Q microcontroller and is available on the NRST pin. NRST signal is tied to GND during reset while it has a permanent internal pull-up tied to VDD\_MCU.

The NRST signal is connected to these peripherals: the Octo-SPI flash memory, expansion connector (CN9), debugging connector (CN11), TAG connector (CN3), and STLINK-V3E (through JP5). The STLINK-V3E can activate the NRST reset function if the JP5 jumper is ON and JP6 OFF (default settings).

UM2967 - Rev 5 page 36/70

### 8.13 Buttons and LEDs function

Table 20 summarizes the different buttons and LEDs of the STM32U5x9J-DKx Discovery kits and their function:

Table 20. Buttons and LEDs

| Reference          | Color                 | Function                      | Comment                                                                                       |

|--------------------|-----------------------|-------------------------------|-----------------------------------------------------------------------------------------------|

| B1                 | Blue                  | USER button (USER_Button)     | PC13                                                                                          |

| B2                 | Black                 | RESET button (NRST)           | Reset the board                                                                               |

| LD1 <sup>(1)</sup> | Green                 | VDD/3V3 LED                   | Lit when VDD and 3V3 are present (VDD_MCU = VDD if JP2/JP3 populated)                         |

| LD2                | Green                 | 5V power LED                  | Lit when 5V is ON                                                                             |

| LD3                | Green                 | USER_GREEN LED                | LED_GREEN, PE0                                                                                |

| LD4                | Red                   | USER_RED LED                  | LED_RED, PE1                                                                                  |

| LD5                | Red                   | ST-LINK overcurrent LED (OVC) | Lit when STLK overcurrent detected                                                            |

| LD6                | Red, green, or orange | ST-LINK COM LED               | Lit according to ST-LINK status                                                               |

| LD7                | Green                 | USBC power LED                | Lit when USB Type-C <sup>®</sup> is connected and V <sub>BUS</sub> is powered from CN4 source |

<sup>1.</sup> The LD1 function is not populated by default.

UM2967 - Rev 5 page 37/70

#### 9 Connectors

Nine connectors are implemented on the STM32U5x9J-DKx products:

- 20-pin audio MEMS connector (CN1)

- DSI V3 connector for display module board (CN2)

- TAG connector (CN3)

- USB Type-C® connector (CN4)

- USB Micro-B (CN5)

- Audio jack connector (not used) (CN6)

- Expansion connectors (CN9 and CN10)

- Debug connector (CN11)

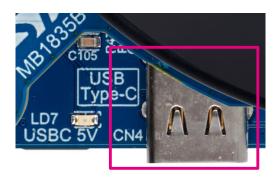

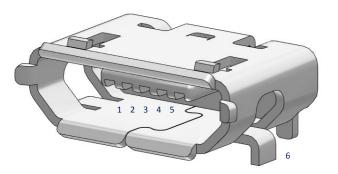

### 9.1 USB Type-C® receptacle connector (CN4)

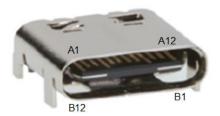

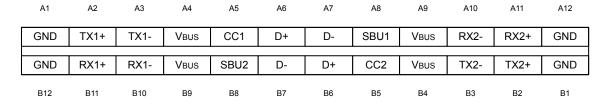

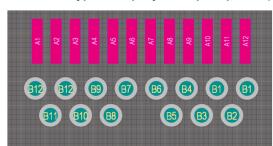

CN4 is a 24-pin double-row USB Type-C<sup>®</sup> hybrid right-angle receptacle compatible with USB Type-C<sup>®</sup> specifications and is shown in Figure 24. Refer also to Section 8.2: USB Type-C<sup>®</sup> (High Speed, sink only).

Figure 24. USB Type-C® receptacle connector (front view) (CN4)

Figure 25. USB Type-C® connector pinout (CN4)

The related top layer footprint pinout for the USB Type-C® connector is detailed in Figure 26 and Table 21.

Figure 26. USB Type-C® top layer footprint pinout (CN4)

UM2967 - Rev 5 page 38/70

Table 21 describes the connections of the USB Type-C® connector (CN4).

Table 21. USB Type-C® receptacle connector (CN4)

| Pin<br>number | Description        | Signal assignment   | Pin<br>number | Description        | Signal assignment   |

|---------------|--------------------|---------------------|---------------|--------------------|---------------------|

| B12           | GND                | GND                 | A1            | GND                | GND                 |

| B11           | RX1_P              | -                   | A2            | TX1_P              | -                   |

| B10           | RX1_N              | -                   | A3            | TX1_N              | -                   |

| В9            | VBUS               | VBUSc               | A4            | VBUS               | VBUSc               |

| B8            | SBU2               | -                   | A5            | CC1 <sup>(1)</sup> | UCPD_CC1_C          |

| B7            | DM2                | USBC_CN_HS_N (PA11) | A6            | DP1                | USBC_CN_HS_P (PA12) |

| B6            | DP2                | USBC_CN_HS_P (PA12) | A7            | DM1                | USBC_CN_HS_N (PA11) |

| B5            | CC2 <sup>(1)</sup> | UCPD_CC2_C          | A8            | SBU1               | -                   |

| B4            | VBUS               | VBUSc               | A9            | VBUS               | VBUSc               |

| В3            | TX2_N              | -                   | A10           | RX2_N              | -                   |

| B2            | TX2_P              | -                   | A11           | RX2_P              | -                   |

| B1            | GND                | GND                 | A12           | GND                | GND                 |

The CCx pins from CN4 are connected to the CCxc pins of TCPP01-M12. Depending on use cases, CCx signals might be used to connect to UCPD.ADCx signals of MCU (PG0 and PF15).

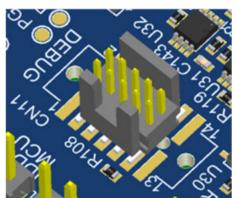

### 9.2 Debug connector (CN11)

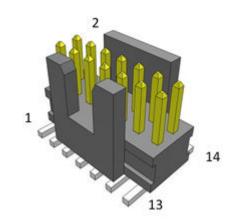

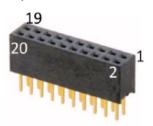

The Discovery kit embeds a MIPI10 debug connector on the bottom side of the main board (the 14-pin footprint also enables the support of an STDC14 connector as an option):

- MIPI10 10-pin connector on the 14-pin footprint (default configuration)

- STDC14 14-pin connector (option)

Attention: Before using CN11, check specific constraints in Section 7.4.5: SWD debug/program/trace and JTAG/USART.

#### 9.2.1 MIPI10 debug connector (default configuration)

Figure 27. MIPI10 debug connector (CN11)

UM2967 - Rev 5 page 39/70

|               |             |                   |               | •           |                   |  |

|---------------|-------------|-------------------|---------------|-------------|-------------------|--|

| Pin<br>number | Description | Signal assignment | Pin<br>number | Description | Signal assignment |  |

| 1             | -           | -                 | 2             | -           | -                 |  |

| 3             | VDD power   | VDD (1.8 V)       | 4             | SWDIO/JTMS  | T.SWDIO (PA13)    |  |

| 5             | GND         | GND               | 6             | SWCLK/JTCK  | T.SWCLK (PA14)    |  |

| 7             | KEY         | GND               | 8             | SWO/JTDO    | T.SWO (PB3)       |  |

| 9             | -           | -                 | 10            | JTDI        | T.JTDI (PA15)     |  |

| 11            | GNDDetect   | 100 Ω pull-down   | 12            | RESET       | NRST              |  |

| 40            |             |                   | 4.4           |             |                   |  |

Table 22. MIPI10 on STDC14 footprint

Note: Pins 1, 2, 13, and 14 belong to the STDC14 footprint and are not accessible with a MIPI10 compatible probe.

### 9.2.2 STDC14 debug connector (option)

The STDC14 debug connector might be implemented, depending on supported tools, for easy interface with ST tools ecosystem.

Figure 28. STDC14 debug connector (CN11)

If needed, a MIPI10 compatible probe can be plugged into the STDC14 connector (CN11) but you might have to bend or cut pins 1, 2, 13, and 14.

Table 23. STDC14 connector pinout

| Pin<br>number | Description | Signal assignment | Pin<br>number | Description | Signal assignment |  |

|---------------|-------------|-------------------|---------------|-------------|-------------------|--|

| 1             | -           | -                 | 2             | -           | -                 |  |

| 3             | VDD power   | VDD (1.8V)        | 4             | SWDIO/JTMS  | T.SWDIO (PA13)    |  |

| 5             | GND         | GND               | 6             | SWCLK/JTCK  | T.SWCLK (PA14)    |  |

| 7             | KEY         | GND               | 8             | SWO/JTDO    | T.SWO (PB3)       |  |

| 9             | -           | -                 | 10            | JTDI        | T.JTDI (PA15)     |  |

| 11            | GNDDetect   | 100 Ω pull-down   | 12            | RESET       | NRST              |  |

| 13            | RX          | USART1_RX (PA10)  | 14            | TX          | USART1_TX (PA9)   |  |

Note: USART1\_RX and USART1\_TX are signals from STM32U5x9NJ.

UM2967 - Rev 5 page 40/70

52375V1

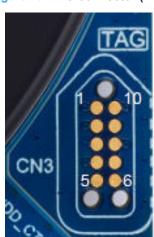

### 9.3 TAG connector (CN3)

A Tag-Connect<sup>™</sup> 10-pin footprint is implemented on the top side of STM32U5x9J-DKx (on the border of the PCB). A 10-pin compatible cable can be used to connect to the STM32U5x9J-DKx Discovery kits.

Attention: Before using CN3, check specific constraints in Section 7.4.5: SWD debug/program/trace and JTAG/USART.

Figure 29. TAG connector (CN3)

Figure 30. 10-pin compatible cable example

Table 24. TAG connector pinout

| Pin<br>number | Description | Signal assignment | Pin<br>number | Description | Signal assignment |  |

|---------------|-------------|-------------------|---------------|-------------|-------------------|--|

| 1             | VDD         | VDD (1.8V)        | 10            | NRST        | T_NRST (PG10)     |  |

| 2             | SWDIO/JTMS  | T.SWDIO (PA13)    | 9             | -           | -                 |  |

| 3             | GND         | GND               | 8             | JTDI        | T.JTDI (PA15)     |  |

| 4             | SWCLK/JTCK  | T.SWCLK (PA14)    | 7             | -           | -                 |  |

| 5             | GND         | -                 | 6             | SWO/JTDO    | T.SWO (PB3)       |  |

UM2967 - Rev 5 page 41/70

### 9.4 DSI\_V3 display board connector (CN2)

The 64-pin DSI V3 connector (CN2) supports DSI\_V3 display add-on boards.

Pin 61 to 64 (central pads for ground reference) are not accessible when an add-on board is plugged in.

The mating connectors used on the MB1829 main board and the MB1835 LCD daughterboard are set to ensure a total height of 8 mm between boards.

Figure 31. DSI\_V3 display connector (CN2)

Table 25. DSI\_V3 connector pin assignment (CN2)

| Function             | GPIO | Signal name | Pin numl | ber (CN2) | Signal name   | GPIO           | Function         |  |

|----------------------|------|-------------|----------|-----------|---------------|----------------|------------------|--|

| General ground       | -    | GND         | 1        | 2         | NC            | -              | -                |  |

| Differential DSI     | -    | DSI.CK_N    | 3        | 4         | DSI_TOUCH_INT | PE8            | Touch interrupt  |  |

| clock <sup>(1)</sup> | -    | DSI.CK_P    | 5        | 6         | GND           | -              | General ground   |  |

| General ground       | -    | GND         | 7        | 8         | DSI_D2_P      | -              | Not connected    |  |

| Differential DSI     | -    | DSI.D0_P    | 9        | 10        | DSI_D2_N      | -              | Not connected    |  |

| data 0               | -    | DSI.D0_N    | 11       | 12        | GND           | -              | General ground   |  |

| General ground       | -    | GND         | 13       | 14        | DSI_D3_P      | -              | Not connected    |  |

| Differential DSI     | -    | DSI.D1_P    | 15       | 16        | DSI_D3_N      | -              | Not connected    |  |

| data 1               | -    | DSI.D1_N    | 17       | 18        | GND           |                | General ground   |  |

| General ground       | -    | GND         | 19       | 20        | NC            | -              | -                |  |

| Power output         | -    | 5V_LCD      | 21       | 22        | DSI_SPI_CS    | PD8            | SPI chip select  |  |

| Power output         | -    | 5V_LCD      | 23       | 24        | DSI_SPI_CLK   | PB13/<br>PD10  | SPI/USART clock  |  |

| -                    | -    | NC          | 25       | 26        | DSI_SPI_MOSI  | PD4/<br>PB10   | SPI/USART data   |  |

| -                    | -    | BLGND       | 27       | 28        | DSI_SPI_DCX   | PD11           | SPI data/control |  |

| -                    | -    | BLGND       | 29       | 30        | NC            | -              | -                |  |

| -                    | -    | NC          | 31       | 32        | RESERVED      | -              | -                |  |

| -                    | -    | NC          | 33       | 34        | NC            | -              | -                |  |

| -                    | -    | NC          | 35       | 36        | 3V3_LCD       | -              | 3.3 V voltage    |  |

| -                    | -    | NC          | 37       | 38        | VDD_LCD       | DD_LCD - \refe |                  |  |

UM2967 - Rev 5 page 42/70

| Function                         | GPIO | Signal name | Pin num | ber (CN2) | Signal name | GPIO | Function                           |

|----------------------------------|------|-------------|---------|-----------|-------------|------|------------------------------------|

| -                                | -    | NC          | 39      | 40        | I2C5.SDA    | PH4  | Touch panel I <sup>2</sup> C data  |

| -                                | -    | NC          | 41      | 42        | NC          | -    | -                                  |

| SWIRE                            | PI7  | DSI_SWIRE   | 43      | 44        | I2C5.SCL    | PH5  | Touch panel I <sup>2</sup> C clock |

| -                                | -    | NC          | 45      | 46        | NC          | -    | -                                  |

| -                                | -    | NC          | 47      | 48        | NC          | -    | -                                  |

| Tearing effect                   | PF11 | DSI_TE      | 49      | 50        | NC          | -    | -                                  |

| -                                | -    | NC          | 51      | 52        | NC          | -    | -                                  |

| DSI backlight control output     | PI6  | DSI_BL_CTRL | 53      | 54        | NC          | -    | -                                  |

| -                                | -    | NC          | 55      | 56        | NC          | -    | -                                  |

| DSI and touch panel reset output | PD5  | DSI_RESETn  | 57      | 58        | NC          | -    | -                                  |

| -                                | -    | NC          | 59      | 60        | 1V8_LCD     | -    | 1.8-V voltage                      |

| General ground                   | -    | GND         | 61      | 62        | GND         | -    | General ground                     |

| General ground                   | -    | GND         | 63      | 64        | GND         | -    | General ground                     |

<sup>1.</sup> The microcontroller software system must invert the DSI.CK\_N and DSI.CK\_P lines together to be aligned with the DSI\_V3 add-on boards. The DSI clock differential signals (\_N and \_P) are originally inverted on the main board for layout reasons (refer to DSI\_V3 connector standard pinning).

UM2967 - Rev 5 page 43/70

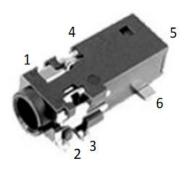

### 9.5 Audio jack (not used) (CN6)

Note: SAI audio codec and audio jack are not present by default.

The 3.5 mm stereo audio jack supports stereo line or headphone outputs and an analog microphone: