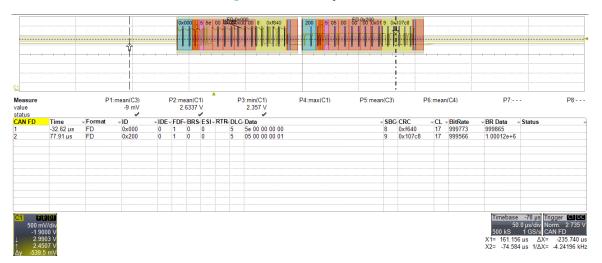

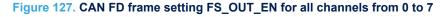

User manual

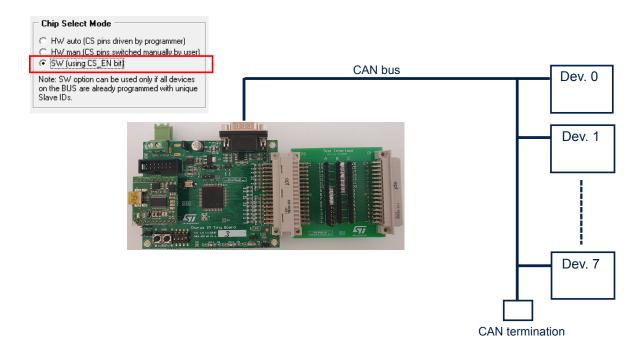

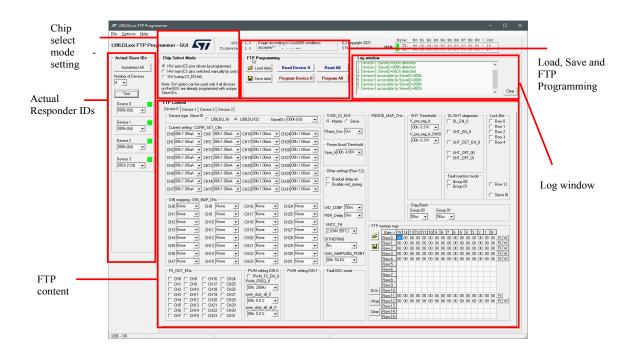

# 32-channel LED driver with automotive CAN FD Light interface

#### Introduction

The L99LDLH32 is a monolithic 32-channels linear current regulator specifically designed for automotive exterior O/LED rear lighting applications. The output channels are in high side configuration, and for this reason, the L99LDLH32 is suitable to drive an OLED panel with a common cathode.

The L99LDLH32 integrates a dedicated CAN FD Light communication interface, allowing high-rate data transmission (at 1 Mbit/s) and using CAN FD structure for long frames. Besides the CAN FD Light physical layer, the device integrates the protocol handler and a precise oscillator, so no external devices required to facilitate communication with Commander ECU.

The L99LDLH32 can operate in Bus mode using CAN FD Light interface or stand-alone/fail-safe mode using internal few time programmable (FTP) memory registers.

Thanks to integrated PHY and protocol handler, the device is ready for zonal architecture and the domain-oriented topology, communicating directly with the zonal controller or body computer module (BCM).

This manual aims at guiding the user through the device's functionality, giving practical guidelines for a quick design and debug. The user should consider this document to hand on the device. It is intended to complement the datasheet, functional safety manual, and other applicative documents such as the FTP programming tool, tiny board (EV-L99LDLH32 evaluation board), and any future supplemental application notes.

## 1 General Items

#### 1.1 Overview

The L99LDLH32 offers a high level of flexibility thanks to its programmability through CAN FD Light communication interface. This feature supports generic platform approaches, which require a software configurability of several parameters.

As the device potentially controls safety-critical functions such as taillight, break light and turn indicators, built-in features are integrated to support a high level of functional safety on the application level. They are supplied directly from a car battery. The L99LDLH32 guarantees up to 35 V output-driving capability, and features 32 regulated current sources. It is able to provide from 1 mA up to 15 mA programmable current to drive each pixel of the O/LED panels. The current can be individually programmed using an integrated 8-bit DAC.

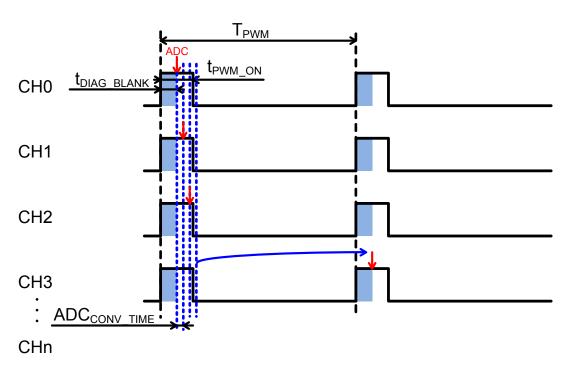

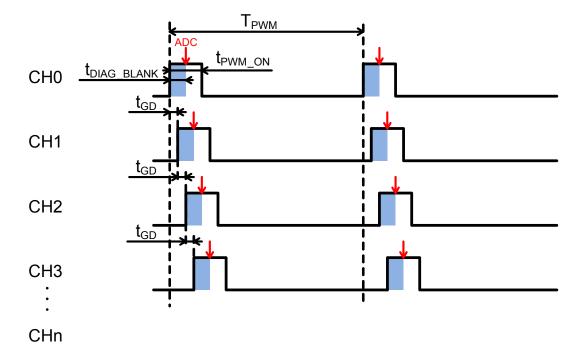

Each O/LED pixel can be supplied through one pre-regulator connected between the battery and the integrated current source. The pre-regulated (and the battery) voltages are internally monitored by an 8-bit ADC; the results are stored in a dedicated result register. The brightness can be adjusted separately for each channel through an 8-bit PWM exponential dimming control. An 8-bit linear global dimming can be superimposed to each channel's individual PWM. A slow turn-on and turn-off time improves the system's low noise generation performances. To simplify light function handling, the 32 channels can be grouped in two different light function groups.

Each channel can be mapped or not mapped to the direct input and through the pre-regulated external supply voltage (VPRE\_REG pin). This feature ensures the highest flexibility to control lighting functions composed of different O/LED types, currents, and string lengths (see Section 5 O(LED) supply voltage regulation). Thanks to the integrated high precision oscillators, the device generates all relevant timing functions such as the PWM frequency, the duty cycle, the trigger points for ADC conversion, the phase shift, etc. No external timers are required.

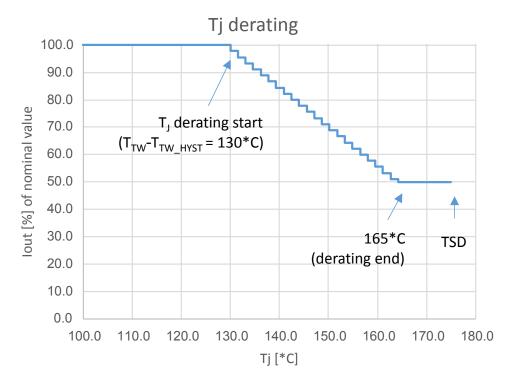

In the L99LDLH32, thanks to integrating an 8-bit ADC, a complete diagnostic is also available: open load detection, short to ground detection, single LED short detection, (O)LED temperature monitoring, protection through NTC, supply voltage monitoring, device temperature monitoring, etc. Diagnostic thresholds are freely configurable for each function group. Moreover, the user can configure the desired device reaction to detected faults, ensuring maximum flexibility for the application and sophisticated auto-recovery strategies (further details in Section 4 Diagnostic and protections). The device also features the gradual output delay, which avoids contemporary turning on all the channels used for a specific light function, reducing the inrush current. To improve EMI performances further, the device implements an internal clock dithering to have a spread spectrum noise reduction. L99LDLH32 is equipped with a thermal warning (TW) and outputs thermal shutdown (TSD). The device performs an automatic thermal derating based on external NTC measurement and device junction temperature (T<sub>J</sub>). The supply voltage range is between VS\_MIN and 40 V avoiding any additional load dump protection on the power supply stage.

Besides the full (2x) AEC-Q100 qualification, the L99LDLH32 is also validated in the application. This either vs specific tests aimed at validating device features or vs. standard and norms like:

- VW80000, ISO 16750-2: road vehicles environmental conditions and testing for electrical and electronic equipment (limited only to some electrical tests)

- long time over voltage

- jumpstart

- load dump test

- slow ramp down and up of VBAT voltage

- slow ramp down and fast ramp-up

- reset behavior at voltage drop

- engine cranking low voltage

- loss of power connection

- loss of ground connection

- 2. Conducted emission, according to IEC 61967-4 (150 Ω method)

- 3. Conducted susceptibility, according to IEC62132-4 (DPI method)

- 4. CISPR25, according to VW TL81000 (artificial network test class 5)

- 5. BCI, according to VW TL81000 (compliance with test severity L2)

- 6. ISO pulses (intended for the reference design): 1, 2a, 3a, 3b

UM2996 - Rev 1 page 2/124

## 1.2 Typical application schematic and description of external components

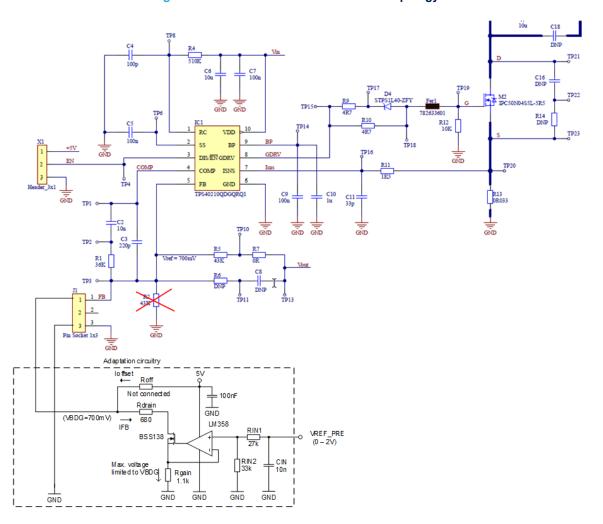

The figure below shows a typical application schematic for the L99LDLH32:

VPRE REG 本 11 GND . OLED panel VPRE\_REG Optional EMC Filter V5V OUTO OUT1 V3V3 OUT3 OUT4 NTC OUT5 OUT6 PWM sychronization input/output OUT7 0 SYNC I/O OUT8 Chip select for NVM <u></u> CS OUT9 programming OUT10 OUT11 CAN\_H OUT12 CAN BUS OUT13 CAN\_L OUT14 L99LDLH32 OUT15 NTC NCU18XH103F6SRB OUT16 OUT17 DIN Direct drive and diagnostic pins for Standalone/ FailSafe mode operation . OUT18 OUT19 FAULT OUT20 (can be used also in BUS OUT21 PWM DC 1/2 OUT22 OUT23 OUT24 OUT25 Voltage reference output OUT26 0 VREF\_PRE\_REG for Preregulation control OUT27 OUT28 OUT29 TEST OUT30 R\_REF\_DAC OUT31 GND GND

Figure 1. Typical application schematics

This paragraph comments on all the external components required by the L99LDLH32. Each external passives are reported with its label (refer to Figure 1. Typical application schematics), and the correspondent pin of the L99LDLH32 is highlighted within brackets. The optional component is labeled with "\*" and enclosed by a dashed box.

- C1(Vs): using 100 nF (C1) ceramic capacitor mounted close to the device VBAT pin, and GND terminals capacitor helps suppress voltage transients originating from other drivers connected in parallel and sharing the same battery line. This capacitor is capable of suppressing only low energetic short-transient pulses.

- C2 (Vs): during an interruption of VBAT, the parallel of C1 and C2 (22uF) capacitors keeps the device active

during short disconnection events.

- C3 (VPRE\_REG): 100 nF is acting as a decoupling capacitor. The external preregulator has its output capacitor (in the case of dc-dc converter used for preregulation, the Cout of the dc-dc is also connected at this pin).

- (OUT0-31): used to connect the OLED (or LED) segment's cathode. If OLED panels require ESD protections, it is allowed to have i.e., capacitors between the OUTx and GND. In general, the L99LDLH32 does not require any output capacitors. It is essential to consider that the eventual capacitors placed on these pins should be chosen according to the set blanking time (as a rule of thumb, the higher the capacitance value required to sustain disconnection events, the higher blanking time should be set).

UM2996 - Rev 1 page 3/124

- R3 (R\_REF\_DAC): this resistor is used to define the reference for the output current. It is recommended to use an E96 resistor (1% tolerance). Using 61.9 kΩ, the output current setting is in the specified range of the datasheet. In our OLED reference design, the output current ranges from 2.5 mA to 5 mA.

- (TEST): not used, connected to GND.

- R2 (FAULT): the FAULT pin is a bidirectional I/O pin and it has an open-drain output stage, and pull-up is needed to define the logic high. If more devices are present, the FAULT pin can be paralleled. Our reference design has a 10 kΩ resistor for each device; another possibility is to have an individual resistor of 4.7 kΩ for both devices (or more). The PU resistor at the FAULT pin should be tied to 3.3 V not to exceed the abs max of the FAULT pin. To dimension, the resistor R2 refers to the parameter I<sub>FAULT</sub> on table 81 of the L99LDLH32 datasheet.

- (CS) this pin is used as a chip select for the NVM programming; this pin should be pulled down to GND in regular operation.

- (Sync\_IO): this pin is used to connect more devices to synchronize the PWM clock. On our tiny board, we have two L99LDLH32 connected through the SYNC\_IO pins: one device acting as "Provider" providing PWM clock and the other one as "Consumer." (refer to the chapter: Section 6 Premises on devices NVM management to define the provider and consumer).

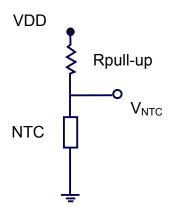

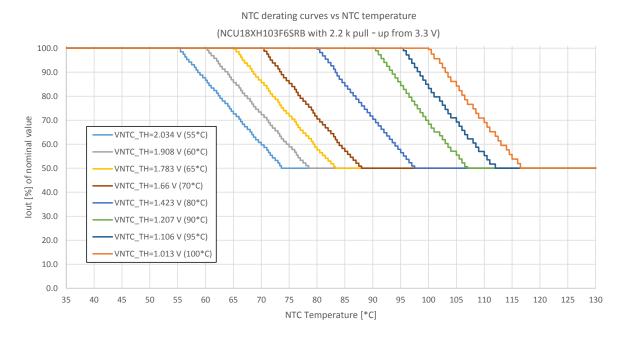

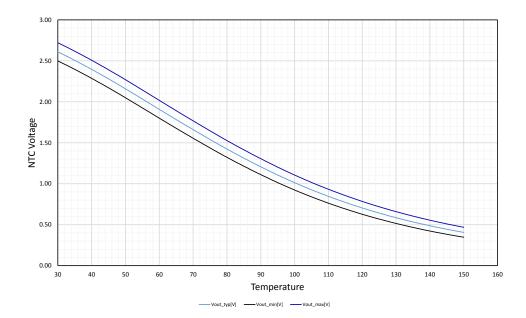

- (NTC): L99LDLH32 has a derating function, and we can configure the starting temperature. With the suggested part number for the NTC and PU resistor R1 (2.2 k $\Omega$ ), the derating function is compliant with the datasheet. We recommend using the following part number NCU18XH103F6SRB or, in case, find an alternative part with similar characteristics.

- **C4, C5** (*V3V3*, *V5V*): for both pins, are recommended 1 uF capacitors for the stability of the internal linear voltage regulators 3.3 V and 5 V. These capacitors also act as decoupling capacitors to sustain the fast transients generated by the internal logic of the IC.

- **D1** (Vs): a reverse polarity protection is required. In this case, we adopted a diode between the battery rail (VBAT) and the pin Vs. According to ISO 7637-2 / 2011, this diode also covers the test pulse 1 and 3a.

- T1 (Vs): transil protection is required to be compliant with ISO7637-2 (2011) (positive pulses ISO 2a and 3b). To select the part number properly, the clamping voltage of the transil (37 V) should be lower than the abs max of the pin (40 V) and be the breakdown voltage should be higher than the 24 V required for the jump start.

- (*DIN*): if the L99LDLH32 is used only in Bus mode and the DIN pin is not used, connecting it to the ground is recommended. Alternatively, DIN can be directly connected to a BCM or Rear Light ECU. A further option is dimming the DIN by switching the battery line through a voltage divider (R4\*, R5\*). The PWM via battery line represents an optional scenario, and in this case, the couple of resistors should be dimensioned according to the maximum level of VBAT, required by the application, and the absolute maximum rating of the DIN pin (see V<sub>DIN</sub> on table 71 of the DS12879). A trade-off should be met, dimensioning also according to the minimum required VBAT, being able to reach the logic high level of the DIN pin (DIN\_H parameter, table 81 of the datasheet). To fulfill both conditions with a voltage divider (R4\*, R5\*), a zener diode Z1 in parallel to R4\* is needed. Z1\* should be selected according to the absolute maximum rating of DIN pin and the minimum logic level (DIN\_H parameter).

- T2\* (CAN\_H, CAN\_L): this component is intended as optional and recommended in case of connection of the L99LDLH32 directly with the BCM. In case of "traditional" approach with dedicated rear light ECU, this optional TVS for CAN bus is not necessary. The integrated CAN FD transceiver was not designed to sustain the ESD system level test according to IEC 61000-4-2. To increase the ESD system-level immunity, we recommend using the ESDCAN03 (available in SOT323 and DFN packages).

- L2\* (CAN\_H, CAN\_L): CAN common mode choke [CMC] is usually used on the external CAN bus (car communication network) on the BCM side. It is an optional component related to the communication bus network. On our tiny board, we used the following part number: 1210CAN-104.

- R6\*, R7\*, C10\* (CAN\_H, CAN\_L): Can FD Light termination is needed at the two ends of the line in our reference design we adopted two resistors (62 Ω each) and 4.7 nF between the common node and ground.

- C6\*,7\*,8\*,9\*, L1\*, Fb\* (Vs): the Pi filter connected between the battery line and ground is tied to the VS pin of the L99LDLH32 through the reverse polarity protection diode D1. This optional EMC filter was used during the evaluations allowing compliance with the conducted emission, susceptibility, and CISPR25 (test 2, 3, 4 in Section 2.1 On the initial state).

UM2996 - Rev 1 page 4/124

# 1.3 Schematic and layout of the tiny board

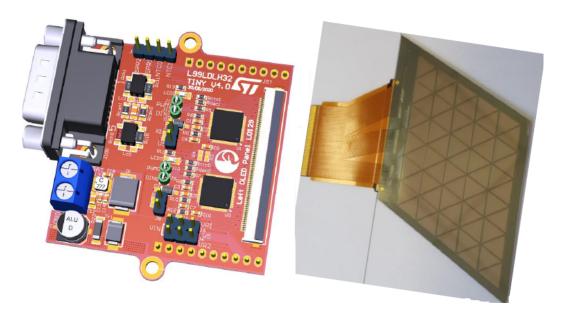

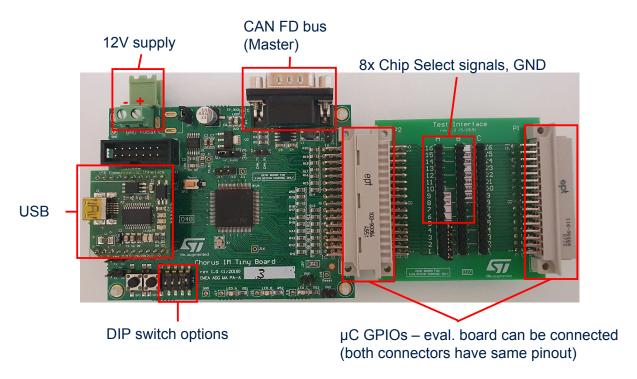

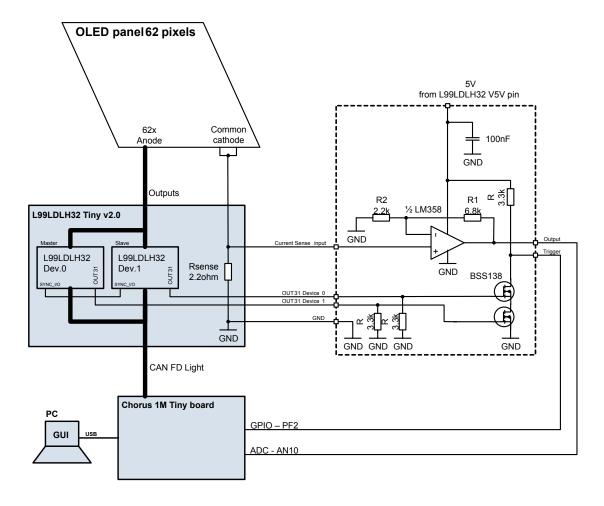

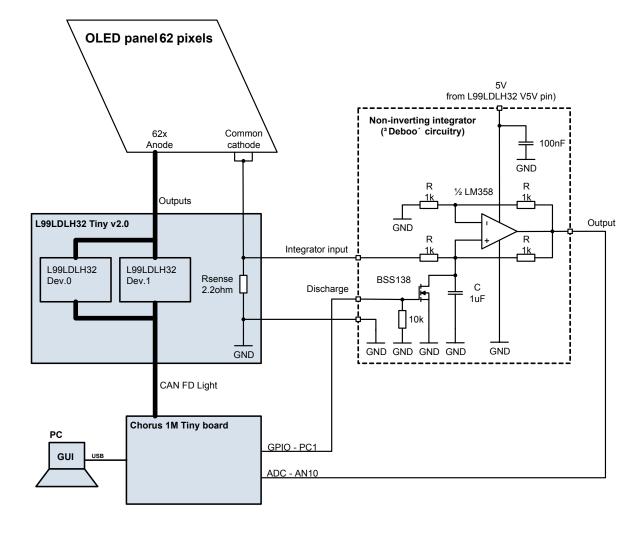

This paragraph shows the layout of the tiny board equipped with two L99LDLH32, driving an OLED panel with 60 segments. The figure below shows the final board and the OLED load board.

The reference design for the OLED tailight application, also foreseen a Chorus 1 M (not shown in Figure 2) acting as BCM or rear light ECU.

This design is not intended to fit any particular form factor. This design aims to provide a compact solution, providing a way to test the board's performance. Several optimizations can be further done by the customer for final production. For example, the test point can be removed, and the capacitors' size, number, and value can be improved.

UM2996 - Rev 1 page 5/124

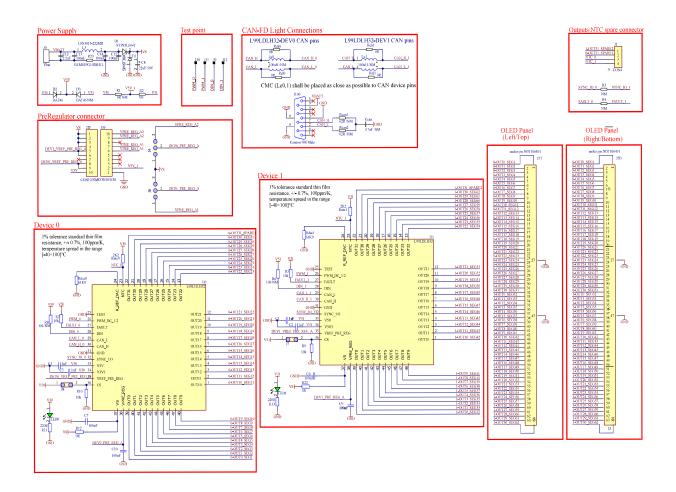

The figure below, unveil the schematic of the tiny board reference design:

Figure 3. Tiny board schematic

Even if the L99LDLH32 (QFN48L) package has an excellent thermal impedance, a good PCB layout can optimize the heat transfer, essential for the long-term reliability of the device.

The L99LDLH32 requires a few tricks for the layout:

- · Place the capacitors close to the pin of the IC

- CMC (if required) should be placed as close as possible to the CAN\_H, CAN\_L pins

- It is not recommended to have a ground plane under the inductor and ferrite (for the optional EMC filter)

UM2996 - Rev 1 page 6/124

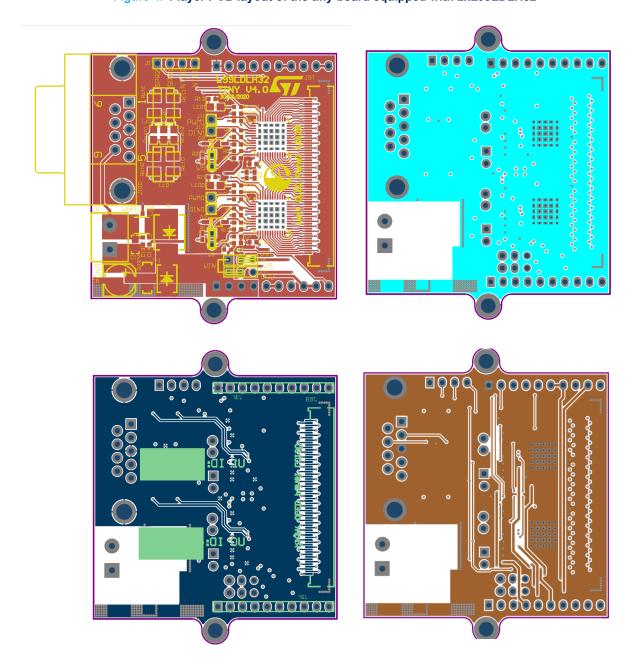

The tiny board is on 4 layer PCB (FR4); in the figure below, each layer is shown.

Figure 4. 4-layer PCB layout of the tiny board equipped with 2xL99LDLH32

In Figure 4, clockwise, starting from top left (red layer): top layer, signal layer 1, ground-bottom plane, and signal layer 2.

UM2996 - Rev 1 page 7/124

The Table 1 reports the mandatory and optional components required by L99LDLH32, according to the typical application schematic reported in Figure 1. All the designators reported in the Table 1 follow the schematic in Figure 1, and the list of components below is intended for one L99LDLH32.

Table 1. BOM

| Quantity | Designator            | Comment               | PN                |

|----------|-----------------------|-----------------------|-------------------|

| 1        | C2*                   | 22 μF/50 V            | EEEFK1H220P       |

| 1        | C1, C3, C7*, C8*, C9* | 100 μF                |                   |

| 1        | C4, C5                | 1 μF                  |                   |

| 1        | C6*                   | 2.2 µF                |                   |

| 1        | C10                   | 4.7 nF                |                   |

| 1        | D1                    | DIODO_SMC             | STPS5L60-Y        |

| 1        | T1                    | DIODO_SMB             | SM6T27A           |

| 1        | T2*                   |                       | ESDCAN03-2BWY     |

| 2        | J5B, J5T              | molex                 | 5051106491        |

| 1        | J100                  | Cannon 9M/Male        | 5504F1-09P-02A-03 |

| 1        | L1*                   | LPS3015-222MR         | LPS3015-222MR     |

| 1        | L2*                   |                       | 1210CAN-104       |

| 1        | Fb*                   | BLM41PG102SH1L        | BLM41PG102SH1L    |

| 1        | R1                    | 2.2 kΩ                |                   |

| 1        | R2                    | 4.7 kΩ                |                   |

| 1        | R3                    | 61.9 kΩ (E96- 1% tol) |                   |

| 2        | R6*, R7*              | 62R                   |                   |

| 1        | NTC                   |                       | NCU18XH103F6SRB   |

UM2996 - Rev 1 page 8/124

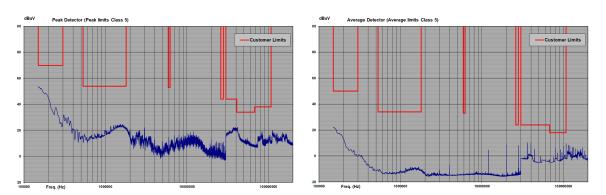

## 1.4 CISPR 25 characterization

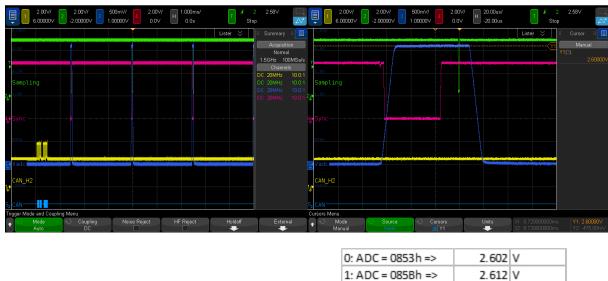

The analysis concerning the conducted emission of the L99LDLH32 was done using the executed emission voltage method and average limits for conducted disturbances (CISPR25) specifications:

- peak detection

- · average detection

To be class 5 compliant, the peak detector should pass the peak limit for class 5 and then the average limit for class 5.

The test was conducted with VBAT = 12.5 V at room temperature. The hardware under test was the L99LDLH32 (v 4.0) Tiny board, the microcontroller Chorus 1 M Tiny board V1.0 and the load board composed of 32 OLED segments. In terms of SW settings, the operation was conducted in Bus mode, and the WD was served via CAN FD Light.

The test configuration is done according to Std CISPR25 limits (2016 edition) and VW TL-81000 AN (2018 edition).

The L99LDLH32 is compliant (with CLASS 5) with standard CISPR25 and VW TL-81000 limits. In the Figure 5 is reported the test result of the standard CISPR25 compliance.

Figure 5. CISPR25 characterization in bus mode

In Figure 5, on left-hand side, it is reported the characterization in the Bus mode peak detection; whilst on right-hand side, there is the characterization in the Bus mode average detection.

UM2996 - Rev 1 page 9/124

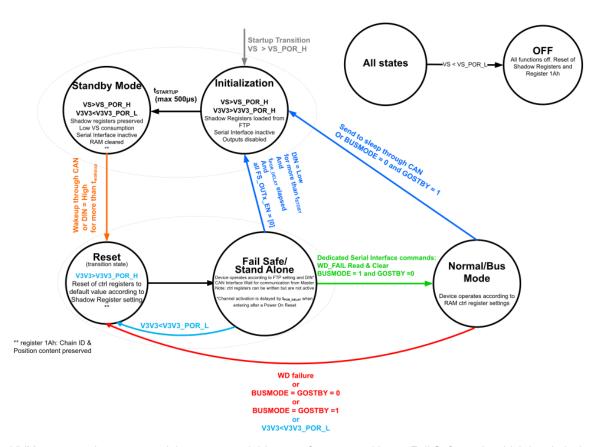

## 2 Device control

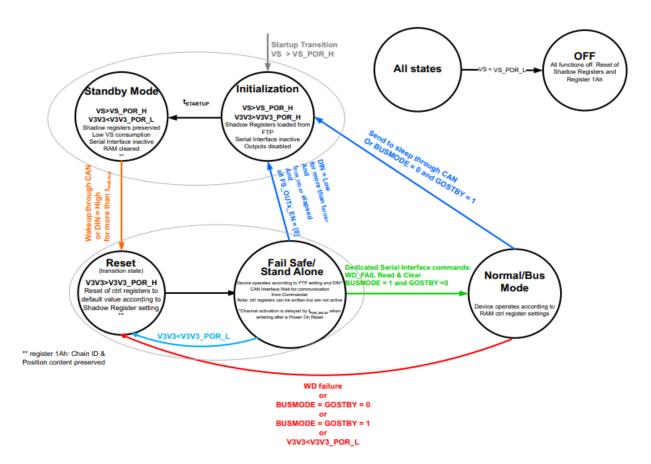

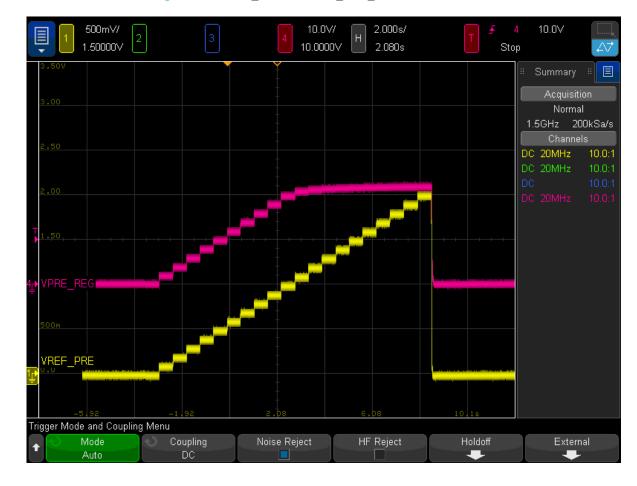

In order to operate the device L99LDLH32 in an application environment, it is necessary to have some knowledge about states into which the device can be driven and the purpose of them. The diagram below provides an overview of the state machine.

Figure 6. L99LDLH32 state machine

As soon as the VS pin of the device is driven above the VS\_POR\_H level, the device gets through the state machine entry point, and the logic becomes active.

From a user perspective, it is worth knowing that three states can be set on purpose, each having distinctive operating conditions:

- Standby mode: low consumption state, regulators off, no logic for control over light functions running

- Fail Safe mode: light function ON according to device NVM memory settings. Diagnostics available on device FAULT pins. This state is meant to allow device control of light function without MCU supervision

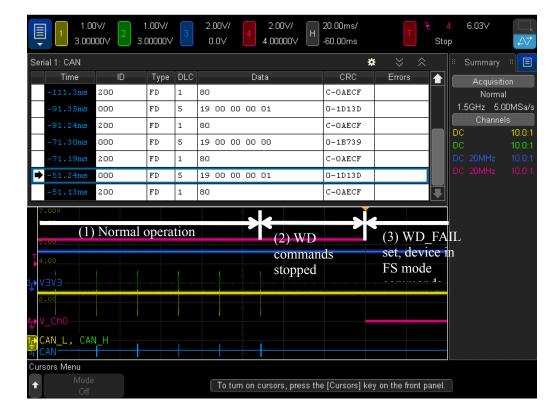

- Bus mode: this mode provides full access to device registers to program the broadest set of device operating conditions and diagnostic information retrieval. An MCU connected to the device CAN FD Light bus pins through a transceiver is mandatory in order to exchange messages (for example, commands from the CAN FD Light commander MCU side vs diagnostic information from device side). Permanence in Bus mode is granted if the device receives periodic watchdog messages from the MCU. Each one needs to toggle the previous value of the lower bit of register 19h within a programmable timeout (of 25, 50, 100, and 200 ms to reset the watchdog counter). Otherwise, the device performs a transition in Fail Safe mode (assuming that MCU is not providing proof of responsiveness, something in the system might have gone wrong).

UM2996 - Rev 1 page 10/124

Permanence in Bus mode is granted if the device receives periodic watchdog messages from the MCU. Each one needs to toggle the previous value of the lower bit of register 19h within a programmable timeout (of 25, 50, 100, and 200 ms to reset the watchdog counter). Otherwise, the device will perform a transition in Fail Safe mode (assuming that MCU is not providing proof of responsiveness, something in the system might have gone wrong). Initialization state and reset state are pass-through states, in the sense that they are not permanent and the exit transition from these states is performed automatically by the device logic, no application command involved. The former state is where the transfer of NVM information into shadow registers takes place while entrance in the latter is triggered by voltage drops of the V3V3 regulator below its POR level. In this case shadow registers defaults are reloaded into control registers, then transition into Fail Safe state takes place.

#### 2.1 On the initial state

The Figure 6 shows that power up starts the state machine entry point, which is the initialization state. The first noticeable point after supply is that depending on hardware settings, the device can then either settle in standby mode or Fail Safe mode. More in detail, after VS>VS POR H one of the two conditions below can happen:

- If DIN pin of the device is kept low and no CAN FD Light frames are sent, the device settles in standby mode

as soon as VS>VS\_POR\_H and remains in such state for a time startup (needed for initialization phase,

max 650 µs)

- If DIN pin is kept high or a determined wake up frame (WUP) sent through the CAN FD Light bus is recognized, then the device performs a transition in Fail Safe mode

For the second case, permanence in Fail Safe mode after transition from standby is granted only if the DIN pin is kept high or if one of the device channels is kept ON by means of the FS\_OUT\_ENx option programmed into the device NVM memory. If conditions for Fail Safe permanence are not being held, the device performs a transition back in standby (passing through the initialization state) within the time specified at the tPOR\_DELAY field within NVM (delay ranging from 0 to 100 ms depending on tPOR\_DELAY programmed value).

#### 2.2 Transition between states and related commands

This section shows some examples of device transitions and how they are supposed to be performed.

For the end user, device transitions are classified in two categories depending on whether the transition is initiated by a CAN FD Light command or not.

State transitions outlined within the table below are initiated through CAN FD Light commands.

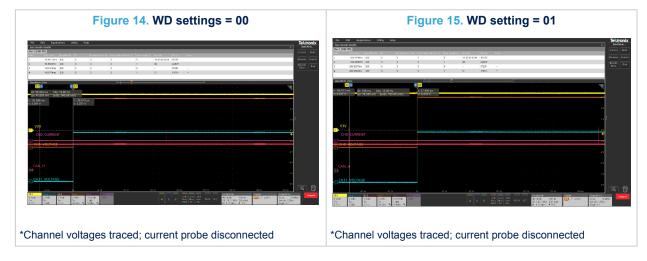

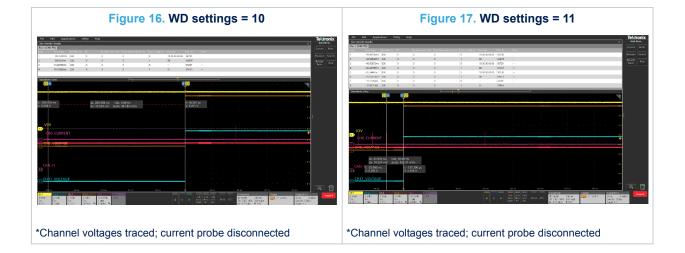

Unicast frame payload content **Transition type** Comments ([Opcode | Address], [Data byte]) (1) Sequence of two commands: [AEh], [00008000] Payload fitting within the CAN FD Light Fail Safe to Bus mode frame structure outlined below and [18h],[00000001h] [18h], [00000000h] Bus mode to Fail Safe or [18h], [00000011h] Broadcast goto stdby possible as well Bus mode to Standby (through init state) [18h], [00000010h] (see Figure 14 and Figure 15)

Table 2. State transitions (with CAN FD Light commands)

device status (check Section 6.3 for more detail).

Each L99LDLH32 device replies with a CAN FD Light frame containing GSB to each of these commands. The GSB byte content is set within the payload of the response and contains information related to the current

Below the state transitions that are started without CAN FD Light commands.

UM2996 - Rev 1 page 11/124

<sup>1.</sup> Colon between address and databyte stands for concatenation of bit strings.

Table 3. State transitions (without CAN FD Light commands)

| Transition type                           | Action for transition initiation                           | Comments                                                                                                                                      |

|-------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Standby to Fail Safe                      | CAN FD wake up pattern<br>or<br>DIN low to high transition | After transition, permanence in Fail Safe mode needs DIN high or FS_OUT_ENx (in NVM, row 1,2, 3, 4 column 9) settings on at least one channel |

| Fail Safe to standby (through init state) | DIN low and no output channel set with FS_OUT_ENx          | DIN needs to be kept low for more than tSTDBY and transition starts after tPOR_DELAY                                                          |

| Bus mode to Fail Safe                     | Watchdog expiration                                        | Watchdog expiration window can be set to 25, 50, 100 ,200 ms in device NVM                                                                    |

## State machine transitions examples:

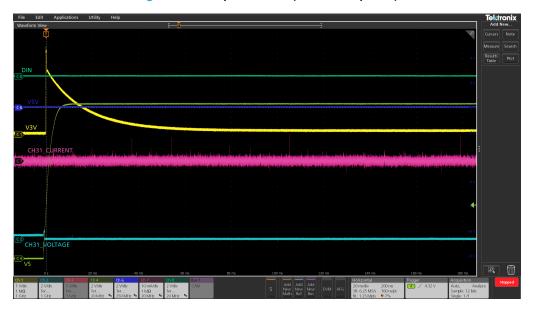

• Device startup: performs init  $\rightarrow$  stdby transition after VS>VS\_POR\_H

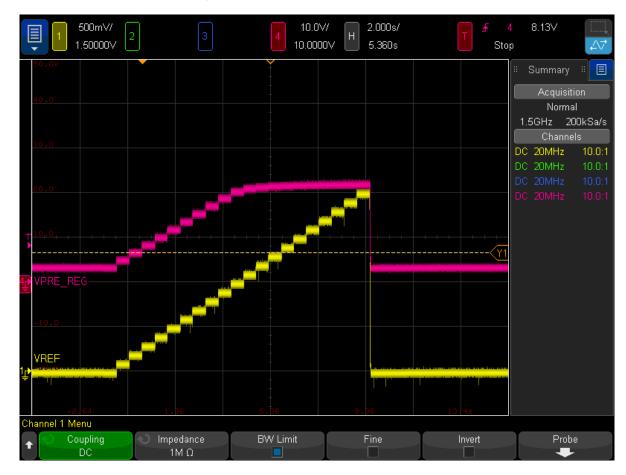

Figure 7. Startup transition (DIN was kept low)

UM2996 - Rev 1 page 12/124

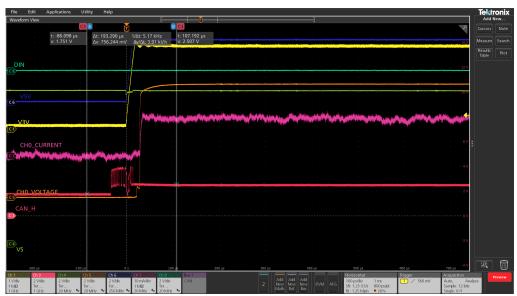

Wake up by CAN FD frame : stdby -> Fail Safe

Figure 8. Device transition from stdby to Fail Safe after wakeup frame

$\bullet \qquad \text{Wake up through DIN}: \text{stdby} \rightarrow \text{Fail Safe}$

Figure 9. DIN startup, 25 µs startup time

UM2996 - Rev 1 page 13/124

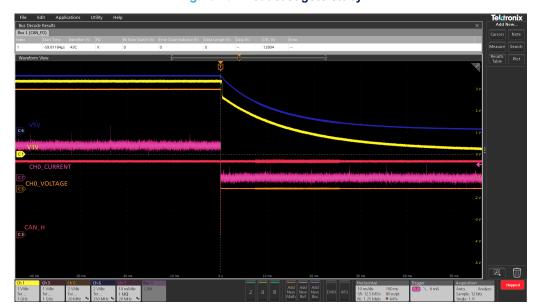

• Fail Safe  $\rightarrow$  stdby due to DIN falling edge:

File Edit Applications Urilary Help

Tel-tronix

Add New.

Massure Search

Figure Pint

CHO\_CURRENT

CHO\_CURRENT

CHO\_VOLTAGE

CAN\_H

CHO\_VOLTAGE

CAN\_H

CAN\_

Figure 10. Transition to stdby after DIN high to low transition

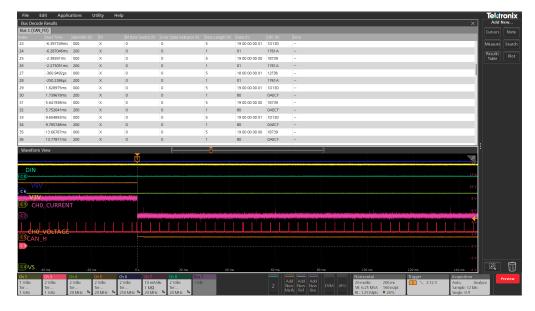

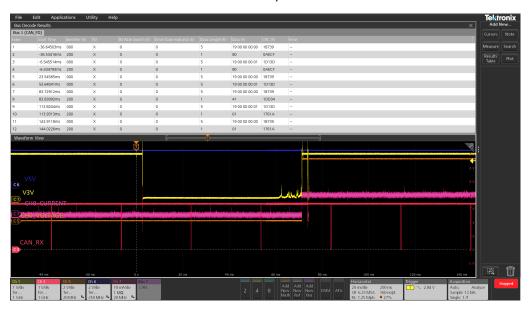

Fail Safe mode to Bus mode through CAN FD light command:

In the example below:

- Fail Safe: channel0 is set permanently on with 15 mA current setting

- Bus mode : channel0 is off

Figure 11. Fail Safe to Bus mode transition (on CAN FD Light command frame n.27)

Bus mode to Fail Safe (through reset) after CAN FD Light command

UM2996 - Rev 1 page 14/124

Figure 12. Bus mode to Fail Safe transition (GO\_STDBY=1 in register 18h)

• Transition from Bus mode to Fail Safe (through reset) after watchdog expiration

UM2996 - Rev 1 page 15/124

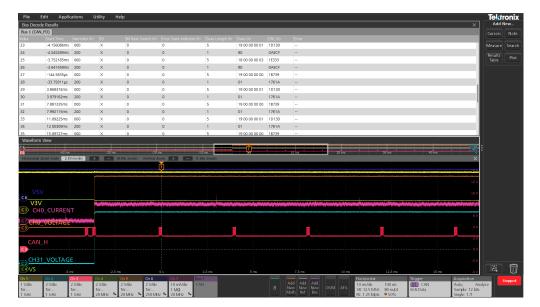

Below Bus mode to Fail Safe transition after tWD expiration (tWD = 50  $\mu$ s and tWD = 100  $\mu$ s):

Below Bus mode to Fail Safe transition after tWD expiration (tWD = 200  $\mu$ s and tWD = 25  $\mu$ s):

UM2996 - Rev 1 page 16/124

Transition from Bus mode to Fail Safe (through reset) after V3V3 regulator drop

Figure 18. From Bus mode to Fail Safe after V3V3 drop (GSB = 80 h for Bus mode, GSB = 41,01 for Fail Safe)

• Bus mode to standby transition (through initialization) after CAN FD Light command

Figure 19. Unicast goto stdby

UM2996 - Rev 1 page 17/124

Figure 20. Broadcast goto stdby

UM2996 - Rev 1 page 18/124

# 3 LED brightness control

Led brightness depends on led current intensity and led dimming through PWM. Both of these parameters can be controlled writing the settings into the user registers when operating in Bus mode or in NVM for Fail Safe mode operation.

# 3.1 Single device led current intensity setting

Each channel can be set with a specific current level that is active during the ON phase of the duty cycle during PWM dimming. Such level can be set within the range from 1 mA to 15 mA with 8-bit granularity (for example, 256 possible levels).

#### 3.1.1 LED current intensity in Bus mode

Current intensity settings in Bus mode operation are mapped on registers addresses (ranging from 0x0A to 0x11) with channel allocation as outlined below.

Addr. 0x0A Addr. 0x10 Addr. 0x11 31 30 29 28 27 26 25 24 23 30 30 0 CURR\_SET\_CH3 CURR\_SET\_CH7 CURR\_SET\_CH11 CURR\_SET\_CH15 CURR\_SET\_CH19 CURR\_SET\_CH23 CURR\_SET\_CH27 CURR\_SET\_CH31 27 26 27 27 26 26 26 24 24 23 24 24 23 23 22 21 20 19 18 17 16 15 21 21 21 21 CURR\_SET\_CH2 18 17 0 18 0 18 18 17 18 0 18 0 18 17 15 15 15 15 15 15 13 12 11 12 CURR\_SET\_CHS 12 CURR\_SET\_CH9 12 12 12 12 12 CURR\_SET\_CH1 CURR\_SET\_CH13 11 10 10 10 9 CURR\_SET\_CHO CURR\_SET\_CH4 CURR\_SET\_CHS CURR\_SET\_CH12 CURR\_SET\_CH16 CURR\_SET\_CH20 CURR\_SET\_CH24 CURR\_SET\_CH28

Figure 21. Channel current setting in Bus mode - register mapping

#### 3.1.2 LED current intensity in Fail Safe mode

Current intensity for Fail Safe mode operation needs to be set within the internal NVM of the device, at rows from 1 up to 4, columns from 0 up to 7 (check the NVM fields layout).

UM2996 - Rev 1 page 19/124

# 3.2 Single device led pwm duty cycle setting

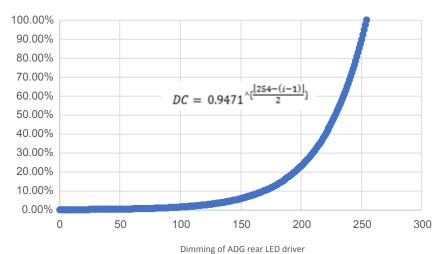

In L99LDLH32, each channel can be individually dimmed on an 8-bit exponential duty cycle to adjust LED brightness change to human eye light perception in a way that gets perceived as linear. The exponential law used to calculate the dimming steps is the following:

Figure 22. Duty cycle vs dimming step

Where "i",  $1 \le i \le 255$ ,  $\alpha \approx 0.9471$ , N = 254. For the step number "i" = 0, DC is set to "0". The function of duty cycle vs 8-bit PWM\_DUTY\_CHx setting is shown in the following graph. The duty cycle is linked to the tPWM\_ON\_OFF (reported in the DS) and the programmed PWM\_FREQ. The minimum duty cycle is clamped to 0.1% for the frequency range 200 Hz - 400 Hz. (for PWM\_FREQ>400 Hz, tPWM\_ON\_OFF is 2.5  $\mu$ s).

PWM frequency options are outlined below:

Table 4. PWM frequency range

|       | PWM_FREQ_DINx [from 2 to 0] |       |               |  |  |  |  |  |  |

|-------|-----------------------------|-------|---------------|--|--|--|--|--|--|

| bit 2 | bit 1                       | bit 0 | PWM_FREQ [Hz] |  |  |  |  |  |  |

| 0     | 0                           | 0     | 200           |  |  |  |  |  |  |

| 0     | 0                           | 1     | 300           |  |  |  |  |  |  |

| 0     | 1                           | 0     | 400           |  |  |  |  |  |  |

| 0     | 1                           | 1     | 500           |  |  |  |  |  |  |

| 1     | 0                           | 0     | 700           |  |  |  |  |  |  |

| 1     | 0                           | 1     | 1000          |  |  |  |  |  |  |

| 1     | 1                           | 0     | 1200          |  |  |  |  |  |  |

| 1     | 1                           | 1     | 1400          |  |  |  |  |  |  |

UM2996 - Rev 1 page 20/124

#### 3.2.1 Duty cycle setting in Bus mode

When operating in Bus mode, duty cycle can be set channel by channel individually through registers in the range 02h to 09h:

Addr. 0x01 Addr. 0x02 Addr. 0x08 Addr. 0x09 Addr. 0x07 0 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 0 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 PWM\_DUTY\_CH12 0 0 0 0

Figure 23. Channel duty cycle setting in Bus mode - register mapping

At register address 01h, PWM\_DUTY\_ALL0 field allows us to set a duty cycle multiplier for all channels belonging to the DIN0 group (internally coded as group 01). This allows simultaneous dimming for all channels belonging to the same group.

Aside from programmed duty cycle control through the device logic, it is possible to drive the PWM duty cycle through a square wave (0 to 3V domain) applied to the DIN pin of the device. This applies only to channels mapped to the DIN0 group (mapping to group 01, which can be set through the DIN\_MAP register) once the DIN0\_ENABLE (bit 18 at register 17h) is set.

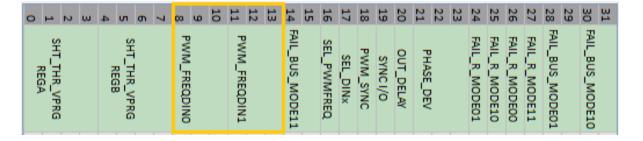

PWM frequency options outlined in the previous section are to be set at register address 15h (bits 8 to 13) when operating in Bus mode:

Figure 24. PWM frequency bits

UM2996 - Rev 1 page 21/124

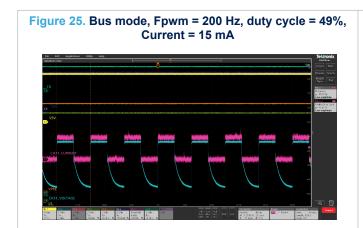

The figures below report some examples:

Figure 26. Bus mode, Fpwm = 700 Hz, duty cycle = 25%, Current = 15 mA

Figure 27. Bus mode, Fpwm = 700 Hz, duty cycle = 95%, Current = 15 mA

Figure 28. Bus mode, Fpwm = 1.4 kHz, duty cycle = 50%, Current = 15 mA, DIN\_EN = 1

The case in the last example shows a condition in which DIN\_EN is set in order to synchronize the leds PWM control with a 0.3 V square wave control signal applied to the DIN pin. Device control can be broken down in 3 windows:

- Initially DIN pin is low and the device operates PWM through the internal logic in accordance with the settings (Fpwm = 1.4 kHz, DC = 50%, current = 15 mA)

- Since DIN\_EN = 1, as soon as DIN raises and starts toggling it takes over the output control. This works as long as the low of the square wave imposed through DIN is shorter than 10 ms. If DIN is held low for more than 10 ms after a high to low transition the logic releases DIN control and give it back to the internal PWM engine.

#### 3.2.2 Duty cycle setting in Fail Safe

When operating in Fail Safe mode duty cycle settings need to be programmed in NVM before operation along with the PWM\_FS\_ALL\_EN0=1 bit setting in NVM. These DC percentages are global for all channels mapped to DIN0 group (to be selected at rows from 1 to 4 and columns 10 and 11 of NVM, for NVM fields layout check related annex). The two duty cycle values set in NVM (PWM\_DUTY\_ALL0, PWM\_DUTY\_ALL\_ALT0) can be selectively activated depending on whether the level of the PWM\_DC\_1/2 pin is low or high (0.3 V). Operation with programmed duty cycle values in Fail Safe mode require DIN0 pin to be high as enabler.

100% DC operation can be achieved equivalently by:

- · Programming maximum duty cycle (FFh) within the previously mentioned NVM cells after indications above

- with PWM\_FS\_ALL\_EN0=0 and DIN pin high for DIN\_MAP01 channels (for example, channels belonging to the DIN0 group)

- Setting FS OUT ENABLE=1 regardless of channel/DIN group

UM2996 - Rev 1 page 22/124

#### 3.2.3 Fail Safe dimming in provider and consumer configuration

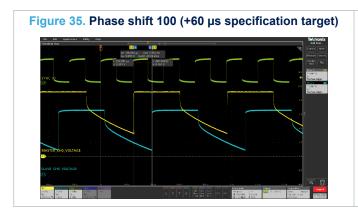

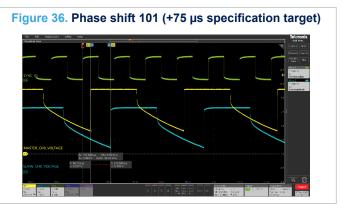

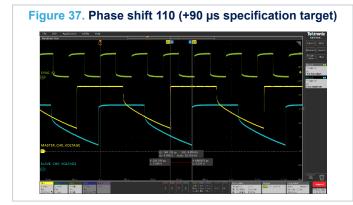

L99LDLH32 has a built-in mechanism to establish a phase shift relationship among several devices during PWM operation. For this purpose, one of the L99LDLH32 devices (the so called "Provider") is required to provide a common clock reference, through a scaled version of the 20 MHz oscillator (down to approximately 4.17 kHz) propagated to the SYNC\_IO pin ("Provider mode" is active when the NVM bit called SYNC I/O\_P/C, shorthand for provider and consumer setting, is set to zero. This is also the default value for newly deployed devices). Once the provider L99LDLH32 device is set, all other devices, subjected to the reference clock, are supposed to be connected to the SYNC\_I/O pin and initialized as consumers (through NVM SYNC I/O\_P/C=1). Each consumer device is supposed to set with the related PWM phase shift in NVM (PHASE\_DEV bits in NVM) according to the following options:

|       | PHASE_xDEV [from 2 to 0] |       |                      |  |  |  |  |  |  |

|-------|--------------------------|-------|----------------------|--|--|--|--|--|--|

| bit 2 | bit 1                    | bit 0 | PWM_PHASE_SHIFT [μs] |  |  |  |  |  |  |

| 0     | 0                        | 0     | 0                    |  |  |  |  |  |  |

| 0     | 0                        | 1     | 15                   |  |  |  |  |  |  |

| 0     | 1                        | 0     | 30                   |  |  |  |  |  |  |

| 0     | 1                        | 1     | 45                   |  |  |  |  |  |  |

| 1     | 0                        | 0     | 60                   |  |  |  |  |  |  |

| 1     | 0                        | 1     | 75                   |  |  |  |  |  |  |

| 1     | 1                        | 0     | 90                   |  |  |  |  |  |  |

| 1     | 1                        | 1     | 105                  |  |  |  |  |  |  |

Table 5. PWM phase shift (in consumer mode)

Note:

Each of the consumer devices, connected to the provider, is subject to a boot sequence after power up. At the end, the phase relation towards the provider is different from 0 despite PHASE\_DEV=0. Therefore, all other non-zero phase shift options are assumed to be relative to the default one after the startup. To have a known initial phase relation, the internal PWM counter can be reset by PWM\_SYNC bit on each device (otherwise, the initial phase shift between devices is not known as there are some differences between devices, such us V3V3 startup).

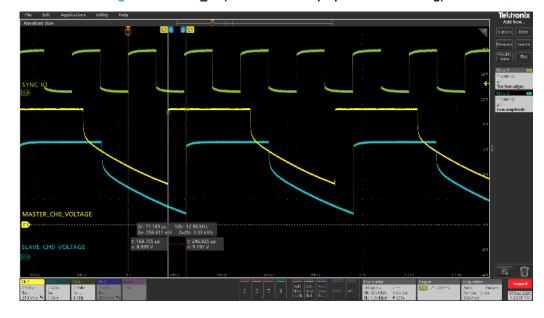

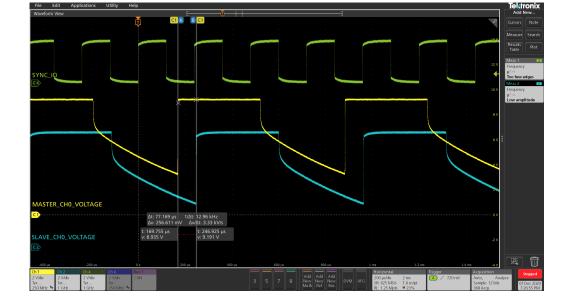

Example of Hardware setup:

- 1 board 2 devices active

- DEV1=Provider (ResponderID 4); SYNC I/O P/C=0 (as by default)

- DEV0=Consumer (ResponderID 0); SYNC I/O P/C=1 (in FTP)

- DEV0, DEV1 SYNC IO pins connected

- DEV1 PreregA=DEV0 PreregA=DEV0=VS

- VS=12 V

- CH0, Dev0 and CH0, DEV1 running at 200 Hz, DC=49% and Current=15 mA for shift comparison

After SYNC I/O\_P/C connection and apply phase shift options to the consumer device and observe output waveform shift increments according to specification.

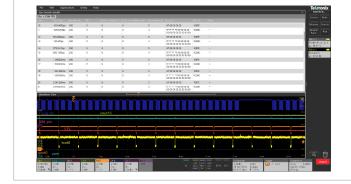

Below starting point with SYNC\_IO frequency provided by provider device and with both provider and consumer running PWM at 200 Hz and 0 us phase shift setting (intrinsic phase shift after devices switch on):

UM2996 - Rev 1 page 23/124

Figure 29. SYNC\_IO (at 200 Hz and 0 µs phase shift setting)

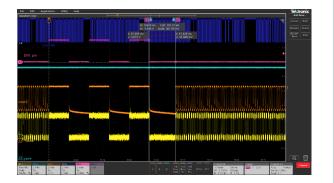

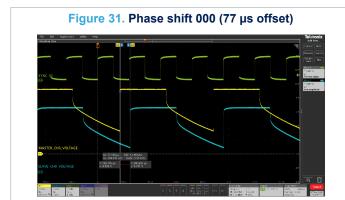

Here below the focus on default time offset (77  $\mu$ s) between provider and consumer device at consumer phase shift setting 000:

Figure 30. Provider and consumer device (offset 77 μs)

UM2996 - Rev 1 page 24/124

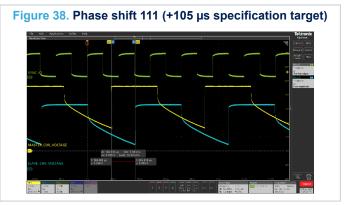

Figure 32. Phase shift 001 (+15 µs specification target)

Figure 33. Phase shift 010 (+30 μs specification target)

Figure 34. Phase shift 011 (+45 µs specification target)

UM2996 - Rev 1 page 25/124

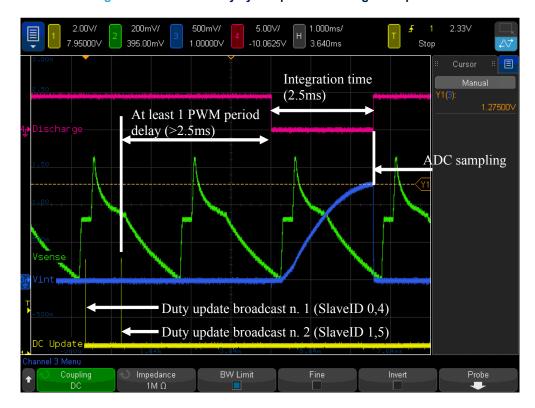

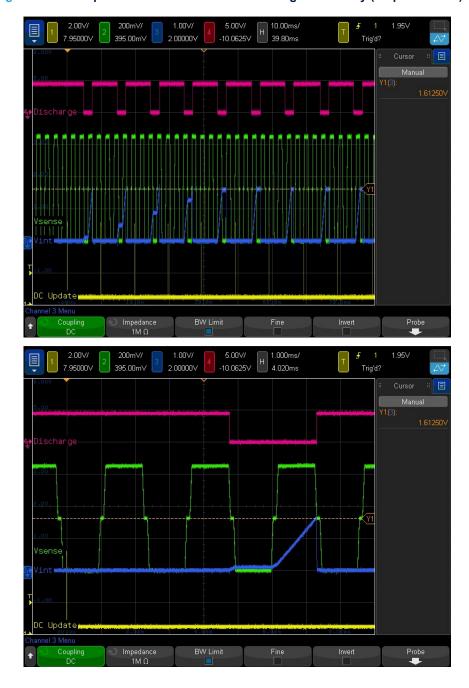

## 3.3 Broadcast setting of current level and duty cycle

In addition to the previously described current intensity and duty cycle setting, performed channel by channel on a single device (maximum of four simultaneous channel updates with a single frame). The L99LDLH32 Bus mode allows broadcast messages to update these parameters on multiple devices simultaneously (up to 16 channels per device and 4 devices in one shot). This feature requires every device to get preliminarily initialized with two parameters:

- A chain identifier, playing essentially the role of an address related to a group of up to 4 devices, to be later

addressed by a single broadcast frame, for current intensity or duty cycle update. Resorting to the broader

context of communication network theory for an analogy, this matches with the multicasting concept.

- A position, specific to each of the devices belonging to the same *Chain identifier*, and can take up to 4 possible values (from 0 to 3). This provides each single device with the pointer to the location in which to fetch the current and duty cycle update data (16 bytes) within the received broadcast frame.

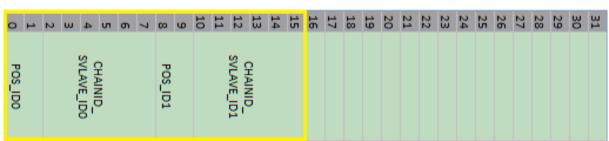

Initialization of these parameters is done through an on-purpose message, which entails a device *ResponderID"*, *Chain ID and position*. As an atomic unit required for a proper management of broadcast messages that is sent by the CAN FD Light commander, during device operation. Once the broadcast initialization message is correctly received by a given device, chain ID and position initialization data show up in register 1Ah (from bits 0 to 15):

Figure 39. Register 1 ah

#### Warning:

In the context of initialization for broadcast messages each device has a twofold ResponderID. The (main) ResponderID gets preassigned through the lower 9 bits of row 0 in NVM (check related annex for NVM fields content) and is valid to address all the CAN-FD light unicast communication frames, as well as broadcast frames addressing current and duty cycle update of the first 16 (from 0 to 15) channels of a given device. The secondary ResponderID is the main ResponderID incremented by one (ResponderID + 1, this doesn't need preliminary setting, it is implicitly adopted by device internal implementation) and will be used for broadcast frames intended to update current/duty cycle of channels with index from 16 to 31.

Figure 40. Broadcast init message

After this initialization scheme, at any time during device operation the CAN FD Light commander can send a broadcast message with the given chain identifier to address the related devices and the updates for the current and the duty cycle (specified within the 5<sup>th</sup> bit of the frame as shown below). The message payload is decoded by all devices matching the chain identifier and data are extracted by each device according to the position that was preassigned through the broadcast initialization message.

Figure 41. Broadcast frame structure

UM2996 - Rev 1 page 26/124

#### **Examples**

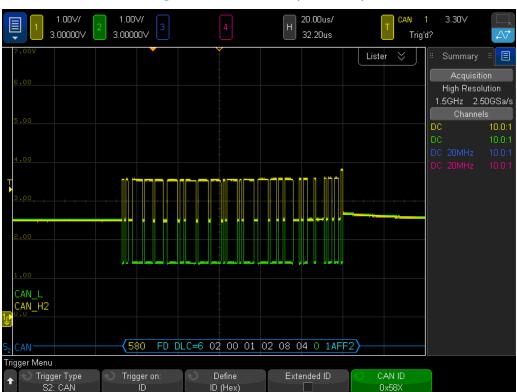

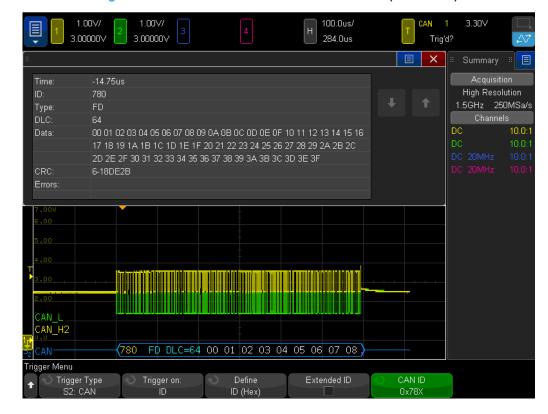

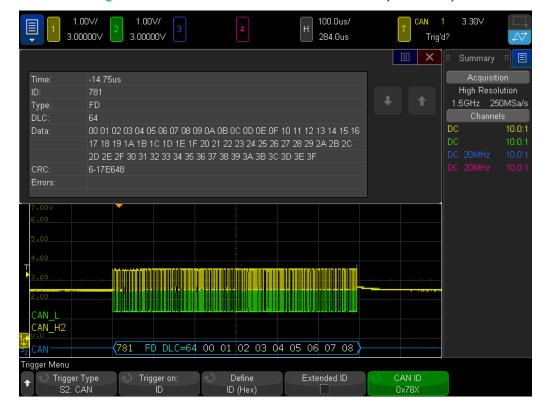

Test case 1. Two devices with ResponderID=0 and 4 respectively. Step by step the procedure below:

- Power-up

- · Go to Bus mode

- Broadcast init with DLC=6; [(ChainID=1, Pos=0, ResponderID=1); (ChainID=1, Pos=1, ResponderID=4)]

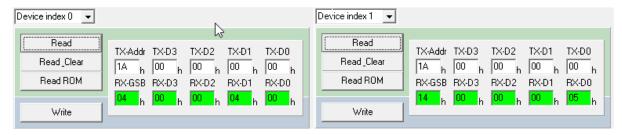

- Device 0: status 1Ah readback

- Device 1: status 1Ah readback

- Broadcast PWM data sent (ChainID=0)

- Data acceptance verification

- Broadcast PWM data sent (ChainID=1)

- · Data acceptance verification

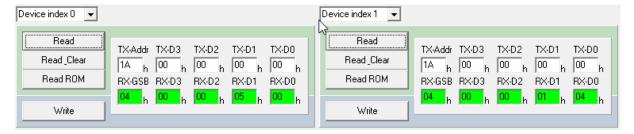

Figure 42. Broadcast init (test case 1)

Figure 43. Broadcast init verification (test case 1)

UM2996 - Rev 1 page 27/124

Figure 44. Broadcast PWM data send to ChainID=0 (test case 1)

Figure 45. Data acceptance verification (device 0 left, device 1 right) - ChainID=0 (test case 1)

| Control registers - Re                               | eadb | ack |    | Control registers - Readback |                                                                                      |

|------------------------------------------------------|------|-----|----|------------------------------|--------------------------------------------------------------------------------------|

| Addr/name                                            | D3   | D2  | D1 | D0                           | Addr/name D3 D2 D1 D0                                                                |

| 01h-Control01:<br>02h-Control02:                     | 03   | 02  | 01 | 00                           | 01h-Control01: 00 00 00 00<br>02h-Control02: 00 00 00 00                             |

| 03h-Control03:<br> 04h-Control04:<br> 05h-Control05: | 0B   | ΟĀ  | 09 | 08                           | 03h-Control03: 00 00 00 00   04h-Control04: 00 00 00 00   05h-Control05: 00 00 00 00 |

| 06h-Control06:<br>07h-Control07:                     | 00   | 00  | 00 |                              | 06h-Control06: 03 02 01 00<br>07h-Control07: 07 06 05 04                             |

| 08h-Control08:<br>09h-Control09:                     | 00   | 00  | 00 |                              | 08h-Control08: 0B 0A 09 08<br>09h-Control09: 0F 0E 0D 0C                             |

UM2996 - Rev 1 page 28/124

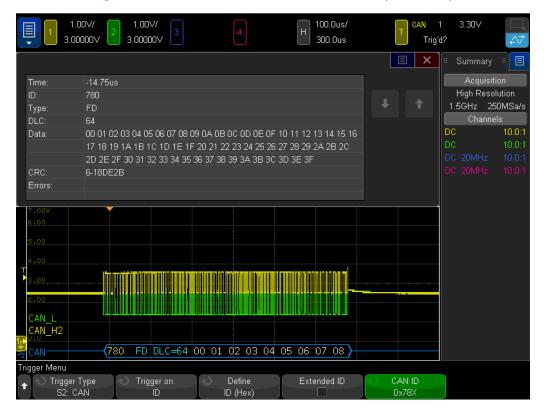

Figure 46. Broadcast PWM data send to ChainID=1 (test case 1)

Figure 47. Data acceptance verification (device 0 left, device 1 right) - ChainID=1 (test case 1)

| Control registers - Re                                                                                                                                         | eadb                                   | ack                                    |                                        |                                  | Control registers - Readback                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr/name                                                                                                                                                      | D3                                     | D2                                     | D1                                     | D0                               | Addr/name D3 D2 D1 D0                                                                                                                                                                                                                                 |

| 01h-Control01:<br>02h-Control02:<br>03h-Control03:<br>04h-Control04:<br>05h-Control05:<br>06h-Control06:<br>07h-Control07:<br>08h-Control08:<br>09h-Control09: | 03<br>07<br>0B<br>0F<br>03<br>07<br>0B | 02<br>06<br>0A<br>0E<br>02<br>06<br>0A | 01<br>05<br>09<br>0D<br>01<br>05<br>09 | 00<br>04<br>08<br>0C<br>00<br>04 | 01h-Control01: 00 00 00 00 00 02h-Control02: 13 12 11 10 03h-Control03: 17 16 15 14 04h-Control04: 1B 1A 19 18 05h-Control05: 1F 1E 1D 1C 06h-Control06: 03 02 01 00 07h-Control07: 07 06 05 04 08h-Control08: 0B 0A 09 08 09h-Control09: 0F 0E 0D 0C |

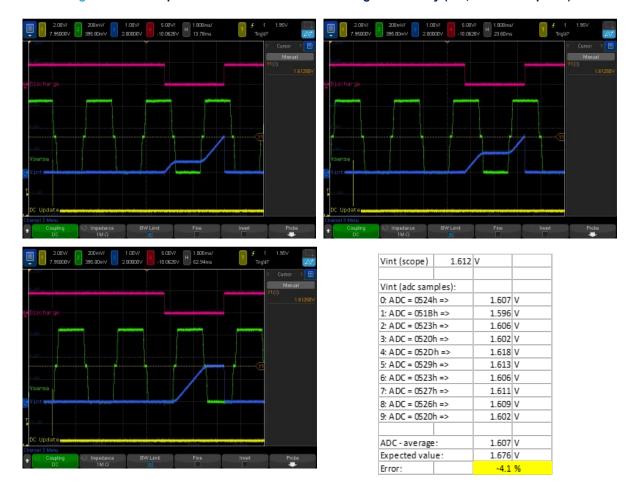

Test case 2. Step by step the procedure below:

- Power-up

- Go to Bus mode

- Broadcast init with DLC=6; [(ChainID=0, Pos=0, ResponderID=0); (ChainID=1,Pos=0, ResponderID=4)]

- Broadcast init with DLC=6; [(ChainID=1, Pos=1, ResponderID=1); (ChainID=0,Pos=1,ResponderID=5)]

- Device 0: status 1Ah readback

- Device 1: status 1Ah readback

- Broadcast PWM data sent (ChainID=0)

- · Data acceptance verification

- Broadcast PWM data sent (ChainID=1)

- Data acceptance verification

UM2996 - Rev 1 page 29/124

Figure 48. Broadcast inits (test case 2)

Figure 49. Broadcast init verification (test case 2)

Figure 50. Broadcast PWM data send to ChainID=0 (test case 2)

UM2996 - Rev 1 page 30/124

Figure 51. Data acceptance verification (device 0 left, device 1 right) - ChainID=0 (test case 2)

Figure 52. Broadcast PWM data send to ChainID=1 (test case 2)

UM2996 - Rev 1 page 31/124

Figure 53. Data acceptance verification (device 0 left, device 1 right) - ChainID=1 (test case 2)

| Control registers - Re                                                                                                                                                                                                                                   | adba                                                                 | ack                                                                        |                                                                      | Control registers - Readback                                         |                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr/name                                                                                                                                                                                                                                                | D3                                                                   | D2                                                                         | D1                                                                   | D0                                                                   | Addr/name D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                  |

| 01h-Control01:<br>02h-Control02:<br>03h-Control03:<br>04h-Control04:<br>05h-Control06:<br>06h-Control06:<br>07h-Control08:<br>09h-Control09:<br>04h-Control10:<br>0Bh-Control11:<br>0Ch-Control12:<br>0Dh-Control13:<br>0Eh-Control14:<br>0Fh-Control15: | 00<br>03<br>07<br>0B<br>0F<br>13<br>17<br>1B<br>1F<br>00<br>00<br>00 | 00<br>02<br>06<br>0A<br>0E<br>12<br>16<br>1A<br>1E<br>00<br>00<br>00<br>00 | 00<br>01<br>05<br>09<br>0D<br>11<br>15<br>19<br>10<br>00<br>00<br>00 | 00<br>00<br>04<br>08<br>0C<br>10<br>14<br>18<br>1C<br>00<br>00<br>00 | O1h-ControlO1: 00 00 00 00 00 02h-ControlO2: 03 02 01 00 03h-ControlO3: 07 06 05 04 04h-ControlO4: 0B 0A 09 08 05h-ControlO5: 0F 0E 0D 0C 06h-ControlO6: 13 12 11 10 07h-ControlO7: 17 16 15 14 08h-ControlO8: 1B 1A 19 18 09h-ControlO9: 1F 1E 1D 1C 0Ah-ControlO9: 1F 1E 1D 1C 0Ah-ControlO9: 00 00 00 00 00 00 00 00 00 00 00 00 00 |

| 10h-Control16:<br> 11h-Control17:                                                                                                                                                                                                                        | 00<br>00                                                             | 00<br>00                                                                   | 00<br>00                                                             | 00<br>00                                                             | 10h-Control16: 00 00 00 00<br> 11h-Control17: 00 00 00 00                                                                                                                                                                                                                                                                              |

Figure 54. Broadcast current data send to ChainID=0 (test case 2)

UM2996 - Rev 1 page 32/124

Figure 55. Data (current) acceptance verification (device 0 left, device 1 right) - ChainID=0 (test case 2)

| Control registers - Re                                                                                                                                                                                                                                   | eadback                                                                                                           |                                                                                                                                  | Control registers - Readback                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr/name                                                                                                                                                                                                                                                | D3 D3                                                                                                             | 2 D1                                                                                                                             | D0                                                                         | Addr/name D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 01h-Control01:<br>02h-Control02:<br>03h-Control03:<br>04h-Control04:<br>05h-Control05:<br>06h-Control06:<br>07h-Control08:<br>09h-Control09:<br>04h-Control10:<br>0Bh-Control11:<br>0Ch-Control12:<br>0Dh-Control13:<br>0Eh-Control14:<br>0Fh-Control15: | 00 00<br>03 00<br>07 00<br>08 07<br>0F 01<br>13 12<br>17 10<br>18 17<br>1F 11<br>03 00<br>07 00<br>08 07<br>00 00 | 01<br>05<br>09<br>00<br>00<br>01<br>11<br>15<br>15<br>10<br>10<br>10<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00 | 00<br>00<br>04<br>08<br>0C<br>10<br>14<br>18<br>1C<br>00<br>04<br>08<br>0C | O1h-Control01: 00 00 00 00 00 02h-Control02: 03 02 01 00 03h-Control03: 07 06 05 04 04h-Control04: 0B 0A 09 08 05h-Control05: 0F 0E 0D 0C 06h-Control06: 13 12 11 10 07h-Control07: 17 16 15 14 08h-Control08: 1B 1A 19 18 09h-Control09: 1F 1E 1D 1C 0Ah-Control109: 1F 1E 1D 1C 0Ah-Control10: 00 00 00 00 0Bh-Control11: 00 00 00 00 00 0Ch-Control12: 00 00 00 00 00 0Ch-Control13: 00 00 00 00 0Eh-Control14: 13 12 11 10 0Fh-Control15: 17 16 15 14 |

| 10h-Control16:<br> 11h-Control17:                                                                                                                                                                                                                        | 00 00                                                                                                             |                                                                                                                                  | 00<br>00                                                                   | 10h-Control16: 1B 1A 19 18<br> 11h-Control17: 1F 1E 1D 1C                                                                                                                                                                                                                                                                                                                                                                                                 |

Figure 56. Broadcast current data send to ChainID=1 (test case 2)

UM2996 - Rev 1 page 33/124

Figure 57. Data (current) acceptance verification (device 0 left, device 1 right) - ChainID=1 (test case 2)

| Control registers - Re                                                                                                                                                                             | adba                                                           | ack                                                |                                                                | Control registers - Readback                                   |                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr/name                                                                                                                                                                                          | D3                                                             | D2                                                 | D1                                                             | D0                                                             | Addr/name D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                  |

| 01h-Control01:<br>02h-Control02:<br>03h-Control03:<br>04h-Control04:<br>05h-Control06:<br>06h-Control06:<br>07h-Control07:<br>08h-Control08:<br>09h-Control09:<br>04h-Control10:<br>0Bh-Control10: | 00<br>03<br>07<br>0B<br>0F<br>13<br>17<br>1B<br>1F<br>03<br>07 | 00<br>02<br>06<br>0E<br>12<br>16<br>1E<br>06<br>0A | 00<br>01<br>05<br>09<br>0D<br>11<br>15<br>19<br>1D<br>01<br>05 | 00<br>00<br>04<br>08<br>0C<br>10<br>14<br>18<br>1C<br>00<br>04 | 01h-Control01: 00 00 00 00 00 02h-Control02: 03 02 01 00 03h-Control03: 07 06 05 04 04h-Control04: 0B 0A 09 08 05h-Control05: 0F 0E 0D 0C 06h-Control06: 13 12 11 10 07h-Control07: 17 16 15 14 08h-Control08: 1B 1A 19 18 09h-Control09: 1F 1E 1D 1C 0Ah-Control10: 03 02 01 00 0Bh-Control11: 07 06 05 04 0Ch-Control12: 0B 0A 09 08 |

| ODh-Control13:<br>  OEh-Control14:<br>  OFh-Control15:<br>  10h-Control16:<br>  11h-Control17:                                                                                                     | 0F<br>13<br>17<br>1B<br>1F                                     | 0E<br>12<br>16<br>1A<br>1E                         | 0D<br>11<br>15<br>19                                           | 0C<br>10<br>14<br>18<br>1C                                     | ODh-Control13: OF OE OD OC   OEh-Control14: 13 12 11 10   OFh-Control15: 17 16 15 14   10h-Control16: 1B 1A 19 18   11h-Control17: 1F 1E 1D 1C                                                                                                                                                                                         |

## 3.4 Bus load management

An L99LDLH32 device operating in Bus mode is subjected to CAN FD Light frames containing commands as well as requests for device status read. Usually, the bus is a resource that gets shared among more devices; therefore, appropriate planning needs to be done upfront to achieve the proper tradeoff between bus load, frequency of commands, and frequency of status read requested by the CAN FD Light commander (MCU) to address application specifications. Constraints on the latter parameters can vary among applications and depend mostly on the overall set of resources present in the system as well as safety requirements. An example of bus allocation is outlined both for ASIL and QM applications below:

- Task schedule Bus mode operation 256 OLED pixel (8 x L99LDLH32 connected on the bus)

- FTTI 400 ms

- Duty cycle updated every 10 ms

- Watchdog timeout 100 ms

- Watchdog refresh 40 ms

- Diagnostic read back period 80 ms

- FuSa register readback period 200 ms

- PWM read back

- Chain ID read back

Once the device is woken up, broadcast initialization, current level settings are fixed and all preliminary consistency checks for safety are performed (if that is required by the application targets). The device can be sent in Bus mode and enter the operating loop with exchanges of CAN FD Light messages as outlined in the next picture (under the assumption of average bit stuffing overhead):

UM2996 - Rev 1 page 34/124

Figure 58. Application scenario 1

## **ASIL**

| Time [ms] Frame Type | Frame Length | Comment                                        |

|----------------------|--------------|------------------------------------------------|

| 0 Broadcast n.1      | 0,63 ms      | Duty cycle update on Device 0.0, 1.0, 2.0, 3.0 |

| 0,63 Broadcast n.2   | 0,63 ms      | Duty cycle update on Device 0.1, 1.1, 2.1, 3.1 |

| 1,26 Broadcast n.3   | 0,63 ms      | Duty cycle update on Device 4.0, 5.0, 6.0, 7.0 |

| 1,89 Broadcast n.4   | 0,63 ms      | Duty cycle update on Device 4.1, 5.1, 6.1, 7.1 |

| 2,52 Burst read m.   | 0,11 ms      | Output Status reading - Device x               |

| 2,62 Burst read s.   | 0,20 ms      |                                                |

| 2,82 Burst read m.   | 0,11 ms      | Status reading - Device x                      |

| 2,93 Burst read s.   | 0,20 ms      |                                                |

| 3,13 WD trig m.      | 0,11 ms      | WD update Device x                             |

| 3,24 WD trig s.      | 0,07 ms      |                                                |

| 3,31 Sync frame      | 0,06 ms      |                                                |

| 3,37 Single Read M   | 0,11 ms      | Safety frame 1                                 |

| 3,48 Single Read S   | 0,11 ms      |                                                |

| 3,58 Single Read M   | 0,11 ms      | Safety frame 2                                 |

| 3,69 Single Read S   | 0,11 ms      |                                                |

| 3,79 Sync frame      | 0,06 ms      |                                                |

| 3,85 Single Read M   | 0,11 ms      | Safety frame 3                                 |

| 3,96 Single Read S   | 0,11 ms      |                                                |

| 4,07 Single Read M   | 0,11 ms      | Safety frame 4                                 |

| 4,17 Single Read S   | 0,11 ms      |                                                |

| 4,28 Sync frame      | 0,06 ms      |                                                |

| 4,34 WD trig m.      | 0,11 ms      | WD update Device y                             |

| 4,44 WD trig s.      | 0,07 ms      |                                                |

| 4,51 Sync frame      | 0,06 ms      |                                                |

| 4,58 Single Clear M  | 0,11 ms      | Status Clear Slot device x                     |

| 4,68 Single Clear S  | 0,11 ms      |                                                |

| 4,79 Sync frame      | 0,06 ms      |                                                |

| 4,85                 |              |                                                |

The recommended safety check frames are:

For ASIL applications only

UM2996 - Rev 1 page 35/124

Figure 59. Safety check frames

Read back PWM Setting Device x 0-3

Read back PWM Setting Device x 4-7

Read back PWM Setting Device x 8-11

Read back PWM Setting Device x 12-15

Read back PWM Setting Device x 16-19

Read back PWM Setting Device x 20-23

Read back PWM Setting Device x 24-27

Read back PWM Setting Device x 28-31

Read back PWM\_DUTY\_ALL Device x

Considering the task schedule period is 10 ms, the total bus load in this application example is 48.5%. In case of QM applications, the busload can be reduced as safety check frames can be eliminated:

Figure 60. QM

|           |                | (            | QM                                             |

|-----------|----------------|--------------|------------------------------------------------|

| Time [ms] | Frame Type     | Frame Length | Comment                                        |

| 0         | Broadcast n.1  | 0,63 ms      | Duty cycle update on Device 0.0, 1.0, 2.0, 3.0 |

| 0,63      | Broadcast n.2  | 0,63 ms      | Duty cycle update on Device 0.1, 1.1, 2.1, 3.1 |

| 1,26      | Broadcast n.3  | 0,63 ms      | Duty cycle update on Device 4.0, 5.0, 6.0, 7.0 |

| 1,89      | Broadcast n.4  | 0,63 ms      | Duty cycle update on Device 4.1, 5.1, 6.1, 7.1 |

| 2,52      | Burst read m.  | 0,11 ms      | Output Status reading - Device x               |

| 2,62      | Burst read s.  | 0,20 ms      |                                                |

| 2,82      | Burst read m.  | 0,11 ms      | Status reading - Device x                      |

| 2,93      | Burst read s.  | 0,20 ms      |                                                |

| 3,13      | WD trig m.     | 0,11 ms      | WD update Device x                             |

| 3,24      | WD trig s.     | 0,07 ms      |                                                |

| 3,31      | Sync frame     | 0,06 ms      |                                                |

| 3,37      | WD trig m.     | 0,11 ms      | WD update Device y                             |

| 3,48      | WD trig s.     | 0,07 ms      |                                                |

| 3,55      | Sync frame     | 0,06 ms      |                                                |

| 3,61      | Single Clear M | 0,11 ms      | Status Clear Slot device x                     |

| 3,71      | Single Clear S | 0,11 ms      |                                                |

| 3,82      | Sync frame     | 0,06 ms      |                                                |

| 3,88      |                |              |                                                |

UM2996 - Rev 1 page 36/124

The busload is reduced to 38.8%.

The following table provides a summary overview for theoretical busload for different use cases.

Table 6. Theoretical busload

| Busload | Devices on the bus |     |  |  |  |

|---------|--------------------|-----|--|--|--|

| Busivau | 5                  | 8   |  |  |  |

| ASIL    | 30%                | 48% |  |  |  |

| QM      | 25%                | 39% |  |  |  |

UM2996 - Rev 1 page 37/124

# 4 Diagnostic and protections

# 4.1 Diagnostic overview

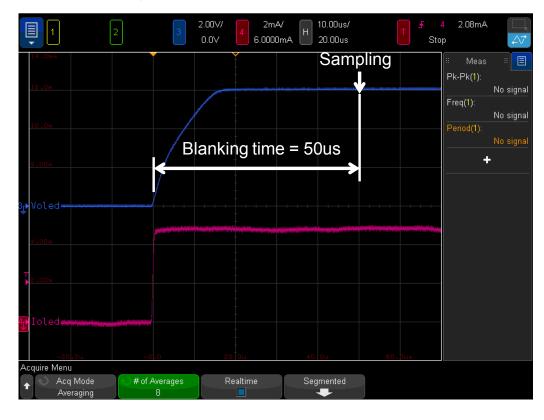

The L99LDLH32 provides the detailed diagnostic information related to output channels and other internal functions. A key part of the diagnostic subsystem is an integrated 8-bit ADC that measures the voltage at all outputs (in PWM on-state),  $V_S$ ,  $V_{PRE\_REG}$ , internal  $T_J$ , and external NTC sensor. These ADC results are then processed by a digital engine that evaluates and controls various fault conditions. The following diagnostic information is available for the user:

### Complete overview of available diagnostic information:

- 8-bit ADC values (in registers 1Fh 26h, 2Ch and 2Dh):

- VLED ON CHx: output on-state voltage on channel x

- VLEDON LOW: highest on-state voltage of an active channel

- VS: VS pin voltage

- VPRE\_REG: VPRE\_REG pin voltage

- Tj: chip temperature

- NTC ADC: NTC pin voltage

- Output channel related diagnostic flags (in registers 27h 2Bh):

- VLEDON RFR CHx: VLEDON ADC refresh status bit of channel x

- OUT\_STATUS\_CHx: readback of channel x state

- SHT CHx: short circuit status bit of channel x

- OL CHx: open load status bit of channel x

- OUT\_SHT\_GND\_CHx: short to GND status bit of channel x

- Output channel related diagnostic flags logic OR of all channels (register 2Eh):

- OR\_OUT\_SHT\_GND: logic OR of all OUT\_SHT\_GND\_CHx bits

- OR\_OUT\_STATUS: logic OR of all OUT\_STATUS\_CHx bits

- OR\_SHT: logic OR of all SHT\_CHx bits

- OR\_OL: logic OR of all OL\_CHx bits

- Device related diagnostic flags (in register address 2Eh):

- PG NOT VPRE REG: PG threshold is not reached

- TSD: thermal shutdown

- TW: thermal warning

- NTC\_DER\_ACT: NTC derating active

- NTC FAULT: NTC fault

- DIN STATUS: readback of DIN pin

- WD STATUS: WD counter status

- VS\_UV: VS undervoltage

- WD\_FAIL: WD timeout indication

- DAC\_RES\_FAULT: external DAC Reference Resistor Fault:

- VREF\_PRE\_REG\_MAX: reference voltage is set to maximum level

UM2996 - Rev 1 page 38/124

- Diagnostic flags in global sStatus byte:

- GSBN: a NOR combination of the remaining bits of GSB

- RSTB: device reset indication

- FE2: functional error 2 → OR combination of:

- SHT\_CHx

- OL CHx

- OUT\_SHT\_GND\_CHx

- FE1: functional error 1: = TSD

- DE: device error 1 → OR combination of:

- NTC\_FAULT

- PG NOT VPRE REG

- VS\_UV

- DAC\_RES\_FAULT

- GW: Global warning → OR combination of:

- TW

- NTC DER ACT

- FS: Fail Safe and standalone mode indication

# 4.2 Diagnostic feedback via CAN FD

All above listed diagnostic information can be read via CAN FD interface. There are several types of diagnostic commands described in this chapter.

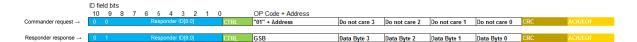

### 4.2.1 Global status byte (GSB)

The global status byte (GSB) information is sent in each device response frame in first data byte 0, except the burst read command. This means that GSB value is obtained after any unicast access (for example after the watchdog refresh command). The GSB information can be fetched also by sending a unicast frame without data. Device responds with frame with one data byte.

Figure 61. GSB request command

|                      | ID field bits          |  |  |  |  |   |   |      |     |         |         |  |  |  |  |

|----------------------|------------------------|--|--|--|--|---|---|------|-----|---------|---------|--|--|--|--|

|                      | 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  | 1 | 0 |      |     |         |         |  |  |  |  |

| Commander request => | 0 0 Responder ID[8:0]  |  |  |  |  |   |   | CTRL | CRC | ACK/EOF |         |  |  |  |  |

|                      |                        |  |  |  |  |   |   |      |     |         |         |  |  |  |  |

| Responder answer =>  | 0 1 Responder ID[8:0]  |  |  |  |  |   |   | CTRL | GSB | CRC     | ACK/EOF |  |  |  |  |

UM2996 - Rev 1 page 39/124

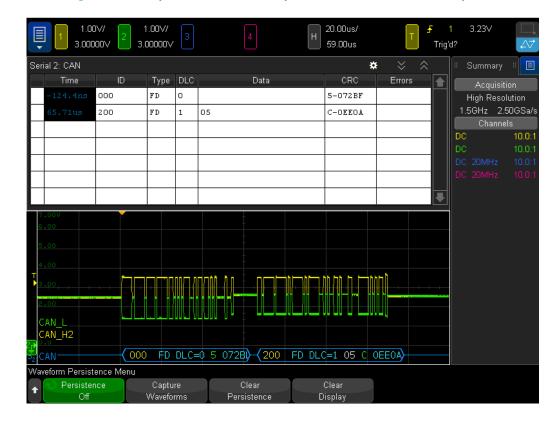

Figure 62. Example of unicast GSB request command with device response

The above screenshot shows the GSB unicast request to the device with ResponderID=000h. Device responds with GSB=05h, indicating that FS and DE bits are set.

Figure 63. Single RAM register write command with GSB response

UM2996 - Rev 1 page 40/124

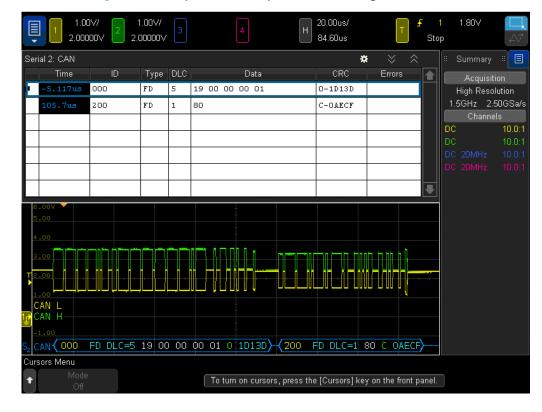

Figure 64. Example of GSB response to watchdog refresh frame

The above screenshot shows the device response to watchdog refresh command. In this case the GSB=80h which means no errors and no warnings are set. Same response is sent to any other single register write command as shown on Figure 63. Single RAM register write command with GSB response.

# 4.2.2 Single RAM register read

This command (OP Code "01") is used to read diagnostic (or other) information from the single register on the specific address. Device responds with 5 data bytes - GSB + 4 byte register content.

Figure 65. Single RAM register read command

UM2996 - Rev 1 page 41/124

Figure 66. Example of single read command

This command can be used for reading any register in the RAM space. However, there are 4 specific registers dedicated for "burst read mode". In case of accessing these addresses, the device responds in burst read mode (see next paragraph Section 4.2.3).

#### 4.2.3 Burst read mode

A burst read mode is available when a single RAM Read request (OP Code "01") is executed on a specific RAM addresses eligible to burst read mode (addresses 1Fh, 23h, 27h, and 2Ch). Then the responder answers with 16 bytes of data. The 4 least significant bytes correspond to the data stored in the register addressed by the commander request. The 12 following bytes correspond to the data stored on the next 3 consecutive addresses. Global status byte is not provided in this case.

Figure 67. Read request on burst read mode RAM register

UM2996 - Rev 1 page 42/124

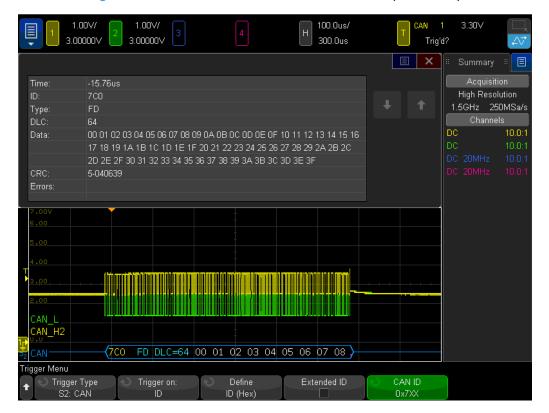

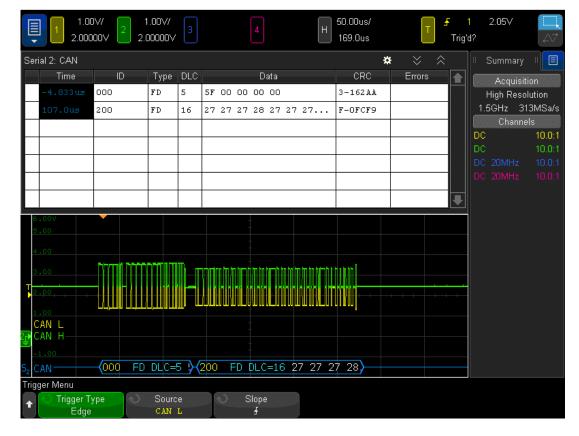

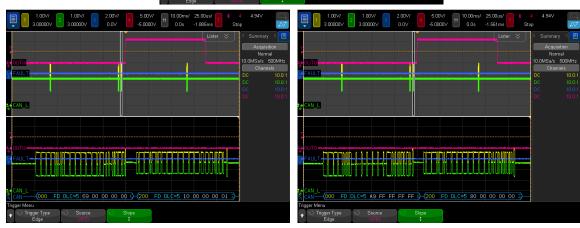

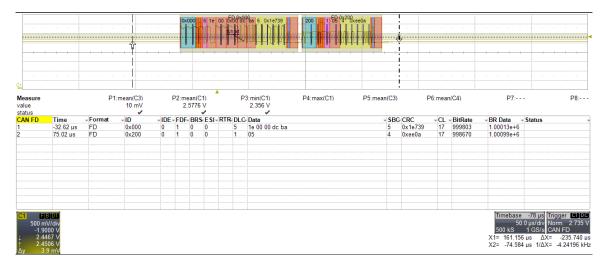

Figure 68. Example burst read mode access on register 1Fh

The above screenshot shows a device response to read command executed on address 1Fh, dedicated for burst mode. As seen in the register map, there is VLEDON ADC information for channels 0 to 15. In this example, the device responds with 16 data bytes (byte 0 = VLEDON\_CH0, byte 1 = VLED\_CH1 ...) with values of 27h ( $\rightarrow$  ~6.1V) or 28h ( $\rightarrow$  ~6.3V).

### 4.2.4 Single RAM register clear

This command (OP code "10") is used to clear diagnostic flags at a specific address. The command is applicable on addresses eligible for clearing (28h, 29h, 2Ah, and 2Eh). The flags to be cleared are selected using a mask defined by data byte 0-3. The device responds with 5 data bytes (GSB + 4 byte register content) immediately after the clear command is executed, therefore providing the already cleared register content. In case of a permanent fault, the corresponding flags are set again after a new fault validation time.

Figure 69. Single RAM register clear command

In the example below there is a sequence of read and clear command on register 29h (open load flags) sent during a permanent open load condition on CH0.

UM2996 - Rev 1 page 43/124

Figure 70. Example of read and clear command sequence on register 29h

The example in Figure 70 shows a permanent open load condition on ch.0. The response to a read command (with a timestamp of -1.985 ms) shows an open load on ch.0. The following clear command removes the fault so the ch.0 is reactivated. Since the open load condition is permanent, the channel is latched off again after the fault validation time of ~35 ms (8 PWM periods filter time).

# 4.3 Diagnostic feedback via Fault pin

### 4.3.1 Diagnostic capability

Diagnostic feedback is also available on the FAULT pin. This is an open drain pin associated to channels mapped to the DIN group "01" (channels with the DIN\_MAP\_CHx bit set to "1"). It is active low and requires an external pull-up. It can indicate the following faults:

- Device related faults (always propagated to FAULT pin):

- TSD thermal shutdown

- VS\_UV VS undervoltage

- DAC\_RES\_FAULT: external DAC reference resistor fault

- Output channel related faults (propagation to FAULT pin configurable)

- OL: open load on channels associated in DIN group (propagation enable by OL\_EN bit)

- SHT: short circuit on channels associated to DIN group (propagation enable by SHT\_EN bit)

- OUT\_SHT\_GND: Short to GND on channels associated to DIN group (propagation enable by SHT\_EN bit)

UM2996 - Rev 1 page 44/124

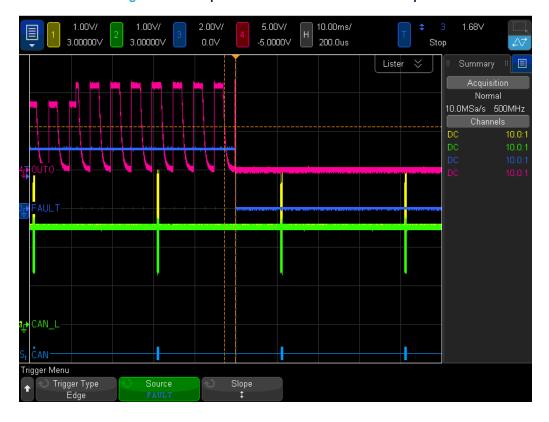

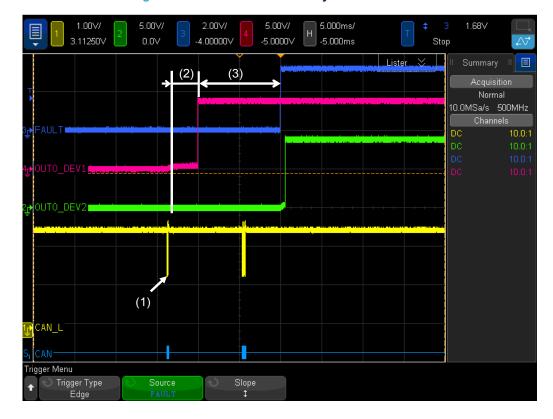

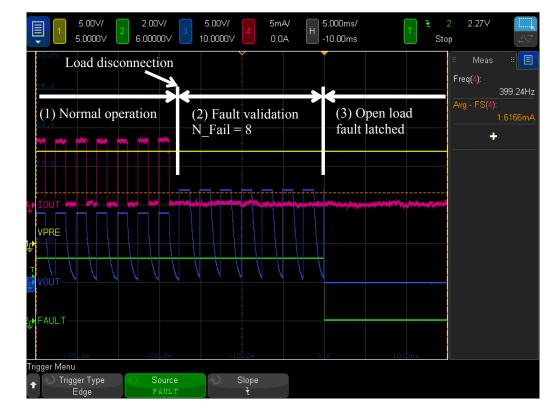

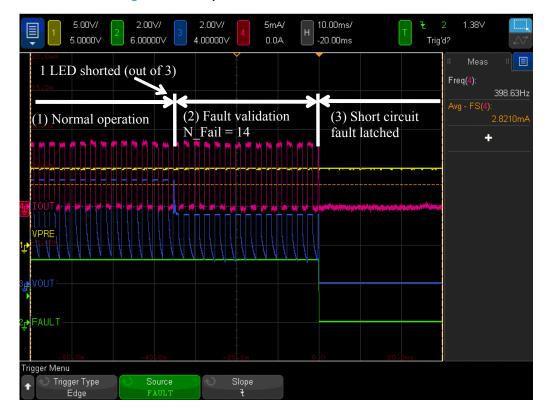

The example below shows an OL fault condition on OUT0. The channel is in PWM mode (200 Hz/50% duty cycle), mapped in the DIN group using DIN\_MAP\_CH0=1. The OL fault propagation to FAULT pin is enabled using OL\_EN=1. Device is configured in Bus mode:

Figure 71. Example of OL fault indication on FAULT pin

The OL event is visible on output voltage 0 signal (purple plot) as a sudden step to 12 V. Then, after the fault validation filter time, the output 0 is latched off and the FAULT pin (blue plot) is pulled low. Green and yellow plots are CAN L and CAN H signals (watchdog refresh activity every 30 ms visible in this case).

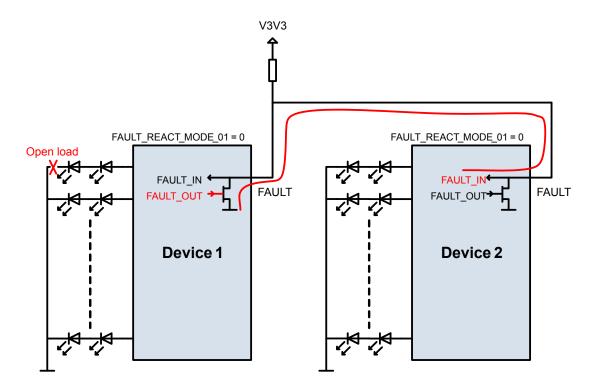

## 4.3.2 FAULT Bus capability

The fault pin has a bidirectional functionality. Several fault pins of several devices can be connected to a common fault bus associated to a particular light function. This allows an automatic deactivation of the complete light function in case of fault on the single O/LED string only, according to the selected fault reaction mode. The fault reaction mode setting is available in configuration register 1 (address 15h) and the setting is individual per function group:

Table 7. Fault reaction mode setting for function group "00" (non-mapped channels)

| FAULT_REACT_MODE_00 | Description                                                                                                 |

|---------------------|-------------------------------------------------------------------------------------------------------------|

| 0                   | Fault on one string $\rightarrow$ all strings of the same function group within the same device deactivated |

| 1                   | Fault on one string → no action on other strings                                                            |

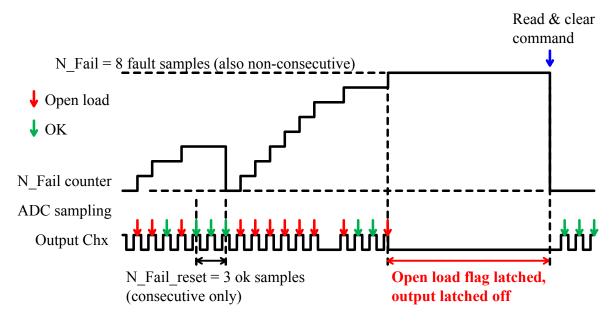

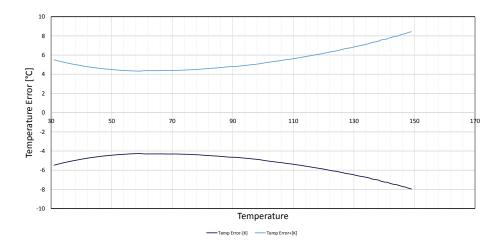

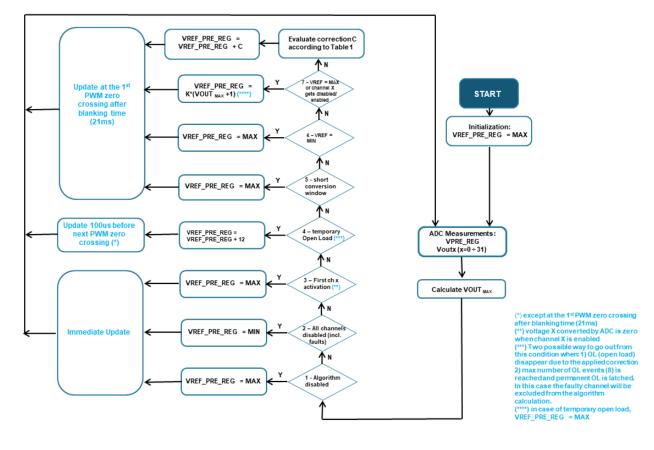

In the case of function group "00", the FAULT bus function is not available because this group is not linked to the FAULT pin.