## 概要

スマートフォンのような組込みデバイスでのハイレベルなグラフィカル・ユーザ・インタフェースに対する需要の高まりは、組込みシステム設計者に大きな課題を投げかけています。現在、マイクロコントローラとディスプレイを接続するために、SPI、パラレル、RGB のインタフェースが幅広く使用されています。解像度およびリフレッシュ・レートに関する要件の増加に伴い、ピン数（1670万色ディスプレイの場合は最大28ピン）が増え、必要となるピクセル・クロック周波数も高まっています。これらの要件によって、マイクロコントローラ側のピン数要件や、ボードのサイズと配線の複雑さ、クロックとデータのスキー問題による PCB 全体の複雑さとコストが増大します。

これらの課題に対処するために、STMicroelectronics は MIPI-DSI ホスト（STM32F469/479、STM32F7x8/x9、STM32L4R9/S9）を組み込んだ初のマイクロコントローラ製品を市場に投入します。これらの新たな DSİ ホスト搭載の STM32 製品には、ディスプレイに接続するためのさらに効果的な方法が実装されています。MIPI-DSI は、本来モバイル産業を対象としたディスプレイ向けのハイスピードかつピン数の少ないシリアル・インターフェースです。DSI インタフェースは、モバイル端末やタブレットに幅広く使用できるため人気があり、DSI ディスプレイのコストを下げ、その他の消費者市場においても魅力的なものとなりました。

STM32 MIPI-DSI ホストは、デバイスのピン数を大幅に削減し、今日市場の至るところで使用できる DSI ディスプレイと接続しやすくなっています。少ないピン数と低消費電力機能によって、DSI ホストは特にウェアラブルなどのサイズや消費電力に厳しい制約があるデバイスでディスプレイを接続する最も効果的な手法です。

本アプリケーション・ノートでは、STM32 マイクロコントローラにおける DSI ホスト・インターフェースについて説明し、DSI ホストのさまざまな動作モードの説明と、アプリケーションのニーズに応じた最適な動作モードを選択するガイドラインを示します。また、動作モードに応じた DSI ホストの設定方法の実例も示します。

## 関連ドキュメント

本アプリケーション・ノートは、[www.st.com](http://www.st.com) で入手できる以下のドキュメントと合わせて読む必要があります。

- **STM32F76xxx および STM32F77xxx advanced Arm®-based 32-bit MCU** (RM0410)

- **STM32F469xx および STM32F479xx advanced Arm®-based 32-bit MCU** (RM0386)

- **STM324Rxxx および STM32L4Sxxx advanced Arm®-based 32-bit MCU** (RM0432)

- 関連の STM32F469/479、STM32F7x8、STM32F7x9、STM32L4R9xx および STM32L4S9xx のデータシート

## 目次

|       |                                        |    |

|-------|----------------------------------------|----|

| 1     | 標準および参考資料 .....                        | 10 |

| 2     | 概要 .....                               | 11 |

| 2.1   | ディスプレイ・インターフェース接続 .....                | 11 |

| 2.2   | MIPI ディスプレイ仕様標準 .....                  | 13 |

| 2.3   | STM32 製品でサポートされるディスプレイ・インターフェース .....  | 14 |

| 2.4   | STM32 マイクロコントローラ全体での DSI ホストの可用性 ..... | 16 |

| 2.5   | DSI ホストの利点 .....                       | 17 |

| 2.6   | スマート・アーキテクチャでの DSI ホスト .....           | 17 |

| 3     | DSI の概要 .....                          | 19 |

| 3.1   | DSI 動作モード .....                        | 20 |

| 3.1.1 | コマンド・モード .....                         | 20 |

| 3.1.2 | ビデオ・モード .....                          | 20 |

| 3.2   | DSI 物理層 .....                          | 20 |

| 3.2.1 | [PHY 設定例] .....                        | 20 |

| 3.2.2 | PHY の信号モード .....                       | 21 |

|       | データ・レーンの状態 .....                       | 22 |

| 3.2.3 | データ・レーンの動作モード .....                    | 22 |

|       | 制御モード .....                            | 22 |

|       | ハイスピード転送モード .....                      | 22 |

|       | エスケープ・モード .....                        | 24 |

| 3.2.4 | 双方向レーンおよびバス・ターンアラウンドの手順 .....          | 30 |

| 3.2.5 | クロックレーンの電力モード .....                    | 30 |

|       | 低消費電力モード .....                         | 30 |

|       | ハイスピード・モード .....                       | 30 |

|       | 超低消費電力状態 (ULPS) .....                  | 32 |

| 3.3   | DSI プロトコル .....                        | 34 |

| 3.3.1 | パケット構造 .....                           | 34 |

|       | ロング・パケット .....                         | 35 |

|       | ショート・パケット .....                        | 35 |

|       | データ識別子バイト .....                        | 35 |

|       | データ保護 (ECC およびチェックサム) .....            | 36 |

| 3.3.2 | 送信終了 (EoT) パケット .....                  | 36 |

| 3.3.3 | パケット送信モード .....                        | 37 |

# 参考資料

|          |                                         |           |

|----------|-----------------------------------------|-----------|

| 3.3.4    | ホストからディスプレイのデータ型 .....                  | 39        |

|          | ビデオ・モードのデータ型 .....                      | 40        |

|          | コマンド・モードのデータ型 .....                     | 43        |

| 3.3.5    | ディスプレイからホストのデータ型 .....                  | 47        |

| 3.3.6    | ビデオ・モードのインターフェース・タイミング .....            | 49        |

| 3.3.7    | コマンド・モードでのティアリング効果信号 .....              | 50        |

| <b>4</b> | <b>DSI ホストの説明 .....</b>                 | <b>52</b> |

| 4.1      | DSI のシステム・レベル・アーキテクチャ .....             | 52        |

|          | DSI ホストの構成要素 .....                      | 52        |

| 4.2      | 動作モード .....                             | 53        |

| 4.2.1    | ビデオ・モード .....                           | 54        |

|          | 同期パルスでの非バースト・モード .....                  | 54        |

|          | 同期イベントでの非バースト・モード .....                 | 58        |

|          | バースト・モード .....                          | 60        |

|          | ビデオ・モードの比較 .....                        | 62        |

| 4.2.2    | アダプティッド・コマンド・モード .....                  | 63        |

|          | アダプティッド・コマンド・モードでのディスプレイ・リフレッシュの例 ..... | 64        |

|          | アダプティッド・コマンド・モードでの部分リフレッシュの例 .....      | 64        |

|          | アダプティッド・コマンド・モードの利点 .....               | 66        |

|          | ティアリング効果管理 .....                        | 67        |

| 4.2.3    | APB コマンド・モード .....                      | 71        |

|          | APB コマンド・モードを使用する場合 .....               | 71        |

| 4.3      | 動作モードの選択 .....                          | 72        |

| 4.4      | DSI 割込み .....                           | 72        |

| 4.5      | 低消費電力モード .....                          | 73        |

| <b>5</b> | <b>DSI ホストの設定 .....</b>                 | <b>74</b> |

| 5.1      | DSI ホストのグローバル設定 .....                   | 74        |

| 5.1.1    | DSI レギュレータの設定 .....                     | 74        |

| 5.1.2    | クロックの設定 .....                           | 74        |

|          | DSI PLL の設定 .....                       | 75        |

|          | TX エスケープ・クロックの設定 .....                  | 76        |

|          | 2 次クロック・ソースのセット .....                   | 77        |

| 5.1.3    | DSI ホストの PHY パラメータ .....                | 77        |

|          | レーン数 .....                              | 77        |

|          | PHY のクロックおよびデジタル・セクション制御 .....          | 77        |

|          | クロック・レーン制御 .....                        | 78        |

| 5.1.4    | DSI ラッパーの PHY パラメータ .....               | 79        |

# 参考資料

## 目次

AN4860

|                                            |     |

|--------------------------------------------|-----|

| HS ビット期間のセット .....                         | 79  |

| 5.1.5 プロトコル・フロー制御 .....                    | 80  |

| 5.1.6 DSI ホストの LTDC インタフェース設定 .....        | 81  |

| カラー・コーディングの設定 .....                        | 81  |

| ビデオ制御信号の極性 .....                           | 82  |

| 5.2 DSI 動作モードの設定 .....                     | 83  |

| 5.2.1 LTDC インタフェースでのビデオ・モード .....          | 83  |

| ビデオ・モードの選択 .....                           | 83  |

| ビデオ・モードでの LP 状態 .....                      | 83  |

| PHY 遷移タイミングの設定 .....                       | 83  |

| LP 遷移の設定 .....                             | 85  |

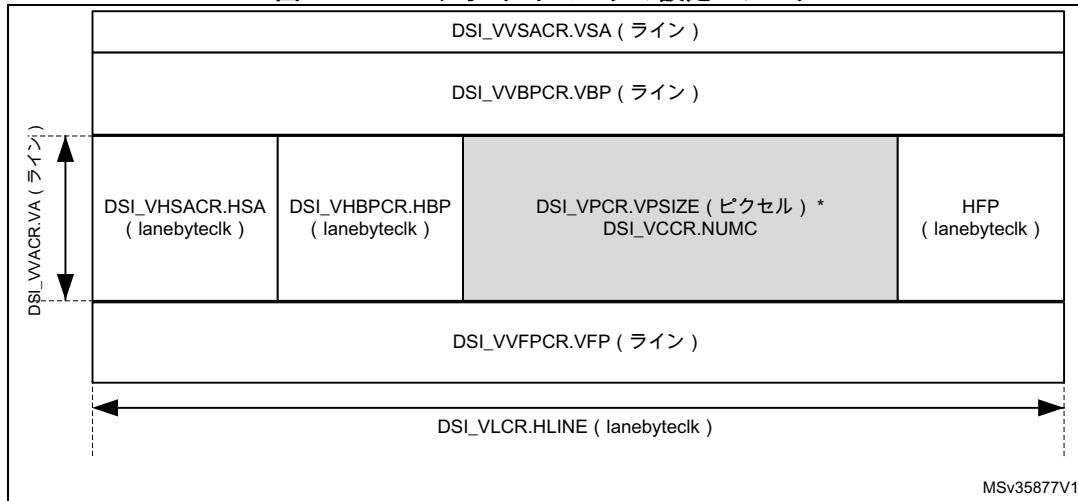

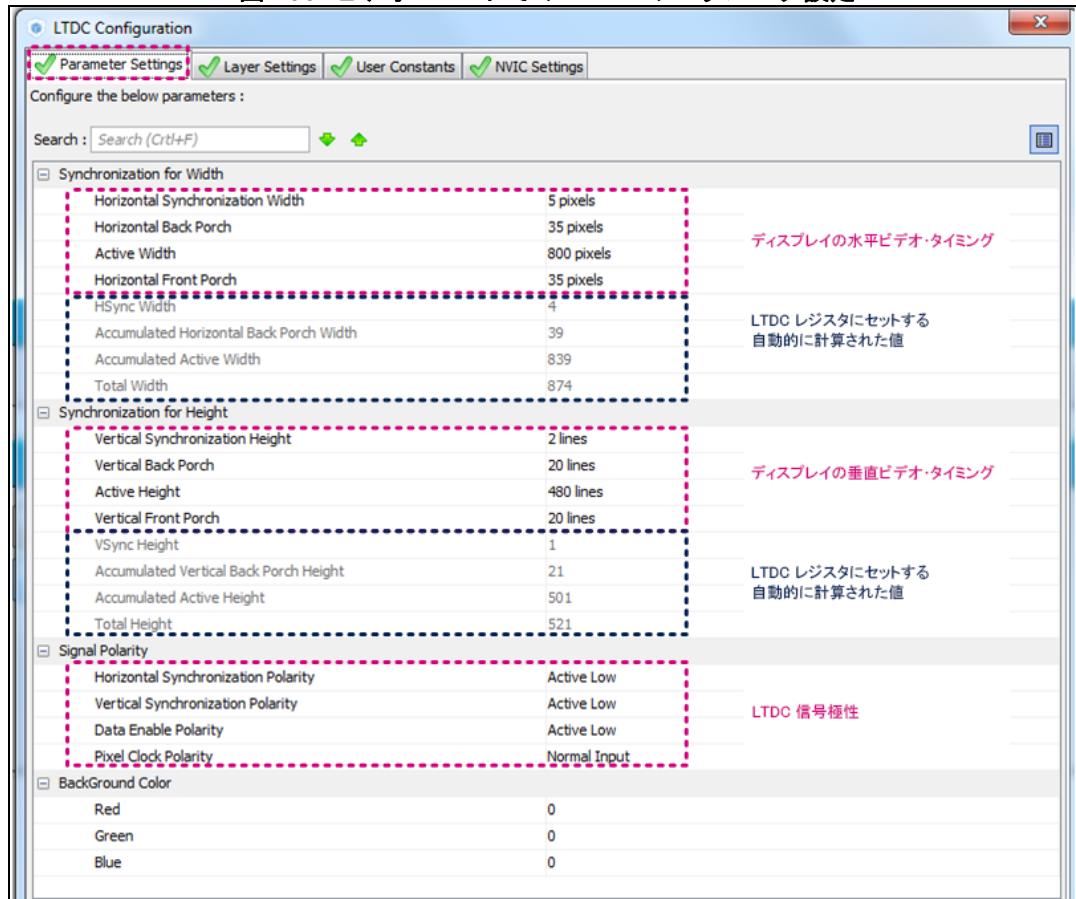

| LTDC の設定 .....                             | 89  |

| DSI ホストのビデオ・タイミング .....                    | 91  |

| DSI クロック設定 .....                           | 93  |

| DSI ビデオ・パケット・パラメータ .....                   | 93  |

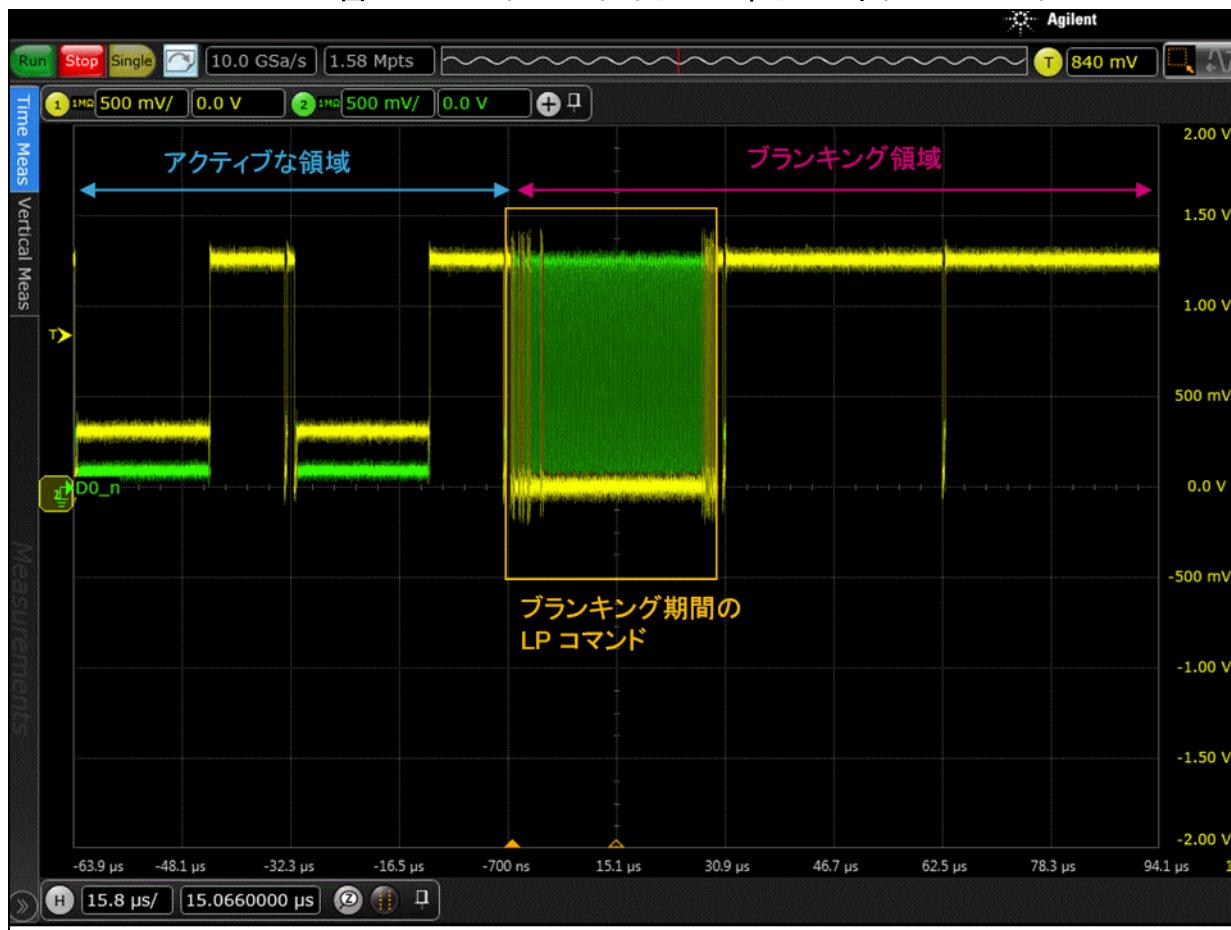

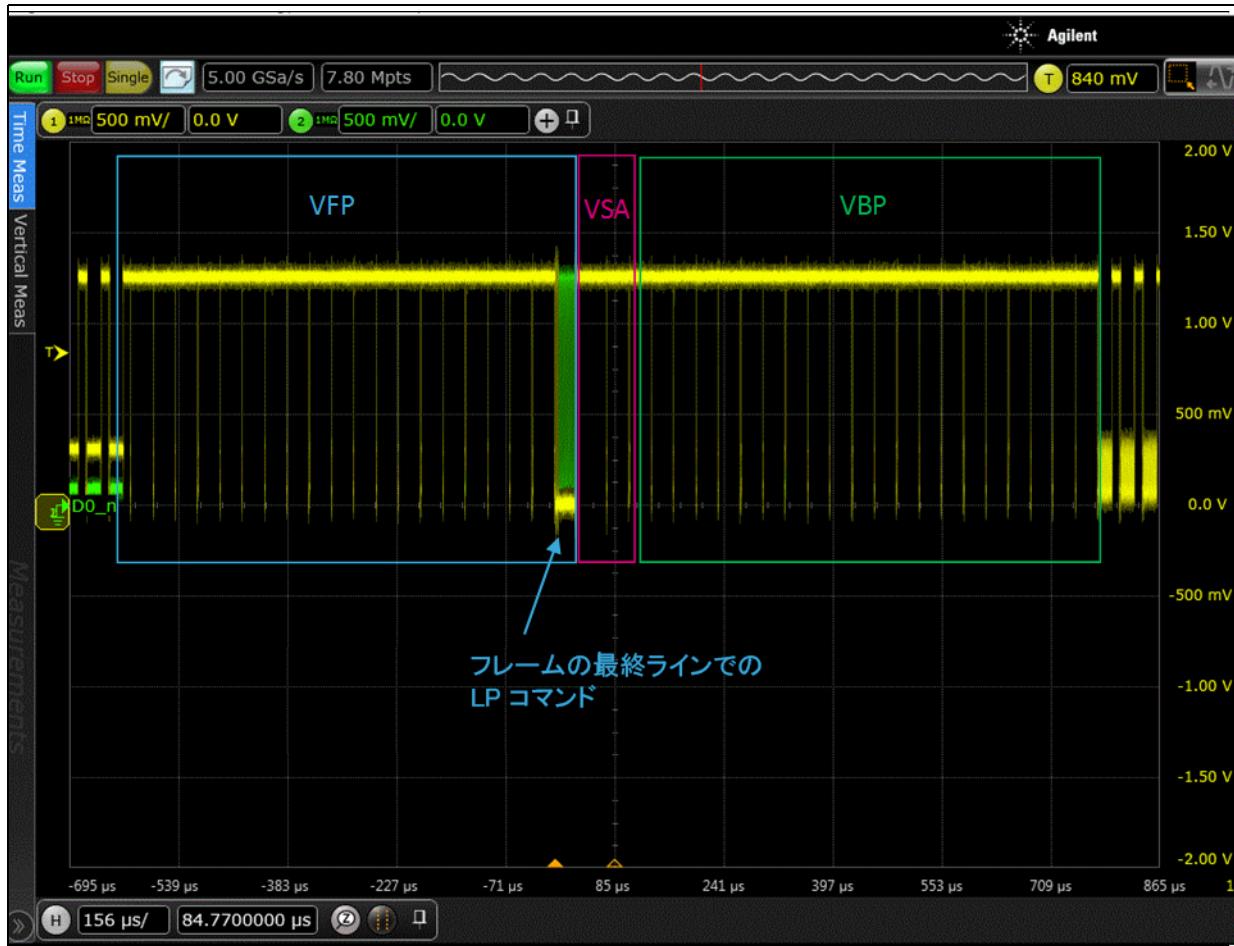

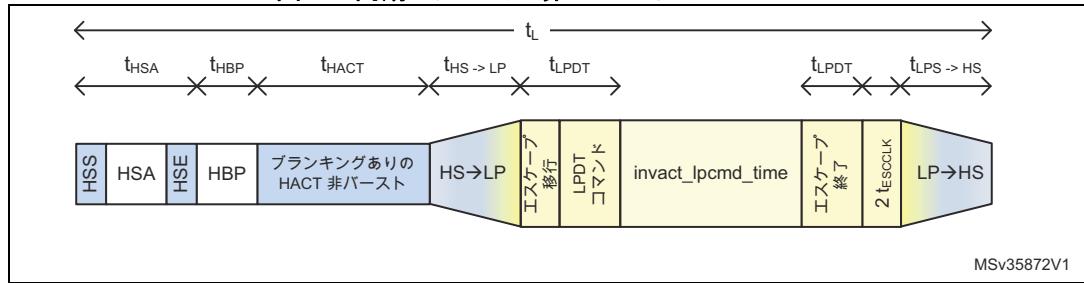

| ビデオ・モードでのコマンド送信 .....                      | 96  |

| フレーム確認応答 .....                             | 104 |

| 5.2.2 LTDC インタフェースでのアダプティッド・コマンド・モード ..... | 105 |

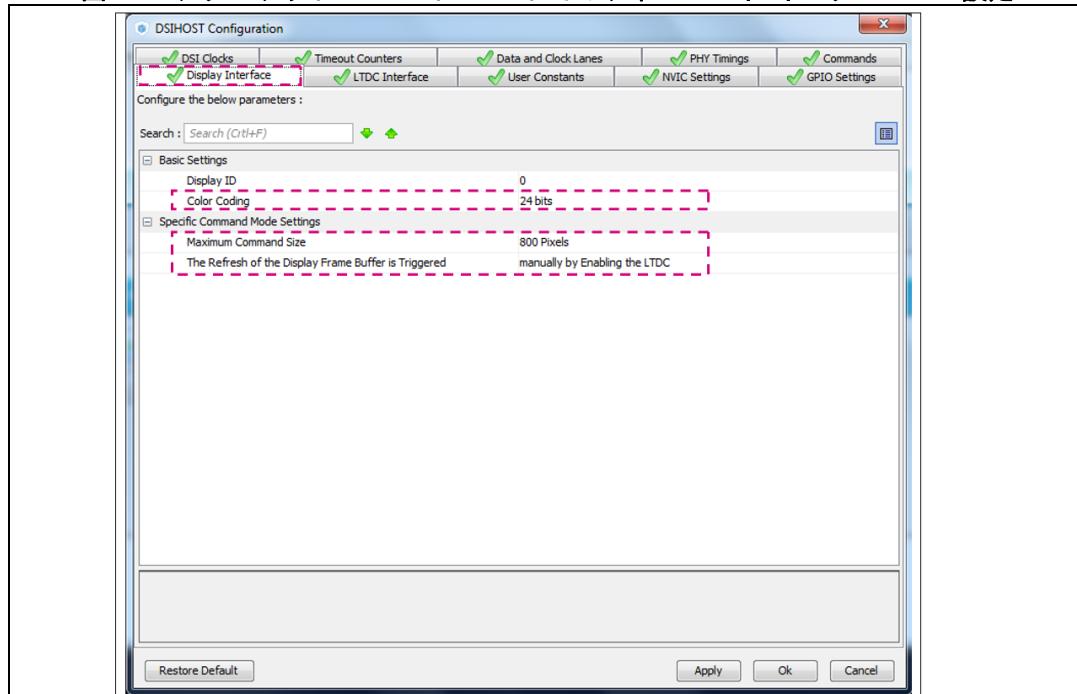

| DSI コマンド・モード .....                         | 105 |

| STOP ウェイト・タイム設定 .....                      | 106 |

| コマンド・サイズ (CMDSIZE) .....                   | 106 |

| LTDC 停止極性 .....                            | 106 |

| ティアリング効果設定 .....                           | 107 |

| リフレッシュ・モード .....                           | 107 |

| LTDC の設定 .....                             | 108 |

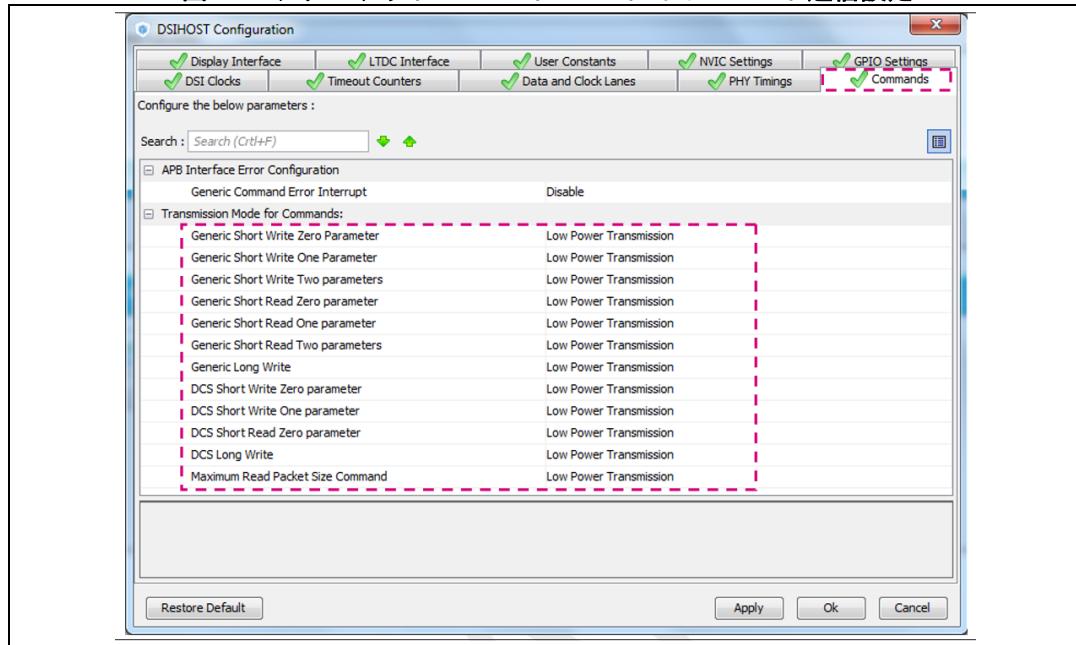

| コマンド送信モード .....                            | 108 |

| 確認応答リクエスト .....                            | 109 |

| 6 STM32CubeMX の設定例 .....                   | 111 |

| 6.1 DSI ホストのビデオ・バースト・モード .....             | 111 |

| 6.1.1 ピン配置設定 .....                         | 111 |

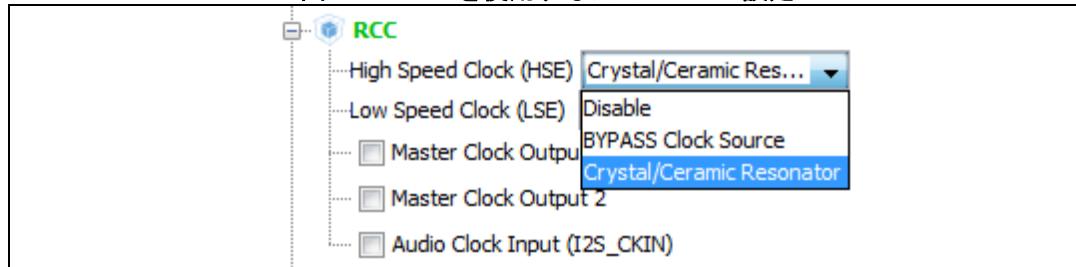

| RCC での HSE 有効化 .....                       | 111 |

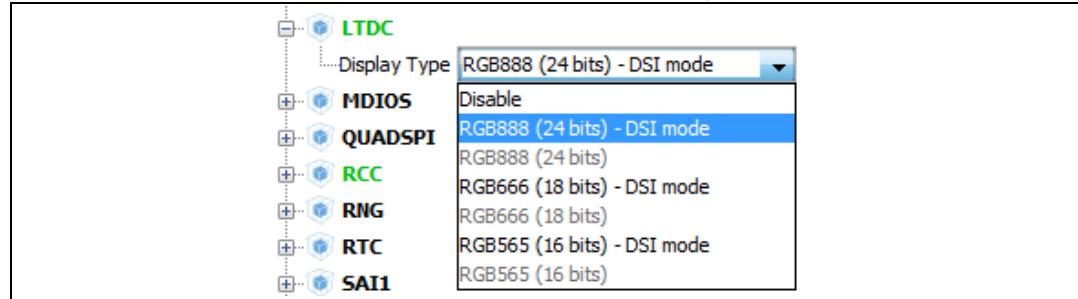

| DSI モードでの LTDC 有効化 .....                   | 112 |

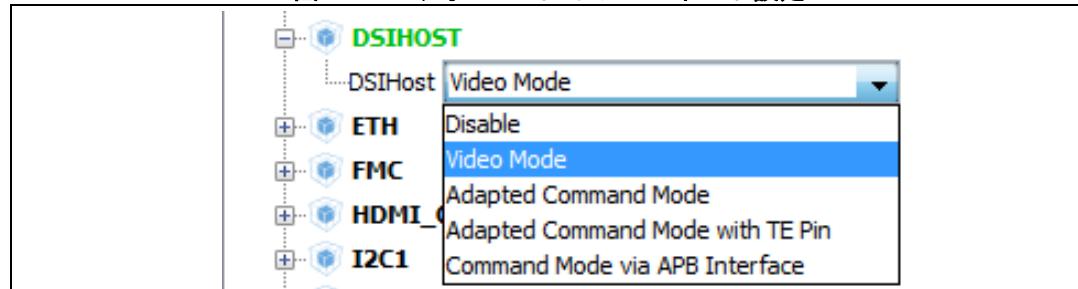

| ビデオ・モードでの DSI ホスト有効化 .....                 | 112 |

| 6.1.2 クロック設定 .....                         | 112 |

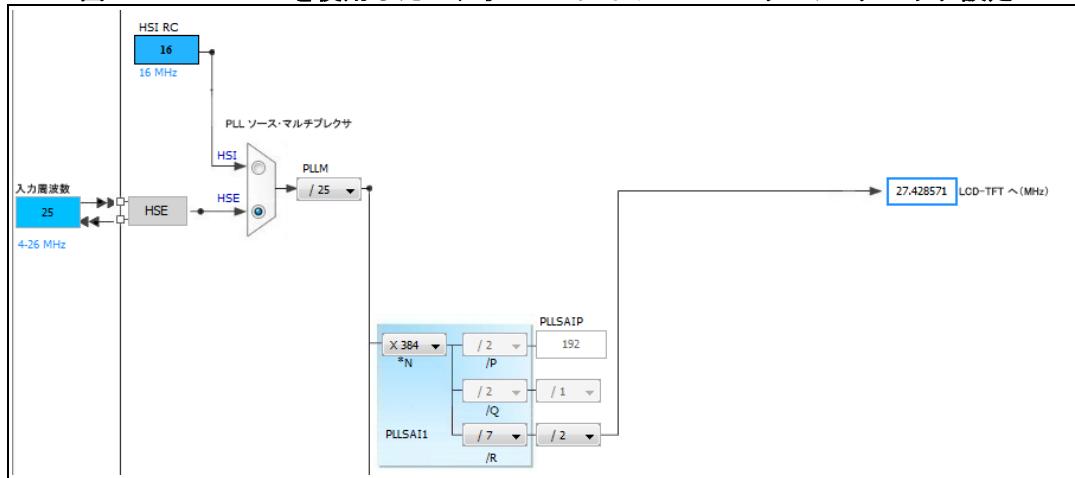

| LTDC クロック設定 .....                          | 112 |

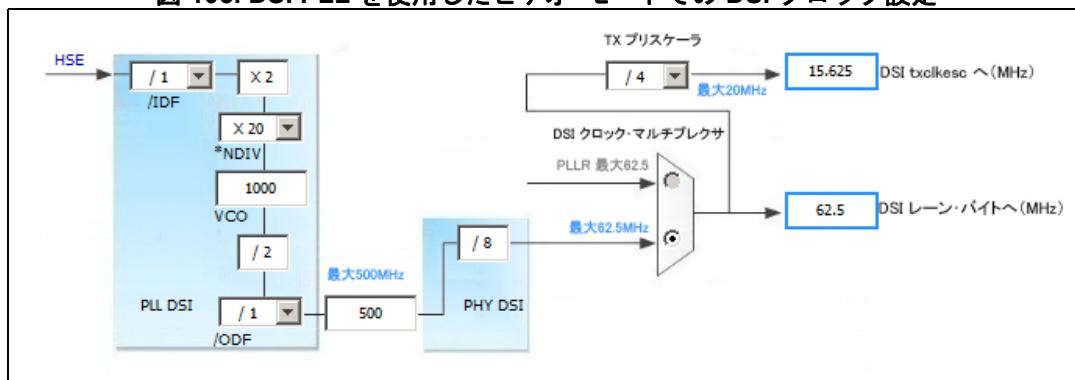

| DSI クロック設定 .....                           | 113 |

| 6.1.3 LTDC および DSI の設定 .....               | 114 |

| LTDC 設定 .....                              | 114 |

| DSI ホストの設定 .....                           | 116 |

# 参考資料

AN4860

目次

|           |                                  |            |

|-----------|----------------------------------|------------|

| 6.1.4     | ビデオ・バースト・モードの生成コードの例             | 120        |

| 6.2       | DSI ホストの同期パルスでの非バースト・モード         | 123        |

| 6.2.1     | コマンド設定                           | 123        |

| 6.2.2     | ディスプレイ・インターフェース設定                | 124        |

| 6.3       | DSI ホストのアダプティッド・コマンド・モード         | 125        |

| 6.3.1     | ピン設定                             | 125        |

| 6.3.2     | クロック設定                           | 125        |

|           | LTDC クロック設定                      | 125        |

| 6.3.3     | LTDC および DSI の設定                 | 126        |

|           | LTDC 設定                          | 126        |

|           | DSI ホストの設定                       | 128        |

| 6.3.4     | アダプティッド・コマンド・モードの生成コードの例         | 131        |

| <b>7</b>  | <b>DSI ホストのパフォーマンス</b>           | <b>135</b> |

| 7.1       | LTDC ピクセル・クロックでの DSI リンク最大帯域幅の影響 | 135        |

| 7.2       | LTDC ピクセル・クロックでのシステム制約の影響        | 135        |

| 7.3       | DSI リンク帯域幅の推定                    | 136        |

| 7.3.1     | ビデオ・モード                          | 136        |

| 7.3.2     | アダプティッド・コマンド・モード                 | 136        |

| <b>8</b>  | <b>DSI ホストのアプリケーション例</b>         | <b>138</b> |

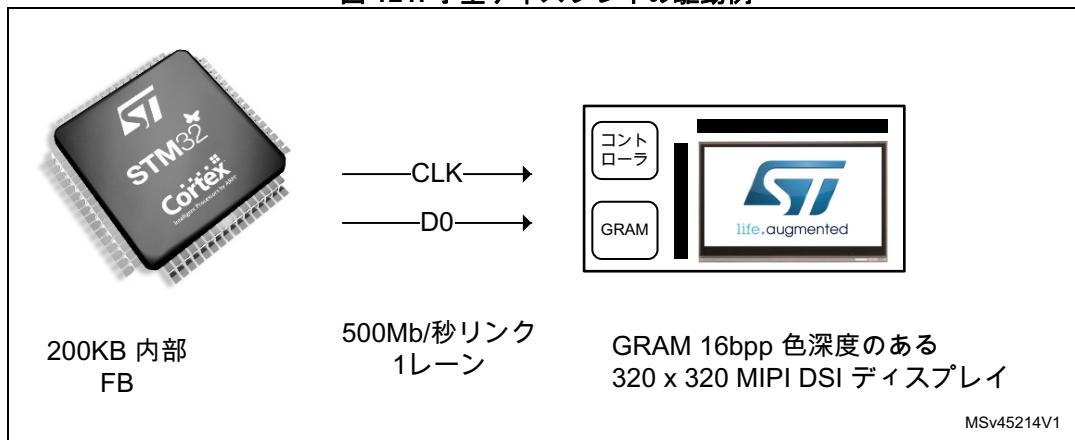

| 8.1       | 小型ディスプレイの駆動例                     | 138        |

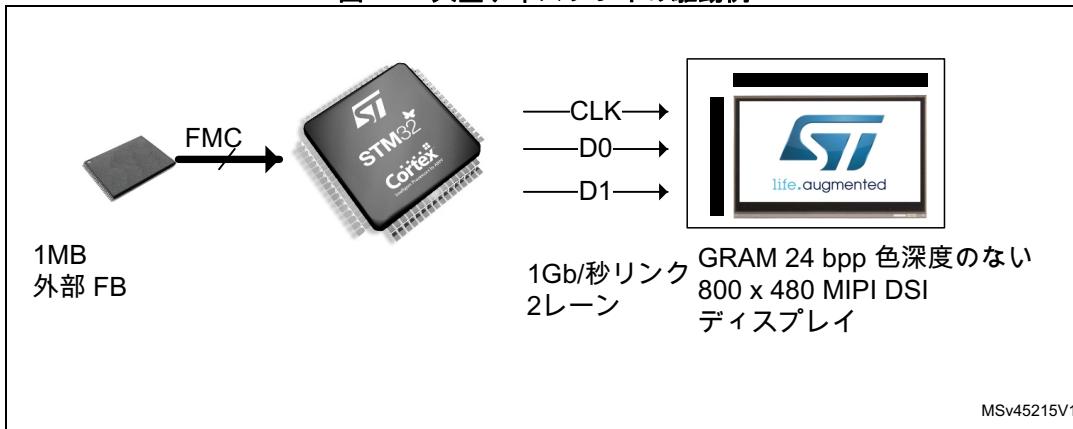

| 8.2       | 大型ディスプレイの駆動例                     | 139        |

| <b>9</b>  | <b>サポートされているデバイス</b>             | <b>140</b> |

| <b>10</b> | <b>まとめ</b>                       | <b>141</b> |

| <b>11</b> | <b>改版履歴</b>                      | <b>142</b> |

# 参考資料

## 表の一覧

AN4860

## 表の一覧

|       |                                                   |     |

|-------|---------------------------------------------------|-----|

| 表 1.  | STM32 製品のディスプレイ・インターフェース接続 . . . . .              | 16  |

| 表 2.  | DSI ホストを搭載した STM32 マイクロコントローラ . . . . .           | 16  |

| 表 3.  | 他のディスプレイ・インターフェースと比べた DSI ホストの利点 . . . . .        | 17  |

| 表 4.  | データ・レーンの状態と動作モード . . . . .                        | 22  |

| 表 5.  | エスケープ・モードのコマンド . . . . .                          | 24  |

| 表 6.  | ホストからディスプレイのデータ型 . . . . .                        | 39  |

| 表 7.  | DCS コマンドの一覧 . . . . .                             | 46  |

| 表 8.  | ディスプレイからホストのデータ型 . . . . .                        | 48  |

| 表 9.  | DSI ホストの低消費電力モード . . . . .                        | 73  |

| 表 10. | DSI レギュレータの設定レジスタ . . . . .                       | 74  |

| 表 11. | DSI PLL の設定レジスタ . . . . .                         | 75  |

| 表 12. | TX エスケープ・クロックの設定レジスタ . . . . .                    | 76  |

| 表 13. | 2 次クロック・ソースのセット・レジスタ . . . . .                    | 77  |

| 表 14. | レーン数の設定レジスタ . . . . .                             | 77  |

| 表 15. | PHY のクロックおよびデジタル・セクションの制御レジスタ . . . . .           | 77  |

| 表 16. | クロック・レーンの制御レジスタ . . . . .                         | 78  |

| 表 17. | HS ビット期間の設定レジスタ . . . . .                         | 79  |

| 表 18. | プロトコル・フロー制御の設定レジスタ . . . . .                      | 80  |

| 表 19. | カラー・コーディングの設定レジスタ . . . . .                       | 81  |

| 表 20. | ビデオ制御信号の極性レジスタ . . . . .                          | 82  |

| 表 21. | ビデオ・モード選択レジスタ . . . . .                           | 83  |

| 表 22. | PHY 遷移タイミングの設定レジスタ . . . . .                      | 83  |

| 表 23. | LP 遷移の設定レジスタ . . . . .                            | 85  |

| 表 24. | ディスプレイ・タイミングの例 . . . . .                          | 90  |

| 表 25. | DSI ホストのビデオ・タイミング・レジスタ . . . . .                  | 91  |

| 表 26. | DSI ビデオ・パケット・パラメータ・レジスタ . . . . .                 | 93  |

| 表 27. | コマンド送信モード・レジスタ . . . . .                          | 97  |

| 表 28. | LP コマンド・パケット・サイズ・レジスタ . . . . .                   | 97  |

| 表 29. | フレーム確認応答レジスタ . . . . .                            | 104 |

| 表 30. | DSI コマンド・モード・レジスタ . . . . .                       | 105 |

| 表 31. | STOP ウェイト・タイム設定レジスタ . . . . .                     | 106 |

| 表 32. | コマンド・サイズ・レジスタ . . . . .                           | 106 |

| 表 33. | LTDC 停止極性 . . . . .                               | 106 |

| 表 34. | ティアリング効果設定レジスタ . . . . .                          | 107 |

| 表 35. | リフレッシュ・モード・レジスタ . . . . .                         | 107 |

| 表 36. | コマンド送信レジスタ . . . . .                              | 108 |

| 表 37. | 確認応答リクエスト・レジスタ . . . . .                          | 109 |

| 表 38. | カラー・コーディングと DSI リンク速度に応じた最大ピクセル・クロック周波数 . . . . . | 135 |

| 表 39. | 文書改版履歴 . . . . .                                  | 142 |

| 表 40. | 日本語版文書改版履歴 . . . . .                              | 142 |

## 図の一覧

|       |                                                            |    |

|-------|------------------------------------------------------------|----|

| 図 1.  | フレームバッファとコントローラのあるディスプレイ・アーキテクチャ .....                     | 12 |

| 図 2.  | コントローラとフレームバッファのないディスプレイ・アーキテクチャ .....                     | 13 |

| 図 3.  | DBI インタフェースの例 .....                                        | 14 |

| 図 4.  | DPI インタフェースの例 .....                                        | 15 |

| 図 5.  | DSI インタフェースの例 .....                                        | 15 |

| 図 6.  | DSI ホストでの STM32 システム・アーキテクチャ .....                         | 18 |

| 図 7.  | DSI インタフェースの概要 .....                                       | 19 |

| 図 8.  | DSI ホストおよびディスプレイ・インターフェース .....                            | 21 |

| 図 9.  | HS および LP の信号レベル .....                                     | 21 |

| 図 10. | 基本的な HS データ送信 .....                                        | 22 |

| 図 11. | ハイスピード・データ転送モード .....                                      | 23 |

| 図 12. | 2 つのデータ・レーンを使用した HS 送信 .....                               | 23 |

| 図 13. | 奇数バイトのある 2 つのデータ・レーンを使用した HS 送信 .....                      | 24 |

| 図 14. | スペース付きワン・ホット・コーディング .....                                  | 25 |

| 図 15. | スペース付きワン・ホット・コーディングを使用した通信例 .....                          | 26 |

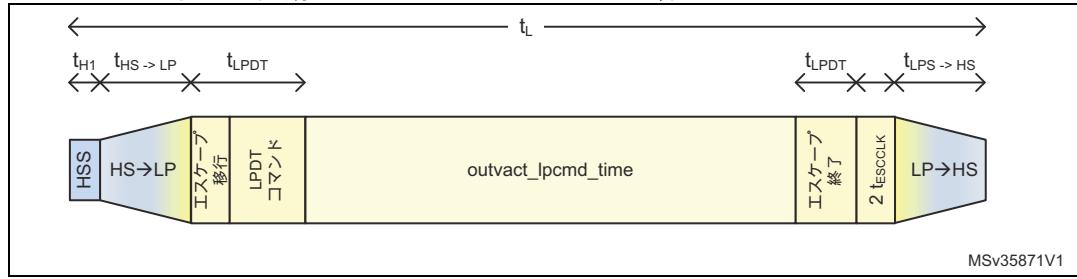

| 図 16. | LPDT エスケープ・モード・シーケンス .....                                 | 26 |

| 図 17. | LPDT ペイロード・データ .....                                       | 27 |

| 図 18. | ULPS エスケープ・モード・シーケンス .....                                 | 27 |

| 図 19. | 確認応答トリガの例 .....                                            | 28 |

| 図 20. | ティアリング効果トリガの例 .....                                        | 29 |

| 図 21. | リセット・トリガの例 .....                                           | 29 |

| 図 22. | バス・ターンアラウンド手順 .....                                        | 30 |

| 図 23. | クロック HS 移行シーケンス .....                                      | 31 |

| 図 24. | クロック HS 終了シーケンス .....                                      | 31 |

| 図 25. | HS モードでのクロック・レーンとデータ・レーンの関係 .....                          | 32 |

| 図 26. | クロック・レーン ULPS 移行シーケンス .....                                | 33 |

| 図 27. | クロック・レーン ULPS 終了シーケンス .....                                | 33 |

| 図 28. | ショート・パケットとロング・パケットの構造 .....                                | 34 |

| 図 29. | ロング・パケットの例 .....                                           | 34 |

| 図 30. | データ識別子バイト .....                                            | 35 |

| 図 31. | EoT パケットのある HS 送信 .....                                    | 36 |

| 図 32. | 1 つのデータ・レーンを使用した HS モードでのショート・パケットの送信 .....                | 37 |

| 図 33. | 2 つのデータ・レーンを使用した HS モードでのショート・パケットの送信 .....                | 37 |

| 図 34. | 低消費電力モードでのショート・パケットの送信 .....                               | 37 |

| 図 35. | 1 つのデータ・レーンを使用した HS モードでのロング・パケットの送信 .....                 | 37 |

| 図 36. | 2 つのデータ・レーンを使用した HS モードでのロング・パケットの送信 .....                 | 38 |

| 図 37. | 奇数のペイロード・データがある 2 つのデータ・レーンを使用した HS モードでのロング・パケットの送信 ..... | 38 |

| 図 38. | 低消費電力モードでのロング・パケットの送信 .....                                | 38 |

| 図 39. | カラー・モードのビデオ・パケット .....                                     | 40 |

| 図 40. | シャットダウン／オンのビデオ・パケット .....                                  | 40 |

| 図 41. | 同期イベントのパケット .....                                          | 41 |

| 図 42. | パック済みピクセル・ストリーム、16-bit フォーマット、データ型 = (0x0E) .....          | 41 |

| 図 43. | パック済みピクセル・ストリーム、18-bit フォーマット、データ型 = (0x1E) .....          | 42 |

| 図 44. | 軽度パック済みピクセル・ストリーム、18-bit フォーマット、データ型 = (0x2E) .....        | 42 |

| 図 45. | パック済みピクセル・ストリーム、24-bit フォーマット、データ型 = (0x3E) .....          | 42 |

| 図 46. | 汎用ショート書込みコマンド .....                                        | 43 |

| 図 47. | 汎用ロング書込みコマンド .....                                         | 43 |

| 図 48. | 汎用読み出しコマンド .....                                           | 43 |

# 参考資料

## 図の一覧

AN4860

|        |                                                |     |

|--------|------------------------------------------------|-----|

| 図 49.  | DCS ショート書込みコマンド.....                           | 44  |

| 図 50.  | DCS ロング書込みコマンド .....                           | 44  |

| 図 51.  | DCS 読出しコマンド .....                              | 45  |

| 図 52.  | 逆方向の通信シーケンス .....                              | 48  |

| 図 53.  | 同期パルスでの非バースト・モード .....                         | 49  |

| 図 54.  | 同期イベントでの非バースト・モード .....                        | 49  |

| 図 55.  | バースト・モード .....                                 | 50  |

| 図 56.  | TE シーケンス .....                                 | 51  |

| 図 57.  | set_tear_scanline の DCS ロング・パケット .....         | 51  |

| 図 58.  | DSI の構成要素 .....                                | 53  |

| 図 59.  | 同期パルスでの非バースト・モードのフレーム .....                    | 55  |

| 図 60.  | ブランкиングまたは LP の定義 .....                        | 56  |

| 図 61.  | 同期パルスでの非バースト・モードの VACT 領域 .....                | 57  |

| 図 62.  | null パケット付きの 4 つのチャンクを設定したアクティブ・ライン .....      | 58  |

| 図 63.  | 同期イベントでの非バーストのフレーム .....                       | 59  |

| 図 64.  | 同期イベントでのバースト・モードの VACT 領域 .....                | 60  |

| 図 65.  | ビデオ・バースト・モードのフレーム .....                        | 61  |

| 図 66.  | バースト・モードでのアクティブなライン .....                      | 62  |

| 図 67.  | ビデオ・モードの比較 .....                               | 63  |

| 図 68.  | WMS/WMC でのフル・ディスプレイ・リフレッシュ .....               | 64  |

| 図 69.  | ディスプレイの部分リフレッシュ .....                          | 65  |

| 図 70.  | 自動リフレッシュでのアダプティッド・コマンド・モードのフロー例 .....          | 65  |

| 図 71.  | アダプティッド・コマンド・モードでのディスプレイ・リフレッシュ .....          | 66  |

| 図 72.  | ティアリング効果のリクエストと応答の例 .....                      | 67  |

| 図 73.  | 2 回の BTA のある set_tear_scanline DCS コマンド .....  | 68  |

| 図 74.  | ディスプレイからのティアリング効果トリガ .....                     | 69  |

| 図 75.  | ピン経由の TE .....                                 | 70  |

| 図 76.  | ピン経由のティアリング効果の拡大図 .....                        | 71  |

| 図 77.  | DSI クロック構成 .....                               | 76  |

| 図 78.  | 自動クロック・レーン制御 .....                             | 78  |

| 図 79.  | 自動クロック・レーン制御を無効にしてクロック・レーンを常に HS モードにした例 ..... | 79  |

| 図 80.  | 読み出しコマンド後の BTA 手順 .....                        | 81  |

| 図 81.  | LP モード移行フロー .....                              | 85  |

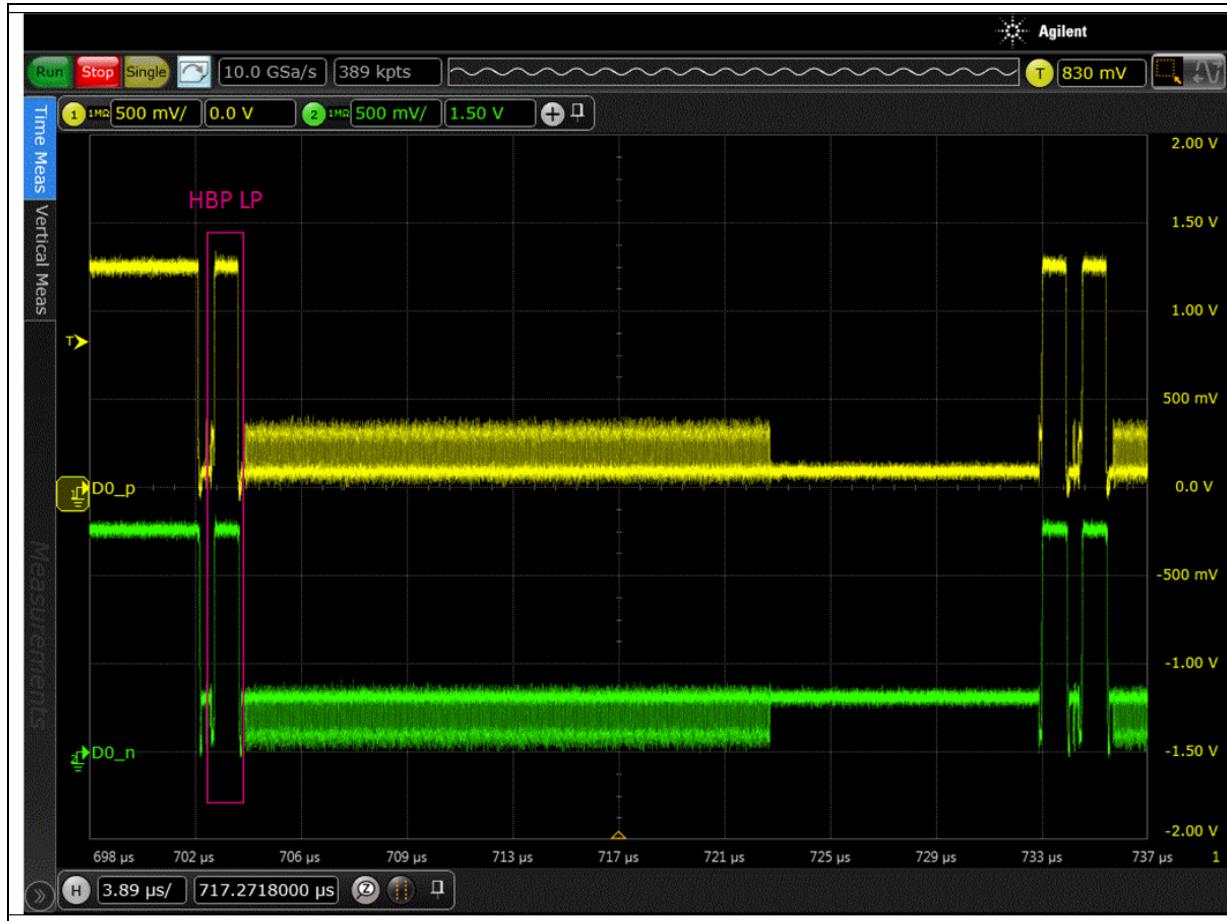

| 図 82.  | HBP 領域で無効化された LP .....                         | 86  |

| 図 83.  | HBP 領域で有効化された LP .....                         | 87  |

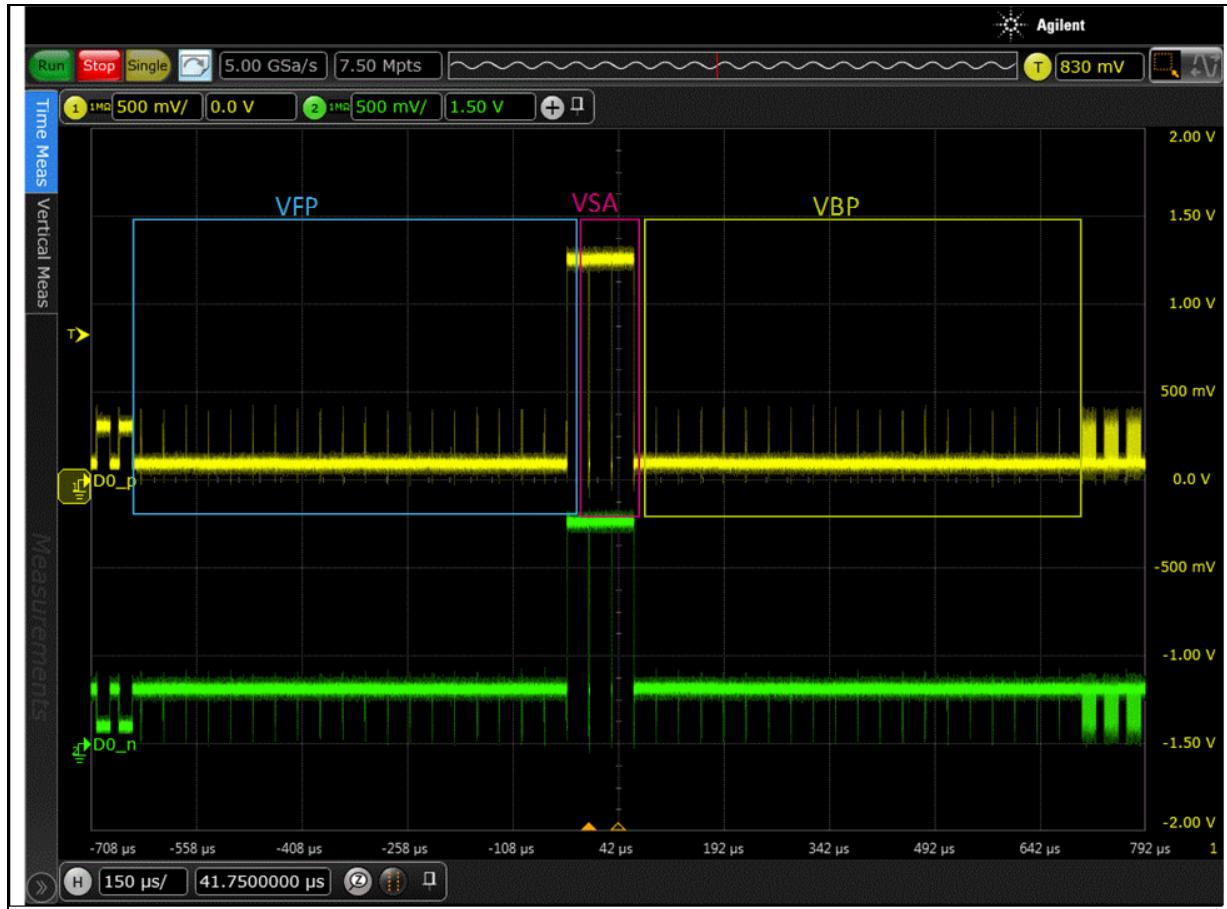

| 図 84.  | VSA 領域でのみ有効化された LP モード .....                   | 88  |

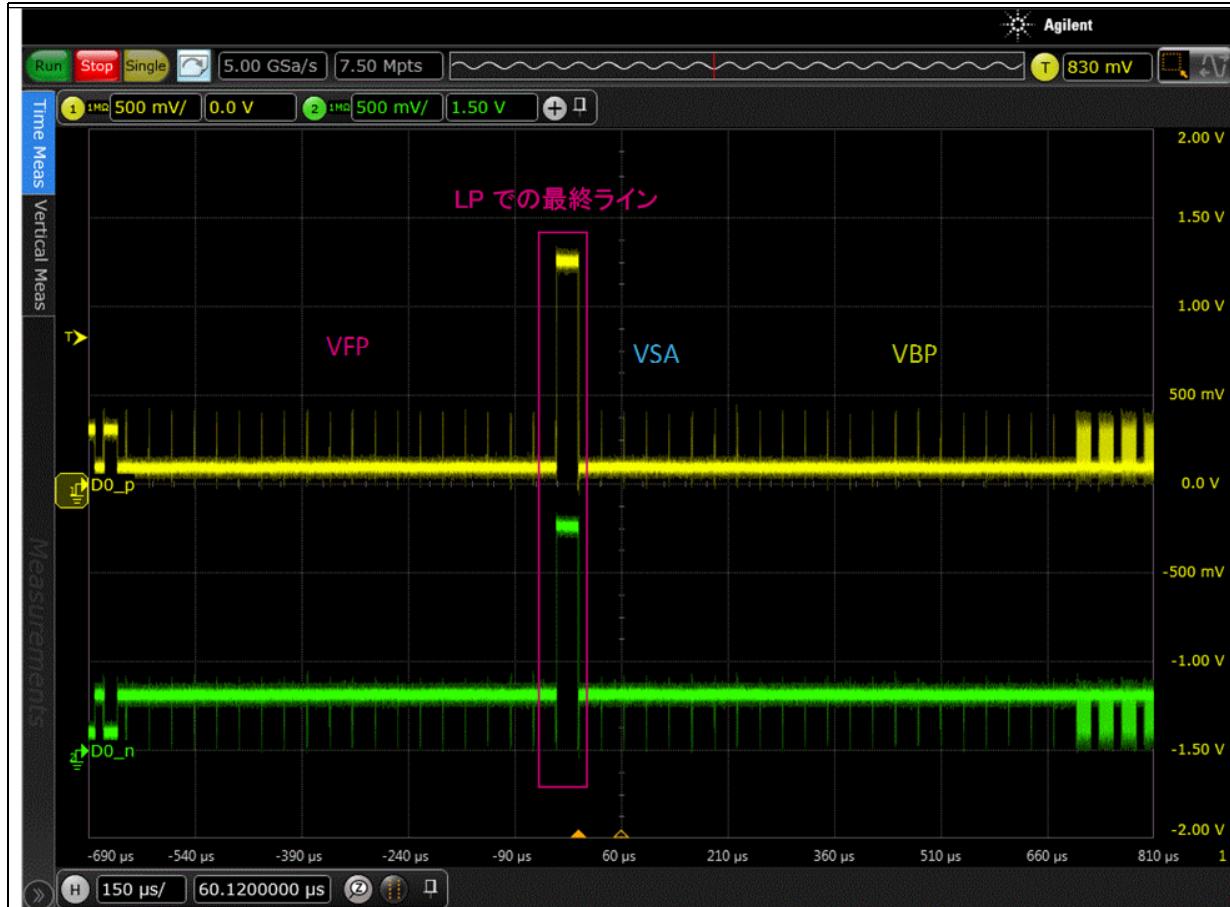

| 図 85.  | 低消費電力モードでの最終ライン .....                          | 89  |

| 図 86.  | DSI ビデオ・タイミングの設定レジスタ .....                     | 92  |

| 図 87.  | バースト・モードでのビデオ・ライン .....                        | 94  |

| 図 88.  | null パケット付きの 4 つのチャンクの設定 .....                 | 95  |

| 図 89.  | null パケットのない 4 つのチャンクの設定 .....                 | 96  |

| 図 90.  | 同期パルスでの非バーストの LPSIZE .....                     | 98  |

| 図 91.  | 同期イベントでのバーストまたは非バーストの LPSIZE .....             | 98  |

| 図 92.  | バースト・モードでの VFP 中の 28 バイト LP コマンド .....         | 100 |

| 図 93.  | 最終ラインまで遅らせた 29 バイト LP コマンド .....               | 101 |

| 図 94.  | 同期パルスでの非バーストの VLPSIZE .....                    | 101 |

| 図 95.  | 同期イベントでの非バーストの VLPSIZE .....                   | 102 |

| 図 96.  | バースト・モードの VLPSIZE .....                        | 102 |

| 図 97.  | バースト・モードでの VACT 中の 8 バイト LP コマンド .....         | 103 |

| 図 98.  | フレーム確認応答の例 .....                               | 104 |

| 図 99.  | フレーム確認応答の拡大図 .....                             | 105 |

| 図 100. | 確認応答リクエストを有効にした汎用ショート書込み .....                 | 110 |

# 参考資料

|        |                                         |     |

|--------|-----------------------------------------|-----|

| 図 101. | HSE を使用するための RCC 設定                     | 111 |

| 図 102. | DSI モードでの LTDC 設定                       | 112 |

| 図 103. | ビデオ・モードでの DSI ホスト設定                     | 112 |

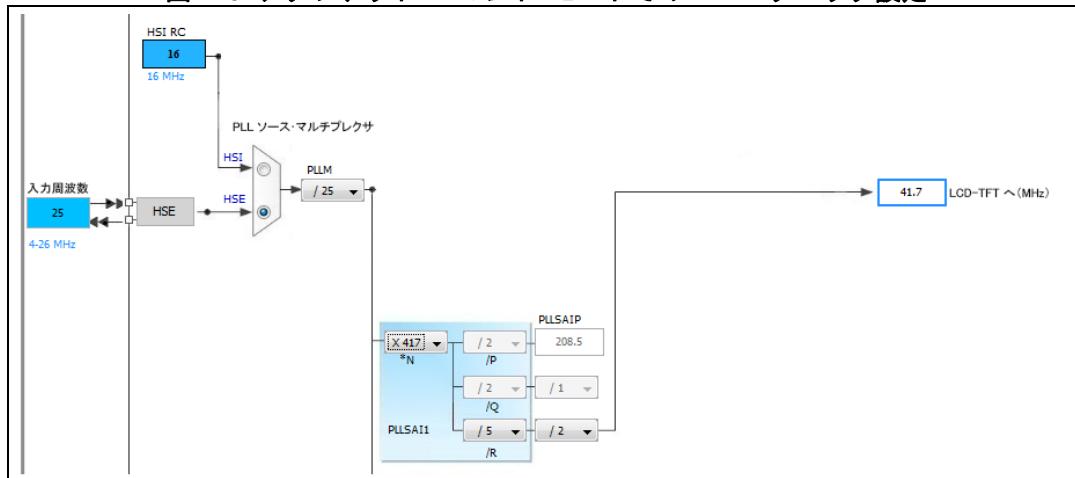

| 図 104. | PLLSAI1 を使用したビデオ・モードでの LTDC ピクセル・クロック設定 | 113 |

| 図 105. | DSI PLL を使用したビデオ・モードでの DSI クロック設定       | 113 |

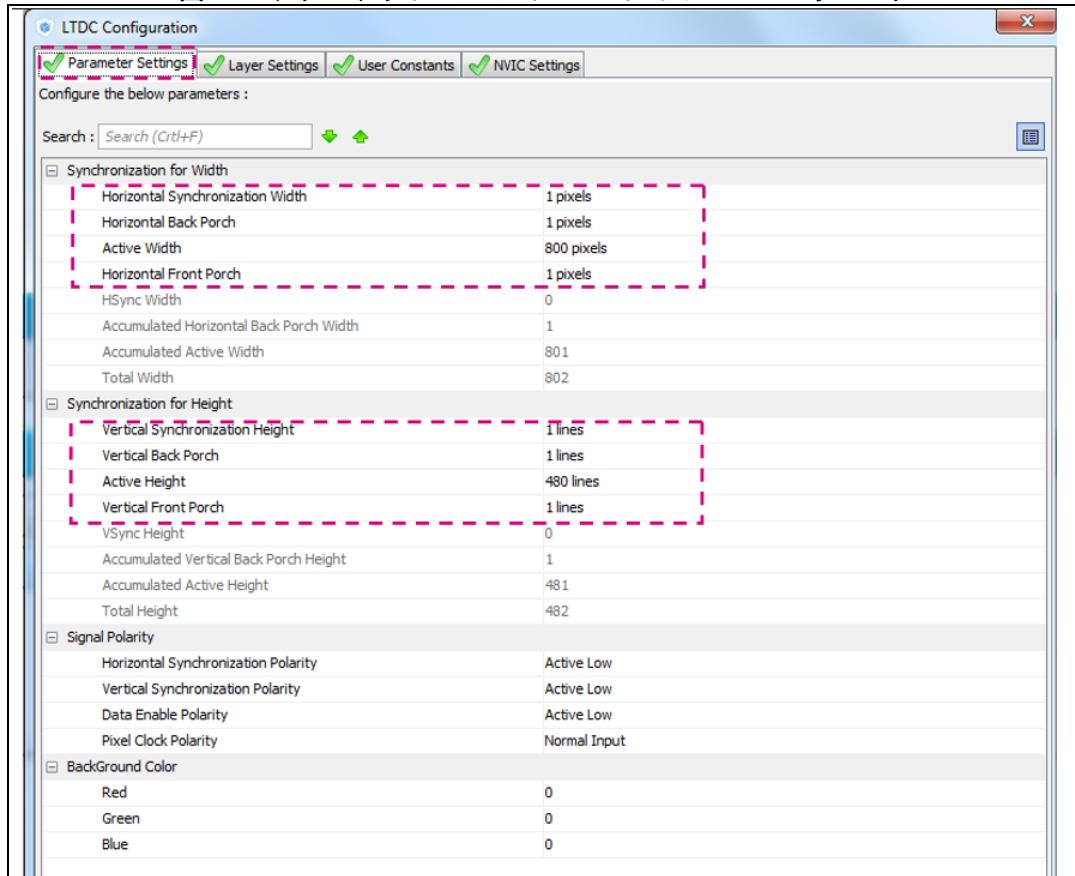

| 図 106. | ビデオ・モードでの LTDC のパラメータ設定                 | 114 |

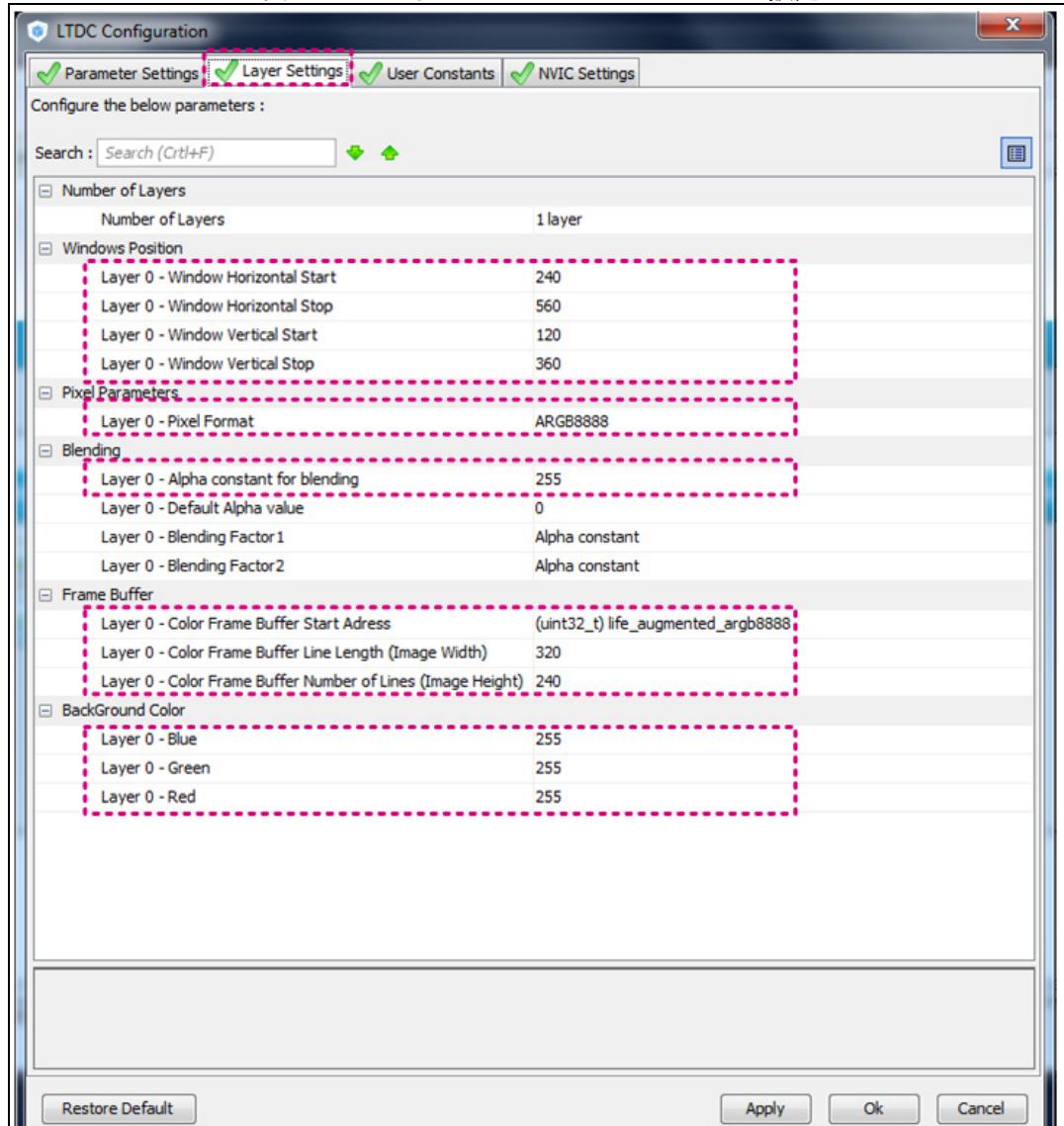

| 図 107. | ビデオ・モードでの LTDC のレイヤ設定                   | 115 |

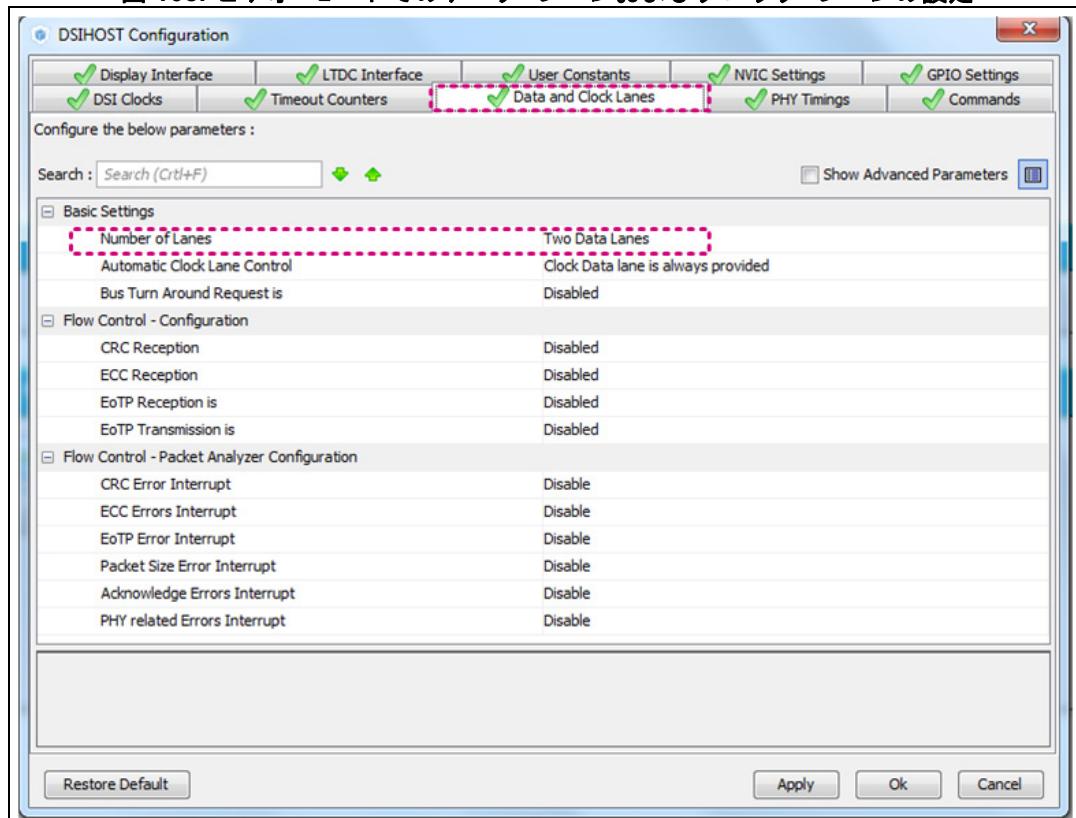

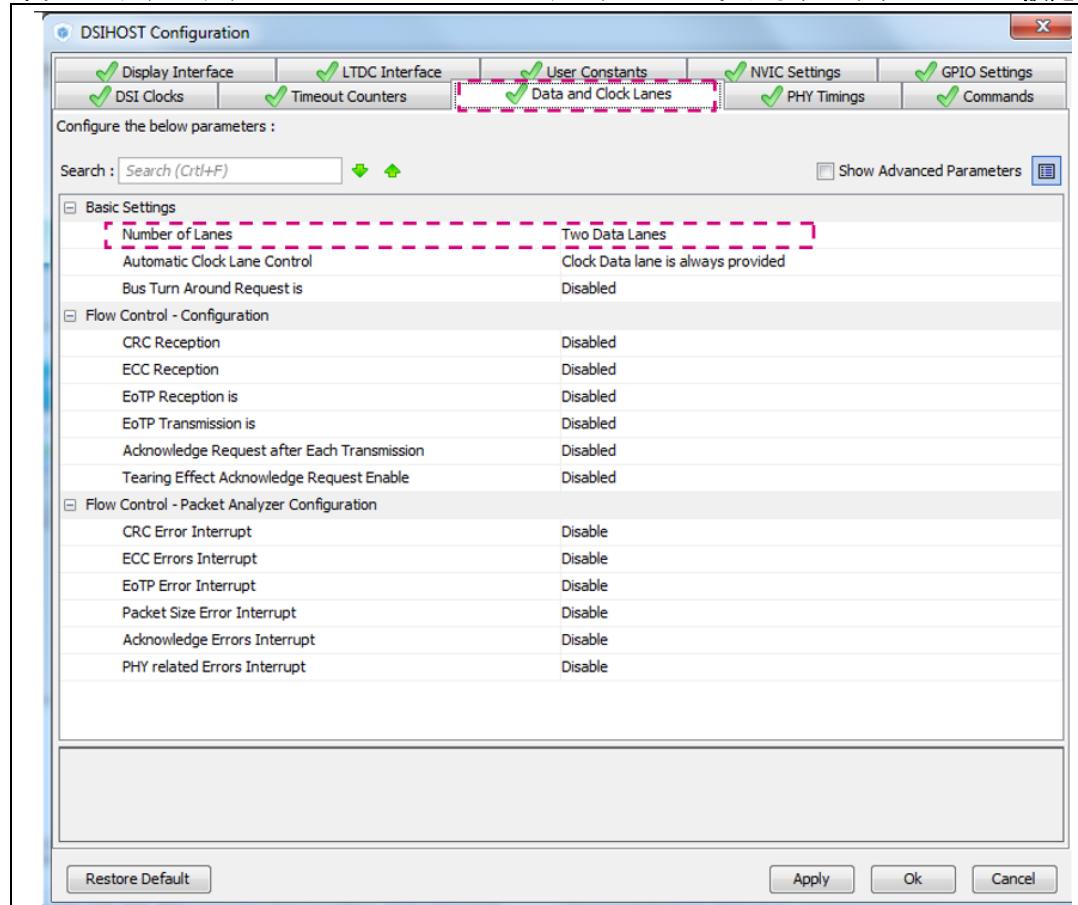

| 図 108. | ビデオ・モードでのデータ・レーンおよびクロック・レーンの設定          | 116 |

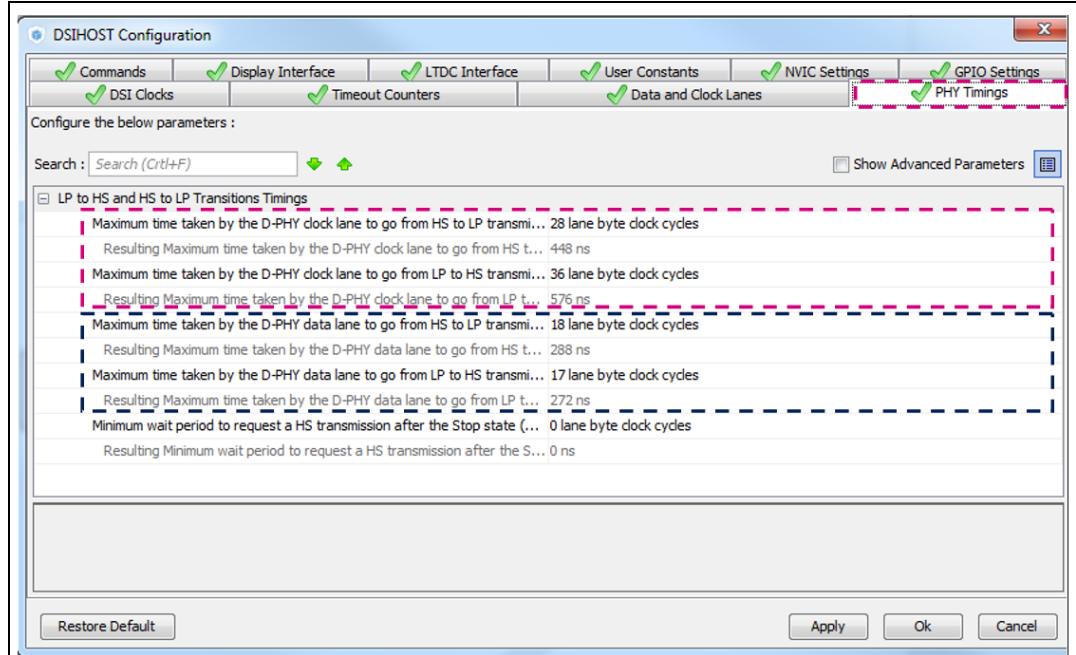

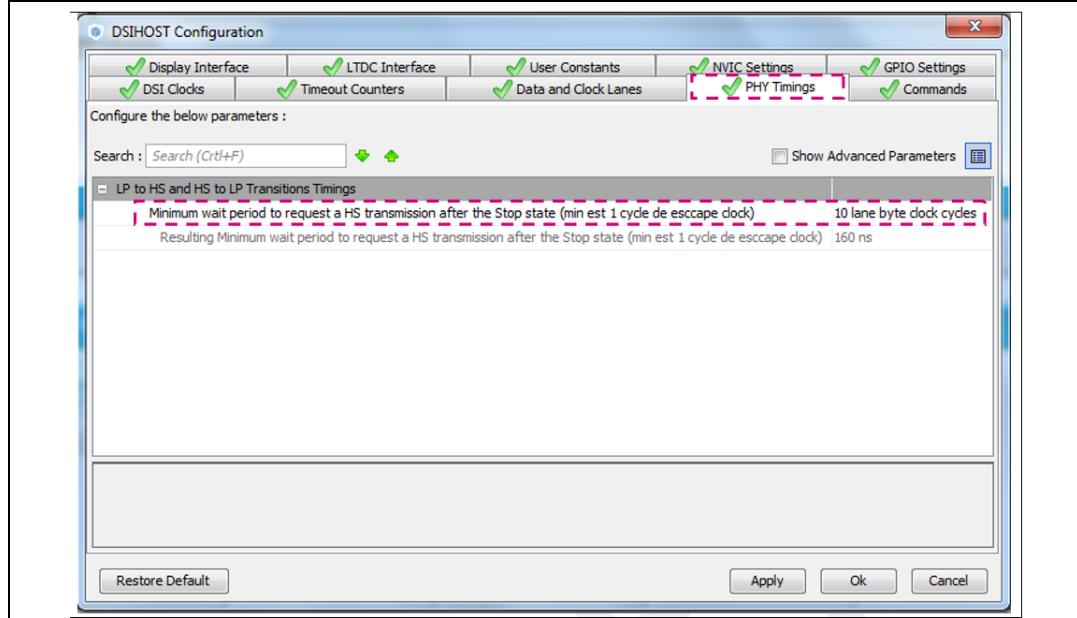

| 図 109. | ビデオ・モードでの PHY タイミング設定                   | 117 |

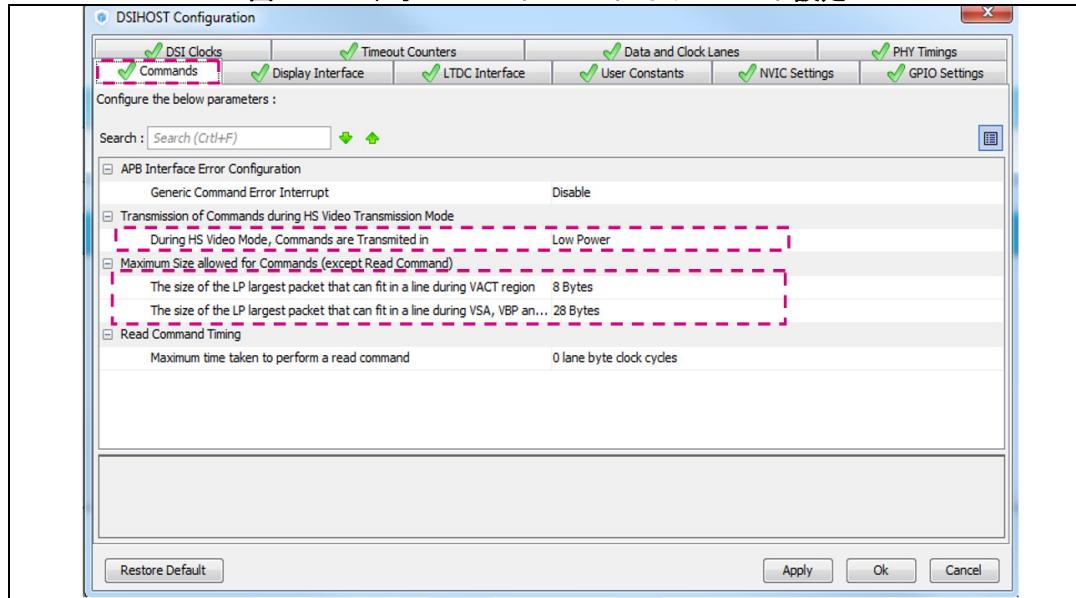

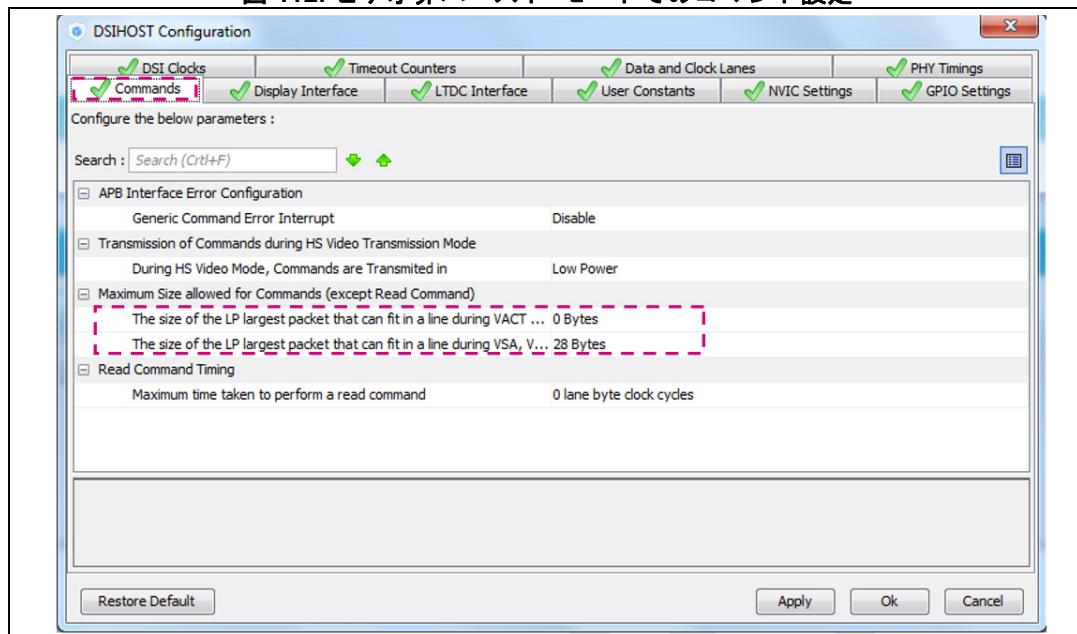

| 図 110. | ビデオ・バースト・モードでのコマンド設定                    | 118 |

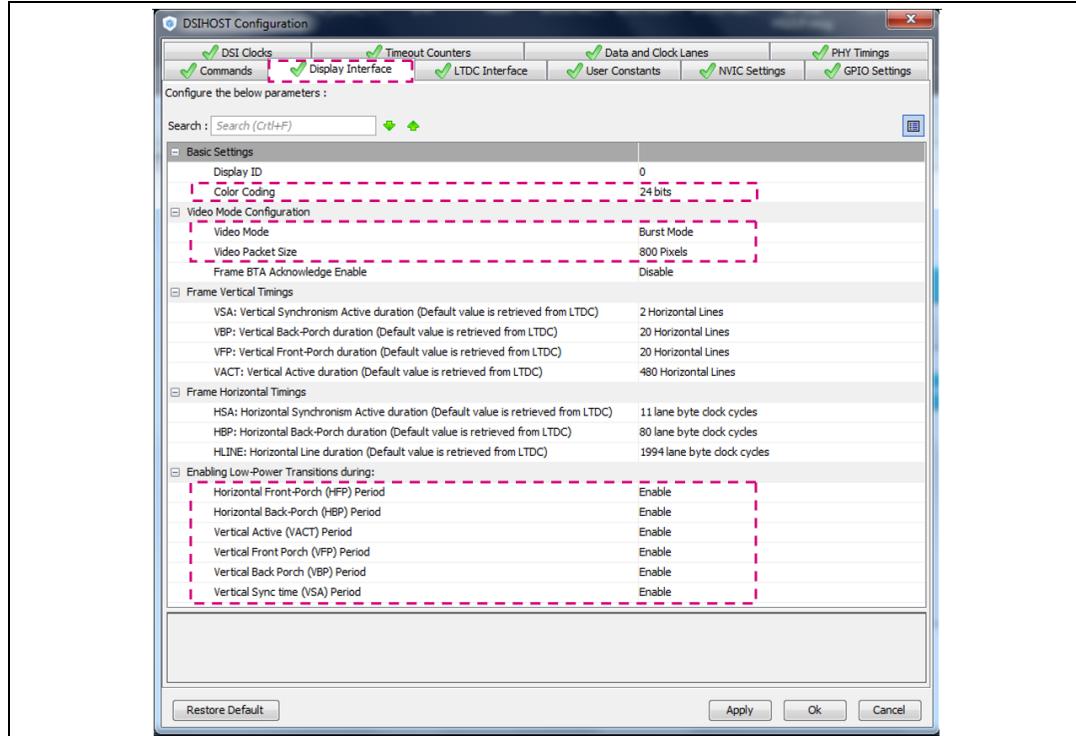

| 図 111. | ビデオ・バースト・モードでのディスプレイ・インターフェース設定         | 119 |

| 図 112. | ビデオ非バースト・モードでのコマンド設定                    | 123 |

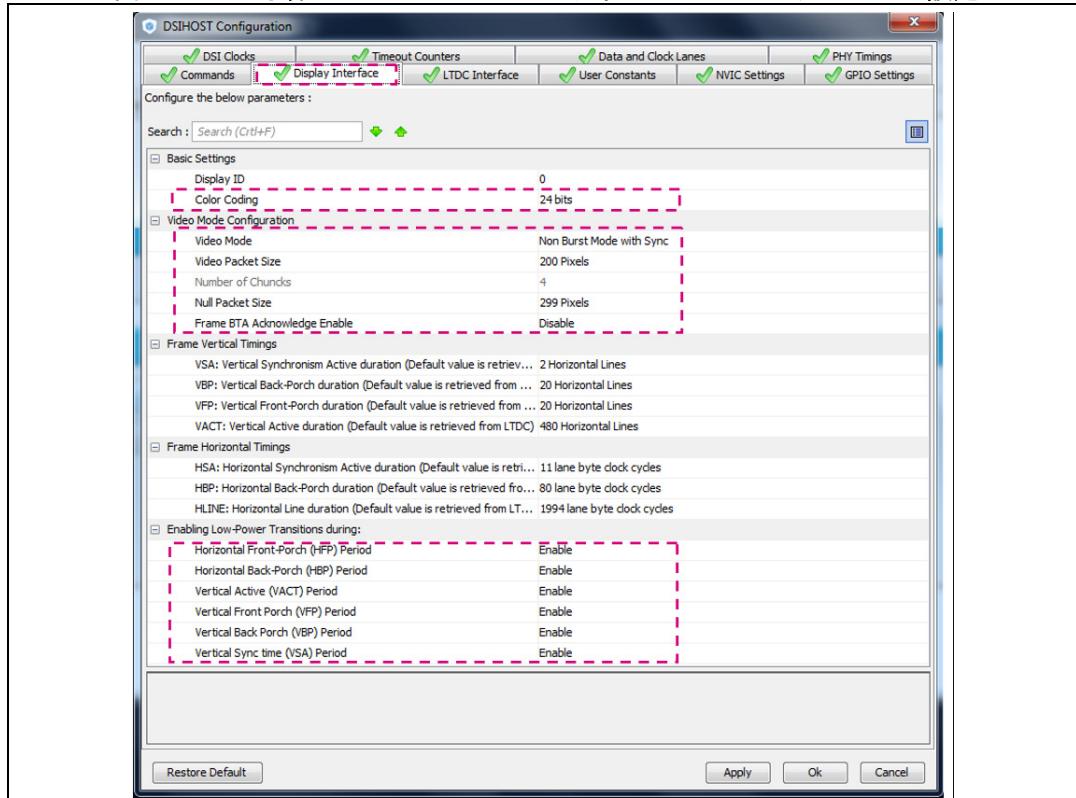

| 図 113. | ビデオ非バースト・モードでのディスプレイ・インターフェース設定         | 124 |

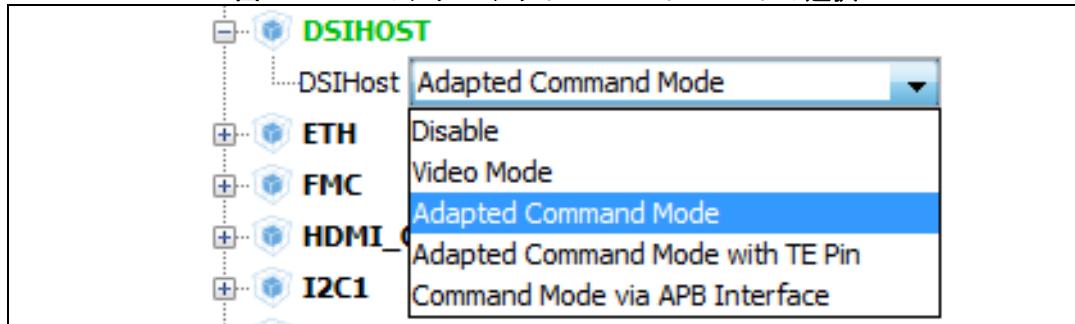

| 図 114. | DSI のアダプティッド・コマンド・モードの選択                | 125 |

| 図 115. | アダプティッド・コマンド・モードでの LTDC クロック設定          | 126 |

| 図 116. | アダプティッド・コマンド・モードでの LTDC パラメータ           | 127 |

| 図 117. | アダプティッド・コマンド・モードでのデータ・レーンおよびクロック・レーンの設定 | 128 |

| 図 118. | アダプティッド・コマンド・モードでの PHY タイミング設定          | 129 |

| 図 119. | アダプティッド・コマンド・モードでのコマンド送信設定              | 130 |

| 図 120. | アダプティッド・コマンド・モードでのディスプレイ・インターフェース設定     | 131 |

| 図 121. | 小型ディスプレイの駆動例                            | 138 |

| 図 122. | 大型ディスプレイの駆動例                            | 139 |

# 参考資料

## 1 標準および参照資料

このセクションでは、本書で用いられる標準および参照資料について説明します。

- ディスプレイ・シリアル・インターフェース（DSI）に関する MIPI® Alliance 仕様

v1.1 - 2011年11月22日

- ディスプレイ・バス・インターフェース（DBI-2）に関する MIPI® Alliance 仕様

v2.00 - 2005年11月16日

- ディスプレイ・コマンド・セット（DCS）に関する MIPI® Alliance 仕様

v1.1 - 2011年11月22日

- ディスプレイ・ピクセル・インターフェース（DPI-2）に関する MIPI® Alliance 仕様

v2.00 - 2005年9月15日

- 立体ディスプレイ形式（SDF）に関する MIPI® Alliance 仕様

v1.0 - 2011年11月22日

- D-PHY に関する MIPI® Alliance 仕様

v1.1 - 2011年11月7日

## 2 概要

ディスプレイ・シリアル・インターフェース (DSI) は、MIPI (モバイル産業プロセッサ・インターフェース) Alliance によって定義されたハイスピード・シリアル・プロトコルで、ディスプレイ・モジュールとホスト・プロセッサとの接続を可能にします。

STM32 は DSI ホスト (STM32F469/479、STM32F7x8/x9、STM32L4R9/S9) を組み込んだ市場で初のマイクロコントローラです。STM32 DSI ホストは、内部 MIPI D-PHY、専用 PLL および 1.2V 電圧レギュレータによって高度に統合されたソリューションを備えています。

DSI ホストは、最大1Gb/秒のハイスピード通信インターフェースを備えています。DSI ホストによって、マイクロコントローラは、外部ブリッジを必要とせずに、わずかなピン数のインターフェースでディスプレイと接続できます。DSI インタフェースは完全に設定可能で、今日市場で入手できる DSI 準拠ディスプレイと接続しやすくなっています。

アプリケーションでは、接続しやすさと DSI ホストで有効にされるピン数の削減というメリットがあり、PCB の複雑さやシステム全体のコストを抑えられます。

DSI ホストは、LCD-TFT ディスプレイ・コントローラ (LTDC) と密接に統合されており、アプリケーションの開発および移植が容易になっています。

STM32 DSI ホストには、スケーラブルなアーキテクチャが搭載されています。帯域幅の要件に応じて、ユーザは1つまたは2つのデータ・レーンを選択できます。

### 2.1 ディスプレイ・インターフェース接続

ディスプレイは、内部コントローラとフレームバッファがあるかどうかに応じて、主に2つのカテゴリに分けられます。

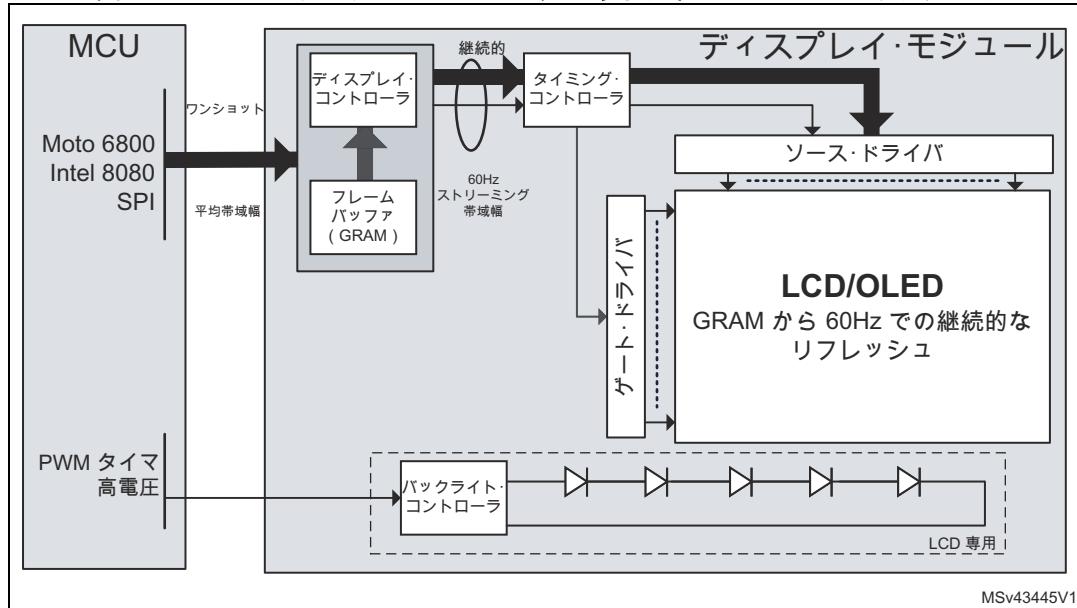

- ディスプレイ・コントローラおよびフレームバッファがあるディスプレイ・モジュール：これらは、表示するフレームを格納するグラフィック RAM (GRAM) を組み込んでおり、リフレッシュ動作を制御するディスプレイ・コントローラがあります。

マイクロコントローラがコマンドのセットを使用して、ディスプレイのフレームバッファの内容を更新します。

- ディスプレイはその内部コントローラとフレームバッファに応じて、マイクロコントローラからの介入なしでリフレッシュ動作を実行します。

- ディスプレイ・コントローラおよびフレームバッファがないディスプレイ・モジュール：これらのディスプレイは、マイクロコントローラに応じてリアルタイムのピクセル・データ・ストリームとビデオ・タイミング情報を送信して、ディスプレイをリフレッシュします。

これらの異なるタイプのディスプレイは、ディスプレイ・インターフェース接続の種類が異なることを意味します。

- コントローラとフレームバッファのあるディスプレイ・モジュールのインターフェース接続：

- SPI インタフェース：少数のピン（最大6ピン）を使用しますが、非常に低速であるため、アニメーションには適していません。

- パラレル・インターフェース：パラレル・バスを使用してコマンドとデータを送信するため、SPI インタフェースより高い帯域幅となります。

一般的なパラレル・インターフェースは、モトローラ6800バスとIntel 8080バスです。パラレル・インターフェースには、最大22ピン（データ信号に16ピン、制御信号に6ピン）が必要になります。

ディスプレイ・コントローラと GRAM フレームバッファはディスプレイ側にあります。マイクロコントローラがコマンドを使用して、ディスプレイの GRAM を更新します。更新は一度に行われます。

図 1に、フレームバッファとディスプレイ・コントローラを組み込んでいるディスプレイのアーキテクチャ、および対応するインターフェースの接続構成を示します。

図 1. フレームバッファとコントローラのあるディスプレイ・アーキテクチャ

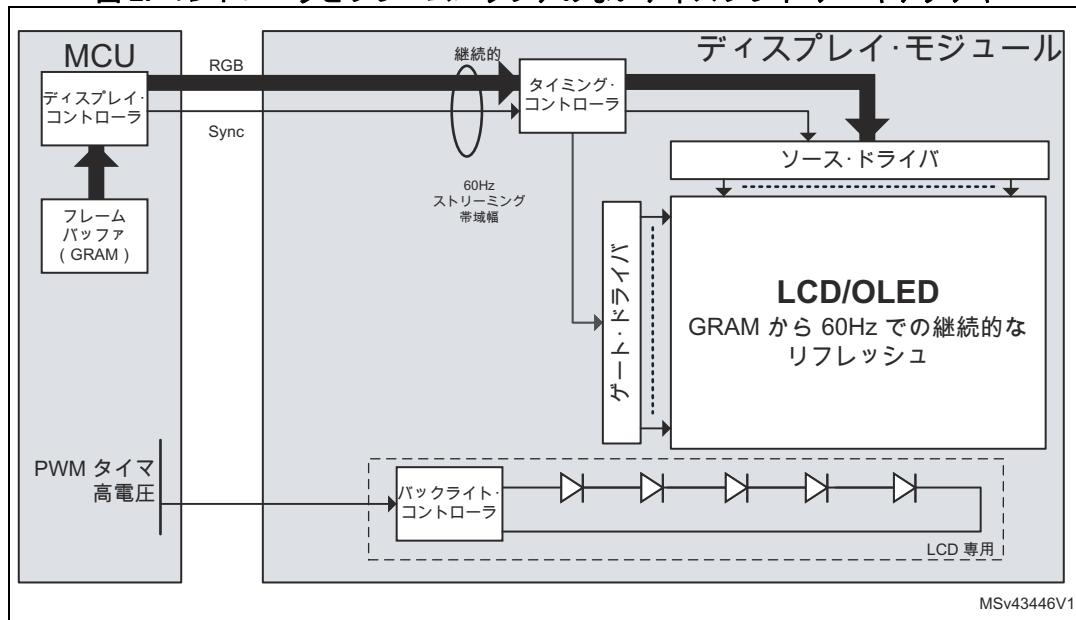

- コントローラとフレームバッファのないディスプレイ・モジュールのインターフェース接続：

- RGB インターフェース：マイクロコントローラがピクセル・データとビデオ・タイミング信号の両方を供給します。RGB インターフェースは非常に優れたリアルタイムのパフォーマンスが可能ですが、ディスプレイに供給するにはマイクロコントローラ側で高い帯域幅が必要になります。また、最大28ピン（RGB データに24ピン（R[0:7]G[0:7]B[0:7]）、同期信号に4ピン（PCLK、HSYNC、VSYNC、DATAEN））が必要になります。

- マイクロコントローラがピクセル・データとビデオ制御信号を継続的に生成して、ディスプレイを駆動させます。フレームバッファはマイクロコントローラ側にあります。

図 2には、フレームバッファとディスプレイ・コントローラのないディスプレイの標準的なアーキテクチャを示しています。

図 2. コントローラとフレームバッファのないディスプレイ・アーキテクチャ

## 2.2 MIPI ディスプレイ仕様標準

MIPI ディスプレイ・ワーキング・グループでは、ホスト・プロセッサとディスプレイの相互接続について指定しています。

このワーキング・グループはディスプレイを処理する既存のプロトコルを標準化するために、一連の仕様を定義しました。

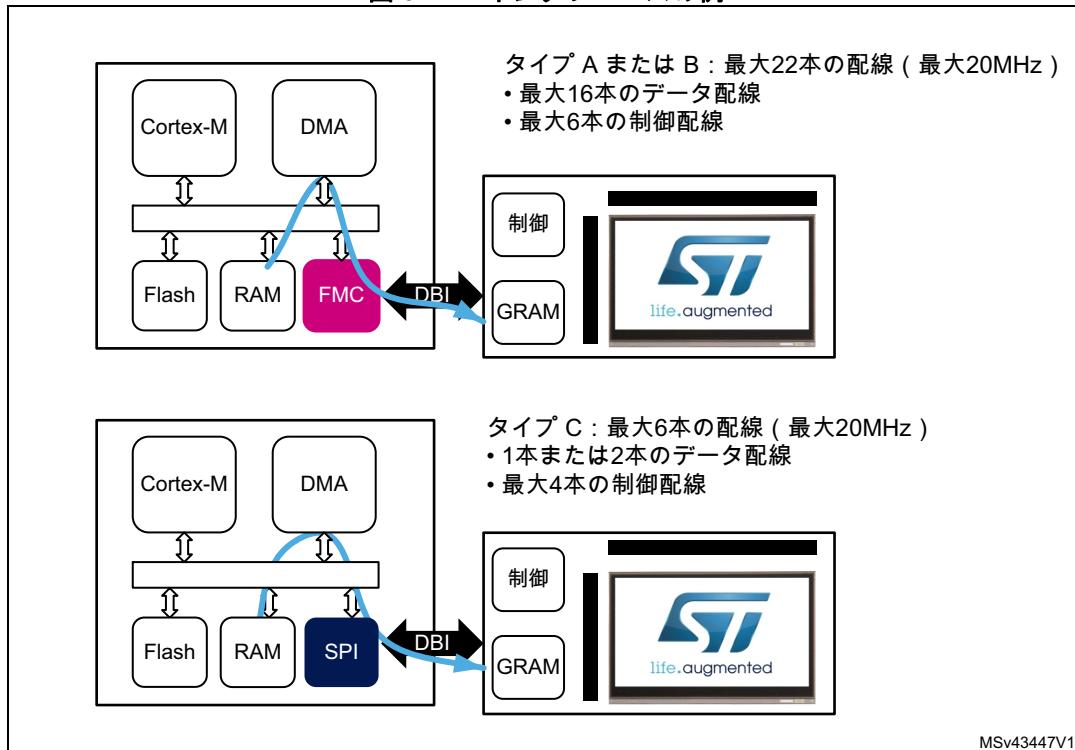

- ディスプレイ・バス・インターフェース (DBI) は、ディスプレイ・コントローラとフレームバッファのあるディスプレイ・モジュールを処理するプロトコルをカバーします。これによって3種類のインターフェース・タイプが定義されます。

- パラレル・モトローラ6800バスをサポートするタイプ A

- パラレル Intel 8080バスをサポートするタイプ B

- SPI インタフェースをサポートするタイプ C

- ディスプレイ・コマンド・セット (DCS) は、MIPI-DBI インタフェースをサポートするディスプレイで使用するコマンドを指定します。

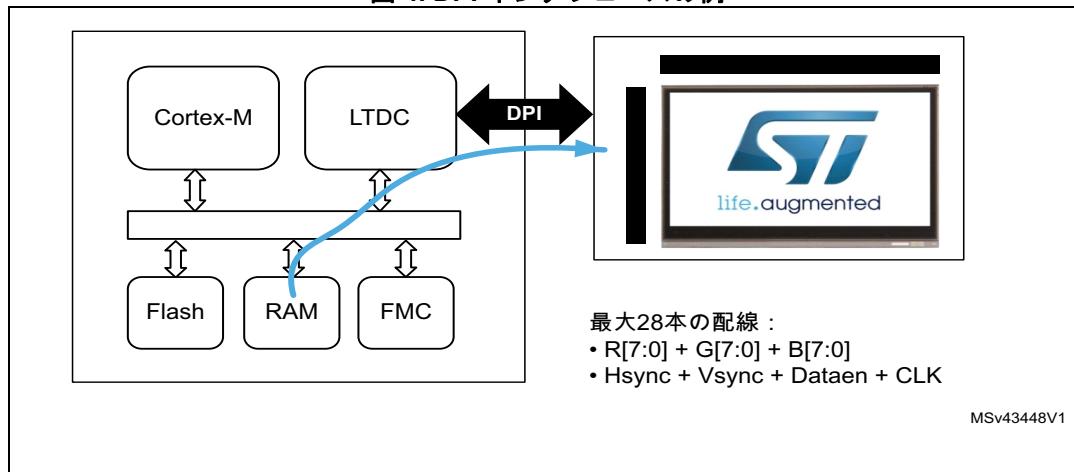

- ディスプレイ・ピクセル・インターフェース (DPI) は、コントローラとフレームバッファのないディスプレイを対象とした RGB インタフェースをサポートします。

MIPI ディスプレイ・ワーキング・グループは、最適な方法で最新のディスプレイを駆動させるための新しいプロトコルを開発しました。

マイクロコントローラとディスプレイの配線数を低減するために、MIPI ディスプレイ・ワーキング・グループは DSI を定義しました。

DSI は、DBI コマンド（いわゆるコマンド・モード）や DPI 信号（いわゆるビデオ・モード）をカプセル化し、連続でディスプレイに送信します。これにより、わずか4ピンまたは6ピンのインターフェースで標準的なディスプレイと接続でき、DPI と同じパフォーマンスを実現します。

この DSI は、1つの信号インターフェースで、想定されるすべてのディスプレイ・アーキテクチャ（ディスプレイ・コントローラとフレームバッファの有無にかかわらず）をサポートできます。

### 2.3 STM32 製品でサポートされるディスプレイ・インターフェース

すべての STM32 製品が、SPI インタフェースを介して MIPI-DBI タイプ C インタフェースをサポートしています。

MIPI-DBI タイプ A およびタイプ B のインターフェースは、F (S) MC (フレキシブル同期メモリ・コントローラ) を組み込んでいる STM32 によってサポートされています。FSMC を介したディスプレイ・インターフェース接続の詳細については、**TFT LCD interfacing with the high-density STM32F10xxx FSMC** (AN2790) のアプリケーション・ノートを参照してください。

図 3 に、DBI インタフェースを使用してディスプレイと接続する STM32 マイクロコントローラを示します。

図 3. DBI インタフェースの例

MIPI-DPI は、LTDC (LCD-TFT ディスプレイ・コントローラ) を組み込んでいる STM32 によってサポートされています。このテーマの詳細については、**LCD-TFT display controller (LTDC) on STM32 microcontrollers** (AN4861) のアプリケーション・ノートを参照してください。

# 参考資料

図 4に、DPI インタフェースを使用してディスプレイと接続する STM32 マイクロコントローラを示します。

図 4. DPI インタフェースの例

MIP-DSI は、DSI ホストを組み込んでいる新しい STM32 製品によってサポートされています (STM32F469/479、STM32F7x8/x9、STM32L4R9/S9)。

DSI インタフェースは、両方のタイプのディスプレイに接続できます。GRAM とディスプレイ・コントローラのあるディスプレイの場合、DSI ホストがコマンドを送信して DBI モードで GRAM をリフレッシュします。GRAM とディスプレイ・コントローラのないディスプレイの場合、DSI ホストが DPI モードでピクセル・データ・ストリームとビデオ同期イベントを送信します。

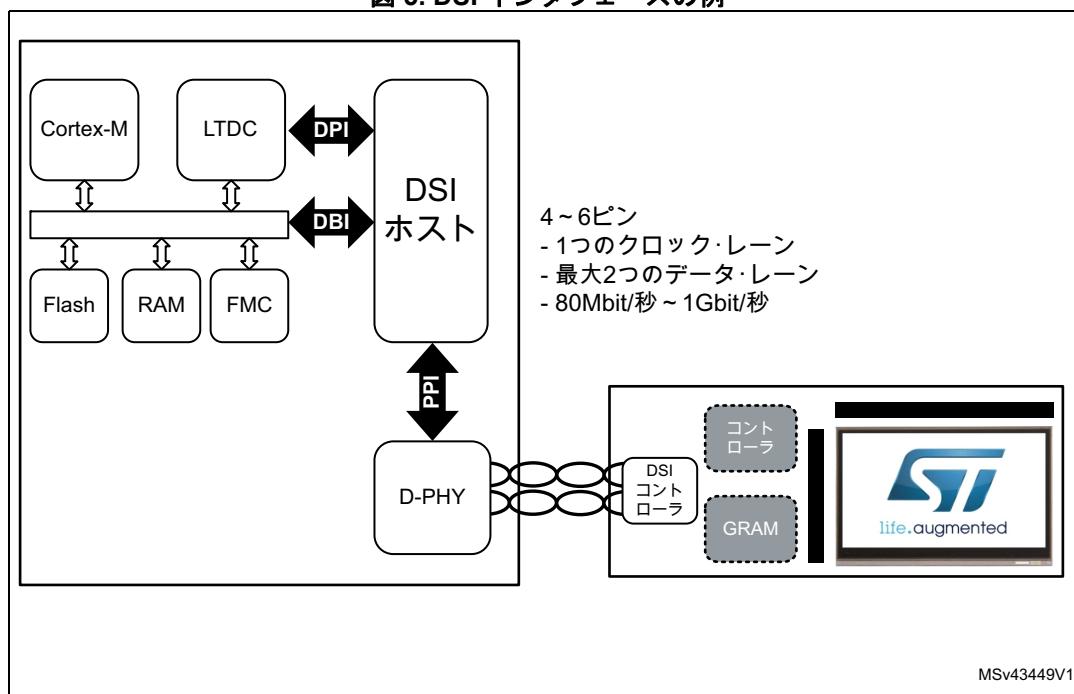

図 5 に、DSI インタフェースを使用してディスプレイと接続する STM32 マイクロコントローラを示します。

図 5. DSI インタフェースの例

# 参考資料

## 概要

AN4860

以下の表 1に、STM32 製品内の異なるディスプレイ・インターフェース構成についてまとめています。

表 1. STM32 製品のディスプレイ・インターフェース接続

| 従来の<br>ディスプレイ・<br>インターフェース | MIPI<br>ディスプレイ・<br>インターフェース<br>標準 | フレーム<br>バッファのある<br>ディスプレイの<br>サポート | フレーム<br>バッファのない<br>ディスプレイの<br>サポート | ピン数   | パラレル/<br>シリアル | STM32 サポート                                                                                |

|----------------------------|-----------------------------------|------------------------------------|------------------------------------|-------|---------------|-------------------------------------------------------------------------------------------|

| モトローラ6800                  | DBI タイプ A                         | 可能                                 | 不可                                 | 12~22 | パラレル          | F (S) MC 搭載の<br>全 STM32                                                                   |

| Intel 8080                 | DBI タイプ B                         | 可能                                 | 不可                                 | 12~22 | パラレル          | F (S) MC 搭載の<br>全 STM32                                                                   |

| SPI                        | DBI タイプ C                         | 可能                                 | 不可                                 | 4~6   | シリアル          | 全 STM32                                                                                   |

| RGB                        | DPI                               | 不可                                 | 可能                                 | 20~28 | パラレル          | LTDC 搭載の全<br>STM32<br>(STM32F4x9、<br>STM32F7x6、<br>STM32F7x7、<br>STM32F7x8、<br>STM32F7x9) |

| -                          | DSI                               | 可能<br>(DSI コマンド・<br>モード)           | 可能<br>(DSI ビデオ・<br>モード)            | 4~6   | シリアル          | STM32F469、<br>STM32F479、<br>STM32F7x8、<br>STM32F7x9                                       |

## 2.4 STM32 マイクロコントローラ全体での DSI ホストの可用性

DSI ホストは、STM32F469/479 ライン、STM32F7x8 ライン、STM32F7x9 ラインのマイクロコントローラによってサポートされています。表 2 で、STM32 マイクロコントローラの DSI の機能について詳しく説明しています。

表 2. DSI ホストを搭載した STM32 マイクロコントローラ

| 製品                             | 機能             |                        |                 |                     |                         |                                 |                                        |                                       |                                             |

|--------------------------------|----------------|------------------------|-----------------|---------------------|-------------------------|---------------------------------|----------------------------------------|---------------------------------------|---------------------------------------------|

|                                | Flash<br>(バイト) | オンチップ<br>SRAM<br>(バイト) | MIPI-DSI<br>ホスト | LTDC <sup>(1)</sup> | Quad-SPI <sup>(2)</sup> | JPEG<br>コーデック<br><sup>(3)</sup> | Chrom-Art<br>アクセラレータ<br><sup>(4)</sup> | 最大 AHB<br>周波数<br>(MHz) <sup>(5)</sup> | 最大 FMC<br>SRAM および<br>SDRAM<br>周波数<br>(MHz) |

| STM32F469/479<br>ライン           | 最大2M           | 384k                   | 可能              | 可能                  | 可能                      | 不可                              | 可能                                     | 180                                   | 90                                          |

| STM32F7x8 ライン<br>STM32F7x9 ライン | 最大2M           | 512k                   | 可能              | 可能                  | 可能                      | 可能                              | 可能                                     | 216                                   | 100                                         |

1. LTDC は、TFT-LCD ディスプレイ・コントローラです。STM32 の LTDC インタフェースの詳細については、アプリケーション・ノート AN4861 を参照してください。

2. Quad-SPI インタフェースで外部メモリと接続して、アプリケーションのサイズを拡張できます。STM32 の QSPI インタフェースの詳細については、アプリケーション・ノート AN4760 を参照してください。

3. JPEG コーデックは、JPEG のエンコードおよびデコードでハードウェアを高速化します。

4. Chrom-Art アクセラレータ<sup>®</sup>は、ST 独自の 2D グラフィック・アクセラレーション・エンジンです。

5. LTDC は AHB 速度でグラフィック・データをフェッチします。

## 2.5 DSI ホストの利点

DSI ホストには、他のディスプレイ・インターフェースと比べて多くの利点があります。

**表 3. 他のディスプレイ・インターフェースと比べた DSI ホストの利点**

| DSI の利点                     | コメント                                                                                                                         |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| ピン数の低減                      | DSI インタフェースによってピンの要件が大幅に低減されます。より少ないピン数で RGB インタフェースと同じ転送レートで伝送できます。たとえば、LTDC では28ピン必要になるところを、DSI では4ピンまたは6ピンまで低減されます。       |

| PCB の複雑さの軽減                 | 配線する信号が少なくなり、PCB ボードの複雑さが軽減され、余分な PCB 層が不要になります。                                                                             |

| EMI (電磁干渉) の低減              | DSI インタフェースでは、異なる信号構成であるため、EMI のレベルを低減します。                                                                                   |

| スケーラブルなアーキテクチャ              | DSI ホストには、スケーラブルなアーキテクチャが搭載されています。帯域幅の要件に応じて、ユーザは1つまたは2つのデータ・レーンを選択できます。                                                     |

| 高度に統合されたソリューション             | DSI ホストには、D-PHY、PLL、電圧レギュレータが組み込まれており、外部コンポーネントが不要になります。                                                                     |

| スマート・アーキテクチャ                | DSI ホストは LTDC コントローラと連携して機能し、ビデオ・エンジンとして動作します。                                                                               |

| 標準化されたインターフェース              | DSI ホストは、MIPI-DSI 仕様に記載されたすべての動作モードをサポートします。標準化されたインターフェースによって、DSI ディスプレイとの相互運用性が高まります。                                      |

| 最適化された動作モード                 | STM32 マイクロコントローラの DSI ホストには最適化されたモードがあり、GRAM (グラフィック RAM) を組み込んでいる DSI ディスプレイで使用できます。このモードは、マイクロコントローラ側での帯域幅とメモリ両方の要件を低減します。 |

| 至るところで使用できる DSI ディスプレイのメリット | DSI ディスプレイは、スマートフォンやタブレットで幅広く採用されています。その他数多くの組込みアプリケーションで非常に魅力的な製品となっています。                                                   |

## 2.6 スマート・アーキテクチャでの DSI ホスト

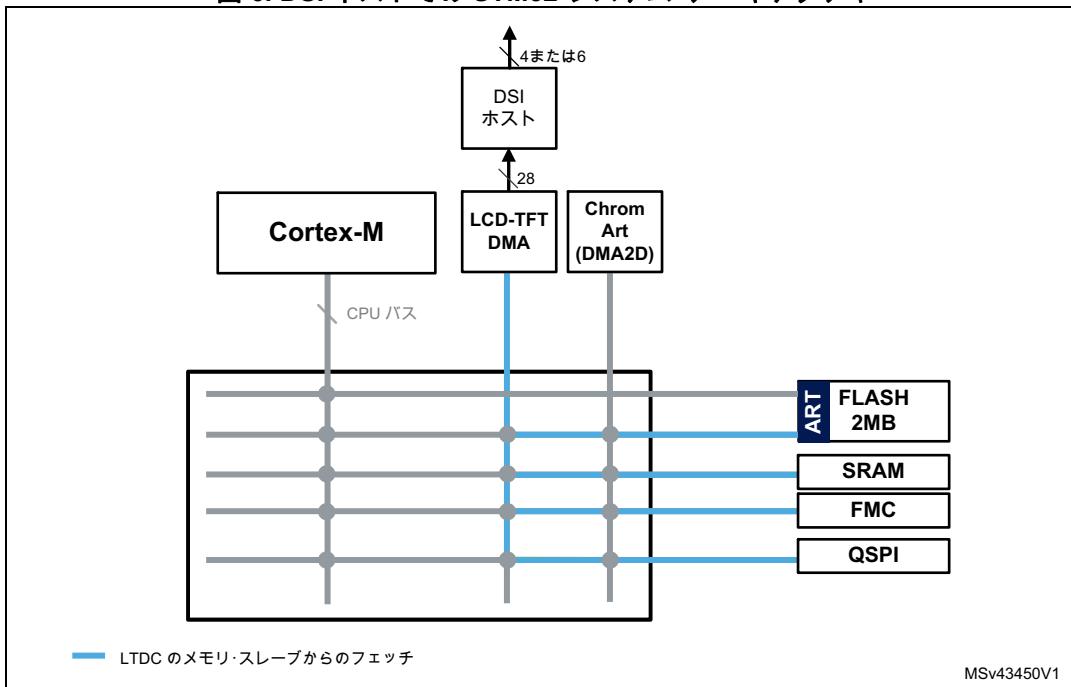

STM32 システム・アーキテクチャは、主にさまざまなマスタをスレーブと相互接続する 32-bit マルチレイヤ・バス・マトリクスで構成されています。

LTDC はバス・マトリクスでマスタとなります。これはさまざまなメモリ位置からグラフィック・データをフェッチします。

DSI ホストは LTDC ディスプレイ・コントローラをビデオ・ストリーマとして使用することで、容易に統合できます。

LTDC からのピクセルおよびビデオ・タイミング・データは、DSI ホストで直列化され、ディスプレイ・モジュールに送信されます。

図 6 に、STM32 システムでの DSI ホストの相互接続について示します。

# 参考資料

図 6. DSI ホストでの STM32 システム・アーキテクチャ

## 3 DSI の概要

DSI は、ホスト・プロセッサとディスプレイ・モジュールの間のインタフェースについて指定します。DPI-2、DBI-2 および DCS 標準で指定されたピクセル・フォーマットとコマンド・セットを採用することで、既存の MIPI Alliance の仕様に基づいて構築されます。

DSI ホストは、ピクセル・データ、信号イベント、コマンドを DSI パケットにカプセル化してからディスプレイに送信します。DSI ホストは、ディスプレイからステータスまたはピクセル情報を読み戻すことができます。

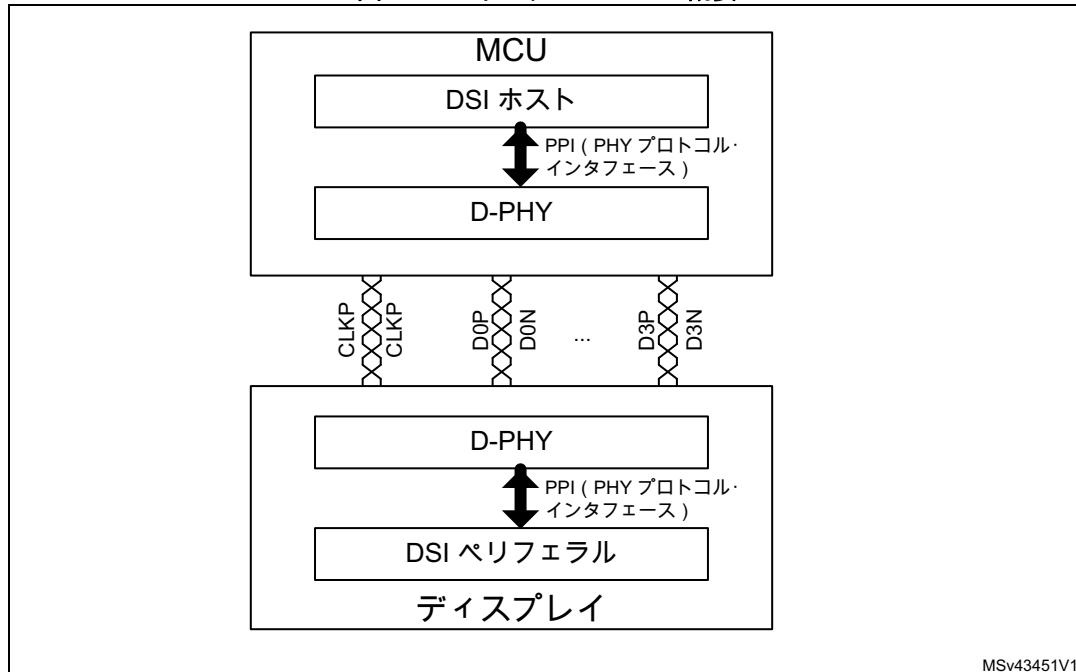

DSI ホストは、PHY プロトコル・インターフェース (PPI) を介してパラレル・データの形式で DSI パケットを D-PHY に送信します。D-PHY はパケットを直列化してシリアル・リンクで送信します。

ディスプレイ側で、このパケットはパラレル・データ、信号イベント、コマンドに分解されます。

図 7 に、ホストとディスプレイの間の DSI インタフェースの概要を示します。

図 7. DSI インタフェースの概要

MSv43451V1

## 3.1 DSI 動作モード

DSI 標準では、DSI ホストと DSI ディスプレイについて2種類の基本的な動作モード（コマンド・モードとビデオ・モード）を定義します。

### 3.1.1 コマンド・モード

コマンド・モードは、トランザクションがディスプレイ・モジュールへのコマンドとデータの送信（DCS 仕様で定義）の形式となる動作を指します。コマンド・モードをサポートするディスプレイ・モジュールには、コントローラとフレームバッファが組み込まれています。

ホスト・プロセッサは、コマンド、パラメータ、データをディスプレイ・コントローラに送信することで、ディスプレイ・モジュールでの動作を間接的に制御します。

### 3.1.2 ビデオ・モード

ビデオ・モードは、ホスト・プロセッサからディスプレイ・モジュールへの転送がリアルタイムのピクセル・ストリームの形式となる動作を指します。ディスプレイ・モジュールはホスト・プロセッサに依存しており、表示された画像でちらつきやその他の視覚的な乱れを回避する十分な帯域幅で画像データを提供します。

## 3.2 DSI 物理層

DSI 物理層は、転送元同期、ハイスピード（HS）および低消費電力（LP）のリンクについて記載した MIPI D-PHY 仕様に基づいています。

### 3.2.1 [PHY 設定例]

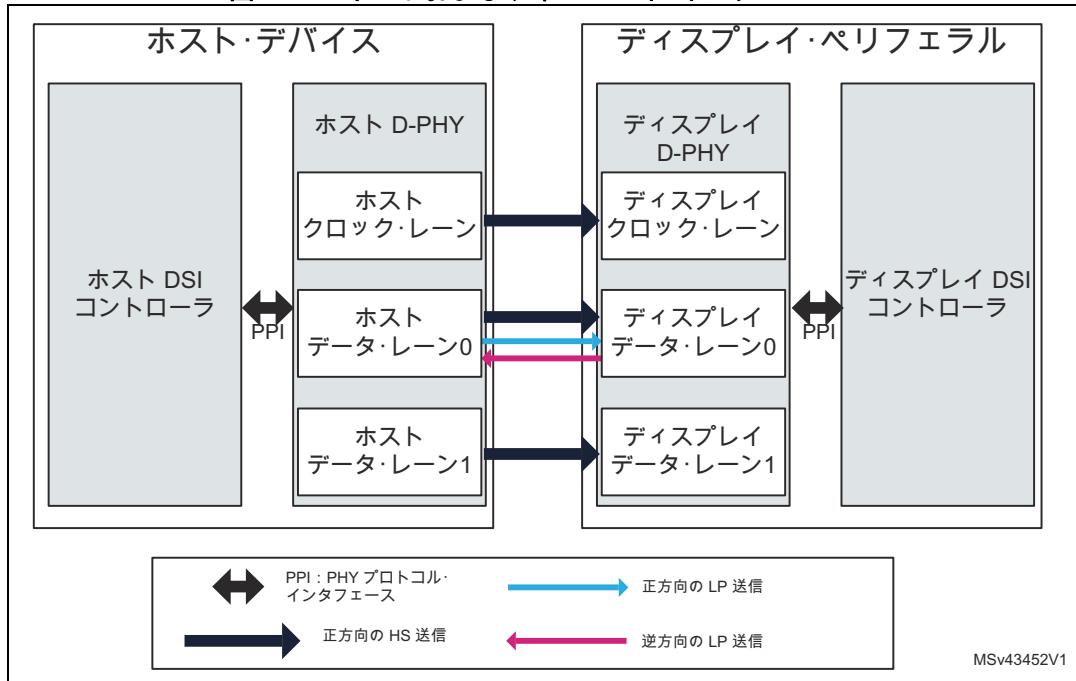

このリンクは、ホスト・プロセッサによって供給される1つのダブル・データ・レート HS クロック・レーンと、1~4つのシリアル・データ・レーンによって構成されています。

最小リンク設定では、クロック・レーン1つとデータ・レーン1つが含まれています。

各レーンは、HS 送信中の低振幅差動モードおよび低消費電力モード中のシングル・エンド・モードで駆動される1組の配線で構成されています。

DSI は、正方向（ホストからディスプレイ）または逆方向（ディスプレイからホスト）で通信できます。

逆方向の通信（ディスプレイからホスト）はすべて低消費電力モードでデータ・レーン0のみを使用して実行されます。

コマンド・モードのシステムでは、レーン0は双方向となりますが、ビデオ・モードのシステムでは単方向または双方向で使用できます。

その他すべてのレーンは単方向となり、ハイスピード・モードのみサポートします。

図 8 に、1つのクロック・レーンと2つのデータ・レーンでの PHY の設定例を示します。

図 8. DSI ホストおよびディスプレイ・インターフェース

### 3.2.2 PHY の信号モード

DSI 物理層には2種類の信号モードがあります。

- ・ ハイスピード (HS) モード：レーン信号が最大1.5Gbit/秒の速度での差動モードで使用される高速データ送信に使用されます。

- ・ 低消費電力 (LP) モード：主に制御目的に使用されます。レーンの信号のペアは、最大転送レート10Mbit/秒でのシングル・エンド・モードで独立して駆動させることができます。

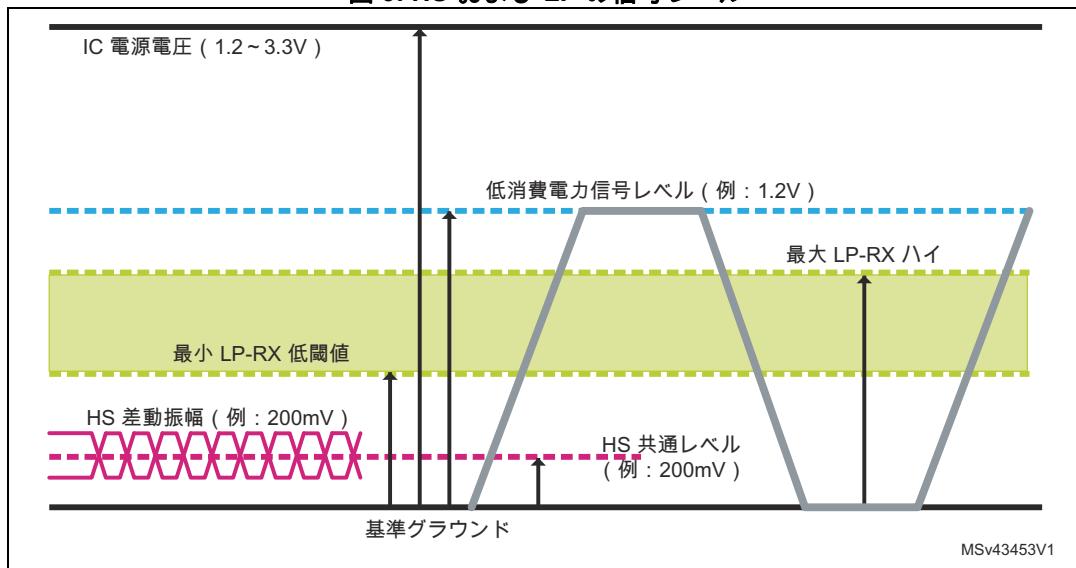

図 9 に、DSI 物理層での HS および LP の信号レベルを示します。

図 9. HS および LP の信号レベル

### データ・レーンの状態

DSI トランスマッタには、HS-0 または HS-1 に個別にラインを駆動させる HS トランスマッタと、シングル・エンド・モードで差分ペア ( $D_P$  および  $D_N$ ) の各ラインを独立して駆動させる2つの LP トランスマッタがあります。これにより、HS トランスマッタでは想定されるレーンの状態が2つ (HS-0 および HS-1)、LP トランスマッタではレーンの状態が4つ (LP-00, LP-10, LP-01, LP-11) となります。

レーンの状態は動作モードを反映し、別のモードへの遷移に使用されます (表 4 を参照)。

表 4. データ・レーンの状態と動作モード

| 状態コード | $D_P$ ライン<br>レベル | $D_N$ ライン<br>レベル | ハイスピード<br>バースト・モード | 低消費電力<br>制御モード | 低消費電力<br>エスケープ・モード |

|-------|------------------|------------------|--------------------|----------------|--------------------|

| HS-0  | HS ロー            | HS ハイ            | 差分 0               | x              | x                  |

| HS-1  | HS ハイ            | HS ロー            | 差分 1               | x              | x                  |

| LP-00 | LP ロー            | LP ロー            | x                  | ブリッジ           | 空間                 |

| LP-01 | LP ロー            | LP ハイ            | x                  | HS リクエスト       | マーク-0              |

| LP-10 | LP ハイ            | LP ロー            | x                  | LP リクエスト       | マーク-1              |

| LP-11 | LP ハイ            | LP ハイ            | x                  | STOP           | (STOP に戻る)         |

### 3.2.3 データ・レーンの動作モード

データ・レーンの動作モードには、制御、ハイスピード転送、エスケープの3種類があります。

#### 制御モード

リセット後、データ・レーンは制御モード (LP-11 STOP 状態) になります。その他すべてのモードは制御モードで開始して終了します。

#### ハイスピード転送モード

ハイスピード転送は開始して STOP 状態 (LP-11) で終了します。

ホストとディスプレイの同期を有効にするために、リーダー・シーケンスとトレーラー・シーケンスが追加されます。これらは実際のペイロード・データの一部ではないため、レシーバ側で削除されます。

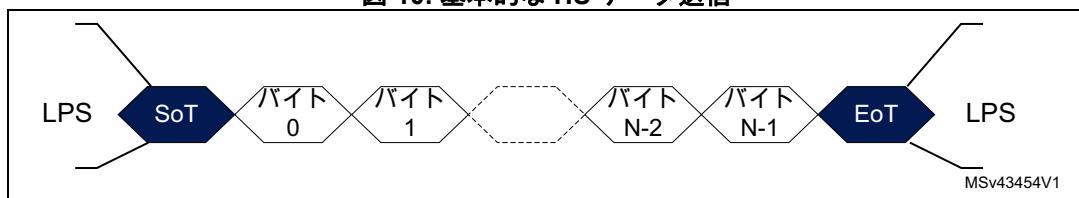

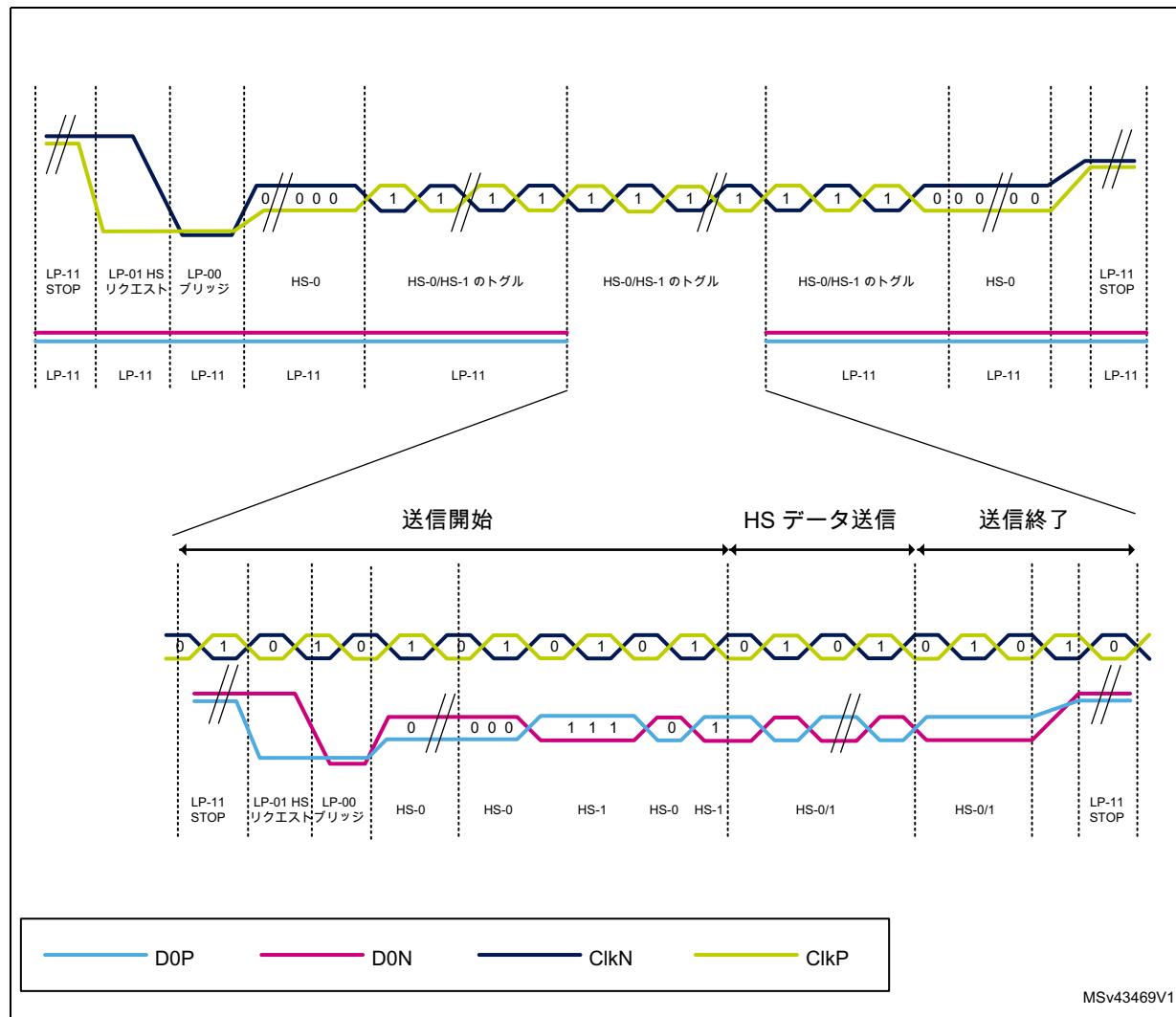

図 10 に基本的な HS 送信の例を示します。

図 10. 基本的な HS データ送信

## 1. 送信開始 (SoT) 手順

HS リクエスト (LP-11、LP-01、LP-00) を受信すると、データ・レーンは HS モードに移行します。ホストが HS-0 を駆動することで開始し、HS 同期シーケンス (00011101) を駆動してスレーブの同期を許可します。

その後、ホストは HS データの送信を続行します。

## 2. 送信終了 (EoT) 手順

HS バーストの終了後、ホストは終端シーケンスを送信します。

終端シーケンスは、送信した最終データ・ビットの逆です。最終ペイロード・ビットが HS-0 の場合、トランスマッタは終端シーケンスとして HS-1 を送信します。そうでない場合は、HS-0 を送信します。

データ・レーンは STOP 状態 LP-11 を経て制御モードに戻ります。

図 11. ハイスピード・データ転送モード

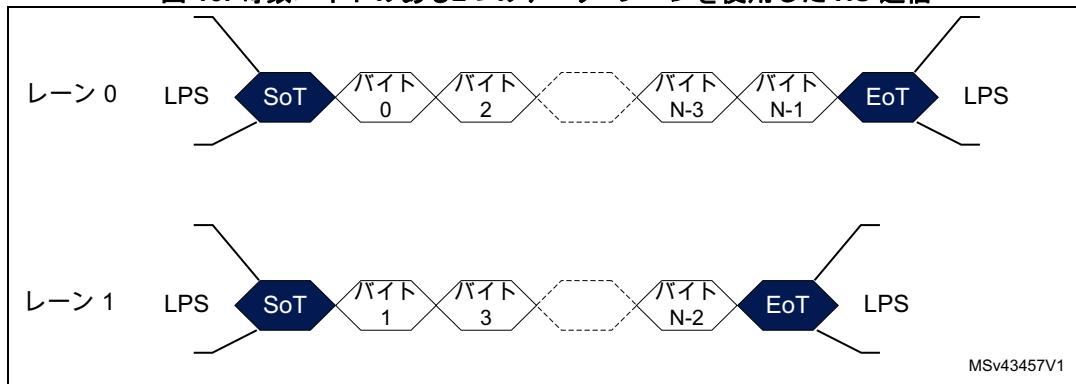

## 3. マルチレーン・サポート

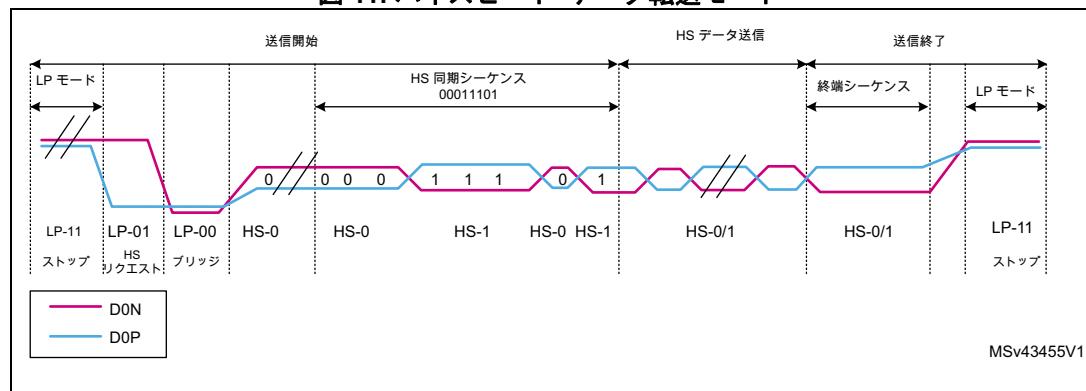

HS 送信は1つ以上のデータ・レーンを使用して実行できます。

図 12 に、2つのデータ・レーンを使用した HS 送信の例を示します。

図 12. 2つのデータ・レーンを使用した HS 送信

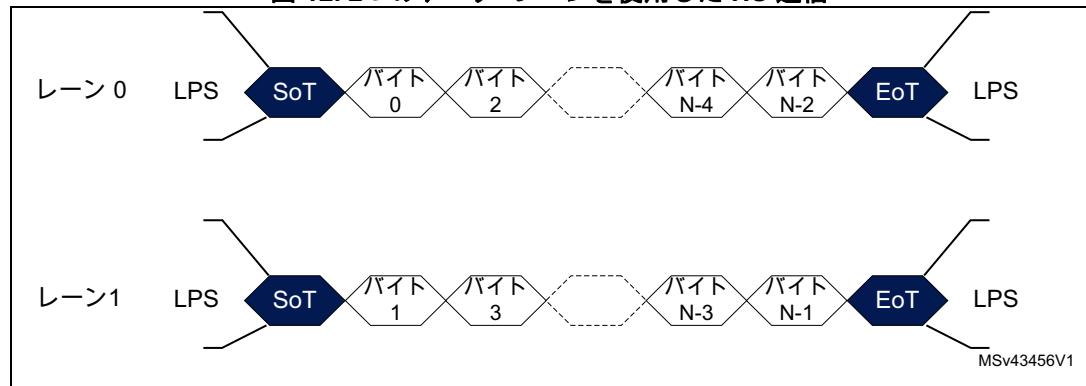

送信したバイト数がレーン数の整数倍ではない場合、一部のレーンが他のレーンより先に HS 送信を完了する場合があります。

図 13 に、2つのデータ・レーンを使用し、データ・レーン0より先にレーン1の HS 送信を完了させて EoT シーケンスを発行する奇数バイトがある例を示します。

# 参考資料

図 13. 奇数バイトのある2つのデータ・レーンを使用した HS 送信

MSv43457V1

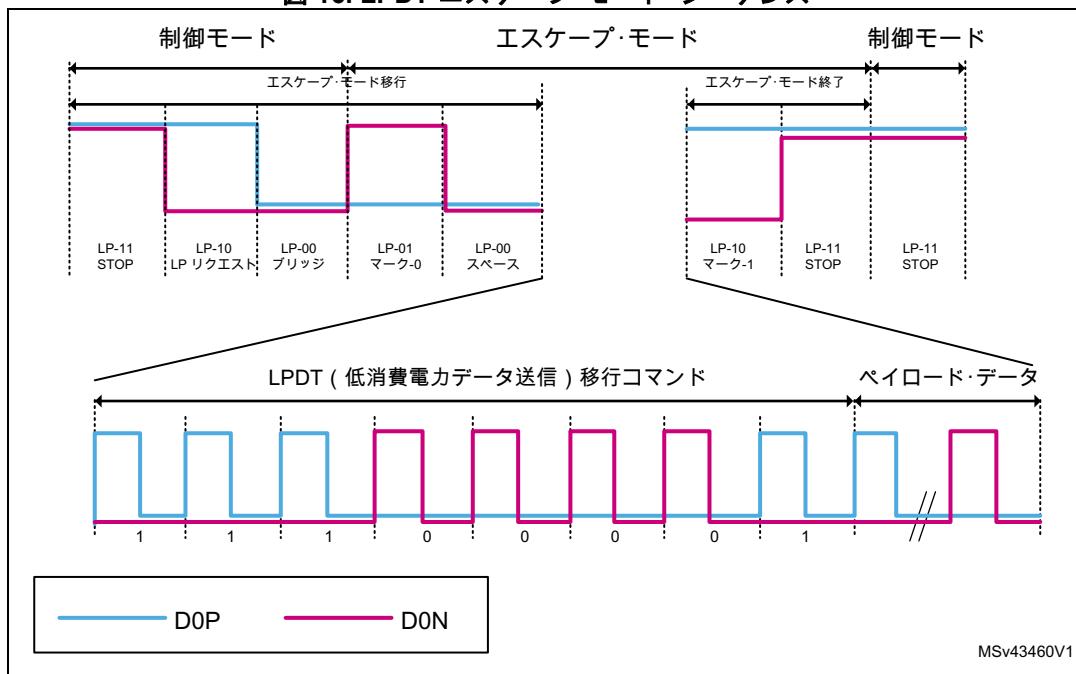

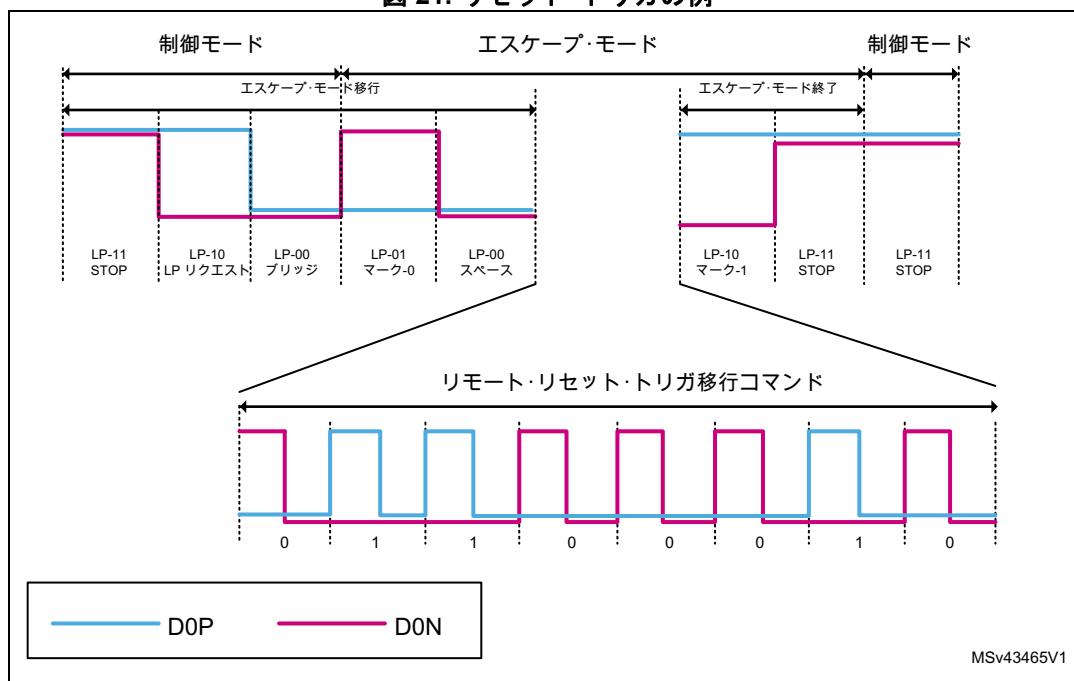

## エスケープ・モード

データ・レーンは、エスケープ・モードのリクエスト手順 (LP-11, LP-10, LP-00, LP-01, LP-00) でエスケープ・モードに移行する場合があります。

エスケープ・モードに移行すると、トランスマッタはリクエストされたアクションを示す 8-bit 移行コマンドを送信します。

エスケープ移行コマンドに次のものが含まれる場合があります。

- 低消費電力データ送信 (LPDT)

- 超低消費電力状態 (ULPS)

- リモート・トリガ

[表 5](#) に、エスケープ・モードでサポートされる異なる移行コマンドを示します。

表 5. エスケープ・モードのコマンド

| エスケープ・モードのアクション | コマンド・タイプ | 移行コマンド・パターン |

|-----------------|----------|-------------|

| 低消費電力データ送信      | モード      | 11100001    |

| 超低消費電力状態        | モード      | 00011110    |

| 未定義-1           | モード      | 10011111    |

| 未定義-2           | モード      | 11011110    |

| リセット・トリガ        | トリガ      | 01100010    |

| ティアリング効果トリガ     | トリガ      | 01011101    |

| 確認応答トリガ         | トリガ      | 00100001    |

| 不明-5            | トリガ      | 10100000    |

# 参考資料

注： 低消費電力データ送信およびトリガ・メッセージはレーン0でのみサポートされます。

エスケープ・モードは、エスケープ・モード終了手順 (LP-10、LP-11) を経て終了します。

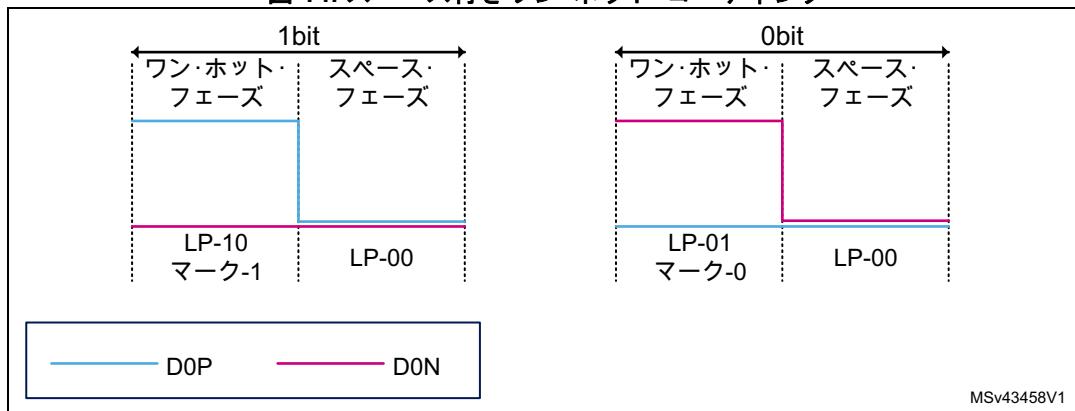

## 1. スペース付きワン・ホット・コーディング

エスケープ・モードでは、移行コマンドと低消費電力データ送信 (LPDT) 通信はスペース付きワン・ホット・コーディングでコードされ、各マーク状態がスペース状態でインタリーブされることを意味します。

そのため、各シンボルがワン・ホット・フェーズ（マーク-0 またはマーク-1）とスペース・フェーズの2つの部分で構成されます。

スペース付きワン・ホット・コーディングには高い信頼性と、データ・ストリームからクロックを抽出する機能が備わっています。ただし、これには、送信したデータの倍の帯域幅が必要になります（図 14 を参照）。

図 14. スペース付きワン・ホット・コーディング

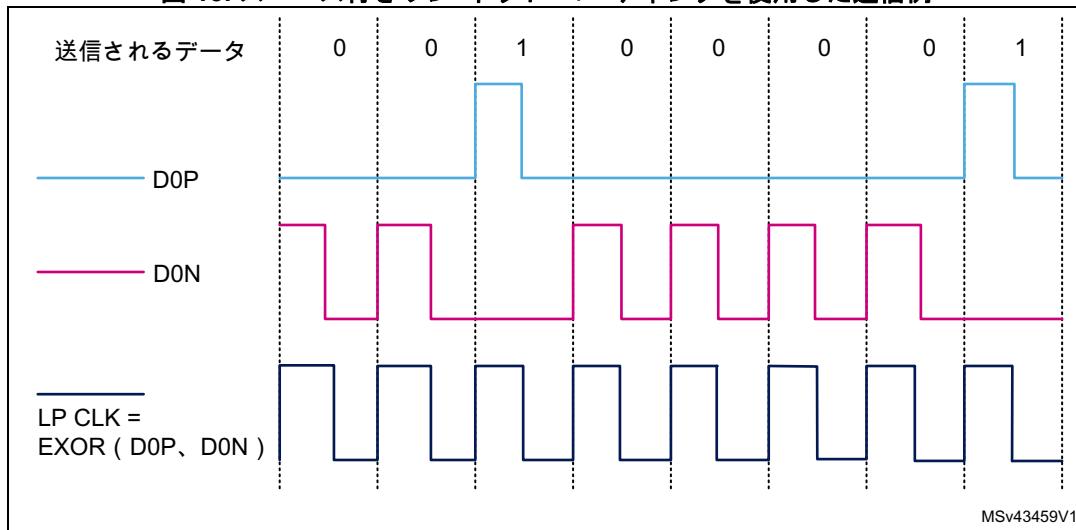

## 2. 低消費電力クロック

トランスマッタは、低消費電力通信に低消費電力クロック信号を使用しますが、このクロックは受信側に送信されません。

データはスペース付きワン・ホット・ビット・エンコーディングでセルフ・クロック供給され、レシーバは排他的論理和閾値で2つのラインの信号からクロックを取得できます。

図 15 に、スペース付きワン・ホット・エンコーディングを使用したデータ送信の例を示します。LP クロックは、2つの信号 (D0P および D0N) に排他的論理和閾値を適用することで取得されます。

# 参考資料

図 15. スペース付きワン・ホット・コーディングを使用した通信例

### 3. 低消費電力データ転送

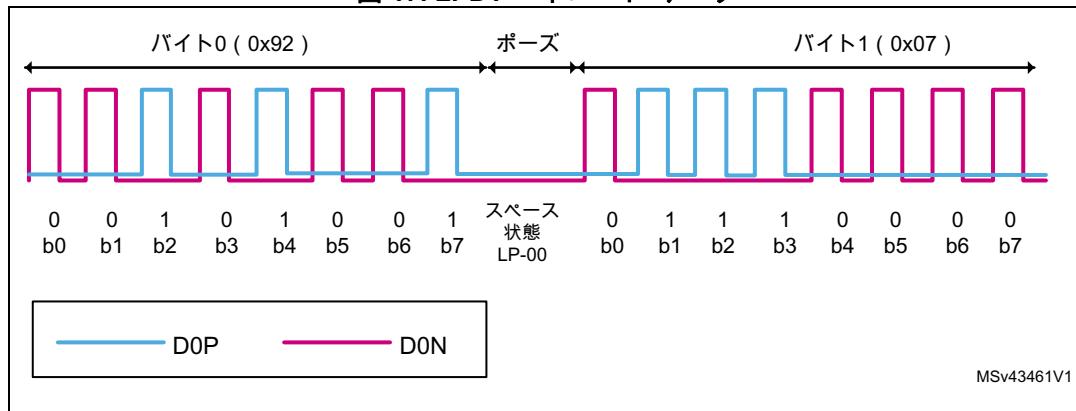

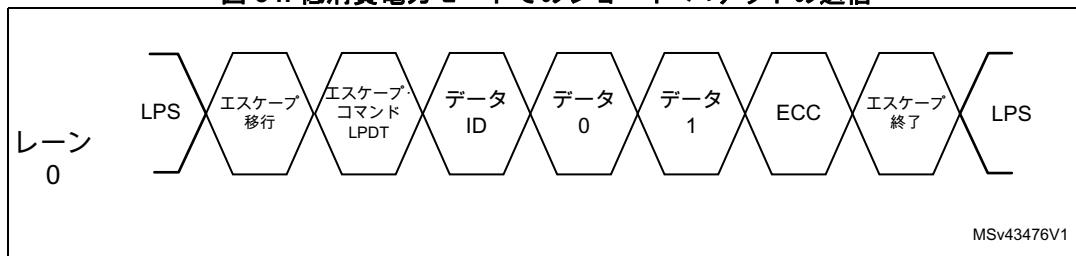

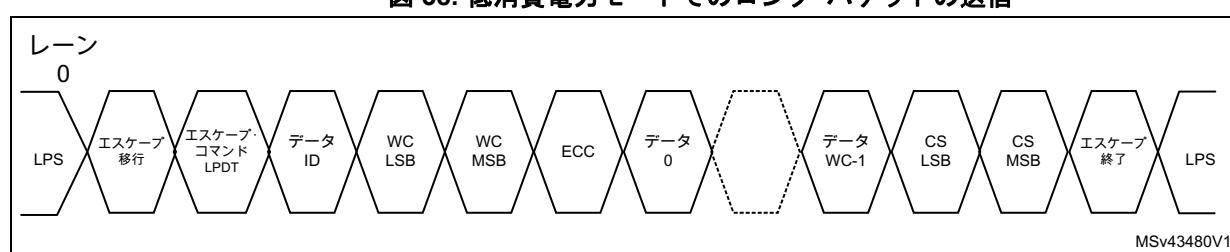

エスケープ・モード移行シーケンス後、トランスマッタは LPDT 移行コマンド (11100001) に続いて実際のペイロード・データを送信します。図 16 に、LPDT エスケープ・モード・シーケンスを示します。

図 16. LPDT エスケープ・モード・シーケンス

# 参考資料

データは LSB (最下位ビット) ファーストで送信され、マルチバイト・ペイロードの場合は最下位バイトがまず転送されます。

LPDT 時、ラインでスペース状態 (LP-00) を維持することでレーンをポーズできます。図 17 に、LPDT ペイロード・データ送信の例を示します。

図 17. LPDT ペイロード・データ

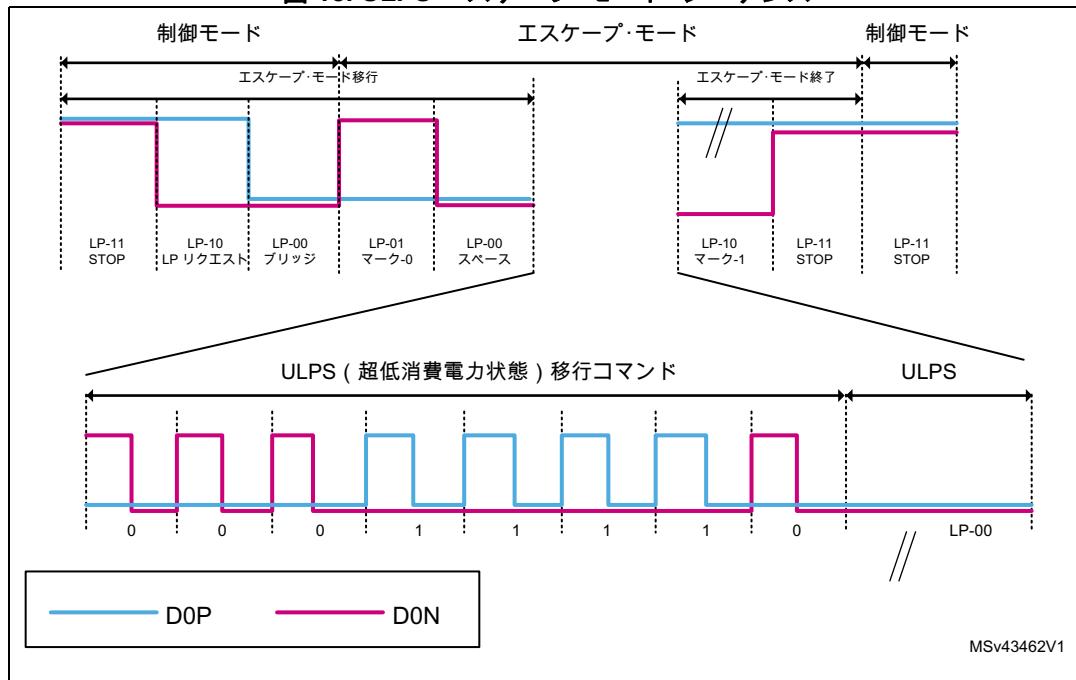

#### 4. 超低消費電力状態

消費電力を削減するために、DSI ホストがデータ・レーンを超低消費電力状態 (ULPS) にする場合があります。これは次の手順に従って行います。

- エスケープ・モード (LP-11、LP-10、LP-00、LP-01、LP-00) に移行します。

- ULPS 移行コマンド (00011110) を送信します。

- レーンの信号を LP-00 状態で維持します。

ULPS 状態はマーク-1 (LP-10) に続いて STOP 状態 (LP-11) になって終了します。

図 18 に、ULPS エスケープ・モード・シーケンスを示します。

図 18. ULPS エスケープ・モード・シーケンス

# 参考資料

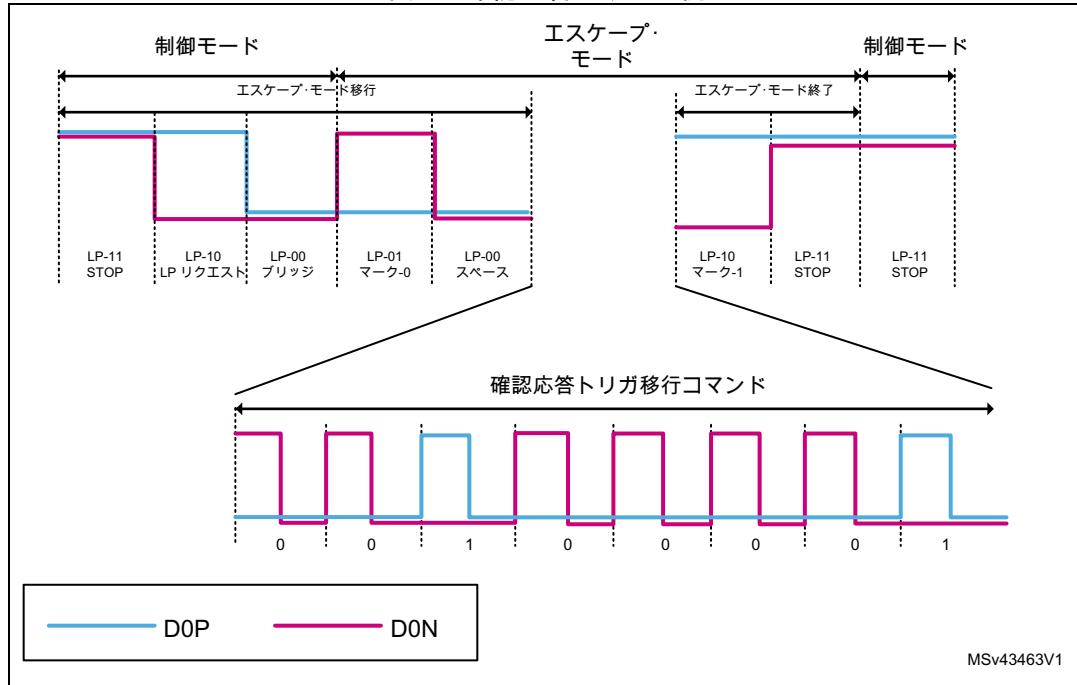

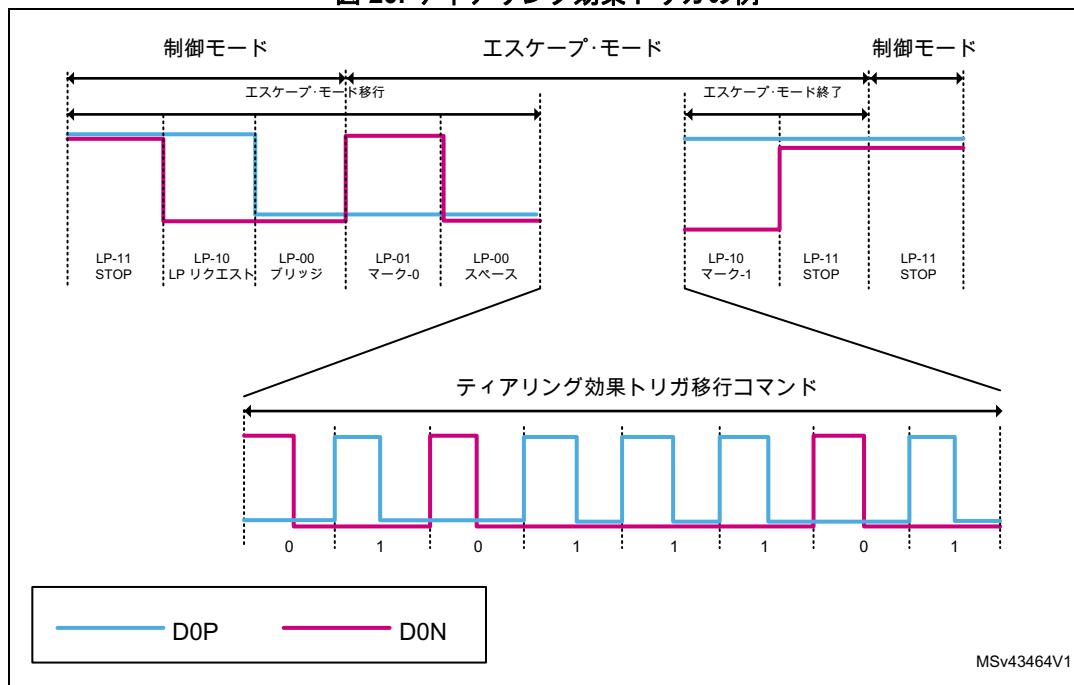

## 5. トリガ

トリガ信号は、受信側にフラグを送信するメッセージング・システムです。これは、正方向または逆方向で使用できます。

DSI では、3つのトリガ・メッセージを使用できます。

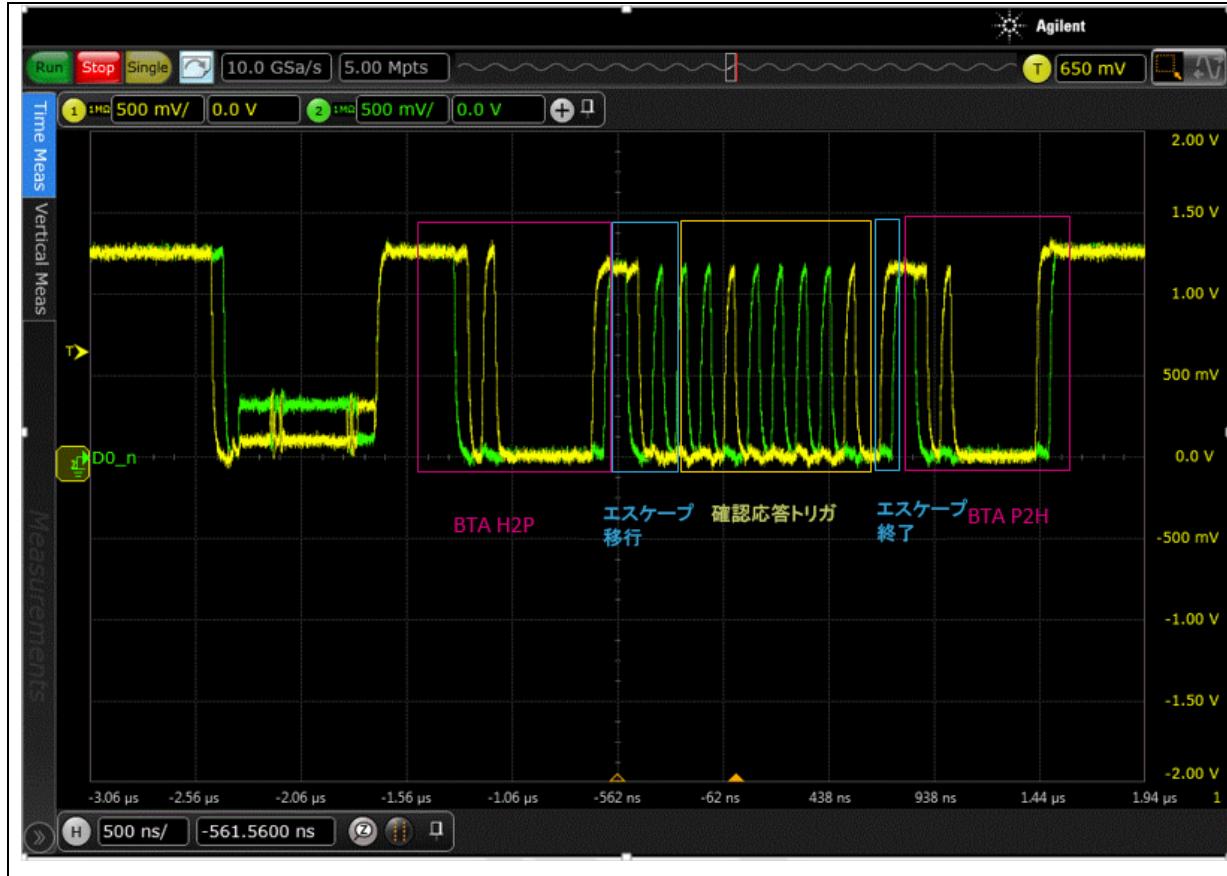

- 確認応答トリガ：ディスプレイによって DSI ホストに送信されるメッセージで、最後の送信がエラーなく受信されたことを示します。これは逆方向の通信です（図 19 を参照）。

- ティアリング効果トリガ：ディスプレイによって使用され、内部タイミングについてホストに通知します。これは逆方向の通信です（図 20 を参照）。

- リセット・トリガ：ホストによって送信され、ディスプレイをリセットします（図 21 を参照）。

図 19. 確認応答トリガの例

# 参考資料

AN4860

DSI の概要

図 20. ティアリング効果トリガの例

図 21. リセット・トリガの例

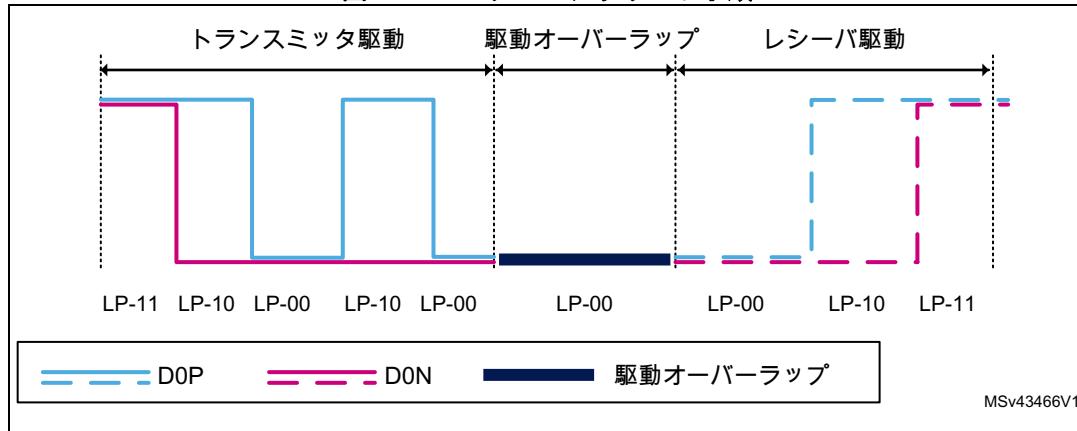

### 3.2.4 双方向レーンおよびバス・ターンアラウンドの手順

DSI は、データ・レーン0でのみ双方向データ・リンクをサポートします。逆方向送信を許可するためには、バス・ターンアラウンド（BTA）手順でデータ・レーンの方向を切り替えることができます。

BTA は STOP 状態 (LP-11) から開始します。レシーバにバスの所有権が渡ると、逆方向送信を開始できます。その後、レシーバは同じターンアラウンド手順でバスの所有権をホストに戻す必要があります。

図 22 に BTA シーケンスを示します。

図 22. バス・ターンアラウンド手順

### 3.2.5 クロックレーンの電力モード

DSI CLK レーンは、3種類の電力モード（低消費電力モード、超低消費電力状態、ハイスピード・クロック・モード）で駆動できます。

#### 低消費電力モード

低消費電力モード時、クロック・レーンは LP-11 STOP 状態になります。その他すべてのモードは LP モードで開始して終了します。

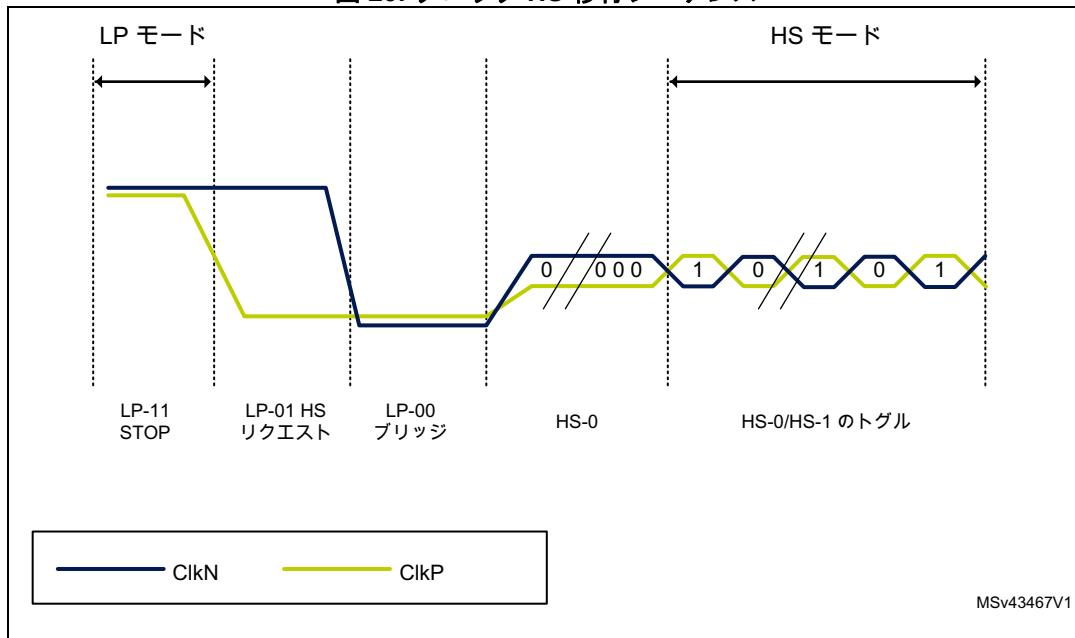

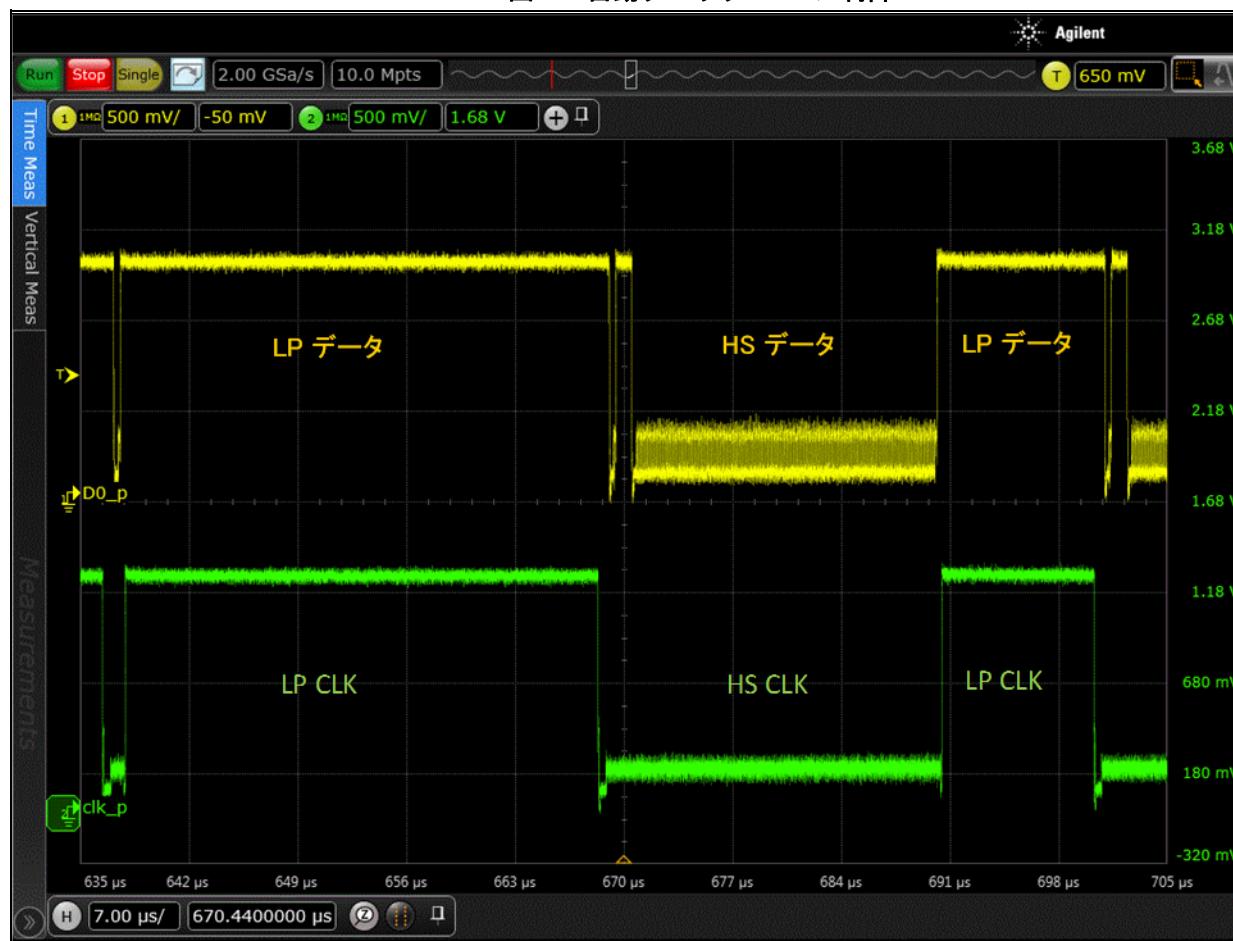

#### ハイスピード・モード

クロック・レーンは、HS 移行シーケンス (LP-11, LP-01, LP-00, HS-0) を駆動することで、LP モードから開始して HS モードに移行します（図 23 を参照）。その後、クロック・レーンは HS モードに移行して、HS-0, HS-1 のトグルを開始します。

# 参考資料

図 23. クロック HS 移行シーケンス

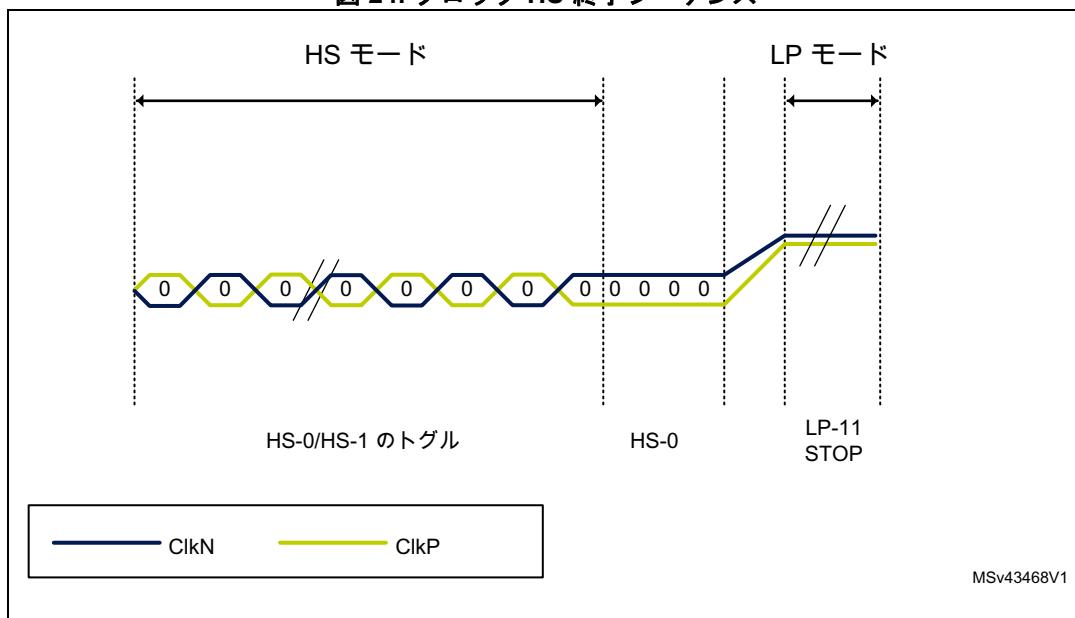

クロック・レーンは、終了シーケンス (HS-0、LP-11) で HS モードを終了します (図 24 を参照)。

図 24. クロック HS 終了シーケンス

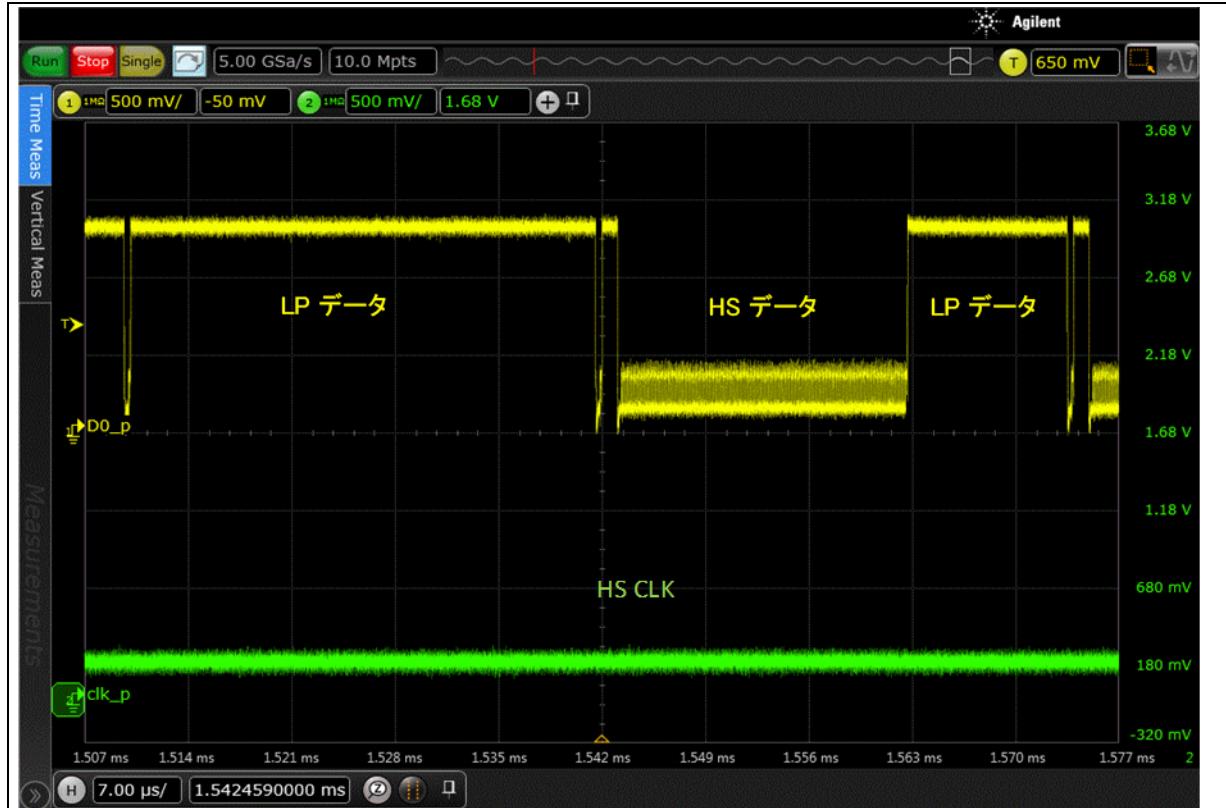

ハイスピード・クロックは、ハイスピード・データがデータ・レーンで送信される前に開始します。ハイスピード・クロックは、ハイスピード・データ・レーンが停止した後も引き続きクロック供給します (図 25 を参照)。

# 参考資料

図 25. HS モードでのクロック・レーンとデータ・レーンの関係

## 超低消費電力状態 (ULPS)

エスケープ・モードは、データ・レーンではサポートされていますが、クロック・レーンではサポートされていません。ただし、クロック・レーンでは ULPS（エスケープ・モードのサブセット）をサポートしています。

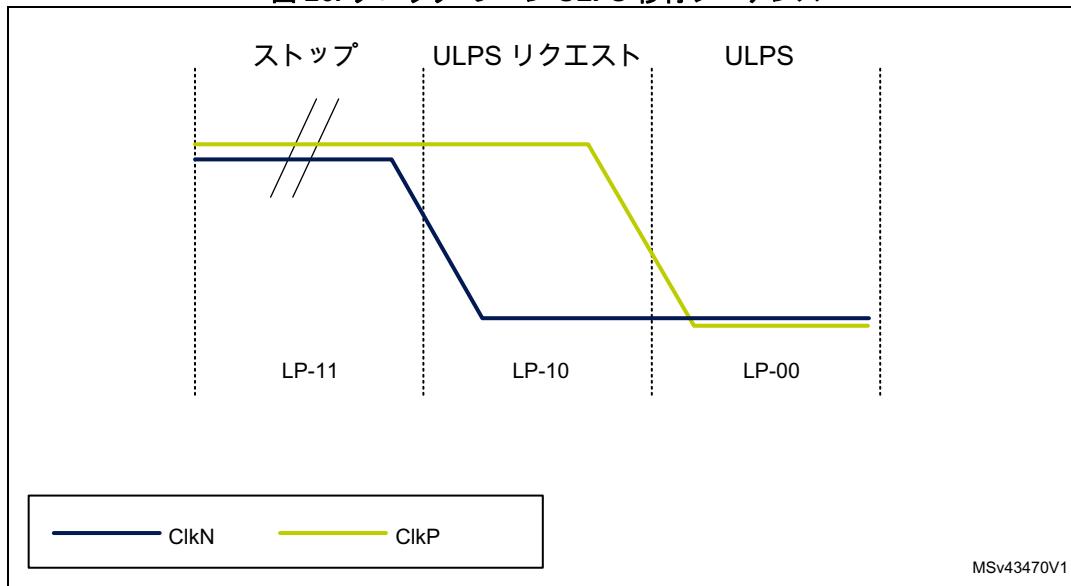

図 26 に示すように、クロック・レーンは ULPS 移行シーケンス (LP-11, LP-10, LP-00) を使用することで、STOP 状態から開始して ULPS に移行できます。

# 参考資料

図 26. クロック・レーン ULPS 移行シーケンス

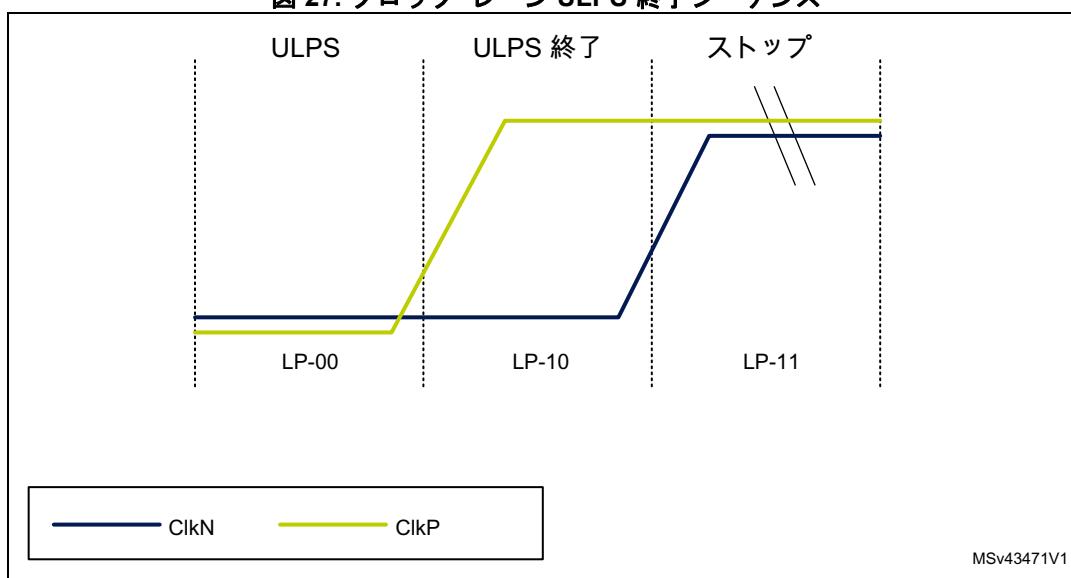

図 27 に示すように、クロック・レーンは ULPS 終了シーケンス (LP-00、LP-10、LP-11) を使用することで、LPM に向けて ULPS 状態を終了します。

図 27. クロック・レーン ULPS 終了シーケンス

# 參考資料

### 3.3 DSI プロトコル

DSI はパケット・ベースのプロトコルです。パラレル・データとコマンドはパケットにカプセル化され、パケット・プロトコル情報とヘッダが付加されます。

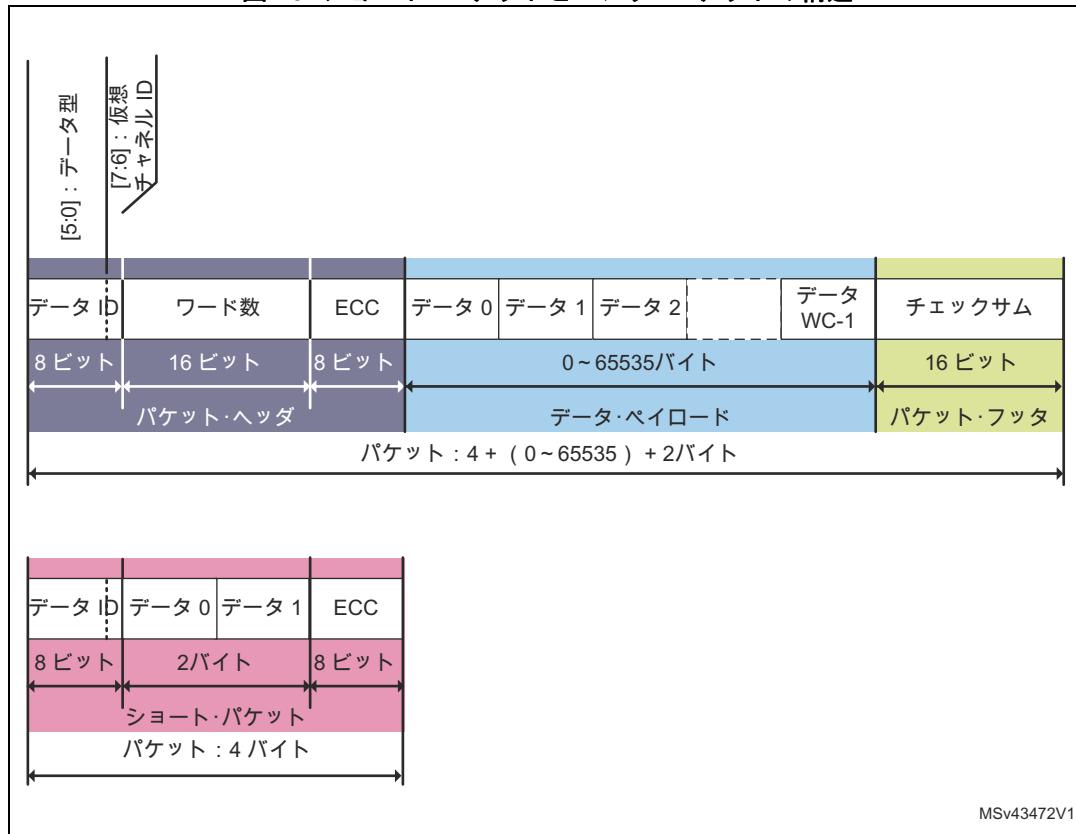

### 3.3.1 パケット構造

ロング・パケットとショート・パケットという2種類のパケット構造が、ローレベルのプロトコル通信に対して定義されます。図 28 を参照してください。

図 28. ショート・パケットとロング・パケットの構造

データは、最下位ビット・ファーストで、バイト単位で送信されます。ワード・カウントやチェックサムなどのマルチバイト・フィールドの場合、データは最下位バイト・ファーストで送信されます。

図 29 にロング・パケットの例を示します。

図 29. ロング・パケットの例

# 参考資料

AN4860

DSI の概要

## ロング・パケット

ロング・パケットは主にピクセル・データなど大きなデータ・ブロックの送信に使用されます。このパケットは、パケット・ヘッダ（PH）、ペイロード・データ、パケット・フッタ（PF）の3つの部分で構成されています。

32-bit パケット・ヘッダには次のものが含まれます。

- 8-bit データ ID

- ペイロード・データの長さ（バイト数）を定義する 16-bit ワード・カウント

- パケット・ヘッダを保護する 8-bit ECC（エラー訂正コード）

ペイロード・データにはアプリケーション固有のデータが含まれます。これは、主にピクセル・データやコマンド・パラメータの伝達に使用されます。長さは、ワード・カウントで定義されます。0～65535 バイトの長さになります。

パケット・フッタは、16-bit チェックサム（CS）で構成されています。トランスマッタによって計算され、レシーバがデータをエラーなしで受信したかどうかを確認するために使用されます。

ロング・パケットの最小長は0ペイロード・データを持つ6バイトです。

- PH 4バイト

- PF 2バイト

最大長は65541バイトです。

- PH 4バイト

- ペイロード・データ65534バイト

- PF 2バイト

## ショート・パケット

ショート・パケットは4バイトで形成されています。

- データ ID 用の1バイト

- コマンドまたはペイロード・データ用の2バイト

- ECC 用の1バイト

これらは、主に短いコマンド送信や、ビデオ同期イベントなどのタイミングが重要な情報に使用されます。

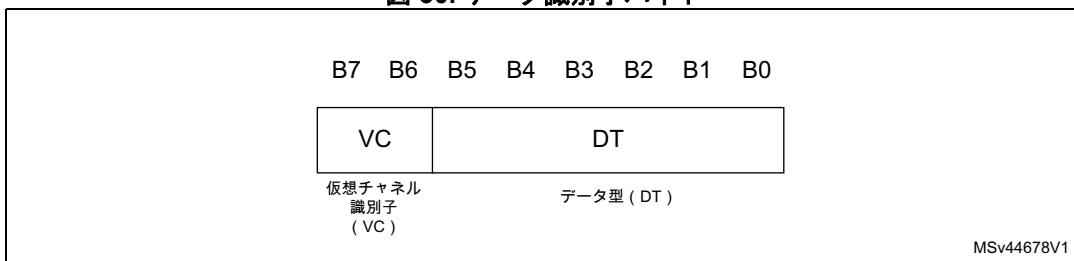

## データ識別子バイト

パケットの最初のバイトは DI（データ識別子）バイトです。DI バイトは仮想チャネル（VC）識別子とデータ型（DT）で構成されています（図 30 を参照）。

図 30. データ識別子バイト

# 参考資料

## 1. 仮想チャネル識別子

DSI ホストは、ヘッダの仮想チャネル ID フィールドを使用して、タグ付きコマンドやデータ・ブロックを最大4つのペリフェラルに供給できます。VC は、データの送信先となるペリフェラルを識別します。

## 2. データ型フィールド DT[5:0]

データ型フィールドは、パケットがロング・パケットかショート・パケットか型を指定します。また、パケット・フォーマットやペイロード・データの内容も指定します。

## データ保護 (ECC およびチェックサム)

DSI 標準には、2つのデータ保護メカニズムがあります。ECC およびチェックサムです。

### 1. エラー訂正コード

エラー訂正コード (ECC) バイトによって、1-bit のエラーを訂正でき、2-bit エラーを検出できます。

ECC は、重要な情報を伝達する際に通常使用されるショート・パケットの堅牢な保護を表します。また、データ識別子とワード・カウント両方のフィールドを含むロング・パケット・ヘッダの優れた保護にもなります。

### 2. チェックサム

ロング・パケットのペイロード・データは、ペイロードに1つ以上のエラーがあることだけを示すことができる 16-bit チェックサムで保護されます。

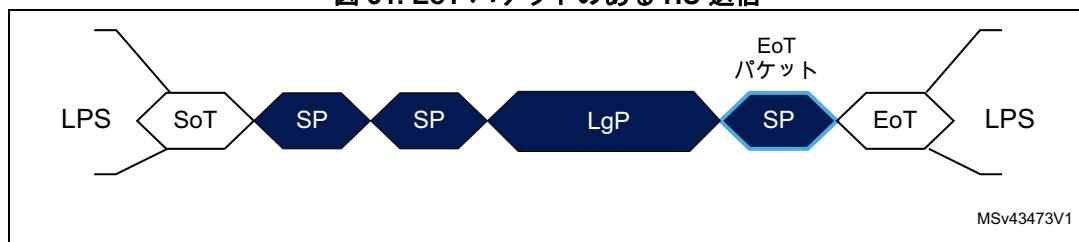

## 3.3.2 送信終了 (EoT) パケット

D-PHY は EoT シーケンスを使用して、HS 送信の終了を通知しますが、このシーケンスはレシーバで有効なデータとして解釈できます。

プロトコル・レベルで堅牢性を付加するために、DSI トランスマッタは EoTp (送信終了パケット) を送信して HS 送信の終了を通知できます。

このメカニズムによって、オーバーヘッド (送信ごとにさらに4バイト分) が増加する代わりに環境の堅牢性が高まります。

図 31 に、EoT パケットを有効にした HS 送信の例を示します。

図 31. EoT パケットのある HS 送信

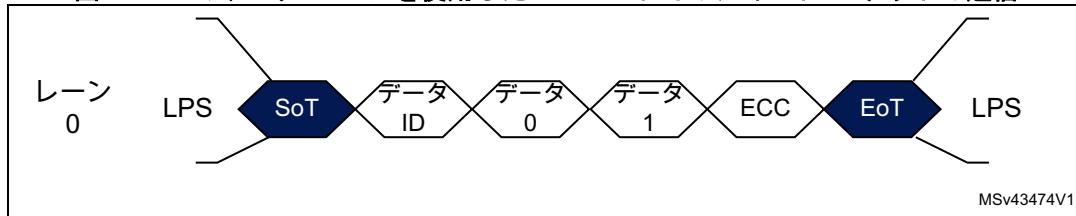

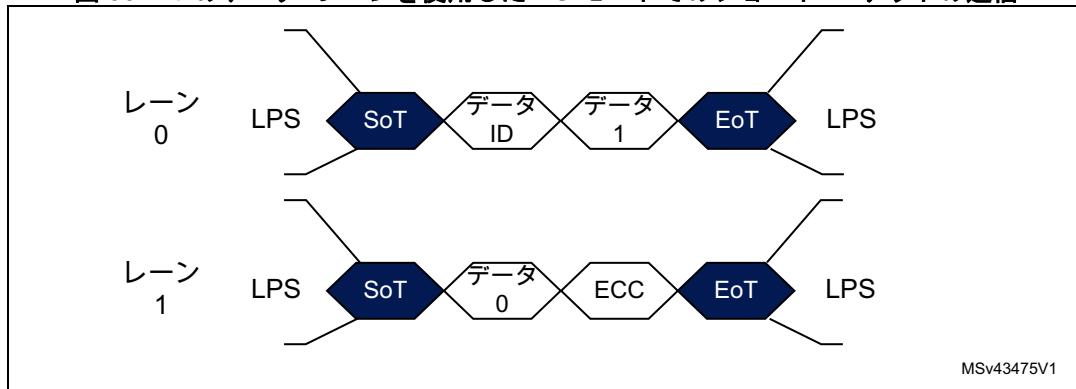

### 3.3.3 パケット送信モード

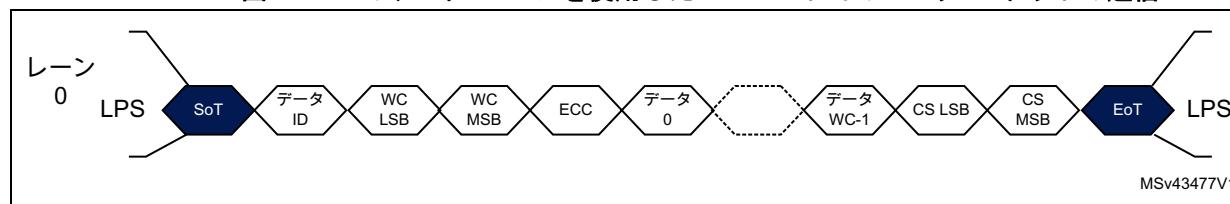

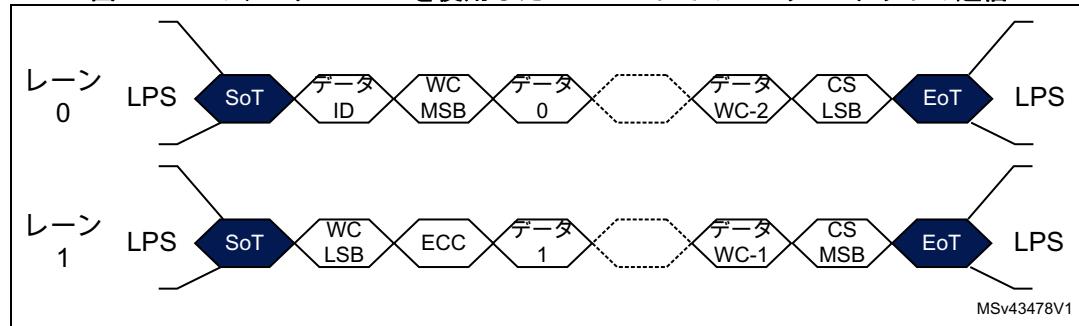

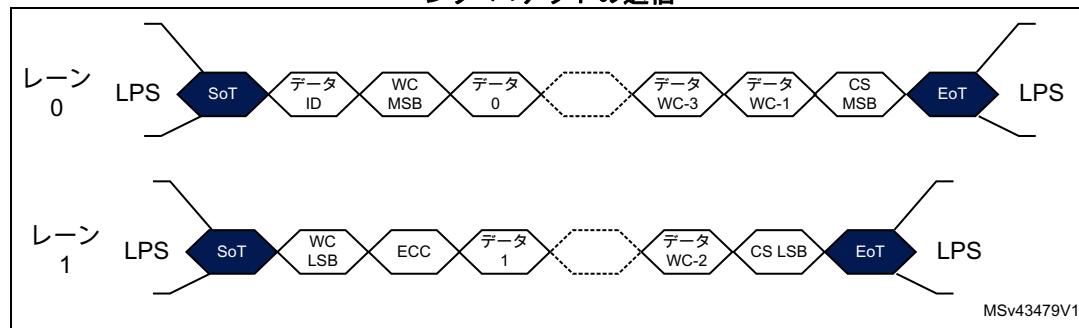

ショート・パケットとロング・パケットは HS または LP モードで送信できます。また、HS モードで送信されるパケットは、使用可能なデータ・レーン間で分けることができます。

図 32 に、1つのデータ・レーンを使用した HS モードでのショート・パケットの送信を示します。

図 32. 1つのデータ・レーンを使用した HS モードでのショート・パケットの送信

図 33 に、2つのデータ・レーンを使用した HS モードでのショート・パケットの送信を示します。

図 33. 2つのデータ・レーンを使用した HS モードでのショート・パケットの送信

図 34 に、LP モードでのショート・パケットの送信を示します。

注： LP モードでは、データ・レーン0のみが送信に使用できます。

図 34. 低消費電力モードでのショート・パケットの送信

図 35 に、1つのデータ・レーンを使用した HS モードでのロング・パケットの送信を示します。

図 35. 1つのデータ・レーンを使用した HS モードでのロング・パケットの送信

# 参考資料

HS モードでは、複数レーンを使用してデータを送信できます。

図 36 に、2つのデータ・レーンを使用した HS モードでのロング・パケットの送信を示します。

図 36. 2つのデータ・レーンを使用した HS モードでのロング・パケットの送信

ペイロード・データの数がレーン数の整数倍ではない場合、一部のレーンが他のレーンより先に HS 送信を完了して、1サイクル（バイト）分早く EoT を送信する場合があります。

図 37 に、2つのデータ・レーンを使用した例を示します。この場合、ペイロード・データに、データ・レーン0より先にデータ・レーン1の HS 送信を完了させる奇数バイトがあります。

図 37. 奇数のペイロード・データがある2つのデータ・レーンを使用した HS モードでのロング・パケットの送信

図 38 に、LP モードでのロング・パケットの送信を示します。

図 38. 低消費電力モードでのロング・パケットの送信

# 参考資料

## 3.3.4 ホストからディスプレイのデータ型

ホストからディスプレイのデータ型は、ショート・パケットまたはロング・パケットを使用できます。これらはビデオまたはコマンドのデータ型となります。ホストからディスプレイのデータ型は、表 6 に示されています。

表 6. ホストからディスプレイのデータ型

| データ型 | 説明                                            | パケット | DSI モード |

|------|-----------------------------------------------|------|---------|

| 0x01 | 同期イベント、V 同期開始                                 | ショート | ビデオ     |

| 0x11 | 同期イベント、V 同期終了                                 | ショート | ビデオ     |

| 0x21 | 同期イベント、H 同期開始                                 | ショート | ビデオ     |

| 0x31 | 同期イベント、H 同期終了                                 | ショート | ビデオ     |

| 0x08 | 送信終了パケット (EoTp)                               | ショート | 両方      |

| 0x02 | カラー・モード (CM) オフ・コマンド                          | ショート | ビデオ     |

| 0x12 | カラー・モード (CM) オン・コマンド                          | ショート | ビデオ     |

| 0x22 | ペリフェラル・シャットダウン・コマンド                           | ショート | ビデオ     |

| 0x32 | ペリフェラル・オン・コマンド                                | ショート | ビデオ     |

| 0x03 | 汎用ショート書込み、パラメータなし                             | ショート | コマンド    |

| 0x13 | 汎用ショート書込み、パラメータ1つ                             | ショート | コマンド    |

| 0x23 | 汎用ショート書込み、パラメータ2つ                             | ショート | コマンド    |

| 0x04 | 汎用読出し、パラメータなし                                 | ショート | コマンド    |

| 0x14 | 汎用読出し、パラメータ1つ                                 | ショート | コマンド    |

| 0x24 | 汎用読出し、パラメータ2つ                                 | ショート | コマンド    |

| 0x05 | DCS ショート書込み、パラメータなし                           | ショート | コマンド    |

| 0x15 | DCS ショート書込み、パラメータ1つ                           | ショート | コマンド    |

| 0x06 | DCS 読出し、パラメータなし                               | ショート | コマンド    |

| 0x37 | 最大戻りパケット・サイズのセット                              | ショート | コマンド    |

| 0x09 | null パケット、データなし                               | ロング  | ビデオ     |

| 0x19 | ブランкиング・パケット、データなし                            | ロング  | ビデオ     |

| 0x29 | 汎用ロング書込み                                      | ロング  | コマンド    |

| 0x39 | DCS ロング書込み／Write_LUT                          | ロング  | コマンド    |

| 0x0C | 軽度パック済みピクセル・ストリーム<br>20-bit YCbCr、4:2:2フォーマット | ロング  | ビデオ     |

| 0x1C | パック済みピクセル・ストリーム<br>24-bit YCbCr、4:2:2フォーマット   | ロング  | ビデオ     |

| 0x2C | パケット・ピクセル・ストリーム<br>16-bit YCbCr、4:2:2フォーマット   | ロング  | ビデオ     |

| 0x0D | パケット・ピクセル・ストリーム<br>30-bit RGB、10-10-10フォーマット  | ロング  | ビデオ     |

| 0x1D | パケット・ピクセル・ストリーム<br>36-bit RGB、12-12-12フォーマット  | ロング  | ビデオ     |

| 0x3D | パケット・ピクセル・ストリーム<br>12-bit YCbCr、4:2:0フォーマット   | ロング  | ビデオ     |

# 参考資料

表 6. ホストからディスプレイのデータ型（続き）

| データ型 | 説明                                          | パケット | DSI モード |

|------|---------------------------------------------|------|---------|

| 0x0E | パケット・ピクセル・ストリーム<br>16-bit RGB、5-6-5フォーマット   | ロング  | ビデオ     |

| 0x1E | パケット・ピクセル・ストリーム<br>18-bit RGB、6-6-6フォーマット   | ロング  | ビデオ     |

| 0x2E | 軽度パック済みピクセル・ストリーム<br>18-bit RGB、6-6-6フォーマット | ロング  | ビデオ     |

| 0x3E | パック済みピクセル・ストリーム<br>24-bit RGB、8-8-8フォーマット   | ロング  | ビデオ     |

## ビデオ・モードのデータ型

ビデオ・モードのデータ型は、主に同期イベントおよびピクセル・データの伝達に使用されます。同期イベントとピクセル・データ・パケットは、タイミングが重要な情報を伝達するため HS モードで送信されます。

他のビデオ・モードのデータ型は、カラー・モードおよびシャットダウン制御に使用されます。これらは HS または LP で送信できます。

注：以下に示したすべての例は  $VC = 0$  の場合です。

### 1. シャットダウンおよびカラー・モード

カラー・モード・コマンドは、ディスプレイ・モジュールを通常モードとロー・カラー・モードで切り替えることができるショート・パケットです。ロー・カラー・モードは節電目的で使用されます（図 39 を参照）。

図 39. カラー・モードのビデオ・パケット

| カラー・モード・オフ |       |       |      | カラー・モード・オン |       |       |      |

|------------|-------|-------|------|------------|-------|-------|------|

| 0x02       | 0x00  | 0x00  | 0x0B | 0x12       | 0x00  | 0x00  | 0x18 |

| データ ID     | Data0 | Data1 | ECC  | データ ID     | Data0 | Data1 | ECC  |

MSv43481V1

シャットダウン・コマンドとオン・コマンドは、ディスプレイ・モジュールのオンまたはオフの切り替えに使用されるショート・パケットです（図 40 を参照）。

図 40. シャットダウン/オンのビデオ・パケット

| ペリフェラル・シャットダウン |       |       |      | ペリフェラル・オン |       |       |      |

|----------------|-------|-------|------|-----------|-------|-------|------|

| 0x22           | 0x00  | 0x00  | 0x1E | 0x32      | 0x00  | 0x00  | 0x0D |

| データ ID         | Data0 | Data1 | ECC  | データ ID    | Data0 | Data1 | ECC  |

MSv43482V1

# 参考資料

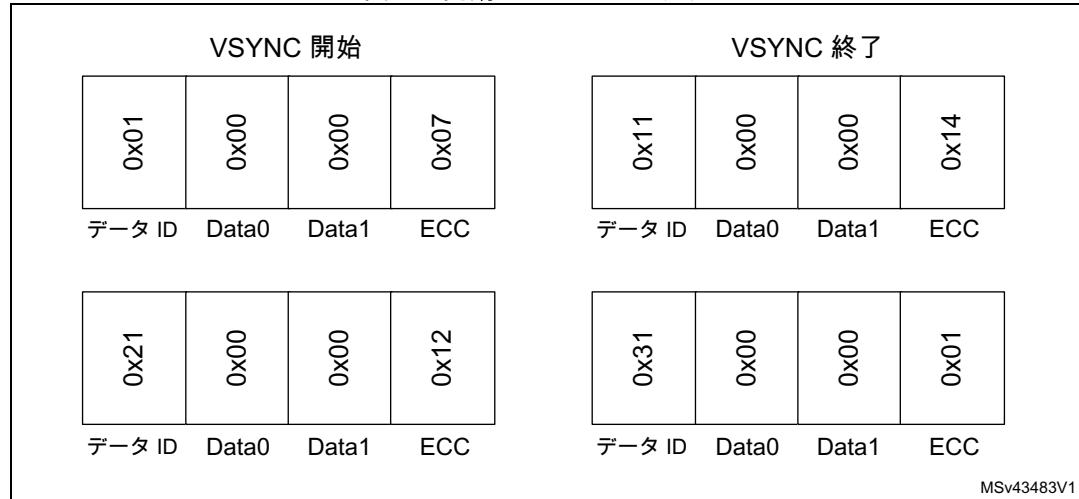

## 2. 同期イベント

ショート・パケットが正確なタイミング情報の伝達により適しているため、同期イベントはショート・パケットで送信されます（図 41 を参照）。

図 41. 同期イベントのパケット

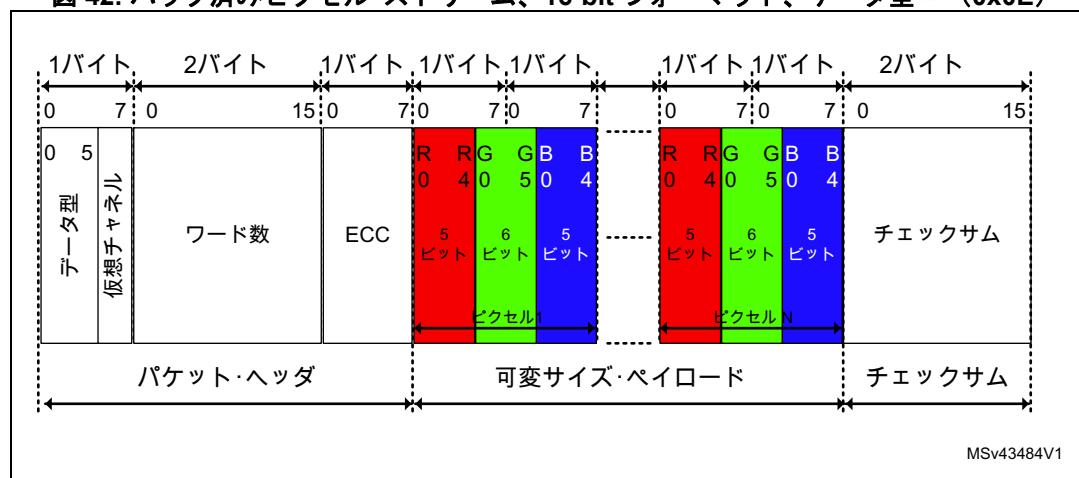

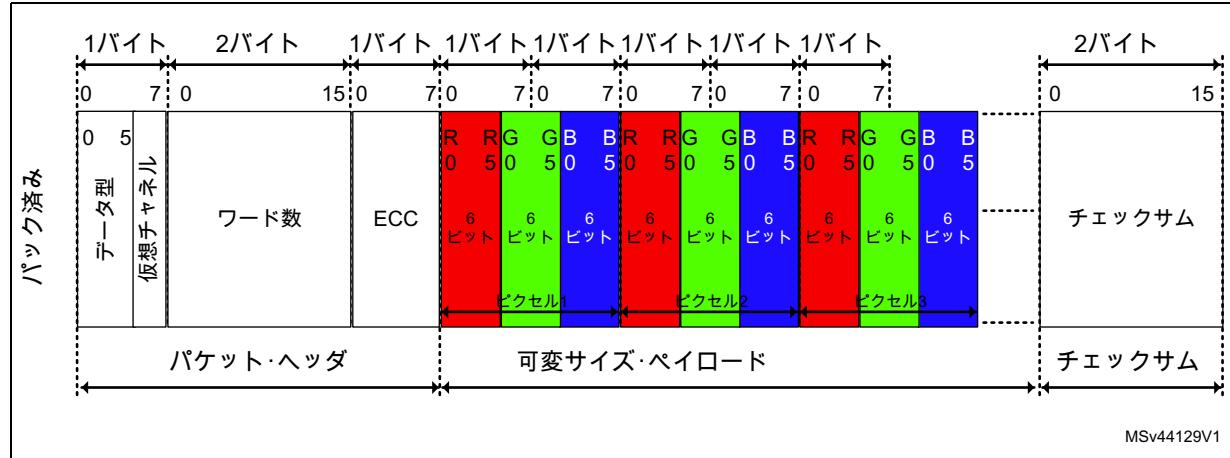

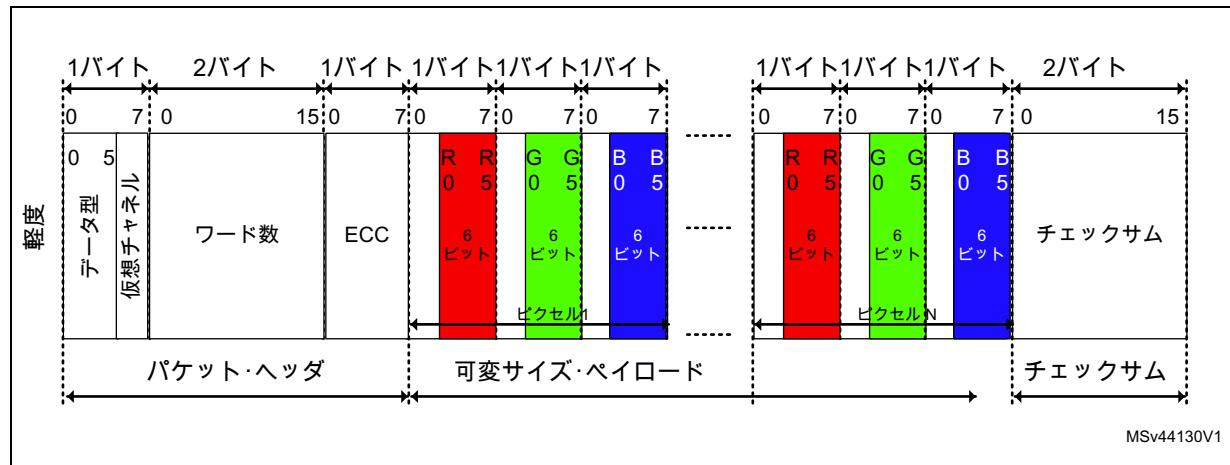

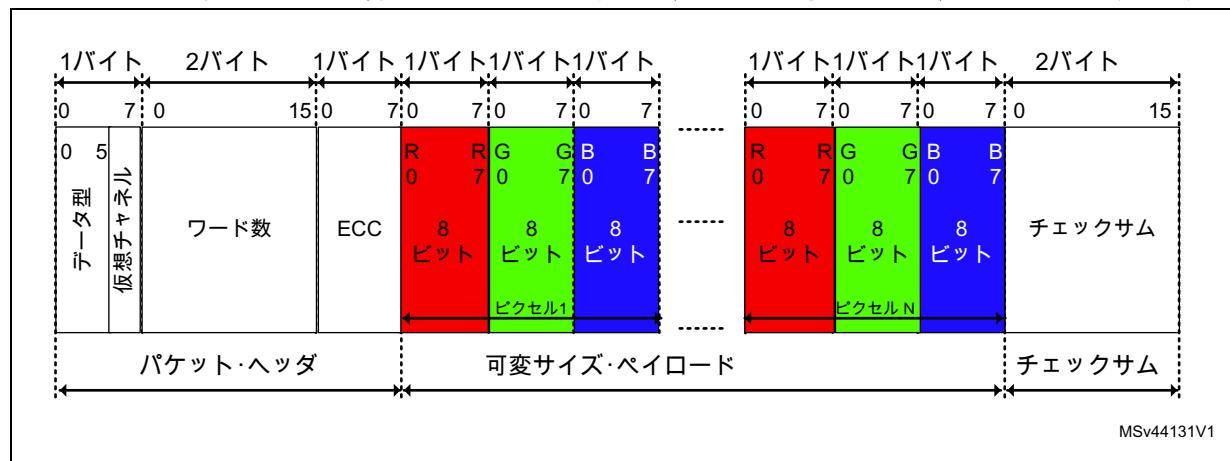

## 3. パック済みピクセル・ストリーム

パック済みピクセル・ストリーム (PPS) パケットは、ピクセルとしてフォーマットされた RGB 画像データを、ビデオ・モード・ディスプレイ・モジュールに送信するために使用されるロング・パケットです。このパケットは、DI バイト、2 バイト WC、ECC バイト、長さの WC バイトと 2 バイト・チェックサムのペイロードで構成されます。

DSI プロトコルは、それぞれのカラー・コーディングに対してパック済みピクセル・ストリームを定義します。

- パック済みピクセル・ストリーム、16-bit フォーマット。図 42 を参照してください。

- パック済みピクセル・ストリーム、18-bit フォーマット。図 43 を参照してください。

- 軽度パック済みピクセル・ストリーム、18-bit フォーマット。図 44 を参照してください。

- パック済みピクセル・ストリーム、24-bit フォーマット。図 45 を参照してください。

図 42. パック済みピクセル・ストリーム、16-bit フォーマット、データ型 = (0x0E)

# 参考資料

図 43. パック済みピクセル・ストリーム、18-bit フォーマット、データ型 = (0x1E)

図 44. 軽度パック済みピクセル・ストリーム、18-bit フォーマット、データ型 = (0x2E)

図 45. パック済みピクセル・ストリーム、24-bit フォーマット、データ型 = (0x3E)

# 参考資料

AN4860

DSI の概要

## コマンド・モードのデータ型

コマンド・モードのデータ型は HS または LP で送信できます。これらは、ディスプレイ・レジスタおよびフレームバッファの書き込みおよび読み出しに使用されます。

### 1. 汎用コマンド

汎用コマンドには次の3種類があります。

- 汎用ショート書き込み。[図 46](#) を参照してください。

- 汎用ロング書き込み。[図 47](#) を参照してください。

- 汎用読み出し。[図 48](#) を参照してください。

図 46. 汎用ショート書き込みコマンド

| 汎用ショート書き込み<br>パラメータ0つ |       |       |     | 汎用ショート書き込み<br>パラメータ1つ |       |       |      | 汎用ショート書き込み<br>パラメータ2つ |        |        |     |

|-----------------------|-------|-------|-----|-----------------------|-------|-------|------|-----------------------|--------|--------|-----|

| 0x03                  | 0x00  | 0x00  | ECC | 0x13                  | パラメータ | 0x00  | 0x01 | 0x23                  | パラメータ1 | パラメータ2 | ECC |

| データ ID                | Data0 | Data1 | ECC | データ ID                | Data0 | Data1 | ECC  | データ ID                | Data0  | Data1  | ECC |

| MSv44132V1            |       |       |     |                       |       |       |      |                       |        |        |     |

図 47. 汎用ロング書き込みコマンド

| 汎用ロング書き込み       |        |        |     |           |      |          |        |

|-----------------|--------|--------|-----|-----------|------|----------|--------|

| 0x29            | WC LSB | WC MSB | ECC | データ0      | データ1 | データ WC-1 | チェックサム |

| 32-bit パケット・ヘッダ |        |        |     | ペイロード・データ |      |          |        |

| 16-bit パケット・フッタ |        |        |     |           |      |          |        |

| MSv44133V1      |        |        |     |           |      |          |        |

図 48. 汎用読み出しコマンド

| 汎用ショート読み出し<br>パラメータ0つ |       |       |     | 汎用ショート読み出し<br>パラメータ1つ |       |       |     | 汎用ショート読み出し<br>パラメータ2つ |        |        |     |

|-----------------------|-------|-------|-----|-----------------------|-------|-------|-----|-----------------------|--------|--------|-----|

| 0x04                  | 0x00  | 0x00  | ECC | 0x14                  | パラメータ | 0x00  | ECC | 0x24                  | パラメータ1 | パラメータ2 | ECC |

| データ ID                | Data0 | Data1 | ECC | データ ID                | Data0 | Data1 | ECC | データ ID                | Data0  | Data1  | ECC |

| MSv44134V1            |       |       |     |                       |       |       |     |                       |        |        |     |

# 参考資料

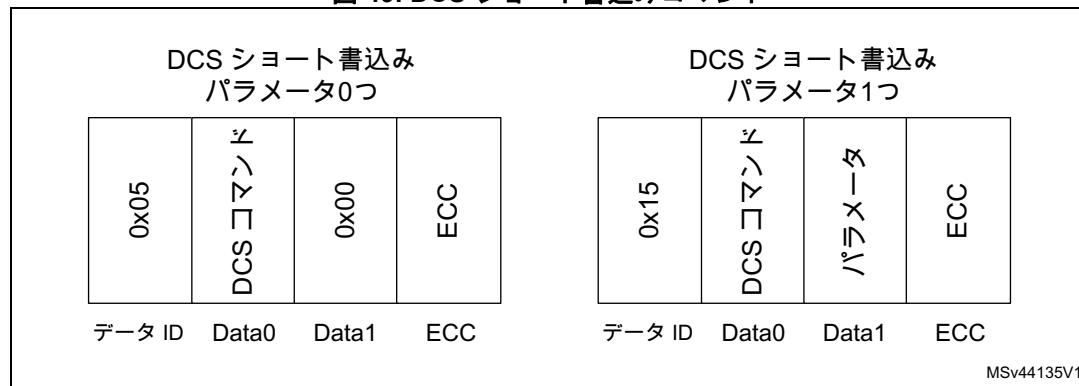

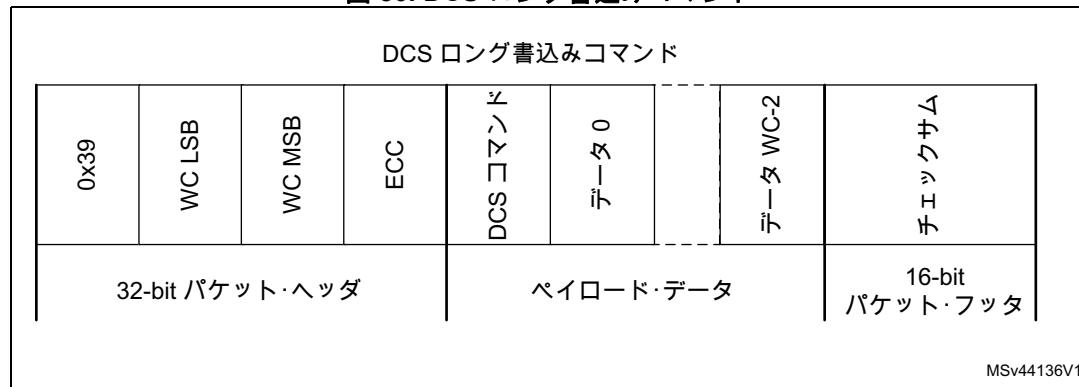

## 2. DCS コマンド

DCS は、コマンド・モード・ディスプレイ向けに MIPI Alliance によって定義された標準化コマンド・セットです。DCS コマンドを表 7 に記載します。

0または1つのパラメータを持つ DCS コマンドはショート・パケットで送信されますが、複数のパラメータを持つ DCS コマンドはロング・パケットで送信されます。

DCS コマンドには次の3種類があります。

- DCS ショート書込み。図 49 を参照してください。

パラメータのない DCS ショート書込みは、DT 0x05でショート・パケットで送信されます。DCS コマンド・インデックスは、データ0フィールドに配置されます。データ1フィールドは使用せず、0にセットされます。

1つのパラメータがある DCS ショート書込みでは、DT 0x15となります。DCS コマンド・インデックスは、データ0フィールドに配置され、パラメータはデータ1フィールドに配置されます。

- DCS ロング書込み。図 50 を参照してください。

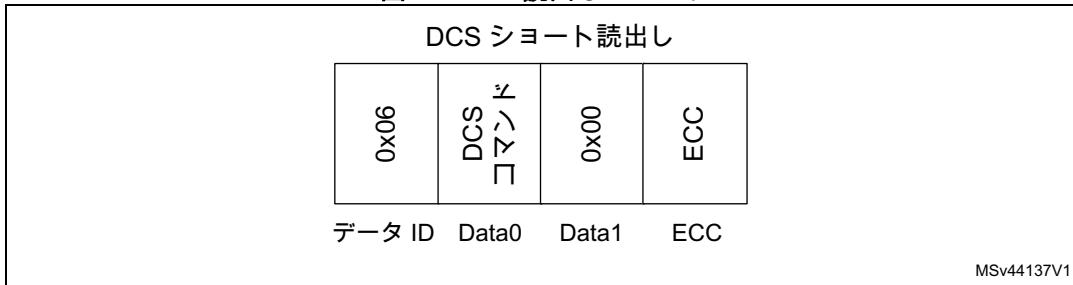

- DCS 読出し。図 51 を参照してください。

ディスプレイへのバス制御を付与して応答を送信できるように、読み出しコマンドの後に BTA を続ける必要があります。

この応答は、DCS ショート読出しままたはロング読出しの応答となります（表 8 を参照）。

図 49. DCS ショート書込みコマンド

図 50. DCS ロング書込みコマンド

# 参考資料

図 51. DCS 読出しコマンド

下の表 7 に、DCS コマンドの一覧を示します。

# 参考資料

表 7. DCS コマンドの一覧

| コマンド                  | 16進数コード | 説明                                                                                       |

|-----------------------|---------|------------------------------------------------------------------------------------------|

| enter_idle_mode       | 39h     | 軽減された色深度がディスプレイ・パネルで使用されます。                                                              |

| enter_invert_mode     | 21h     | 表示される画像の色が反転します。                                                                         |

| enter_normal_mode     | 13h     | 表示エリア全体が画像表示に使用されます。                                                                     |

| enter_partial_mode    | 12h     | 表示エリアの一部が画像表示に使用されます。                                                                    |

| enter_sleep_mode      | 10h     | ディスプレイ・パネルの電源がオフになります。                                                                   |

| exit_idle_mode        | 38h     | フル色深度がディスプレイ・パネルで使用されます。                                                                 |

| exit_invert_mode      | 20h     | 表示される画像の色が反転しません。                                                                        |

| exit_sleep_mode       | 11h     | ディスプレイ・パネルの電源がオンになります。                                                                   |

| get_3D_control        | 3Fh     | ディスプレイ・モジュール 3D モードを取得します。                                                               |

| get_address_mode      | 0Bh     | ホストからディスプレイ・モジュールと、メモリからディスプレイ・デバイスに転送するデータの順序を取得します。                                    |

| get_blue_channel      | 08h     | (0, 0) でピクセルの青のコンポーネントを取得します。                                                            |

| get_diagnostic_result | 0Fh     | ペリフェラルの自己診断結果を取得します。                                                                     |

| get_display_mode      | 0Dh     | ペリフェラルから現在のディスプレイ・モードを取得します。                                                             |

| get_green_channel     | 07h     | (0, 0) でピクセルの緑のコンポーネントを取得します。                                                            |

| get_pixel_format      | 0Ch     | 現在のピクセル・フォーマットを取得します。                                                                    |

| get_power_mode        | 0Ah     | 現在の電力モードを取得します。                                                                          |

| get_red_channel       | 06h     | (0, 0) でピクセルの赤のコンポーネントを取得します。                                                            |

| get_scanline          | 45h     | 現在のスキャンラインを取得します。                                                                        |

| get_signal_mode       | 0Eh     | ディスプレイ・モジュールの信号モードを取得します。                                                                |

| nop                   | 00h     | 何もしません。                                                                                  |

| read_DDB_continue     | A8h     | 最後の読み出し位置から DDB を引き続き読み出します。                                                             |

| read_DDB_start        | A1h     | 指定された位置から DDB を読み出します。                                                                   |

| read_memory_continue  | 3Eh     | 最後の read_memory_continue または read_memory_start 以降<br>続けてペリフェラルから画像データを読み出します。            |

| read_memory_start     | 2Eh     | set_column_address または set_page_address で指定された<br>位置から画像データを<br>ペリフェラルからホスト・プロセッサに転送します。 |

| set_3D_control        | 3Dh     | 3D がディスプレイ・パネルで使用されます。                                                                   |

| set_address_mode      | 36h     | ホストからディスプレイ・モジュールと、メモリからディスプレイ・デバイスに転送するデータの順序をセットします。                                   |

| set_column_address    | 2Ah     | 列の範囲をセットします。                                                                             |

| set_display_off       | 28h     | ディスプレイ・デバイスをブランクにします。                                                                    |

| set_display_on        | 29h     | ディスプレイ・パネルに画像を表示します。                                                                     |

| set_gamma_curve       | 26h     | ディスプレイ・デバイスで使用されるガンマ曲線を選択します。                                                            |

| set_page_address      | 2Bh     | ページの範囲をセットします。                                                                           |

| set_partial_columns   | 31h     | ディスプレイ・デバイスの一部の表示エリアでの列の数を<br>定義します。                                                     |

# 参考資料

表 7. DCS コマンドの一覧（続き）

| コマンド                  | 16進数コード | 説明                                                                                 |

|-----------------------|---------|------------------------------------------------------------------------------------|

| set_partial_rows      | 30h     | ディスプレイ・デバイスの一部の表示エリアでの行の数を定義します。                                                   |

| set_pixel_format      | 3Ah     | インターフェースで使用するピクセルごとのビット数を定義します。                                                    |

| set_scroll_area       | 33h     | ディスプレイ・デバイスの縦スクロールと固定エリアを定義します。                                                    |

| set_scroll_start      | 37h     | 縦スクロールの開始点を定義します。                                                                  |

| set_tear_off          | 34h     | 同期情報がディスプレイ・モジュールからホスト・プロセッサに送信されません。                                              |

| set_tear_on           | 35h     | 同期情報がVFP の開始時にディスプレイ・モジュールからホスト・プロセッサに送信されます。                                      |

| set_tear_scanline     | 44h     | ディスプレイ・デバイスのリフレッシュが指定されたスキヤンラインに達したときに、同期情報がディスプレイ・モジュールからホスト・プロセッサに送信されます。        |

| set_vsync_timing      | 40h     | VSYNC タイミングをセットします。                                                                |

| soft_reset            | 01h     | ソフトウェア・リセットします。                                                                    |

| write_LUT             | 2Dh     | ペリフェラル・ルックアップ・テーブルに指定されたデータを記入します。                                                 |

| write_memory_continue | 3Ch     | 最後に書き込まれた位置から、画像データをホスト・プロセッサ・インターフェースからペリフェラルに転送します。                              |

| write_memory_start    | 2Ch     | set_column_address および set_page_address で指定された位置から、画像データをホスト・プロセッサ・からペリフェラルに転送します。 |

### 3. 最大戻りパケット・サイズのセット

**最大戻りパケット・サイズのセット・コマンド**で、ホスト・プロセッサはペリフェラルから受け取る応答パケットのサイズを制限できます。

最大戻りパケット・サイズの初期値は1バイトです。2バイト以上取得するには、ホストは読み出しコマンドを送信する前に、目的のサイズをパラメータとしてこのコマンドを送信する必要があります。

注：

**最大戻りパケット・サイズ**は、オーバーフローを回避するために、ホストの読み出し FIFO サイズを超えてはなりません。DSI ホストの読み出し FIFO は 32 x 32-bit ワード・サイズです。

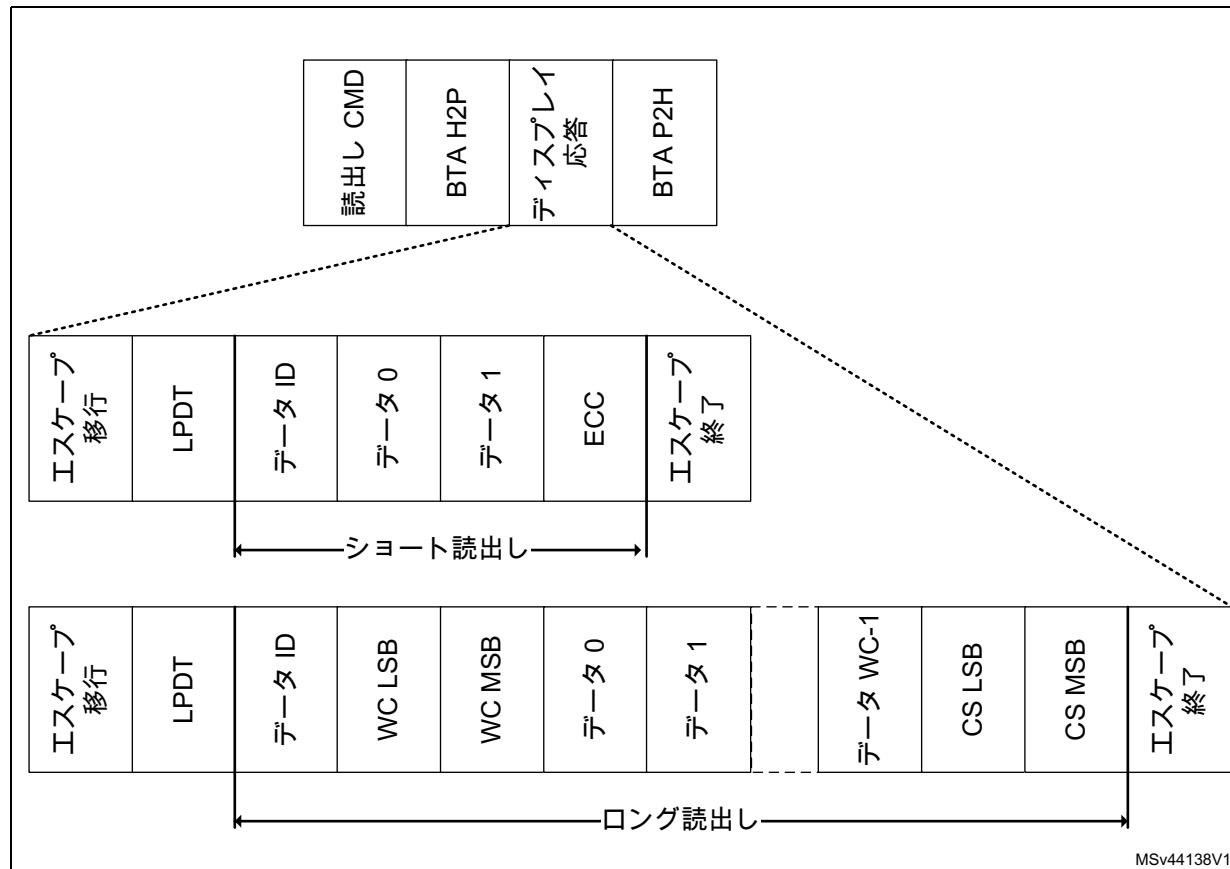

### 3.3.5 ディスプレイからホストのデータ型

すべてのコマンド・モード・システムは、逆方向の通信をサポートします。一方、ビデオ・モード・システムでは、逆方向の通信のサポートはオプションとなります。

ディスプレイからホストの送信は、正方向の送信と同じショート・パケットとロング・パケットを使用します。

ディスプレイからホストの送信は、ホストが BTA シーケンスを使用してバスの所有権をディスプレイに渡した後のみ開始できます。

応答を送信した後、ディスプレイが BTA シーケンスでバスの制御をホストに戻します。

# 参考資料

図 52 に、逆方向の通信シーケンスの例を示します。ディスプレイからホストの送信は、データ・レン0を使用した LP モードで発生します。

図 52. 逆方向の通信シーケンス

ディスプレイからホストのデータ型は、下の表 8 に示されています。

表 8. ディスプレイからホストのデータ型

| データ型 | 説明                        | パケット |

|------|---------------------------|------|

| 0x02 | 確認応答およびエラー・レポート           | ショート |

| 0x08 | 送信終了パケット (EoTp)           | ショート |

| 0x11 | 汎用ショート読み出しの応答<br>1バイト戻り   | ショート |

| 0x12 | 汎用ショート読み出しの応答<br>2バイト戻り   | ショート |

| 0x1A | 汎用ロング読み出しの応答              | ロング  |

| 0x1C | DCS ロング読み出しの応答            | ロング  |

| 0x21 | DCS ショート読み出しの応答<br>1バイト戻り | ショート |

| 0x22 | DCS ショート読み出しの応答<br>2バイト戻り | ショート |

# 参考資料

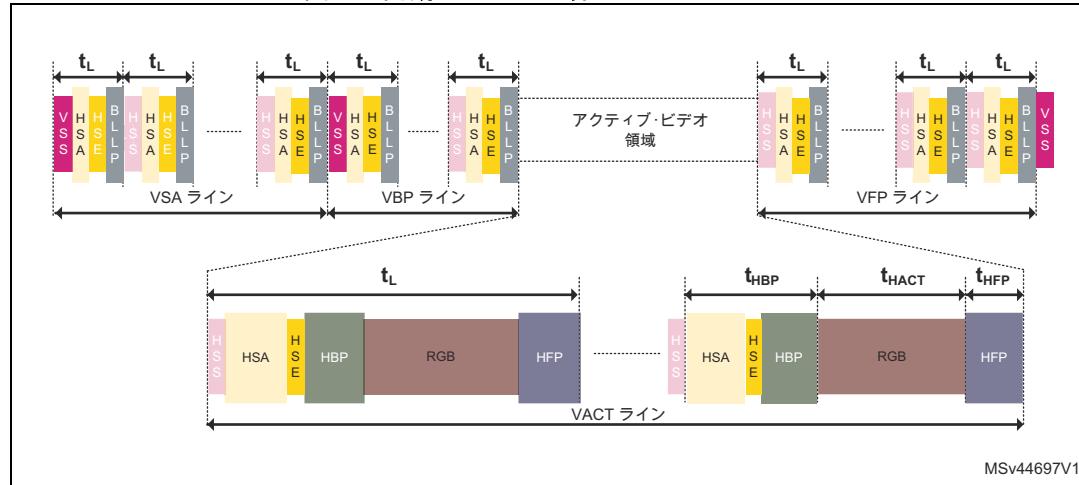

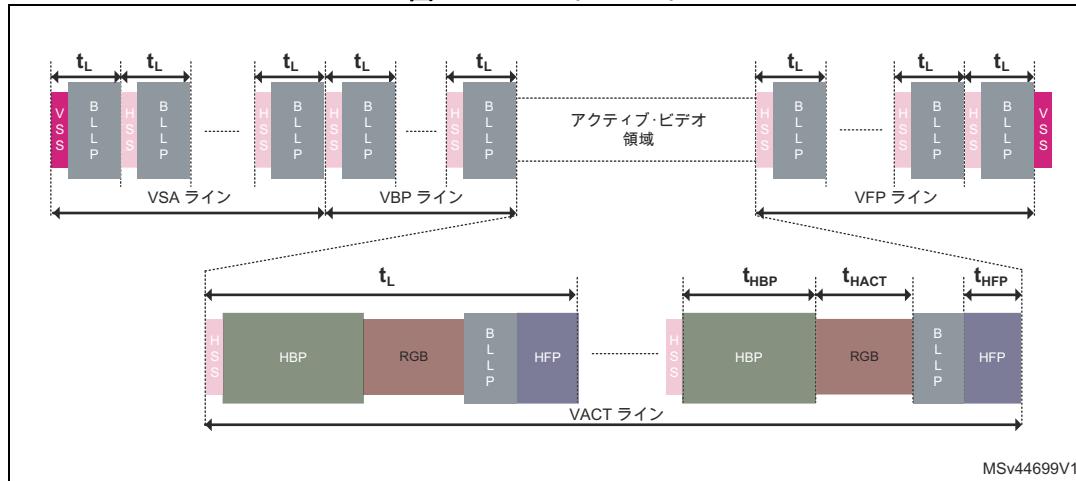

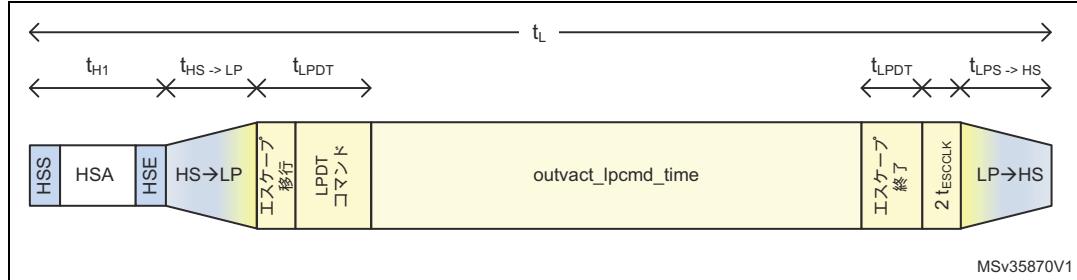

## 3.3.6 ビデオ・モードのインタフェース・タイミング

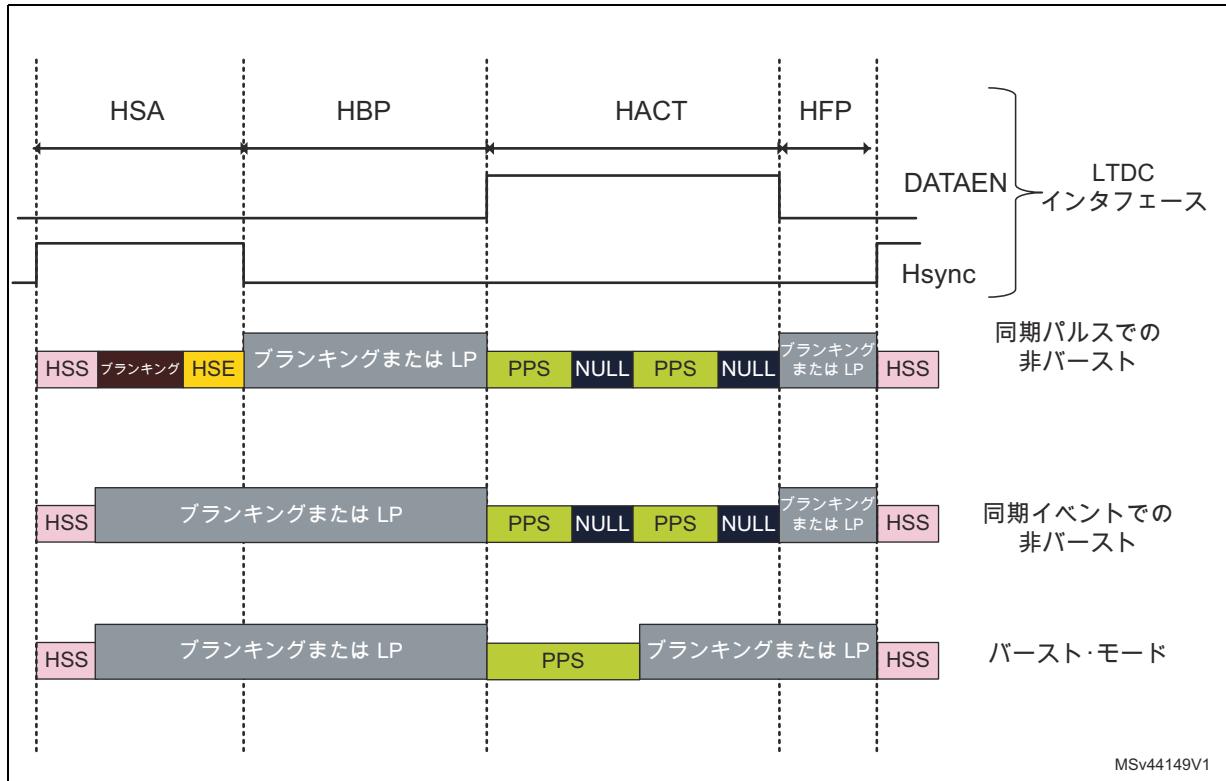

ビデオ・モードのペリフェラルは、ピクセル・データをリアルタイムで伝達する必要があります。DSI は、ビデオ・モードのデータ送信で複数のフォーマットをサポートします。

- 同期パルスでの非バースト・モード：ペリフェラルは同期パルス幅を含めて元のビデオ・タイミングを正確に再構築できます。[図 53](#) を参照してください。LP モードへの切り替えに十分な時間がない場合、LP の時間間隔はブランкиング・パケットで置き換えられます。

- 同期イベントでの非バースト・モード：上記モードと同様ですが、こちらでは同期パルス幅の正確な再構築が不要となり、1つの同期イベントが置き換えられます。[図 54](#) を参照してください。

- バースト・モード：RGB ピクセル・パケットが時間圧縮され、LP モード（節電）または DSI リンク上のその他の送信のマルチプレクスのために、スキャンライン中の時間が増えます。[図 55](#) を参照してください。

注：

タイミングの正確な再構築では、パケット・オーバーヘッド（データ ID、ECC、チェックサムのバイトを含む）について考慮する必要があります。

DSI ホストは、3種類すべてのビデオ・モードのパケット・シーケンスをサポートします。DSI ディスプレイは、上記のモードを最低1種類サポートします。

図 53. 同期パルスでの非バースト・モード

図 54. 同期イベントでの非バースト・モード

図 55. パースト・モード

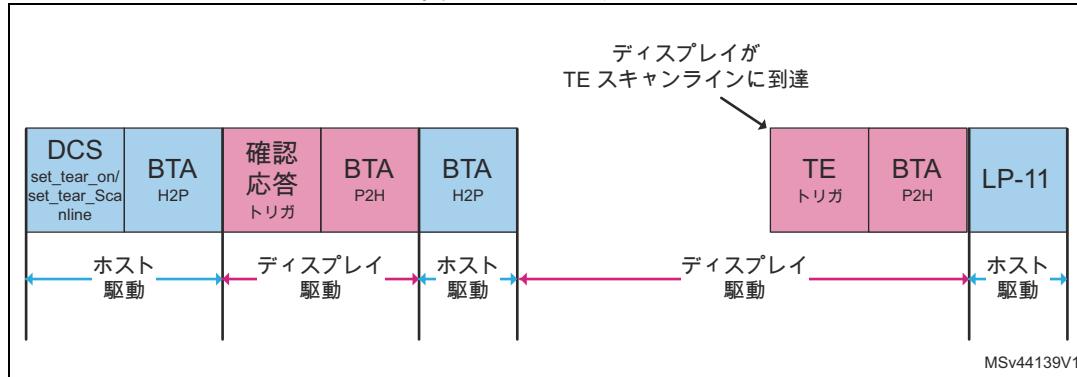

### 3.3.7 コマンド・モードでのティアリング効果信号

ティアリング効果 (TE) は、ディスプレイ・デバイスが1回の画面描画で2フレーム以上から情報を表示する視覚的な乱れです。この乱れは、ホストによるディスプレイ GRAM の更新がディスプレイのスキャン・プロセスと同期していない場合に発生します。

ティアリング効果信号は、ホストにディスプレイ側でのタイミング・イベントを通知できる同期メカニズムです。これは、ディスプレイに独自のコントローラがあり、内部 GRAM を使用してディスプレイを更新するコマンド・モード・システムで使用されます。

コマンド・モード・システムでは、ディスプレイが特定のスキャンラインに達したときに必ず TE 信号でホストに通知します。このアクションによって、ホストはティアリング効果を発生させることなくディスプレイ GRAM を更新するタイミングを認識できるようになります。

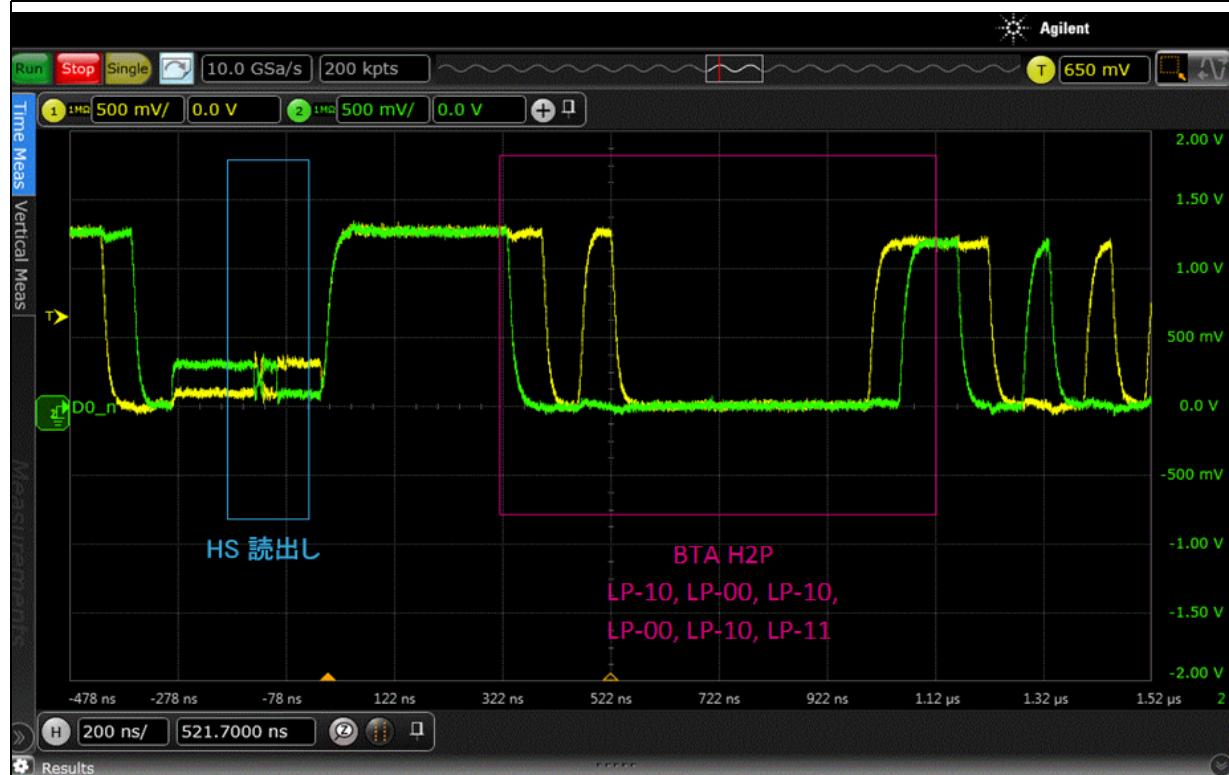

TE レポートが必要である場合、DSI ホストは2回の BTA (バス・ターンアラウンド) 手順の前に `set_tear_on` または `set_tear_scanline` の DCS コマンドを送信して、バスの制御をディスプレイに渡します。

ディスプレイの DSI プロトコル層は確認応答トリガまたはエラー・レポートで1回目の BTA に応答し、ホストにバスの制御を戻すため (DCS コマンドを解釈しないため)、2回の BTA が必要になります。

TE レポートを許可するには、ホストは BTA をもう1回実行して、バスの制御をディスプレイに渡す必要があります。ディスプレイは、スキャンラインに達するとすぐに TE トリガ (01011101) で応答します。

# 参考資料

図 56 にティアリング効果シーケンスを示します。

図 56. TE シーケンス

1. BTA H2P はホストがバスの制御をペリフェラルに渡すために開始する BTA 手順です。BTA P2H はペリフェラルがバスの制御をホストに渡すために開始する BTA 手順です。

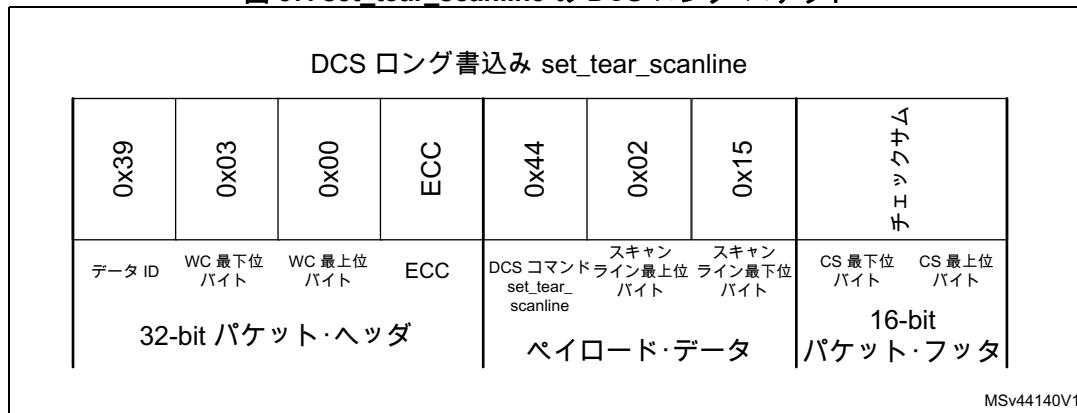

`set_tear_scanline` は、`set_tear_on` 同じように TE レポートが可能ですが、`set_tear_scanline` は TE レポートが発生すべきスキャンラインも定義します。ディスプレイがライン 533（例）に達した際に TE レポートが必要になる場合の `set_tear_scanline` の DCS ロング・パケットについて、図 57 に示します。

一般的に、`set_tear_scanline` は TE スキャンラインをプログラムするために初期化フェーズで使用され、TE レポートを有効にする必要がある場合にはホストが `set_tear_on` を送信します。

`set_tear_scanline` コマンドは、ロング DCS 書込みコマンドです。TE スキャンラインを定義するためには、2つのパラメータを取ります。

注： TE スキャンラインは、最上位バイト・ファーストで2バイトで送信されます。

図 57. set\_tear\_scanline の DCS ロング・パケット

## 4 DSI ホストの説明

本セクションでは、STM32 DSI ホストのシステム・レベル・アーキテクチャと動作モードについて説明し、アプリケーションのニーズに応じて適切な動作モードを選択するためのガイダンスを示します。

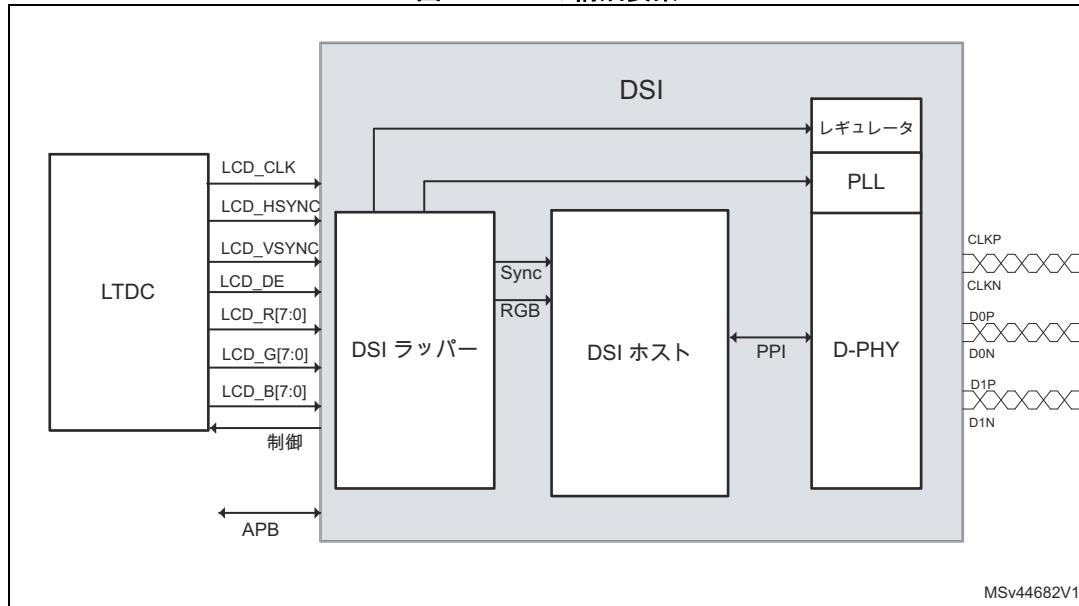

### 4.1 DSI のシステム・レベル・アーキテクチャ

DSI ホストは、LTDC と密接に統合されています。LTDC に依存してピクセル・データをフェッチし、ビデオ同期信号を供給します。

DSI ホストには2つのシステム・インターフェースがあります。

- LTDC インタフェース

- このインターフェースで、DSI ホストは LTDC からピクセル・データとビデオ同期信号をキャプチャして、DSI パケットにカプセル化できます。

- ビデオ・モード時のビデオ・パケット（ビデオ同期イベント、ピクセル・パケット・ストリーム）

- アダプティッド・コマンド・モード時の memory\_write\_start (WMS) と memory\_write\_continue (WMC) の DCS コマンド

- APB インタフェース

- このインターフェースは、DCS および汎用コマンド・モードのパケットの送信に使用されます。これらのパケットは APB レジスタのアクセスで構築されます。

これはアダプティッド・モードまたはビデオ・モードで同時にアクセスして DCS または汎用パケットをディスプレイに転送できます。

### DSI ホストの構成要素

DSI システムの構成要素は次のとおりです。

- DSI ラッパー : LTDC を DSI ホストに相互接続して、ビデオ・モードやアダプティッド・コマンド・モードのいずれかでピクセル・データとビデオ制御信号をリダイレクトします。

DSI ラッパーは DSI レギュレータ、DSI PLL、D-PHY の一部の機能も制御します。

- DSI ホスト・コントローラ : ロングまたはショート DSI パケットを構築して、対応する ECC コードおよび CRC コードを生成します。パケットは、直列化するために D-PHY にバイト単位で送信されます。

複数のレーンを使用している場合、DSI ホストは使用可能な D-PHY レーン間でデータを分割します。

- D-PHY : DSI ホストから出力されたデータを直列化してシリアル・リンクで送信します。

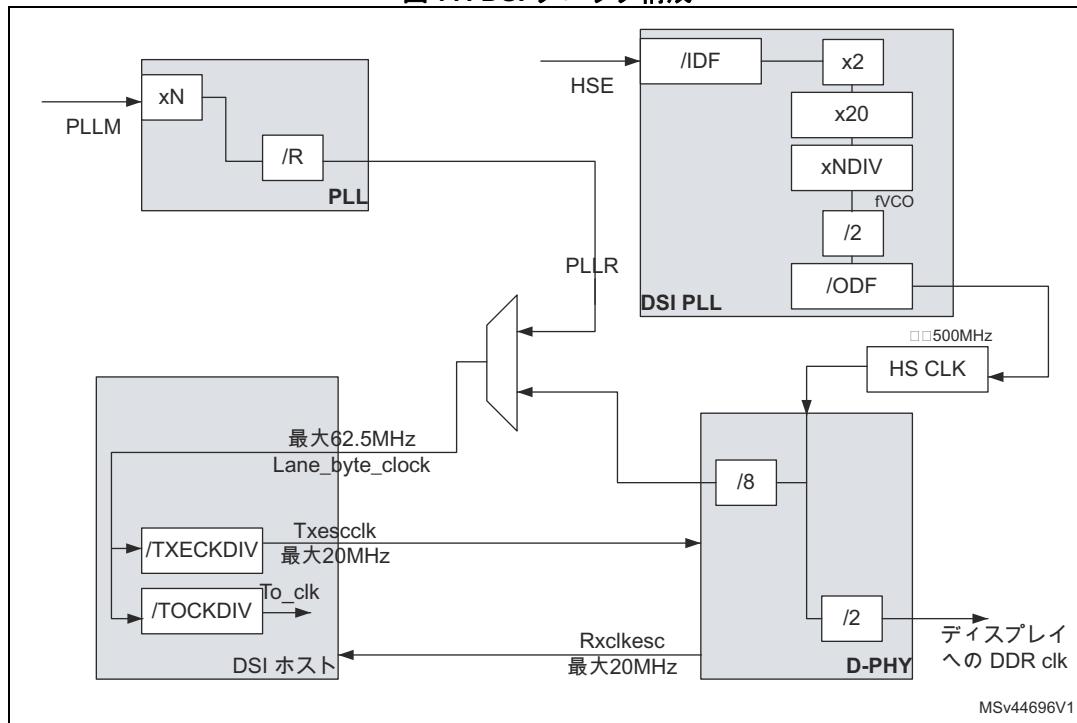

- 内部 PLL : D-PHY で使用される HS クロックを生成します。

- 内部レギュレータ : PLL および D-PHY に 1.2V の電源を供給します。

[図 58](#) に DSI の構成要素を示します。

図 58. DSI の構成要素

## 4.2 動作モード

STM32 DSI ホストは、DSI 仕様バージョン1.1で定義されたすべての動作モードをサポートします。コマンド・モードおよびビデオ・モードのシーケンス（バースト、同期パルスでの非バースト、同期イベントでの非バースト）をサポートしています。

また、STM32 DSI ホストは、GRAM を組み込んでいるディスプレイで最適に動作するように強化されたコマンド・モードもサポートしています。

ディスプレイへのグラフィック・データの伝達に使用できる次の3種類の動作モードがあります。

- ビデオ・モード**

ハイスピード・リンクで RGB データおよび LTDC によって直接生成された関連の同期信号 (Vsync, Hsync) をストリーミングするために使用します。

LTDC インタフェースがデータと同期信号をキャプチャし、FIFO インタフェースに伝達します。

インターフェースには、ビデオ制御信号とピクセル・データという2種類のデータ・ストリームがあります。

DSI ホストは両方のデータ・ストリームを使用し、DSI ビデオ・パケットを構築して、これが DSI リンクで送信されます。

ストリーミングは、DSI ホストと LTDC が有効になり次第開始します。この継続的なリフレッシュが、グラフィカル RAM のないディスプレイでインターフェース接続する最適な方法となります。

- アダプティッド・コマンド・モード**

このモードは、独自で内部グラフィカル RAM を持つディスプレイでインターフェース接続する最も優れた方法です。DSI ホストは LTDC から受け取る完全な1フレームだけをキャプチャし、一連の DCS 書込みコマンドに変換して、ディスプレイのグラフィカル RAM を更新します。このワンショット・リフレッシュは、DSI ホストで制御ビットをセットしたときに自動的に実行されます。

- APB コマンド・モード**

このモードは、SPI を使用した場合のようにハイスピード・リンクで設定用にコマンドを送信するために使用されます。コマンドは、DSI ホストの APB インタフェースを使用して開始されます。

### 4.2.1 ビデオ・モード

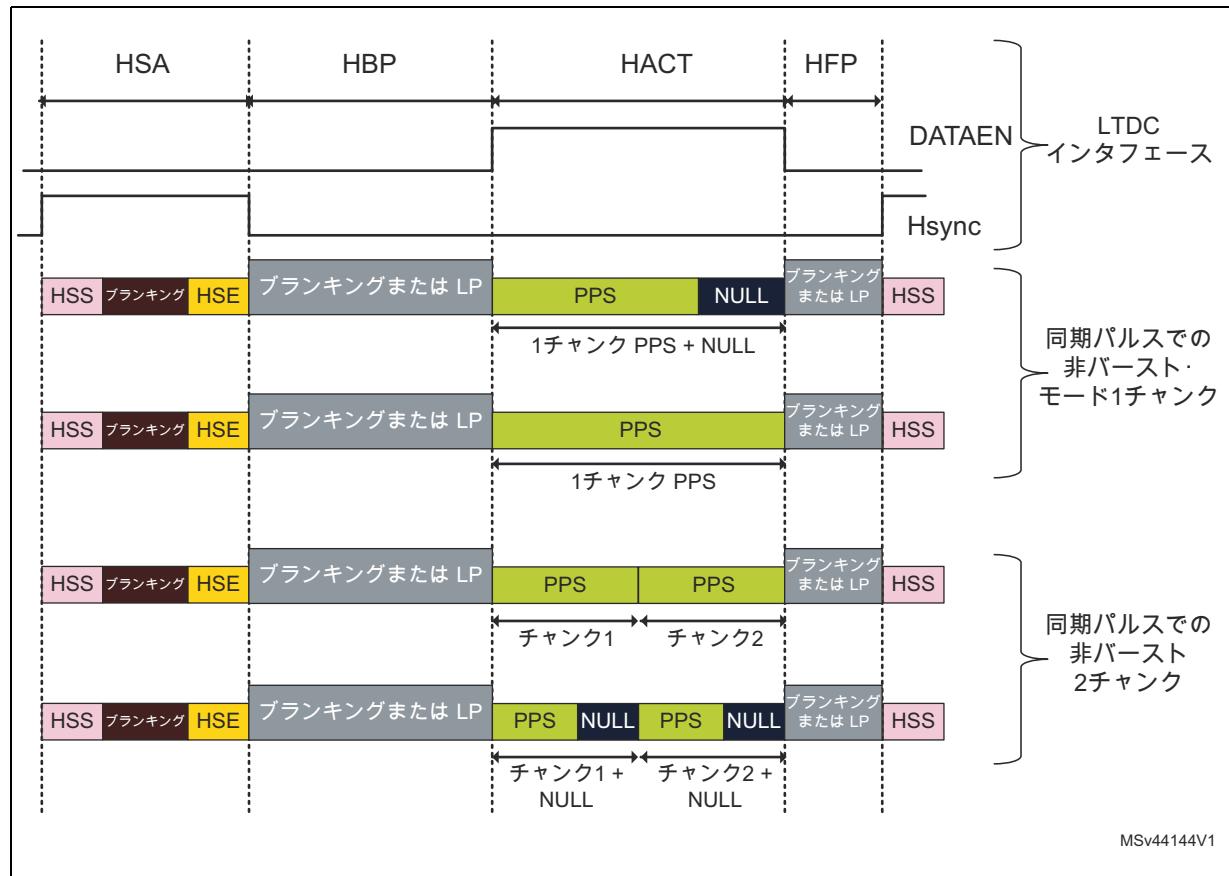

DSI ホストのビデオ・モードは、DSI 仕様で定義された3種類の動作モードをサポートします。

ビデオ・モードは、完全なフレームを保持できるグラフィカル RAM を組み込んでいないディスプレイで使用されます。

ビデオ・モードのディスプレイは内部コントローラがないため、継続的なピクセル・ストリームを供給するために DSI ホストに依存します。

#### 同期パルスでの非バースト・モード

非バースト・モードでは、プロセッサが DSI ホストのパーティション分割特性を利用して、ビデオ・ライン送信を複数のピクセルのチャンクに分割し、オプションで null パケットを使ってインターリープします。この処理は、LTDC インタフェース入力ピクセルの帯域幅を DSI リンクの帯域幅と合わせるために実行されます。

このモードでは、ホスト・コントローラとディスプレイでピクセル・データの完全なラインを格納する必要はありません。このモードでは、1つのビデオ・パケットの内容のみを格納する必要があり、メモリ要件を最低限に抑えます。

このモードを使用すれば、ペリフェラルは同期パルス幅を含めて元のビデオ・タイミングを正確に再構築できます。

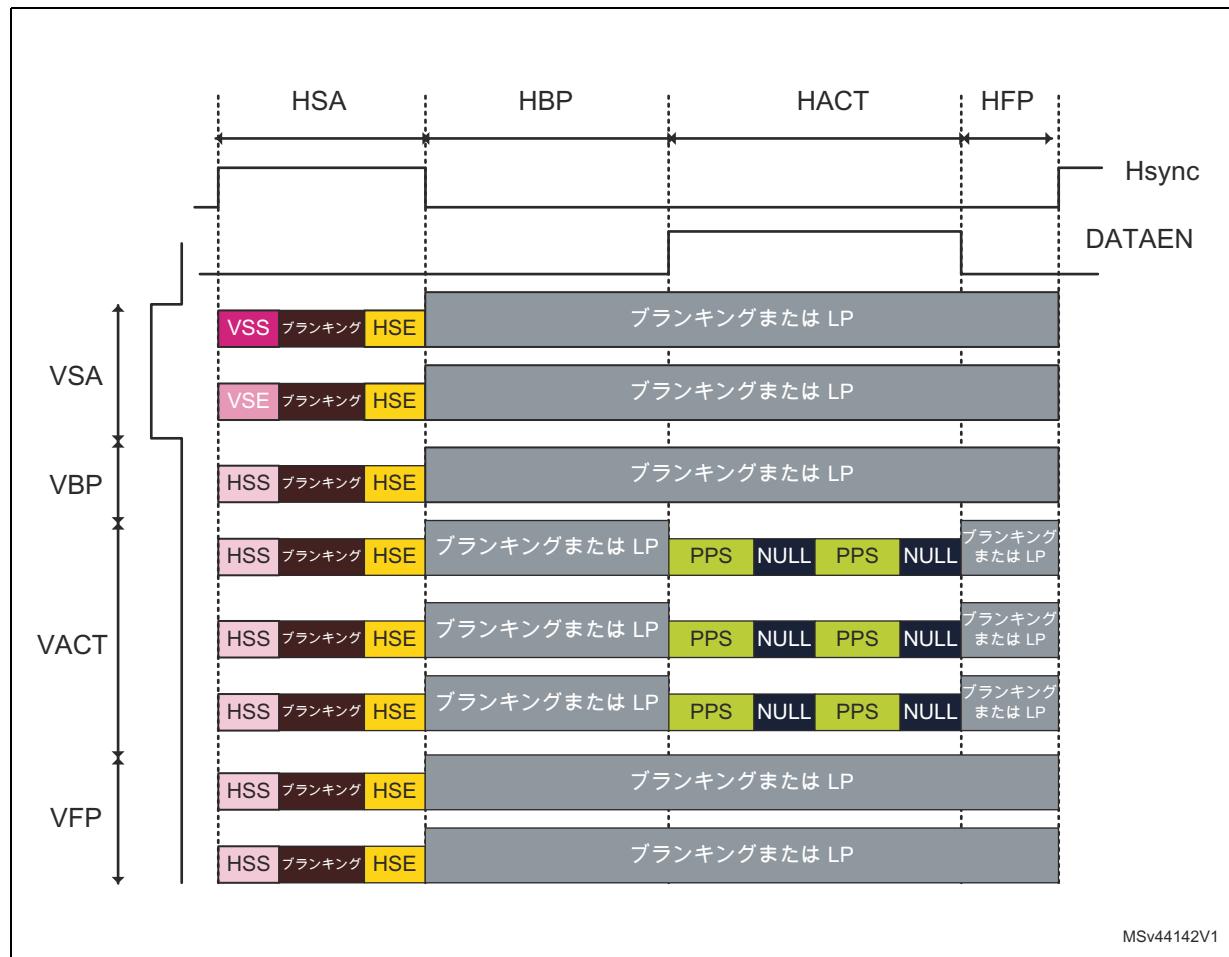

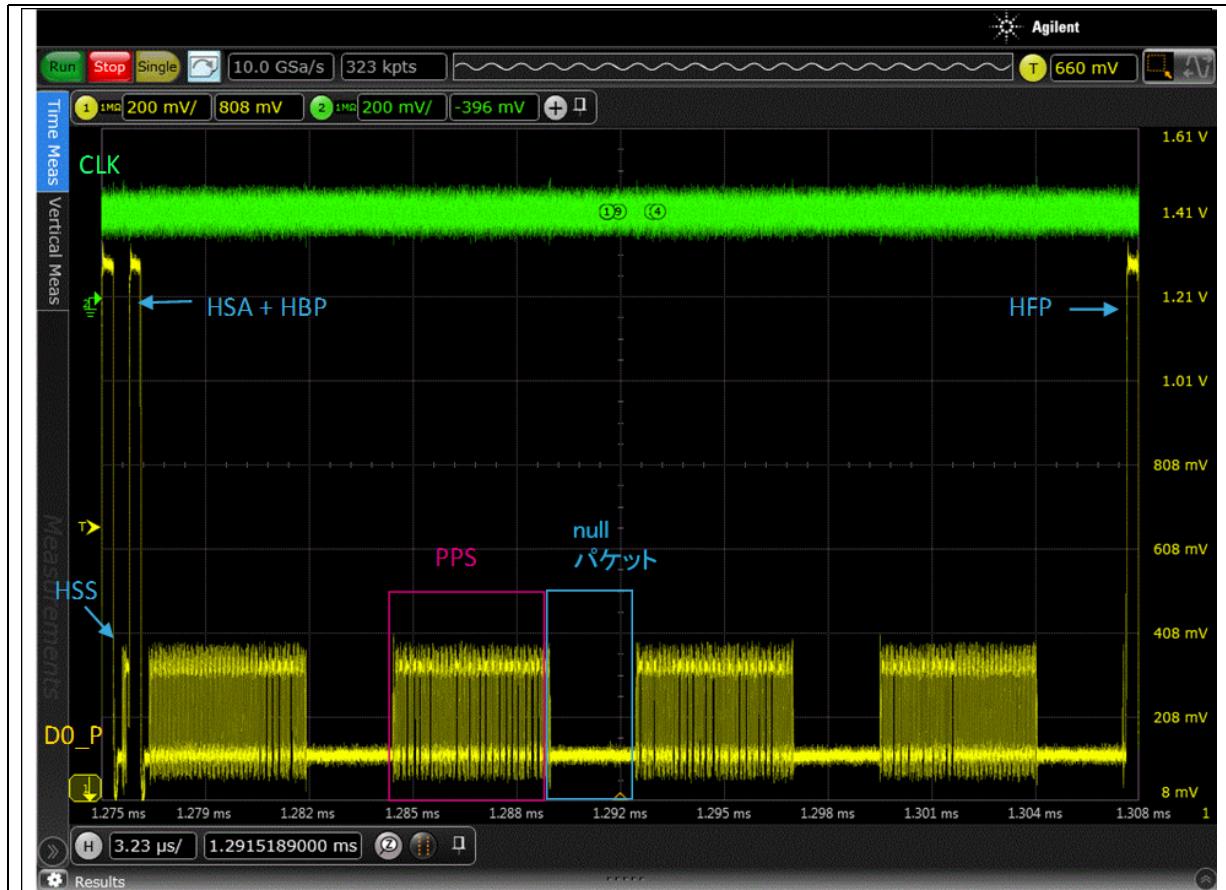

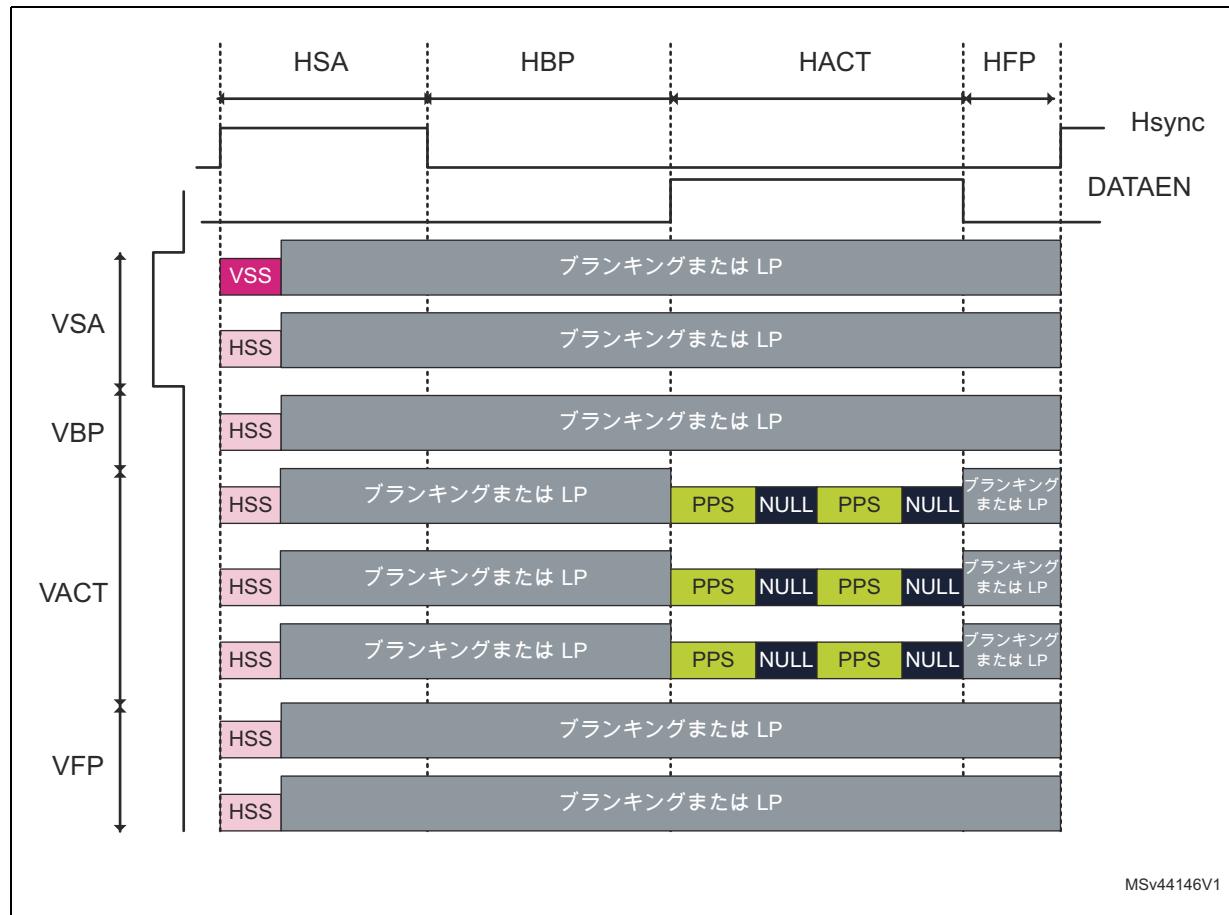

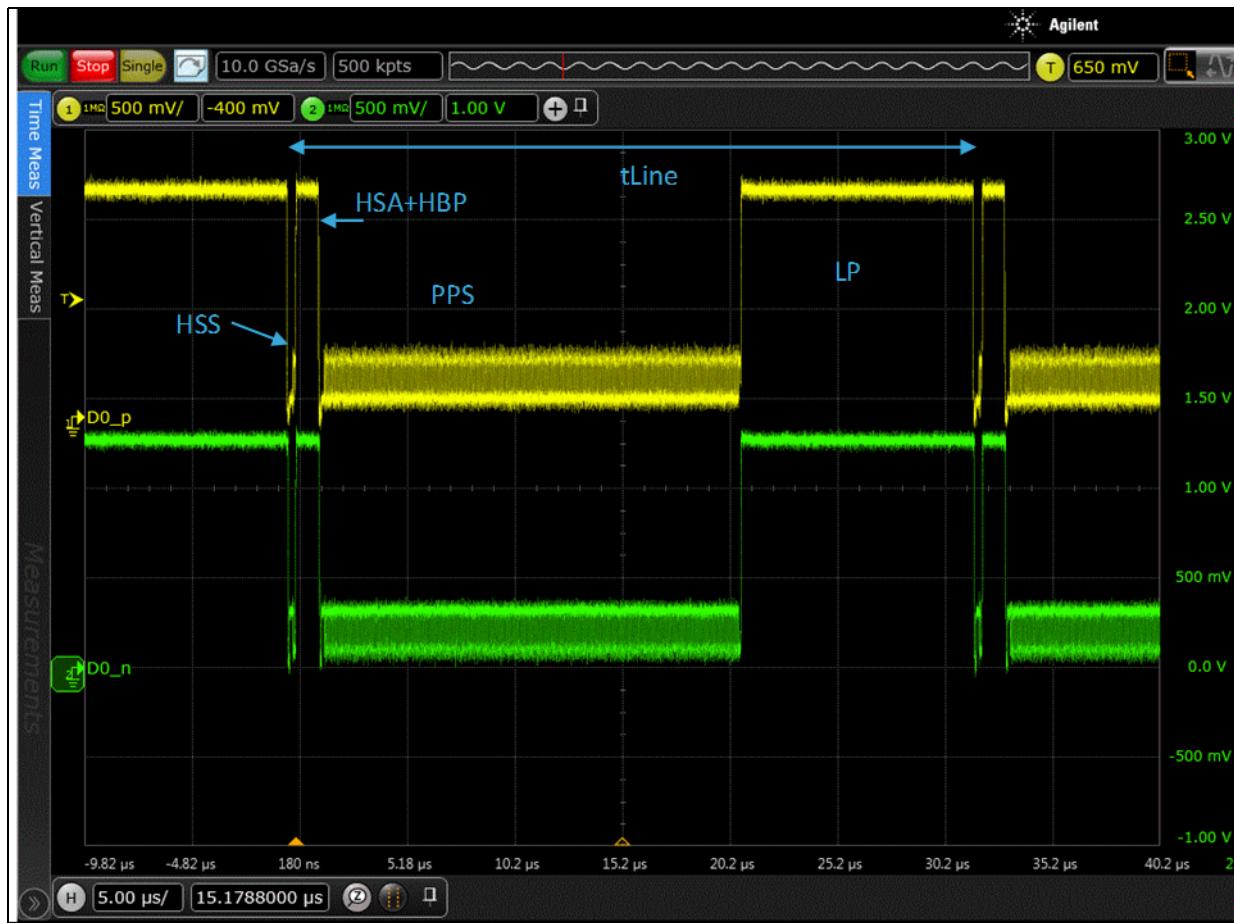

同期パルスでの非バースト・モードにおける標準的なフレームを図 59 に示します。

# 参考資料

図 59. 同期パルスでの非バースト・モードのフレーム

MSv44142V1

HSA (Hsync アクティブ) 期間は、HSS (Hsync 開始) 、ブランкиング・パケット、HSE (Hsync 終了) パケットで構成されます。この領域のパケットはハイスピード・モードで送信され、HSA 期間中はリンクが LP に移行しません。

DSI ホストは、HSS パケットと HSE パケットのタイミングを HSA 期間と合わせるために必要なブランкиング・パケット・サイズを自動的に計算します。

DSI ホストが Vsync 立ち上がりエッジ (Vsync 信号がアクティブ・ハイ) を検出すると、HSS パケットではなく Vsync 開始 (VSS) パケットで HSA 期間を開始します。

Vsync 立ち下がりエッジが検出されると、DSI ホストは HSS パケットではなく Vsync 終了 (VSE) パケットを送信して VSA 期間の終了を示します。

Vsync アクティブ (VSA) 領域内のその他のラインは HSS パケットで開始されます。

垂直アクティブ (VACT) 期間外では、HSA 期間後から水平ラインの終了までリンクが LP に移行します。

VACT 領域では、DSI ホストが上記に示した HSA 期間を伝達してから、リンクは LP に移行するか、水平バック・ポーチ (HBP) 期間に相当するタイミング期間のブランкиング・パケットを送信します。その後、DSI ホストは、最終的にピクセル送信タイミングを水平アクティブ (HACT) 期間と合わせる null パケットとともに、PPS (パック済みピクセル・ストリーム) パケットを1つ以上送信します。

# 参考資料

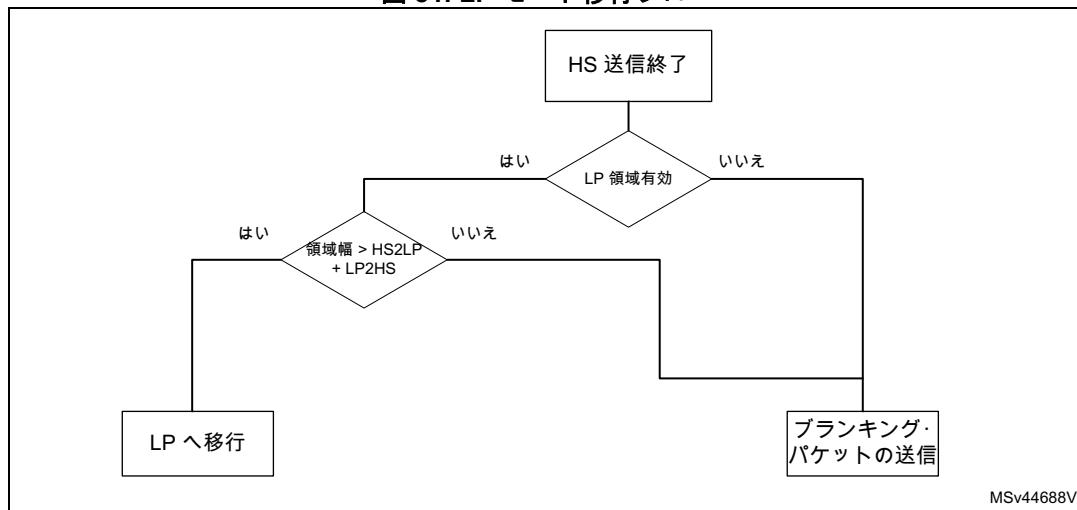

HACT 期間が終了すると、DSI ホストは LP に移行するか、水平フロント・ポーチ (HFP) 期間に相当する期間のブランкиング・パケットを送信します。

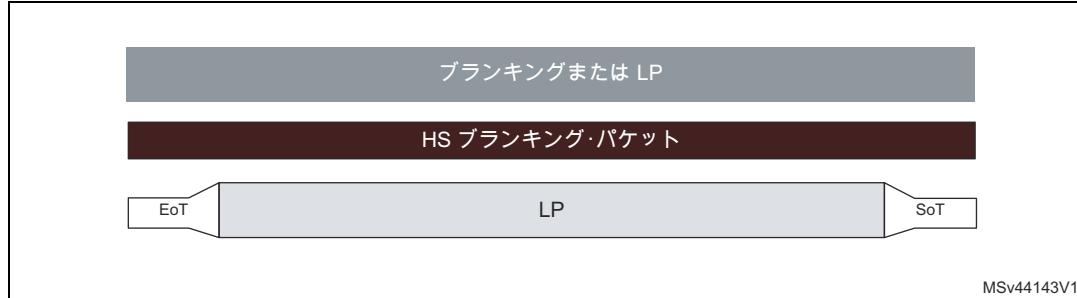

注： 領域がブランкиングまたは LP でタグ付けされている場合、DSI ホストが合計期間のハイスピード・ブランкиング・パケットを送信するか、リンクを低消費電力モードに移行できることを意味します。

DSI ホストには、期間タイミングを合わせるためにブランкиング・パケット内で必要になるバイト数を計算する機能があります。

低消費電力モードの場合、DSI PHY は低消費電力モードに移行する前に送信終了シーケンスを開始します。その後、新たな HS 送信を開始する前に、DSI PHY は送信開始シーケンスを発行します。

DSI ホストは、特定の期間において低消費電力への切り替えが可能なのかを把握するために、低消費電力遷移 (EoT および SoT のシーケンス) のオーバーヘッドを把握する目的でユーザからの入力が必要になります。

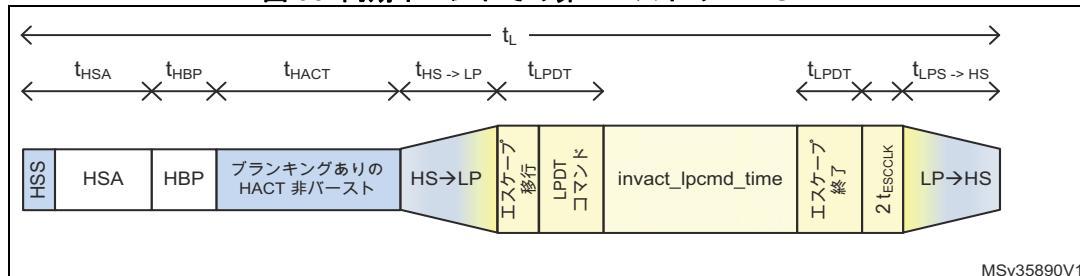

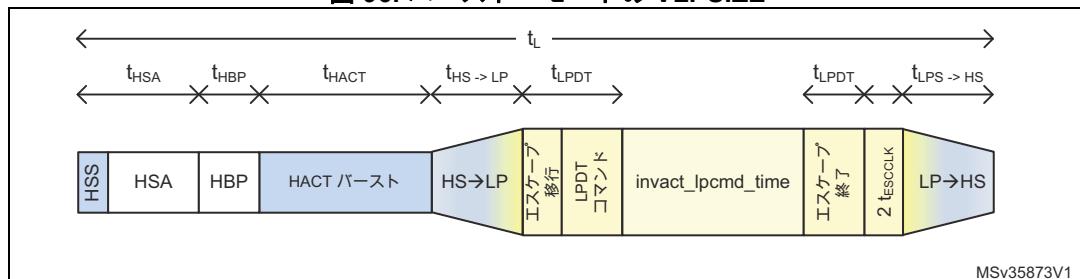

図 60 に、ブランкиングまたは低消費電力の領域で使用可能な2つのシナリオを示します。

図 60. ブランкиングまたは LP の定義

VACT 期間中、数多くの水平ラインの設定があります。

# 参考資料

図 61 では、個別に使用可能な VACT 領域ラインの設定を示します。

図 61. 同期パルスでの非バースト・モードの VACT 領域

HBP期間中およびHFP期間中、HSモードとLPモードの遷移に十分な時間がない場合は、リンクがLPに移行するか、DSIホストがブランкиング・パケットを送信します。

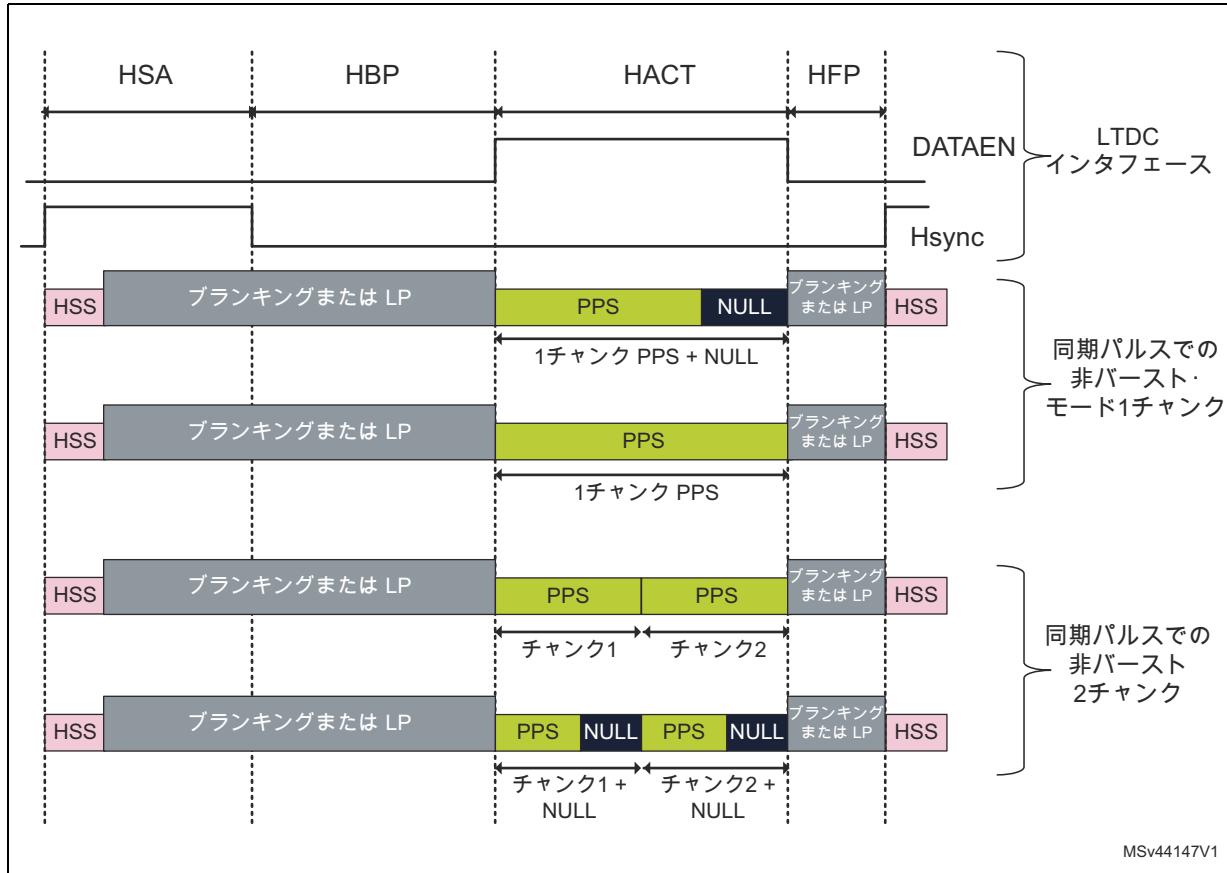

HACT期間中、DSIホストはLTCD HACT期間に合ったタイミング期間でピクセル・データを送信する必要があります。DSIとピクセル・クロック周波数に応じて、DSIホストは1つ以上のチャンクを使用してピクセル・データを送信できます。

各チャンクには、パケット・ピクセル・ストリーム (PPS) パケットまたはnullパケット付きのPPSパケットのみを含めることができます。

非バースト・モードでのチャンク数とnullパケットのサイズの選択方法は、[セクション 5.2.1 : LTDC インタフェースでのビデオ・モード](#)で説明しています。

# 参考資料

## DSI ホストの説明

AN4860

図 62 に4つのチャンクでのアクティブ・ラインを示します。各チャンクは PPS パケットと null パケットで構成されています。

図 62. null パケット付きの4つのチャンクを設定したアクティブ・ライン

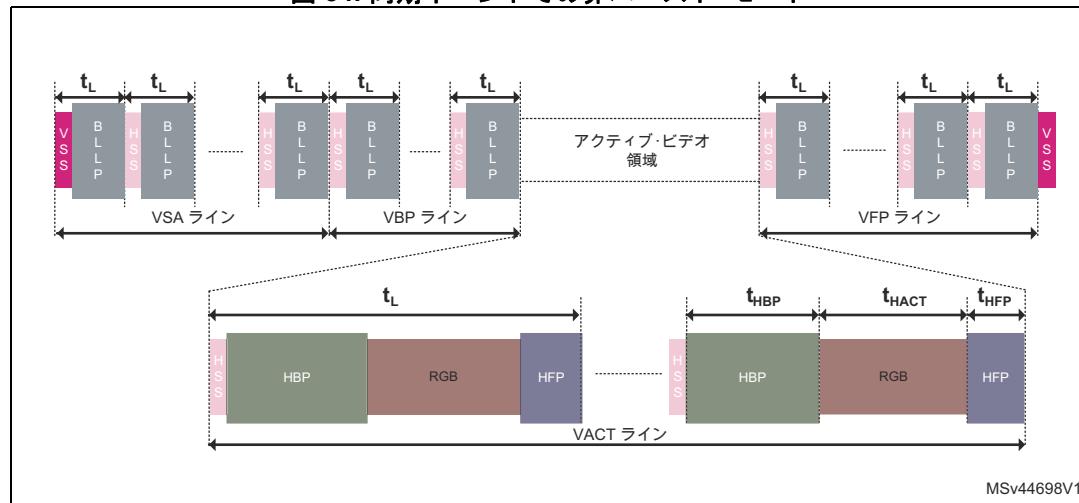

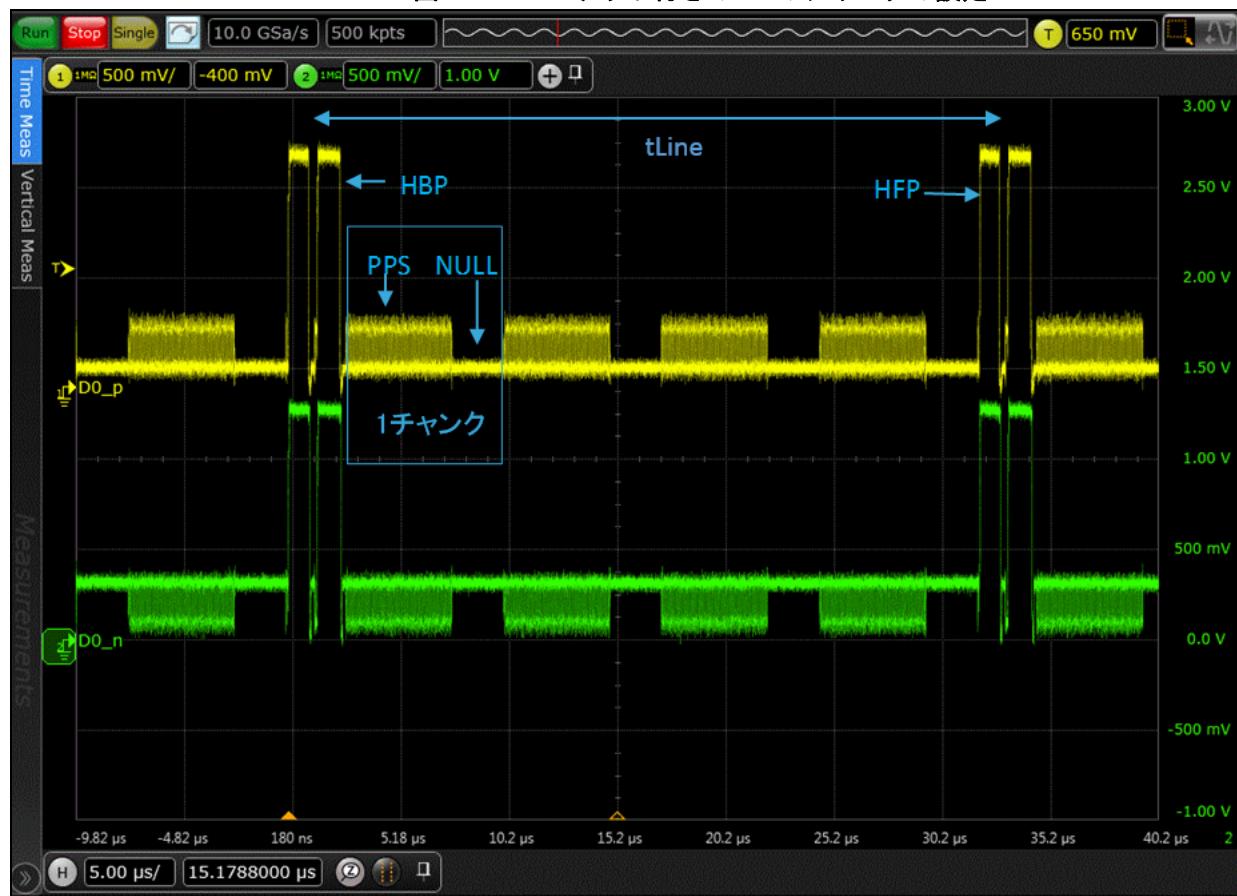

### 同期イベントでの非バースト・モード

このモードでは、同期パルス幅の正確な再構築が不要となり、1つの同期イベントが置き換えられます。このモードでは次のように動作します。

- 各同期パルスの開始のみが送信されます。

- 送信は、LTDC と同じレートで実行されます。

- LP モードへの切り替えに十分な時間がない場合、LP の時間間隔はブランкиング・パケットで置き換えられます。

# 参考資料

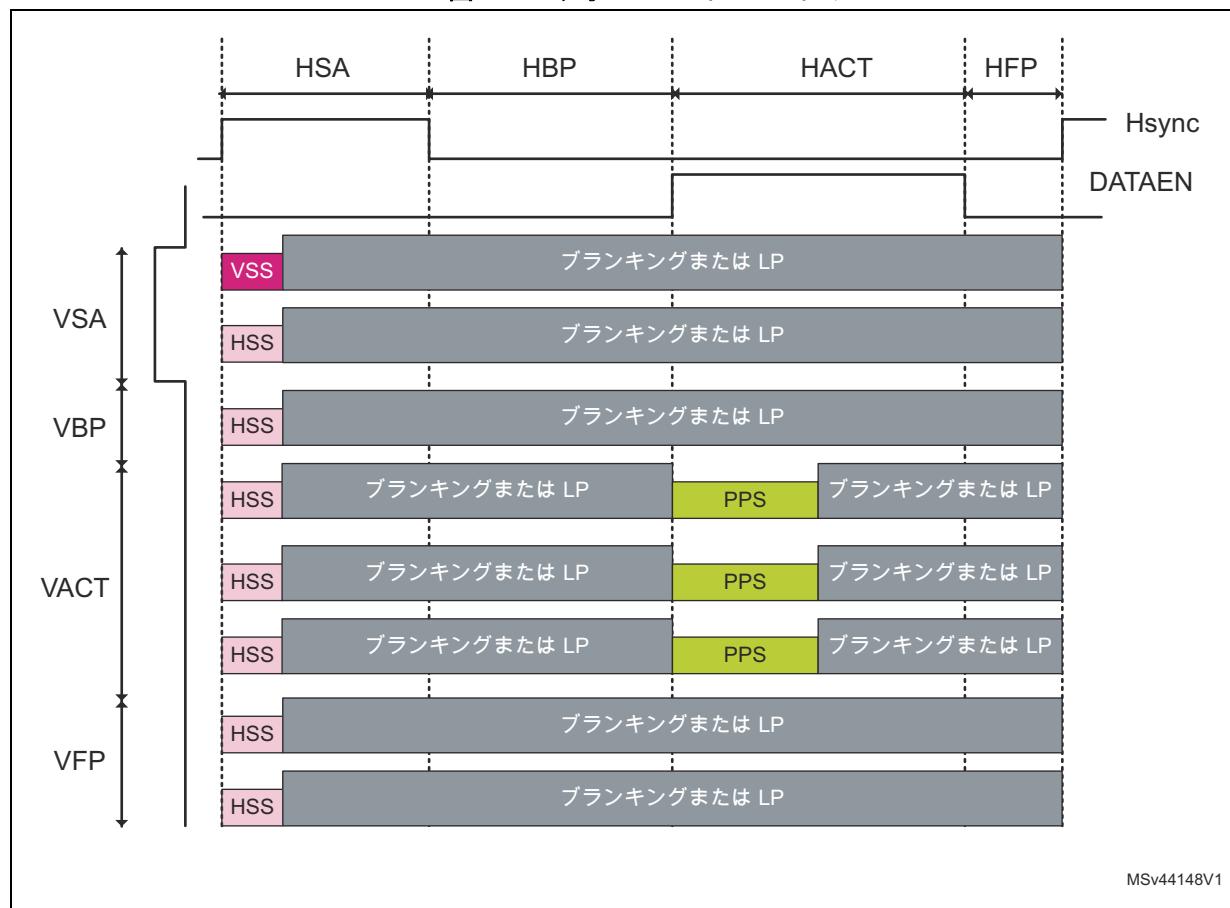

同期イベントでの非バースト・モードにおける標準的なフレームを図 63 に示します。

図 63. 同期イベントでの非バーストのフレーム

VSA 領域の開始は、VSS パケットで始まるラインで決まります。フレーム内のその他すべてのラインは HSS パケットで始まります。

非アクティブ領域 (VSA、VBP、VFP) では、リンクが HSS パケットを送信してから次のラインまで LP に移行します。

VACT 領域では、DSI ホストが HSS パケットを送信してから、HSA + HBP 期間の終了まで LP に移行するか、ブランкиング・パケットを送信します。

HACT 領域は、同期パルスでの非バースト・モードと同じです。

# 参考資料

図 64 に、同期イベントでのバースト・モードの VACT 領域を示します。

図 64. 同期イベントでのバースト・モードの VACT 領域

同期イベントでの非バースト・モードの VACT 領域は、HSA 期間中のみ同期パルスとは異なります。

DSI ホストは HSS パケットを送信して、HSA 期間の開始を通知します。その後、リンクが LP に移行するか、ホストが HACT 領域の開始までブランкиング・パケットを送信します。

## 非バースト・モードを使用する場合

非バースト・モードは、ピクセル送信のレートを合わせやすくなります。このモードでは次のことが可能です。

- 特定数のピクセルだけメモリに格納して、ピクセル・ライン全体を必要としません (DSI ホストでの RAM 要件を抑えます)。

- 少量のピクセル・バッファリングだけ (ピクセル・ライン全体より少ない) をサポートするデバイスで動作します。

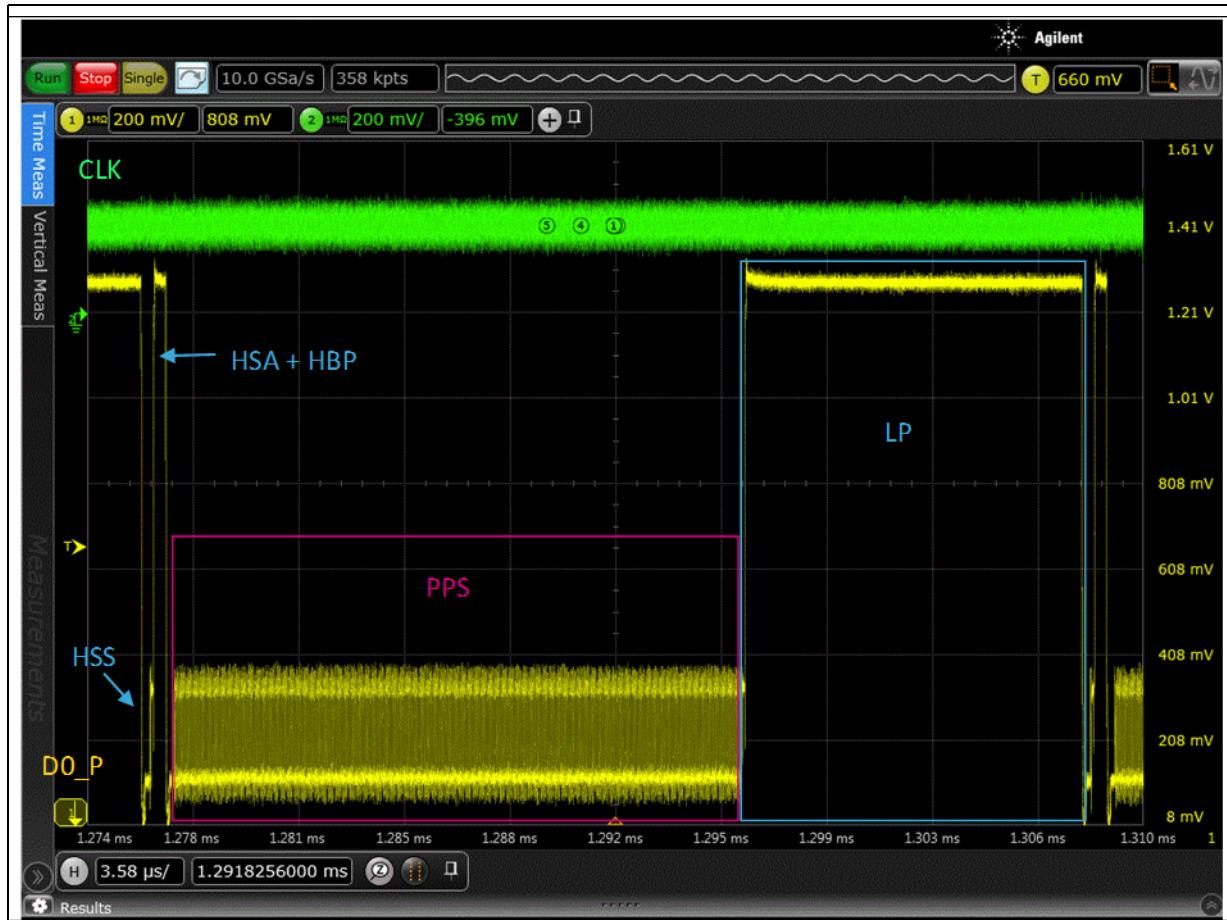

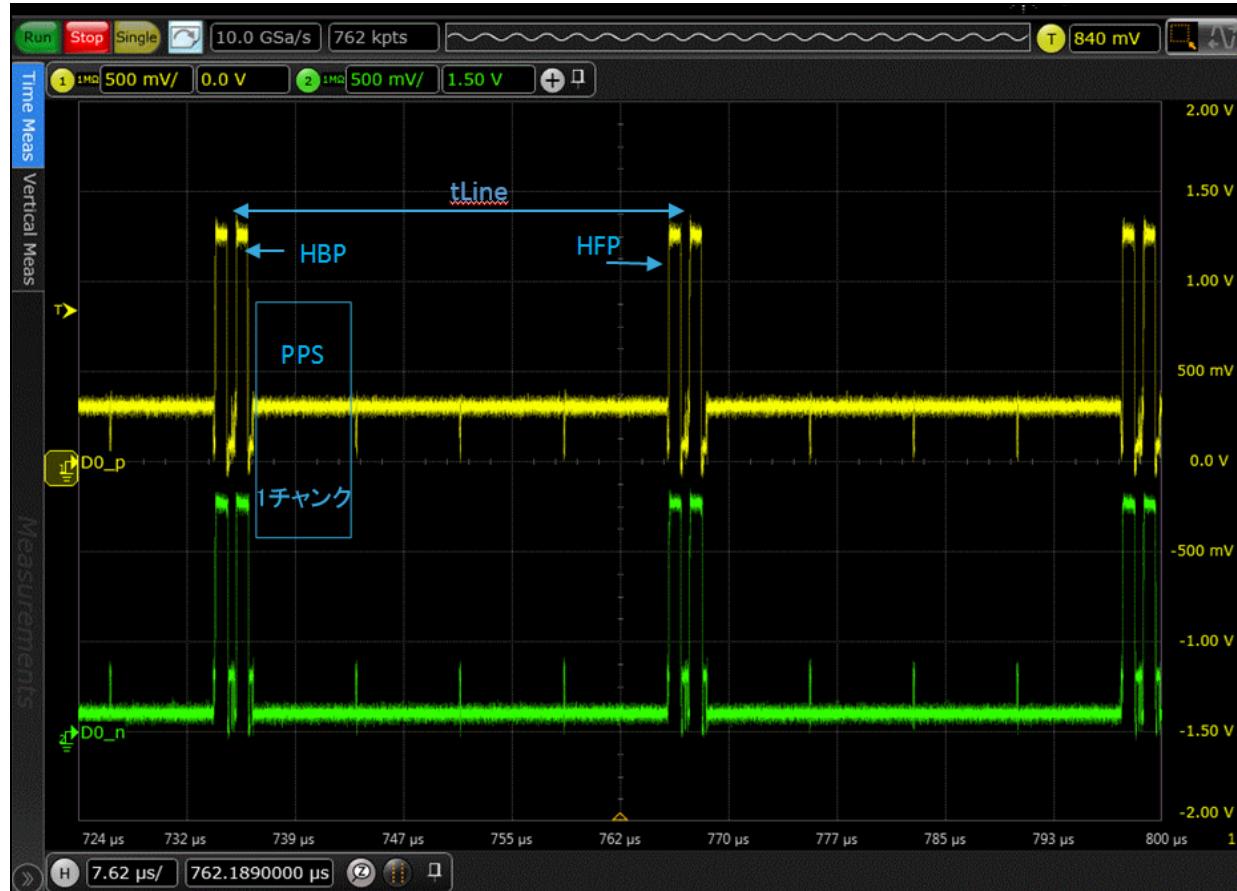

## バースト・モード

ビデオ・バースト・モードでは、RGB ピクセル・パケットが時間圧縮され、LP モード (節電) または DSI リンク上のその他の送信のマルチプレクスのために、スキャンライン中の時間が増えます。

このモードでは、アクティブなピクセル・ライン全体を FIFO にバッファリングし、割込みなしの1つのパケットで送信します。この送信モードでは、DSI ペイロード・ピクセル FIFO にアクティブなピクセル・データの全ラインを格納できる容量が必要になります。

# 参考資料

このモードは、LTDC 帯域幅と DSI リンク帯域幅の差が大きい場合に適しています。バースト・モードによって、DSI ホストは1回のデータ・バーストでアクティブ・ビデオ・ライン全体を素早くディスパッチして、低消費電力モードに戻ることができます。

図 65 に、ビデオ・バースト・モードでの標準的なフレームを示します。HACT 領域に同期イベントでの非バースト・モードとの違いがあります。バースト・モードでは、HACT 領域において RGB データを最大速度で1つのパケットで送信してから、リンクが LP モードに移行します。

図 65. ビデオ・バースト・モードのフレーム

# 参考資料

## DSI ホストの説明

AN4860

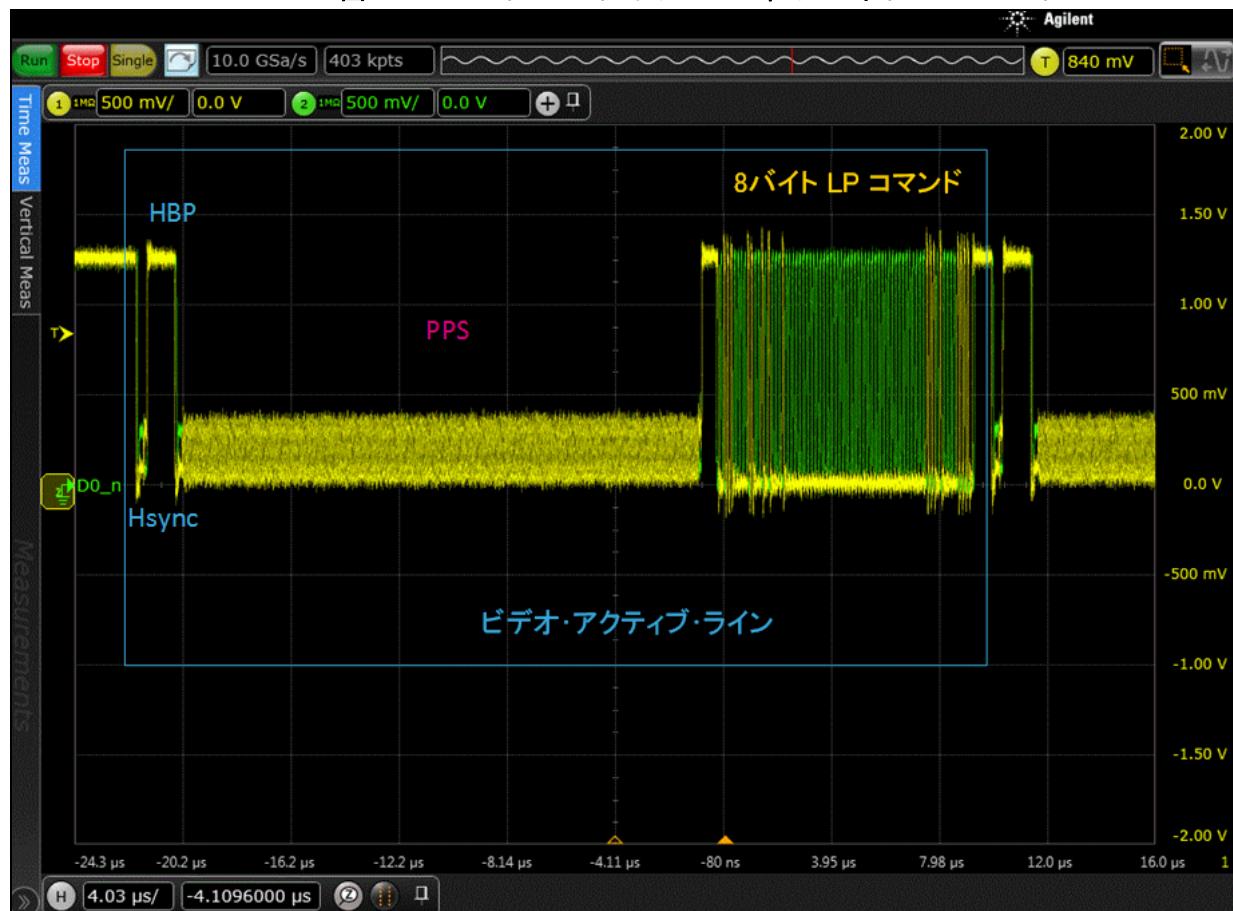

図 66 には、PPS パケットを使用して送信した RGB ピクセル・データのあるビデオ・アクティブ・ラインを示しています。DSI リンク帯域幅が LTDC からの DSI 入力帯域幅より高いため、リンクは長時間 LP モードに移行します。

図 66. バースト・モードでのアクティブなライン

### バースト・モードを使用する場合

バースト・モードは次の場合に使用されます。

- ディスプレイ・デバイスが、受信バッファでのオーバーフローを避けるために1つのパケット・バーストでピクセル・ライン全体の受信をサポートしています。

- DSI 出力帯域幅は、リンクがラインごとに低消費電力に移行できる関係において、LTDC インタフェース入力帯域幅より高くする必要があります。

### ビデオ・モードの比較 :

図 67 に、3種類のビデオ・モード・フォーマットの比較を示します。

同期パルスでの非バースト・モードは、ビデオ・タイミング情報の伝達において最も精度の高いモードですが、HSA および HACT の領域で LP に移行できません。

同期イベントでの非バースト・モードは、HSA 領域で LP モードに移行できます。

バースト・モードは、HACT 領域で LP モードに移行できるため、最も電力効率の良いモードです。

図 67. ビデオ・モードの比較

## 4.2.2 アダプティッド・コマンド・モード

アダプティッド・コマンド・モードは、独自のグラフィカル RAM を持つディスプレイとのインターフェース接続に非常に適した動作モードです。

このモードは、CPU や DMA の負荷なく LTDC でディスプレイのグラフィカル RAM を自動的にリフレッシュします。

GRAM のリフレッシュ動作は LTDC と連携して実行されます。

- DSI ホストが LTDC を制御し、1フレームで有効にします。

- LTDC から受け取る RGB データをキャプチャして、一連の DCS ロング書き込みコマンド・パケットをディスプレイに送信します。

- グラフィカル RAM が完全にリフレッシュされると、DSI ホストが LTDC を自動的に停止させ、DSI リンクが低消費電力モードに移行します。

ユーザは、フレームバッファの送信準備ができたときに1つのビットをセットするだけで、ディスプレイのリフレッシュ動作を制御します。

フレームバッファの内容を更新する必要がない限り、ディスプレイはリフレッシュ動作に内部グラフィカル RAM を使用します。これはディスプレイの更新頻度が低い場合に役立ち、マイクロコントローラ側の帯域幅使用量と全体の消費電力を最小限にします。

リフレッシュは、リフレッシュ時間を低減するために、リンクの最大速度で実行できます。LTDC 側の帯域幅要件には、特に注意を払う必要があります。

ユーザはフレームバッファの一部だけをリフレッシュでき、アニメーションを高速化して、マイクロコントローラ側の帯域幅要件を削減できます。

# 参考資料

アダプティッド・コマンド・モードは、DCS (ディスプレイ・コマンド・セット)、WMS (write\_memory\_start)、WMC (write\_memory\_continue) のコマンドのみサポートしています。正常に動作させるには、ディスプレイ設定コマンドおよびティアリング効果の初期化など追加のコマンドが必要になります。これらのコマンドは、APB インタフェースを介して送信する必要があります。

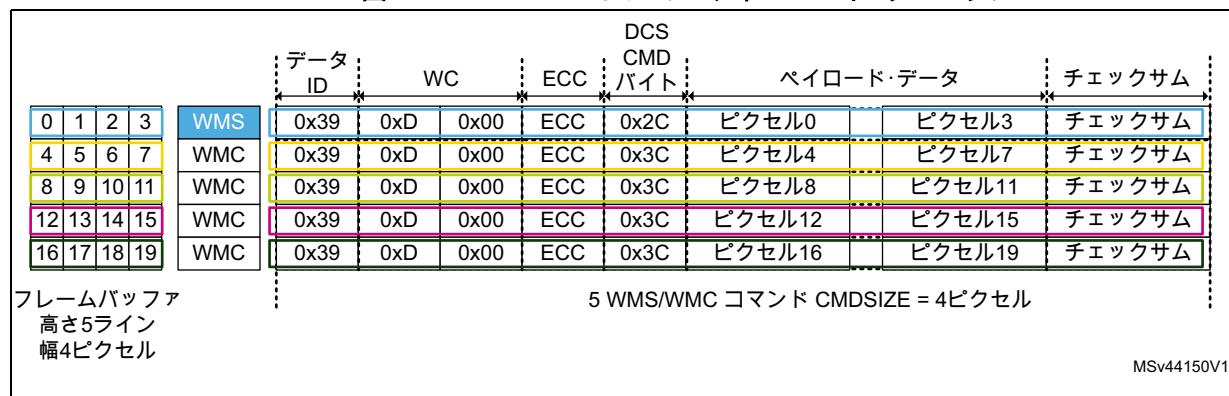

## アダプティッド・コマンド・モードでのディスプレイ・リフレッシュの例

リフレッシュ・プロセスは、アダプティッド・コマンド・モード時に DSI ホストによって自動的に実行されます。

DSI ホストは、フレームバッファからピクセル・データをフェッチして DSI ホストに渡す LTDC を有効にします。DSI ホストは、専用 FIFO にピクセル・データを格納してから、WMS および WMC の DCS コマンドにカプセル化します。

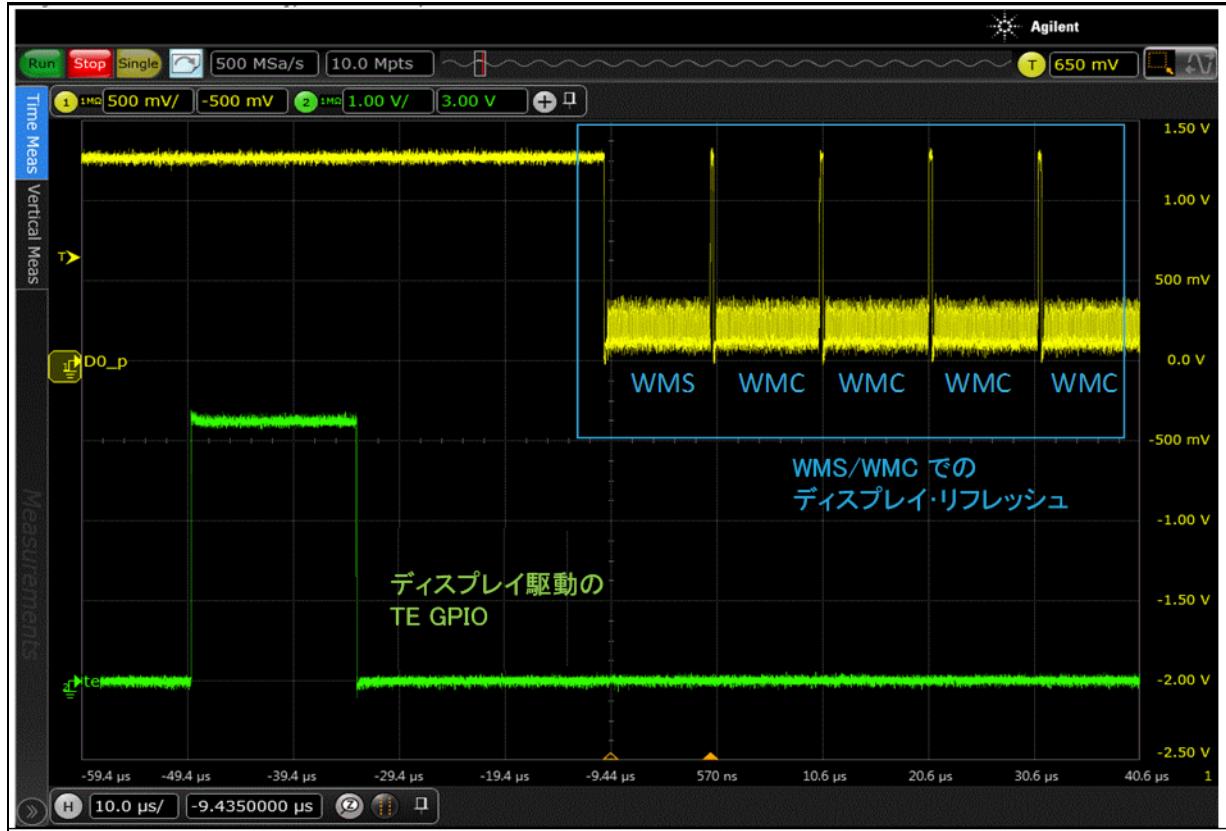

図 68 に示す例では、5つのラインのフレームを、5つの DCS ロング書込みコマンド (Write\_Memory\_Start (WMS) 1つと、Write\_Memory\_Continue (WMC) 4つ) で伝達できます。

CMDSIZE パラメータは、各 WMS/WMC コマンドで転送されるピクセル数を定義します。

この例では、CMDSIZE がピクセル単位のライン・サイズと同等になるようにセットされているため、各 DCS コマンドは4ピクセルで構成される完全なラインをカプセル化します。

図 68. WMS/WMC でのフル・ディスプレイ・リフレッシュ

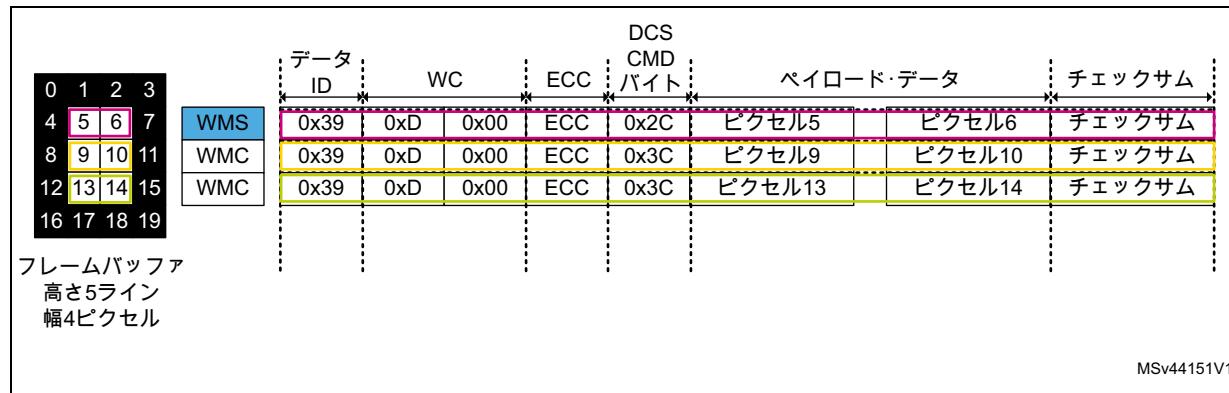

## アダプティッド・コマンド・モードでの部分リフレッシュの例

アダプティッド・コマンド・モードは、画面全体を送信する必要なく、画面の特定の部分をリフレッシュできる部分リフレッシュ機能をサポートしています。

画面全体ではなく、画面の一部だけを再送信することで次のことが可能です。

- 一部のピクセルだけをフレームバッファからフェッチするため、システム帯域幅を低減します。

- リフレッシュ時間を低減してアニメーションを高速化できます。

- DSI リンクがより長く LP モードに移行するため、消費電力を低減します。

- 最終的にフレームバッファ・ストレージに必要なメモリ量を削減します（フレームの一部だけを格納できます）。

図 69 に示す例では、中央のピクセルだけが送信されます。

CMDSIZE は、各 DCS コマンドで送信されるピクセル数にセットされます。この例では2になっています。

# 参考資料

注： ユーザは、ディスプレイ側でリフレッシュする領域を選択するために、APB インタフェースで DCS コマンドを送信しなければならない場合があります（`set_column_address` および `set_page_address`）。また、ユーザは LTDC パラメータを再プログラムして、フェッチするピクセルのウィンドウを選択する必要があります。

必要な設定に関する詳細については、STM32cube コマンド・モードの例を参照してください。

図 69. ディスプレイの部分リフレッシュ

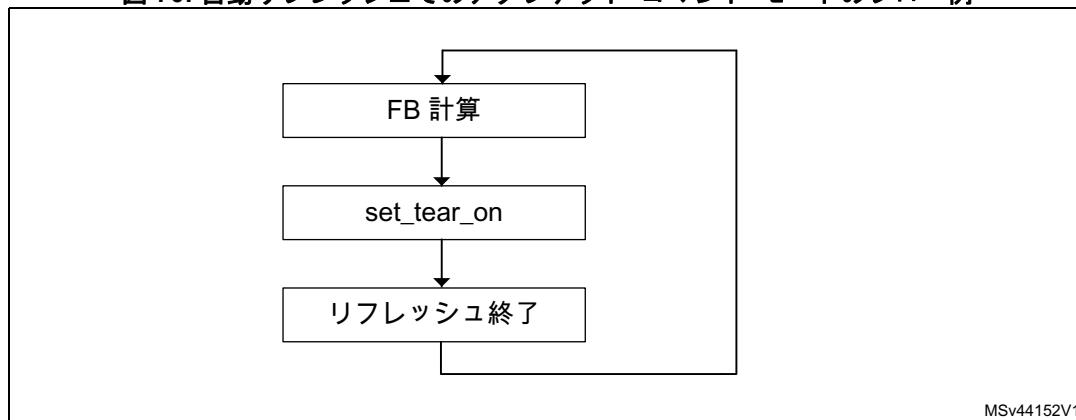

アダプティッド・コマンド・モードの基本的なフローを図 70 に示します。

フレームバッファの準備ができたら、ユーザは `set_tear_on` コマンドを送信してディスプレイ側で TE レポートを有効にします。ディスプレイがプログラムされたスキヤンラインに達すると、TE トリガーメッセージを送信します。

自動リフレッシュ機能が有効になっている場合、TE イベントを受信すると、ホストは WMS/WMC の DCS コマンドを送信してディスプレイを自動的にリフレッシュします。

自動リフレッシュ機能が有効になっていない場合、DSI ラッパーで1つのビット（LTDC\_EN ビット）をセットするだけでリフレッシュが実行されます。

リフレッシュ動作が終了すると、`EndOfRefresh` イベントが DSI ホストに通知され、次のフレームの計算を開始できるようになります。

図 70. 自動リフレッシュでのアダプティッド・コマンド・モードのフロー例

### アダプティッド・コマンド・モードの利点

アダプティッド・コマンド・モードには、数多くの利点があります。

- さらに統合されたソリューションが可能です。

- 画像計算と GRAM 更新が同時に発生しません。これにより、フレームバッファからデータをフェッチする際に、LTDC と DMA2D グラフィック・エンジンの並行処理問題を回避できます。

- マイクロコントローラ側にはフレームバッファ 1つで十分です。

- フレームバッファが内部マイクロコントローラ SRAM に収まります (16bpp の色深度の 320 x 320 ディスプレイでは、フレームバッファに約 200KB が必要になります)。

- 低消費電力消費：フレームを更新する必要がない限り、ディスプレイはリフレッシュにグラフィカル RAM を使用して、リンクを低消費電力モードに移行させることができます。

- 部分リフレッシュ・サポート：ユーザはディスプレイの一部のみの更新を選択できます。これにより、リフレッシュ時間、マイクロコントローラ側の帯域幅使用量、消費電力を低減できます。

- ピクセル・クロックは、短い期間で最大帯域幅を使用できる最大周波数で設定できます。

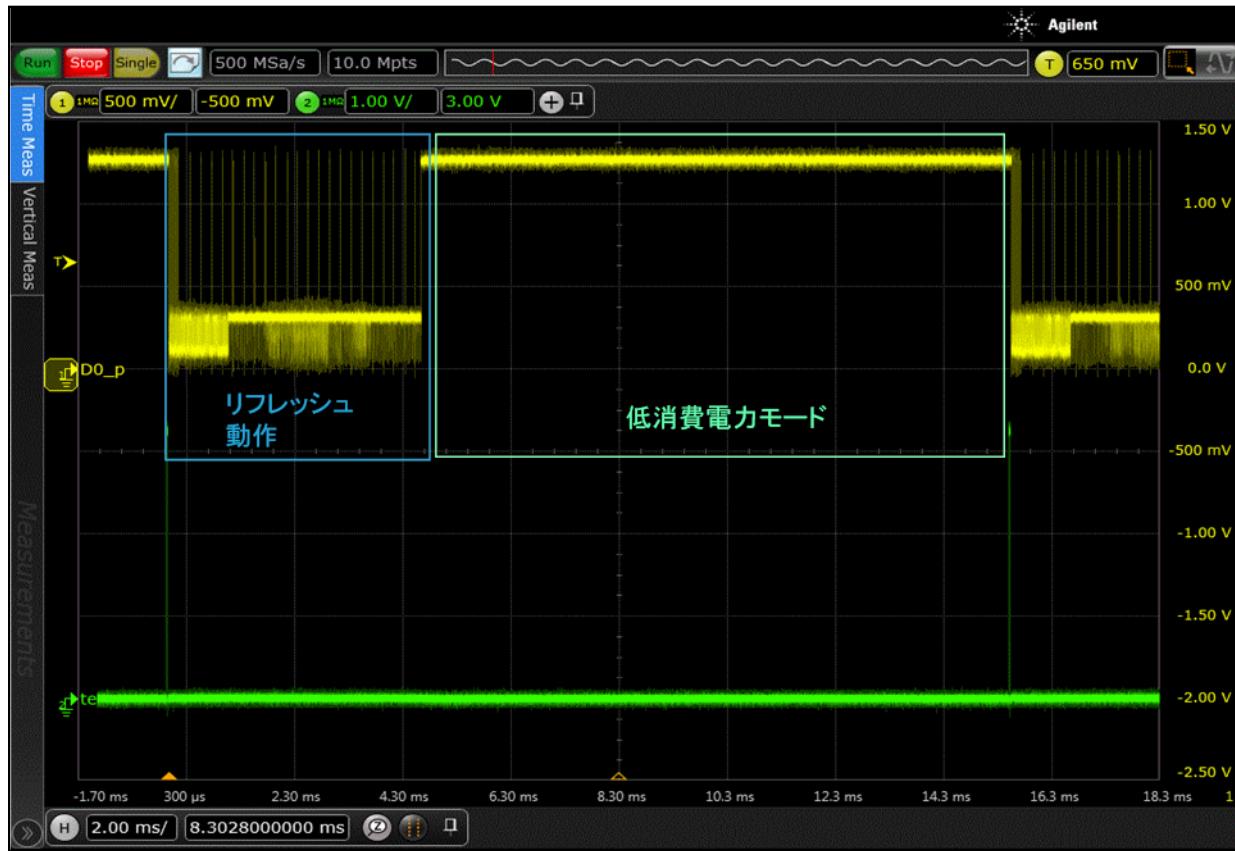

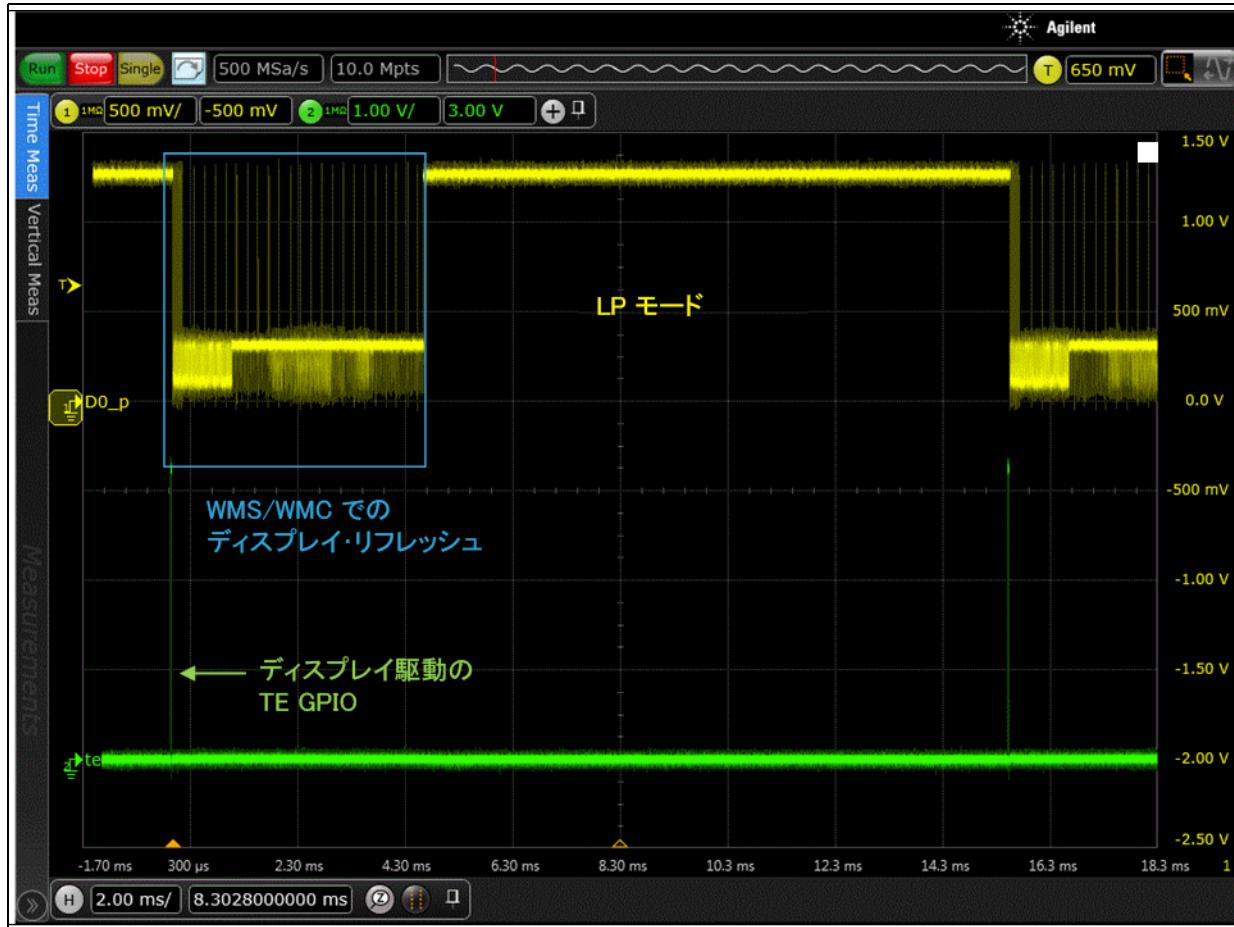

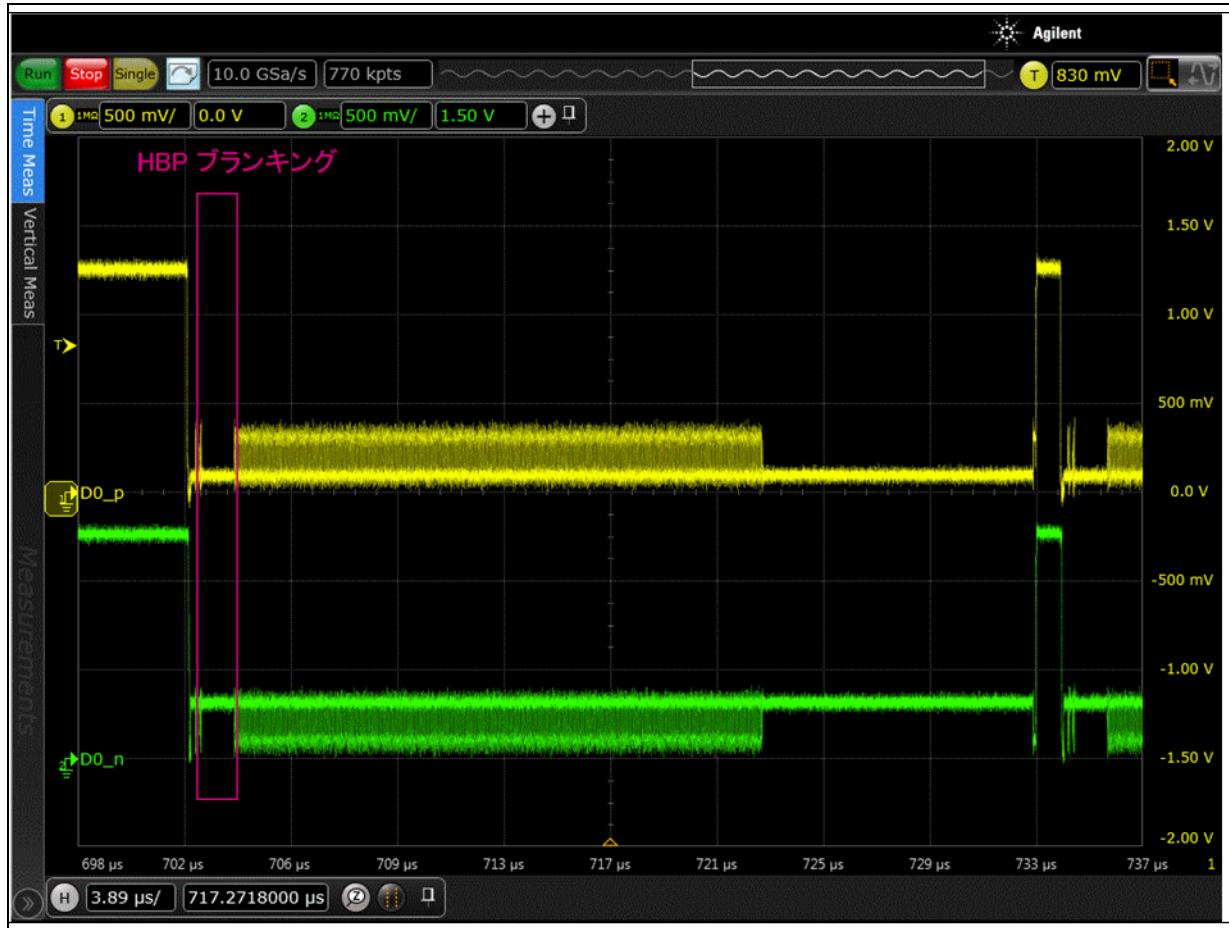

図 71 に、アダプティッド・コマンド・モードのディスプレイ・リフレッシュの例を示します。DSI ホストは DCS コマンドを送信してフレームを更新してから、LP モードに戻ります。

図 71. アダプティッド・コマンド・モードでのディスプレイ・リフレッシュ

## ティアリング効果管理

ティアリング効果は、独自のグラフィカル RAM を持つディスプレイでのリフレッシュ動作でディスプレイと DSI ホストの完全な同期を可能にします。

ティアリング効果信号は次の2つの方法で送信できます。

- 追加ピンを使用しないリンク経由

- 追加ピンの使用

### リンク経由のティアリング効果

ティアリング効果がリンク経由で実行される場合、DSI ホストは `set_tear_on` または `set_tear_scanline` のコマンドを送信して、BTA 手順でバスの制御をディスプレイに渡します。1 回目の BTA 後、ディスプレイは確認応答トリガで応答し、バスの制御をホストに戻します。ホストはもう1回 BTA 手順を開始して、バスの制御をディスプレイに渡します。プログラムされたスキャンラインにディスプレイが達すると、トリガを DSI ホストに送信して、DSI ホストにバスの制御を戻します。

割込みを発生させてグラフィカル RAM のリフレッシュを開始するか、ユーザが自動リフレッシュを選択することができます。

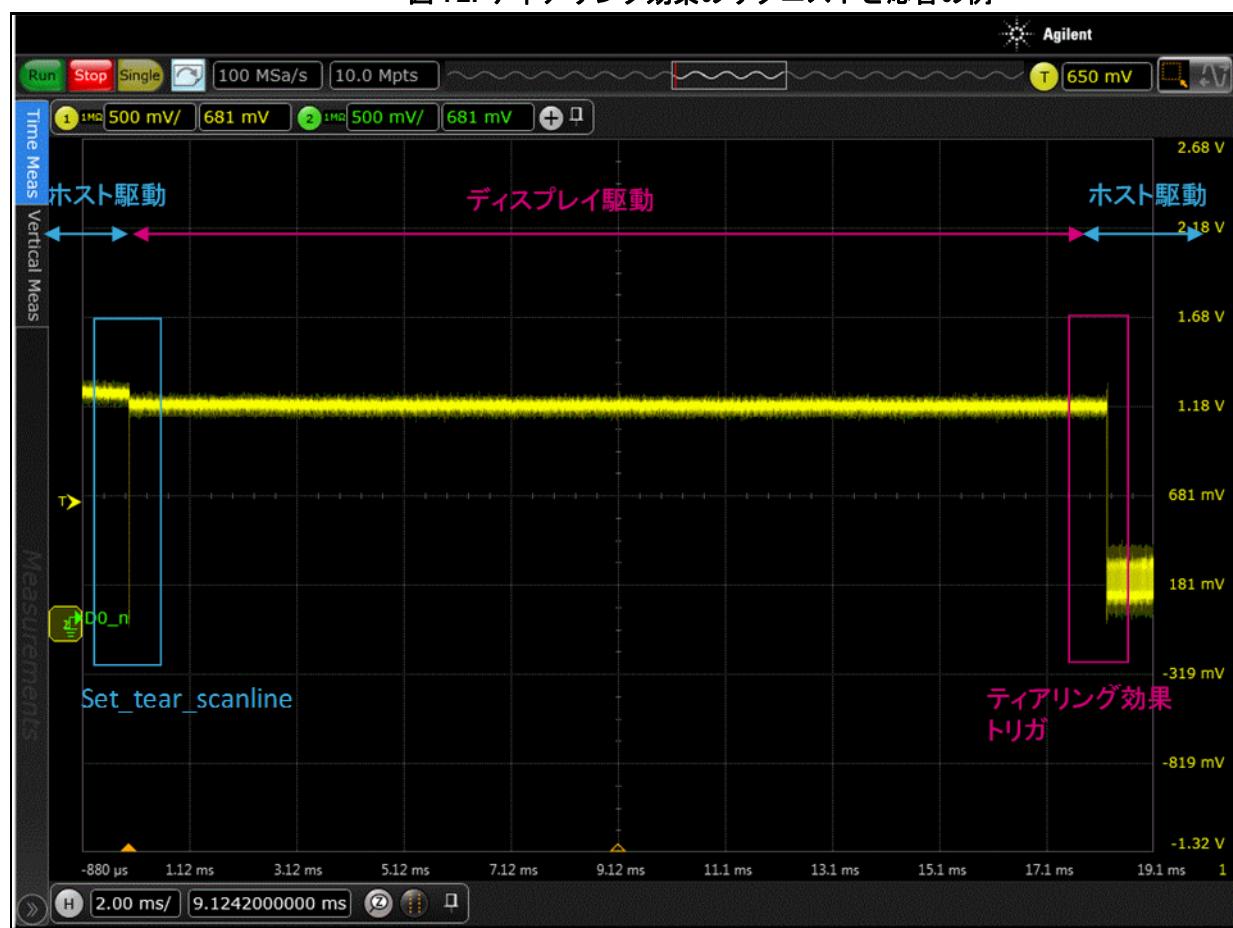

図 73 に DSI リンク経由で通知するティアリング効果を示します。

図 72. ティアリング効果のリクエストと応答の例

# 参考資料

## DSI ホストの説明

AN4860

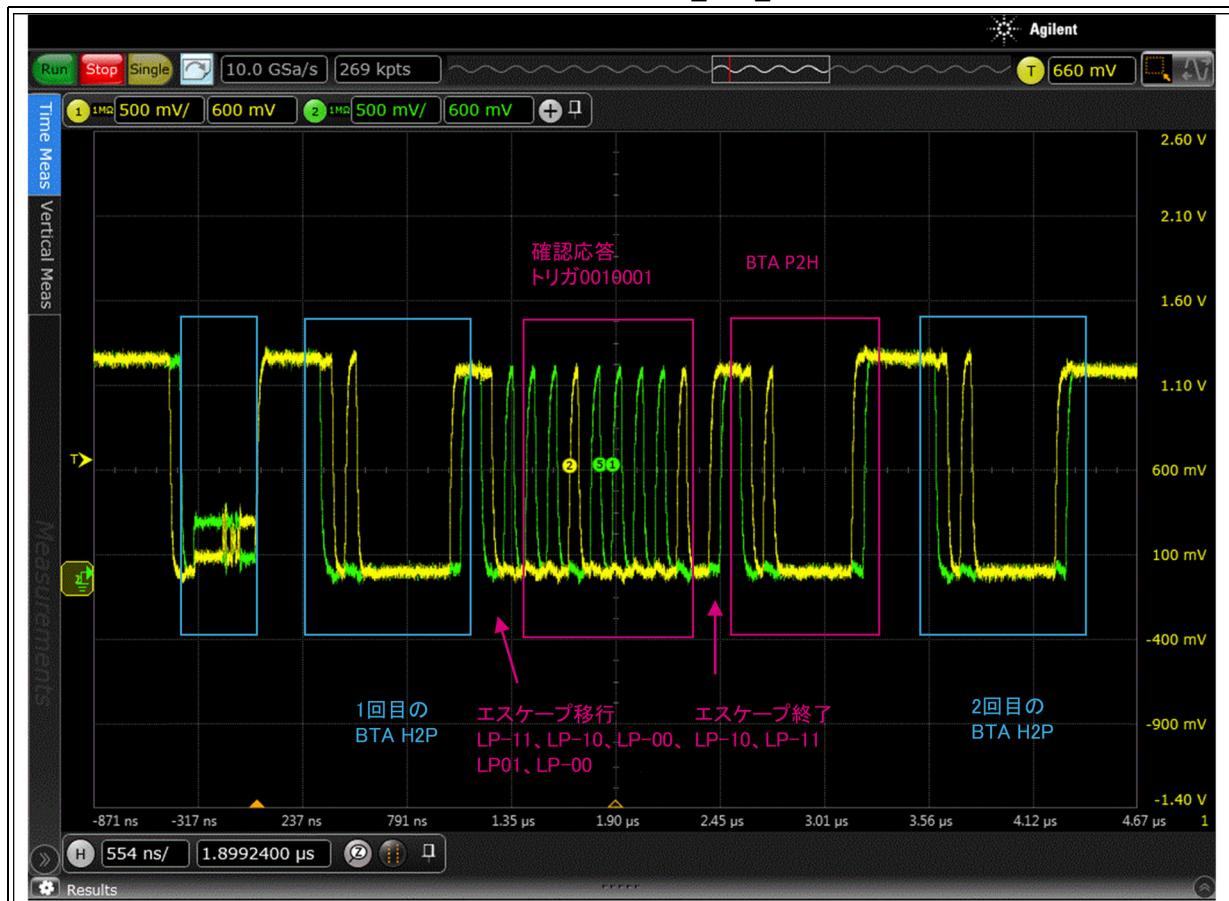

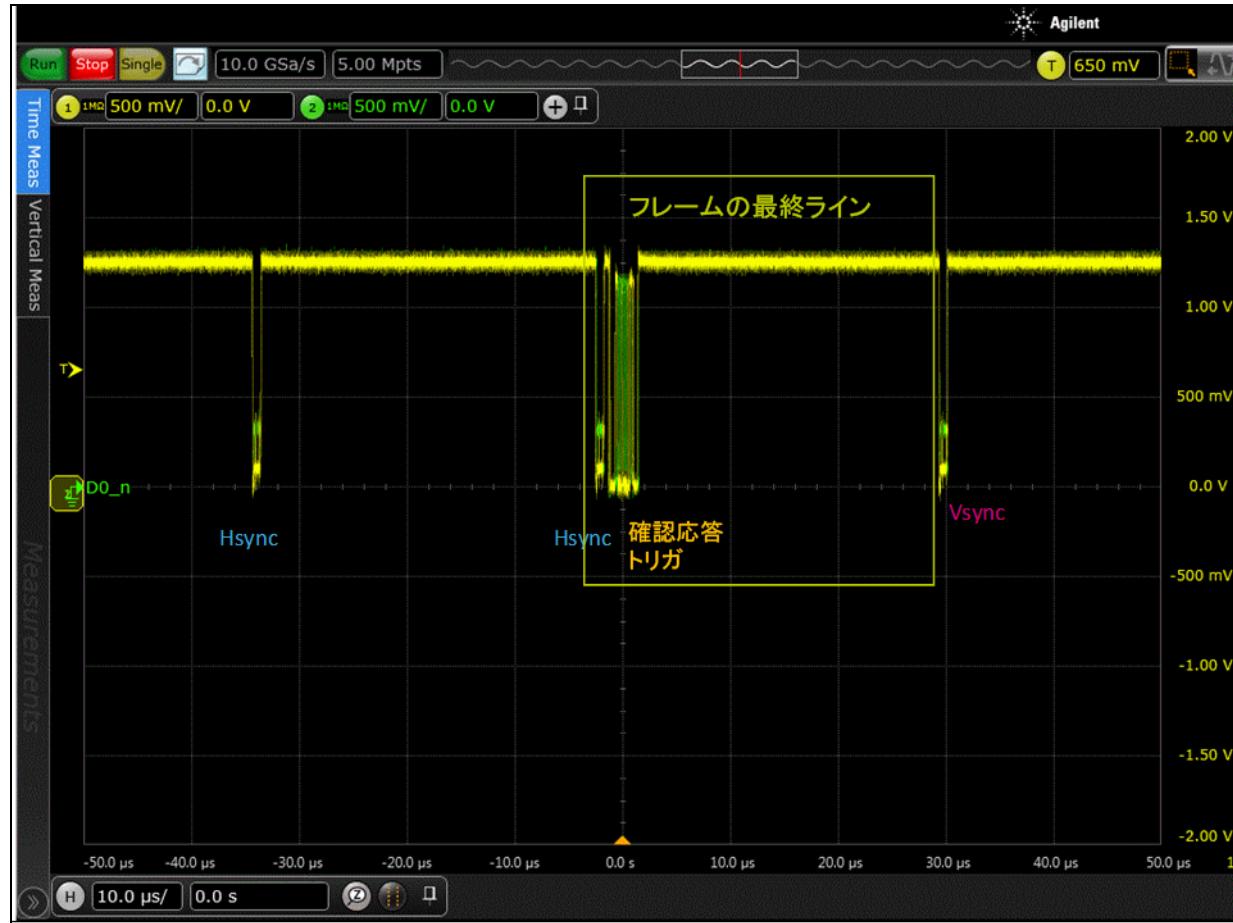

図 73 に、2回の BTA のある set\_tear\_scanline コマンドの拡大図を示します。

図 73. 2回の BTA のある set\_tear\_scanline DCS コマンド

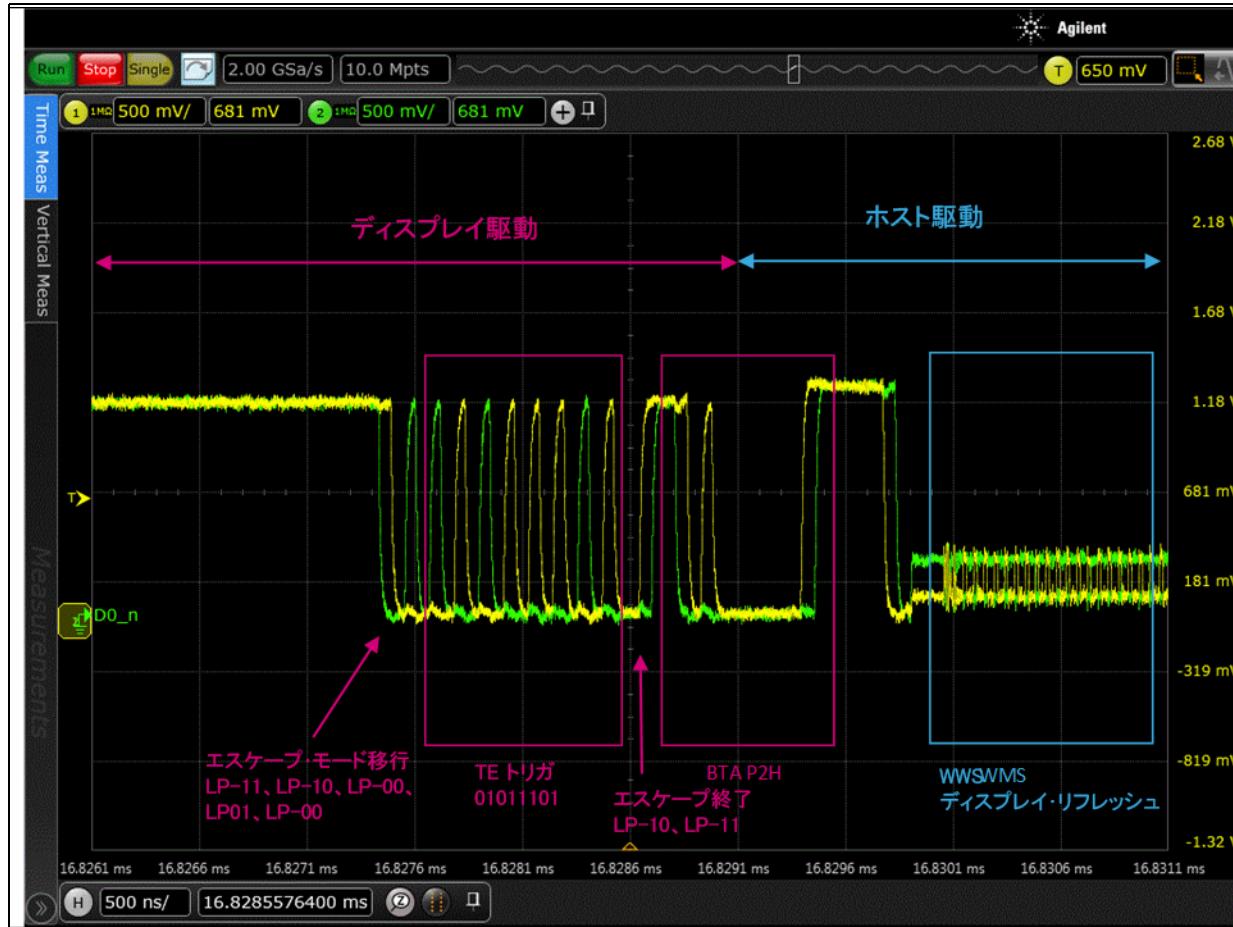

ディスプレイが指定したスキャンラインに達すると、BTA 手順でティアリング効果を送信して、DSI ホストにバスの制御を戻します。

# 参考資料

AN4860

DSI ホストの説明

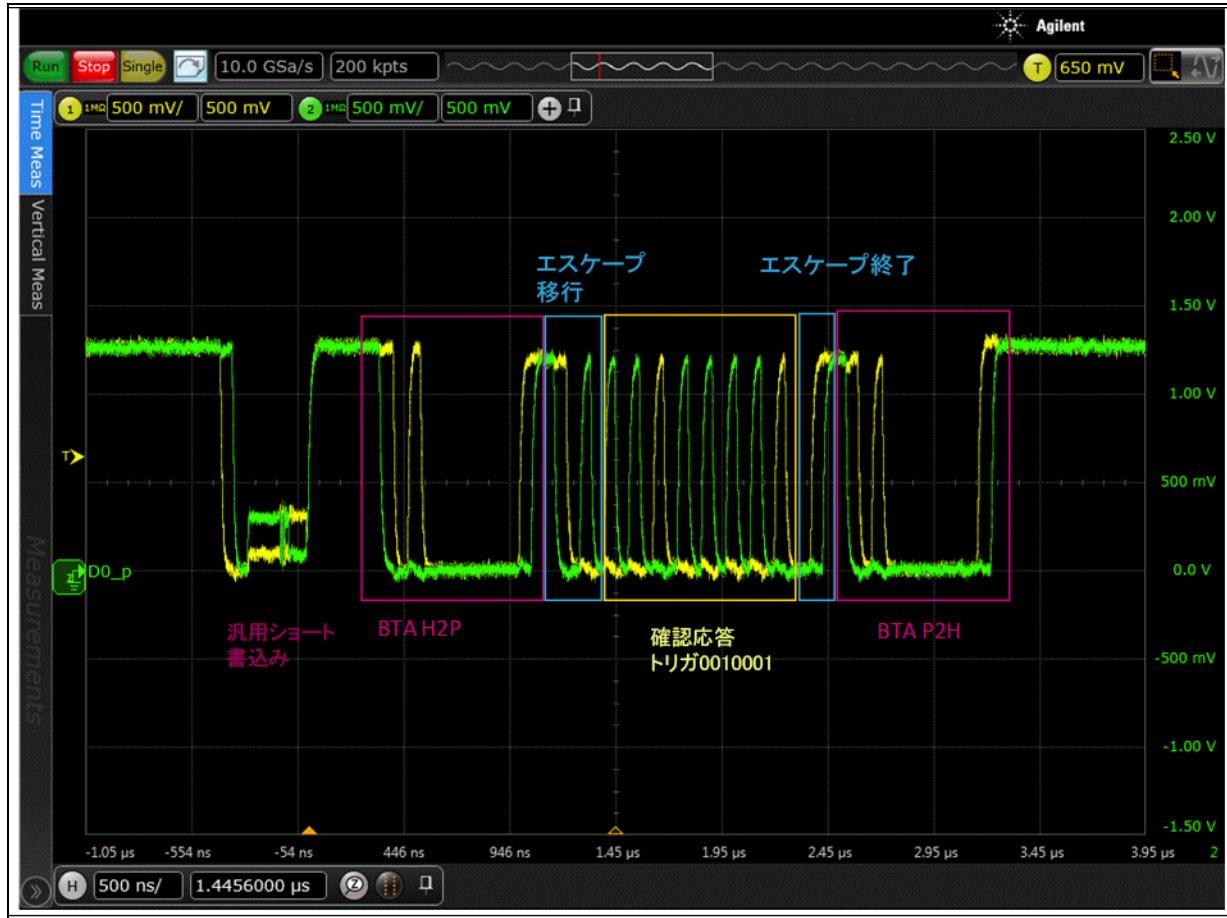

図 74 に、ティアリング効果トリガ・メッセージの拡大図を示します。

その後、DSI ホストは WMS/WMC の DCS コマンドでディスプレイのリフレッシュ動作を開始できます。

図 74. ディスプレイからのティアリング効果トリガ

## ピン経由のティアリング効果

ティアリング効果がピン経由で実行される場合、DSI ホストは `set_tear_on` または `set_tear_scanline` の DCS コマンドを送信します。その後、プログラムされたスキャンラインに達すると、ディスプレイは専用ピンをトグルして、DSI ホストをトリガします。

`set_tear_on` または `set_tear_scanline` の DCS コマンドは1回だけ送信でき、ディスプレイが継続的な同期信号を生成します。

追加ピンが必要な場合でも、このメカニズムによって DSI ホストとディスプレイのリンクでの複数回のやり取りを避けることができます。

ピンのトグル時に割込みを発生させてグラフィカル RAM のリフレッシュを開始できます。

その後、DSI ホストは WMS/WMC の DCS コマンドを送信してリフレッシュ動作を開始します。

リフレッシュは、TE 割込みの検出時に自動的に実行するか、ソフトウェアで有効にできます。

# 参考資料

## DSI ホストの説明

AN4860

図 75 に、GPIO での TE レポートを示します。ディスプレイ・モジュールがプログラムされたスキヤンラインに達すると、TE ピンでパルスを生成します。

図 76 に、GPIO 経由のティアリング効果の拡大図を示します。

図 75. ピン経由の TE

図 76. ピン経由のティアリング効果の拡大図

### 4.2.3 APB コマンド・モード

APB コマンド・モードは、DSI ホストの APB レジスタ・インターフェースを介したコマンド送信に使用されます。

起動時のディスプレイ設定やアプリケーション実行時のメンテナンス操作のために、汎用コマンドや DCS コマンドを送信できます。

一部のディスプレイは起動時に低消費電力通信のみを受け入れるため、すべてのコマンドはハイスピードまたは低消費電力モードで送信できます。

また、ビデオ・ストリーミング中にもコマンドを送信できます。DSI ホスト・スケジューラは、プログラムされたタイミングに応じて、ビデオ送信中にコマンドを挿入できる十分な時間があるかどうかを自動的に評価します。

すべてのコマンドはソフトウェアによって完全にプログラム可能になっており、DSI ホストですべての標準的な DCS コマンドとディスプレイ依存のカスタム・コマンドをサポートします。

#### APB コマンド・モードを使用する場合

APB コマンド・モードは、主にディスプレイの初期化フェーズとディスプレイのメンテナンス操作に使用されます。このモードは、ビデオ・モードやアダプティッド・コマンド・モードと同時に動作します。

### 4.3 動作モードの選択

ビデオ・モードかアダプティッド・コマンド・モードかの選択は、ソリューションのアーキテクチャとコストに大きく影響します。

マイクロコントローラの観点からすると、コストを最適化するソリューションではアダプティッド・コマンド・モードのほうが適しています。

ビデオ・モードはディスプレイ側にグラフィカル RAM を必要としないため、このソリューションはコスト最適化のためにグラフィカル RAM を使用しない大型ディスプレイに適用されます。マイクロコントローラ 側の帯域幅やメモリ使用量に関する制約は、現在の LTDC ベースのソリューションのものと同様のままです。ほとんどの場合、外部 RAM がフレームバッファのダブル・バッファリングに必要になります。

アダプティッド・コマンド・モードは、グラフィカル RAM を持つディスプレイが必要になります。このディスプレイはややコストが高くなる場合がありますが、480 x 480未満のほとんどの小型ディスプレイにグラフィカル RAM が組み込まれています。結果として、小型ディスプレイでのアダプティッド・コマンド・モードでは、フレームバッファが内部マイクロコントローラ RAM に格納できるため、外部 RAM を必要としません。これにより、マイクロコントローラでの帯域幅問題が減り、また外部RAM が不要になるため、全体のBOMコストの削減とソリューション統合が可能になります。

### 4.4 DSI 割込み

DSI ホストには、すべての通信のタイミングとイベントを監視する数多くの割込みがあります。すべての割込みソースの詳細な説明については、関連する STM32 リファレンス・マニュアルを参照してください。

割込みは、DSI ラッパー・ホストまたは DSI ホストで生成できます。すべての割込みは、割込みコントローラへの1つの割込みラインに統合されます。

プロトコル関連の割込みに加えて、DSI ホストは次のものを管理する割込みも備えています。

- レギュレータ・イベント

- PLL イベント

- ティアリング効果イベント（コマンド・モードのみ）

- リフレッシュ終了イベント（コマンド・モードのみ）

## 4.5 低消費電力モード

DSI ホストは、RUN モードおよび SLEEP モードでアクティブです。DSI ホストの割込みによって、デバイスは SLEEP モードから復帰します。

STOP モードでは、DSI ホストは停止し、レジスタの内容は保持されます。STANDBY モードでは、DSI ホストはパワーダウンされ、レジスタの内容は後で再初期化されます。

[表 9](#) で DSI ホストの低消費電力モードについて説明します。

表 9. DSI ホストの低消費電力モード

| モード     | 説明                                              |

|---------|-------------------------------------------------|

| RUN     | アクティブです。                                        |

| SLEEP   | アクティブです。ペリフェラルの割込みによって、デバイスは SLEEP モードから復帰します。  |

| STOP    | 停止。ペリフェラル・レジスタの内容は保持されます。                       |

| STANDBY | パワーダウンします。ペリフェラルは、STANDBY モード終了後に再初期化する必要があります。 |