# USB Type-C® protection and filtering

#### Introduction

The USB interface has been present on the market for nearly two decades and thanks to that, nowadays it is quite obvious for everybody to connect electronic devices in this manner. However, the presence of different types of connectors: type A, type B, mini USB, micro USB etc., makes difficult and complicated the choice of the right one. For this reason USB Type-C®, a unique connector to drive power and data up to 5, 10 or 20 Gbps, is now available.

Because for its own nature a connector is a link to the outside world, it may be exposed to a lot of disturbances, which can ruin the transceivers. Moreover, the high-speed links radiate therefore an efficient filter has to be used to solve antenna desense. STMicroelectronics has developed some specific protection devices and common mode filters with optimized performance and layout

This application note proposes different solutions in order to simplify the designer's work and explain their benefits. Further information about protection and filtering devices for USB Type-C are available on www.st.com/protection-typec.

# 1 USB Type-C

#### 1.1 Overview

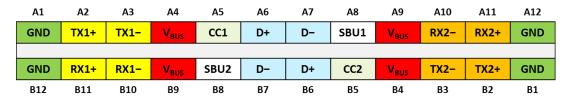

This connector includes three groups of differential lanes that drive standards such as: USB 3.2, USB4, DisplayPort, ThunderBolt $^{TM}$ , PCI express etc., and two control lines (configuration channel and sideband use). Furthermore, it embeds a power line,  $V_{BUS}$ , which drives high current for charging and supply (see Figure 1).

Figure 1. USB Type-C links

This connector is highly integrated and compact. It is particularly suitable for small applications such as: tablet PC, laptops, phablets, and even smartphones. A typical view of the USB Type-C is shown in the Figure 2.

Figure 2. USB Type-C typical view

The Figure 3 describes the different pins of the receptacle connector.

AN4871 - Rev 3 page 2/32

Figure 3. Receptacle interface pinout (front view)

The Table 1 describes the function of each pin:

Table 1. Definition of the pin functions

| Pin#                 | Pin name                   | Function                                                                                                                                      |

|----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| A1 / A12<br>B1 / B12 | GND                        | Ground return                                                                                                                                 |

| A4 / A9<br>B4 / B9   | VBUS                       | Bus power supply                                                                                                                              |

| A2 / A3<br>B11 / B10 | TX1+ / TX1-<br>RX1+ / RX1- | Positive and negative of the first SuperSpeed $T_X$ differential pair Positive and negative of the first SuperSpeed $R_X$ differential pair   |

| B2 / B3<br>A11 / A10 | TX2+ / TX2-<br>RX2+ / RX2- | Positive and negative of the second SuperSpeed $T_X$ differential pair Positive and negative of the second SuperSpeed $R_X$ differential pair |

| A6 / B6<br>A7 / B7   | D+ / D-                    | Positive half of the USB 2.0 differential pair (position 1 and 2)  Negative half of the USB 2.0 differential pair (position 1 and 2)          |

| A5 / B5              | CC1 / CC2                  | Used to detect connections and configure the interface  One CC pin repurposed as V <sub>CONN</sub> for powering electronics                   |

| A8 / B8              | SBU1 / SBU2                | Sideband use: Audio adapter accessory configuration Additional function to be defined                                                         |

Furthermore, type-C is compliant with USB Power Delivery that allows a maximum current up to 5 A and a maximum voltage up to 20 V, for standard power range (SPR).

AN4871 - Rev 3 page 3/32

#### 1.2 Power supply

#### 1.2.1 Power supply options

USB standard defines V<sub>BUS</sub> as the path to deliver power between a host and a device or between a charger and a host/device.

The Table 2 summarizes the available power options.

Table 2. Power supply options

| Mode of operation              | Nominal voltage                  | Maximum current        | Notes                                          |

|--------------------------------|----------------------------------|------------------------|------------------------------------------------|

| USB 2.0                        | 5 V                              | 500 mA                 | Default current, based on definitions in the   |

| USB 3.1                        | 5 V                              | 900 mA                 | base specifications                            |

| USB BC 1.2                     | 5 V                              | Up to 1.5 A            | Legacy charging                                |

| USB Type-C current<br>at 1.5 A | 5 V                              | 1.5 A                  | Supports higher power devices                  |

| USB Type-C current at 3.0 A    | 5 V                              | 3 A                    | Supports higher power devices                  |

| USB PD                         | Configurable up to 20 V, for SPR | Configurable up to 5 A | Directional control and power level management |

USB 2.0 and USB 3.2 are the only ones with a default level of 5 V nominal voltage and current up to 900 mA. Legacy charging increases maximum current to 1.5 A.

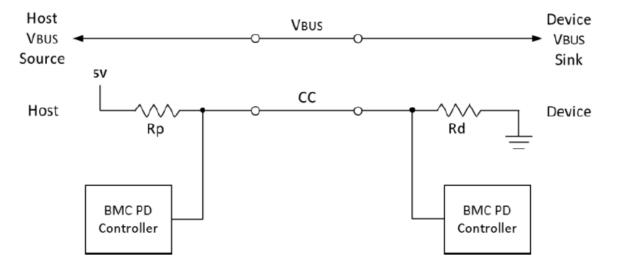

Configuration channels (CC1 and C2) detect the cable position on the connector. Pull up resistor on the provider gives some information on current capability (22 k $\Omega$  +/- 5% for 1.5 A and 10 k $\Omega$  +/- 5% for three A on the host associated with 5.1 k $\Omega$  +/- 10% pull-down resistor on the device).

#### 1.2.2 USB Power Delivery

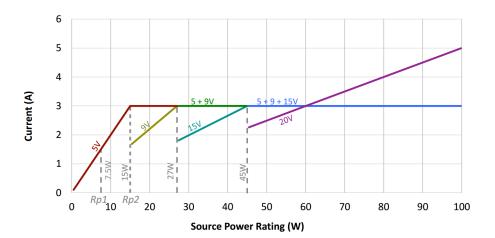

The USB Power Delivery (USB PD) communication over CC is used for the advanced power delivery negotiation with current up to 5 A and voltage up to 20 V, for SPR. 300 kbit/s BMC (biphase mark code) controller negotiates power profile and directivity.

USB PD rules are fixed by USB Power Delivery revision 3, where voltages and currents for each power are defined.

SPR normative voltages are as follows:

- 5 V to reach 15 W maximum

- 9 V to reach 27 W maximum

- 15 V to reach 45 W maximum

- 20 V to reach 100 W maximum but 5 A cable is required for power higher than 60 W

The Figure 4 illustrates the maximum current and power rails that the USB PD source can deliver.

AN4871 - Rev 3 page 4/32

Figure 4. Source power rule outline for SPR

The maximum power is 100 W. These power rules respect the safety requirements imposed by the IEC/UL 60950 regulation.

The Figure 5 shows the USB PD over CC pins on the host, the device configuration with pull-up (Rp) and pull-down (Rd) resistors.

Figure 5. USB PD over CC pins

The receptacle is specified up to 5 A current but Type-C cables are rated for 3 A. So, for current higher than 3 A, the electronic marking of the cable is mandatory.

AN4871 - Rev 3 page 5/32

## 1.3 Differential lines

The USB type receptacle delivers six differential pairs dedicated to high-speed signals:

- 2 differential pairs drive USB 2.0 high-speed signal, up to 480 Mbps

- 4 differential pairs dedicated to super speed signal, drive USB 3.2 Gen 2 signal up to 10 Gbps, or USB4 up to 20 Gbps

All hosts and devices with USB Type-C receptacle show the USB interface. According to the USB Type-C standard, alternate modes are allowed only when host and device are directly connected, while they are not allowed when the connection is through the USB hub.

#### 1.3.1 USB interface

#### 1.3.1.1 USB 2.0 interface

The USB Type-C connector exhibits four pins A6, A7, B6, and B7 dedicated to USB 2.0. On the USB Type-C plug connector, B6(D+) and B7(D-) should not be present. The plug orientation determines which differential pair A6/A7 or B6/B7 is used on the receptacle side.

Dp1 (A6) and Dp2 (B6) pins may be shorted together on the PCB as close as possible to the receptacle to minimize the stub length, with trace length shorter than 3.5 mm as specified in the standard. Dn1 (A7) and Dn2 (B7) may be also shorted together.

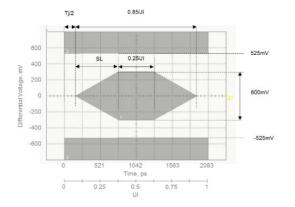

The signal on Dp/Dn data lines fulfills USB 2.0 electrical requirements, in particular the eye diagram pattern (see the Figure 6) measured on the connector output of the device under test.

Figure 6. USB 2.0 high-speed 480 Mbps eye diagram mask (template 1)

| Signal Characteristics | Minimal | Nominal | Maximum | Units |

|------------------------|---------|---------|---------|-------|

| Eye Height             | 600     |         | 1050    | mV    |

| Eye width              | 0.850   |         |         | UI    |

| Tj                     |         |         | 0.150   | UI    |

| SL                     |         | 0.300   |         | UI    |

#### 1.3.1.2 USB 3 interface

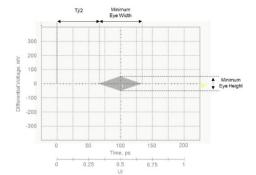

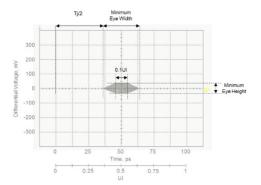

SuperSpeed data lanes fulfill USB 3.2 electrical requirements. USB 3.2 standard defines the eye pattern mask for USB Gen 1, that is, 5 Gbps data rate (see the Figure 7) and that for USB Gen 2, that is, 10 Gbps data rate (Figure 8). The eye pattern is measured at the end of a reference cable and after an equalizer.

Figure 7. USB 3.1 Gen 1, 5 Gbps eye diagram mask

| Signal Characteristics | Minimal | Nominal | Maximum | Units |

|------------------------|---------|---------|---------|-------|

| Eye Height             | 100     |         | 1200    | mV    |

| Dj                     |         |         | 0.43    | UI    |

| Rj                     |         |         | 0.23    | UI    |

| Tj                     |         |         | 0.66    | UI    |

AN4871 - Rev 3 page 6/32

Figure 8. USB 3.2 Gen 2, 10 Gbps eye diagram mask

| Signal Characteristics | Minimal | Nominal | Maximum | Units |

|------------------------|---------|---------|---------|-------|

| Eye Height             | 70      |         | 1200    | mV    |

| Dj                     |         |         | 0.530   | UI    |

| Rj                     |         |         | 0.184   | UI    |

| Tj                     |         |         | 0.714   | UI    |

During standard mode, only one Tx differential pair and one Rx differential pair is used. In alternate mode, all Tx and Rx differential pairs can be used simultaneously.

#### 1.3.2 Alternate mode

The alternate mode allows the non-USB signal to be transmitted through USB Type-C cable and connectors. In this configuration, all high-speed lanes can be used.

The alternate mode is configured through the configuration channel (contact CC1 and CC2).

AN4871 - Rev 3 page 7/32

## 2 Constraints to be faced

Due to the fast transition times of high-speed links, the risk of EMI is real and can cause some issues in mobile applications such as antenna desense. In this case, the use of common mode filters on the data lines is recommended.

Since  $V_{BUS}$  connection and command lines are directly exposed to external stresses, they also need protections and filters, which have to be chosen by taking into account different constraints:

- **Data rates and voltage levels:** they give the minimum differential bandwidths, which have to comply with the eye diagram templates specified by the different standards.

- **Rejection:** the common mode rejection has to be better than -20 dB in the frequency range where the device can get some issues (from 700 MHz up to 2.7 GHz in mobile applications, 2.4 GHz / 5 GHz for WiFi).

- Protection: the clamping voltage levels must secure the transceivers and enable the application to withstand standard such as IEC61000-4-2 up to level 4 and sometimes IEC61000-4-5 on the V<sub>BUS</sub>.

AN4871 - Rev 3 page 8/32

## 3 Power supply protection

V<sub>BUS</sub> line can be used to charge mobile devices or share power with other devices/hosts.

European standard EN 55024 (information technology equipment - immunity characteristics - limits and methods of measurement) requires the following ESD discharge robustness: IEC 61000-4-2 4 kV contact and 8 kV air, criteria B (temporary perturbation and self-recovery).

EOS (electrical overstress) can appear due to unstable power supply. As consequence, TVS protection devices with high surge current capability are expected.

Protection voltage must be in accordance with maximal  $V_{BUS}$  voltage, and protection capacitance is not limited due to DC voltage.

The ESDA7P60-1U1M is a product dedicated to protect systems with V<sub>BUS</sub> maximum voltage equal to 5 V.

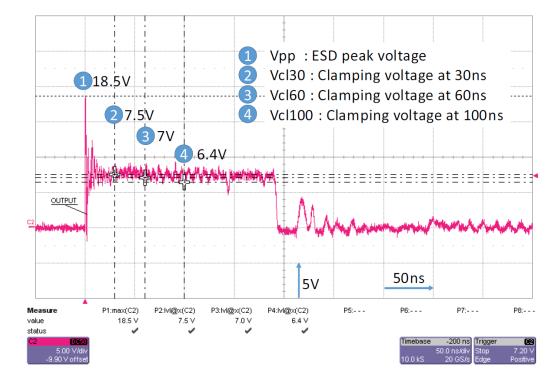

The Figure 9 presents the ESDA7P60-1U1M response towards the 8 kV ESD discharge.

Figure 9. IEC 61000-4-2 +8 kV contact response of ESDA7P60-1U1M

This protection presents a very low ESD peak voltage (18.5 V) and 30 ns clamping voltage (7.5 V) very close to the maximal working voltage (5.5 V) when 8 kV ESD is applied. Both results show a very good quality protection,  $5 \text{ V} \text{ V}_{\text{BUS}}$ .

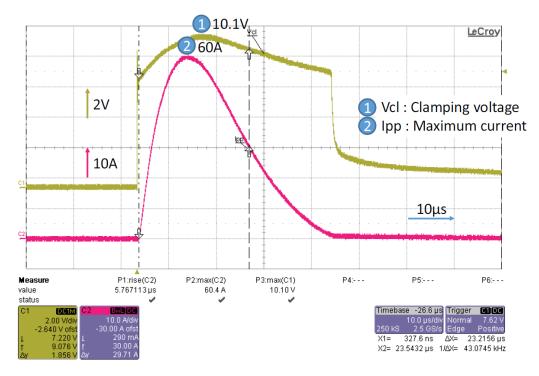

The Figure 10 presents the response of the ESDA7P60-1U1M towards a 60 A 8/20 µs surge and the resulting clamping voltage. It illustrates the current capability (60 A peak pulse current for this product) and associated low clamping voltage (10.1 V at maximum current). The resulting peak pulse power is 600 W. This parameter sometimes used to rank TVS is not the key. Indeed, the current must be as high as possible (protection robustness) and the clamping voltage must be as low as possible (protection quality).

AN4871 - Rev 3 page 9/32

Figure 10. IEC61000-4-5 with 60 A 8/20 µs max. current response of ESDA7P60-1U1M

According to voltages the following TVS can be used:

- For Vbus = 5V, ESDA7P60-1U1M, ESDA7P120-1U1M

- For Vbus = 9V, ESDA13P70-1U1M

- For Vbus = 15V, ESDA17P50-1U1M, ESDA17P100-1U2M

- For Vbus = 20V, ESDA25P35-1U1M, ESDA24P140-1U3M

Others solutions, with OVP and OCP on Vbus, are presented on the Section 5 Type-C Vbus and CC protections solutions for STM32.

AN4871 - Rev 3 page 10/32

# 4 Configuration line protection

Configuration channel lines are not only used to establish and manage DFP-to-UFP connection but also to transmit USB PD communication using BMC coding. Protection constraints are the following:

- Maximal voltage is 5.5 V when V<sub>CONN</sub> is used and no negative signal

- Protection capacitance and receiver capacitance must be between 200 pF and 600 pF

These lines require classical unidirectional ESD protections with low constraints on capacitance and no special feature on peak pulse current.

Solutions to protect CC against the short to Vbus are presented on the Section 5.

AN4871 - Rev 3 page 11/32

## Type-C Vbus and CC protections solutions for STM32

STM32 has a unique built-in USB Type-C and PD controller (UCPD) that controls the CC lines (configuration and communications channels) of the USB Type-C connector, which are used during the attachment with a USB Type-C device and carry the USB Power Delivery protocol messages.

This STM32 peripheral (UCPD) and its associated PD middleware stack allows CC lines to implement USB Type-C connection for sink, source, or dual role without the use of an external PD controller.

The companion Type-C Port Protection (TCPP series) protects against EMI aggressions on Vbus and CC lines and complies with USB Type-C and USB PD standards. This high-voltage device integrates a gate driver to drive the load switch of the power path.

- TCPP01-M12 is optimized for Sink USB PD SPR applications (device mode)

- TCPP02-M18 is for source USB PD SPR applications (host mode)

- TCPP03-M20 for dual role Power USB PD SPR applications (dual role data mode).

TCPP01-M12 and TCPP02-M18 can also be used for 5V only legacy applications associated with any STM32.

TCPP's features can be split according to protected lines. Protections and high voltage elements offer an effective integration to optimize BOM when a STM32 is used.

Features of TCPPs are summarized:

Table 3. Features of TCPPs

|               |                              | Sink       | Source     | Dual role power |

|---------------|------------------------------|------------|------------|-----------------|

|               |                              | TCPP01-M12 | TCPP02-M18 | TCPP03-M20      |

|               |                              | QFN-12L    | QFN-18L    | QFN-20L         |

|               | ESD +8kV, OVP                | x          | x          | x               |

| CC            | Dead batteries               | x          |            | Х               |

|               | Vconn switch, OCP, discharge |            | x          | x               |

|               | Gate driver                  | Sink       | Source     | Sink / source   |

|               | OVP                          | x          |            | Х               |

| VBUS          | OCP                          |            | x          | Bidirectional   |

|               | High side current sense      |            | x          | Х               |

|               | Discharge                    |            | x          | x               |

| Communication | Flag                         | x          | x          | х               |

| Communication | I2C                          |            | x          | Х               |

Note:

- All TCPPs embed over temperature protection (OTP).

- ESD: IEC 61000-4-2

- OVP: Over voltage protection

- OCP: Over current protection

AN4871 - Rev 3 page 12/32

## 6 Differential line ESD protection

The ESD protection device must be carefully chosen in order not to compromise the signal transmission. In particular, the frequency bandwidth of the protection device defined by its cutoff frequency must be quite high in comparison to the signal bandwidth.

#### 6.1 Signal bandwidth

The signal bandwidth of an aperiodic trapezoidal signal depends on minimum value of signal rise or fall time as shown by the equation below:

$$BW = \frac{0.35}{t_T(10\% - 90\%)}\tag{1}$$

or

$$BW = \frac{0.22}{t_r(20\% - 80\%)} \tag{2}$$

To minimize the impact of the ESD protection on the transmitted signal, the frequency bandwidth of the ESD protection must be higher than the signal bandwidth.

#### 6.2 Impact of ESD protection device on transmitted signal rise time

The intrinsic capacitance of ESD protection device influences the signal rise time and the TDR response. The equation below gives the signal rise time on the output of the ESD protection assuming an input square signal.

$$t_{r ESD} = 0.35*Z_0*\pi*C_{ESD}$$

(3)

Considering ESD protection as a low pass filter instead of a parallel capacitor, ESD protection rise time can be evaluated function of the filter cut-off frequency  $f_{ESD}$  -3 dB, as shown in the following equation:

$$t_{r\_ESD} = \frac{0.35}{f_{ESD\_} - 3dB} \tag{4}$$

The following equation gives the system rise time with ESD protection:

$$t_{r\_system} = \sqrt{t_{r\_signal}^2 + t_{r\_ESD}^2}$$

(5)

Assuming an impact of ESD protection on rise time lower than 10% of initial rise time, the intrinsic capacitance maximum value for the rise time frequency is given by the equation below:

$$C_{ESD\_max} = \frac{\sqrt{0.21} \ t_{r\_signal}}{Z_0 * 0.35 * \pi} \tag{6}$$

The minimum cut-off frequency of the protection device is given as follows:

$$f_{-3dB\_ESD\_min} = \frac{0.35}{\sqrt{0.21} \ t_{r\_signal}} \tag{7}$$

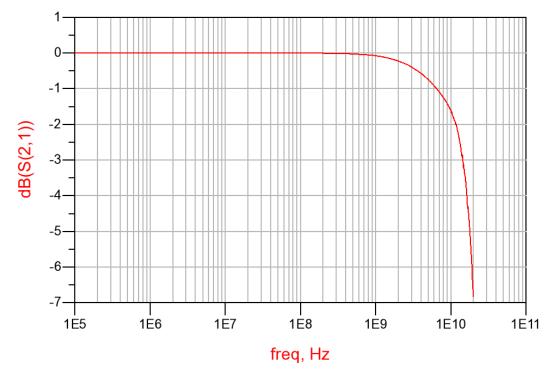

An example of attenuation curve measurement performed on the HSP051-4M10 is presented in the following figure. The cut-off frequency is measured at 14.5 GHz.

AN4871 - Rev 3 page 13/32

Figure 11. Attenuation measurement results on HSP051-4M10

## 6.3 Eye diagrams

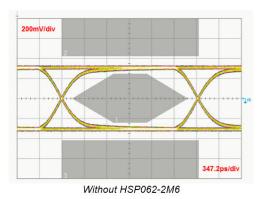

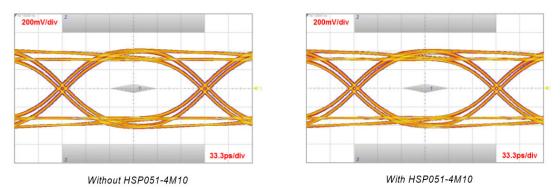

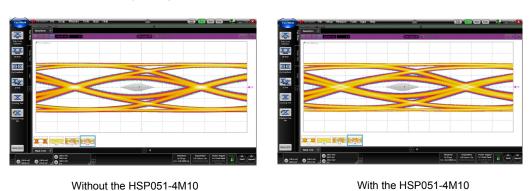

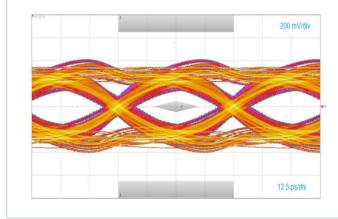

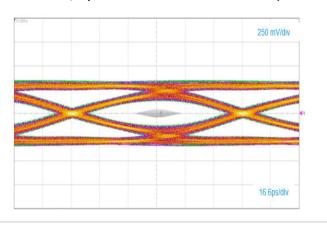

The impact of the protection device on the transmitted signal is illustrated by the eye diagram measurements during compliance certification. Examples of eye diagram measurements performed with and without ESD protection devices are presented in the figure below with a data rate of 480 Mbps, USB 2.0 template 1 eye mask, in Figure 13. USB 3.2 Gen 1 eye diagram example without and with HSP051-4M10, after reference cable and equalizer with a data rate of 5 Gbps and Figure 14. USB 3.2 Gen 2 eye diagram example for HSP051-4M10, after reference cable and equalizer with a data rate of 10 Gbps, USB 3.2 eye masks.

Figure 12. Eye diagram measurements without and with the HSP062-2M6 for 480 Mbps data rate, USB 2.0 template 1 mask

200mV/div 2 347.2ps/div With HSP062-2M6

AN4871 - Rev 3 page 14/32

Figure 13. USB 3.2 Gen 1 eye diagram example without and with HSP051-4M10, after reference cable and equalizer

Figure 14. USB 3.2 Gen 2 eye diagram example for HSP051-4M10, after reference cable and equalizer

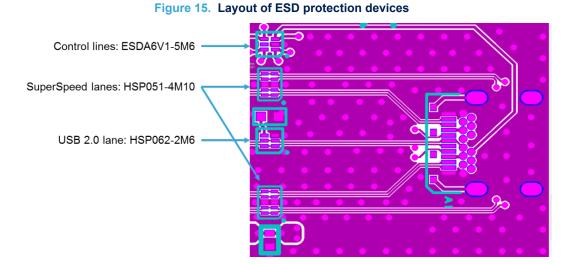

ESD protection devices are usually placed close to the connector. An example of layout is given in the following figure.

AN4871 - Rev 3 page 15/32

## Antenna desense and noise rejection: common mode filters

### 7.1 Choosing the right bandwidth

As explained above, the maximum value of the data rate used defines the bandwidth of the common mode filter. To be sure that CMF is compliant with the standard, each datasheet includes an eye diagram in various standard configurations. Figure below shows an example of the Figure 16 and the Figure 17 test conditions. It fulfills the templates and in that manner, the choice of the suitable device is easier.

Figure 16. USB4 20.0 Gbps eye diagram with ECMFx-40A100Nx (with Preset 0, reference cable 0.8 m,equalizer with ADC = 0dB and DFE)

Figure 17. USB3.2 Gen 2 10.0 Gbps eye diagram with ECMFx-40A100Nx (with type C connector, reference cable, equalizer with ADC = 5 dB and DFE)

### 7.2 Common mode rejection

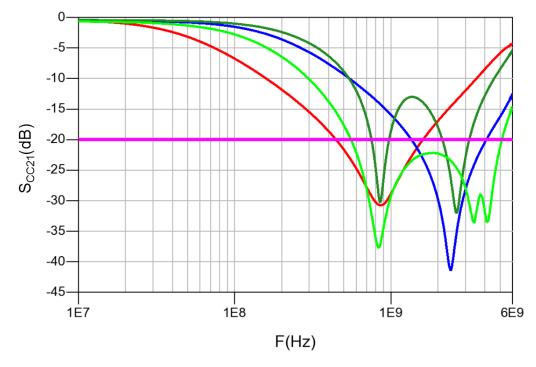

For each lane of the high-speed links, a common mode filter dedicated to the range of frequency, which can cause some issues to the application, exists. The following figure presents various  $S_{CC21}$  common mode rejections.

AN4871 - Rev 3 page 16/32

Figure 18. Typical STMicroelectronics ECMF/CMF common mode rejection (in red, the market reference)

The purple line represents the optimized common mode rejection, generally set to -20 dB. For example, if the sensitivity in LTE Rx Band-5 of the application decreases, due to a lot of noises generated by digital traffic, CMF with the light green  $S_{CC21}$  characteristic must be chosen. It assumes a deep rejection in this frequency range, better than -30 dB. If the application encounters issues in Wi-Fi 2.4 GHz reception, CMF with blue characteristic is recommended. Its  $S_{CC21}$  characteristic is better than -35 dB at this frequency.

### 7.3 The PCB layout

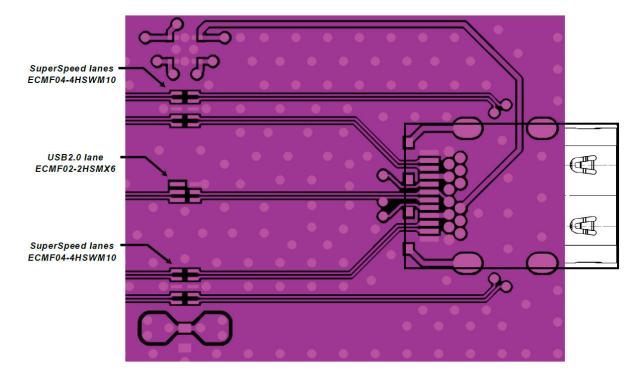

Filters are user-friendly and ensure a simple layout around the Type-C connector. This helps to keep the differential impedance of the lane to  $100~\Omega$  or  $90~\Omega$ .

The figure below presents a typical layout around a USB Type-C connector.

AN4871 - Rev 3 page 17/32

Figure 19. Layout example with three ECMF filters on the high-speed lanes

### 7.4 Benefits of the common mode filters

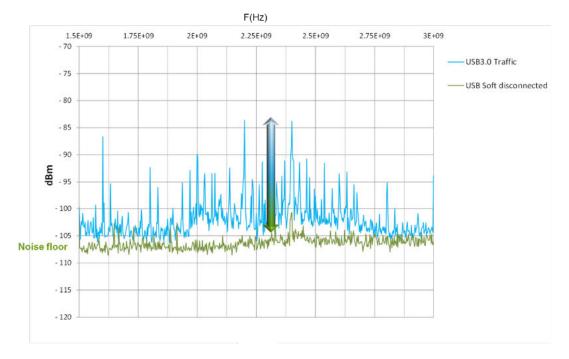

The figure below shows the noise radiated by a USB 3.2 Gen 1 cable, measured between 1.5 GHz and 3 GHz. It is possible to see that high level spikes can appear with a difference up to 20 dB respect to the noise floor. These spikes are in the same frequency range as Bluetooth or Wi-Fi, and antenna desense occurs, causing disruptions on the signal reception.

Figure 20. Noise measured on a USB 3.2 Gen 1 link

AN4871 - Rev 3 page 18/32

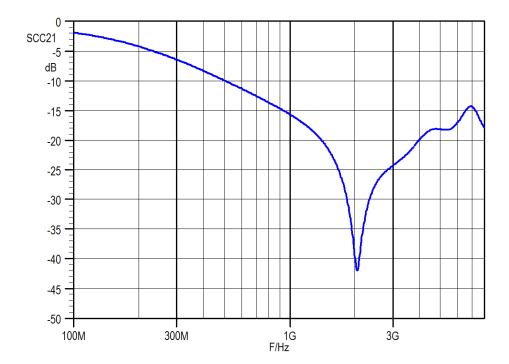

This kind of noise can be filtered by common mode filters. In this example, the ECMF04-4HSWM10 filter (from STMicroelectronics's ECMF series) has been placed on each side of the link with common mode rejection centered on 2 GHz. The figure below shows its typical rejection  $S_{CC21}$ , better than 25 dB between 1.8 GHz up to 2.9 GHz.

Figure 21. Typical common mode rejection of the ECMF04-4HSWM10 dedicated to 2.4 GHz application

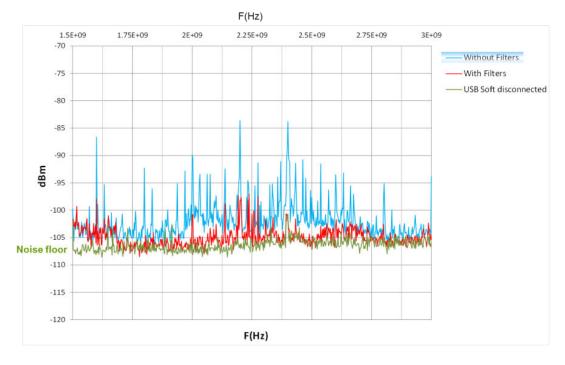

Next figure shows the attenuation on the common mode noise thanks to the ECMF.

The average gain is around -25dB. However, the result on a standard application is not known yet.

AN4871 - Rev 3 page 19/32

Figure 22. In red, the noise level after ECMF insertion on the USB 3.1 Gen 1 link

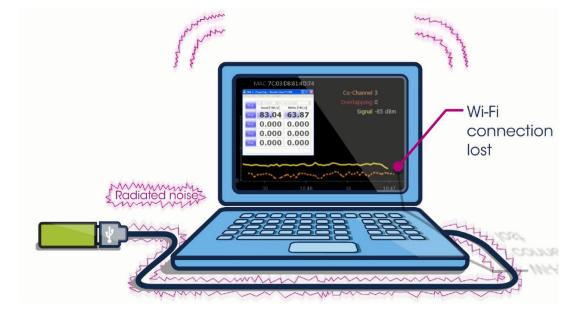

Below a trial on the Wi-Fi gateway. On a PC connected to the internet, a USB 3.2 Gen 1 external device is plugged. When the USB 3.1 Gen 1 communication is established, the low power Wi-Fi connection evaluated by the received signal strength indication (RSSI) is lost (figure below). The radiated noise, generated by the digital link, influences the transmission.

Figure 23. RSSI Wi-Fi behavior with USB 3.2 Gen 1 traffic ("InSSIDer" window)

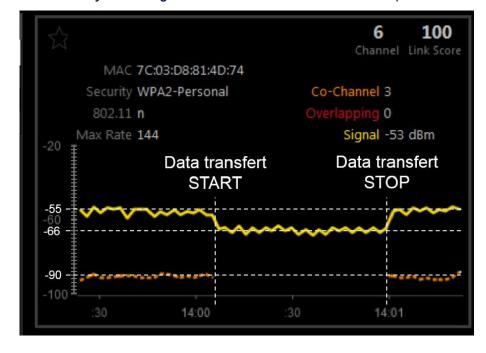

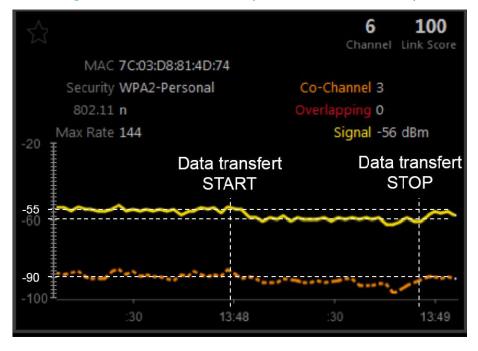

Next figure shows more in detail the noise influence on Wi-Fi transmission. When the USB 3.2 Gen 1 traffic starts, the RSSI level (yellow curve) decreases by 11 dB, and during this time the low level Wi-Fi is lost (orange curve).

AN4871 - Rev 3 page 20/32

Figure 24. Sensitivity lost during USB 3.2 traffic on a Wi-Fi transmission ("inSSIDer" window)

Thanks to the insertion of the ECMF02-2HSMX6 (in this case) on the link, the Wi-Fi connection is safe (figure below).

Figure 25. Safe Wi-Fi connection

After CMF insertion, during the USB 3.2 Gen 1 data transfer, the high level Wi-Fi communication is just slightly affected and the low level communication is maintained (figure below).

AN4871 - Rev 3 page 21/32

Figure 26. Safe Wi-Fi connection (USB 3.2 Gen 1 data transfer)

Moreover, the ECMF family integrates ESD protection. Therefore, it is not necessary to add TVS to the data lines to ensure efficient protection and it saves room on the PCB.

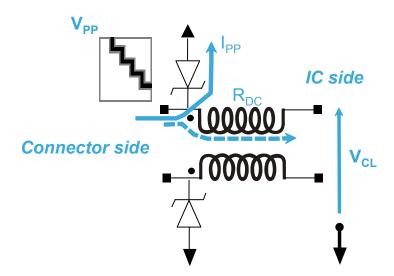

Another benefit of this family is to limit the current through the transceiver to protect, thanks to the internal resistance  $R_{DC}$  of the common mode filter (figure below).

Figure 27. Resistance  $R_{DC}$  of the common mode filter

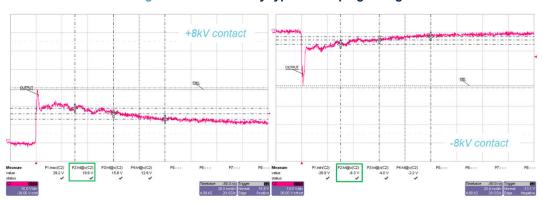

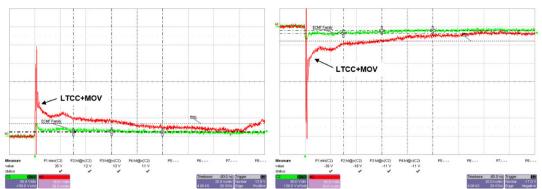

Next figure shows a typical clamping voltage that can be obtained by ECMF during the IEC61000-4-2 surge at  $\pm$  8 kV contact. 30 nanoseconds after the surge, the voltage level is less than 19 V during positive surge and 6.5 V during negative surge.

AN4871 - Rev 3 page 22/32

Figure 28. ECMF family typical clamping voltage

These results are much better than the MOV protection embedded in some LTCC common mode filters. The following figure presents the comparison between the two devices. The green curve is the ECMF clamping characteristic.

AN4871 - Rev 3 page 23/32

# 8 Available solutions for testing

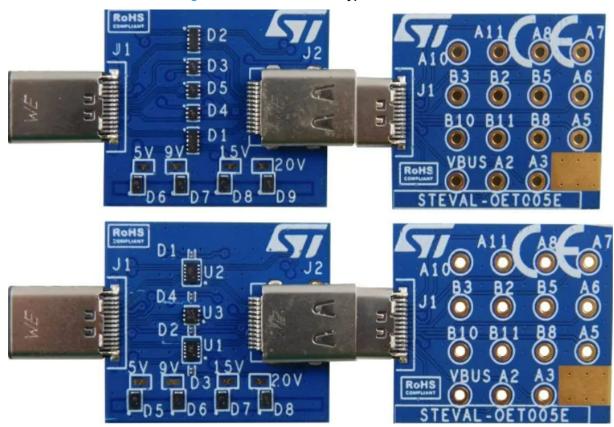

In order to easily verify the functionality of our devices, several evaluation boards are available with many configurations.

## 8.1 Protection and filtering evaluation boards

Protection and filtering are implemented on each lines of below PCB. They can be ordered on ST web site, reference is STEVAL-OET005.

Figure 30. Evaluation board Type-C connector

AN4871 - Rev 3 page 24/32

## 8.2 Type-C protection for STM32 evaluation boards

STM32 USB Type-C Nucleo shields are designed for nonexpert developers, looking for an easy way to quickly develop basic applications, using STM32 and companion TCPP devices:

The X-NUCLEO-SNK1M1 expansion board allows evaluating the features of the TCPP01-M12 for the USB Type-C and the protections for VBUS and CC lines suitable for sink applications for any STM32 (5V only without UCPD and Power delivery SPR with UCPD).

Figure 31. X-NUCLEO-SNK1M1

The X-NUCLEO-SRC1M1 expansion board allows evaluating the features of the TCPP02-M18 for the USB Type-C and the protections for VBUS and CC lines suitable for source applications for any STM32 (5V only without UCPD and Power delivery SPR with UCPD)

AN4871 - Rev 3 page 25/32

Figure 32. X-NUCLEO-SRC1M1

• The X-NUCLEO-DRP1M1 expansion board allows evaluating the features of the TCPP03-M20 for the USB Type-C and the protections for VBUS and CC lines suitable for source applications for STM32 with UCPD.

Figure 33. X-NUCLEO-DRP1M1

AN4871 - Rev 3 page 26/32

## 9 Conclusion

USB Type-C is the future of the USB. High-speed data, high current charging and reversibility, all in the same small connector is a must.

However, although it is a good and cheap connector, it cannot protect and filter all its pins against external aggressions, exposing to damage or disturb the device where it is being used.

STMicroelectronics offers a wide range of transient voltage suppressors , OVP and common mode filters allowing the designer to choose the right solution to ensure reliability and good performance, avoiding electrical overstress or antenna desense.

A secure Type-C connector is the guarantee of a satisfied user.

AN4871 - Rev 3 page 27/32

# **Revision history**

Table 4. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Sep-2016 | 1        | First release.                                                                                                                                                                             |

| 15-Dec-2016 | 2        | Updated Figure 14: "USB 3.1 Gen 2 eye diagram example for HSP051-4M10, after reference cable and equalizer".  Changed Figure 30: "Evaluation board Type-C connector".  Minor text changes. |

| 22-Feb-2023 | 3        | Inserted Section 8.1 Protection and filtering evaluation boards and Section 8.2 Type-C protection for STM32 evaluation boards. Removed audio properties chapter.                           |

AN4871 - Rev 3 page 28/32

# **Contents**

| 1           | USE     | 3 Type-C                                                        | 2  |

|-------------|---------|-----------------------------------------------------------------|----|

|             | 1.1     | Overview                                                        | 2  |

|             | 1.2     | Power supply                                                    | 4  |

|             |         | 1.2.1 Power supply options                                      | 4  |

|             |         | 1.2.2 USB Power Delivery                                        | 4  |

|             | 1.3     | Differential lines                                              | 6  |

|             |         | 1.3.1 USB interface                                             | 6  |

|             |         | 1.3.2 Alternate mode                                            | 7  |

| 2           | Con     | nstraints to be faced                                           | 8  |

| 3           | Pow     | ver supply protection                                           | 9  |

| 4           | Cor     | nfiguration line protection                                     |    |

| 5           | Тур     | e-C Vbus and CC protections solutions for STM32                 |    |

| 6           | Diffe   | erential line ESD protection                                    |    |

|             | 6.1     | Signal bandwidth                                                | 13 |

|             | 6.2     | Impact of ESD protection device on transmitted signal rise time |    |

|             | 6.3     | Eye diagrams                                                    |    |

| 7           | Ante    | enna desense and noise rejection: common mode filters           | 16 |

|             | 7.1     | Choosing the right bandwidth                                    |    |

|             | 7.2     | Common mode rejection                                           |    |

|             | 7.3     | The PCB layout                                                  |    |

|             | 7.4     | Benefits of the common mode filters                             | 18 |

| 8           | Ava     | ilable solutions for testing                                    | 24 |

|             | 8.1     | Protection and filtering evaluation boards                      |    |

|             | 8.2     | Type-C protection for STM32 evaluation boards                   | 25 |

| 9           | Con     | nclusion                                                        |    |

|             |         | history                                                         |    |

|             |         | ıbles                                                           |    |

|             |         | gures                                                           |    |

| <b>∟</b> 13 | ווו ווו | yuico                                                           |    |

# **List of tables**

| Table 1. | Definition of the pin functions |   |

|----------|---------------------------------|---|

| Table 2. | Power supply options            | 1 |

| Table 3. | Features of TCPPs               |   |

| Table 4. | Document revision history       |   |

AN4871 - Rev 3 page 30/32

# **List of figures**

| Figure 1.  | USB Type-C links                                                                                                              | 2    |

|------------|-------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | USB Type-C typical view                                                                                                       | 2    |

| Figure 3.  | Receptacle interface pinout (front view)                                                                                      | 3    |

| Figure 4.  | Source power rule outline for SPR                                                                                             | 5    |

| Figure 5.  | USB PD over CC pins                                                                                                           | 5    |

| Figure 6.  | USB 2.0 high-speed 480 Mbps eye diagram mask (template 1)                                                                     | 6    |

| Figure 7.  | USB 3.1 Gen 1, 5 Gbps eye diagram mask                                                                                        | 6    |

| Figure 8.  | USB 3.2 Gen 2, 10 Gbps eye diagram mask                                                                                       | 7    |

| Figure 9.  | IEC 61000-4-2 +8 kV contact response of ESDA7P60-1U1M                                                                         | 9    |

| Figure 10. | IEC61000-4-5 with 60 A 8/20 μs max. current response of ESDA7P60-1U1M                                                         | . 10 |

| Figure 11. | Attenuation measurement results on HSP051-4M10                                                                                | . 14 |

| Figure 12. | Eye diagram measurements without and with the HSP062-2M6 for 480 Mbps data rate, USB 2.0 template 1 m                         |      |

| Figure 13. | USB 3.2 Gen 1 eye diagram example without and with HSP051-4M10, after reference cable and equalizer                           |      |

| Figure 14. | USB 3.2 Gen 2 eye diagram example for HSP051-4M10, after reference cable and equalizer                                        | . 15 |

| Figure 15. | Layout of ESD protection devices                                                                                              | . 15 |

| Figure 16. | USB4 20.0 Gbps eye diagram with ECMFx-40A100Nx (with Preset 0, reference cable 0.8 m,equalizer with AE 0dB and DFE)           |      |

| Figure 17. | USB3.2 Gen 2 10.0 Gbps eye diagram with ECMFx-40A100Nx (with type C connector, reference cable, equa with ADC = 5 dB and DFE) |      |

| Figure 18. | Typical STMicroelectronics ECMF/CMF common mode rejection (in red, the market reference)                                      |      |

| Figure 19. | Layout example with three ECMF filters on the high-speed lanes                                                                |      |

| Figure 20. | Noise measured on a USB 3.2 Gen 1 link                                                                                        |      |

| Figure 21. | Typical common mode rejection of the ECMF04-4HSWM10 dedicated to 2.4 GHz application                                          |      |

| Figure 22. | In red, the noise level after ECMF insertion on the USB 3.1 Gen 1 link                                                        |      |

| Figure 23. | RSSI Wi-Fi behavior with USB 3.2 Gen 1 traffic ("InSSIDer" window)                                                            |      |

| Figure 24. | Sensitivity lost during USB 3.2 traffic on a Wi-Fi transmission ("inSSIDer" window)                                           |      |

| Figure 25. | Safe Wi-Fi connection                                                                                                         | . 21 |

| Figure 26. | Safe Wi-Fi connection (USB 3.2 Gen 1 data transfer)                                                                           | . 22 |

| Figure 27. | Resistance R <sub>DC</sub> of the common mode filter                                                                          | . 22 |

| Figure 28. | ECMF family typical clamping voltage                                                                                          | . 23 |

| Figure 29. | Clamping comparison between ECMF and LTCC+MOV technology (IEC61000-4-2 ± 8 kV contact)                                        |      |

| Figure 30. | Evaluation board Type-C connector                                                                                             |      |

| Figure 31. | X-NUCLEO-SNK1M1                                                                                                               | . 25 |

| Figure 32. | X-NUCLEO-SRC1M1                                                                                                               | . 26 |

| Figure 33. | X-NUCLEO-DRP1M1                                                                                                               | . 26 |

AN4871 - Rev 3 page 31/32

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

AN4871 - Rev 3 page 32/32