## はじめに

本アプリケーション・ノートでは、ST25R3916、ST25R3917、およびST25R3920の各デバイスを採用した基板設計において、不要な輻射を低減し、全体のノイズフロアを低く抑えるための基本的な考慮事項を取り上げています。本書は、ST25R3916デバイスを基本とした説明になっていますが、ST25R3917デバイスとST25R3920デバイスにも同様に適用できます。

部品のレイアウト段階では、クリーンな信号伝送を確実に実現するために、これらのデバイスと他のアクティブなコンポーネント（レシート・プリンタやディスプレイなど）との干渉を考慮する必要があります。

回路パターンを伝播する各信号とそのスペクトラムには特に注意が必要です。各信号を時間ドメインと周波数ドメインで解析し、不要な信号の発生源を突き止め、適切な対策を講じる必要があります。

適切なPCBレイアウトとすることで、多くのEMI問題を最小限に抑え、FCC、RED、CISPRなどの各種規格に適合したアプリケーションを実現できます。

## 目次

|       |                               |    |

|-------|-------------------------------|----|

| 1     | 略語                            | 4  |

| 2     | 一般的な推奨事項                      | 5  |

| 3     | 基本的な検討事項                      | 6  |

| 4     | 回路パターンからの輻射                   | 9  |

| 4.1   | 差動信号                          | 9  |

| 4.1.1 | RFO と RFI の配線                 | 10 |

| 4.2   | コモン・モード信号                     | 12 |

| 4.2.1 | SPI データ信号の配線                  | 14 |

| 5     | 寄生効果を持つ部品と電流リターン経路            | 15 |

| 6     | デカップリング・コンデンサとバイパス・コンデンサ      | 16 |

| 7     | 電源フィルタ                        | 19 |

| 8     | サーマル・パッド                      | 20 |

| 9     | アナログ信号とデジタル信号が混在する PCB のレイアウト | 21 |

| 10    | まとめ                           | 23 |

| 11    | 改版履歴                          | 24 |

## 図の一覧

|       |                              |    |

|-------|------------------------------|----|

| 図 1.  | 矩形波                          | 6  |

| 図 2.  | 矩形波のスペクトラム                   | 6  |

| 図 3.  | 台形波                          | 6  |

| 図 4.  | ローパス・フィルタ                    | 7  |

| 図 5.  | PCB 上でのローパス・フィルタの位置          | 8  |

| 図 6.  | ST25R3916 および対称性を持つ整合回路レイアウト | 9  |

| 図 7.  | PCB 上のループ面積                  | 10 |

| 図 8.  | 整合回路の配線                      | 10 |

| 図 9.  | GND プレーンのスロット発生防止            | 12 |

| 図 10. | コモン・モード・フィルタ - PCB 上の配置      | 13 |

| 図 11. | コモン・モード・フィルタ - 回路図           | 13 |

| 図 12. | デカップリング・コンデンサの配置 (表面側)       | 16 |

| 図 13. | デカップリング・コンデンサの位置 (裏面側)       | 17 |

| 図 14. | デカップリング・コンデンサの回路図            | 18 |

| 図 15. | 電源の詳細回路図                     | 19 |

| 図 16. | ST25R3916 のサーマル・パッド          | 20 |

| 図 17. | アナログ信号とデジタル信号の垂直方向分離         | 22 |

| 図 18. | 4 層 PCB の構成                  | 22 |

## 1 略語

|             |                |

|-------------|----------------|

| <b>AGND</b> | アナログ・グランド      |

| <b>DGND</b> | デジタル・グランド      |

| <b>EMC</b>  | 電磁適合性          |

| <b>EMI</b>  | 電磁干渉           |

| <b>EUT</b>  | 被測定輻射源         |

| <b>ESD</b>  | 静電気放電          |

| <b>GND</b>  | 電圧のグランド（基準）レベル |

| <b>IC</b>   | 集積回路           |

| <b>PCB</b>  | プリント回路基板       |

| <b>RFI</b>  | 無線入力           |

| <b>RFO</b>  | 無線出力           |

| <b>USB</b>  | ユニバーサル・シリアル・バス |

## 2 一般的な推奨事項

PCBの設計には、最適なEMC性能を得るためのガイドラインがあります。

- リターン電流がどこをどのように流れるかを必ず考慮し、判断します。

- グランドのギャップ上に信号を配線しないようにします。

- 独立したアナログ部とデジタル部を使用して、PCB 上に混在するアナログ信号とデジタル信号を分離します。

- 電流リターン・プレーンは分割しないようにします。基板のアナログ部とデジタル部双方の下方に1つの全面プレーンを配置します。

- デジタル信号は、基板のデジタル部（デジタル関連の層）のみに配線します。

- アナログ信号は、基板のアナログ部（アナログ関連の層）のみに配線します。

- 機械的または電気的な何らかの理由でグランド・プレーンまたは電源プレーンを分割する場合、そのプレーンの隣接層において、分割部分を横断する回路パターンを配線しないようにします。

- 電源プレーンの分割部を横断する必要があるアナログまたはデジタルの回路パターンは、それぞれアナログまたはデジタルの全面グランド・プレーンに隣接する層に配置する必要があります。

- A/DコンバータとD/Aコンバータ、およびアナログ信号とデジタル信号が混在する他のほとんどのICは、デジタル部を持つアナログ・デバイスと見なします。アナログ部を持つデジタル・デバイスとは見なしません。

- アナログ信号とデジタル信号が混在するICのピン名にあるAGNDとDGNDは、IC内部でそのピンがどこに接続されているかを示しています。そのピンをICの外部でどこにどのように接続すればよいかを示唆するものではありません。アナログ信号とデジタル信号が混在するICのほとんどでは、AGNDピンとDGNDピンの両方をアナログ・リターン・プレーンに接続する必要があります。

- デジタル電源のデカップリング・コンデンサは、デジタル・グランド・ピンに直接接続する必要があります。

- ICの論理ゲートの論理切り替えに必要な過渡電源電流のすべてまたは一部を、低インダクタンス経路を通じて供給するには、デカップリング・コンデンサが必要です。

- 電源のグランド系統に逆流する雑音を短絡、または少なくとも低減するにはデカップリング・コンデンサが必要です。

- デカップリングは、ICの近傍にL-C回路を配置して過渡スイッチング電流を供給する措置です。ICの近傍にコンデンサを配置して過渡スイッチング電流を供給する措置ではありません。

- 低周波数域で高いデカップリング効果を得るには、デカップリング・コンデンサの容量値が重要です。

- 高周波域では、デカップリング・コンデンサの容量値は重要ではありません。高周波域で最も重要な条件は、デカップリング・コンデンサと直列に存在するインダクタンスを小さくすることです。

- 高周波域で高いデカップリング効果を得るには、配置するコンデンサの数を多くする必要があります。

- 可能な限りデバイスに近い位置にデカップリング・コンデンサを配置します。

- RFI信号とRFO信号を対称な配線とします。また、整合回路の信号回路パターンが長くならないようにします。RFO1とRFO2の回路パターンを常に近接させます。RFI1とRFI2も同様です。

- 整合部品は、互いに近接させ、対称に配置する必要があります。

### 3 基本的な検討事項

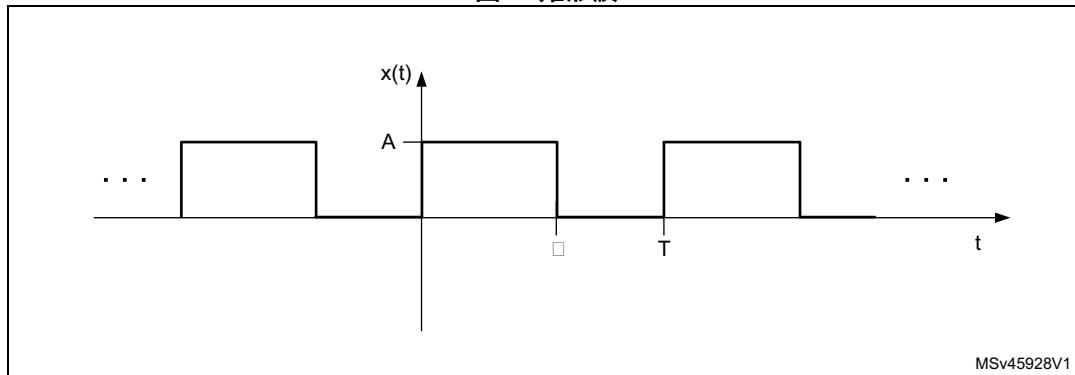

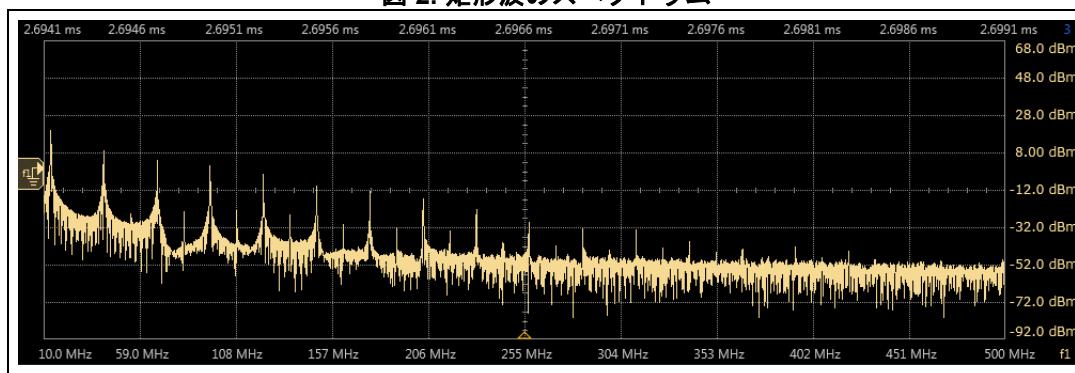

ICで生成される信号の大半は、周期的な矩形波信号であり（図 1）、図 2のようなスペクトラムとなります。

図 1. 矩形波

図 2. 矩形波のスペクトラム

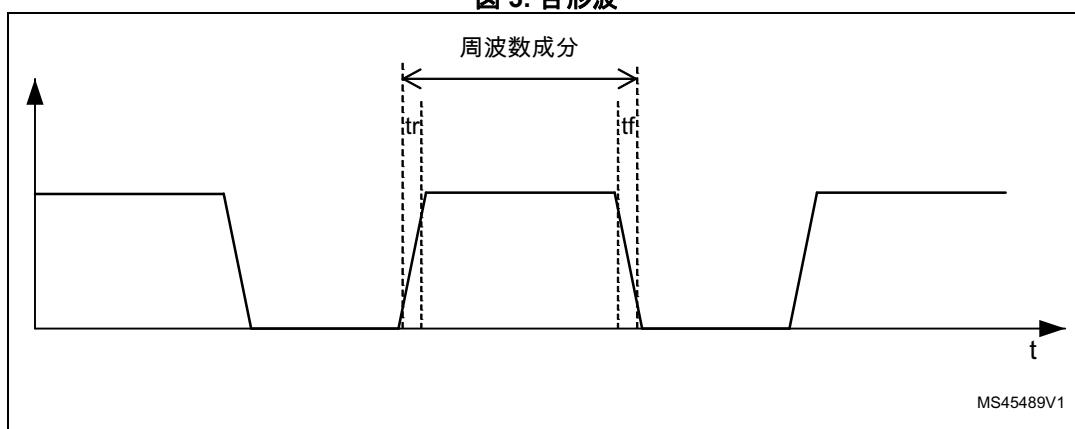

実際のデバイスでは理想的な矩形波を生成できないので、ICやクロックから得られる台形パルスを扱う必要があります。台形波ではスルーレートが有限値なので、立上り時間と立下がり時間が0ではなくなります（図 3）。高周波域の高調波の振幅は、信号の立上り時間と立下がり時間で決まり、立上り時間が長いほど振幅が小さくなります。

図 3. 台形波

ST25R3916では、その内部でスルー・レートが制御されます。

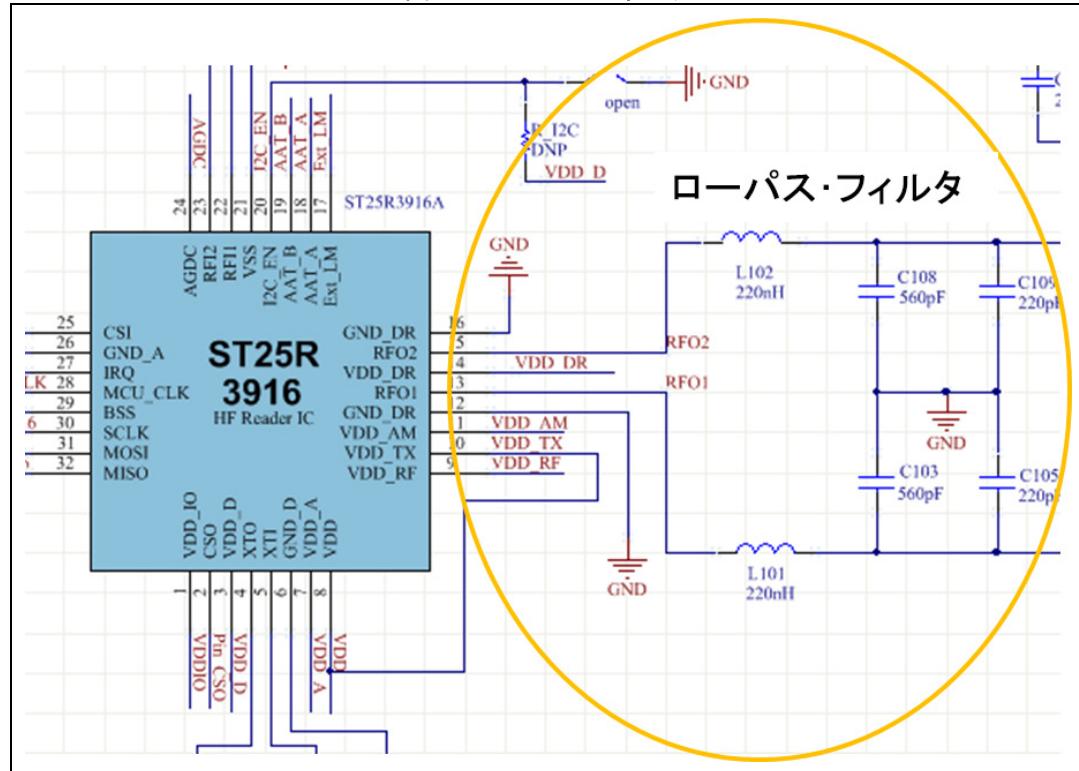

高調波を低減する手段として、ローパス・フィルタを使用して波形の立上りと立下がりのエッジを丸める方法もあります。この方法は、図 4に示すように、RF ドライバの出力にインダクタとコンデンサを使用することで実現できます。

図 4. ローパス・フィルタ

長い回路パターンからの不要輻射を防止するために、可能な限り出力段の近傍にフィルタ回路を設けることが重要です（図 5を参照）。

図 5. PCB 上でのローパス・フィルタの位置

## 4 回路パターンからの輻射

露出した回路パターンは不要輻射の発生源の一つです。回路パターンから輻射が発生する様子を把握するには、伝播中の信号を解析する必要があります。回路パターンを伝播している信号は、その2つの主要な構成要素である差動信号とコモン・モード信号に分けて考えることができます。

### 4.1 差動信号

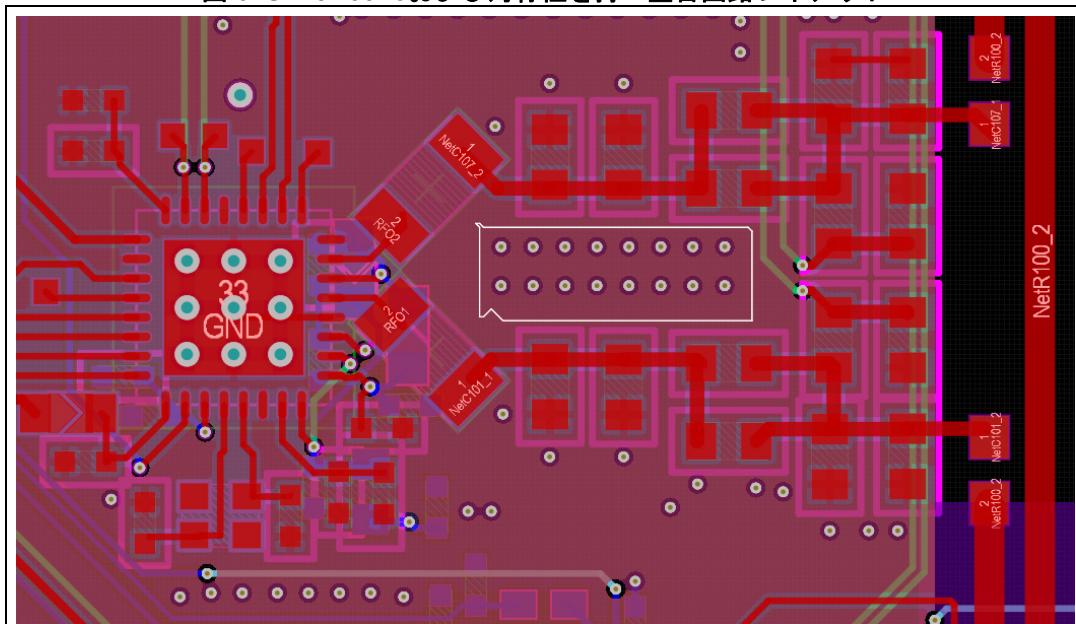

2本の回路パターン上を伝播する差動信号による輻射電界は互いに打ち消し合う方向に形成され、理想的な条件下では合計輻射電界がゼロになります。ST25R3916の出力ドライバも差動モードで動作しているので、同様の効果が得られます。しかし、差動両側の部品の許容誤差および回路パターン上で信号の非対称性により、差動電流間に差が発生し、“実質的にゼロ”ではない電界が生成されます。対称性が維持される整合回路のレイアウトとなるように留意する必要があります。

図 6. ST25R3916および対称性を持つ整合回路レイアウト

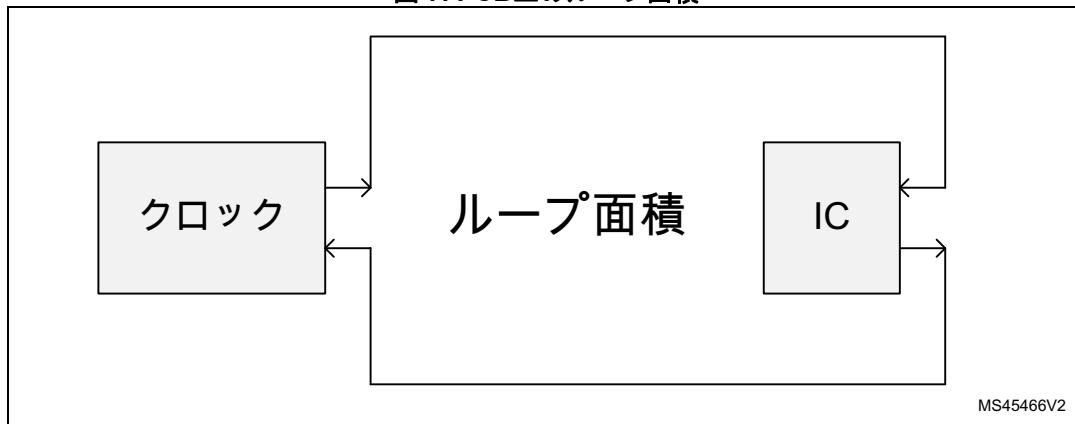

また、差動モードで放射される輻射を制御するには、信号の回路パターンとそのリターン電流経路によって形成されるループ面積（図 7を参照）を最小限にすることが重要です。特にクロック信号の場合は、最小のループ面積が得られるように、この回路パターンと経路の長さを最小限にする必要があります。

図 7. PCB上のループ面積

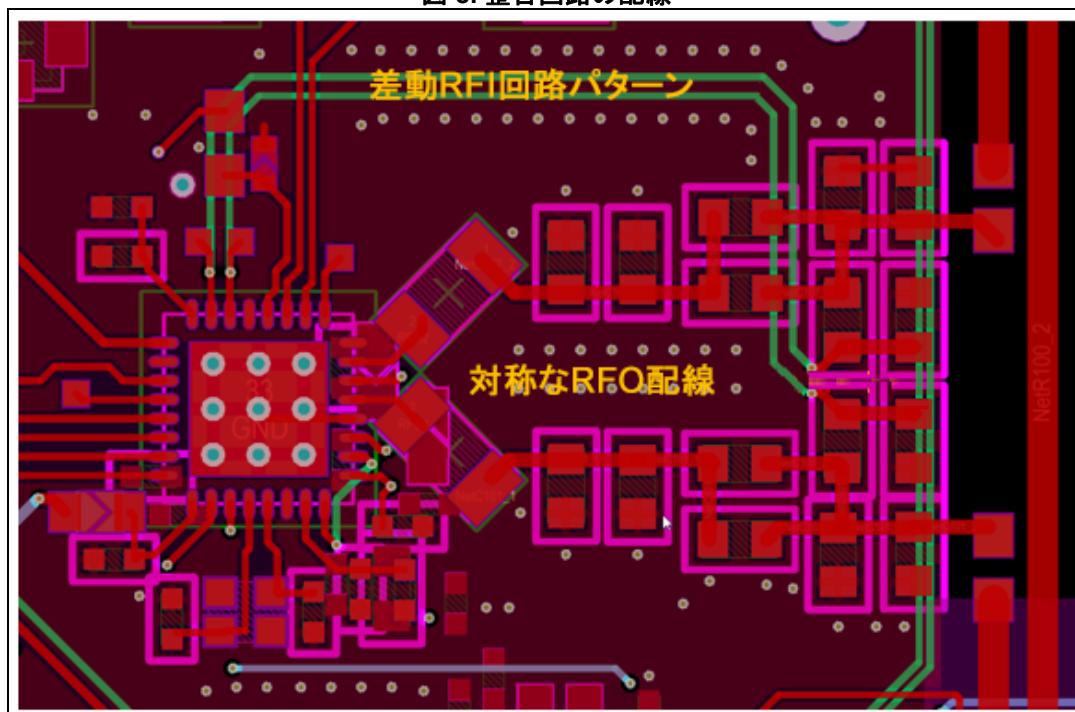

#### 4.1.1 RFOとRFIの配線

ST25R3916の送信と受信は、それぞれ差動配線となっているため、PCBのレイアウトにおいて、不要な信号結合と不要輻射が最小限になるよう細心の注意を払って取り扱う必要があります。これらの信号はPCBの内層に配線する必要がありますが、整合部品の回路パターンを相互接続するビアが多くならないように、整合回路はすべてPCBの片側（表面側の層）に配置します。リターン電流は、GND層を流れます。整合回路の下にあるGND層には切れ込みを設けないことが重要です。

図 8. 整合回路の配線

不要輻射が増加するため、整合回路の配線においては、いわゆるスルーホールは使用しないようにします。RFOからアンテナ給電部までの回路パターン長を短くするために、整合部品どうしが近接配置されている点に留意してください。LCフィルタとそれを除く整合部品間の信号回路パターンを長くすることはお勧めできません。RFOの後に続く各インダクタは、結合を最小限にするために、互いに直角となるように配置します。

RFIラインは対称な配線として、RFOラインから適切な距離に配置します。受信信号は、整合回路の中点と結合しないようにして、キャリア信号レベルが比較的低くなる場所である直列コンデンサと交差するようにします。2本のRFI信号は互いに離れないように配線し、配線長に差がないようにします。

RFIラインを、整合回路の中央を通り、RFIピンに戻るように配線することもできます。

また、RFO経路上でGNDとの間にあるすべての部品（コンデンサ）を、複数のビアを使用してGNDに接続します。これにより、インダクタンスを最小限にして不要な共振を減らします。

## 4.2 コモン・モード信号

コモン・モード輻射は、PCBに接続されたケーブルから主に発生します。

コモン・モード輻射に最も大きく影響する要素は、PCBの基準グランド・プレーンに存在するインダクタンス（およびそれに起因するグランド電圧）です。コモン・モード輻射は、差動モード輻射よりも影響が大きいです。コモン・モード電流がわずかでも、輻射上の大きな問題となることがあります。

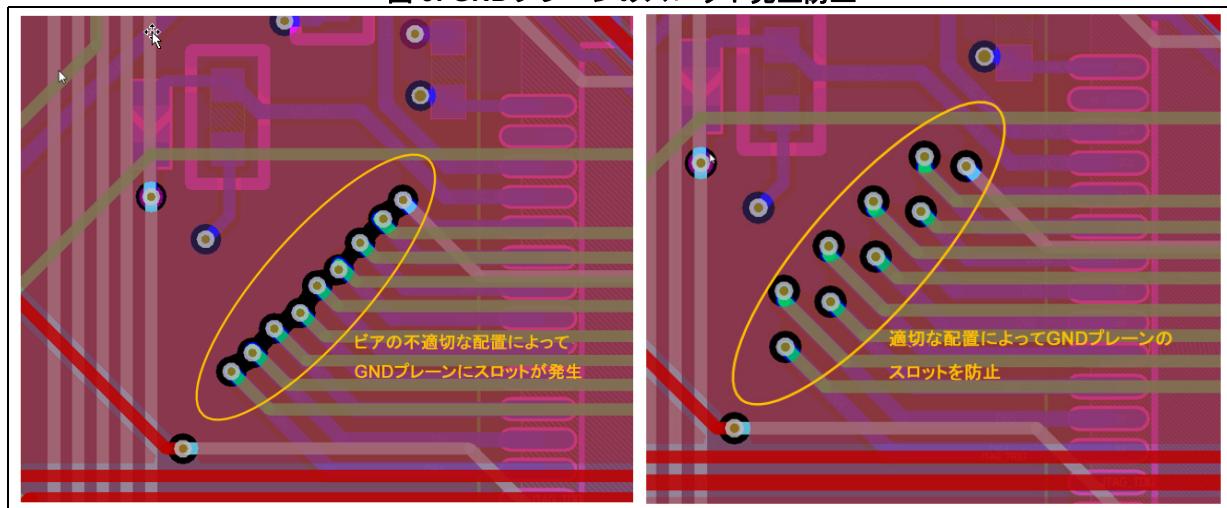

コモン・モード輻射を低減するには以下の措置が必要です。

- 電流供給経路を電流リターン経路に近い位置に配置します。

- ケーブルの長さを短縮します。

- コモン・モード電圧（通常はグランド電位）を最小限にします。グランドのインピーダンスを低減するには、全面グランド・プレーンを使用します。また、グランド・プレーンにスロットが発生しないようにします（図 9 で違いを確認してください）。

図 9. GND プレーンのスロット発生防止

ケーブルを接続している場合は、その取り扱いに注意し、適切なシールドを施します。これを実現するには、たとえば、ケーブルからPCBのグランドまでの各接続を何らかの方法で互いに分離したうえで、ケーブルと直列にコモン・モード・インピーダンス・チョークを使用します。

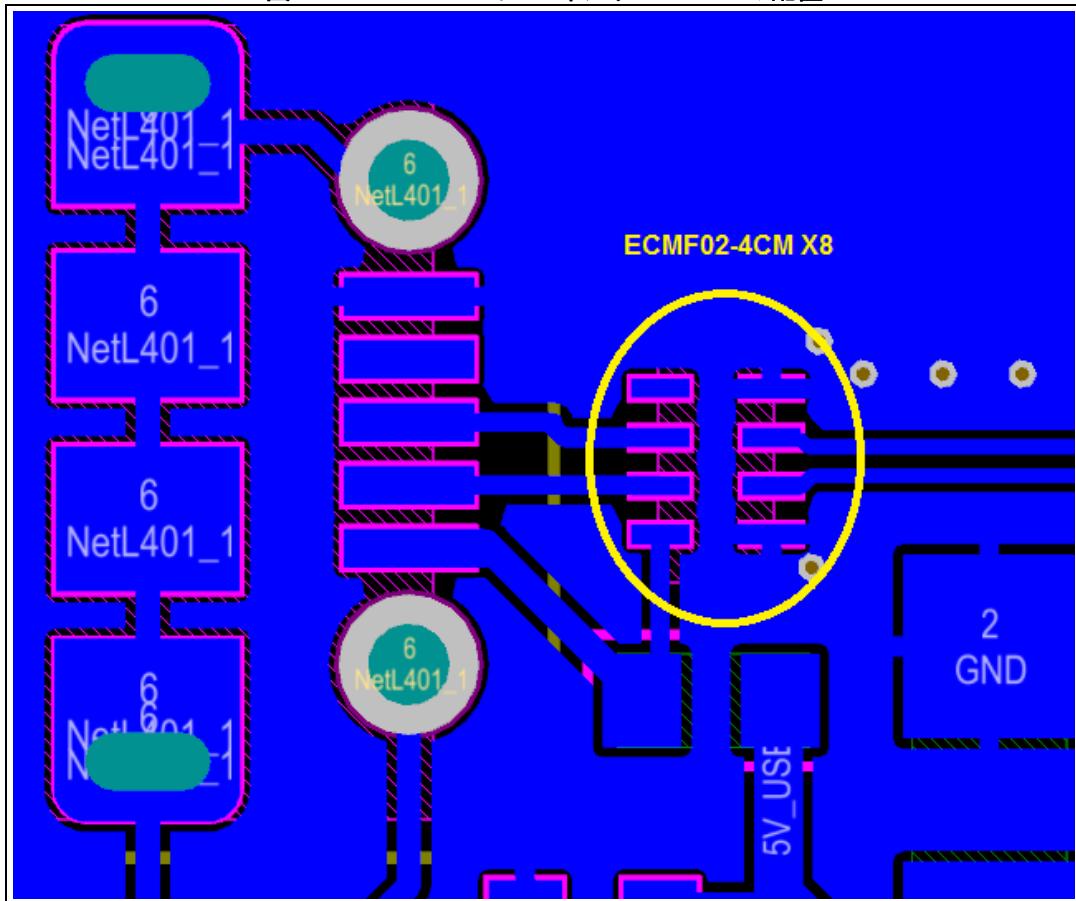

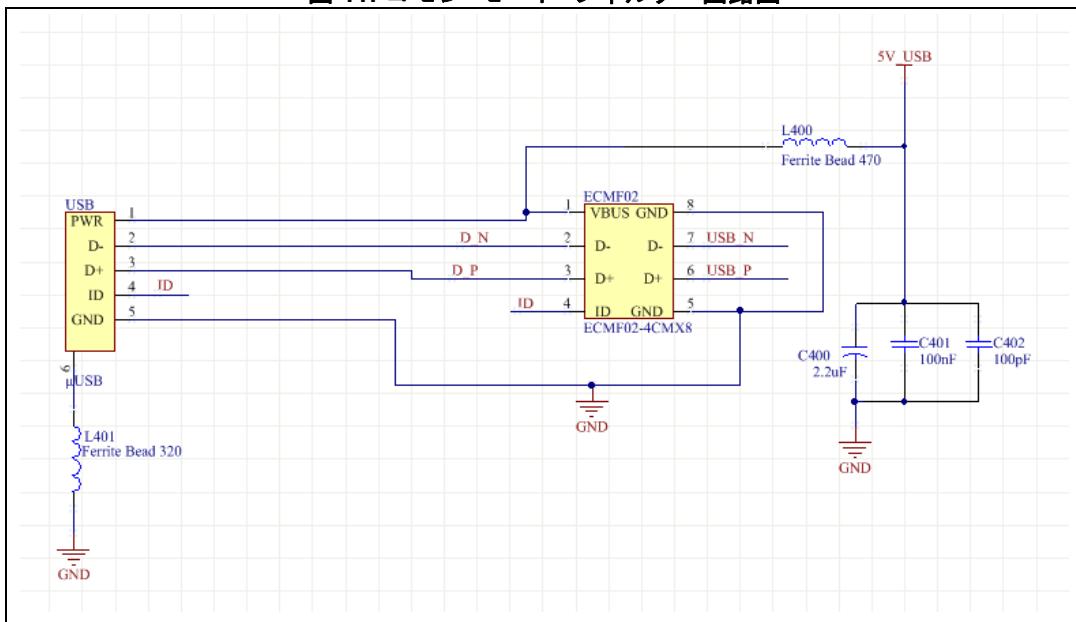

USBのD+ラインとD-ラインに内蔵コモン・モード・フィルタ（ECMF02-4CMX8）およびすべてのラインにESD保護を使用できます。そのPCB上の配置例を図 10、回路図の例を図 11に示します。

図 10. コモン・モード・フィルタ - PCB上の配置

図 11. コモン・モード・フィルタ - 回路図

#### 4.2.1 SPIデータ信号の配線

ST25R3916からマイクロコントローラへのSPIデータ信号は、可能な限り等長で、インピーダンスを管理して配線する必要があります。

SPIインターフェースの回路パターン長を各部で短くし、ビアの使用を最小限にします。

27.12MHzや13.56MHzなどの周波数を生成する水晶発振器の上にSPI信号を配線しないようにして、クロストークと信号ひずみを最小限に抑えます。

## 5 寄生効果を持つ部品と電流リターン経路

PCBの設計では、パッシブ部品の選択とその寄生効果に注意を払う必要があります。

部品製造元が提供する各種の測定値は、低周波のみでの値、またはPCBにおいて実際に使用する周波数範囲とは異なる周波数範囲での値であることがほとんどです。したがって、意図しない輻射効果の原因となる不要な共振を避けるために、設計で使用する各パッシブ部品の動作域とする周波数範囲全体で、正確な測定値と寄生効果を知ることが重要になります。

寄生効果と共に、PCB上での電流リターン経路も評価する必要があります。

信号源へのすべての電流リターン: 電流はループの中を流れるので、そのリターン経路は輻射に大きく影響します。信号源に戻る電流は、その周波数に応じてさまざまな経路をたどることに注意します。低周波域では抵抗値が最も低い経路に流れやすく、高周波域ではインダクタンス値が最も低い経路に流れやすくなります。

リターン経路の抵抗値を把握するには、PCB上のストリップラインとマイクロストリップのインピーダンスを計算し、高インピーダンスの経路と低インピーダンスの経路を特定することが重要です。

## 6 デカップリング・コンデンサとバイパス・コンデンサ

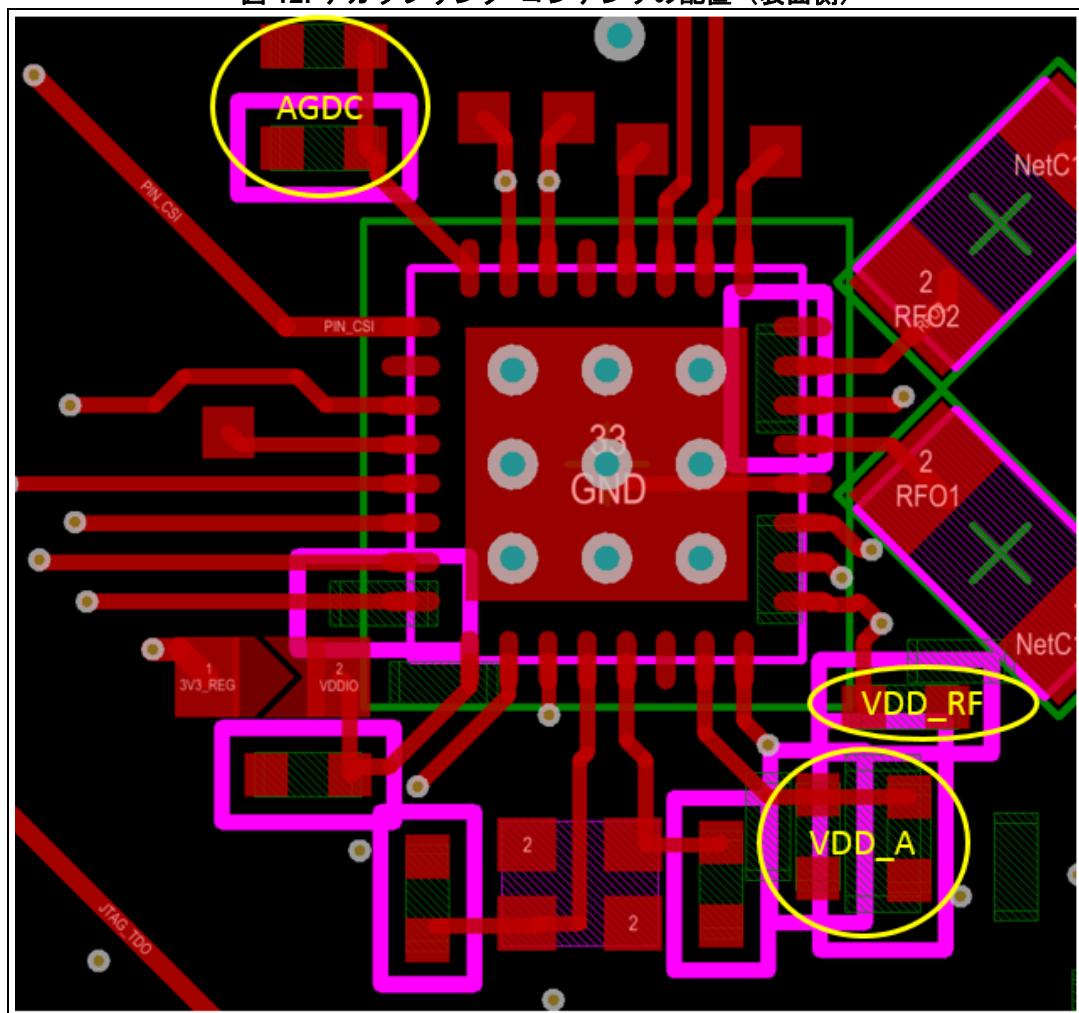

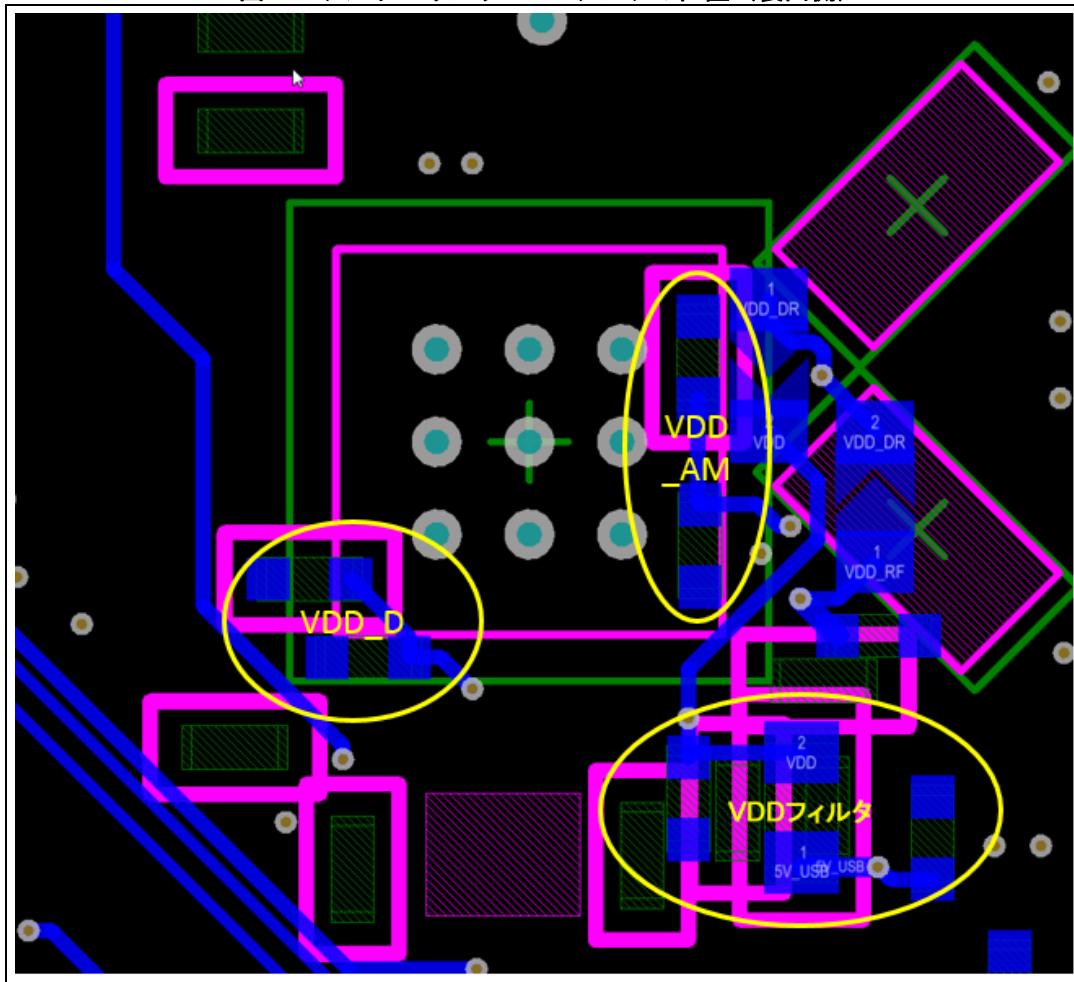

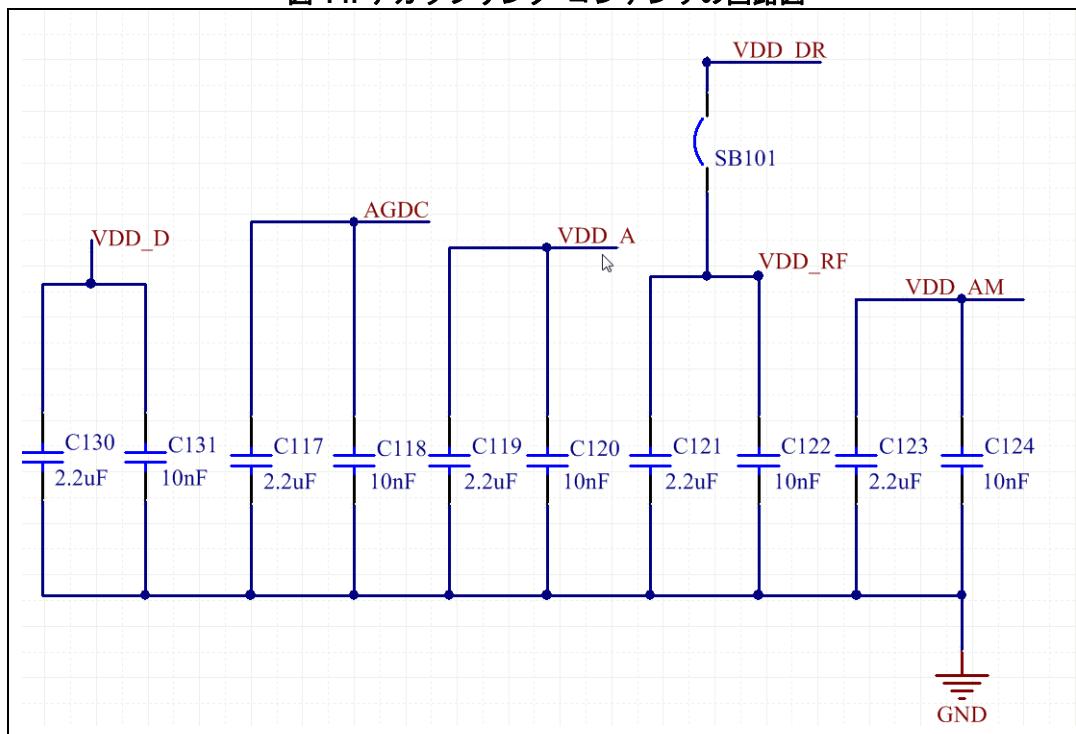

ST25R3916レギュレータと各AGD電圧ピン（VSP\_D, VSP\_A, VSP\_RF、およびAGD）に付随するすべてのコンデンサは、可能な限りチップに近い位置に配置する必要があります。

2.2 $\mu$ Fと10nFを並列接続したデカップリング・コンデンサの一般的な配置を図 12と図 13に示します。

図 12. デカップリング・コンデンサの配置（表面側）

図 13. デカップリング・コンデンサの位置（裏面側）

図 14. デカップリング・コンデンサの回路図

## 7 電源フィルタ

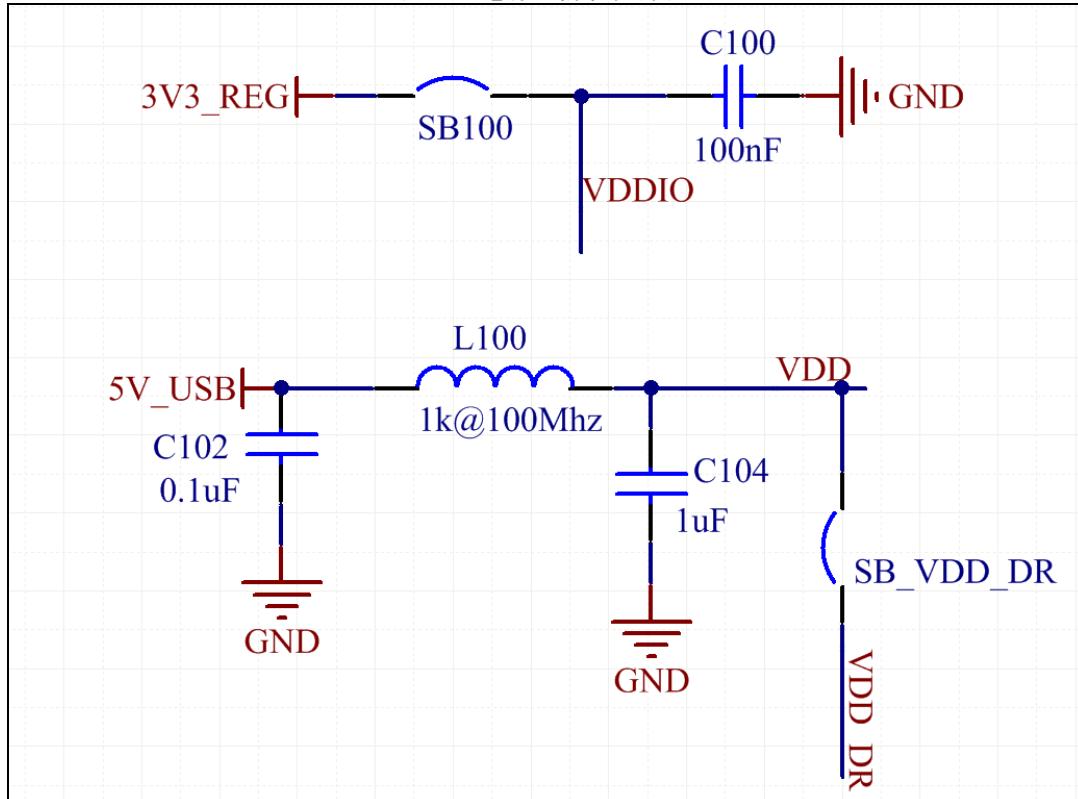

外部雑音が電源を通じてシステムに侵入することがあり、同様に内部のノイズが直流電源のリードを通じて基板に伝わることがあります。ライン上の雑音と過渡電流による影響を低減するために、PCBの電源系統の設計においてフィルタを配置することをお勧めします。コモン・モード・フィルタと差動モード・フィルタの両方をPCB上に設けます。

ST25R3916のVDDピンの電源にPIフィルタを構成します。設計対象とする周波数範囲で、コンデンサの一般的な容量値は1 ~ 0.01 $\mu$ F、フェライト・ビーズの一般的な抵抗値は50 ~ 1,500 $\Omega$ です（直流電流によってフェライト・ビーズが磁気飽和しないように注意します）。

図 15. 電源の詳細回路図

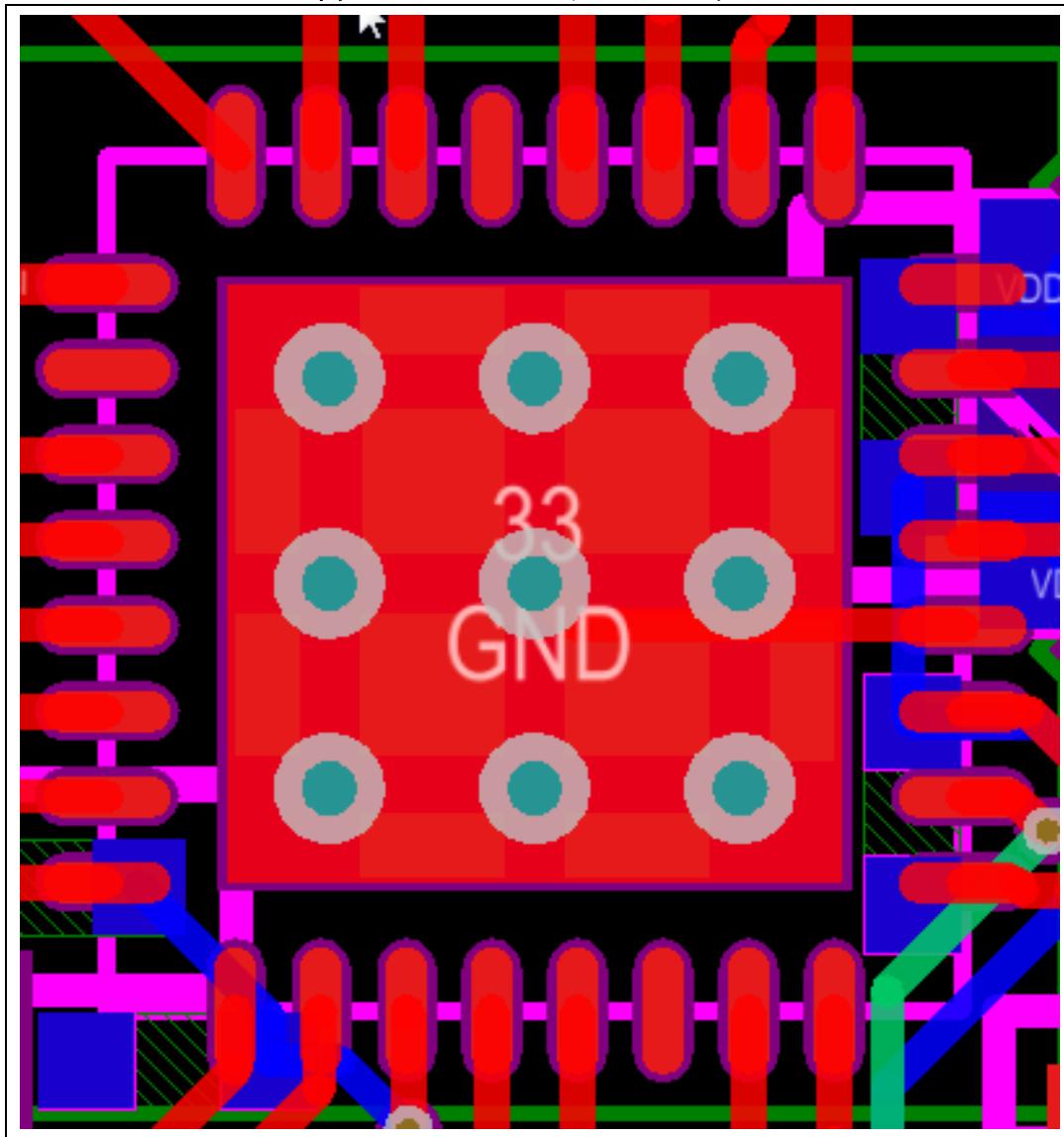

## 8 サーマル・パッド

ST25R3916の下に設けたサーマル・パッドは、グランド・プレーンとサーマル・ヒート・シンクの両方として機能します。このパッドは、PCBのグランド・プレーンに複数のビアによって接続します。はんだ付けが良好に行われるよう、パッド表面にはめっき処理が必要です。これらの複数のビアによって、この領域の合計寄生インダクタンスを小さい値に維持できます。

図 16. ST25R3916のサーマル・パッド

## 9 アナログ信号とデジタル信号が混在するPCBのレイアウト

アナログ信号とデジタル信号が混在するシステムの設計では、PCBのレイアウトを決める際に、アナログ部とデジタル部の分離に関連する問題が重要になります。それに伴って、この2つのサブシステム間でグランドをどのように扱うべきかという点も課題になります。

GNDを分離することは、アナログとデジタルのサブシステムそれぞれのリターン電流を分離する必要性から生じています。この2つのサブシステムを互いに分離するには、2つのグランドを物理的に分離するか（実際に切断するか）、空間的に離して配置します。アナログ信号とデジタル信号に共通のGND接続を持つ複数のミックスドシグナルICを使用する場合、分離したグランドを使用する方法では、単一のGNDで構成する場合よりも多くの問題が発生することがあります。

この場合は、電流リターン・プレーンを1つのみとすることをお勧めします。その際に、PCB上でデジタル部とアナログ部を別々の区画に配置すること、アナログ信号をアナログ部でのみ配線し、デジタル信号をデジタル部でのみ配線すること、リターン電流経路をデジタルとアナログで分離することに留意します。

分離したGNDプレーンを使用すると、電源電流のリターン経路が複数発生して電流ループが形成される可能性があるので、別の問題が生じることがあります。アナログ・サブシステムとデジタル・サブシステムの両方の電圧基準点となっているグランド端子を通じて、電源電流が戻ってくるようにする必要があります。電流ループが存在すると輻射が生成され、その放射レベルはループ面積と電流強度に比例します。

システムのアナログ部とデジタル部を全面的に分離して実装した8層PCBの一般的な構成を図 17に示します。この構成では、アナログ部品をPCBの表面側の層に配置し、デジタル部品を裏面側の層に配置しています。

図 18は、4層PCBの積層構成を示しています。信号は表面側と裏面側の層に配線しています。内部の層は、独立したGND層と電源層で構成されています。

図 17. アナログ信号とデジタル信号の垂直方向分離

| Layer Name                        | Type                 | Material         |

|-----------------------------------|----------------------|------------------|

| Top Overlay                       | Overlay              |                  |

| Top Solder                        | Solder Mask/Coverlay | Surface Material |

| Component Side - ANALOG           | Signal               | Copper           |

| Dielectric1                       | Dielectric           | Core             |

| Ground Plane 1 (GND) - ANALOG     | Signal               | Copper           |

| Dielectric2                       | Dielectric           | Prepreg          |

| Inner Layer 1 - ANALOG            | Signal               | Copper           |

| Dielectric 6                      | Dielectric           | Core             |

| Power Plane (VRF) - ANALOG POWER  | Signal               | Copper           |

| Dielectric5                       | Dielectric           | Prepreg          |

| Power Plane (VCC) - DIGITAL POWER | Signal               | Copper           |

| Dielectric 7                      | Dielectric           | Core             |

| Inner Layer 3 - DIGITAL           | Signal               | Copper           |

| Dielectric4                       | Dielectric           | Prepreg          |

| Ground Plane 2 (GND) - DIGITAL    | Signal               | Copper           |

| Dielectric3                       | Dielectric           | Core             |

| Solder Side - DIGITAL             | Signal               | Copper           |

| Bottom Solder                     | Solder Mask/Coverlay | Surface Material |

| Bottom Overlay                    | Overlay              |                  |

図 18. 4層PCBの構成

| Layer Name     | Type                 | Material         |

|----------------|----------------------|------------------|

| Top Overlay    | Overlay              |                  |

| Top Solder     | Solder Mask/Coverlay | Surface Material |

| Top Layer      | Signal               | Copper           |

| Dielectric1    | Dielectric           | Core             |

| GND            | Signal               | Copper           |

| Dielectric 3   | Dielectric           | Prepreg          |

| VBUS           | Signal               | Copper           |

| Dielectric 2   | Dielectric           | Core             |

| Bottom Layer   | Signal               | Copper           |

| Bottom Solder  | Solder Mask/Coverlay | Surface Material |

| Bottom Overlay | Overlay              |                  |

## 10 まとめ

高出力RFシステムの設計に影響を与えるEMCの問題と運用上で発生しやすい問題の多くは、本書で説明したガイドラインに従うことで回避できます。

信号の配線と、PCBのどの層に信号を配線するかという点に特に注意が必要です。

PCBの積層、各部品の配置、複数の直流電圧の取り扱い、電流リターン経路、ビアの配置は、基板設計において常に十分な検討を必要とする要素です。多くの場合、要求される性能を実現するためには、PCBレイアウトの最適化が必要となります。

## 11 改版履歴

表 1. 文書改版履歴

| 日付          | 版 | 変更内容                                                                                   |

|-------------|---|----------------------------------------------------------------------------------------|

| 2018年12月20日 | 1 | 初版発行                                                                                   |

| 2019年2月26日  | 2 | 文書の分類を“ST限定”から“公開”に更新。                                                                 |

| 2020年8月24日  | 3 | 文書の適用範囲をST25R3917デバイスとST25R3920デバイスに拡大。<br><a href="#">はじめに</a> を更新。<br>文書全体の微調整および編集。 |

**重要なお知らせ（よくお読み下さい）**

STMicroelectronics NV およびその子会社（以下、ST）は、ST製品及び本書の内容をいつでも予告なく変更、修正、改善、改定及び改良する権利を留保します。購入される方は、発注前にST製品に関する最新の関連情報を必ず入手してください。ST 製品は、注文請求書発行時点で有効なST の販売条件に従って販売されます。

ST製品の選択並びに使用については購入される方が全ての責任を負うものとします。購入される方の製品上の操作や設計に関してST は一切の責任を負いません。

明示又は默示を問わず、STは本書においていかなる知的財産権の実施権も許諾致しません。

本書で説明されている情報とは異なる条件でST 製品が再販された場合、その製品についてSTが与えたいかなる保証も無効となります。

ST およびST ロゴはSTMicroelectronics の商標です。STの登録商標についてはSTウェブサイトをご覧ください。www.st.com/trademarks その他の製品またはサービスの名称は、それぞれの所有者に帰属します。

本書の情報は本書の以前のバージョンで提供された全ての情報に優先し、これに代わるものです。

この資料は、STMicroelectronics NV 並びにその子会社(以下ST)が英文で記述した資料（以下、「正規英語版資料」）を、皆様のご理解の一部として頂くためにSTマイクロエレクトロニクス株が英文から和文へ翻訳して作成したものです。この資料は現行の正規英語版資料の近時の更新に対応していない場合があります。この資料は、あくまでも正規英語版資料をご理解頂くための補助的参考資料のみにご利用下さい。この資料で説明される製品のご検討及びご採用にあたりましては、必ず最新の正規英語版資料を事前にご確認下さい。ST及びSTマイクロエレクトロニクス株は、現行の正規英語版資料の更新により製品に関する最新の情報を提供しているにも関わらず、当該英語版資料に対応した更新がなされていないこの資料の情報に基づいて発生した問題や障害などにつきましては如何なる責任も負いません。

© 2021 STMicroelectronics - All rights reserved