## STM32WL シリーズ用 RF 整合ネットワーク設計ガイド

### 概要

STM32WL シリーズ・マイクロコントローラは、LoRa®、(G)FSK、(G)MSK、BPSK 変調などの高効率の長距離ワイヤレス・アプリケーション用に設計された Sub-GHz トランシーバです。

このアプリケーション・ノートでは、STM32WL シリーズ・デバイスの標準的な RF 整合およびフィルタリングのアプリケーション回路、特に、整合回路で最大の RF 性能を引き出すための方法論、およびフィルタリング回路を適用して認証標準に準拠する方法について詳しく説明します。

この文書には、特定の電力/周波数の組み合わせに対する出カインピーダンス値が記載されており、一致する出カインピーダンス値が異なることがあります。インピーダンスは、定義された周波数および電力仕様に対するものです。

## 1 一般情報

本書は STM32WL シリーズの Arm® ベースのマイクロコントローラに適用されます。

注 Arm は、米国内およびその他の地域にある Arm Limited(またはその子会社)の登録商標です。

表 1. 項目(略称)

| 項目(略称)           | 定義                                                            |

|------------------|---------------------------------------------------------------|

| BALUN            | Balanced to unbalanced circuit(平衡回路と不平衡回路)                    |

| BOM              | Bill of materials(部品表)                                        |

| BPSK             | Binary phase-shift keying(バイナリ・フェーズシフト・キーイング)                 |

| (G)FSK           | Gaussian frequency-shift keying modulation(ガウス周波数シフト・キーイング変調) |

| (G)MSK           | Gaussian minimum-shift keying modulation(ガウス最小シフト・キーイング変調)    |

| GND              | Ground(接地:回路電圧基準)                                             |

| LNA              | Low-noise power amplifier(低ノイズ・パワー・アンプ)                       |

| LoRa             | Long-range proprietary modulation(長距離独自変調)                    |

| PA               | Power amplifier(パワー・アンプ)                                      |

| PCB              | Printed-circuit board(プリント回路基板)                               |

| PWM              | Pulse-width modulation(パルス幅変調)                                |

| RFO              | Radio-frequency output(無線周波数出力)                               |

| RFO_HP           | High-power radio-frequency output(高電力無線周波出力)                  |

| RFO_LP           | Low-power radio-frequency output(低電力無線周波数出力)                  |

| RFI_N            | Negative radio-frequency input(負の無線周波数入力)(GND を基準)            |

| RFI_P            | Positive radio-frequency input(正の無線周波数入力)(GND を基準)            |

| Rx               | レシーバ                                                          |

| SMD              | Surface-mounted device(表面実装デバイス)                              |

| SRF              | Self-resonant frequency(自己共振周波数)                              |

| SPDT             | Single-pole double-throw switch(单極双投スイッチ)                     |

| SP3T             | Single-pole triple-throw switch(单極 3 投スイッチ)                   |

| Tx               | トランスマッタ                                                       |

| RSSI             | Received signal strength indication(受信信号強度表示)                 |

| NF               | Noise figure(雑音指数)                                            |

| Z <sub>OPT</sub> | Optimal impedance(最適インピーダンス)                                  |

## 参照

- [1] T. S. Bird, "Definition and Misuse of Return Loss [Report of the Transactions Editor-in-Chief]," in IEEE Antennas and Propagation Magazine, vol. 51, no. 2, pp. 166-167, April 2009.

- [2] Banerjee, Amal. Automated broad and narrow band impedance matching for RF and microwave circuits. Cham, Switzerland: Springer, 2019.

- [3] White, Joseph F. High frequency techniques: an introduction to rf and microwave design and computer simulation. 発行場所未特定: John Wiley, 2016.

- [4] Cutler, Phillip. Electronic circuit analysis. New York: McGraw-Hill, 1960.

- [5] Ludwig, Reinhold, and Pavel Bretschko. RF circuit design: theory and applications. Upper Saddle River, New Jersey: Prentice-Hall, 2000.

- [6] Khan, Ahmad S. Microwave engineering: concepts and fundamentals. Boca Raton: CRC Press, Taylor and Francis Group, 2014. Print.

- [7] Teppati, Valeria et al. Modern RF and microwave measurement techniques. New York: Cambridge University Press, 2013. Print.

- [8] Mariscotti, Andrea. RF and Microwave Measurements: Device Characterization, Signal Integrity and Spectrum Analysis. Chiasso (Switzerland: ASTM Analysis, Simulation, Test and Measurement Sagl, 2015. Print.

- [9] Steer, Michael B. Microwave and RF design: networks. NC State University: University of North Carolina Press, 2019. Print.

- [10] Ghannouchi, Fadhel M., and Mohammad S. Hashmi. Load-pull techniques with applications to power amplifier design. Dordrecht New York: Springer, 2013. Print.

## 2 RF の基礎

### 2.1 RF の用語

#### 2.1.1 パワー

パワーは RF 信号の測定値で、多くの場合 dBm で表され、次の式によって P(mW 単位)から計算されます。

$$dBm = 10 \times \log_{10} \left( \frac{P}{1 \text{ mW}} \right)$$

#### 2.1.2 ゲイン

ゲインとは、入力に対する増幅装置の出力の比のことです(dB 単位)。

#### 2.1.3 損失

RF では、損失は 2 つのタイプに分けられます。

- インピーダンス不整合または誤った送信ライン設計に起因する不整合による損失

- 以下に起因するオーム損失

- ボード製造で使用されたラミネートおよび予備浸透材料に依存する誘電損失。

- 導通損失:

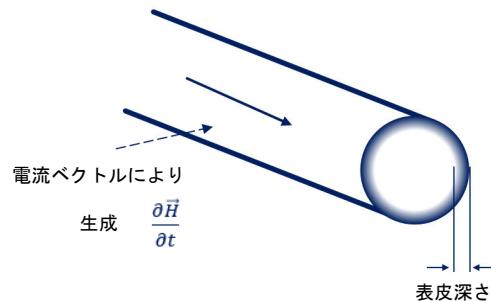

- RF のオーム損失(周波数とともに抵抗が増加)の最も一般的な原因である、表皮効果。

図 1. 表皮効果

- 近接効果(導体間の磁界相互作用に起因する抵抗増加)

図 2. 近接効果

いずれの場合も、あるステージから次のステージにすべてのパワーが送信されるわけではないので、アンテナから放射される電力は少なくなります。

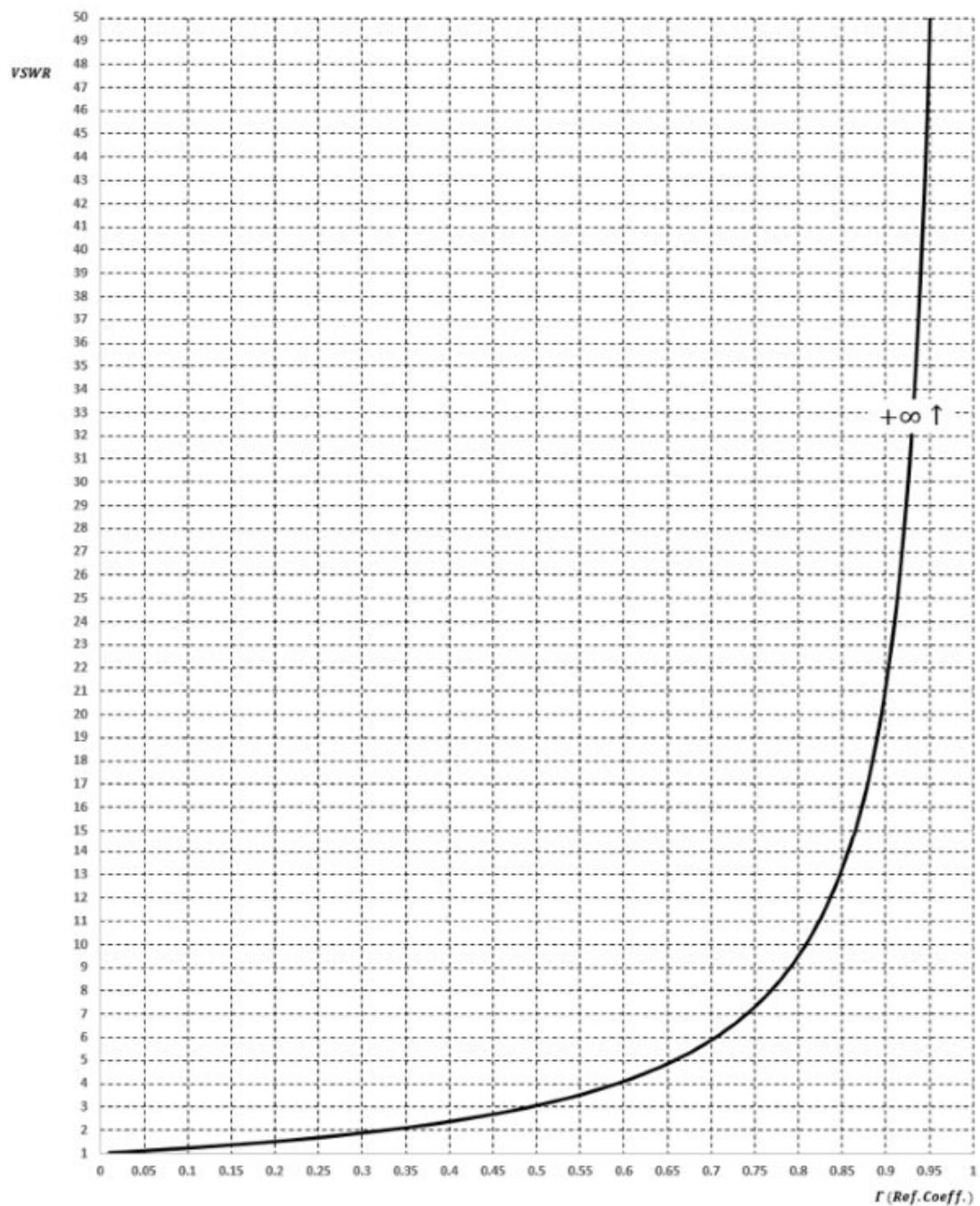

#### 2.1.4 反射係数( $\Gamma$ )、電圧定在波比(VSWR)、およびリターン・ロス(RL)

信号が送信ラインを介して電源から負荷へ流れる場合、送信ラインの特性インピーダンスと負荷の間に不一致が存在すると、信号の一部が負荷から電源へ逆流します。

メモ ほとんどの場合、RF 負荷(ここでは  $Z_L$  または単に「負荷」という言葉で表されます)はアンテナです。

反射信号の極性と大きさは、負荷インピーダンスがライン・インピーダンスよりも高いか低いかによって異なります。

反射係数( $\Gamma$ )は、入射波の振幅に対する反射波の振幅を表す尺度です。負荷インピーダンス( $Z_L$ )や送信ラインの特性インピーダンス( $Z_0$ )によって、次のように表すことができます。

$$\Gamma = \frac{V^-}{V^+} = \frac{Z_L - Z_0}{Z_L + Z_0}$$

VSWR(Voltage standing wave ratio:電圧定在波比、または単に SWR、「ビズワー」と発音)は、接続ポイントでのインピーダンス整合の精度を表す尺度です。VSWR は、ライン上の定在波の最大電圧と最小電圧の比率として定義されます。また、反射係数比の関数として次のように表すこともできます。

$$VSWR = \frac{V_{Z \max}}{V_{Z \min}} = \frac{1 + \Gamma}{1 - \Gamma}, \quad 1 \leq VSWR \leq \infty$$

VSWR = 1.0 の場合、反射電力はありません。

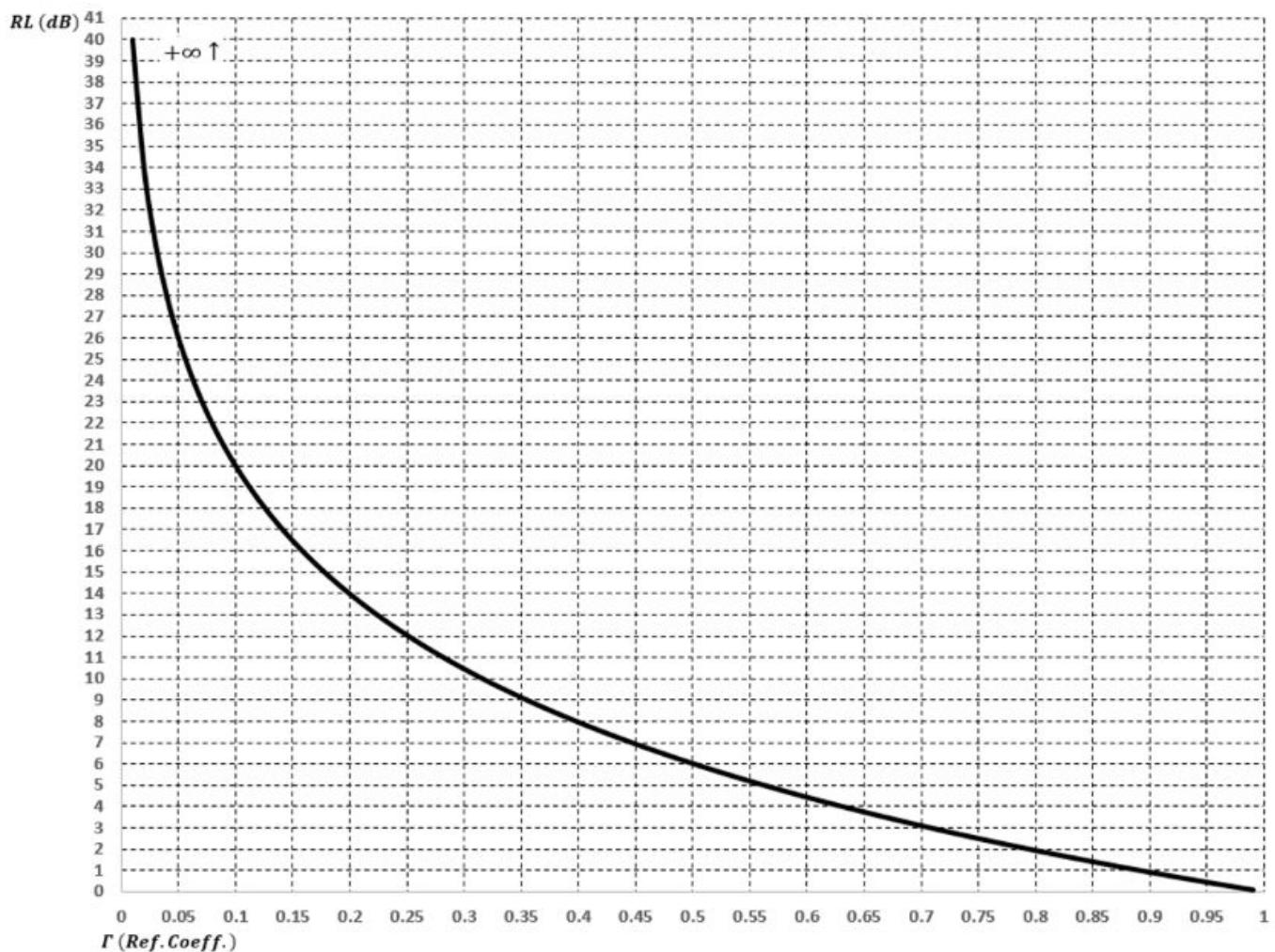

RL(Return loss:リターン・ロス)は反射係数の関数ですが、dB 単位で表されます。

$$\begin{aligned} RL &= 10 \times \log_{10} \left( \frac{P_{incident}}{P_{reflected}} \right) = P_{incident} - P_{reflected} \\ &\Rightarrow P_{reflected \ (in \ dB)} = P_{incident \ (in \ dB)} - RL \end{aligned}$$

$$\Rightarrow P_{reflected \ (in \ dB)} = P_{incident \ (in \ dB)} - RL$$

数値的に、RL は 0 dB から  $\infty$  までの値を取ります。RL = 0 dB の場合、反射電力は入射電力に等しく、負荷に到達する電力はありません。RL は常に正です(文書 [1] を参照)。

これらの量の数値表現については、[付録 B](#) を参照してください。

## 2.1.5

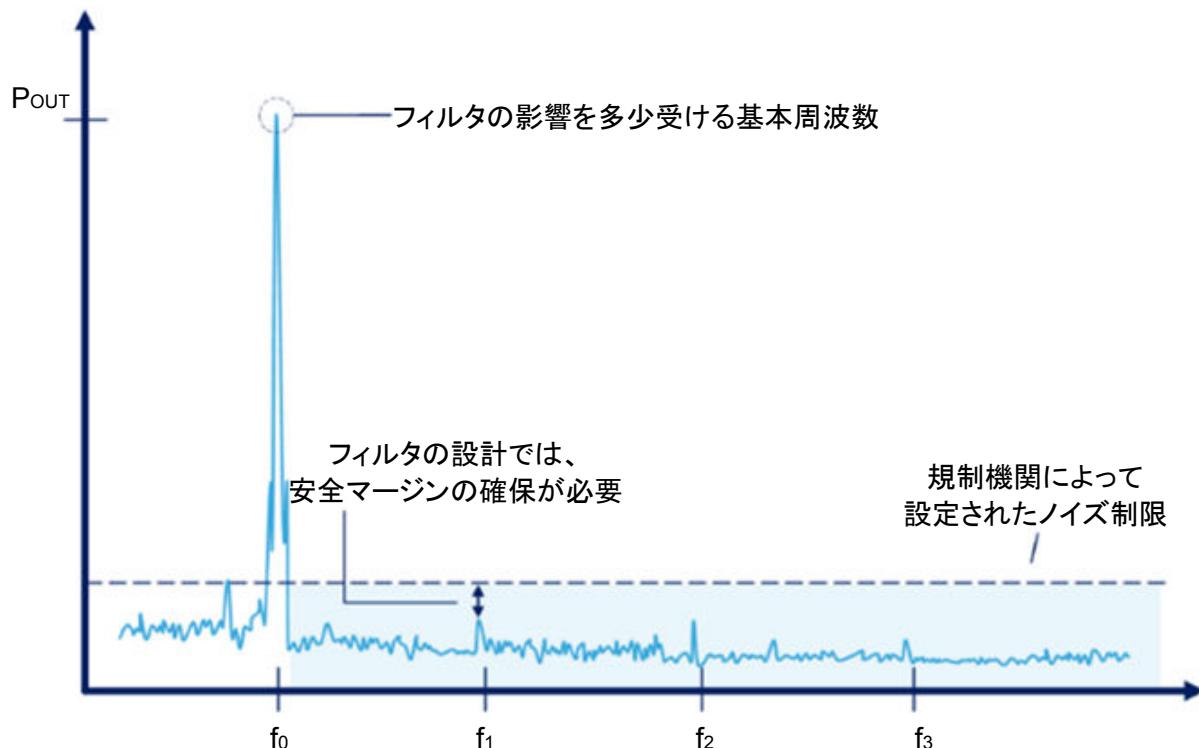

## 高調波と不要波

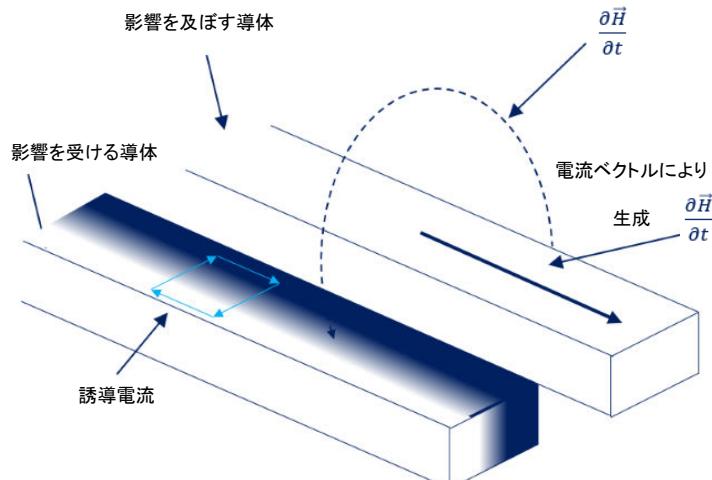

高調波は、入力周波数または出力周波数(基本周波数)の整数倍です。

不要波は、入力周波数(不要周波数)の非整数倍です。

図 3. 周波数における基本信号、高調波、および不要波電力の表示

## 2.2

## インピーダンス整合とスミス・チャート

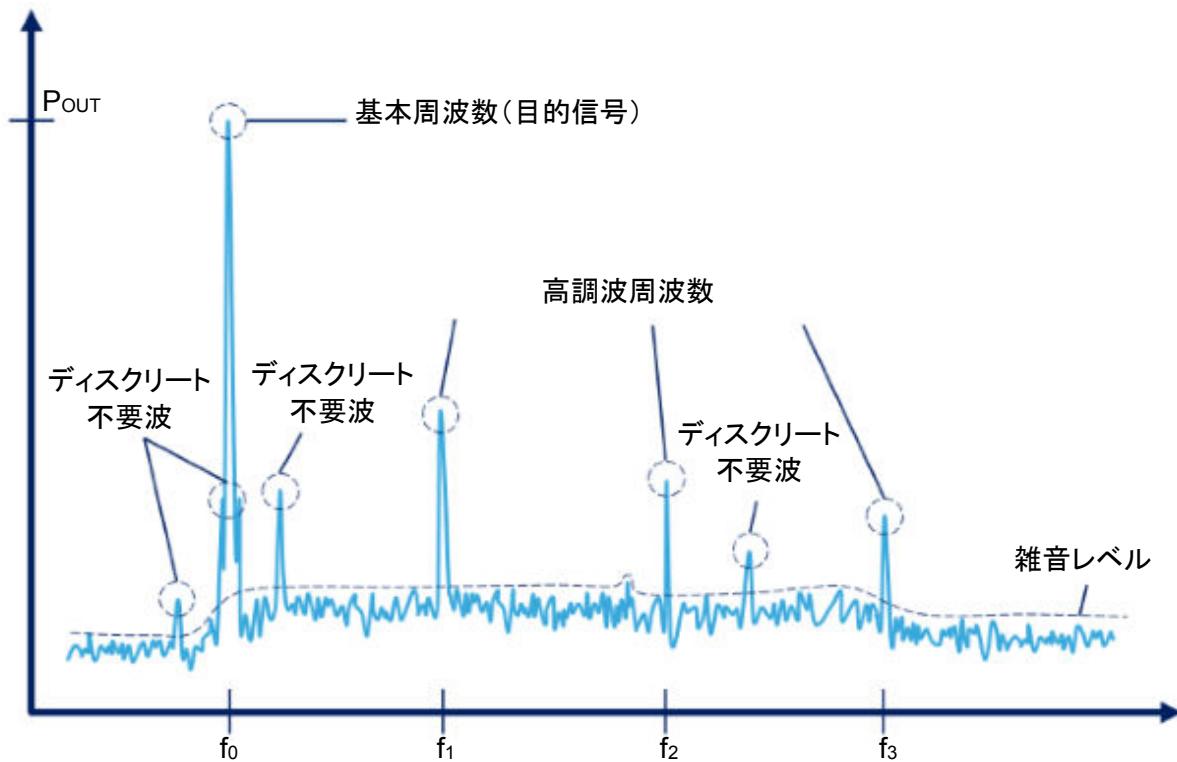

RF では、基準インピーダンスは  $50 \Omega$  の真の値を持ちます。設計または技術の制約により、PA(パワー・アンプ)の最適インピーダンスや LNA(Low-noise amplifier: ローノイズ・アンプ)の最適インピーダンスは  $50 \Omega$  にならないことがあります。これが、インピーダンス整合ネットワークを設計しなければならない理由です。

インピーダンス整合は、最大/最適な信号電力が信号ソースから受信デバイスに転送されることを保証し、電源への信号電力の反射を最小にすることを保証する技術です。整合は、リアクティブ・ネットワークによって行われます。

下の図は、送信ラインを表したものではありません ( $Z_0 = 50 \Omega$  を想定)。

図 4. 電源インピーダンス(RF PA など)と負荷インピーダンス(アンテナなど)の間のインピーダンス整合ネットワークによって生じる共役インピーダンス

文書 [2] によると、電子信号処理回路(特に、通信/ワイヤレス通信機器や民生用電子機器などの数百 MHz および数十 GHz で動作する回路)は、サブ回路間のインピーダンス整合なしでは動作できません。

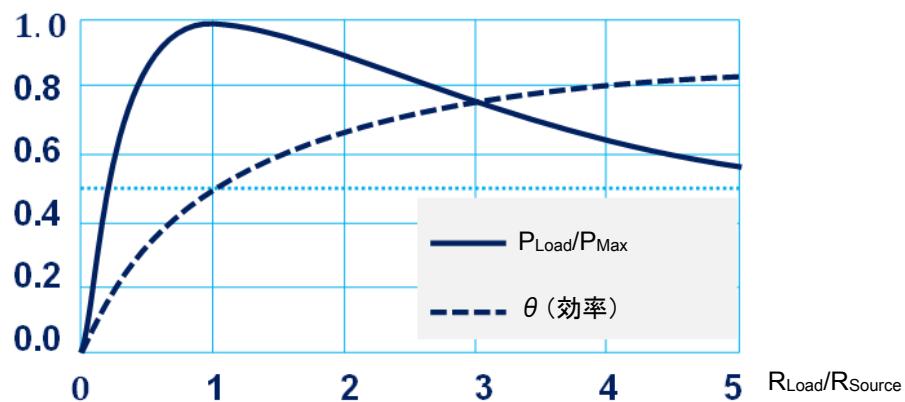

インピーダンス整合には、広帯域と狭帯域の 2 種類があります。広帯域のインピーダンス整合は、実現がより困難です。下の図で、 $R_{\text{LOAD}}$  と  $R_{\text{SOURCE}}$  の比が 1 の場合、最大電力が 50% の効率で電源から負荷に転送されます。

図 5. 負荷時の電力と電源から供給される最大電力の関係

PA または LNA の最適なインピーダンス整合は、計算またはシミュレートすることができますが、微調整が必要になることがあります。このインピーダンス調整を実行するには、整合ネットワークを実装した後、スペクトルアナライザを使用して出力電力を測定します。

## 2.2.1

## 正規化インピーダンス

スミス・チャートのインピーダンス値は、送信ラインの特性インピーダンスである既知の値で正規化されます（通常  $50\Omega$ ）。インピーダンス値を正規化するには、次の例のように、実数部と虚数部の両方を基準値で除算します。

$$Z = (R + jX) \Omega \Rightarrow \frac{Z}{Z_0} = \frac{R}{Z_0} + j \frac{X}{Z_0} \Rightarrow z = r + jx \quad (\text{unitless})$$

ここで、 $Z_0$  は送信ラインの特性インピーダンスです。

## 注

大文字は正規化なしの値を表すために使用し、小文字は正規化された値を表すために使用します。

スミス・チャートでインピーダンス値を読み出すときは、 $Z_0$  倍して値を非正規化することを忘れないでください。

## 例

読み出し値が  $0.5 + j0.2$  の場合、インピーダンス値は  $25 + j10$  となります。スミス・チャートで読み取ったインピーダンスの虚数部  $X$ （リアクタンス）を変換するには、次の計算式を使用します。

- 負の値の場合（容量性リアクタンス）：

$$C = \frac{1}{2\pi f \times Z_0 \times X}$$

$Z_0 = 50$ 、 $f = 915 \text{ MHz}$ 、読み出し値が  $-0.3$  の場合、コンデンサの値は  $C = 11.60 \text{ pF}$  です。

- 正の値の場合（誘導性リアクタンス）：

$$L = \frac{Z_0 \times X}{2 \times \pi \times f}$$

$Z_0 = 50$ 、 $f = 915 \text{ MHz}$ 、読み出し値が  $0.3$  の場合、インダクタの値は  $L = 2.6 \text{ nH}$  です。

## 2.2.2

## スミス・チャートの読み取り

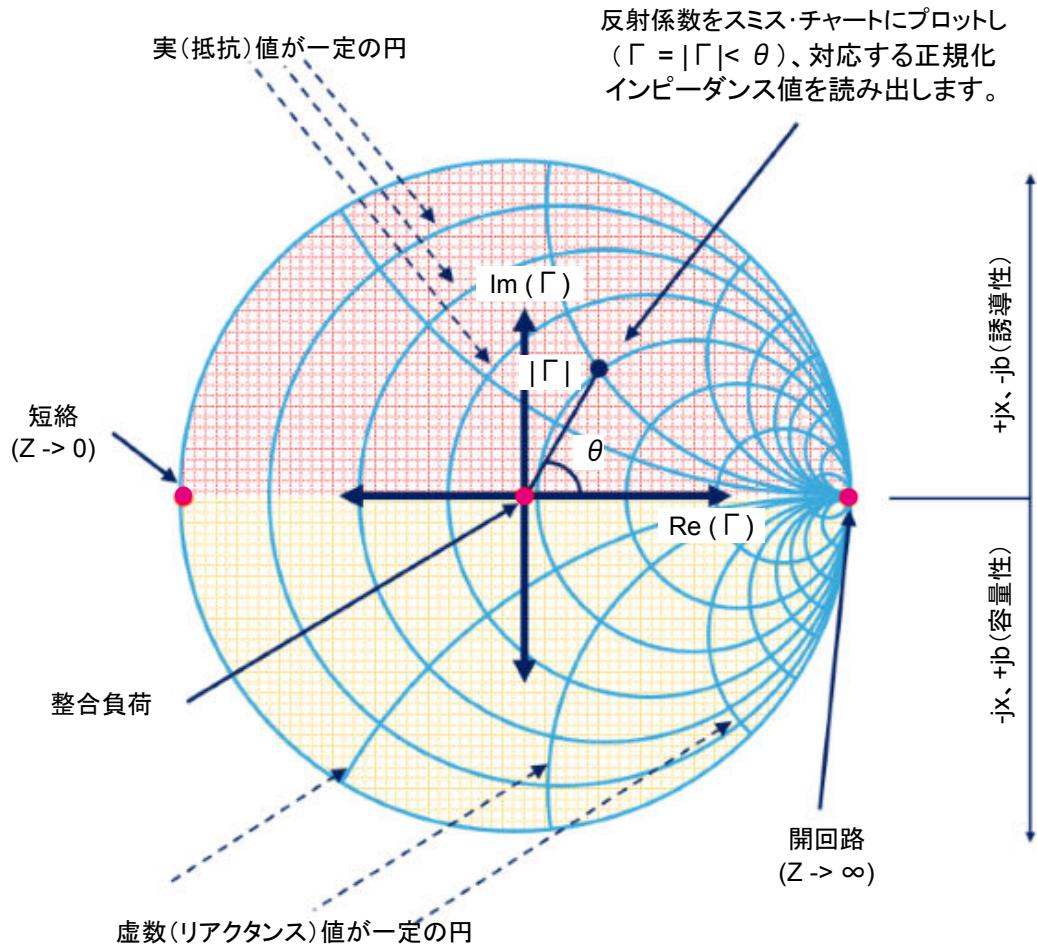

スミス・チャートは、正規化インピーダンスの目盛り（ $z = Z/Z_0$ ）で表されます。

$Z_0 = 50 \Omega$  で整合がある（ $Z = Z_0$ ）場合、 $50 \Omega$  での正規化インピーダンスは 1 となり、これがスミス・チャートの中心です。

整合ネットワークを決定する際の目標は、スミス・チャートの中心に向かって収束することです。

以下の図は、スミス・チャートの軸を表しています。

- スミス・チャートの横軸は純粋な抵抗を表し、左側は  $z = 0$ （短絡）、右側は  $z = \infty$  です。

- 横軸の上部分（赤色の部分）は、正の虚部を持つインピーダンスを表します（直列インダクタ  $+jX$  または並列コンデンサ  $-jb$ ）。

- 横軸の下部分（黄色の部分）は、不の虚部を持つインピーダンスを表します（直列コンデンサ  $+jX$  または並列インダクタ  $-jb$ ）。

図 6. スミス・チャートの特性の単純な表現

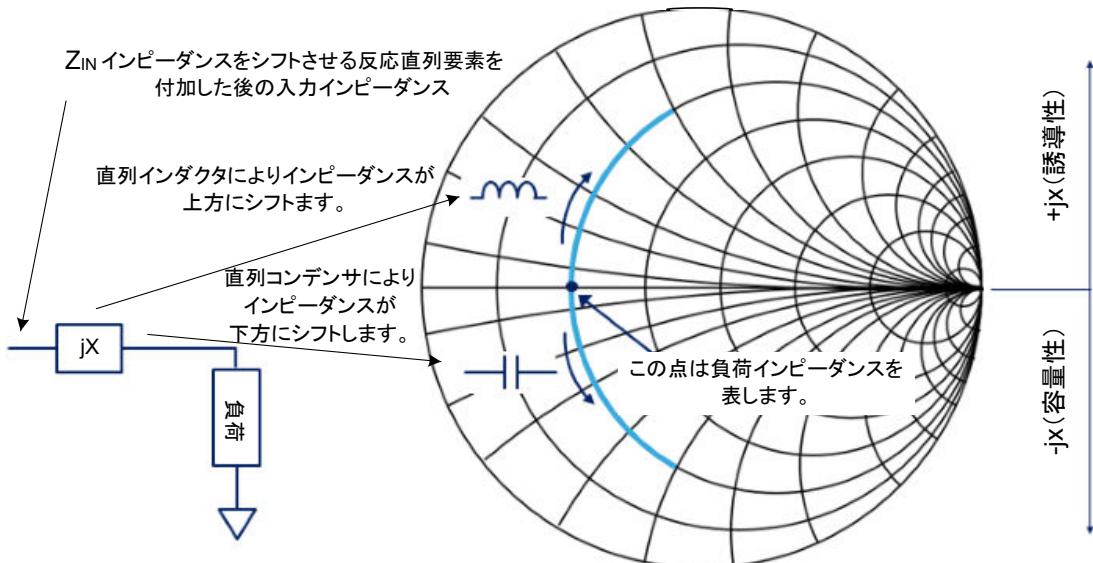

下の図に、インダクタまたはコンデンサを負荷(または電源インピーダンス)と直列に配置した場合の結果を示します。

図 7. 直列コンデンサまたはインダクタを追加したときのインピーダンスの変化を示すスミス・チャートの図

インピーダンス・スミス・チャートでは、インピーダンスは次の形式で表されます。 $Z = R + jX$ 。

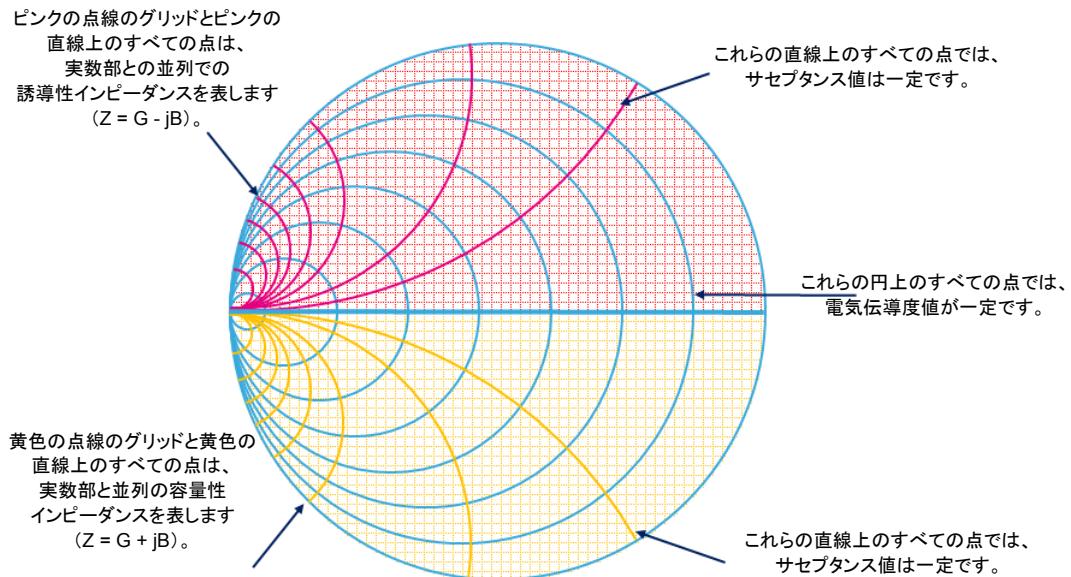

並列コンポーネントを使用した場合のスミス・チャートには、アドミタンス・スミス・チャートという別の「バージョン」があります。この構造はインピーダンス・スミス・チャートに似ていますが、「反転」したものです(下の図を参照)。

図 8. アドミタンス・スミス・チャート

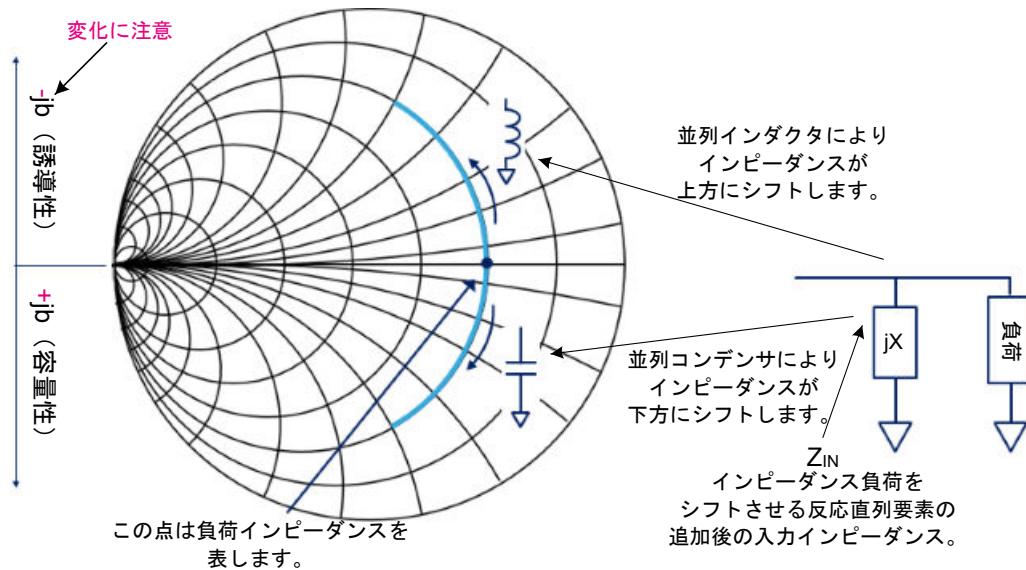

下の図は、負荷(または電源)と並列にインダクタまたはコンデンサを配置した場合の結果を示します。

図 9. 並列コンデンサまたはインダクタを追加したときのアドミタンスの変化を示すスミス・チャートの図

アドミタンス・スミス・チャートで、アドミタンスは  $Y = G + jB$  で表されます。

メモ

インピーダンスとアドミタンスの関係は、 $Z = 1/Y$  または  $Y = 1/z$  です。

### 3 RF コンポーネントの選択

ディスクリート SMD コンポーネントは、RF 信号の波長に対するその挙動から、RF では「集中コンポーネント」と呼ばれることがあります。一方で、マイクロ波工学で使用される分散コンポーネントがあります。このアプリケーション・ノートでは、SMD インダクタやコンデンサなどの集中コンポーネントについて説明します。

STM32WL デバイスが Sub-GHz 帯域で動作する場合でも、さまざまな規制に準拠する必要があるため、FCC(連邦通信委員会)などの一部の規格では不要波および高調波の含有量を 10 GHz まで制御する必要があります。そのため、正しい動作(フィルタ除去など)を得るために、整合およびフィルタ・ネットワークで使用される受動集中コンポーネントを選択する必要があります。このセクションでは、SMD コンポーネントの周波数制限と、その周波数応答が複雑化する様子について詳しく説明します。

#### 3.1 RF コンデンサ

コンデンサは、電界でエネルギーを蓄積するために使用される受動電気コンポーネントであり、製造技術や製造に使用される材料が互いに異なります。コンデンサには、サイズの異なる多くの種類(二重層、ポリエスチル、ポリプロピレンなど)のものがあります。

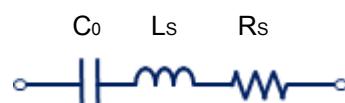

コンデンサの高周波等価回路を下の図に示します。

図 10. コンデンサの高周波等価回路

抵抗  $R_S$  は ESR(Equivalent series resistance: 等価直列抵抗)であり、コンデンサの全オーム損失を表します。インダクタ  $L_S$  は ESL(Equivalent series inductance: 等価直列インダクタンス)であり、その値は SRF(Self resonant frequency: 自己共振周波数)の関数です。

コンデンサの理想的な周波数応答を下の図に示します。

図 11. コンデンサの理想的な周波数応答

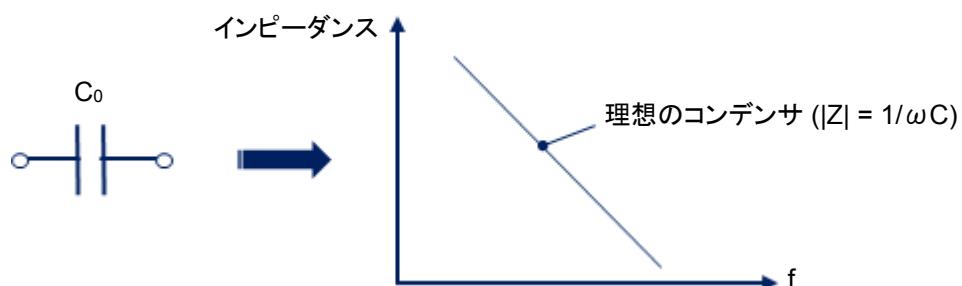

寄生効果に基づくコンデンサの実際の周波数応答を下の図に示します。

図 12. コンデンサの実際の周波数応答

高周波アプリケーション用のコンデンサは、必要な周波数挙動を維持するため、 $L_S$  と  $R_S$  を非常に小さくする必要があります。そうしないと、適切な設計が得られない可能性があります。RF アプリケーションでは、コンデンサを選択する前にその周波数応答を知ることが重要です。非常に良好なコンデンサの場合、寄生要素  $L_S$  と  $R_S$  を非常に小さくする必要があります。

注 コンデンサを SRF の近くに配置しないでください。

高周波アプリケーションでは、品質係数が高い(品質係数 =  $\text{Im}(Z)/\text{Re}(Z)$ )セラミック SMD コンデンサ・クラス I C0G/NOP が適しています。

### 3.2 RF インダクタ

インダクタは、磁界内にエネルギーを蓄積するために使用される受動電気コンポーネントです。インダクタごとに、構築技術と製造に使用される材料が異なります。

挿入損失を下げるために高い Q 係数が必要な高周波アプリケーションでは、通常、空芯インダクタの使用を推奨します。これらのインダクタでは、強磁性体でできた磁性コアではなく、プラスチックやセラミックなどの非磁性体にコイルを巻いたものを使用しています。

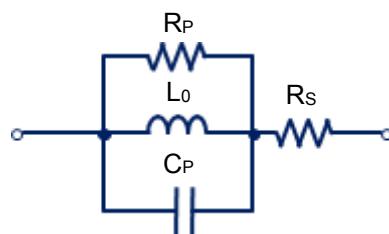

インダクタの等価回路を下に示します。

図 13. インダクタの等価回路

抵抗  $R_S$  は巻線と端子に起因する抵抗を表すもので、温度とともに増加します。抵抗  $R_P$  は磁気コア損失を表すもので、周波数、温度、電流によって変化します。コンデンサ  $C_P$  はインダクタの巻線による容量を表します。

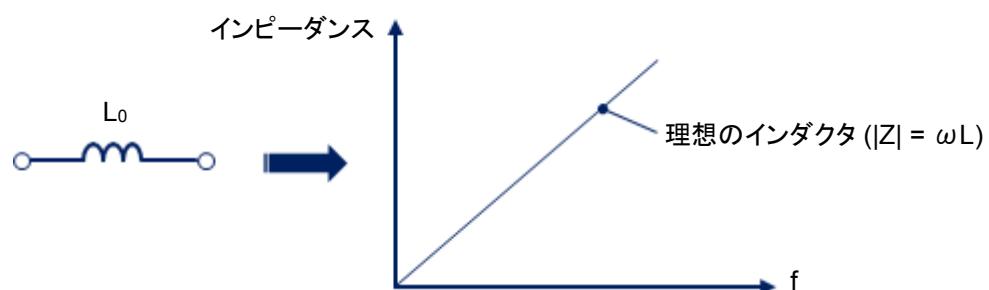

インダクタの理想的な周波数応答を下の図に示します。

図 14. インダクタの理想的な周波数応答

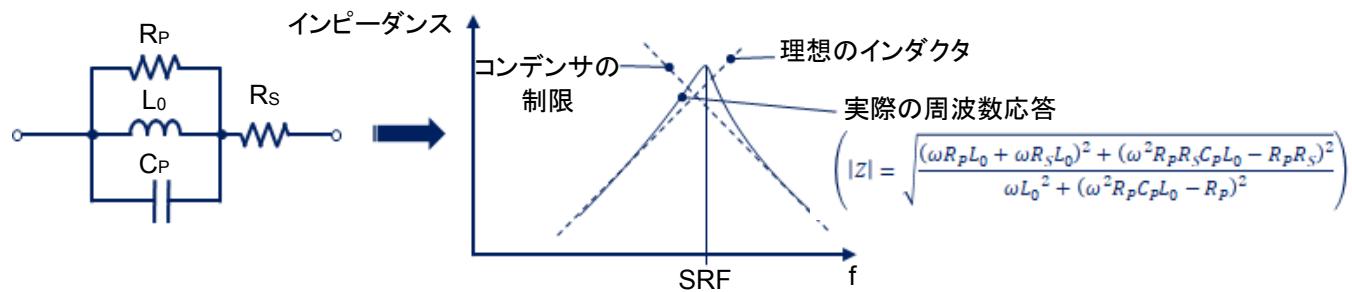

寄生効果に基づくインダクタの実際の周波数応答を下の図に示します。

図 15. インダクタの実際の周波数応答

非常に良好なインダクタの場合、寄生要素  $R_S$  と  $C_P$  を非常に小さくする必要があり、 $R_P$  を非常に大きくする必要があります。

注

インダクタを SRF の近くで使用しないでください。

高周波アプリケーションでは、巻線 SMD コアなしの Q 係数の高いインダクタが適しています。

## 4 STM32WL RF の説明

このセクションでは、Tx パス (RF 出力) と Rx パス (RF 入力) について説明します。RF 回路の各部の機能と、各部の構築方法について説明します。

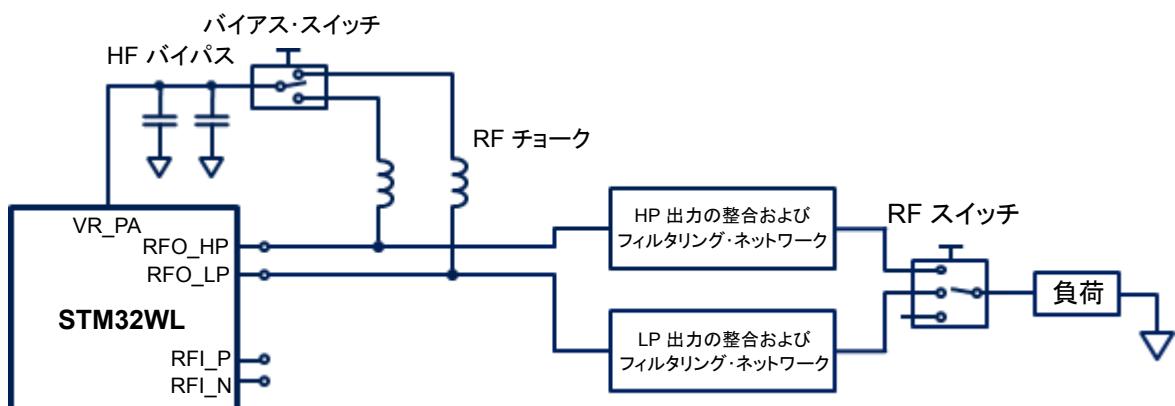

### 4.1 トランスマッタ

STM32WL トランスマッタは、次の 2 つの出力 (RFO) を備えた高効率 RF PA を内蔵しています。

- 最大 +22 dBm までプログラム可能な高出力の出力 (RFO\_HP)

- 最大 +15 dBm までプログラム可能な低出力の出力 (RFO\_LP)

アプリケーションでは、バイアス回路の DC スイッチを使用して、1 つの RF 出力 (RFO) を使用するか、両方の RFO を使用するかを選択できます。

注

一度に使用できるのは、1 つの RFO だけです。

1 つの RFO を使用する場合、下の図に示すように、必要な RF Tx 整合回路は 1 つです。RFO\_LP または RFO\_HP の設定用に整合ネットワークを選択する必要があります。

図 16. アプリケーションが 1 つの RF 出力用にのみ設計されている場合の RFO\_HP または RFO\_LP の選択例

RFO を 2 つ使用する場合、下の図に示すように RF Tx 整合回路が 2 つ必要です。

図 17. 2 つの RF 出力を使用するときに必要な整合ネットワークの例

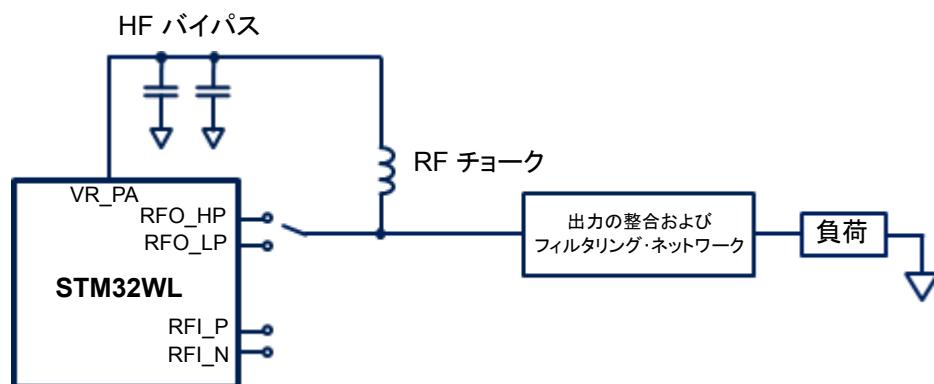

バイアス回路に 2 つの RF 出力を使用する場合は、スイッチがもう 1 つ必要です。このスイッチでは、一方の RFO パスを使用するときに、他方の RFO パスが干渉しないようにする必要があります。必要な電圧レベルと電流を VR\_PA ピン(調整済みのパワー・アンプの電源)から RF 回路に供給するために、RF チョークまたはバイアスフィード・インダクタは常に、使用中の RFO に接続されます。RF PA は、常に VR\_PA 接続から供給される必要があります。RF チョークの役割の 1 つは、RF ノイズがデバイス内部の DC 安定化 PA 電源(VR\_PA ピン)に侵入するのを防止することです。この RF チョーク・インピーダンスは十分に高くないため(理想的なコンポーネントではない)、一定量の RF ノイズがこのコンポーネントを通って VR\_PA 回路に侵入します。このリーケ・エネルギーを「吸収」するために、VR\_PA ピンと RF チョーク・インダクタの間に高周波(HF)バイパス・コンデンサが追加されます。

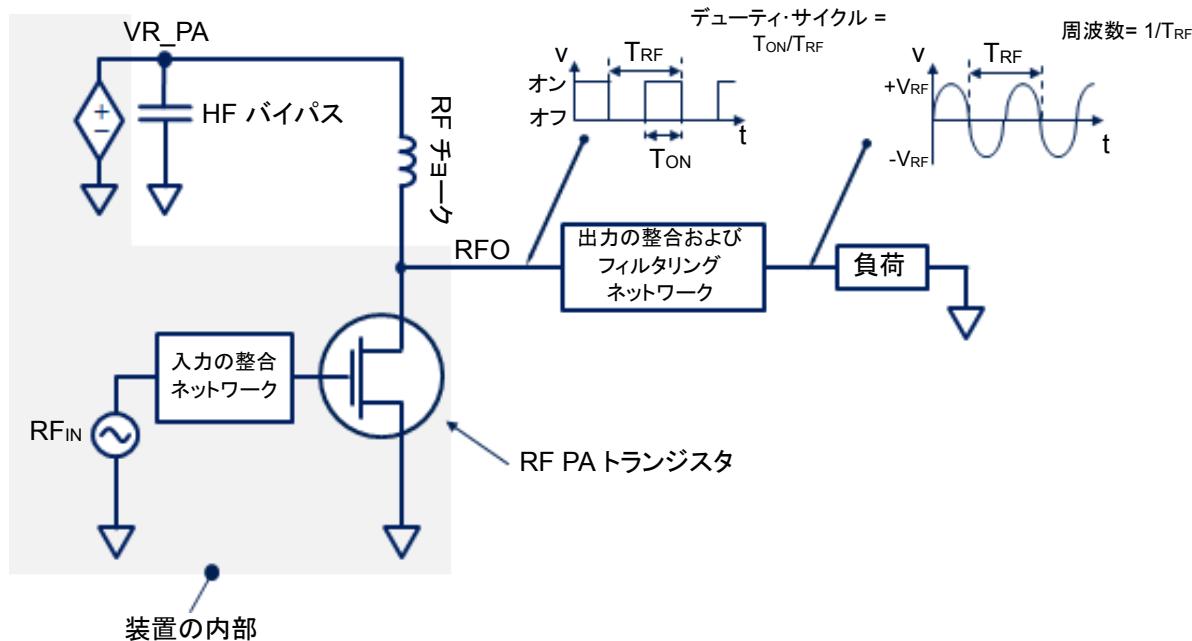

デバイス内部の RF PA は、CMOS 技術を使用して構成されます。パワー・アンプは、真のアンプというよりは、電源コンバータのように動作します。PA MOS トランジスタはスイッチとして使用されるため、その出力は、アンプ制御回路によって生成された入力制御信号に応じて、V<sub>DD</sub>(オン状態)または GND(オフ状態)に接続されます。PA 出力は PWM 高周波電圧信号で、その基本周波数はユーザが求める RF 正弦波形です。

下の図に、この動作を示します。

図 18. デバイス内部の RF PA の概要(出力波形付き)

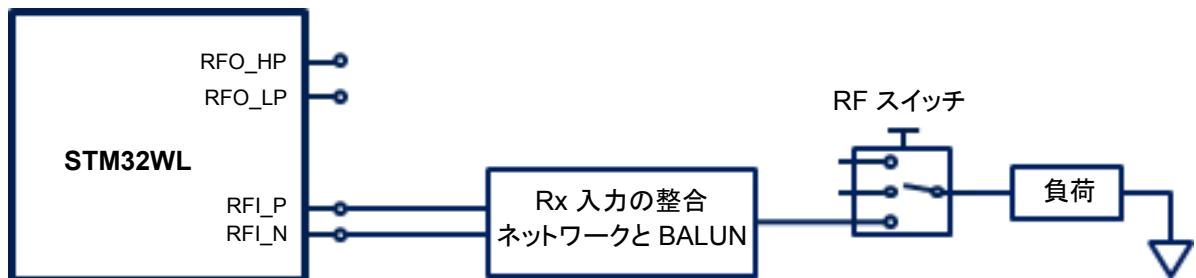

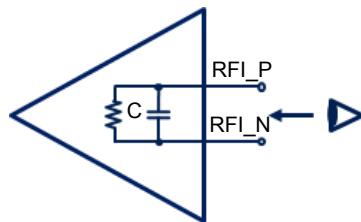

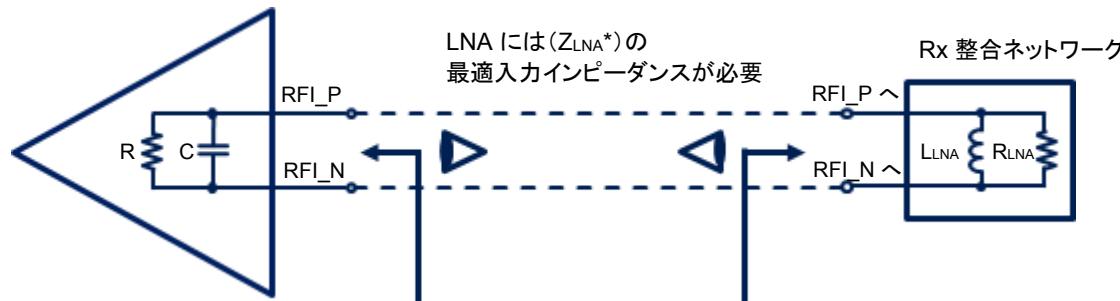

## 4.2 レシーバ

STM32WL レシーバは、LoRa、(G)MSK、および (G)FSK 変調に対応する高性能差動 LNA (Low-noise amplifier: ローノイズ・アンプ)を内蔵しています。このレシーバの差動入力(RFI\_P および RFI\_N)は、0 dBm の最大 RF 電力、最小 -148 dBm の感度に対応します(詳細については、製品データシートを参照)。

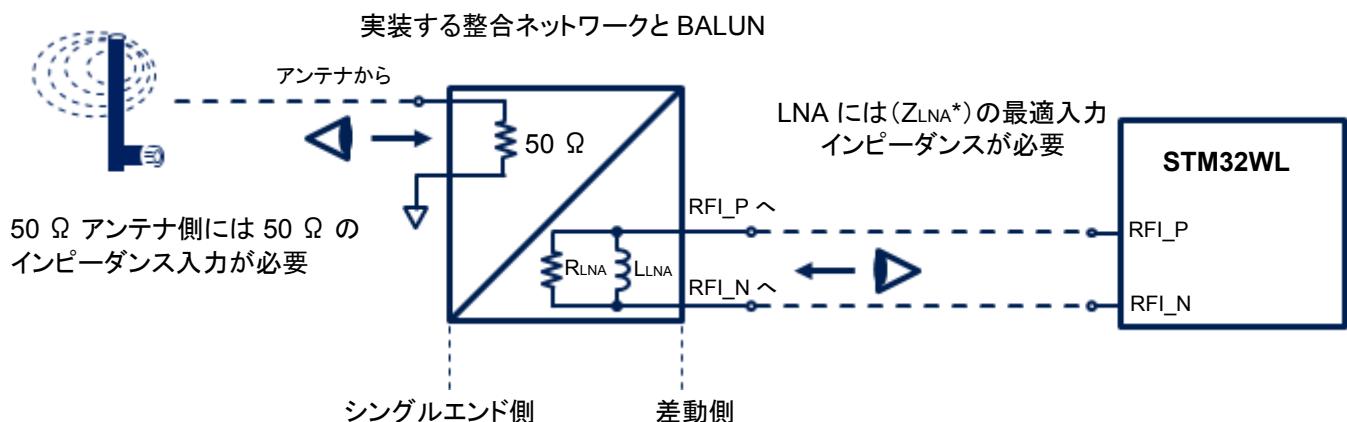

LNA の高入力インピーダンスとアンテナ側の 50 Ω 回路の間のインターフェースは、整合ネットワーク回路によって実行され、さらに、シングルエンド入力を差動出力に変換する必要があります。シングルエンド(GND を基準)回路は不平衡回路とも呼ばれ、差動回路は平衡回路とも呼ばれます。平衡回路を不平衡回路に変換する回路を BALUN と呼びます。そのため、Rx 整合ネットワークは BALUN の役割も果たします。

図 19. 負荷のある Rx 回路の図

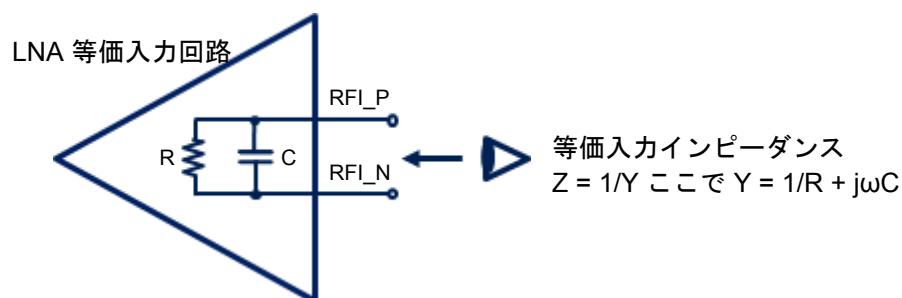

LNA の入力等価回路を次の図に示します。

図 20. レシーバの入力等価回路

このドキュメントで説明されている Rx 整合ネットワークと BALUN は、下の図に示した特性を備えています。

図 21. 集中コンポーネントにより PCB に実装される整合ネットワークと BALUN の特性

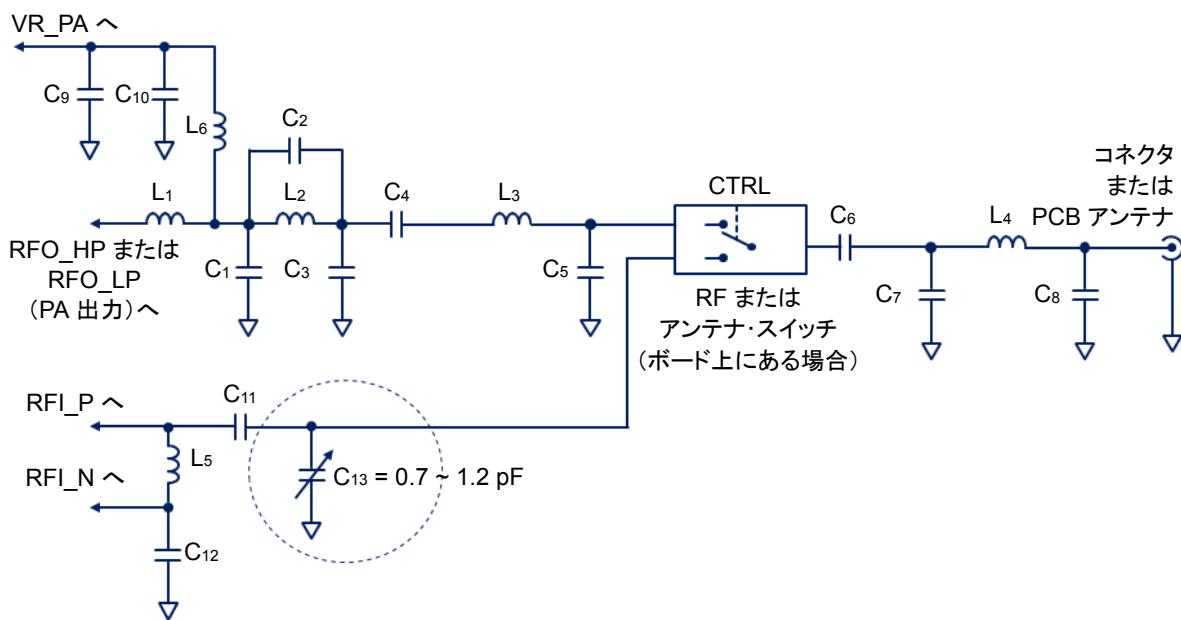

## 5 STM32WL 整合/フィルタ・ネットワーク

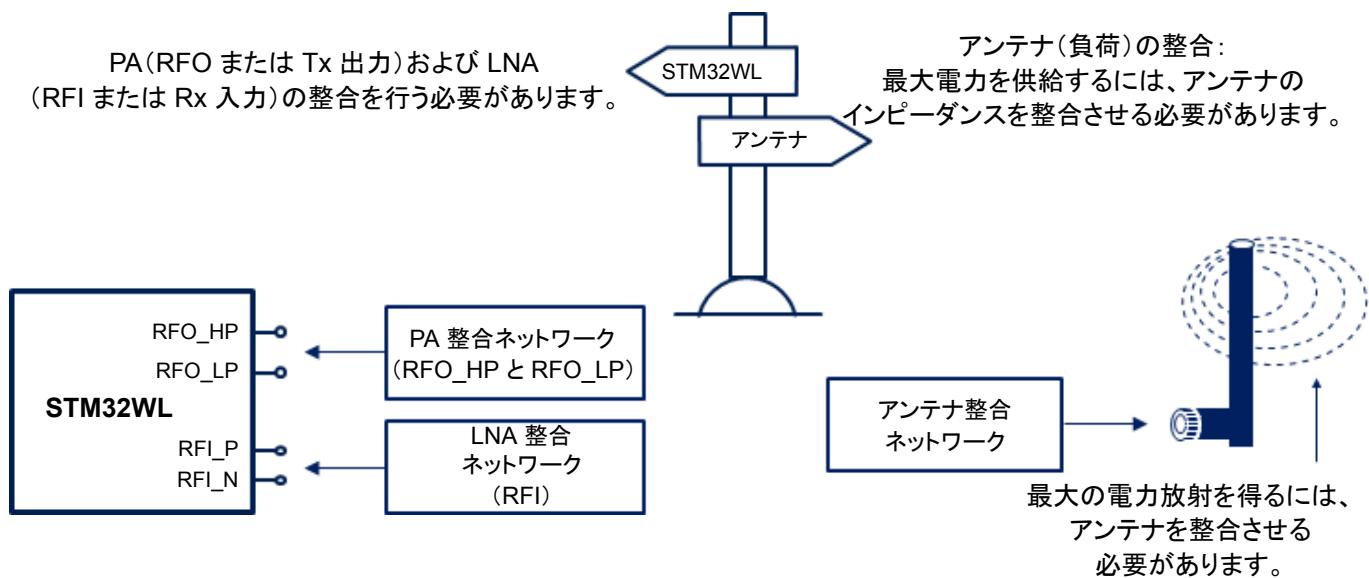

STM32WL は半二重モードで動作し、より良い RF 性能を得るために、RF スイッチを使用して Tx パスと Rx パスを分離します。RF スイッチには、1 つの RFO(トランスマッタ出力)または RFI(レシーバ入力)を切り替える 2 つのポート、または RFO\_HP(高電力)と RFO\_LP(低電力)または RFI の両方を切り替える 3 つのポートを装備することができます。

2 つの異なるインピーダンス整合ネットワーク(電気工学では、「ネットワーク」は「回路」の意味でよく使用されます)が必要になることがあります。そのうちの 1 つは STM32WL PA および LNA 用のインピーダンス整合ネットワークに対応します。別のインピーダンス整合ネットワークがアンテナに対応します。アンテナ・インピーダンス整合ネットワークは、選択したアンテナ・インピーダンスに応じて、お客様が管理する必要があります。このドキュメントでは、RFO(PA 出力)および RFI(LNA 差動入力)の整合ネットワークの構築方法について説明します。同じ原理を使用して、選択したアンテナのインピーダンス整合を行うことができます。

図 22. 実装が可能な 2 つの整合ネットワークの図

## 5.1 パワー・アンプ・ネットワーク

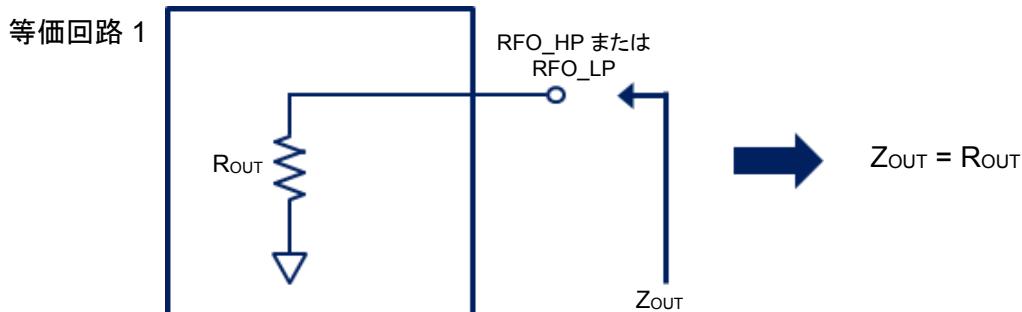

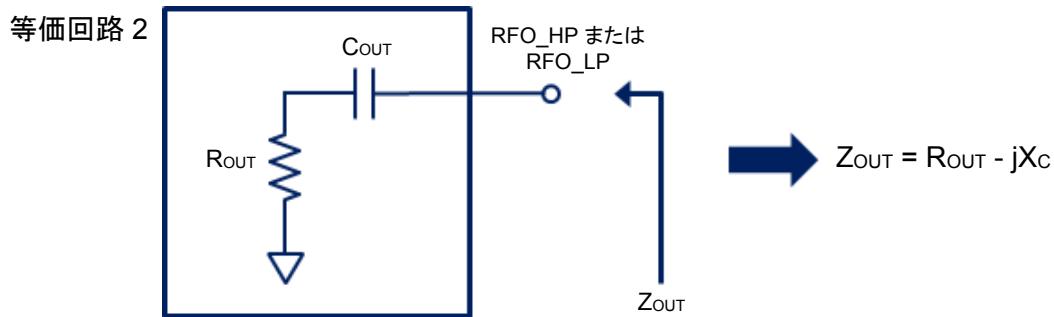

### 5.1.1 出力等価回路

PA 出力インピーダンスを表すには、2 種類の等価回路があります。下の図は、これら 2 種類の出力等価回路を表しています。適切な整合ネットワークを構築するには、PA の出力等価回路が必要です。

図 23. インピーダンスが純粋な抵抗である場合の PA 出力等価回路

図 24. インピーダンスが容量性リアクタンスを持つ抵抗である場合の PA 出力等価回路

PA の出力等価回路は、[付録 A](#) に示す出力インピーダンス測定値から求めることができます。

注 PA の出力インピーダンスは、動作周波数、電力、および `Set_PaConfig()` コマンドにより渡される `PaDutyCycle`、`HpMax`、`PaSel` パラメータに依存します。

### 5.1.2 最適な設定

最大出力電力が公称電力値(+22 dBm(RFO\_HP 使用時)または+14 dBm(RFO\_LP 使用時))と異なる場合に PA (Power amplifier: パワー・アンプ) の効率を最大化する RF PA の設定がいくつかあります。消費電力への影響の詳細は、製品データシートに記載されています。

その場合、これらの最適な設定のメリットを得るには、次の手順に従います。

1. フームウェア: 下の表に記載されている RF PA 設定を適用します。

2. ハードウェア: 選択した最適な設定に対応する RF PA 設定を持つ専用の RF 整合ネットワークを決定します。

これは、RF PA 出力インピーダンスの値は RF PA の設定によって変化するためです。

RF 整合ネットワークを特定の最適な設定にするには、[セクション 5.1](#) の手順に従います。

たとえば、アプリケーションで必要な最大 RF 出力電力が+10 dBm または+17 dBm の場合、次のようにになります。

- RF PA の効率を高めるために適用する最適な設定(消費電流の低減)

- 専用の RF 整合ネットワーク

表 2. RF PA の最適な設定

| モード             | 出力電力(dBm) | Set_PaConfig() |       |           |       | SetTxParams 値(dBm) |

|-----------------|-----------|----------------|-------|-----------|-------|--------------------|

|                 |           | paDutyCycle    | hpMax | deviceSel | paLut |                    |

| 低電力<br>(RFO_LP) | +15       | 0x06           | 0x00  | 0x01      |       | +14                |

|                 | +14       | 0x04           |       |           |       | +14                |

|                 | +10       | 0x01           |       |           |       | +13                |

| 高電力<br>(RFO_HP) | +22       | 0x04           | 0x07  | 0x00      | 0x01  | +22                |

|                 | +20       | 0x03           | 0x05  |           |       |                    |

|                 | +17       | 0x02           | 0x03  |           |       |                    |

|                 | +14       |                | 0x02  |           |       | +14                |

### 注意

デバイスに致命的な損傷を与える可能性のある最大定格の超過が発生しないようにするには、RF PA への過大なストレスを防止するためのいくつかの制限に従う必要があります。

- 低電力モード

- 400 MHz を超える周波数では、`PaDutyCycle` が 0x07 を超えてはなりません。

- 400 MHz 未満の周波数では、`PaDutyCycle` が 0x04 を超えてはなりません。

- 高電力モード:

- 任意の周波数に対して、`PaDutyCycle` が 0x04 を超えてはなりません。

注 指定された最適な設定に対して異なる電力値を使用すると、この値は最適でなくなるか、達成できなくなります。

このアプリケーション・ノートで報告されているインピーダンス値は、RF PA の最適な設定により測定されたものです。ユーザ・アプリケーション用のインピーダンス値が示されていない場合は、ST の営業所にお問い合わせください。

### 5.1.3 標準的な Tx アプリケーション・ネットワーク

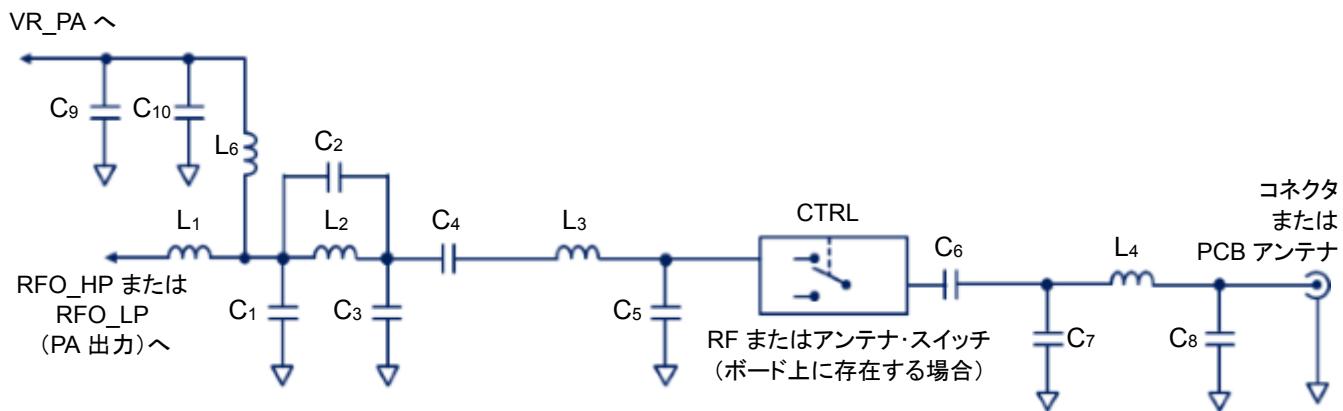

標準的な Tx 整合/フィルタのアプリケーション・ネットワークを下の図に示します。整合する PA 出力インピーダンスは、周波数と電力によって決ります。そして、各電源および周波数設定に対して、高効率が必要な場合(より高い電力でより低い消費電流)は異なる BOM があります。

図 25. 標準的な Tx アプリケーション・ネットワーク

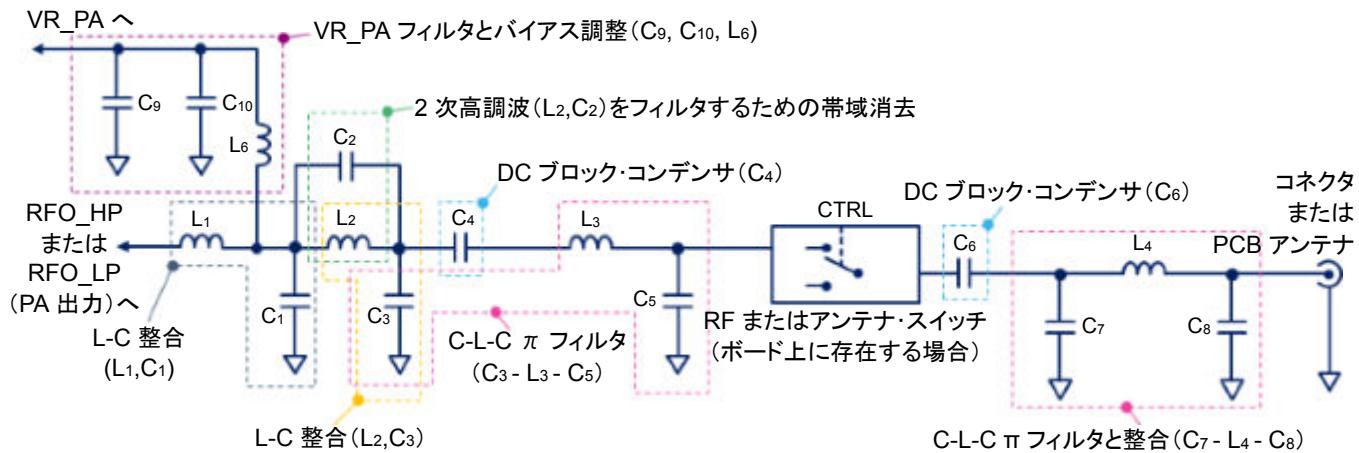

標準的な Tx アプリケーション・ネットワークの各機能を下の図に示します。使用する RF スイッチのリファレンスは、Infineon SP3T BGS13SN8 および SPDT Infineon BGS12SN6 です。

図 26. 標準的な Tx アプリケーション・ネットワークの各部の説明

注 一部の RF スイッチでは、入力および出力で DC 電流をブロックするために DC ブロック・コンデンサ(直列ローインピーダンス・コンデンサ)が必要です(スイッチのデータシートを参照)。

## 5.1.4

## VR\_PA のバイアス調整とフィルタリング

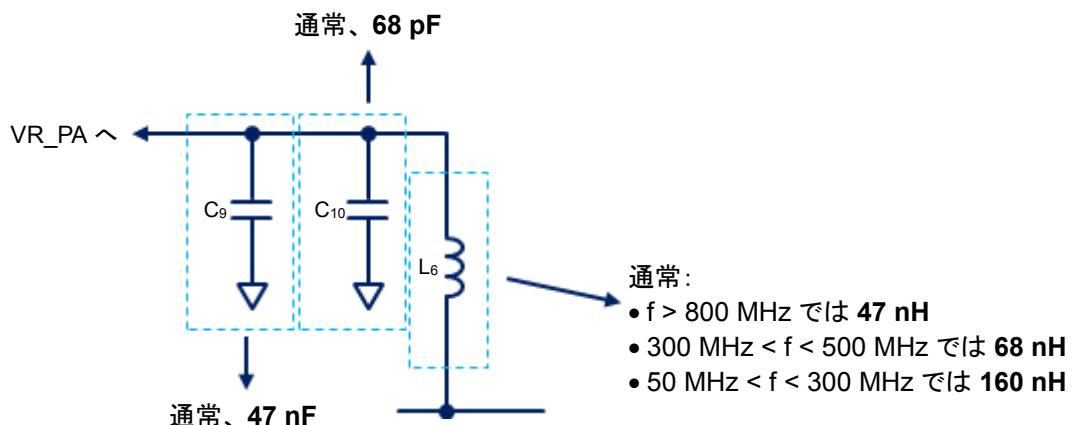

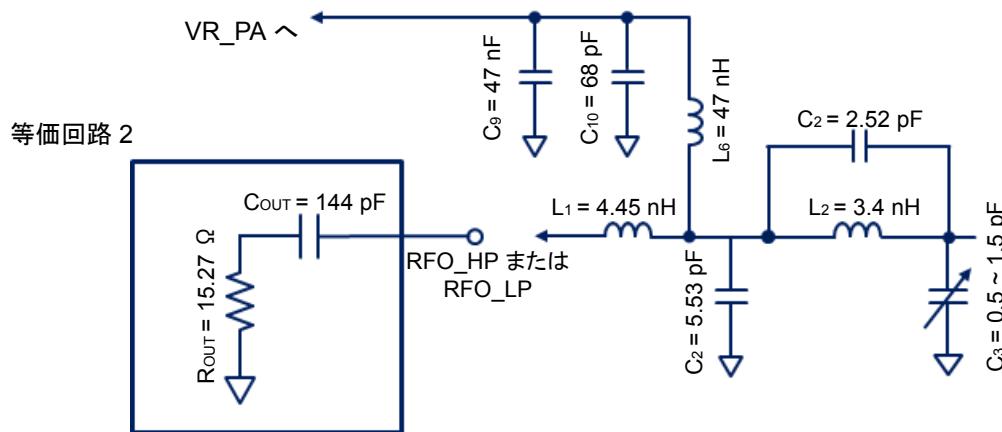

RF アンプでは、RF 信号がデバイスを通過し、DC 電源に戻らないことを保証するために、ハイインピーダンス・コンポーネントが使用されます。このために、RF チョーク(RFC)が使用されます(バイアス・インダクタまたは DC フィードとも呼ばれます)。RFC は、RF 信号に対してはハイインピーダンス(入力整合インピーダンスの最大 10 倍)のコンポーネントであり、DC に対してはローインピーダンスのコンポーネントであることが理想的です。この「ハイインピーダンス」は完全ではなく、RF リークの一部が電源に戻る可能性があります。これが、このリーク・エネルギーを「吸収」するためにコンデンサが追加される理由です。RFC は下の図では L6 によって表され、HF バイパス・コンデンサは C9 と C10 によって表されます。

- コンデンサ C9 は通常、47 nF (Murata GCM155R71E473KA55)。

- コンデンサ C10 は通常、68 pF (Murata GCM1555C1H680JA16)。

- 通常、RFC(RF チョークまたは DC バイアス・インダクタ)は次のとおりです。

- 800 MHz を超える周波数では 47 nH(Murata LQW15AN47NG00)

- 300 MHz ~ 500 MHz の周波数では 68 nH(Murata LQW15AN68NG00)

- 150 MHz ~ 300 MHz の周波数では 160 nH(Murata LQW18CAR16J0)

- 損失を低減するために、RFC では高い Q 係数が必要です。ESR(等価直列抵抗)が低い RFC では、ESR での電圧降下のために RF 出力電力が低下します。

図 27. VR\_PA 標準アプリケーション回路

## 5.1.5

## PA 出力整合

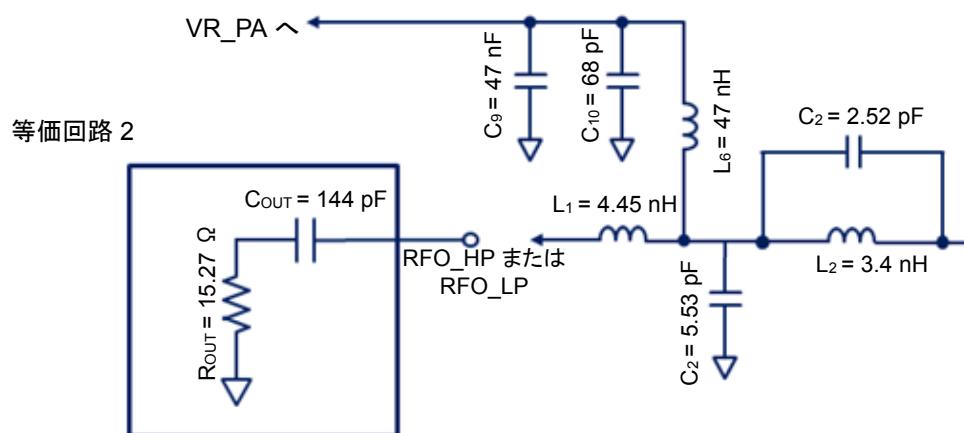

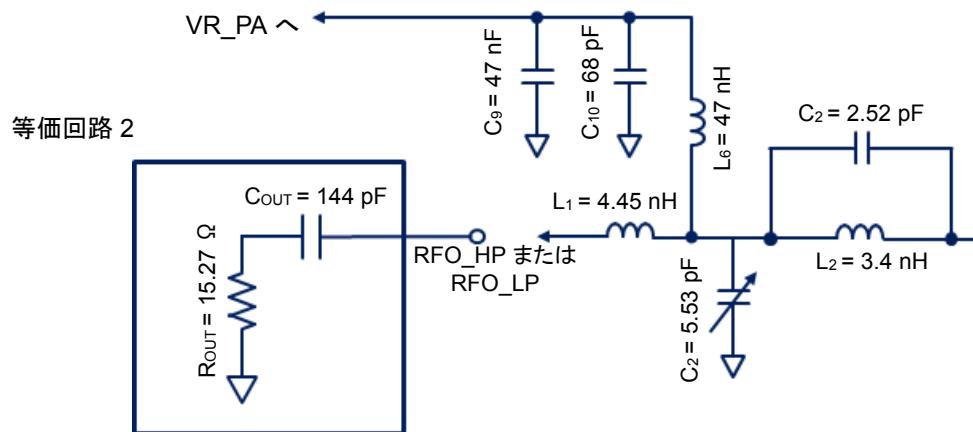

PA 整合ネットワークの方法論は、ロードプル解析によって測定されたインピーダンスを考慮した例に基づいています(セクション 付録 A.1.7 例 7(UFQFPN48、14 dBm、868 MHz) で報告)。

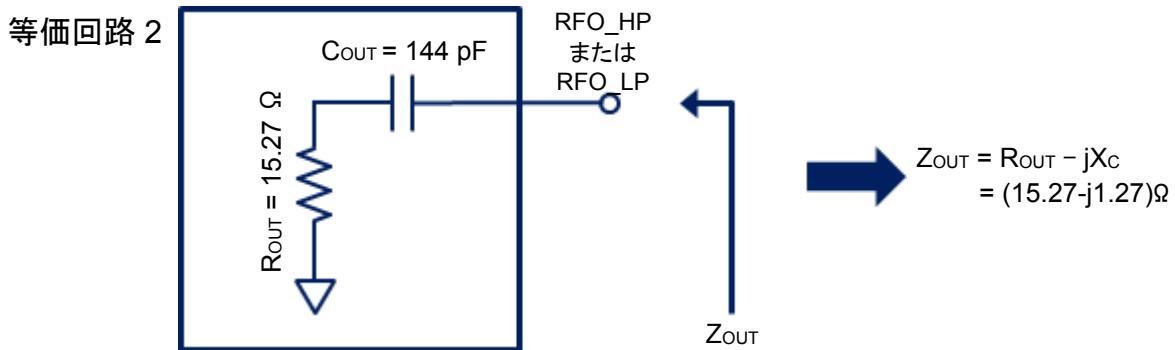

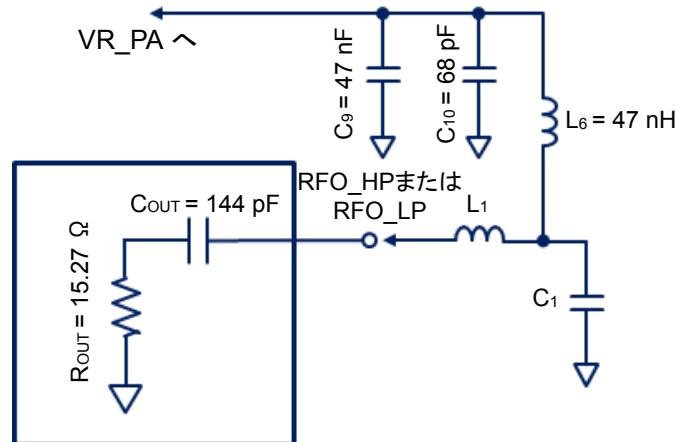

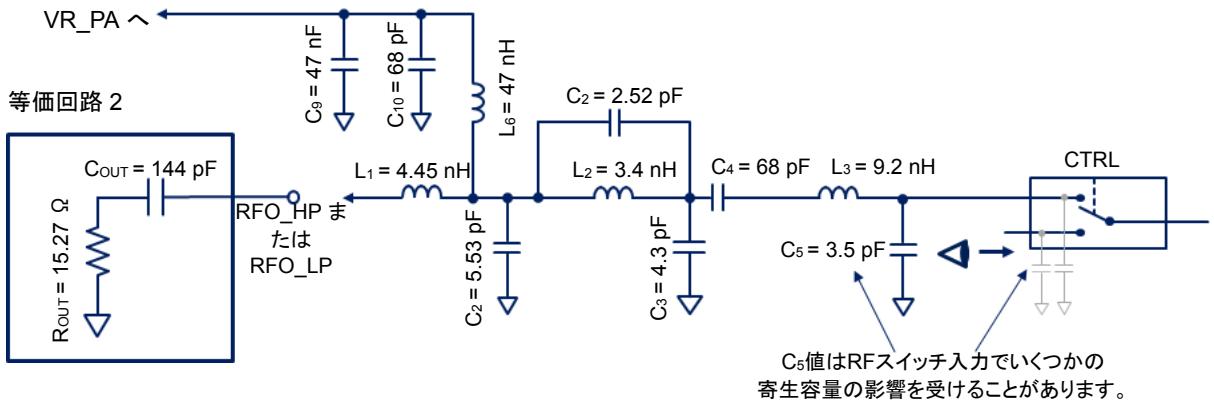

最初の L-C セル(L1, C1)は、PA の最適なインピーダンス(最小の消費電流で必要な出力電力が得られるインピーダンス)の整合に使用されます。14 dBm @ 868 MHz について抽出した以下の結果から、最適なインピーダンス(ポイント 1)は約  $(15.27 + j1.27) \Omega$  です。このインピーダンスに対応する測定電力は 14 dBm です(RF ケーブル、コネクタ、およびチューナの損失のため、付録 A で説明しているように + 0.5 dB を追加します)。

14 dBm を得るために PA 出力に与えられるインピーダンスが  $(15.27 + j1.27) \Omega$  である場合、その出力インピーダンスはこの値の複素共役の値となります。そのため、PA の出力インピーダンスは  $(15.27 - j1.27) \Omega$  であり、前に示した  $R_{OUT} = 15.27 \Omega$  と以下の値を持つ等価回路 2 に対応します。

$$C_{OUT} = \frac{1}{2\pi \times 868 \text{ MHz} \times 1.27} = 144 \text{ pF}$$

図 28. UFQFPN48、14 dBm、868 MHz の出力等価回路

この出力等価回路は、次のように L-C セル ( $L_1, C_1$ ) と整合します。

図 29. 最初の LC 整合ネットワーク・セルの配置

注

以下に示すすべての計算式をスキップするため、インターネットで入手可能な無料のスミス・チャート・ツールがいくつか利用できます([www.ae6ty.com](http://www.ae6ty.com) の SimSmith、[www.fritz.dellspurger.net](http://www.fritz.dellspurger.net) の Smith、[will-kelsey.com/smith\\_chart/](http://will-kelsey.com/smith_chart/) の Online Smith Chart Tool など)。これらのツールからは、下の式で計算するのと同じ値が得られます。

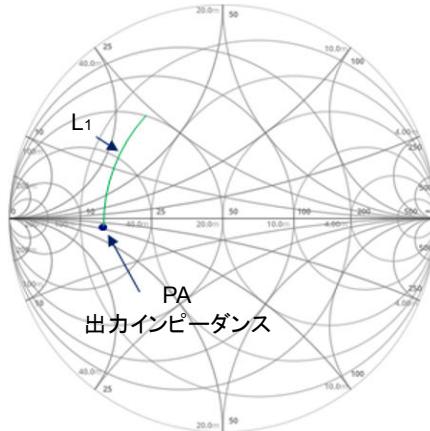

$L_1$  と  $C_1$  の理論値は、次のように計算されます。

1.  $m$  を計算します。

$$m = \sqrt{\frac{50}{R_{out}} - 1} = \sqrt{\frac{50}{15.27} - 1} = 1.508$$

2. 整合インダクタ  $L_1$  の値を計算します。

$$L1 = \frac{1}{2\pi f} \times \left( \frac{50m}{m^2 + 1} + X_C \right)$$

$$\Rightarrow L1 = \frac{1}{2\pi \times 868MHz} \times \left( \frac{50 \times 1.508}{1.508^2 + 1} + 1.27 \right) = 4.45 \text{ nH}$$

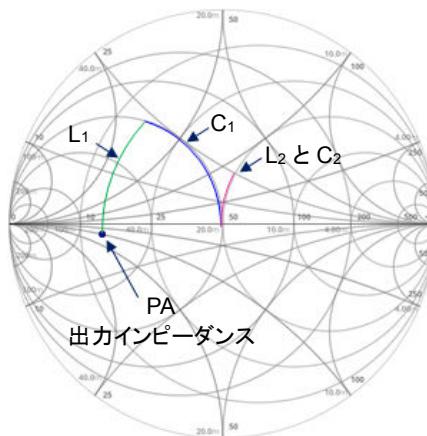

スミス・チャート上の結果を下の図に示します。

図 30. L1 を使用して RF PA の無効部分に整合し、20 ms の円に到達

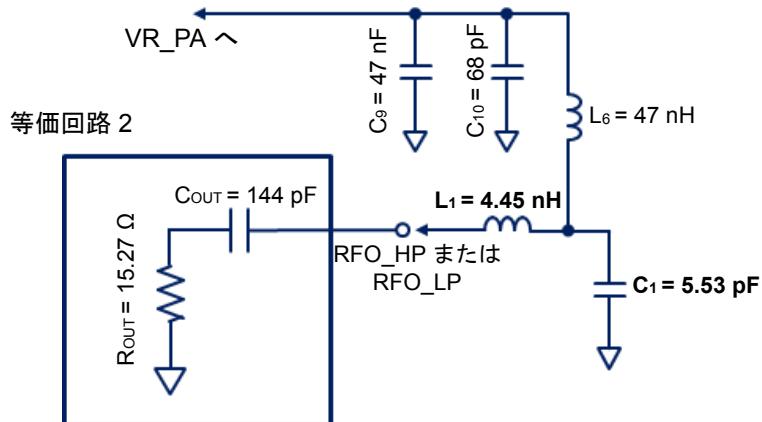

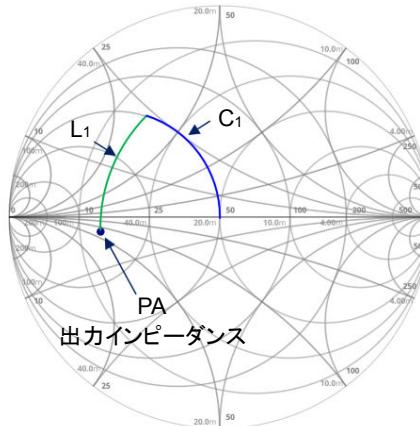

3. 整合コンデンサ  $C_1$ (次の式のモジュール)の値を求めます。

$$C_1 = \left| \frac{1}{2\pi f} \times \frac{\sqrt{\frac{R_{out}}{50} (1 + m^2)} - 1 + m}{R_{out} (1 + m^2)} \right|$$

$$\Rightarrow C_1 = \left| \frac{1}{2\pi \times 868MHz} \times \frac{\sqrt{\frac{15.27}{50} (1 + 1.508^2)} - 1 + 1.508}{15.27 (1 + 1.508^2)} \right| = 5.53 \text{ pF}$$

これらの値を持つネットワークは次のようにになります。

図 31. 計算値を持つ最初の LC 整合セル

スミス・チャート上の結果を下の図に示します。

図 32. 最初の LC 整合セルを追加するスミス・チャート上の図

4. 出力電力を測定して、PCB に実装されたこの L-C が必要な L-C 整合に対応するかどうかを確認します。PCB がこれらの値に大きな影響を与える可能性があることに注意してください。出力電力が期待値から離れている場合は、L1 と C1 の値を調整して、出力電力にどう影響するかを確認します。ユーザ固有の PCB に対しては、これらの値の調整が必要な場合があります。

注

- コンポーネントの値は、直近の既存の SMD 値に切り上げる必要があります。

- 一部の周波数、出力電力設定、PCB では、最初の L-C 整合セルを L2 と C3 で直接実装し、L1 と C1 を未入力のままにすることができます。適用方法は同じです。

## 5.1.6 PA 出力のフィルタリング

RF PA は常に非線形システムであり、入力 RF 信号の非線形歪みや出力信号の高調波成分に起因する不要波信号が発生します。RF PA において、フィルタの主な目的は、目的の周波数から不要波および高調波成分を除去することです。

フィルタ前後の RF スペクトルの出力電力は、図 3 のようになります。.

フィルタ・ステージを実装すると、下の図のような結果になると考えられます。

図 33. 高調波および寄生放射が制御された出力スペクトルの例

## ノッチ・フィルタ値の算出

- 2次高調波(H2)を除去するためのノッチ・フィルタ・コンポーネント(L2、C2)の値を計算します。

$$H2 = 868 \text{ MHz} \times 2 = 1.736 \text{ GHz} \quad \text{and} \quad 2\pi \times H2 = \frac{1}{\sqrt{L2 \times C2}}$$

原則として、L2 は  $L1 = 3.34 \text{ nH}$  の  $3/4$  として選択されます。

$$C2 = \frac{1}{(2\pi \times H2)^2 \times L2} = \frac{1}{(2\pi \times 1.736)^2 \times 3.34} = 2.52 \text{ pF}$$

これらの値を持つネットワークは次のようになります。

図 34. 前の例の算出後のノッチ・フィルタ値を適用したネットワーク

スミス・チャート上の結果を下の図に示します。

図 35. ノッチ・フィルタ・コンポーネントを追加したときのインピーダンス変化をスミス・チャート上に示した図

このポイントで出力電力を測定し、この値を保持します。以下で説明するように、H2 除去を測定し、ノッチ・フィルタの微調整を試みます。

注 PCB の寄生効果により、ユーザはノッチ・フィルタ値の調整が必要となることがあります。たとえば、PCB に関する前の例を挙げると、ノッチ・フィルタの実際の実装では  $3.4 \text{ nH}$  と  $2.0 \text{ pF}$  の値を持つことができます ( $3.4 \text{ nH}$  と  $2.5 \text{ pF}$  の代わりに)。

2. コンデンサ  $C_1$  の値を  $0.3 \text{ pF}$  刻みでわずかに増加させて、ノッチ・フィルタによって発生した不一致を補正し、出力電力への影響を確認します。また、この値を減らして、出力電力への影響を確認します。これで正しい結果が得られない場合は、次の手順を参照してください。

図 36. ノッチ・フィルタによって発生した不一致を補正するための  $C_2$  の値の調整

注 PCB 上に実装すべき実際の値を得るために、同じ手順を  $L_1$  の値に対して実行できます ( $\pm 0.2 \text{ nH}$  から)。

3. 前の手順で期待される結果が得られない場合は初期値に戻り、ノッチ・フィルタの後に  $0.5 \text{ pF} \sim 1.5 \text{ pF}$  の値で並列コンデンサ ( $C_3$ ) を配置して、出力電力と H2 除去への影響を確認します。

図 37. コンデンサ  $C_3$  を追加することで、ノッチ・フィルタによって発生した不一致を低減

注 PA 出力インピーダンスが純粋な抵抗である場合(等価回路 1)、同じ手順を使用できます。上の式では値  $X_C$  はゼロに等しくなります。

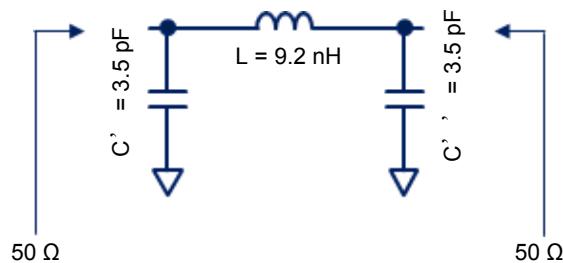

### ローパス・フィルタの実装方法

この高調波フィルタ(H3、H4、H5などの場合)は、π ラダー・ネットワーク(T型ラダーよりもインダクタの数が少ない)を使用して実装されます。ローパス・フィルタの応答はチェビシェフ型です。阻止帯域のロールオフの優れた H1 で 0 をセットできます。

1. 次のパラメトリック方程式を使用して、ローパス・フィルタの値を算出します。

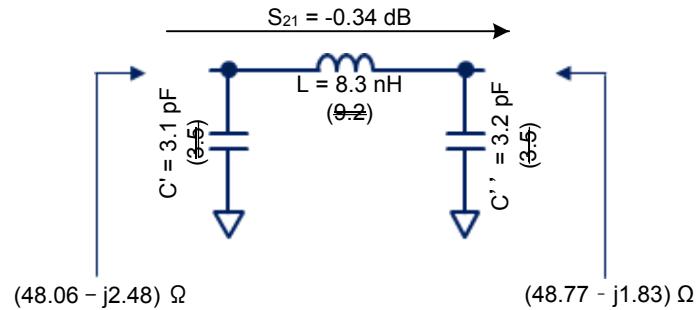

$$L = \frac{50}{2\pi f} \text{ and } C' = C'' = \frac{0.95}{50 \times 2\pi f}$$

14 dBm@868 MHz という前の整合ネットワークの例の値では、フィルタ値は次のようにになります。

$$L = \frac{50}{2\pi \times 868} = 9.2 \text{ nH} \text{ and } C' = C'' = \frac{0.95}{50 \times 2\pi \times 868} = 3.5 \text{ pF}$$

図 38. 入出力インピーダンスが 50 Ω のローパス Pi フィルタ

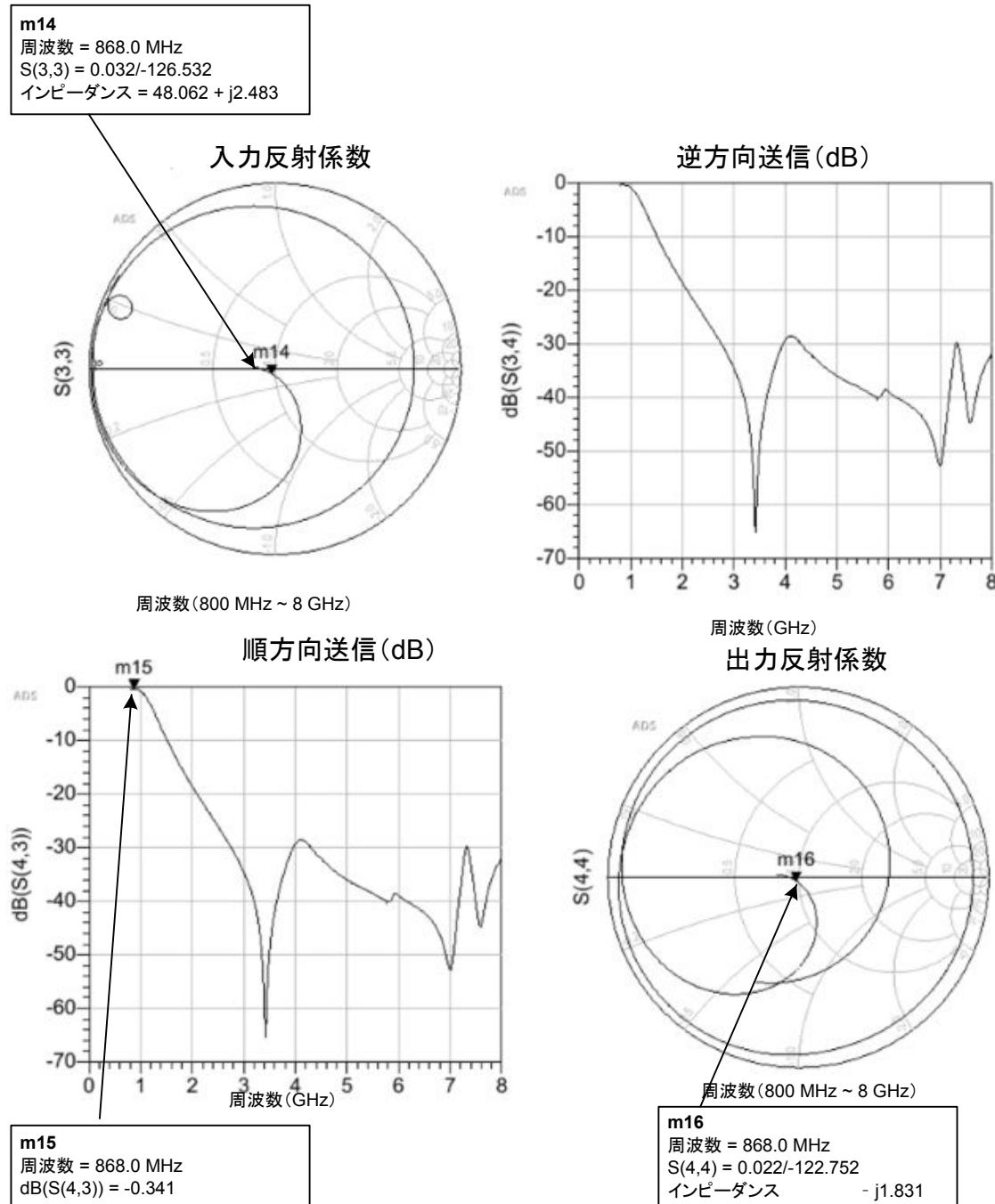

これらの値でのシミュレーションを以下に示します。黒で示す(ポート 1 および 2)のは理想のコンポーネント、赤で示す(ポート 3 および 4)のは実際のコンポーネントの S パラメータです。

図 39. 理想(黒)と実際のコンポーネントの S パラメータ(赤)の S パラメータと周波数のローパス Pi フィルタのシミュレーション

注

868 MHz ではインピーダンスはチャートの中央にあり、実際のコンポーネントの S パラメータを使ったシミュレーションの順方向送信係数は -0.1 dB です。

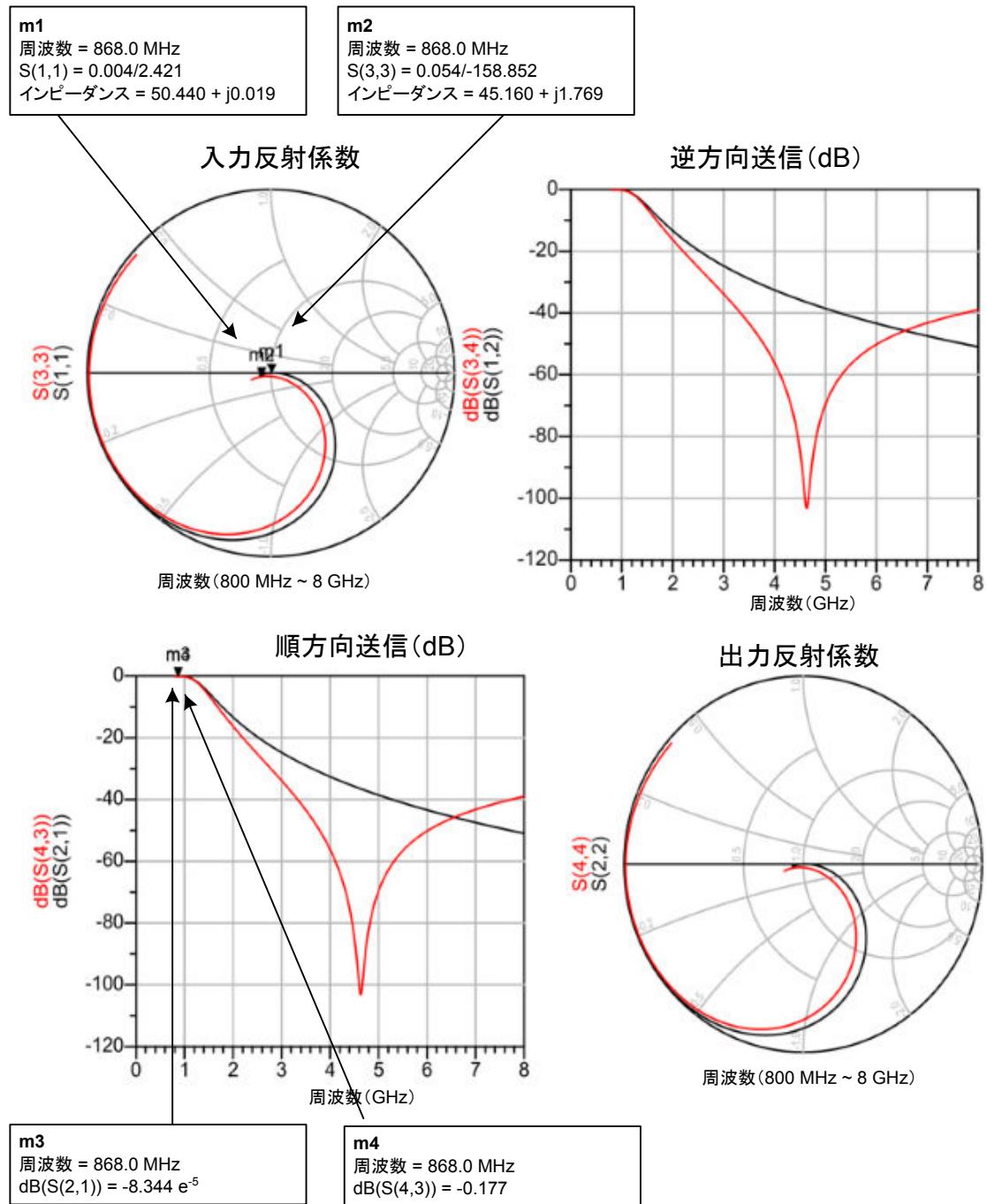

同じフィルタを PCB に実装すると、次の結果が得られます。

図 40. PCB への実装のためのローパス Pi フィルタの S パラメータと周波数

入力反射係数はチャートの中央ではありません。これは、PCB によって発生する寄生効果と、実際の集中コンポーネントの効果によるものです。このような場合、ユーザは一方のコンデンサや他方のコンデンサの値をわずかに変更して、高調波除去と出力電力への影響を確認できます。

コンデンサとインダクタの値を調整して PCB への影響を考慮すると、結果は次のようにになります。

図 41. 揿入損失付きのローパス Pi フィルタ(S21)の計算値(括弧内)と実装値との関係を示す例

図 42. コンポーネント値の調整後の PCB への実装のためのローパス Pi フィルタの S パラメータと周波数

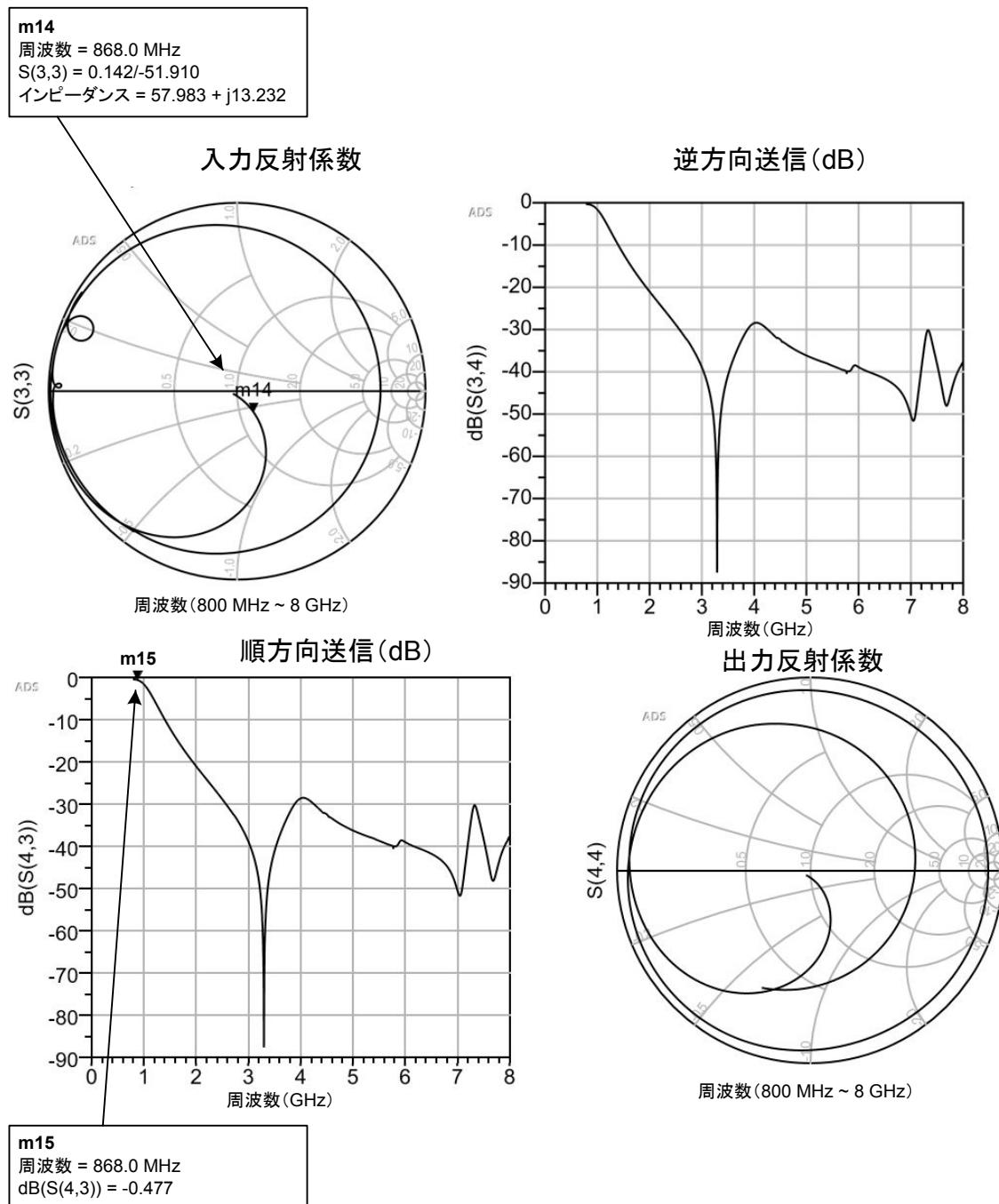

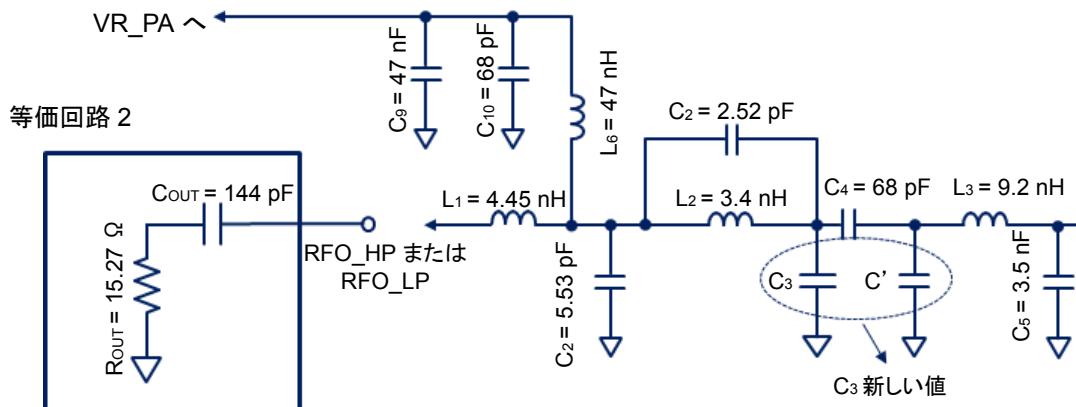

2. C3 の追加容量を Pi フィルタと組み合わせます。

ノッチ・フィルタによって発生したインピーダンスへの影響を補正するためにコンデンサ C3 が追加された場合(ノッチ・フィルタ値の算出の最後を参照)、C3 はローパス・フィルタのコンデンサと組み合わせる必要があります。

$$C3 \text{ new value} = C' + C3$$

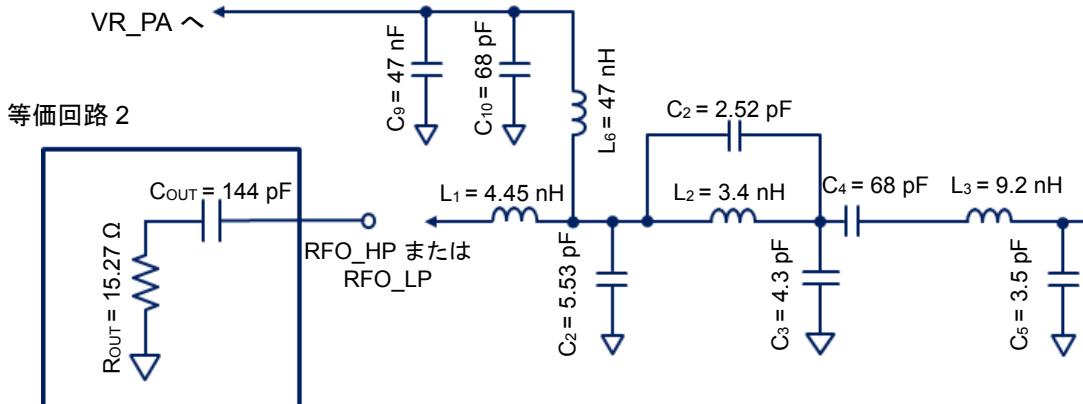

図 43. ローパス Pi フィルタの追加後のネットワーク内での並列コンデンサの再結合

たとえば、 $C3 = 0.8 \text{ pF}$  で  $C' = 3.5 \text{ pF}$  の場合、新しい  $C3$  の値は  $4.3 \text{ pF}$  になります。

完全なネットワークは次の図のようになります。

図 44. ネットワークで再結合される並列コンデンサ

注

一部の RF スイッチには、 $C5$  の値で考慮する必要がある一種の寄生入力容量があります。たとえば、正しい出力電力を得るために  $C5$  の値を数 pF 下げる必要がある場合もあります。この仮説を確認するには、スイッチありなしでテストを行い、出力電力値への影響をチェックします(下の図を参照)。

図 45. スイッチの寄生入力容量を組み込むために、場合によっては C5 の値の変更が必要

アプリケーションで高電力 RF 出力 (RFO\_HP) を使用する場合、高調波放出レベルを低減するために、RF スイッチとアンテナの間に別のフィルタが必要になることがあります。このような場合は、ローパス・フィルタの実装方法に記載した手順を実行してください。.

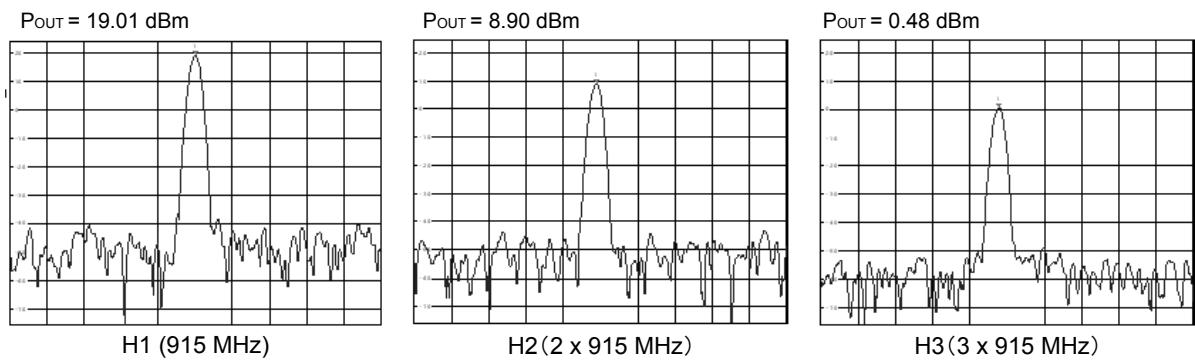

### 5.1.7 基本周波数の電力と高調波レベル

高調波周波数の電力レベルは、基本周波数の出力電力と消費電流に影響します。高調波レベルを下げるることによって、基本周波数の電力を上げて、消費電流を(場合によってはわずかに)下げることができます。2 次 (H2) および 3 次 (H3) レベルの高調波は、基本周波数の出力電力に重大な影響を与える可能性があります。

H2 と H3 の電力レベルは、これらの高調波に関連する反射係数のモジュールと位相に依存します。次の図に例として示すのは、L-C 整合セルなしでスペクトル・アナライザを使用してキャプチャしたものです。

図 46. L-C 整合セルなしの H1、H2、および H3 の出力電力(伝導モード)の値

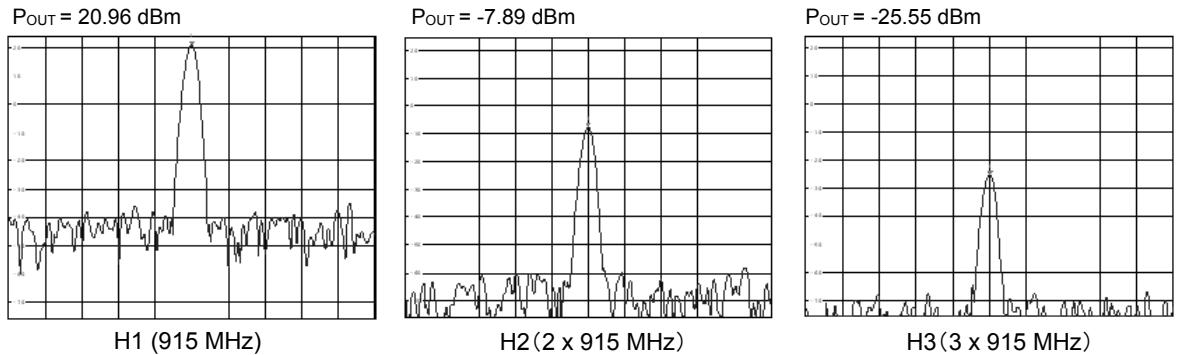

同じ測定を行い、L-C セルに整合させた結果を下の図に示します。

図 47. L-C 整合セルがある場合の H1、H2、および H3 の出力電力(伝導モード)の値

## 注

L-C 整合セルはローパス・フィルタを兼ねています。同一ボード上で整合およびフィルタ・ネットワークを引き続き使用すると、次の値が得られます(伝導モード)。

表 3. 電力と周波数

$I_{DD} = 117.6 \text{ mA}$ 。リファレンス・デザイン・ボードに搭載された UFQFPN48 で測定。

| 周波数 (H1 = 915 MHz) | 電力 (dBm) |

|--------------------|----------|

| H1                 | 21.79    |

| H2                 | -63.1    |

| H3                 | -60.6    |

| H4                 | -55.1    |

| H5                 | -52.6    |

| H6                 | -65.0    |

| H7                 | -61.9    |

| H8                 | -68.3    |

| H9                 | -65.6    |

| H10                | -59.9    |

## 5.1.8

## インピーダンスへの PCB の影響

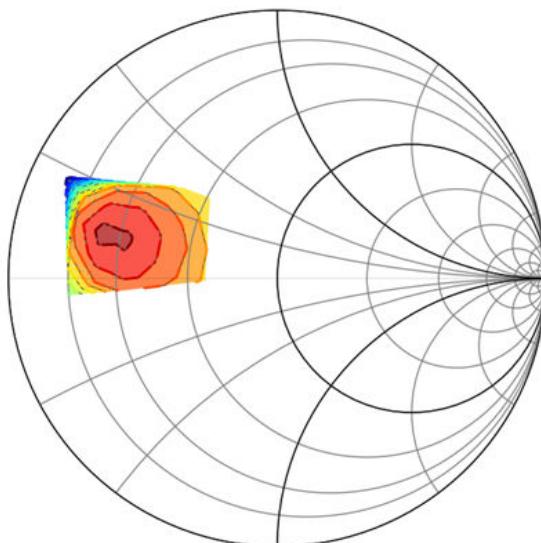

前述のように、PCB は整合およびフィルタ・ネットワークに大きな影響を与える可能性があります。これを示すために、2 つの異なるボードを使用して行った 2 つの異なるインピーダンス抽出を下の図に示します。

図 48. RF PA から見たインピーダンスへの PCB の影響

ボード A

ボード B

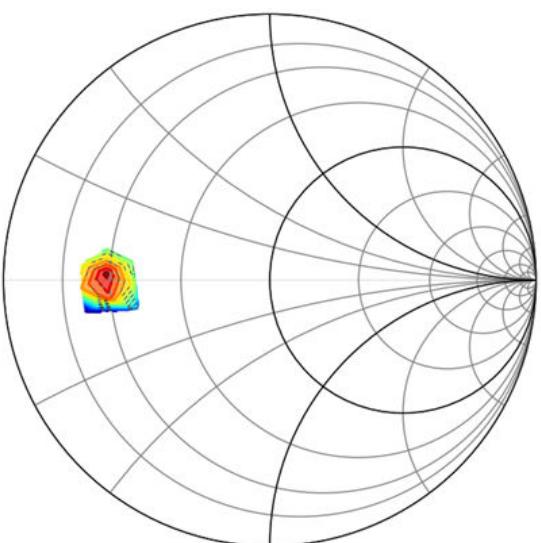

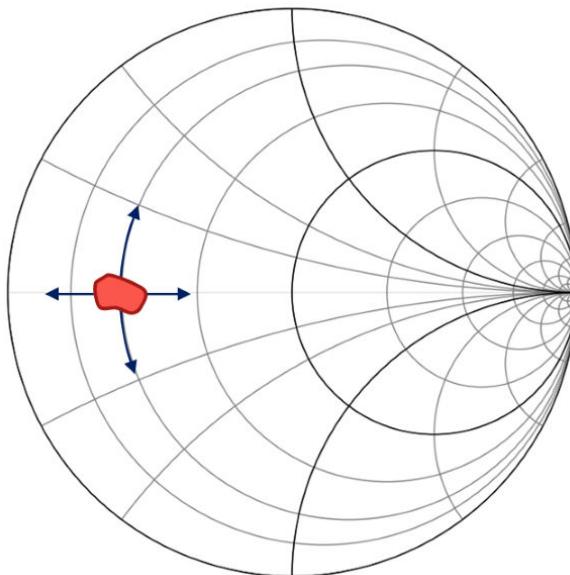

スミス・チャート上のホットスポット(最大電力値のインピーダンス)は、さまざまな領域に存在する可能性があります。下の図は、ホットスポットの移動方法を示しています。

図 49. さまざまな PCB でのホットスポットの移動を示す図

このため、RF ネットワークで使用される SMD コンポーネントの値(前に示した式で計算)の微調整が必要な場合があります。

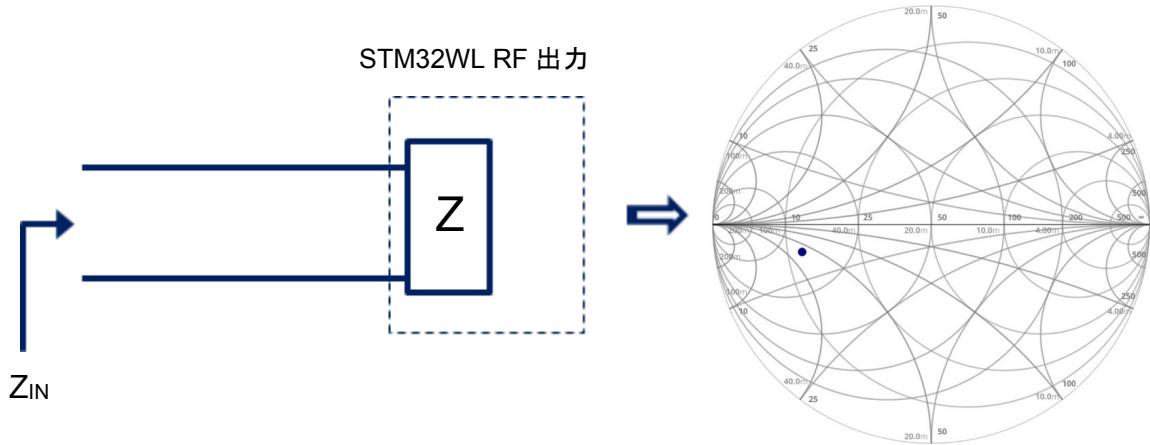

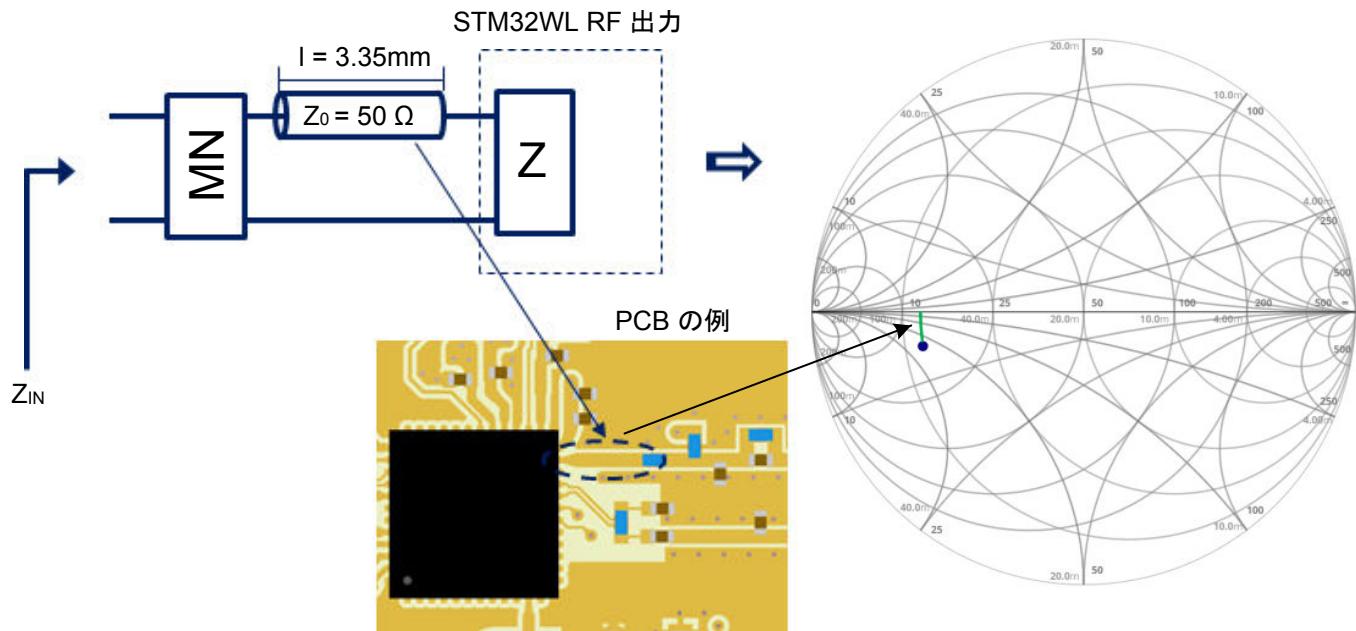

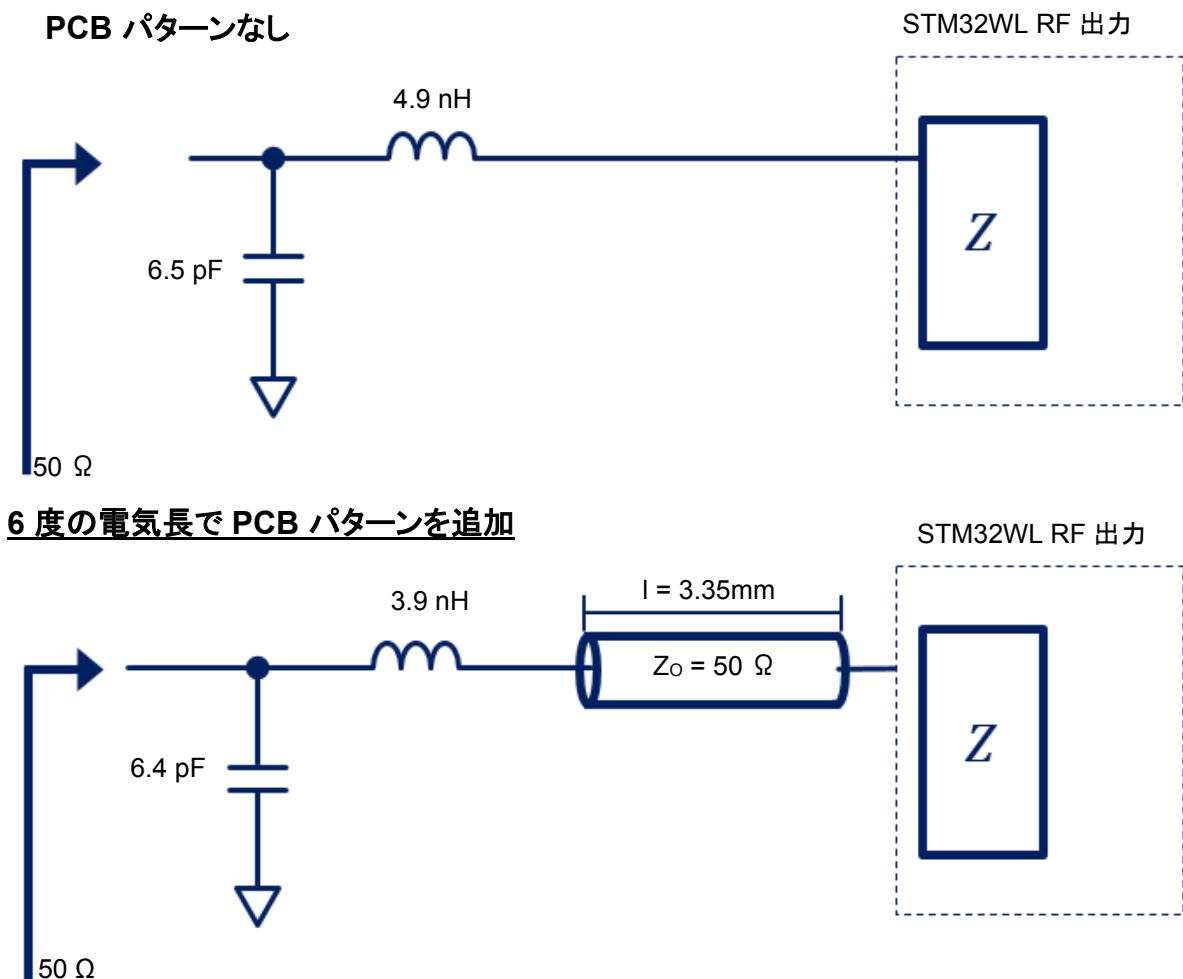

#### インピーダンス整合に対する TLine の影響について

インピーダンス整合作業にかかる時間を節約するには、平面 PCB 送信ライン(ここでは TLine と呼ぶ)がインピーダンス整合に与える影響を認識し、送信ラインによってデバイスから見たインピーダンスがどう変化するかを理解し、整合ネットワークコンポーネントの値の決定を続ける必要があります。インピーダンス整合ネットワークへの送信ラインの影響を以下に示します。

負荷で終端された送信ラインの始点で確認されるインピーダンスは、次のように定義されます(損失ライン)。

$$Z_{in} = Z_0 \left( \frac{Z_L + Z_0 \tanh(\gamma l)}{Z_0 + Z_L \tanh(\gamma l)} \right)$$

ここで、 $\gamma$  は伝搬定数、 $l$  はラインの長さです。

TLine インピーダンスの式は、パッケージの RF 出力ピンと整合ネットワークの基準面の間に TLine(またはなんらかの PCB パターン)が追加された場合、デバイスでは TLine の特性インピーダンスを中心として、観測される反射係数が時計回りに回転することを示します。

次の例では、デバイスの出力インピーダンスは負荷です。目標は、デバイスの出力インピーダンスを  $50 \Omega$  システムに整合させることです。デバイスの出力インピーダンスは  $Z_{868MHz} = (12 - j5) \Omega$  であるため、このインピーダンスはスミス・チャートでは次のように表されます。

図 50. スミス・チャートで表した前の例のインピーダンス

前述のように、最初の LC 整合セルとデバイスの RF 出力の間にある程度の長さの TLine(PCB パターン)を配置すると、反射係数は TLine の特性インピーダンスを中心にして時計回りに回転します。たとえば、デバイスと最初の LC 整合ネットワーク・セルの間に 3.35 mm の PCB パターンが追加され、単純化されたモデルで PCB 上の TLine の速度係数が 0.58 であるとみなした場合の結果を下の図に示します。：

図 51. デバイスの RF 出力と整合ネットワーク(MN)の間に 3.35 mm の TLine を追加した後のインピーダンスへの影響

前の図に示すように、この短い TLine を追加すると、インピーダンスの虚数部が相殺されます。

注 この例では、電気長は 6 度のみでした。AE6TY の無償の CAD ツール SimSmith でも同じ練習を行えます。

前の例の整合ネットワークでは、この短い PCB パターンが存在しない場合、必要なインダクタンスは 4.9 nH ではなく、3.9 nH だけです。

図 52. PCB パターンなしのインダクタ値と電気長 6 度の PCB パターンの違い

注 この例では、TLine は誘導性挙動を示しますが、基板によっては容量性挙動を示すものもあります。。

## 5.2 LNA 整合ネットワーク

前述のように、LNA の入力等価回路は並列コンデンサを備えた並列の抵抗です。

注 LNA の入力等価インピーダンスは、常に負の虚数部(リアクタンス)を持ちます。

図 53. 入力等価回路とローノイズ・アンプのインピーダンス

LNA 入力等価回路

$$Y = 1/R + j\omega C \text{ または } Z = 1/Y \text{ または } Z = R//X_C$$

$$\rightarrow Z = \frac{R_{LNA} - j\omega R_{LNA}^2 C_{LNA}}{(\omega R_{LNA} C_{LNA})^2 + 1}$$

LNA の最適インピーダンスに整合するインピーダンスは、下の図に示すように、LNA 自身のインピーダンスの複素共役です(シンボルは黄色でハイライトされています)。

図 54. 整合ネットワークを備えた LNA の入力等価回路とインピーダンスが必要

LNA 入力等価回路

$$Z = \frac{R - j\omega R^2 C}{(\omega R C)^2 + 1}$$

$$Z = \frac{R + j\omega R^2 C}{(\omega R C)^2 + 1}$$

LNA の最適入力インピーダンスは、下の図のようにスミス・チャートの最下部に示されます。

図 55. スミス・チャートの最下部の LNA 入力等価インピーダンス

### LNA 整合の方法論

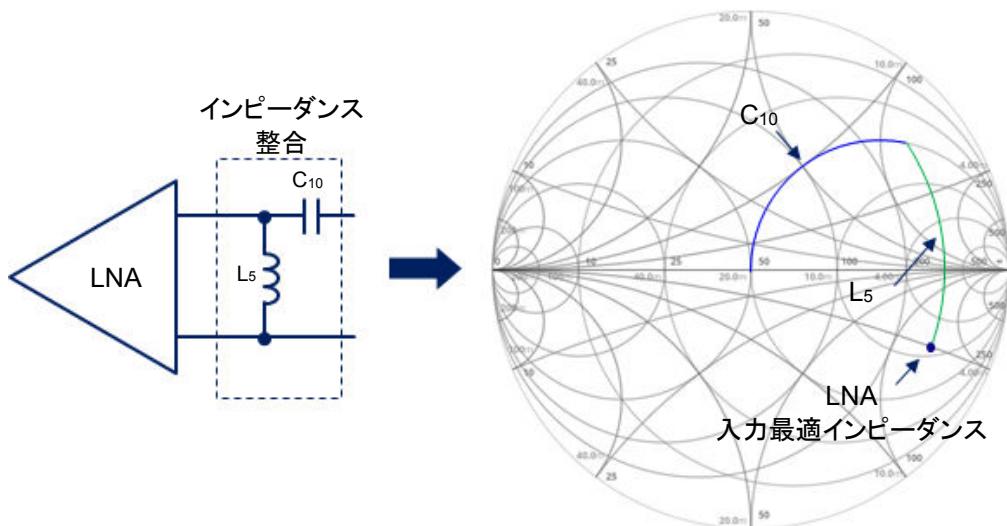

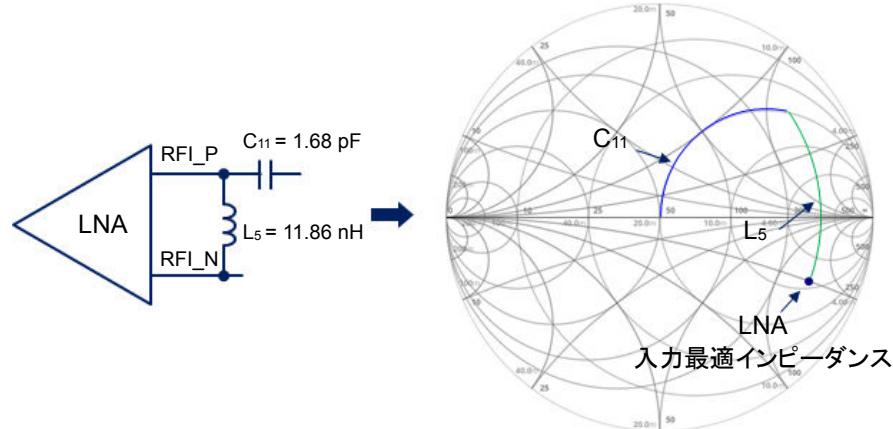

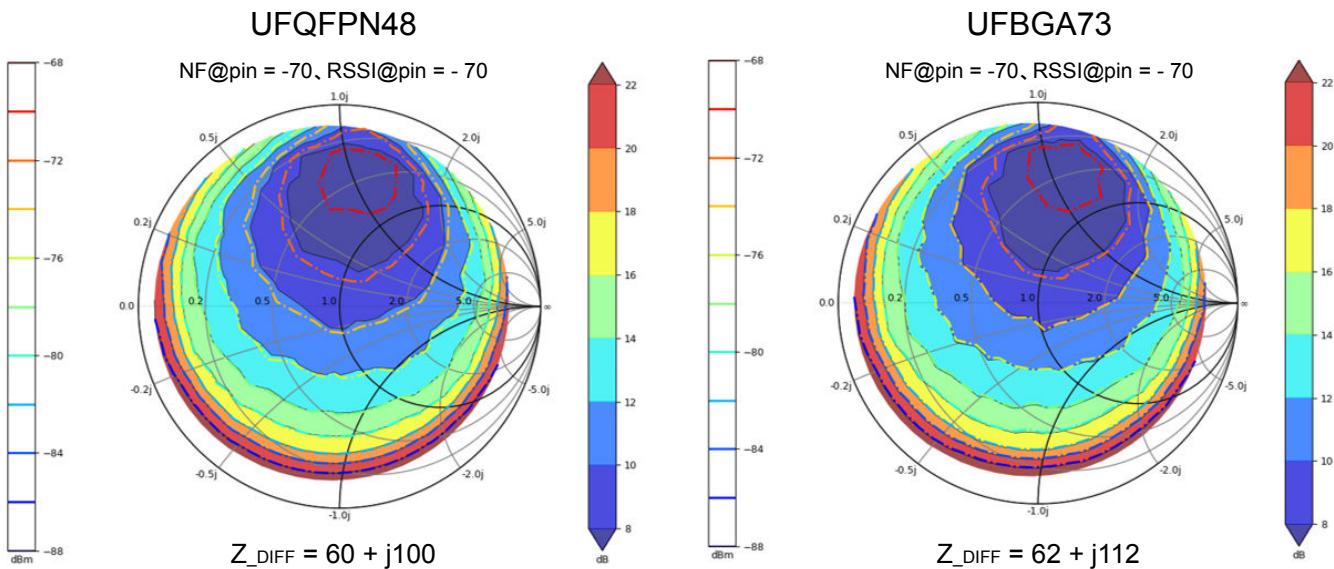

最初の手順は、LNA 入力インピーダンスの虚数部を整合させることです。この方法論は、915 MHz での BGA パッケージの LNA 最適インピーダンスなどの例に基づいています。この対応するインピーダンスは、[付録 A.2](#) に示すように、 $Z_{OPT} = (62 + j112)\Omega$  の複素共役です。

つまり、 $Z_{LNA} = Z_{OPT}^* = (62 - j112)$  ということです。

下の図に、LNA の最適インピーダンスの整合の原理を示します。これは直列コンデンサを備えた並列インダクタで、LNA のリアクタンスに整合し、入力インピーダンスはチャートを中心として回転します。

図 56. LNA インピーダンスを 50 Ω システムに整合させるために必要なコンポーネント

1. LNA 入力コンデンサのリアクタンスを整合させます。

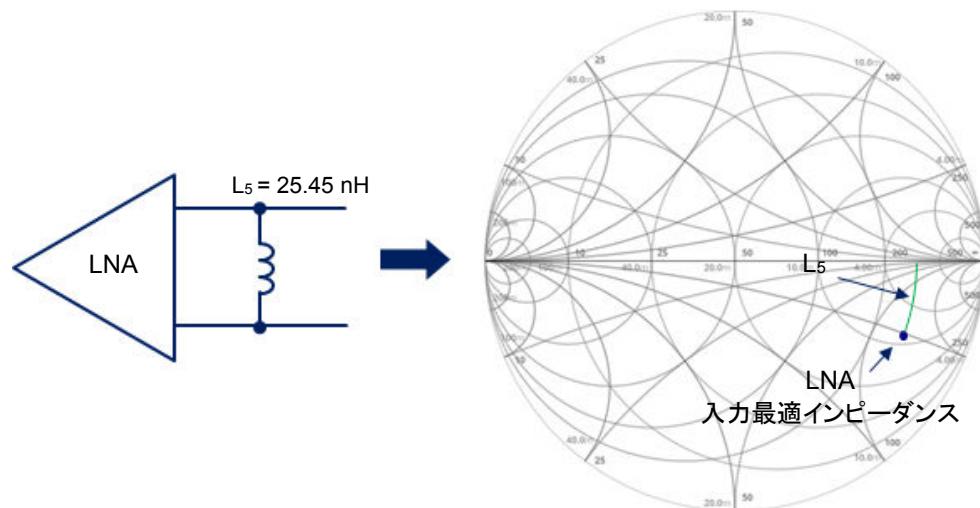

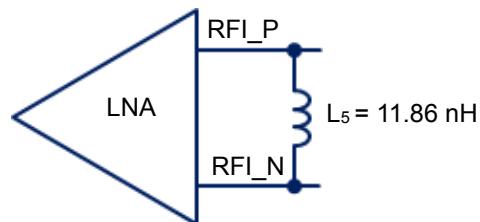

並列インダクタの 1 番目の値を計算します。

$$L_5 = \frac{1}{2\pi f \sqrt{\frac{1}{R^2 + X^2} - \left(\frac{R}{R^2 + X^2}\right)^2}}$$

BGA の例では、 $f = 915 \text{ MHz}$ 、 $R = 62$ 、 $X = 112$  です。そして、 $L_5 = 25.45 \text{ nH}$  です。

このインダクタンス値により、LNA の最適インピーダンスの無効部分が整合されます。スミス・チャートでの結果を下の図に示します。

図 57. LNA インピーダンスの無効部分の整合

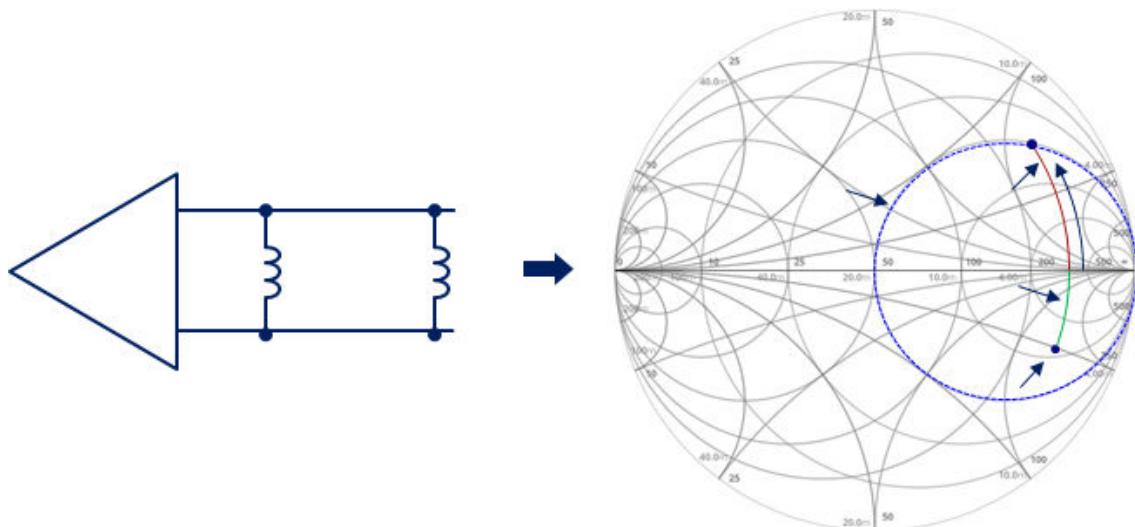

2. インピーダンス変換

ハイ・インピーダンス LNA 側と  $50 \Omega$  のネットワークであるアンテナ側の間のインピーダンス変換を行うために、整合インダクタ  $L_5$  の値が増加します。下の図に示すように、スミス・チャートの  $50 \Omega$  の円に達するように別の並列インダクタが追加されます。

図 58. LNA インピーダンスの無効部分の整合後に  $50 \Omega$  の円に到達

$$L' = \frac{1}{2\pi f \sqrt{\frac{1}{50} \left(\frac{R}{R^2 + X^2}\right) - \left(\frac{R}{R^2 + X^2}\right)^2}}$$

BGA の例では、 $f = 915 \text{ MHz}$ 、 $R = 62$ 、 $X = 112$  です。そして、 $L' = 22.21 \text{ nH}$  です。

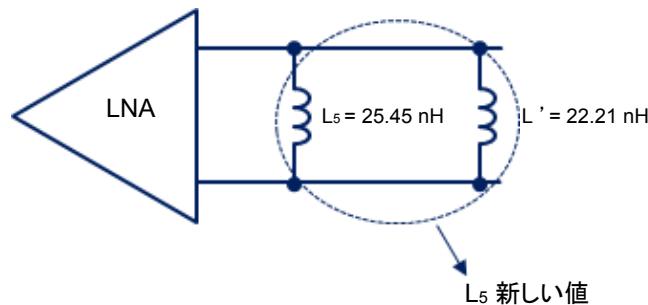

- 並列インダクタの 2 つの値を組み合わせます。

2 つの並列インダクタを 1 つのインダクタ値にまとめることにより、BOM と PCB 面積を節約できます。

図 59. 前のケースの値

$$L_5 \text{ 新しい値} = \frac{L_5 \times L'}{L_5 + L'}$$

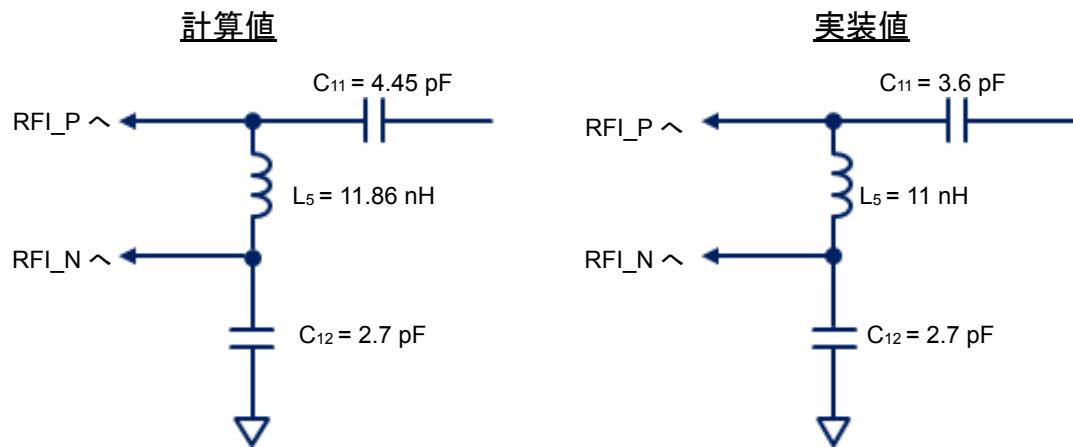

BGA の例では、 $L_5 = 25.45 \text{ nH}$ 、 $L' = 22.21 \text{ nH}$  です。そして、 $L_5 = 11.86 \text{ nH}$  の新しい値です。

図 60. 2 つのインダクタを 1 つにまとめる

注

すでに  $T_X$  整合ネットワークについて説明したように、インダクタ  $L_5$  の値は PCB の寄生効果の影響を受けることがあります。たとえば、実際の実装では、 $L_5$  の値を  $11.80 \text{ nH}$  ではなく  $11.00 \text{ nH}$  にすることもできます。

4. スミス・チャートの中心に達する直列コンデンサの値を計算します。

$$C_{10} = \frac{1}{2\pi f \times 50 \sqrt{\frac{1}{50} \left( \frac{R^2 + X^2}{R} \right) - 1}}$$

BGA の例では、 $f = 915 \text{ MHz}$ 、 $R = 62$ 、 $X = 112$  です。そして、 $C_{10} = 1.68 \text{ pF}$  です。

スミス・チャートでの結果を下の図に示します。

図 61. 直列コンデンサでのチャートの中央への到達

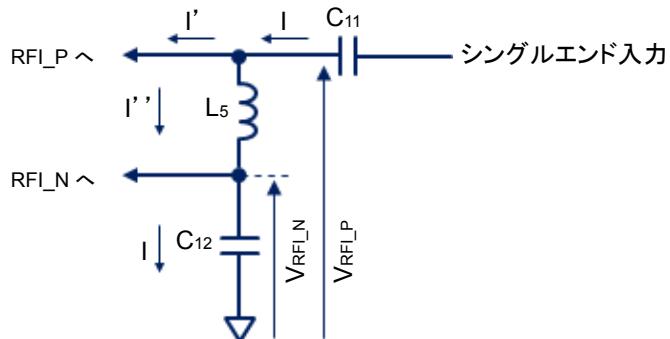

レシーバは差動入力を備えているため、アンテナ側からの信号(GND と呼ばれるシングルエンド信号)を差動信号に変換するための回路を構築する必要があります。通常、これには、平衡信号を不平衡信号に、またはその逆に変換する回路である BALUN を使用します。集中コンポーネントを含む BALUN は、4 つまたは 6 つの要素により実装され、レーン間で振幅が同じで  $180^\circ$  の電圧位相差を確保します。

5. RFI\_N と RFI\_P に差動電圧を生成する回路を定義します。

インダクタ(BALUN インダクタと整合インダクタ)の値が高いため、4 または 6 要素の真の BALUN では、受信性能を低下させる損失(ESR の高いインダクタ)が発生する可能性があります。そのため、ユーザは 3 つの要素だけで「BALUN のような」回路を構築し、性能とコストのバランスをとる必要があります。

注 LNA 入力インピーダンスは無限大ではないため、RFI\_N 電圧と RFI\_P 電圧の間には位相アンバランスが存在し、正確に 180°の位相差は生成されません。

以下の図に回路の分析を示します。

図 62. Rx 整合ネットワークの分析

RFI\_P の電圧は、マイナス RFI\_N にする必要があります。

$$\text{条件 1: } V_{RFI\_P} = -V_{RFI\_N}$$

上記の回路から:

$$V_{L5} = I'' \times jX_{L5} = V_{RFI\_P} + V_{RFI\_N}$$

および

$$V_{C12} = I \times jX_{C12} = V_{RFI\_N} = \frac{V_{L5}}{2}$$

条件 1 から、コンデンサ C12 の電圧はインダクタ L5 の電圧の半分です。

$$I \times jX_{C12} = \frac{I'' \times jX_{L5}}{2}$$

ただし、

$$I'' = I - I'$$

そして、

$$I \times X_{C12} = \frac{(I - I') \times X_{L5}}{2}$$

$X_{C12} = X_{L5}$  の場合、前の式は次のようにになります。 $I = \frac{(I - I')}{2} \Rightarrow I' = -I$

これは、この回路の実際の機能には対応していません。そのため、唯一の解決策は次のとおりです。

$$I \times X_{C12} = \frac{I'' \times X_{L5}}{2} \Rightarrow X_{C12} = \frac{X_{L5}}{2}$$

これは、C12 のリアクタンスが L5 の半分であることを意味しますが、前述のように、L5 値の一部は、LNA の容量性リアクタンスを相殺するために使用されます。そして、前の結果で使用する必要のある L5 の値は、ステップ #3 のスミス・チャートで 50 Ω の円に到達するために使用されるものです(I' と呼ばれます)。そのため、C12 は次のように計算されます。

$$C12 = \frac{2\sqrt{\frac{1}{50} \left( \frac{R}{R^2 + X^2} \right) - \left( \frac{R}{R^2 + X^2} \right)^2}}{2\pi f}$$

BGA の例では、 $f = 915 \text{ MHz}$ 、 $R = 62$ 、 $X = 112$  です。そして、 $C12 = 2.7 \text{ pF}$  です。

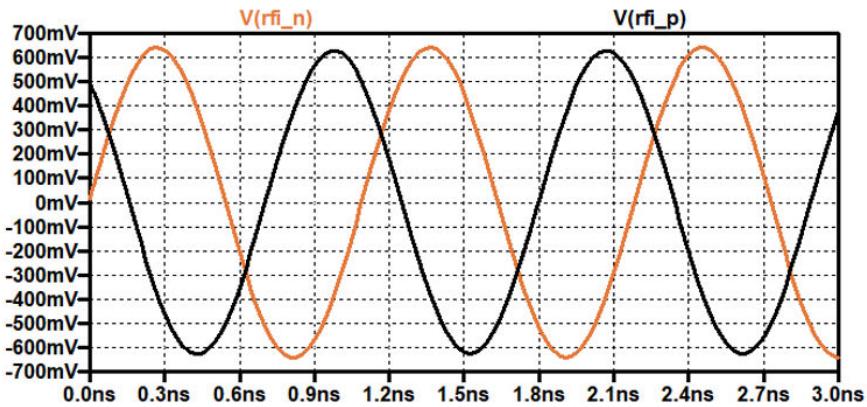

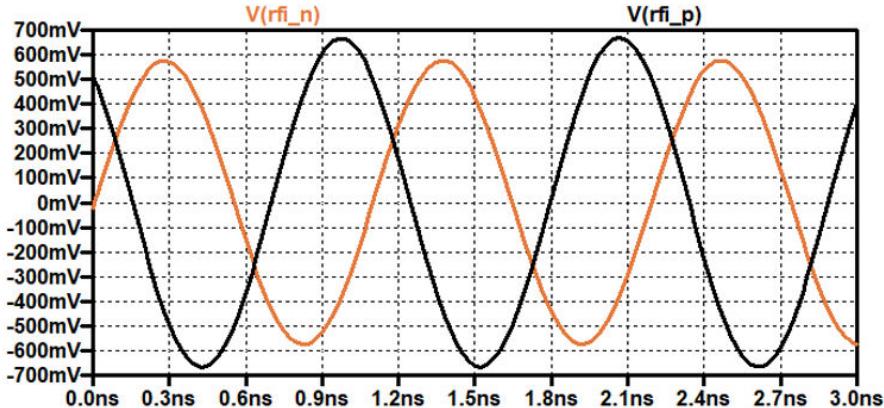

L5、C11、および C12 の値を使用して、915 MHz の正弦波形を入力として SPICE 過渡シミュレーションを行うと、下の図に示す結果が得られます。

図 63. Zoptimal の使用時に位相アンバランスを示すシミュレーション波形

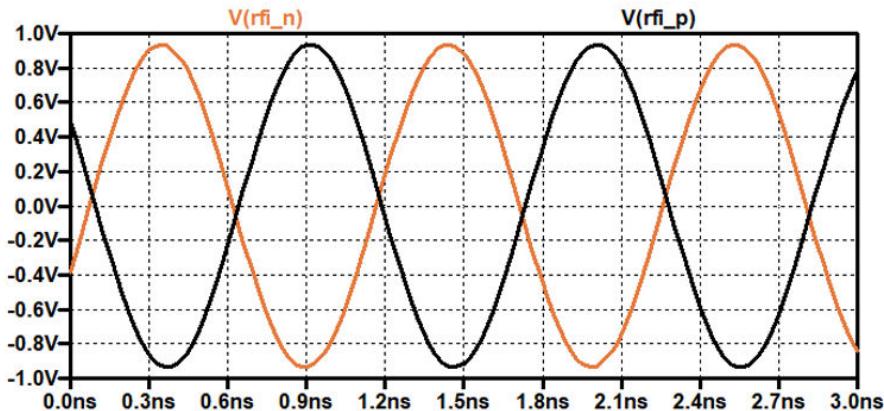

C12 に謝った値(たとえば、2.7 pF ではなく 3 pF)を設定した場合、結果は異なります。

図 64. C12 に謝った値を使用した場合の振幅の不一致

RLNA が報告値の 10 倍である場合、結果は次のようにになります。

図 65. LNA 入力等価並列抵抗が大きい場合の位相差を示す RFI\_N および RFI\_P の波形

この 3 要素構成の BALUN のようなものを使用した場合、位相アンバランスは RLNA に大きく比例します。実際には、RLNA 値が Optimal より大きいため、位相アンバランスは図 63 に示すものよりも小さくなります。

注 上記の電圧波形は、Analog Devices の LTspice® ソフトウェアによる過渡分析に基づいてシミュレーションされています。

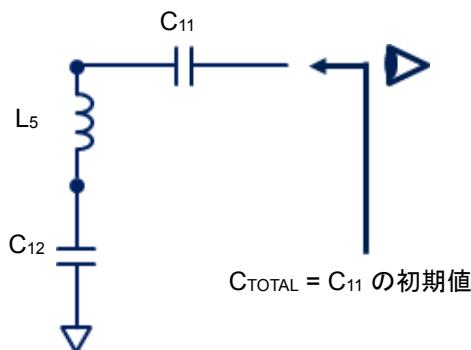

6. C12 によって生じる不一致のため、C11 の値を再計算します。

注 C11 および C12 コンデンサは直列であり、結果は C11 の初期値と等しくなければなりません。

図 66. 50 Ω 側から見た総容量

$$\frac{1}{C_{TOTAL}} = \frac{1}{C_{11}} + \frac{1}{C_{12}}$$

BGA の例では、 $C_{TOTAL} = 1.68 \text{ pF}$  および  $C_{12} = 2.7 \text{ pF}$  の場合、次のようにになります。

$$\frac{1}{1.68 \text{ pF}} = \frac{1}{C_{11\text{新しい値}}} + \frac{1}{2.7 \text{ pF}} \Rightarrow C_{11\text{新しい値}} = 4.45 \text{ pF}$$

一部の RF スイッチでは、Rx パスの RF スイッチの前にコンデンサを 1 つ追加する必要があります。アンテナに達する高調波エネルギーの量を低減するためです。このコンデンサを配置しても高調波出力電力が変化しない場合、このコンデンサを実装しない状態にすることもできます(下の図を参照)。

図 67. Rx パスにコンデンサを追加することにより、Tx と Rx パスの間で結合される高調波エネルギーの量を低減

下の図には、計算値と比較して、PCB に実装した前の  $R_X$  整合回路 の例の値を示します。

図 68. 計算値と、 $R_X$  インピーダンス整合ネットワークの PCB 実装値との比較

### 5.3 計算されたコンポーネントの RF BOM

前の例の回路全体を図 67 に示します。

以前に計算したコンポーネント値の RF BOM を次に示します。インダクタには Murata の高 Q コンポーネント・シリーズ LQW15AN、整合ネットワーク・コンデンサには GJM1555C、バイパスおよび DC ブロック・コンデンサには GRM1555 を使用します。

表 4. 前の例の RF BOM

| コンポーネント名 | Murata の部品番号      |

|----------|-------------------|

| L1       | LQW15AN4N4G80     |

| L2       | LQW15AN3N4G80     |

| L3       | LQW15AN9N2G80     |

| L5       | LQW15AN12NG80     |

| L6       | LQW15AN47NG80     |

| C1       | GJM1555C1H5R5WB01 |

| C2       | GJM1555C1H2R5WB01 |

| C3       | GJM1555C1H4R3WB01 |

| C4       | GRM1555C1E680JA01 |

| C5       | GJM1555C1H3R5WB01 |

| C6       | GRM1555C1E680JA01 |

| C9       | GRM155C71H473KE19 |

| C10      | GRM1555C1E680JA01 |

| C11      | GJM1555C1H4R5WB01 |

| C12      | GJM1555C1H2R7WB01 |

#### 重要

ユーザ PCB で初めて整合ネットワークを実行するとき、高精度(低許容誤差)のコンポーネントを使用してください。そうしないと、PCB の寄生効果やコンポーネントのばらつきにより問題が発生することがあります。

## 6

## 結論

RF アプリケーションには、理論と実際の実装において一定レベルの知識が必要です。このタスクは、適切な EDA ソフトウェアを使用すると、より簡単に実行できます。このアプリケーション・ノートでは、EDA ソフトウェアからも実行できる整合およびフィルタ・ネットワーク・コンポーネントを分析的に説明します。強調すべきもう 1 つの重要なポイントは、すべてのコンポーネント値における PCB の影響です。PCB は、送信ラインが正しく設計/製造されていないことによって発生するインピーダンスの不整合により、重大な影響を及ぼす可能性があります。

## 付録 A

### A.1 PA 整合インピーダンスの測定

#### プロットの概要

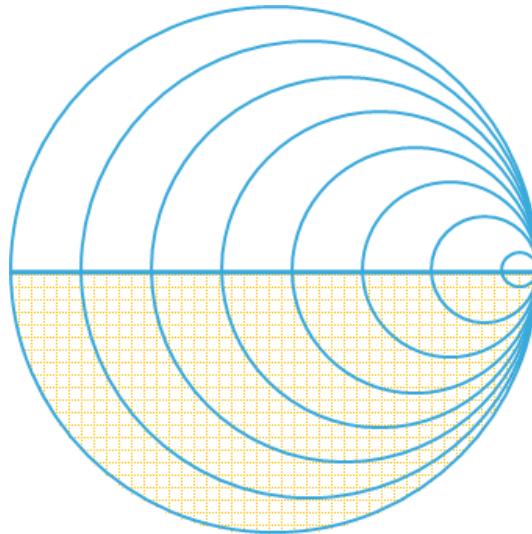

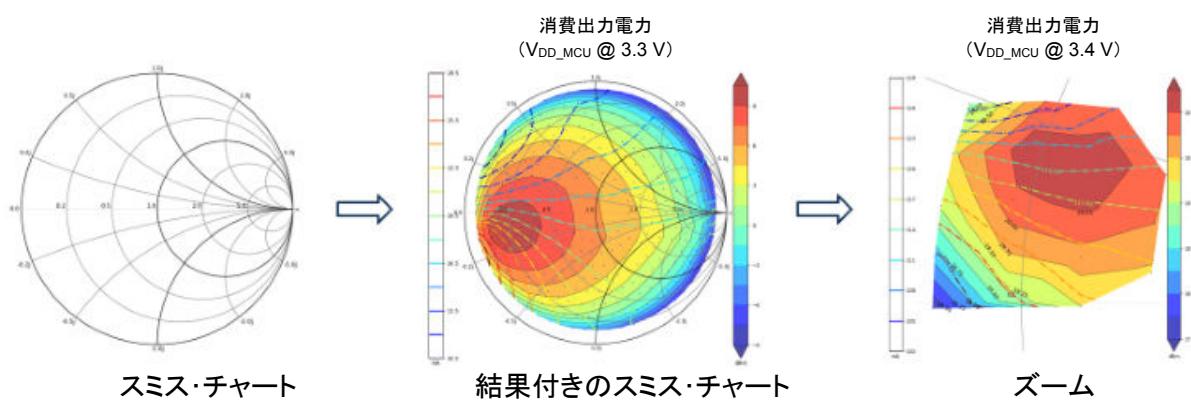

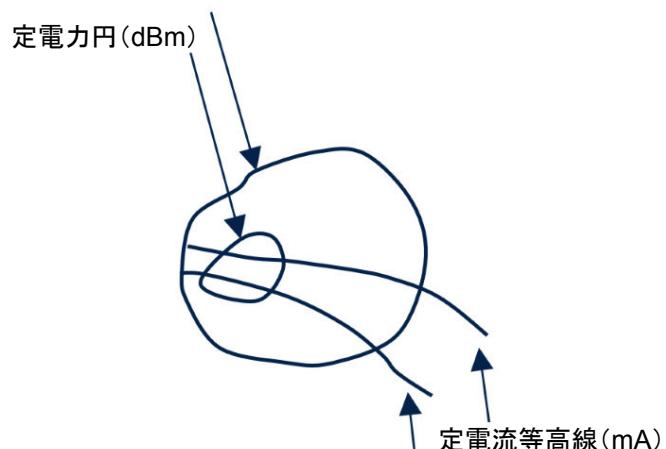

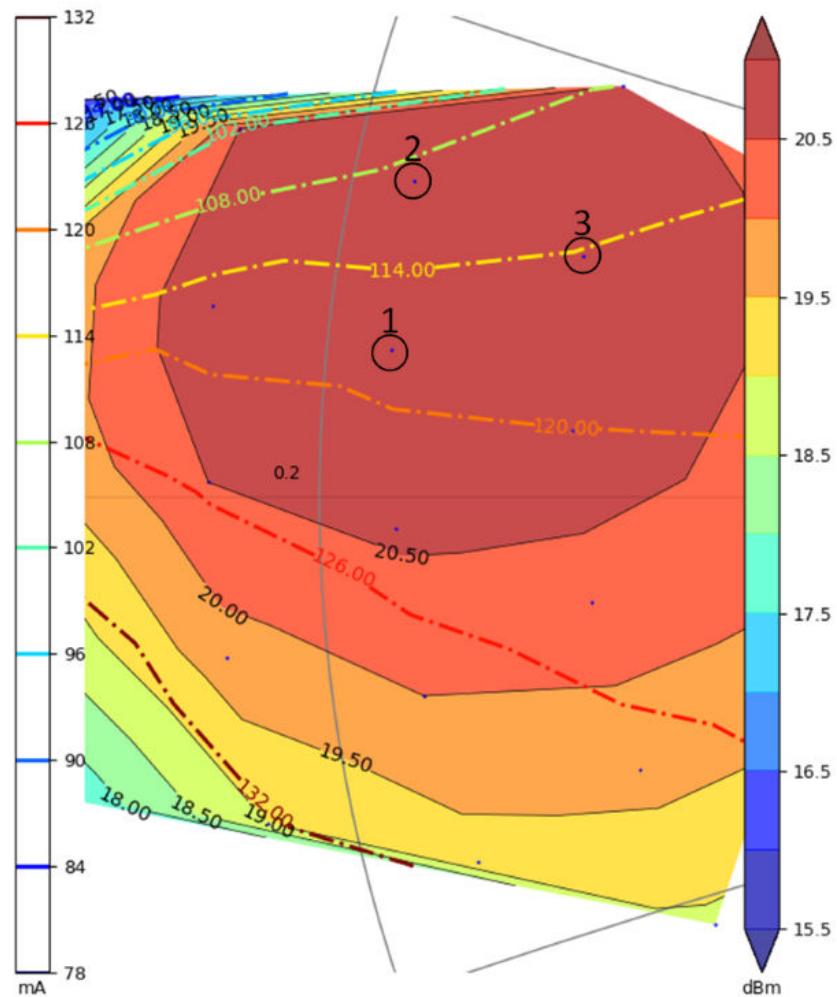

整合インピーダンスは、各パッケージおよび電源/周波数の設定に対して行われたロードプル解析から得られます。結果は、次のようにスミス・チャートにプロットされます。

- 出力電力(dBm)の値が一定である領域を表す色付きの円

- 一定の消費電流を表す色付きの等高線

目的は、最小の消費電流(最大の効率)で必要な電力値に達するインピーダンス出力値を見つけることです。このインピーダンス値を最適インピーダンスと呼びます。読み出された値をグラフで表示する場合、PA 出力インピーダンスは整合しています。結果の表示方法の例を以下に示します(右側の拡大図)。

図 69. スミス・チャートにプロットした RF PA からのインピーダンス抽出(ロードプル解析による)結果の例

図 70. ロードプル解析による標準的なインピーダンス抽出の定電力円と定電流等高線の例

## 結果

### 重要

- この結果は、「PA の最適設定と動作モード」を使用して得たものです(詳細については、製品リファレンス・マニュアルを参照)。

- 測定に使用した RF ケーブル、コネクタ、およびチューナで損失が発生するため、以下の結果に 0.5 dB を加算してください。

- 大電流値(> 100 mA)での動作時には、ケーブルまたはボードのトレースにより、 $V_{DD\_MCU}/V_{DDRF}$  の電圧降下(約 数 10 mV)が発生することがあります。このような場合、ユーザは電圧降下を補正するか、 $V_{DD\_MCU}$  を 100 または 150 mV 増加させる必要があります。

- 下の表に記載されているインピーダンス値はプロットからの値ですが、試験装置から取得された値です。

- PA 出力インピーダンスは、以降のページで報告されるインピーダンス値の複素共役です。たとえば、プロットからの読み出し値が  $(15.27 + j1.27)\Omega$  の場合、これが PA に供給されたインピーダンスであることを意味します。したがって、PA 出力インピーダンスは  $(15.27 - j1.27)\Omega$  となります。

## A.1.1 例 1(UFBGA73、22 dBm、868 MHz)

UFBGA73 パッケージ、22 dBm @ 868 MHz、V<sub>DD\_MCU</sub> = 3.3 V

設定(最適設定):

- 周波数: 868 MHz

- PA モード: HP

- PaDutyCycle: 0x4

- HpMax: 0x7

- PaSel: 0

- Power: 0x16

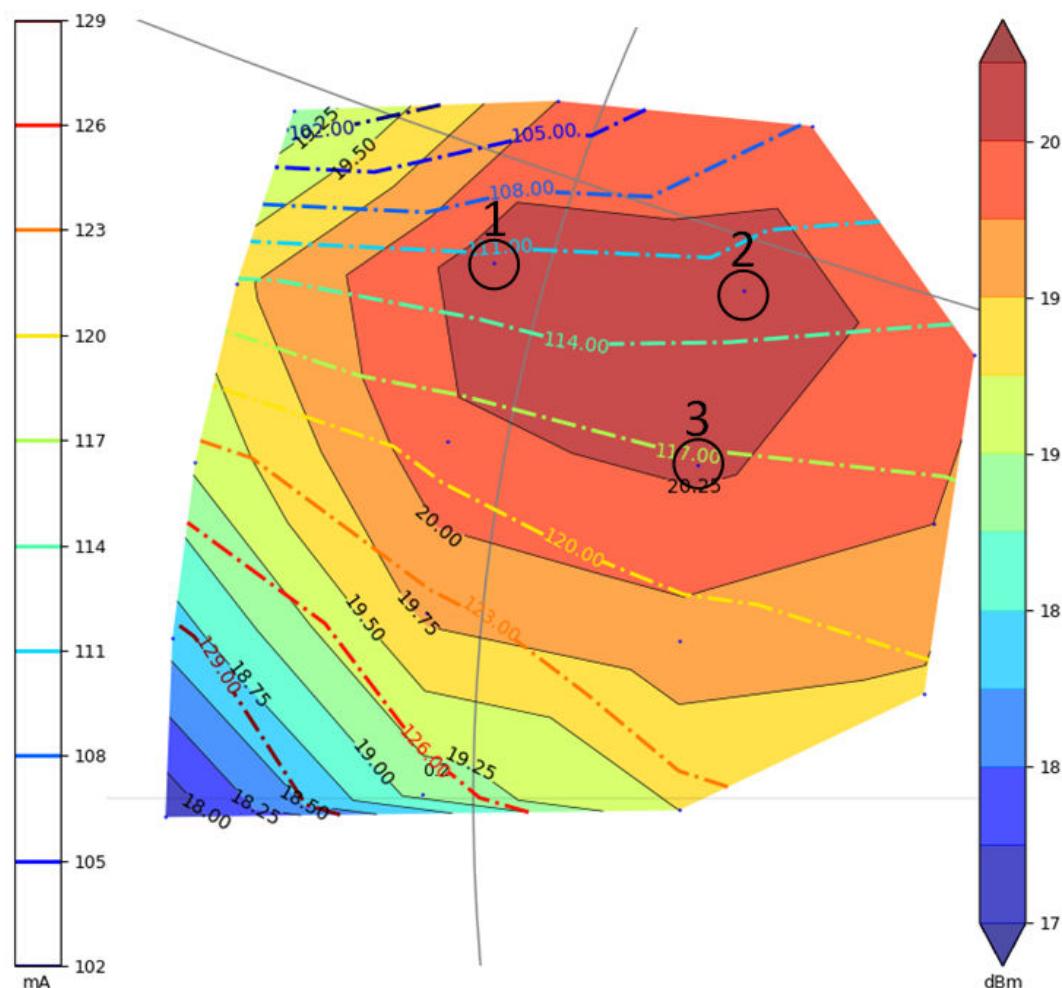

図 71. 出力消費電力(UFBGA73、22 dBm @ 868 MHz、V<sub>DD\_MCU</sub> = 3.3 V)

表 5. 例 1 の結果

| インピーダンス(Ω) |             | 電流(mA) | 電力(dBm) |

|------------|-------------|--------|---------|

| 1          | 11.83+j4.55 | 117.94 | 21      |

| 2          | 12.37+j8.25 | 109.44 | 20.9    |

| 3          | 16.26+j6.51 | 114.24 | 20.9    |

## A.1.2 例 2(UFBGA73、14 dBm、868 MHz)

UFBGA73 パッケージ、14 dBm @ 868 MHz、 $V_{DD\_MCU} = 3.3$  V

設定(最適設定):

- 周波数: 868 MHz

- PA モード: LP

- PaDutyCycle: 0x4

- HpMax: 0x0

- PaSel: 1

- Power: 0x0E

図 72. 出力消費電力(UFBGA73、14 dBm @ 868 MHz、 $V_{DD\_MCU} = 3.3$  V)

表 6. 例 2 の結果

| インピーダンス(Ω) |             | 電流(mA) | 電力(dBm) |

|------------|-------------|--------|---------|

| 1          | 11.92+j1.00 | 25.36  | 14.0    |

| 2          | 11.75+j4.65 | 22.44  | 13.6    |

| 3          | 8.38+j2.08  | 25.58  | 13.7    |

## A.1.3 例 3(UFBGA73、22 dBm、900 MHz)

UFBGA73 パッケージ、22 dBm @ 900 MHz、 $V_{DD\_MCU} = 3.3$  V

設定(最適設定):

- 周波数: 900 MHz

- PA モード: HP

- PaDutyCycle: 0x4

- HpMax: 0x7

- PaSel: 0

- Power: 0x16

図 73. 出力消費電力(UFBGA73、22 dBm @ 900 MHz、 $V_{DD\_MCU} = 3.3$  V)

表 7. 例 3 の結果

| インピーダンス(Ω) |              | 電流(mA) | 電力(dBm) |

|------------|--------------|--------|---------|

| 1          | 16.32+j14.50 | 107.43 | 20.3    |

| 2          | 15.14+j10.92 | 112.56 | 20.6    |

| 3          | 14.32+j7.48  | 117.88 | 20.5    |

## A.1.4 例 4(UFBGA73、22 dBm、915 MHz)

UFBGA73 パッケージ、22 dBm @ 915 MHz、 $V_{DD\_MCU} = 3.3$  V

設定(最適設定):

- 周波数: 9150 MHz

- PA モード: HP

- PaDutyCycle: 0x4

- HpMax: 0x7

- PaSel: 0

- Power: 0x16

図 74. 出力消費電力(UFBGA73、22 dBm @ 915 MHz、 $V_{DD\_MCU} = 3.3$  V)

表 8. 例 4 の結果

| インピーダンス(Ω) |             | 電流(mA) | 電力(dBm) |

|------------|-------------|--------|---------|

| 1          | 10.13+j3.52 | 117.96 | 20.7    |

| 2          | 10.73+j7.23 | 108.87 | 20.6    |

| 3          | 14.01+j7.00 | 111.57 | 20.6    |

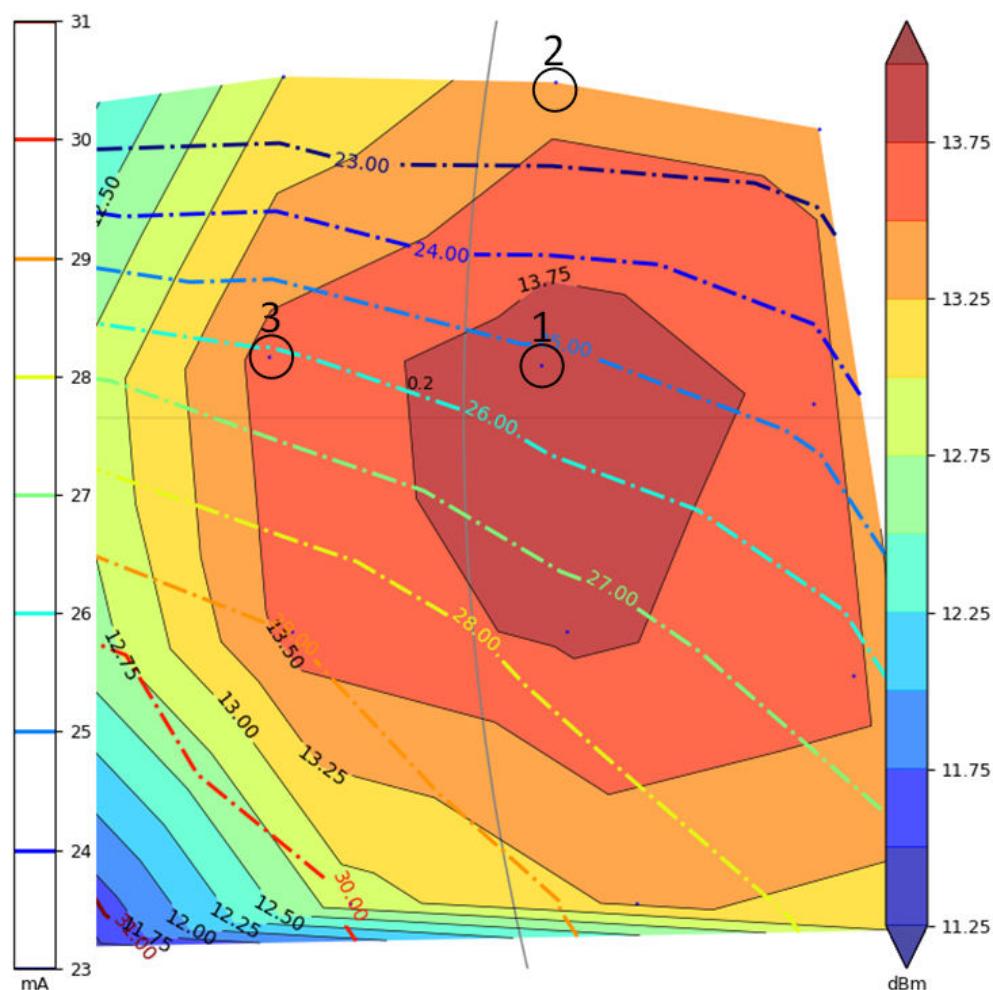

## A.1.5 例 5(UFBGA73、14 dBm、915 MHz)

UFBGA73 パッケージ、14 dBm @ 915 MHz、 $V_{DD\_MCU} = 3.3$  V

設定(最適設定):

- 周波数: 915 MHz

- PA モード: LP

- PaDutyCycle: 0x4

- HpMax: 0x0

- PaSel: 1

- Power: 0x0E

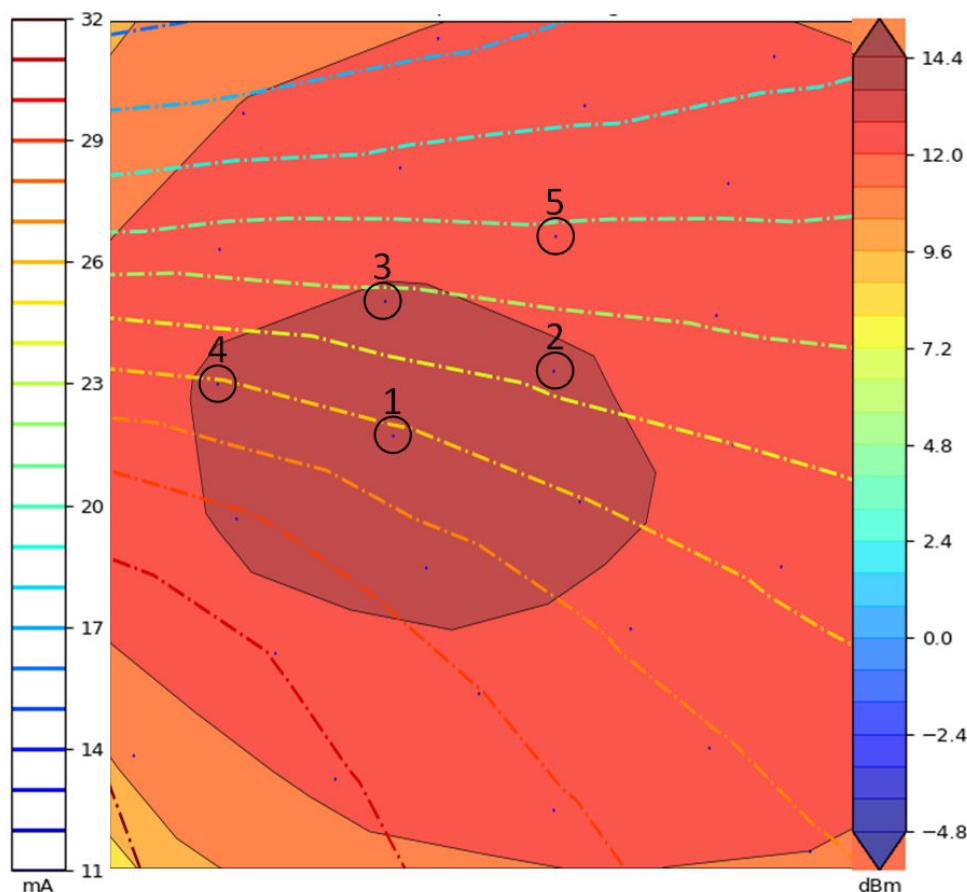

図 75. 出力消費電力(UFBGA73、14 dBm @ 915 MHz、 $V_{DD\_MCU} = 3.3$  V)

表 9. 例 5 の結果

| インピーダンス(Ω) |               | 電流(mA) | 電力(dBm) |

|------------|---------------|--------|---------|

| 1          | $10.97+j0.66$ | 25.24  | 13.9    |

| 2          | $10.85+j4.27$ | 22.06  | 13.4    |

| 3          | $7.67+j0.70$  | 26.14  | 13.6    |

## A.1.6 例 6(UFBGA73、22 dBm、923 MHz)

UFBGA73 パッケージ、22 dBm @ 923 MHz、 $V_{DD\_MCU} = 3.3$  V

設定(最適設定):

- 周波数: 923 MHz

- PA モード: HP

- PaDutyCycle: 0x4

- HpMax: 0x7

- PaSel: 0

- Power: 0x16

図 76. 出力消費電力(UFBGA73、22 dBm @ 923 MHz、 $V_{DD\_MCU} = 3.3$  V)

表 10. 例 6 の結果

| インピーダンス(Ω) |                 | 電流(mA) | 電力(dBm) |

|------------|-----------------|--------|---------|

| 1          | $10.58+j10.71$  | 111.8  | 20.4    |

| 2          | $15.48+j10.60$  | 112.63 | 20.4    |

| 3          | $14.475+j7.189$ | 117.26 | 20.3    |

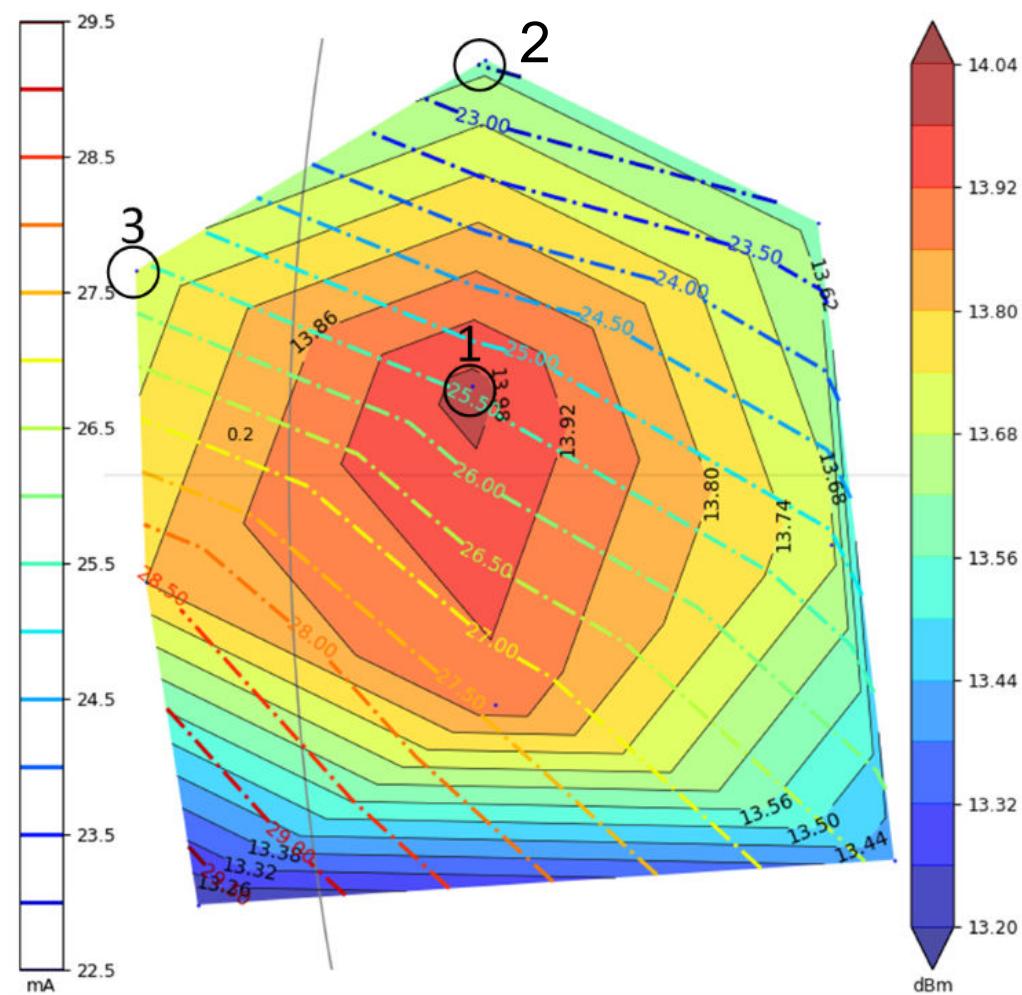

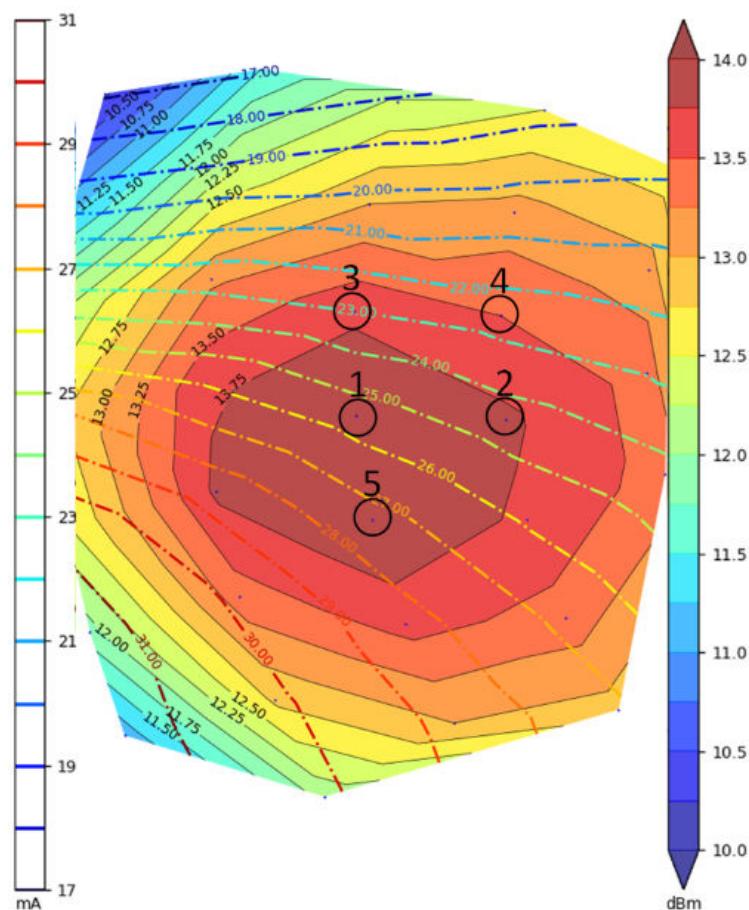

## A.1.7 例 7(UFQFPN48、14 dBm、868 MHz)

UFQFPN48 パッケージ、14 dBm @ 868 MHz、 $V_{DD\_MCU} = 3.3$  V

設定(最適設定):

- 周波数: 868 MHz

- PA モード: LP

- PaDutyCycle: 0x4

- HpMax: 0x0

- PaSel: 1

- Power: 0x0E

図 77. 出力消費電力(UFQFPN48、14 dBm @ 868 MHz、 $V_{DD\_MCU} = 3.3$  V)

表 11. 例 7 の結果

| インピーダンス(Ω) |                | 電流(mA) | 電力(dBm) |

|------------|----------------|--------|---------|

| 1          | $11.36+j0.37$  | 25.74  | 14.0    |

| 2          | $15.27 + 1.27$ | 23.58  | 13.6    |

| 3          | $11.58+j3.67$  | 22.78  | 13.6    |

| 4          | $7.924+j1.97$  | 25.60  | 13.7    |

| 5          | $15.80+j5.16$  | 21.22  | 13.2    |

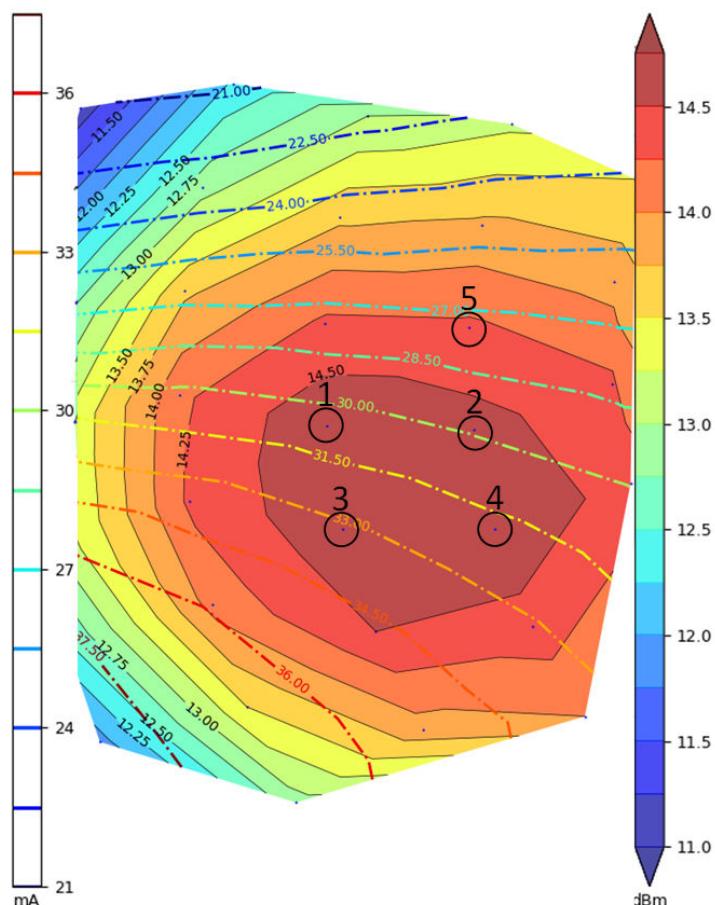

## A.1.8 例 8(UFQFPN48、15 dBm、868 MHz)

UFQFPN48 パッケージ、15 dBm @ 868 MHz、 $V_{DD\_MCU} = 3.3$  V

## 設定(最適設定):

- 周波数: 868 MHz

- PA モード: LP

- PaDutyCycle: 0x6

- HpMax: 0x0

- PaSel: 1

- Power: 0x0E

図 78. 出力消費電力(UFQFPN48、15 dBm @ 868 MHz、VDD\_MCU = 3.3 V)

表 12. 例 8 の結果

| インピーダンス(Ω) |               | 電流(mA) | 電力(dBm) |

|------------|---------------|--------|---------|

| 1          | 11.30+j0.08   | 31.41  | 14.9    |

| 2          | 15.27+j1.25   | 28.63  | 14.7    |

| 3          | 11.65+j3.64   | 28.23  | 14.7    |

| 4          | 7.88+j1.97    | 31.68  | 14.5    |

| 5          | 14.86 - j2.65 | 30.7   | 14.6    |

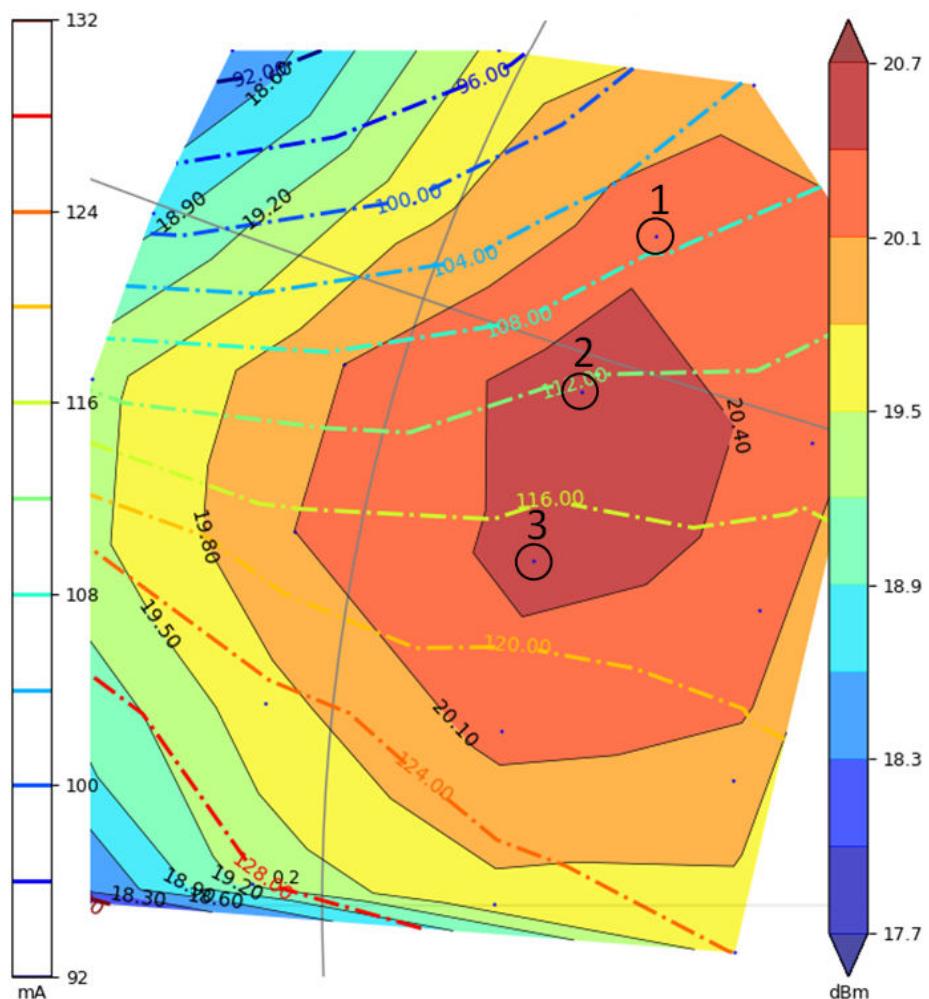

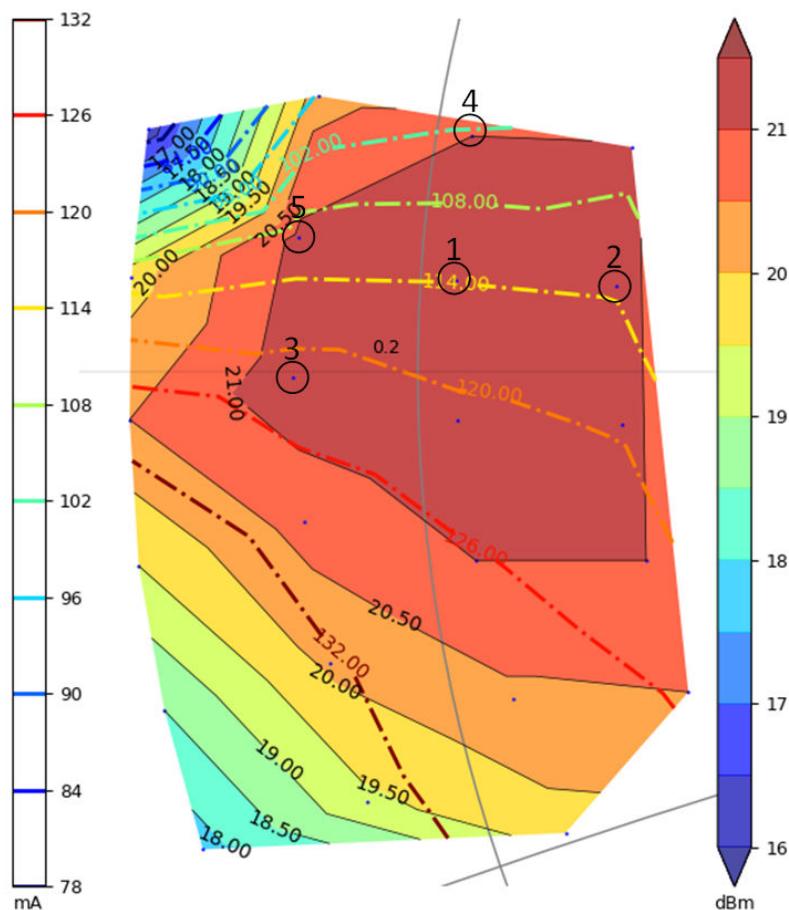

## A.1.9 例 9(UFQFPN48、22 dBm、868 MHz)

UFQFPN48 パッケージ、22 dBm @ 868 MHz、V<sub>DD\_MCU</sub> = 3.3 V

設定(最適設定):

- 周波数: 868 MHz

- PA モード: HP

- PaDutyCycle: 0x4

- HpMax: 0x7

- PaSel: 0

- Power: 0x16

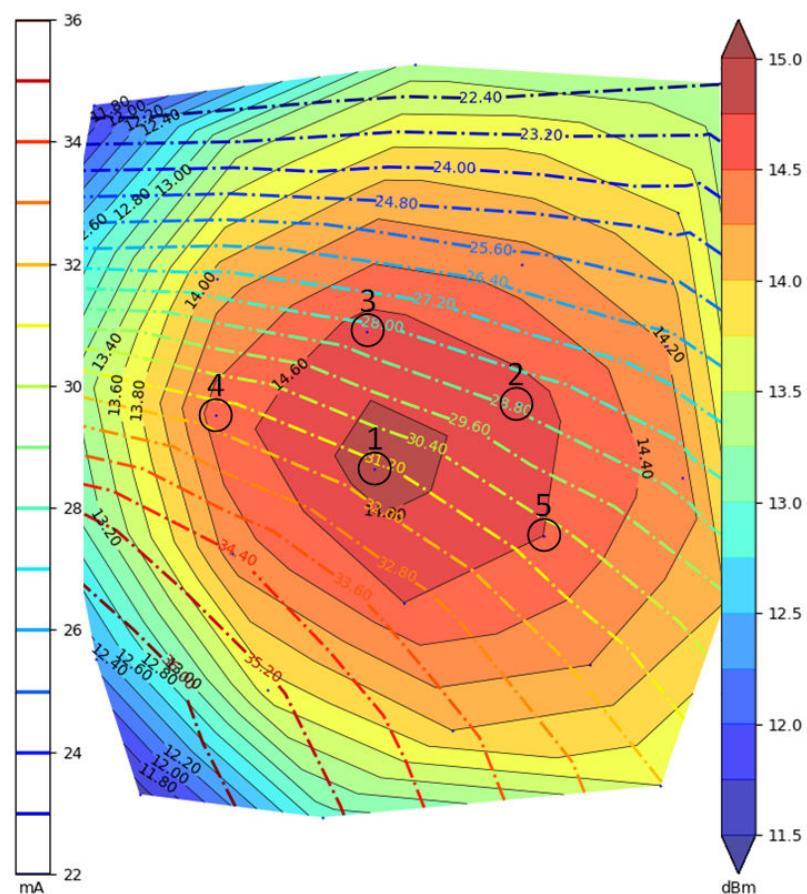

図 79. 出力消費電力(UFQFPN48、22 dBm @ 868 MHz、V<sub>DD\_MCU</sub> = 3.3 V)

表 13. 例 9 の結果

| インピーダンス(Ω) |             | 電流(mA) | 電力(dBm) |

|------------|-------------|--------|---------|

| 1          | 11.31+j0.91 | 132.57 | 21.5    |

| 2          | 7.85+j2.04  | 131.77 | 21.3    |

| 3          | 15.26+j3.00 | 125.54 | 21.4    |

| 4          | 11.39+j4.43 | 121.24 | 21.3    |

| 5          | 15.29+j6.91 | 116.22 | 20.9    |

## A.1.10 例 10(UFQFPN48、14 dBm、915 MHz)

UFQFPN48 パッケージ、14 dBm @ 915 MHz、V<sub>DD\_MCU</sub> = 3.3 V

設定(最適設定):

- 周波数: 915 MHz

- PA モード: LP

- PaDutyCycle: 0x4

- HpMax: 0x0

- PaSel: 1

- Power: 0x0E

図 80. 出力消費電力(UFQFPN48、14 dBm @ 915 MHz、V<sub>DD\_MCU</sub> = 3.3 V)

表 14. 例 10 の結果

| インピーダンス(Ω) |               | 電流(mA) | 電力(dBm) |

|------------|---------------|--------|---------|

| 1          | 10.80+j2.026  | 25.51  | 14.0    |

| 2          | 14.25+j1.24   | 24.46  | 13.8    |

| 3          | 11.09+j4.90   | 23.01  | 13.7    |

| 4          | 14.65+j4.37   | 22.54  | 13.5    |

| 5          | 10.59 - j0.82 | 27.38  | 14.0    |

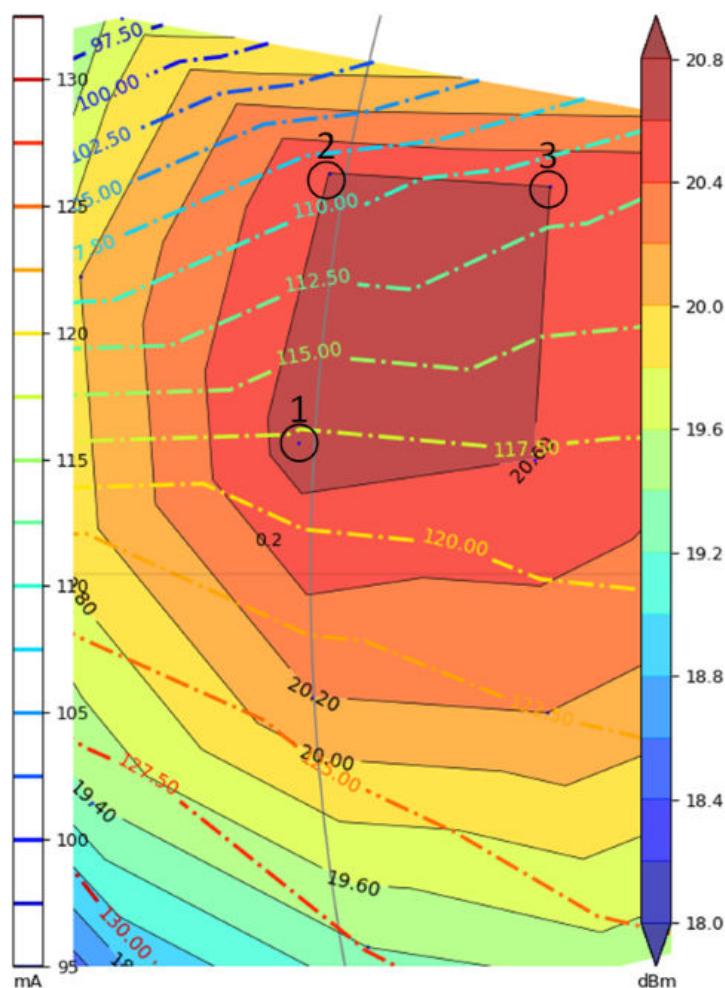

## A.1.11

## 例 11(UFQFPN48、15 dBm、915 MHz)

UFQFPN48 パッケージ、15 dBm @ 915 MHz、V<sub>DD\_MCU</sub> = 3.3 V

設定(最適設定):

- 周波数: 915 MHz

- PA モード: LP

- PaDutyCycle: 0x6

- HpMax: 0x0

- PaSel: 1

- Power: 0x0E

図 81. 出力消費電力(UFQFPN48、15 dBm @ 915 MHz、V<sub>DD\_MCU</sub> = 3.3 V)

表 15. 例 11 の結果

| インピーダンス(Ω) |               | 電流(mA) | 電力(dBm) |

|------------|---------------|--------|---------|

| 1          | 10.83+j2.01   | 30.65  | 14.7    |

| 2          | 14.18+j1.20   | 29.87  | 14.6    |

| 3          | 10.63 - j0.81 | 33.22  | 14.7    |

| 4          | 14.01 - j1.80 | 31.87  | 14.7    |

| 5          | 14.62+j4.44   | 27.41  | 14.3    |

## A.1.12 例 12(UFQFPN48、22 dBm、915 MHz)

UFQFPN48 パッケージ、22 dBm @ 915 MHz、V<sub>DD\_MCU</sub> = 3.3 V

設定(最適設定):

- 周波数: 915 MHz

- PA モード: HP

- PaDutyCycle: 0x4

- HpMax: 0x7

- PaSel: 0

- Power: 0x16

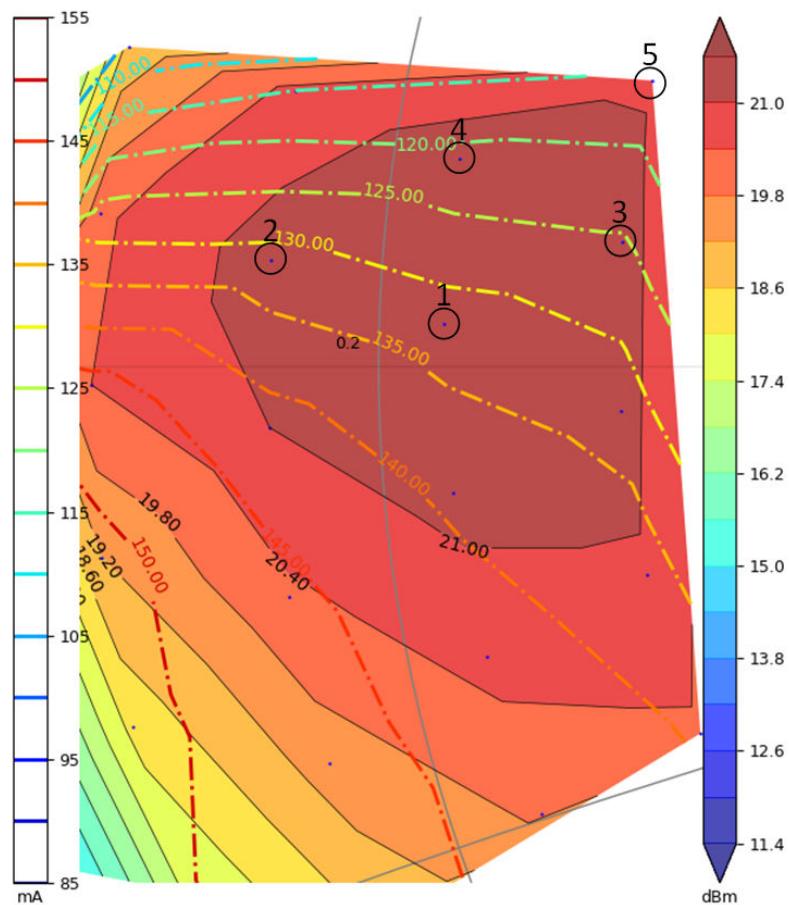

図 82. 出力消費電力(UFQFPN48、22 dBm @ 915 MHz、V<sub>DD\_MCU</sub> = 3.3 V)

表 16. 例 12 の結果

| インピーダンス(Ω) |              | 電流(mA) | 電力(dBm) |

|------------|--------------|--------|---------|

| 1          | 10.71+j1.85  | 113.86 | 21.5    |

| 2          | 14.13+j1.96  | 113.31 | 21.4    |

| 3          | 7.63 - j0.12 | 122.48 | 21.3    |

| 4          | 10.69+j4.77  | 102.97 | 21.0    |

| 5          | 7.65+j2.47   | 110.40 | 21.1    |

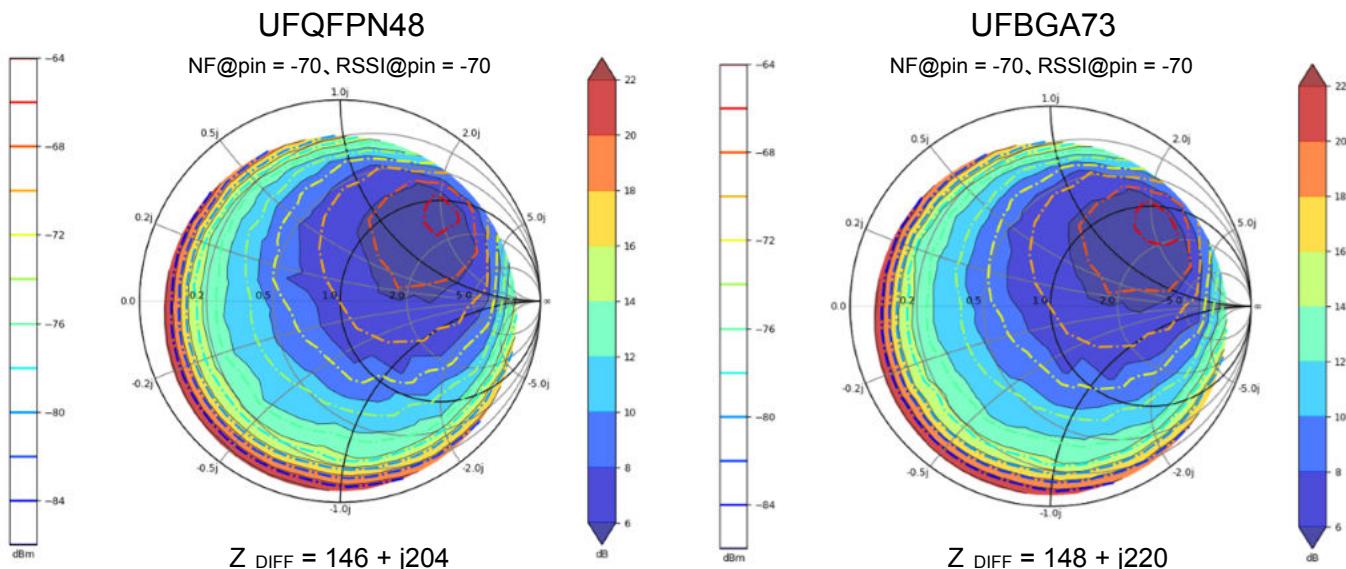

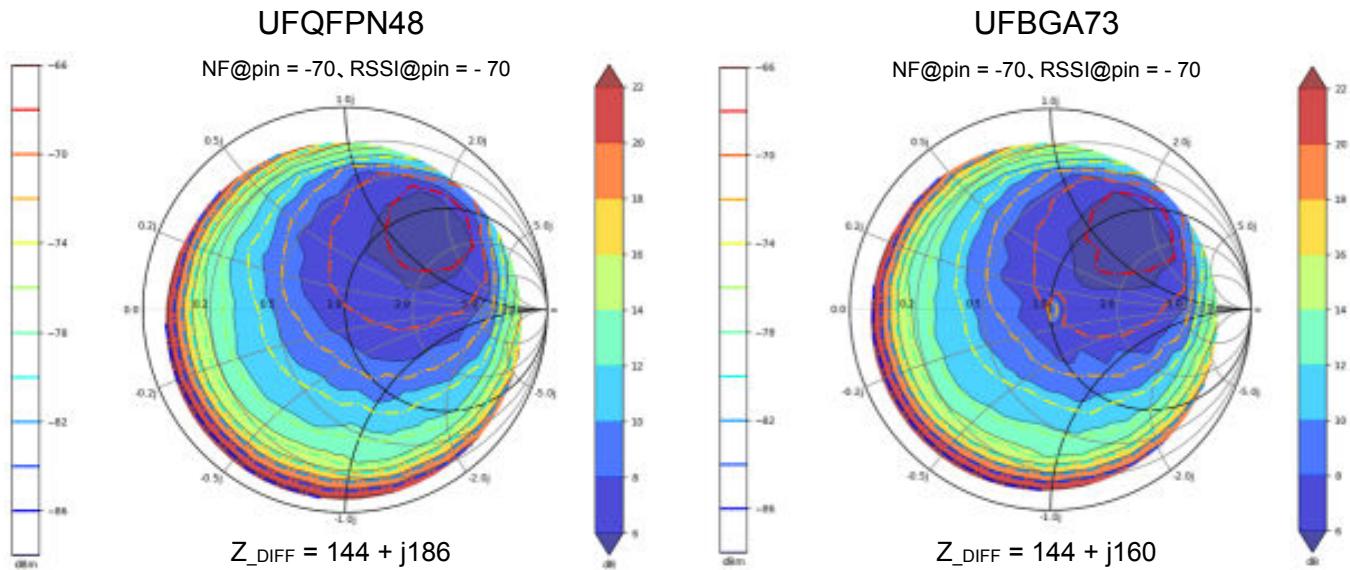

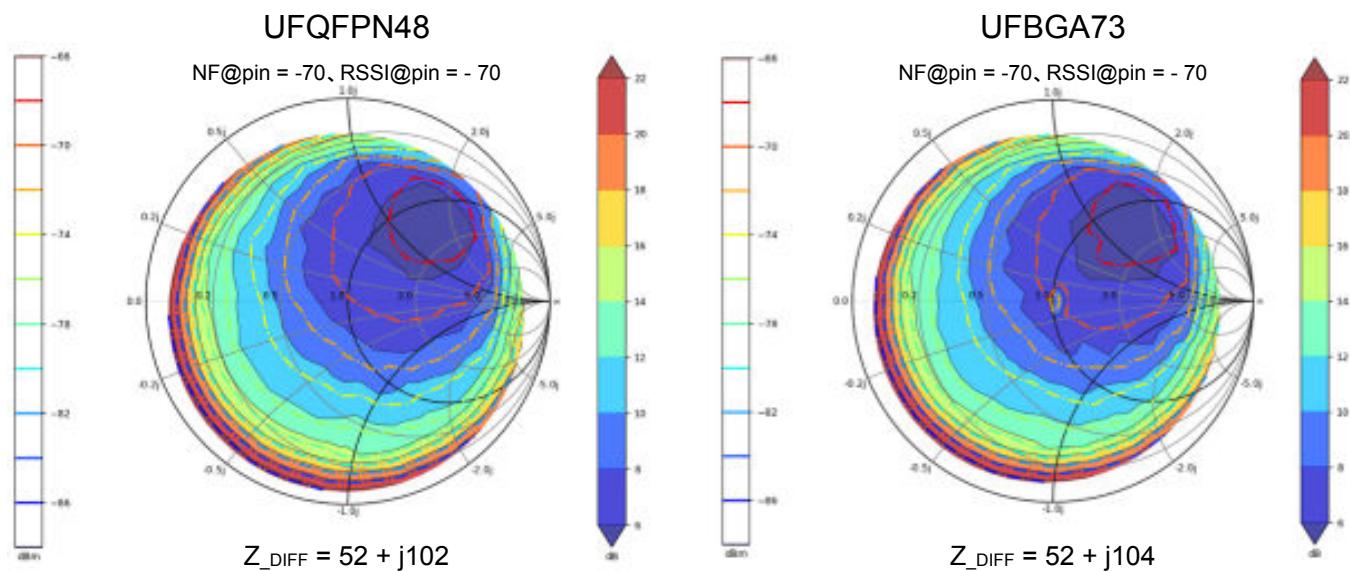

## A.2 LNA 整合インピーダンスの測定

最適インピーダンスは、レシーバの RSSI と NF(Noise figure: 雑音指数)を考慮して、ソースプル解析によって得られます。LNA インピーダンスの測定値と、レシーバの最大性能を得るために LNA に与える最適インピーダンスの詳細を下の表に示します。この文書では、インピーダンスは常にオーム単位で記載されています。

表 17. デバイス・ピン・レベルでの最適差動インピーダンス値

| 周波数 (MHz) | Z <sub>OPT</sub> (Ω) |          |

|-----------|----------------------|----------|

|           | UFQFPN48             | UFBGA73  |

| 433       | 146+j204             | 148+j220 |

| 490       | 142+j186             | 144+j160 |

| 868       | 52+j102              | 52+j104  |

| 915       | 60+j100              | 62+j112  |

### Z<sub>OPT</sub> のイラスト

図 83. 433 MHz のソースプル解析結果

図 84. 490 MHz のソースプル解析結果

図 85. 868 MHz のソースプル解析結果

図 86. 915 MHz のソースプル解析結果

## 付録 B

表 18. RF 測定の高速変換表

| 反射係数( $\Gamma$ ) | リターン・ロス(dB) | 不一致ロス(dB) | VSWR   | 反射波電力(%) | 送信電力(%) |

|------------------|-------------|-----------|--------|----------|---------|

| 0.99             | 0.09        | 17.01     | 199.00 | 98.01    | 1.99    |

| 0.90             | 0.92        | 7.21      | 19.00  | 81.00    | 19.00   |

| 0.85             | 1.41        | 5.57      | 12.33  | 72.25    | 27.75   |

| 0.80             | 1.94        | 4.44      | 9.00   | 64.00    | 36.00   |

| 0.75             | 2.50        | 3.59      | 7.00   | 56.25    | 43.75   |

| 0.70             | 3.10        | 2.92      | 5.67   | 49.00    | 51.00   |

| 0.65             | 3.74        | 2.38      | 4.71   | 42.25    | 57.75   |

| 0.60             | 4.44        | 1.94      | 4.00   | 36.00    | 64.00   |

| 0.55             | 5.19        | 1.56      | 3.44   | 30.25    | 69.75   |

| 0.50             | 6.02        | 1.25      | 3.00   | 25.00    | 75.00   |

| 0.45             | 6.94        | 0.98      | 2.64   | 20.25    | 79.75   |

| 0.40             | 7.96        | 0.76      | 2.33   | 16.00    | 84.00   |

| 0.35             | 9.12        | 0.57      | 2.08   | 12.25    | 87.75   |

| 0.30             | 10.46       | 0.41      | 1.86   | 9.00     | 91.00   |

| 0.25             | 12.04       | 0.28      | 1.67   | 6.25     | 93.75   |

| 0.20             | 13.98       | 0.18      | 1.50   | 4.00     | 96.00   |

| 0.15             | 16.48       | 0.10      | 1.35   | 2.25     | 97.75   |

| 0.10             | 20.00       | 0.04      | 1.22   | 1.00     | 99.00   |

| 0.05             | 26.02       | 0.01      | 1.11   | 0.25     | 99.75   |

| 0.01             | 40.00       | 0.00      | 1.02   | 0.01     | 99.99   |

表 19. 主な定義

| パラメータ                                      | 定義                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 反射係数( $\Gamma$ )                           | $\Gamma = \frac{V_-}{V_+} = \frac{V_{reflected}}{V_{incident}} = \frac{Z_L - Z_0}{Z_L + Z_0}, \quad -1 \leq \Gamma > 1 \text{ or } 0 \leq  \Gamma  \leq 1$                                                                                                                                                   |

| VSWR (Voltage standing wave ratio: 電圧定在波比) | $VSWR = \frac{V_{z \max}}{V_{z \min}} = \frac{1 + \Gamma}{1 - \Gamma}, \quad 1 \leq VSWR \leq \infty$                                                                                                                                                                                                        |

| リターン・ロス(dB)                                | $RL = 10 \times \log \left( \frac{P_{incident}}{P_{reflected}} \right) = P_{incident} \text{ dB} - P_{reflected} \text{ dB}$<br>$RL = 10 \times \log \left( \frac{1}{ \Gamma ^2} \right) = -20 \times \log (  \Gamma  ) \quad \text{or} \quad RL = -20 \times \log \left( \frac{VSWR - 1}{VSWR + 1} \right)$ |

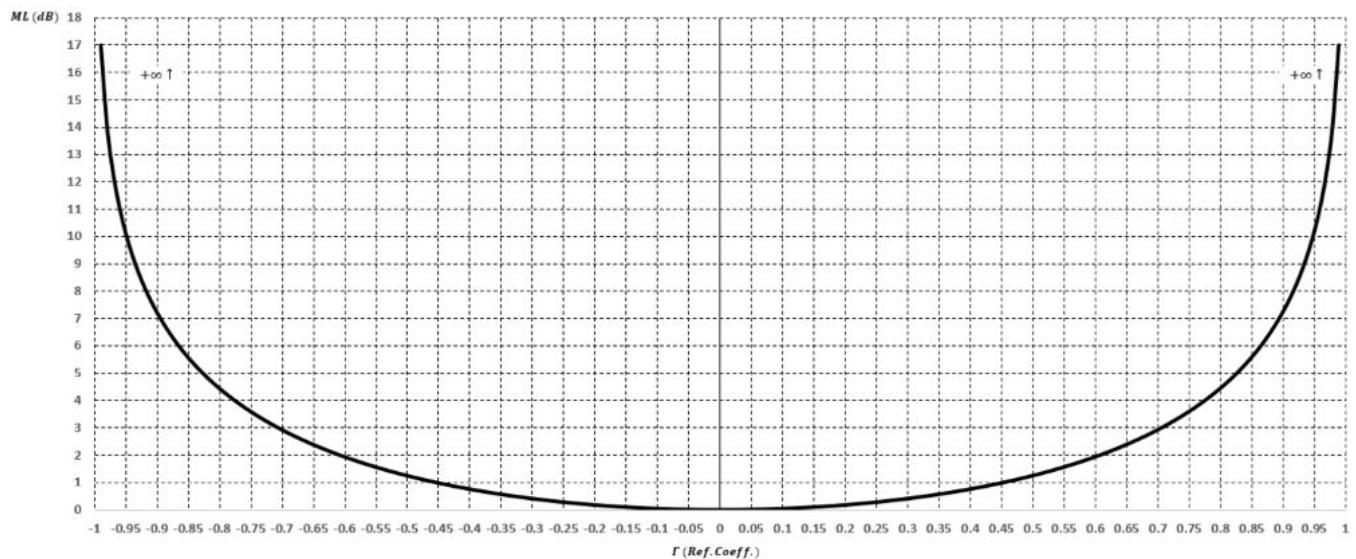

| 不一致ロス(dB)                                  | $ML = 10 \times \log \left( \frac{P_{incident}}{P_{incident} - P_{reflected}} \right) = P_{incident} \text{ dB} - P_{delivered} \text{ dB}$<br>$ML = 10 \times \log ( 1 - \Gamma^2 )$<br>反射波電力(%) = $P_{reflected} = 100 \times \Gamma^2$ および<br>供給電力(%) = $P_{delivered} = 100 \times (1 - \Gamma^2)$       |

図 87. VSWR と  $\Gamma$

図 88. DB 内の不一致ロス( $-10 \log(1-\Gamma^2)$ )図 89. DB のリターン・ロス( $-10 \log(|\Gamma|^2)$ )

## 改版履歴

表 20. 文書改版履歴

| 日付               | 版 | 変更内容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2020 年 12 月 8 日  | 1 | 初版発行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2020 年 12 月 15 日 | 2 | <p>更新:</p> <ul style="list-style-type: none"><li>図 32. 最初の LC 整合セルを追加するスミス・チャート上の図</li><li>図 39. 理想(黒)と実際のコンポーネントの S パラメータ(赤)の S パラメータと周波数のローパス Pi フィルタのシミュレーション</li><li>図 40. PCB への実装のためのローパス Pi フィルタの S パラメータと周波数</li><li>図 42. コンポーネント値の調整後の PCB への実装のためのローパス Pi フィルタの S パラメータと周波数</li><li>図 50. スミス・チャートで表した前の例のインピーダンス</li><li>図 51. デバイスの RF 出力と整合ネットワーク(MN)の間に 3.35 mm の TLine を追加した後のインピーダンスへの影響</li><li>表 11. 例 7 の結果</li><li>図 80. 出力消費電力(UFQFPN48、14 dBm @ 915 MHz、VDD_MCU = 3.3 V)</li></ul> |

## 目次

|              |                                                              |           |

|--------------|--------------------------------------------------------------|-----------|

| <b>1</b>     | <b>一般情報</b>                                                  | <b>2</b>  |

| <b>2</b>     | <b>RF の基礎</b>                                                | <b>4</b>  |

| <b>2.1</b>   | <b>RF の用語</b>                                                | <b>4</b>  |

| <b>2.1.1</b> | <b>パワー</b>                                                   | <b>4</b>  |

| <b>2.1.2</b> | <b>ゲイン</b>                                                   | <b>4</b>  |

| <b>2.1.3</b> | <b>損失</b>                                                    | <b>4</b>  |

| <b>2.1.4</b> | <b>反射係数(<math>\Gamma</math>)、電圧定在波比(VSWR)、およびリターン・ロス(RL)</b> | <b>5</b>  |

| <b>2.1.5</b> | <b>高調波と不要波</b>                                               | <b>6</b>  |

| <b>2.2</b>   | <b>インピーダンス整合とスミス・チャート</b>                                    | <b>6</b>  |

| <b>2.2.1</b> | <b>正規化インピーダンス</b>                                            | <b>8</b>  |

| <b>2.2.2</b> | <b>スミス・チャートの読み取り</b>                                         | <b>8</b>  |

| <b>3</b>     | <b>RF コンポーネントの選択</b>                                         | <b>11</b> |

| <b>3.1</b>   | <b>RF コンデンサ</b>                                              | <b>11</b> |

| <b>3.2</b>   | <b>RF インダクタ</b>                                              | <b>12</b> |

| <b>4</b>     | <b>STM32WL RF の説明</b>                                        | <b>14</b> |

| <b>4.1</b>   | <b>トランスマッタ</b>                                               | <b>14</b> |

| <b>4.2</b>   | <b>レシーバ</b>                                                  | <b>15</b> |

| <b>5</b>     | <b>STM32WL 整合/フィルタ・ネットワーク</b>                                | <b>17</b> |

| <b>5.1</b>   | <b>パワー・アンプ・ネットワーク</b>                                        | <b>17</b> |

| <b>5.1.1</b> | <b>出力等価回路</b>                                                | <b>17</b> |

| <b>5.1.2</b> | <b>最適な設定</b>                                                 | <b>18</b> |

| <b>5.1.3</b> | <b>標準的な Tx アプリケーション・ネットワーク</b>                               | <b>19</b> |

| <b>5.1.4</b> | <b>VR_PA のバイアス調整とフィルタリング</b>                                 | <b>20</b> |

| <b>5.1.5</b> | <b>PA 出力整合</b>                                               | <b>20</b> |

| <b>5.1.6</b> | <b>PA 出力のフィルタリング</b>                                         | <b>24</b> |

| <b>5.1.7</b> | <b>基本周波数の電力と高調波レベル</b>                                       | <b>33</b> |

| <b>5.1.8</b> | <b>インピーダンスへの PCB の影響</b>                                     | <b>34</b> |

| <b>5.2</b>   | <b>LNA 整合ネットワーク</b>                                          | <b>38</b> |

| <b>5.3</b>   | <b>計算されたコンポーネントの RF BOM</b>                                  | <b>46</b> |

| <b>6</b>     | <b>結論</b>                                                    | <b>47</b> |

| <b>付 錄</b>   | <b>A</b>                                                     | <b>48</b> |

| <b>A.1</b>   | <b>PA 整合インピーダンスの測定</b>                                       | <b>48</b> |

| <b>A.1.1</b> | <b>例 1(UFBGA73、22 dBm、868 MHz)</b>                           | <b>50</b> |

| <b>A.1.2</b> | <b>例 2(UFBGA73、14 dBm、868 MHz)</b>                           | <b>51</b> |

| <b>A.1.3</b> | <b>例 3(UFBGA73、22 dBm、900 MHz)</b>                           | <b>52</b> |

---

|               |                                     |    |

|---------------|-------------------------------------|----|

| <b>A.1.4</b>  | 例 4(UFBGA73、22 dBm、915 MHz) .....   | 53 |

| <b>A.1.5</b>  | 例 5(UFBGA73、14 dBm、915 MHz) .....   | 54 |

| <b>A.1.6</b>  | 例 6(UFBGA73、22 dBm、923 MHz) .....   | 55 |

| <b>A.1.7</b>  | 例 7(UFQFPN48、14 dBm、868 MHz) .....  | 56 |

| <b>A.1.8</b>  | 例 8(UFQFPN48、15 dBm、868 MHz) .....  | 56 |

| <b>A.1.9</b>  | 例 9(UFQFPN48、22 dBm、868 MHz) .....  | 58 |

| <b>A.1.10</b> | 例 10(UFQFPN48、14 dBm、915 MHz) ..... | 59 |

| <b>A.1.11</b> | 例 11(UFQFPN48、15 dBm、915 MHz) ..... | 60 |

| <b>A.1.12</b> | 例 12(UFQFPN48、22 dBm、915 MHz) ..... | 61 |

| <b>A.2</b>    | LNA 整合インピーダンスの測定 .....              | 62 |

| <b>付 錄</b>    | <b>B</b> .....                      | 65 |

| 改版履歴          | .....                               | 68 |

| 表一覧           | .....                               | 71 |

| 図一覧           | .....                               | 72 |

## 表一覧

|       |                                     |    |

|-------|-------------------------------------|----|

| 表 1.  | 項目(略称) . . . . .                    | 2  |

| 表 2.  | RF PA の最適な設定 . . . . .              | 18 |

| 表 3.  | 電力と周波数 . . . . .                    | 34 |

| 表 4.  | 前の例の RF BOM . . . . .               | 46 |

| 表 5.  | 例 1 の結果 . . . . .                   | 50 |

| 表 6.  | 例 2 の結果 . . . . .                   | 51 |

| 表 7.  | 例 3 の結果 . . . . .                   | 52 |

| 表 8.  | 例 4 の結果 . . . . .                   | 53 |

| 表 9.  | 例 5 の結果 . . . . .                   | 54 |

| 表 10. | 例 6 の結果 . . . . .                   | 55 |

| 表 11. | 例 7 の結果 . . . . .                   | 56 |

| 表 12. | 例 8 の結果 . . . . .                   | 57 |

| 表 13. | 例 9 の結果 . . . . .                   | 58 |

| 表 14. | 例 10 の結果 . . . . .                  | 59 |

| 表 15. | 例 11 の結果 . . . . .                  | 60 |

| 表 16. | 例 12 の結果 . . . . .                  | 61 |

| 表 17. | デバイス・ピン・レベルでの最適差動インピーダンス値 . . . . . | 62 |

| 表 18. | RF 測定の高速変換表 . . . . .               | 65 |

| 表 19. | 主な定義 . . . . .                      | 65 |

| 表 20. | 文書改版履歴 . . . . .                    | 68 |

## 図一覧

|       |                                                                        |    |

|-------|------------------------------------------------------------------------|----|

| 図 1.  | 表皮効果                                                                   | 4  |

| 図 2.  | 近接効果                                                                   | 4  |

| 図 3.  | 周波数における基本信号、高調波、および不要波電力の表示                                            | 6  |

| 図 4.  | 電源インピーダンス(RF PAなど)と負荷インピーダンス(アンテナなど)の間のインピーダンス整合ネットワークによって生じる共役インピーダンス | 7  |

| 図 5.  | 負荷時の電力と電源から供給される最大電力の関係                                                | 7  |

| 図 6.  | スミス・チャートの特性の単純な表現                                                      | 9  |

| 図 7.  | 直列コンデンサまたはインダクタを追加したときのインピーダンスの変化を示すスミス・チャートの図                         | 9  |

| 図 8.  | アドミタンス・スミス・チャート                                                        | 10 |

| 図 9.  | 並列コンデンサまたはインダクタを追加したときのアドミタンスの変化を示すスミス・チャートの図                          | 10 |

| 図 10. | コンデンサの高周波等価回路                                                          | 11 |

| 図 11. | コンデンサの理想的な周波数応答                                                        | 11 |

| 図 12. | コンデンサの実際の周波数応答                                                         | 11 |

| 図 13. | インダクタの等価回路                                                             | 12 |

| 図 14. | インダクタの理想的な周波数応答                                                        | 12 |

| 図 15. | インダクタの実際の周波数応答                                                         | 13 |

| 図 16. | アプリケーションが 1 つの RF 出力用にのみ設計されている場合の RFO_HP または RFO_LP の選択例              | 14 |

| 図 17. | 2 つの RF 出力を使用するときに必要な整合ネットワークの例                                        | 14 |

| 図 18. | デバイス内部の RF PA の概要(出力波形付き)                                              | 15 |

| 図 19. | 負荷のある Rx 回路の図                                                          | 16 |

| 図 20. | レシーバの入力等価回路                                                            | 16 |

| 図 21. | 集中コンポーネントにより PCB に実装される整合ネットワークと BALUN の特性                             | 16 |

| 図 22. | 実装が可能な 2 つの整合ネットワークの図                                                  | 17 |

| 図 23. | インピーダンスが純粋な抵抗である場合の PA 出力等価回路                                          | 17 |

| 図 24. | インピーダンスが容量性リアクタンスを持つ抵抗である場合の PA 出力等価回路                                 | 18 |

| 図 25. | 標準的な Tx アプリケーション・ネットワーク                                                | 19 |

| 図 26. | 標準的な Tx アプリケーション・ネットワークの各部の説明                                          | 19 |

| 図 27. | VR_PA 標準アプリケーション回路                                                     | 20 |

| 図 28. | UFQFPN48、14 dBm、868 MHz の出力等価回路                                        | 21 |

| 図 29. | 最初の LC 整合ネットワーク・セルの配置                                                  | 21 |

| 図 30. | L1 を使用して RF PA の無効部分に整合し、20 ms の円に到達                                   | 22 |

| 図 31. | 計算値を持つ最初の LC 整合セル                                                      | 23 |

| 図 32. | 最初の LC 整合セルを追加するスミス・チャート上の図                                            | 23 |

| 図 33. | 高調波および寄生放射が制御された出力スペクトルの例                                              | 24 |

| 図 34. | 前の例の算出後のノッチ・フィルタ値を適用したネットワーク                                           | 25 |

| 図 35. | ノッチ・フィルタ・コンポーネントを追加したときのインピーダンス変化をスミス・チャート上に示した図                       | 25 |

| 図 36. | ノッチ・フィルタによって発生した不一致を補正するための C2 の値の調整                                   | 26 |

| 図 37. | コンデンサ C3 を追加することで、ノッチ・フィルタによって発生した不一致を低減                               | 26 |

| 図 38. | 入出力インピーダンスが 50 Ω のローパス Pi フィルタ                                         | 27 |

| 図 39. | 理想(黒)と実際のコンポーネントの S パラメータ(赤)の S パラメータと周波数のローパス Pi フィルタのシミュレーション        | 28 |

| 図 40. | PCB への実装のためのローパス Pi フィルタの S パラメータと周波数                                  | 29 |

| 図 41. | 挿入損失付きのローパス Pi フィルタ(S21)の計算値(括弧内)と実装値との関係を示す例                          | 30 |

| 図 42. | コンポーネント値の調整後の PCB への実装のためのローパス Pi フィルタの S パラメータと周波数                    | 31 |

| 図 43. | ローパス Pi フィルタの追加後のネットワーク内の並列コンデンサの再結合                                   | 32 |

| 図 44. | ネットワークで再結合される並列コンデンサ                                                   | 32 |

| 図 45. | スイッチの寄生入力容量を組み込むために、場合によっては C5 の値の変更が必要                                | 33 |

| 図 46. | L-C 整合セルなしの H1、H2、および H3 の出力電力(伝導モード)の値                                | 33 |

| 図 47. | L-C 整合セルがある場合の H1、H2、および H3 の出力電力(伝導モード)の値                             | 33 |

| 図 48. | RF PA から見たインピーダンスへの PCB の影響                                            | 34 |

| 図 49. | さまざまな PCB でのホットスポットの移動を示す図                                             | 35 |

| 図 50. | スミス・チャートで表した前の例のインピーダンス                                                | 36 |

| 図 51. | デバイスの RF 出力と整合ネットワーク(MN)の間に 3.35 mm の TLine を追加した後のインピーダンスへの影響         | 36 |

|       |                                                       |    |

|-------|-------------------------------------------------------|----|

| 図 52. | PCB パターンなしのインダクタ値と電気長 6 度の PCB パターンの違い                | 37 |

| 図 53. | 入力等価回路とローノイズ・アンプのインピーダンス                              | 38 |

| 図 54. | 整合ネットワークを備えた LNA の入力等価回路とインピーダンスが必要                   | 38 |

| 図 55. | スミス・チャートの最下部の LNA 入力等価インピーダンス                         | 39 |

| 図 56. | LNA インピーダンスを 50 Ω システムに整合させるために必要なコンポーネント             | 39 |

| 図 57. | LNA インピーダンスの無効部分の整合                                   | 40 |

| 図 58. | LNA インピーダンスの無効部分の整合後に 50 Ω の円に到達                      | 40 |

| 図 59. | 前のケースの値                                               | 41 |

| 図 60. | 2 つのインダクタを 1 つにまとめる                                   | 41 |

| 図 61. | 直列コンデンサでのチャートの中央への到達                                  | 42 |

| 図 62. | Rx 整合ネットワークの分析                                        | 43 |

| 図 63. | Zoptimal の使用時に位相アンバランスを示すシミュレーション波形                   | 44 |

| 図 64. | C12 に謝った値を使用した場合の振幅の不一致                               | 44 |

| 図 65. | LNA 入力等価並列抵抗が大きい場合の位相差を示す RFI_N および RFI_P の波形         | 44 |

| 図 66. | 50 Ω 側から見た総容量                                         | 45 |

| 図 67. | Rx パスにコンデンサを追加することにより、Tx と Rx パスの間で結合される高調波エネルギーの量を低減 | 45 |

| 図 68. | 計算値と、Rx インピーダンス整合ネットワークの PCB 実装値との比較                  | 46 |

| 図 69. | スミス・チャートにプロットした RF PA からのインピーダンス抽出(ロードプル解析による)結果の例    | 48 |

| 図 70. | ロードプル解析による標準的なインピーダンス抽出の定電力円と定電流等高線の例                 | 48 |

| 図 71. | 出力消費電力(UFBGA73, 22 dBm @ 868 MHz, VDD MCU = 3.3 V)    | 50 |

| 図 72. | 出力消費電力(UFBGA73, 14 dBm @ 868 MHz, VDD MCU = 3.3 V)    | 51 |

| 図 73. | 出力消費電力(UFBGA73, 22 dBm @ 900 MHz, VDD MCU = 3.3 V)    | 52 |

| 図 74. | 出力消費電力(UFBGA73, 22 dBm @ 915 MHz, VDD MCU = 3.3 V)    | 53 |

| 図 75. | 出力消費電力(UFBGA73, 14 dBm @ 915 MHz, VDD MCU = 3.3 V)    | 54 |

| 図 76. | 出力消費電力(UFBGA73, 22 dBm @ 923 MHz, VDD MCU = 3.3 V)    | 55 |

| 図 77. | 出力消費電力(UFQFPN48, 14 dBm @ 868 MHz, VDD MCU = 3.3 V)   | 56 |

| 図 78. | 出力消費電力(UFQFPN48, 15 dBm @ 868 MHz, VDD MCU = 3.3 V)   | 57 |

| 図 79. | 出力消費電力(UFQFPN48, 22 dBm @ 868 MHz, VDD MCU = 3.3 V)   | 58 |

| 図 80. | 出力消費電力(UFQFPN48, 14 dBm @ 915 MHz, VDD MCU = 3.3 V)   | 59 |

| 図 81. | 出力消費電力(UFQFPN48, 15 dBm @ 915 MHz, VDD MCU = 3.3 V)   | 60 |

| 図 82. | 出力消費電力(UFQFPN48, 22 dBm @ 915 MHz, VDD MCU = 3.3 V)   | 61 |

| 図 83. | 433 MHz のソースプル解析結果                                    | 62 |

| 図 84. | 490 MHz のソースプル解析結果                                    | 63 |

| 図 85. | 868 MHz のソースプル解析結果                                    | 63 |

| 図 86. | 915 MHz のソースプル解析結果                                    | 64 |

| 図 87. | VSWR と $\Gamma$                                       | 66 |

| 図 88. | DB 内の不一致ロス( $-10 \log(1-\Gamma^2)$ )                  | 67 |

| 図 89. | DB のリターン・ロス( $-10 \log( \Gamma ^2)$ )                 | 67 |

**重要なお知らせ(よくお読み下さい)**

STMicroelectronics NV およびその子会社(以下、ST)は、ST 製品及び本書の内容をいつでも予告なく変更、修正、改善、改定及び改良する権利を留保します。購入される方は、発注前に ST 製品に関する最新の関連情報を必ず入手してください。ST 製品は、注文請書発行時点で有効な ST の販売条件に従って販売されます。

ST 製品の選択並びに使用については購入される方が全ての責任を負うものとします。購入される方の製品上の操作や設計に関して ST は一切の責任を負いません。明示又は默示を問わず、ST は本書においていかなる知的財産権の実施権も許諾致しません。

本書で説明されている情報とは異なる条件で ST 製品が再販された場合、その製品について ST が与えたいかなる保証も無効となります。

ST および ST ロゴは STMicroelectronics の商標です。ST の登録商標については ST ウェブサイトをご覧ください。[www.st.com/trademarks](http://www.st.com/trademarks). その他の製品またはサービスの名称は、それぞれの所有者に帰属します。

本書の情報は本書の以前のバージョンで提供された全ての情報に優先し、これに代わるものです。

© 2023 STMicroelectronics – All rights reserved