# 参考資料

life.augmented

AN4488

## アプリケーション・ノート

### STM32F4xxxx マイクロコントローラ・ハードウェア開発の手引書

## はじめに

このアプリケーション・ノートは、開発ボードのハードウェア実装の概要を知る必要があるシステム設計者を対象としており、次のような機能について説明します。

- 電源

- パッケージの選択

- クロック管理

- リセット制御

- ブート・モード設定

- デバッグ管理

本書は、[表 1](#) にリストされている高密度、高性能マイクロコントローラの使用方法、およびそれらの製品を使用してアプリケーションを開発するために必要な最小ハードウェア・リソースについて説明します。

本書には、詳細なリファレンスデザインの回路図のほか、主要コンポーネント、インターフェース、およびモードに関する説明も記載されています。

表 1. 対象とする製品

| タイプ        | 部品番号と製品ライン              |

|------------|-------------------------|

| マイクロコントローラ | STM32F401xB/STM32F401xC |

|            | STM32F401xD/STM32F401xE |

|            | STM32F405/415 ライン       |

|            | STM32F407/417 ライン       |

|            | STM32F410x8/STM32F410xB |

|            | STM32F411xC/STM32F411xE |

|            | STM32F412xE/STM32F412xG |

|            | STM32F413/423 ライン       |

|            | STM32F427/437 ライン       |

|            | STM32F429/439 ライン       |

|            | STM32F446 ライン           |

|            | STM32F469/479 ライン       |

# 参考資料

## 目次

AN4488

## 目次

|       |                                            |    |

|-------|--------------------------------------------|----|

| 1     | 参照文献 .....                                 | 6  |

| 2     | 電源 .....                                   | 7  |

| 2.1   | デジタル電源 .....                               | 7  |

| 2.1.1 | 電圧レギュレータ .....                             | 7  |

| 2.1.2 | レギュレータ OFF モード .....                       | 7  |

| 2.2   | 電源供給方法 .....                               | 9  |

| 2.3   | アナログ電源 .....                               | 12 |

| 3     | リセットおよび電源供給スーパバイザ .....                    | 13 |

| 3.1   | システム・リセット .....                            | 13 |

| 3.1.1 | NRST 回路例 .....                             | 13 |

| 3.2   | 電源供給スーパバイザ .....                           | 15 |

| 3.2.1 | PDR_ON 回路例 .....                           | 15 |

| 3.2.2 | パワーオン・リセット (POR) / パワーダウン・リセット (PDR) ..... | 18 |

| 3.2.3 | プログラム可能な電圧検出器 (PWD) .....                  | 18 |

| 4     | パッケージ .....                                | 20 |

| 4.1   | パッケージの選択 .....                             | 20 |

| 4.2   | ピンの互換性 .....                               | 21 |

| 4.2.1 | I/O 速度 .....                               | 21 |

| 4.3   | オルタネート機能 .....                             | 23 |

| 4.3.1 | 未使用ピンの処理 .....                             | 24 |

| 4.4   | ブート・モード選択 .....                            | 25 |

| 4.4.1 | ブート・モード選択 .....                            | 25 |

| 4.5   | BOOT ピン接続 .....                            | 26 |

| 4.6   | 内蔵ブート・ローダ・モード .....                        | 26 |

| 5     | デバッグ管理 .....                               | 28 |

| 5.1   | SWJ デバッグ・ポート (シリアル・ワイヤと JTAG) .....        | 28 |

| 5.2   | ピンとデバッグ・ポート・ピン .....                       | 28 |

| 5.2.1 | SWJ デバッグ・ポート・ピン .....                      | 29 |

| 5.2.2 | JTAG ピンでの内部プルアップ / プルダウン抵抗 .....           | 29 |

# 参考資料

AN4488

目次

|           |                                           |           |

|-----------|-------------------------------------------|-----------|

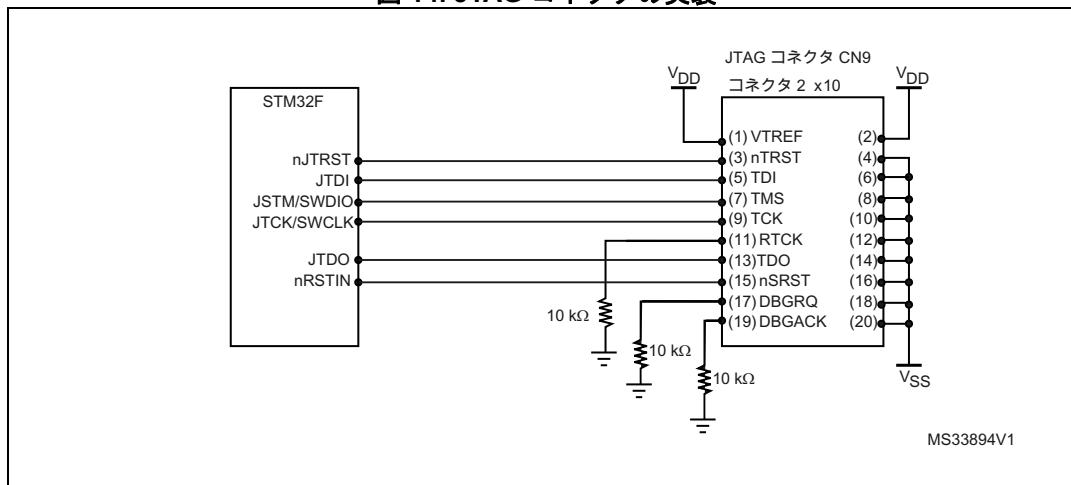

| 5.2.3     | SWJ デバッグ・ポートと標準 JTAG コネクタの接続              | 30        |

| <b>6</b>  | <b>クロック</b>                               | <b>31</b> |

| 6.1       | HSE OSC クロック                              | 31        |

| 6.2       | LSE OSC クロック                              | 32        |

| <b>7</b>  | <b>参照設計</b>                               | <b>33</b> |

| <b>8</b>  | <b>STM32F4xxxx デバイスの推奨する PCB 配線ガイドライン</b> | <b>35</b> |

| 8.1       | PCB スタックアップ                               | 35        |

| 8.2       | クリスタル・オシレータ                               | 36        |

| 8.3       | 電源デカップリング                                 | 36        |

| 8.4       | ハイスピード信号レイアウト                             | 37        |

| 8.4.1     | SDMMC バス・インターフェース                         | 37        |

| 8.4.2     | フレキシブル・メモリ・コントローラ (FMC) インタフェース           | 38        |

| 8.4.3     | クワッド・シリアル・パラレル・インターフェース (Quad SPI)        | 39        |

| 8.4.4     | 組込みトレース・マクロセル (ETM)                       | 39        |

| <b>9</b>  | <b>よくある質問</b>                             | <b>40</b> |

| 9.1       | STM32F4xxxx の識別                           | 40        |

| 9.2       | 使用可能なハードウェア・ツール                           | 40        |

| 9.2.1     | Nucleo ボード                                | 40        |

| 9.2.2     | ディスカバリ・キット                                | 40        |

| 9.2.3     | 評価ボード                                     | 40        |

| 9.2.4     | IBIS モデルはどこにありますか。                        | 41        |

| 9.3       | マイクロコントローラが正常に動作しない                       | 41        |

| <b>10</b> | <b>結論</b>                                 | <b>42</b> |

| <b>11</b> | <b>改版履歴</b>                               | <b>43</b> |

# 参考資料

表の一覧

AN4488

## 表の一覧

|       |                                  |    |

|-------|----------------------------------|----|

| 表 1.  | 対象とする製品 .....                    | 1  |

| 表 2.  | 参照文献 .....                       | 6  |

| 表 3.  | パッケージ一覧 .....                    | 20 |

| 表 4.  | I/O AC 特性 .....                  | 21 |

| 表 5.  | オルタネート機能 .....                   | 23 |

| 表 6.  | ブート・モード .....                    | 25 |

| 表 7.  | STM32F4xxxx ブートローダ通信ペリフェラル ..... | 26 |

| 表 8.  | デバッグ・ポート・ピンの割当て .....            | 29 |

| 表 9.  | マイクロコントローラが正常に動作しない .....        | 41 |

| 表 10. | 文書改版履歴 .....                     | 43 |

| 表 11. | 日本語版文書改版履歴 .....                 | 44 |

## 図の一覧

|       |                                                                                                                                                 |    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 図 1.  | BYPASS_REG スーパバイザ・リセット接続 .....                                                                                                                  | 8  |

| 図 2.  | 電源供給方式 (STM32F469xx/F479xx を除く) .....                                                                                                           | 10 |

| 図 3.  | 電源供給方式 (STM32F469xx/F479xx) .....                                                                                                               | 11 |

| 図 4.  | リセット回路 .....                                                                                                                                    | 13 |

| 図 5.  | NRST 回路例 (STM32F410xx、STM32F411xx、<br>STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、STM32F469xx、<br>および STM32F479xx の場合のみ) .....              | 14 |

| 図 6.  | NRST 回路タイミング例 (ノンスケール、STM32F410xx、<br>STM32F411xx、STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、<br>STM32F469xx、および STM32F479xx の場合のみ) .....  | 15 |

| 図 7.  | 簡単な PDR_ON 回路例 (STM32F410xx、<br>STM32F411xx、STM32F413xx、STM32F423xx、STM32F412xx、STM32F446xx、<br>STM32F469xx、および STM32F479xx の場合は不要) .....       | 16 |

| 図 8.  | PDR_ON タイミング例 (ノンスケール、STM32F410xx、<br>STM32F411xx、STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、<br>STM32F469xx、および STM32F479xx の場合は不要) ..... | 17 |

| 図 9.  | パワーオン・リセット / パワーダウン・リセット波形 .....                                                                                                                | 18 |

| 図 10. | PVD の閾値 .....                                                                                                                                   | 19 |

| 図 11. | STM32CubeMX の例のスクリーンショット .....                                                                                                                  | 24 |

| 図 12. | BOOT モード選択の実装例 .....                                                                                                                            | 26 |

| 図 13. | ホストとボードの接続 .....                                                                                                                                | 28 |

| 図 14. | JTAG コネクタの実装 .....                                                                                                                              | 30 |

| 図 15. | HSE 外部クロック .....                                                                                                                                | 31 |

| 図 16. | HSE クリスタル / セラミック発振子 .....                                                                                                                      | 31 |

| 図 17. | LSE 外部クロック .....                                                                                                                                | 32 |

| 図 18. | LSE クリスタル / セラミック発振子 .....                                                                                                                      | 32 |

| 図 19. | 参照回路図 .....                                                                                                                                     | 33 |

| 図 20. | 部品表 .....                                                                                                                                       | 34 |

| 図 21. | 4 層 PCB スタックアップ例 .....                                                                                                                          | 35 |

| 図 22. | 6 層 PCB スタックアップ例 .....                                                                                                                          | 36 |

| 図 23. | V <sub>DD</sub> /V <sub>SS</sub> ペアの標準レイアウト .....                                                                                               | 37 |

| 図 24. | STM32 ST-LINK ユーティリティ .....                                                                                                                     | 40 |

# 参考資料

## 1 参照文献

以下のドキュメントを、[www.st.com](http://www.st.com) で入手できます。

表 2. 参照文献

| 文書番号   | タイトル                                             |

|--------|--------------------------------------------------|

| AN2867 | STM8AF/AL/S および STM32 マイクロコントローラ用発振器設計ガイド        |

| AN2606 | STM32 マイクロコントローラ システム・メモリ・ブート・モード                |

| AN3364 | STM32 マイクロコントローラ アプリケーションのマイグレーションと互換性に関するガイドライン |

## 2 電源

動作電圧 ( $V_{DD}$ ) 範囲は 1.8 V ~ 3.6 V ですが、制約を付けて 1.7 V まで下げるすることができます。詳細は、製品データシートを参照してください。内部の 1.2 V デジタル電源を供給するために、レギュレータが搭載されています。

リアルタイム・クロック (RTC) およびバックアップ・レジスタは、主電源  $V_{DD}$  がオフの場合、 $V_{BAT}$  から供給することができます。

### 2.1 デジタル電源

#### 2.1.1 電圧レギュレータ

リセット後、電圧レギュレータは常に使用可能になります。レギュレータは、アプリケーションのモードに応じて、3 種類のモードで動作します。

- RUN モードでは、レギュレータは 1.2 V ドメイン（コア、メモリ、デジタル・ペリフェラル）にフル電力を供給します。

- STOP モードでは、レジスタと SRAM の内容のみを保持するために、レギュレータは 1.2 V ドメインに低電力を供給します。

- STANDBY モードでは、レギュレータは停止状態になります。STANDBY 回路とバックアップドメインに関する内容を除き、レジスタと SRAM の内容は失われます。

注：選択したパッケージによっては、電圧レギュレータを有効または無効にするために  $V_{SS}$  または  $V_{DD}$  に接続する必要があるピンが存在します。詳細については、データシートの電圧レギュレータのセクションを参照してください。

#### 2.1.2 レギュレータ OFF モード

詳細については、データシートの電圧レギュレータのセクションを参照してください。

- BYPASS\_REG =  $V_{DD}$  の場合は、相互に接続されている  $V_{CAP1}$  ピンと  $V_{CAP2}$  ピンからコア電源を供給する必要があります。

- 2 つの  $V_{CAP}$  セラミック・コンデンサは、2 つの 100 nF デカップリング・コンデンサで置き換える必要があります。

- 内部電圧スケーリングは内部では管理されていないので、外部電圧値を目標の最大周波数に合わせる必要があります。

- 内部レギュレータが OFF の場合、V12 の内部監視は行われません。外部電源供給スーパーバイザを使用して、論理電源ドメインの V12 ( $V_{CAP}$ ) を監視する必要があります。

それには、PA0 ピンを使用して、V12 電源ドメインのパワーオン・リセットとして動作させる必要があります。

# 参考資料

- レギュレータ OFF モードでは、以下の機能はサポートされません。

- PA0 は、GPIO ピンとしては使用できません。これは、V12 論理電源ドメインの NRST ピンでリセットされない部分をリセットするためです。

- PA0 がローに保持されている限り、パワーオン・リセット時にデバッグ モードは使用できません。したがって、リセット時またはプリリセット時にデバッグ接続を使用する必要がある場合は、PA0 ピンと NRST ピンを個別に管理する必要があります。

- オーバードライブ・モードとアンダードライブ・モードは使用できません。

- STANDBY モードは使用できません。

図 1. BYPASS\_REG スーパバイザ・リセット接続

- $V_{CAP2}$  はすべてのパッケージで使用できるわけではありません。使用できない場合は、 $V_{CAP1}$  に 100 nF デカップリング・コンデンサを 1つ接続します。

次の条件に従う必要があります。

- 電源ドメイン間の電流注入を避けるために  $V_{DD}$  を常に  $V_{CAP}$  より高電圧に維持する必要があります。

- $V_{CAP}$  が  $V_{12}$  最小値に達するまでの時間が、 $V_{DD}$  が 1.7 V に達する時間よりも短い場合は、PA0 をローに保持して、両方の条件 ( $V_{CAP}$  が  $V_{12}$  最小値に達するまで、および  $V_{DD}$  が 1.7 V に達するまで) に対応する必要があります。

- そうしないと、 $V_{CAP}$  が  $V_{12}$  最小値に達するまでの時間が、 $V_{DD}$  が 1.7 V に達するまでの時間よりも短い場合、PA0 は外部にローとしてアサートされる可能性があります。

- $V_{CAP}$  が  $V_{12}$  最小値を下回り、 $V_{DD}$  が 1.7 V より高い場合、PA0 は外部にローとしてアサートされる必要があります。

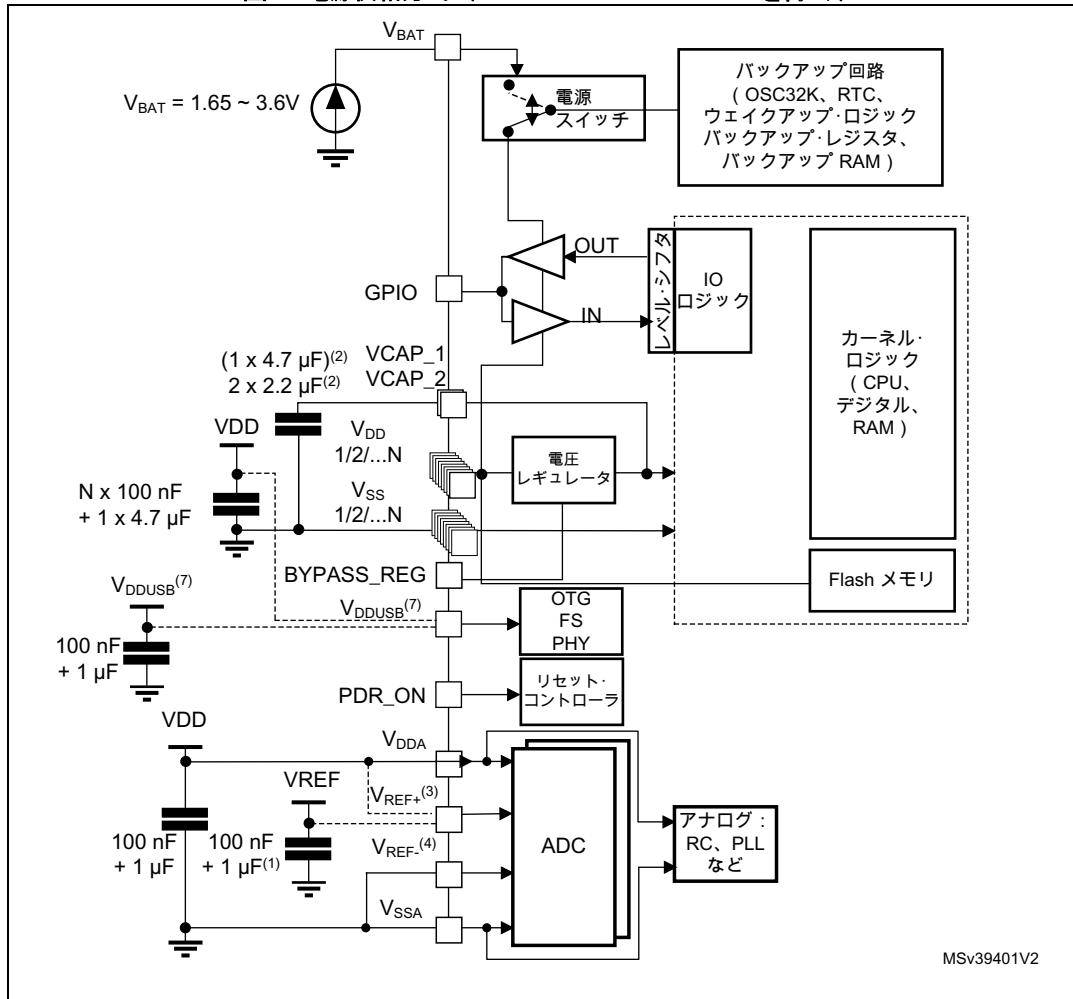

## 2.2 電源供給方法

回路には、安定化電源  $V_{DD}$  から電力を供給します。

**注意：**  $V_{DD}$  の電圧範囲は 1.8 V ~ 3.6 V です（制約を付けて 1.7 V まで下げるることができます。詳細は、該当するデータシートを参照してください）。

- $V_{DD}$  のピンを  $V_{DD}$  電源に接続する場合は、外部デカップリング・コンデンサとして、パッケージにタンタル・コンデンサまたはセラミック・コンデンサ（最小値 4.7  $\mu$ F、標準値 10  $\mu$ F）を 1 つ、 $V_{DD}$  の各ピンに 100 nF セラミック・コンデンサを 1 つずつ、それぞれ接続する必要があります。

- $V_{BAT}$  ピンは、外部バッテリに接続できます ( $1.65 \text{ V} < V_{BAT} < 3.6 \text{ V}$ )。外部バッテリを使用しない場合は、このピンを  $V_{DD}$  に接続し、デカップリング用の 100 nF の外部セラミック・コンデンサを接続することを推奨します。

- $V_{DDA}$  ピンには、デカップリング用の外部コンデンサを 2 つ（100 nF セラミック + 1  $\mu$ F タンタルまたはセラミック）接続する必要があります。

- $V_{REF+}$  ピンは、 $V_{DDA}$  外部電源に接続できます。独立した外部基準電圧が  $V_{REF+}$  に印可されている場合は、100 nF と 1  $\mu$ F のコンデンサをこのピンに接続する必要があります。いずれの場合も、 $V_{REF+}$  は ( $V_{DDA}-1.2 \text{ V}$ ) と  $V_{DDA}$  の間（最小値 1.7 V）に保持する必要があります。

- アナログ・ノイズをフィルタリングするには、事前に次のことに注意してください。

- $V_{DDA}$  は、フェライト・ビーズを介して  $V_{DD}$  に接続できます。

- $V_{REF+}$  ピンは、抵抗を介して  $V_{DDA}$  に接続できます。

- 電圧レギュレータ構成では、電圧レギュレータを有効または無効にするために  $V_{SS}$  または  $V_{DD}$  に接続する必要がある固有の BYPASS\_REG ピンが存在します（すべてのパッケージにあるとは限りません）。

- 詳細は、[セクション 2.1.2](#) および関連するデバイスデータシートの電圧レギュレータのセクションを参照してください。

- 電圧レギュレータが有効な場合、 $V_{CAP1}$  ピンと  $V_{CAP2}$  ピンは、2.2  $\mu$ F、2  $\Omega$ 未満の低 ESR セラミック・コンデンサ 2 つ（または  $V_{CAP1}$  ピンのみを使用可能な一部のパッケージでは 4.7  $\mu$ F、1  $\Omega$ 未満の低 ESR セラミック・コンデンサ 1 つ）に接続する必要があります。

図 2. 電源供給方式 (STM32F469xx/F479xx を除く)

- オプション。独立した外部基準電圧が  $V_{REF+}$  に接続されている場合は、2つのコンデンサ (100 nF と 1 μF) を接続する必要があります。

- $V_{CAP2}$  はすべてのパッケージで使用できるわけではありません。使用できない場合は、 $V_{CAP1}$  に 4.7 μF (1 Ω未満のESR) を 1つ接続します。

- $V_{REF+}$  は、(パッケージに応じて)  $V_{REF+}$  または  $V_{DDA}$  のどちらかに接続します。

- $V_{REF-}$  は、(パッケージに応じて)  $V_{REF-}$  または  $V_{SSA}$  のどちらかに接続します。

- N は  $V_{DD}$  入力と  $V_{SS}$  入力の数です。

- BYPASS\_REG ピンと PDR\_ON ピンの接続は、データシートを参照してください。

- $V_{DDUSB}$  は STM32F446xx でのみ使用可能です。

- バックアップ RAM は STM32F410xx、STM32F411xx、STM32F412xx、STM32F413xx、および STM32F423xx では使用できません。

# 參考資料

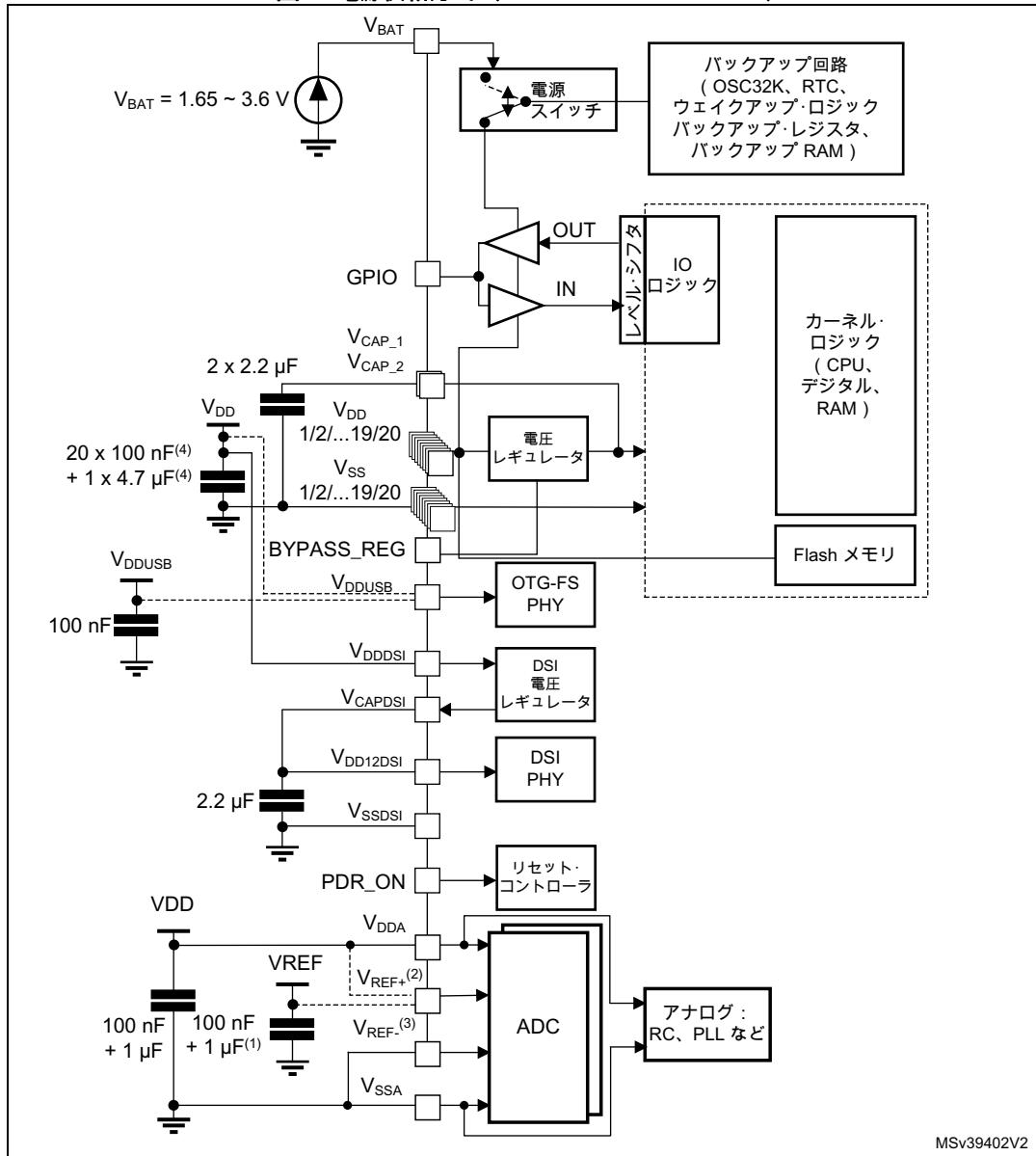

図 3. 電源供給方式 (STM32F469xx/F479xx)

- オプション。独立した外部基準電圧が  $V_{REF+}$  に接続されている場合は、2つのコンデンサ（100 nF と 1  $\mu$ F）を接続する必要があります。

- $V_{REF+}$  は、(パッケージに応じて)  $V_{REF+}$  または  $V_{DDA}$  のどちらかに接続します。

- $V_{REF-}$  は、(パッケージに応じて)  $V_{REF-}$  または  $V_{SSA}$  のどちらかに接続します。

- BYPASS REG ピンと PDR ON ピンの接続は、データシートを参照してください。

## 2.3 アナログ電源

AD 変換の精度を向上させるため、ADC には独立した電源が供給されます。この電源回路は、フィルタやシールドを内蔵しているため、PCB のノイズを防ぐことができます。

- ADC 用の電源入力は、 $V_{DDA}$  ピンから供給されます。

- ADC 電源のグランドは、独立した  $V_{SSA}$  ピンとして用意されています。

いずれの場合も、 $V_{SSA}$  ピンは、VSS と同じグランドに外部で接続する必要があります。

低電圧入力時の精度を確保するため、独立した外部基準電圧を ADC の  $V_{REF+}$  入力に接続できます。 $V_{REF+}$  の電圧は ( $V_{DDA} - 1.2\text{ V}$ ) から  $V_{DDA}$  の範囲になります (最小値  $1.7\text{ V}$ )。

$V_{REF-}$  ピンが用意されているパッケージでは、このピンを外部で  $V_{SSA}$  に固定する必要があります。

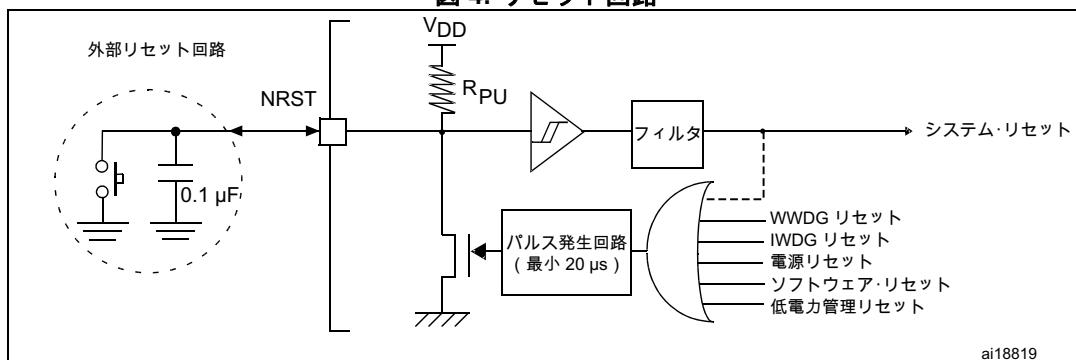

## 3 リセットおよび電源供給スーパーバイザ

### 3.1 システム・リセット

システム・リセットは、クロック・コントローラ CSR レジスタのリセット・フラグとバックアップ・ドメインのレジスタを除き、すべてのレジスタをリセット値にセットします（図 2 を参照）。

システム・リセットは、次のイベントのいずれかの発生時に生成されます。

1. NRST ピンのロー・レベル（外部リセット）

2. ウィンドウ型ウォッチドッグのカウント終了条件（WWDG リセット）

3. 独立型ウォッチドッグのカウント終了条件（IWDG リセット）

4. ソフトウェア・リセット（SW リセット）

5. 低電力管理リセット

リセット・ソースは、制御/ステータス・レジスタ（RCC\_CSR）のリセット・フラグを確認することによって識別できます。

表 1 にリストされている製品は、正常にパワーアップするために外部リセット回路を必要としません。図 4 に例示されているように、寄生回路によるリセットからデバイスを保護することによって EMS 性能を向上させるには、プルダウン・コンデンサのみを推奨します。

内部抵抗を介してプルダウン・コンデンサの充電と放電を行うと、デバイスの消費電力が増加します。コンデンサ推奨値（100 nF）を 10 nF まで減らして、この消費電力を制限できます。

図 4. リセット回路

#### 3.1.1 NRST 回路例

この例は、STM32F410xx、STM32F411xx、STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、および STM32F469 に適用されます。PDR\_ON を V<sub>SS</sub> に接続すると、内部リセット回路を恒久的に無効にできます。

# 参考資料

## 制限事項 :

- PDR\_ON = 0 は、主に  $V_{DD}$  電源が 1.7 V ~ 1.9V (すなわち、1.8V ±5% 電源) の場合に使用します。電源範囲が最小値の 1.8V を下回ることがない場合、これは内部回路で管理するほうが適切です (リセット・コントローラが完全に内蔵されており、コンポーネントを追加する必要はありません)。

- 内部リセットがオフの場合、以下の統合機能はサポートされなくなります。

- 統合パワーオン・リセット (POR) /パワーダウン・リセット (PDR) 回路は無効になります。

- ブラウンアウト・リセット (BOR) 回路は無効にする必要があります。

- 内蔵のプログラム可能な電圧検出器 (PWD) は無効になります。

- VBAT 機能は使用できなくなり、 $V_{BAT}$  ピンを  $V_{DD}$  に接続する必要があります。

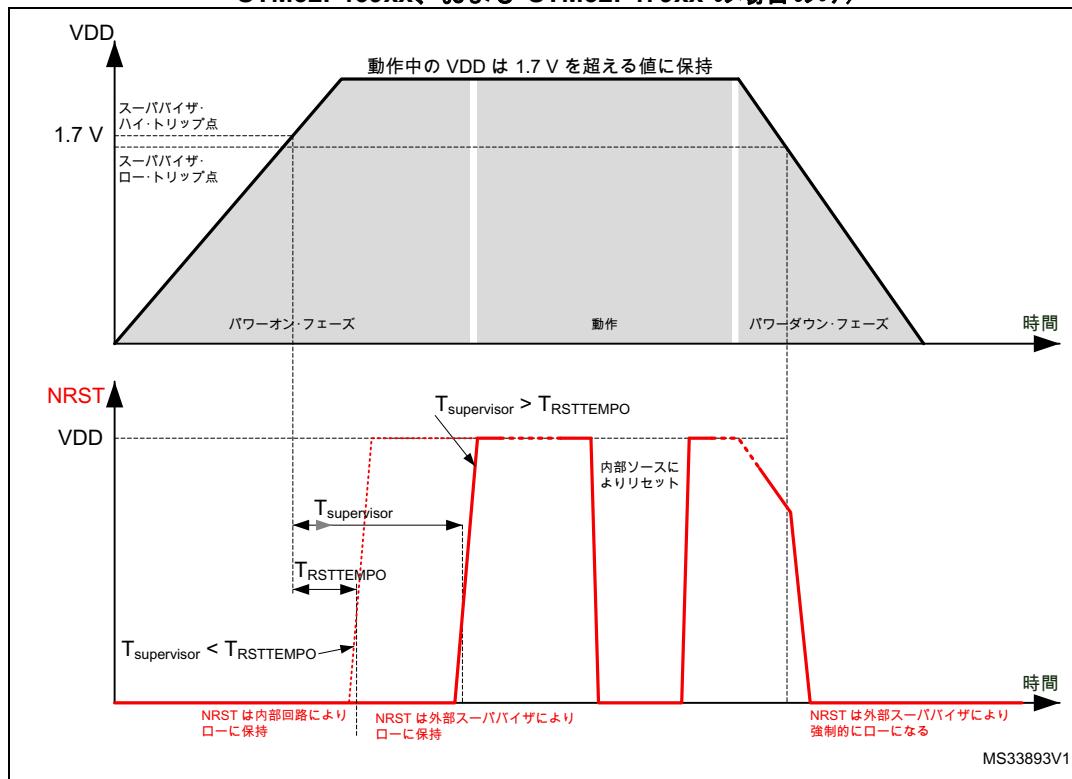

図 5. NRST 回路例 (STM32F410xx、STM32F411xx、

STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、STM32F469xx、

および STM32F479xx の場合のみ)

PDR\_ON=0 であっても、パワーアップ中の NRST は、内部アナログ回路を安定化できるように、 $T_{RSTTEMPO}$  中は内部リセット・コントローラによってローに駆動されます。実際のタイミング値は、STM32F4xxxx のデータシートを参照してください。

図 6. NRST 回路タイミング例（ノンスケール、STM32F410xx、

STM32F411xx、STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、

STM32F469xx、および STM32F479xx の場合のみ）

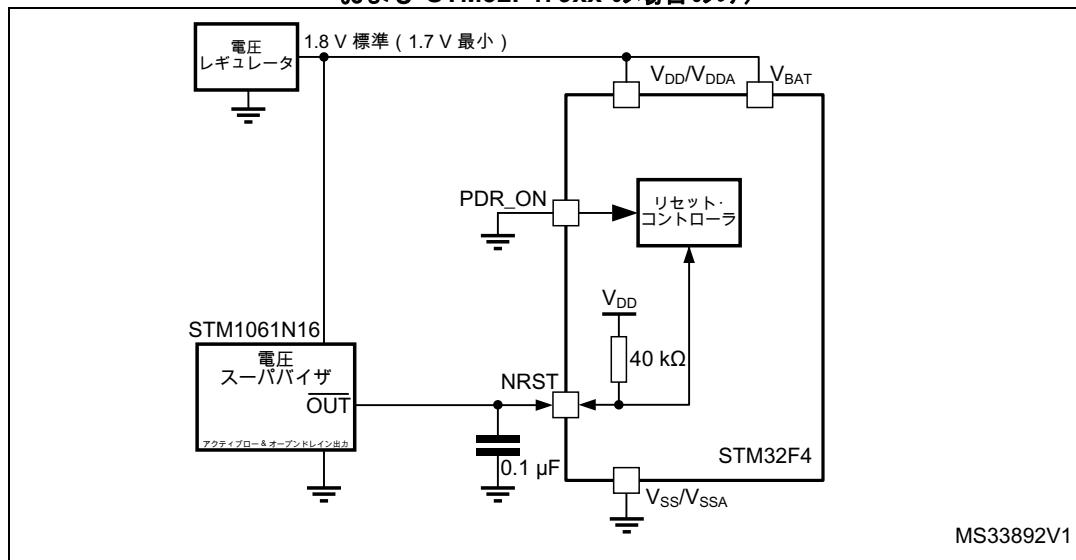

## NRST 電圧スーパーバイザの選択

電圧スーパーバイザには、以下の特性が必要です。

- リセット出力はアクティブロー、オープンドレイン（電圧がトリップ点を下回っている場合にローに駆動される出力）

- スーパーバイザのトリップ点（許容値とヒステリシスを含む）は予想される  $V_{DD}$  範囲に収まっている必要があります。

- スーパーバイザ仕様で通常指定されているのは電源電圧の立ち下がり時のトリップ点なので、パワーオン・フェーズを確認する場合はヒステリシスを加える必要があります。

## 3.2 電源供給スーパーバイザ

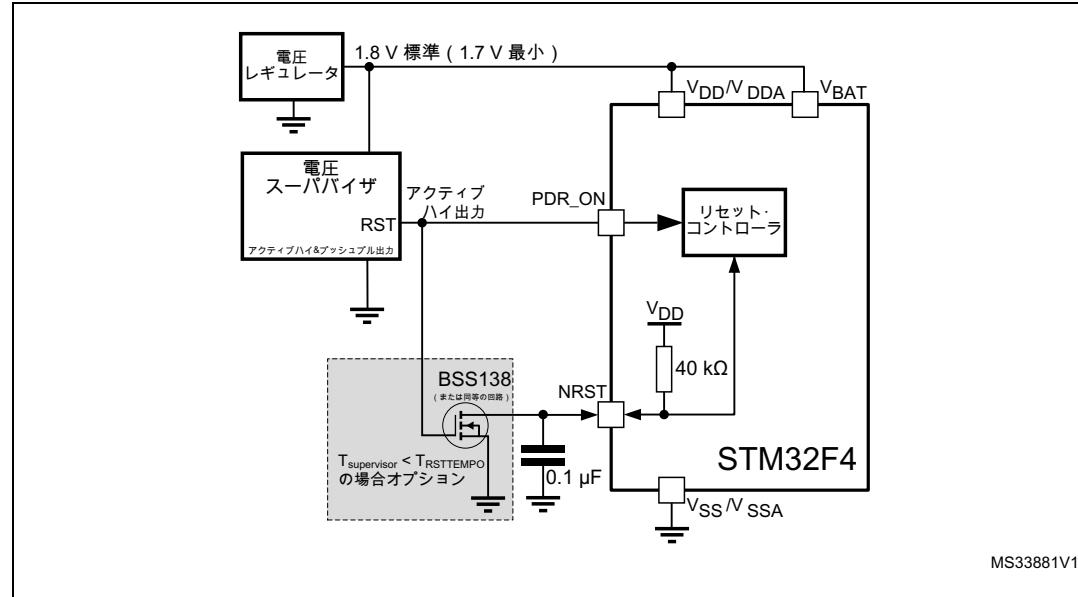

### 3.2.1 PDR\_ON 回路例

注：この例は、STM32F410xx、STM32F411xx、STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、STM32F469xx、および STM32F479xx の場合は適用されません。その場合は、PDR\_ON を VSS に接続すると、恒久的に内部リセット回路を無効にできます（NRST ピンに外部電源供給スーパーバイザを接続する必要があります）。他の STM32F4xxxx 製品向けに作成された回路は、下位互換性があるので、STM32F410xx、STM32F411xx、STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、STM32F469xx、および STM32F479xx で動作します。

注：以下に示す回路とは異なる回路を使用する場合は、お住まいの地域の ST マイクロエレクトロニクスの販売代理店までご連絡いただくか、[www.st.com](http://www.st.com) をご覧ください。

# 参考資料

## 制限事項 :

- PDR\_ON = 0 は、主に V<sub>DD</sub> 電源が 1.7 V ~ 1.9V (すなわち、1.8V ±5% 電源) の場合に使用します。電源範囲が最小値の 1.8 V を下回ることがない場合、これは内部回路で管理するほうが適切です (リセット・コントローラが完全に内蔵されており、コンポーネントを追加する必要はありません)。

- 安全なパワーダウンを保証するために、外部電圧スーパバイザ (または同等の回路) により、パワーオフ・シーケンス中に PDR\_ON=1 に駆動する必要があります。

内部リセットがオフの場合、以下の統合機能はサポートされなくなります。

- 統合パワーオン・リセット (POR) //パワーダウン・リセット (PDR) 回路は無効になります。

- ブラウンアウト・リセット (BOR) 回路は無効にする必要があります。

- 内蔵のプログラム可能な電圧検出器 (PWD) は無効になります。

- V<sub>BAT</sub> 機能は使用できなくなり、V<sub>BAT</sub> ピンを V<sub>DD</sub> に接続する必要があります。

図 7. 簡単な PDR\_ON 回路例 (STM32F410xx、STM32F411xx、STM32F413xx、STM32F423xx、STM32F412xx、STM32F446xx、STM32F469xx、および STM32F479xx の場合は不要)

MS33881V1

# 参考資料

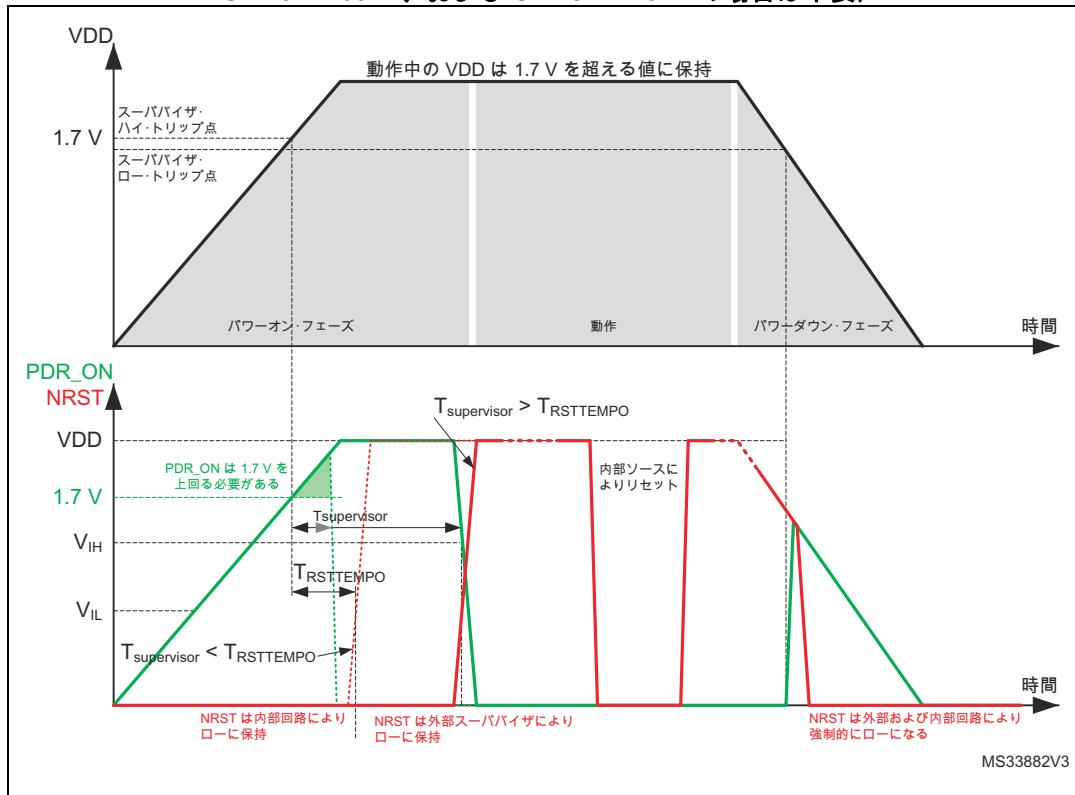

図 8. PDR\_ON タイミング例（ノンスケール、STM32F410xx、

STM32F411xx、STM32F412xx、STM32F413xx、STM32F423xx、STM32F446xx、

STM32F469xx、および STM32F479xx の場合は不要）

## PDR\_ON 電圧スーパー・バイザの選択

電圧スーパー・バイザには、以下の特性が必要です。

- リセット出力はアクティブハイ、プッシュプル（電圧がトリップ点を下回っている場合にハイに駆動される出力）

- スーパー・バイザのトリップ点（許容値とヒステリシスを含む）は予想される  $V_{DD}$  範囲に収まっている必要があります。

スーパー・バイザ仕様で通常指定されているのは電源電圧の立ち上がり時のトリップ点なので、パワーオン・フェーズを確認する場合はヒステリシスを加える必要があります。

例：

- 電圧レギュレータ  $1.8V \pm 5\%$  は  $V_{DD}$  最小値  $1.71V$  を意味します。

- スーパー・バイザが  $1.66V \pm 2.5\%$ （ヒステリシス  $0.5\%$ ）であるということは以下を意味します。

- 立ち上がり時トリップ最大値 =  $1.71V$  ( $1.66V + 2.5\% + 0.5\%$ )

- 立ち下がり時トリップ最小値 =  $1.62V$  ( $1.66V - 2.5\%$ )

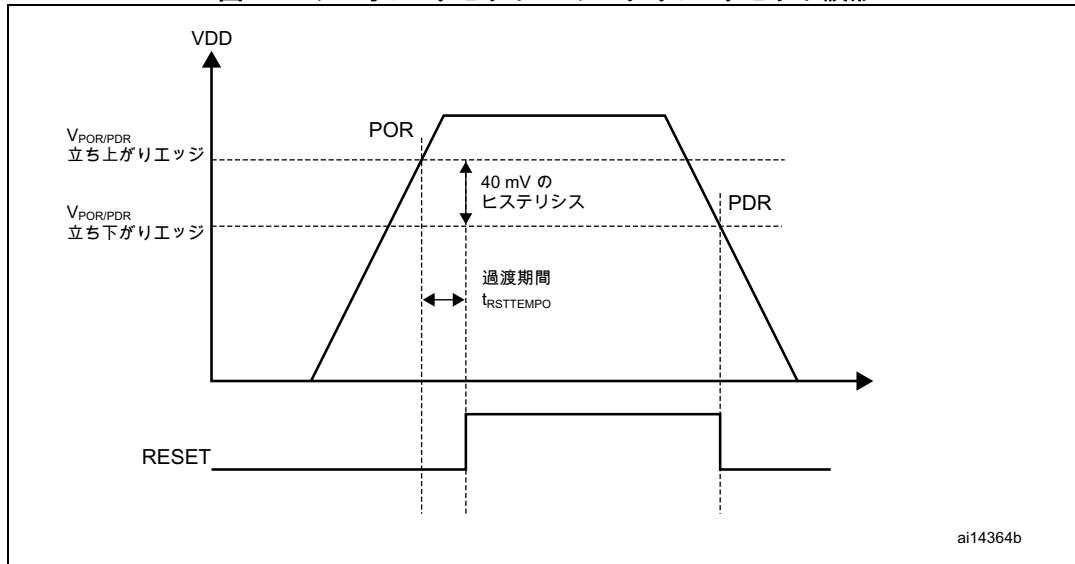

### 3.2.2 パワーオン・リセット (POR) /パワーダウン・リセット (PDR)

このデバイスには、1.8 V 以上での正常な動作を可能にする POR/PDR 統合回路が搭載されています。

デバイスは、 $V_{DD}$  が規定の閾値  $V_{POR/PDR}$  を下回っている間は、外部のリセット回路を必要とせずに、リセットモードを維持します。POR/PDR 閾値の詳細については、製品データシートの電気的特性を参照してください。

図 9. パワーオン・リセット/パワーダウン・リセット波形

- $t_{RSTTEMPO}$  は約 2.6 ms です。 $V_{POR/PDR}$  立ち上がりエッジは 1.74 V (標準)、 $V_{POR/PDR}$  立ち下がりエッジは 1.70 V (標準) です。実際の値については、STM32F4xxxx のデータシートを参照してください。

内部パワーオン・リセット (POR) /パワーダウン・リセット (PDR) 回路は、PDO\_ON ピンによって無効になります。外部電源供給スーパーバイザでは  $V_{DD}$  を監視する必要があります、 $V_{DD}$  が指定されている閾値を下回っている間はデバイスをリセットモードに維持する必要があります。PDR\_ON は、この外部電源供給スーパーバイザに接続する必要があります。詳細は、[セクション 3.2.1](#) を参照してください。

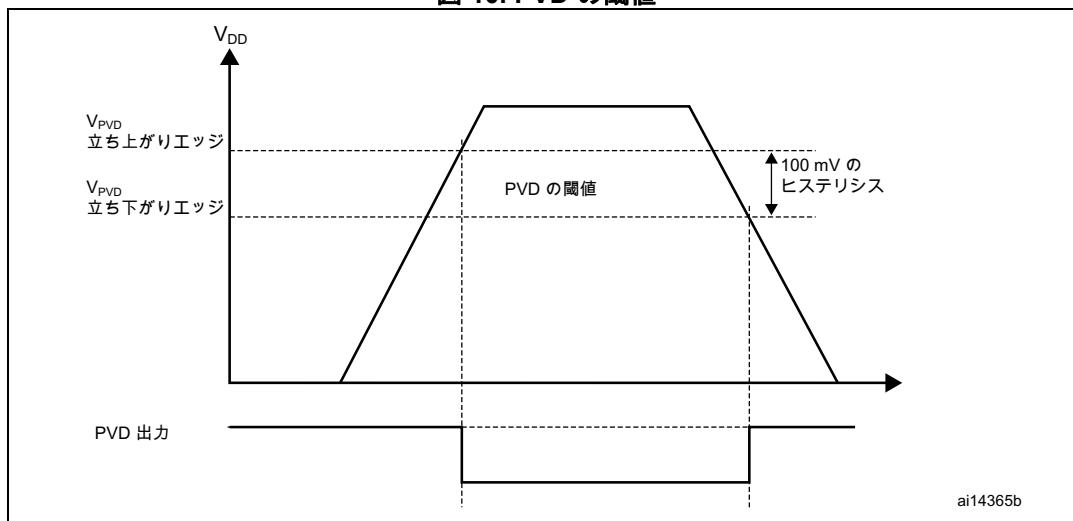

### 3.2.3 プログラム可能な電圧検出器 (PVD)

PVD を使用した  $V_{DD}$  電源の監視が可能です。電源制御レジスタ (PWR\_CR) の PLS[2:0] ビットで選択した閾値と比較することで監視します。

PVD は PVDE ビットをセットすることで有効になります。

$V_{DD}$  が PVD の閾値よりも高いか低いかを示すために、電源制御/ステータスレジスタ (PWR\_CSR) の PVDO フラグが使用できます。このイベントは EXTI のライン 16 に内部接続され、EXTI レジスタで有効な場合は割り込みリクエストを生成させることができます。EXTI ライン 16 の立ち上がり/立ち下がりエッジの設定に応じて、 $V_{DD}$  が PVD の閾値を下回るか、上回ったとき、あるいはその両方で、PVD 出力割り込みを生成させることができます。たとえば、サービスルーチンで、緊急停止処理を実行することなどができます。

# 参考資料

AN4488

リセットおよび電源供給スーパーバイザ

図 10. PVD の閾値

## 4 パッケージ

### 4.1 パッケージの選択

パッケージを選択する際は、アプリケーションに強く依存する制約を考慮する必要があります。

以下のリストに、よくある制約をまとめます。

- 必要なインターフェースの数。

パッケージによっては、一部のインターフェースを使用できない場合があります。

- パッケージによっては、一部のインターフェースを組み合わせることができない場合があります。

- PCB テクノロジーの制約。

ピッチを小さく、ボール密度を高くするには、PCB の層数を増やし、上位クラスの PCB が必要となる場合があります。

- パッケージの高さ

- PCB の使用可能面積

- ハイスピード・インターフェースのノイズ輻射またはシグナル・インテグリティ。

パッケージが小さいほどシグナル・インテグリティが向上します。ピッチが小さくボール密度が高くなると、PCB を多層にする必要があり、電源/グラウンドをより適切に分配できるので、シグナル・インテグリティはさらに向上します。

- 他のデバイスとの互換性。

表 3 に、すべての STM32F4xxxx ファミリの使用可能パッケージをまとめます。

表 3. パッケージ一覧

| サイズ (mm) <sup>(1)</sup>        | 10 x 10 | 10 x 14 | 14 x 14 | 20 x 20 | 24 x 24 | 28 x 28 | 13 x 13  | 7 x 7    | 7 x 7    | 7 x 7    | 10 x 10  | 7 x 7    | 10 x 10  | 2.553 x 2.579 | 3.034 x 3.220 | 3.060 x 3.060 | 3.658 x 3.686 | 4.039 x 3.951 | 5.693 x 3.815 | 4.223 x 4.223 | 4.521 x 5.547 | 4.891 x 5.692 |          |

|--------------------------------|---------|---------|---------|---------|---------|---------|----------|----------|----------|----------|----------|----------|----------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----------|

| 販売番号                           | LQFP64  | LQFP100 | LQFP144 | LQFP144 | LQFP176 | LQFP208 | TFBGA216 | UFQFPN48 | UFQFPN48 | UFQFPN48 | UFBGA100 | UFBGA144 | UFBGA144 | UFBGA169      | UFBGA176      | WLCSP36       | WLCSP49       | WLCSP49       | WLCSP81       | WLCSP81       | WLCSP90       | WLCSP143      | WLCSP168 |

| STM32F401xB/C<br>STM32F401xD/E | X       | X       |         |         |         |         | X        | X        |          |          |          |          |          |               | X             |               |               |               |               |               |               |               |          |

| STM32F405xx/407xx              | X       | X       | X       | X       |         |         |          |          |          |          |          |          |          | X             |               |               |               |               |               |               | X             |               |          |

| STM32F410xx                    | X       |         |         |         |         |         | X        |          |          |          |          |          |          |               | X             |               |               |               |               |               |               |               |          |

| STM32F411xx                    | X       | X       |         |         |         |         | X        | X        |          |          |          |          |          |               |               | X             |               |               |               |               |               |               |          |

| STM32F412xx                    | X       | X       | X       |         |         |         | X        | X        |          | X        |          |          |          |               |               |               |               | X             |               |               |               |               |          |

| STM32F413xx/423xx              | X       | X       | X       |         |         |         | X        | X        |          | X        |          |          |          |               |               |               |               | X             |               |               |               |               |          |

| STM32F415xx/417xx              | X       | X       | X       | X       |         |         |          |          |          |          |          |          |          |               | X             |               |               |               |               |               | X             |               |          |

| STM32F427xx/429xx              |         | X       | X       | X       | X       | X       |          |          |          |          |          |          |          | X             | X             |               |               |               |               |               | X             |               |          |

| STM32F437xx/439xx              |         | X       | X       | X       | X       | X       |          |          |          |          |          |          |          | X             | X             |               |               |               |               |               | X             |               |          |

| STM32F446XX                    | X       | X       | X       |         |         |         |          |          | X        | X        |          |          |          |               |               |               |               |               | X             |               |               |               |          |

| STM32F469xx                    |         |         |         | X       | X       | X       |          |          |          |          |          |          |          | X             | X             |               |               |               |               |               |               | X             |          |

| STM32F479xx                    |         |         |         | X       | X       | X       |          |          |          |          |          |          |          | X             | X             |               |               |               |               |               |               | X             |          |

1. 本体サイズ（ピンを除く）

## 4.2 ピンの互換性

### 4.2.1 I/O 速度

- GPIO を I/O として使用する場合、意図したとおりの動作を保証するには、設計上の考慮が必要になります。

- 負荷容量が大きくなると、I/O ピンの立ち上がり／立ち下がり時間が長くなります。この容量には、基板トレースの影響が含まれています。

- I/O 特性については、製品のデータシートを参照してください。

- [表 4](#) に、STM32F469xx の I/O AC 特性を示します。

表 4. I/O AC 特性<sup>(1)(2)</sup>

| OSPEEDRy[1:0]<br>ビット値 <sup>(1)</sup> | 記号                          | パラメータ                                                 | 条件                                                               | 最小値 | 標準値 | 最大値                | 単位  |

|--------------------------------------|-----------------------------|-------------------------------------------------------|------------------------------------------------------------------|-----|-----|--------------------|-----|

| 00                                   | $f_{max(IO)out}$            | 最大周波数                                                 | $C_L = 50 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 4                  | MHz |

|                                      |                             |                                                       | $C_L = 50 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 2                  |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 8                  |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$                 | -   | -   | 4                  |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 3                  |     |

|                                      | $t_{f(IO)out}/t_{r(IO)out}$ | 出力のハイ・レベルからロー・レベルへの立ち下がり時間と出力のロー・レベルからハイ・レベルへの立ち上がり時間 | $C_L = 50 \text{ pF}, V_{DD} = 1.7 \text{ V} \sim 3.6 \text{ V}$ | -   | -   | 100                | ns  |

|                                      | $f_{max(IO)out}$            | 最大周波数 <sup>(3)</sup>                                  | $C_L = 50 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 25                 | MHz |

|                                      |                             |                                                       | $C_L = 50 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$                 | -   | -   | 12.5               |     |

|                                      |                             |                                                       | $C_L = 50 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 10                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 50                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$                 | -   | -   | 20                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 12.5               |     |

| 01                                   | $f_{max(IO)out}$            | 出力のハイ・レベルからロー・レベルへの立ち下がり時間と出力のロー・レベルからハイ・レベルへの立ち上がり時間 | $C_L = 50 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 10                 | ns  |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 6                  |     |

|                                      |                             |                                                       | $C_L = 50 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 20                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 10                 |     |

|                                      |                             |                                                       | $C_L = 40 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 50 <sup>(3)</sup>  | MHz |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 100 <sup>(3)</sup> |     |

|                                      | $t_{f(IO)out}/t_{r(IO)out}$ | 最大周波数 <sup>(3)</sup>                                  | $C_L = 40 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 25                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$                 | -   | -   | 50                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 42.5               |     |

|                                      |                             |                                                       | $C_L = 40 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 6                  | ns  |

| 10                                   | $t_{f(IO)out}/t_{r(IO)out}$ | 出力のハイ・レベルからロー・レベルへの立ち下がり時間と出力のロー・レベルからハイ・レベルへの立ち上がり時間 | $C_L = 10 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$                 | -   | -   | 4                  |     |

|                                      |                             |                                                       | $C_L = 40 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 10                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 6                  |     |

|                                      |                             |                                                       | $C_L = 40 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 10                 |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$                 | -   | -   | 6                  |     |

# 参考資料

表 4. I/O AC 特性<sup>(1)(2)</sup> (続き)

| OSPEEDRy[1:0]<br>ビット値 <sup>(1)</sup> | 記号                          | パラメータ                                                 | 条件                                               | 最小値 | 標準値 | 最大値                | 単位  |

|--------------------------------------|-----------------------------|-------------------------------------------------------|--------------------------------------------------|-----|-----|--------------------|-----|

| 11                                   | $f_{max(IO)out}$            | 最大周波数 <sup>(3)</sup>                                  | $C_L = 30 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$ | -   | -   | 100 <sup>(3)</sup> | MHz |

|                                      |                             |                                                       | $C_L = 30 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$ | -   | -   | 50                 |     |

|                                      |                             |                                                       | $C_L = 30 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$ | -   | -   | 42.5               |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$ | -   | -   | 180 <sup>(3)</sup> |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$ | -   | -   | 100                |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$ | -   | -   | 72.5               |     |

|                                      | $t_{f(IO)out}/t_{r(IO)out}$ | 出力のハイ・レベルからロー・レベルへの立ち下がり時間と出力のロー・レベルからハイ・レベルへの立ち上がり時間 | $C_L = 30 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$ | -   | -   | 4                  | ns  |

|                                      |                             |                                                       | $C_L = 30 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$ | -   | -   | 6                  |     |

|                                      |                             |                                                       | $C_L = 30 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$ | -   | -   | 7                  |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 2.7 \text{ V}$ | -   | -   | 2.5                |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.8 \text{ V}$ | -   | -   | 3.5                |     |

|                                      |                             |                                                       | $C_L = 10 \text{ pF}, V_{DD} \geq 1.7 \text{ V}$ | -   | -   | 4                  |     |

| -                                    | $t_{EXTIpw}$                | EXTI コントローラで検出される外部信号のパルス幅                            | -                                                | 10  | -   | -                  | ns  |

1. 設計保証。

2. I/O 速度は OSPEEDRy[1:0] ビットで設定します。GPIOx\_SPEEDR GPIO ポートの出力スピード・レジスタの説明については、STM32F4xx リファレンス・マニュアルを参照してください。

3. 最大周波数が 50 MHz を超え、 $V_{DD} > 2.4 \text{ V}$  の場合、プロセスのばらつきの影響を最小限に抑えるために、IO 補正セルを有効にして、立ち上がり/立ち下がり時のオーバーシュートを減らすことができます。

## 4.3 オルタネート機能

マイクロコントローラの各ピンは、複数の機能に設定できます。これらの機能は、ソフトウェアによって選択されます。

I/O オルタネート機能の詳細については、選択したデバイスのデータシートを参照してください。ピン設定に使用するレジスタについては、リファレンス・マニュアルを参照してください。

表 5. オルタネート機能

| ポート      |      | AF0       | AF1           | AF2          | AF3              | AF4           | AF5                       | AF6             | AF7                       | AF8                        | AF9                                            | AF10                                | AF11                                     | AF12                         | AF13                 | AF14   | AF15          |

|----------|------|-----------|---------------|--------------|------------------|---------------|---------------------------|-----------------|---------------------------|----------------------------|------------------------------------------------|-------------------------------------|------------------------------------------|------------------------------|----------------------|--------|---------------|

|          |      | SYS       | TIM1/2        | TIM3/4/5     | TIM8/9/<br>10/11 | I2C1/2/<br>3  | SPI1/2/<br>3/4/5/6        | SPI2/3/<br>SAI1 | SPI2/3/<br>USART<br>1/2/3 | USART6/<br>UART4/<br>5/7/8 | CAN1/2/<br>TIM12/<br>13/14/<br>QUAD<br>SPI/LCD | QUADS<br>PI/OTG2<br>_HS/OT<br>G1_FS | ETH                                      | FMC/<br>SDIO/<br>OTG2_<br>FS | DCMI/<br>DSI<br>HOST | LCD    | SYS           |

| ポート<br>B | PB0  | -         | TIM1_<br>CH2N | TIM3_<br>CH3 | TIM8_<br>CH2N    | -             | -                         | -               | -                         | -                          | LCD_R3                                         | OTG_HS_<br>ULPI_D1                  | ETH_MII_<br>RXD2                         | -                            | -                    | LCD_G1 | EVENT<br>OUT  |

|          | PB11 | -         | TIM2_<br>CH4  | -            | -                | I2C2_<br>SDA  |                           | -               | USART3_<br>RX             | -                          |                                                | OTG_HS_<br>ULPI_D4                  | ETH_MII_<br>TX_EN/<br>ETH_RMII_<br>TX_EN | -                            | DSI<br>HOST<br>_TE   | LCD_G5 | EVENT<br>OUT  |

|          | PB12 | -         | TIM1_<br>BKIN | -            | -                | I2C2_SM<br>BA | SPI2_<br>NSS/<br>I2S2_WS  | -               | USART3_<br>CK             | -                          | CAN2_RX                                        | OTG_HS_<br>ULPI_D5                  | ETH_MII_<br>TXD0/<br>ETH_RMII_<br>TXD0   | OTG_HS_ID                    | -                    | -      | EVENT<br>OUT  |

|          | PB13 | -         | TIM1_<br>CH1N | -            | -                | -             | SPI2_<br>SCK/<br>I2S2_CK  | -               | USART3_<br>CTS            | -                          | CAN2_TX                                        | OTG_HS_<br>ULPI_D6                  | ETH_MII_<br>TXD1/ETH_<br>RMII_TxD1       | -                            | -                    | -      | EVENT<br>OUT  |

|          | PB14 | -         | TIM1_<br>CH2N | -            | TIM8_<br>CH2N    | -             | SPI2_MIS<br>O             | I2S2ext_<br>SD  | USART3_<br>RTS            | -                          | TIM12_C<br>H1                                  | -                                   | -                                        | OTG_HS_DM                    | -                    | -      | EVENT<br>OUT  |

|          | PB15 | RTC_REFIN | TIM1_<br>CH3N | -            | TIM8_<br>CH3N    | -             | SPI2_<br>MOSI/<br>I2S2_SD | -               | -                         | -                          | TIM12_C<br>H2                                  | -                                   | -                                        | OTG_H<br>S_DP                | -                    | -      | EVENT<br>'OUT |

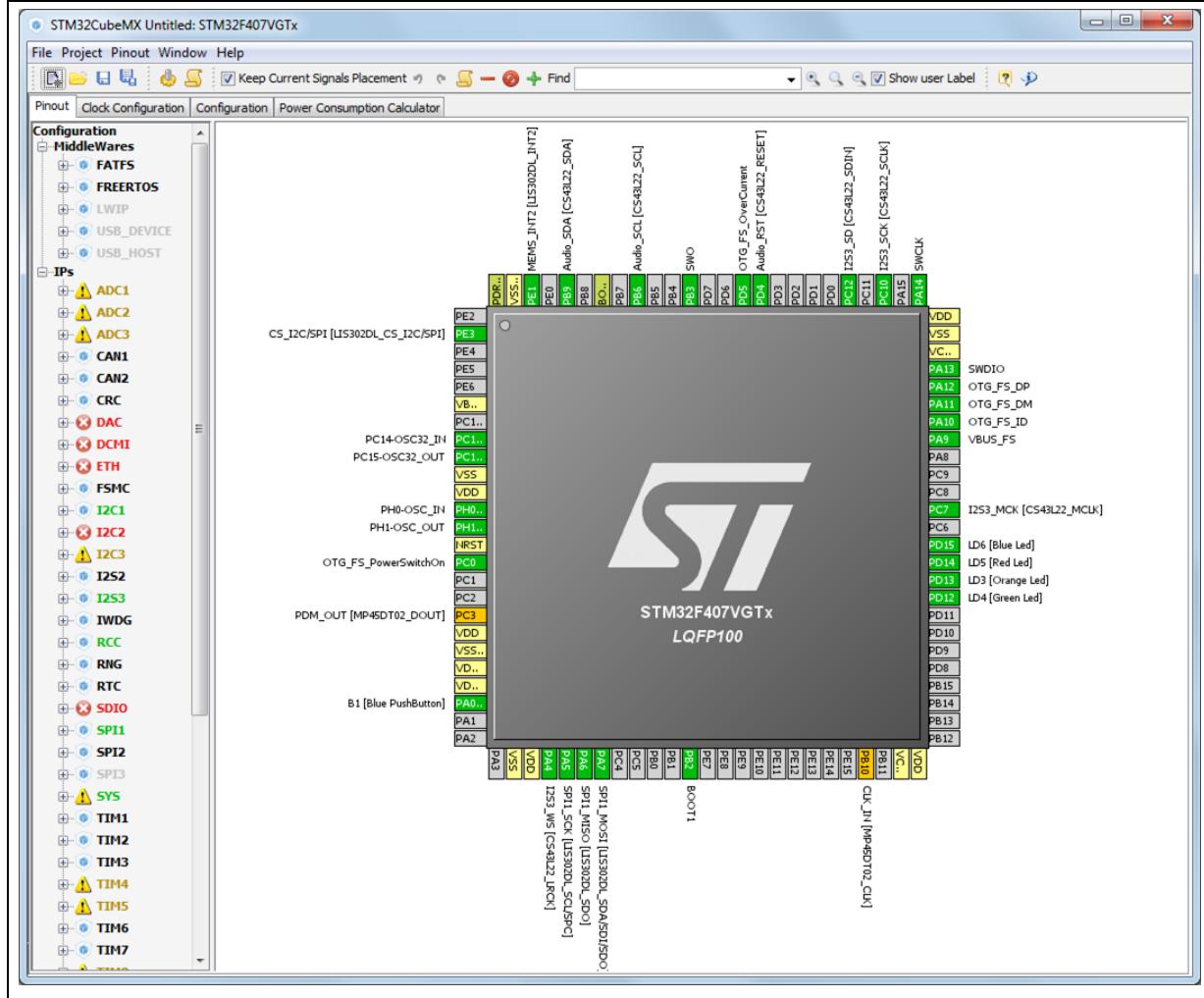

ペリフェラル・オルタネート機能のピン・マッピングを簡単に調べるには、[www.st.com](http://www.st.com) に用意されている STM32CubeMX ツールを使用することをお勧めします。

# 參考資料

図 11. STM32CubeMX の例のスクリーンショット

#### 4.3.1 未使用ピンの処理

すべてのマイクロコントローラはさまざまなアプリケーションで使用できるように設計されており、通常は特定のアプリケーションがマイクロコントローラのリソースを 100% 使用することはありません。

EMC 性能を向上するには、未使用的クロック、カウンタ、または I/O をフリーにしないでください。たとえば、I/O は “0” または “1” に設定（未使用 I/O ピンにプルアップまたはプルダウン）する必要があります、未使用的機能は「停止」または無効にする必要があります。

注： リークを減らすには、I/O をアナログ入力として設定するか、またはプッシュプルに設定して “0” に設定することをお勧めします。

## 4.4 ブート・モード選択

### 4.4.1 ブート・モード選択

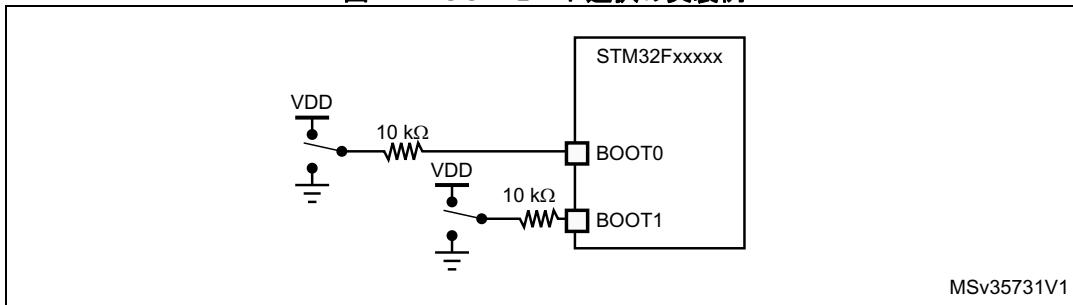

STM32F4xxxx では、表 6 に示すように、BOOT[1:0] ピンによって 3 種類のブート・モードを選択できます。

表 6. ブート・モード

| ブート・モード選択ピン |       | ブート・モード       | エイリアシング                       |

|-------------|-------|---------------|-------------------------------|

| BOOT1       | BOOT0 |               |                               |

| x           | 0     | メイン Flash メモリ | メイン Flash メモリがブート領域として選択されます。 |

| 0           | 1     | システム・メモリ      | システム・メモリがブート領域として選択されます。      |

| 1           | 1     | 内蔵 SRAM       | 内蔵 SRAM がブート領域として選択されます。      |

BOOT ピンの値は、リセット後、SYSCLK の 4 番目の立ち上がりエッジでラッチされます。ユーザは、リセット後に BOOT1 と BOOT0 ピンを設定して必要なブート・モードを指定します。

#### ユーザ Flash モードからのブート

リセット後に実行されるアプリケーション・コードは、ユーザ Flash メモリに配置されます。

このモードのユーザ Flash メモリは、エイリアスがブート・メモリ空間のアドレス 0x00000000 から作成されます。リセット時にアドレス 0x00000000 からスタック最上位の値がフェッチされ、コードはアドレス 0x00000004 から実行を開始します。

#### システム・メモリ・モードからのブート

システム・メモリ（ユーザ Flash ではなく）は、エイリアスがアドレス 0x00000000 から作成されます。この場合、アプリケーション・コードは、事前にシステム・メモリにロードしておく必要があります。

#### 内蔵 SRAM モードからのブート

SRAM は、アドレス 0x00000000 から始まります。このモードが選択されている場合、デバイスは、NVIC 例外テーブルとオフセット・レジスタを使用してベクタ・テーブルが再配置されていることを想定して、内蔵 SRAM の先頭から実行を開始します。この場合、アプリケーション・コードは、事前に内蔵 SRAM にロードしておく必要があります。

この最後のモードは、通常はデバッグで使用します。

# 参考資料

## 4.5 BOOT ピン接続

図 12 は、STM32F4xxxx のブート・メモリを選択するために必要な外部接続を示します。

図 12. BOOT モード選択の実装例

1. レジスタ値は、一般的な例としてのみ示されています。

## 4.6 内蔵ブート・ローダ・モード

内蔵ブートローダは、システム・メモリに配置され、生産時に ST によってプログラムされています。

次のシリアル・インターフェースのいずれかを使用して、Flash メモリを再プログラムするために使用します。

次の表に、システム・ブートローダによってサポートされている通信ペリフェラルを示します。

表 7. STM32F4xxxx ブートローダ通信ペリフェラル

| ブートローダ・ペリフェラル | STM32F401xB/C<br>STM32F401xD/E               | STM32F405/415<br>STM32F407/417<br>STM32F427/437<br>STM32F429/439 | STM32F410xx             | STM32F411xC/<br>STM32F411xE                   | STM32F412xx/<br>STM32F413xx/<br>STM32F423xx   | STM32F469xx/<br>STM32F479xx                   |

|---------------|----------------------------------------------|------------------------------------------------------------------|-------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| DFU           | デバイス・モード<br>で USB OTG<br>フルスピード<br>(PA11/12) | デバイス・モード<br>で USB OTG<br>フル・スピード<br>(PA11/12)                    | -                       | デバイス・モード<br>で USB OTG<br>フル・スピード<br>(PA11/12) | デバイス・モード<br>で USB OTG<br>フル・スピード<br>(PA11/12) | デバイス・モード<br>で USB OTG<br>フル・スピード<br>(PA11/12) |

| USART1        | PA9/PA10                                     | PA9/PA10                                                         | PA9/PA10                | PA9/PA10                                      | PA9/PA10                                      | PA9/PA10                                      |

| USART2        | PD5/PD6                                      | -                                                                | -                       | PD5/PD6                                       | PD5/PD6                                       | -                                             |

| USART3        | -                                            | PB10/PB11/<br>PC10/PC11                                          | -                       | -                                             | PB10/PB11                                     | PB10/PB11,<br>PC10/PC11                       |

| CAN           | -                                            | PB5/PB13                                                         | -                       | -                                             | PB5/PB13                                      | PB5/PB13                                      |

| I2C1          | PB6/PB7                                      | -                                                                | PB6/PB7                 | PB6/PB7                                       | PB6/PB7                                       | -                                             |

| I2C2          | PB3/PB10                                     | -                                                                | PB3/PB10                | PB3/PB10                                      | PF0/PF1                                       | -                                             |

| I2C3          | PA8/PB4                                      | -                                                                | -                       | PA8/PB4                                       | PA8/PB4                                       | -                                             |

| I2C FMP1      | -                                            | -                                                                | -                       | -                                             | PB14/PB15                                     | -                                             |

| SPI1          | PA4/PA5/<br>PA6/PA7                          | -                                                                | PA4/PA5/<br>PA6/PA7     | PA4/PA5/<br>PA6/PA7                           | PA4/PA5/<br>PA6/PA7                           | -                                             |

| SPI2          | PB12/PB13/<br>PB14/PB15                      | -                                                                | PB12/PB13/<br>PB14/PB15 | PB12/PB13/<br>PB14/PB15                       | -                                             | -                                             |

# 参考資料

表 7. STM32F4xxxx ブートローダ通信ペリフェラル（続き）

| ブートローダ・ペリフェラル | STM32F401xB/C<br>STM32F401xD/E | STM32F405/415<br>STM32F407/417<br>STM32F427/437<br>STM32F429/439 | STM32F410xx | STM32F411xC/<br>STM32F411xE | STM32F412xx/<br>STM32F413xx/<br>STM32F423xx | STM32F469xx/<br>STM32F479xx |

|---------------|--------------------------------|------------------------------------------------------------------|-------------|-----------------------------|---------------------------------------------|-----------------------------|

| SPI3          | PA15/PC10/<br>PC11/PC12        | -                                                                | -           | PA15/PC10/<br>PC11/PC12     | PA15/PC10/<br>PC11/PC12                     | -                           |

| SPI4          | -                              | -                                                                | -           | -                           | PE11/PE12/<br>PE13/PE14                     | -                           |

詳細については、AN2606（表 2）を参照してください。

## 5 デバッグ管理

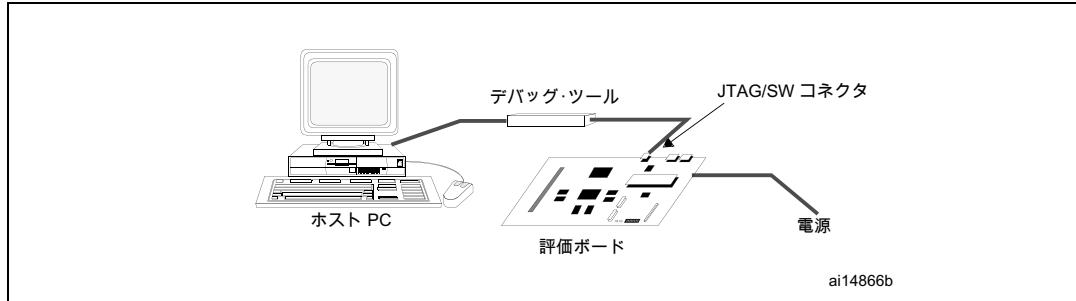

ホスト/ターゲット・インターフェースは、ホストをアプリケーション・ボードに接続するハードウェア機器です。このインターフェースは、ハードウェア・デバッグ・ツール、JTAG または SW コネクタ、およびホストをデバッグ・ツールに接続するケーブルの 3 つのコンポーネントで構成されています。

図 13 は、ホストと評価ボードの接続を示しています。

図 13. ホストとボードの接続

### 5.1 SWJ デバッグ・ポート（シリアル・ワイヤと JTAG）

STM32F4xxxx のコアには、シリアル・ワイヤ/JTAG デバッグ・ポート (SWJ-DP) が組み込まれています。これは、JTAG-DP (5 ピン) インタフェースと SW-DP (2 ピン) インタフェースを組み合わせた ARM® 標準の CoreSight™ デバッグ・ポートです。

- JTAG デバッグ・ポート (JTAG-DP) は、AHP-AP ポートに 5 ピンの標準 JTAG インタフェースを提供します。

- シリアル・ワイヤ・デバッグ・ポート (SW-DP) は、AHP-AP ポートに 2 ピン (クロック + データ) のインターフェースを提供します。

SWJ-DP では、SW-DP の 2 個の JTAG ピンが、JTAG-DP の 5 個の JTAG ピンの一部と多重化されています。

SWJ デバッグ・ポートの詳細については、製品のリファレンス・マニュアルの SWJ デバッグ・ポートのセクション（シリアル・ワイヤと JTAG）を参照してください。

### 5.2 ピンとデバッグ・ポート・ピン

STM32F4xxxx のマイクロコントローラは、使用できるピン数の異なるさまざまなパッケージで提供されています。このため、ピンを使用する一部の機能は、パッケージによって異なることがあります。

## 5.2.1 SWJ デバッグ・ポート・ピン

汎用入出力のオルタネート機能として、5 個のピンが SWJ-DP 用の出力に使用されます。これらのピン（表 8 を参照）はすべてのパッケージで使用できます。

表 8. デバッグ・ポート・ピンの割当て

| SWJ-DP ピン名    | JTAG デバッグ・ポート |                 | SW デバッグ・ポート |                         | ピン割当て |

|---------------|---------------|-----------------|-------------|-------------------------|-------|

|               | タイプ           | 説明              | タイプ         | デバッグ割当て                 |       |

| JTMS/SWDIO    | I             | JTAG テスト・モード選択  | I/O         | シリアル・ワイヤ・データ入出力         | PA13  |

| JTCK/SWCLK    | I             | JTAG テスト・クロック   | I           | シリアル・ワイヤ・クロック           | PA14  |

| JTDI          | I             | JTAG テスト・データ入力  | -           | -                       | PA15  |

| JTDO/TRACESWO | O             | JTAG テスト・データ出力  | -           | 非同期トレースが有効な場合は TRACESWO | PB3   |

| JNTRST        | I             | JTAG テスト nReset | -           | -                       | PB4   |

## 5.2.2 JTAG ピンでの内部プルアップ/プルダウン抵抗

JTAG 入力ピンは、デバッグ・モード機能を制御するためにフリップフロップに直結されます。したがって、JTAG 入力ピンをフロート状態にしないでください。これらのフリップフロップの一部のクロックに直結される SWCLK/TCK ピンについては、特に注意が必要です。

入出力レベルを正しく制御するため、STM32F4xxxx には内部プルアップ/プルダウン抵抗が JTAG 入力ピンに内蔵されています。

- JNTRST : 内部プルアップ

- JTDI : 内部プルアップ

- JTMS/SWDIO : 内部プルアップ

- TCK/SWCLK : 内部プルダウン

JTAG 入出力がユーザ・ソフトウェアによって解放されると、GPIO コントローラが再び制御権を獲得します。GPIO 制御レジスタがリセット状態にあるとき、入出力も同じ状態になります。

- JNTRST : 入力プルアップ

- JTDI : 入力プルアップ

- JTMS/SWDIO : 入力プルアップ

- JTCK/SWCLK : 入力プルダウン

- JTDO : 入力フローティング

ソフトウェアはこれらの入出力を標準の GPIO 信号として使用することができます。

注 : JTAG IEEE 規格では、TDI、TMS、および nTRST にプルアップ抵抗を追加することを推奨していますが、TCK に関しては特別な推奨はありません。ただし、STM32F4xxxx の場合は、JTCK に内蔵プルダウン抵抗が使用されます。

プルアップおよびプルダウン抵抗を内蔵しているため、外部抵抗を追加する必要がありません。

### 5.2.3 SWJ デバッグ・ポートと標準 JTAG コネクタの接続

図 14 は、STM32F4xxxx と標準 JTAG コネクタとの接続を示しています。

図 14. JTAG コネクタの実装

## 6 クロック

次の 3 つのクロック・ソースを使用して、システム・クロック (SYSCLK) を駆動できます。

- HSI オシレータ・クロック (ハイスピード内部クロック信号)

- HSE オシレータ・クロック (ハイスピード外部クロック信号)

- PLL クロック

デバイスには、次の 2 つの 2 次クロック・ソースがあります。

- 32 kHz ロースピード内蔵 RC (LSI RC)。独立型ウォッチャドッグを駆動し、オプションで、STOP/STANDBY モードからの自動ウェイクアップに使用される RTC を駆動します。

- 32.768 kHz ロースピード外部クリスタル (LSE クリスタル)。オプションで、リアルタイム・クロック (RTCCLK) を駆動します。

それぞれのクロック・ソースは、使用しないときに個別にオン/オフを切り替えて、電力消費を最適化可能です。

クロック・ツリーについては、リファレンス・マニュアルを参照してください。

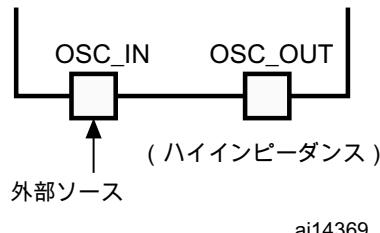

### 6.1 HSE OSC クロック

ハイスピード外部クロック信号 (HSE) は、次のどちらかのクロック・ソースから生成できます。

- HSE ユーザ外部クロック (図 15 を参照)

- HSE 外部クリスタル/セラミック発振子 (図 16 を参照)

図 15. HSE 外部クロック

ハードウェア構成

ai14369

図 16. HSE クリスタル/セラミック発振子

ハードウェア構成

STM32F

ai14370a

1.  $R_{EXT}$  の値は、クリスタルの特性に依存します。標準値は、 $5 \sim 6 R_S$  (発振子の直列抵抗) です。

詳細については、専用アプリケーション・ノート (AN2867 「STM8AF/AL/S および STM32 マイクロコントローラ用発振器設計ガイド」) および製品データシートの電気的特性のセクションを参照してください。

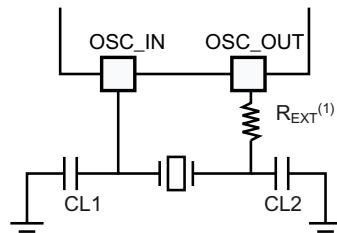

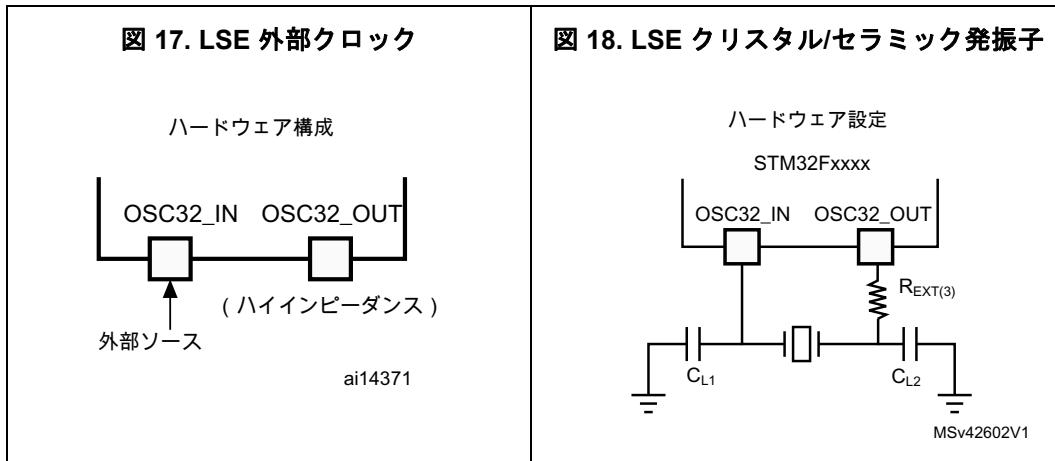

### 6.2 LSE OSC クロック

ロースピード外部クロック信号 (LSE) は、次のどちらかのクロック・ソースから生成できます。

- LSE ユーザ外部クロック (図 17 を参照)

- LSE 外部クリスタル/セラミック発振子 (図 18 を参照)

1. 「LSE クリスタル/セラミック発振子」の図：

C<sub>L1</sub> と C<sub>L2</sub> の最大値 (15 pF) を超えるのを避けるために、負荷容量 C<sub>L</sub> ≤ 7 pF の発振子を使用すること強くお勧めします。負荷容量 12.5 pF の発振子は使用しないでください。

2. 「LSE 外部クロック」と「LSE クリスタル/セラミック発振子」の図：

OSC32\_IN ピンと OSC32\_OUT ピンは、GPIO としても使用できますが、同一アプリケーションで RTC ピンと GPIO ピンの両方として使用しないことをお勧めします。

3. 「LSE クリスタル/セラミック発振子」の図：

R<sub>EXT</sub> の値は、クリスタルの特性に依存します。A 0 Ω レジスタは、動作しますが、最適ではありません。R<sub>S</sub> 値の微調整の詳細については、AN2867 「STM8AF/AL/S および STM32 マイクロコントローラ用発振器設計ガイド」 (表 2) および製品データシートの電気的特性のセクションを参照してください。

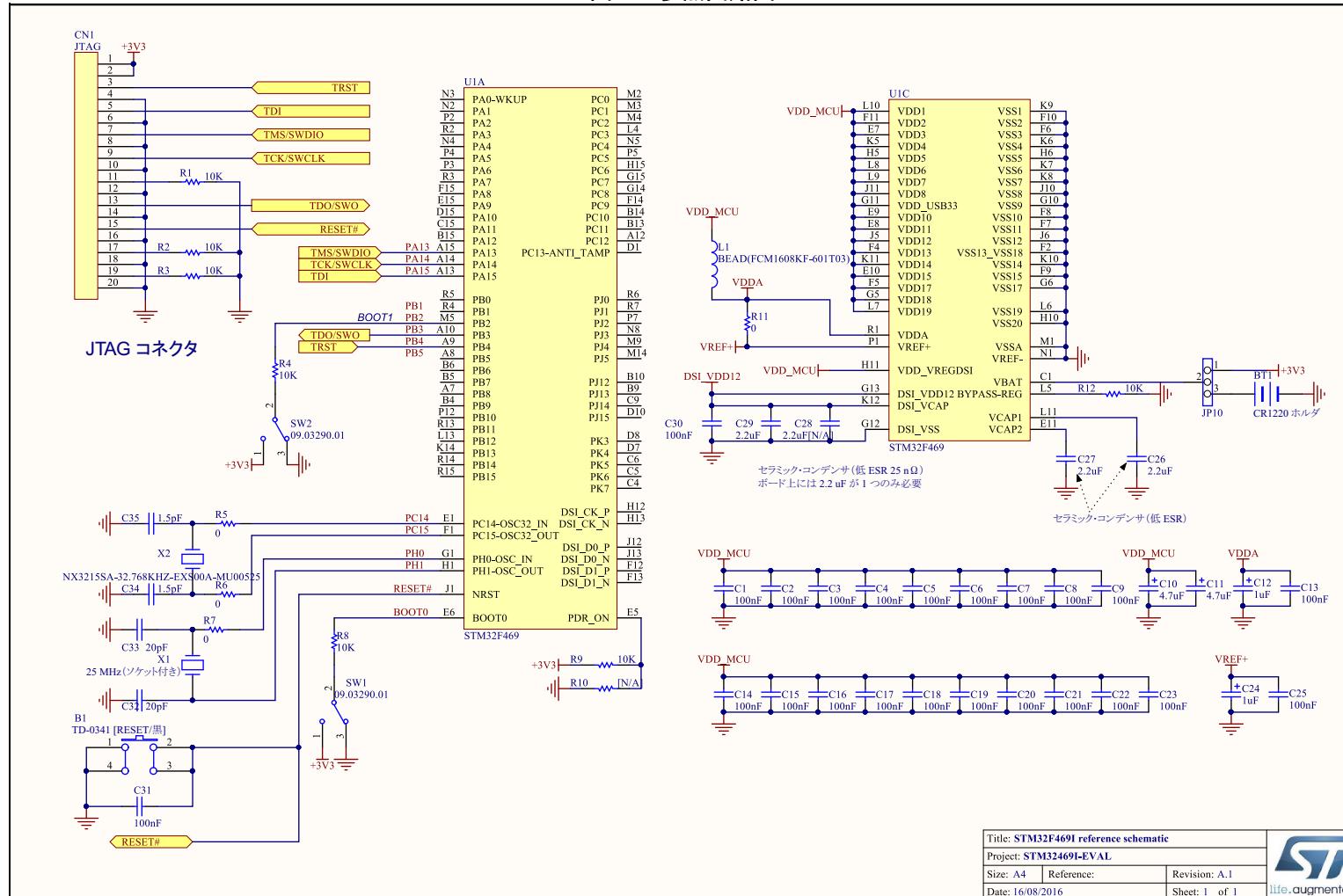

參照設計

図 19. 参照回路図

Title: **STM32F469I reference schematic**

Project: **STM32469I-EVAL**

Size: **A4** Reference: **Revision: A.1**

Date: **16/08/2016** Sheet: **1 of 1**

life...augmented

図 20. 部品表

| コメント                              | 説明                                     | 部品番号                                                                                                | フットプリント              | 数量 |

|-----------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|----|

| TD-0341 [RESET/黒]                 | SE PUSHBUTTON                          | B1                                                                                                  | PB10                 | 1  |

| CR1220 ホルダ                        | バッテリ                                   | BT1                                                                                                 | BAT_2SM_CR1220       | 1  |

| 100nF                             | コンデンサ                                  | C1, C2, C3, C4, C5, C6, C7, C8, C9, C13, C14, C15, C16, C17, C18, C19, C20, C21, C22, C23, C25, C30 | 0402C                | 22 |

| 4.7uF                             | 有極コンデンサ(ラジアル)                          | C10, C11                                                                                            | TAN-A                | 2  |

| 1uF                               | 有極コンデンサ(ラジアル)                          | C12, C24                                                                                            | TAN-A                | 2  |

| 2.2uF                             | コンデンサ                                  | C26, C27                                                                                            | 1206C                | 2  |

| 2.2uF[N/A]                        | コンデンサ                                  | C28                                                                                                 | 1206C                | 1  |

| 2.2uF                             | コンデンサ                                  | C29                                                                                                 | 0402C                | 1  |

| 100nF                             | コンデンサ                                  | C31                                                                                                 | 0603C                | 1  |

| 20pF                              | コンデンサ                                  | C32, C33                                                                                            | 0603C                | 2  |

| 1.5pF                             | コンデンサ                                  | C34, C35                                                                                            | 0603C                | 2  |

| JTAG                              |                                        | CN1                                                                                                 | IDC20S               | 1  |

|                                   |                                        | JP10                                                                                                | SIP3                 | 1  |

| BEAD(FCM1608KF-601T03)            | インダクタ                                  | L1                                                                                                  | 0603L                | 1  |

| 10K                               | 抵抗                                     | R1, R2, R3, R4, R8, R9, R12                                                                         | 0603R                | 7  |

| 0                                 | 抵抗                                     | R5, R6, R7, R11                                                                                     | 0603R                | 4  |

| [N/A]                             | 抵抗                                     | R10                                                                                                 | 0603R                | 1  |

| 09.03290.01                       | SPDT 超小型トグル・スイッチ、ライト・アングル・マウンティング、垂直作動 | SW1, SW2                                                                                            | SW1_3TH_2R54_10X2R5  | 2  |

| STM32F469                         |                                        | U1                                                                                                  | BGA216_0R8_13X13_SKT | 1  |

| 25 MHz (ソケット付き)                   | クリスタル発振子                               | X1                                                                                                  | XTAL_socket          | 1  |

| NX3215SA-32.768KHZ-EXS00A-MU00525 | クリスタル発振子                               | X2                                                                                                  | XTAL_2SM_3R2X1R5     | 1  |

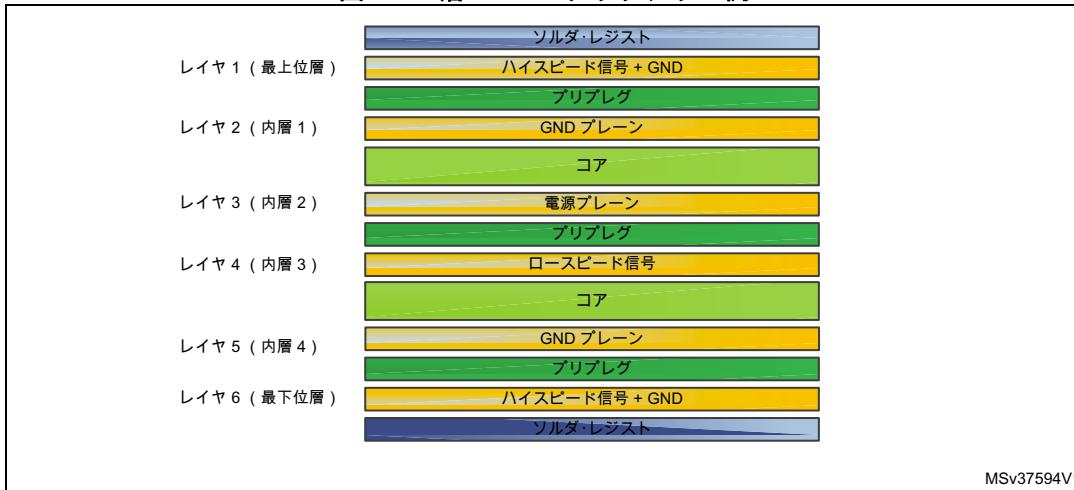

## 8 STM32F4xxxx デバイスの推奨する PCB 配線ガイドライン

### 8.1 PCB スタックアップ

ハイスピード信号に対する反射を減らすために、ソース、シンク、および伝送線路の間でインピーダンスを一致させる必要があります。信号トレースのインピーダンスは、その形状と、任意の基準面に対する位置に依存します。

特定のインピーダンス要件に対する差動ペア間のトレースの幅と間隔は、選択した PCB スタックアップに依存します。トレースの幅と間隔の最小値には制限があり、これは PCB テクノロジのタイプとコスト要件に依存します。したがって、必要なインピーダンスをすべて実現可能な PCB スタックアップを選択する必要があります。

使用可能な最小構成は、4 層または 6 層のスタックアップです。複数の SDRAM/SRAM/NOR/LCD コンポーネントが存在する高密度 PCB の場合は、8 層のボードが必要になる場合もあります。

以下に示すスタックアップの例は、スタックアップの評価と選択に役立つ出発点として使用できます。これらのスタックアップ構成では、GND プレーンを電源プレーンに隣接させて使用することで、容量を増やし、GND と電源プレーンの間隔を小さくしています。したがって、最上位層のハイスピード信号は、EMC エミッションの削減に役立つベタの GND 基準面を持つことになります。層数が増えて、PCB の信号層ごとに GND 基準面が用意されることで、放射 EMC 性能がさらに向上するからです。

図 21. 4 層 PCB スタックアップ例

図 22. 6 層 PCB スタックアップ例

## 8.2 クリスタル・オシレータ

クリスタル・オシレータ回路のレイアウトおよび配線方法の詳細なガイダンスについては、アプリケーション・ノート「STM8AF/AL/S および STM32 マイクロコントローラ用発振器設計ガイド」(AN2867) を参照してください。

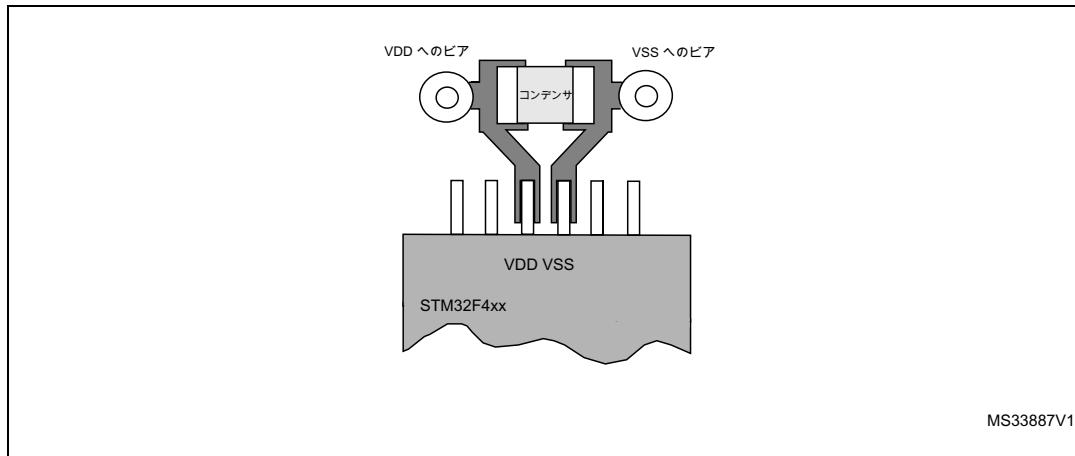

## 8.3 電源デカップリング

すべての電源ピンとグランド・ピンは、電源に適切に接続する必要があります。パッド、パターン、ビアを含むこれらの接続のインピーダンスは、できる限り低くする必要があります。

通常は、パターン幅を太くし、できれば多層 PCB で専用電源プレーンを使用することで、これを実現します。

さらに、各電源ペアを、フィルタリング用の複数のセラミック・コンデンサ (100 nF) と、タンタル・コンデンサまたはセラミック・コンデンサ (最小値 4.7 µF、標準値 10 µF) 1 つを並列接続してデカップリングする必要があります。これらのコンデンサは、PCB の裏面の、該当するピンのできる限り近くに、またはその下に、配置する必要があります。標準値は 10 nF ~ 100 nF ですが、正確な値はアプリケーションのニーズによって異なります。図 22 は、そのような VDD/VSS ペアの標準レイアウトを示します。

図 23.  $V_{DD}/V_{SS}$  ペアの標準レイアウト

## 8.4 ハイスピード信号レイアウト

### 8.4.1 SDMMC バス・インターフェース

#### インターフェース接続

SD/SDIO MMC カード・ホスト・インターフェース (SDMMC) は、APB2 ペリフェラル・バスとマルチ・メディア・カード (MMC)、SD メモリ・カード、および SDIO カード間のインターフェースを提供します。SDMMC インタフェースはシリアル・データ・バス・インターフェースであり、クロック (CK)、コマンド信号 (CMD)、および 8 本のデータ・ライン (D [0:7]) で構成されます。

インターフェースの信号レイアウトのガイドライン：

- GND または PWR を使用するプレーンを基準面とします (PWR を使用する場合は、PWR と GND の間に 10 nF スイッチング・コンデンサを追加)。

- $50\Omega \pm 10\%$  のインピーダンスになるように配線します。

- パターン長と負荷が等しくない場合、クロックシ・ステムにスキューが生じるので、ボード・スキューを最小化し、データとクロックのパターン長を等しくします。

- データとクロックの間の最大スキューは 250 ps @ 10mm 未満とする必要があります。

- 最大パターン長は 120 mm 未満とする必要があります。信号パターンがこのパターン長/速度条件を超える場合は、終端が必要になります。

- パターン容量は 3.3 V で 20 pF 以下、1.8 V で 15 pF 以下である必要があります。

- 最大信号パターン・インダクタンスは 16 nH 未満とする必要があります。

- バス・フローティングを防止するために、CMD 信号とデータ信号には推奨プルアップ抵抗を使用します。

- データ・バス、データと CK、または CK と CMD のパターン長の不一致は 10 mm 未満とする必要があります。

- データ信号間のビア数を同じにします。

注：

**SD メモリ・カード・バスの総容量は、バス・マスタ容量の合計です。**

CHOST、バス容量 CBUS、およびこのラインに接続される各カードの容量 CCARD の総バス容量は  $CL = C_{Host} + C_{Bus} + N * C_{Card}$  となります。ここで、ホストは STM32F4xxxx、バスは全信号、カードは SD カードです。

## 8.4.2 フレキシブル・メモリ・コントローラ (FMC) インタフェース

### インタフェース接続

FMC コントローラ、特に SDRAM メモリ・コントローラは、多数の信号がありますが、その多くは同じ機能を持ち、連携して動作します。コントローラの I/O 信号は、以下のように 4 つのグループに分割できます。

- アドレス・グループ。ロウ/カラム・アドレスとバンク・アドレスで構成されます。

- コマンド・グループ。ロウ・アドレス・ストローブ (NRAS)、カラム・アドレス・ストローブ (NCAS)、および書き込みイネーブル (SDWE) が含まれます。

- 制御グループ。バンク 1 とバンク 2 のチップ・セレクト (SDNE0/1)、バンク 1 とバンク 2 のクロック・イネーブル (SDCKE0/1)、および書き込みアクセスの出力バイト・マスク (DQM) が含まれます。

- データ・グループ/レーン。8 本の信号 (8 本の D (D7-D0)) とデータ・マスクが含まれます。

**注 :** これは、使用するメモリに依存します。バス幅が x8 の SDRAM には 1 つのデータ・グループのみが存在し、バス幅が x16 または x32 の SDRAM にはそれぞれ 2 つまたは 4 つのレーンがそれぞれ存在します。

### インタフェースの信号レイアウトのガイドライン :

- GND または PWR を使用するプレーンを基準面とします (PWR を使用する場合は、PWR と GND の間に 10 nF スイッチング・コンデンサを追加)。

- 50Ω ± 10% のインピーダンスになるように配線します。

- 最大パターン長は 120 mm 未満とする必要があります。信号パターンがこのパターン長/速度条件を超える場合は、終端が必要になります。

- クロストークを減らし、可能であればアドレスおよび制御レーンとは異なる層にデータ・パターンを配置します。ただし、データ・パターンとアドレス/制御パターンが同じ層に共存する場合は、相互の間隔が少なくとも 5 mm になるように分離する必要があります。

- データ・グループのパターン長は、それぞれの差が±10 mm 以内になるようにして、スキーを減らします。蛇行パターン ("S" 字になるように蛇行させてパターンを長くする) を使用して長さを合わせることができます。

- 内層にクロック (SDCLK) 信号を配置して、ノイズ (EMI) を最小化します。

- クロック信号を他の信号からパターンの 3 倍以上離して配線します。インピーダンスの変化と反射を防止するため、できる限りビア数を少なくします。蛇行配線の使用は避けます。

- クロック・パターンとデータ/アドレス・グループ・パターンの長さを、その差が±10 mm 以内になるように合わせます。

- クロック・パターンと、アドレスおよびコマンド・グループの各信号パターンの長さを、その差が±10 mm 以内 (最大値 20 mm 以下) になるように合わせます。

- 以下の容量になるように配線します。

- 3.3 V では、パターンを 20 pF 以内、総静電容量負荷 (データ、アドレス、SDCLK、制御を含む) を 30 pF 以下に維持します。

- 1.8 V では、パターンを 15 pF 以内、総静電容量負荷 (データ、アドレス、SDCLK、および制御を含む) を 20 pF 以下に維持します。

## 8.4.3 クワッド・シリアル・パラレル・インタフェース (Quad SPI)

### インタフェース接続

QUADSPI は、シングル、デュアル、またはQuad SPI Flash メモリを対象とする特殊な通信インターフェースです。QUAD SPI インタフェースはシリアル・データ・バス・インタフェースであり、クロック (SCLK)、チップ・セレクト信号 (nCS)、および 4 本のデータ・ライン (IO[0:3]) で構成されます。

#### インタフェースの信号レイアウトのガイドライン

- GND または PWR を使用するプレーンを基準面とします (PWR を使用する場合は、PWR と GND の間に 10 nF スイッチング・コンデンサを追加)。

- $50\Omega \pm 10\%$  のインピーダンスになるように配線します。

- 最大パターン長は 120 mm 未満とする必要があります。信号パターンがこのパターン長/速度条件を超える場合は、終端が必要になります。

- データ信号を配線する場合、複数の信号層の使用は避けます。

- クロック信号を他の信号からパターンの 3 倍以上離して配線します。インピーダンスの変化と反射を防止するため、できる限りビア数を少なくします。蛇行配線の使用は避けます。

- データ・グループのパターン長は、それぞれの差が $\pm 10\text{ mm}$  以内になるようにして、スキーを減らします。蛇行パターン ("S" 字になるように蛇行させてパターンを長くする) を使用して長さを合わせることができます。

クロック信号の場合、蛇行配線の使用は避けます。ビアによってインピーダンスが変化し、信号の反射が増加するので、パス全体のビア数はできる限り少なくします。

## 8.4.4 組込みトレース・マクロセル (ETM)

### インタフェース接続

ETM はプログラム実行の再構築を有効にします。データはデータ・ウォッчポイントおよびトレース (DWT) コンポーネントまたは命令トレース・マクロセル (ITM) を使用してトレースされます。一方、命令は組込みトレース・マクロセル (ETM) を使用してトレースされます。ETM インタフェースは、4 本のデータ・バス (D [0:3]) およびクロック信号 (CLK) と同期します。

#### インタフェースの信号レイアウトのガイドライン

- GND または PWR を使用するプレーンを基準面とします (PWR を使用する場合は、PWR と GND の間に 10 nF スイッチング・コンデンサを追加)。

- $50\Omega \pm 10\%$  のインピーダンスになるように配線します。

- すべてのデータ・パターンをできる限り短く (25 mm以下) します。

- 直下にベタのグランド・プレーンがある同一層に配線する必要があるラインをビアなしで配線します。

- ポイントツーポイント接続のみのクロックを配線します。スタブは避ける必要があります。

- 他の (データ) ラインもポイントツーポイントのみにすることを強く推奨します。スタブが必要な場合は、できる限り短くする必要があります。長くする必要がある場合は、(ジャンパなどを使用して) 切り離すことができるオプションが必要です。

## 9 よくある質問

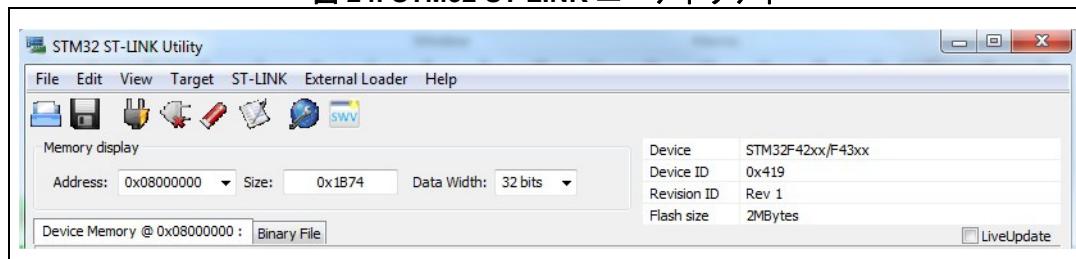

### 9.1 STM32F4xxxx の識別

STM32F4 を識別するには、製品データシートの部品番号のセクションを参照してください。

マイクロコントローラの ID は、ST-LINK ユーティリティを使用して取得できます。このツールを接続すると、ターゲットを識別して、以下に示すようにデバイスの ID、サブファミリ、リビジョン、および Flash サイズを表示します。

図 24. STM32 ST-LINK ユーティリティ

### 9.2 使用可能なハードウェア・ツール

ST は以下の 3 つの開発プラットフォームを提供しています。

#### 9.2.1 Nucleo ボード

Arduino™ Uno などの特殊シールドを使用して、広範囲にわたる機能を提供します。

Nucleo ボードは、さまざまなアドオン・ボードを使用して簡単に拡張できます。

#### 9.2.2 ディスカバリ・キット

ディスカバリ・ボードは、STM32 F4 シリーズの高性能マイクロコントローラを理解し、簡単にアプリケーションを開発するのに役立ちます。

さまざまなディスカバリ・ボードが用意されています。たとえば、STM32F429I-DISCO には、以下の機能が搭載されています。

- SDRAM 64MB

- L3GD20、MEMS モーション・センサ、3 軸デジタル出力ジャイロ・センサ

- USB OTG (Micro AB コネクタ付き) など

#### 9.2.3 評価ボード

評価ボードは、STM32 F4 シリーズ向けの完全なデモおよび開発用プラットフォームです。

このボードが提供する豊富なハードウェア機能は、あらゆるペリフェラル (USB OTG HS、USB OTG FS、Ethernet、モータ制御、CAN、MicroSD カード、スマートカード、USART、Audio DAC、RS-232、IrDA、SRAM、MEMS、EEPROM など) の評価および独自のアプリケーションの開発に役立ちます。

## 9.2.4 IBIS モデルはどこにありますか。

IBIS モデルは、 $I=f(V)$  と  $V=f(T)$  のデータを通じて STM32F4xxxx のデジタル入出力の電気的特性を記述します。

IBIS モデルの詳細については、AN4803 (STM32 の IBIS を使用したハイスピード SI シミュレーションおよび HyperLynx SI を使用したボードレベルシミュレーション) を参照してください。

IBIS モデルは、ST の Web サイトで入手できます。

## 9.3 マイクロコントローラが正常に動作しない

次の表に、マイクロコントローラが正常に起動しない場合に考えられる根本原因の一覧を示します。この表には、考えられる根本原因に関連して最も疑わしく、確認が必要と思われる箇所も示しています。

表 9. マイクロコントローラが正常に動作しない

| 考えられる根本原因            | 確認が必要な箇所                                                                                                                                                                                                                                                                     |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| デバイスへの VDD と GND の供給 | <ul style="list-style-type: none"><li>デバイスには安定した電源を供給する必要があります。</li><li>電源供給を監視します。</li><li>GND がデバイスに正しく供給されているかどうかを確認します。</li><li>GND カップリングを確認します。</li></ul>                                                                                                              |

| OSC_OUT              | <ul style="list-style-type: none"><li>オシレータで OSC_OUT を監視して、正常に動作しているかどうかを確認します。</li><li>AN2867 「STM8AF/AL/S および STM32 マイクロコントローラ用発振器設計ガイド」を参照してください。</li></ul>                                                                                                               |

| RESET ピン             | <ul style="list-style-type: none"><li>RESET ピンが正しく駆動されているかどうかを確認します。</li><li>NRST 接続には、グランドに接続する 100 nF コンデンサが含まれています。</li></ul>                                                                                                                                             |

| BOOT ピン              | <ul style="list-style-type: none"><li>BOOT ピンを監視します。</li><li>BOOT0 と BOOT1 がフローティング状態にあると、マイクロコントローラが正常に動作しない場合があります。</li></ul>                                                                                                                                              |

| VCAP                 | <ul style="list-style-type: none"><li>VCAP1 と VCAP2 は、<math>2 \times 2.2 \mu\text{F}</math>、<math>2 \Omega</math>未満の低 ESR セラミック・コンデンサ（または VCAP1 ピンしか提供されない一部のパッケージでは <math>1 \times 4.7 \mu\text{F}</math>、<math>1 \Omega</math>未満の低 ESR セラミック・コンデンサ）に接続する必要があります。</li></ul> |

| PVD                  | <ul style="list-style-type: none"><li>マイクロコントローラをプログラミングする場合、PLS [2:0] オプションビットを確認します。（これは ST-Link ユーティリティで確認できます）。</li><li>プログラムされている PVD 閾値に応じて割込みが生成されます。</li></ul>                                                                                                       |

| 温度範囲                 | <ul style="list-style-type: none"><li>ST によってデータシートで保証されている最悪の温度条件に従います。</li></ul>                                                                                                                                                                                           |

| システム・リセット            | <ul style="list-style-type: none"><li>PDR_ON ピン = 1 の場合は、特に注意が必要です。そのような設定では、PDR ブロックがアクティブです。これは、VDD が 1.74 V（実際の値については、STM32F4xxxx データシートを参照）まで下降した場合、システム・リセットが発生することを意味します。</li></ul>                                                                                    |

# 参考資料

## 10 結論

このアプリケーションノートは、STM32F4xxxx デバイスを使用して新しく設計を行う際に、最初に読むリファレンスとして使用してください。

## 11 改版履歴

表 10. 文書改版履歴

| 日付               | 版 | 変更内容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2014 年 6 月 20 日  | 1 | 初版発行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2014 年 10 月 28 日 | 2 | <p>表 1 に STM32F411xC/xE を追加<br/>         表 3 に脚注を追加<br/>         表 5 と表 11 を更新<br/>         図 2、図 7、および図 8 を更新<br/>         セクション 3.2.1 を更新<br/>         STM32F411xC/xE 向けにセクション 2.3.5 を追加<br/>         図 5 および図 6 を追加</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2015 年 3 月 20 日  | 3 | <p>表 1: 対象とする製品を更新<br/>         Table 3 : Regulator ON/OFF and internal power supply supervisor availability、表 3: パッケージ一覧、Table 6: WLCSP Package summary、Table 5: Pinout summary、および Table 11: Reference connection for all packages を更新。<br/>         Figure 9: STM32F4 family compatible board design for LQFP64 package、Figure 10: STM32F4 family compatible board design for LQFP100 package、Figure 12: Compatible board design STM32F10xx/STM32F4xx for LQFP64 package、Figure 13: Compatible board design STM32F10xx/STM32F2xx/STM32F4xx for LQFP100 package、Figure 14: Compatible board design STM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package を更新。<br/>         Figure 11: Compatible board design STM32F4xx / STM32F446xx for LQFP144 package を追加。</p> |

| 2015 年 8 月 21 日  | 4 | <p>更新：<br/>         - 図 2: 電源供給方式 (STM32F469xx/F479xx を除く)<br/>         - 図 3: 電源供給方式 (STM32F469xx/F479xx) と関連する注<br/>         - 表 1: 対象とする製品<br/>         - Table 3: Regulator ON/OFF and internal power supply supervisor availability<br/>         - 表 3: パッケージ一覧<br/>         - Table 6: WLCSP Package summary<br/>         - Table 17: Reference connection for all packages<br/>         追加：<br/>         - 図 12: BOOT モード選択の実装例の注 2</p>                                                                                                                                                                                                                                                                                                                    |

# 参考資料

## 改版履歴

AN4488

表 10. 文書改版履歴 (続き)

| 日付              | 版 | 変更内容                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2016 年 10 月 7 日 | 5 | <p>追加 :</p> <ul style="list-style-type: none"><li>- STM32F410x8、STM32F410xB、STM32F412xE、STM32F412xG、STM32F446xx、STM32F467xx、および STM32F469xx。</li><li>- セクション 8: STM32F4xxxx デバイスの推奨する PCB 配線ガイドライン</li><li>- セクション 9: よくある質問</li><li>- 図 19: 参照回路図</li><li>- 図 20: 部品表</li><li>- 図 24: STM32 ST-LINK ユーティリティ</li></ul> <p>更新 :</p> <ul style="list-style-type: none"><li>- セクション 7: 参照設計</li></ul> |

| 2016 年 12 月 5 日 | 6 | <p>追加 :</p> <p>STM32F413/423 ファミリ</p> <p>更新 :</p> <ul style="list-style-type: none"><li>- 表 1: 対象とする製品</li><li>- 表 3: パッケージ一覧</li><li>- 表 7: STM32F4xxxx ブートローダ通信ペリフェラル</li></ul>                                                                                                                                                                                                                  |

表 11. 日本語版文書改版履歴

| 日付          | 版 | 変更内容      |

|-------------|---|-----------|

| 2018 年 12 月 | 1 | 日本語版 初版発行 |

# 参考資料

AN4488

---

## 重要なお知らせ（よくお読み下さい）

STMicroelectronics NV およびその子会社（以下、ST）は、ST製品及び本書の内容をいつでも予告なく変更、修正、改善、改定及び改良する権利を留保します。購入される方は、発注前にST製品に関する最新の関連情報を必ず入手してください。ST 製品は、注文請求書発行時点での有効なST の販売条件に従って販売されます。

ST製品の選択並びに使用については購入される方が全ての責任を負うものとします。購入される方の製品上の操作や設計に関してST は一切の責任を負いません。

明示又は黙示を問わず、STは本書においていかなる知的財産権の実施権も許諾致しません。

本書で説明されている情報とは異なる条件でST 製品が再販された場合、その製品についてSTが与えたいかなる保証も無効となります。

ST およびST ロゴはSTMicroelectronics の商標です。その他の製品またはサービスの名称は、それぞれの所有者に帰属します。

本書の情報は本書の以前のバージョンで提供された全ての情報に優先し、これに代わるものです。

この資料は、STMicroelectronics NV 並びにその子会社(以下ST)が英文で記述した資料（以下、「正規英語版資料」）を、皆様のご理解の一助として頂くためにSTマイクロエレクトロニクス株が英文から和文へ翻訳して作成したものです。この資料は現行の正規英語版資料の近時の更新に対応していない場合があります。この資料は、あくまでも正規英語版資料をご理解頂くための補助的参考資料のみにご利用下さい。この資料で説明される製品のご検討及びご採用にあたりましては、必ず最新の正規英語版資料を事前にご確認下さい。ST及びSTマイクロエレクトロニクス株は、現行の正規英語版資料の更新により製品に関する最新の情報を提供しているにも関わらず、当該英語版資料に対応した更新がなされていないこの資料の情報に基づいて発生した問題や障害などにつきましては如何なる責任も負いません。

© 2018 STMicroelectronics - All rights reserved