# 参考資料

life.augmented

AN5031

## アプリケーションノート

STM32MP151, STM32MP153, STM32MP157 ラインの

ハードウェア開発の手引書

### 概要

本アプリケーションノートでは、STM32MP151、STM32MP153、STM32MP157 の各ラインの使用方法、およびそれらの MPU 製品を使用してアプリケーションを開発するために必要な最小ハードウェアリソースについて説明します。

このアプリケーションノートは、開発ボードのハードウェア実装の概要を知る必要があるシステム設計者を対象としており、次のような機能について説明します。

- 電源

- パッケージの選択

- クロック管理

- リセット制御

- ブートモード設定

- デバッグ管理

本書には、詳細なリファレンスデザインの回路図のほか、主要コンポーネント、インターフェース、およびモードに関する説明も記載されています。

# 参考資料

## 目次

AN5031

## 目次

|       |                                    |    |

|-------|------------------------------------|----|

| 1     | 一般情報                               | 8  |

| 2     | 参照文献                               | 8  |

| 3     | 用語                                 | 9  |

| 4     | 電源                                 | 11 |

| 4.1   | 概要                                 | 12 |

| 4.1.1 | 独立した ADC および DAC コンバータ用電源と基準電圧     | 12 |

| 4.1.2 | バッテリバックアップ                         | 13 |

| 4.1.3 | 電圧レギュレータ                           | 13 |

| 4.2   | 電源供給方式                             | 14 |

| 4.3   | リセットおよび電源供給スーパバイザ                  | 17 |

| 4.3.1 | パワーオンリセット (POR) / パワーダウンリセット (PDR) | 17 |

| 4.3.2 | プログラム可能な電圧検出器 (PWD)                | 17 |

| 4.3.3 | アプリケーションリセットとシステムリセット              | 18 |

| 5     | パッケージ                              | 20 |

| 5.1   | パッケージの選択                           | 20 |

| 5.2   | ピンへのオルタネート機能のマッピング                 | 22 |

| 5.3   | 異なる型番間のパッケージ互換性                    | 23 |

| 6     | クロック                               | 28 |

| 6.1   | HSE OSC クロック                       | 28 |

| 6.1.1 | 外部ソース (HSE バイパス)                   | 29 |

| 6.1.2 | 外部クリスタル/セラミック発振子 (HSE クリスタル)       | 29 |

| 6.2   | LSE OSC クロック                       | 30 |

| 6.2.1 | 外部ソース (LSE バイパス)                   | 30 |

| 6.2.2 | 外部クリスタル/セラミック発振子 (LSE クリスタル)       | 30 |

| 6.3   | クロックセキュリティシステム (CSS)               | 31 |

| 6.3.1 | HSE の CSS                          | 31 |

| 6.3.2 | LSE の CSS                          | 31 |

# 参考資料

|           |                                           |           |

|-----------|-------------------------------------------|-----------|

| <b>7</b>  | <b>ブート設定 .....</b>                        | <b>32</b> |

| 7.1       | ブート・モード選択 .....                           | 32        |

| 7.2       | BOOT ピンの接続 .....                          | 33        |

| 7.3       | 内蔵ブート・ローダ・モード .....                       | 35        |

| <b>8</b>  | <b>デバッグ管理 .....</b>                       | <b>36</b> |

| 8.1       | 概要 .....                                  | 36        |

| 8.2       | SWJ デバッグポート（シリアルワイヤと JTAG） .....          | 36        |

| 8.3       | ピン名とデバッグポートピン .....                       | 36        |

| 8.3.1     | JTAG ピンでの内部プルアップ / プルダウン抵抗 .....          | 36        |

| 8.3.2     | デバッグポートと標準 JTAG コネクタの接続 .....             | 37        |

| 8.3.3     | STDC14 コネクタへのデバッグポートと UART の接続 .....      | 38        |

| 8.3.4     | パラレルトレースと HDP .....                       | 39        |

| 8.3.5     | デバッグトリガと LED .....                        | 41        |

| <b>9</b>  | <b>推奨事項 .....</b>                         | <b>42</b> |

| 9.1       | プリント回路基板 .....                            | 42        |

| 9.2       | コンポーネントの位置 .....                          | 42        |

| 9.3       | グランドおよび電源 ( $V_{SSx}$ , $V_{DDx}$ ) ..... | 42        |

| 9.4       | IO 速度の設定 .....                            | 42        |

| 9.5       | PCB スタックおよびテクノロジー .....                   | 46        |

| 9.6       | デカッピング .....                              | 50        |

| 9.7       | ESD/EMI 保護 .....                          | 50        |

| 9.8       | ノイズに敏感な信号 .....                           | 51        |

| 9.9       | 未使用の I/O および機能 .....                      | 51        |

| <b>10</b> | <b>リファレンスデザイン例 .....</b>                  | <b>52</b> |

| 10.1      | 説明 .....                                  | 52        |

| 10.1.1    | クロック .....                                | 52        |

| 10.1.2    | リセット .....                                | 53        |

| 10.1.3    | ブートモード .....                              | 53        |

| 10.1.4    | SWD/JTAG インタフェース .....                    | 53        |

| 10.1.5    | 電源 .....                                  | 54        |

| 10.1.6    | DDR3/DDR3L SDRAM .....                    | 57        |

| 10.1.7    | LpDDR2/LpDDR3 SDRAM .....                 | 58        |

# 参考資料

## 目次

AN5031

|         |                                 |    |

|---------|---------------------------------|----|

| 10.1.8  | SD カード .....                    | 59 |

| 10.1.9  | eMMC™ Flash .....               | 61 |

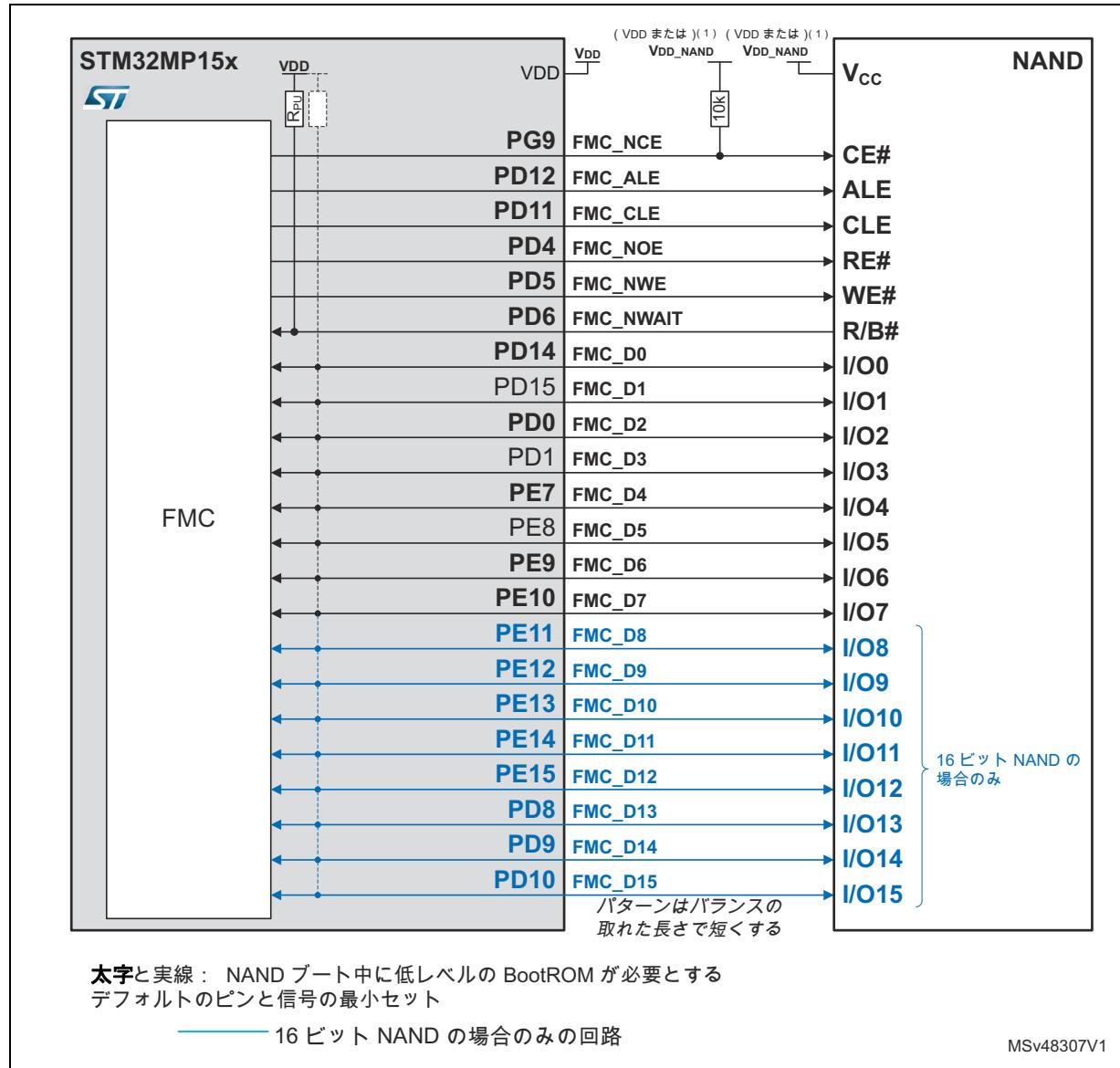

| 10.1.10 | SLC NAND-Flash .....            | 63 |

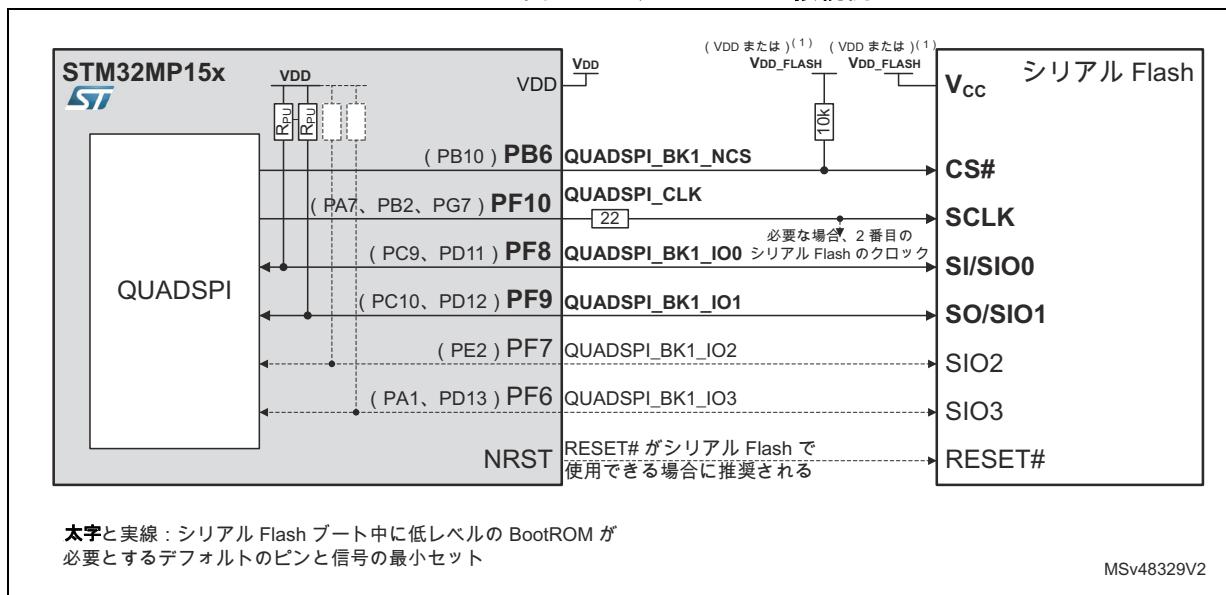

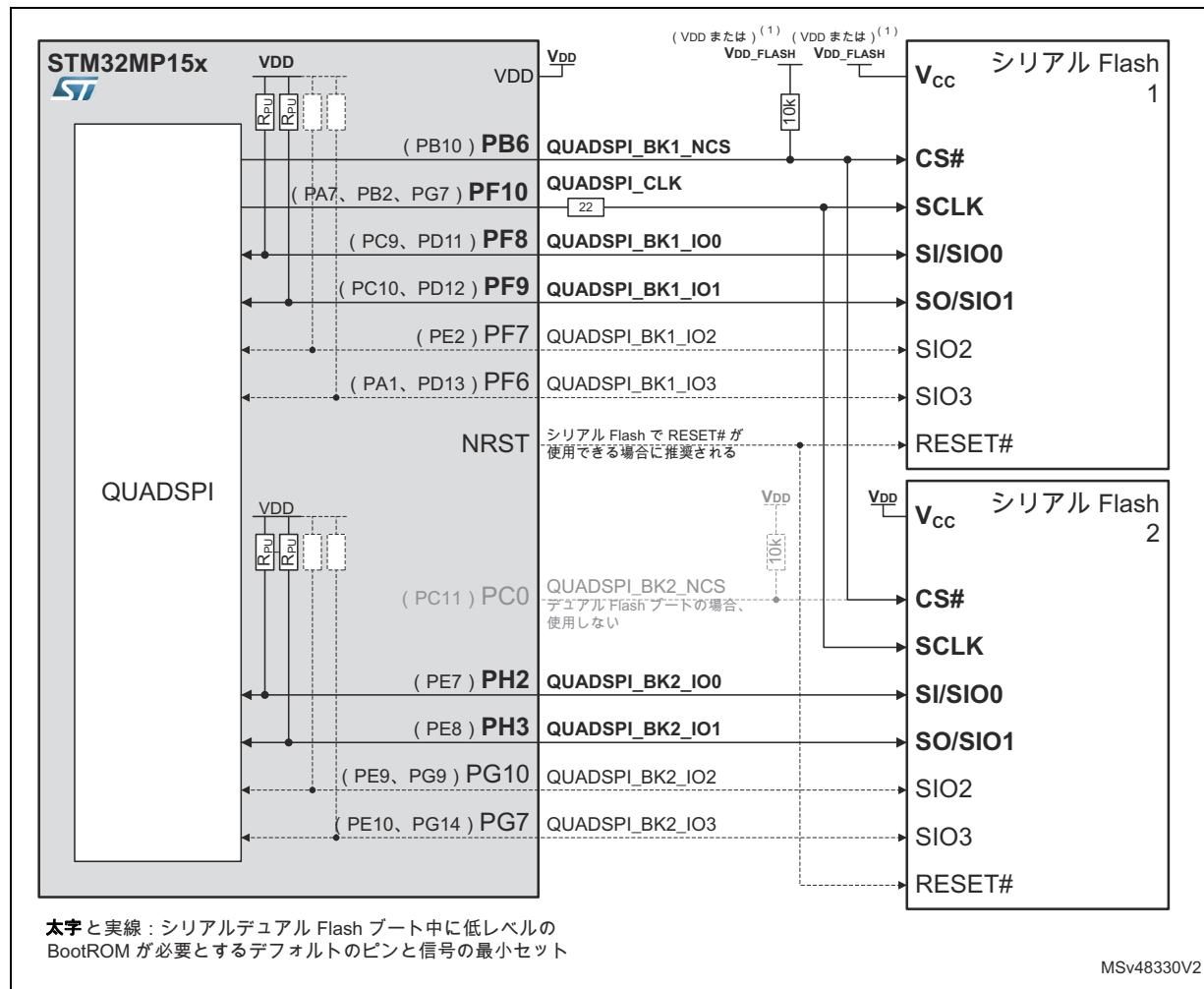

| 10.1.11 | シリアル NOR-Flash/NAND-Flash ..... | 64 |

| 10.1.12 | USB .....                       | 66 |

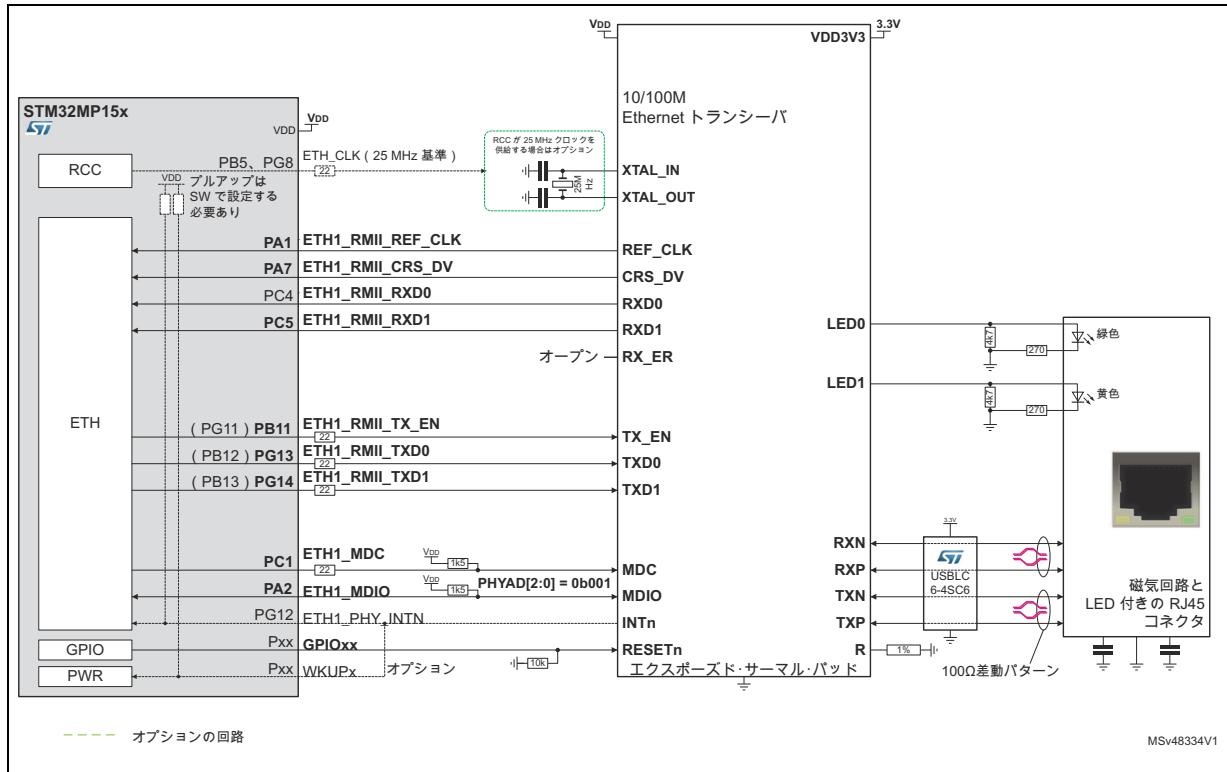

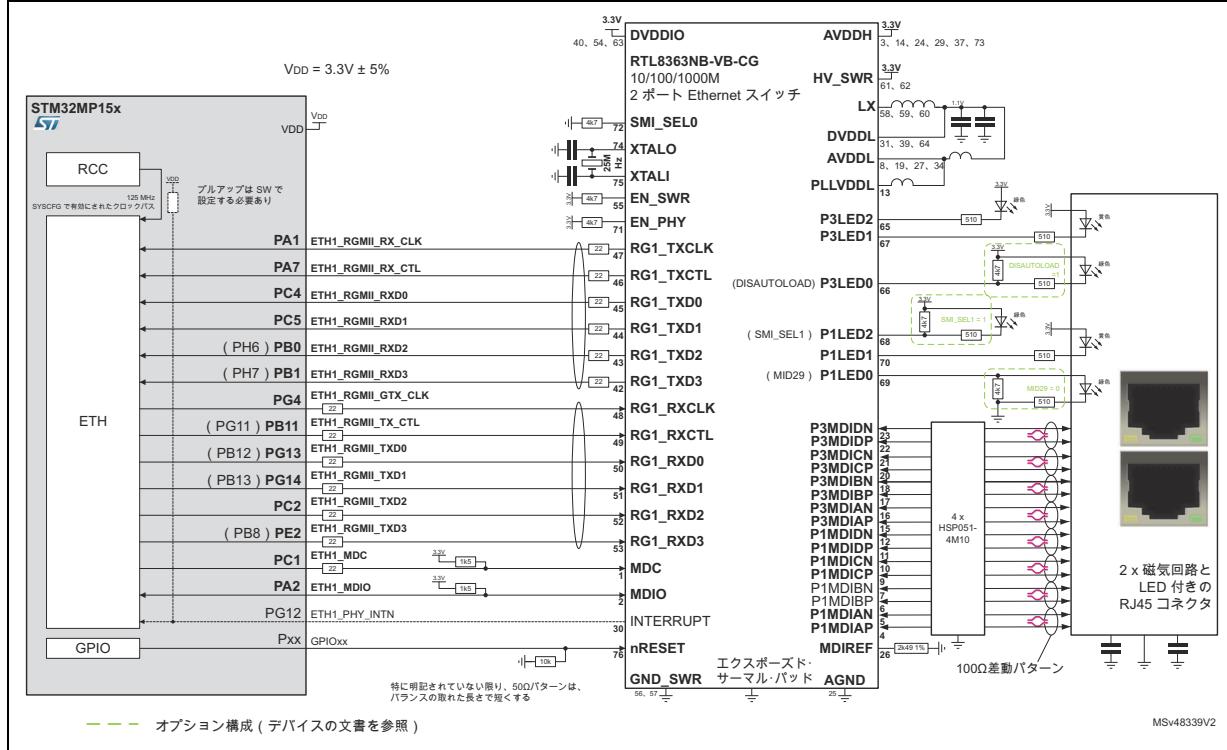

| 10.1.13 | Ethernet .....                  | 69 |

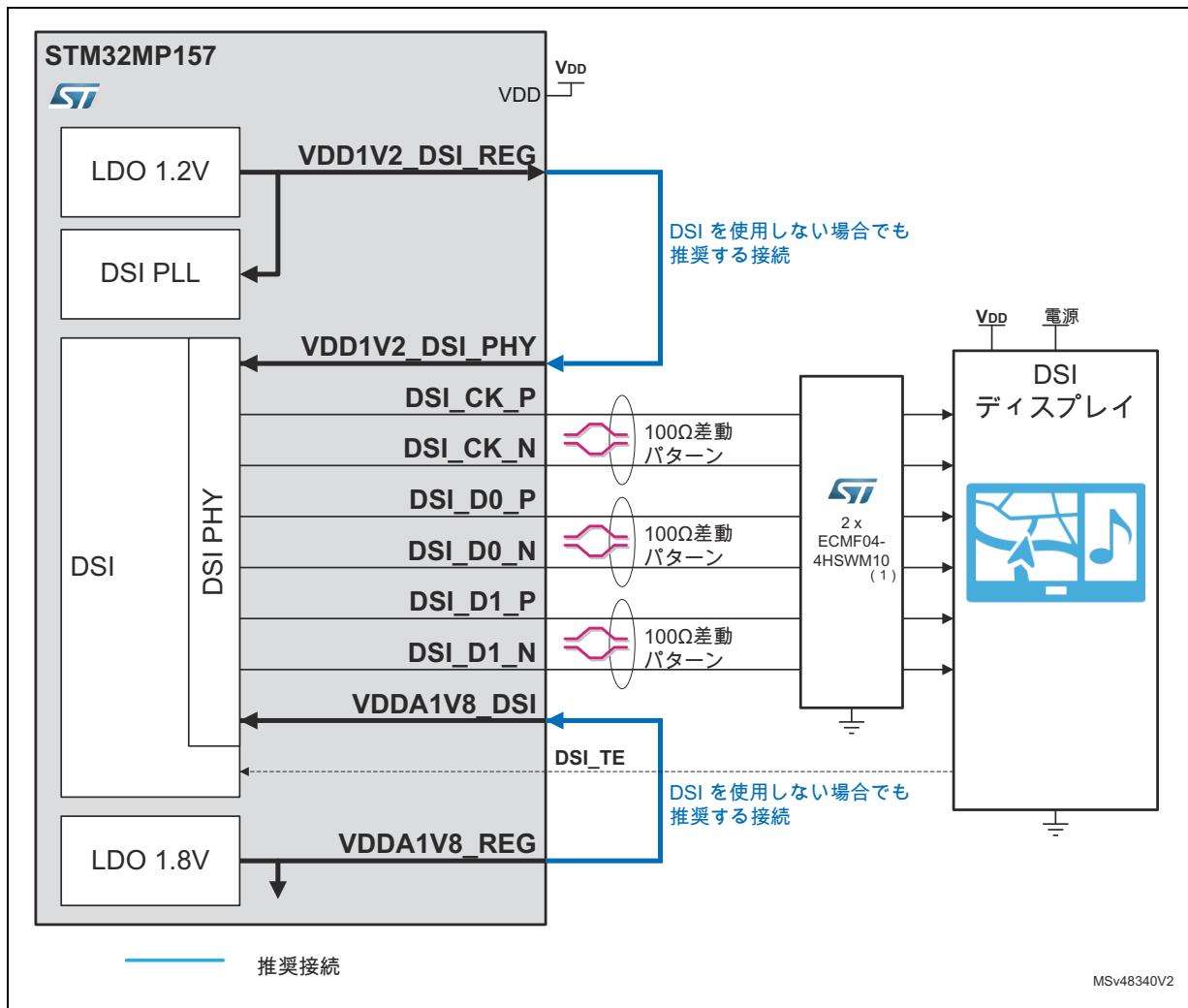

| 10.1.14 | ディスプレイシリアルインターフェース (DSI) .....  | 74 |

| 11      | 改版履歴 .....                      | 76 |

# 参考資料

AN5031

表の一覧

## 表の一覧

|       |                                                              |    |

|-------|--------------------------------------------------------------|----|

| 表 1.  | 参照文献 .....                                                   | 8  |

| 表 2.  | 用語 .....                                                     | 9  |

| 表 3.  | ANASWVDD および EN_BOOSTER 用の推奨設定 .....                         | 13 |

| 表 4.  | パッケージ別デカップリングコンデンサ値と数量の推奨値 .....                             | 16 |

| 表 5.  | パッケージ一覧 .....                                                | 20 |

| 表 6.  | パッケージ別主要機能の相違 .....                                          | 21 |

| 表 7.  | デバイスの互換性のまとめ .....                                           | 23 |

| 表 8.  | 16x16 LFBGA354 用の STM32MP151xxx および STM32MP153xxx の互換性 ..... | 24 |

| 表 9.  | 10x10 TFBGA257 用の STM32MP151xxx および STM32MP153xxx の互換性 ..... | 25 |

| 表 10. | 12x12 TFBGA361 用の STM32MP151xxx および STM32MP153xxx の互換性 ..... | 26 |

| 表 11. | 18x18 LFBGA448 用の STM32MP151xxx および STM32MP153xxx の互換性 ..... | 27 |

| 表 12. | ブートモード .....                                                 | 32 |

| 表 13. | VDD = 標準 3.3 V での OSPEEDR 設定例 .....                          | 43 |

| 表 14. | VDD = 標準 1.8 V での OSPEEDR 設定例 .....                          | 44 |

| 表 15. | オシレータまたはクリスタル発振子用の HSE 部品表 .....                             | 52 |

| 表 16. | ブート可能な UART ピン .....                                         | 53 |

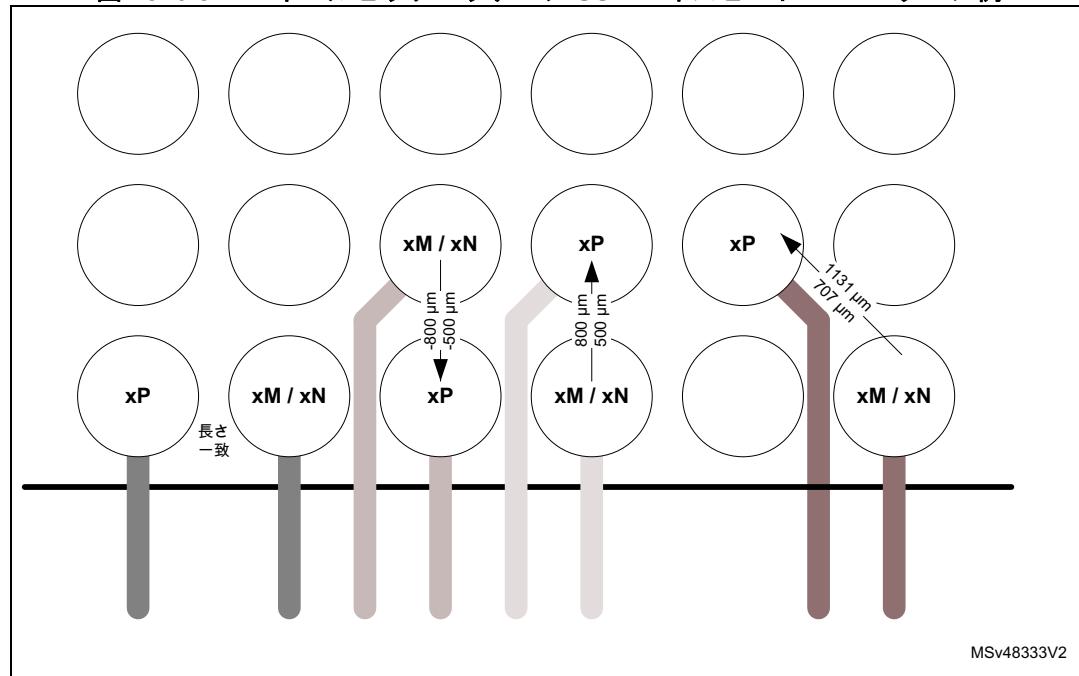

| 表 17. | USB 用のパッケージの長さマッチング値 .....                                   | 68 |

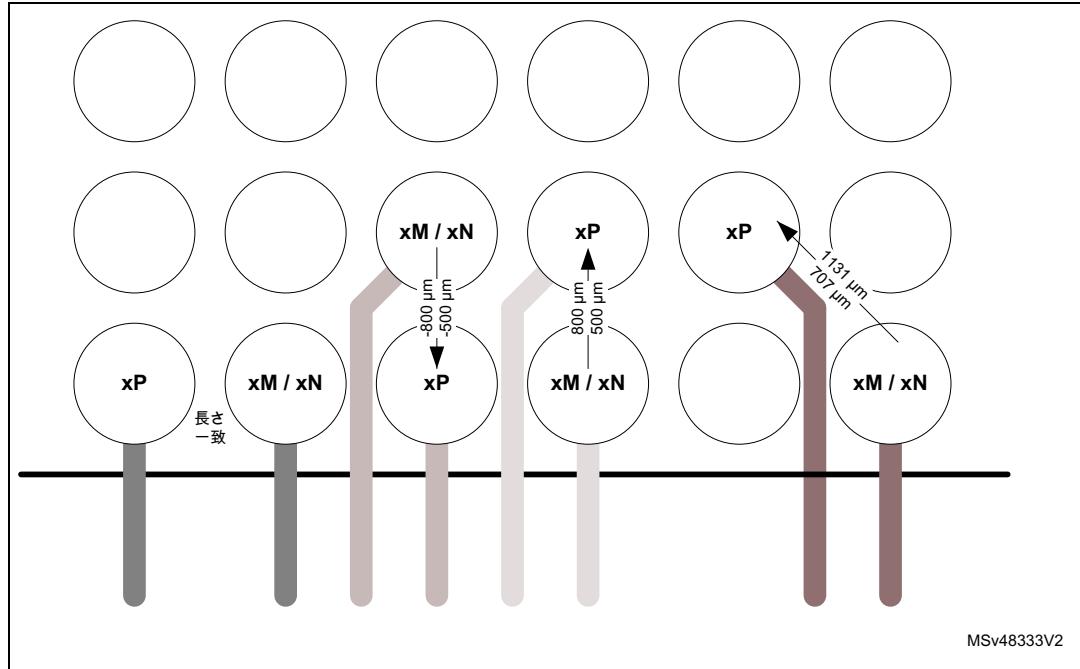

| 表 18. | DSI 用のパッケージの長さマッチング値 .....                                   | 75 |

| 表 19. | 文書改版履歴 .....                                                 | 76 |

| 表 20. | 日本語版文書改版履歴 .....                                             | 76 |

## 図の一覧

|       |                                                          |    |

|-------|----------------------------------------------------------|----|

| 図 1.  | 電源供給方式                                                   | 11 |

| 図 2.  | パワーオンリセット／パワーダウンリセット波形                                   | 17 |

| 図 3.  | PVD の閾値                                                  | 18 |

| 図 4.  | リセットピン回路概要                                               | 19 |

| 図 5.  | STM32CubeMX のスクリーンショット例                                  | 22 |

| 図 6.  | 16x16 LFBGA354 互換性                                       | 24 |

| 図 7.  | 10x10 TFBGA257 互換性                                       | 25 |

| 図 8.  | 12x12 TFBGA361 互換性                                       | 26 |

| 図 9.  | 18x18 LFBGA448 互換性                                       | 27 |

| 図 10. | HSE 外部クロック                                               | 28 |

| 図 11. | HSE クリスタル / セラミック発振子                                     | 28 |

| 図 12. | LSE 外部クロック                                               | 30 |

| 図 13. | LSE クリスタル / セラミック発振子                                     | 30 |

| 図 14. | BOOT モード選択の例                                             | 33 |

| 図 15. | BOOT ピンの一般的な接続図                                          | 34 |

| 図 16. | ブートフロー概要                                                 | 35 |

| 図 17. | ホストとボードの接続                                               | 36 |

| 図 18. | JTAG/SWD MIPI10 コネクタ接続例                                  | 37 |

| 図 19. | JTAG/SWD/UART VCP STDC14 コネクタ接続例                         | 38 |

| 図 20. | パラレルトレースポート付き JTAG/SWD の Mictor38 接続例                    | 40 |

| 図 21. | LED の接続例                                                 | 41 |

| 図 22. | 負荷容量と電圧別 I/O 速度概要                                        | 43 |

| 図 23. | 6 層 PCB スタック例                                            | 46 |

| 図 24. | 4 層 PCB スタック例                                            | 47 |

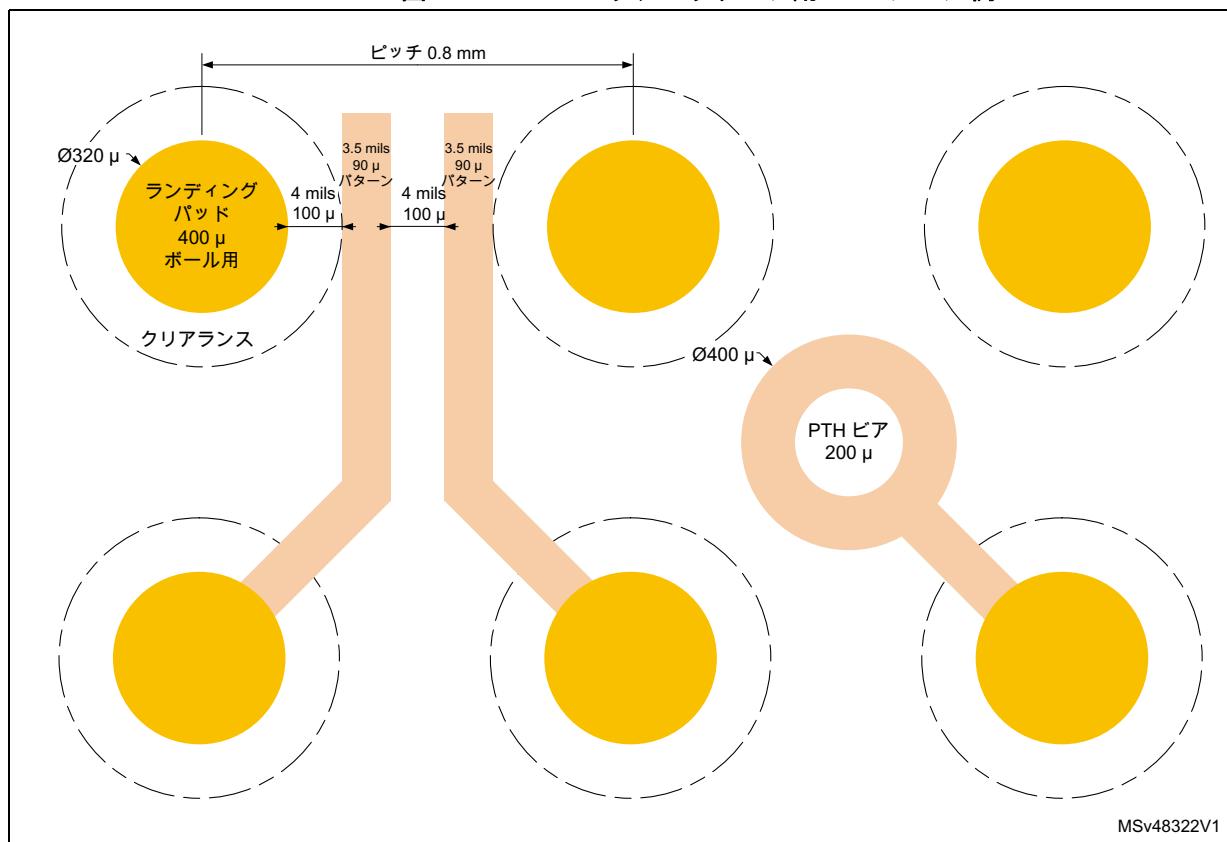

| 図 25. | 0.8 mm ピッチパッケージ用 PCB ルール例                                | 48 |

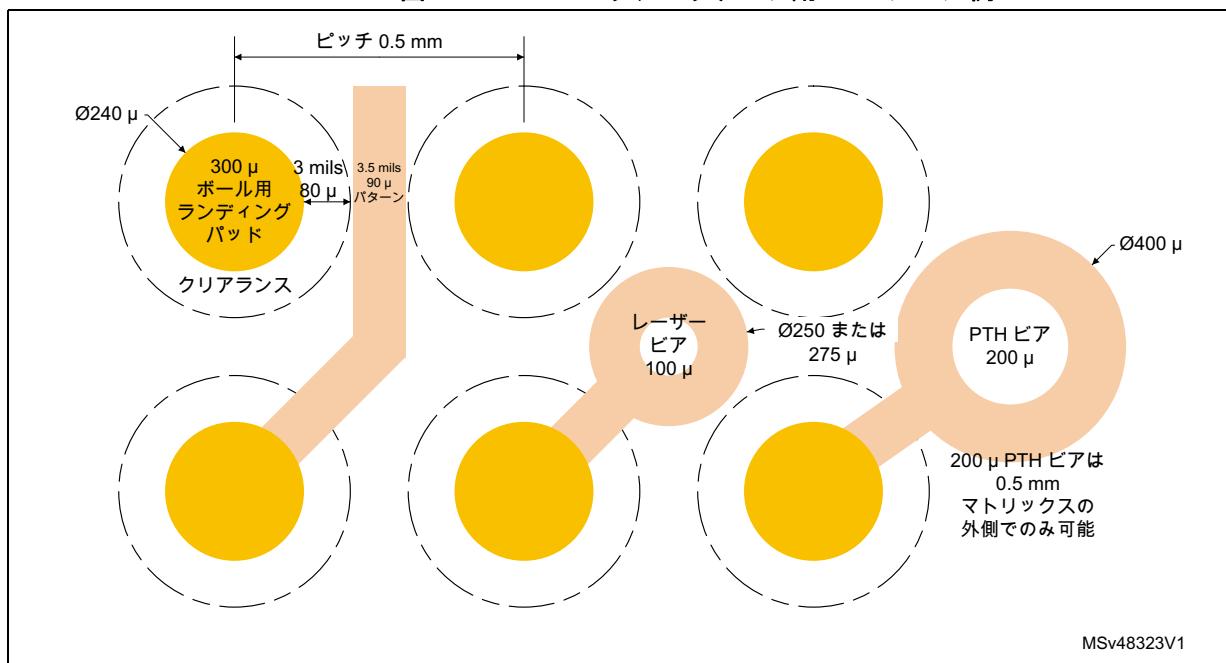

| 図 26. | 0.5 mm ピッチパッケージ用 PCB ルール例                                | 49 |

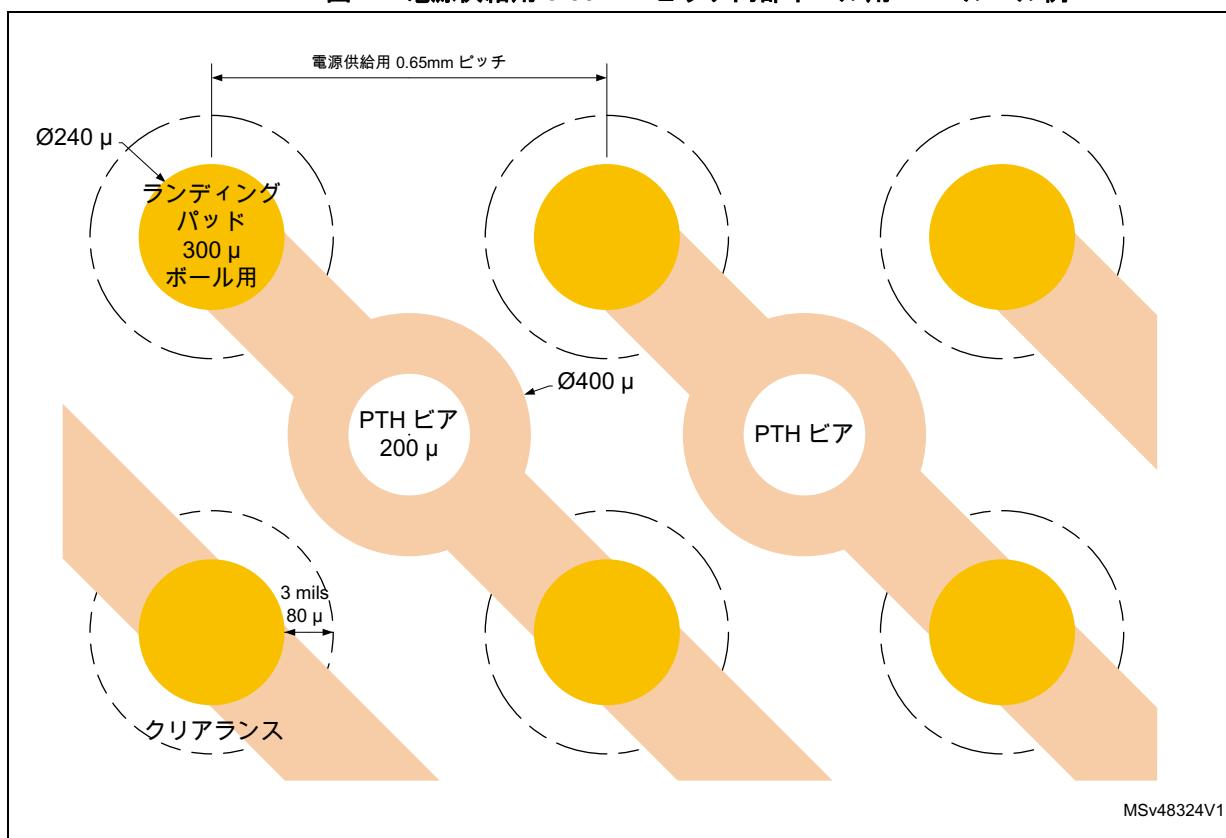

| 図 27. | 電源供給用 0.65mm ピッチ内部ボール用 PCB ルール例                          | 49 |

| 図 28. | デカップリング用コンデンサのレイアウト例                                     | 50 |

| 図 29. | オシレータ／クリスタル発振子 HSE 推奨回路                                  | 52 |

| 図 30. | DDR3L 使用時の 3.3 V I/O ディスクリート電源例                          | 54 |

| 図 31. | DDR3L 使用時の 3.3 V I/O PMIC 例                              | 55 |

| 図 32. | LPDDR2/LPDDR3 使用時の 1.8 V I/O PMIC 例                      | 56 |

| 図 33. | DDR3L 16/32 ビット接続例                                       | 57 |

| 図 34. | LPDDR2/LPDDR3 32 ビット接続例                                  | 58 |

| 図 35. | 外部レベルシフタ付き SD カード接続例                                     | 60 |

| 図 36. | 3.3 V I/O SD カード接続例                                      | 61 |

| 図 37. | eMMC™ 接続例                                                | 62 |

| 図 38. | SLC NAND-Flash 接続例                                       | 63 |

| 図 39. | シリアル Flash 接続例                                           | 64 |

| 図 40. | デュアルシリアル Flash 接続例                                       | 65 |

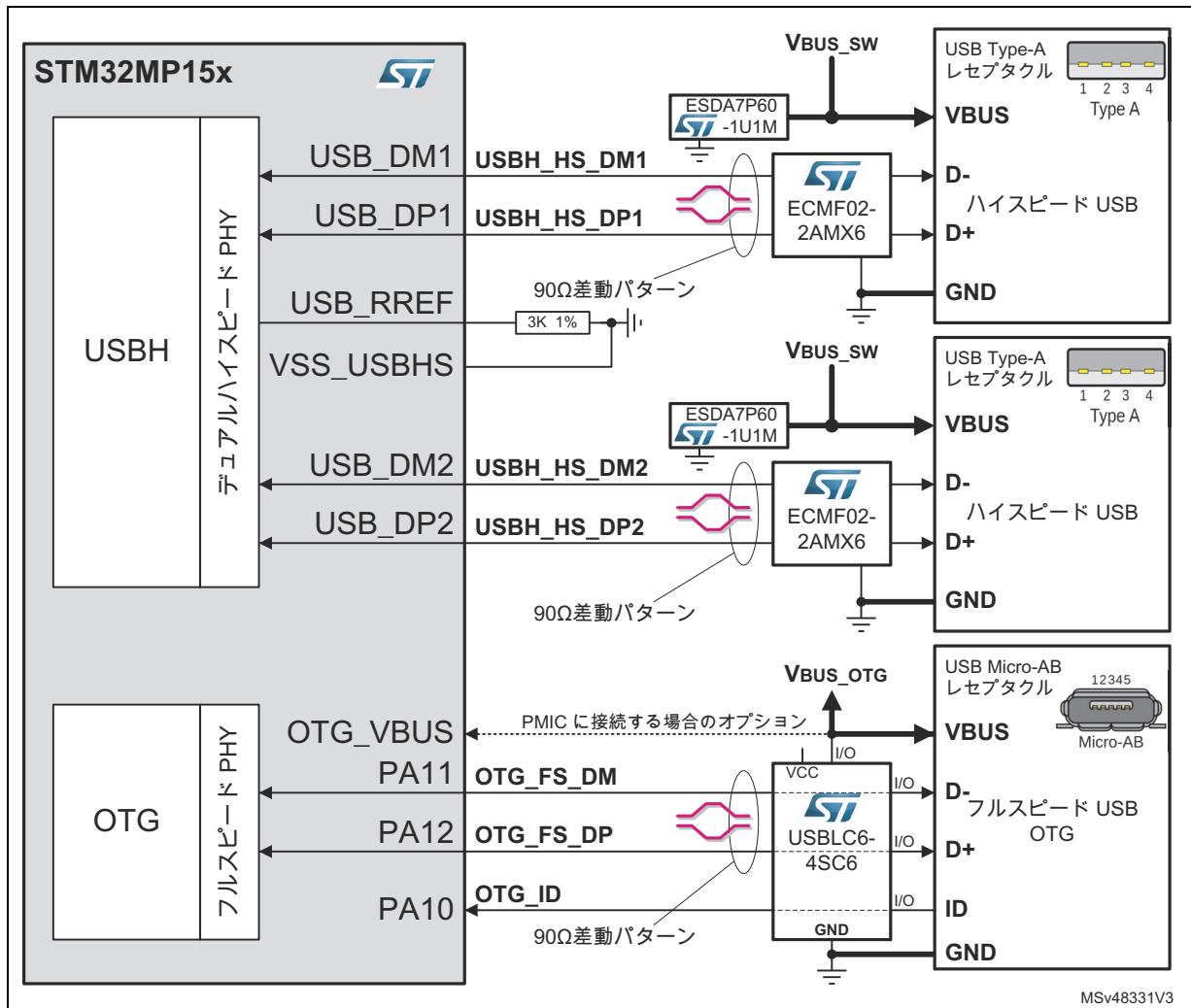

| 図 41. | USB 2 ポートホストハイスピード + OTG フルスピード接続例                       | 66 |

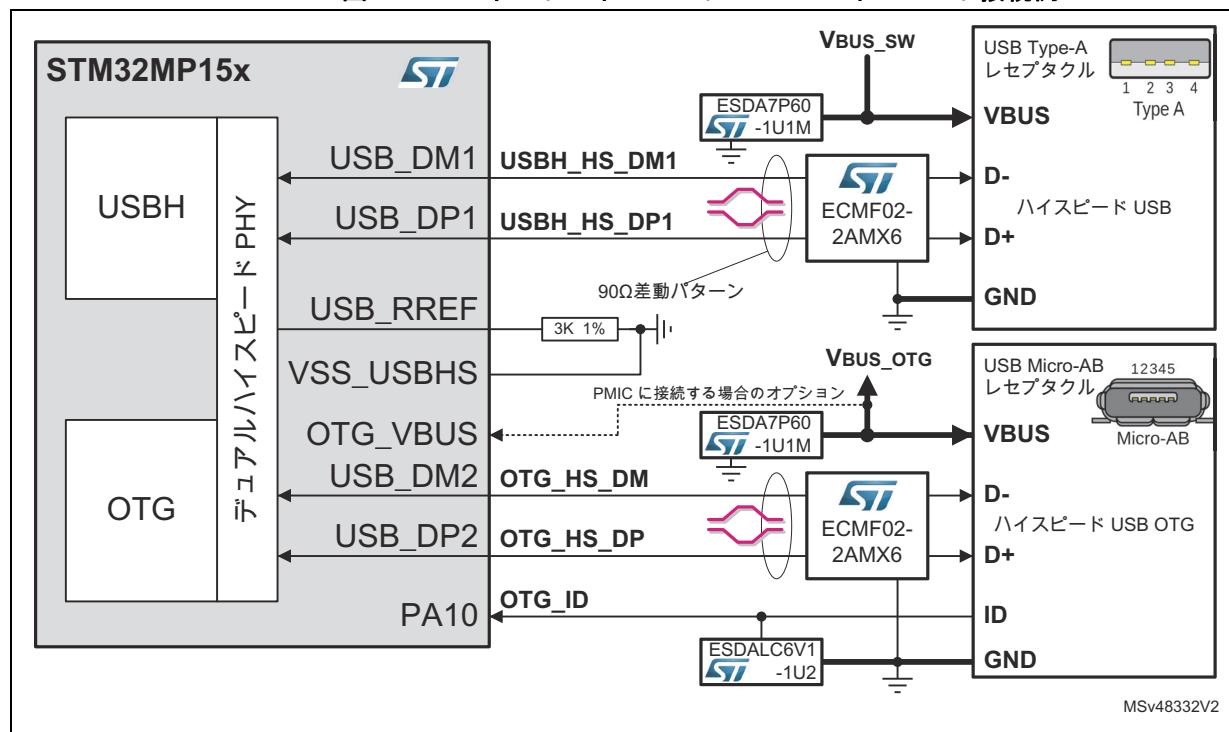

| 図 42. | USB ホストハイスピード + OTG ハイスピード接続例                            | 67 |

| 図 43. | 0.8 mm ボールピッチパッケージ USB ハイスピード PCB パターン例                  | 68 |

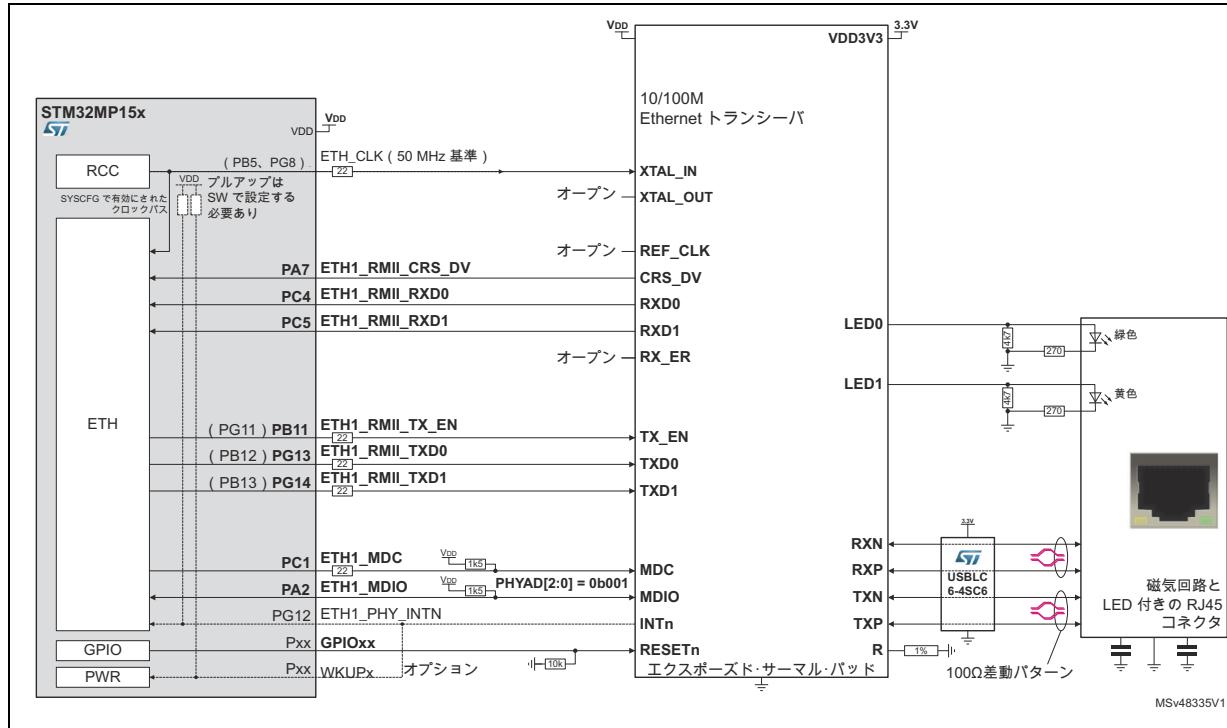

| 図 44. | 10/100M Ethernet PHY 接続例                                 | 69 |

| 図 45. | RCC からの REFCLK を使った 10/100M Ethernet PHY 接続例             | 70 |

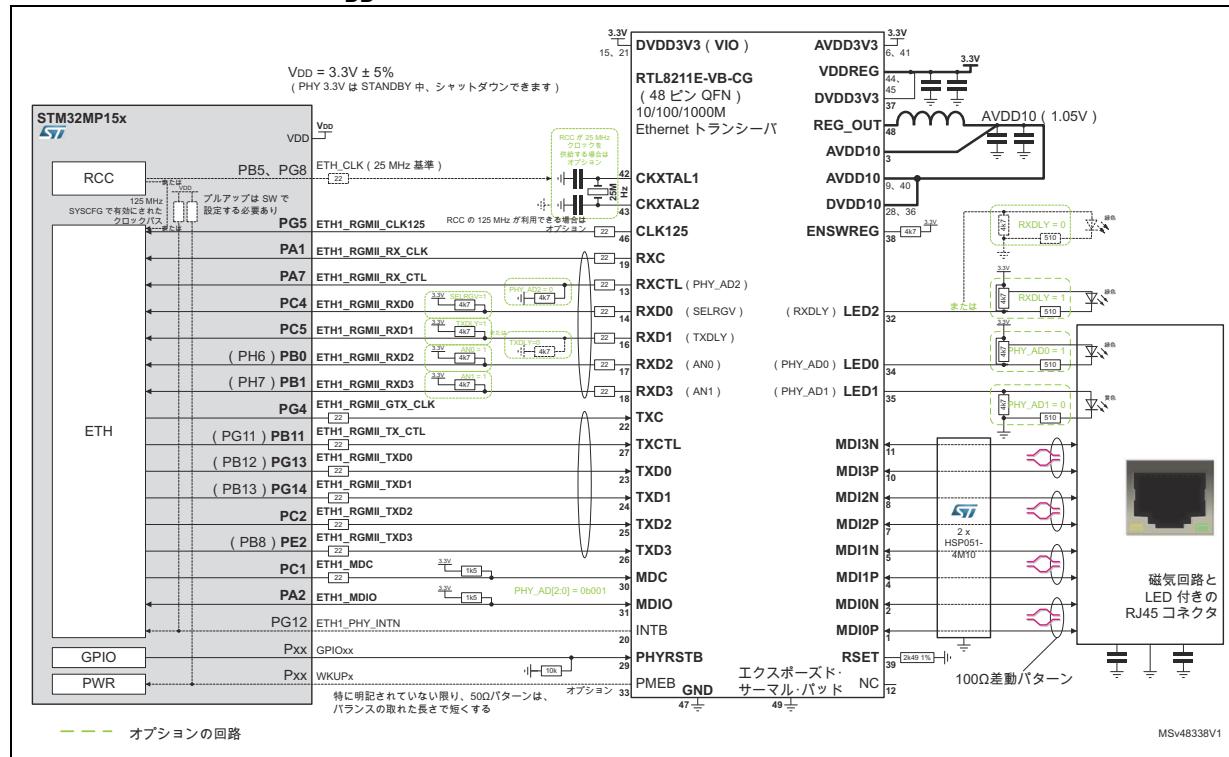

| 図 46. | VDD = 3.3 V (RTL8211E) を使ったギガビット Ethernet PHY 接続例        | 71 |

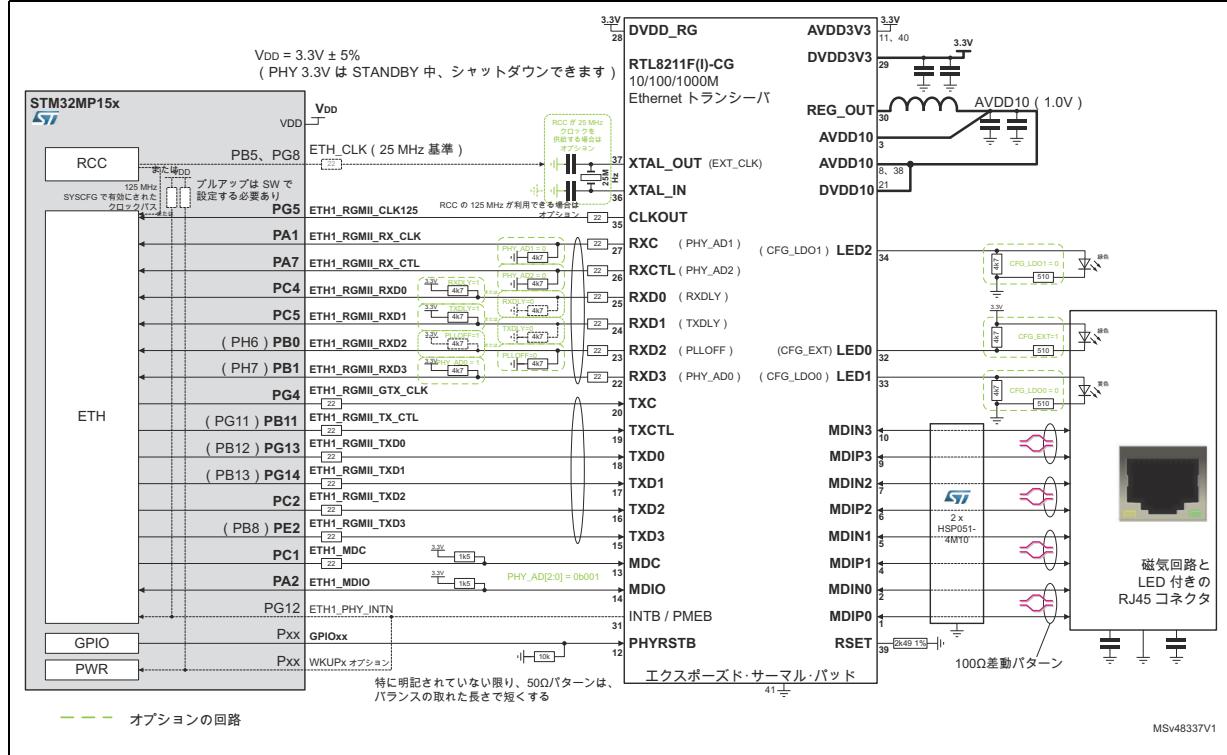

| 図 47. | VDD = 3.3 V (RTL8211F) を使ったギガビット Ethernet PHY 接続例        | 72 |

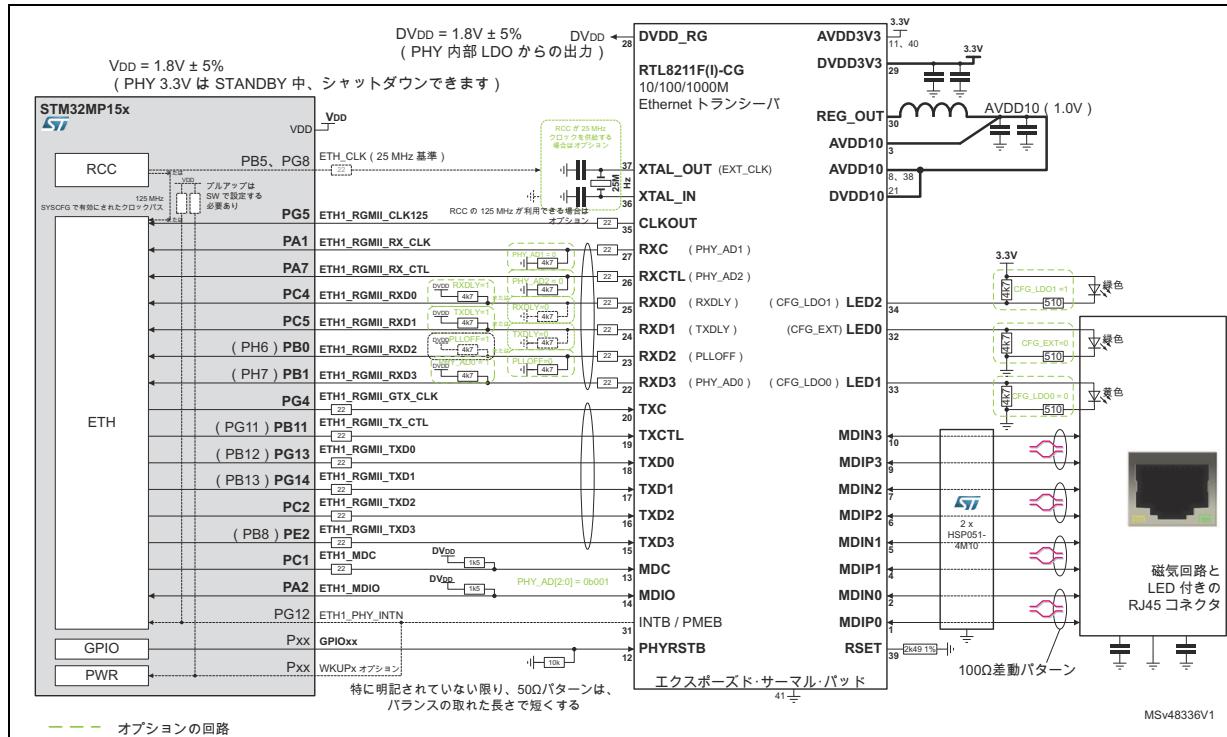

| 図 48. | VDD = 1.8 V (RTL8211F) を使ったギガビット Ethernet PHY 接続例        | 72 |

| 図 49. | VDD = 3.3 V (RTL8363NB-VG) を使ったギガビット Ethernet 2 ポートスイッチ例 | 73 |

# 参考資料

AN5031

図の一覧

|       |                                          |    |

|-------|------------------------------------------|----|

| 図 50. | DSI によるディスプレイ接続例                         | 74 |

| 図 51. | 0.8 mm ポールピッチパッケージ DSI インタフェース PCB パターン例 | 75 |

# 参考資料

## 1 一般情報

本書は、Arm<sup>®(a)</sup> ベースのデバイスに適用されます。

## 2 参照文献

以下のドキュメントを、[www.st.com](http://www.st.com) より入手できます。

表 1. 参照文献

| 参照      | タイトル                                                                             |

|---------|----------------------------------------------------------------------------------|

| AN2867  | STM8AF/AL/SおよびSTM32マイクロコントローラ用発振器設計ガイド                                           |

| AN1709  | STマイクロコントローラ EMCデザインガイド                                                          |

| AN5275  | USB DFU/USART protocols used in STM32MP1 Series bootloaders                      |

| AN5168  | DDR configuration on STM32MP1 Series MPUs                                        |

| AN5089  | STM32MP1 Series and STPMIC1 hardware / software integration                      |

| AN5122  | STM32MP1 Series DDR memory routing guidelines                                    |

| AN5256  | STM32MP151, STM32MP153 and STM32MP157 discrete power supply hardware integration |

| UM2535  | Evaluation boards with STM32MP157 MPUs                                           |

| UM2534  | Discovery kits with STM32MP157 MPUs                                              |

| RM0441  | STM32MP151 advanced Arm <sup>®</sup> -based 32-bit MPU                           |

| RM0442  | STM32MP153 advanced Arm <sup>®</sup> -based 32-bit MPU                           |

| RM0436  | STM32MP157 advanced Arm <sup>®</sup> -based 32-bit MPU                           |

| DS12500 | STM32MP151A/D データシート                                                             |

| DS12501 | STM32MP151C/F データシート                                                             |

| DS12502 | STM32MP153A/D データシート                                                             |

| DS12503 | STM32MP153C/F データシート                                                             |

| DS12504 | STM32MP157A/D データシート                                                             |

| DS12505 | STM32MP157C/F データシート                                                             |

a. Arm は、米国内およびその他の地域にある Arm Limited（またはその子会社）の登録商標です。

## 3 用語

表 2. 用語

| 用語      | 意味                                                                                                       |

|---------|----------------------------------------------------------------------------------------------------------|

| ADC     | A/D コンバータ                                                                                                |

| AHB     | Advanced high-performance bus(アドバンスト・ハイパフォーマンス・バス)                                                       |

| CSI     | 低電力内部オシレータ                                                                                               |

| CTI     | Cross-trigger interface(クロストリガインターフェース)                                                                  |

| DAC     | D/A コンバータ                                                                                                |

| DAP     | Debug access port(デバッグアクセスポート)                                                                           |

| DDRCTRL | Double data rate SDRAM controller(ダブルデータレート SDRAM コントローラ)LPDDR2 および DDR3/DDR3L プロトコルをサポート                |

| DDRPHYC | DDR 物理インターフェースコントロール                                                                                     |

| DSI     | Display serial interface master(ディスプレイ・シリアル・インターフェース・マスター)                                               |

| ETH     | Ethernet コントローラ                                                                                          |

| EXTI    | Extended interrupt and event controller(拡張割込み／イベントコントローラ)                                                |

| FMC     | Flexible memory controller(フレキシブル・メモリ・コントローラ)                                                            |

| GPIO    | General Purpose input Output (汎用入出力)                                                                     |

| HDP     | Hardware debug port(ハードウェア・デバッグ・ポート)                                                                     |

| HSE     | High-speed external quartz oscillator(高速外部水晶発振器)                                                         |

| HSI     | High-speed internal oscillator(高速内部オシレータ)                                                                |

| I2C     | Inter IC bus(インター IC バス)                                                                                 |

| IWDG    | Independent watchdog(独立型ウォッチドッグ)                                                                         |

| JTAG    | Joint Test Action Group(ジェイタグ)デバッグインターフェース                                                               |

| LSE     | Low-speed external quartz oscillator(低速外部水晶発振器)                                                          |

| LSI     | Low-speed internal oscillator(低速内部オシレータ)                                                                 |

| MDIOS   | Management data input/output slave(マネージメント・データ・インプット/アウトプット・スレーブ)Ethernet 物理インターフェースを制御するために使われるインターフェース |

| OTG     | USB on the Go ホストにもデバイスにもなれるインターフェースの USB 規格                                                             |

| OTP     | One time program memory(ワンタイム・プログラム・メモリ)                                                                 |

| PMIC    | Power management integrated circuit(電源管理IC)外部信号とシリアルインターフェースから制御可能なさまざまなプラットフォーム電源を提供する外部回路              |

| PWR     | 電源制御                                                                                                     |

| QUADSPI | Quad data lanes serial peripheral interface(クワッド・データ・レーン・シリアル・ペリフェラル・インターフェース)                           |

| RCC     | Reset and clock control(リセットおよびクロック制御)                                                                   |

| ROM     | Read-only memory(読み出し専用メモリ)                                                                              |

| RTC     | Real time clock(リアルタイムクロック)                                                                              |

# 参考資料

表 2. 用語 (続き)

| 用語      | 意味                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------|

| SDMMC   | Secure digital and multiMedia card interface(セキュア・デジタル・マルチメディア・カード・インターフェース)SD、MMC、eMMC、および SDIO プロトコルをサポート |

| SMPS    | Switched mode power supply(スイッチモード電源)                                                                       |

| SPI     | Serial peripheral interface(シリアル・ペリフェラル・インターフェース)                                                           |

| STM     | System trace microcell(システム・トレース・マクロセル)                                                                     |

| SW      | ソフトウェア                                                                                                      |

| SWD     | Serial wire debug(シリアル・ワイヤ・デバッグ)                                                                            |

| SWO     | Single wire output(シングルワイヤ出力)トレースポート                                                                        |

| SYSCFG  | System configuration(システム設定)                                                                                |

| TAMP    | Tamper detection IP(タンパ検出 IP)                                                                               |

| TEMP    | Temperature sensor(温度センサ)                                                                                   |

| UART    | Universal asynchronous receiver/transmitter (ユニバーサル非同期レシーバ／トランスマッタ)                                         |

| USART   | Universal synchronous/asynchronous receiver/transmitter (ユニバーサル同期／非同期レシーバ／トランスマッタ)                          |

| USB     | Universal serial bus(ユニバーサル・シリアル・バス)                                                                        |

| USBH    | USB host controller (USB ホストコントローラ)                                                                         |

| VREFBUF | ADC/DAC voltage reference buffer (ADC/DAC 電圧リファレンスバッファ )                                                    |

# 参考資料

AN5031

電源

4

## 電源

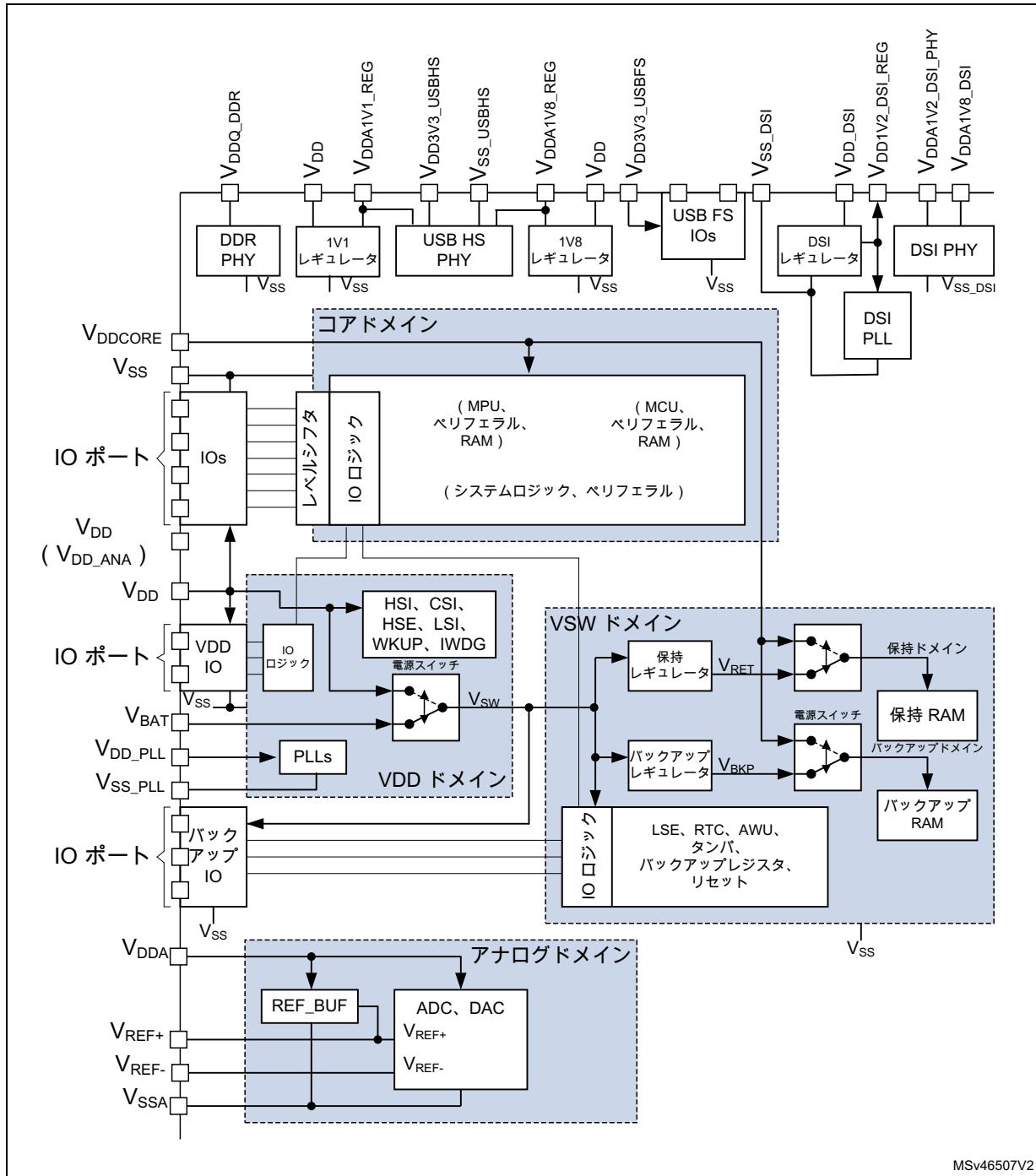

図 1. 電源供給方式

MSv46507V2

AN5031Rev 1 [English Rev 2]

11/77

## 4.1 概要

注： 詳細および保証動作範囲については製品データシートを参照してください。

- メイン IO 電圧源 ( $V_{DD}$ ) の範囲は 1.71~3.6 V です。

- コアロジック動作電圧源 ( $V_{DDCORE}$ ) の範囲は 1.18~1.25 V です。

- USB 電源 ( $V_{DD3V3\_USBHS}$  および  $V_{DD3V3\_USBFS}$ ) の範囲は 3.07~3.6 V です。

- 一部の内部ブロックに電源供給するために、内蔵レギュレータが使用されます。

- DSI 用の 1.2 V LDO は、DSI PLL および  $V_{DD1V2\_DSI\_PHY}$  ピンに電源供給するために使用され、 $V_{DD1V2\_DSI\_REG}$  から出力されます。範囲は 1.15~1.26 V です。

- DSI および USB 用の 1.8 V LDO は、内部的に USB および  $V_{DDA1V8\_DSI}$  に電源供給するために使用され、 $V_{DDA1V8\_REG}$  から出力されます。BYPASS\_REG1V8 =  $V_{DD}$  の場合、 $V_{DDA1V8\_REG}$  は外部から供給する必要があります。その場合、範囲は 1.65~1.95 V です。

- USB 用の 1.1 V LDO は、外部デカッピング用の  $V_{DD1V1\_REG}$  から出力されます。

- 注： 内蔵レギュレータは外部コンポーネントの電源供給に使用出来ません。

- リアルタイムクロック (RTC) およびバックアップレジスタは、主電源  $V_{DD}$  がオフの場合、 $V_{BAT}$  から電源供給することができます。 $V_{BAT}$  と  $V_{DD}$  の間の自動スイッチを備えたこの内部電源は  $V_{SW}$  ドメインと呼ばれ、PI8、PC13、PC14、PC15 パッドへの電源供給にも使用されます。 $V_{BAT}$  電圧の範囲は 1.20~3.6 V です。

- $V_{DD}$  が  $V_{BAT}$  より高い電圧の場合、外部バックアップ電圧デバイス (スーパーイヤパシタなど) 用に  $V_{BAT}$  から少量の充電電流を供給できます。

### 4.1.1 独立した ADC および DAC コンバータ用電源と基準電圧

変換の精度とダイナミックレンジを向上させるため、ADC、DAC、およびリファレンスには独立した電源が供給されます。この電源は、PCB のノイズを防ぐために、個別にフィルタしシールドすることができます。

アナログ動作電圧源 ( $V_{DDA}$ ) の範囲は 1.71~3.6 V です (DAC は、 $V_{DDA}$  が 1.8 V 以上の場合にのみ使用できます)。

- ADC/DAC/VREFBUF 用の電源入力は、独立した  $V_{DDA}$  ピンから供給されます。

- ADC 電源のグランドは、独立した  $V_{SSA}$  ピンとして用意されています。

いずれの場合も、 $V_{SSA}$  ピンは、 $V_{SS}$  と同じグランドに外部で接続する必要があります。

#### 外部 VREF

独立した外部基準電圧を ADC/DAC の  $V_{REF+}$  入力に接続できます。 $V_{REF+}$  の電圧は、1.62 V から  $V_{DDA}$  の範囲にすることができます。

注： DAC を機能させるには、1.8 V を超える  $V_{REF+}$  が必要です。

#### 内部 VREF

VREFBUF ブロックで  $V_{REF+}$  の内部基準電圧を有効にすることができます。

$V_{REF+}$  の電圧は、1.5 V、1.8 V、2.048 V、および 2.5 V から選択できます。

$V_{REF+}$  ピンで内部 VREF を使用できるので、負荷がデータシートの値内に保たれていれば、外部で (たとえば、アナログコンパレータのリファレンス用に) これを使用できます。

注： DAC を機能させるには、1.8 V を超える  $V_{REF+}$  が必要です。

注： VREFBUF には、 $V_{REF+} + 0.3$  V 以上の  $V_{DDA}$  が必要です。

# 参考資料

AN5031

電源

注意： $V_{REF-}$  ピンが用意されているパッケージでは、このピンを外部で  $V_{SSA}$  に固定する必要があります。

## ADC アナログ入力スイッチ用ブースタ

ADC 入力はアナログスイッチで切り替えられますが、このスイッチは  $V_{DDA}$  電源が 2.7 V 未満の場合に性能が低下します。ADC のアナログ性能を最大化するために、 $V_{DD}$  (2.7 V を超える場合) または  $V_{DDA}$  からの内蔵 3.3 V ブースタのいずれかをアナログスイッチに供給することもできます。

これは SYSCFG\_PMCR レジスタで制御されます。

表 3. ANASWVDD および EN\_BOOSTER 用の推奨設定

| $V_{DDA}$<br>(V) | $V_{DD}$<br>(V) | --> | SYSCFG_PMCR.<br>ANASWVDD | SYSCFG_PMCR.<br>EN_BOOSTER | スイッチ電源             | ADC アナログ性能 |

|------------------|-----------------|-----|--------------------------|----------------------------|--------------------|------------|

| >2.7             | 1.71~3.6        | -   | 0                        | 0                          | $V_{DDA}$ (>2.7 V) | 最大         |

| <2.7             | >2.7            | -   | 1                        | 0                          | $V_{DD}$ (>2.7 V)  |            |

|                  | <2.7            | -   | 0                        | 1 <sup>(1)</sup>           | ブースタ (~3.3 V)      |            |

|                  |                 |     |                          | 0 <sup>(2)</sup>           | $V_{DDA}$ (<2.7 V) | 低下         |

1. ブースタ電圧は安定するまでに最大 50  $\mu$ s かかることがあります。

2. ADC アナログ性能の低下が許容できる場合、ブースタを無効にすれば最大 250  $\mu$ A を節約できます。

## 4.1.2 バッテリバックアップ

$V_{DD}$  がオフになった場合に、バックアップレジスタ、BKPSRAM、および RETRAM の内容を保持するため、 $V_{BAT}$  ピンをバッテリやその他の電源に接続することができます。

$V_{BAT}$  ピンから RTC ユニットにも電源が供給され、主デジタル電源 ( $V_{DD}$ ) がオフの場合でも RTC が動作できるようにします。 $V_{BAT}$  電源への切り替えは、リセットブロックに組み込まれているパワーダウンリセット (PDR) 回路によって制御されます。

外部バッテリを使用しないアプリケーションでは、 $V_{BAT}$  を  $V_{DD}$  に外部接続する必要があります。

## 4.1.3 電圧レギュレータ

BYPASS\_REG1V8 =  $V_{SS}$  の場合、パワーオンリセット後に 1.8 V LDO (USB および DSI 用) は常に有効になります。これは、(LP/LPLV-) STOP による影響を受けませんが、STANDBY への移行時に無効になります。

1.1 V LDO (USB 用) は、パワーオンリセット後に常に有効になります。これは、(LP/LPLV-) STOP による影響を受けませんが、STANDBY への移行時に無効になります。

1.2 V LDO (DSI 用) は、システムリセット後に無効になり、DSI を使用する前にソフトウェアで有効にする必要があります。これは、(LP/LPLV-) STOP による影響を受けませんが、STANDBY への移行時に無効になります。

注：特に明記されていない限り、内蔵レギュレータは外部コンポーネントの電源供給に使用出来ません。

## 4.2 電源供給方式

回路には、以下の複数の電源から電力供給されます。

- $V_{DD}$  は、IO および STANDBY モード中に電源が供給され続ける内部部品の主電源です。有効な電圧範囲は 1.71~3.6 V です（例：1.8 V、2.5 V、3.0 V、または 3.3 V 標準）。

- これらの電源は外部のデカップリングコンデンサに接続する必要があります（表 4 参照）。

- $V_{DD\_DSI}$ 、 $V_{DD\_PLL}$ 、および  $V_{DD\_ANA}$  は  $V_{DD}$  に接続する必要があります。

- $V_{DDCORE}$  は、メインのデジタル電圧で、STANDBY モード中に外部から停止できます。RUN モード中の電圧範囲は 1.18~1.25/1.38 V（標準 1.2/1.34 V）です。

- この電源は外部のデカップリングコンデンサに接続する必要があります（表 4 参照）

- $V_{DDCORE}$  は特定の STOP モード（LPLV\_Stop）でさらに低減できます。これには、PWR\_ON 信号（たとえば、外部電源管理 IC のSTPMIC1）または PWR\_LP 信号（ディスクリート SMPS コンポーネントによる）のどちらかが関与します。

- $V_{BAT}$  ピンは、外部バッテリに接続できます（ $1.2 \text{ V} < V_{BAT} < 3.6 \text{ V}$ ）。

- RETRAM が使われている場合は、 $V_{BAT}$  の最小値は 1.4 V です。

- アプリケーションでバックアップバッテリをサポートしていない場合は、このピンを  $V_{DD}$  に接続することを推奨します。

- アプリケーションでバックアップバッテリをサポートしている場合は、 $V_{BAT}$  と  $V_{SS}$  間に 100 nF のセラミックデカップリングコンデンサを付加することを推奨します。

- アプリケーションで  $V_{BAT}$  にスーパーキャパシタを使っている場合は、追加のデカップリングは必要ありません。

- $V_{DDA}$  ピンはアナログ（ADC/DAC/VREFBUF）電源で、外部のデカップリングコンデンサに接続する必要があります（表 4 参照）。

- $V_{REF+}$  ピンは、 $V_{DDA}$  外部電源に接続できます。独立した内部または外部の基準電圧が  $V_{REF+}$  に印加されている場合は、デカップリングコンデンサをこのピンと  $V_{REF-}$  の間に接続する必要があります（表 4 参照）。セクション 4.1.1：を参照してください。

アナログ・ノイズをフィルタリングするには、事前に次のことに注意してください。

- $V_{DDA}$  は、インダクタベースのフィルタを介して  $V_{DD}$  に接続できます。

- $V_{DDQ\_DDR}$  は DDR IO の電源で、外部のデカップリングコンデンサに接続する必要があります（表 4 参照）。

- DDR3 メモリとのインターフェース用の電圧範囲は 1.425~1.575 V です（標準 1.5 V）。

- DDR3L メモリとのインターフェース用の電圧範囲は 1.283~1.45 V です（標準 1.35 V）。

- LPDDR2 または LPDDR3 メモリとのインターフェース用の電圧範囲は 1.14~1.3 V です（標準 1.2 V）。

- $V_{DDA1V2\_DSI\_REG}$  ピンは 内部レギュレータの出力で、外部のデカップリングコンデンサに接続する必要があります（表 4 参照）。

- $V_{DDA1V2\_DSI\_REG}$  は DS1 PLL に内部的に接続されています。

- $V_{DDA1V2\_DSI\_PHY}$  はアナログDSI PHY 電源です。電圧範囲は 1.15~1.26 V です（標準 1.2 V）。 $V_{DDA1V2\_DSI\_PHY}$  は  $V_{DDA1V2\_DSI\_REG}$  に接続する必要があります。

- $V_{DD3V3\_USBHS}$  および  $V_{DD3V3\_USBFS}$  はそれぞれ、USB ハイスピード PHY および USB フルスピード PHY の電源です。電圧範囲は 3.07~3.6 V です。ともに外部のデカップリングコンデンサに接続する必要があります（表 4 参照）。

- $V_{DD3V3\_USBFS}$  は OTG\_VBUS および OTG\_ID (PA10) ピンに供給するために使用されます。そのため、USB ハイスピードデュアルポートまたは USB ハイスピードデバイスを使用する

# 参考資料

場合は、 $V_{DD3V3\_USBFS}$  も供給する必要があります。使用しない場合は、 $V_{DD}$  に接続する必要があります。

- $V_{DDA1V8\_REG}$  ピンは 内部レギュレータの出力で、外部のデカッピングコンデンサに接続する必要があります (表 4 参照)。

- $V_{DDA1V8\_REG}$  は USB PHY および USB PLL に内部的に接続されています。

- 内部  $V_{DDA1V8\_REG}$  レギュレータはデフォルトで有効であり、ソフトウェアで制御できます。これは STANDBY 中、常に停止されます。

- 1.8 V 電圧レギュレータ構成では、電圧レギュレータを有効または無効にするために BYPASS\_REG1V8 ピンを  $V_{SS}$  または  $V_{DD}$  に接続する必要があります。 $V_{DD}$  が 2.25 V を下回る場合には、以下のように 1.8 V レギュレータをバイパスすることが必須です。

- BYPASS\_REG1V8 =  $V_{DD}$ 。この場合、 $V_{DDA1V8\_REG}$  ピンは  $V_{DD}$  (1.98V 未満の場合) または専用の 1.65~1.98 V 電源 (標準 1.8 V) に接続する必要があります。

- BYPASS\_REG1V8 =  $V_{SS}$ 。この場合、1.8 V 電圧レギュレータを正しく動作させるためには、 $V_{DD}$  は 2.25 V を超えていなければなりません。

- 詳細は、セクション 4.1.3: および関連するデバイスデータシートの「Embedded regulators characteristics」のセクションを参照してください。

- $V_{DDA1V8\_DSI}$  はアナログ DSI 電源です。電圧範囲は 1.65~1.98 V です (標準 1.8 V)。 $V_{DDA1V8\_DSI}$  は  $V_{DDA1V8\_REG}$  に接続する必要があります。また、外部のデカッピングコンデンサにも接続する必要があります (表 4 参照)。

- $V_{DDA1V1\_REG}$  ピンは 内部レギュレータの出力で、外部のデカッピングコンデンサに接続する必要があります (表 4 参照)。電圧範囲は 1.045~1.155 V です (標準 1.1 V)。

- $V_{DDA1V1\_REG}$  は USB PHY に内部的に接続されています。

- 内部  $V_{DDA1V1\_REG}$  レギュレータはデフォルトで有効であり、ソフトウェアで制御できます。これは STANDBY 中、常に停止されます。

**注意 :**  $V_{DDA1V8\_REG}$  がオフの時は、 $V_{DD3V3\_USBHS}$  はオフにしてください。そうしないと、永続的な STM32MP15x ラインの損傷が発生する可能性があります。PMIC を使用するか、またはディスクリート部品で電源を実装する場合は外部コンポーネントを使用して電源投入の順序を守る必要があります。

**注意 :** すべての電源グランド ( $V_{SS}$ 、 $V_{SS\_ANA}$ 、 $V_{SS\_PLL}$ 、 $V_{SS\_USBHS}$ 、 $V_{SS\_DSI}$ 、 $V_{SSA}$ 、および  $V_{REF-}$ ) は、共に電源ブレーンと接続する必要があります。

# 参考資料

表 4. パッケージ別デカップリングコンデンサ値と数量の推奨値<sup>(1)</sup>

| 電源ピン                                                       | デカップリング<br>ポイント <sup>(2)</sup>                | 値                               | LFBGA354 | TFBGA257           | TFBGA361           | LFBGA448 | コメント                                                                             |

|------------------------------------------------------------|-----------------------------------------------|---------------------------------|----------|--------------------|--------------------|----------|----------------------------------------------------------------------------------|

| V <sub>BAT</sub>                                           | V <sub>SS</sub>                               | 100 nF                          | 1        | 1                  | 1                  | 1        | V <sub>BAT</sub> が V <sub>DD</sub> に接続されているか、バッテリの代わりにスーパー・キャパシタが使われている場合は、省略できる |

| V <sub>DDCORE</sub>                                        | V <sub>SS</sub>                               | 1 μF <sup>(3)</sup>             | 15       | 15                 | 15                 | 15       | PMIC/SMPS のコンデンサは含まない                                                            |

| V <sub>DDQ_DDR</sub>                                       | V <sub>SS</sub>                               | 1 nF                            | 2        | 2                  | 2                  | 2        | PMIC/SMPS のコンデンサおよび DDR メモリの追加コンデンサは含まない                                         |

|                                                            |                                               | 3.3 nF                          | 0        | 3                  | 0                  | 0        |                                                                                  |

|                                                            |                                               | 1 μF <sup>(3)</sup>             | 4        | 2                  | 7                  | 7        |                                                                                  |

| V <sub>DD_ANA</sub>                                        | V <sub>SS_ANA</sub>                           | 1 μF <sup>(3)</sup>             | 1        | - <sup>(4)</sup>   | 1                  | 1        | -                                                                                |

| V <sub>DD_PLL</sub> 、V <sub>DD_PLL2</sub>                  | V <sub>SS_PLL</sub> 、<br>V <sub>SS_PLL2</sub> | 1 μF <sup>(3)</sup>             | 2        | -<br>(4)           | -<br>(4)           | 2        | PMIC/SMPS のコンデンサは含まない                                                            |

| V <sub>DD</sub> 、V <sub>DD_DSI</sub>                       | V <sub>SS</sub>                               | 1 μF <sup>(3)</sup>             | 4        | 4                  | 4                  | 4        |                                                                                  |

| V <sub>DD1V2_DSI_REG</sub> 、<br>V <sub>DD1V2_DSI_PHY</sub> | V <sub>SS_DSI</sub>                           | 2.2 μF <sup>(3)</sup>           | 1        | -                  | 1                  | 1        | -                                                                                |

|                                                            | V <sub>SS</sub>                               |                                 | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                                  |

| V <sub>DDA1V8_REG</sub>                                    | V <sub>SS_USBHS</sub>                         | 2.2 μF <sup>(3)</sup>           | 1        | -                  | 1                  | 1        | -                                                                                |

|                                                            | V <sub>SS</sub>                               |                                 | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                                  |

| V <sub>DDA1V8_DSI</sub>                                    | V <sub>SS_DSI</sub>                           | 1 μF <sup>(3)</sup>             | 1        | -                  | 1                  | 1        | V <sub>DDA1V8_DSI</sub> は V <sub>DDA1V8_REG</sub> に接続する必要がある                     |

|                                                            | V <sub>SS</sub>                               |                                 | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                                  |

| V <sub>DDA1V1_REG</sub>                                    | V <sub>SS_USBHS</sub>                         | 2.2 μF <sup>(3)</sup>           | 1        | -                  | 1                  | 1        | -                                                                                |

|                                                            | V <sub>SS</sub>                               |                                 | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                                  |

| V <sub>DD3V3_USBHS</sub> 、<br>V <sub>DD3V3_USBFS</sub>     | V <sub>SS_USBHS</sub>                         | 1 μF <sup>(3)</sup>             | 1        | -                  | 1                  | 1        | -                                                                                |

| V <sub>DD3V3_USB</sub>                                     | V <sub>SS</sub>                               |                                 | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                                  |

| V <sub>DDA</sub>                                           | V <sub>SSA</sub>                              | 100 nF +<br>1 μF <sup>(3)</sup> | 1+1      | 1+1                | 1+1                | 1+1      | V <sub>SSA</sub> は V <sub>SS</sub> プレーンに接続する必要がある                                |

| V <sub>REF+</sub>                                          | V <sub>REF-</sub> および<br>V <sub>SSA</sub>     | 100 nF +<br>1 μF <sup>(3)</sup> | 1+1      | -                  | -                  | 1+1      | V <sub>REF-</sub> は V <sub>SSA</sub> 、次に V <sub>SS</sub> プレーンに接続する必要がある          |

|                                                            | V <sub>SSA</sub>                              |                                 | -        | 1+1 <sup>(6)</sup> | 1+1 <sup>(6)</sup> | -        | V <sub>SSA</sub> は V <sub>SS</sub> プレーンに接続する必要がある                                |

- この表はガイドラインとして使用できます。コンデンサの実際の数と値は、コンデンサのサイズ、コンデンサの誘電体、PCB テクノロジーなど、さまざまなパラメータに応じて、製品の電源インテグリティシミュレーション結果を使用して調整できます。

- すべての V<sub>SS\_X</sub> と V<sub>SSA</sub> は共通の V<sub>SS</sub> プレーンに接続する必要があります。

- 多層セラミックコンデンサ (MLCC)

- 電源は内部で V<sub>DD</sub> とマージされます。

- 電源リターンバスは内部で V<sub>SS</sub> とマージされます。

- V<sub>REF-</sub> は内部で V<sub>SSA</sub> とマージされます。

## 4.3 リセットおよび電源供給スーパーバイザ

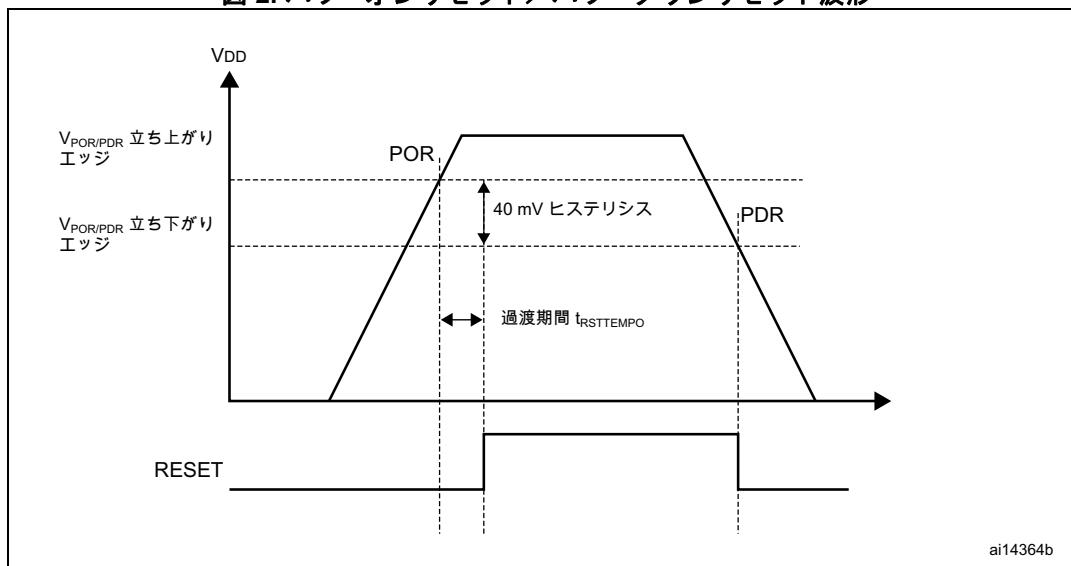

### 4.3.1 パワーオンリセット (POR) / パワーダウンリセット (PDR)

このデバイスには、1.71 V 以上での正常な動作を可能にする POR/PDR 統合回路が搭載されています。

デバイスは、 $V_{DD}$  が規定の閾値  $V_{POR/PDR}$  を下回っている間は、外部のリセット回路を必要とせずに、リセットモードを維持します。POR/PDR 閾値の詳細については、製品データシートの電気的特性を参照してください。

図 2. パワーオンリセット/パワーダウンリセット波形

ai14364b

- $t_{RSTTEMPO}$  は約 2.6 ms です。 $V_{POR/PDR}$  立ち上がりエッジは 1.67 V（標準）、 $V_{POR/PDR}$  立ち下がりエッジは 1.63 V（標準）です。実際の値については、STM32MP15x のデータシートを参照してください。

内部パワーオンリセット (POR) / パワーダウンリセット (PDR) 回路は、PDO\_ON ピンによって無効にできます。その場合、外部電源供給スーパーバイザでは  $V_{DD}$  を監視する必要があり、 $V_{DD}$  が指定されている閾値を下回っている間はデバイスをリセットモードに維持する必要があります。

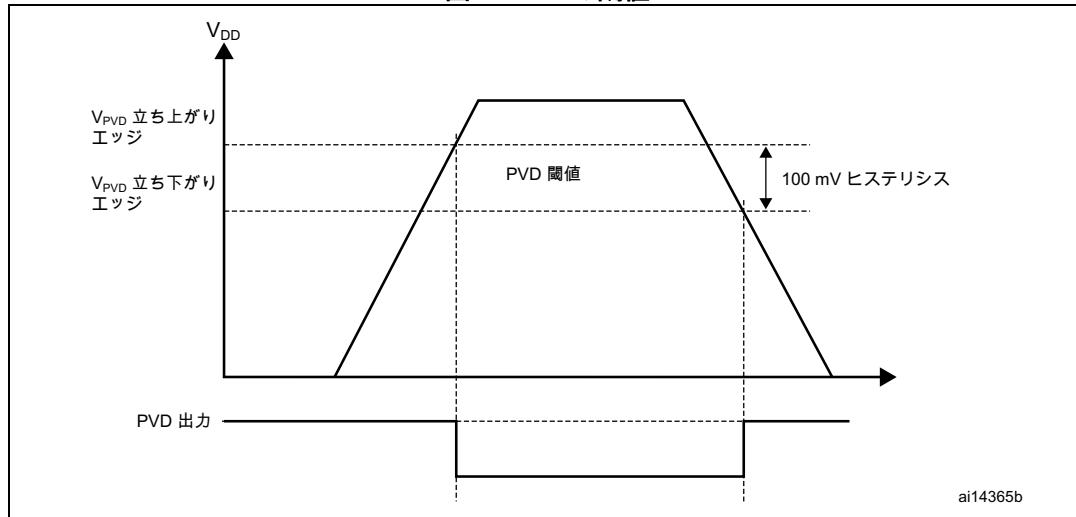

### 4.3.2 プログラム可能な電圧検出器 (PVD)

PVD を使用した  $V_{DD}$  電源の監視が可能です。電源制御レジスタ (PWR\_CR) の PLS[2:0] ビットで選択した閾値と比較することで監視します。

PVD は PVDE ビットをセットすることで有効になります。

$V_{DD}$  が PVD の閾値よりも高いか低いかを示すために、電源制御/ステータスレジスタ (PWR\_CSR) の PVDO フラグが使用できます。このイベントは EXTI のライン 16 に内部接続され、EXTI レジスタで有効な場合は割込みリクエストを生成させることができます。EXTI ライン 16 の立ち上がり/立ち下がりエッジの設定に応じて、 $V_{DD}$  が PVD の閾値を下回るか、上回ったとき、あるいはその両方で、PVD 出力割込みを生成させることができます。たとえば、サービスルーチンで、緊急停止処理を実行することなどが可能です。

図 3. PVD の閾値

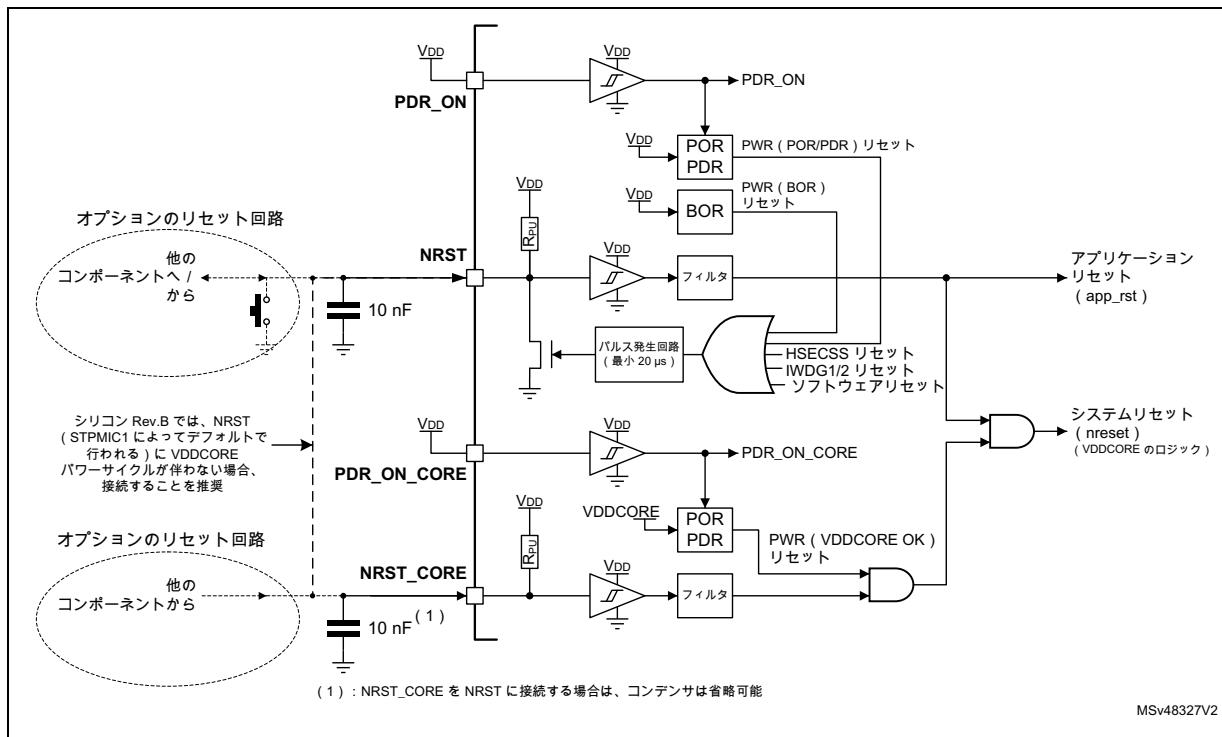

### 4.3.3 アプリケーションリセットとシステムリセット

アプリケーションリセット (app\_rst) は、次のいずれかのソースから生成されます。

- NRST パッドからのリセット

- por\_rst 信号からのリセット（一般にパワーオンリセットと呼ばれます）

- bor\_rst 信号からのリセット（一般にブラウンアウトと呼ばれます）

- 独立型ウォッチドッグ 1 からのリセット (iwdg1\_rst)

- 独立型ウォッチドッグ 2 からのリセット (iwdg2\_rst)

- AIRCR レジスタ (MCYSRST) 経由の Cortex-M4 (MCU) からのソフトウェアリセット（オプションバイトの OPT MCU\_SYSRST\_EN が許可している場合）

- Cortex-A7 (MPU) で RCC の MPSYSRST ビットが“1”にセットされている場合、RCC からのソフトウェアリセット

- クロックセキュリティシステム機能がアクティブになっている場合、HSE の障害 (hcss\_rst)

システムリセット (nreset) は、次のいずれかのソースから生成されます。

- app\_rst 信号からのリセット（アプリケーションリセット）

- vcore\_rst 信号からのリセット

**注：** システムが STANDBY になっている場合、V<sub>DDCORE</sub> はオフになりますが、V<sub>DD</sub> はまだ継続します。そのため、システムが STANDBY を終了するときに、vcore\_rst 信号がアクティブになり nreset リセットが生成されます。

**注：** シリコン Rev.B (DBGMCU\_IDC.REV\_ID = 0x2000) では、NRST (STPMIC1 によってデフォルトで行われる) に VDDCORE パワーサイクルが伴わない場合、NRST を NRST\_CORE に接続することを推奨します。詳細については、製品の正誤表シートを参照してください。

リセットの適用範囲の詳細については、リファレンスマニュアルの RCC のセクションを参照してください。

# 参考資料

AN5031

電源

図 4. リセットピン回路概要

## 5 パッケージ

### 5.1 パッケージの選択

パッケージを選択する際は、アプリケーションに強く依存する制約を考慮する必要があります。

以下のリストに、よくある制約をまとめます。

- 必要なインターフェースの数。

パッケージによっては、一部のインターフェースを使用できない場合があります。

パッケージによっては、一部のインターフェースを組み合わせることができない場合があります。

詳細については、製品データシートを参照してください。

- PCB テクノロジーの制約。

ピッチを小さく、ボール密度を高くするには、PCB の層数を増やし、上位クラスの PCB が必要となり、マイクロビア（レーザービア）テクノロジーでのスタックアップが必要になります。

- パッケージの高さ

- PCB の使用可能面積

- 热的制約（パッケージが大きいほど放熱能力が向上します）

表 5. パッケージ一覧

| サイズ (mm) <sup>(1)</sup> | 16 x 16  | 10 x 10  | 12 x 12  | 18 x 18  |

|-------------------------|----------|----------|----------|----------|

| 最小ピッチ (mm)              | 0.8      | 0.5      | 0.5      | 0.8      |

| 高さ (mm)                 | 1.4      | 1.2      | 1.2      | 1.4      |

| 販売番号                    | LFBGA354 | TFBGA257 | TFBGA361 | LFBGA448 |

| STM32MP151xxx           | X        | X        | X        | X        |

| STM32MP153xxx           | X        | X        | X        | X        |

| STM32MP157xxx           | X        | X        | X        | X        |

1. 標準本体サイズ

# 参考資料

表 6. パッケージ別主要機能の相違

| パッケージ            |                       | TFBGA257                                              | LFBGA354                             | TFBGA361         | LFBGA448        |  |  |  |  |  |

|------------------|-----------------------|-------------------------------------------------------|--------------------------------------|------------------|-----------------|--|--|--|--|--|

| パッケージ            | 本体サイズ (mm)            | 10x10                                                 | 16x16                                | 12x12            | 18x18           |  |  |  |  |  |

|                  | ピッチ (mm)<br>(中央 0.65) | 0.5<br>(中央 0.65)                                      | 0.8                                  | 0.5<br>(中央 0.65) | 0.8             |  |  |  |  |  |

|                  | 厚さ (mm)               | <1.2                                                  | <1.4                                 | <1.2             | <1.4            |  |  |  |  |  |

|                  | ボール数                  | 257                                                   | 354                                  | 361              | 448             |  |  |  |  |  |

| SDRAM            | LPDDR2/3              | 16 ビット 533 MHz                                        | 最大 1 GB、シングルランク                      | -                | 最大 1 GB、シングルランク |  |  |  |  |  |

|                  |                       | 32 ビット 533 MHz                                        | -                                    | 最大 1 GB、シングルランク  | -               |  |  |  |  |  |

|                  | DDR3/3L               | 16 ビット 533 MHz                                        | 最大 1 GB、シングルランク                      |                  |                 |  |  |  |  |  |

|                  |                       | 32 ビット 533 MHz                                        | -                                    | 最大 1 GB、シングルランク  |                 |  |  |  |  |  |

| FMC              | パラレルアドレス/データ 8/16 ビット | -                                                     | 4×CS、最大 4×64 MB                      |                  |                 |  |  |  |  |  |

|                  | パラレル AD-Mux 8/16 ビット  | 4×CS、最大 4×64 MB                                       |                                      |                  |                 |  |  |  |  |  |

|                  | NAND 8/16 ビット         | 可、2×CS、SLC、BCH4/8                                     |                                      |                  |                 |  |  |  |  |  |

| ギガビット Ethernet   |                       | -                                                     | PTP および EEE 機能付き MII、RMII、GMII、RGMII |                  |                 |  |  |  |  |  |

| 10/100M Ethernet |                       | PTP および EEE 機能付き MII、RMII                             |                                      |                  |                 |  |  |  |  |  |

| 割込み付き GPIO (合計数) |                       | 98                                                    | 148                                  | 176              |                 |  |  |  |  |  |

| -                | セキュリティ保護可能 GPIO       | -                                                     | 8                                    |                  |                 |  |  |  |  |  |

|                  | ウェイクアップピン             | 4                                                     | 6                                    |                  |                 |  |  |  |  |  |

|                  | タンパピン (アクティブランプ)      | 2 (1)                                                 | 3 (1)                                |                  |                 |  |  |  |  |  |

| 最大 16 ビット同期 ADC  |                       | 2 (それぞれ 16/14/12/10/8 ビットで最大 0.25/4.4/5/5.7/6.7 Msps) |                                      |                  |                 |  |  |  |  |  |

| -                | 低ノイズ 16 ビット (差動)      | -                                                     | 2 (1)                                |                  |                 |  |  |  |  |  |

|                  | 16 ビット (差動)           | 6 (1)                                                 | 7 (1)                                |                  |                 |  |  |  |  |  |

|                  | 14 ビット (差動)           | 11 (3)                                                | 13 (3)                               |                  |                 |  |  |  |  |  |

|                  | ADC チャネル合計            | 17                                                    | 22                                   |                  |                 |  |  |  |  |  |

## 5.2 ピンへのオルタネート機能のマッピング

ピンへのペリフェラルのオルタネート機能マッピングを簡単に調べるには、[www.st.com](http://www.st.com) から入手できる STM32CubeMX ツールを使用することを推奨します。

図 5. STM32CubeMX のスクリーンショット例

## 5.3 異なる型番間のパッケージ互換性

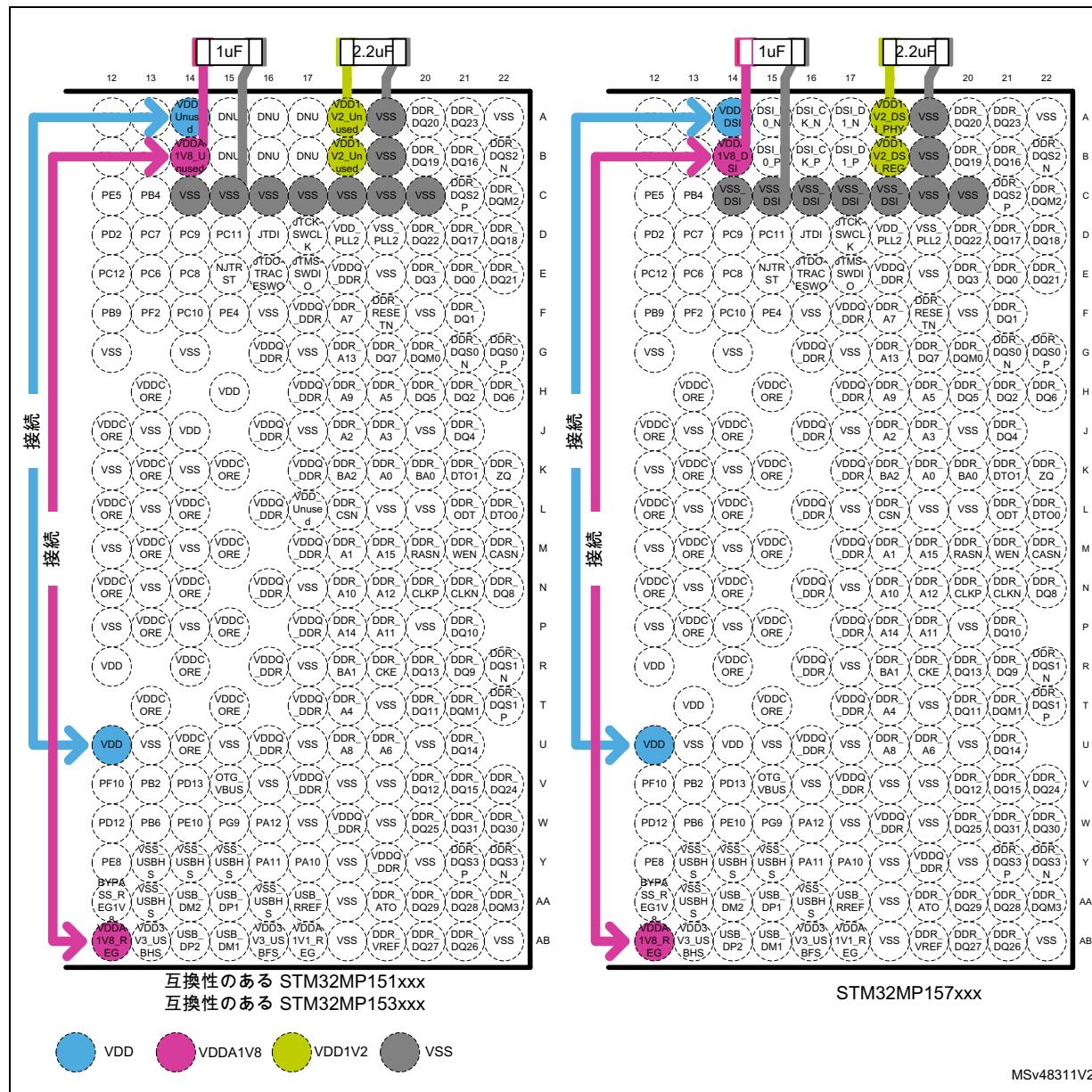

STM32MP151xxx、STM32MP153xxx デバイスは STM32MP157xxx デバイスとは少し異なります。しかししながら、わずかの追加の接続を犠牲にして互換性のある PCB を構築することができます。

表 7. デバイスの互換性のまとめ

| PCB の用途対象     | 使用するデバイス      |               |                                       |

|---------------|---------------|---------------|---------------------------------------|

|               | STM32MP151xxx | STM32MP153xxx | STM32MP157xxx                         |

| STM32MP151xxx | 互換性あり         | 互換性あり         | 互換可能<br>(表 8~表 11 および<br>図 6~図 9 を参照) |

| STM32MP153xxx | 互換性あり         | 互換性あり         |                                       |

| STM32MP157xxx | 互換性あり         | 互換性あり         | 互換性あり                                 |

# 參考資料

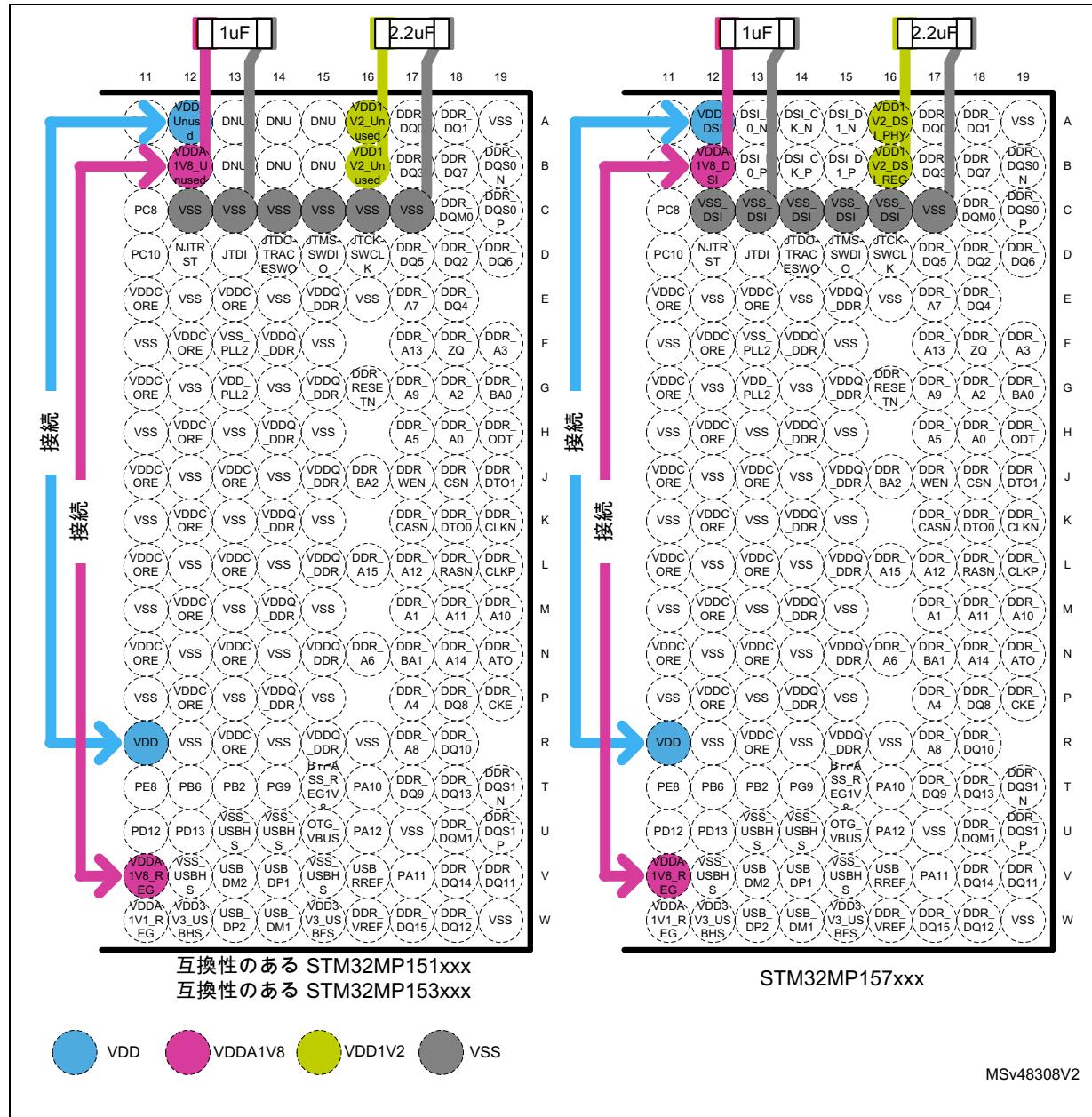

表 8. 16x16 LFBGA354 用の STM32MP151xxx および STM32MP153xxx の互換性

| 追加するポート接続                     | STM32MP151xxx  | STM32MP153xxx | STM32MP157xxx                      |

|-------------------------------|----------------|---------------|------------------------------------|

| B12 から V11 (VDD1V8_REG)       | VDDA1V8_Unused | VDDA1V8_DSI   |                                    |

| A16 から B16 + 1 $\mu$ F から VSS | VDD1V2_Unused  |               | VDD1V2_DSI_PHY /<br>VDD1V2_DSI_REG |

| A12 ~ VDD                     | VDD_Unused     |               | VDD_DSI                            |

図 6. 16x16 LFBGA354 互換性

注：この図は理解を助けるためのものであり、実際の基板パターンとコンポーネントのサイズ/配置を反映していません。

# 參考資料

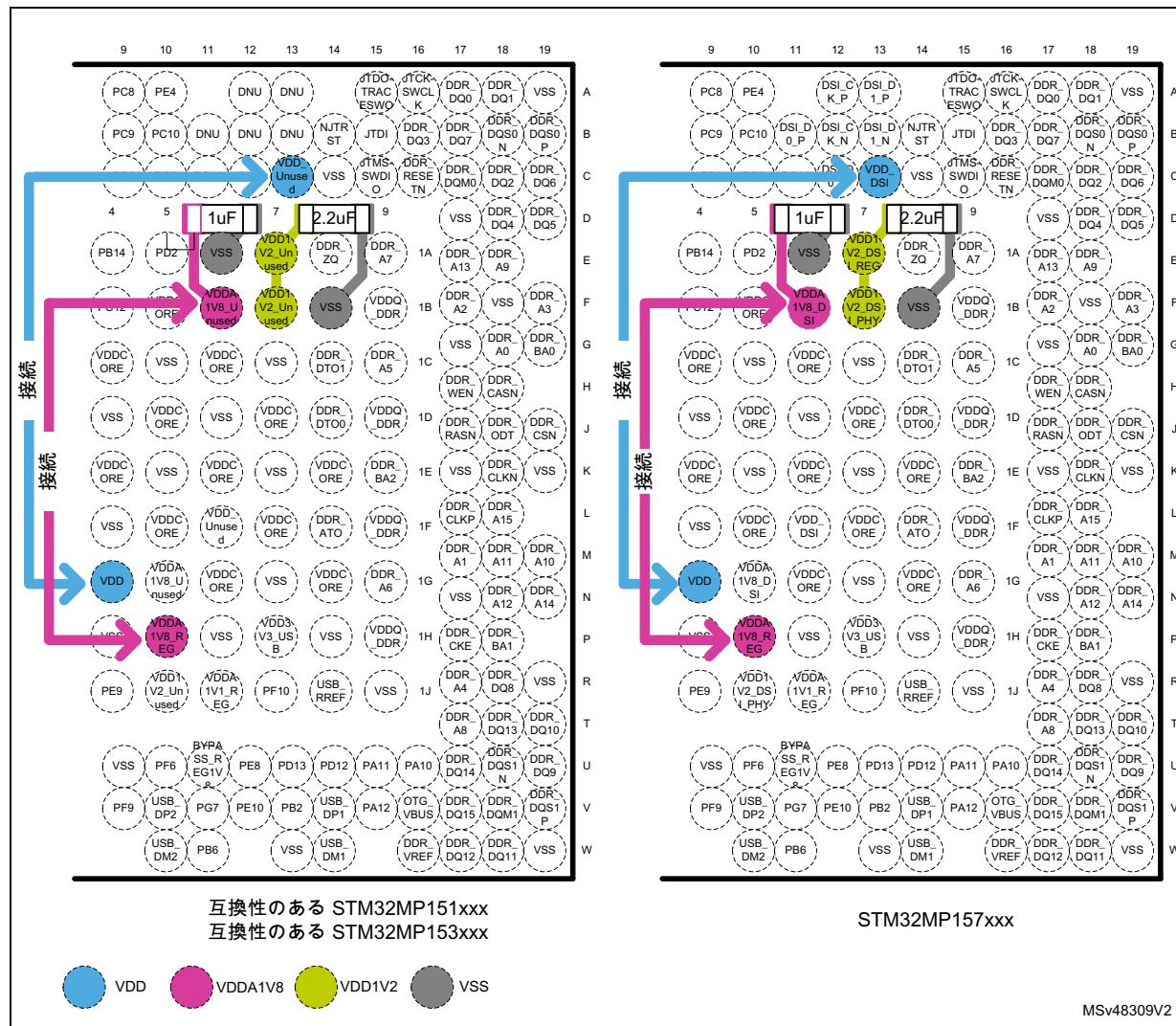

表 9. 10x10 TFBGA257 用の STM32MP151xxx および STM32MP153xxx の互換性

| 追加するポート接続                | STM32MP151xxx  | STM32MP153xxx | STM32MP157xxx                      |

|--------------------------|----------------|---------------|------------------------------------|

| 1B6 から 1H5 (VDD1V8_REG)  | VDDA1V8_Unused | VDDA1V8_DSI   |                                    |

| 1B7 から 1A7 + 1 μF から VSS | VDD1V2_Unused  |               | VDD1V2_DSI_PHY /<br>VDD1V2_DSI_REG |

| C13 ~ VDD                | VDD_Unused     |               | VDD_DSI                            |

図 7. 10x10 TFBGA257 互換性

注：この図は理解を助けるためのものであり、実際の基板パターンとコンポーネントのサイズ/配置を反映していません。

# 参考資料

## パッケージ

AN5031

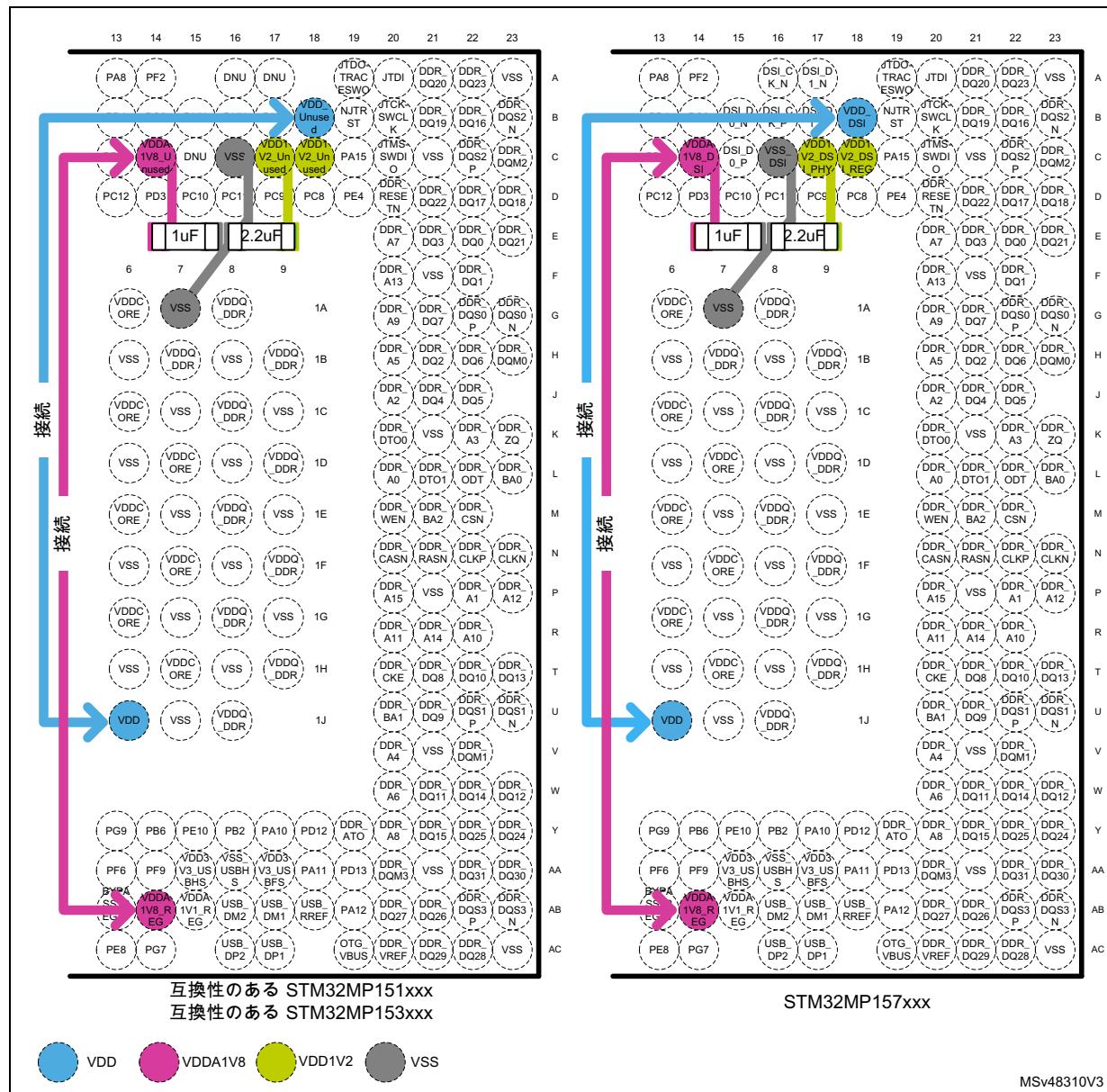

表 10. 12x12 TFBGA361 用の STM32MP151xxx および STM32MP153xxx の互換性

| 追加するボール接続                | STM32MP151xxx  | STM32MP153xxx | STM32MP157xxx                      |

|--------------------------|----------------|---------------|------------------------------------|

| C14 から AB14 (VDD1V8_REG) | VDDA1V8_Unused |               | VDDA1V8_DSI                        |

| C17 から C18 + 1 μF から VSS | VDD1V2_Unused  |               | VDD1V2_DS1_PHY /<br>VDD1V2_DS1_REG |

| B18 ~ VDD                | VDD_Unused     |               | VDD_DSI                            |

図 8. 12x12 TFBGA361 互換性

注: この図は理解を助けるためのものであり、実際の基板パターンとコンポーネントのサイズ/配置を反映していません。

# 参考資料

AN5031

パッケージ

表 11. 18x18 LFBGA448 用の STM32MP151xxx および STM32MP153xxx の互換性

| 追加するポール接続                | STM32MP151xxx  | STM32MP153xxx                   | STM32MP157xxx |

|--------------------------|----------------|---------------------------------|---------------|

| B14 から AB12 (VDD1V8_REG) | VDDA1V8_Unused | VDDA1V8_DSI                     |               |

| A18 から B18 + 1 μF から VSS | VDD1V2_Unused  | VDD1V2_DS1_PHY / VDD1V2_DS1_REG |               |

| A14 ~ VDD                | VDD_Unused     | VDD_DSI                         |               |

図 9. 18x18 LFBGA448 互換性

注: この図は理解を助けるためのものであり、実際の基板パターンとコンポーネントのサイズ/配置を反映していません。

## 6 クロック

サブシステムクロックを駆動するために、下記のさまざまなクロックソースが使用できます。

- HSI オシレータ・クロック（ハイスピード内部クロック信号）

- CSI オシレータ・クロック（低電力内部クロック信号）

- HSE オシレータ・クロック（ハイスピード外部クロック信号）

- PLL1/2/3/4 クロック

- DSI クロックを生成する PLL\_DSI（最大 1 GHz）<sup>(a)</sup>

- USB クロックを生成する PLL\_USB（480 MHz）

デバイスには、2 つの 2 次クロックソースがあります。

- 32 kHz ロースピード内蔵 RC（LSI RC）。独立型ウォッчドッグを駆動し、オプションで、STOP/STANDBY モードからの自動ウェイクアップに使用される RTC を駆動します。

- 32.768 kHz ロースピード外部クリスタル（LSE クリスタル）。オプションで、リアルタイムクロック（RTCCLK）を駆動します。

それぞれのクロック・ソースは、使用しないときに個別にオン/オフを切り替えて、電力消費を最適化可能です。

クロックツリーについては、RM0436、RM0441、RM0442 リファレンスマニュアルを参照してください。

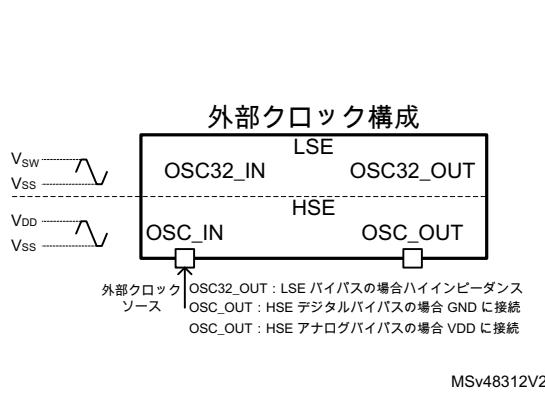

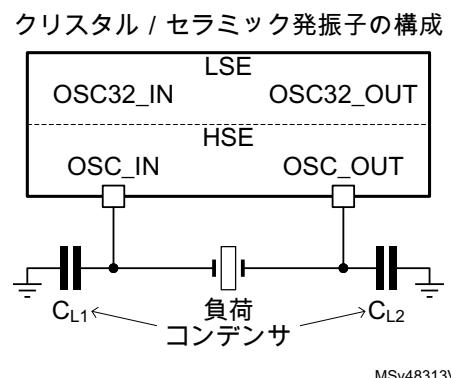

### 6.1 HSE OSC クロック

ハイスピード外部クロック信号（HSE）は、次のどちらかのクロックソースから生成できます。

- HSE ユーザ外部クロック（図 10 を参照）

- HSE 外部クリスタル/セラミック発振子（図 11 を参照）

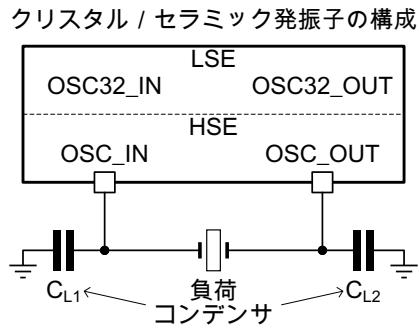

図 10. HSE 外部クロック

図 11. HSE クリスタル/セラミック発振子

- ST マイクロコントローラ用発振器設計ガイドアプリケーションノート (AN2867) を参照してください。

- 負荷容量  $C_L$  の計算式は次のとおりです。 $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  ここで、 $C_{stray}$  は、ピンの容量と、基板やパターンの PCB 関連容量です。一般的には 2~4 pF の範囲です。この値を最小に抑えるには、[セクション 9 : 42 ページの推奨事項](#) を参照してください。

- 使用できるかどうかは STM32MP15x ラインのデバイスによって異なります。

## 6.1.1 外部ソース (HSE バイパス)

このモードでは、外部クロックソースが必要です。8~50 MHz の周波数を使用できます（実際の最大値については、STM32MP15x データシートを参照してください）。

約 50% のデューティサイクルの外部デジタル ( $V_{IL}/V_{IH}$ ) またはアナログ（最小振幅 200 mV pk-pk）クロック信号によって OSC\_IN ピンを駆動する必要があります。

注：USB ブートを可能にするために、BootROM では起動フェーズ中（つまり、NRST 立ち上がりエッジ時）に OSC\_OUT の接続をチェックすることにより、下記のように HSE モードを自動的に選択します。

- OSC\_OUT が GND に接続されている（最大 1 kΩ）: HSE デジタルバイパス

- OSC\_OUT が VDD に接続されている（最大 1 kΩ）: HSE アナログバイパス

- OSC\_OUT はハイインピーダンス、またはクリスタル／セラミック発振子に接続されている: HSE クリスタル／セラミック発振子モード

バイパスを使用すると、PWR\_ON によって外部クロックジェネレータを有効にして電力を節約できます（STANDBY では無効になります）。その場合、OSC\_IN クロック入力は、PWR\_ON の立ち上がりエッジが発生してから 10 ms 以内に安定している必要があります。

## 6.1.2 外部クリスタル／セラミック発振子 (HSE クリスタル)

外部オシレータの周波数範囲は 8~48 MHz です。

外部オシレータには、メインクロックの周波数を非常に高い精度で生成できるという利点があります。関連するハードウェア構成を [図 11](#) に示します。正確な USB ハイスピードクロックを取得するには、24 MHz のクリスタル周波数を使用することが適しています。

波形ひずみと発振開始時の安定化までの時間を少なくするために、クリスタル／セラミック発振子と負荷コンデンサはオシレータのピンのできるだけ近くに接続する必要があります。負荷コンデンサの値は、選択したクリスタル／セラミック発振子に応じて調整する必要があります。

$C_{L1}$  と  $C_{L2}$  には、クリスタル／セラミック発振子の負荷要件を満たすように選択された 5~25 pF の範囲（標準）の NP0/C0G コンデンサを使用することを推奨します。 $C_{L1}$  と  $C_{L2}$  は通常、同じ値とします。クリスタルのメーカーは通常、 $C_{L1}$  と  $C_{L2}$  の直列結合である負荷容量を指定します。 $C_{L1}$  と  $C_{L2}$  の大きさを決定するときは、PCB とピンの容量を含める必要があります（ピンと基板の合計容量の概算として 10 pF を使用できます）。

詳細については、ST マイクロコントローラ用発振器設計ガイド アプリケーションノート (AN2867) および製品データシートの電気特性のセクションを参照してください。

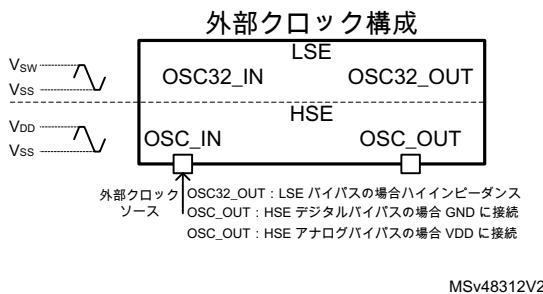

### 6.2 LSE OSC クロック

ロースピード外部クロック信号 (LSE) は、次のどちらかのクロック・ソースから生成できます。

- LSE ユーザ外部クロック (図 12 を参照)

- LSE 外部クリスタル/セラミック発振子 (図 13 を参照)

図 12. LSE 外部クロック

図 13. LSE クリスタル/セラミック発振子

1. 「LSE クリスタル/セラミック発振子」の図：

負荷容量  $C_L \leq 12.5 \text{ pF}$  の発振子を使用することを強くお勧めします。

2. 「LSE 外部クロック」と「LSE クリスタル/セラミック発振子」の図：

OSC32\_IN ピンと OSC32\_OUT ピンは、GPIO としても使用できますが、同一アプリケーションで RTC ピンと GPIO ピンの両方として使用しないことをお勧めします。

#### 6.2.1 外部ソース (LSE バイパス)

このモードでは、外部クロックソースが必要です。最大 1 MHz までの周波数を使用できます。約 50% のデューティサイクルの外部デジタル (VIL/VIH) またはアナログ (最小振幅 200 mV pk-pk) クロック信号によって OSC32\_IN ピンを駆動する必要があります、OSC32\_OUT ピンはハイインピーダンスに保つ必要があります (図 12 を参照)。バイパスモードの設定およびデジタルとアナログの選択は、RCC レジスタ内で行われます。

#### 6.2.2 外部クリスタル/セラミック発振子 (LSE クリスタル)

LSE クリスタルは、32.768 kHz のロースピード外部クリスタルまたはセラミック発振子です。時計／カレンダ、その他のタイミング機能のためのリアルタイムクロックペリフェラル (RTC) に、低消費電力ながら高精度のクロックソースを供給できるという利点があります。

波形ひずみと発振開始時の安定化までの時間を少なくするために、発振子と負荷コンデンサはオシレータのピンのできるだけ近くに接続する必要があります。負荷コンデンサの値  $C_{L1}$  と  $C_{L2}$  は、選択したオシレータに応じて調整する必要があります。

詳細については、ST マイクロコントローラ用発振器設計ガイド 専用アプリケーションノート (AN2867) および製品データシートの電気特性のセクションを参照してください。

## 6.3 クロックセキュリティシステム (CSS)

詳細は製品のリファレンスマニュアルをご覧ください（表 1 : [参照文献](#) を参照）。

### 6.3.1 HSE の CSS

クロックセキュリティシステムはソフトウェアで有効にできます。この場合、HSE オシレータのスタートアップ遅延時間の後にクロック検出回路が有効になり、オシレータが停止すると検出回路も無効になります。

- HSE オシレータクロックで障害が検出されると、システムリセットが生成されると共に、セキュリティ保護のために TAMP ブロックに通知されます。

### 6.3.2 LSE の CSS

クロックセキュリティシステムはソフトウェアで有効にできます。この場合、LSE オシレータのスタートアップ遅延時間の後にクロック検出回路が有効になり、オシレータが停止すると検出回路も無効になります。

- LSE オシレータクロックで障害が検出されると、RTC/TAMP クロックソースは停止すると共に、セキュリティ保護のために TAMP ブロックに通知されます。

## 7 ブート設定

### 7.1 ブート・モード選択

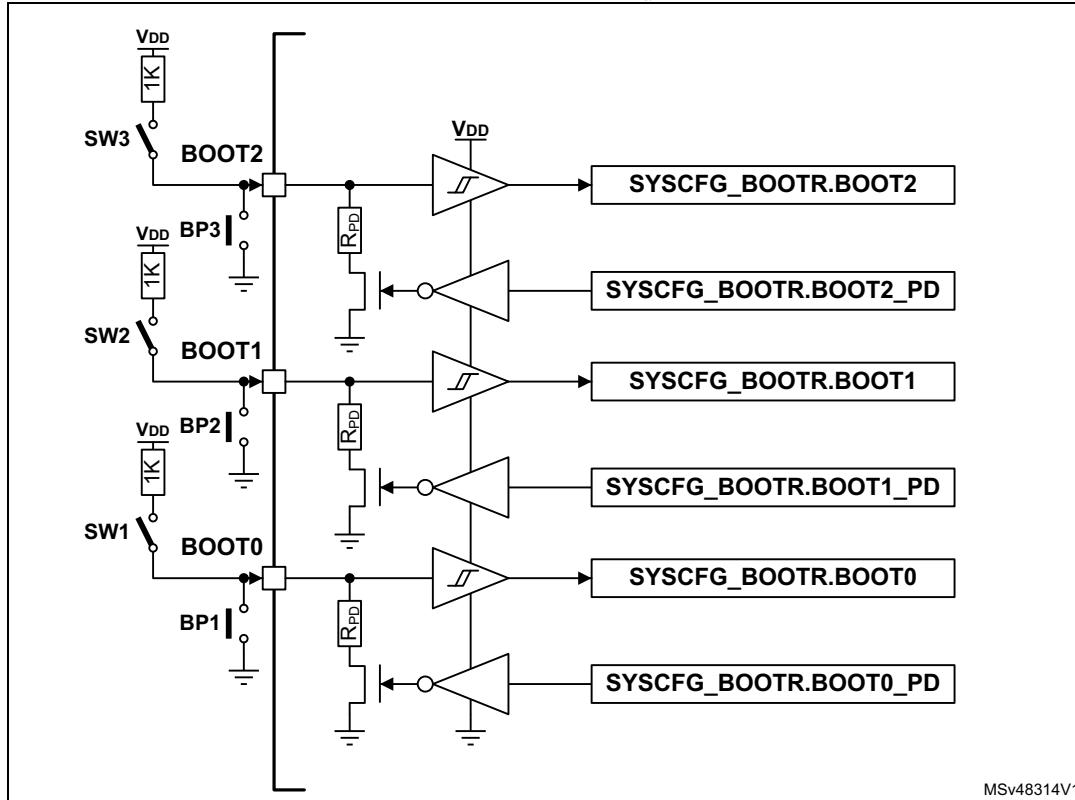

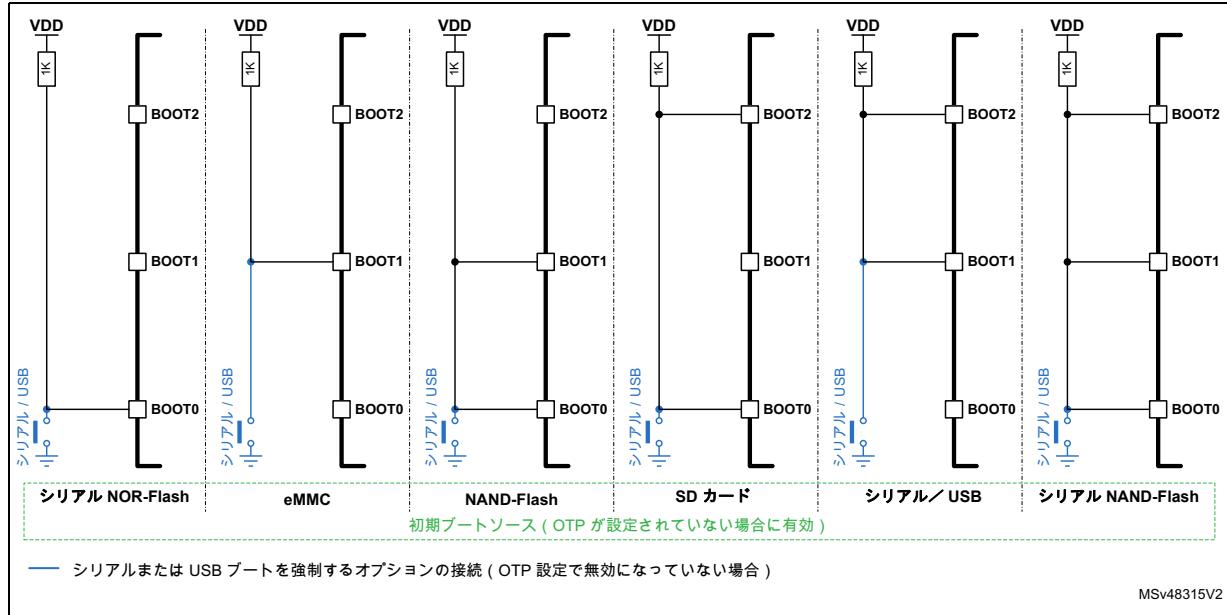

STM32MP15x ラインデバイスでは、BOOT[2:0] ピンによってさまざまなブートモードを選択できます。表では予約済みの設定がグレー表示されています。

表 12. ブートモード

| BOOT2 | BOOT1 | BOOT0 | 初期ブートモード                       | コメント                                                                                                         |

|-------|-------|-------|--------------------------------|--------------------------------------------------------------------------------------------------------------|

| 0     | 0     | 0     | UART および USB <sup>(1)</sup>    | 下記からの着信待ち：<br>– デフォルトピン上の USART2/3/6 および UART4/5/7/8<br>– OTG_HS_DP/DM ピン上の USB ハイスピードデバイス <sup>(2)</sup>    |

| 0     | 0     | 1     | シリアル NOR-Flash <sup>(3)</sup>  | QUADSPI 上のシリアル NOR-Flash <sup>(5)</sup>                                                                      |

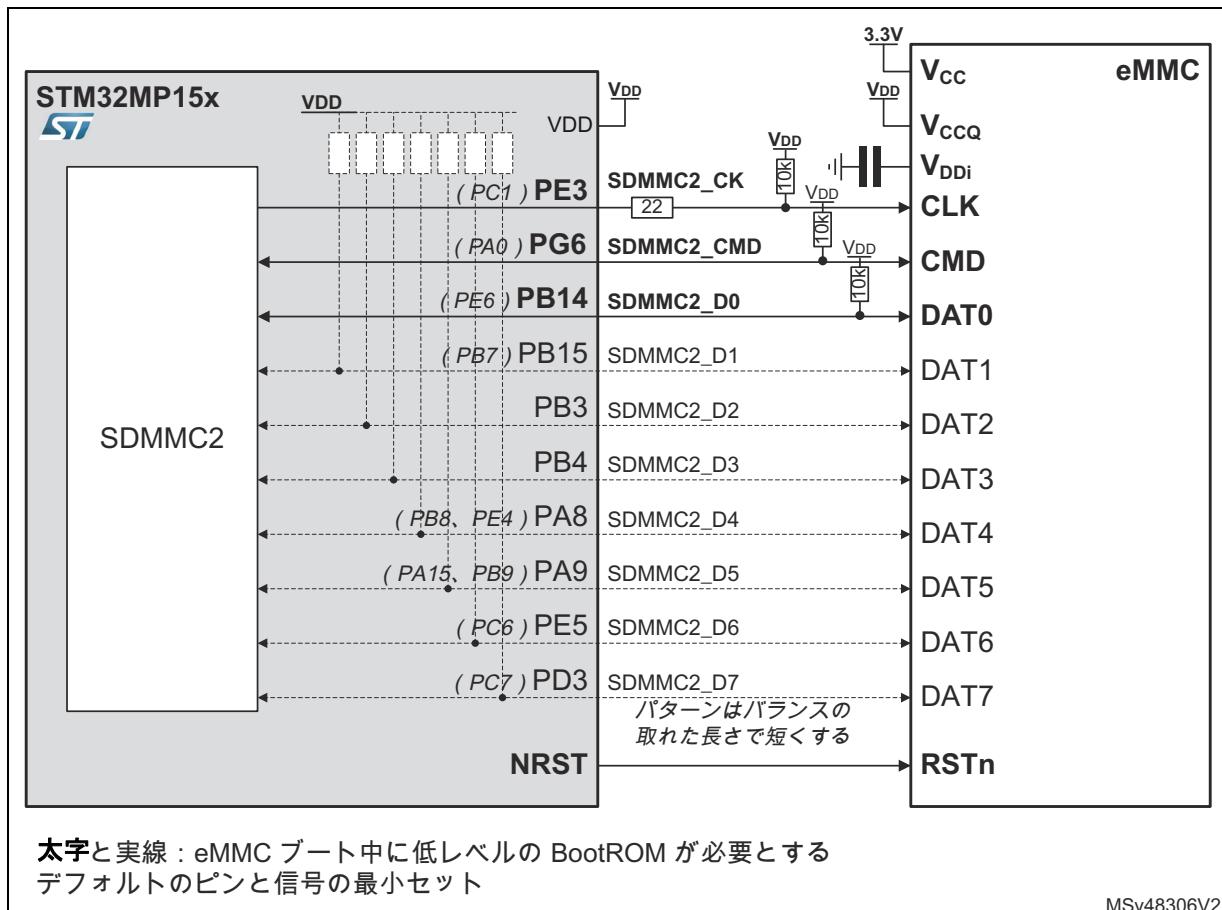

| 0     | 1     | 0     | eMMC™ <sup>(3)</sup>           | SDMMC2 上の eMMC™（デフォルト） <sup>(5)(6)</sup>                                                                     |

| 0     | 1     | 1     | NAND-Flash <sup>(3)</sup>      | FMC 上の SLC NAND-Flash                                                                                        |

| 1     | 0     | 0     | 予約済みです。                        | Flash からのブートなしにデバッグアクセスするために使用される <sup>(4)</sup>                                                             |

| 1     | 0     | 1     | SD カード <sup>(3)</sup>          | SDMMC1 上の SD カード（デフォルト） <sup>(5)(6)</sup>                                                                    |

| 1     | 1     | 0     | UART および USB <sup>(1)(3)</sup> | 下記からの着信接続を待機：<br>– デフォルトピン上の USART2/3/6 および UART4/5/7/8<br>– OTG_HS_DP/DM ピン上の USB ハイスピードデバイス <sup>(2)</sup> |

| 1     | 1     | 1     | シリアル NAND-Flash <sup>(3)</sup> | QUADSPI 上のシリアル NAND-Flash <sup>(5)</sup>                                                                     |

1. OTP 設定で無効にできます。

2. OTP で異なる周波数にプログラムされていなければ、USB には 24 MHz HSE クロック／クリスタルが必要です（セクション 7.3：内蔵ブート・ローダ・モード を参照）。

3. ブートソースは、OTP 設定によって変更できます（OTP 設定によって、SD カードで初期ブート、次に eMMC など）。

4. PA13 をトグルする無限ループ状態の Cortex-A7 Core0、RETRAM での無限ループ状態の Cortex-M4。

5. デフォルトピンは OTP で変更できます。

6. あるいは、このデフォルト以外の別の SDMMC インタフェースを OTP で選択できます。

BOOT ピンの値は、リセット後に BootROM によってサンプリングされます。リセットが終了する前に BOOT[2:0] ピンを設定して必要なブートモードを選択出来ます。

BOOT ピンは、STANDBY モードを終了するときに、ソフトウェアによって（SYSCFG\_BOOTR\_BOOT[2:0] フィールドを読み取るなど）または BootROM によって後で再サンプリングすることもできます。したがって、これらのピンは常に必要なブートモード設定にする必要があります。

STOP モード中、BOOT[2:0] ピンが V<sub>DD</sub> に接続されている場合、3 つの内蔵プルダウンがデフォルトで有効になっているため、プルダウンを介して電流が流れています。

数十μA の電力を節約するために、ソフトウェアによって、フィールド SYSCFG\_BOOTR\_BOOT[2:0]\_PD を SYSCFG\_BOOTR\_BOOT[2:0] フィールドで読み取られた値に等しく設定する事で、V<sub>DD</sub> に接続されているピンのプルダウンを無効にすることができます。STANDBY 時に SYSCFG\_BOOTR レジスタがリセットされたため、各 STANDBY の終了後にこれを再度設定する必要があります。STANDBY 時には、BOOT[2:0] ピンがトライステートに設定され、V<sub>DD</sub> に接続されていても、BOOT[2:0] ピンには電流が流れていませんことに注意してください。

## 7.2 BOOT ピンの接続

図 14 には、STM32MP15x ラインデバイスのブートメモリを選択するため必要な外部接続の例を示します。

図 14. BOOT モード選択の例

ソフトウェアのすべてのリカバリケースにもかかわらず、間違ったまたは破損した Flash コンテンツ（ユーザのミス、間違ってプログラムされた Flash コンテンツ、電源喪失など）があると、システムが起動しなくなる（「ブリック」とも呼ばれる）可能性があります。

空の Flash の場合、ブートコードでは自動的に UART/USB 接続に切り替えられます。

ボードの Flash を再プログラミングできるようにするために、UART/USB 接続の使用を強制する方法が必要になる場合があります（例：アフターサービス、ファームウェアの更新）。

通常のブートとは異なる Flash で初期ブートを行う場合もあります（たとえば、シリアル NOR、シリアル NAND、eMMC、SLC NAND などの別の Flash にバイナリデータをコピーする SD カードからの初期ブート）。初期ブートコードによって、その後はプログラムされた Flash からのブートを強制するように関連する OTP ビットを設定することができるので、これが可能になります（図 16 を参照）。これにより、BOOT ピンの設定作業が不要で、単純かつ柔軟性の高い大量生産が可能になります。

ボードの一般的な接続例を図 15 に示します。

「スイッチ」は、押しボタン、はんだブリッジ、コネクタ接点、テストポイントなど、さまざまな方法で実現できますが、通常の製品のブート中は、外部抵抗に電流が流れないように、デフォルトで「オープン」と想定されています。

製品のセキュリティ要件を満たすために、OTP 設定においてブートソースのいずれかを強制または禁止することがあることに注意してください。

# 参考資料

図 15. BOOT ピンの一般的な接続図

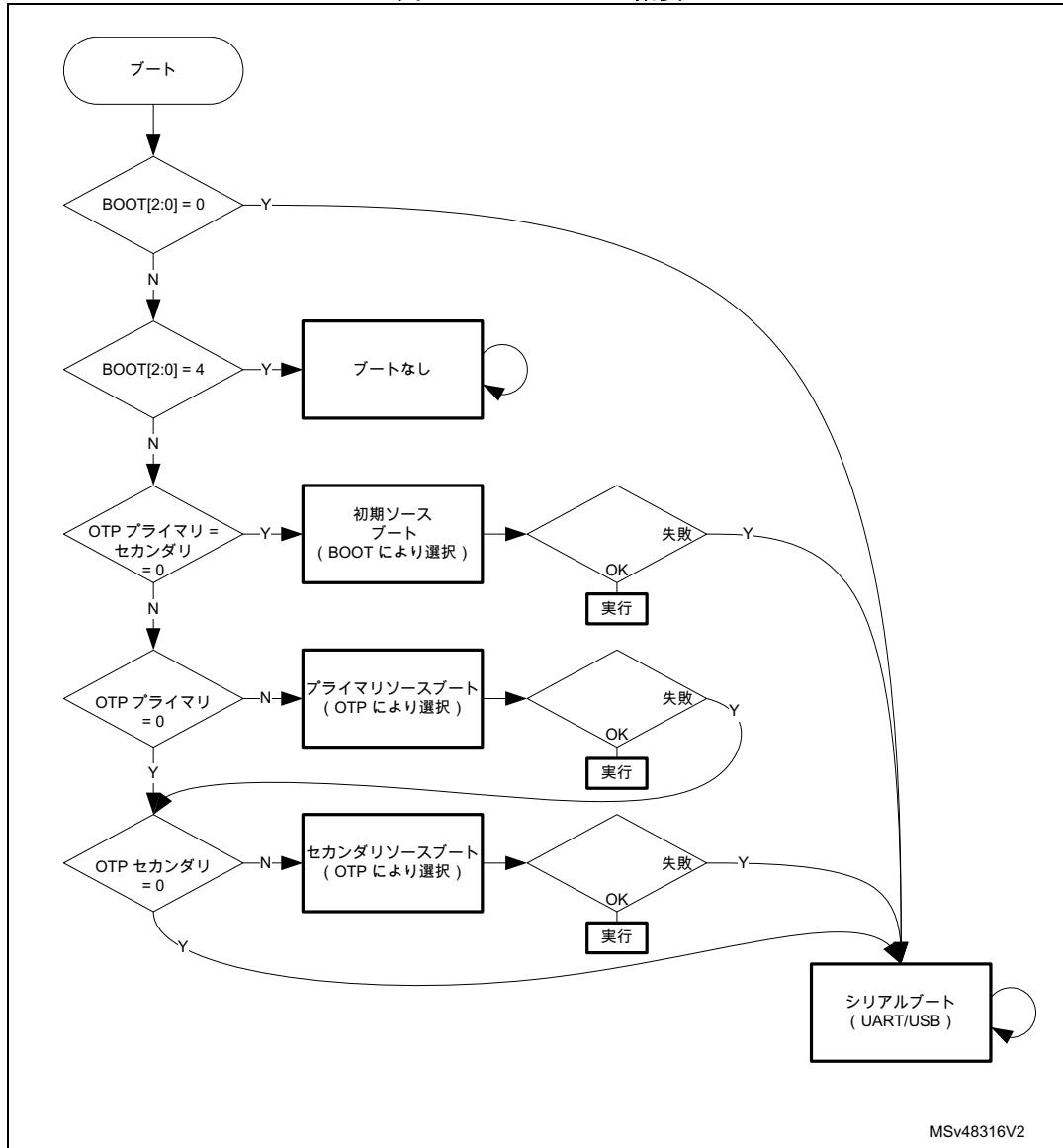

## 7.3 内蔵ブート・ローダ・モード

この内蔵ブートローダは BootROM メモリ内にあります。

詳しい情報は、USB DFU/USART protocols used in STM32MP1 Series bootloaders (AN5275) (表 1) を参照してください。

ブート中、QUADSPI、FMC、SDMMC、および USART ペリフェラルは内部 64 MHz オシレータ (HSI) で動作します。

ただし、USB OTG HS デバイスは、デフォルト周波数 24 MHz の外部クロック (HSE) が存在する場合にのみ機能します（デフォルト周波数の代わりに、8、10、12、14、16、20、24、25、26、28、32、36、40、48 MHz も、OTP 設定や自動周波数検出によって使用できます）。

図 16. ブートフロー概要

## 8 デバッグ管理

### 8.1 概要

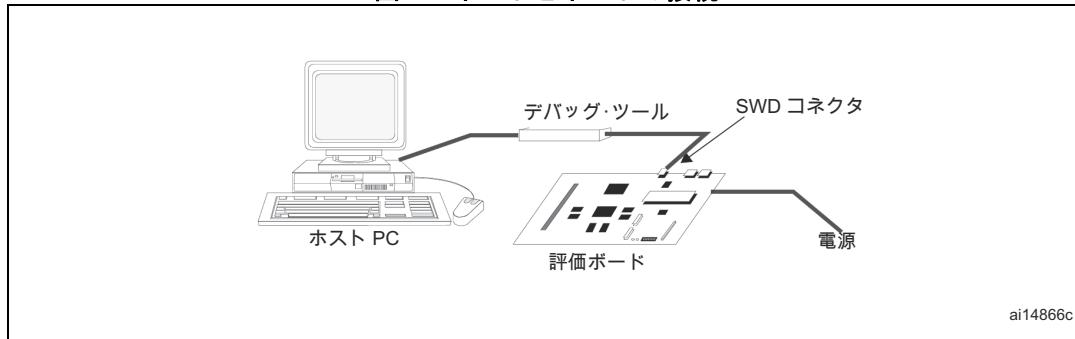

ホスト／ターゲット・インターフェースは、ホストをアプリケーションボードに接続するハードウェア機器です。このインターフェースは、ハードウェアデバッグツール、JTAG または SWD コネクタ、およびホストをデバッグツールに接続するケーブルの 3 つのコンポーネントで構成されています。

図 17 は、ホストと評価ボードの接続を示しています。

図 17. ホストとボードの接続

### 8.2 SWJ デバッグポート（シリアルワイヤと JTAG）

STM32MP15x ラインのコアには、シリアルワイヤ／JTAG デバッグポート (SWJ-DP) が組み込まれています。これは、JTAG-DP (5 ピン) インタフェースと SW-DP (2 ピン) インタフェースを組み合わせた Arm® の標準の CoreSight™ デバッグポートです。

- JTAG デバッグ・ポート (JTAG-DP) は、AHP-AP ポートに 5 ピンの標準 JTAG インタフェースを提供します。

- シリアルワイヤデバッグポート (SW-DP) は、AHB-AP ポートに 2 ピン (クロック + データ) のインターフェースを提供します。

SW-DP の 2 個のピンは、JTAG-DP の 5 個の JTAG ピンのうち 2 個と共に用されています。

### 8.3 ピン名とデバッグポートピン

#### 8.3.1 JTAG ピンでの内部プルアップ/プルダウン抵抗

入出力レベルを正しく制御するため、STM32MP15x ラインには内部プルアップ／プルダウン抵抗が JTAG ピンに内蔵されています。

- NJTRST : 内部プルアップ

- JTDI : 内部プルアップ

- JTDO-TRACESWO : 内部プルアップ

- JTMS-SWDIO : 内部プルアップ

- JTCK-SWCLK : 内部プルダウン

注： IEEE 規格では、 JTAG の TDI 、 TMS 、および nTRST にプルアップ抵抗を追加することを推奨していますが、 TCK に関しては特別な推奨はありません。ただし、 STM32MP15x ラインの場合は、 JTCK に内蔵プルダウン抵抗が使用されます。

プルアップおよびプルダウン抵抗を内蔵しているため、外部抵抗を追加する必要がありません。

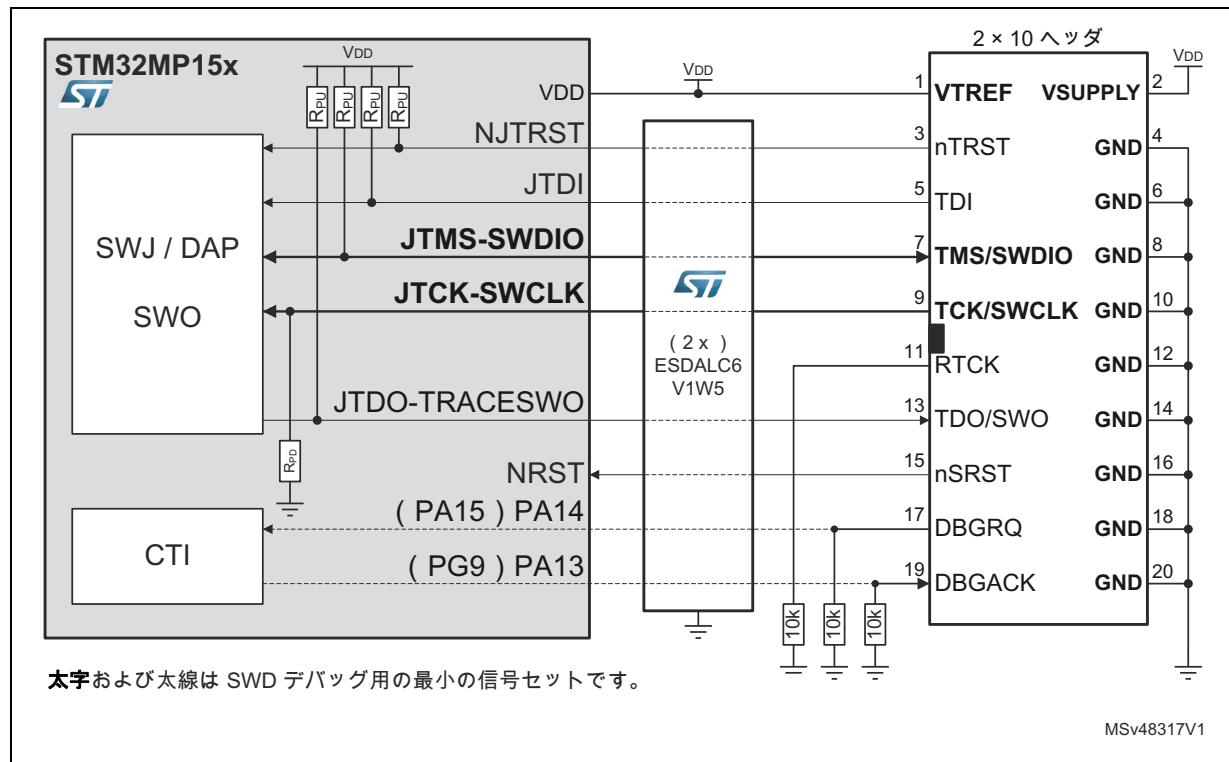

## 8.3.2 デバッグポートと標準 JTAG コネクタの接続

図 18 は、 STM32MP15x ラインと標準 JTAG/SWD コネクタとの接続を示しています。

図 18. JTAG/SWD MIPI10 コネクタ接続例

注： TRACESWO ピンでのシングルワイヤトレースは Cortex-M4 コアでのみ使用できます。すべてのコアの動作をトレースするためには、パラレルトレースポートを使う必要があります（[セクション 8.3.4 : パラレルトレースと HDP を参照](#)）。

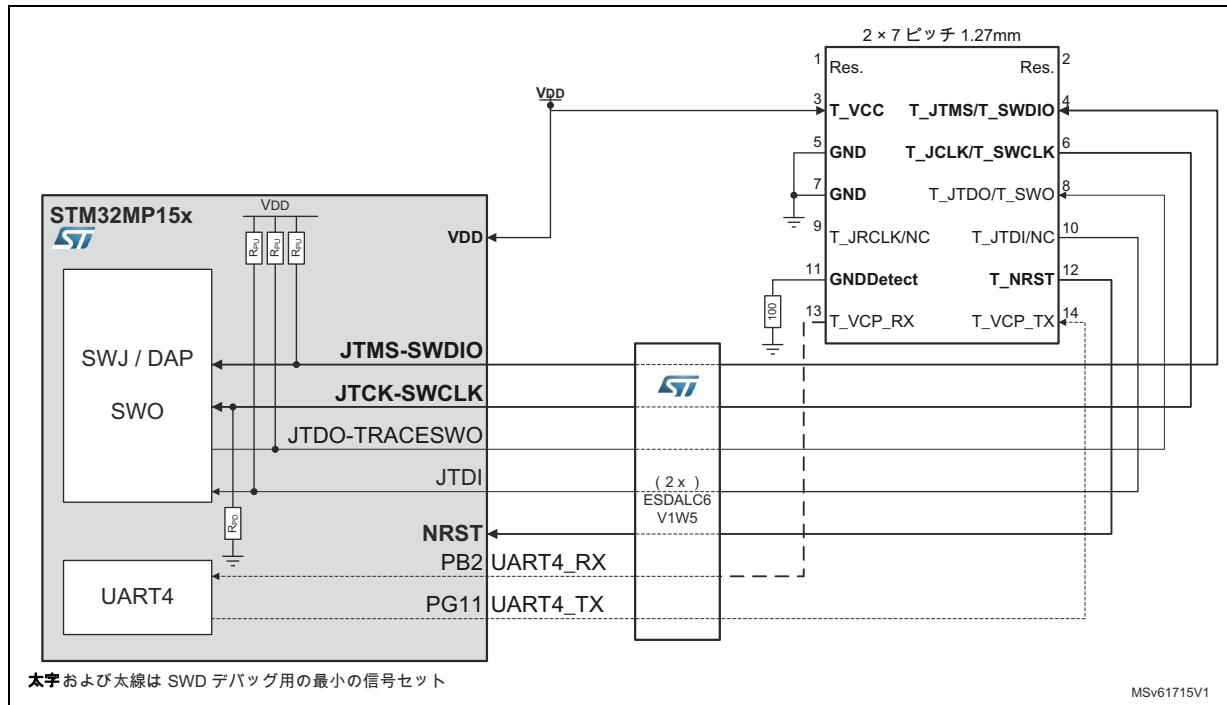

### 8.3.3 STDC14 コネクタへのデバッグポートと UART の接続

図 19 は、STM32MP15x ラインと STDC14 コネクタとの接続、および UART 仮想 COM ポートの接続を示しています。

STDC14 ヘッダの参照例は FTSH-107-01-L-DV-K-A です。

図 19. JTAG/SWD/UART VCP STDC14 コネクタ接続例

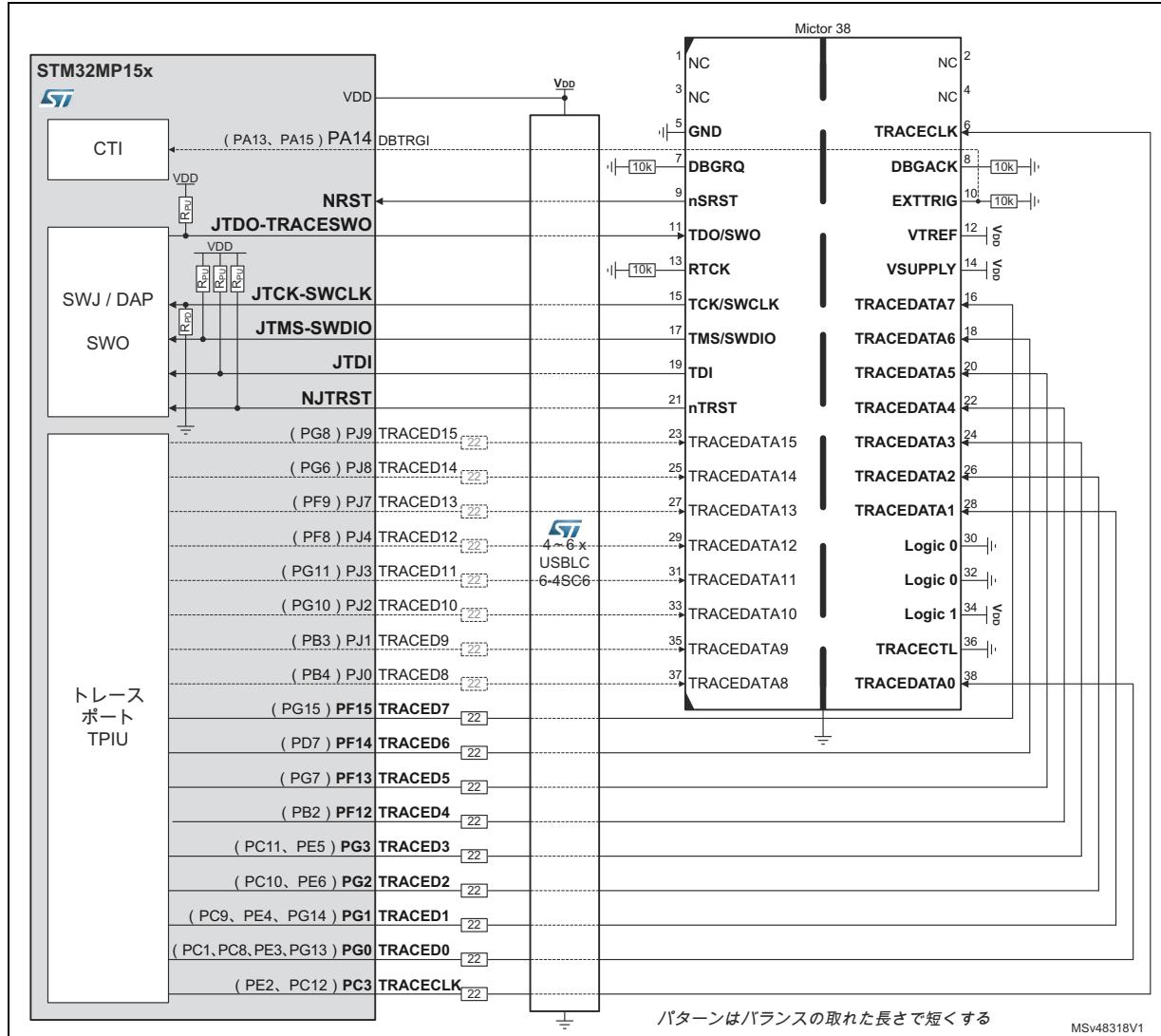

## 8.3.4 パラレルトレースと HDP

### パラレルトレース

TRACED[15:0] および TRACECLK 信号は IO ピンでオルタネート機能として使用できます。トレースデータの数  $N = 1, 2, 4, 8$ 、または 16 ピンを選択できます。トレースデータの数が少ないと、利用可能なトレース帯域幅が少なくなるため、トレースのオーバーランなしでトレースできる情報（トレースソースの数、コードやデータトレースなど）が少なくなります（STM32MP15x ラインには 8 KB のバッファがあります）。製品ごとに、使用可能な機能とトレースバスの間にトレードオフがあるため、製品開発中にトレースを使用しているときに機能が制限される可能性があります。

トレースは Arm® CoreSight™ トレースに準拠しており、SWD または JTAG を介しデバッグするためには、専用のトレースツールが必要です。

トレースポートインターフェース CoreSight™ コンポーネントの詳細情報は、製品のリファレンスマニュアルと Arm® CoreSight™ SoC-400 Technical Reference Manual を参照してください。

トレース帯域幅を効率的に利用するには、すべてのパラレルトレース信号のシグナルインテグリティを良好に維持しながら、TRACECLK をできるだけ高速に実行する必要があります。これは、ボードとコネクタの選択、GPIO の能力設定 (GPIO\_OSPEEDR レジスタ)、および  $V_{DD}$  電圧に依存します。 $V_{DD} = 1.8\text{ V}$  を使用する場合、トレース信号で使用されるパッドで最高の速度を確保するには、OTP ビットとレジスタ SYSCFG\_ICTRLSETR (HSLVEN\_TRACE ビット) の設定が必要になることがあります。

---

**警告 :**  $V_{DD}$  が 2.7 V を超える場合、UHSLVEN および HSLVEN は設定しないでください。IC が損傷する可能性があります。

---

# 参考資料

図 20. パラレルトレースポート付き JTAG/SWD の Mictor38 接続例

## ハードウェアデバッグポート

一部の内部信号は、詳細なデバッグに使用できます。使用時には専門知識とオシロスコープまたはロジックアナライザが必要です。詳細については、製品のリファレンスマニュアルおよびデータシートを参照してください。

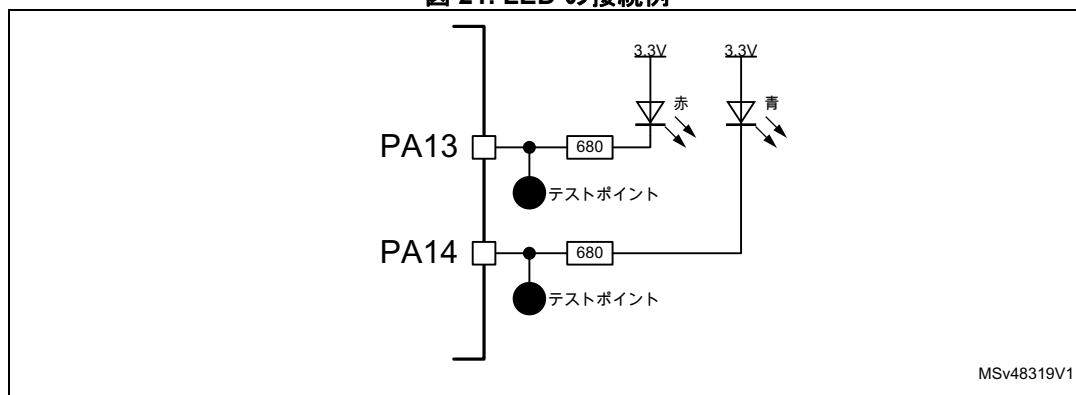

## 8.3.5 デバッグトリガとLED

CoreSight™ クロストリガインターフェース (CTI) はピン上で DBTRGI および DBTRGO として使用できます。

DBTRGI は外部ユーザ信号によって生成でき、CoreSight™ コンポーネント内でプログラムして、トレースを開始／停止したり、デバッグモード（ブレーク）で特定のコアに入ることができます。

DBTRGO は CTI によって生成され、これにより CoreSight™ コンポーネントの 1 つによってトリガ条件に達したことが外部から確認できます（コアブレーク、トレース開始など）。

DBTRGO は、PA13、PA14、または PG9 で使用可能です。

DBTRGI は、PA13、PA14、または PA15 で使用可能です。

PA13 固有の動作（詳細はブートの文書を参照）：

- ブートフェーズ中、ブートが失敗した場合、PA13 ピンはロー・オーブンドレインに設定されます（すなわち、エラー LED が明るく点灯します）。

- UART/USB ブート中、PA13 ピンは、接続が開始されるまで、約 5 Hz の速度でオーブンドレインを切り替えます（すなわち、エラー LED が速く点滅します）。

- BOOT[2:0] = 0b100（ブートなし、特定のデバッグに使用）の場合、PA13 は約 5 kHz の速度でオーブンドレインを切り替えます（すなわち、エラー LED が弱く点灯します）。

- それ以外の場合はすべて、PA13 はリセット値、すなわち、ソフトウェアで設定されるまでハイインピーダンスに保たれます。

図 21 に示すように、PA13 に赤色 LED を接続することをお勧めします。

システムの動作を視覚的にすばやく確認するために、PA13 と PA14 に LED を接続することをお勧めします。これは、デバッグのために PA13 または PA14 で DBTRGI および DBTRGO を使用することを妨げるものではありません（デバッグ中にはソフトウェアは LED の制御を停止すると想定）。

図 21. LED の接続例

## 9 推奨事項

### 9.1 プリント回路基板

技術的な理由により、グランド ( $V_{SS}$ ) 専用の個別の層と、 $V_{DD}$  や  $V_{DDCORE}$  などの電源専用の別の層を持つ多層プリント回路基板 (PCB) を使用することが必須です。これにより、デカッピングとシールド効果が向上します。

### 9.2 コンポーネントの位置

PCB の暫定レイアウトでは、PCB 上のクロスカッピングを削減するために、EMI の影響に応じてさまざまな回路、すなわちノイズの多い高電流回路、低電圧回路、およびデジタルコンポーネントを分離する必要があります。

### 9.3 グランドおよび電源 ( $V_{SSx}$ 、 $V_{DDx}$ )

STM32MP15x ライン には大きな電力と高周波が含まれるため、 $V_{SSx}$  および  $V_{DDx}$  専用の電源プレーンを備えた少なくとも 4 層の PCB を使用することが必須です。

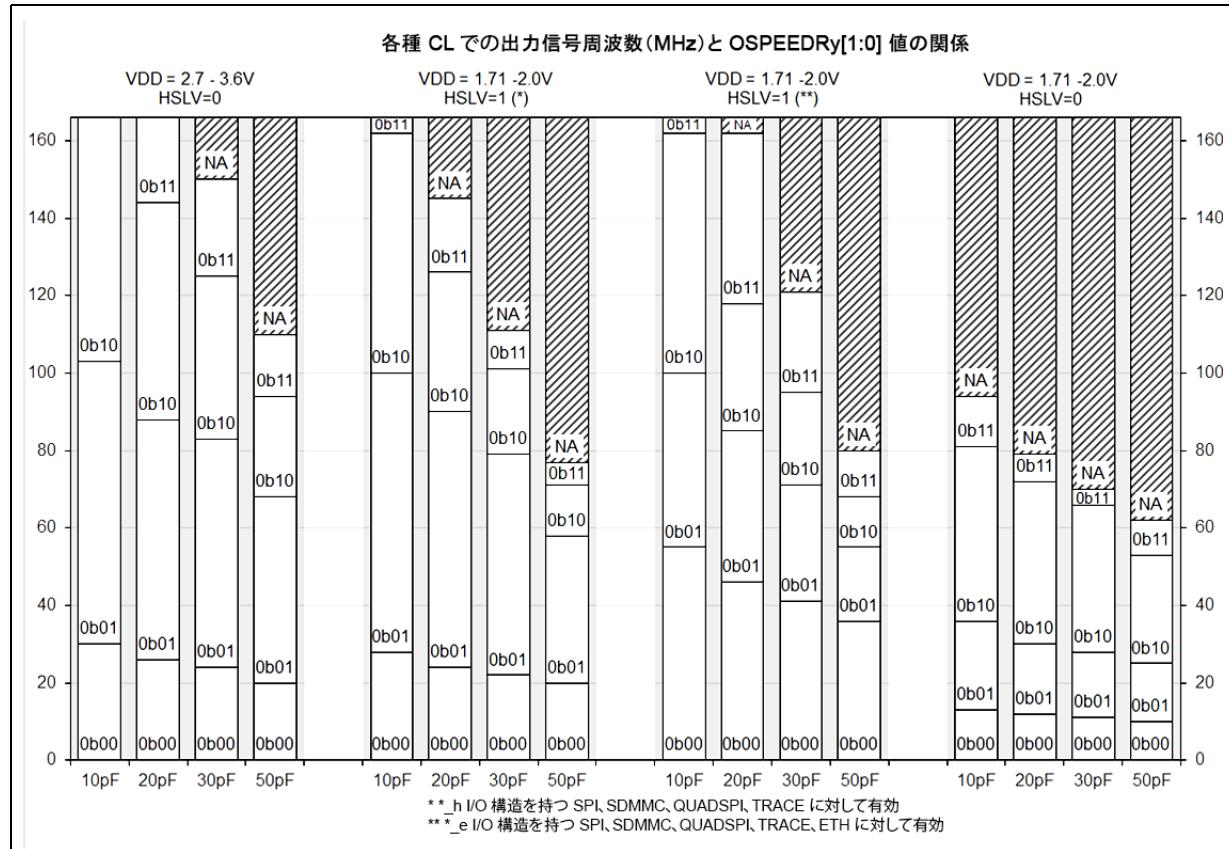

### 9.4 IO 速度の設定

十分な立ち上がり時間と立ち下がり時間を確保するために、IO に適切な出力駆動を設定することが重要ですが、リングやノイズの増加を避けることも重要です。

IO 速度に特に具体的な要件がなければ、OSPEEDR に 0 を設定することが必須です。

次の図と表を使用して、信号の周波数と容量性負荷に応じて適用する適切な設定をすばやく選択できます。シグナルインテグリティの問題が発生した場合は、この設定を調整する必要があります。

ほとんどの場合、IO 補正を SYSCFG で有効にする必要があります。詳細については、製品データシートを参照してください。

注： 非同期またはシングルエッジクロックのデータレーン (SDR など) の場合、最速のデータ周波数のトグルは事実上データレートの半分です。たとえば、10 M ビット／秒で動作する SPI の最大周波数は、データ信号 (たとえば、出力シリアルデータ 01010101 ...) では 5 MHz ですが、クロック信号では 10 MHz です。デュアルエッジクロックのデータレーン (DDR など) の場合、クロックとデータの最大トグル周波数は同じです。

注： OTP ビット PRODUCT\_BELOW\_2V5 = 0 (デフォルト状態) の場合、HSLVEN\_xxx ビットは考慮されません。

注：  $VDD > 2.7 \text{ V}$  のときに HSLVEN\_xxx=1 および product\_below\_2V5=1 を設定すると、IC が損傷する可能性があります。

# 参考資料

図 22. 負荷容量と電圧別 IO 速度概要

表 13. VDD = 標準 3.3 V での OSPEEDR 設定例

| ペリフェラル                     | 信号     | トグルレート (MHz) | OSPEEDR CL=30 pF |                       | OSPEEDR CL=10 pF |           |

|----------------------------|--------|--------------|------------------|-----------------------|------------------|-----------|

|                            |        |              | 1                | ミディアムスピード             | 1                | ミディアムスピード |

| FMC 非同期                    | データ／制御 | 50           | 1                | ミディアムスピード             | 1                | ミディアムスピード |

| FMC 同期                     | CLK    | 100          | 2                | ハイスピード                | 1                | ミディアムスピード |

|                            | データ／制御 | 50           | 1                | ミディアムスピード             | 1                | ミディアムスピード |

| QUADSPI (SDR)              | CLK    | 133          | 2                | ハイスピード <sup>(1)</sup> | 2                | ハイスピード    |

|                            | データ／制御 | 66.5         | 1                | ミディアムスピード             | 1                | ミディアムスピード |

| QUADSPI (DDR)              | すべて    | 66.5         | 1                | ミディアムスピード             | 1                | ミディアムスピード |

| LTDC (HDMI) <sup>(2)</sup> | CLK    | 74.25        | 1                | ミディアムスピード             | 1                | ミディアムスピード |

|                            | データ／制御 | 37.125       | 1                | ミディアムスピード             | 1                | ミディアムスピード |

| LTDC <sup>(2)</sup>        | CLK    | 90           | 2                | ハイスピード                | 1                | ミディアムスピード |

|                            | データ／制御 | 45           | 1                | ミディアムスピード             | 1                | ミディアムスピード |

| LTDC                       | CLK    | 48           | 1                | ミディアムスピード             | 1                | ミディアムスピード |

|                            | データ／制御 | 24           | 0                | ロースピード                | 0                | ロースピード    |

| TIM/LPTIM                  | すべて    | 5            | 0                | ロースピード                | 0                | ロースピード    |

| I2C                        | すべて    | 1            | 0                | ロースピード                | 0                | ロースピード    |

# 参考資料

表 13. VDD = 標準 3.3 V での OSPEEDR 設定例（続き）

| ペリフェラル      | 信号     | トグルレート<br>(MHz) | OSPEEDR CL=30 pF        | OSPEEDR CL=10 pF |

|-------------|--------|-----------------|-------------------------|------------------|

| USART       | すべて    | 5               | 0 ロースピード                | 0 ロースピード         |

| SPI         | CLK    | 50              | 1 ミディアムスピード             | 1 ミディアムスピード      |

|             | データ／制御 | 25              | 1 ミディアムスピード             | 0 ロースピード         |

| SAI         | MCLK   | 15              | 0 ロースピード                | 0 ロースピード         |

|             | CLK    | 1               | 0 ロースピード                | 0 ロースピード         |

|             | データ／制御 | 0.5             | 0 ロースピード                | 0 ロースピード         |

| MDIOS       | すべて    | 5               | 0 ロースピード                | 0 ロースピード         |

| SDMMC (SDR) | CLK    | 133             | 2 ハイスピード <sup>(1)</sup> | 2 ハイスピード         |

|             | データ／制御 | 66.5            | 1 ミディアムスピード             | 1 ミディアムスピード      |

| SDMMC (DDR) | すべて    | 52              | 1 ミディアムスピード             | 1 ミディアムスピード      |

| FDCAN       | すべて    | 5               | 0 ロースピード                | 0 ロースピード         |

| ETH (MII)   | CLK    | 50              | 1 ミディアムスピード             | 1 ミディアムスピード      |

|             | データ／制御 | 25              | 1 ミディアムスピード             | 0 ロースピード         |

| ETH (RMII)  | すべて    | 50              | 1 ミディアムスピード             | 1 ミディアムスピード      |

| ETH (GMII)  | CLK    | 125             | 2 ハイスピード                | 2 ハイスピード         |

|             | データ／制御 | 62.5            | 1 ミディアムスピード             | 1 ミディアムスピード      |

| ETH (RGMII) | すべて    | 125             | 2 ハイスピード                | 2 ハイスピード         |

| ETH (MDIO)  | MDIO   | 2.5             | 0 ロースピード                | 0 ロースピード         |

| TRACE       | すべて    | 133             | 3 超ハイスピード               | 2 ハイスピード         |

|             |        | 100             | 2 ハイスピード                | 1 ミディアムスピード      |

1. CL=20 pF に対する値

2. HSE 用の外部オシレータが必要

表 14. VDD = 標準 1.8 V での OSPEEDR 設定例<sup>(1)</sup>

| ペリフェラル                       | 信号     | トグルレート<br>(MHz) | OSPEEDR CL=30 pF         | OSPEEDR CL=10 pF |

|------------------------------|--------|-----------------|--------------------------|------------------|

| FMC 非同期                      | データ／制御 | 50              | 2 ハイスピード                 | 2 ハイスピード         |

| FMC 同期                       | CLK    | 69              | 3 超ハイスピード                | 3 超ハイスピード        |

|                              | データ／制御 | 34.5            | 2 ハイスピード                 | 1 ミディアムスピード      |

| QUADSPI (SDR) <sup>(2)</sup> | CLK    | 133             | 3 超ハイスピード <sup>(3)</sup> | 2 ハイスピード         |

|                              | データ／制御 | 66.5            | 1 ミディアムスピード              | 1 ミディアムスピード      |

| QUADSPI (DDR) <sup>(2)</sup> | すべて    | 66.5            | 1 ミディアムスピード              | 1 ミディアムスピード      |

| LTDC (HDMI)                  | CLK    | 74.25           | 3 超ハイスピード <sup>(3)</sup> | 3 超ハイスピード        |

|                              | データ／制御 | 37.125          | 2 ハイスピード                 | 2 ハイスピード         |

| LTDC                         | CLK    | 69              | 3 超ハイスピード                | 3 超ハイスピード        |

|                              | データ／制御 | 34.5            | 2 ハイスピード                 | 1 ミディアムスピード      |

| TIM/LPTIM                    | すべて    | 5               | 0 ロースピード                 | 0 ロースピード         |

| I2C                          | すべて    | 1               | 0 ロースピード                 | 0 ロースピード         |

# 参考資料

AN5031

推奨事項

表 14. VDD = 標準 1.8 V での OSPEEDR 設定例<sup>(1)</sup> (続き)

| ペリフェラル                     | 信号     | トグルレート<br>(MHz) | OSPEEDR CL=30 pF         | OSPEEDR CL=10 pF |

|----------------------------|--------|-----------------|--------------------------|------------------|

| USART                      | すべて    | 5               | 0 ロースピード                 | 0 ロースピード         |

| SPI <sup>(4)</sup>         | CLK    | 50              | 1 ミディアムスピード              | 1 ミディアムスピード      |

|                            | データ／制御 | 25              | 1 ミディアムスピード              | 0 ロースピード         |

| SAI                        | MCLK   | 15              | 1 ミディアムスピード              | 1 ミディアムスピード      |

|                            | CLK    | 1               | 0 ロースピード                 | 0 ロースピード         |

|                            | データ／制御 | 0.5             | 0 ロースピード                 | 0 ロースピード         |

| MDIOS                      | すべて    | 5               | 0 ロースピード                 | 0 ロースピード         |

| SDMMC (SDR) <sup>(5)</sup> | CLK    | 133             | 3 超ハイスピード <sup>(3)</sup> | 2 ハイスピード         |

|                            | データ／制御 | 66.5            | 1 ミディアムスピード              | 1 ミディアムスピード      |

| SDMMC (DDR) <sup>(5)</sup> | すべて    | 52              | 1 ミディアムスピード              | 1 ミディアムスピード      |

| FDCAN                      | すべて    | 5               | 0 ロースピード                 | 0 ロースピード         |

| ETH (MII) <sup>(6)</sup>   | CLK    | 50              | 1 ミディアムスピード              | 0 ロースピード         |

|                            | データ／制御 | 25              | 0 ロースピード                 | 0 ロースピード         |

| ETH (RMII) <sup>(6)</sup>  | すべて    | 50              | 1 ミディアムスピード              | 0 ロースピード         |

| ETH (GMII) <sup>(6)</sup>  | CLK    | 125             | 3 超ハイスピード <sup>(3)</sup> | 2 ハイスピード         |

|                            | データ／制御 | 62.5            | 1 ミディアムスピード              | 1 ミディアムスピード      |

| ETH (RGMII) <sup>(6)</sup> | すべて    | 125             | 3 超ハイスピード <sup>(3)</sup> | 2 ハイスピード         |

| ETH (MDIO)                 | MDIO   | 2.5             | 0 ロースピード                 | 0 ロースピード         |

| TRACE <sup>(7)</sup>       | すべて    | 133             | 3 超ハイスピード <sup>(3)</sup> | 2 ハイスピード         |

|                            |        | 100             | 2 ハイスピード                 | 1 ミディアムスピード      |

1. OTP ビット PRODUCT\_BELOW\_2V5 がセットされている場合のみ、HSLVEN\_xxx=1 は考慮されます。

2. HSLVEN\_QUADSPI=1

3. CL=20pF に対する値

4. HSLVEN\_SPI=1

5. HSLVEN\_SDMMC=1

6. HSLVEN\_ETH=1

7. HSLVEN\_TRACE=1

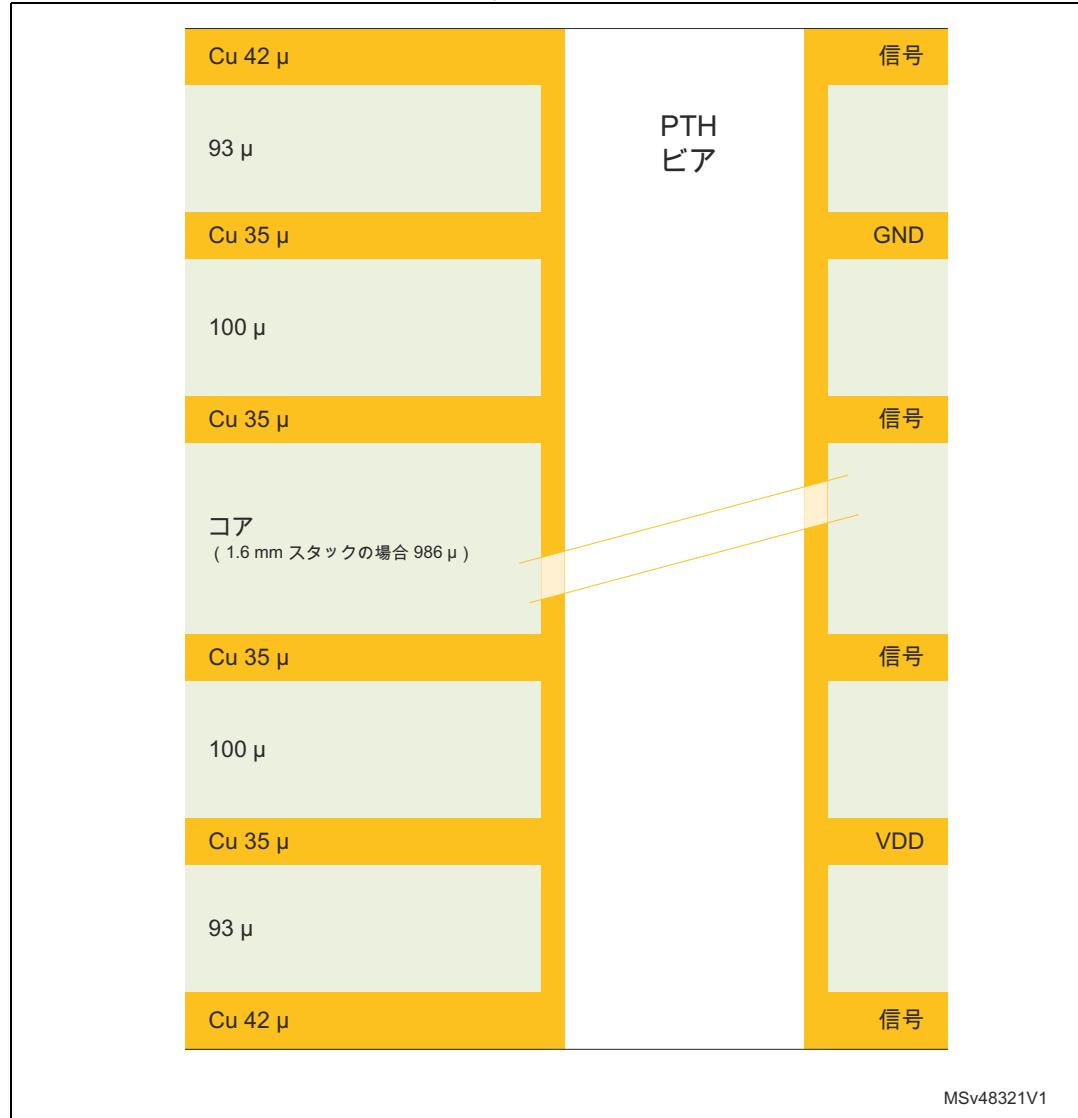

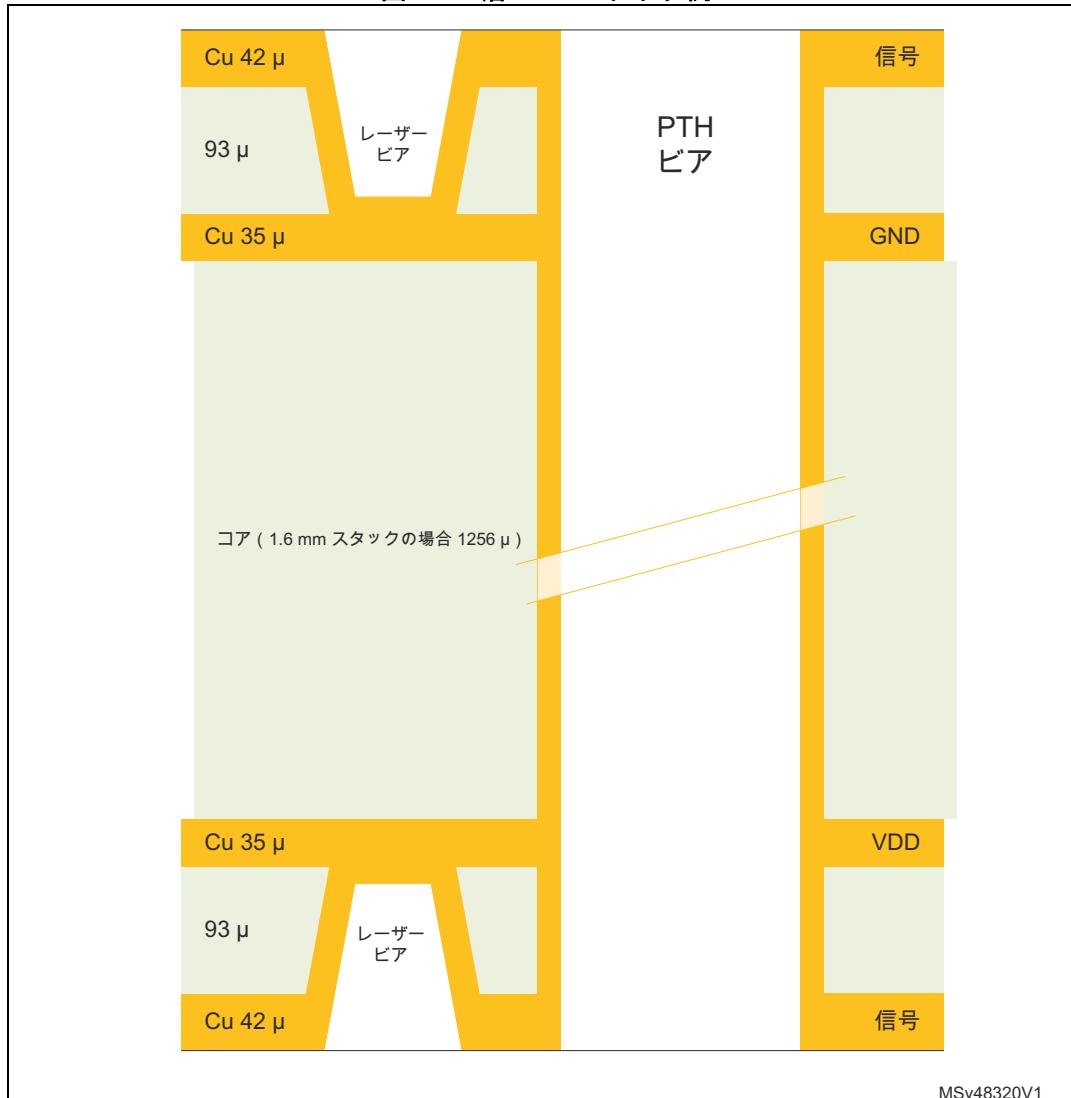

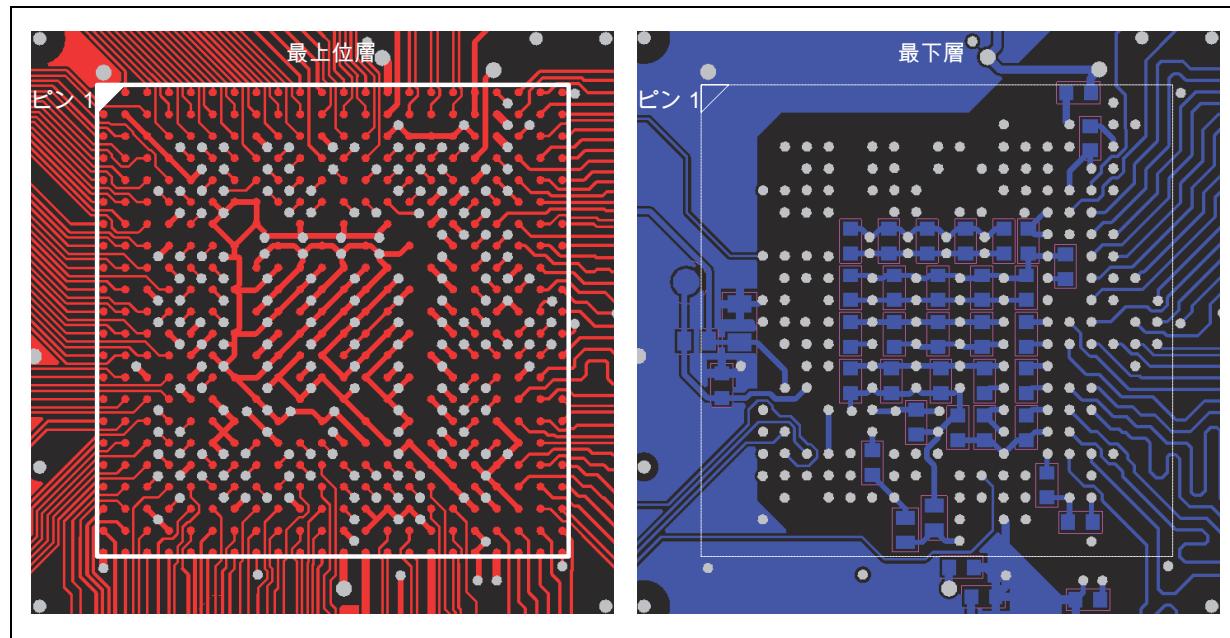

### 9.5 PCB スタックおよびテクノロジー

PCB のコストと電気接続の容易さの間のトレードオフを図る必要があります。以下の例は、PTH のみを備えた 4 層または 6 層 PCB (0.8 mm ピッチパッケージに適しています) または PTH とレーザー ドリルビアの両方を備えた 4 層 PCB (0.5 mm ピッチパッケージに適しています) のいずれかです。

外側のボールピッチが 0.5 mm の一部の STM32MP15x ライン パッケージでは、0.65 mm のピッチで電力が改善された中央ボールマトリックスが提供され、ボール間の大きな PTH ビアが可能になります。これにより、小さなベリッドレーザードリルビアよりも優れた電源接続と最適化された熱伝導率が保証されます。

図 23. 6 層 PCB スタック例

# 参考資料

AN5031

推奨事項

図 24. 4 層 PCB スタック例

MSv48320V1

# 参考資料

図 25. 0.8 mm ピッチパッケージ用 PCB ルール例

# 参考資料

AN5031

推奨事項

図 26. 0.5 mm ピッチパッケージ用 PCB ルール例

図 27. 電源供給用 0.65mm ピッチ内部ボール用 PCB ルール例

### 9.6 デカップリング

すべての電源ピンとグランドピンは、各電源に適切に接続する必要があります。パッド、パターン、ビアを含むこれらの接続のインピーダンスは、できる限り低くする必要があります。通常は、パターン幅を太くし、できれば多層 PCB で専用電源プレーンを使用することで、これを実現します。

さらに、各電源ペアを、セラミックコンデンサ（ほとんどの場合、 $100\text{ nF}$  または  $1\text{ }\mu\text{F}$ 、表 4 参照）でデカップリングする必要があります。これらのコンデンサは、PCB の裏面の、該当するピンのできる限り近くに、またはその下に、配置する必要があります。正確な値は、アプリケーションによって異なることがあります。図 28 に、そのようなデカップリングの配置の標準的なレイアウトを示します。

図 28. デカップリング用コンデンサのレイアウト例

1. 電源とデカップリングコンデンサを内部プレーンに接続している PTH ビアが、灰色で表示されています。

### 9.7 ESD/EMI 保護

静電放電 (ESD) と電磁干渉 (EMI) は、後で追加するのが非常に複雑で費用がかかる可能性があるため、製品開発の最初から考慮する必要があります。

ESD と EMI は、国際規格 (IEC 61000、JESD 22 など) によって推進されており、ほとんどの国では、製品に必須のマーキング (CE、FCC など) を適用できるようにするための認証が必要です。

ESD と EMI は、標準化されたインターフェースの認証または要件 (たとえば USB など) によっても推進されています。

STM32MP15x ラインではデバイスレベルの ESD 保護を組み込んでいますが、最終製品の保護は外部コンポーネント、特に最終製品で外部ユーザがアクセスするインターフェース (Ethernet、USB、SD カードなど) で行う必要があります。

一部のコンポーネントでは、ESD 保護と EMI コモンモードフィルタリングが提供されています (USB で使用される ECMF02-2AMX6 など)。

ESD/EMI 保護のいくつかの例を [セクション 10 : リファレンスデザイン例](#) に示します。

詳細については、ST マイクロコントローラ用 EMC 設計ガイド アプリケーションノート (AN1709) を参照してください。

## 9.8 ノイズに敏感な信号

アプリケーションを設計するときは、以下を詳細に検討することにより、電磁両立性 (EMC) の性能を向上させることができます。

- 一時的な障害が実行中のプロセスに永続的に影響する信号(割込み信号およびハンドシェイクストローブ信号の場合。LED コマンドの場合は除く)。

これらの信号に対しては、グランドパターンで取り囲むこと、長さを短くすること、近くにノイズが多く敏感な配線（クロストーク効果）が無いことにより、EMC 性能が向上します。

デジタル信号の場合、2つの論理状態に対してできる限り最高の電気的マージンを持たせる必要があり、寄生状態を排除するために遅いシュミットトリガを推奨します。

- ノイズの多い信号（クロックなど）

- 敏感な信号（ハイインピーダンスなど）

詳細については、ST マイクロコントローラ用 EMC 設計ガイド アプリケーションノート (AN1709) を参照してください。

## 9.9 未使用的 I/O および機能

STM32MP15x ラインは広範囲のアプリケーションで使用できるように設計されており、通常は特定のアプリケーションがリソースを 100% 使用することはありません。

EMC 性能を向上するには、未使用的クロック、カウンタ、または I/O をフリーにしないでください。たとえば、I/O は “0” または “1” に設定（未使用 I/O ピンにプルアップまたはプルダウン）する必要があります。未使用的機能は「停止」または無効にする必要があります。

# 参考資料

## 10 リファレンスデザイン例

### 10.1 説明

以下のセクションでは、主要なインターフェースおよび重要なインターフェースを STM32MP15x ラインに接続するのに役立つ例を述べます。

#### 10.1.1 クロック

STM32MP15x ラインには 2 つのクロックソースが使用され、次の選択肢があります。

- LSE : 内蔵 RTC 用の 32.768 kHz クリスタル発振子

- HSE : STM32MP15x ラインのメインクロックとして 24 MHz クリスタル発振子または外部オシレータ

セクション 6 : 28 ページの [クロック](#) を参照してください。

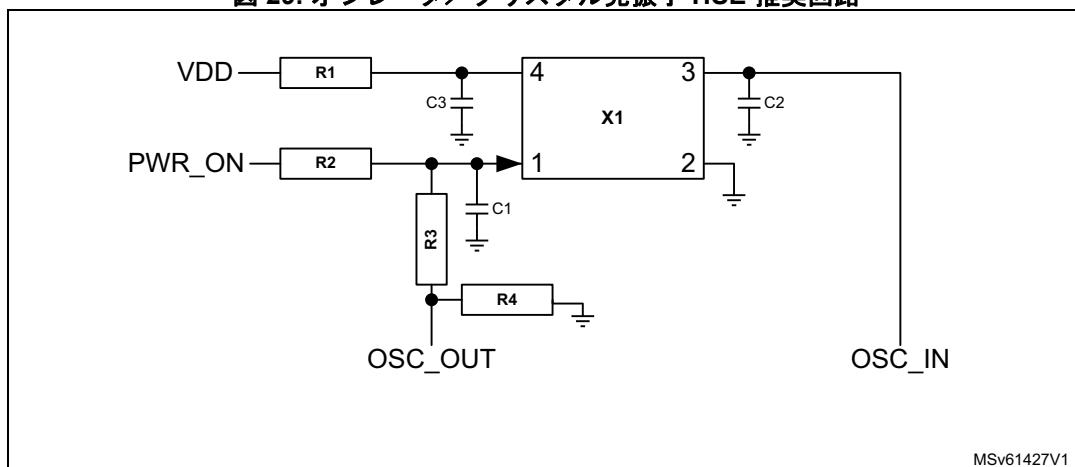

図 29. オシレータ／クリスタル発振子 HSE 推奨回路

表 15. オシレータまたはクリスタル発振子用の HSE 部品表

| -  | オシレータ           | クリスタル発振子        |

|----|-----------------|-----------------|

| X1 | NZ2016SH 24 MHz | NX2016SA 24 MHz |

| R1 | 10Ω             | -               |

| R2 | 10 kΩ           | -               |

| R3 | -               | 0Ω              |

| R4 | 1 kΩ            | -               |

| C1 | -               | 6.8 pF          |

| C2 | -               | 6.8 pF          |

| C3 | 10 nF           | -               |

## 10.1.2 リセット

図 4 の NRST リセット信号はアクティブローです。リセットソースには下記が含まれます。

- リセットボタン

- JTAG コネクタ経由のデバッグツール

[セクション 4.3 : 17 ページのリセットおよび電源供給スーパバイザ](#)を参照してください。

## 10.1.3 ブートモード

ブートオプションは、恒久的なワイヤまたはスイッチ SW3 (BOOT2)、SW2 (BOOT1)、SW1 (BOOT0) と内部 OTP を設定することによって構成されます。セクション 7 : 32 ページのブート設定を参照してください。

可能な U (S) ARTx\_RX ピンの 1 つを使用する UART ブートの場合 (STM32MP1 シリーズ wiki を参照)、ホストにフローティング信号が送信されるのを回避するために、初期化文字が受信され、BootROM によってデコードされるまで、それぞれの U (S) ARTx\_TX ピンに 10 kΩ の V<sub>DD</sub> プルアップが必要です。

表 16. ブート可能な UART ピン

| ペリフェラル               | 信号 | ピン   |

|----------------------|----|------|

| USART2               | RX | PA3  |

|                      | TX | PA2  |

| USART3               | RX | PB12 |

|                      | TX | PB10 |

| UART4 <sup>(1)</sup> | RX | PB2  |

|                      | TX | PG11 |

| UART5                | RX | PB5  |

|                      | TX | PB13 |

| USART6               | RX | PC7  |

|                      | TX | PC6  |

| UART7                | RX | PF6  |

|                      | TX | PF7  |

| UART8                | RX | PE0  |

|                      | TX | PE1  |

1. Linux コンソールの推奨デフォルト UART (すなわち、STLINK STDC14 コネクタの VCP として)。

## 10.1.4 SWD/JTAG インタフェース

リファレンスデザインでは、STM32MP15x ラインと標準コネクタとの間の接続を示しています。セクション 8 : 36 ページのデバッグ管理を参照してください。

注： 可能な場合は、デバッガからアプリケーションをリセットできるようにするために、デバッガプロープシステムのリセットピンを NRST に接続することをお勧めします。

### 10.1.5 電源

セクション 4 : 11 ページの電源を参照してください。

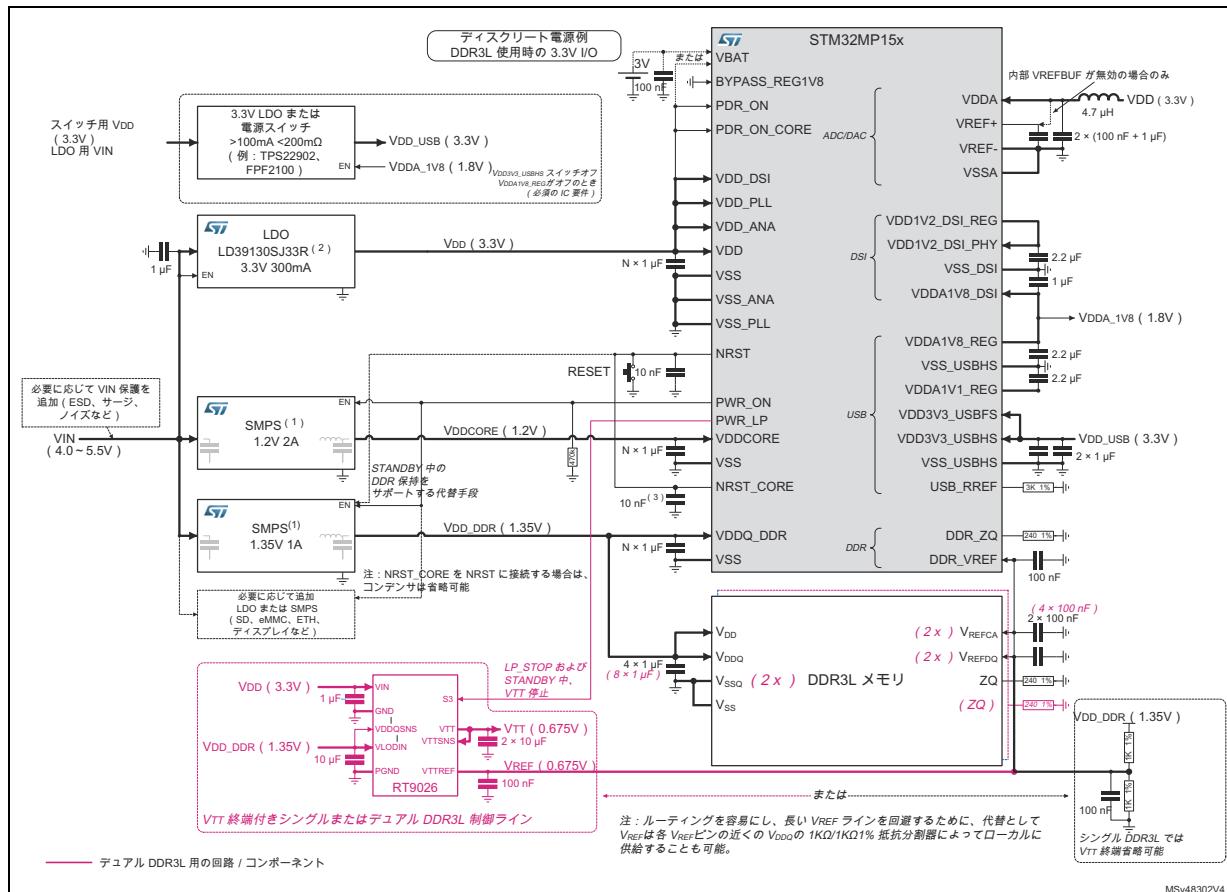

#### DDR3L 使用時の 3.3 V I/O のディスクリート電源例

このリファレンスデザインの例は、電力削減を重視せずに、低コストの DDR3L を使用するシンプルな 3.3 VIO プラットフォームを対象としています。SLEEP/STOP/STANDBY モードがサポートされています。LP-STOP および DDR3L 保持が可能な低消費電力 STANDBY は使用できますが、セルフリフレッシュ時に低消費電力ではない DDR3L を使用しているため、ほとんど効果がないと思われます。

STM32MP151, STM32MP153 and STM32MP157 discrete power supply hardware integration (AN5256) も参照してください。

図 30. DDR3L 使用時の 3.3 V I/O ディスクリート電源例

- 追加の SMPS コンポーネントは示されていません。

- より小さい NCP161AFCT330 を使用することもできます。

- NRST\_CORE を NRST に接続する場合は、NRST\_CORE ピンの 10 nF のコンデンサは省略できます。

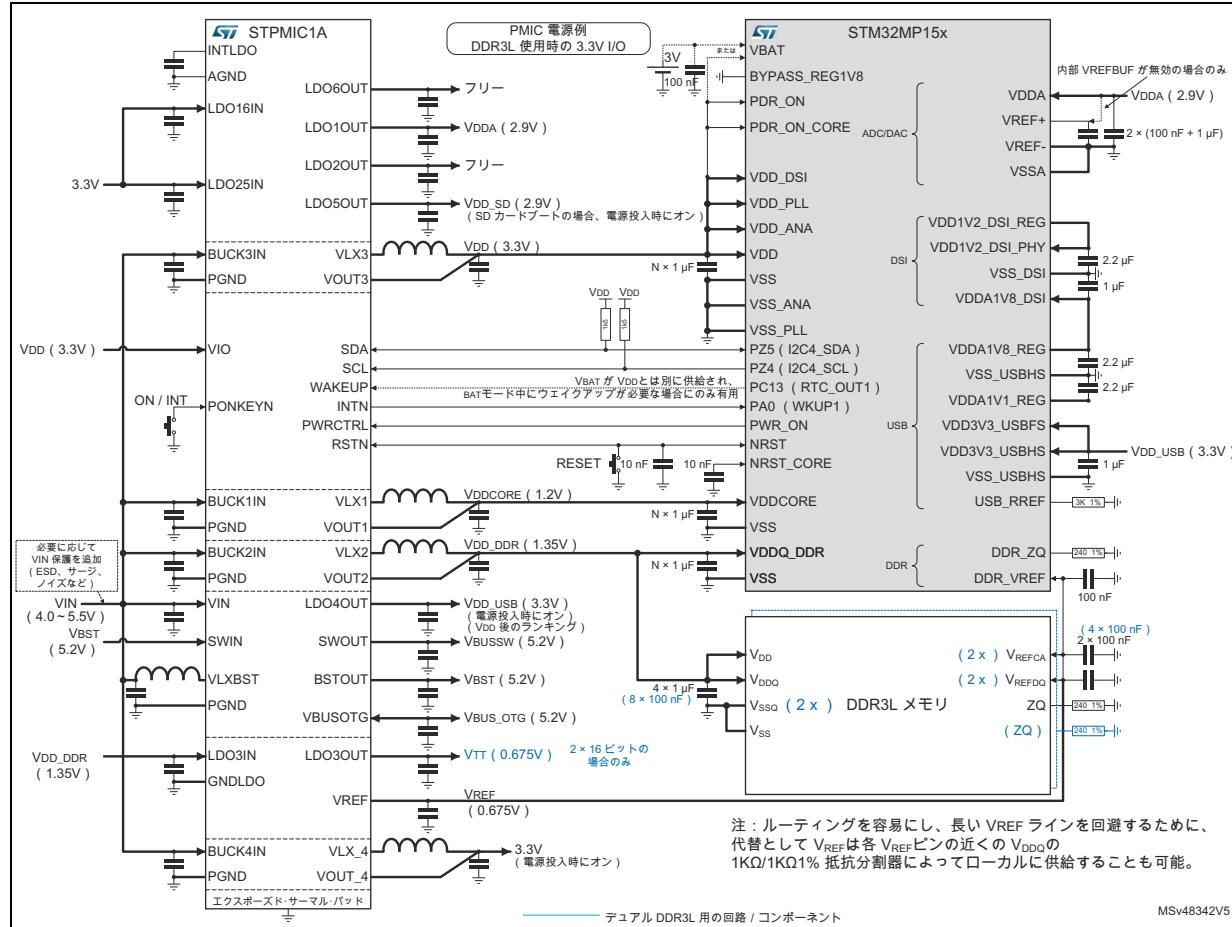

#### DDR3L 使用時の 3.3 V I/O の PMIC 電源例

このリファレンスデザインの例は、低コストの DDR3L と高集積 PMIC を備えた複雑な 3.3 VIO プラットフォームを対象としています。通常、プラットフォームのすべてのコンポーネントは PMIC で電力供給できます。PMIC I2C およびサイドバンド信号により、完全な電源制御がサポートされています。SLEEP/STOP/STANDBY モードがサポートされています。PMIC コンポーネントの詳細は、PMIC のドキュメントを参照してください。

# 参考資料

図 31. DDR3L 使用時の 3.3 V I/O PMIC 例

# 参考資料

## リファレンスデザイン例

AN5031

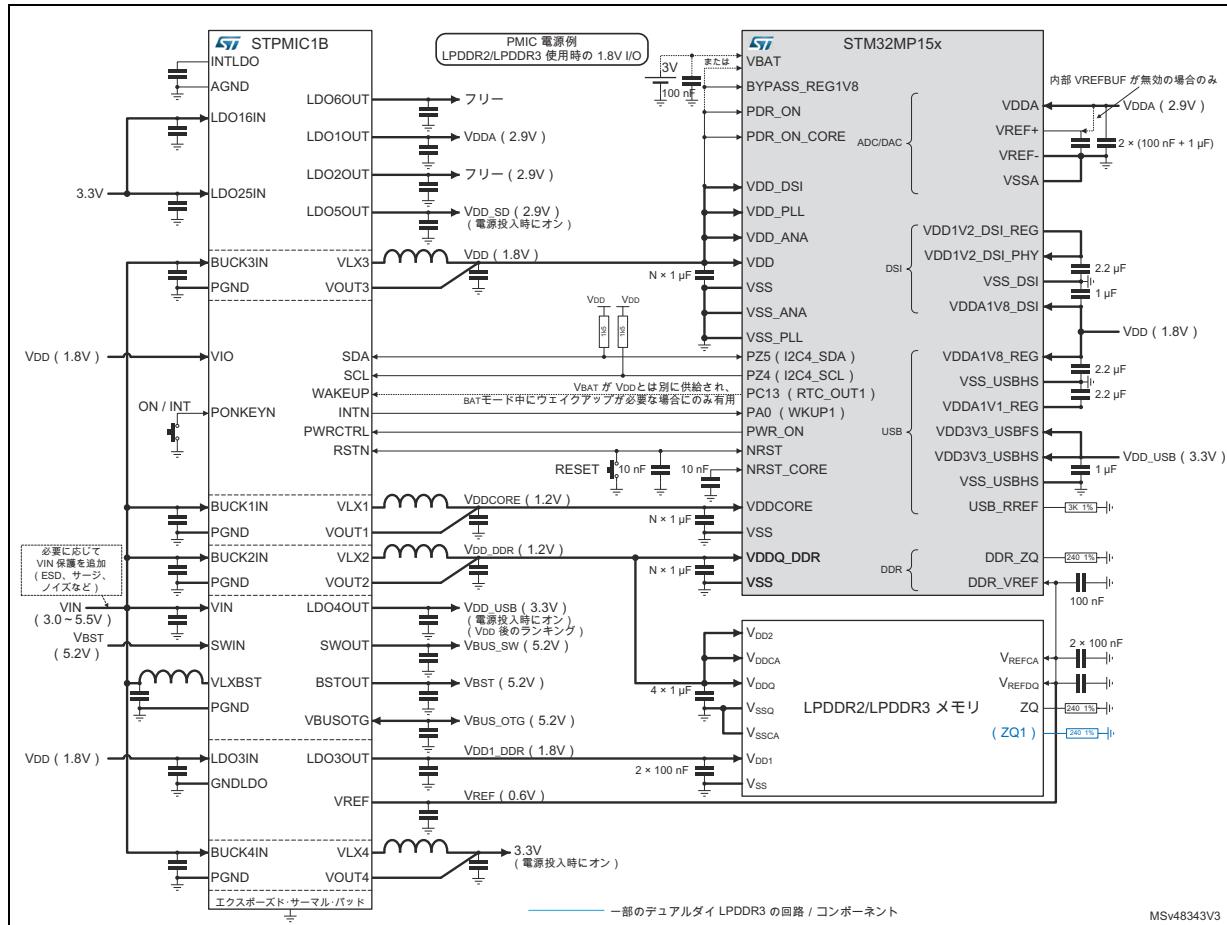

### LPDDR2/LPDDR3 使用時の 1.8 V I/O の PMIC 電源例

このリファレンスデザインの例は、低電力の LPDDR2/LPDDR3 と高集積 PMIC を備えた複雑な 1.8 V I/O プラットフォームを対象としています。通常、プラットフォームのすべてのコンポーネントは PMIC で電力供給できます。PMIC I<sub>2</sub>C およびサイドバンド信号により、完全な電源制御がサポートされています。SLEEP/STOP/STANDBY モードのほか、LPDDR2/LPDDR3 保持を使用可能な超低消費電力 STANDBY もサポートされています。PMIC コンポーネントの詳細は、PMIC のドキュメントを参照してください。

図 32. LPDDR2/LPDDR3 使用時の 1.8 V I/O PMIC 例

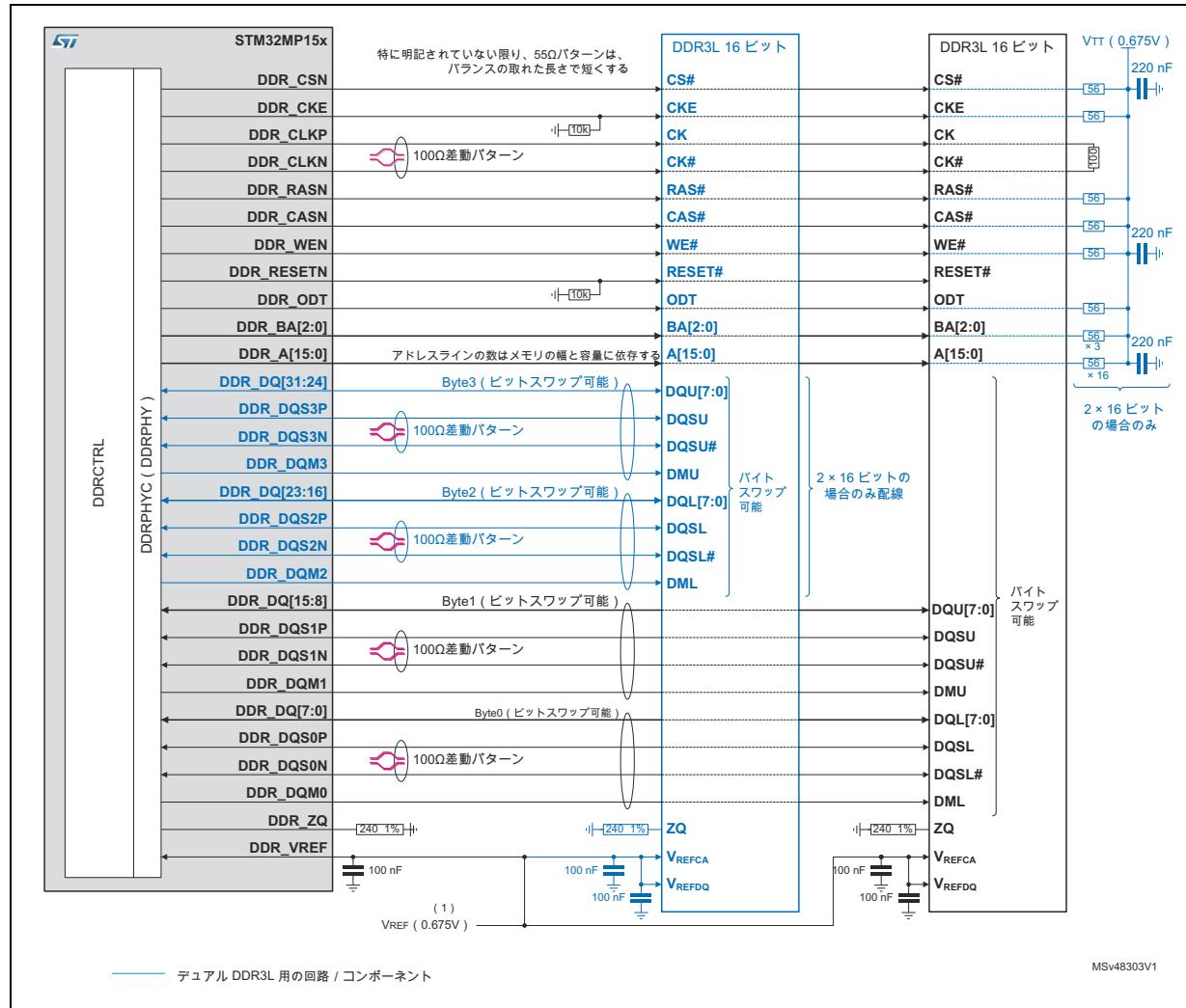

## 10.1.6 DDR3/DDR3L SDRAM

DDR3 と DDR3L の違いは、電源電圧（1.5 V 対 1.35 V）と  $V_{REF}$  レベル（0.75 V 対 0.675 V）が異なることだけです。DDR3L は、ほとんどの DDR3 設計に取って代わりました。

240Ω 1% 抵抗を DDR\_ZQ と  $V_{SS}$  の間に接続する必要があります。この抵抗は、各 DDR3/DDR3L コンポーネントで必要な ZQ 抵抗と共用しないでください。

2x16 ビットデバイスの場合、終端電圧（VTT）電源に接続されたインピーダンス整合抵抗ネットワークは、最後のデバイスのできるだけ近くに配置する必要があります。インピーダンスの不連続性を回避するには、「フライバイ」ルーティング技術を使用する必要があります。以下の例の値はほとんどの場合に機能しますが、IO 駆動能力と PCB インピーダンスのそれぞれの側に合わせて調整できます。

図 33. DDR3L 16/32 ビット接続例

- ルーティングを容易にし、長い  $V_{REF}$  ラインを回避するために、代替として  $V_{REF}$  は各  $V_{REF}$  ピンの近くの  $V_{DDQ}$  の 1kΩ/1KΩ1% 抵抗分割器によってローカルに供給可能。

- 電源およびデカッピングコンデンサは表示されていない。

詳細なルーティング例は STM32MP1 Series DDR memory routing guidelines (AN5122) に記載されています。

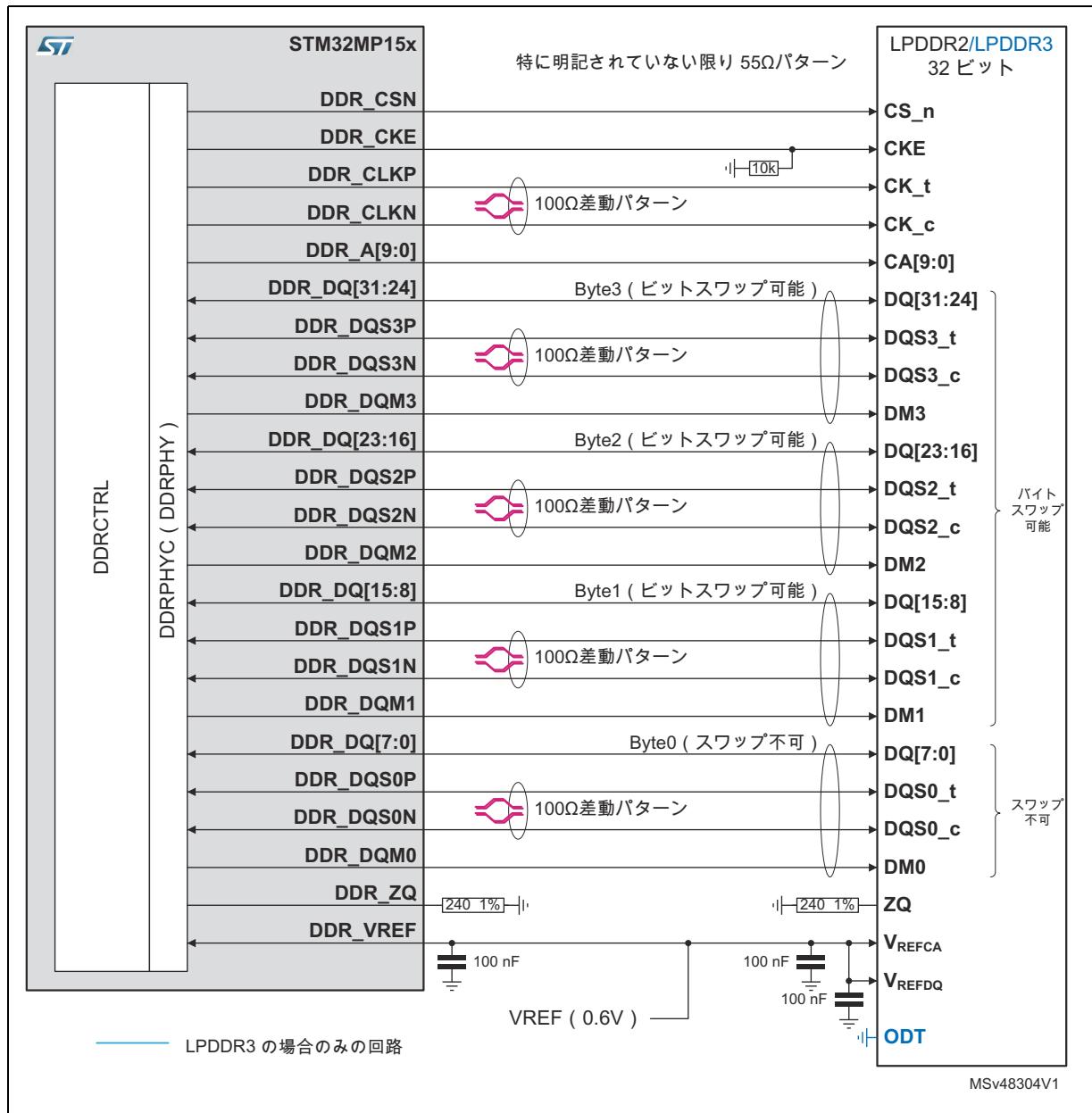

### 10.1.7 LpDDR2/LpDDR3 SDRAM

240Ω 1% 抵抗を DDR\_ZQ と V<sub>SS</sub> の間に接続する必要があります。この抵抗は、LPDDR2/LPDDR3 コンポーネントで必要な 1 つ以上の ZQ 抵抗と共にしないでください。

図 34. LPDDR2/LPDDR3 32 ビット接続例

- 電源およびデカップリングコンデンサは表示されていない。

詳細なルーティング例は STM32MP1 Series DDR memory routing guidelines (AN5122) に記載されています。

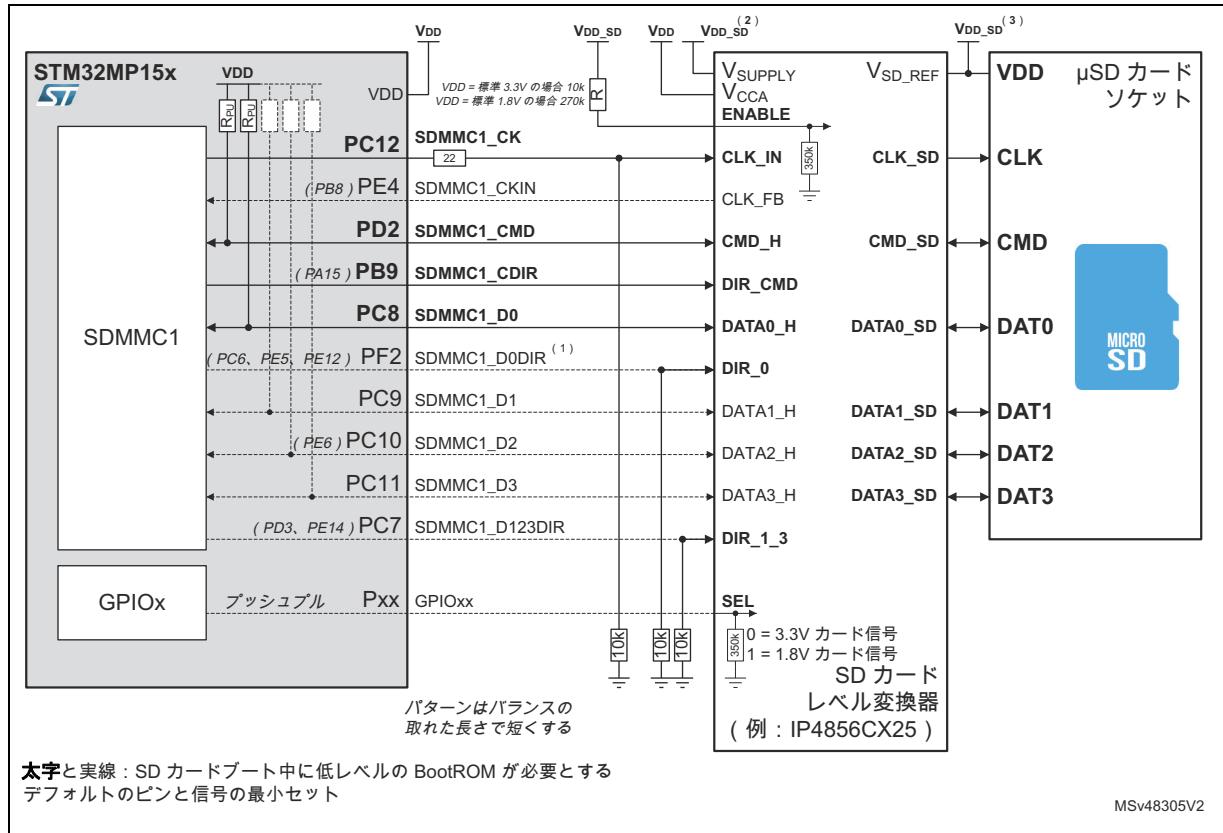

## 10.1.8 SD カード

### 外部レベルシフタ

これにより、1.8 V カード I/O 電圧に切り替える必要のある UHS-I 高速モード（最大 SDR50 および DDR50、すなわち 50 MB/秒のバス速度）が使用できます（SD カードは 3 V カード I/O で起動されます）。

注：ブートは常に「標準」モード（3 V IO）で行われるため、カードを UHS-I のアプリケーションで使用する場合、リセットまたは STANDBY 後にカード電源のパワーサイクルが必要です。

この例は、1.71 V から 3.6 V の間の MPU IO 電圧  $V_{DD}$  とは無関係です。標準の 1.8 V の VDD の場合、すべての SD カードは 3 V 信号電圧を使用する「標準」モードでトランザクションを開始するため、外部レベルシフターが必須です。

良好なシグナルインテグリティは、ボード、GPIO の能力設定（GPIO\_OSPEEDR レジスタ）、および  $V_{DD}$  電圧に依存することにご注意ください。

$V_{DD} = 1.8 \text{ V}$  を使用する場合、SDMMC 出力で使用されるパッドで最高の速度を確保するには、OTP ビットとレジスタ SYSCFG\_IOCTRLSETR (HSLVEN\_SDMMC ビット) の設定が必要になることがあります。

---

警告： $V_{DD}$  が 2.7 V を超える場合、UHSLVEN および HSLVEN は設定しないでください。IC が損傷する可能性があります。

---

必要に応じて、インピーダンス整合抵抗を出力駆動ピンのできるだけ近くに配置する必要があります。以下の例の値はほとんどの場合に機能しますが、IO 駆動能力と PCB インピーダンスに合わせて調整できます。

# 参考資料

図 35. 外部レベルシフタ付き SD カード接続例

1. SDMMC1\_D0DIR は、SD カードの DATA0 から読み込みデータのみが要求されるため、ブートフェーズでは使用されません。それでも、カードから MPU への正しい DATA0\_SD 方向を保証するために、SDMMC1\_D0DIR のプルダウンが必要です。

2. UHS-I で使用する場合、再起動（リセットまたは STANDBY の終了時）を可能にするために、V<sub>DD\_SD</sub> を 1 ms 以上カットする必要があります。

V<sub>DD</sub> > V<sub>DD\_SD</sub> の場合、V<sub>DD</sub> を使用します。

3. UHS-I で使用する場合、再起動（リセットまたは STANDBY の終了時）を可能にするために、V<sub>DD\_SD</sub> を 1 ms 以上カットする必要があります。

4. デカップリングコンデンサは表示されていません。

V<sub>DD\_SD</sub> シャットダウンの前（たとえば、STANDBY の前）に、カードに送られるすべての信号を SDMMC1 ドライバによって 0 またはハイインピーダンスに設定する必要があります。

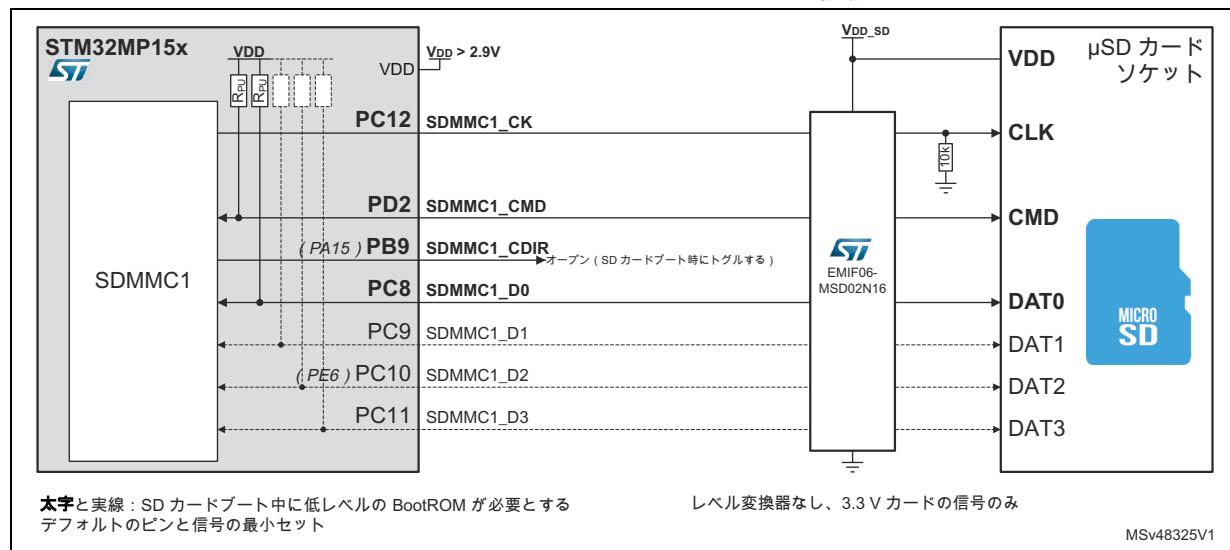

## ダイレクト 3.3 V IO 電圧

これは、 $V_{DD} > 2.9\text{ V}$  を必要とするシンプルなインターフェースであり、標準の SD カード速度（最大 ハイスピード 25 MB/s のバス速度まで）に制限されています。大容量 SD カードには大電流が必要で あり、STANDBY 時の電力を制限するために、 $V_{DD\_SD}$  を  $V_{DD}$  から分離できますが、それらの間の電 圧レベルは、電力を節約するために  $V_{DD\_SD}$  が切断されている場合を除き、200 mV 以内である必 要があります。

図 36. 3.3 V I/O SD カード接続例

### 10.1.9 eMMC™ Flash

良好なシグナルインテグリティは、ボード、GPIO の能力設定 (GPIO\_OSPEEDR レジスタ)、およ び  $V_{DD}$  電圧に依存することにご注意ください。

$V_{DD} = 1.8\text{ V}$  を使用する場合、SDMMC 出力で使用されるパッドで最高の速度を確保するには、OTP ビットとレジスタ SYSCFG\_IOCTRLSETR (HSLVEN\_SDMMC ビット) の設定が必要になることが あります。

**警告 :**  $V_{DD}$  が 2.7 V を超える場合、UHSLVEN および HSLVEN は設定しないで ください。IC が損傷する可能性があります。

必要に応じて、インピーダンス整合抵抗を出力駆動ピンのできるだけ近くに配置する必要がありま す。以下の例の値はほとんどの場合に機能しますが、IO 駆動能力と PCB インピーダンスに合わせて 調整できます。

# 参考資料

図 37. eMMC™ 接続例

1. デカップリングコンデンサは表示されていません。

eMMC では RSTn がデフォルトで無効になっており、eMMC 電源にパワーサイクルがない場合は、リセット後に再起動できるように、eMMC レジスタで RSTn を有効にする必要があります。

V<sub>DD</sub> とは独立にメモリ IO 電源をシャットダウンできる場合は、NRST をメモリリセットピンに直接接続しないでください。代わって次のオプションが使用できます。

- メモリに内部パワーオンリセットがある場合、メモリリセットピンは開いたままにする。

- メモリリセットピンをショットキーダイオードを介して NRST 側のカソードに接続する。