# 参考資料

life.augmented

AN5276

アプリケーション・ノート

ST25R3916向けアンテナ設計

## はじめに

NFC技術の課題として、特定の13.56 MHzアプリケーション向けに近接アンテナを設計し、そのインピーダンスの整合を図ることがあります。NFCの磁気ループ・アンテナは、システム性能の劣化原因となるような環境条件に曝されることが少なくありません。

このアプリケーション・ノートは、ST25R3916デバイスに直接接続される磁気ループ・アンテナの設計ガイドです。アンテナの設計のほか、アンテナ・パラメータの測定、インピーダンスの整合、設計検証の方法についても記載します。

本稿ではST25R3916デバイスを例に説明していますが、その手法やツールは同一ファミリの他製品にも適用できます。

ST25R3916は、NFCイニシエータ、NFCターゲット、NFCリーダ、NFCカード・エミュレーション・モードに対応した高性能NFCフロントエンドです。

ST25R3916は、高機能アナログ・フロント・エンド (AFE) と、以下のモードに対応した高度に統合されたデータ・フレーミング・システムを備えています。

- ISO 18092 (NFCIP-1) パッシブ・イニシエータおよびアクティブ・イニシエータ、ISO 18092 (NFCIP-1) パッシブ・ターゲットおよびアクティブ・ターゲット、

- 高ビット・レートに対応したNFC-A/B (ISO 14443A/B) リーダ、NFC-F (FeliCa™) リーダ、NFC-AおよびNFC-Fカード・エミュレーションAFEおよびフレーミング・システムの独自動作モードであるストリーム・モードやトランスペアレント・モードを使用すれば、MIFARE® Classicなど、上記以外のカスタム・プロトコルをリーダまたはカード・エミュレーション・モードで実装できます。

本稿は、ST25R antenna matching tool ソフトウェア (STSW-ST25R004) の使用を前提としています。このソフトウェアは、整合用部品の計算に対応し、再調整作業の繰り返しを最小限にします。このツールとともに、オープン・ソースのシミュレータも用意されており、シミュレーションによる基本的なシステム検証が可能です。

参考文献として、次の資料があります。

- ST25R3916のデータシート ([www.st.com](http://www.st.com)より入手可能)

- アプリケーション・ノート (AN4914) ([www.st.com](http://www.st.com)より入手可能)

- ISO/IEC 14443およびISO/IEC 10373-6:2011 ([www.iso.org](http://www.iso.org)より入手可能)

- EMVCo ([www.emvco.com](http://www.emvco.com)より入手可能)

# 参考資料

## 目次

AN5276

## 目次

|       |                     |    |

|-------|---------------------|----|

| 1     | 略号と表記法一覧            | 6  |

| 1.1   | 略号                  | 6  |

| 1.2   | 数値の表記               | 6  |

| 2     | ハードウェアおよびソフトウェアの要件  | 7  |

| 3     | アンテナ・インターフェース段      | 8  |

| 3.1   | カード・エミュレーション・モード    | 9  |

| 3.1.1 | 内部ドライバによるパッシブ負荷変調   | 9  |

| 3.1.2 | 外部トランジスタによるパッシブ負荷変調 | 9  |

| 3.2   | リーダ・モードと出力電力        | 10 |

| 3.3   | EMC フィルタ            | 12 |

| 3.4   | 整合回路                | 13 |

| 3.5   | コンデンサ分圧回路           | 13 |

| 3.6   | アンテナ                | 13 |

| 4     | アンテナ・パラメータ          | 14 |

| 4.1   | ネットワーク・アナライザの準備     | 14 |

| 4.2   | パラメータ測定             | 14 |

| 4.3   | アンテナの等価回路           | 15 |

| 5     | アンテナ設計              | 20 |

| 5.1   | 境界条件とシミュレーション・モデル   | 20 |

| 5.2   | シミュレーション結果          | 21 |

| 6     | アンテナの整合             | 26 |

| 6.1   | 整合ツール               | 26 |

| 6.2   | シミュレーション            | 28 |

| 6.2.1 | モデル                 | 29 |

| 6.2.2 | 結果                  | 33 |

| 6.3   | 整合回路の挙動             | 34 |

| 7     | 設計検証                | 36 |

# 参考資料

AN5276

目次

---

|     |                              |    |

|-----|------------------------------|----|

| 7.1 | PCD の RF アナログ・パラメータの測定 ..... | 36 |

| 7.2 | 時間ドメインでの Q 値の検証 .....        | 38 |

| 7.3 | 周波数ドメインでの Q 値の検証 .....       | 38 |

| 7.4 | 目標整合インピーダンスの測定 .....         | 40 |

| 8   | 結論 .....                     | 41 |

| 9   | 改版履歴 .....                   | 42 |

# 参考資料

表の一覧

AN5276

## 表の一覧

|      |                                        |    |

|------|----------------------------------------|----|

| 表 1. | 106 Kb/s の Type-A 信号のタイミング・パラメータ ..... | 18 |

| 表 2. | 形状パラメータの変化に対するアンテナ・パラメータの挙動 .....      | 24 |

| 表 3. | 文書改版履歴 .....                           | 42 |

| 表 4. | 日本語版文書改版履歴 .....                       | 42 |

## 図の一覧

|       |                                             |    |

|-------|---------------------------------------------|----|

| 図 1.  | アンテナ・インタフェース段（差動整合回路網）                      | 8  |

| 図 2.  | アンテナ回路（EMI フィルタ、整合回路、可変容量コンデンサを含む）          | 9  |

| 図 3.  | 外部負荷変調回路                                    | 10 |

| 図 4.  | 推奨整合インピーダンス                                 | 11 |

| 図 5.  | Q 値                                         | 12 |

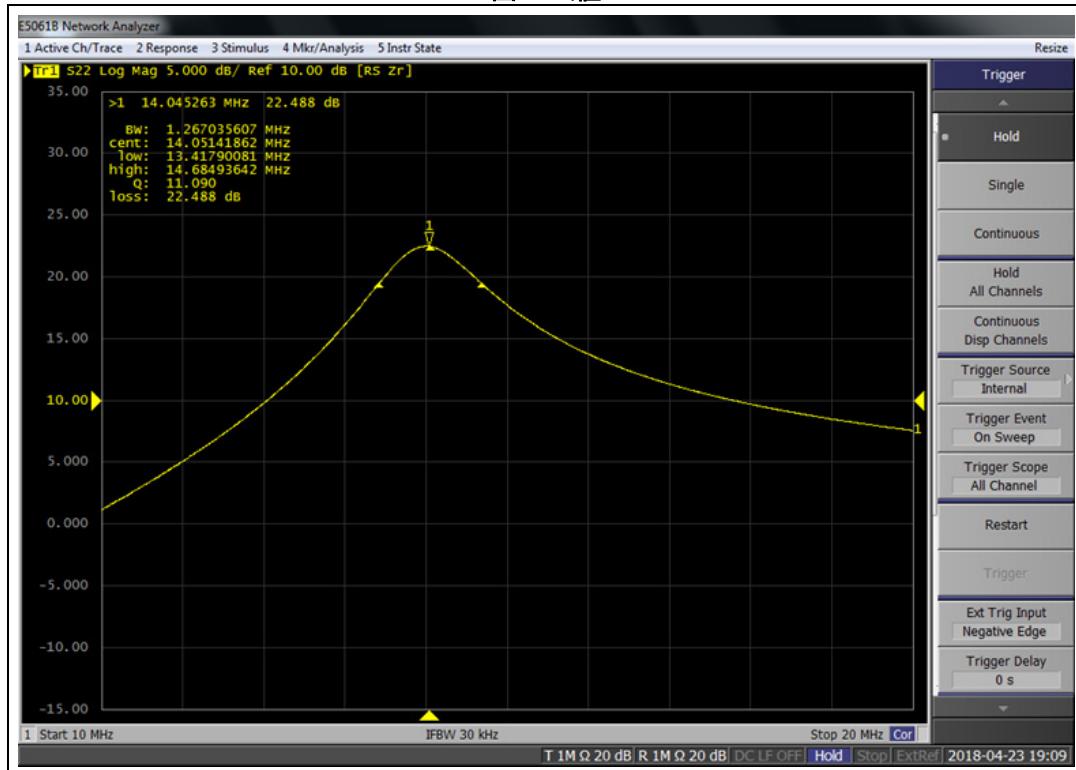

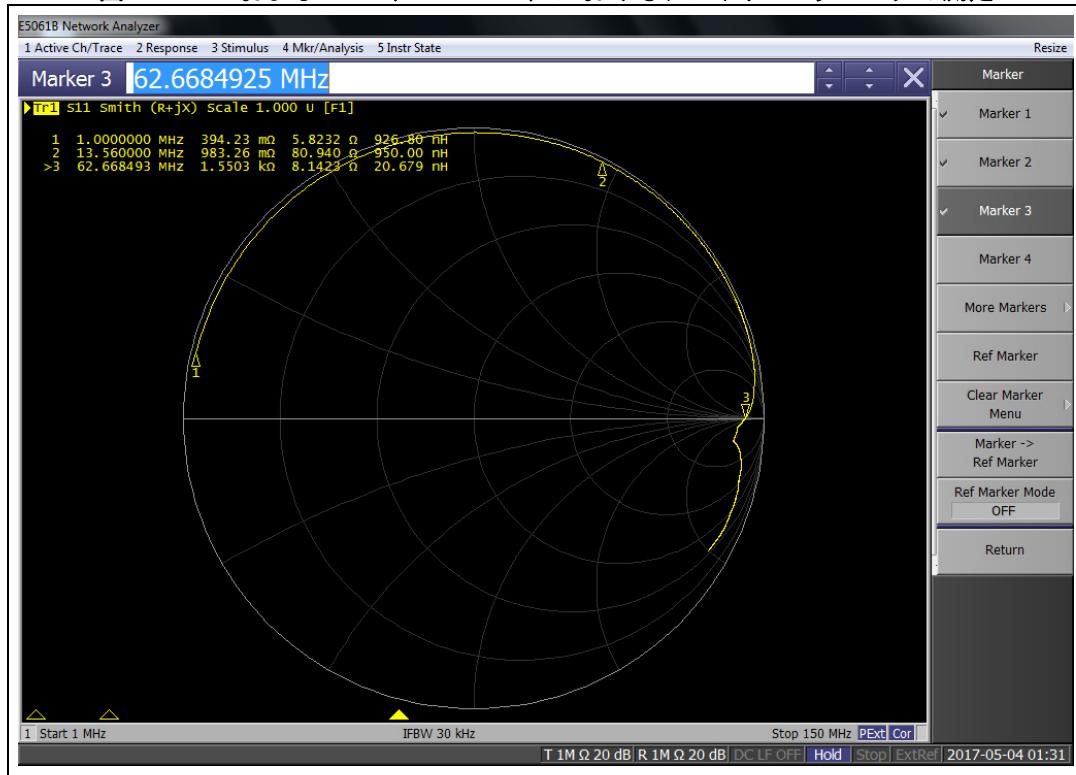

| 図 6.  | 1 MHz および SRF (62.67 MHz) におけるアンテナ・パラメータの測定 | 15 |

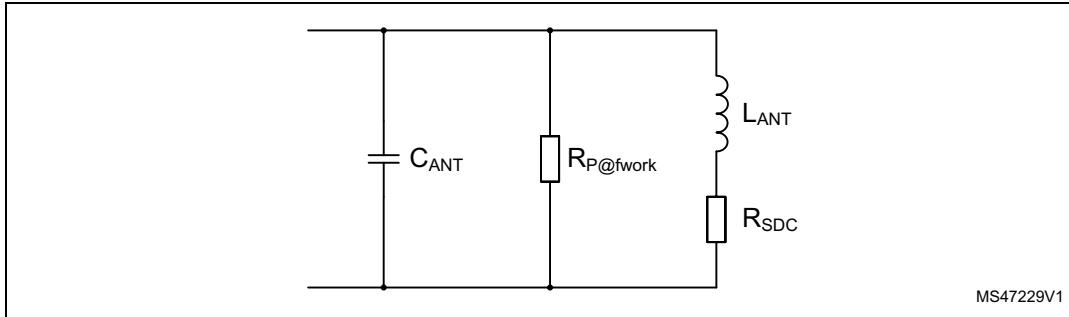

| 図 7.  | アンテナの等価回路                                   | 16 |

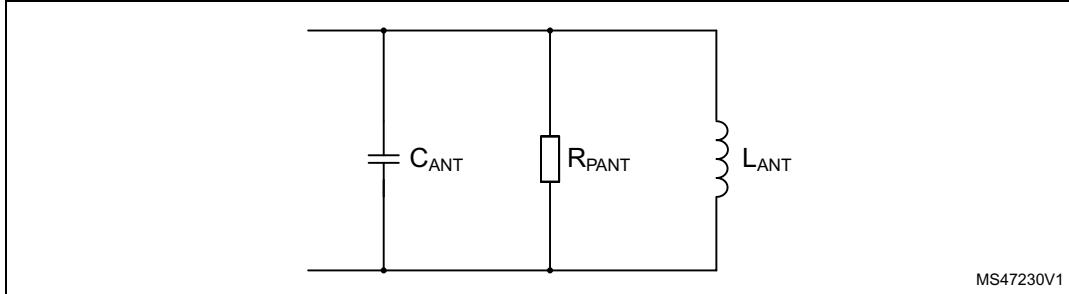

| 図 8.  | アンテナの等価回路（最終的な回路）                           | 16 |

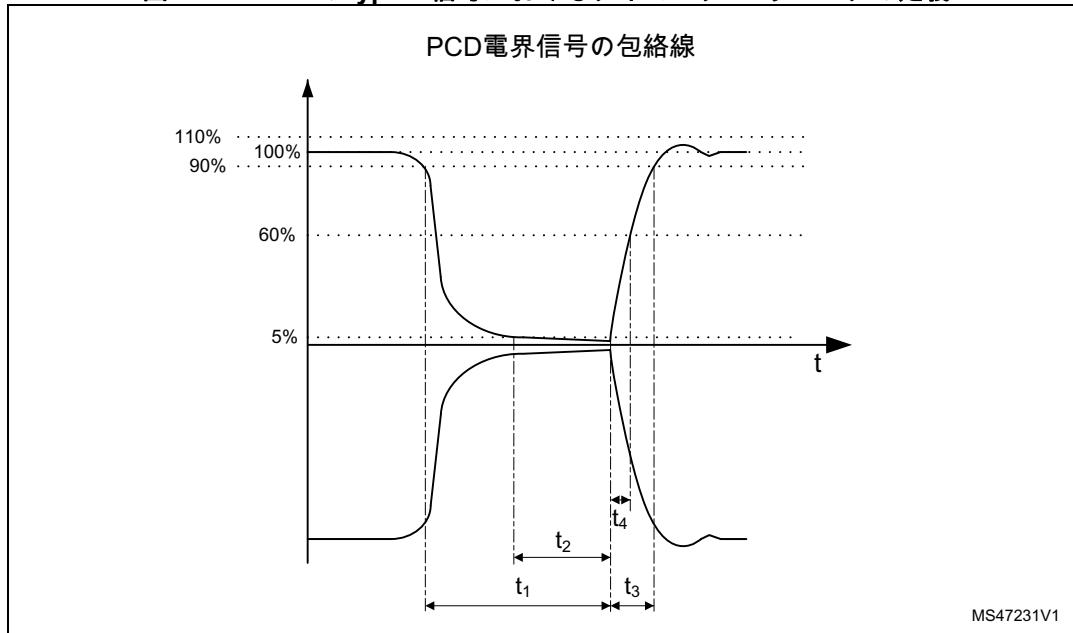

| 図 9.  | 106 Kb/s の Type-A 信号におけるタイミング・パラメータの定義      | 17 |

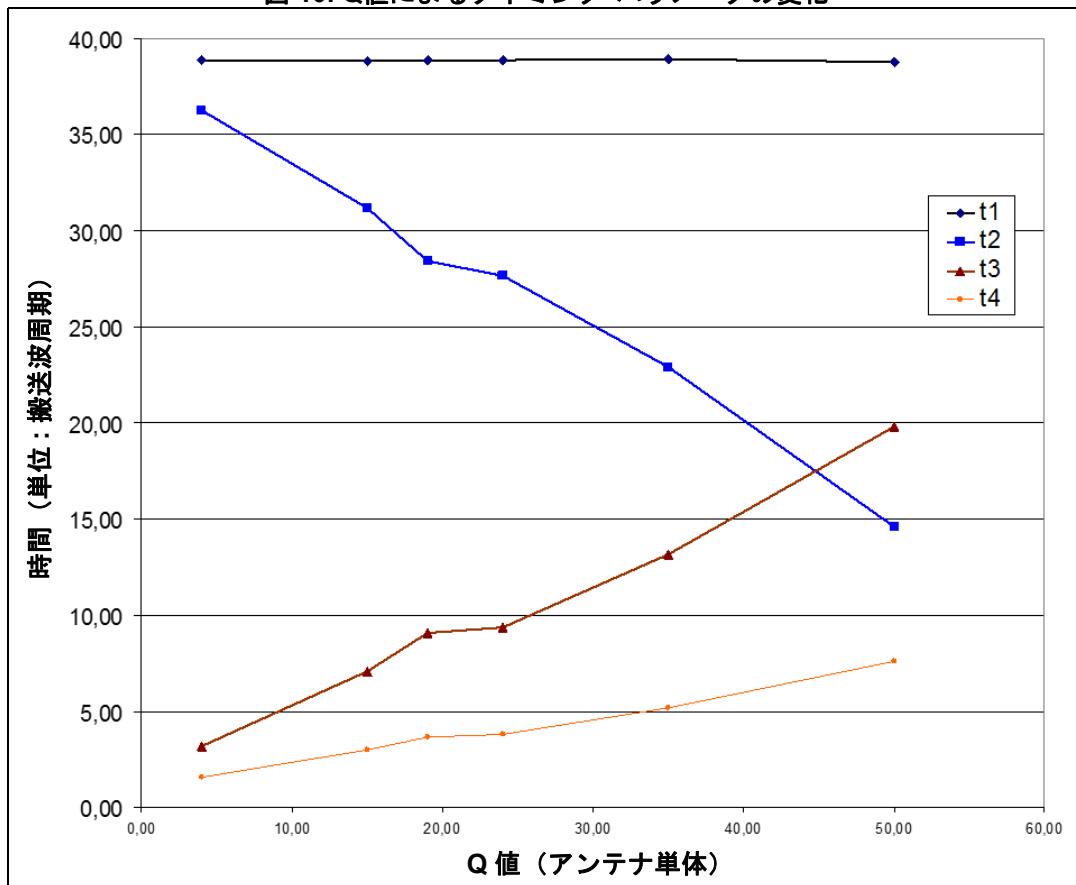

| 図 10. | Q 値によるタイミング・パラメータの変化                        | 18 |

| 図 11. | データ・レート 106 Kb/s の Type-A 信号における $t_1$ の定義  | 19 |

| 図 12. | コイル・アンテナのシミュレーション・モデル                       | 21 |

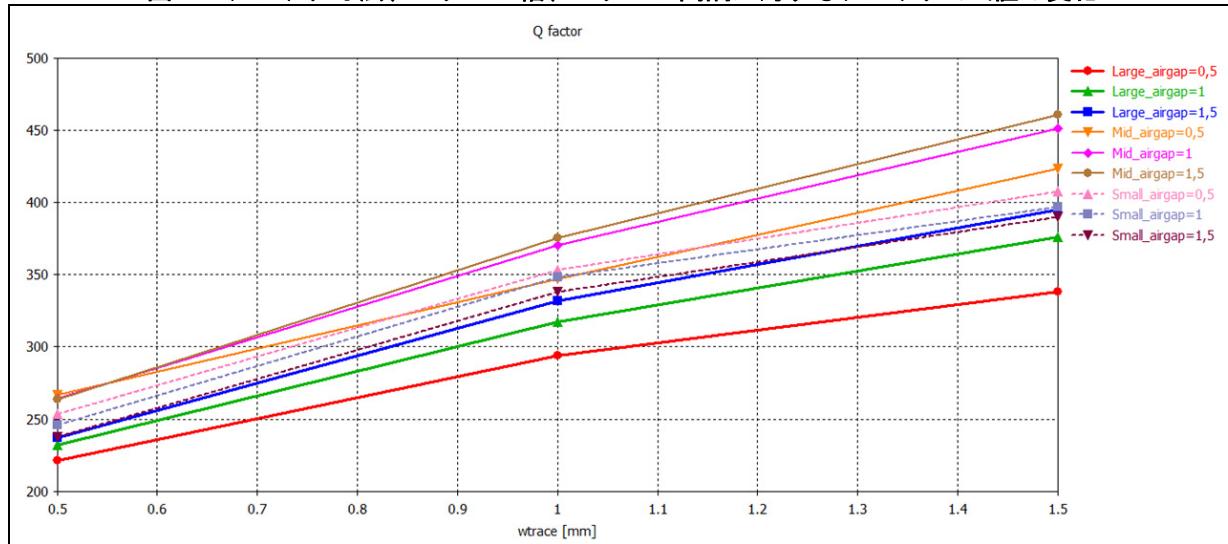

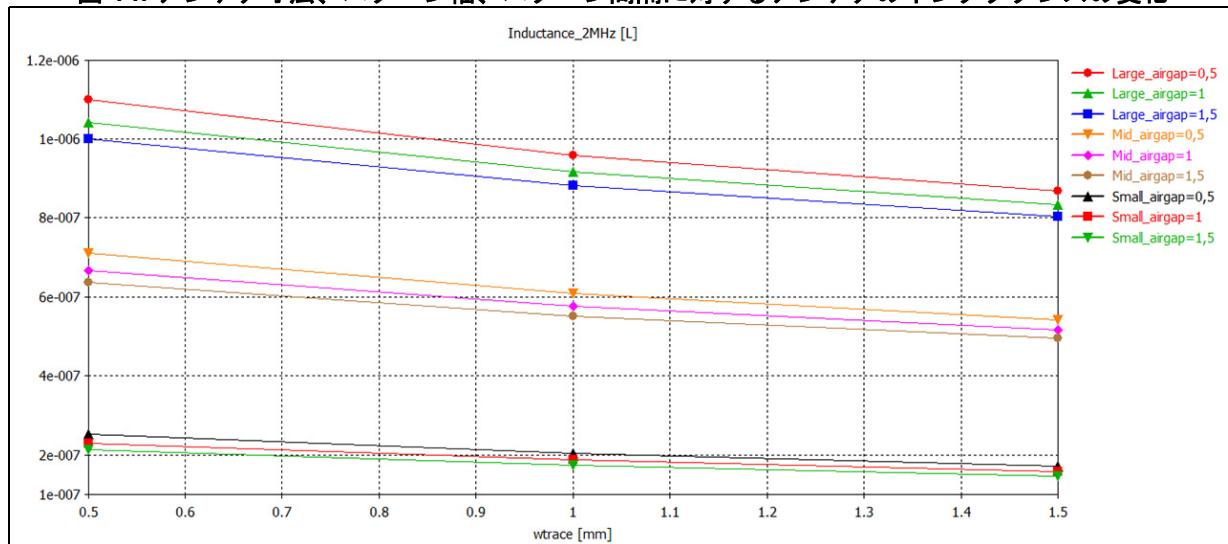

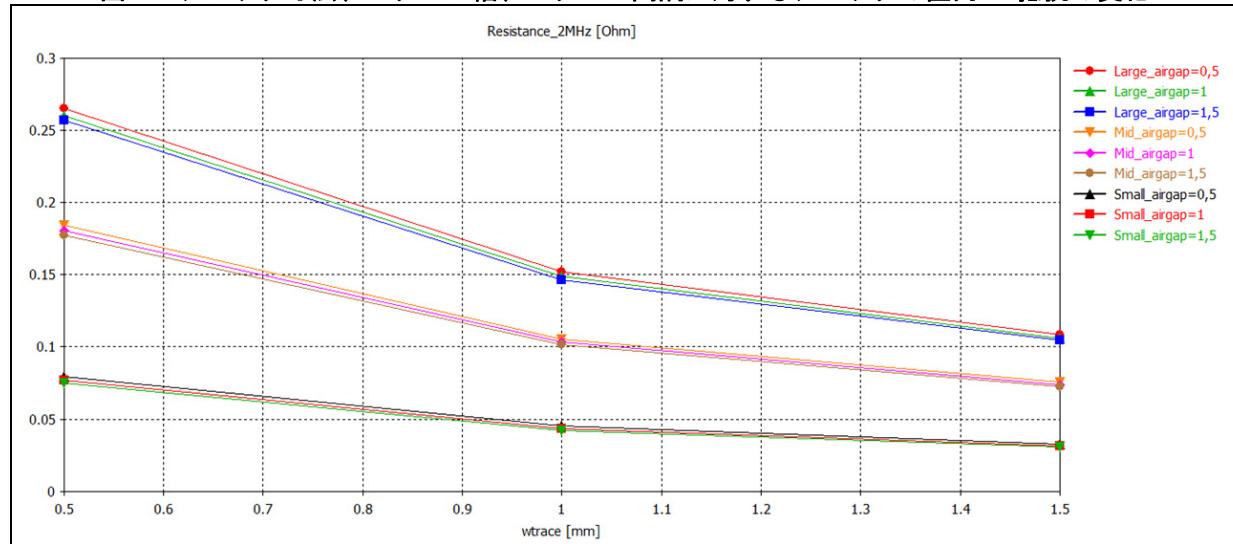

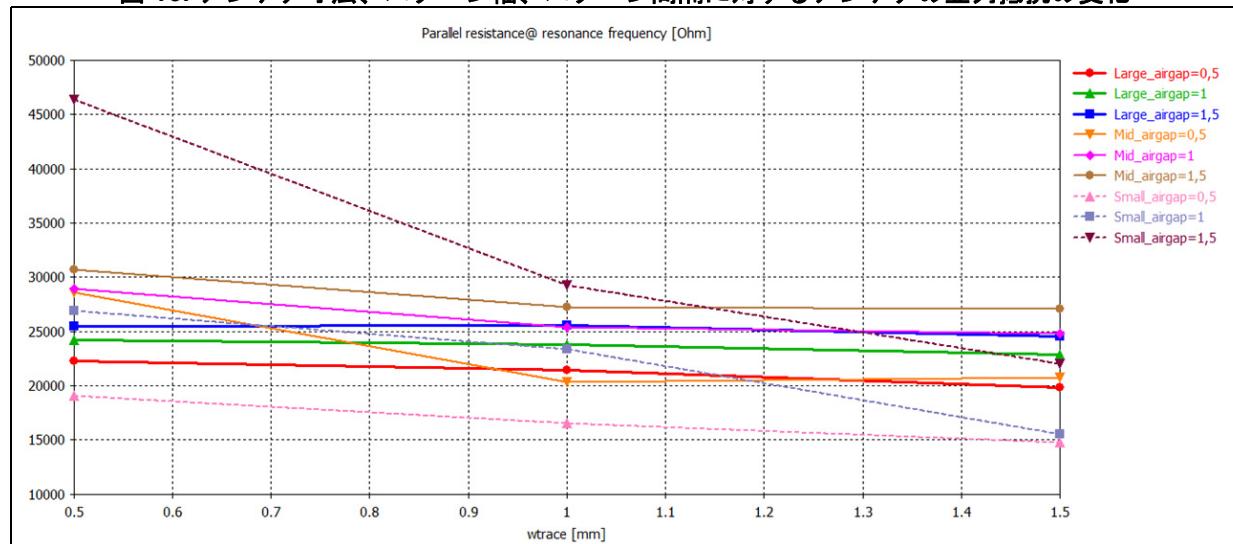

| 図 13. | アンテナ寸法、パターン幅、パターン間隔に対するアンテナの Q 値の変化         | 22 |

| 図 14. | アンテナ寸法、パターン幅、パターン間隔に対するアンテナのインダクタンスの変化      | 22 |

| 図 15. | アンテナ寸法、パターン幅、パターン間隔に対するアンテナの直列 DC 抵抗の変化     | 23 |

| 図 16. | アンテナ寸法、パターン幅、パターン間隔に対するアンテナの並列抵抗の変化         | 23 |

| 図 17. | アンテナ寸法、パターン幅、パターン間隔に対するアンテナの共振周波数の変化        | 24 |

| 図 18. | 差動型整合トポロジ                                   | 26 |

| 図 19. | ST25R antenna matching tool - メイン・ウィンドウ     | 27 |

| 図 20. | ST25R antenna matching tool - 整合回路定数値の計算結果  | 28 |

| 図 21. | シミュレーション・パラメータ                              | 29 |

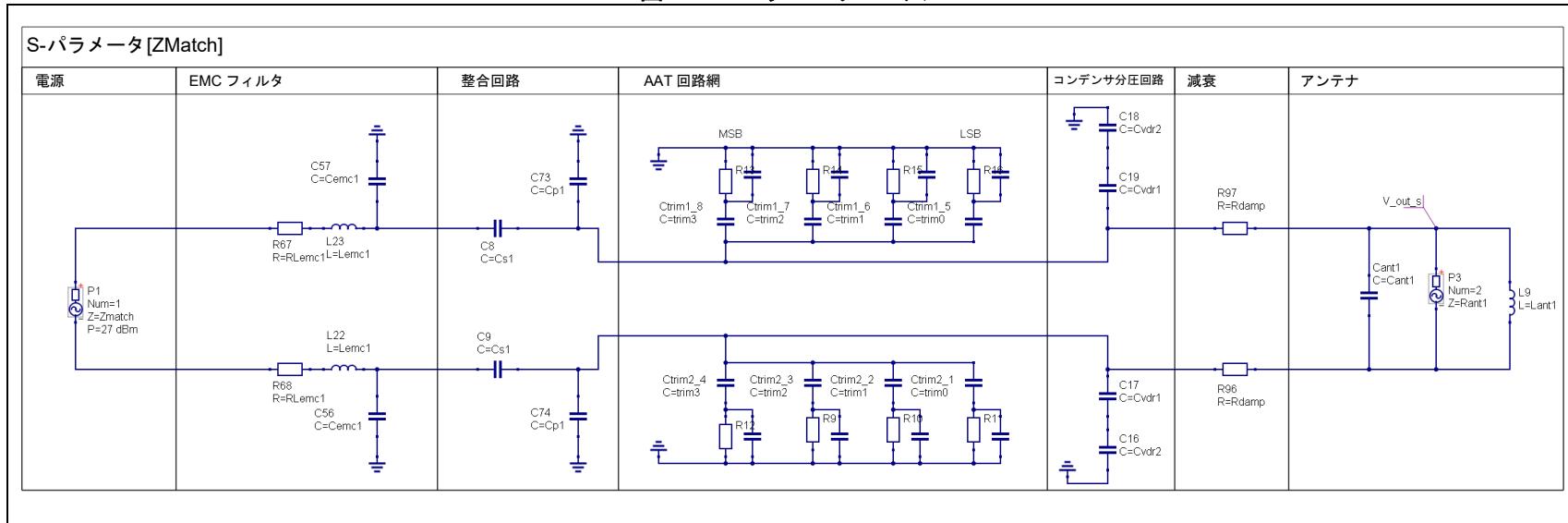

| 図 22. | S-パラメータ・モデル                                 | 31 |

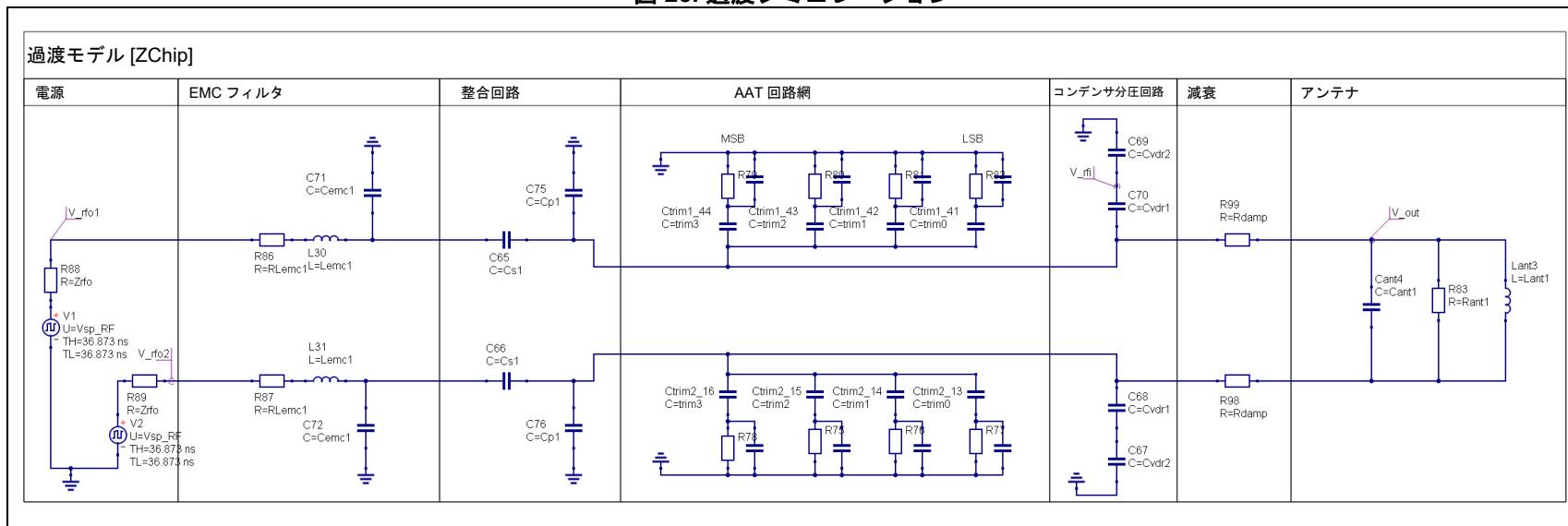

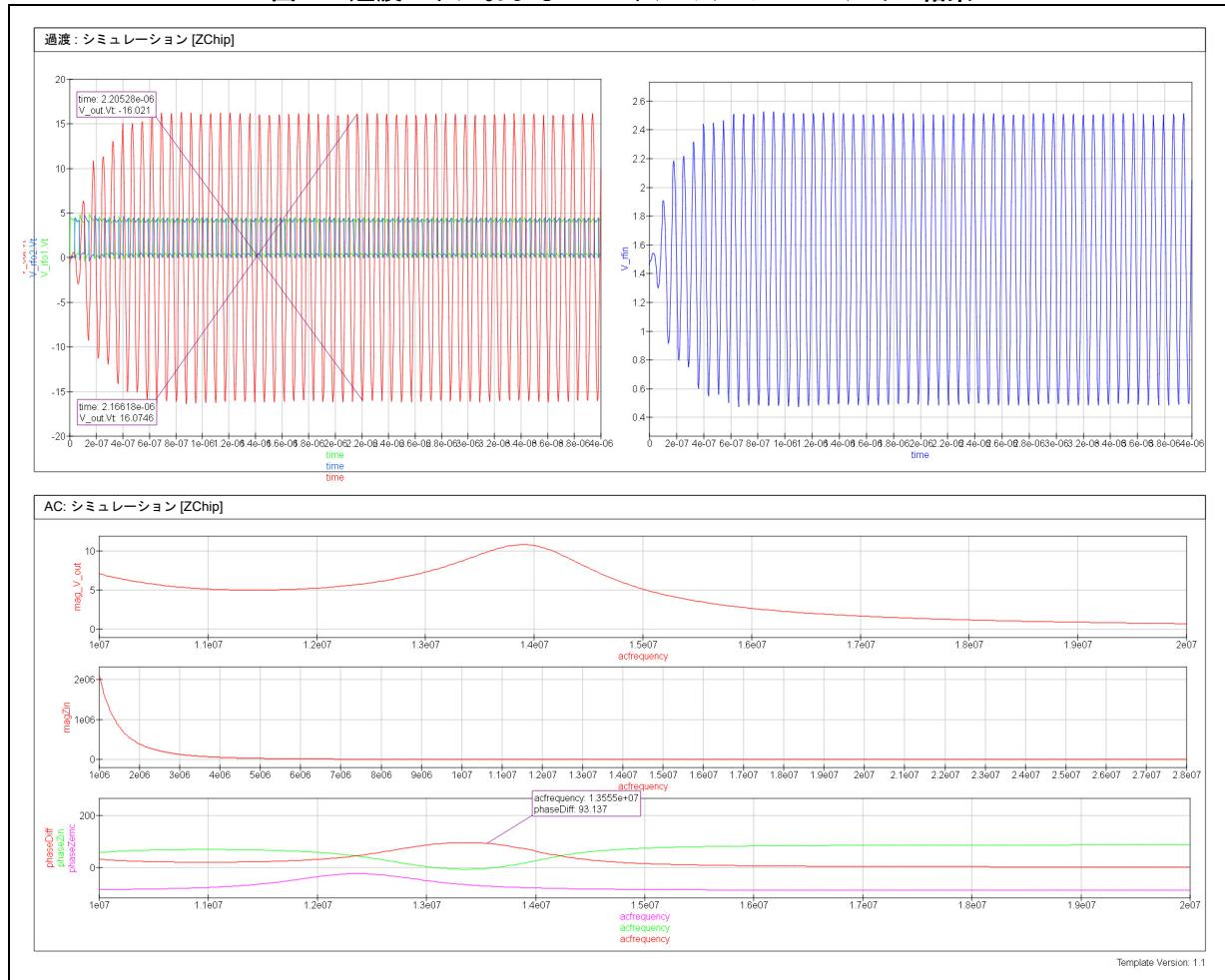

| 図 23. | 過渡シミュレーション                                  | 31 |

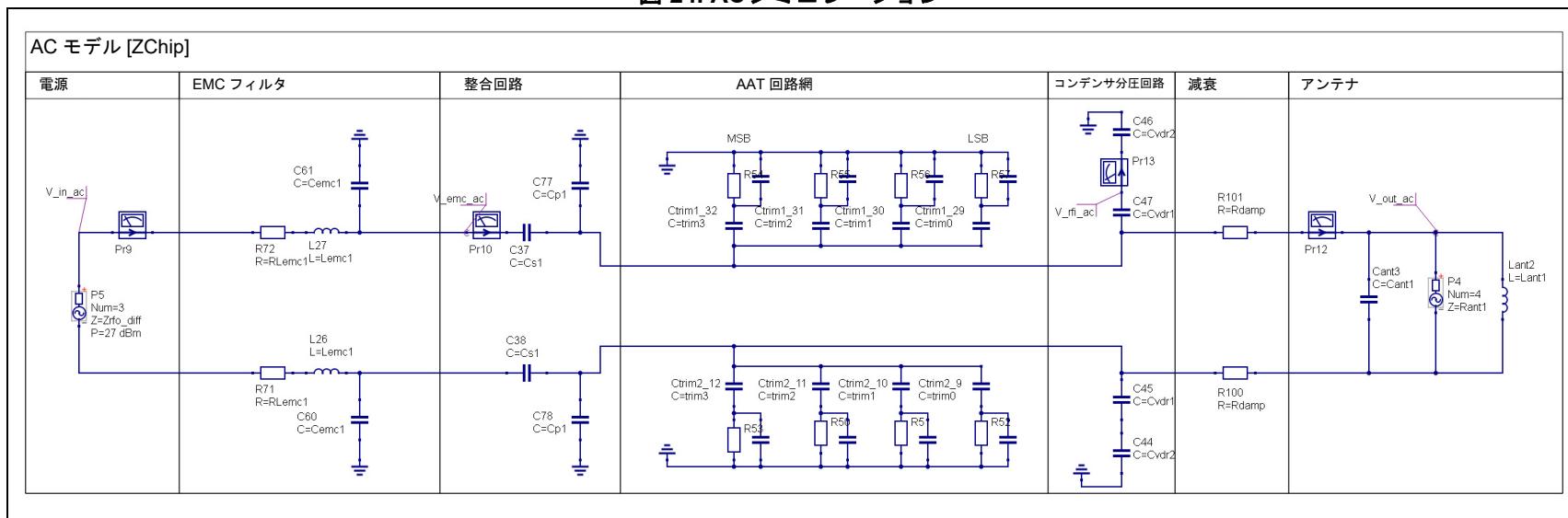

| 図 24. | AC シミュレーション                                 | 32 |

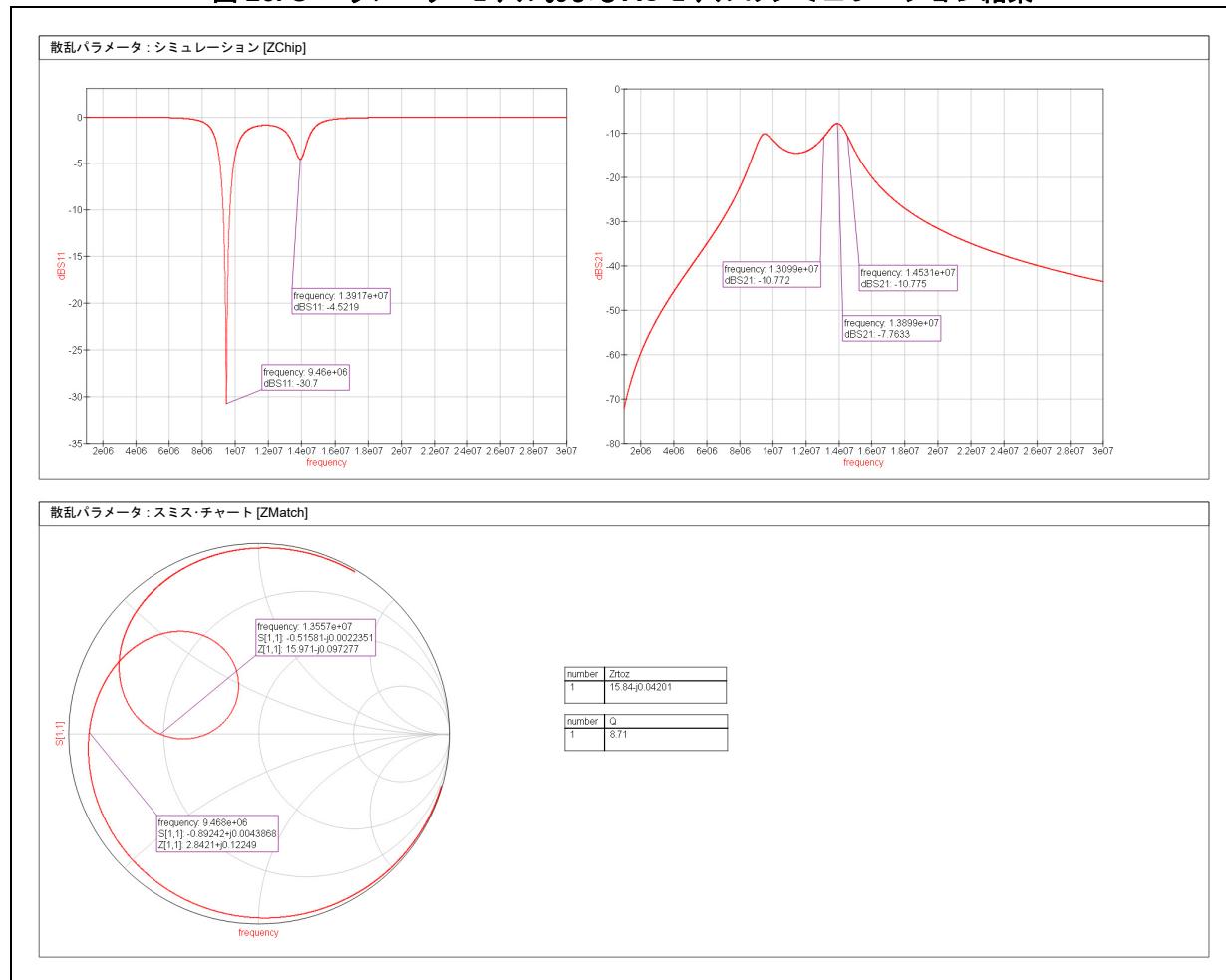

| 図 25. | S-パラメータ・モデルおよび AC モデルのシミュレーション結果            | 33 |

| 図 26. | 過渡モデルおよび AC モデルのシミュレーション結果                  | 34 |

| 図 27. | 整合回路の微調整                                    | 35 |

| 図 28. | ISO 14443 Type A の波形測定                      | 36 |

| 図 29. | ISO 14443 Type B の波形測定                      | 37 |

| 図 30. | Felica™ の波形測定                               | 37 |

| 図 31. | ネットワーク・アナライザによる Q 値の測定                      | 39 |

| 図 32. | ネットワーク・アナライザによって測定した目標整合インピーダンス             | 40 |

# 参考資料

## 1 略号と表記法一覧

### 1.1 略号

RFO1、RFO2: ST25R3916のアンテナ・ドライバ出力ピン

RFI1、RFI2: ST25R3916のレシーバ入力ピン

Tx: 送信信号（RFOからアンテナへの信号）

Rx: 受信信号（アンテナからRFIへの信号）

$L_{EMC1}$ 、 $L_{EMC2}$ : EMCフィルタのインダクタ

$C_{EMC1}$ 、 $C_{EMC2}$ : EMCフィルタのコンデンサ

$C_{S1}$ 、 $C_{S2}$ : 整合回路の直列コンデンサ

$C_P$ : 整合回路の並列コンデンサ

$R_Q$ : Q値の調整に使用する並列抵抗（計算値）

$L_{ANT}$ : アンテナのインダクタンス（測定値）

$C_{ANT}$ : アンテナの寄生並列容量（計算値）

$R_{PANT}$ : アンテナの全並列抵抗（計算値）

$f_{work}$ : NFC動作周波数（13.56 MHz）

$f_{res}$ : アンテナの自己共振周波数（測定値）

$R_{SDC}$ : アンテナの直列抵抗（測定値）

$R_{P@fres}$ : 自己共振状態におけるアンテナの並列抵抗（測定値）

$K$ : 表皮効果の補正係数（計算値）

$R_{P@work}$ : 動作周波数におけるアンテナの並列抵抗（計算値）

$R_{PDC}$ : アンテナの直列抵抗測定値から換算した並列抵抗（計算値）

$R_T$ : 目標Q値を実現するための並列抵抗（計算値）

$Q$ : アンテナのQ値（計算値）

### 1.2 数値の表記

本書では、特に指定のない限り、以下の表記法に従います。

- **2進数**は、最上位ビットMSBを左端、最下位ビットLSBを右端に記述して、0と1の文字列で表し、先頭に"0b"を付加します。例: 0b11110101

- **16進数**は、0 ~ 9の数字とA ~ Fの文字で表し、先頭に"0x"を付加します。最上位バイトMSBを左端、最下位バイトLSBを右端に記述します。例: 0xF5

- **10進数**は、先頭に文字を付加せずに記述します。例: 245

## 2 ハードウェアおよびソフトウェアの要件

ST25R antenna matching toolを使用してアンテナの測定や設計の検証を実施するには、以下のハードウェアおよびソフトウェア・リソースが必要です。

- ネットワーク・アナライザ

- オシロスコープ（パルス・トリガ機能搭載）

- SMAケーブル

- ISO 10373-6較正用コイル1

- ST25R3916-DISCOデモ・ボード

- Windows® OS

- ST25R antenna matching tool

## 3 アンテナ・インターフェース段

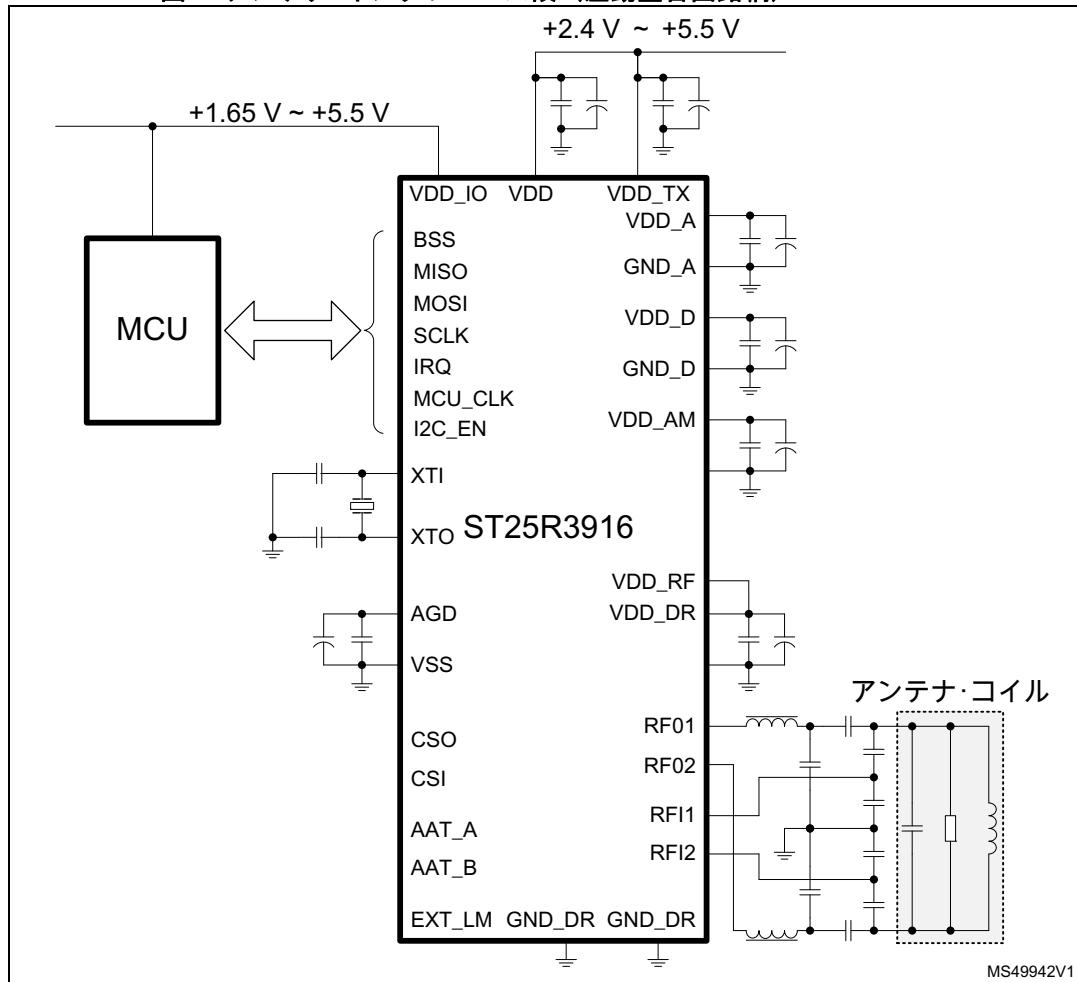

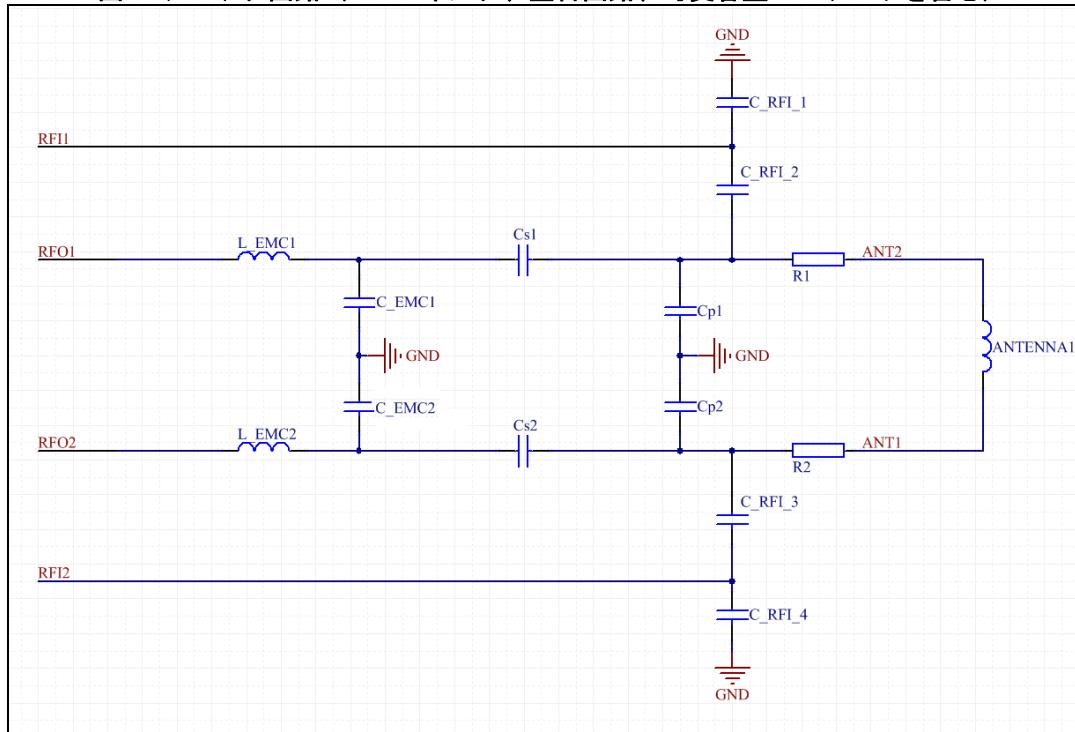

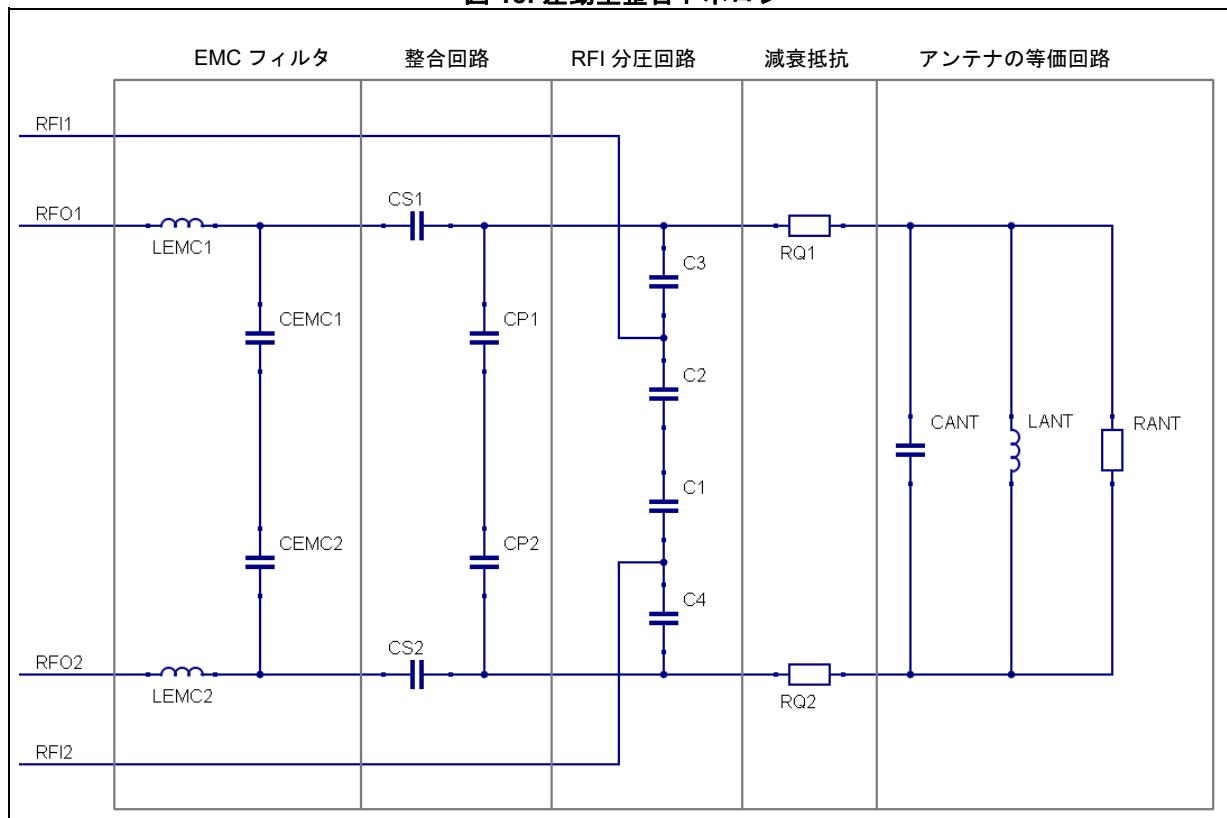

図 1に、差動整合回路を介してアンテナを駆動する最低限の構成、図 2にその回路図を示します。

TX信号は、ST25R3916のアンテナ・ドライバ出力ピンRF01とRF02から、EMC フィルタと整合回路を経由してアンテナへ出力されます。RX 信号は、アンテナからコンデンサ分圧回路を経て、ST25R3916のレシーバ入力ピンRF11とRF12に入力されます。アンテナ・インターフェース段はシングル・エンド・トポロジまたは差動トポロジで構成できますが、本稿では差動構成を中心に取り上げます。

図 1. アンテナ・インターフェース段（差動整合回路網）

# 参考資料

図 2. アンテナ回路 (EMI フィルタ、整合回路、可変容量コンデンサを含む)

## 3.1 カード・エミュレーション・モード

カード・エミュレーション・モードでは、ST25R3916デバイスをパッシブ通信モードに設定します。カード・エミュレーション・モードのトランスマッタでは、RFO1とRFO2を介してアンテナに接続する内部アンテナ・ドライバの抵抗値を変更することで負荷変調信号を生成します。したがって、リーダ・モードと同じアンテナおよび同調回路を使用できます。

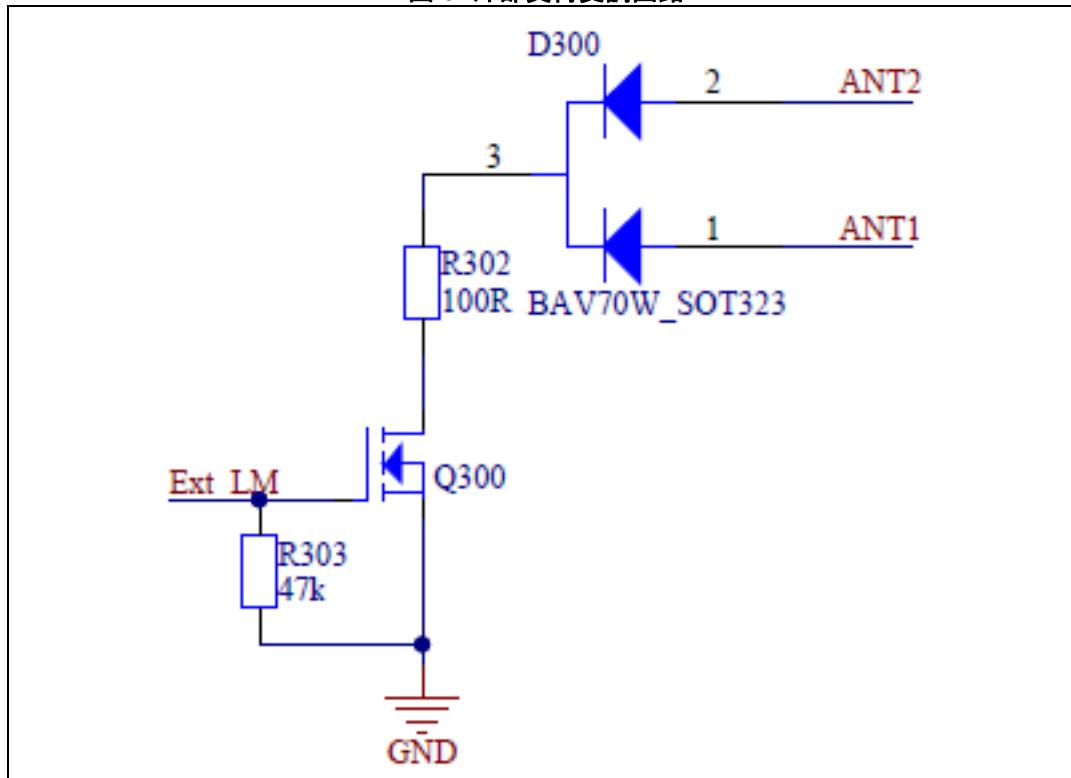

また、EXT\_LMピンを介して外付けのMOSトランジスタを駆動する機能も備え、これによって負荷変調信号を生成することもできます。この構成は、"通常"モードよりも高いパッシブ変調レベルが得られますが、部品の追加とアンテナ固有の接続が必要になります。

### 3.1.1 内部ドライバによるパッシブ負荷変調

ST25R3916で内部ドライバによるパッシブ負荷変調ができるようにするには、パッシブ・ターゲット変調レジスタ（レジスタ空間A、アドレス29h）と補助変調設定レジスタを設定する必要があります。パッシブ・ターゲット変調レジスタで、変調状態（ptm\_res）、および非変調状態（pt\_res）におけるドライバ抵抗をそれぞれ定義します。ptm\_res<3:0>をFh、pt\_res<3:0>を0hに設定することで最大変調度が得られます。非変調状態で低インピーダンス、変調状態で高インピーダンスを使用することで、極性を反転したドライバ負荷変調も可能です。

さらに、レジスタ空間Bのアドレス29hにある補助変調設定レジスタで、ドライバ負荷変調（Im\_dri）ビットを有効、外部負荷変調（Im\_ext）ビットを無効に設定する必要があります。

### 3.1.2 外部トランジスタによるパッシブ負荷変調

内部負荷変調では対応できない厳しい要件のアプリケーションでは、MOSトランジスタを使用した外部変調を使用できます。外部MOSトランジスタを使用した概念図を図3に示します。外部変調MOSのゲートをext\_Imピンで駆動します。

外部変調を有効にするには、補助変調設定レジスタのIm\_extビットを有効、Im\_driビットを無効に設定します。このように設定することで、ext\_lmピンをデジタル負荷変調信号（848 kHzの副搬送波あるいは424 kHzまたは212 kHzの変調信号）で駆動します。Im\_ext\_polを設定することで変調の極性を反転できます。

図 3. 外部負荷変調回路

## 3.2 リーダ・モードと出力電力

NFC/RFIDリーダの設計プロセスでは各種の要件を考慮する必要がありますが、重要な要件として出力電力があります。

システム全体の低消費電力化は、静電容量方式ウェイクアップや電磁誘導方式ウェイクアップなど、いくつかの方法で実現できます。これらの省電力機能の採用やポーリング周期の最適化などによって消費電力を削減するほかに、きわめて本質的な基準として、電磁界で動作している間の消費電力があります。

この消費電力は、次の3つの手順に従って調整します。

1. インピーダンス整合

2. アンテナ・ドライバの出力抵抗（レジスタ0x28）

3. チップ内蔵レギュレータ電圧

インピーダンス整合は、ST25R3916の消費電力を左右する最も重要な項目です。整合回路の設計と目標整合インピーダンスの設定では、図 4の特性に注目する必要があります。この図から、目標整合インピーダンスが大きいほど、アンテナに伝送される電力が少なくなり、リーダ装置全体の消費電力も少なくなることがわかります。

# 参考資料

出力電力調整の最後の要点は、ドライバ段の電源電圧です。ドライバの電源電圧 $V_{DD\_RF}$ は、 $V_{DD}$ からレギュレータのドロップアウト電圧を差し引いた値に自動的に設定できます。これが動作およびノイズ除去の面から最適な値です。レギュレータの設定を手動で上書きして、 $V_{DD\_TX}$ をデータシート規定の値に設定することも可能です。

図 4 のスミス・チャートに、リーダ・モード設計の第一ステップである、インピーダンス整合の推奨特性を示します。図 5 に示すように、Q 値を低く抑えることで、アンテナ・システムは各種リーダ・モード技術で使用する基本的なビット・レートや、より高いビット・レートに対応できます。それ以降の手順で、ユーザ要件に適合した整合インピーダンスと Q 値とすることが必要な場合もあります。

図 4. 推奨整合インピーダンス

図 5. Q値

### 3.3 EMC フィルタ

直列インダクタと並列コンデンサから成る1段のロー・パス・フィルタでEMCフィルタを構成しています。EMCフィルタの目的は、プッシュプル・ドライバの矩形波出力信号によって発生する高次の高調波を除去することです。このフィルタの遮断周波数は8 MHz ~ 17 MHzに設定すべきですが、実際の値はアプリケーションや要求される動作によって異なります。

リーダ・ボードのEMC特性を最適化するには、次に挙げる点を検討する必要があります。

- フィルタ・コイル:

- インダクタンスの自己共振周波数: 測定する周波数範囲で不要輻射が増加する可能性があります。

- 等価直列抵抗 (ESR): リーダの総合的なQ値の低下や伝導出力電力の減少の原因となることが考えられます。ESRが高い ( $> 1\Omega$ ) EMCインダクタを使用できるのは、中電力および低電力の整合に限られます。ESRは、RFO出力抵抗と直列に接続された状態になります。したがって、ESRが大きいと総合的なQ値が低下し、EMCインダクタによる電力損失が増加します。

- 整合回路の電流よりも定格電流が大きいフィルタ・コイルを選択する必要があります。

- フィルタの遮断周波数（フィルタの共振周波数）:

- フィルタの遮断周波数が搬送波周波数 (13.56 MHz) に近すぎると、総合的なQ値が著しく低下します。その原因は、アンテナとフィルタのQ値の組み合わせにあります。このことから、EMCフィルタの遮断周波数が13 MHz ~ 14 MHzの範囲にないことが必要です。

- アンテナ設計

- 回路の配線長を極力短くして、不要輻射が増加する原因となる余分な自己共振の発生を防止する必要があります。

## 3.4 整合回路

EMC フィルタの後には、Lトポロジの整合回路が続きます。この整合回路は、1個の直列コンデンサと2個の並列コンデンサから成る差動トポロジで構成されています。

整合回路の目的は、アンテナのインピーダンスが所望の値に整合するようにして、アプリケーションに応じ、ST25R3916からアンテナへの伝送電力を最大にする、もしくは、所望の消費電流を達成することにあります。

[図 2](#)に、アンテナ・インターフェース段を示します。

## 3.5 コンデンサ分圧回路

高いアンテナ電圧が発生する可能性があることから、受信経路のアンテナ端子部分にコンデンサ分圧回路を設け、RFIピンの入力信号の強度を制限する必要があります。この分圧回路はアンテナに接続され、2つのコンデンサで構成されます。

[図 2](#)では、RFI\_1とRFI\_2、RFI\_3とRFI\_4でそれぞれコンデンサ分圧回路を構成しています。

受信ピンの電圧は、3 V<sub>PP</sub>を超えないことが必要です。HFリーダ・モードとNFC送信モードの推奨信号レベルは2.8 V<sub>pp</sub>です。

## 3.6 アンテナ

HFリーダのアンテナには磁気ループ・アンテナが採用されています。通常はプリント・コイルで実現していますが、フレキシブルPCB、巻線アンテナ、金属筐体を使用する方法もあります。

寸法、導体パターンのループ数、パターンの幅と間隔などの要因によってアンテナの電気的パラメータが決まります。このパラメータとして、インダクタンス、直列抵抗と並列抵抗、自己共振周波数のほか、最も重要なパラメータであるQ値があります。

アンテナのQ値は、システム全体で目標とするQ値よりも大きくなるように設計する必要があります。システム全体のQ値は、アンテナに続く減衰抵抗によって低下することはあるが、アンテナ自体のQ値よりも高くなることはないからです。

## 4 アンテナ・パラメータ

どのようなアンテナにも、インダクタンス、抵抗、静電容量があります。まず、これらの値とアンテナの自己共振周波数を決定してアンテナの等価回路とそのQ値を計算したうえで、整合回路部品の回路定数を決定する必要があります。

### 4.1 ネットワーク・アナライザの準備

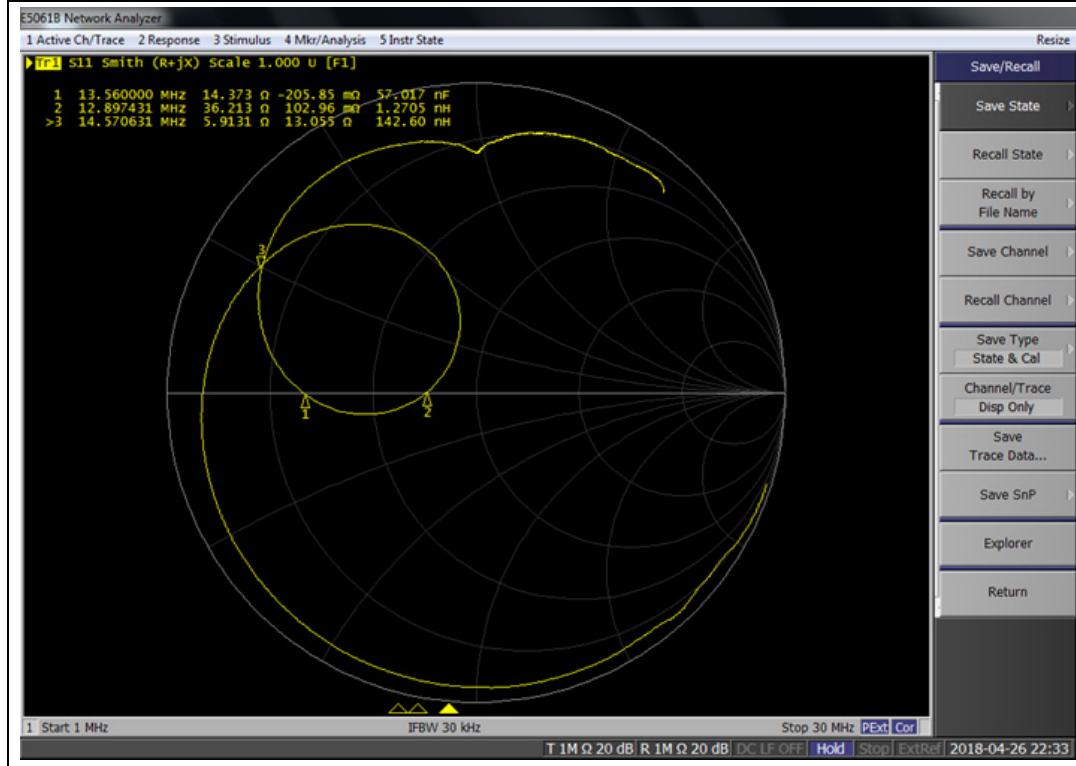

アンテナ・パラメータを測定するには、ネットワーク・アナライザ（インピーダンス・アナライザ）を使用する必要があります。以下に詳しく述べる手順に従ってネットワーク・アナライザを設定します。

1. ネットワーク・アナライザの測定モードをS11の反射特性測定に設定します。

2. インピーダンス曲線を表示するために、スマス・チャート ( $R + jX$ ) を使用します。

3. 測定開始周波数を1 MHz、測定終了周波数を300 MHzに設定します。

注：一部のアンテナ・パラメータは、1 MHzで測定します。

これは、アンテナの自己共振周波数とはかけ離れていますが、高周波領域での表皮効果を最小限に抑えるためです。測定終了周波数は、リーダ・アンテナの最も低い自己共振周波数（通常は50 MHz ~ 250 MHz）よりも高く設定する必要があります。

4. 正確な測定値が確実に得られるように、ネットワーク・アナライザの分解能（測定ポイント数）を最大に設定する必要があります。

5. 短いSMAケーブル（50 cm未満）をネットワーク・アナライザのRFポートに接続し、較正キットでOPEN、SHORT、LOADを使用して較正を開始するか、自動較正を実行します。較正キットを使用できない場合は、ケーブルに $50\Omega$ の負荷抵抗を接続した状態（LOAD）、ケーブルを開放した状態（OPEN）、およびケーブルを短絡した状態（SHORT）を代替手段として使用します。この較正ではSMAケーブル長も考慮されます。

6. SMAケーブルを測定対象のアンテナに接続するために、ピンとのプローブ接続を構成する必要があります。一方のピンをSMAコネクタの信号端子にはんだ付けし、もう一方のピンをSMAコネクタのグラウンド部分にはんだ付けします。

7. ベクトル・ネットワーク・アナライザ（VNA）の自動ポート延長機能を使用すると、上記以外のピンも較正で考慮できます。

### 4.2 パラメータ測定

1. VNAのケーブルをアンテナ端に接続します。アンテナをリーダと整合回路から切り離し、リーダの電源をオフにする必要があります。通電状態のリーダをVNAに接続すると、VNAを破損する恐れがあります。

2. 図 6に示すように、スマス・チャートに1 MHz ~ 300 MHzのインピーダンス曲線が表示されます。

3. マーカーを1 MHzに合わせると、次に挙げる直列インダクタンスとDC直列抵抗の値を読み取ることができます（図 6では、ネットワーク・アナライザ画面上部に表示されています）。

- $L_{ANT} = 926 \text{ nH}$

- $R_{SDC} = 394 \text{ m}\Omega$

4. 別のマーカーをスマス・チャートの実数軸上に合わせます。この点で、インピーダンスの誘導性成分と容量性成分が相殺されます。この点で、アンテナの並列抵抗と自己共振周波数が次のように測定できます。

- $R_{P@fres} = 1.55 \text{ k}\Omega$

- $f_{res} = 62.67 \text{ MHz}$

図 6.1 MHzおよびSRF (62.67 MHz) におけるアンテナ・パラメータの測定

アンテナ・パラメータの測定値が得られたので、等価回路を決定できます。その手順を[セクション 4.3](#)で説明します。

## 4.3 アンテナの等価回路

1 MHzで測定したアンテナのインダクタンスに基づいて、自己共振周波数における寄生容量を次のように計算できます。

$$C_{\text{ANT}} = 1 / (\omega^2 \times L) = 1 / [(2\pi \times f_{\text{res}})^2 \times L_{\text{ANT}}] = 1 / [(2\pi \times 62.7 \text{ MHz})^2 \times 926 \text{ nH}] = 6.96 \text{ pF}$$

並列抵抗の測定値を、自己共振周波数における値から動作周波数 ( $f_{\text{work}} = 13.56 \text{ MHz}$ ) における値に変換する必要があります。この変換が必要となる理由は、表皮効果に起因する抵抗値の周波数依存性を補正することにあります。自己共振周波数における並列抵抗を変換するには、次式で補正係数を計算する必要があります。

$$K = \sqrt{\frac{f_{\text{res}}}{f_{\text{work}}}} = \sqrt{\frac{62.7 \text{ MHz}}{13.56 \text{ MHz}}} = 2.15$$

動作周波数における並列抵抗は次式で計算できます。

$$R_{P@f\text{work}} = K \times R_{P@\text{fres}} = 2.15 \times 1.55 \text{ kΩ} = 3.33 \text{ kΩ}$$

アンテナの構成要素をすべて把握したので、等価回路を決定できます（[図 7](#)参照）。

# 参考資料

図 7. アンテナの等価回路

次式により、動作周波数における直列抵抗を並列抵抗（図 8参照）に換算することで、等価回路を簡素化できます。

$$Q = \frac{\omega L_{ANT}}{R_{SDC}} \approx \frac{R_{PDC}}{\omega L_{ANT}} \Rightarrow R_{PDC} = \frac{(2 \cdot \pi \cdot f_{res} \cdot L_{ANT})^2}{R_{SDC}} = \frac{(2 \cdot \pi \cdot 13,56\text{MHz} \cdot 926\text{nH})^2}{394\text{m}\Omega} = 15.9\text{k}\Omega$$

これによって、インダクタのDC直列抵抗（上式で並列抵抗に換算した抵抗）と動作周波数における並列抵抗のみを並列接続した抵抗値として、アンテナ等価回路全体の抵抗を表すことができます。

これら2つの並列抵抗から、次式のように合計の並列抵抗が得られます。

$$R_{PANT} = \frac{R_{PDC} \cdot R_{P@fwork}}{R_{PDC} + R_{P@fwork}} = \frac{15.9\Omega \cdot 3.33\text{k}\Omega}{15.9\text{k}\Omega + 3.33\text{k}\Omega} = 2.76\text{k}\Omega$$

図 8. アンテナの等価回路（最終的な回路）

簡素化した最終的なアンテナ等価共振回路の回路定数は次のとおりです。

- $R_{PANT} = 2.76\text{k}\Omega$

- $C_{ANT} = 6.96\text{pF}$

- $L_{ANT} = 926\text{nH}$

ここから、このアンテナで実現可能な最大のQ値を次のように計算できます。

$$Q = R_{PANT} / (\omega \cdot L_{ANT}) = 2.76\text{k}\Omega / (2\pi \times 13.56\text{MHz} \times 926\text{nH}) = 34.8$$

これは、アンテナ単体として有効なQ値です。

Q値は、変調信号の立ち上がり時間と立ち下がり時間に直接影響します。

図 9と表 1は、100%のASKで変調したデータ・レート106 Kb/s ( $f_{work}/128$ ) のType-A信号について、立ち上がり時間と立ち下がり時間の定義を示しています。図 10は、これらの時間がQ値によって変化する例を示しています。

# 参考資料

図 9. 106 Kb/s の Type-A 信号におけるタイミング・パラメータの定義

# 参考資料

表 1. 106 Kb/sのType-A信号のタイミング・パラメータ

| パラメータ | 条件                | 最小値       | 最大値        |

|-------|-------------------|-----------|------------|

| $t_1$ | -                 | $6/f_c$   | $40.5/f_c$ |

| $t_2$ | $t_1 > 34/f_c$    | $7/f_c$   | $t_1$      |

|       | $t_1 \leq 34/f_c$ | $10/f_c$  |            |

| $t_3$ | -                 | $1.5 t_4$ | $16/f_c$   |

| $t_4$ | -                 | 0         | $6/f_c$    |

図 10. Q値によるタイミング・パラメータの変化

Q値の最大許容値は、プロトコル（Type-A、Type-B）およびデータ・レートごとに決定できます。ISO 波形に準拠した変調信号を得るには、Q値がこの最大許容値を超えないことが必要です。

データ・レート106 Kb/sのType-A信号の場合、最大許容Q値は、帯域幅と時間の積およびQ値の定義に基づいて、次の式で計算できます。

$$B \times T \geq 1, Q = f_{\text{work}} / B \rightarrow Q \leq f_{\text{work}} \times T \rightarrow Q \leq 13.56 \text{ MHz} \times 3 \mu\text{s} = 41$$

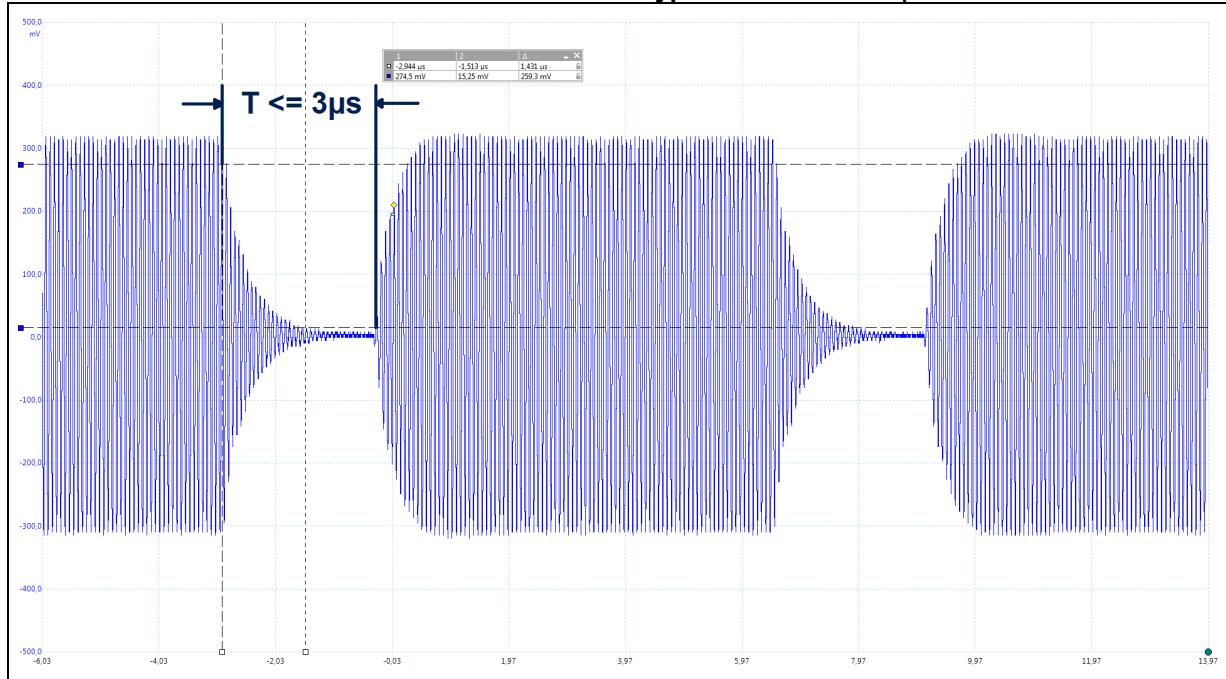

この計算で、図 11に示す時間Tは、ISO 14443に準拠するためにタイミング・パラメータ $t_1$ に許容できる最大値です。

# 参考資料

図 11. データ・レート 106 Kb/s の Type-A 信号における  $t_1$  の定義

106 Kb/s の Type-A 信号で、規格に準拠した立ち上がり時間と立ち下がり時間を実現するには、アプリケーションの Q 値を 41 未満とする必要があります。

したがって、先ほど計算した Q 値は大きすぎるので、小さくする必要があります。そのためには、アンテナ・ピンに並列抵抗 ( $R_Q$ ) を外付けします。この抵抗の値は、目標とする Q 値によって決まり、次式で求めます。目標とする Q 値を 8 とします。

$$R_T = Q \times \omega \times L_{ANT} = 8 \times 2 \pi \times 13.56 \text{ MHz} \times 926 \text{ nH} = 631 \Omega$$

アンテナ等価回路の寄生抵抗  $R_{PANT}$  を考慮すると、Q 値を 8 に調整する実効的な抵抗値  $R_Q$  は、次式で得られます。

$$R_Q = (R_{PANT} \times R_T) / (R_{PANT} - R_T) = (2.76 \text{ k}\Omega \times 631 \Omega) / (2.76 \text{ k}\Omega - 631 \Omega) = 818 \Omega$$

入手できる抵抗値で最も近い値は 820 Ω です。

ここで説明した、アンテナの等価回路および Q 値調整のための抵抗を決定する方法は、ST25R antenna matching tool の理論的な基盤です。

## 5 アンテナ設計

### 5.1 境界条件とシミュレーション・モデル

近接リーダ・システムを設計するには、エンド・ユーザ・アプリケーションについての情報が必要です。この情報として、リーダを設置する環境の条件や使用するカードの種類などがあります。

いくつかの基本的な境界条件をあらかじめ検討しておく必要があります。特に以下の条件が重要です。

- 目標とする読み取り距離

- タグ/カードの種類

- 出力電力

- EMC規制

- 工業デザイン

- アンテナの配置

- 環境の影響

- 対応するNFC技術と規格、およびデータ・レート

アンテナの設計は、アプリケーションの工業デザインに適している必要があり、磁気ループの配置に必ずしも十分な自由度があるとは限りません。最も望ましいアンテナ位置は、放射する実効RF電界に影響する電子回路などの構成要素から遠く離れた場所です。このような構成要素として、バッテリ、ディスプレイ、大きなグランド・プレーンなどがあります。

アンテナ設計の指針を示すために、3種類の寸法（具体的な寸法は挙げていません）のアンテナをシミュレーションしています。3つのアンテナは、いずれも厚さ1.5 mmのFR4基板上に、厚さ35 µmの銅箔パターンを使用して、どこでもループが2つになるように構成されています。

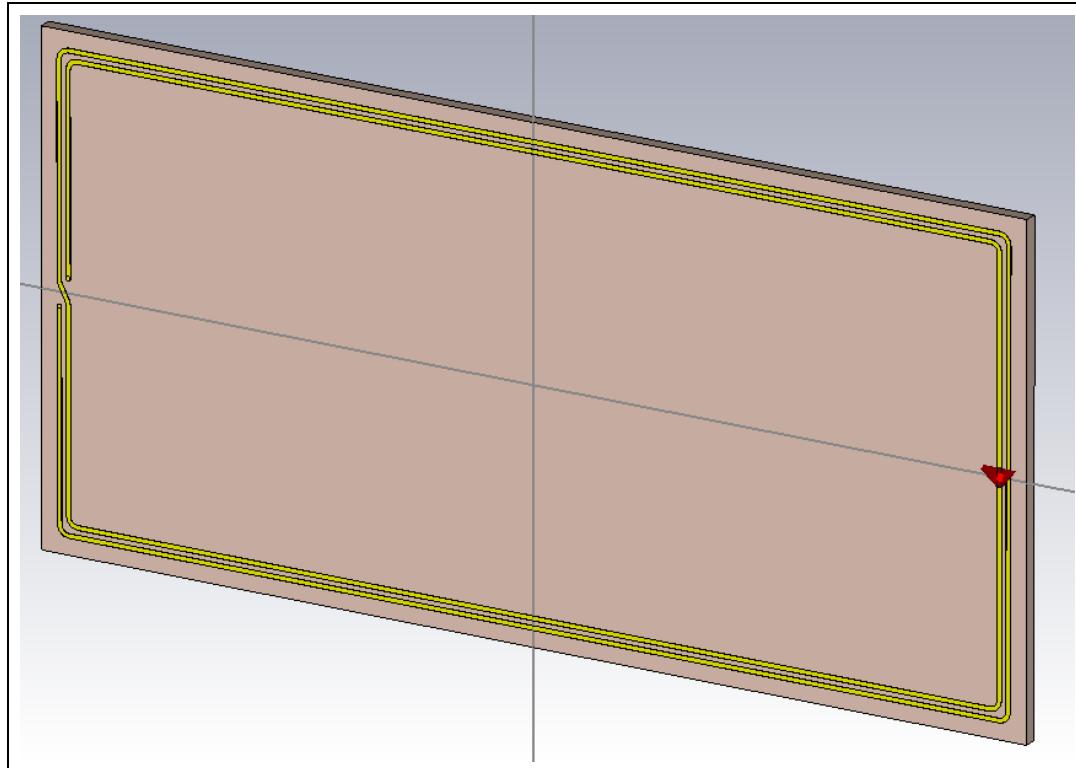

図 12に、最も寸法が大きいアンテナのEMシミュレーション・モデルを示します。このシミュレーションは、周波数ドメインで実行しています。

図 12. コイル・アンテナのシミュレーション・モデル

アンテナのQ値をはじめとする各種パラメータがアンテナ形状でどのように変化するか確認するためには、シミュレーションではパターン幅、パターン間隔、アンテナ寸法を変更しています。

## 5.2 シミュレーション結果

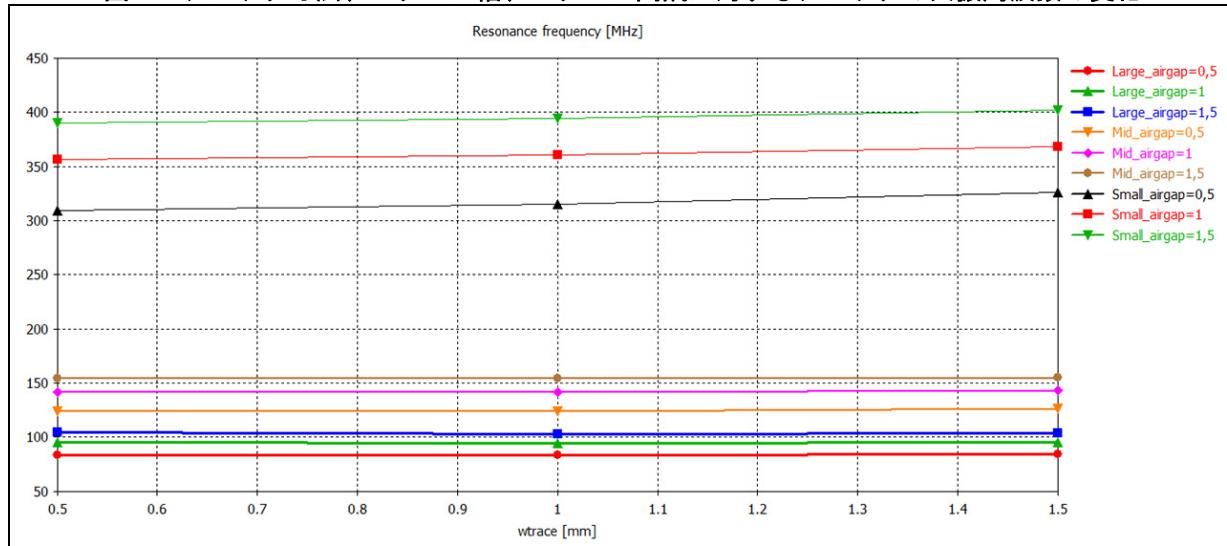

図 13、図 14、図 15、図 16、図 17に、アンテナの主な電気的パラメータを、アンテナ寸法、パターン幅、パターン間隔の関数として示します。表 2は、パラメータの挙動をまとめた表です。

Q値もアンテナ寸法に依存しますが、その関係は複雑であるため、より詳細な解析が必要です。インダクタンス、直列DC抵抗、並列抵抗、自己共振周波数など、その他のアンテナ・パラメータによってもQ値が変化します。

並列共振回路のQ値は、次式で与えられます。

$$Q = R_{PANT} / (2 \pi f_{carrier} L)$$

ここで、

- $R_{PANT}$ は、総合並列抵抗です。詳細は、セクション 4.3を参照してください。

- $L$ はアンテナのインダクタンスです。

- $f_{carrier}$ は、搬送波周波数です。

共振周波数は、アンテナの電気的長さに依存します。電気的長さが短いほど、共振周波数は高くなります。

# 参考資料

図 13. アンテナ寸法、パターン幅、パターン間隔に対するアンテナのQ値の変化

図 14. アンテナ寸法、パターン幅、パターン間隔に対するアンテナのインダクタンスの変化

# 参考資料

図 15. アンテナ寸法、パターン幅、パターン間隔に対するアンテナの直列DC抵抗の変化

図 16. アンテナ寸法、パターン幅、パターン間隔に対するアンテナの並列抵抗の変化

# 参考資料

図 17. アンテナ寸法、パターン幅、パターン間隔に対するアンテナの共振周波数の変化

表 2. 形状パラメータの変化に対するアンテナ・パラメータの挙動

| パラメータ   | 変化        | パラメータへの影響 | Q値 |

|---------|-----------|-----------|----|

| Q値      | パターン幅の増加  | -         | 増加 |

|         | パターン間隔の増加 |           |    |

| インダクタンス | アンテナ寸法の増加 | 増加        | 減少 |

|         | パターン幅の減少  |           |    |

|         | パターン間隔の減少 |           |    |

| 直列DC抵抗  | アンテナ寸法の増加 | 増加        | 減少 |

|         | パターン幅の減少  |           |    |

|         | パターン間隔の減少 |           |    |

| 並列抵抗    | パターン幅の減少  | 増加        | 増加 |

|         | パターン間隔の増加 |           |    |

| 共振周波数   | アンテナ寸法の減少 | 増加        | 増加 |

|         | パターン間隔の増加 |           |    |

注：この表では、アンテナ・パラメータの基本的な挙動を理解するために、各パラメータを単独で変更した場合に見られる理論上の挙動を示しています。実際には、すべてのパラメータが相互に関連しています。たとえば、アンテナ寸法を大きくすると（Q値が低下する効果）、インダクタンスが大きくなり、電気的長さが長くなります。その結果、共振周波数が低下し（Q値が高くなる効果）、直列DC抵抗は増加します（Q値が低下する効果）。

磁気ループ・アンテナのインダクタンスは、導体の電気的長さで決まります。信号の伝搬経路が長く（電気的長さが長い）、導体が薄いほど、コイルのインダクタンスは増加します。一方、伝搬経路が太く短くなるほど、静電容量性の挙動が目立ってきます。このように、ループ・アンテナのインダクタンスは、パターンの厚み、パターン間隔、アンテナ寸法によって変えることができます。

# 参考資料

NFCリーダ・アプリケーションのループ・アンテナ設計で目標とすべきインダクタンス推奨値は200 nH ~ 1500 nHです。アプリケーションによっては、これより大きなインダクタンス値を選択して、チップ側で対応することができます。

インダクタンスの変化に直接関係する要因はループ・アンテナの直列抵抗です。この抵抗は、アンテナのパターンがより長く、薄くなるほど大きくなります。アンテナの自己共振周波数は、アンテナのパターン間隔が広くなるほど、またアンテナ寸法が小さくなるほど増加する傾向にあります。

[セクション 5](#)で指摘したように、アンテナのQ値は、アプリケーションに必要とされるQ値よりも高い値を目標に設計する必要があります。Q値は、アンテナに接続した減衰抵抗によって低くすることはできるものの、アンテナを再設計しない限り、アンテナの設計値より高くすることはできないからです。

## 6 アンテナの整合

図 18に、EMC フィルタ、整合回路、RFI 分圧回路で構成し、差動トポロジとしたアンテナのインターフェース段全体を示します。Q値を調整する抵抗およびアンテナ等価回路も共に示しています。

EMC フィルタは、直列インダクタとグランドに接続した並列コンデンサから成る1段のフィルタ回路です。整合回路は、直列コンデンサと並列コンデンサで構成しますが、このトポロジで使用している並列部品は1つのみです。Q値調整のための抵抗は直列抵抗です。アンテナは、インダクタ、抵抗、コンデンサの並列回路による等価回路として示しています。受信経路の分圧回路はコンデンサによるもので、アンテナ・ピンに直接接続されています。

図 18. 差動型整合トポロジ

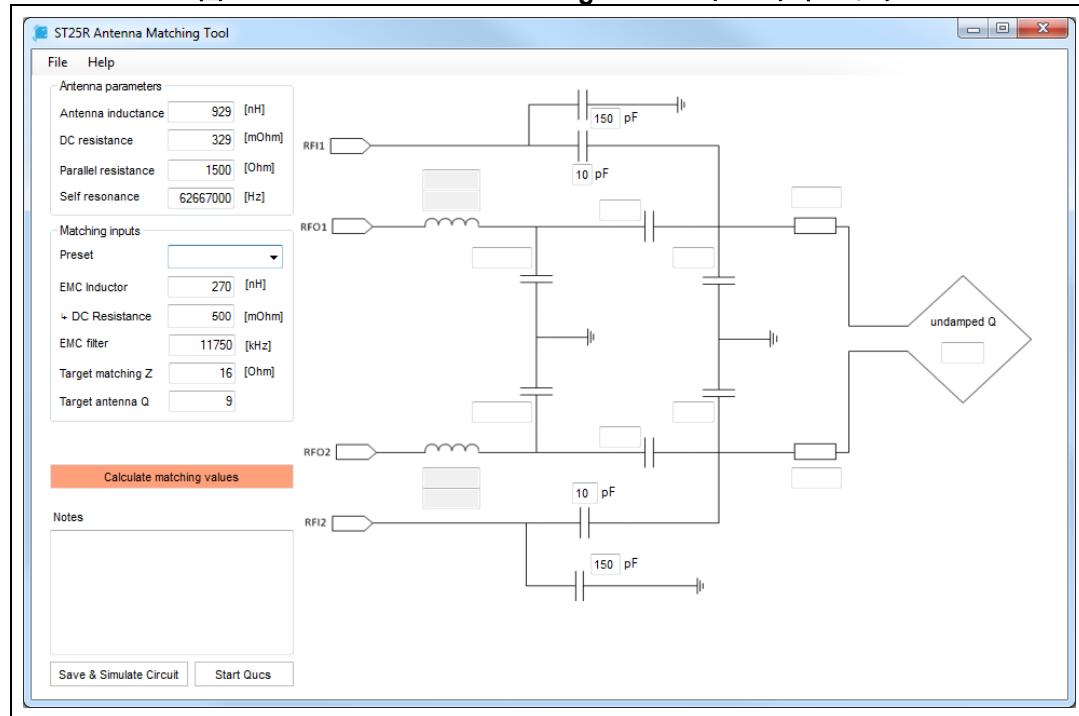

### 6.1 整合ツール

STマイクロエレクトロニクスのST25R antenna matching toolは、電気的パラメータの測定が完了したアンテナの整合を判断する、使いやすいツールです。このツールは、直感的なGUIを備え、回路定数を求めるプロセスを容易にしています。さらに、このGUIから、回路シミュレータ・プログラムであるQUCSを直接起動できます。QUCSシミュレーション・ツールを使用すると、AC、S-パラメータ、過渡現象の各シミュレーションを通して回路定数を検証できます。

QUCSはST25R antenna matching toolのインストーラに組み込まれたものを利用するほか、<http://sourceforge.net>からも無償でダウンロードできます（その場合は、ST25R antenna matching toolに組み込まれたものと同じバージョン0.0.18の使用を推奨します）。インストール先のパスとして、Windowsのデフォルトのディレクトリではなく、C:\Tools\Qucsなどを使用してください。整合ツー

# 参考資料

ルを起動するには、[www.st.com](http://www.st.com)から実行可能ファイル（STSW-ST25R004）をダウンロードします。表示されるメイン・ウィンドウを図 19に示します。

作業のフローは次の5つの基本的手順で構成され、画面の上から下へ進みます。

- 1 MHzで測定したアンテナの入力パラメータとSRFを入力します。

- 事前設定条件を選択するか、独自の条件を設定します。

- EMCフィルタのコイルのインダクタンスとDC抵抗を設定します。

- 目標整合インピーダンスおよび目標Q値を入力します。

- 計算を実行し、得られた値でシミュレーションを実行します。

図 19. ST25R antenna matching tool - メイン・ウィンドウ

図 19では、1番目の手順は既に完了しています。各入力パラメータ・フィールドには、セクション 4.2 で説明したアンテナ・パラメータの値が入力済みです。

事前設定条件のタブで、EMCフィルタに必要とする遮断周波数、目標整合インピーダンス、アンテナの目標Q値を入力します。3種類の事前設定条件が用意されています。アプリケーションに応じて、これらのいずれかを選択するか、独自の条件を設定します。

3番目の手順では、EMCフィルタのインダクタンス値を選択します。

EMCフィルタで選択する周波数とインダクタンスは互いに依存関係にあるので、相互の調整が必要になる場合があります。これら2つの入力に基づいて、EMCフィルタのコンデンサの容量値が計算されます。選択したEMCのインダクタに応じて、その適切なDC抵抗を入力する必要があります。この値はインダクタのデータシートに記載されています。計算後、アンテナのQ値が回路図領域に表示されます。目標Q値が、計算されたQ値よりも大きい場合は、負の減衰抵抗値が表示されます。

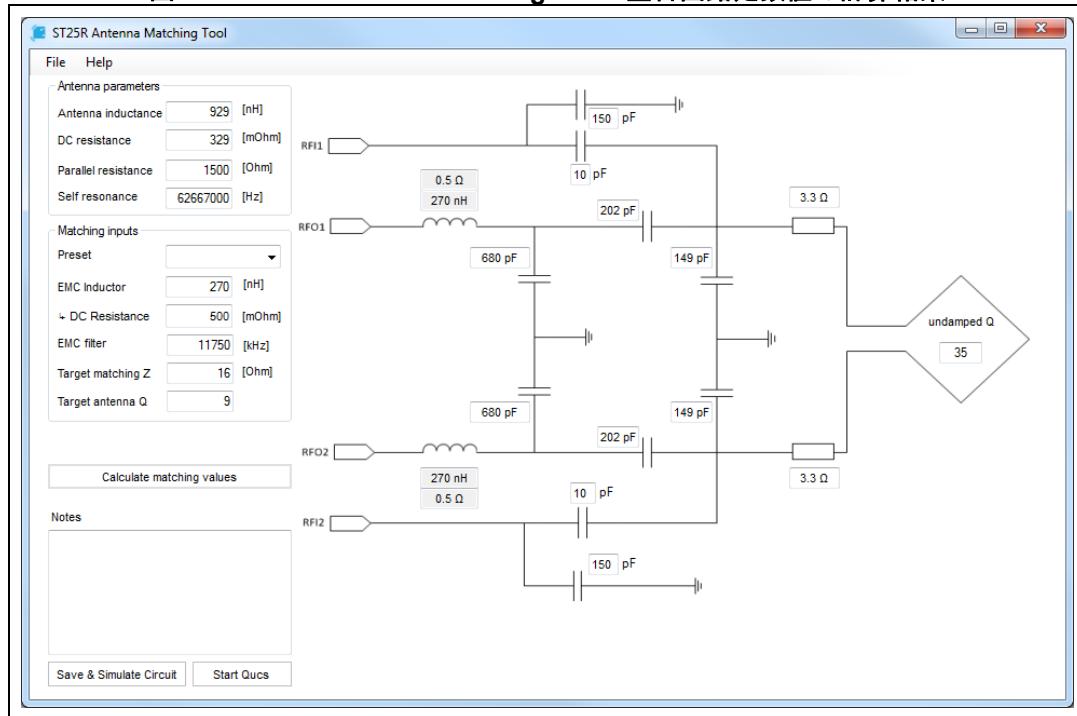

計算ボタンをクリックすると、すべての部品の値が計算され、回路図領域に表示されます（図 20）。

図 20. ST25R antenna matching tool - 整合回路定数値の計算結果

コンデンサのESRのような寄生要因の値や特殊な部品パラメータは考慮されていません。

すべての値が計算されたら、その結果を使用してシミュレーションを実行できます。"Simulate Circuit"をクリックすると、回路図ファイルを保存するかどうかの確認を求める保存ダイアログが表示されます。データの保存場所を（読み取りと書き込みの権限に応じて）慎重に選択します。推薦される保存場所は次のとおりです。

```

%userprofile%\.qucs\$PROJECT_prj (PROJECT = プロジェクト名,

_prj = 接尾辞 "QUCS")

```

シミュレーションを継続するために回路図ファイルの読み込みが必要な場合は、"Start Qucs"ボタンをクリックしてQUCSを起動します。前述の保存場所にファイルを保存していれば、そのファイルが自動的に検出され、プロジェクト・パネルに表示されます。

## 6.2 シミュレーション

回路図ファイルを適切に保存していれば、"Simulate Circuit"ボタンでQUCSを起動すると、保存した回路図が自動的に読み込まれます。自動的に読み込まれない場合は、回路図を開くダイアログを使用して読み込みます。

回路図ファイルに基づいて、シミュレーションの計算およびその結果を表示するファイルが設定されます。ST25R antenna matching toolによって事前に計算した値がQUCS回路図テンプレートに自動的に挿入され、保存作業の間、表示されています。

部品の値とシミュレーションのパラメータがシート上部に表示されます。ここにはファイルの表示に必要な数式も示されます。回路定数を変更する場合は、必ず"Component-Values"のセクションで変更するようにして、シミュレーション・モデル自体は変更しないことを強く推奨します。図 21に、アンテナ・パラメータを示します。ST25R antenna matching toolによって事前に計算した値にきわめて近い値が表示されています。

# 参考資料

図 21. シミュレーション・パラメータ

| Simulations                                                                                                                         | Antenna - Trim                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>AC-Simulation</b><br>Type=lin<br>Start=1 MHz<br>Stop=28 MHz<br>Points=1001<br>Noise=no                                           | <b>Gleichung</b><br>Eqn10<br>trm3=56 p<br>trm2=27 p<br>trm1=12 p<br>trm0=5.6 p                                                                                                         |

| <b>Transientsimulation</b><br>TR1<br>Type=lin<br>Start=0<br>Stop=4 us<br>Points=1024                                                | <b>Gleichung</b><br>Eqn9<br>Ctrmpara3=1.5 p<br>Ctrmpara2=1.5 p<br>Ctrmpara1=1.5 p<br>Ctrmpara0=1.5 p                                                                                   |

| <b>S-Parameter Simulation</b><br>SP1<br>Type=lin<br>Start=1 MHz<br>Stop=30 MHz<br>Points=1001                                       | <b>Gleichung</b><br>Eqn8<br>Rontrim3=5e5<br>Rontrim2=5e5<br>Rontrim1=5e5<br>Rontrim0=5e5                                                                                               |

| <b>Component- Values</b>                                                                                                            | <b>Capacitive Voltage Divider</b>                                                                                                                                                      |

| <b>Gleichung</b><br>Eqn17<br>Zmatch=50<br>Zrf0=1<br>AnalogSupplyVoltage=5<br>Zrf0_diff=Zrf0+Zrf0<br>Vsp_RF=AnalogSupplyVoltage-0.25 | <b>Gleichung</b><br>Eqn2<br>V_rf1=V_rf1_Vt + 1.5                                                                                                                                       |

| <b>Gleichung</b><br>Eqn20<br>Lemc1=270 n<br>RLemc1=0.5<br>Cemc1=680 p                                                               | <b>Impedance Calculation</b>                                                                                                                                                           |

| <b>Gleichung</b><br>Eqn22<br>Cs1=302 p<br>Cp1=149 p<br>Cpd2=150 p                                                                   | <b>Gleichung</b><br>Eqn1<br>Zrtoz=value(rtoz(S[1,1],P1,Z),13560000)                                                                                                                    |

| <b>Gleichung</b><br>Eqn18<br>Qdr1=10 p<br>Qdr2=150 p                                                                                |                                                                                                                                                                                        |

| <b>Gleichung</b><br>Eqn23<br>Cant1=6.94 p<br>Lant1=929 n<br>Rant1=2758                                                              |                                                                                                                                                                                        |

| <b>AC Equations</b>                                                                                                                 | <b>S-Parameter Equations</b>                                                                                                                                                           |

| <b>Gleichung</b><br>Eqn7<br>magZin=mag((V_in_ac_v)/Pr13.i)                                                                          | <b>Gleichung</b><br>Eqn5<br>phaseZin=phase((V_in_ac_v)/Pr0.i)<br>phaseCapDiff=phase((V_rf1_ac_v)/Pr13.i)<br>phaseDiff=phaseCapDiff_phaseZin+180<br>phaseZemc=phase((V_emc_ac_v)/Pr9.i) |

| <b>Gleichung</b><br>Eqn3<br>magV_out=mag((V_out_ac_v))                                                                              | <b>Gleichung</b><br>Eqn6<br>phaseZout=phase((V_out_ac_v)/Pr9.i)                                                                                                                        |

|                                                                                                                                     | <b>Gleichung</b><br>Eqn4<br>dBS11=dB(S[3,3])<br>dBS21=dB(S[4,3])                                                                                                                       |

|                                                                                                                                     | <b>Gleichung</b><br>Eqn24<br>myphase=phaseDiff<br>mymag=mag((V_rf1_ac_v))                                                                                                              |

|                                                                                                                                     | <b>Gleichung</b><br>Eqn16<br>Q=xvalue(dBS21,max(dBS21))/abs(xvalue(dBS21,(max(dBS21)-3)-(xvalue(dBS21,max(dBS21))))*2)                                                                 |

## 6.2.1 モデル

シミュレーションの実行には、次の3つのモデルが使用されます。

1. S-パラメータ・モデル（図 22）：スミス・チャートで目標整合インピーダンスを計算する際に使用します。VNAによる測定と結果を比較できるように、電源インピーダンスとして50 Ωを使用しています。結果を図 25に示します。

2. 過渡シミュレーション（図 23）：OOKの波形を確認し、コンデンサ分圧回路の回路定数を求めるためにRFI電圧を計算します。ICの出力ドライバのインピーダンスには概算値の2 Ωを使用しています。結果を図 27に示します。

3. ACシミュレーション（図 24）：ICのドライバの出力インピーダンスを2 Ωとして、反射係数と透過係数（S11およびS21）を計算します。このモデルは、Q値やRFOとRFIとの位相差の計算、およびアンテナの共振周波数とEMCフィルタの共振周波数との関係の監視に使用します。結果を図 25と図 27に示します。

図 22はS-パラメータのモデルです。図 21に"Component-Values"と"Antenna-Trim"の領域を示します。ここで割り当てられる値は、3つのモデルのすべてに自動的にリンクされます。

S-パラメータ・モデルとACモデルの違いは、電源インピーダンスです。

インピーダンスの測定期（S-パラメータ測定期）、整合回路とアンテナは、VNAから電源供給を受けます。VNAのインピーダンスはほとんどの場合50Ωであるため、S-パラメータ・モデルの電源インピーダンスは50Ωにする必要があります。

# 参考資料

注： ST25R3916にはシミュレーション・ツールのAAT回路を使用できません。ST25R antenna matching toolは、各種のHFリーダICに使用できる汎用ツールです。

過渡モデルは、2つの周期的な矩形波電圧パルス源によって駆動されます。電源のそれぞれが、1つのシングルエンドのドライバ段になっています。ドライバ段の出力抵抗は $Z_{RFO}$ で設定できます。

ACモデルを使用して、通常動作時の整合回路をシミュレートします。したがって、AC電源の電源インピーダンスは、チップ・インピーダンスと相互に関連している必要があります。このシミュレーションでは、順方向反射係数（S11）と順方向透過係数（S21）に加えて、位相や振幅の特性も計算できます。最後に結果が新しいタブに表示されます。パラメータ値のスイープなどの詳しいシミュレーションも実行できます。

図 22. S-パラメータ・モデル

図 23. 過渡シミュレーション

図 24. ACシミュレーション

## 6.2.2 結果

伝達関数dB [S11]とdB [S21]は、Eqn4で計算します（図 21の"S-Parameter Equations"ボックス）。この式は、ACシミュレーション・モデルのポート3および4を使用します。

dB [S11]は、RFOxピンにおける反射電力を表します。ST25R3916のドライバ段と整合回路の間の整合を改善すれば、反射する電力が減少します。今回の例では、出力抵抗を差動構成の $2\Omega$ とし、整合回路のインピーダンスを $15.97 - j0.042\Omega$ に調整しています。

図 25に示す順方向透過係数は、周波数に対する減衰の変化を示します。スミス・チャートには、整合回路とアンテナをまとめた公称抵抗が周波数に対して変化する様子が表示されます。曲線が実数軸と交わる位置では、虚数成分がゼロになって回路は共振状態になります。ここで検討している例では、整合回路の共振周波数の1つが $13.57\text{MHz}$ になります。この周波数における回路の複素抵抗は $15.97 - j0.042\Omega$ です。公称抵抗が $50\Omega$ であるため、このグラフはVNAによる測定結果と一致する必要があります。

図 25. S-パラメータ・モデルおよびACモデルのシミュレーション結果

# 参考資料

## アンテナの整合

AN5276

Q値シミュレーションの結果は、dB [S21]の結果から計算されます。

過渡シミュレーションの結果から、アンテナ電圧とRFIxピン電圧の波形を確認できます。Eqn2(図21)の"Capacitive Voltage Divider"ボックス)は、RFIxピンの電圧が、AGD(アナログ基準電圧)のレベルに向けてどの程度分圧されているかを記述する式です。入力電圧は3V<sub>PP</sub>を超えないことが必要です。図26の下部には、アンテナ電圧の振幅と整合インピーダンスのほか、RFOxとRFIxピンとの位相差(phaseDiff)も表示されています。

図26. 過渡モデルおよびACモデルのシミュレーション結果

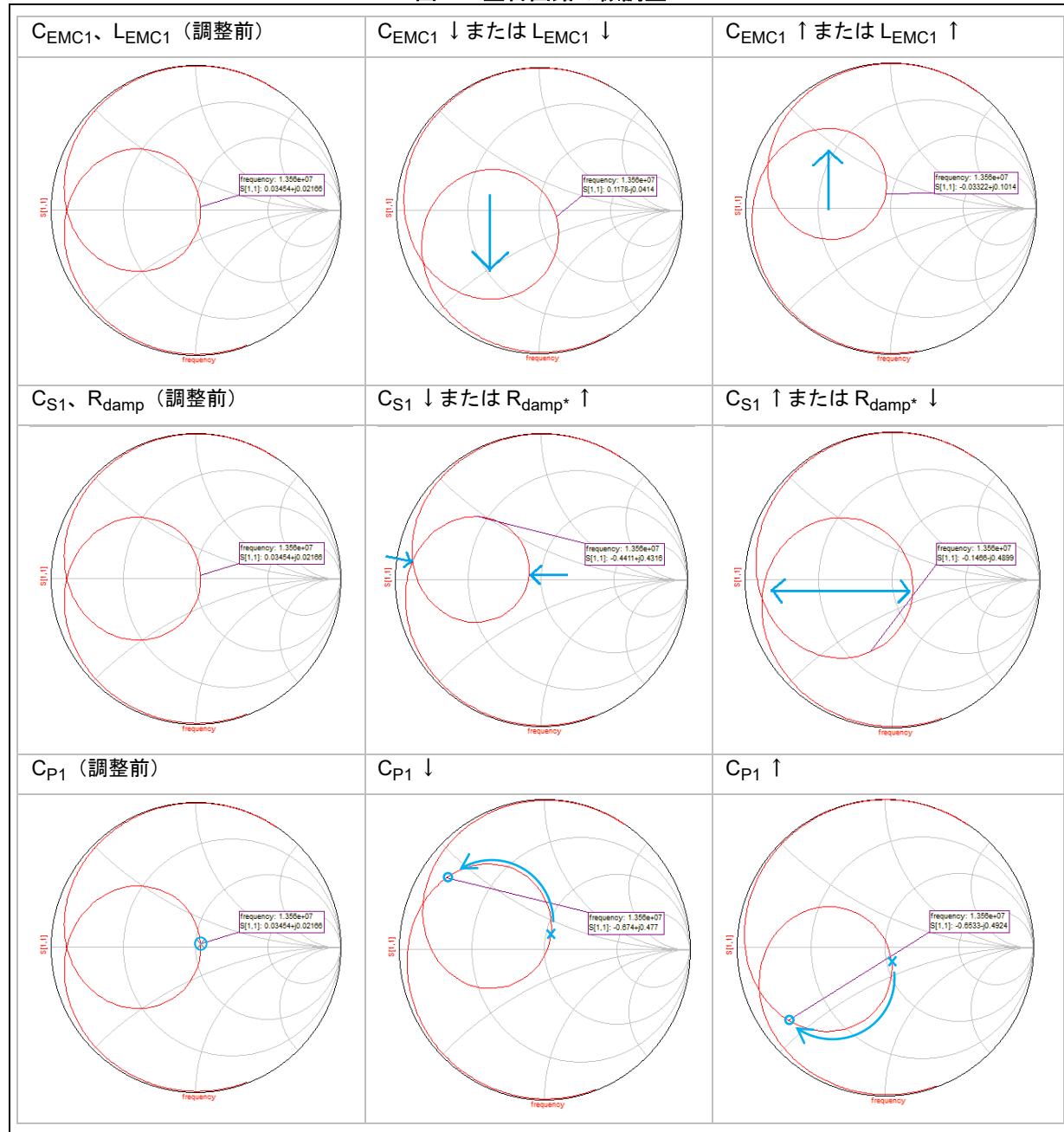

## 6.3 整合回路の挙動

シミュレーションが必ず現実と一致するとは限らないため、何らかの微調整が必要になる場合があります。

図27は、回路定数の一部を変更すると整合回路がどのように振る舞うかを示しています。

この図が示すR<sub>damp</sub>の挙動は、直列抵抗の構成でのみ見られることに注意が必要です。並列の減衰抵抗を使用した場合の挙動は、これと逆になります。

部品の1つを変更すると、その変更による直接の影響以外の影響も発生することがあります。たとえば、直列コンデンサの容量値を変更すると共振サイクルの直径が変化しますが、並列コンデンサの容量値を変更した場合と同様に共振周波数自体も変化します。

# 参考資料

AN5276

アンテナの整合

図 27. 整合回路の微調整

## 7 設計検証

ここでは、設計したアンテナの検証方法を検討し、タイミング・パラメータ、Q値、目標整合インピーダンスの測定方法について説明します。

### 7.1 PCDのRFアナログ・パラメータの測定

リーダ・システムの適切な動作および相互運用性を実現するには、すべての測定を所定の規格（例：ISO 14443やEMVなどの非接触ICカード規格）に従って実施する必要があります。たとえば、ISO 14443の非接触ICカード規格に従って試験するには、ISO/IEC 10373-6で規定されているISO基準PICCを使用する必要があります。

RF信号伝送パラメータをオシロスコープのループで検証しても、得られるのは信号波形の初期的な様相のみで、規格に対して有意な、もしくは比較検証可能な結果は一切得られません。

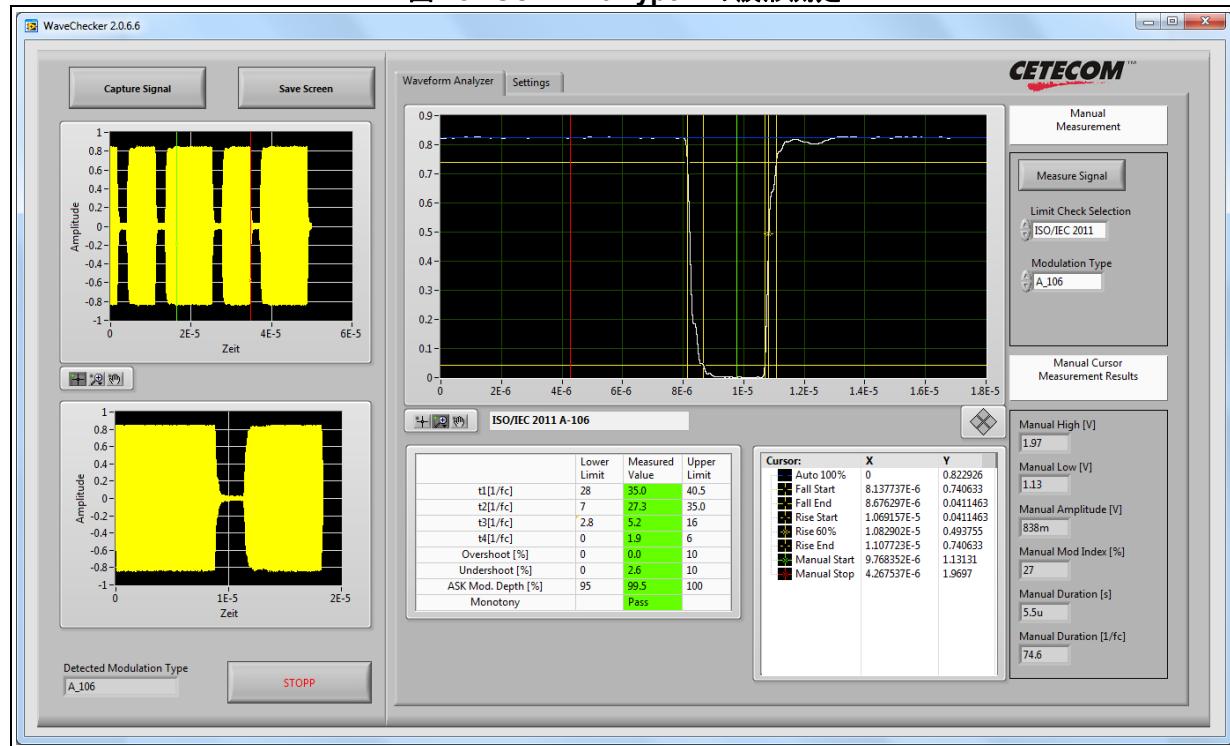

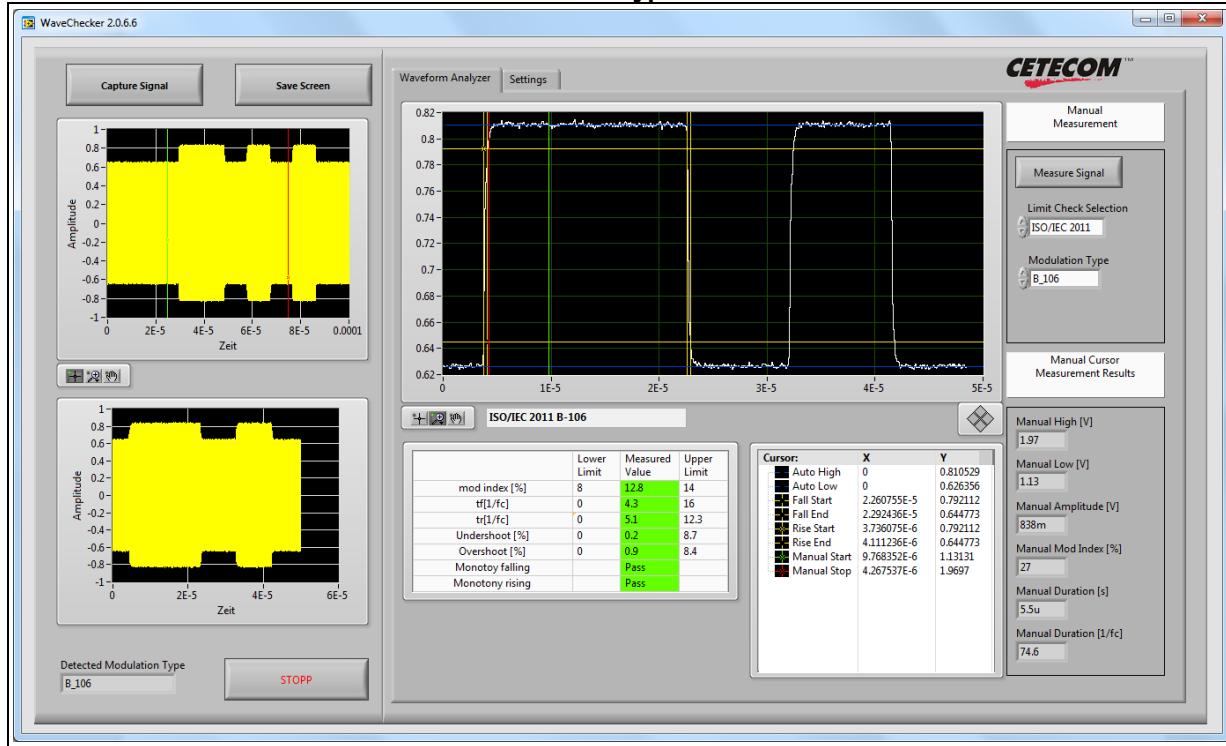

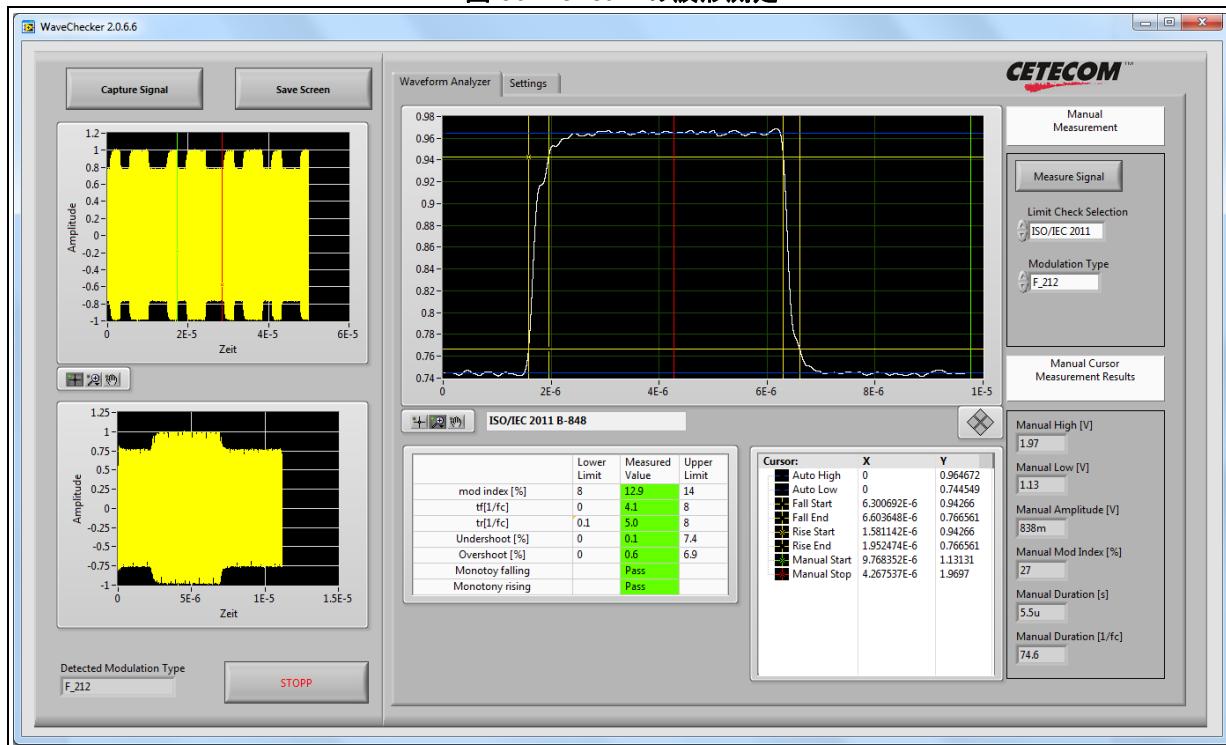

**図 28、図 29、図 30**に、それぞれ106 Kb/sのType A、106 Kb/sのType B、FeliCa™の信号を、基準PICCで測定したスナップショットを示します。

図 28. ISO 14443 Type Aの波形測定

# 参考資料

AN5276

設計検証

図 29. ISO 14443 Type Bの波形測定

図 30. Felica™の波形測定

## 7.2 時間ドメインでのQ値の検証

立ち上がりエッジと立ち下がりエッジに対する共振回路のエンベロープは、指数関数を使用して次のように計算できます。

$$Q_f = 2 \pi f_{work} [(t_1 - t_2) / (\ln 0.9 - \ln 0.05)]$$

$$Q_r = 2 \pi f_{work} [t_3 / (\ln 0.9 - \ln 0.05)]$$

総合的なQ値は、 $Q_f$ と $Q_r$ の平均値である $Q = (Q_f + Q_r) / 2$ として得られます。

## 7.3 周波数ドメインでのQ値の検証

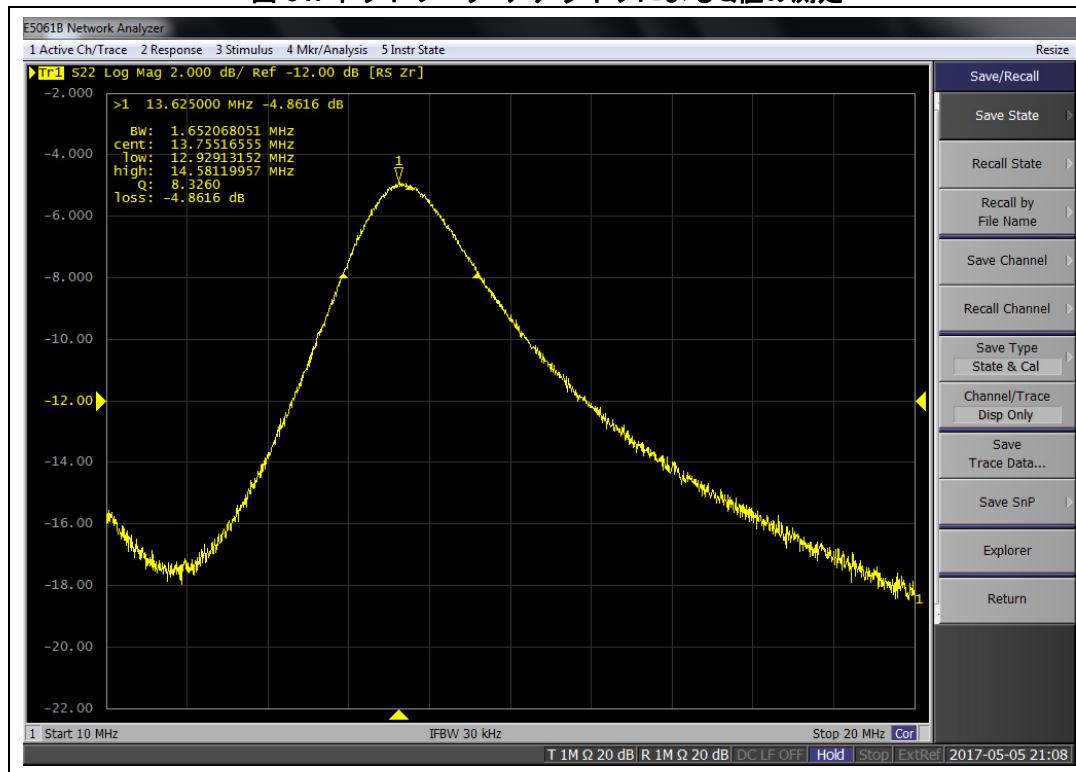

ベクトル・ネットワーク・アナライザ (VNA) とISO10373-6のClass 1 ~ Class 3の較正用コイルを使用してQ値を測定できます。

以下の手順を実行します。

1. ネットワーク・アナライザを約10 MHz ~ 20 MHzの周波数スイープで較正します。

2. S11の測定値をLog MAGフォーマットで表示します。

3. 較正用コイルをVNAに接続します。

4. "Short"条件でコイルを較正し、"Z: 反射特性"に変換表示します。

5. マーカー 1を設定し、帯域幅/Q値測定を有効にします。

6. 測定コイル上にPCDアンテナを設置します。

注：

リーダを接続して通電状態にしている場合は、VNAポートに大きな電力が伝送されないように、送信 (Tx) ドライバをHigh Zに設定していることを確認してください。大電力が伝送されるとVNAを破損する恐れがあります。

7. 動作中のチップ抵抗を模した $2 \Omega$ の抵抗をRFOピン間に接続します。

8. "Max Search"を押して、マーカーをPCDアンテナの共振周波数ピークに合わせます。

図 31に、この測定の結果を示します。

# 参考資料

AN5276

設計検証

図 31. ネットワーク・アナライザによるQ値の測定

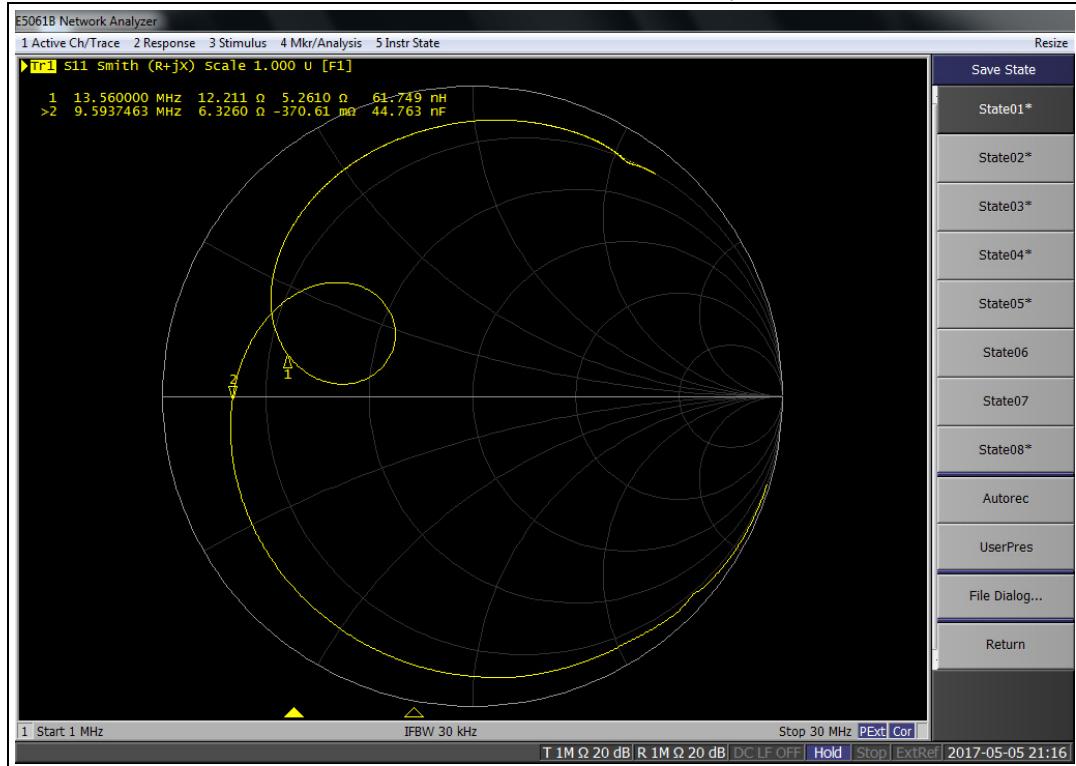

### 7.4 目標整合インピーダンスの測定

リーダ・システムの整合インピーダンスは、アンテナを最終的な設置場所に置いて測定する必要があります。この測定には、[セクション 4.1](#)の説明に従って設定したネットワーク・アナライザが必要です。

**注：**リーダを接続している場合は、VNAポートに大きな電力が伝送されないように、レジスタ0x28を0xFに設定していることを確認してください。

目標整合インピーダンスが差動トポロジで測定されます。

測定結果（[図 32](#)参照）は、シミュレーション結果と良好に一致しています。

**図 32. ネットワーク・アナライザによって測定した目標整合インピーダンス**

## 8 結論

本稿では、ST25R3916のアンテナを設計および調整するための基本的なプロセスを解説しました。

このプロセスは、リーダの出力電力を規定する場合や、整合回路に使用するEMCインダクタなどの部品定数を決定する際に有用です。また、アンテナ・パラメータの測定や、整合回路の計算およびシミュレーション手順も取り上げました。

最後のセクションでは、整合回路を適切に設計できていることを確認する、基本的な設計検証の手順を解説しました。

# 參考資料

改版履歴

AN5276

9

## 改版履歴

表 3. 文書改版履歴

| 日付         | 版 | 変更内容                  |

|------------|---|-----------------------|

| 2019年1月25日 | 1 | 初版発行                  |

| 2019年2月26日 | 2 | 文書の適用範囲をST限定からST公開に更新 |

表 4. 日本語版文書改版履歴

| 日付      | 版 | 変更内容      |

|---------|---|-----------|

| 2019年9月 | 1 | 日本語版 初版発行 |

**重要なお知らせ（よくお読み下さい）**

STMicroelectronics NV およびその子会社（以下、ST）は、ST製品及び本書の内容をいつでも予告なく変更、修正、改善、改定及び改良する権利を留保します。購入される方は、発注前にST製品に関する最新の関連情報を必ず入手してください。ST 製品は、注文請求書発行時点での有効なST の販売条件に従って販売されます。

ST製品の選択並びに使用については購入される方が全ての責任を負うものとします。購入される方の製品上の操作や設計に関してST は一切の責任を負いません。

明示又は默示を問わず、STは本書においていかなる知的財産権の実施権も許諾致しません。

本書で説明されている情報とは異なる条件でST 製品が再販された場合、その製品についてSTが与えたいかなる保証も無効となります。

ST およびST ロゴはSTMicroelectronics の商標です。その他の製品またはサービスの名称は、それぞれの所有者に帰属します。

本書の情報は本書の以前のバージョンで提供された全ての情報に優先し、これに代わるものです。

この資料は、STMicroelectronics NV 並びにその子会社(以下ST)が英文で記述した資料（以下、「正規英語版資料」）を、皆様のご理解の一助として頂くためにSTマイクロエレクトロニクス(株)が英文から和文へ翻訳して作成したものです。この資料は現行の正規英語版資料の近時の更新に対応していない場合があります。この資料は、あくまでも正規英語版資料をご理解頂くための補助的参考資料のみにご利用下さい。この資料で説明される製品のご検討及びご採用にあたりましては、必ず最新の正規英語版資料を事前にご確認下さい。ST及びSTマイクロエレクトロニクス(株)は、現行の正規英語版資料の更新により製品に関する最新の情報を提供しているにも関わらず、当該英語版資料に対応した更新がなされていないこの資料の情報に基づいて発生した問題や障害などにつきましては如何なる責任も負いません。

© 2019 STMicroelectronics - All rights reserved