# 参考資料

life.augmented

**ST25DV02K-W1**

**ST25DV02K-W2**

**2KビットEEPROM内蔵NFC/RFIDダイナミック・タグIC

最大2本のPWM出力機能付き**

データシート

SO8N(4.9 x 6 mm)

TSSOP8(3 x 6.4 mm)

## 特徴

### パルス幅変調出力

- 最大2本の独立出力

- ST25DV02K-W1はPWM出力 x1

- ST25DV02K-W2はPWM出力 x2

- 488 Hzから31250 Hz

- 62.5 nsのパルス幅分解能:

- 488 Hzにおける15 ビット分解能から

- 31.25 kHzにおける9 ビット分解能まで

- 精度:温度範囲全体に対して±10%

- 外付け水晶不要

- 電源電圧1.8 ~ 5.5 V、RFインターフェース（リーダライタ磁界）のみではPWM使用不可

- 独立プッシュ・プル出力

- 出力あたり最大4 mAの駆動能力

- 低消費電力かつノイズ制約のあるアプリケーションのための調整可能出力駆動段

- RFインターフェースによって制御される PWM パラメータの動作中更新

### RFインターフェース (NFC)

- ISO/IEC 15693とNFC Forum Type 5タグ準拠

- ISO/IEC 15693の変調、符号化、サブキャリアモード、データレートにすべて対応

- 単一および複数のブロック読み取り

- 内蔵同調キャパシタンス: 28.5 pF

### メモリ

- 2KbitのEEPROM

- 4xバイトのブロックでアクセス可能

- 標準書き込み時間5 ms (1ブロック)

- データ保持: 40年

- 書き込みサイクル耐久性:

- 85°Cにおける書き込みサイクル10万回

### データ保護

- 32/64 ビットパスワードに基づく柔軟性のある保護機能を備えた、最大4個の独立メモリエリア (PWM制御レジスタエリアを含む)

- システム設定: 32 ビットパスワードによる書き込み保護

- 認証・真贋判定用のTruST25™デジタル署名機能

### 温度範囲

- 40 ~ +85°C (RFインターフェース)

- 40 ~ +105°C (PWMインターフェース)

### パッケージ

- 8 ピンパッケージ

- ECOPACK2® (RoHS適合)

# 參考資料

ST25DV02K-W1 ST25DV02K-W2

---

# 参考資料

## 目次

|       |                             |    |

|-------|-----------------------------|----|

| 1     | 説明 .....                    | 9  |

| 1.1   | ブロック図 .....                 | 9  |

| 1.2   | パッケージ .....                 | 10 |

| 2     | 信号説明 .....                  | 11 |

| 2.1   | パルス幅変調出力 (PWM1) .....       | 11 |

| 2.2   | パルス幅変調出力 (PWM2) .....       | 11 |

| 2.3   | PWM 電源 (VCC) .....          | 11 |

| 2.4   | PWM グラウンドリファレンス (VSS) ..... | 11 |

| 2.5   | アンテナコイル (AC0、AC1) .....     | 11 |

| 3     | パワー・マネージメント .....           | 12 |

| 3.1   | 有線インタフェース .....             | 12 |

| 3.2   | RF インタフェース .....            | 13 |

| 3.3   | RF と PWM ブートの優先度 .....      | 13 |

| 4     | メモリ・マネージメント .....           | 14 |

| 4.1   | メモリ構成 .....                 | 14 |

| 4.2   | ユーザメモリ .....                | 15 |

| 4.3   | システム設定メモリ .....             | 17 |

| 5     | 固有の特徴 .....                 | 18 |

| 5.1   | パルス幅変調出力 .....              | 19 |

| 5.1.1 | パルス幅変調レジスタ .....            | 19 |

| 5.1.2 | パルス幅変調機能の説明 .....           | 21 |

| 5.2   | データ保護 .....                 | 26 |

| 5.2.1 | データ保護レジスタ .....             | 26 |

| 5.2.2 | パスワードとセキュリティセッション .....     | 30 |

| 5.2.3 | ユーザメモリの保護 .....             | 32 |

| 5.2.4 | システム設定メモリ保護 .....           | 32 |

| 5.3   | TruST25™ デジタル署名 .....       | 33 |

| 5.4   | デバイスパラメータレジスタ .....         | 33 |

# 参考資料

## 目次

|          |                                    | ST25DV02K-W1 | ST25DV02K-W2 |

|----------|------------------------------------|--------------|--------------|

| <b>6</b> | <b>RF 動作</b>                       | <b>36</b>    |              |

| 6.1      | RF 通信                              | 36           |              |

| 6.1.1    | ISO/IEC 15693 デバイスに対するアクセス         | 36           |              |

| 6.2      | RF プロトコル                           | 37           |              |

| 6.2.1    | 説明                                 | 37           |              |

| 6.2.2    | 対応状態                               | 37           |              |

| 6.2.3    | モード                                | 39           |              |

| 6.2.4    | リクエストフォーマット                        | 40           |              |

| 6.2.5    | リクエストフラグ                           | 40           |              |

| 6.2.6    | レスポンスフォーマット                        | 42           |              |

| 6.2.7    | レスポンスフラグ                           | 42           |              |

| 6.2.8    | レスポンスとエラーコード                       | 43           |              |

| 6.3      | タイミングの定義                           | 43           |              |

| 6.4      | RF コマンド                            | 45           |              |

| 6.4.1    | Inventory                          | 46           |              |

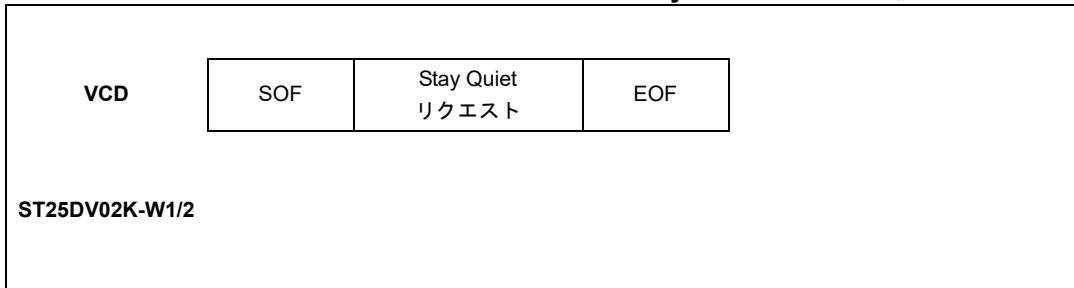

| 6.4.2    | Stay Quiet                         | 47           |              |

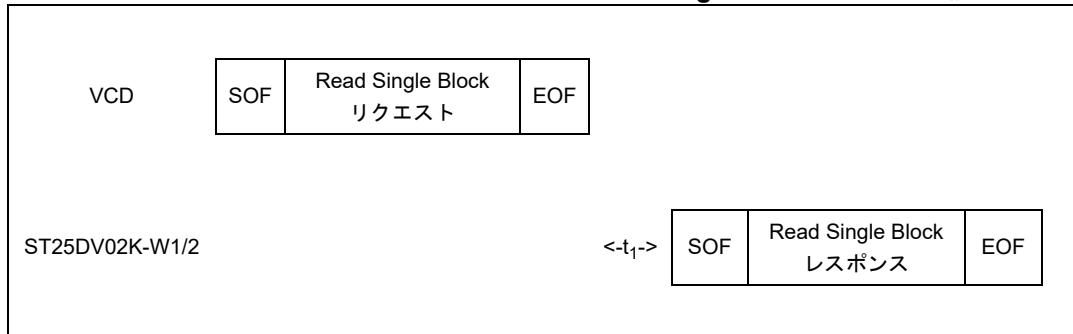

| 6.4.3    | Read Single Block                  | 47           |              |

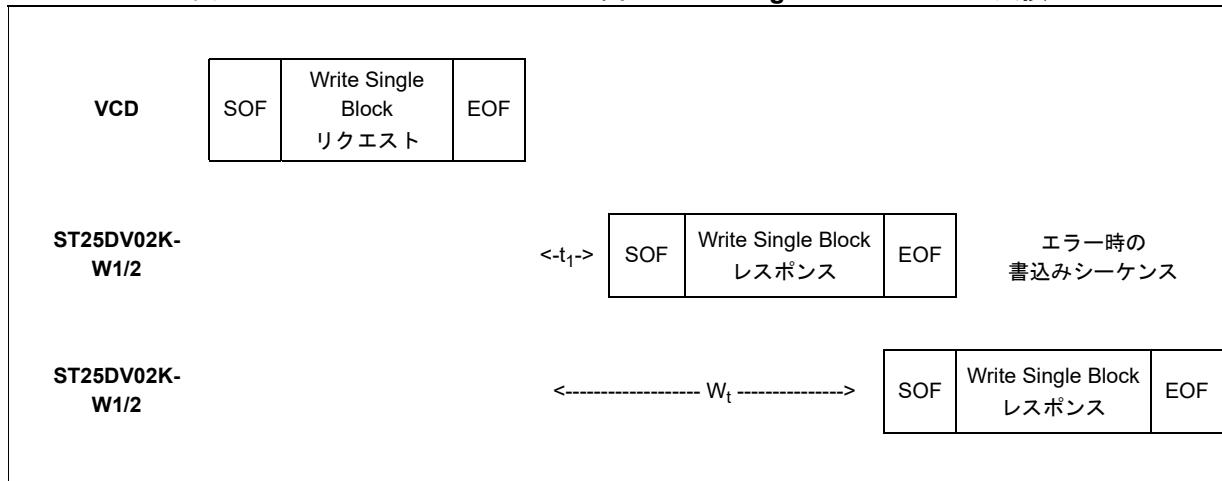

| 6.4.4    | Write Single Block                 | 49           |              |

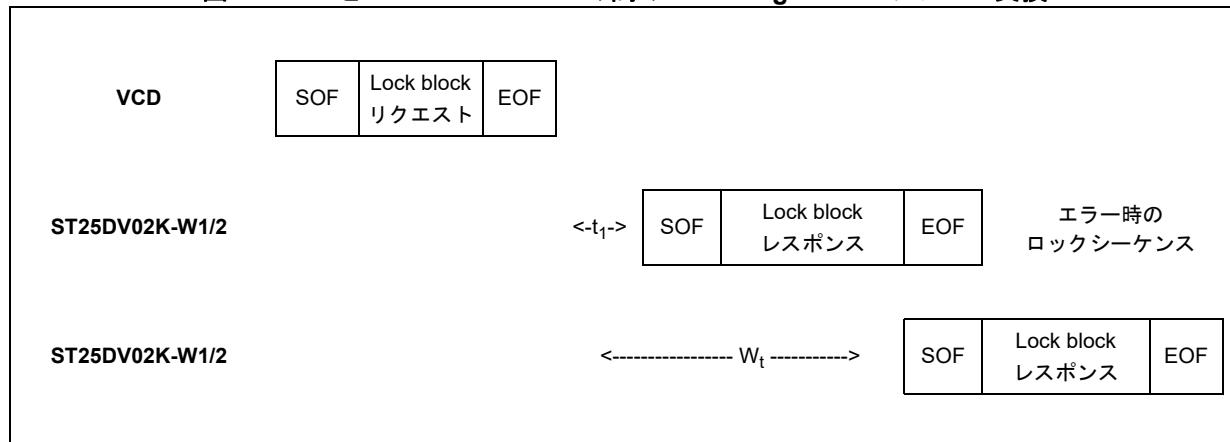

| 6.4.5    | Lock block                         | 50           |              |

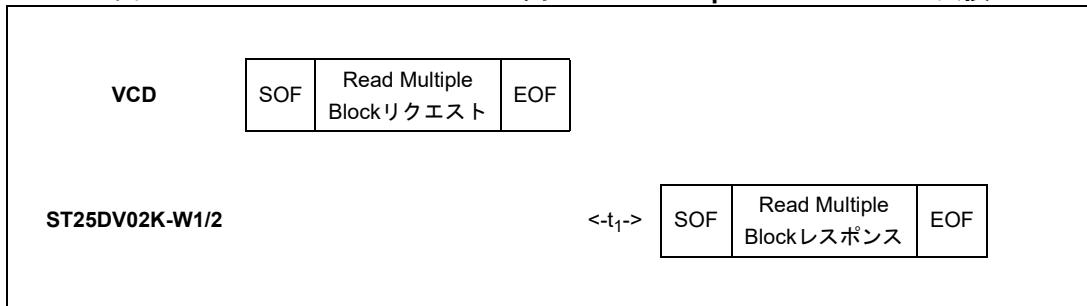

| 6.4.6    | Read Multiple Blocks               | 52           |              |

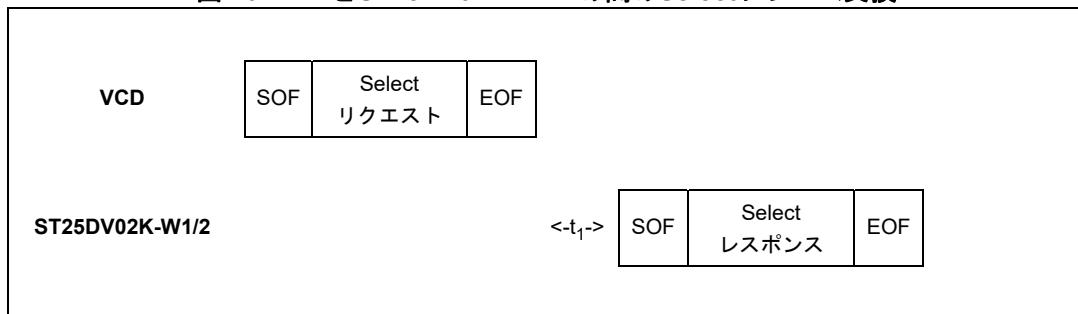

| 6.4.7    | Select                             | 53           |              |

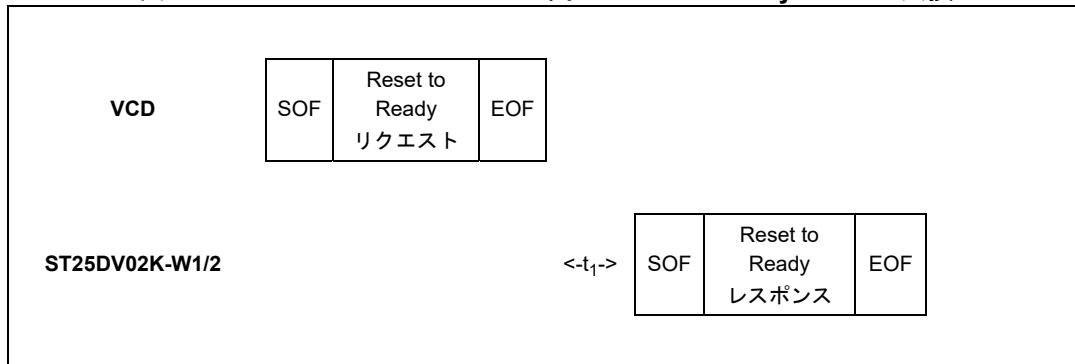

| 6.4.8    | Reset to Ready                     | 54           |              |

| 6.4.9    | Write AFI                          | 55           |              |

| 6.4.10   | Lock AFI                           | 56           |              |

| 6.4.11   | Write DSFID                        | 58           |              |

| 6.4.12   | Lock DSFID                         | 59           |              |

| 6.4.13   | Get System Info                    | 60           |              |

| 6.4.14   | Get Multiple Block Security Status | 61           |              |

| 6.4.15   | Read Configuration                 | 63           |              |

| 6.4.16   | Write Configuration                | 64           |              |

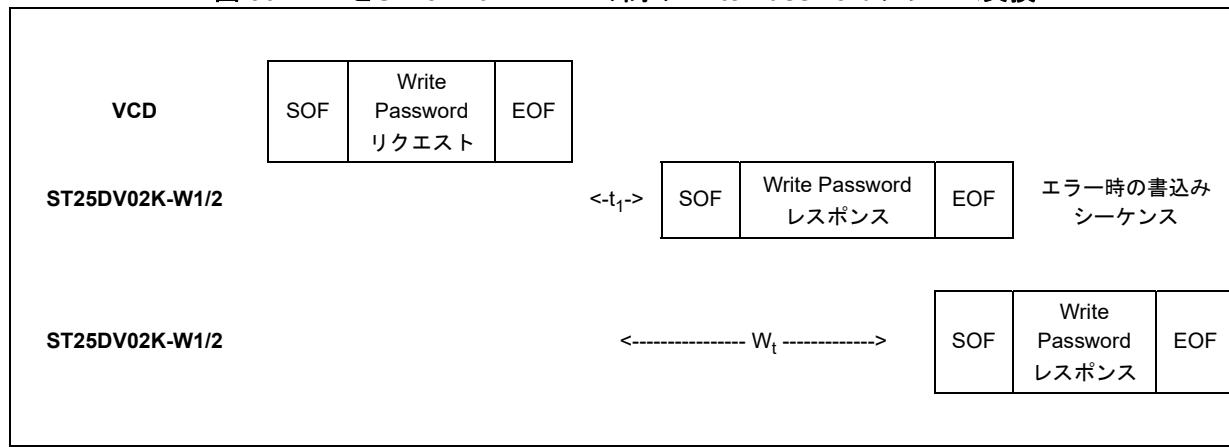

| 6.4.17   | Write Password                     | 66           |              |

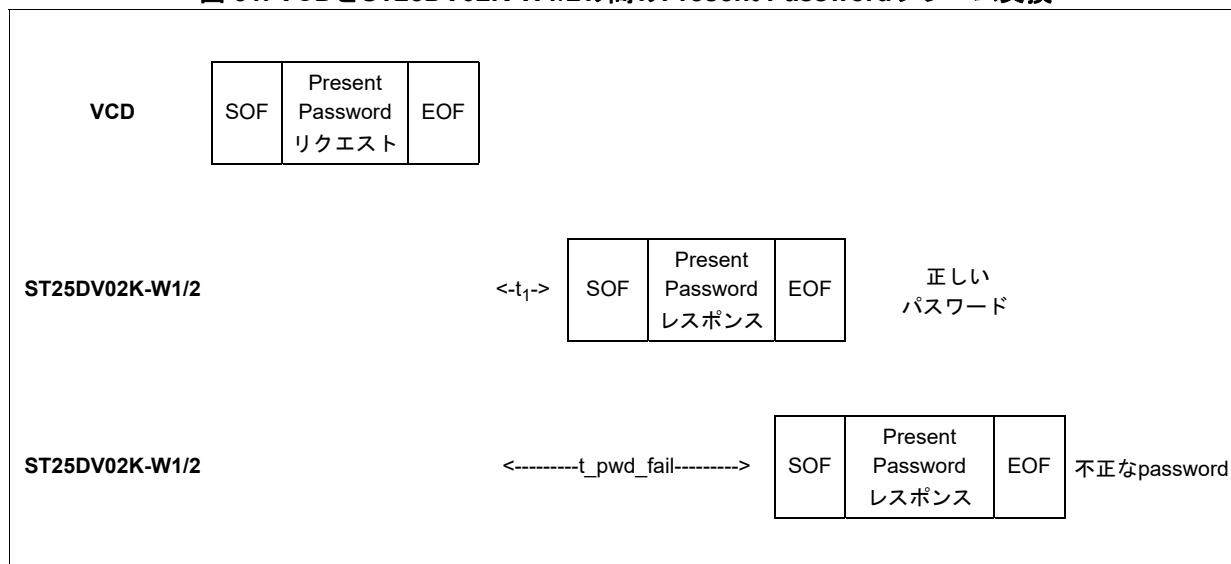

| 6.4.18   | Present Password                   | 67           |              |

| <b>7</b> | <b>固有識別子 (UID)</b>                 | <b>70</b>    |              |

# 参考資料

|     |                      |    |

|-----|----------------------|----|

| 8   | デバイスパラメータ .....      | 71 |

| 8.1 | 最大定格 .....           | 71 |

| 8.2 | RF 電気的パラメータ .....    | 72 |

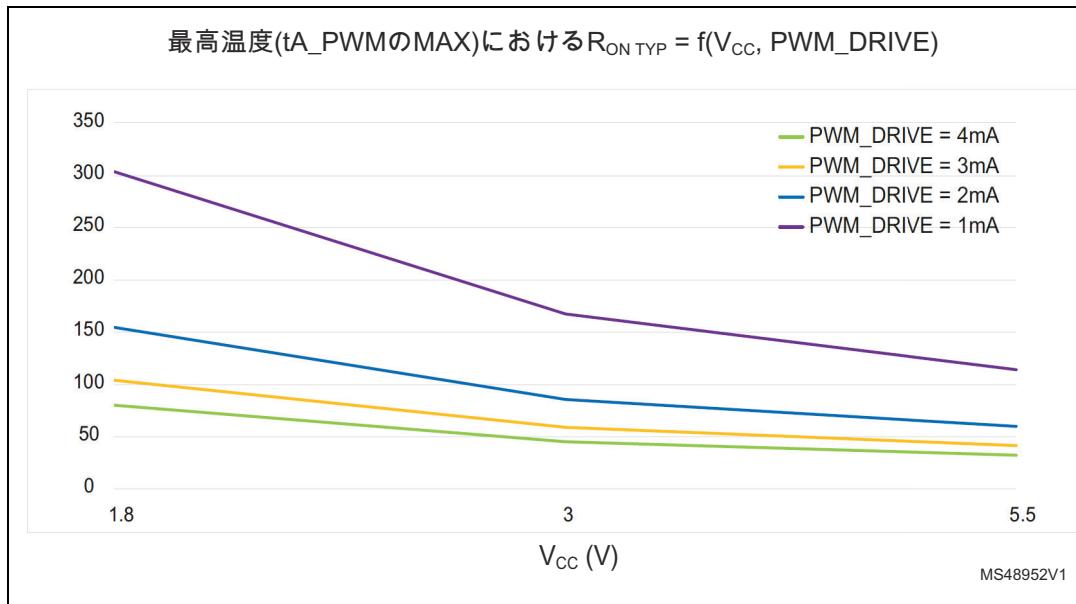

| 8.3 | PWM 電気的パラメータ .....   | 73 |

| 9   | パッケージ情報 .....        | 75 |

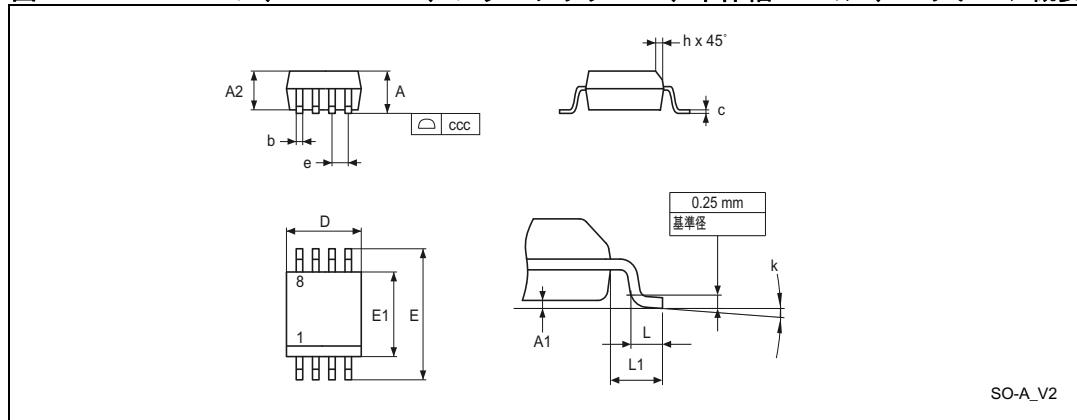

| 9.1 | SO8N パッケージ情報 .....   | 75 |

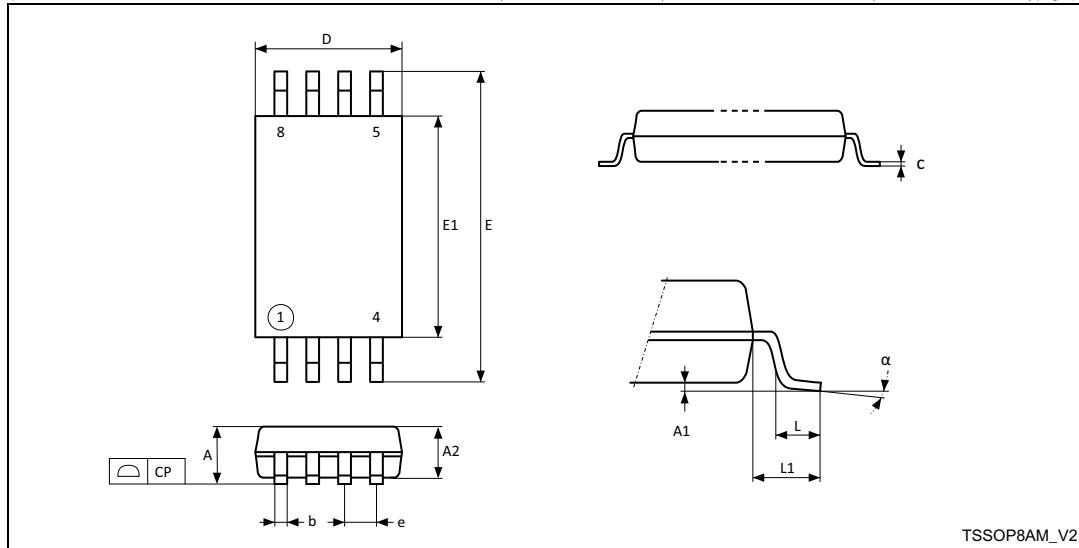

| 9.2 | TSSOP8 パッケージ情報 ..... | 76 |

| 10  | 発注情報 .....           | 77 |

| 11  | 改版履歴 .....           | 78 |

# 参考資料

## 表の一覧

ST25DV02K-W1 ST25DV02K-W2

## 表の一覧

|       |                                                            |    |

|-------|------------------------------------------------------------|----|

| 表 1.  | 信号名                                                        | 10 |

| 表 2.  | ユーザメモリ 4x 領域の構成                                            | 16 |

| 表 3.  | ユーザメモリ 3x 領域の構成                                            | 16 |

| 表 4.  | システム設定メモリマップ                                               | 17 |

| 表 5.  | PWM1_CTRL                                                  | 19 |

| 表 6.  | PWM2_CTRL                                                  | 20 |

| 表 7.  | PWM_CFG                                                    | 21 |

| 表 8.  | PWM 出力パラメータ                                                | 22 |

| 表 9.  | PWM 出力分解能                                                  | 22 |

| 表 10. | A1SA                                                       | 26 |

| 表 11. | A2SA                                                       | 27 |

| 表 12. | APSA                                                       | 27 |

| 表 13. | LOCK_CFG                                                   | 28 |

| 表 14. | AREA0/1/2 と PWM_CTRL の LOCK_BLOCK                          | 28 |

| 表 15. | PWD_PWM                                                    | 28 |

| 表 16. | PWD_A1                                                     | 29 |

| 表 17. | PWD_A2                                                     | 29 |

| 表 18. | PWD_CFG                                                    | 29 |

| 表 19. | セキュリティセッションのタイプ                                            | 30 |

| 表 20. | LOCK_DSFID                                                 | 33 |

| 表 21. | LOCK_AFI                                                   | 34 |

| 表 22. | DSFID                                                      | 34 |

| 表 23. | AFI                                                        | 34 |

| 表 24. | IC_REF                                                     | 34 |

| 表 25. | UID                                                        | 35 |

| 表 26. | Request_flags による ST25DV02K-W1/2 の応答                       | 38 |

| 表 27. | 一般リクエストフォーマット                                              | 40 |

| 表 28. | リクエストフラグ 1~4 の定義                                           | 40 |

| 表 29. | inventory_flag (ビット 3) = 0 の場合のリクエストフラグ 5~8                | 41 |

| 表 30. | inventory_flag (ビット 3) = 1 の場合のリクエストフラグ 5~8                | 41 |

| 表 31. | 一般レスポンスフォーマット                                              | 42 |

| 表 32. | レスポンスフラグ 1~8 の定義                                           | 42 |

| 表 33. | レスポンスエラーコードの定義                                             | 43 |

| 表 34. | タイミング値                                                     | 44 |

| 表 35. | コマンドコード                                                    | 45 |

| 表 36. | Inventory リクエストフォーマット                                      | 46 |

| 表 37. | Inventory レスポンスフォーマット                                      | 46 |

| 表 38. | Stay Quiet リクエストフォーマット                                     | 47 |

| 表 39. | Read Single Block リクエストフォーマット                              | 48 |

| 表 40. | Error_flag がセットされていない場合の Read Single Block レスponsusフォーマット  | 48 |

| 表 41. | ロックセキュリティ状態                                                | 48 |

| 表 42. | Error_flag がセットされている場合の Read Single Block レスponsusフォーマット   | 48 |

| 表 43. | Write Single Block リクエストフォーマット                             | 49 |

| 表 44. | Error_flag がセットされていない場合の Write Single Block レスponsusフォーマット | 49 |

| 表 45. | Error_flag がセットされている場合の Write Single Block レスponsusフォーマット  | 49 |

| 表 46. | Lock block リクエストフォーマット                                     | 50 |

| 表 47. | Error_flag がセットされていない場合の Lock block レスponsusフォーマット         | 51 |

| 表 48. | Error_flag がセットされている場合の Lock single block レスponsusフォーマット   | 51 |

| 表 49. | Read Multiple Block リクエストフォーマット                            | 52 |

# 参考資料

|       |                                                                                   |    |

|-------|-----------------------------------------------------------------------------------|----|

| 表 50. | Error_flag がセットされていない場合の Read Multiple Block レスポンスフォーマット .....                    | 52 |

| 表 51. | ロックセキュリティ状態 .....                                                                 | 52 |

| 表 52. | Error_flag がセットされている場合の Read Multiple Block レஸپونスフォーマット .....                    | 52 |

| 表 53. | Select リクエストフォーマット .....                                                          | 53 |

| 表 54. | Error_flag がセットされていない場合の Select Block レஸپونスフォーマット .....                          | 53 |

| 表 55. | Error_flag がセットされている場合の Select レஸپونスフォーマット .....                                 | 54 |

| 表 56. | Reset to Ready リクエストフォーマット .....                                                  | 54 |

| 表 57. | Error_flag がセットされていない場合の Reset to Ready レஸپونスフォーマット .....                        | 54 |

| 表 58. | Error_flag がセットされている場合の Reset to Ready レஸپونスフォーマット .....                         | 55 |

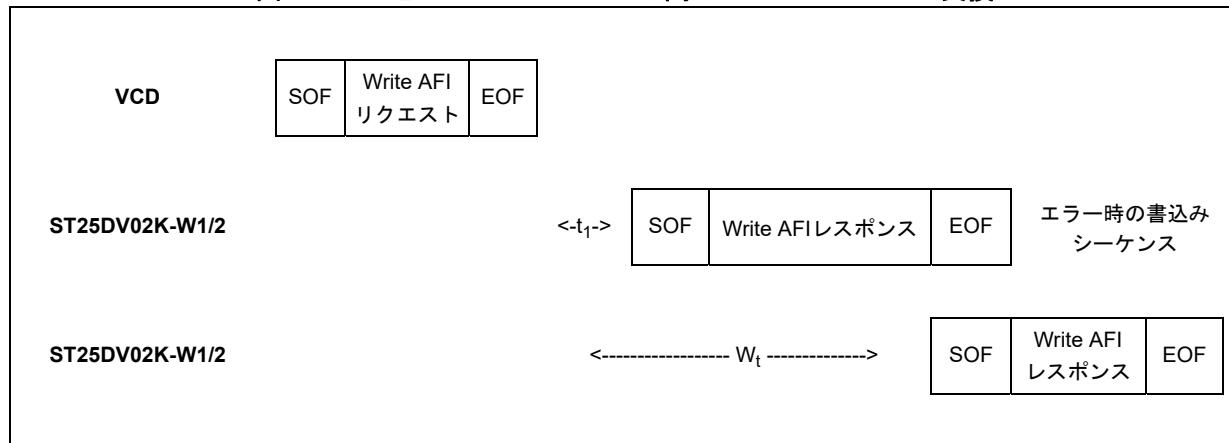

| 表 59. | Write AFI リクエストフォーマット .....                                                       | 55 |

| 表 60. | Error_flag がセットされていない場合の Write AFI レஸپونスフォーマット .....                             | 56 |

| 表 61. | Error_flag がセットされている場合の Write AFI レஸپونスフォーマット .....                              | 56 |

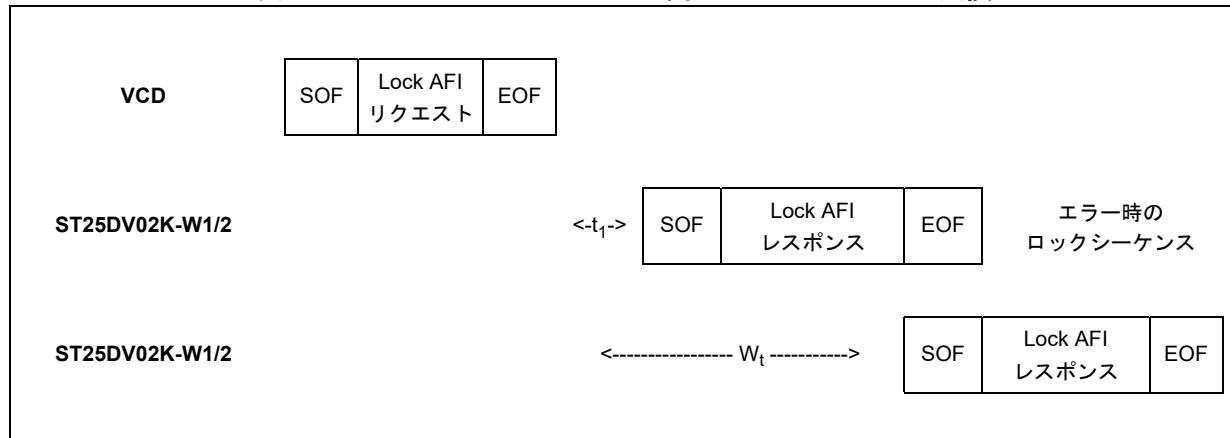

| 表 62. | Lock AFI リクエストフォーマット .....                                                        | 57 |

| 表 63. | Error_flag がセットされていない場合の Lock AFI レஸپونスフォーマット .....                              | 57 |

| 表 64. | Error_flag がセットされている場合の Lock AFI レஸپونスフォーマット .....                               | 57 |

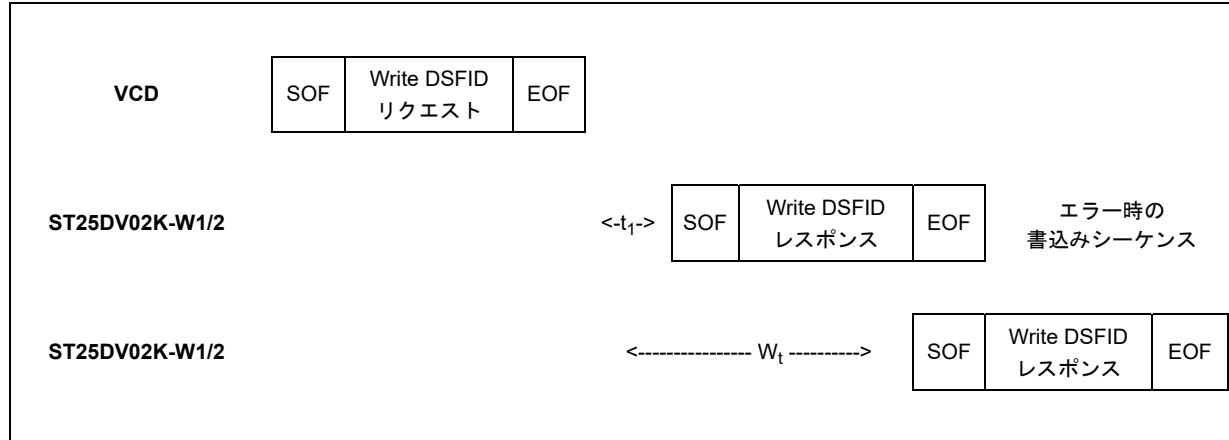

| 表 65. | Write DSFID リクエストフォーマット .....                                                     | 58 |

| 表 66. | Error_flag がセットされていない場合の Write DSFID レஸپونスフォーマット .....                           | 58 |

| 表 67. | Error_flag がセットされている場合の Write DSFID レஸپونスフォーマット .....                            | 58 |

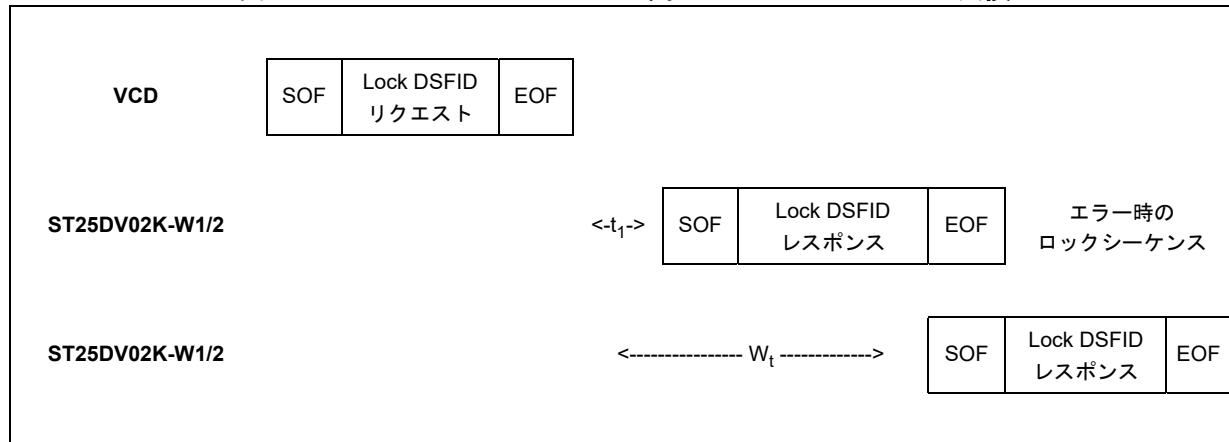

| 表 68. | Lock DSFID リクエストフォーマット .....                                                      | 59 |

| 表 69. | Error_flag がセットされていない場合の Lock DSFID レஸپونスフォーマット .....                            | 59 |

| 表 70. | Error_flag がセットされている場合の Lock DSFID レஸپونスフォーマット .....                             | 59 |

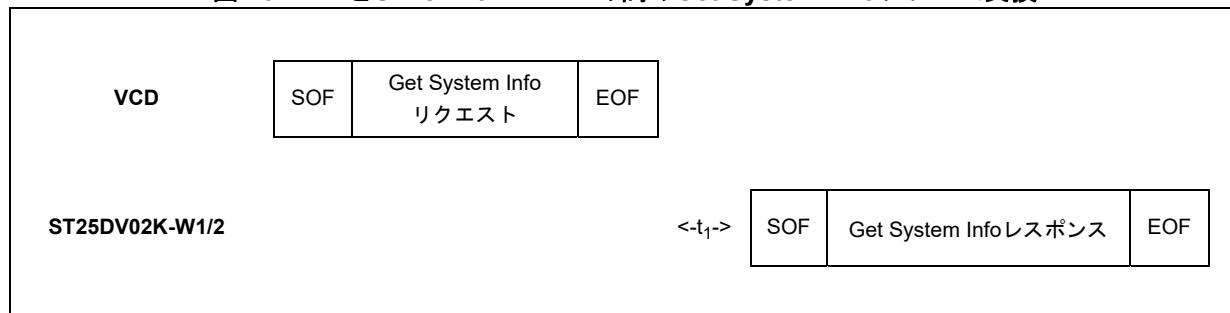

| 表 71. | Get System Info リクエストフォーマット .....                                                 | 60 |

| 表 72. | Error_flag がセットされていない場合の Get System Info レஸپونスフォーマット .....                       | 60 |

| 表 73. | Error_flag がセットされている場合の Get System Info レஸپونスフォーマット .....                        | 61 |

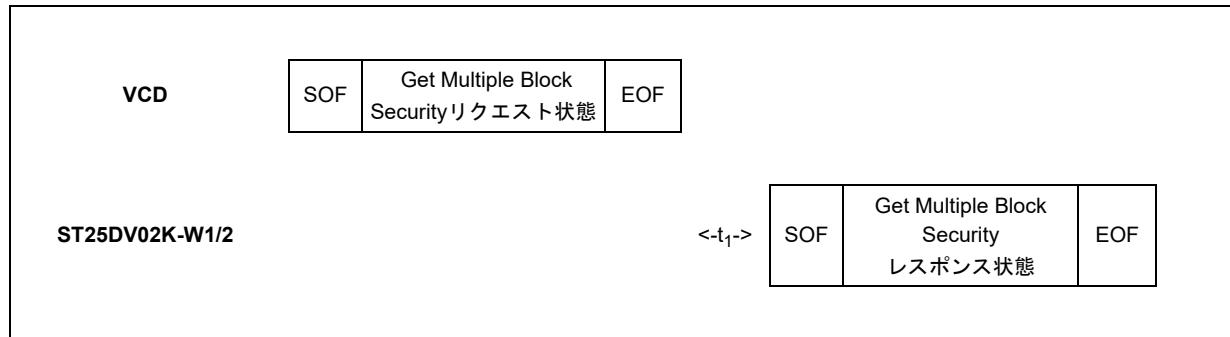

| 表 74. | Get Multiple Block Security Status リクエストフォーマット .....                              | 62 |

| 表 75. | Error_flag がセットされていない場合の Get Multiple Block Security Status<br>レスپونスフォーマット ..... | 62 |

| 表 76. | ロックセキュリティ状態 .....                                                                 | 62 |

| 表 77. | Error_flag がセットされている場合の Get Multiple Block Security Status<br>レスپونスフォーマット .....  | 62 |

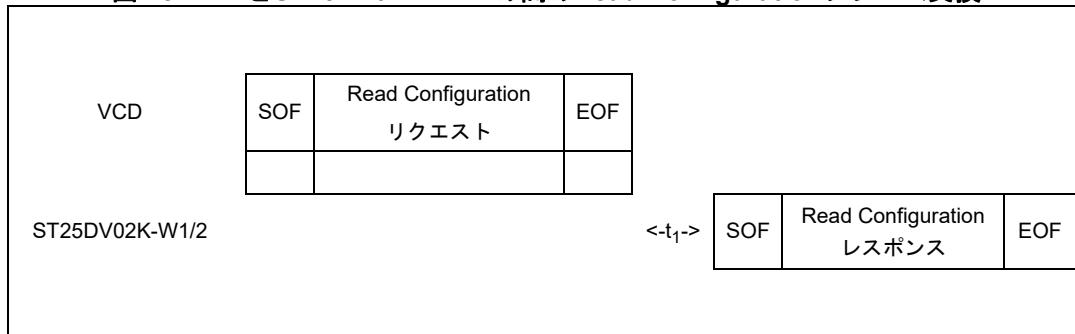

| 表 78. | Read Configuration リクエストフォーマット .....                                              | 63 |

| 表 79. | Error_flag がセットされていない場合の Read Configuration レஸپونスフォーマット .....                    | 63 |

| 表 80. | Error_flag がセットされている場合の Read Configuration レஸپونスフォーマット .....                     | 63 |

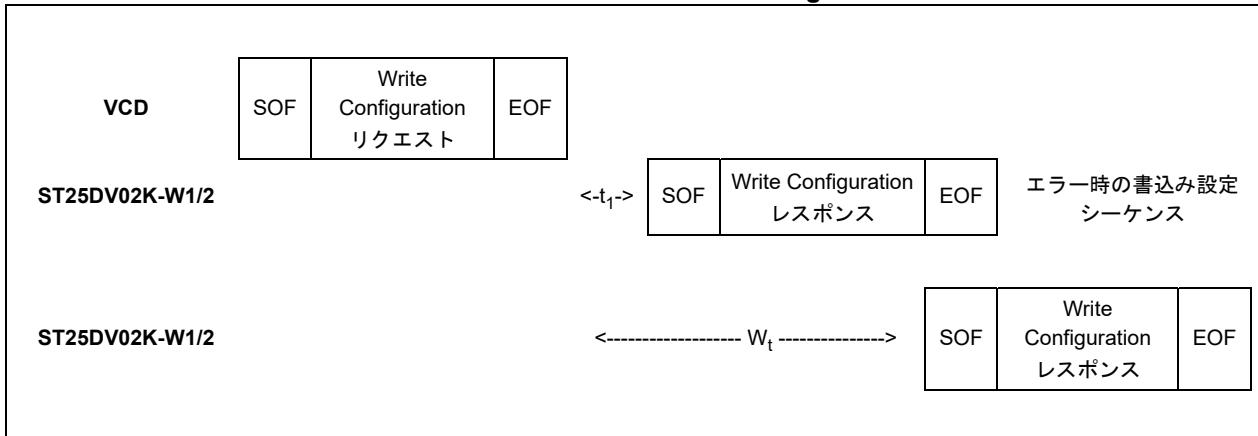

| 表 81. | Write Configuration リクエストフォーマット .....                                             | 64 |

| 表 82. | Error_flag がセットされていない場合の Write Configuration レஸپونスフォーマット .....                   | 65 |

| 表 83. | Error_flag がセットされている場合の Write Configuration レஸپونسフォーマット .....                    | 65 |

| 表 84. | Write Password リクエストフォーマット .....                                                  | 66 |

| 表 85. | Error_flag がセットされていない場合の Write Password レஸپونスフォーマット .....                        | 67 |

| 表 86. | Error_flag がセットされている場合の Write Password レஸپونスフォーマット .....                         | 67 |

| 表 87. | Present Password リクエストフォーマット .....                                                | 68 |

| 表 88. | Error_flag がセットされていない場合の Present Password レஸپونスフォーマット .....                      | 68 |

| 表 89. | Error_flag がセットされている場合の Present Password レஸپونסフォーマット .....                       | 68 |

| 表 90. | UID format .....                                                                  | 70 |

| 表 91. | 絶対最大定格 .....                                                                      | 71 |

| 表 92. | RF 特性 .....                                                                       | 72 |

| 表 93. | PWM 特性 .....                                                                      | 73 |

| 表 94. | SO8N-8 ピン、4.9 x 6 mm、プラスチック SOP、本体幅 150 ミル、パッケージ機械的データ .....                      | 75 |

| 表 95. | TSSOP8-8 ピン Thin Shrink SOP、3 x 6.4 mm、0.65 mm ピッチ、パッケージ機械的データ .....              | 76 |

| 表 96. | 発注情報の仕組み .....                                                                    | 77 |

| 表 97. | 文書改版履歴 .....                                                                      | 78 |

| 表 98. | 日本語版文書改版履歴 .....                                                                  | 78 |

# 参考資料

## 図の一覧

ST25DV02K-W1 ST25DV02K-W2

## 図の一覧

|       |                                                                    |    |

|-------|--------------------------------------------------------------------|----|

| 図 1.  | ブロック図                                                              | 9  |

| 図 2.  | ST25DV02K-W1/28 ピンパッケージの接続                                         | 10 |

| 図 3.  | ST25DV02K-W1/2 パワーアップ / ダウンシーケンス                                   | 12 |

| 図 4.  | RF パワーアップ・シーケンス                                                    | 13 |

| 図 5.  | メモリ構成                                                              | 14 |

| 図 6.  | PWM 出力                                                             | 21 |

| 図 7.  | PWM 出力の変化                                                          | 23 |

| 図 8.  | PWM 出力ドライバのトリミング                                                   | 24 |

| 図 9.  | PWM 出力の RF インタフェースとの共存                                             | 24 |

| 図 10. | PWM 応答                                                             | 24 |

| 図 11. | PWM 出力の変化                                                          | 25 |

| 図 12. | セキュリティセッション・マネージメント                                                | 31 |

| 図 13. | ST25DV02K-W1/2 プロトコルタイミング                                          | 37 |

| 図 14. | ST25DV02K-W1/2 状態遷移図                                               | 39 |

| 図 15. | VCD と ST25DV02K-W1/2 の間の Stay Quiet フレーム交換                         | 47 |

| 図 16. | VCD と ST25DV02K-W1/2 の間の Read Single Block フレーム交換                  | 49 |

| 図 17. | VCD と ST25DV02K-W1/2 の間の Write Single Block フレーム交換                 | 50 |

| 図 18. | VCD と ST25DV02K-W1/2 の間の Lock single block フレーム交換                  | 51 |

| 図 19. | VCD と ST25DV02K-W1/2 の間の Read Multiple Block フレーム交換                | 53 |

| 図 20. | VCD と ST25DV02K-W1/2 の間の Select フレーム交換                             | 54 |

| 図 21. | VCD と ST25DV02K-W1/2 の間の Reset to Ready フレーム交換                     | 55 |

| 図 22. | VCD と ST25DV02K-W1/2 の間の Write AFI フレーム交換                          | 56 |

| 図 23. | VCD と ST25DV02K-W1/2 の間の Lock AFI フレーム交換                           | 57 |

| 図 24. | VCD と ST25DV02K-W1/2 の間の Write DSFID フレーム交換                        | 59 |

| 図 25. | VCD と ST25DV02K-W1/2 の間の Lock DSFID フレーム交換                         | 60 |

| 図 26. | VCD と ST25DV02K-W1/2 の間の Get System Info フレーム交換                    | 61 |

| 図 27. | VCD と ST25DV02K-W1/2 の間の Get Multiple Block Security Status フレーム交換 | 63 |

| 図 28. | VCD と ST25DV02K-W1/2 の間の Read Configuration フレーム交換                 | 64 |

| 図 29. | VCD と ST25DV02K-W1/2 の間の Write Configuration フレーム交換                | 65 |

| 図 30. | VCD と ST25DV02K-W1/2 の間の Write Password フレーム交換                     | 67 |

| 図 31. | VCD と ST25DV02K-W1/2 の間の Present Password フレーム交換                   | 69 |

| 図 32. | VCC および PWM_CFG/PWMx_DRIVE による最高温度における RON 標準値の変動                  | 74 |

| 図 33. | SO8N – 8 ピン、4.9 × 6 mm、プラスチック SOP、本体幅 150 ミル、パッケージ概要               | 75 |

| 図 34. | TSSOP8 – 8 ピン Thin Shrink SOP、3 × 6.4 mm、0.65 mm ピッチ、パッケージ概要       | 76 |

# 参考資料

ST25DV02K-W1 ST25DV02K-W2

説明

## 1 説明

ST25DV02K-W1/W2は2Kビットの電気的消去可能メモリ（EEPROM）を搭載したNFC/RFIDタグICデバイスです。

インターフェースを2種備えています。1本目のインターフェースは最大2本の独立パルス幅変調（PWM）出力信号で、2本目は外部のリーダライタ磁界（以下、RFフィールド、または、フィールド）により起電するパッシブRFIDです。

PWM出力はブート時に設定され、RFを通じて動作中に更新可能です。RFとPWMは電源が独立しており、それぞれスタンダードアロン・モードで動作可能です。

ST25DV02K-W1/W2にはユーザデータとして256バイト（64ブロック）のメモリが搭載されています。このメモリはRFインターフェースを通じてアクセス可能であり、ISO/IEC 15693仕様またはNFC Forum Type 5 Tag仕様に準拠しています。

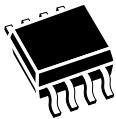

### 1.1 ブロック図

図 1. ブロック図

注： PWM2 は ST25DV02K-W2 でのみ使用できます。

# 参考資料

## 説明

ST25DV02K-W1 ST25DV02K-W2

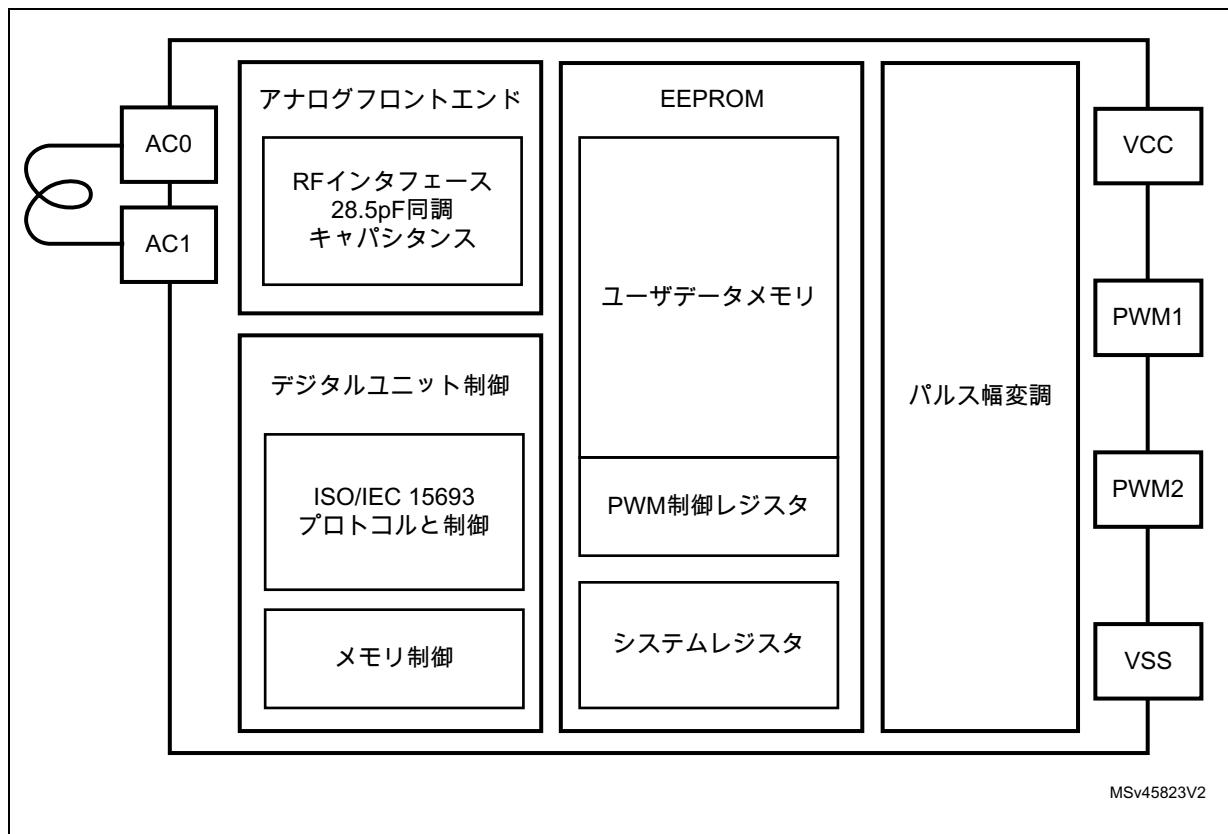

### 1.2 パッケージ

ST25DV02K-W1/2は2種類の異なるパッケージで提供されます。

- SO8N

- TSSOP8

表 1. 信号名

| 信号名                 | 機能       | 方向  |

|---------------------|----------|-----|

| AC0                 | アンテナ・コイル | I/O |

| AC1                 | アンテナ・コイル | I/O |

| V <sub>CC</sub>     | PWM電源    | 電源  |

| PWM1                | PWM出力    | 出力  |

| PWM2 <sup>(1)</sup> | PWM出力    | 出力  |

| V <sub>SS</sub>     | グラウンド    | -   |

1. ST25DV02K-W2 でのみ使用可能です。

図 2. ST25DV02K-W1/28 ピンパッケージの接続

# 参考資料

## 2 信号説明

### 2.1 パルス幅変調出力 (PWM1)

この信号はパルス幅変調 (PWM) 出力を生成します。プッシュ・ブル出力信号で、 $V_{SS}$ と $V_{CC}$ の間で駆動されます。PWM1出力は、ディスエーブルされている限りハイインピーダンス状態となっています。

### 2.2 パルス幅変調出力 (PWM2)

この信号はパルス幅変調出力です。プッシュ・ブル出力信号で、 $V_{SS}$ と $V_{CC}$ の間で駆動されます。PWM2はPWM1から独立しています。PWM2出力は、ST25DV02K-W2でのみ使用可能であり、ディスエーブルされている限りハイインピーダンス状態となっています。

### 2.3 PWM電源 ( $V_{CC}$ )

PWM出力を動作させるためには、このピンを外部DC電源に接続する必要があります。

PWM電源はRF NFCタグ部分から独立しています。NFCタグは、 $V_{CC}$ 電源がいずれの状態であっても動作します。その一方で、PWM出力は、RFフィールドの状態が何であれ、 $V_{CC}$ 電源が供給されると直ちに動作します。

### 2.4 PWMグラウンドリファレンス ( $V_{SS}$ )

$V_{SS}$ は $V_{CC}$ ピンとPWMピンのリファレンスとなります。

### 2.5 アンテナコイル (AC0、AC1)

これらの入力は、ST25DV02K-W1/2デバイスを外部コイルに接続する目的専用で使用されます。他のDCまたはACの経路をAC0またはAC1に接続しないことを推奨します。

正しくチューニングすることで、ISO/IEC 15693プロトコルとISO 18000-3モード1プロトコルを使ってデバイスに電源を供給してアクセスを行うためにコイルが使用されます。

## 3 パワー・マネージメント

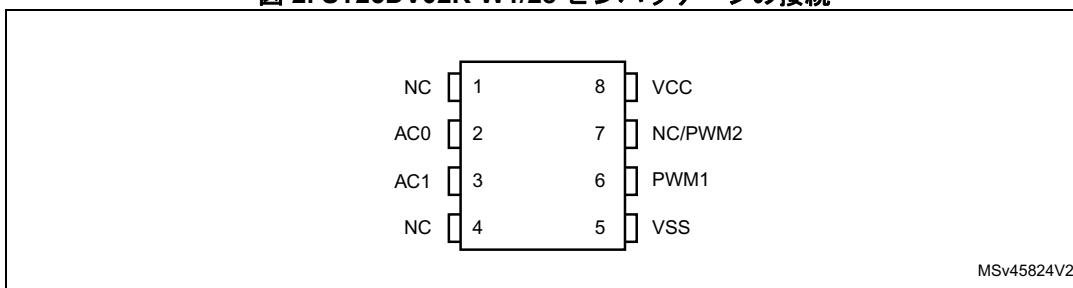

### 3.1 有線インタフェース

#### 動作電源 $V_{CC}$

期待する範囲（クロック安定性、ジッタ）のPWM出力を保証するためには、規定範囲 [ $V_{CC(min)}$ 、 $V_{CC(max)}$ ] 内の有効で安定な $V_{CC}$ 電圧が印加される必要があります。安定したDC電源電圧を維持するためには、 $V_{CC}/V_{SS}$ パッケージピン近傍に適切なコンデンサ（通常、10nFの桁のコンデンサ + 100pFの桁のコンデンサ）を用いて、 $V_{CC}$ ラインのデカップリングを行うことを推奨します。

#### パワーアップ条件

電源がオンになると、 $V_{CC}$ は $V_{SS}$ から $V_{CC}$ に上昇します。 $V_{CC}$ の立ち上がり時間は、1V/ $\mu$ sよりも大幅に高速であってはなりません。

パワーアップ時（ $V_{CC}$ の連続的上昇）、 $V_{CC}$ がパワー・オン・リセット閾値電圧に到達すると直ちに、ST25DV02K-WはPWMブートに入ります。

PWMブートを完了させて有効なPWM出力信号を得るために、 $t_{boot\_PWM}$ 時間が適用されます。

EEPROMに対してRFインターフェースからアクセスする場合には、PWMブートは、EEPROMアクセスの終了を待って開始します。

#### パワーダウン条件

パワーダウン時（ $V_{CC}$ の連続的減少）、 $V_{CC}$ がパワー・オン・リセット閾値電圧未満まで下がった直後から、PWM出力状態は保証されなくなります。

図 3. ST25DV02K-W1/2/パワーアップ/ダウンシーケンス

1. RFインターフェースがオフである場合に有効です。オンである場合には、[セクション 3.3 : RFとPWMブートの優先度](#)に記載された優先度が適用されます。

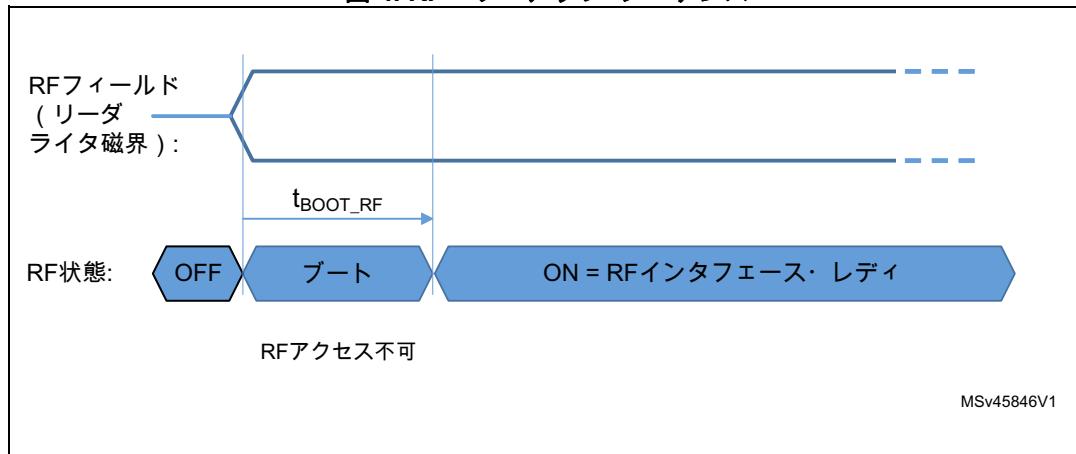

## 3.2 RFインターフェース

### RFモードでセットされたデバイス

RF回路を確実に正しくブートするためには、少なくとも $t_{RF\_ON}$ の時間だけ変調を行わずにRFフィールドをオンにする必要があります。この時間までは、ST25DV02K-W1/2は受信したすべてのRFコマンドを無視します。(図 4 : RFパワーアップ・シーケンスを参照)。

### RFモードでリセットされたデバイス

RF回路を確実に正しくリセットするためには、少なくとも $t_{RF\_OFF}$ の時間だけRFフィールドをオフにする必要があります。

図 4. RFパワーアップ・シーケンス

1. PWM電源 ( $V_{CC}$ ) が $t_{boot\_PWM}$ 以降安定している場合に有効です。そうではない場合には、セクション 3.3: RFとPWMブートの優先度に記載された優先度が適用されます。

## 3.3 RFとPWMブートの優先度

RFインターフェースとPWMインターフェースは独立しています。ただし、以下のようなブート優先度が適用されます。

- RFがブート中またはRFが使用中にPWMブート ( $V_{CC}$ 立ち上がりエッジ) が発生した場合には、RFブートの終了までまたはRF動作の終了 (EOF) までPWMブートは遅延させられます。

- PWMがブート中にRFブート (フィールドオン) が発生した場合には、PWMブートが完了するまでRFブートは遅延させられます。

- PWM動作中 (PWM出力信号が有効) にRFブート (フィールドオン) が発生した場合には、RFブートはセクション 3.2 : RFインターフェースに記述されているように開始します。

**注 :** PWMブートの前 ( $V_{CC}$ 電源がオフで安定) もしくはPWMブートの完了の後 ( $V_{CC}$ 電源がオンで安定) にRFシーケンス (RFフィールドオン、RFコマンドの設定、RFフィールドオフ) を実行することをお勧めします。

# 参考資料

## 4 メモリ・マネージメント

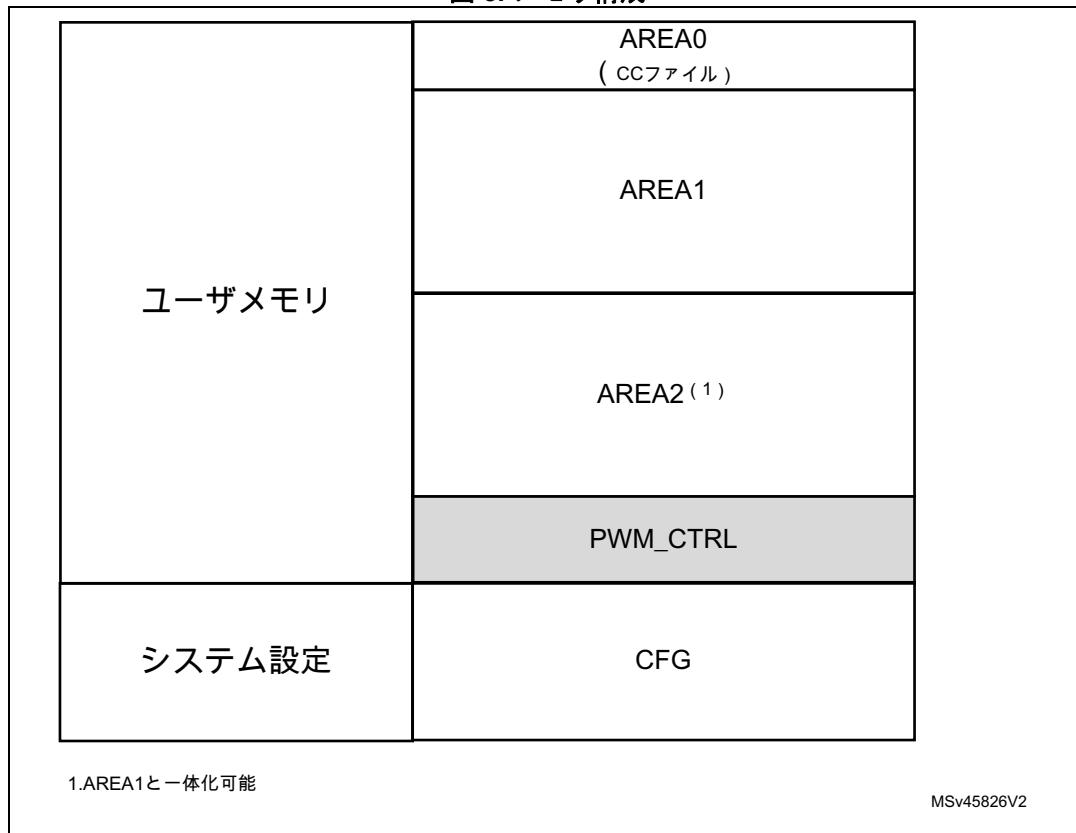

### 4.1 メモリ構成

ST25DV02K-W1/2のメモリは、次のように構成されています。

- ユーザメモリ: 4.2章に記載されている4つの異なる領域から構成されています。これにはユーザデータ用の領域、PWM制御用の領域、ならびに、必要時にNFC T5 CCファイルを格納する領域が含まれています。

- システム設定メモリ: 各種の設定レジスタから構成されており、デバイス設定レジスタ、ISO15693 AFIレジスタとDSFIDレジスタも含まれています。これには、UIDレジスタと各種の保護レジスタも含まれます。詳細については、4.3章を参照してください。

図 5. メモリ構成

## 4.2 ユーザメモリ

ユーザメモリは、アドレス0から始まる4バイトのブロック（ページ）としてアドレス指定されます。

ユーザメモリのブロックは、IC製造工程ですべて00hに初期化されます。

ST25DV02K-W1/2のユーザメモリ領域は、次のように定義されています。

- AREA0はアドレス00hから始まります。常に読み取り可能な1ブロック（4バイト）から構成されており、ロック可能です。AREA0は、NFC Type 5形式に則ったCCファイルの内容のためのものです。ただし、NFC Type 5に合致している必要のないアプリケーションでは、このブロックをどのように使っても構いません。

- AREA1はアドレス01hから始まります。31ブロック（124バイト）から構成されています。専用の1x32ビット長パスワードによって、読み取りや書き込みを制限できます。AREA1はユーザデータ専用です。

- AREA2はアドレス20hから始まります。32ブロック（128バイト）から構成されています。専用の1x32ビット長パスワードによって、読み取りや書き込みを制限できます。AREA2はユーザデータ専用です。

**注：** AREA1とAREA2は、63ブロック（252バイト）の単一領域に統合可能であり、1x64ビット長パスワードによって読み取り禁止や書き込み禁止に設定できます。

- PWM CTRL領域はアドレスF8hから始まります。2ブロック（PWM 1本あたり1ブロック）から構成されており、PWM制御（Enable、Period値、Pulse Width値）専用です。32ビット長パスワードによって、独立して読み取りや書き込みを制限できます。

領域の定義は固定しており、変更できません（AREA1とAREA2の統合を除く）。

[表 2](#)および[表 3](#)に上記のユーザ領域モードを示します。

# 参考資料

表 2. ユーザメモリ4x領域の構成

| ロックアドレス<br>(16進) | データビット[31:1] | コメント                                  | RFコマンド                                                          |

|------------------|--------------|---------------------------------------|-----------------------------------------------------------------|

| 0                | ユーザ0 (4xバイト) | AREA0 = CCファイル<br>(NFC T5アプリケーションの場合) |                                                                 |

| 1                |              |                                       |                                                                 |

| 2                |              |                                       |                                                                 |

| ...              |              |                                       |                                                                 |

| 1E               |              |                                       |                                                                 |

| 1F               |              |                                       |                                                                 |

| 20               |              |                                       |                                                                 |

| ...              |              |                                       |                                                                 |

| ...              |              |                                       |                                                                 |

| 3F               |              |                                       |                                                                 |

| -                | -            | -                                     |                                                                 |

| F8               | PWM1 制御      | AREA2                                 | Read Single Block<br>Read Multiple Blocks<br>Write Single Block |

| F9               | PWM2 制御      |                                       |                                                                 |

表 3. ユーザメモリ3x領域の構成

| ロックアドレス<br>(16進) | データビット[31:0] | コメント                                  | RFコマンド                                                          |

|------------------|--------------|---------------------------------------|-----------------------------------------------------------------|

| 0                | ユーザ0 (4xバイト) | AREA0 = CCファイル<br>(NFC T5アプリケーションの場合) |                                                                 |

| 1                |              |                                       |                                                                 |

| 2                |              |                                       |                                                                 |

| ...              |              |                                       |                                                                 |

| 1E               |              |                                       |                                                                 |

| 1F               |              |                                       |                                                                 |

| 20               |              |                                       |                                                                 |

| ...              |              |                                       |                                                                 |

| ...              |              |                                       |                                                                 |

| 3F               |              |                                       |                                                                 |

| -                | -            | -                                     |                                                                 |

| F8               | PWM1 制御      | AREA2と統合されたAREA1                      | Read Single Block<br>Read Multiple Blocks<br>Write Single Block |

| F9               | PWM2 制御      |                                       |                                                                 |

# 参考資料

## 4.3 システム設定メモリ

ユーザメモリの他に、ST25DV02K-W1/2にはシステム構成メモリの中に位置するレジスタのセットが含まれています。レジスタの内容はブートシーケンス中に読み取られ、ST25DV02K-W1/2の基本的な動作が定義されます。

これらのレジスタの一部は、レジスタのアドレスとして機能する識別子を用いて、Read ConfigurationコマンドとWrite Configurationコマンドでアクセス可能です。

表 4 に、アクセス可能性（読み取り/書き込み）と関連する条件を含む、システム設定レジスタの完全なマップを示します。詳細は、関係するレジスタの説明表に記載されています。

表 4. システム設定メモリマップ

| RFアクセス |                                   | 静的レジスタ                               |                                  |

|--------|-----------------------------------|--------------------------------------|----------------------------------|

| アドレス   | タイプ                               | 名前                                   | 機能                               |

| 00h    | RW <sup>(1)</sup>                 | 表 10 : A1SA                          | AREA1セキュリティ属性                    |

| 01h    | RW <sup>(1)</sup>                 | 表 11 : A2SA                          | AREA2セキュリティ属性                    |

| 02h    | RW <sup>(1)</sup>                 | 表 12 : APSA                          | 領域PWM_CTRLセキュリティ属性               |

| 03h    | RW <sup>(1)</sup>                 | 表 7 : PWM_CFG                        | PWM設定とRFインターフェースとの共存             |

| 04h    | RW <sup>(1)</sup>                 | 表 13 : LOCK_CFG                      | 設定レジスタの永久ロック                     |

| N/A    | R <sup>(2)</sup> W <sup>(3)</sup> | 表 14 : AREA0/1/2とPWM_CTRLのLOCK_BLOCK | ブロックの書き込み保護 (1ブロックあたり1xロックビット)   |

| N/A    | WO <sup>(4)</sup>                 | 表 20 : LOCK_DSFID                    | DSFIDロック状態                       |

| NA     | WO <sup>(5)</sup>                 | 表 21 : LOCK_AFI                      | AFIロック状態                         |

| N/A    | RW <sup>(4)</sup>                 | 表 22 : DSFID                         | DSFID値                           |

| N/A    | RW <sup>(5)</sup>                 | 表 23 : AFI                           | AFI値                             |

| N/A    | RO                                | 表 24 : IC_REF                        | ICリファレンス値                        |

| NA     | RO                                | 表 25 : UID                           | 固有識別子 (UID、8 バイト)                |

| N/A    | WO <sup>(6)</sup>                 | 表 15 : PWD_PWM                       | PWM制御領域のセキュリティセッションパスワード (4バイト)  |

| N/A    | WO <sup>(6)</sup>                 | 表 16 : PWD_A1                        | ユーザAREA1のセキュリティセッションパスワード (4バイト) |

| N/A    | WO <sup>(6)</sup>                 | 表 17 : PWD_A2                        | ユーザAREA2のセキュリティセッションパスワード (4バイト) |

| N/A    | WO <sup>(6)</sup>                 | 表 18 : PWD_CFG                       | 設定のセキュリティセッションパスワード (4バイト)       |

- RF設定セキュリティセッションがオープンされていて、設定がロックされていない (LOCK\_CFG レジスタが0) 場合に、書き込みアクセスが許可されています。

- LOCK\_BLOCKの内容は、ブロックのロックセキュリティ状態を読み取ることによってのみ読み取り可能です。

- ブロックがロック済みではない (対応するセキュリティセッションがオープンされている + 前のLOCK\_BLOCKコマンドによってブロックがロック済みではない) 場合の書き込みアクセス

- 前のLOCK\_DSFIDコマンドによってDSFIDがロック済みではない場合の書き込みアクセス

- 前のLOCK\_AFIコマンドによってAFIがロック済みではない場合の書き込みアクセス

- 対応するセキュリティセッションがオープンされている場合に限る書き込みアクセス

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

## 5 固有の特徴

ST25DV02K-W1/2は以下の特徴を備えています。

- パルス幅変調出力

- データ保護

- TruST25™デジタル署名

- デバイスパラメータレジスタ

これらの一部では、制御レジスタがシステム設定領域の中にあり、Read\_ConfigurationコマンドまたはWrite\_Configurationコマンドを使用する必要があります。設定パスワード（PWD\_CFG）の提示によってアクセス権が許可されており、（LOCK\_CFG=1によって）システム設定がロック済みではない場合にのみ、更新が可能です。

設定レジスタに有効な書き込みアクセスがあると、新しい設定が直ちに適用されます。

# 参考資料

## 5.1 パルス幅変調出力

ST25DV02K-W1/2は、パルス幅変調（PWM）出力を最大2本備えています。この章では、各PWMの設定方法と使用方法を説明します。

### 5.1.1 パルス幅変調レジスタ

表 5. PWM1\_CTRL<sup>(1)</sup>

|           |             |                                                                                                                                                                                |              |

|-----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| RF        | コマンド        | Read Single Block (コマンドコード20h) @F8h<br>Read Multiple Blocks (コマンドコード23h) @F8h<br>Lock Single Block (コマンドコード22h) @F8h<br>Write Single Block (コマンドコード21h) @F8h                   |              |

|           | タイプ         | APSAレジスタの内容、ロックロックステータス、セキュリティロックステータス（オープンまたはクローズ）によってRとW保護可能                                                                                                                 |              |

| ビット       | 名前          | 機能                                                                                                                                                                             | ファクトリ<br>設定値 |

| b14 ~ b0  | PWM1_PERIOD | PWM Period値:<br>PWM1出力信号の周期は、次の式から計算されます。<br>$Period = 'PWM1_PERIOD' \times PWMres$ (表 93 : PWM 特性参照)<br>PWM1_PERIODの値は、[512 : 32767]の範囲としてください。 <sup>(2)</sup>                | 0000h        |

| b15       | RFU         | 将来の使用のために予約済み。                                                                                                                                                                 | 0b           |

| b30 ~ b16 | PWM1_PULSEW | PWM Pulse Width値:<br>PWM1出力信号のパルス幅の時間は、次の式から計算されます。<br>$Pulse\ Width = 'PWM1_PULSEW' \times PWMres$ (表 93 : PWM 特性参照)<br>PWM1_PULSEWの値は、[0 : 32767]の範囲としてください <sup>(2)</sup> 。 | 00000h       |

| b31       | PWM1_ENABLE | PWM出力信号のイネーブル                                                                                                                                                                  | 0b           |

1. PWM1\_CTRLレジスタについては、表 2 : ユーザメモリ4x領域の構成および表 3 : ユーザメモリ3x領域の構成を参照してください。

2. PWM1\_PERIODとPWM1\_PULSEWの値については、セクション 5.1.2 : パルス幅変調機能の説明を参照してください。

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

表 6. PWM2\_CTRL<sup>(1) (2)</sup>

|           |             |                                                                                                                                                                              |          |

|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| RF        | コマンド        | Read Single Block (コマンドコード20h) @F9h<br>Read Multiple Blocks (コマンドコード23h) @F9h<br>Lock Single Block (コマンドコード22h) @F9h<br>Write Single Block (コマンドコード21h) @F9h                 |          |

|           | タイプ         | APSAレジスタの内容、ブロックロックステータス、セキュリティロックステータス（オープンまたはクローズ）によってRとW保護可能                                                                                                              |          |

| ビット       | 名前          | 機能                                                                                                                                                                           | ファクトリ設定値 |

| b14 ~ b0  | PWM2_PERIOD | PWM Period値:<br>PWM2出力信号の周期は、次の式から計算されます。<br>$Period = 'PWM2_PERIOD' \times PWMres$ (表 93 : PWM 特性参照)<br>PWM2_PERIODの値は、[512 : 32767]の範囲としてください。 <sup>(3)</sup>              | 0000h    |

| b15       | RFU         | 将来の使用のために予約済み。                                                                                                                                                               | 0b       |

| b30 ~ b16 | PWM2_PULSEW | PWM Pulse Width値:<br>PWM2出力信号のパルス幅の時間は、次の式から計算されます。<br>$Pulse Width = 'PWM2_PULSEW' \times PWMres$ (表 93 : PWM 特性参照)<br>PWM2_PULSEWの値は、[0 : 32767]の範囲としてください。 <sup>(3)</sup> | 00000h   |

| b31       | PWM2_ENABLE | PWM出力信号のイネーブル                                                                                                                                                                | 0b       |

1. PWM1\_CTRLレジスタについては、表 2 : ユーザメモリ4x領域の構成および表 3 : ユーザメモリ3x領域の構成を参照してください。

2. 単一PWMデバイスバージョン (ST25DV02K-W1) の場合、PWM2\_CTRLレジスタの値はファクトリ設定値（全ビット = 0）のままでください。

3. PWM2\_PERIODとPWM2\_PULSEWの値については、セクション 5.1.2 : パルス幅変調機能の説明を参照してください。

# 参考資料

ST25DV02K-W1 ST25DV02K-W2

固有の特徴

表 7. PWM\_CFG<sup>(1)</sup>

|         |              |                                                                                                                                                                                                                                                       |              |

|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| RF      | コマンド         | Read Configuration (コマンドコードA0h) @03h<br>Write Configuration (コマンドコードA1h) @03h                                                                                                                                                                         |              |

|         | タイプ          | 常にR。設定セキュリティセッションがオープンされていて、設定がロックされていない場合にW。                                                                                                                                                                                                         |              |

| ビット     | 名前           | 機能                                                                                                                                                                                                                                                    | ファクトリ<br>設定値 |

| b1 ~ b0 | PWM1_DRIVE   | PWM出力ドライバトリミング:<br>– 00 : フルパワー出力が利用可能<br>– 01 : フルパワー出力の¼が利用可能<br>– 10 : フルパワー出力の½が利用可能<br>– 11 : フルパワー出力の¾が利用可能                                                                                                                                     | 00b          |

| b3 ~ b2 | PWM2_DRIVE   | – 11 : フルパワー出力の¾が利用可能                                                                                                                                                                                                                                 | 00b          |

| b6 ~ b4 | DUALITY_MNGT | PWMとRFインターフェースの共存（両方のPWMに適用）:<br>– 000 : PWM出力とRFインターフェースが完全に共存<br>– 1xx: RFコマンドの間はPWM出力はHiZ設定 <sup>(2)</sup><br>– 01x: RFコマンドの間は、PWM出力のパワーがフルパワーの¼に低下 <sup>(2)</sup><br>– 0x1: RFコマンドの間は (2)、PWMデューティーサイクルはそのままでPWM周波数がLow_Freq <sup>(3)</sup> 以下に低下 | 000b         |

| b7      | RFU          | 将来の使用のために予約済み。                                                                                                                                                                                                                                        | 0b           |

1. PWM\_CFGレジスタについては、表 4: システム設定メモリマップを参照してください。

2. RFコマンド中とは、SOF（フレーム開始）からAnswerの終わりまでを指します。

3. セクション 8: デバイスパラメータを参照してください。

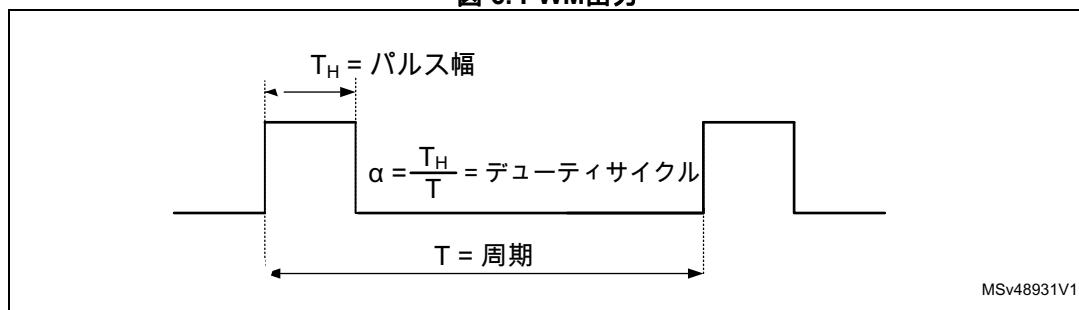

## 5.1.2 パルス幅変調機能の説明

PWM出力は、次の2つのパラメータによって特徴が記述されます。

- 周期（または周波数）

- 信号がHigh状態のときの時間%を示すデューティーサイクル

図 6. PWM出力

PeriodとPulse Widthは、Enable信号とともにPWM出力の定義と制御に用いられ、PWM出力をHiZ状態とすることを可能とします。

PWM段には、 $V_{CC}/V_{SS}$ 電源ピンから電源供給されます。RFインターフェースによって電源供給されるのではありません。PWMは、 $V_{CC}/V_{SS}$ ピンから電源が供給されている限り、RFインターフェースがオフであっても動作します。同様に、RFインターフェースは $V_{CC}/V_{SS}$ 電源がなくとも動作します。

PWMの出力段はプッシュプルとなっています。

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

$V_{CC}$ パワーオン/パワーオフと関係するPWM出力状態については、パワー・マネージメントの章を参照してください。

### PWM制御（PWM1\_CTRLとPWM2\_CTRL）

PWMを制御するレジスタは、専用パスワード（PWD\_PWM）とアクセス権レジスタ（APSA）で保護可能な、専用のPWM\_CTRLユーザ領域でアクセス可能です。PWM出力には、それぞれ専用の独立したPWM\_CTRLレジスタ（PWM1\_CTRLとPWM2\_CTRL）があります。

- PWM\_CTRLレジスタの内容

これによってユーザは、Period値とPulse Width値、Enableビットにアクセスできます。PeriodパラメータとPulse Widthパラメータは、各15ビットのPWMx\_PERIODとPWMx\_PULSEWにコード化されています。

PWM出力の状態は、以下の3個のパラメータから定義されます。

表 8. PWM出力パラメータ

| PWM_EN | PWMx_PERIOD        | PWMx_PULSEW | PWM出力状態                                                                            | コメント          |

|--------|--------------------|-------------|------------------------------------------------------------------------------------|---------------|

| 0      | x                  | x           | HiZ                                                                                | 無効            |

| 1      | P<br>[512 : 32767] | 0           | 0                                                                                  | $< V_{OL}$    |

|        |                    | $0 < W < P$ |  | PWMデューティーサイクル |

|        |                    | $\geq P$    | 1                                                                                  | $> V_{OH}$    |

内蔵オシレータによってPWM分解能がPWMresに固定されます（表 93：PWM特性参照）。PWMの出力周期とパルス幅は、この分解能の値の倍数として定義されます。

- Period = PWMres x PWMx\_PERIOD

- Pulse Width = PWMres x PWMx\_PULSEW

PWM出力機能は、PWMx\_PERIODが512から32767までの範囲で保証されていますが、これはPeriodの範囲が32 usから2048 usまで（周波数範囲として31250 Hzから488.3 Hz）であることを示しています。この範囲におけるPWM出力の分解能は、次のとおりです。

表 9. PWM出力分解能

| PWM出力周波数<br>(Hz) | PWMx_PERIODに使用される<br>ビット数 | PWM分解能 =<br>PWMx_PULSEWのコード化に<br>利用できるビット数 |

|------------------|---------------------------|--------------------------------------------|

| 31250            | 9                         | 9                                          |

| 15625            | 10                        | 10                                         |

| 7813             | 11                        | 11                                         |

| 3906             | 12                        | 12                                         |

| 1953             | 13                        | 13                                         |

| 977              | 14                        | 14                                         |

| 488              | 15                        | 15                                         |

# 参考資料

## ST25DV02K-W1 ST25DV02K-W2

## 固有の特徴

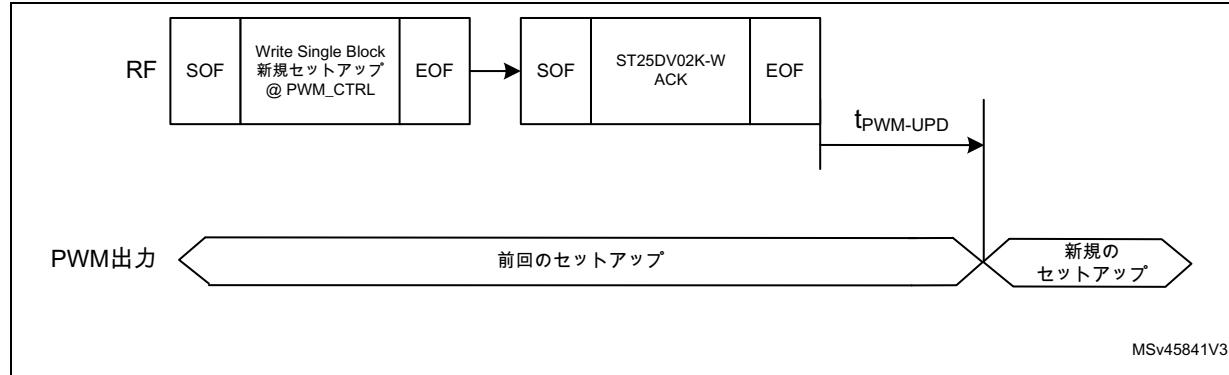

- PWM\_CTRLレジスタの更新

RFコマンド (Write Single Block @ F8h/F9hとACK応答) が正常に処理されてPWM\_CTRLレジスタが更新されると、関係するPWM出力が次のように変化します。

図 7. PWM出力の変化

PWM\_CTRLレジスタにはアンチ・ティアリングの仕組みはありません。PWM\_CTRLレジスタへの書き込みアクセスは、RFフィールドが安定しており、VCC状態が一定しているとき（オンまたはオフ）に行う必要があります。そうしないと、RF書き込み操作が正常に完了しないおそれがあり、レジスタの内容が失われたり破壊されたりして、別の書き込み操作が必要となることがあります。

### PWM設定 (PWM\_CFG)

PWMのオプションを設定するレジスタは、システム設定領域の中でアクセス可能です。

RF感度レベルが高く、(構造により) PWM出力によりスイッ칭ノイズが生成されるため、PWMインターフェースとRFインターフェースの共存を強化するために、さまざまなPWMパラメータの調整が水晶されます。

- PWM出力ドライバのトリミング

PWMプッシュプル出力段は、デフォルトで  $I_{\text{MAX}}^{(a)}$  までの駆動が可能です。PWM\_CFG トリミングレジスタ (PWM1に対してはPWM\_CFGのビットb1 ~ b0、PWM2に対してはPWM\_CFGのビットb3 ~ b2) によって、アプリケーションがフルパワーを必要としない場合に、出力の駆動能力を独立して減らすことができます。

a. セクション 8: デバイスパラメータ を参照してください。

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

図 8. PWM出力ドライバのトリミング

| PWM_CFG[1:0]/<br>PWM_CFG[3:2]/ | PWM1/PWM2出力のドライブ能力（シンクとソース） |

|--------------------------------|-----------------------------|

| 00b                            | $I_{MAX}^{(1)}$ （デフォルト設定）   |

| 01b                            | $I_{MAX}^{(1)}$ の75%        |

| 10b                            | $I_{MAX}^{(1)}$ の50%        |

| 11b                            | $I_{MAX}^{(1)}$ の25%        |

1. セクション 8 : デバイスパラメータを参照してください。

- PWM出力のRFインターフェースとの共存

PWM出力とRFインターフェースの共存が不可能である場合、PWM\_CFG Duality\_Mngt レジスタ（PWM\_CFGのビットb6 ~ b4）によってRFインターフェースに対するPWMノイズの影響を押さえて共存できるようにすることができます。このレジスタは、PWM1とPWM2両方に適用されます（適用可能な場合）。

図 9. PWM出力のRFインターフェースとの共存

| PWM_CFG[6:4] | 共存設定                                                                                                                          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| 000b         | PWMとRFは正常に同時に動作（デフォルト）                                                                                                        |

| 1xxb         | RFコマンドの間はPWM出力をHiZ状態に設定します。                                                                                                   |

| 01xb         | RFコマンドの間はPWM出力の駆動能力を最小パワーレベル（最大出力パワー レベルの25%）まで減少させます。                                                                        |

| 0x1b         | （デューティーサイクルは保ちながら）PWM出力周波数を減少させて規定値（Low_Freq、表 93 : PWM特性参照）以下とし、VCD RF感度領域の外とします。このオプションは、PWM出力周波数が規定周波数値を上回っている場合にのみ適用されます。 |

「PWM出力をHiZ状態にする」は排他的なオプションですが、「PWM駆動能力の減少」と「周波数の減少」のオプションは必要であれば組み合わせ可能です。

共存オプションは、PWM出力信号への影響を最小限とするため、「RFコマンド中」にのみ適用されます。「RFコマンド中」の期間とは、リクエストコマンドのフレーム開始で始まり、対応する応答のフレーム終了までとして定義されます。

図 10. PWM応答

# 参考資料

ST25DV02K-W1 ST25DV02K-W2

固有の特徴

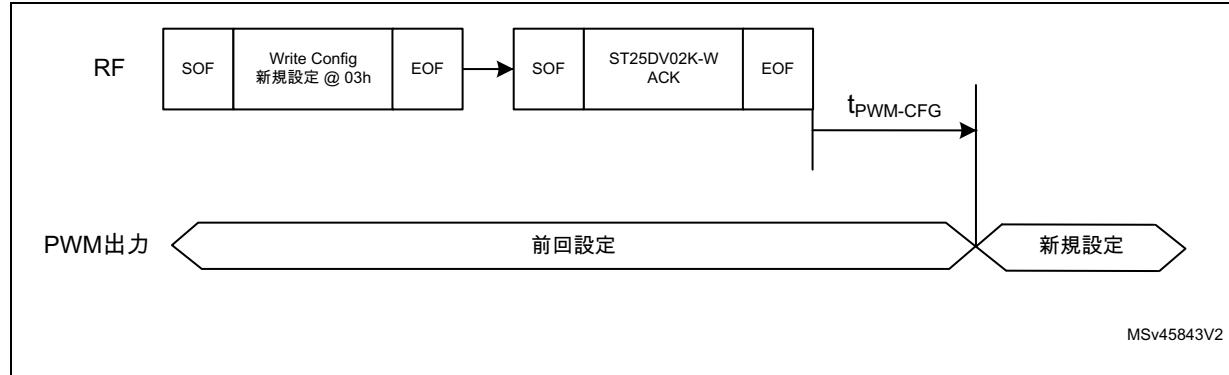

- PWM\_CFGレジスタの更新

RFコマンド（Write\_Config @ 03hとACK応答）が正常に処理されてPWM\_CFGレジスタが更新されると、PWM出力が次のように変化します。

図 11. PWM出力の変化

PWM\_CFGレジスタにはアンチ・ティアリングの仕組みはありません。PWM\_CFGレジスタへの書き込みアクセスは、RFフィールドが安定しており、VCC状態が一定しているとき（オンまたはオフ）に行う必要があります。そうしないと、RF書き込み操作が正常に完了しないおそれがあり、レジスタの内容が失われたり破壊されたりして、別の書き込み設定操作が必要となることがあります。

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

### 5.2 データ保護

ST25DV02K-W1/2には、セキュリティセッションをアンロックするパスワードに基づく特別なデータ保護機構が備わっています。4 x 32ビット長パスワードがEEPROMに格納されており、その対象は以下のとおりです。

- AREA1のパスワード

- AREA2のパスワード (AREA1とAREA2が統合されている場合には、対応する領域は64ビット長パスワードによって保護されます)

- PWM制御領域のパスワード

- システム設定領域のパスワード

ユーザメモリを読み取りアクセスと書き込みアクセスから保護可能です。システム設定は、書き込みアクセスから常に保護されています。

以下のセクションに記載されているように、他のロック機構（ロックブロック、ロックAFI、ロックDSFID）にも対応しています。

#### 5.2.1 データ保護レジスタ

表 10. A1SA<sup>(1)</sup>

| RF      | コマンド             | Read Configuration (コマンドコードA0h) @00h<br>Write Configuration (コマンドコードA1h) @00h                                                                                                                                                                                                                      | ファクトリ<br>設定値 |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|         | タイプ              | 常にR。設定セキュリティセッションがオープンされていて、設定がロックされていない場合にW。                                                                                                                                                                                                                                                      |              |

| ビット     | 名前               | 機能                                                                                                                                                                                                                                                                                                 |              |

| b1 ~ b0 | RW_PROTECTION_A1 | AREA1のアクセス権:<br>00 : 読取りは常に許可 / 書込みは常に許可<br>01 : 読取りは常に許可 / AREA1ユーザセキュリティセッションがオープンされている (= 正しいAREA1パスワードが示されている) 場合にのみ書込みを許可<br>10 : AREA1ユーザセキュリティセッションがオープンされている (正しいAREA1パスワードが示されている) 場合にのみ読み取りと書き込みを許可<br>11 : AREA1ユーザセキュリティセッションがオープンされている (正しいAREA1パスワードが示されている) 場合にのみ読み取りを許可 / 書込みは常に禁止 | 00b          |

| b2      | MEM_ORG          | ユーザメモリ分割:<br>0: ユーザメモリが4つの領域 (AREA0/1/2とPWM_CTRL) に分割<br>1: ユーザメモリが3つの領域 (AREA0/1とPWM_CTRL) に分割 = AREA1とAREA2は単一のAREA1に統合された領域の場合、アクセス権としてRW_PROTECTION_A1レジスタが適用されます。                                                                                                                             | 1b           |

| b7 ~ b3 | RFU              | -                                                                                                                                                                                                                                                                                                  | 00000b       |

1. A1SAレジスタについては、表 4 : システム設定メモリマップを参照してください。

# 参考資料

ST25DV02K-W1 ST25DV02K-W2

固有の特徴

表 11. A2SA<sup>(1)</sup>

|         |                  |                                                                                                                                                                                                                                                                                                                                                              |          |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| RF      | コマンド             | Read Configuration (コマンドコードA0h) @01h<br>Write Configuration (コマンドコードA1h) @01h                                                                                                                                                                                                                                                                                |          |

|         | タイプ              | 常にR。設定セキュリティセッションがオープンされていて、設定がロックされていない場合にW。                                                                                                                                                                                                                                                                                                                |          |

| ビット     | 名前               | 機能                                                                                                                                                                                                                                                                                                                                                           | ファクトリ設定値 |

| b1 ~ b0 | RW_PROTECTION_A2 | AREA2のアクセス権:<br>00 : 読取りは常に許可 / 書込みは常に許可<br>01 : 読取りは常に許可。AREA2ユーザセキュリティセッションがオープンされている（正しいAREA2パスワードが示されている）場合にのみ書込みが許可<br>10 : AREA2ユーザセキュリティセッションがオープンされている（正しいAREA2パスワードが示されている）場合にのみ読み取りと書込みが許可<br>11 : AREA2ユーザセキュリティセッションがオープンされている（正しいAREA2パスワードが示されている）場合にのみ読み取りが許可 / 書込みは常に禁止<br>単一の AREA1 領域に統合された AREA1 + AREA2 の場合、RW_PROTECTION_A2ビットは使用されません。 | 00b      |

| b7 ~ b2 | RFU              | -                                                                                                                                                                                                                                                                                                                                                            | 00000b   |

1. A2SAレジスタについては、表 4 : システム設定メモリマップを参照してください。

表 12. APSA<sup>(1)</sup>

|         |                  |                                                                                                                                                                                                                                                                                                                          |          |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| RF      | コマンド             | Read Configuration (コマンドコードA0h) @02h<br>Write Configuration (コマンドコードA1h) @02h                                                                                                                                                                                                                                            |          |

|         | タイプ              | 常にR。設定セキュリティセッションがオープンされていて、設定がロックされていない場合にW。                                                                                                                                                                                                                                                                            |          |

| ビット     | 名前               | 機能                                                                                                                                                                                                                                                                                                                       | ファクトリ設定値 |

| b1 ~ b0 | RW_PROTECTION_AP | 領域PWM_CTRLアクセス権:<br>00 : 読取りと書込みは常に許可<br>01 : 読取りは常に許可。領域PWM_CTRLユーザセキュリティセッションがオープンされている (= 正しい領域PWM_CTRLパスワードが示されている) 場合にのみ書込みが許可<br>10 : 領域PWM_CTRLユーザセキュリティセッションがオープンされている (正しい領域PWM_CTRLパスワードが示されている) 場合にのみ読み取りと書込みが許可<br>11 : 領域PWM_CTRLユーザセキュリティセッションがオープンされている (正しい領域PWM_CTRLパスワードが示されている) 場合にのみ読み取りが許可。書込みは常に禁止 | 00b      |

| b7 ~ b2 | RFU              | -                                                                                                                                                                                                                                                                                                                        | 00000b   |

1. APSAレジスタについては、表 4 : システム設定メモリマップを参照してください。

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

表 13. LOCK\_CFG<sup>(1)</sup>

|         |          |                                                                                                                                                                                |              |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| RF      | コマンド     | Read Configuration (コマンドコードA0h) @04h<br>Write Configuration (コマンドコードA1h) @04h                                                                                                  |              |

|         | タイプ      | 常にR。設定セキュリティセッションがオープンされていて、設定がロックされていない場合にW。                                                                                                                                  |              |

| ビット     | 名前       | 機能                                                                                                                                                                             | ファクトリ<br>設定値 |

| b0      | LOCK_CFG | ロック設定レジスタ:<br>0 : 設定レジスタがアンロックされています。<br>1 : 設定レジスタは永久に書き込みにロックされています。<br>Write_Configコマンドによってアクセス可能な設定レジスタのみ対象となります。パスワード、AFI、DSFID、ブロックロック、AFIロックとDSFIDロックは、この仕組みの対象ではありません。 | 0b           |

| b7 ~ b1 | RFU      | -                                                                                                                                                                              | 0000000b     |

- LOCK\_CFGレジスタについては、表 4 : システム設定メモリマップを参照してください。

表 14. AREA0/1/2とPWM\_CTRLのLOCK\_BLOCK<sup>(1)</sup>

|     |            |                                                                                 |                                                                                                                                        |  |

|-----|------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| RF  | コマンド       | Read lock block                                                                 | Read Block (コマンドコード20h) @ブロックアドレス<br>Read Multi Block (コマンドコード23h) @ブロックアドレス<br>Get Multi Block Security Status (コマンドコード2Ch) @ブロックアドレス |  |

|     |            | Write lock block                                                                | Lock single Block (コマンドコード22h) @ブロックアドレス                                                                                               |  |

|     | タイプ        | 常にR。対応するブロックがロックされていない場合にのみW。                                                   |                                                                                                                                        |  |

| ビット | 名前         | 機能                                                                              | ファクトリ<br>設定値                                                                                                                           |  |

| N/A | LOCK_BLOCK | 対応するブロックの書き込みアクセスのロック:<br>0 : ブロックは書き込みではロックされません。<br>1 : ブロックは書き込みで永久にロックされます。 | 0b                                                                                                                                     |  |

- LOCK\_BLOCKレジスタについては、表 4 : システム設定メモリマップを参照してください。

表 15. PWD\_PWM (1)

|          |         |                                                    |              |

|----------|---------|----------------------------------------------------|--------------|

| RF       | コマンド    | 読み取り不可<br>Write Password (コマンドコードB1h)、Pwd_Id = 00h |              |

|          | タイプ     | 読み取り不可。PWM_CTRL領域セキュリティセッションがオープンされている場合に限りW       |              |

| ビット      | 名前      | 機能                                                 | ファクトリ<br>設定値 |

| b31 ~ b0 | PWD_PWM | PWM_CTRL領域のパスワード値                                  | 00000000h    |

- PWD\_PWMレジスタについては、表 4 : システム設定メモリマップを参照してください。

# 参考資料

ST25DV02K-W1 ST25DV02K-W2

固有の特徴

表 16. PWD\_A1<sup>(1)</sup>

|          |        |                                                                                                 |              |

|----------|--------|-------------------------------------------------------------------------------------------------|--------------|

| RF       | コマンド   | 読み取り不可<br>Write Password (コマンドコードB1h)、Pwd_Id = 01h                                              |              |

|          | タイプ    | 読み取り不可。AREA1セキュリティセッションがオープンされている場合に限りW                                                         |              |

| ビット      | 名前     | 機能                                                                                              | ファクトリ<br>設定値 |

| b31 ~ b0 | PWD_A1 | MEM_ORG=0の場合: ユーザAREA1のパスワード値<br>MEM_ORG=1の場合: ユーザAREA1 (AREA2と統合) の LSB パスワード値 (64 ビット中の32ビット) | 00000000h    |

1. PWM\_A1レジスタについては、[表 4 : システム設定メモリマップ](#)を参照してください。

表 17. PWD\_A2<sup>(1)</sup>

|          |        |                                                                                                                                  |              |

|----------|--------|----------------------------------------------------------------------------------------------------------------------------------|--------------|

| RF       | コマンド   | 読み取り不可<br>Write Password (コマンドコードB1h)、Pwd_Id = 02h                                                                               |              |

|          | タイプ    | 読み取り不可<br>以下の場合に限りW<br>– AREA2セキュリティセッションがオープンされている (MEM_ORG=0の場合)<br>– AREA1セキュリティセッションがオープンされている (MEM_ORG=1、AREA1+AREA2が統合の場合) |              |

| ビット      | 名前     | 機能                                                                                                                               | ファクトリ<br>設定値 |

| b31 ~ b0 | PWD_A2 | MEM_ORG = 0の場合: ユーザAREA2のパスワード値<br>MEM_ORG = 1の場合: ユーザAREA1 (AREA2と統合) のMSB パスワード値 (64 ビット中の32ビット)                               | 00000000h    |

1. PWM\_A2レジスタについては、[表 4 : システム設定メモリマップ](#)を参照してください。

表 18. PWD\_CFG<sup>(1)</sup>

|          |         |                                                    |              |

|----------|---------|----------------------------------------------------|--------------|

| RF       | コマンド    | 読み取り不可<br>Write Password (コマンドコードB1h)、Pwd_Id = 03h |              |

|          | タイプ     | 読み取り不可。システム設定領域セキュリティセッションがオープンされている場合に限りW         |              |

| ビット      | 名前      | 機能                                                 | ファクトリ<br>設定値 |

| b31 ~ b0 | PWD_CFG | 設定領域のパスワード値                                        | 00000000h    |

1. PWM\_CFGレジスタについては、[表 4 : システム設定メモリマップ](#)を参照してください。

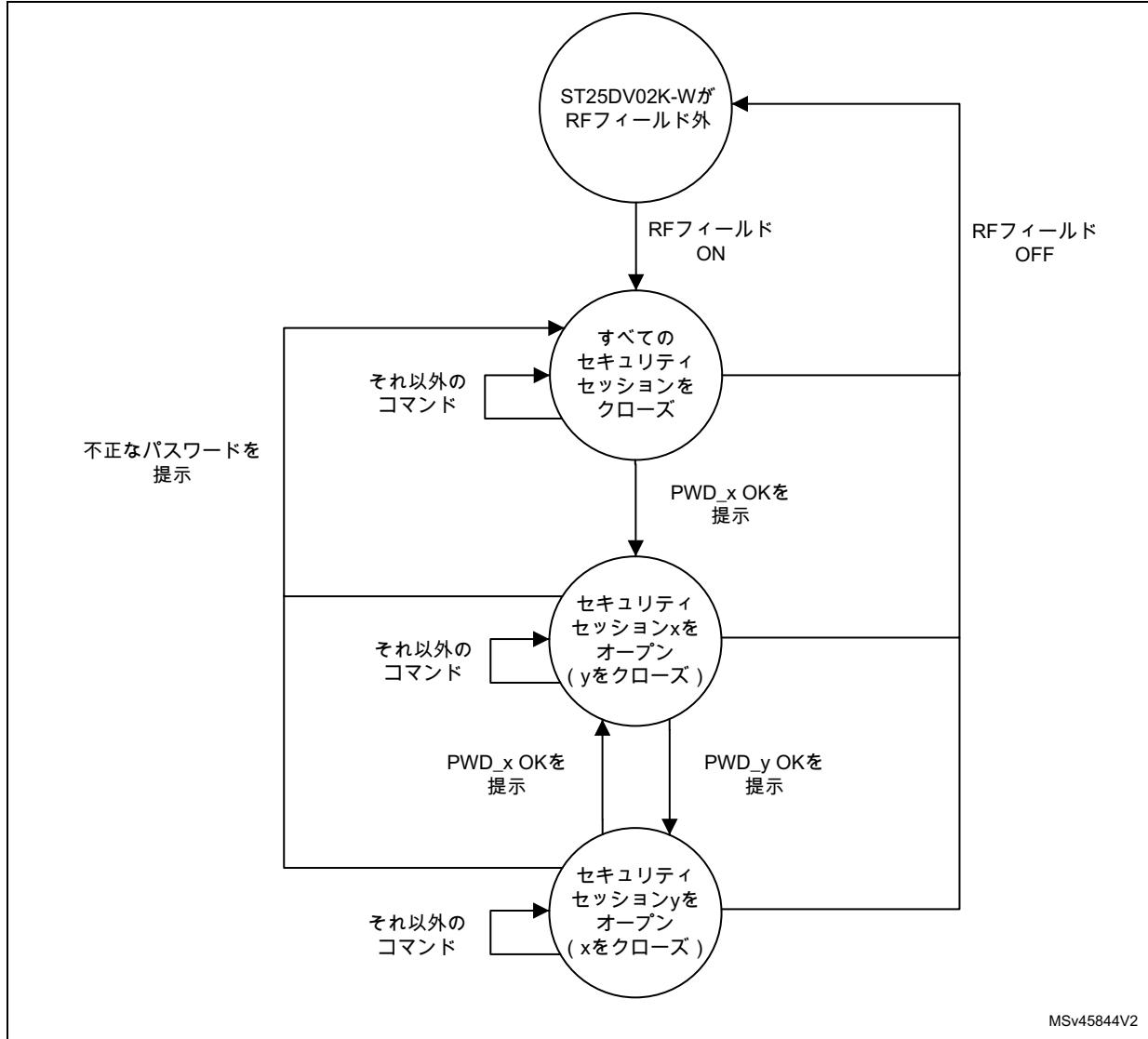

### 5.2.2 パスワードとセキュリティセッション

ST25DV02K-W1/2は、ユーザメモリとシステム設定レジスタを保護可能です。ユーザは、対応するパスワードを使って、セキュリティセッションをオープンすることにより保護されたデータにアクセスできます。

[表 19](#)に示すように、セキュリティセッションには2種類存在します。

表 19. セキュリティセッションのタイプ

| セキュリティセッション | オープンのために提示するもの              | セキュリティセッションのオープンからクローズまで与えられる権利                                                |

|-------------|-----------------------------|--------------------------------------------------------------------------------|

| ユーザ         | PWD_A1<br>PWD_A2<br>PWD_PWM | ユーザは、AiSAレジスタに定義された対応するユーザメモリにアクセスできます。<br>ユーザは、オープンされたセッションに対応するパスワードを更新できます。 |

| 設定          | PWD_CFG                     | ユーザは、設定レジスタに書き込みできます（永久にロックされていない場合）。<br>ユーザは、PWM_CFGパスワードを更新できます。             |

AREA1とAREA2が独立している場合 (MEM\_ORG = 0b)、AREA1のパスワードとAREA2のパスワードはそれぞれ32ビット長となります。

AREA1とAREA2が単一領域に統合された場合 (MEM\_ORG = 1b)、統合された領域のパスワードは64ビット長 (32ビットのAREA1パスワード + 32ビットのAREA2パスワード) となります。

ST25DV02K-W1/2のパスワード・マネージメントは、以下の2つのコマンドに基づいています。

- Write Password (コードB1h) ([セクション 6.4.17 : Write Password](#)参照)

- Present Password (コードB3h) ([セクション 6.4.18 : Present Password](#)参照)

利用可能な4つのパスワードのいずれかに対して、以下の3つの操作が可能です。

- セキュリティセッションのオープン: パスワード識別子 (PWD\_PWMには00h、PWD\_A1には01h、PWD\_A2には02h、PWD\_CFGには03h) と対応する有効なパスワードとともにPresent\_Passwordコマンドを使用します。

- パスワードの書き込み: パスワード識別子 (PWD\_PWMには00h、PWD\_A1には01h、PWD\_A2には02h、PWD\_CFGには03h) と対応する有効なパスワードとともにPresent\_Passwordコマンドを使用します。次に、同じパスワード識別子と新しいパスワードで、Write\_Passwordコマンドを使用します。

- セキュリティセッションのクローズ: 現在のセキュリティセッションをクローズするために、ユーザは次のオプションのいずれかを選択できます。

- RFフィールドからタグを削除

- 不正なパスワードでPresent\_Passwordコマンドを使用

- Present\_Passwordコマンドを使用して別領域のセキュリティセッションをオープン (異なるパスワード識別子を使用) 新しいセキュリティセッション (ユーザまたは設定) をオープンすると、(新規オープンがエラーになったとしても) 前にオープンしていたセッションは自動的にクローズします。

注: 統合されたAREA1 + AREA2の場合 (MEM\_ORG=1b)、セキュリティセッションのオープンは異なります。

- 1回のPresent\_Password操作で64ビット長パスワードが提示されます。

- Write\_Passwordコマンドは、今までどおりに32ビット長パスワードに適用されます。したがって、64ビットを更新するには、AREA1 パスワード ID と AREA2 パスワード ID を用いてWrite\_Password操作を2回行う必要があります。

# 参考資料

ST25DV02K-W1 ST25DV02K-W2

固有の特徴

図 12にセキュリティセッションをオープン/クローズする仕組みを示します。

図 12. セキュリティセッション・マネージメント

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

### 5.2.3 ユーザメモリの保護

- AREA0（ブロック0の單一ブロックから構成）：

- 常に読み取り可能です。

- Lock Single Blockコマンドを発行することによってのみ個別に書き込みロック可能です。このロックは永久的です。

- ユーザはブロック0のロックにパスワードは不要です。

- 設定がロックされていても（LOCK\_CFG=1）、ブロック0はロック可能です。

- AREA1、AREA2、PWM\_CTRL領域：

- 保護は、対応するAiSAレジスタ（A1SA、A2SA、APSA）によって独立して定義されます。利用可能な読み取り保護と書き込み保護の詳細については、[表 10 : A1SA](#)と[表 11 : A2SA](#)と[表 12 : APSA](#)を参照してください。

- AiSAレジスタの更新時には、レジスタへの書き込みが完了すると直ちに新しい保護値が有効となります。

ファクトリ出荷時には、ユーザ領域は保護されていません。

#### ユーザメモリのブロックまたはバイトのセキュリティ状態の取得

ユーザは、次のコマンドを発行することにより、ブロックセキュリティ状態を読み取ることができます。

- Get Multiple Blocks Security Statusコマンド

- オプションフラグを1にセットして、Read Single Blockコマンド

- オプションフラグを1にセットして、Read Multiple Blocksコマンド

ST25DV02K-W1/2は、ISO 15693規格に定義されたLock\_bitフラグが含まれるブロックセキュリティ状態で応答します。このlock\_bitフラグは、ブロックが書き込みに対してロックされている場合に1にセットされます。

書き込みに対するこのようなロックは、以下のいろいろな方法で行うことができます。

- ブロックのいずれかのLock\_Blockビットが（永久的に）セットされている。

- セキュリティセッションが書き込み保護付きでクローズされた（RW\_PROTECTION\_Ax = 01bまたは10bまたは11b）

- セキュリティセッションが常時書き込み禁止の保護付きでオープンされた（RW\_PROTECTION\_Ax = 11b）

### 5.2.4 システム設定メモリ保護

デフォルトでシステムメモリは書き込み保護されています。

システム設定レジスタへの書き込みアクセスをイネーブルするには、ユーザは、有効なパスワード PWM\_CFG (Id=03h) を提示して設定セキュリティセッションをオープンする必要があり、システム設定は永久的にロックされていてはなりません（LOCK\_CFG=00h）。

デフォルトでユーザは、パスワードとLOCK\_DSFIIDとLOCK\_AFIを除く、すべてのシステム設定レジスタを読み取ることができます。

# 参考資料

設定のロック:

- システム設定レジスタへの書き込みアクセスは、LOCK\_CFG レジスタに 01h を書き込むことによって永久的にロックできます。

- LOCK\_CFG=01hであると、設定セキュリティセッションをオープンした後であっても、ユーザはシステム設定をアンロックできません（ロックは確定的）。

- システム設定がロックされているとき（LOCK\_CFG=01h）には、今までどおりにパスワード（PWD\_A1、PWD\_A2、PWD\_PWM、PWD\_CFG）の変更は可能です。

- システム設定がロックされているとき（LOCK\_CFG=01h）には、今までどおりにAFI レジスタとDSFIDレジスタをロックできます（後述）。

デバイス識別レジスタ:

- AFI レジスタとDSFID レジスタは、ユーザは、それぞれLock AFIコマンドかLock DSFIDコマンドを発行して独立してロックできます。ロックは確定的です。一度ロックされると、AFI レジスタとDSFID レジスタはアンロックできません。

- その他のデバイス識別レジスタ（IC\_REF、UID）は読み取り専用レジスタです。

## 5.3 TruST25™ デジタル署名

ST25DV02K-Wは、デバイス個体毎に固有なデジタル署名に基づいてデバイスの真正性を検証可能なTruST25™ デジタル署名機能に対応しています。

TruST25™ソリューションは、デバイスの署名の生成、格納、確認のためにSTマイクロエレクトロニクスによって導入されたセキュアな工程とツールを包含するものです。

その使用方法の詳細については、NDAのもとで入手可能な「ANxxxx – ST25DV02K-W TruST25™ Digital Signature」を参照してください。この資料を入手するには、お近くのSTマイクロエレクトロニクスの営業所までお問い合わせください。

## 5.4 デバイスパラメータレジスタ

表 20. LOCK\_DSFID<sup>(1)</sup>

| ビット     | コマンド       | Lock DSFID（コマンドコード2Ah）                    |          |

|---------|------------|-------------------------------------------|----------|

|         | タイプ        | DSFIDがロックされていない場合WO                       |          |

|         | 名前         | 機能                                        | ファクトリ設定値 |

| b0      | LOCK_DSFID | 0 : DSFIDはロックされません。<br>1 : DSFIDはロックされます。 | 0b       |

| b7 ~ b1 | RFU        | -                                         | 0000000b |

1. LOCK\_DSFID レジスタについては、表 4 : システム設定メモリマップを参照してください。

# 参考資料

## 固有の特徴

ST25DV02K-W1 ST25DV02K-W2

表 21. LOCK\_AFI<sup>(1)</sup>

| ビット     | コマンド     | Lock AFI (コマンドコード28h)                 |          |

|---------|----------|---------------------------------------|----------|

|         | タイプ      | AFIがロックされていない場合W0                     |          |

|         | 名前       | 機能                                    | ファクトリ設定値 |

| b0      | LOCK_AFI | 0 : AFIはロックされません。<br>1 : AFIはロックされます。 | 0b       |

| b7 ~ b1 | RFU      | -                                     | 0000000b |

1. LOCK\_AFIレジスタについては、表 4 : システム設定メモリマップを参照してください。

表 22. DSFID<sup>(1)</sup>

| ビット     | コマンド  | Inventory (コマンドコード01h)<br>Get System Info (コマンドコード2Bh)<br>Write DSFID (コマンドコード28h) |          |

|---------|-------|------------------------------------------------------------------------------------|----------|

|         | タイプ   | 常にR、DSFIDがロックされていない場合W                                                             |          |

|         | 名前    | 機能                                                                                 | ファクトリ設定値 |

| b7 ~ b0 | DSFID | ISO/IEC 15693データ格納フォーマット識別子                                                        | 00h      |

1. DSFIDレジスタについては、表 4 : システム設定メモリマップを参照してください。

表 23. AFI<sup>(1)</sup>

| ビット     | コマンド | Inventory (コマンドコード01h)<br>Get System Info (コマンドコード2Bh)<br>Write AFI (コマンドコード27h) |          |

|---------|------|----------------------------------------------------------------------------------|----------|

|         | タイプ  | 常にR、AFIがロックされていない場合W                                                             |          |

|         | 名前   | 機能                                                                               | ファクトリ設定値 |

| b7 ~ b0 | AFI  | ISO/IEC 15693アプリケーションファミリ識別子                                                     | 00h      |

1. AFIレジスタについては、表 4 : システム設定メモリマップを参照してください。

表 24. IC\_REF<sup>(1)</sup>

| ビット     | コマンド   | Get System Info (コマンドコード2Bh) |                       |

|---------|--------|------------------------------|-----------------------|

|         | タイプ    | RO                           |                       |

|         | 名前     | 機能                           | ファクトリ設定値              |

| b7 ~ b0 | IC_REF | ISO/IEC 15693 ICリファレンス       | 38/39h <sup>(2)</sup> |

1. IC\_REFレジスタについては、表 4 : システム設定メモリマップを参照してください。

2. 38hはST25DV02K-W1に適用され、39hはST25DV02K-W2に適用されます。

# 参考資料

ST25DV02K-W1 ST25DV02K-W2

固有の特徴

表 25. UID<sup>(1)</sup>

| ビット     | コマンド | Inventory (コマンドコード01h)<br>Get System Info (コマンドコード2Bh) |                        |

|---------|------|--------------------------------------------------------|------------------------|

|         | タイプ  | RO                                                     |                        |

|         | 名前   | 機能                                                     | ファクトリ設定値               |

| b7 ~ b0 | UID  | ISO/IEC 15693 UIDバイト0 (LSB)                            | ICメーカーシリアル番号           |

| b7 ~ b0 |      | ISO/IEC 15693 UIDバイト1                                  |                        |

| b7 ~ b0 |      | ISO/IEC 15693 UIDバイト2                                  |                        |

| b7 ~ b0 |      | ISO/IEC 15693 UIDバイト3                                  |                        |

| b7 ~ b0 |      | ISO/IEC 15693 UIDバイト4                                  |                        |

| b7 ~ b0 |      | ISO/IEC 15693 UIDバイト5ST製品コード                           | 38/39 <sup>(2)</sup> h |

| b7 ~ b0 |      | ISO/IEC 15693 UIDバイト6IC Mfgコード                         | 02h                    |

| b7 ~ b0 |      | ISO/IEC 15693 UIDバイト7 (MSB)                            | E0h                    |

1. UIDレジスタについては、[表 4 : システム設定メモリマップ](#)を参照してください。

2. 38hはST25DV02K-W1に適用され、39hはST25DV02K-W2に適用されます。

# 参考資料

## 6 RF動作

非接触交換は、ISO/IEC 15693とNFC Forum Type 5のタグによって規定されているとおりに行われます。ST25DV02K-W1/2は、13.56 MHzの搬送波を通じて通信を行い、振幅変調（ASK: 振幅シフトキーイング）された受信信号から受信データが復調されます。受信したASK波は、1/256パルスコーディングモードを用いた1.6 Kbit/sのデータレート、または、1/4パルスコーディングモードを用いた26 Kbit/sのデータレートで10%変調または100%変調されます。

出力データは、423 kHzと484 kHzのサブキャリア周波数の1つまたは2つのマンチェスタコーディングを使用して、ST25DV02K-W1/2の負荷変動によって生成されます。低データレートモードでは6.6 Kbit/s、高データレートモードでは26 Kbit/sで、データがST25DV02K-W1/2から転送されます。

ST25DV02K-W1/2は、RFパワーおよび信号インターフェースならびにアンチコリジョンと送信のプロトコルについて、ISO/IEC 15693とNFC Forum Type 5 Tag仕様に準拠しています。

### 6.1 RF通信

#### 6.1.1 ISO/IEC 15693デバイスに対するアクセス

「リーダライタ（リーダ）」とST25DV02K-W1/2の間のダイアログは以下のように行われます。

- リーダの動作フィールドによるST25DV02K-W1/2のアクティベーション

- リーダによるコマンド送信（ST25DV02K-W1/2はキャリア振幅変調を検出）

- 負荷変調を使用してST25DV02K-W1/2がレスポンスを送信

これらの操作は、下記の電力伝送と通信信号のインターフェースを使用します。この技術は、RTF（リーダトークファースト）と呼ばれます。

#### 動作フィールド

ST25DV02K-W1/2は、[表 92 : RF特性](#)に規定された電磁場Hの最小値と最大値の間で連続的に動作しています。リーダはこの限界値の中でフィールドを生成する必要があります。

#### 電力伝送

ST25DV02K-W1/2とリーダの中のカップリングアンテナを通じて、13.56 MHzのRFでST25DV02K-W1/2に電力が伝送されます。リーダの動作フィールドは、ST25DV02K-W1/2のアンテナにおいてAC電圧に変換され、整流、フィルタリングと内部で安定化が行われます。通信中には、この受信信号の振幅変調（ASK）がASK復調器によって復調されます。

#### 周波数

ISO 15693規格には、動作フィールドのキャリア周波数( $f_C$ )は13.56 MHz  $\pm$  7 kHzと規定されています。

# 参考資料

## 6.2 RFプロトコル

### 6.2.1 説明

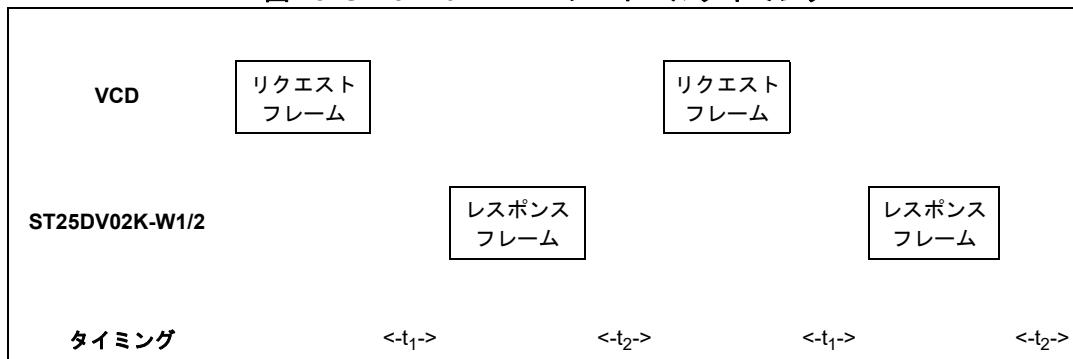

伝送プロトコル（または単純に「プロトコル」）には、VCD（近傍型結合装置、リーダライタ）とVICC（近傍型 IC カード）の間で双方向に命令とデータを交換するために使用される手順が規定されています。この手順は、「VCD トーカスファースト」のコンセプトに基づいています。ST25DV02K-W1/2はVICCとして振る舞います。

このことは、VCDから送信された命令を受信して正しくデコードしない限り、ST25DV02K-W1/2は送信を開始しないことを意味しています。このプロトコルは、以下の交換に基づいています。

- VCDからST25DV02K-W1/2へのリクエスト

- ST25DV02K-W1/2からVCDへのレスポンス

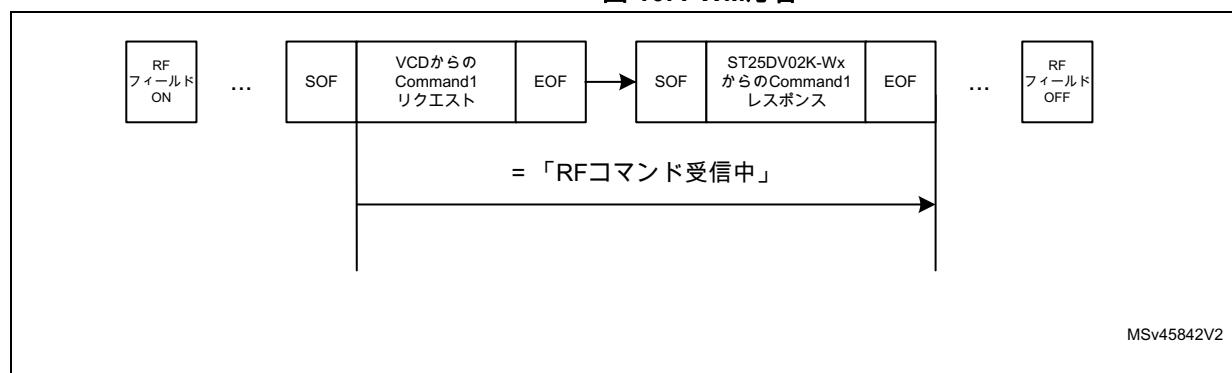

リクエストとレスポンスはそれぞれ1つのフレームの中に収められています。フレームは、フレーム開始 (SOF) とフレーム終了 (EOF) で区切られます。

図 13. ST25DV02K-W1/2プロトコルタイミング

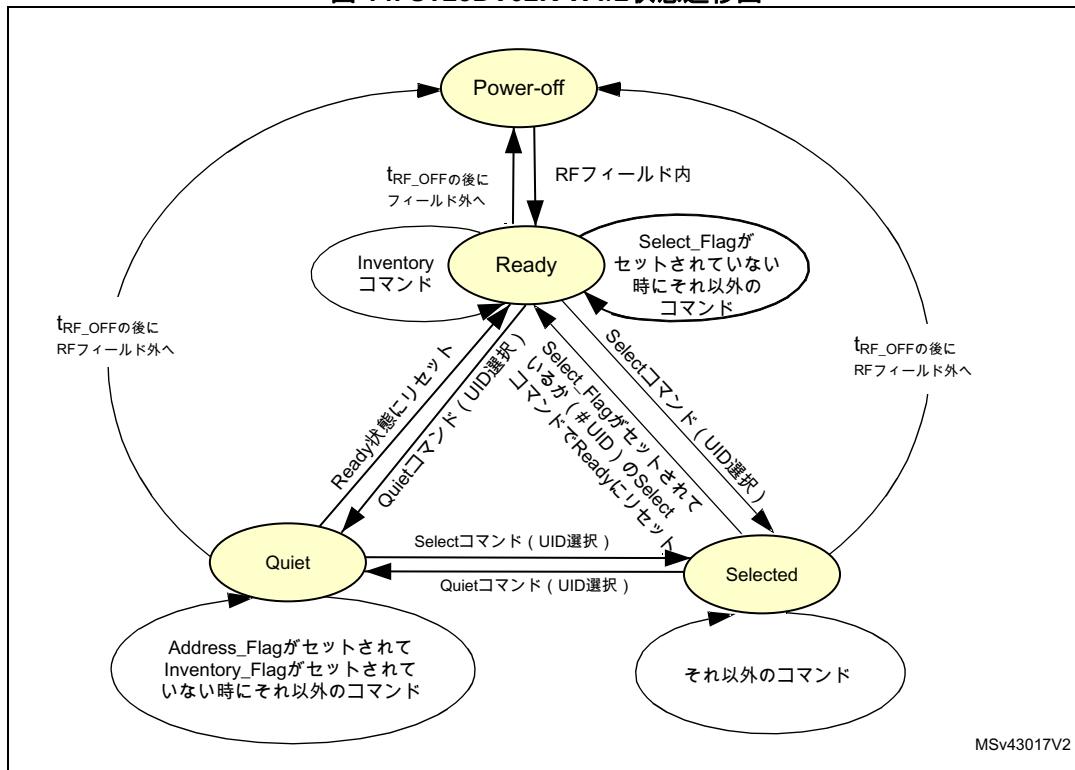

### 6.2.2 対応状態

- Power-off

- Ready

- Quiet

- Selected

これらの状態の間の遷移は、[図 14 : ST25DV02K-W1/2状態遷移図](#)と[表 26 : Request\\_flagsによるST25DV02K-W1/2の応答](#)に規定されています。

#### Power-off状態

ST25DV02K-W1/2は、VCDから十分なエネルギーを受信していないときにRF Power-off状態となります。

#### Ready状態

ST25DV02K-W1/2は、VCDから十分なエネルギーを受信しているときにReady状態となります。Ready状態のときには、ST25DV02K-W1/2はSelect\_flagがセットされていないあらゆるリクエストに応答します。

# 参考資料

## Quiet状態

Quiet状態のときには、ST25DV02K-W1/2は、Inventoryリクエストを除き、Address\_flagがセットされているあらゆるリクエストに応答します。

## Selected状態

Selected状態のときには、ST25DV02K-W1/2はすべてのモードのあらゆるリクエストに応答します（セクション 6.2.3 : モード参照）。

- Select\_flagがセットされている選択モードでのリクエスト

- UIDが一致する場合のアドレスモードでのリクエスト

- 一般リクエスト用のモードである場合の非アドレスモードでのリクエスト

表 26. Request\_flagsによるST25DV02K-W1/2の応答

| フラグ                                                          | Address_flag   |                    | Select_flag   |                   |

|--------------------------------------------------------------|----------------|--------------------|---------------|-------------------|

|                                                              | 1<br>Addressed | 0<br>Non addressed | 1<br>Selected | 0<br>Non selected |

| ST25DV02K-W1/2 は Ready 状態か Selected状態 (Quiet状態のデバイスは応答せず)    | -              | X                  | -             | X                 |

| ST25DV02K-W1/2はSelected状態                                    | -              | X                  | X             | -                 |

| ST25DV02K-W1/2 は Ready 状態か Quiet状態かSelected状態 (UIDに一致するデバイス) | X              | -                  | -             | X                 |

| エラー (03h) または無レスポンス (コマンド依存)                                 | X              | -                  | X             | -                 |

# 参考資料

図 14. ST25DV02K-W1/2状態遷移図

1. タグが $t_{RF\_OFF}$ 以上の時間フィールド外であると、ST25DV02K-W1/2はPower Off状態に戻ります。

この状態遷移方式の目的は、同時にSelected状態となるST25DV02K-W1/2を1つだけとすることです。

Select\_flagが1にセットされると、リクエストにはUIDが含まれません。

address\_flagが0にセットされると、リクエストにはUIDが含まれません。

## 6.2.3 モード

「モード」という用語は、リクエストを実行するST25DV02K-W1/2デバイスの集合を規定するためにリクエストに使用される仕組みを意味します。

### アドレスモード

Address\_flag が1にセットされると（アドレスモード）、リクエストにはアドレス指定されたST25DV02K-W1/2の固有識別子（UID）が含まれます。

Address\_flagが1にセットされたリクエストを受信したあらゆるST25DV02K-W1/2は、受信したUIDを自分のものと比較します。一致した場合、ST25DV02K-W1/2はコマンド説明に規定されているようにリクエストを実行し（可能な場合）、VCDにレスポンスを返します。

UIDが一致しない場合には、Silentモードのままとなります。

### 非アドレスモード（一般リクエスト）

Address\_flagが0にクリアされると（非アドレスモード）、リクエストにはUIDが含まれません。

# 参考資料

## 選択モード

Select\_flagが1にセットされると（選択モード）、リクエストにはUIDが含まれません。Select\_flagが1にセットされたリクエストを受信した選択状態のST25DV02K-W1/2は、コマンド説明に規定されているようにリクエストを実行し、VCDIにレスポンスを返します。

選択状態にあるST25DV02K-W1/2のみが、Select\_flagが1にセットされたリクエストに応答します。

このシステム設計によって、同時にSelect状態となるST25DV02K-W1/2は1つだけであることが保証されます。

### 6.2.4 リクエストフォーマット

リクエストは以下から構成されます。

- SOF

- フラグ

- コマンドコード

- パラメータとデータ

- CRC

- EOF

表 27. 一般リクエストフォーマット

| S<br>O<br>F | Request_flags | コマンドコード | パラメータ | データ | 2 バイト<br>CRC | E<br>O<br>F |

|-------------|---------------|---------|-------|-----|--------------|-------------|

|-------------|---------------|---------|-------|-----|--------------|-------------|

### 6.2.5 リクエストフラグ

あるリクエストの中で、ST25DV02K-W1/2によって行われる動作と対応するフィールドの有無が、「フラグ」フィールドによって規定されます。

フラグフィールドは8ビットで構成されます。リクエストフラグのビット3（Inventory\_flag）によって、MSB側4ビット（ビット5～8）の内容が定義されます。ビット3がリセット（0）されているときには、ビット5～8によってST25DV02K-W1/2の選択基準が定義されます。ビット3がセット（1）されているときには、ビット5～8によってST25DV02K-W1/2のInventoryパラメータが定義されます。

表 28. リクエストフラグ1～4の定義

| ビット<br>No. | フラグ                            | レベル | 説明                                 |

|------------|--------------------------------|-----|------------------------------------|

| ビット 1      | Subcarrier_flag <sup>(1)</sup> | 0   | ST25DV02K-W1/2は単一のサブキャリア周波数を使用します。 |

|            |                                | 1   | ST25DV02K-W1/2は2つのサブキャリアを使用します。    |

# 参考資料

表 28. リクエストフラグ1～4の定義 (continued)

| ビット No. | フラグ                           | レベル | 説明                                                                 |

|---------|-------------------------------|-----|--------------------------------------------------------------------|

| ビット 2   | Data_rate_flag <sup>(2)</sup> | 0   | 低データレートが使用されます。                                                    |

|         |                               | 1   | 高データレートが使用されます。                                                    |

| ビット 3   | Inventory_flag                | 0   | フラグ5～8の意味は表 29 : inventory_flag (ビット3) = 0の場合のリクエストフラグ5～8に示されています。 |

|         |                               | 1   | フラグ5～8の意味は表 30 : inventory_flag (ビット3) = 1の場合のリクエストフラグ5～8に示されています。 |

| ビット 4   | Protocol_extension_flag       | 0   | プロトコルフォーマット拡張なし                                                    |

|         |                               | 1   | プロトコルフォーマット拡張。将来の使用のために予約済み。                                       |

1. Subcarrier\_flagは、ST25DV02K-W1/2とVCDとの間の通信に関連しています。

2. Data\_rate\_flagは、ST25DV02K-W1/2とVCDとの間の通信に関連しています。

表 29. inventory\_flag (ビット3) = 0の場合のリクエストフラグ5～8

| ビット No. | フラグ                  | レベル | 説明                                                                                     |

|---------|----------------------|-----|----------------------------------------------------------------------------------------|

| ビット 5   | 選択フラグ <sup>(1)</sup> | 0   | リクエストは、Address_flagの設定に従ってST25DV02K-W1/2によって実行されます。                                    |

|         |                      | 1   | リクエストは、Selected状態にあるST25DV02K-W1/2のみによって実行されます。                                        |

| ビット 6   | アドレスフラグ              | 0   | リクエストはアドレス指定されていません。UIDは存在しません。リクエストは、すべてのST25DV02K-W1/2によって実行されます。                    |

|         |                      | 1   | リクエストはアドレス指定されています。UIDが存在します。リクエストは、UIDがリクエストに指定されたUIDと一致するST25DV02K-W1/2のみによって実行されます。 |

| ビット 7   | オプションフラグ             | 0   | オプションは有効ではありません。                                                                       |

|         |                      | 1   | オプションが有効です。                                                                            |

| ビット 8   | RFU                  | 0   | -                                                                                      |

1. Select\_flagが1にセットされている場合、Address\_flagは0にセットされ、UIDフィールドはリクエストの中に存在しません。

表 30. inventory\_flag (ビット3) = 1の場合のリクエストフラグ5～8

| ビット No. | フラグ         | レベル | 説明               |

|---------|-------------|-----|------------------|

| ビット 5   | AFIフラグ      | 0   | AFIフィールドは存在しません。 |

|         |             | 1   | AFIフィールドが存在します。  |

| ビット 6   | Nb_slotsフラグ | 0   | 16スロット           |

|         |             | 1   | 1スロット            |

| ビット 7   | オプションフラグ    | 0   | -                |