## 高性能HF/NFCリーダライタ 1.4W出力とVHBR、AAT機能付き

データシート

### 機能

- ISO 18092 (NFCIP-1) アクティブP2P

- ISO14443A、ISO14443B、FeliCa™

- VHBR(3.4 Mbit/s PICCからPCDへのフレーミング、6.8 Mbit/s アナログフロントエンドとPCDからPICCへのフレーミング) に対応

- 静電容量センシング - ウェイクアップ

- 自動アンテナ・チューニング (AAT) によりアンテナLCタンクのチューニングが可能

- 自動復調指数調整

- 自動選択対応AM・PM (I/Q) 復調チャネル

- DPO (ダイナミック・パワー・アウトプット)

- 差動出力時は最大1.4 W

- 半自動およびAGC (自動ゲイン・コントロール)

- MIFARE™ Classic互換フレームやその他のカスタム・フレームに対応するためのトランスペアレント・モードとストリーム・モード

- シングルエンド・モードでアンテナ2本を駆動可能

- 13.56 MHzまたは27.12 MHz (高速起動対応) の水晶で動作可能な発振器入力

- 96バイトFIFO付き6 Mbit/s SPI

- 2.4 ~ 5.5 V対応の広い電源電圧範囲

- 広温度範囲: -40 ~ 125 °C

- QFN32、5 mm x 5 mmパッケージ

### 説明

ST25R3911Bは、高集積度のNFC イニシエータ / HF リーダライタICであり、アナログ・フロントエンド (AFE) ならびに、ISO 18092 (NFCIP-1) イニシエータとISO 18092 (NFCIP-1) P2Pアクティブ・ターゲット、ISO 14443A/B (VHBR含む)、FeliCa™のための高度に統合されたデータ・フレーミング・システムが含まれています。外部マイクロコントローラにフレーミングを実装することにより (ストリーム・モードとトランスペアレントモード)、MIFARE™ Classicのような標準以外のカスタム・プロトコルを実装することもできます。

ST25R3911Bは、最高のRF性能と柔軟性が低消費電力との組み合わせで求められる、NFCシステムインチップに最適な製品です。

自動アンテナ・チューニング (AAT) 技術により、このデバイスは、金属環境などにおかれた、直接駆動アンテナを組み込むアプリケーションに最適化が可能です。ST25R3911Bは、HFリーダライタICの領域の中で、低インピーダンス (1Ω) 差動アンテナ・ドライバを2個搭載している唯一のデバイスです。

ST25R3911Bには、このデバイスを低消費電力用途に最適化する複数の機能が含まれています。リーダライタ磁界をオンにすることなく、カードの存在を検出する、低消費電力の静電容量センサが含まれています。カードの存在は、アンテナのLCタンクにおける信号の振幅か位相を測定し、格納されている基準値と比較することによっても検出できます。このデバイスには、低消費電力のRC発振器とウェイクアップ・タイマも含まれており、規定時間後にシステムを立ち上げて、低消費検出方法 (容量、位相、または振幅) の1つ以上を用いて、タグの存在を確認するために使用できます。

ST25R3911Bは、広い電源電圧範囲 (2.4 ~ 5.5 V) で動作するように設計されており、ペリフェラル・インターフェースIOピンは、1.65 ~ 5.5 Vの電源電圧範囲に対応しています。

# 目次

|          |                            |           |

|----------|----------------------------|-----------|

| <b>1</b> | <b>機能概要</b>                | <b>10</b> |

| 1.1      | ブロック図                      | 10        |

| 1.1.1    | トランスマッタ                    | 11        |

| 1.1.2    | レシーバ                       | 11        |

| 1.1.3    | 位相・振幅検出器                   | 11        |

| 1.1.4    | A/D コンバータ                  | 11        |

| 1.1.5    | 静電容量センサ                    | 11        |

| 1.1.6    | 外部フィールド検出器                 | 12        |

| 1.1.7    | 水晶発振器                      | 12        |

| 1.1.8    | 電源レギュレータ                   | 12        |

| 1.1.9    | POR とバイアス                  | 12        |

| 1.1.10   | RC 発振器とウェイクアップ・タイマ         | 12        |

| 1.1.11   | ISO-14443 と NFCIP-1 フレーミング | 13        |

| 1.1.12   | FIFO                       | 13        |

| 1.1.13   | コントロール・ロジック                | 13        |

| 1.1.14   | SPI                        | 13        |

| 1.2      | アプリケーション情報                 | 13        |

| 1.2.1    | 動作モード                      | 15        |

| 1.2.2    | トランスマッタ                    | 15        |

| 1.2.3    | レシーバ                       | 16        |

| 1.2.4    | 静電容量センサ                    | 21        |

| 1.2.5    | ウェイクアップ・モード                | 23        |

| 1.2.6    | 水晶発振器                      | 24        |

| 1.2.7    | タイマ                        | 25        |

| 1.2.8    | A/D コンバータ                  | 27        |

| 1.2.9    | 位相振幅検出器                    | 27        |

| 1.2.10   | 外部フィールド検出器                 | 28        |

| 1.2.11   | 電源システム                     | 29        |

| 1.2.12   | 外部マイクロコントローラとの通信           | 31        |

| 1.2.13   | ダイレクト・コマンド                 | 41        |

| 1.2.14   | Start Timer コマンド群          | 50        |

| 1.2.15   | Test Access                | 51        |

| 1.2.16   | 起動シーケンス                    | 52        |

| 1.2.17   | リーダ動作                      | 52        |

|        |                                      |    |

|--------|--------------------------------------|----|

| 1.2.18 | FeliCa™ リーダ・モード .....                | 58 |

| 1.2.19 | NFCIP-1 動作 .....                     | 58 |

| 1.2.20 | AM 変調度：設定と補正 .....                   | 63 |

| 1.2.21 | アンテナの同調 .....                        | 65 |

| 1.2.22 | ストリーム・モードとトランスペアレント・モード .....        | 67 |

| 1.3    | レジスタ .....                           | 71 |

| 1.3.1  | IO コンフィギュレーション・レジスタ 1 .....          | 74 |

| 1.3.2  | IO コンフィギュレーション・レジスタ 2 .....          | 75 |

| 1.3.3  | 動作コントロール・レジスタ .....                  | 76 |

| 1.3.4  | モード設定レジスタ .....                      | 77 |

| 1.3.5  | ビット・レート設定レジスタ .....                  | 78 |

| 1.3.6  | ISO14443A / NFC 106kb/s 設定レジスタ ..... | 79 |

| 1.3.7  | ISO14443B 設定レジスタ 1 .....             | 80 |

| 1.3.8  | ISO14443B / FeliCa 設定レジスタ .....      | 81 |

| 1.3.9  | ストリーム・モード設定レジスタ .....                | 82 |

| 1.3.10 | 補助設定レジスタ .....                       | 83 |

| 1.3.11 | レシーバ・コンフィギュレーション・レジスタ 1 .....        | 84 |

| 1.3.12 | レシーバ・コンフィギュレーション・レジスタ 2 .....        | 85 |

| 1.3.13 | レシーバ・コンフィギュレーション・レジスタ 3 .....        | 86 |

| 1.3.14 | レシーバ・コンフィギュレーション・レジスタ 4 .....        | 86 |

| 1.3.15 | マスク受信タイマ・レジスタ .....                  | 87 |

| 1.3.16 | 応答なしタイマ・レジスタ 1 .....                 | 88 |

| 1.3.17 | 応答なしタイマ・レジスタ 2 .....                 | 88 |

| 1.3.18 | 汎用 / 応答なしタイマ・コントロール・レジスタ .....       | 89 |

| 1.3.19 | 汎用タイマ・レジスタ 1 .....                   | 90 |

| 1.3.20 | 汎用タイマ・レジスタ 2 .....                   | 90 |

| 1.3.21 | マスク・メイン割込みレジスタ .....                 | 91 |

| 1.3.22 | マスク・タイマ / NFC 割込みレジスタ .....          | 91 |

| 1.3.23 | マスク・エラー / ウェイクアップ割込みレジスタ .....       | 92 |

| 1.3.24 | メイン割込みレジスタ .....                     | 92 |

| 1.3.25 | タイマ / NFC 割込みレジスタ .....              | 93 |

| 1.3.26 | エラー / ウェイクアップ割込みレジスタ .....           | 94 |

| 1.3.27 | FIFO ステータス・レジスタ 1 .....              | 95 |

| 1.3.28 | FIFO ステータス・レジスタ 2 .....              | 95 |

| 1.3.29 | コリジョン表示レジスタ .....                    | 96 |

| 1.3.30 | 送信バイト数レジスタ 1 .....                   | 96 |

| 1.3.31 | 送信バイト数レジスタ 2 .....                   | 97 |

|        |                         |     |

|--------|-------------------------|-----|

| 1.3.32 | NFCIP ビット・レート検出表示レジスタ   | 97  |

| 1.3.33 | A/D コンバータ出力レジスタ         | 98  |

| 1.3.34 | アンテナ補正コントロール・レジスタ       | 98  |

| 1.3.35 | アンテナ補正ターゲット・レジスタ        | 99  |

| 1.3.36 | アンテナ補正表示レジスタ            | 99  |

| 1.3.37 | AM 変調度コントロール・レジスタ       | 100 |

| 1.3.38 | AM 変調度表示レジスタ            | 100 |

| 1.3.39 | RFO AM 変調レベル設定レジスタ      | 101 |

| 1.3.40 | RFO 通常レベル設定レジスタ         | 101 |

| 1.3.41 | 外部フィールド検出器閾値レジスタ        | 102 |

| 1.3.42 | レギュレータ電圧コントロール・レジスタ     | 103 |

| 1.3.43 | レギュレータ / タイマ表示レジスタ      | 104 |

| 1.3.44 | RSSI 表示レジスタ             | 105 |

| 1.3.45 | ゲイン減少状態レジスタ             | 106 |

| 1.3.46 | 静電容量センサ・コントロール・レジスタ     | 106 |

| 1.3.47 | 静電容量センサ表示レジスタ           | 107 |

| 1.3.48 | 補助表示レジスタ                | 107 |

| 1.3.49 | ウェイクアップ・タイマ・コントロール・レジスタ | 108 |

| 1.3.50 | 振幅測定コンフィギュレーション・レジスタ    | 109 |

| 1.3.51 | 振幅測定基準レジスタ              | 109 |

| 1.3.52 | 振幅測定自動平均化表示レジスタ         | 110 |

| 1.3.53 | 振幅測定表示レジスタ              | 110 |

| 1.3.54 | 位相測定コンフィギュレーション・レジスタ    | 111 |

| 1.3.55 | 位相測定基準レジスタ              | 111 |

| 1.3.56 | 位相測定自動平均化表示レジスタ         | 112 |

| 1.3.57 | 位相測定表示レジスタ              | 112 |

| 1.3.58 | 静電容量測定コンフィギュレーション・レジスタ  | 113 |

| 1.3.59 | 静電容量測定基準レジスタ            | 113 |

| 1.3.60 | 静電容量測定自動平均化表示レジスタ       | 114 |

| 1.3.61 | 静電容量測定ディスプレイ・レジスタ       | 114 |

| 1.3.62 | IC 識別レジスタ               | 115 |

| 2      | ピン配列とピン説明               | 116 |

---

|          |                   |            |

|----------|-------------------|------------|

| <b>3</b> | <b>電気的特性</b>      | <b>118</b> |

| 3.1      | 絶対最大定格            | 118        |

| 3.2      | 動作条件              | 119        |

| 3.3      | デジタル入出力の DC/AC 特性 | 119        |

| 3.3.1    | CMOS 入力           | 119        |

| 3.3.2    | CMOS 出力           | 119        |

| 3.4      | 電気的仕様             | 120        |

| 3.5      | 標準動作特性            | 122        |

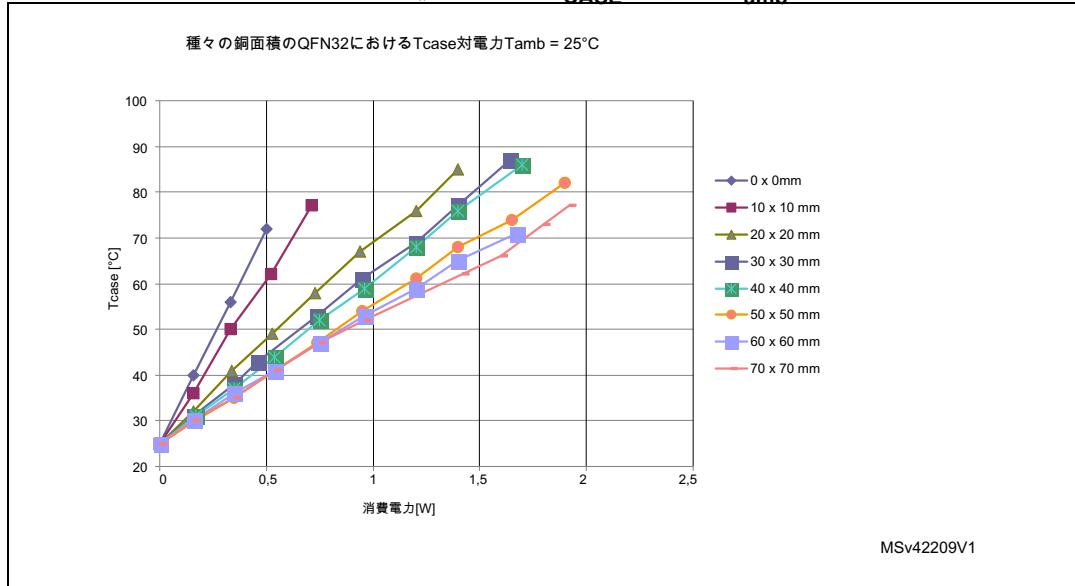

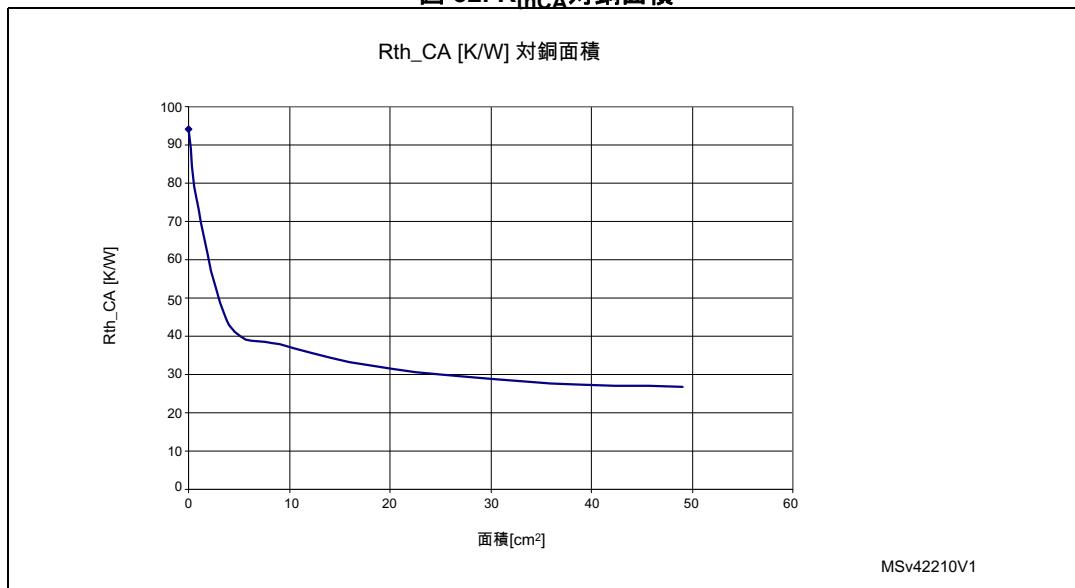

| 3.5.1    | 耐熱性と最大消費電力        | 122        |

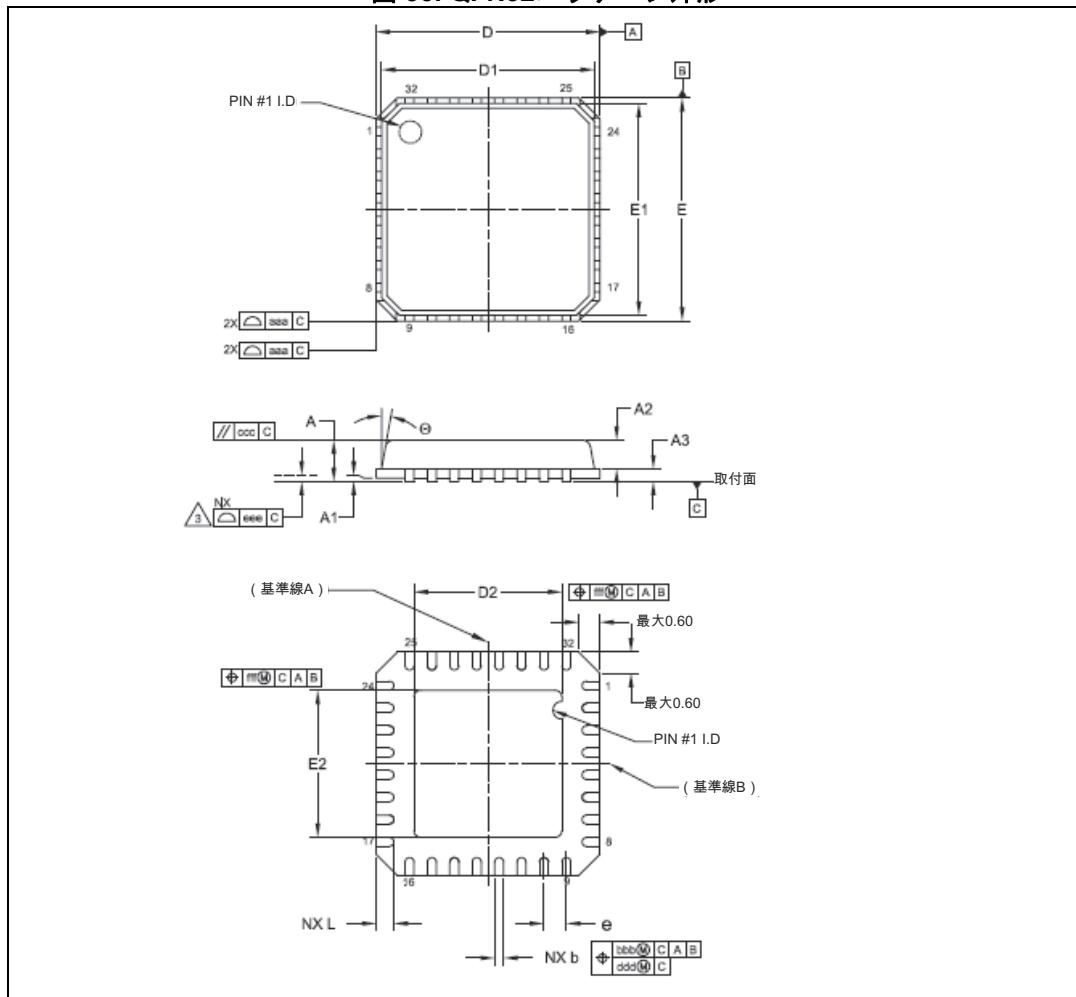

| <b>4</b> | <b>パッケージ情報</b>    | <b>123</b> |

| 4.1      | QFN32 パッケージ情報     | 123        |

| <b>5</b> | <b>部品番号</b>       | <b>125</b> |

| <b>6</b> | <b>改訂履歴</b>       | <b>127</b> |

## 表の一覧

|       |                                            |    |

|-------|--------------------------------------------|----|

| 表 1.  | 第 1/ 第 3 ステージゼロ点設定                         | 18 |

| 表 2.  | ローパス・コントロール                                | 19 |

| 表 3.  | レシーバのフィルタ選択とゲイン範囲                          | 19 |

| 表 4.  | ブロッキング・コンデンサの推奨値                           | 30 |

| 表 5.  | シリアル・データ・インターフェース（4 線式インターフェース）信号ライン       | 32 |

| 表 6.  | SPI 動作モード                                  | 33 |

| 表 7.  | SPI タイミング                                  | 38 |

| 表 8.  | IRQ 出力                                     | 39 |

| 表 9.  | ダイレクト・コマンド                                 | 41 |

| 表 10. | NFC Field ON コマンド群のタイミング・パラメータ             | 45 |

| 表 11. | レジスタ・プリセット・ビット                             | 46 |

| 表 12. | アナログ・テスト / 監視レジスタ                          | 51 |

| 表 13. | テスト・アクセス・レジスタ - CSI ピンと CSO ピン の Tana 信号選択 | 51 |

| 表 14. | NFCIP-1 パッシブ通信の動作モード / ビット・レート設定           | 59 |

| 表 15. | NFCIP-1 アクティブ通信イニシエータの動作モード / ビット・レート設定    | 60 |

| 表 16. | mod ビットの設定                                 | 64 |

| 表 17. | レジスタ・マップ                                   | 71 |

| 表 18. | IO コンフィギュレーション・レジスタ 1                      | 74 |

| 表 19. | IO コンフィギュレーション・レジスタ 2                      | 75 |

| 表 20. | 動作コントロール・レジスタ                              | 76 |

| 表 21. | モード設定レジスタ                                  | 77 |

| 表 22. | イニシエータ動作モード                                | 77 |

| 表 23. | ターゲット動作モード                                 | 77 |

| 表 24. | ビット・レート設定レジスタ                              | 78 |

| 表 25. | ビット・レート・コーディング                             | 78 |

| 表 26. | ISO14443A / NFC 106kb/s 設定レジスタ             | 79 |

| 表 27. | ISO14443A 変調パルス幅                           | 79 |

| 表 28. | ISO14443B 設定レジスタ 1                         | 80 |

| 表 29. | ISO14443B / FeliCa 設定レジスタ                  | 81 |

| 表 30. | 最小 TR1 コーディング                              | 81 |

| 表 31. | ストリーム・モード設定レジスタ                            | 82 |

| 表 32. | サブキャリア /BPSK ストリーム・モードのサブキャリア周波数設定         | 82 |

| 表 33. | ストリーム・モード Tx 変調器制御用時間周期の設定                 | 82 |

| 表 34. | 補助設定レジスタ                                   | 83 |

| 表 35. | レシーバ・コンフィギュレーション・レジスタ 1                    | 84 |

| 表 36. | レシーバ・コンフィギュレーション・レジスタ 2                    | 85 |

| 表 37. | レシーバ・コンフィギュレーション・レジスタ 3                    | 86 |

| 表 38. | レシーバ・コンフィギュレーション・レジスタ 4                    | 86 |

| 表 39. | マスク受信タイマ・レジスタ                              | 87 |

| 表 40. | 応答なしタイマ・レジスタ 1                             | 88 |

| 表 41. | 応答なしタイマ・レジスタ 2                             | 88 |

| 表 42. | 汎用 / 応答なしタイマ・コントロール・レジスタ                   | 89 |

| 表 43. | タイマのトリガ源                                   | 89 |

| 表 44. | 汎用タイマ・レジスタ 1                               | 90 |

| 表 45. | 汎用タイマ・レジスタ 2                               | 90 |

| 表 46. | マスク・メイン割込みレジスタ                             | 91 |

| 表 47. | マスク・タイマ /NFC 割込みレジスタ                       | 91 |

| 表 48. | マスク・エラー / ウェイクアップ割込みレジスタ                   | 92 |

| 表 49. | メイン割込みレジスタ                                 | 92 |

|        |                                    |     |

|--------|------------------------------------|-----|

| 表 50.  | タイム /NFC 割込みレジスタ.....              | 93  |

| 表 51.  | エラー / ウェイクアップ割込みレジスタ.....          | 94  |

| 表 52.  | FIFO ステータス・レジスタ 1.....             | 95  |

| 表 53.  | FIFO ステータス・レジスタ 2.....             | 95  |

| 表 54.  | コリジョン表示レジスタ.....                   | 96  |

| 表 55.  | 送信バイト数レジスタ 1.....                  | 96  |

| 表 56.  | 送信バイト数レジスタ 2.....                  | 97  |

| 表 57.  | NFCIP ビット・レート検出表示レジスタ.....         | 97  |

| 表 58.  | A/D コンバータ出力レジスタ.....               | 98  |

| 表 59.  | アンテナ補正コントロール・レジスタ.....             | 98  |

| 表 60.  | アンテナ補正ターゲット・レジスタ.....              | 99  |

| 表 61.  | アンテナ補正表示レジスタ.....                  | 99  |

| 表 62.  | AM 変調度コントロール・レジスタ.....             | 100 |

| 表 63.  | AM 変調度表示レジスタ.....                  | 100 |

| 表 64.  | RFO AM 変調レベル設定レジスタ.....            | 101 |

| 表 65.  | RFO 通常レベル設定レジスタ.....               | 101 |

| 表 66.  | 外部フィールド検出器閾値レジスタ.....              | 102 |

| 表 67.  | RFI1 入力から見たピア検出閾値.....             | 102 |

| 表 68.  | RFI1 入力から見たコリジョン防止閾値.....          | 102 |

| 表 69.  | レギュレータ電圧コントロール・レジスタ.....           | 103 |

| 表 70.  | レギュレータ / タイマ表示レジスタ.....            | 104 |

| 表 71.  | 安定化電圧.....                         | 104 |

| 表 72.  | RSSI 表示レジスタ.....                   | 105 |

| 表 73.  | RSSI .....                         | 105 |

| 表 74.  | ゲイン減少状態レジスタ.....                   | 106 |

| 表 75.  | 静電容量センサ・コントロール・レジスタ.....           | 106 |

| 表 76.  | 静電容量センサ表示レジスタ.....                 | 107 |

| 表 77.  | 補助表示レジスタ.....                      | 107 |

| 表 78.  | ウェイクアップ・タイマ・コントロール・レジスタ.....       | 108 |

| 表 79.  | 標準ウェイクアップ時間.....                   | 108 |

| 表 80.  | 振幅測定コンフィギュレーション・レジスタ.....          | 109 |

| 表 81.  | 振幅測定基準レジスタ.....                    | 109 |

| 表 82.  | 振幅測定自動平均化表示レジスタ.....               | 110 |

| 表 83.  | 振幅測定表示レジスタ.....                    | 110 |

| 表 84.  | 位相測定コンフィギュレーション・レジスタ.....          | 111 |

| 表 85.  | 位相測定基準レジスタ.....                    | 111 |

| 表 86.  | 位相測定自動平均化表示レジスタ.....               | 112 |

| 表 87.  | 位相測定表示レジスタ.....                    | 112 |

| 表 88.  | 静電容量測定コンフィギュレーション・レジスタ.....        | 113 |

| 表 89.  | 静電容量測定基準レジスタ.....                  | 113 |

| 表 90.  | 静電容量測定自動平均化表示レジスタ.....             | 114 |

| 表 91.  | 静電容量測定ディスプレイ・レジスタ.....             | 114 |

| 表 92.  | IC 識別レジスタ.....                     | 115 |

| 表 93.  | ST25R3911B ピン定義 - QFN32 パッケージ..... | 116 |

| 表 94.  | 電気的パラメータ.....                      | 118 |

| 表 95.  | 静電気放電.....                         | 118 |

| 表 96.  | 温度範囲と保存条件.....                     | 118 |

| 表 97.  | 動作条件 .....                         | 119 |

| 表 98.  | CMOS 入力 .....                      | 119 |

| 表 99.  | CMOS 出力 .....                      | 119 |

| 表 100. | 電気的仕様.....                         | 120 |

| 表 101. | QFN32 5 mm x 5 mm 寸法 .....         | 124 |

---

|        |                |     |

|--------|----------------|-----|

| 表 102. | 発注情報体系         | 125 |

| 表 103. | 発注情報体系（未切断ウェハ） | 126 |

| 表 104. | 文書改訂履歴         | 127 |

## 図の一覧

|       |                                                   |     |

|-------|---------------------------------------------------|-----|

| 図 1.  | ST25R3911B ブロック図                                  | 10  |

| 図 2.  | シングル・エンド・アンテナ駆動の最小構成 (EMC フィルタを含む)                | 14  |

| 図 3.  | 差動アンテナ駆動の最小構成 (EMC フィルタを含む)                       | 14  |

| 図 4.  | レシーバのブロック図                                        | 17  |

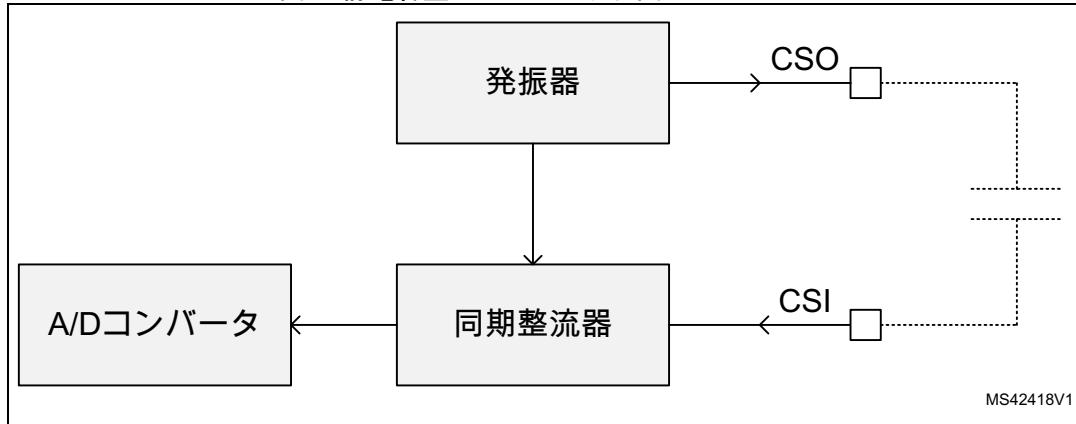

| 図 5.  | 静電容量センサブロック図                                      | 22  |

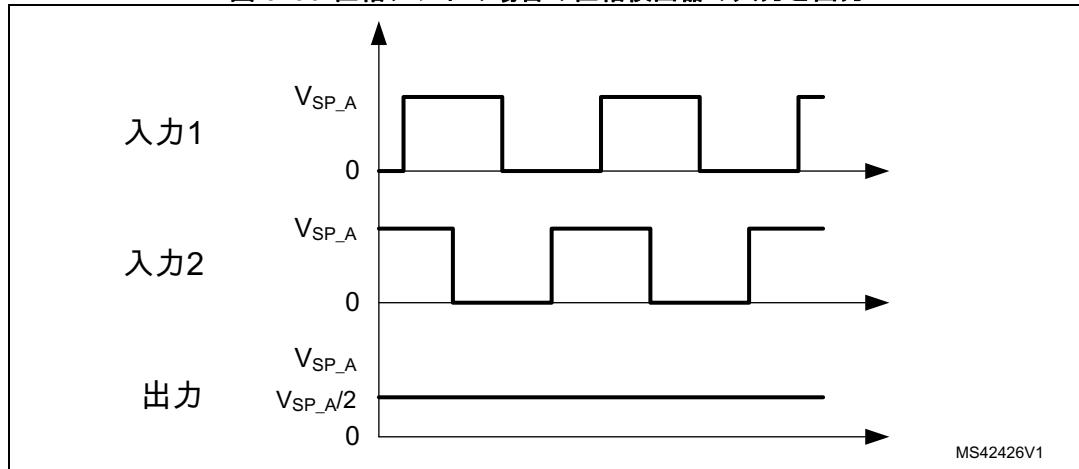

| 図 6.  | 90° 位相シフトの場合の位相検出器の入力と出力                          | 27  |

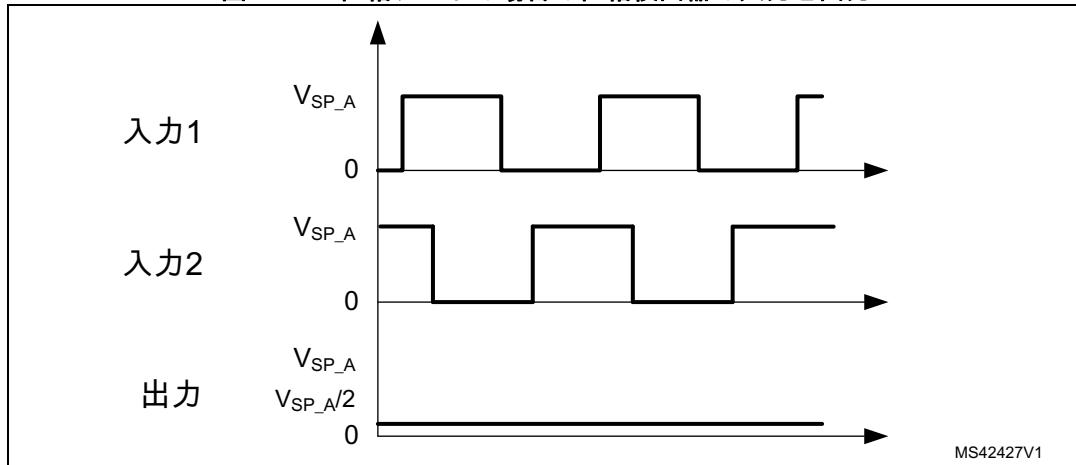

| 図 7.  | 135° 位相シフトの場合の位相検出器の入力と出力                         | 28  |

| 図 8.  | ST25R3911B の電源                                    | 29  |

| 図 9.  | マイクロコントローラとの信号のやりとり                               | 32  |

| 図 10. | SPI 通信：単一バイト書込み                                   | 33  |

| 図 11. | SPI 通信：複数バイト書込み                                   | 34  |

| 図 12. | SPI 通信：単一バイト読み込み                                  | 35  |

| 図 13. | SPI 通信：FIFO のロード                                  | 35  |

| 図 14. | SPI 通信：FIFO の読み込み                                 | 36  |

| 図 15. | SPI 通信：ダイレクト・コマンド                                 | 37  |

| 図 16. | SPI 通信：ダイレクト・コマンドの連鎖                              | 37  |

| 図 17. | SPI 一般タイミング                                       | 38  |

| 図 18. | SPI 読込みタイミング                                      | 39  |

| 図 19. | ダイレクト・コマンド NFC Initial Field ON                   | 45  |

| 図 20. | ダイレクト・コマンド NFC Response Field ON                  | 45  |

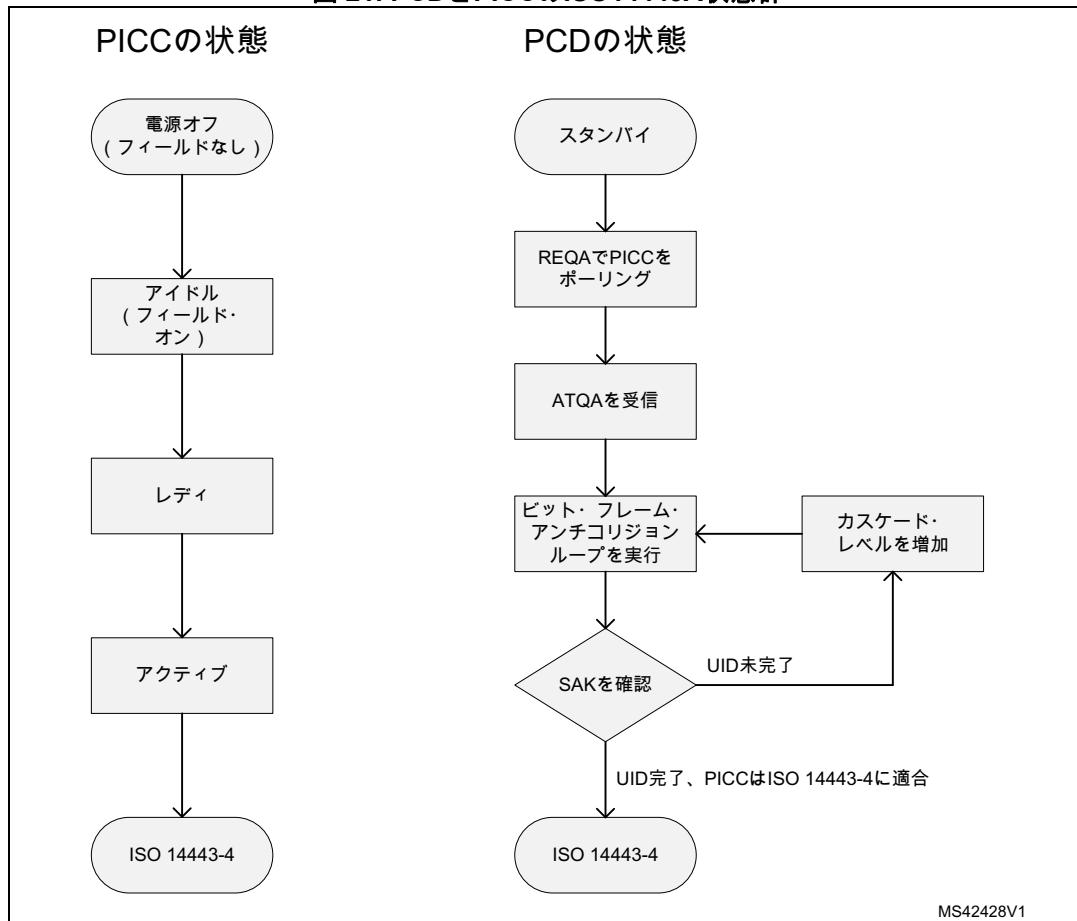

| 図 21. | PCD と PICC の ISO14443A 状態群                        | 54  |

| 図 22. | ある特定の FDT に対する MRT と NRT の選択                      | 55  |

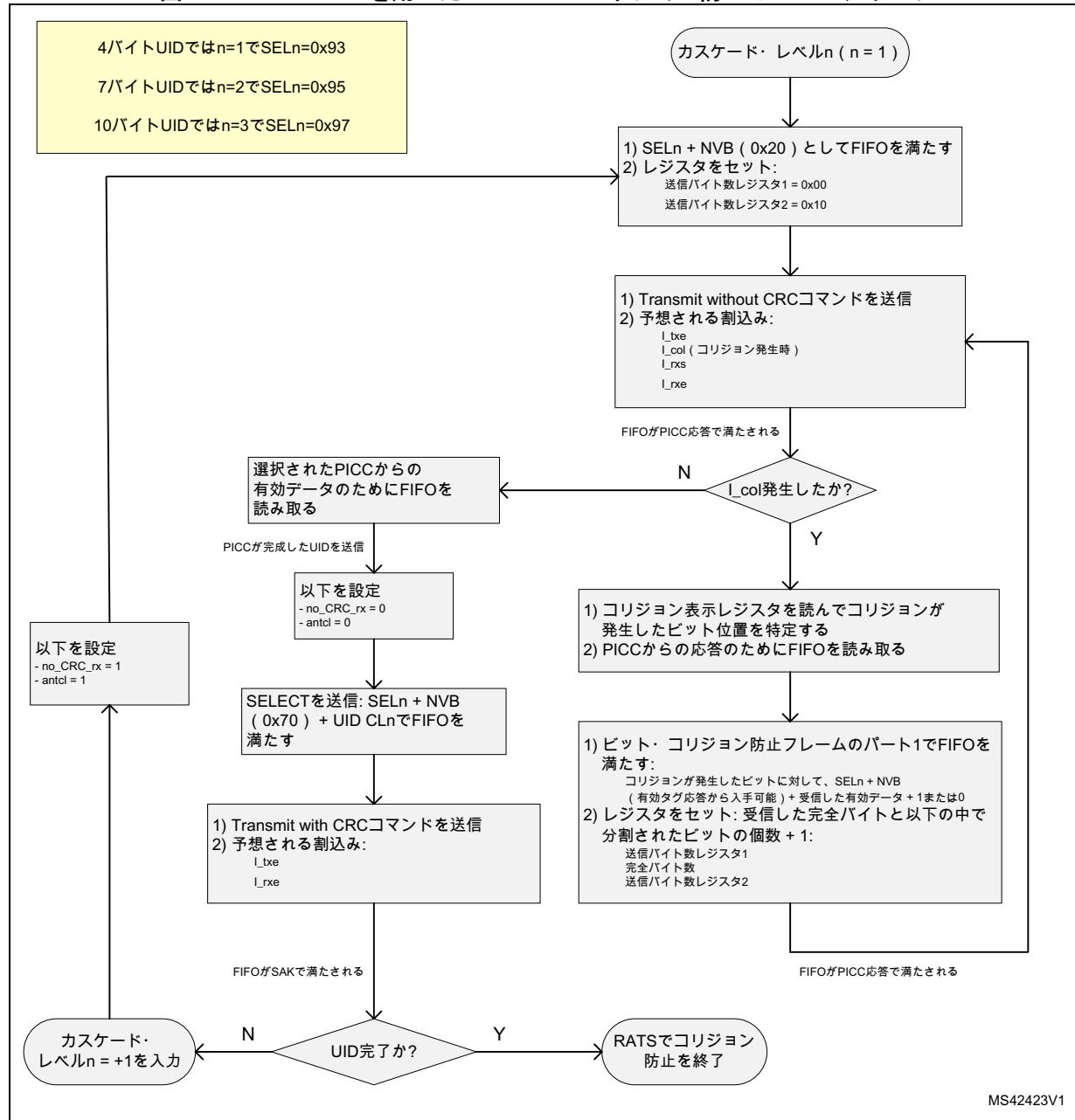

| 図 23. | ST25R3911B を用いた ISO14443A コリジョン防止のフローチャート         | 57  |

| 図 24. | FeliCa™ フレーム・フォーマット                               | 58  |

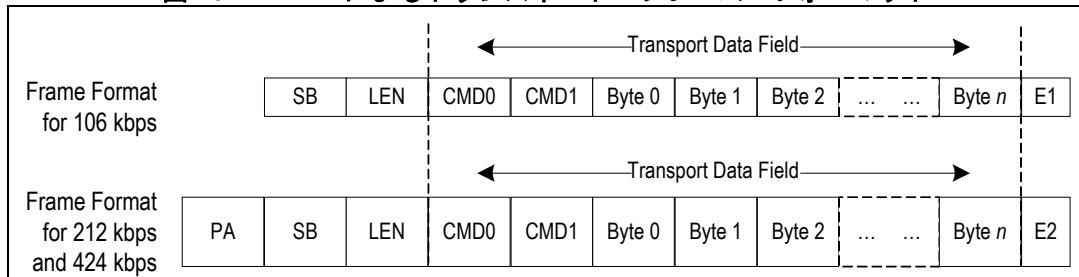

| 図 25. | NFCIP-1 によるトランスポート・フレーム・フォーマット                    | 59  |

| 図 26. | アンテナ LC タンクに対する同調コンデンサの接続                         | 66  |

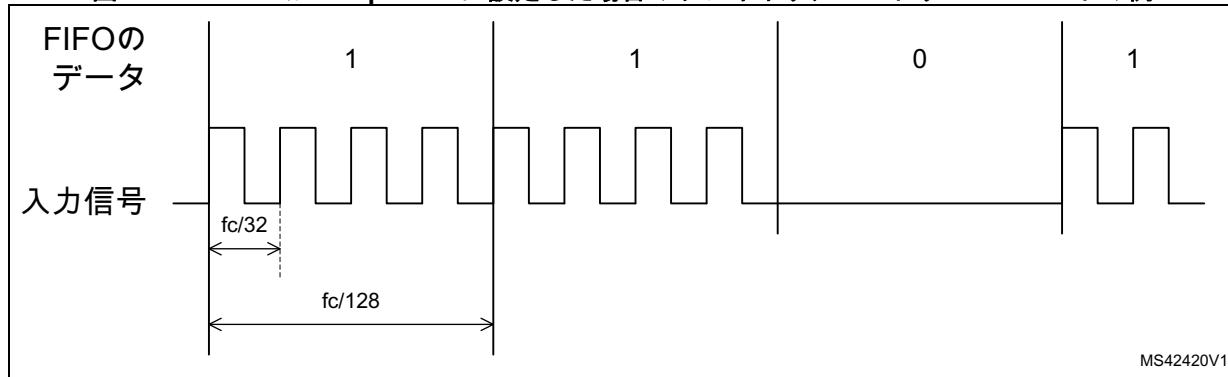

| 図 27. | scf = 01b かつ scp = 10b に設定した場合のサブキャリア・ストリーム・モードの例 | 69  |

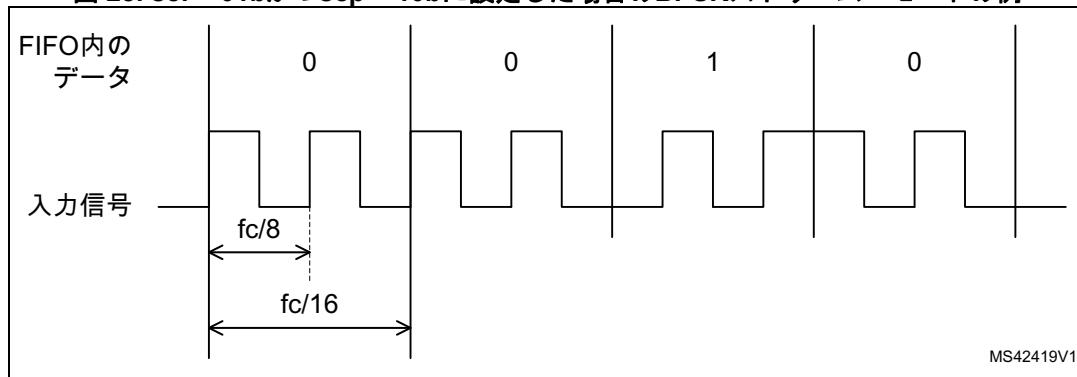

| 図 28. | scf = 01b かつ scp = 10b に設定した場合の BPSK ストリーム・モードの例  | 70  |

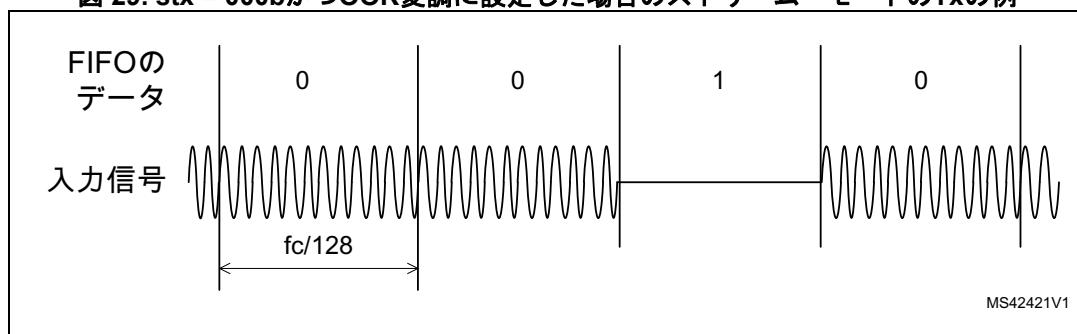

| 図 29. | stx = 000b かつ OOK 変調に設定した場合のストリーム・モードの Tx の例      | 70  |

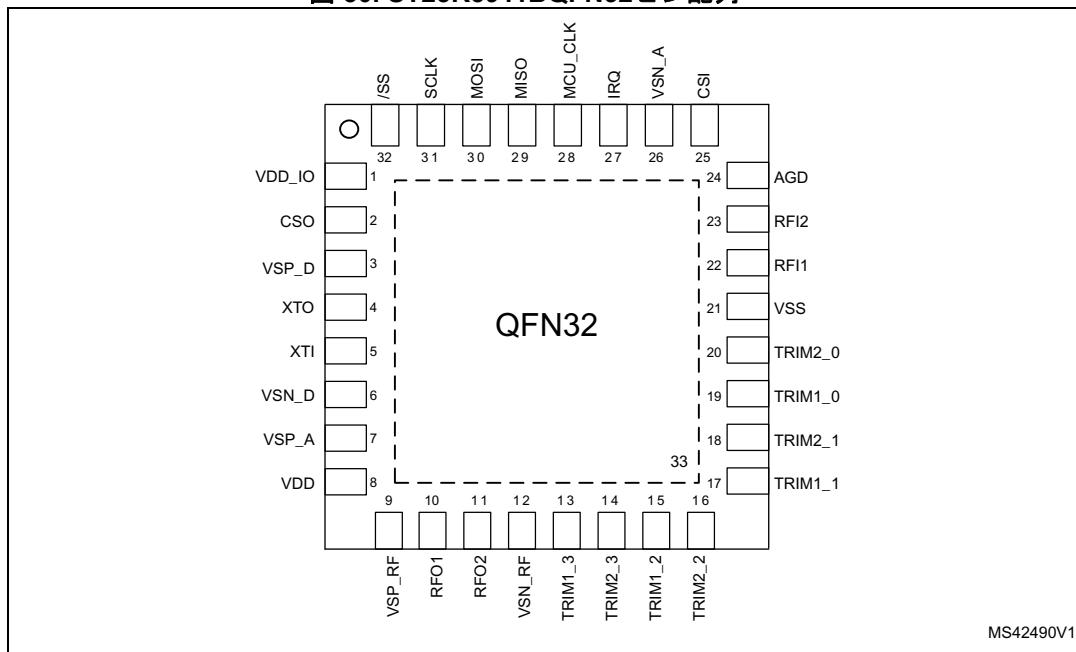

| 図 30. | ST25R3911BQFN32 ピン配列 <sup>(1)</sup>               | 116 |

| 図 31. | 異なる銅面積における TCASE 対電力 (Tamb = 25°C)                | 122 |

| 図 32. | RthCA 対銅面積                                        | 122 |

| 図 33. | QFN32 パッケージ外形                                     | 123 |

# 1 機能概要

ST25R3911Bは、以下のような広範囲な用途に適しています。

- EMV支払い

- 公文書電子認証

- アクセス・コントロール

- NFCインフラ

- チケット販売

## 1.1 ブロック図

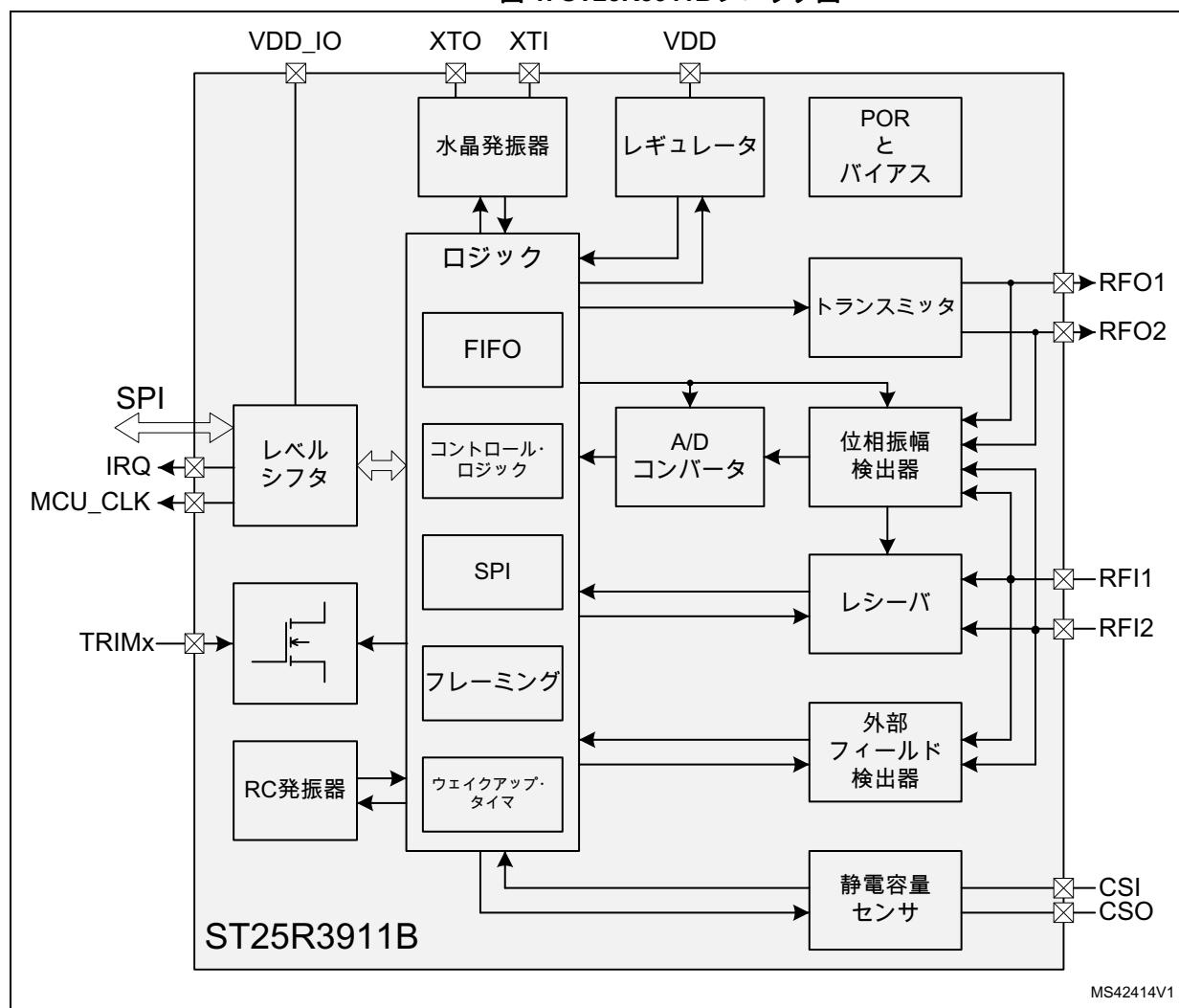

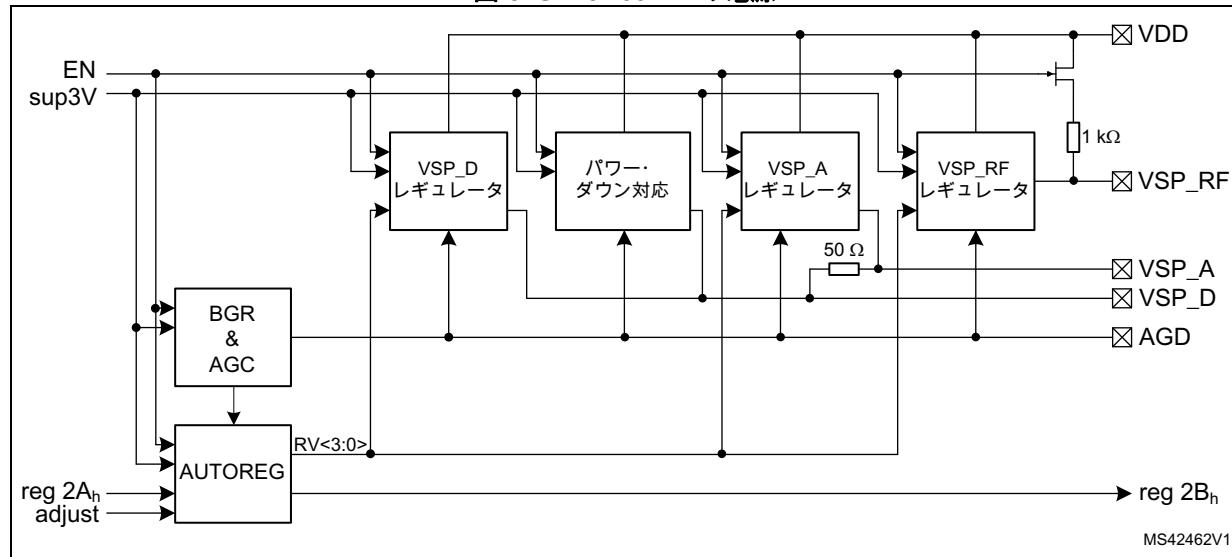

ブロック図を図1に示します。

図1. ST25R3911Bブロック図

### 1.1.1 トランスマッタ

トランスマッタには、RFO1ピンとRFO2ピンを通じて外部アンテナを駆動するドライバが組み込まれています。シングル・エンド駆動と差動駆動が可能です。更に、トランスマッタ・ブロックには、送信信号を変調（On-Off-Keying変調または設定可能な振幅変調）するサブブロックも含まれています。

ST25R3911Bのトランスマッタは、アンテナ（50 Ωケーブルを含みません。通常、アンテナは同一PCB上にあるため）を直接駆動するためのものです。50 Ωケーブル付きでの動作も可能ですが、この場合には、高度な機能群の一部が利用できません。

### 1.1.2 レシーバ

レシーバは、13.56 MHzキャリア信号に重畠されたトランスポンダ（カード・タグ）負荷変調を検出します。このレシーバには、受信回路が2つ（1つは振幅復調用、もう1つは位相復調用）含まれており、それぞれは、ピーク検出器の後にある2つのゲイン/フィルタリングステージと、最終デジタイザステージから構成されています。フィルタ特性は、それぞれのモードとビット・レート（212 kHzから6.8 MHzまでのサブキャリア周波数に対応）の性能を最適化するように調整されています。レシーバ回路の入力はRFI1ピンとRFI2ピンです。レシーバ回路には、位相とノイズ状態が厳しくとも信頼性の高い動作を可能とする機能が複数組み込まれています。

### 1.1.3 位相・振幅検出器

位相検出器は、トランスマッタ出力信号（RFO1とRFO2）と、レシーバ入力信号（RFI1とRFI2）との間の位相差を観測しています。振幅検出器は、自己ミキシングを通じて、レシーバ入力信号（RFI1とRFI2）の振幅を観測しています。レシーバ入力信号（RFI1とRFI2）の振幅は、アンテナLCタンク信号の振幅と正比例関係にあります。

位相検出器と振幅検出器は、次のような目的に使用できます。

- RFI1とRFI2の位相変動を観測することによる位相復調

- RFO<sub>x</sub>ピンとRFI<sub>x</sub>ピンの間の平均位相差を使用したアンテナ共振の確認と最適化

- RFI1ピンとRFI2ピンに現れる信号の振幅を使用したアンテナ共振の確認と最適化

### 1.1.4 A/Dコンバータ

ST25R3911Bには、アナログ/デジタル（A/D）コンバータが内蔵されています。その入力は、さまざまな信号源を多重化可能であり、複数の用途（RF振幅と位相の測定、変調度の補正など）で使用されます。A/D変換の結果はA/Dコンバータ出力レジスタに格納され、SPIを通じて読み出し可能です。

### 1.1.5 静電容量センサ

静電容量センサは、ローパワーでのトランスポンダ（カード・タグ）存在検出を実現するために使用され、CSIピンとCSOピンに接続された2枚の銅パッチの間の静電容量を測定します。物体（カード、手など）の存在によって、静電容量が変化します。補正の間に、基準静電容量（環境の寄生容量を示します）が格納されます。通常動作では、静電容量が周期的に測定され、格納された基準値との比較が行われます。測定された静電容量が、レジスタで設定された閾値を超えて、格納された基準値と異なる場合には、外部コントローラに割込みが送信されます。

### 1.1.6 外部フィールド検出器

外部フィールド検出器は、外部RFフィールドの存在を検出するために、NFCモードで使用される低消費電力のブロックです。ピア検出閾値とコリジョン防止閾値の2つの異なる検出閾値に対応しています。ピア検出閾値は、イニシエータ・フィールドの存在検出するためにNFCIP-1ターゲット・モードで使用されますが、アクティブイニシエータ・モードでも、ターゲット・フィールドのアクティブ化を検出するために使用されます。コリジョン防止閾値は、NFCIP-1 RFコリジョン防止シーケンス手続きの間に、RFフィールドの存在検出のために使用されます。

### 1.1.7 水晶発振器

水晶発振器は、13.56 MHzから27.12 MHzまでの水晶振動子で動作可能です。起動時には、発振器の相互コンダクタンスが増して起動を高速にします。起動時間は、水晶振動子の種類や温度などのパラメータによって変動しますので、発振器の振幅が監視されて、発振器の動作が安定すると割込みが送信されます。VHBR動作では、27.12 MHz水晶振動子を必ず使用してください。

発振器ブロックは、[IOコンフィギュレーション・レジスタ1](#)の設定に従って、外部マイクロコントローラにクロック信号 (MCU\_CLK) の供給も行います。

### 1.1.8 電源レギュレータ

内蔵の電源レギュレータによって、リーダ・システム全体に対して、高い電源除去比 (PSRR) が保証されます。リーダ・システムのPSRRを改善する必要がある場合には、Adjust Regulatorsコマンドが送られます。このコマンドの結果として、最大負荷状態で電源レベル $V_{DD}$ が測定され、安定化電源の安定性を保証するために、この測定レベルよりも250 mV低い値に安定化電圧基準が設定されます。その結果として得られた安定化電圧は、[レギュレータ/タイマ表示レジスタ](#)に格納されます。を [レギュレータ電圧コントロール・レジスタ](#)に書き込むことによっても、安定化電圧の設定が可能です。ICのさまざまな部分からあらゆるノイズ源を分離するために、独立した外付けブロッキング・コンデンサと内蔵されたレギュレータが3個存在します (3.3 V電源モードでは、そのすべての安定化電圧は同じです)。レギュレータの1つはアナログ・ブロック用、1つはデジタル・ブロック用、もう1つはアンテナ・ドライバ用です。

このブロックは、アナログ処理用の基準電圧の生成も行います (AGD - アナログGND)。

この電圧には、関連する外部バッファ・コンデンサもあります。

### 1.1.9 PORとバイアス

このブロックは、これ以外のすべてのブロックに対するバイアス電流と基準電圧を供給します。ここにはパワーオンリセット (POR) 回路も組み込まれており、起動時と電源電圧レベルが低い場合にリセット信号を供給します。

### 1.1.10 RC発振器とウェイクアップ・タイマ

ST25R3911Bには、ローパワーでのカード存在検出に複数の手段 (静電容量センサ、位相測定、振幅測定) が組み込まれています。RC発振器とレジスタで設定可能なウェイクアップ・タイマは、周期的なカード存在検出をスケジュール設定するために使用します。

### 1.1.11 ISO-14443とNFCIP-1フレーミング

このブロックは、選択されたISOモードとビット・レート設定に従って、送受信のフレーミングを行います。

受信時には、レシーバから復調されたサブキャリア信号を取り出します。SOF (Start Of Frame) とEOF (End Of Frame) とデータ・ビットを認識し、パリティとCRCのチェックを実行し、受信データをバイト列に並べ直してFIFOに置きます。

送信時には、その反対の動作を行います。FIFOからバイト列を取り出して、パリティ・ビットとCRCビットを生成し、変調信号をトランスマッタに渡す前に、SOFとEOFを追加して最終エンコードを行います。

トランスペアレント・モードでは、フレーミングとFIFOがバイパスされて、デジタル化されたサブキャリア信号（レシーバ出力）がMISOピンに直接送られ、MOSIピンに印加された信号がトランスマッタの変調に直接使用されます。

### 1.1.12 FIFO

ST25R3911Bには、96バイトFIFOが含まれています。モードによって、受信済みのデータと送信予定のデータのいずれかが含まれています。

### 1.1.13 コントロール・ロジック

コントロール・ロジックには、デバイスの動作を設定するI/Oレジスタが含まれています。

### 1.1.14 SPI

外部マイクロコントローラとST25R3911Bとの間の通信には、4線式シリアル・ペリフェラル・インターフェース (SPI) が用いられます。

## 1.2 アプリケーション情報

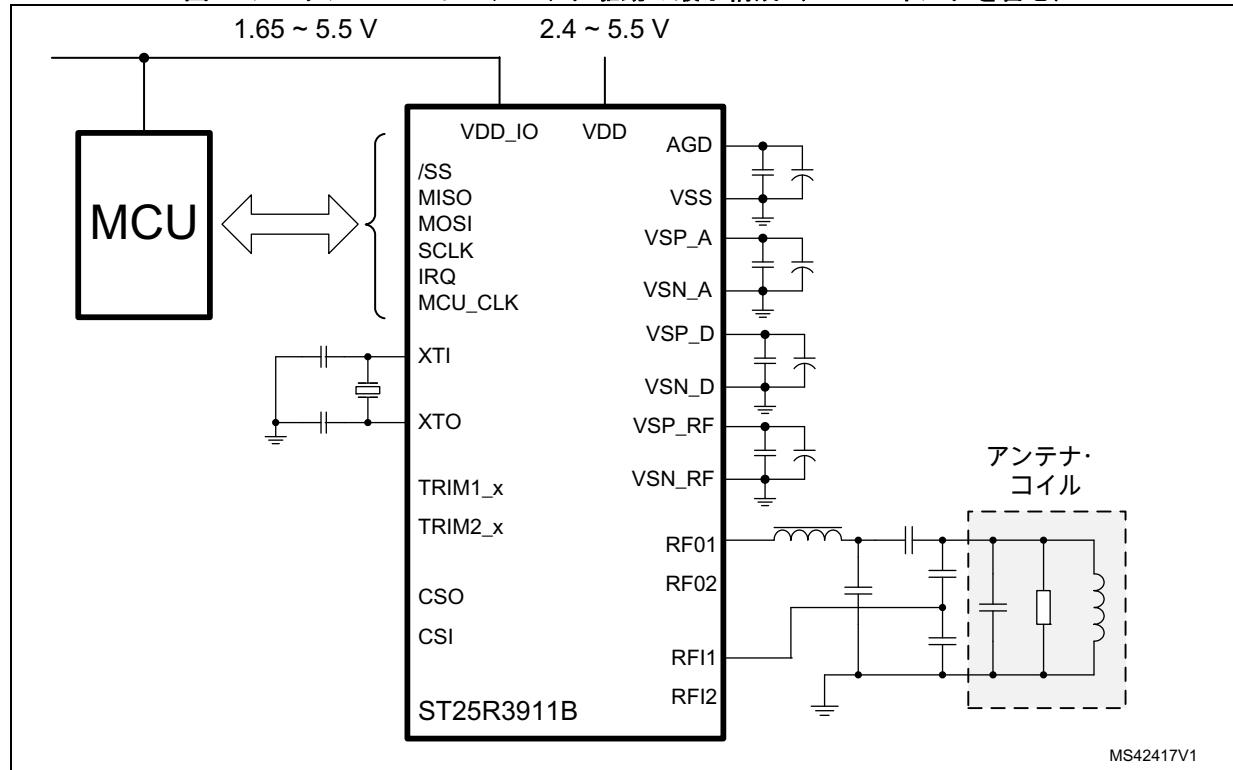

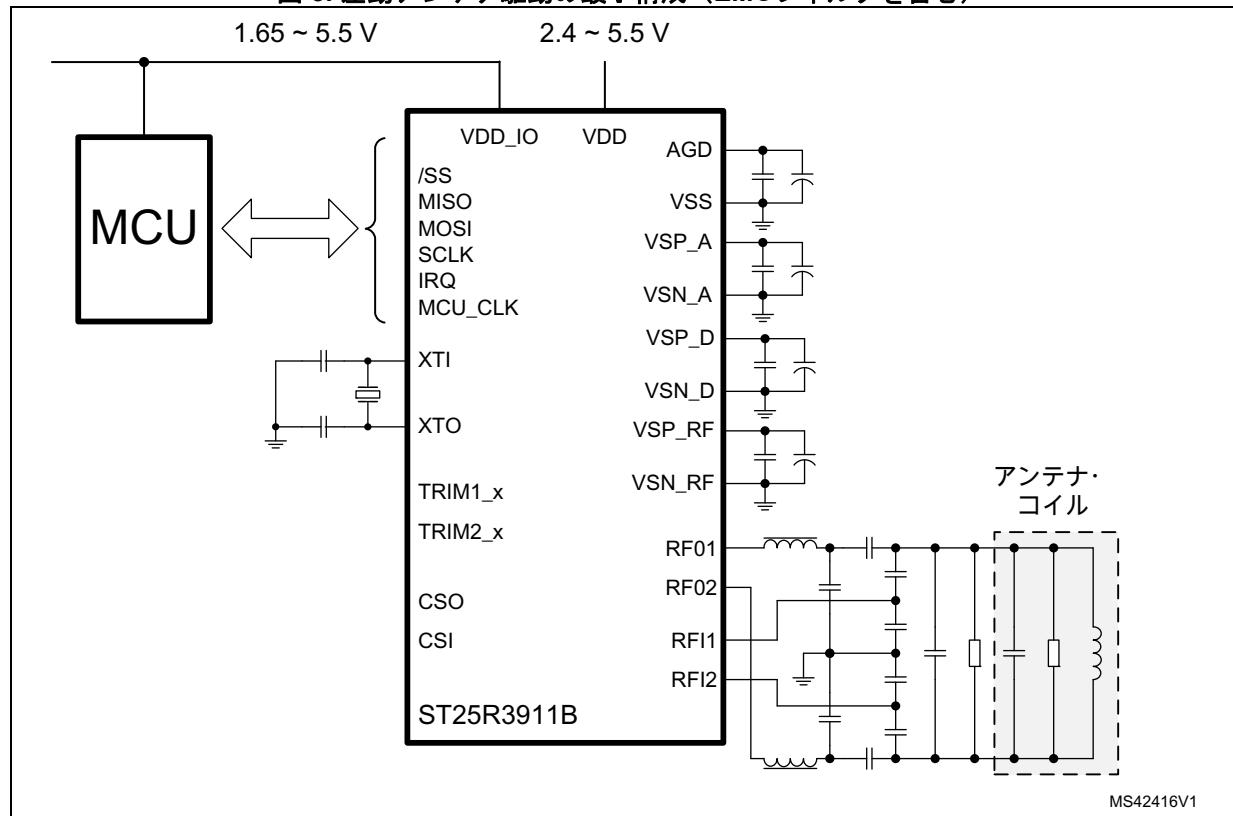

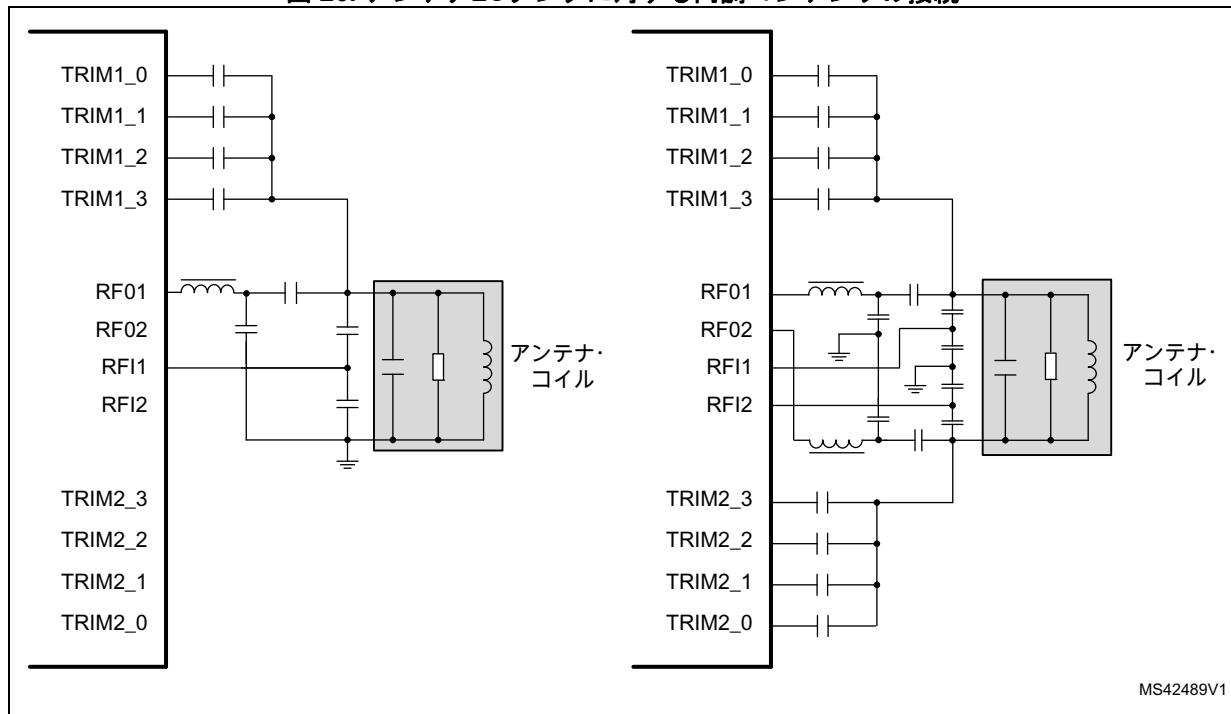

ST25R3911Bの動作に必要な最低限の構成を図2と図3に示します。

図2. シングル・エンド・アンテナ駆動の最小構成（EMCフィルタを含む）

図3. 差動アンテナ駆動の最小構成（EMCフィルタを含む）

## 1.2.1 動作モード

ST25R3911Bの動作モードは、[動作コントロール・レジスタ](#)の内容によって設定されます。

起動時に、[動作コントロール・レジスタ](#)の全ビットは0にセットされ、ST25R3911Bはパワーダウン・モードとなります。このモードでは、アナログ・フロントエンドの静的消費電力は最小限に抑えられて、PORとバイアスの一部だけがアクティブとなり、レギュレータは完全にOFFとなり動作していません。それにもかかわらず、このモードではSPIが動作していますので、ISOモード設定とコンフィギュレーション・レジスタのすべての設定を行うことは可能です。

コントロール・ビットen ([動作コントロール・レジスタ](#)のビット7) が、水晶発振器とレギュレータを制御しています。このビットがセットされると、デバイスはレディ・モードに入ります。このモードでは、水晶発振器とレギュレータが有効化されます。発振器の周波数が安定すると、割込みが送信されてマイクロコントローラに通知します。

レシーバとトランスマッタのイネーブルは独立していますので、もう一方をオンせずに片方を動作させることができます (コントロール・ビットrx\_enとtx\_en)。場合によってはこの機能が有用なことがあります。例えば、リーダ・フィールドが保持される必要があり、トランスポンダ応答が見込まれていない場合には、レシーバをオフにして電流を節約できます。もう1つの例は、イニシエータによってRFフィールドが生成され、レシーバだけが動作している、NFCIP-1アクティブ通信受信モードです。

[動作コントロール・レジスタ](#)のwuビットをアサートしてそれ以外のビットを0にセットすると、ST25R3911Bは、ローパワーでカードの存在を検出するために使用されるウェイクアップ・モードとなります。このモードでは、低消費電力のRC発振器とレジスタで設定可能なウェイクアップ・タイマを使用して、周期的な測定のスケジュール設定を行います。測定値とあらかじめ設定された基準値との差が検出されると、マイクロコントローラをウェイクアップするために割込みが送信されます。

## 1.2.2 トランスマッタ

トランスマッタには、RFO1ピンとRFO2ピンに接続されている同一のプッシュプル・ドライバ・ブロックが2個搭載されています。これらのドライバは、外部アンテナLCタンクを差動で駆動しています。また、[IOコンフィギュレーション・レジスタ1](#)のsingleビットを1にセットすると、この2個のドライバのうち1個だけを動作させることもできます。それぞれのドライバは、バイナリ重み付け出力抵抗を持つセグメント8個によって構成されています。全セグメントがオンになった場合のMSBセグメントの標準ON抵抗は $2\Omega$ です。通常、出力抵抗は $1\Omega$ です。通常送信 (非変調) レベルを設定するために、全セグメントがオンになります。アンテナの信号振幅を下げるため、および/またはハードウェアを何も変更せずにアンテナQ値を下げる目的で、非変調レベルを駆動する場合に、特定のセグメントをオフにすることも可能です。[RFO通常レベル設定レジスタ](#)によって、どのセグメントをオンにして通常送信 (非変調) レベルを設定するかが設定されます。デフォルト設定は、全セグメントのオンです。

シングル・エンド・モードを使うと、アンテナLCタンクの部品数 (それゆえにコストも) が半分になりますが、出力パワーも下がります。シングル・モードでは、[IOコンフィギュレーション・レジスタ1](#)のrfo2ビットを制御することによって、2個のアンテナLCタンクを2つのRFO出力に接続して、その間を多重化できます。

データを送信するには、トランスマッタ出力レベルが変調される必要があります。AM変調とOOK変調の両方にに対応しています。変調の種類は、[補助設定レジスタ](#)のtr\_amビットを設定することによって設定されます。

OOK変調 (ISO14443Aなど) の間、トランスマッタのドライバはキャリア周波数の駆動を停止しています。その結果として、アンテナLCタンク発振の振幅が減衰しますが、この減衰の時定数は、LCタンクのQ値によって設定されます。[補助設定レジスタ](#)のbit ook\_hrビットをアサートすることによって、OOK変調の場合の減衰時間を短縮できます。このビットが論理値の1に設定されると、OOK変調の間、ドライバはトライステートとなります。

変調期間の間、出力ドライバのインピーダンスを増加させることによって、AM変調 (ISO14443Bなど) が行われます。この変調は、オンになっているドライバ・セグメントの個数を減らすことによって行われます。AM変調されたレベルは、[AM変調度コントロール・レジスタ](#)にターゲットの変調度を設定し、ダイレクト・コマンド Calibrate Modulation Depthを送信することによって、ターゲットの変調度に自動調整できます。詳細は、[セクション 1.2.20: AM変調度: 設定と補正](#)を参照してください。

### 緩やかなトランスマッタ立上げ

トランスマッタが有効化されると、アンテナLCタンクをフル・パワーで駆動し始めますが、アンテナが放射するフィールドの立上がりは、アンテナLCタンクのQ値によって設定されます。

しかしながら、有効化されたときに、より長い遷移時間でリーダ・フィールドが立ち上がる必要のあるリーダ・システムもあります。STIF (Syndicat des transports d'Ile de France) 仕様では、フィールドの10%から90%の遷移時間が10  $\mu$ s以上であることが求められます。ST25R3911Bはこの機能に対応しています。トランスマッタが無効化されたときには、VSP\_RF安定化電圧が急激に下がることで、トランスマッタが有効化されたときには、その電圧が立ち上がることでわかります。標準遷移時間は、3 V電源で15  $\mu$ s、5 V電源で20  $\mu$ sとなります。

緩やかな遷移を実装する手順:

- トランスマッタが無効化されているときに、[IOコンフィギュレーション・レジスタ2](#)のslow\_upビットを1にセットします。この状態を最低2 ms保ち、VSP\_RFを放電させます。

- トランスマッタをイネーブルすると、その出力が緩やかに立ち上がります。

- 何かコマンドを送信する前に、slow\_upビットを0に戻します。

### 1.2.3 レシーバ

レシーバは、13.56 MHzキャリア周波数に重畠されたトランスポンダのサブキャリア変調の復調を行います。サブキャリア信号のAM復調および/またはPM復調、増幅、バンドパス・フィルタ処理、デジタル化を行います。さらには、RSSI測定と自動ゲイン・コントロール (AGC) とスケルチも行います。

標準的な用途では、レシーバ入力のRFI1とRFI2は、アンテナ・コイルの端子に直接接続された容量分圧器の出力となります。この考え方によって、この2つの入力信号がアンテナ・コイルの電圧と同相であることが保証されます。容量分圧器は、RFI1とRFI2の入力信号のピーク値がV<sub>SP\_A</sub>電源電圧レベルを超えないことが保証されるように設計されなければなりません。

レシーバは、完全な受信チャネル2本から構成されており、その1本がAM復調用、もう1本がPM復調用です。両方のチャネルが有効化されている場合、受信フレーミングに使用されるチャネルは、受信フレーミング・ロジックによって自動的に選択されます。[動作コントロール・レジスタ](#)のrx\_enビットが1にセットされると、レシーバはオンになります。さらに、[動作コントロール・レジスタ](#)にはrx\_chnビットとrx\_manビットが含まれていて、rx\_chnビットによって、AMとPMの両方の復調チャネルが有効になるのか、その1つだけが有効になるのかが設定され、rx\_manビットによって、両方のチャネルが（自動で、または手動で）有効である場合のチャネル選択モードが設定されます。レシーバの動作は、4個のレシーバ・コンフィギュレーション・レジスタによって制御されます。

レシーバの動作は、レシーバの入力に変調信号が見込まれる場合にHighにセットされるrx\_on信号によっても制御されます。この信号は、RSSIとAGCの制御に用いられており、フレーミング・ロジックによるレシーバの出力の処理の有効化も行います。マスク受信タイマがタイムアウトすると、rx\_on信号は自動的にHighにセットされます。ダイレクト・コマンド Mask Receive DataとUnmask Receive Dataを送信することにより、rx\_on信号を直接制御することも可能です。[図 4 レシーバのブロック図](#)の詳細を図4に示します。

図4. レシーバのブロック図

## 復調ステージ

第1ステージは、HFフィールド・キャリアに重畠されたトランスポンダのサブキャリア信号の復調を行います。AM復調用として、次の2つの異なるブロックが組み込まれています。

- ピーク検出器

- AM復調器ミキサ

使用される復調器の選択は、[レシーバ・コンフィギュレーション・レジスタ1](#)のamd\_selビットによります。

ピーク検出器では、ピーク・フォロワを使用してAM復調を行います。あらゆるコモン・モード信号を抑圧するために、プラス側のピークとマイナス側のピークが両方とも追跡されます。ピーク検出器には速度上の制限があり、fc/8 (1700 kHz) までのサブキャリア周波数で動作可能です。その復調ゲインはG = 0.7となります。その入力は、復調器入力（通常RFI1）のみから取られます。

AM復調器ミキサでは、両方のレシーバ入力（RFI1とRFI2）の同期整流が使用されます。そのゲインはG = 0.55となります。ミキサ復調器は、VHBRサブキャリア周波数（fc/8以上）に最適化されています。fc/8 (1700 kHz) のサブキャリア周波数では、ピーク・フォロワとミキサ復調器のどちらも使用できますが、fc/4とfc/2ではミキサ復調器のみが使用可能です。

PM復調についてもミキサで行うことができます。PM復調ミキサには、1%の位相変化に対して60 mV差動信号 (16.67 mV / °) の差動出力があります。その動作は、fc/8 (1700 kHz) までのサブキャリア周波数に最適化されています。

復調が外部で行われる場合には、[レシーバ・コンフィギュレーション・レジスタ2](#)のlf\_enビットを選択することにより、RFI1ピンとRFI2ピンに印加されたLF信号を、直接ゲイン/フィルタリングステージに多重化することができます。

## フィルタリング/ゲインステージ

レシーバ・チェーンは、バンドパス・フィルタリング特性を備えています。フィルタリングは、キャリア周波数と低周波ノイズとDC成分は除去しながら、サブキャリア周波数を通すように最適化されています。

フィルタリングとゲインは3つのステージで実装されており、第1ステージと最終ステージは一次のハイパス特性、第2ステージは二次のローパス特性を備えています。

ゲイン特性とフィルタリング特性は、[レシーバ・コンフィギュレーション・レジスタ1](#)（フィルタリング）、[レシーバ・コンフィギュレーション・レジスタ3](#)（第1ステージゲイン）、[レシーバ・コンフィギュレーション・レジスタ4](#)（第2と最終のゲインステージ）に書き込むことによって最適化可能です。

第1ステージのゲインは約20 dBあり、2.5 dB刻みで6ステップ分下げることができます。スペシャル・ブースト・モードも備えており、最大ゲインがさらに5.5 dBブーストされます。VHBR (fc/8とfc/4) の場合には、ゲインは下がります。第1ステージのゲインは、[レシーバ・コンフィギュレーション・レジスタ3](#)に書き込むことによってのみ修正可能です。このレジスタのデフォルト設定は、最小ゲインです。デフォルトの第1ステージゼロ点は60 kHzに設定されていますが、[レシーバ・コンフィギュレーション・レジスタ1](#)のオプション・ビットに書き込むことによって、40 kHzまたは12 kHzに下げることもできます。第1ステージと第3ステージのゼロ点は、共通コントロール・ビットで制御します（[表 1](#)参照）。

表 1. 第1/第3ステージゼロ点設定

| rec1<2> h200 | rec1<1> h80 | rec1<0> z12k | 第1ステージゼロ点 | 第3ステージゼロ点 |

|--------------|-------------|--------------|-----------|-----------|

| 0            | 0           | 0            | 60 kHz    | 400 kHz   |

| 1            | 0           | 0            | 60 kHz    | 200 kHz   |

| 0            | 1           | 0            | 40 kHz    | 80 kHz    |

| 0            | 0           | 1            | 12 kHz    | 200 kHz   |

| 0            | 1           | 1            | 12 kHz    | 80 kHz    |

| 1            | 0           | 1            | 12 kHz    | 200 kHz   |

| その他          |             |              | 未使用       |           |

第2と第3ステージのゲインは23 dBあり、3 dB刻みで6ステップ分下げることができます。これら2つのステージのゲインは、AGCループとスケルチ・ループに含まれています。[レシーバ・コンフィギュレーション・レジスタ4](#)で手動設定することもできます。AGC/スケルチ/RSSIブロックをリセットするには、ダイレクト・コマンドReset Rx Gainを送信する必要があります。このコマンドを送信すると、現在のスケルチ設定がクリアされ、ゲイン減少コンフィギュレーションが、[レシーバ・コンフィギュレーション・レジスタ4](#)からAGC/スケルチ・ブロックの内部シャドウ・レジスタにロードされます。第2ステージは二次のローパス・フィルタ特性を備えており、通過帯域は、[レシーバ・コンフィギュレーション・レジスタ1](#)のlp2 ~ lp0ビットを用いて、サブキャリア周波数に従って調整されます。

各設定に対する-1 dB周波数とカットオフ周波数は、[表 2](#)を参照してください。

表 2. ローパス・コントロール

| rec1<5> lp2 | rec1<4> lp1 | rec1<3> lp0 | -1 dBポイント |

|-------------|-------------|-------------|-----------|

| 0           | 0           | 0           | 1200 kHz  |

| 0           | 0           | 1           | 600 kHz   |

| 0           | 1           | 1           | 300 kHz   |

| 1           | 0           | 0           | 2 MHz     |

| 1           | 0           | 1           | 7 MHz     |

| その他         |             |             | 未使用       |

推奨フィルタ設定の情報を表 3に示します。対応するすべての動作モードと受信ビット・レートに対して、自動プリセットが設定されており、その上に、別の選択肢がいくつか列挙されています。自動プリセットは、ダイレクト・コマンドAnalog Presetを送信することによって行われます。ストリーム・モードとトランスペアレント・モードには自動プリセットはありません。フィルタ特性を選択することによってゲインも変更されるため、各種フィルタ設定に対するゲイン範囲も示されています。

表 3. レシーバのフィルタ選択とゲイン範囲

| rec1<5:3>lp<2:0> | rec1<2>h200 | rec1<1>h80 | rec1<0>z12k | ゲイン (dB) |            |            |       |        | コメント                                                            |

|------------------|-------------|------------|-------------|----------|------------|------------|-------|--------|-----------------------------------------------------------------|

|                  |             |            |             | 最大すべて    | Min1 Max23 | Max1 Min23 | 最小すべて | ブーストあり |                                                                 |

| 000              | 0           | 0          | 0           | 43.4     | 28.0       | 26.4       | 11.0  | 49.8   | ISO14443A fc/128とNFCフォーラム・タイプ1タグ用自動プリセット                        |

| 000              | 1           | 0          | 0           | 44.0     | 29.0       | 27.5       | 12.0  | 49.7   | ISO14443B fc/128とISO14443 fc/64用自動プリセット                         |

| 001              | 1           | 0          | 0           | 44.3     | 29         | 27.0       | 11.7  | 49.8   | 424/484 kHzサブキャリアに推奨                                            |

| 000              | 0           | 1          | 0           | 41.1     | 25.8       | 23.6       | 8.3   | 46.8   | ISO14443 fc/32とfc/16に対する代替選択肢                                   |

| 100              | 0           | 1          | 0           | 32.0     | 17.0       | 17.2       | 2.0   | 37.6   | ISO14443 fc/32とfc/16用自動プリセット<br>fc/8 (1.7 kb/s)に対する代替選択肢        |

| 100              | 0           | 0          | 0           | 32.0     | 17.0       | 17.2       | 2.0   | 37.6   | fc/8 (1.7 kb/s)に対する代替選択肢                                        |

| 000              | 0           | 1          | 1           | 41.1     | 25.8       | 23.6       | 8.3   | 46.8   | FeliCa™ (fc/64, fc/32)用自動プリセット<br>ISO14443 fc/32とfc/16に対する代替選択肢 |

| 101              | 0           | 1          | 0           | 30.0     | 20.0       | 12.0       | 2.0   | 34.0   | fc/8とfc/4に対する代替選択肢                                              |

| 101              | 1           | 0          | 0           | 30.0     | 20.0       | 12.0       | 2.0   | 34.0   | fc/8とfc/4用自動プリセット                                               |

| 000              | 1           | 0          | 1           | 36.5     | 21.5       | 24.9       | 9.9   | 41.5   | NFCIP-1用自動プリセット (イニシャルとターゲット)                                   |

## デジタル化ステージ

デジタル化ステージでは、レシーバから入力されるサブキャリア信号のデジタル表現が生成されます。その後、このデジタル信号は、レシーバ・フレーミング・ロジックによって処理されます。デジタル化ステージは、調整可能なデジタル化ウィンドウ付きウィンドウ・コンパレータ（5段階で設定可能、3 dB刻み、調整範囲 $\pm 33$  mVから $\pm 120$  mVまで）で構成されています。デジタル化ウィンドウの調整は、AGCループとスケルチ・ループに含まれています。デジタル化ウィンドウは、さらに、[レシーバ・コンフィギュレーション・レジスタ4](#)で手動設定も可能です。

## AGC、スケルチ、RSSI

先に述べたように、第2と第3のゲインステージでは、ゲインとデジタル化ステージウィンドウはAGCループとスケルチ・ループに含まれています。11種類の設定が利用可能です。デフォルト状態は、最小のデジタイザ・ウィンドウと最大ゲインを特徴としています。最初の4ステップでは、デジタイザ・ウィンドウが3 dB刻みで増加し、さらに次の6刻みでは、第2と第3のゲインステージのゲインがこちらも3 dBステップで減少します。スケルチとAGCが開始される初期設定は、[レシーバ・コンフィギュレーション・レジスタ4](#)に設定されています。[ゲイン減少状態レジスタ](#)には、スケルチとAGCとレシーバ・コンフィギュレーション・レジスタ4の初期設定値の結果である、ゲインの実際の状態が表示されます。タイプAなどのビット・コリジョン防止の間は、AGCを無効とする必要があります。

### スケルチ

この機能は、ノイズの多い状態におけるレシーバの動作のために設計されています。ノイズはタグから出ていることも（リーダ・コマンドの処理が原因）、ノイズの多い環境から出ていることもあります。このノイズは、トランスポンダ（カード・タグ）応答の開始と誤って解釈されることがあります。コード・エラーの原因となります。

スケルチ・手続きの間に、デジタル化コンパレータの出力が監視されています。50  $\mu$ sの時間周期の間にこの出力に2回を超える遷移がある場合には、レシーバのゲインが3 dB引き下げられ、次の50  $\mu$ sの間、出力が監視されます。50  $\mu$ sの間の遷移回数が2回以下となるまで、またはゲインの下げ幅が最大値となるまで、この手続きが繰り返されます。このゲインの引き下げは、ダイレクト・コマンド Reset Rx Gainを送信することによってクリアされます。

スケルチを行う方法としては、自動モードとダイレクト・コマンドSquelchを用いるものとの2つがあります。

1. [レシーバ・コンフィギュレーション・レジスタ2](#)のsqm\_dynビットがセットされると、自動モードが有効になります。Txの終了から18.88 s後に自動的にアクティブ化され、マスク受信タイマがタイムアウトすると停止します。このモードは、主として、タグ応答が予期されていない間（マスク受信タイマによって保護）にタグの処理によって生まれるノイズを抑圧するためのものです。

2. rx\_on信号がLowであるときに送信された場合には、Squelch コマンドは受理されます。ノイズのあるタイム・ウィンドウがコントローラに既知である場合に使用できます。

### AGC

AGC（自動ゲイン・コントロール）は、ゲインを下げてレシーバ・チェーンが飽和しないように保つために使われます。ゲインが適切に調整されると、復調処理でもシステムのノイズによる影響を受けてくくなります。

AGC動作は、rx\_on信号がHighにアサートされたときに開始され、それがLowにリセットされるとリセットされます。rx\_on信号がHighからLowに遷移すると、レシーバのゲインの状態が[ゲイン減少状態レジスタ](#)に格納されます。後続ステージでこのレジスタを読み出すことにより、最後の受信中に使用されたゲイン設定の情報が得られます。

AGCがオンになると、デジタイザステージへの入力が飽和しないように、レシーバのゲインが下がります。AGCシステムには、デジタル化ウィンドウ・コンパレータよりも3.5倍大きいウィンドウを備えたコンパレータが含まれています。AGC機能が有効化されると、そのウィンドウ・コンパレータの出力に遷移がなくなるまで、ゲインが下げられます。この手続きによって、デジタル化ウィンドウのコンパレータへの入力は、その閾値の3.5倍未満の大きさであることが保証されます。

AGC動作は、[レシーバ・コンフィギュレーション・レジスタ2](#)のコントロール・ビットagc\_enとagc\_mとagc\_fastによって制御されます。agc\_enビットによってAGC動作が有効となり、agc\_mビットによってAGCモードが設定され、agc\_algビットによってAGCアルゴリズムが設定されます。

2つのAGCモードが利用可能です。AGCは（rx\_on信号がHighである限り）Rx処理全体を通じて動作可能ですし、最初の8パルスのサブキャリア・パルスの間だけ有効とすることもできます。

2つのAGCアルゴリズムが利用可能です。コード4h（最大デジタイザ・ウィンドウ、最大ゲイン）をプリセットするか、コードを0h（最小デジタイザ・ウィンドウ、最大ゲイン）にリセットすることによって、AGCの動作を開始できます。

プリセット・コード付きアルゴリズムの方が高速ですので、短いSOF（ISO14443A fc/128など）のプロトコルにはこちらを推奨します。

デフォルトのAGC設定を次に示します。

- AGCが有効

- Rx処理全体でAGCが動作

- プリセット付きアルゴリズムを使用

## RSSI

レシーバは、両チャネルに対する対数RSSI（受信信号強度インジケータ）測定も行います。RSSI測定は、rx\_onの立上がりエッジの後に開始されます。rx\_on信号がHighである限りアクティブのままであり、rx\_onがLowになるとフリーズします。RSSIはピーク・ホールド・システムであり、その値は初期値のゼロから増えるのみです。AGCがゲインを下げるたびに、RSSI測定はリセットされてゼロから始まります。RSSI測定の結果は4ビットの値であり、[RSSI表示レジスタ](#)を読み出すことによって確認できます。 LSBステップは2.8 dBであり、最大コードはDh（13d）です。

RSSI測定はピーク・ホールド型ですので、RSSI測定の結果は信号強度の変動に追従しません（最大値が保持されます）。RSSIの変動に追従するために、ダイレクト・コマンドClear RSSIを送信することによって、RSSIビットをリセットして測定を再スタートできます。

## NFCIP-1アクティブ通信モードのレシーバ

アクティブNFCIP-1通信を確実に受信可能とするために、レシーバにはいくつかの機能が組み込まれています。

NFCIP-1モードが設定された後に、ダイレクト・コマンドAnalog Presetを送信することによって、これらのすべての設定値を自動的にプリセットできます。フィルタリング・オプションに加えて、[レシーバ・コンフィギュレーション・レジスタ3](#)の中には、NFCIP-1アクティブ通信モード専用のコンフィギュレーション・ビットが2ビット格納されています。

limビットによって、第1と第2のゲインステージの後に位置するクリッピング回路が有効化されます。クリッピング回路の機能は、それ以降のフィルタリング段に対する信号レベルを制限することです（NFCIP-1ピアが近接している場合には、入力信号レベルが非常に高くなることがあります）。

rg\_nfcビットによって、第2と第3のフィルタリングステージのゲイン下げ幅が強制的に-6 dBとなる一方で、デジタイザのコンパレータ・ウィンドウが最大レベルに維持されます。

### 1.2.4 静電容量センサ

静電容量センサ・ブロック（[図 5](#)）によって、タグの存在をローパワーで検出可能となります。

静電容量測定システムには電極が2つ含まれています。1つは数百kHzレンジの固定周波数の電界を放射する励起電極（CSO）であり、2つめは検出電極（CSI）です。検出電極に生成される電荷量は、2つの電極の間の静電容量を示しています。静電容量センサ電極は、GNDに対する寄生容量（最大25 pF）と、入力漏洩（最大1 MΩ）に耐性があります。

検出電極上の電荷は、励起電極の周波数で生成されますので、その検出には同期整流器が用いられます。これによって、妨害が十分に排除され、（励起電極を除く全ノードの）寄生容量に対して高い耐性を持つことが保証されます。同期整流器の出力は、励起電極と検出電極の間の静電容量に比例する

DC電圧です。出力DC電圧は、絶対モードでA/Dコンバータによって変換されます。その結果は、[A/Dコンバータ出力レジスタ](#)に格納されます（[セクション 1.2.8: A/Dコンバータ](#)も参照）。

図 5. 静電容量センサブロック図

この2個の電極に近づくあらゆる導電性の物体（人間の手またはタグのアンテナ巻線）により、励起電極と検出電極の間の静電容量が変化しますが、それは、2個の電極の間の経路の一部にコンダクタنسを与えることにより、この2つの間の距離が「短縮」されるためです。

静電容量の測定は、ダイレクト・コマンドMeasure Capacitanceの送信によって始まります。ST25R3911Bは、自動的にウェイクアップし、静電容量の測定を周期的に行うように設定することも可能です。その結果は、格納された基準値または過去の測定結果の平均値と比較され、この差が既定値よりも大きい場合には、IRQがトリガされてコントローラをウェイクアップします（[セクション 1.2.5: ウェイクアップ・モード](#)も参照）。

静電容量センサのゲインは、[静電容量センサ・コントロール・レジスタ](#)で調整可能です。デフォルト・ゲインは2.8 V/pF（標準値）、最大ゲインは6.5 V/pF（標準値）です。A/Dコンバータの LSBは約7.8 mVに相当しますので、デフォルト・ゲインでは感度は2.8 fF/LSB（最大ゲインの場合には1.2 fF/LSB）となります。

静電容量の測定時間は200  $\mu$ sであり、測定中の消費電流は1.1 mA（標準値）です。たとえば、ウェイクアップ・モードで静電容量の測定が100 msごとに行われたとすると、その結果としての平均消費電流は5.8  $\mu$ Aとなります（3.6  $\mu$ Aはウェイクアップ・モードでのスタンバイ消費電流です）。

### 静電容量センサ補正

静電容量センサには、CSIとCSOの間の寄生容量を内部的に補償して、容量の変動に関する情報に対して測定範囲の全体が使えるようにする補正ユニットが含まれています。補正の制御には5ビットが使用されます。最小補正単位は0.1 pF、利用可能な補正範囲は3.1 pFです。補正は、[静電容量センサ・コントロール・レジスタ](#)に書き込むことによって手動で、またはダイレクト・コマンドCalibrate Capacitive Sensorを送信することによって自動で行うことができます。Calibrate Capacitive Sensorコマンドの状態と、その結果として得られる補正值は、[静電容量センサ表示レジスタ](#)に格納されます。

水晶発振器とリーダ磁界による静電容量センサへの妨害を回避し、再現性のある結果を保証するためには、静電容量の測定と補正は、パワーダウン・モードでのみ行うことを強く推奨します。

## 1.2.5 ウェイクアップ・モード

[動作コントロール・レジスタ](#)のwuビットをアサートしてそれ以外のビットを0にセットすると、ST25R3911Bは、ローパワーでカードの存在を検出するために使用されるウェイクアップ・モードとなります。ST25R3911Bには、ローパワーでのカード存在検出に複数の手段（静電容量センサ、位相測定、振幅測定）が組み込まれています。内蔵されたローパワー 32 kHz RC発振器とレジスタで設定可能なウェイクアップ・タイマを使用して、周期的な検出のスケジュール設定を行います。

通常、カードの存在は、いわゆるポーリング・ループによって検出されます。この処理では、リーダ・フィールドに定期的に同調させて、コントローラは、RFコマンドを使用してカードが存在するかどうかを確認します。コマンドが送信可能となる5 ms前にリーダ・フィールドに同調している必要があるため、この手続きは大量のエネルギーを消費します。

カードの存在をローパワーで検出するには、カードによって生まれるリーダ環境の変化を検出します。変化が検出されると、マイクロコントローラに割込みが送信されます。その結果として、コントローラは通常のポーリング・ループを実行できます。

ウェイクアップ・モードでは、ST25R3911Bは、設定されたリーダ環境の測定を定期的に実施し、設定された基準値との差が検出された場合には、IRQをコントローラに送信します。

カードの存在は、位相、振幅、静電容量センサの測定を行うことにより検出可能です。

リーダのアンテナ・コイルに近接してカードが存在すると、アンテナのLCタンク信号の位相と振幅に変化が生じます。位相または振幅の測定を行うために必要なリーダ・フィールドのアクティベーション時間は、プロトコル・アクティベーション・コマンドの送信に必要なアクティベーション時間と比較すると、非常に短く（~20  $\mu$ s）なっています。

さらに、カードに電源を入れて結合効果を生じさせる必要がないため、測定中のパワー・レベルは、通常動作中のパワー・レベルよりも低い場合があります。[RFO通常レベル設定レジスタ](#)を変更することで、放射パワーを下げることができます。

静電容量センサは、2個の励起電極の間の寄生容量の変化を検出します。この静電容量の変化は、カードのアンテナまたはカードを保持する手によって生じている可能性があります。静電容量センサの詳細は、[セクション 1.1.5: 静電容量センサ](#)を参照してください。

31hから3Dhまでの位置のレジスタは、ウェイクアップ・タイマのセットと表示専用です。[ウェイクアップ・タイマ・コントロール・レジスタ](#)は、メインのウェイクアップ・モード設定レジスタです。連続する検出から測定までのタイムアウト時間は、このレジスタで選択します。10 msから800 msまでの範囲のタイムアウトが用意されており、100 msがデフォルト値です。利用可能な測定の組み合わせはどれでも選択可能（1、2、またはそれらのすべて）。

次の12個のレジスタ（32hから3Dhまで）では、3通りの可能な検出測定の設定と結果の格納を行います。各測定には、レジスタが4個使用されます。

測定値と基準値の間の差が設定された閾値よりも大きい場合、IRQが送信されます。基準値には、以下の2通りの可能な定義があります。

1. ST25R3911Bは、以前の測定値に基づいて基準値を計算可能です。

(自動平均化)

2. コントローラが基準値を決定し、レジスタに格納します。

4個連続のうちの最初のレジスタは、[振幅測定コンフィギュレーション・レジスタ](#)です。IRQがトリガされる基準値に対する差と、基準値の設定方法と、自動平均化の場合の最終測定結果の重みが、このレジスタによって設定されます。基準がコントローラによって設定される場合には、次のレジスタに基準値が格納されます。その次の2個のレジスタは表示レジスタです。最初のレジスタに自動平均化の基準が格納され、次のレジスタに最後の測定の結果が格納されます。

ウェイクアップ・モード・コンフィギュレーション・レジスタは、ウェイクアップ・モードに入る前に設定する必要があります。ウェイクアップ・モードがアクティブである間に設定を何か修正すると、予測不可能な結果になるおそれがあります。

### 自動平均化

自動平均化の場合、毎回の測定後に、基準値は以下の式によって再計算されます。

$$\text{新しい平均値} = \text{元の平均値} + (\text{測定値} + \text{元の平均値}) / \text{重み}$$

十分な精度を得るために、この計算は13ビットで行われます。初期化後（起動時またはSet Defaultコマンドの後）に初めてウェイクアップ・モードに入ったときに、自動平均化処理は初期化されます。初期値は、このレジスタの内容が非ゼロになるまで、測定表示レジスタ（[振幅測定表示レジスタ](#)など）から取得されます。

どの測定コンフィギュレーション・レジスタにも、割込みの原因となる測定が平均値計算のためであるかどうかを設定するビット（[振幅測定コンフィギュレーション・レジスタ](#)のam\_aamビットなど）が含まれています。

## 1.2.6 水晶発振器

水晶発振器は、13.56 MHzから27.12 MHzまでの水晶振動子で動作可能です。[動作コントロール・レジスタ](#)のenビットが1にセットされると、水晶発振器の動作が有効となります。発振器の周波数が安定すると、割込みが送信されてマイクロコントローラに通知します（[セクション 1.3.24: メイン割込みレジスタ](#)参照）。

[補助表示レジスタ](#)のosc\_okビットを見れば、発振器の状態を確認できます。発振器の周波数が安定すると、このビットが「1」にセットされます。

この発振器は、制御された電流源から電源を供給されるインバータステージに基づいています。XTIピンの振幅を1 V<sub>pp</sub>に調節するために、フィードバック・ループがバイアス電流を制御します。

リーダの高速起動を可能とするために、発振器の振幅が750 mV<sub>pp</sub>を超えた時点で割込みが送信されます。

2分周することによって、13.56 MHz信号のデューティー・サイクルが50%であり、トランスマッタの性能に望ましいことが保証されます（PW歪みなし）。したがって、性能向上のために、27.12 MHz水晶振動子を使用することを推奨します。

13.56 MHz水晶振動子の場合には、発振器信号をデジタル化するステージのバイアス電流を増やして、可能な限り低いPW歪みを確保します。

**注：** [VHBR 受信（ビット・レートfc/8以上）](#) の場合には、受信フレーミングに高周波クロックが必要であるため、[27.12 MHz水晶振動子](#)の使用が必須です。

発振器出力は、外部マイクロコントローラによって使用可能である、クロック信号の出力ピン（MCU\_CLK）の駆動にも使用されます。MCU\_CLKピンは、[IOコンフィギュレーション・レジスタ2](#)によって設定します。

## 1.2.7 タイマ

ST25R3911Bには、コントローラのカウンタを動かす必要をなくす複数のタイマが搭載されているため、コントローラのコードを実装する手間が減り、別品種のコントローラへのコードの移植性が向上します。

すべてのタイマには1つ以上の関連するコンフィギュレーション・レジスタがあり、その中で、タイマアウト時間と各種の動作モードが設定されます。これらのコンフィギュレーション・レジスタは、対応するタイマが動作していない間に設定する必要があります。タイマがアクティブである間にタイマの設定をどこか修正すると、予測不可能な結果になるおそれがあります。

ウェイクアップ・タイマ以外のすべてのタイマは、ダイレクト・コマンドClearで停止します。

**注:** [汎用/応答なしタイマ・コントロール・レジスタのnrt\\_envビットが1にセットされている場合には、応答なしタイマは停止しません。](#)

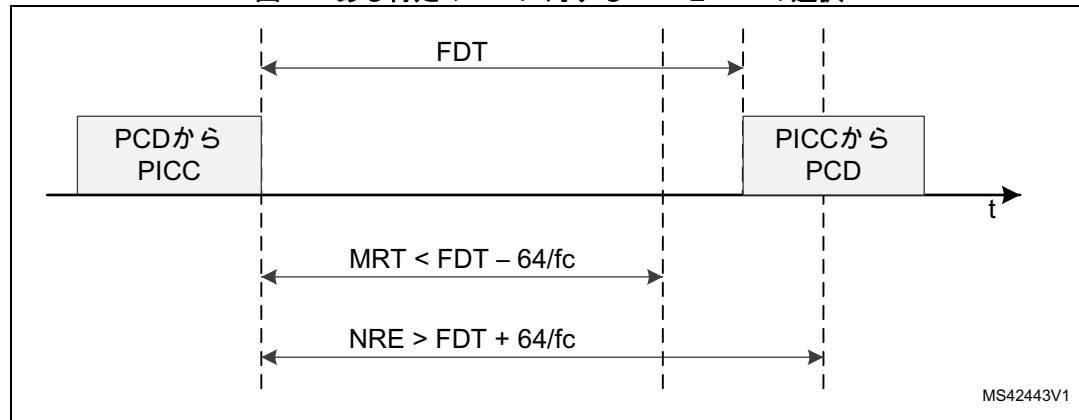

### マスク受信タイマと応答なしタイマ

マスク受信タイマと応答なしタイマは、送信の終わり（EOFの最後）にどちらも自動的に開始されます。

#### マスク受信タイマ

マスク受信タイマは、Txの終了後でタグの応答が予期されていないときに、rx\_on信号をLowに保つことによって、レシーバとフレーミング・ロジック内の受信処理をブロックします。

マスク受信タイマの動作中にスケルチが自動的にオンになります（有効化されている場合）。マスク受信タイマではIRQは生成されません。

マスク受信タイマのタイムアウトは、[マスク受信タイマ・レジスタ](#)で設定します。

NFCIP-1アクティブ通信モードでは、ピアNFCデバイス（通信が行われている相手デバイス）がそのフィールドをオンにすると、マスク受信タイマが開始されます。

ローパワー初期NFCターゲット・モードでは、マスク受信タイマには特別な使い方があります。イニシエータ・フィールドが検出された後に、コントローラは発振器とレギュレータとレシーバをオンにします。マスク受信タイマは、ダイレクト・コマンドStart Mask Receive Timerを送信することで開始されます。マスク受信タイマがタイムアウトした後、イニシエータのメッセージの開始を検出するためにレシーバ出力の監視が始まります。このモードでは、約9.6 msまでの範囲をカバーするために、マスク受信タイマのクロックはさらに8で割られます（1カウントは512/fc）。

#### 応答なしタイマ

名前が示すとおり、このタイマは、送信の最後に始まるある設定時間内に、タグの応答が検出されたかどうかを確認するためのものです。[タイマ/NFC割込みレジスタのl\\_nre](#)フラグは、このタイマのタイムアウトの結果である割込みイベントを示しています。

応答なしタイマは、[応答なしタイマ・レジスタ1](#)と[応答なしタイマ・レジスタ2](#)の2個のレジスタに書き込むことによって設定されます。応答なしタイマの動作オプションは、[汎用/応答なしタイマ・コントロール・レジスタ](#)のnrt\_envビットとnrt\_stepビットを設定することによって設定されます。

nrt\_stepビットによって、応答なしタイマの時間ステップが設定されます。2種類のステップが利用可能であり、64/fc (4.72 μs)は309 msまでの範囲をカバーし、4096/fcは19.8 sまでの範囲をカバーしています。

nrt\_emvビットによって、タイマ動作モードが制御されます。

- このビットが0（デフォルト・モード）にセットされたときには、タグの応答が検出される前に応答なしタイマがタイムアウトした場合にIRQが生成され、レシーバの処理を止めるためにrx\_onが強制的にLowになります。その反対に、タイムアウト前にタグの応答が検出された場合、タイマが停止し、IRQは生成されません。

- このビットが1にセットされたときには、タイマがタイムアウトすると無条件でIRQを生成し、ダイレクト・コマンドClearでも停止しません。これは、タグの応答が検出されたかどうかとIRQは無関係であることを意味しています。タイムアウトの時点でタグの応答の処理が進んでいた場合には、それ以外の処理は行われず、その反対にタグの応答が行われていなかった場合には、rx\_on信号も強制的にLowとなってレシーバの処理が停止します。

ダイレクト・コマンドStart No-Response Timerによっても、応答なしタイマを開始することができます。このコマンドの目的は、応答なしタイマのコントロール・レジスタで設定された範囲を超えて、応答なしタイマのタイムアウトを延長することです。タイマの動作中にこのコマンドが送信された場合には、リセットされて再起動されます。NFCIP-1アクティブ通信モードでは、ダイレクト・コマンドを使用して応答なしタイマを開始することはできません。

ピアNFCデバイス（通信が行われている相手デバイス）がそのフィールドをオンにする前に、このタイマがタイムアウトした場合には、割込みが送信されます。

タイマが非ゼロ値に設定されるすべてのモードにおいて、トランスマッタとタイマの間の同期のため、M\_txeは設定せずに、SPIを通じて割込みl\_txeを読み出すことが不可欠です。

## 汎用タイマ

汎用タイマのトリガは、[汎用/応答なしタイマ・コントロール・レジスタ](#)で設定します。応答処理（受信開始でトリガ、SOFの後）時間の調査や、PCDからPICCへの応答時間（受信終了でトリガ、EOFの後）のタイム・アウトに使用できます。NFCIP-1アクティブ通信モードでは、フィールドのオフ状態のタイムアウトに使用します。どの場合にも、タイムアウトするとIRQが送信されます。

ダイレクト・コマンドStart General Purpose Timerを送信しても、汎用タイマをスタートできます。タイマの動作中にこのコマンドが送信された場合には、リセットされて再起動されます。

## ウェイクアップ・タイマ

ウェイクアップ・タイマは、主としてウェイクアップ・モードで使用されます（[セクション 1.2.5: ウェイクアップ・モード](#)参照）。更に、ダイレクト・コマンドStart Wake-Up Timerを送信することでも使用できます。このコマンドは、ウェイクアップ・モード以外のどの動作モードでも受け付けられます。このコマンドが送信されると、ウェイクアップ・タイマのクロック源として用いられているRC発振器がスタートし、タイムアウトは[ウェイクアップ・タイマ・コントロール・レジスタ](#)の送信によって設定されます。このタイマがタイムアウトすると、[エラー/ウェイクアップ割込みレジスタ](#)のl\_wtフラグとともにIRQが送信されます。

ウェイクアップ・タイマは、他のタイマが使用できないローパワー動作モードで有用です（ローパワー動作モードでは、他のタイマのクロック源である水晶発振器が動作していません）。

注：

ウェイクアップ・タイマのタイムアウト時間の許容誤差は、RC発振器の許容誤差によって決まります。

## 1.2.8 A/Dコンバータ

ST25R3911Bには、8ビット逐次比較型A/Dコンバータが内蔵されています。A/Dコンバータへの入力には、複数のダイレクト・コマンドと調整手続きで使用される異なる信号源からの多重化が可能です。A/D変換の結果はA/Dコンバータ出力レジスタに格納されます。

A/Dコンバータには、絶対モードと相対モードの2つの動作モードがあります。

- 絶対モードでは、下側の基準値は0 Vであり、上側の基準値は2 Vです。このことは、A/Dコンバータの入力範囲が0 ~ 2 Vであることを意味しており、コードの00hは入力が0 V以下であることを、FFhは入力が2 V - 1 LSB以上 (LSBは7.8125 mV) であることを意味します。

- 相対モードでは、下側の基準値は $V_{SP\_A}$ の1/6、上側の基準値は $V_{SP\_A}$ の5/6であるため、入力範囲は1/6 ~ 5/6  $V_{SP\_A}$ となります。

相対モードは、位相測定（位相検出器の出力は電源に比例）でのみ使用されます。それ以外の場合には、絶対モードが使用されます。

## 1.2.9 位相振幅検出器

このブロックは、A/Dコンバータへの入力を供給して、ダイレクト・コマンドMeasure Amplitude and Measure Phaseによって求められる、振幅と位相の測定を実施するために使用されます。ダイレクト・コマンドCalibrate Modulation Depth and Calibrate Antennaによっても、位相と振幅の測定がいくつか行われます。

### 位相検出器

位相検出器は、トランスマッタ出力信号 (RFO1とRFO2) と、アンテナLCタンクの信号に比例している、レシーバ入力信号RFI1とRFI2との間の位相差を観測しています。これらの信号は、まずデジタル化コンバータで処理されます。その後に、このデジタル信号が、強力なローパス・フィルタを備えた位相検出器によって処理されて、平均位相差を得ます。

位相検出器の出力は、2つの入力の位相差に逆比例しています。90°位相シフトによって $V_{SP\_A}/2$ の出力電圧が得られますので、両方の入力が同相であれば出力電圧は $V_{SP\_A}$ となり、逆相であれば出力電圧は0 Vとなります。ダイレクト・コマンドMeasure Phaseを実行中、この出力はA/Dコンバータ入力に多重化されます (Measure Phaseコマンドの実行中には、A/Dコンバータは相対モードとなります)。A/Dコンバータの範囲は1/6 ~ 5/6  $V_{SP\_A}$ であるため、位相検出器の実際の範囲は30°から150°となります。

シフト量が90°と135°である場合の位相検出器の2入力と出力を、それぞれ図6と図7に示します。

図6. 90°位相シフトの場合の位相検出器の入力と出力

図 7. 135°位相シフトの場合の位相検出器の入力と出力

### 振幅検出器

RFI1とRFI2からの信号は、自己ミキシングステージへの入力として使用されます。このステージの出力は、RFI1ピンとRFI2ピンの信号振幅に比例するDC電圧です。ダイレクト・コマンドMeasure Amplitudeの実行中、この出力はA/Dコンバータ入力に多重化されます。

## 1.2.10 外部フィールド検出器

外部フィールド検出器は、RFフィールドを生成する外部デバイスの存在検出に使用されます。NFCIP-1アクティブ通信モードで自動的に起動され、それ以外のモードでも使用可能です。外部フィールド検出器は、ピア検出閾値とコリジョン防止閾値の2つの異なる検出閾値に対応しています。この2つの閾値は、[外部フィールド検出器閾値レジスタ](#)に書き込むことによって、別々に設定できます。外部フィールド検出器の出力の実際の状態は、[補助表示レジスタ](#)を読むことで確認できます。このブロックへの入力は、RFI1ピンからの信号です。

### ピア検出閾値

この閾値は、NFC通信が行われている相手側ピアNFCデバイスによって放射されるフィールド (ST25R3911B が ターゲットと相手側の場合にはイニシエータ・フィールド、ST25R3911B が イニシエータの場合にはターゲット・フィールド) の検出に使用されます。75 mV<sub>pp</sub>から800 mV<sub>pp</sub>までの範囲で選択可能です。この閾値が有効化されると、外部フィールド検出器はローパワー・モードになります。外部フィールドが検出されて、さらにそれがオフされると、割込みが生成されます。このような実装により、外部フィールドが消滅した瞬間の検出にも使用できます。この機能は、ピアNFCデバイス (イニシエータの場合もターゲットの場合もあります) がRFフィールドの放射を停止した瞬間の検出に有用です。

[ビット・レート設定レジスタ](#)でNFCIP-1モード (イニシエータまたはターゲット) が選択されると、外部フィールド検出器は、自動的にローパワー・ピア検出モードで有効化されます。

さらに、[補助設定レジスタ](#)のen\_fdビットを設定することによっても有効化できます。

### コリジョン防止閾値

この閾値は、NFC Field ONコマンド ([NFC Field ONコマンド群](#)参照) を送信することで実行されるRFコリジョン防止シーケンスの間に用いられます。25 mV<sub>pp</sub>から800 mV<sub>pp</sub>までの範囲で選択可能です。

### 1.2.11 電源システム

ST25R3911B (図 8) は、VDD と VDD\_IO の 2 本の正電源ピンを特徴としています。

VDD はメインの電源ピンです。3 個のレギュレータ (VSP\_A、VSP\_D、VSP\_RF) を通じて、ST25R3911B の各ブロックに電源を供給します。

2.4 V から 5.5 V までの範囲の VDD に対応しています。

VDD\_IO は、デジタル通信ピン (I2S、MISO、MOSI、SCLK、IRQ、MCU\_CLK) に対する電源レベルを設定するために使われます。デジタル通信ピンはレベル・シフタを介して ST25R3911B のロジックとインターフェースしますので、内部電源電圧は VDD\_IO よりも高くても低くとも構いません。1.65 V から 5.5 V までの範囲の VDD\_IO に対応しています。

図 8. ST25R3911B の電源

ST25R3911B の電源システムとそれを制御する信号の構成要素を図 8 に示します。

電源システムには、レギュレータ 3 個と、パワーダウン対応ブロック、アナログ基準電圧 (AGD) を生成するブロック、自動電源調整手続きを実行するブロックが含まれています。この 3 個のレギュレータは、アナログ・ブロック (VSP\_A)、ロジック (VSP\_D)、トランスマッタ (VSP\_RF) に電源を供給しています。5 V 電源では、3.3 V デバイスのみを使用しているアナログ・ブロックとロジック・ブロックに安定化電圧を供給するために、VSP\_A と VSP\_D のレギュレータを必ず使用しなければなりません。3 V 電源での VSP\_A レギュレータと VSP\_D のレギュレータの使用と、あらゆる電源電圧での VSP\_RF の使用は、システム PSRR の向上のために推奨されています。

安定化電圧は、良好な PSRR を維持しながらも、できるだけ高い電圧で安定化されるように、自動的に調整されます。レギュレータのすべてのピンには、それに対応する負電源ピンがあり、外部で接地電位 (VSS) に接続されています。分離されている理由は、内部の電源ライン上の電圧降下によって引き起こされるノイズをデカップリングするためです。

すべてのレギュレータが使用されている ST25R3911B の標準的な応用回路図を図 2 と図 3 に示します。レギュレータのすべてのピンと AGD 電圧は、コンデンサでバッファリングされています。ブロッキング・コンデンサの推奨値の詳細を表 4 に示します。

表 4. ブロッキング・コンデンサの推奨値

| ピン            | 推奨コンデンサ                |

|---------------|------------------------|

| AGD-VSS       | 1 $\mu$ Fと10 nFを並列使用   |

| VSP_A-VSN_A   | 2.2 $\mu$ Fと10 nFを並列使用 |

| VSP_D-VSN_D   | 2.2 $\mu$ Fと10 nFを並列使用 |

| VSP_RF-VSN_RF | 2.2 $\mu$ Fと10 nFを並列使用 |

レギュレータには、電源電圧によって、3.3 V電源モード（最大3.6 V）と5 V電源モード（最大5.5 V）の2種類の基本動作モードがあります。電源モードは、[IOコンフィギュレーション・レジスタ2](#)のsup3 Vビットに書き込むことによって設定されます。デフォルト設定は5 Vですので、3.3 V電源の場合には、起動後にこのビットを1にセットする必要があります。

3.3 Vモードでは、すべてのレギュレータは、2.4 Vから3.4 Vまでの範囲の同じ安定化電圧に設定されます、5 Vモードでは、VSP\_AとVSP\_Dは3.4 V固定で、VSP\_RFのみが3.9 Vから5.1 Vまでの範囲に設定可能です。

レギュレータは、en信号（enは[動作コントロール・レジスタ](#)のコンフィギュレーション・ビットです）がHighのときに動作します。en信号がLowであるときには、ST25R3911Bはローパワーのパワーダウン・モードとなります。このモードでは、電源システムの消費電力についても最小限に抑えられます。

### VSP\_RFレギュレータ

このレギュレータは、トランスマッタのPSRRを向上するためにあります（トランスマッタから電源ノイズが放射されレシーバにフィードバックされます）。次の2つのレジスタを読み書きすることによって、VSP\_RFレギュレータの動作の制御と監視が行われます。

- [レギュレータ電圧コントロール・レジスタ](#)は、レギュレータ・モードと安定化電圧の制御を行います。reg\_sビットによってレギュレータ・モードが制御されます。このビットが0（デフォルト状態）にセットされている場合、安定化電圧はダイレクト・コマンドAdjust Regulatorsを用いて設定されます。reg\_sビットが1にアサートされると、安定化電圧は、同じレジスタのrege\_3ビットからrege\_1ビットによって設定されます。安定化電圧の調整範囲は、電源モードに依存します。5 V電源モードでは、調整範囲は3.9 Vから5.1 Vまでの120 mV刻みであり、3.3 V電源モードでは、調整範囲は2.4 Vから3.4 Vまでの100 mV刻みとなります。デフォルトの安定化電圧が最大電圧（5 V電源モードでは5.1 V、3.3 V電源モードでは3.4 V）となります。

- [レギュレータ/タイマ表示レジスタ](#)は読み出し専用レジスタであり、レギュレータの動作中に実際の安定化電圧を示します。ダイレクト・コマンドAdjust Regulatorsの結果である、実際の安定化電圧を確認できるため、このレジスタは特に自動モードで有用です。

VSP\_RFレギュレータには電流リミッタも含まれており、通常動作では、レギュレータの電流を標準で200 mA<sub>rms</sub>に制限します（短絡時には500 mA）。トランスマッタの出力電流が200 mA<sub>rms</sub>よりも大きいことが求められる場合には、VSP\_RFレギュレータはトランスマッタの電源としては使用できませんので、VSP\_RFを外部でVDDに接続する必要があります（V<sub>DD</sub>よりも高い電源電圧にVSP\_RFを接続することはできません）。

トランスマッタ電流の電圧降下が、ST25R3911Bの消費電力の主な発生源です。この電圧降下は、トランスマッタ・ドライバ内部の降下とVSP\_RFレギュレータの降下から構成されています。このため、ダイレクト・コマンドAdjust Regulatorsを用いて安定化電圧を設定することが推奨されます。そうすることで、レギュレータの電圧降下による消費電力が比較的小さい状態で、良好な電源電圧変動除去比が得られます。

パワーダウン・モードでは、VSP\_RFレギュレータは動作していません。

VSP\_RFピンは、1 kΩ抵抗を介してVDDに接続されています。

抵抗を介して接続することにより、システムの起動が円滑になり、パワーダウン・モードからそれ以外の動作モードへの移行も円滑となります。

### VSP\_AレギュレータとVSP\_Dレギュレータ

VSP\_AレギュレータとVSP\_Dレギュレータは、それぞれST25R3911Bのアナログ・ブロックとデジタル・ブロックへの電源供給に使われます。3.3 Vモードでは、VSP\_AレギュレータとVSP\_Dレギュレータは、VSP\_RFレギュレータと同じ安定化電圧に設定されますが、5 Vモードでは、VSP\_AとVSP\_Dの安定化電圧は3.4 Vに固定されます。

これら2本のピンから電源供給を受けるアナログ・ブロックとデジタル・ブロックには、対応最大電圧が3.6 Vの低電圧トランジスタが含まれているため、5 Vモードでは、VSP\_AレギュレータとVSP\_Dレギュレータを必ず使用しなければなりません。3.3 V電源モードでは、アナログ処理のPSRRを向上させるために、レギュレータの使用を強くお薦めします。

ローコストのアプリケーションでは、VSP\_Dレギュレータを無効にして、デジタル・ブロックにはVSP\_AとVSP\_Dを外部で短絡して電源供給することができます（[IOコンフィギュレーション・レジスタ2](#)のコンフィギュレーション・ビットvsdpd\_off）。VSP\_Dレギュレータが無効化された場合、VSP\_Aが300 mVを超えてVDDよりも低くない限り、VSP\_Dは代わりにVDDから電源供給を受けることができます（3.3 Vモードのみ）。

### パワー・ダウン対応ブロック

パワーダウン・モードでは、電流節約のためにレギュレータは無効となっています。このモードでは、VSP\_DとVSP\_Aが3.6 V未満に維持される、ローパワーのパワーダウン対応ブロックが有効化されます。このモードでの標準的な安定化電圧は、5 V電源で3.1 V、3 V電源で2.2 Vとなります。3.3 V電源モードが設定されると、パワーダウン対応ブロックが無効化され、その出力は1 kΩ抵抗を介してVDDに接続されます。

パワーダウン対応ブロックの標準的な消費電流は、5 V電源で600 nAとなります。

### 電源電圧の測定

ダイレクト・コマンドMeasure Power Supplyを使用すれば、VDDと安定化電圧のVSP\_AとVSP\_DとVSP\_RFを測定できます。

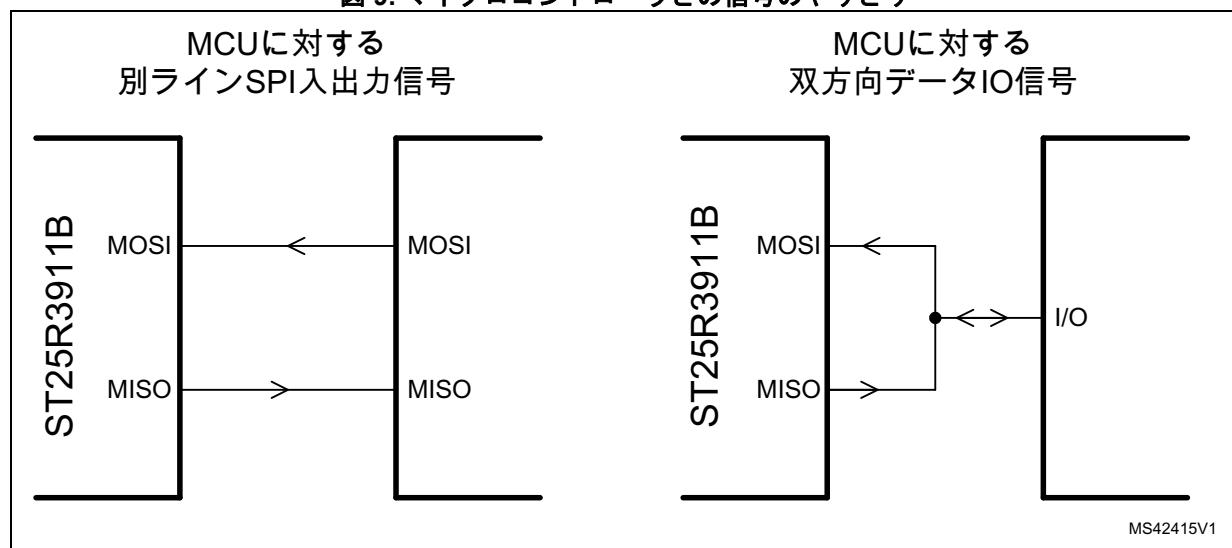

## 1.2.12 外部マイクロコントローラとの通信

ST25R3911Bはスレーブ・デバイスであり、外付けのマイクロコントローラによってすべての通信が開始されます。通信は、4線式シリアル・ペリフェラル・インターフェース（SPI）によって行われます。ST25R3911Bがマイクロコントローラに割込みリクエスト（IRQピン）を送信し、マイクロコントローラは、発振器の動作中にMCU\_CLKピン上に提供されるクロック信号を使用できます。

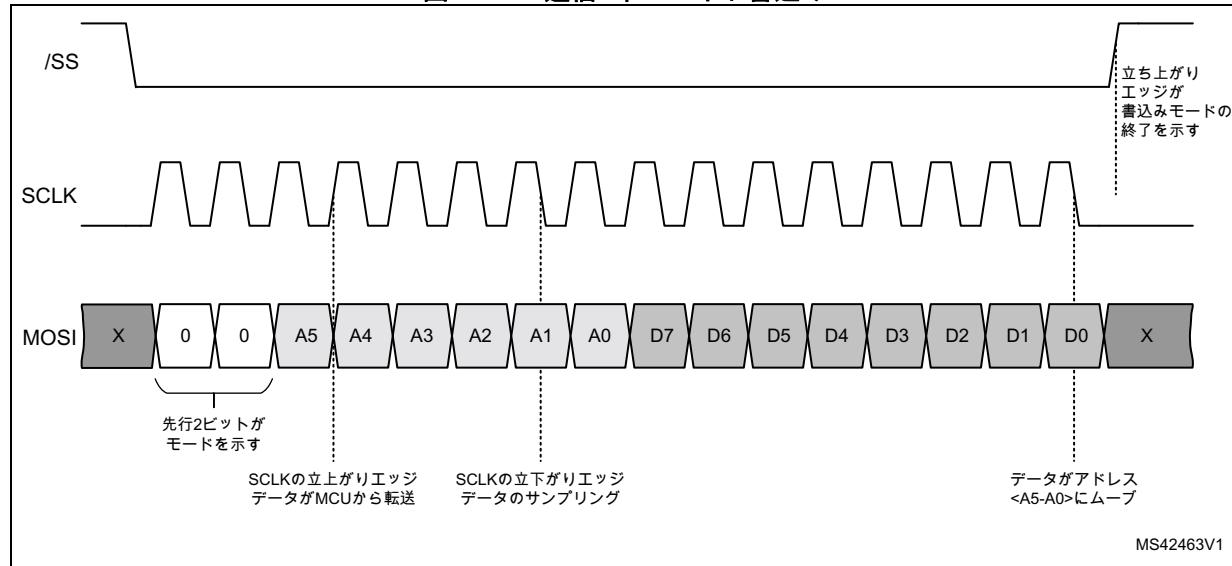

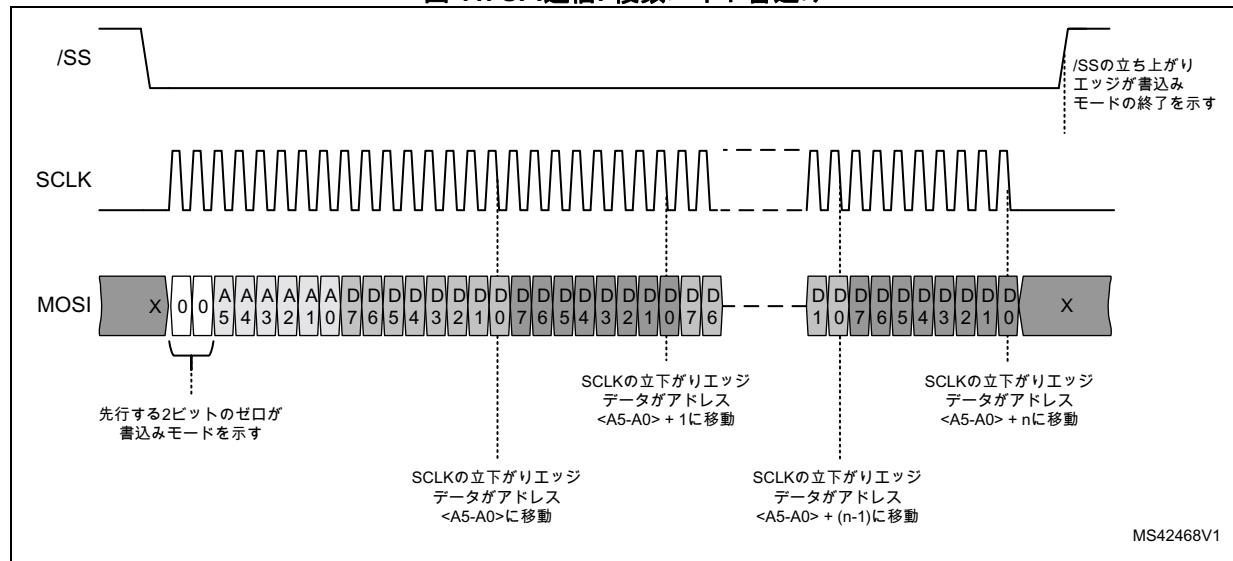

### シリアル・ペリフェラル・インターフェース（SPI）

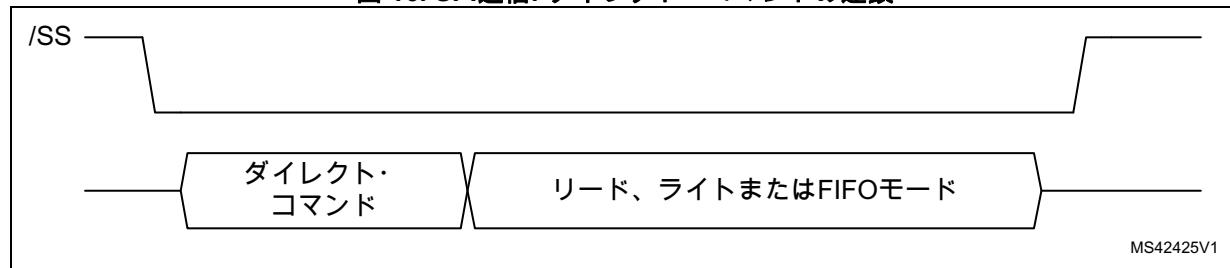

/SS信号がHighであればSPIインターフェースはリセット状態にあり、Lowであれば有効となっています。SPIを使用しないときには、常に/SSをHighに保つことを推奨します。SCLKの立下がりエッジでMOSIがサンプリングされます。すべての通信は8ビット（バイト）のブロック単位で行われます。/SSがHighからLowに遷移した後に最初に送信されるバイトの最初の2ビットによって、SPIの動作モードが設定されます。

表 5. シリアル・データ・インターフェース（4線式インターフェース）信号ライン

| 名称   | 信号             | 信号レベル | 説明                 |

|------|----------------|-------|--------------------|

| /SS  | デジタル入力         | CMOS  | SPIイネーブル（アクティブLow） |

| MOSI | デジタル入力         |       | シリアル・データ入力         |

| MISO | トライステート・デジタル出力 |       | シリアル・データ出力         |

| SCLK | デジタル入力         |       | シリアル通信用クロック        |

MSBビットは必ず最初に送信されます（アドレスとデータが該当）。

読み込みモードと書込みモードは、アドレス自動インクリメントに対応しています。このことは、アドレスと最初のデータ・バイトの後に別のデータ・バイトが送信/読み込まれたとすると、そのデータ・バイトは1だけインクリメントされたアドレスに対して書込み/読み込みが行われることを意味しています。取り得るモードを図 9に示します。

図 9. マイクロコントローラとの信号のやりとり

通常、MISO出力はトライステートであり、出力データ有効時にのみ駆動されます。このため、MOSIとMISOを外部で短絡して双方向信号とすることができます。

MISO出力がトライステートである間、[IOコンフィギュレーション・レジスタ2](#)のオプション・ビットmiso\_pd1とmiso\_pd2をアクティブ化することで、10 kΩプルダウン抵抗をオンにすることができます。

SPI動作モードの情報を表 6に示します。レジスタの読み書きは、どのST25R3911B動作モードでも可能です。en（[動作コントロール・レジスタ](#)のビット7）がセットされていて、水晶発振器の周波数が安定している場合に、FIFOが操作可能です。

表 6. SPI動作モード

| モード            | パターン (通信ビット) |    |      |    |    |    |    |    | 関連データ                        |  |

|----------------|--------------|----|------|----|----|----|----|----|------------------------------|--|

|                | モード          |    | トレーラ |    |    |    |    |    |                              |  |

|                | M1           | M0 | C5   | C4 | C3 | C2 | C1 | C0 |                              |  |

| レジスタ書込み        | 0            | 0  | A5   | A4 | A3 | A2 | A1 | A0 | データ・バイト (自動インクリメントの場合は追加バイト) |  |

| レジスタ読出し        | 0            | 0  | A5   | A4 | A3 | A2 | A1 | A0 |                              |  |

| FIFOロード        | 1            | 0  | 0    | 0  | 0  | 0  | 0  | 0  | FIFOデータの1バイトまたは複数バイト         |  |

| FIFOリセット       | 1            | 0  | 1    | 1  | 1  | 1  | 1  | 1  |                              |  |

| ダイレクト・コマンド・モード | 1            | 1  | C5   | C4 | C3 | C2 | C1 | C0 | -                            |  |

### アドレス指定可能レジスタへのデータ書込み (書き込みモード)

単一バイト書込みの場合と、自動インクリメント・アドレスを用いた複数バイト書込みの場合を図 10 と図 11 に示しますSPI動作モード・ビットの後、書込みが行われるレジスタのアドレスが出力されます。その後、データ・バイトが1バイトまたは複数バイトSPIから転送されますが、必ずMSBからLSBの順番となっています。データ・バイトは、その最終立下がりエッジでレジスタに書き込まれます。8ビット (1バイト) のパケットが送信される前に/SSがHighとなって通信が終了した場合には、このレジスタへの書込みは行われません。設定されたアドレスのレジスタが存在しない場合や、それが読み出し専用レジスタである場合には、書込みは実行されません。

図 10. SPI通信: 単一バイト書込み

図 11. SPI通信: 複数バイト書き込み

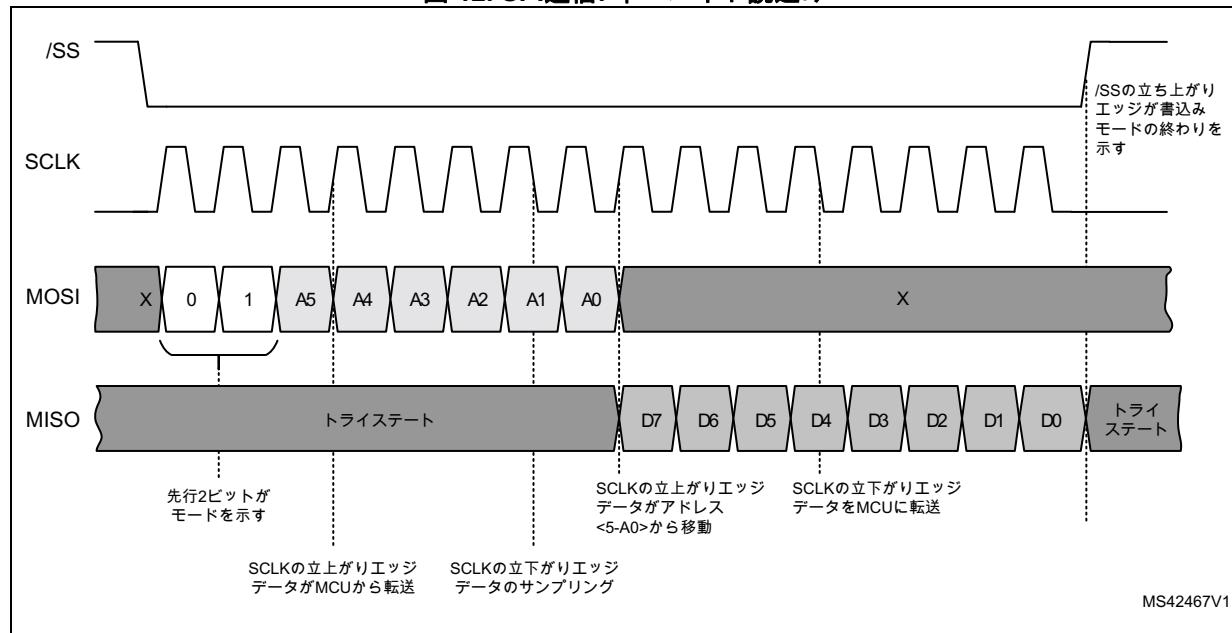

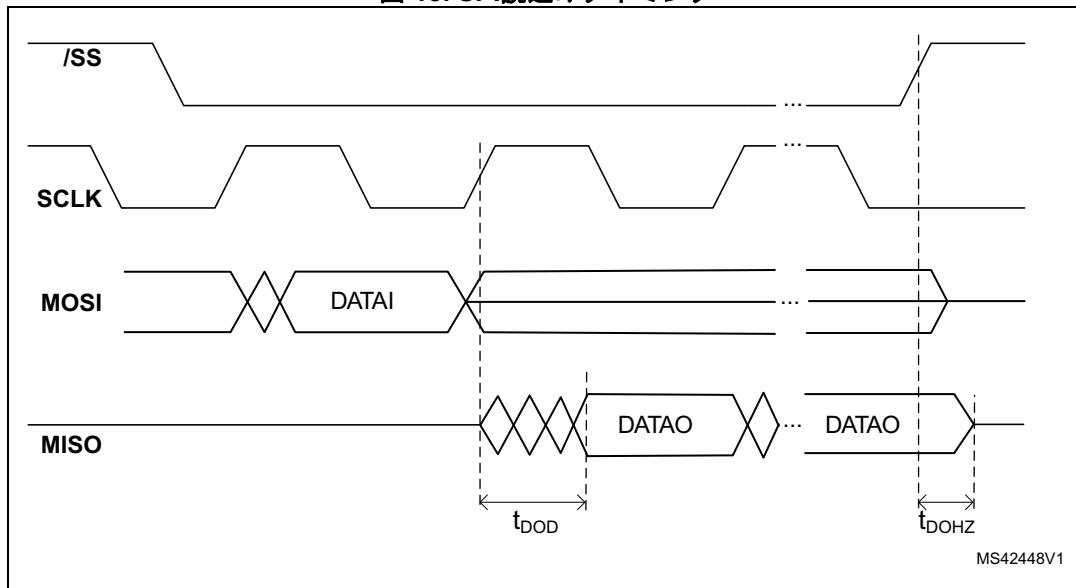

### アドレス指定可能レジスタからのデータ読み込み（読み込みモード）

SPI動作モード・ビットの後、読み込みが行われるレジスタのアドレスがMSBからLSBの順番で出力されます。その後、データ・バイトが1バイト以上MISO出力に転送されますが、必ずMSBからLSBの順番となっています。書き込みモードの場合と同様に、読み込みモードも自動インクリメント・アドレスに対応しています。

MOSIはSCLKの立下がりエッジでサンプリングされ（下図参照）、ST25R3911Bの内部レジスタから読み込まれるデータは、SCLKの立上がりエッジでMISOピンに転送されて、SCLKの立下がりエッジでマスターによりサンプリングされます。

指定アドレスのレジスタが存在しない場合には、オール0のデータがMISOに送信されます。

単一バイトの読み込みの例を図 12に示します。

図 12. SPI通信: 単一バイト読み込み

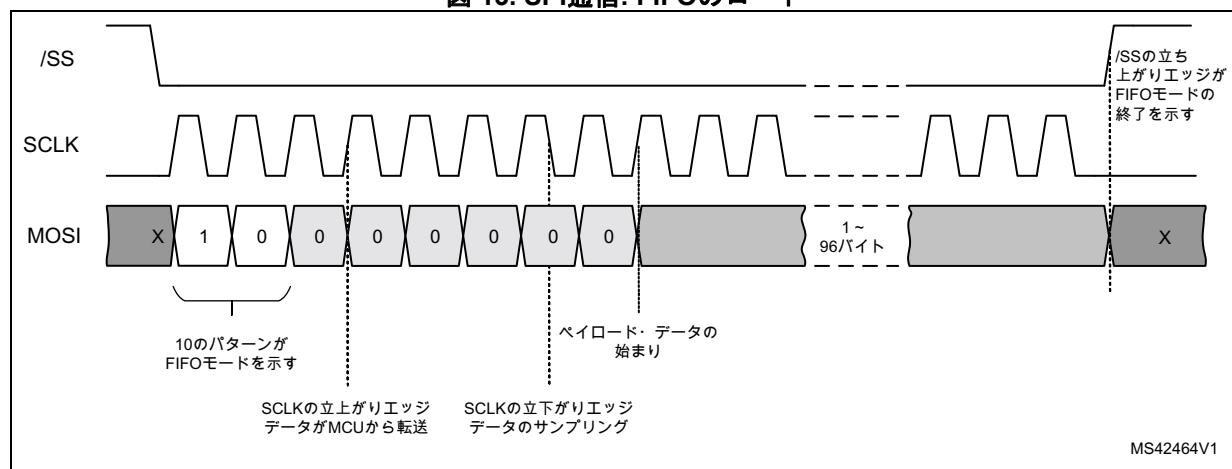

### 送信データのFIFOへのロード

送信データのFIFOへのロードは、アドレス指定可能なレジスタへのデータの書き込みと似ています。違いは、バイトをさらにロードする場合には、すべてのバイトがFIFOに送られることです。SPI動作モード・ビットの10は、FIFO動作であることを示しています。送信データをFIFOにロードする場合には、C5～C0の全ビットが0にセットされます。その後、送信データ（1～96バイト）であるビットストリームが送信可能となります。8ビット（1バイト）のパケットが送信される前に/SSがHighとなってコマンドが終了した場合には、FIFOの中のこの特定バイトへの書き込みは行われません。

FIFOへの送信データのロード方法を図 13に示します。

図 13. SPI通信: FIFOのロード

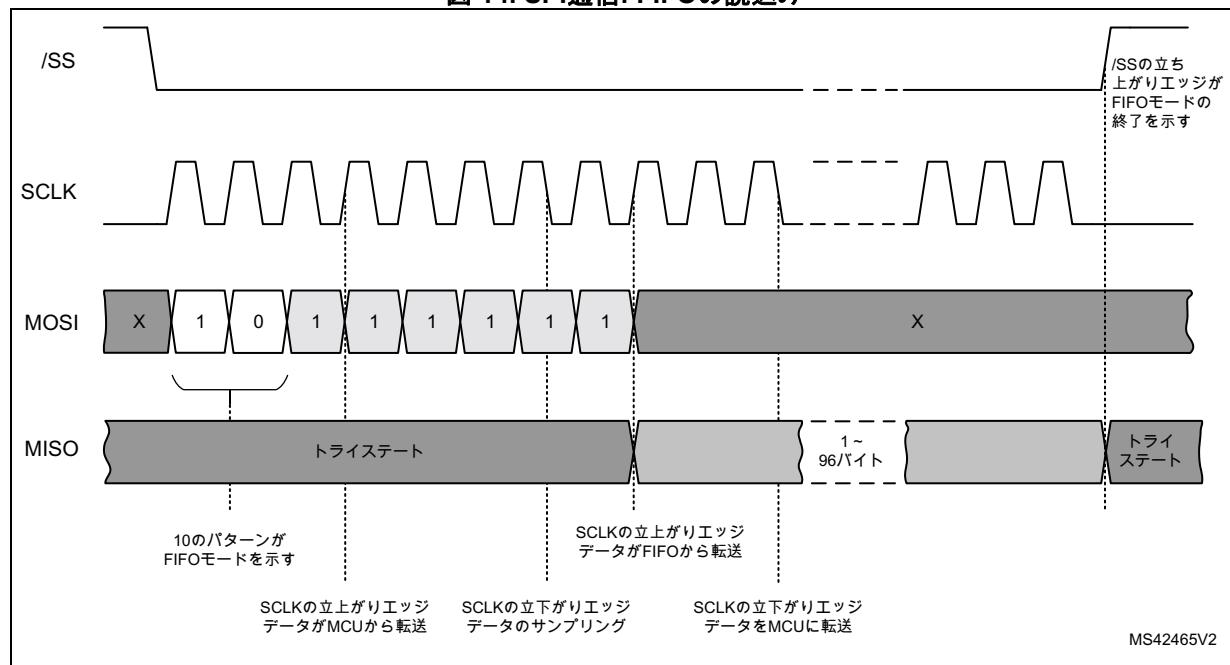

### 受信データのFIFOからの読み込み

受信データのFIFOからの読み込みは、アドレス指定可能なレジスタからのデータの読み込みと似ています。違いは、バイトをさらに読み込む場合には、そのすべてがFIFOからやってくることです。SPI動作モード・ビットの10は、FIFO動作であることを示しています。受信データをFIFOから読み込む場合には、C5～C0の全ビットが1にセットされます。アドレス指定可能なレジスタからのデータの読み込みの場合のように、続くSCLKの立上がりエッジでFIFOからのデータが現れます。8ビット(1バイト)のパケットが読み込まれる前に/SSがHighとなってコマンドが終了した場合には、この特定バイトは読み込まれなかったものとみなされ、次回のFIFO読み込み操作にて最初に読み込まれます。

図 14. SPI通信: FIFOの読み込み

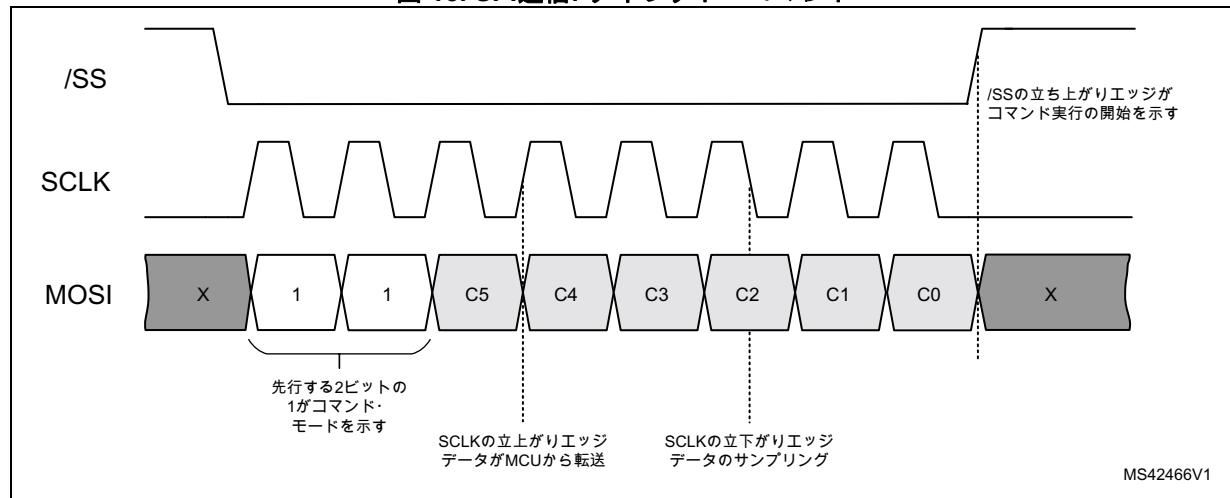

### ダイレクト・コマンド・モード

ダイレクト・コマンド・モードには引数がないため、1バイトのみ送信されます。SPI動作モード・ビットの11は、ダイレクト・コマンド・モードであることを示しています。それに続く6ビットがダイレクト・コマンドの設定であり、MSBからLSBの順に送信されます。コマンドは、最終クロックの立下がりエッジで実行されます(図 15参照)。

ダイレクト・コマンドの中にはすぐに実行されるものもありますが、特定時間要する処理(補正や測定など)を開始するものもあります。このようなコマンドの実行中には、SPIインターフェースで別の処理を開始しないでください。このようなコマンドの実行が終了された後には、IRQが送信されます。

図 15. SPI通信: ダイレクト・コマンド

### ダイレクト・コマンドの連鎖

図 16に示すように、即時実行されるダイレクト・コマンドには、その間で/SS信号を非アクティブとすることなく、別のSPIモード（読み込み、書き込み、FIFO）を続けることができます。

図 16. SPI通信: ダイレクト・コマンドの連鎖

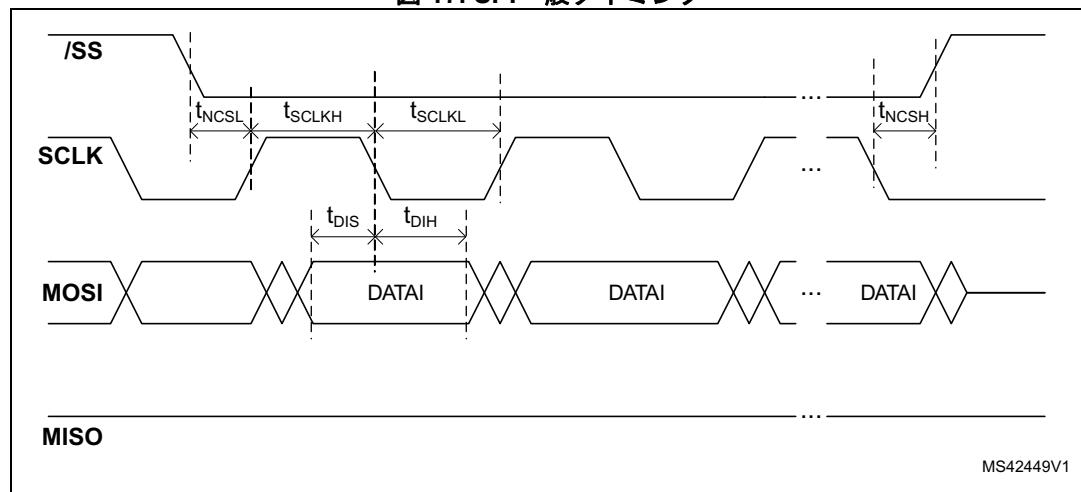

## SPIタイミング

表 7. SPIタイミング

| 記号                                                                                                                 | パラメータ                 | 最小  | 標準 | 最大 | 単位 | コメント                                                                         |

|--------------------------------------------------------------------------------------------------------------------|-----------------------|-----|----|----|----|------------------------------------------------------------------------------|

| 一般タイミング ( $V_{DD} = V_{DD\_IO} = V_{SP\_D} = 3.3\text{ V}$ 、 $25^\circ\text{C}$ )                                  |                       |     |    |    |    |                                                                              |

| $T_{SCLK}$                                                                                                         | SCLK周期                | 167 | -  | -  | ns | $T_{SCLK} = T_{SCLKL} + T_{SCLKH}$ 、これよりも短いSCLK周期を使用すると、不正なFIFO操作となる場合があります。 |

| $T_{SCLKL}$                                                                                                        | SCLK Low              | 70  | -  | 1  |    | -                                                                            |

| $T_{SCLKH}$                                                                                                        | SCLK High             | 70  | -  | -  |    | -                                                                            |

| $T_{SSH}$                                                                                                          | SPIリセット (/SS High)    | 100 | -  | -  |    | -                                                                            |

| $T_{NCSL}$                                                                                                         | /SSの立下がりからSCLKの立上がりまで | 25  | -  | -  |    | 最初のSCLKパルス                                                                   |

| $T_{NCSH}$                                                                                                         | SCLKの立下がりから/SSの立上がりまで | 300 | -  | -  |    | 最後のSCLKパルス                                                                   |

| $T_{DIS}$                                                                                                          | セットアップ時間のデータ          | 10  | -  | -  |    | -                                                                            |

| $T_{DIH}$                                                                                                          | ホールド時間のデータ            | 10  | -  | -  |    | -                                                                            |

| 読み込みタイミング ( $V_{DD} = V_{DD\_IO} = V_{SP\_D} = 3.3\text{ V}$ 、 $25^\circ\text{C}$ 、 $C_{LOAD} \leq 50\text{ pF}$ ) |                       |     |    |    |    |                                                                              |

| $T_{DOD}$                                                                                                          | データ・アウト遅延             | -   | 20 | -  | ns | -                                                                            |

| $T_{DOHZ}$                                                                                                         | データ・アウトからハイ・インピーダンス遅延 | -   | 20 | -  |    | -                                                                            |

図 17. SPI一般タイミング

図 18. SPI読み込みタイミング

### 割込みインターフェース

ST25R3911Bに実装されている割込みレジスタは、次の3つです。[メイン割込みレジスタ](#) メイン割込みレジスタには、6本の割込み原因に関する情報が含まれているのに加えて、2ビットが[TIMA/NFC割込みレジスタ](#)と[エラー/ウェイクアップ割込みレジスタ](#)に詳細がある割込み原因に対する参照となっています。

割込み条件が満たされると、割込み原因が[メイン割込みレジスタ](#)に設定されて、IRQピンがHighに変化します。

表 8. IRQ出力

| 名称  | 信号     | 信号レベル | 説明      |

|-----|--------|-------|---------|

| IRQ | デジタル出力 | CMOS  | 割込み出力ピン |

次にマイクロコントローラが[メイン割込みレジスタ](#)を読み込んで、各種割込み原因の識別を行います。割込みレジスタの0x17と0x18と0x19は、一度に読み込む必要があります。ある割込みレジスタが読み込まれると、その内容は0にリセットされます。この規則の例外は、補助レジスタを指定しているビットです。これらのビットは、対応する補助レジスタが読み込まれたときにのみクリアされます。そのHighへの遷移の原因となった割込みビットが読み込まれると、IRQピンがLowに遷移します。

**注：**IRQ信号がセットされた後速やかにマイクロコントローラが割込みレジスタを読み込みます、割込みの原因となる別イベントが発生した場合には、複数の割込みビットがセットされていることがあります。この場合には、割込みの原因となった最後のビットが読み込まれると、IRQピンがLowに遷移します。

ある特定原因の割込みが不要なのであれば、マスク割込みレジスタの対応ビットを設定して、その割込みを無効にできます。ある特定の割込み原因をマスクすると、その割込みは生成されませんが、それでもなお割込み原因ビットは、割込みレジスタの中でセットされます。

## FIFOウォーター・レベルとFIFOステータス・レジスタ

ST25R3911Bには、96バイトFIFOが含まれています。送信の場合には、外部マイクロコントローラにより前もってロードされたデータを、制御ロジックがフレーミング・ブロックに、そしてトランスマッタへとシフトします。受信中には、復調データはFIFOに格納されており、外部マイクロコントローラが後で受信データをダウンロードできます。

FIFOウォーター・レベル割込みシステムのおかげで、ST25R3911Bの送受信機能は、FIFOサイズによる制限を受けません。FIFO内のデータ内容が「ウォーター・レベル + 1」からウォーター・レベルになり、送信フレーム全体がFIFOにまだロードされていないときには、送信中に割込み（[メイン割込みレジスタ](#)のFIFOウォーター・レベルによるIRQ）が送信されます。このときには、外部マイクロコントローラはFIFOにデータを追加可能です。受信時も同様であり、受信バイト数が「ウォーター・レベル - 1」からウォーター・レベルになると割込みが送信され、FIFOのオーバーフローのために受信データを失わないようにするためには、FIFOからデータをダウンロードする必要があることを、外部マイクロコントローラに通知します。

送信バイトがFIFOにまだすべて書き込まれておらず、FIFOに書き込まれているバイト数がウォーター・レベルよりも少ない場合にも、送信中にウォーター・レベルIRQがセットされます。この場合には、FIFO内のバイト数が4を下回ったときにIRQが送信されます。

注：

**FIFO ロード/読み込みモードで SPI が有効となっている場合には、FIFO IRQ は生成されません。**このため、FIFO ロード/読み込み速度は Tx/Rx ビット・レートよりも速い必要があります。いったん FIFO のロード/読み込みが終了すると、/SS ピンは VDD に上げられる必要があります（/SS が Low のままで、ロジックが FIFO ロード/読み込みモードのままとなります）。

受信データ・フレームがFIFOサイズよりも小さいことをコントローラが知っている場合には、ウォーター・レベル割込みを処理する必要はありません。このような場合には、ウォーター・レベル割込みをマスク可能です。

外部マイクロコントローラは、データが送受信されるよりも早くFIFOを処理する必要があります。実際の送受信ビット・レートの2倍以上のSCLK周波数を使用することをお薦めします。

送受信で利用可能なFIFOウォーター・レベルの設定には[IOコンフィギュレーション・レジスタ1](#)に2つあります。

外部マイクロコントローラは、データ受信の終了後に、どれだけのデータがまだFIFOに格納されているかを知る必要があります。この情報は、未読み出しのFIFO内のバイト数が示されている、[FIFOステータス・レジスタ1](#)と[FIFOステータス・レジスタ2](#)にあります。[FIFOステータス・レジスタ1](#)は、送受信処理中にも読み出し可能であり、FIFO内の現在のバイト数に関する情報を取得できます。その場合には、Rx/Tx処理が進行中であり、レジスタの読み込みが完了したときには、FIFO内のデータ・バイト数はすでに変化している可能性があることを考慮する必要があります。

さらに、[FIFOステータス・レジスタ2](#)には、FIFOが送受信処理中に正しく処理されなかったこと（FIFOオーバーフローまたはFIFOアンダーフロー）を示すビットが2ビット含まれています。

あまりに大量のデータがFIFOに書き込まれると、FIFOオーバーフローがセットされます。受信中にこのビットがセットされた場合は、ウォーター・レベルIRQに対して外部マイクロコントローラが時間通りに対応しておらず、96バイトを超えるデータがFIFOに書き込まれています。このような場合には、当然、受信データは破壊されています。送信時であれば、FIFOサイズを超えてコントローラがデータを書き込んでいることを意味します。送信されるデータは破壊されています。

空のFIFOからデータが読み込まれると、FIFOアンダーフローがセットされます。受信中にこのビットがセットされた場合は、実際に受信したデータ以上のデータを外部マイクロコントローラが読み込んでいます。送信時であれば、送信バイト数レジスタに設定されているだけのデータ量を、コントローラが時間通りに供給できなかったことを意味しています。

### MCU\_CLKピン

MCU\_CLKピンは、外部マイクロコントローラのクロック源として使用しても構いません。動作モードに応じて、RC発振器からの低周波数クロック（32 kHz）と、水晶発振器から派生したクロック信号とのいずれかが、MCU\_CLKピンから供給されます。

MCU\_CLK出力ピンは、[IOコンフィギュレーション・レジスタ1](#)のout\_c1ビットとout\_c0ビットとlf\_clk\_offビットによって制御されます。out\_c1の2ビットによって、MCU\_CLKピンをクロック源として使用できるようになります。水晶発振器（13.56 MHz、6.78 MHz、3.39 MHzに対応）が動作している場合の分周比が設定されます。lf\_clk\_offビットによって、水晶発振器が動作していない場合の低周波数クロック（32 kHz）の使用が制御されます。デフォルト設定（起動時に設定）では、3.39 MHzクロックが選択され、低周波数クロックが有効となっています。

トランスペアレント・モード（[セクション 1.2.22: ストリーム・モードとトランスペアレント・モード](#)参照）では、外部コントローラで送受信フレーミングを実装するためには、フィールド・キャリア周波数に同期するクロックが必要であるため、必ずMCU\_CLKを使用する必要があります。内部フレーミングを使用するときにも、MCU\_CLKの使用をお薦めします。マイクロコントローラのクロック源としてMCU\_CLKを使用すると、リーダ・キャリア周波数に同期したノイズが生成されるため、レシーバによってフィルタで除去されますが、それ以外のコヒーレントではないクロック源を使用すると、受信を妨害するノイズが生成されることがあります。

MCU\_CLKの使用は、EMC適合のためにも優れています。

### 1.2.13 ダイレクト・コマンド

表 9. ダイレクト・コマンド

| コマンド・コード<br>(16進) | コマンド                           | コメント                             | コマンド連鎖 | 終了後の割込み | 動作モード<br>(1) |

|-------------------|--------------------------------|----------------------------------|--------|---------|--------------|

| C1                | Set Default                    | ST25R3911Bをデフォルト状態（起動後と同じ）に設定    | N      | N       | すべて          |

| C2、C3             | Clear                          | すべての動作を停止し、FIFOをクリア              | Y      | N       | en           |

| C4                | Transmit With CRC              | 自動CRC生成を使用して送信シーケンスを開始           | Y      | N       | en, tx_en    |

| C5                | Transmit With CRC              | 自動CRC生成を使用せずに送信シーケンスを開始          | Y      | N       | en, tx_en    |

| C6                | Transmit REQA                  | REQAコマンドを送信（ISO14443Aモードのみ）      | Y      | N       | en, tx_en    |

| C7                | Transmit WUPA                  | WUPAコマンドを送信（ISO14443Aモードのみ）      | Y      | N       | en, tx_en    |

| C8                | NFC Initial Field ON           | 初期RFコリジョン防止を実行し、フィールドをオン         | Y      | Y       | en(2)        |

| C9                | NFC Response Field ON          | 応答RFコリジョン防止を実行し、フィールドをオン         | Y      | Y       | en (2)       |

| CA                | NFC Response Field ON with n=0 | n=0で応答RFコリジョン防止を実行し、フィールドをオン     | Y      | Y       | en (2)       |

| CB                | Go to Normal NFC Mode          | NFCIP-1アクティブ通信ビット・レート検出モードにて受け付け | Y      | N       | -            |

表 9. ダイレクト・コマンド (続き)

| コマンド・コード<br>(16進) | コマンド                        | コメント                                                     | コマンド連鎖 | 終了後の割込み | 動作モード<br>(1) |

|-------------------|-----------------------------|----------------------------------------------------------|--------|---------|--------------|

| CC                | Analog Preset               | モード設定レジスタとビット・レート設定レジスタの状態に基づいてRxとTxの設定をプリセット            | Y      | N       | すべて          |

| D0                | Mask Receive Data           | このコマンドが無視された後に受信                                         | Y      | N       | en, rx_en    |

| D1                | Unmask Receive Data         | このコマンドが正常処理された後にデータを受信 (このコマンドは内部マスク受信タイマよりも優先)          | Y      | N       | en, rx_en    |

| D2                | -                           | 未使用                                                      | -      | -       | -            |

| D3                | Measure Amplitude           | RFI入力に現れている信号の振幅を測定し、結果をA/Dコンバータ出力レジスタに格納                | N      | Y       | en           |

| D4                | Squelch                     | 現在のノイズ・レベルに応じてゲインを減少                                     | N      | N       | en, rx_en    |

| D5                | Reset Rx Gain               | 現在のスケルチ設定をクリアし、手動ゲイン減少量をレシーバ・コンフィギュレーション・レジスタ1からロード      | N      | N       | en           |

| D6                | Adjust Regulators           | 現在の電源電圧レベルに応じて電源レギュレータを調整                                | N      | Y       | en(3)        |

| D7                | Calibrate Modulation Depth  | Txをアクティブ化するシーケンスを開始して変調度を測定し、指定された変調度に適合するように変調度を調整      | N      | Y       | en           |

| D8                | Calibrate Antenna           | アンテナLCタンクが共振状態となるように、TRIMx,yピンに接続された並列コンデンサを調整するシーケンスを開始 | N      | Y       | en           |

| D9                | Measure Phase               | RFO信号とRFI信号の間の位相差を測定                                     | N      | Y       | en           |

| DA                | Clear RSSI                  | RSSIビットをクリアし、測定を再開                                       | Y      | N       | en           |

| DC                | Transparent Mode            | RFI入力に現れている信号の振幅を測定し、結果をA/Dコンバータ出力レジスタに格納                | N      | Y       | en           |

| DD                | Calibrate Capacitive Sensor | 静電容量センサを補正                                               | N      | Y       | ノート参照(4)     |

| DE                | Measure Capacitance         | 静電容量センサ測定を実行                                             | N      | Y       | ノート参照(5)     |

| DF                | Measure Power Supply        | -                                                        | N      | Y       | en           |

| E0                | Start General Purpose Timer | -                                                        | Y      | N       | en           |

| E1                | Start Wake-Up Timer         | -                                                        | Y      | N       | wu以外<br>すべて  |

表 9. ダイレクト・コマンド (続き)

| コマンド・コード (16進) | コマンド                     | コメント                | コマンド連鎖 | 終了後の割込み | 動作モード (1) |

|----------------|--------------------------|---------------------|--------|---------|-----------|

| E2             | Start Mask Receive Timer | -                   | Y      | N       | ノート参照 (6) |

| E3             | Start No-Response Timer  | -                   | Y      | N       | en, rx_en |

| FC             | Test Access              | レジスタのテストのためにWをイネーブル | Y      | N       | すべて       |

| 他のFx           | -                        | テスト用に予約             | -      | -       | -         |

| 他のコード          | -                        | 未使用                 | -      | -       | -         |

- 特定コマンドを受け入れるためにセットする必要のある[動作コントロール・レジスタ](#)の各ビットを設定します。

- このコマンドの終了後に、l\_catまたはl\_cac IRQが送信されます。

- [レギュレータ電圧コントロール・レジスタ](#)において安定化電圧の外部設定が選択されている場合 (reg\_s ビットがHighにセット) には、このコマンドは受け付けられません。

- [静電容量センサ・コントロール・レジスタ](#)のcs\_mcalビットが0にセットされると、すべてのモードで受け付けられます。パワーダウン・モードでこのコマンドを実行することを推奨します。

- すべてのモードで受け付けられます。パワーダウン・モードでこのコマンドを実行することを推奨します。

- 初期NFCターゲット通信モードでのみ受け付けられます。

### Set Default

このダイレクト・コマンドによって、ST25R3911Bは起動時の初期化状態と同じ状態となります。すべてのレジスタはデフォルト状態に初期化されます。唯一の例外は、起動時にのみデフォルト状態に設定される[IOコンフィギュレーション・レジスタ1](#)と[IOコンフィギュレーション・レジスタ2](#)と[動作コントロール・レジスタ](#) (Set Defaultによる影響を受けません) です。

注:

[各種の補正と調整コマンドの結果も失われます。](#)

このダイレクト・コマンドは、すべての動作モードで受け付けられます。en ([動作コントロール・レジスタ](#)のビット7) がセットされていないときにこのコマンドが送信された場合には、FIFOとFIFOステータス・レジスタはクリアされません。

このコマンドによってすべてのレジスタがクリアされるため、ダイレクト・コマンドの連鎖はできません。

ダイレクト・コマンドの終了によるIRQは生成されません。

### Clear

このダイレクト・コマンドによって、すべての現在の動作 (送受信) が停止し、FIFOがクリアされ、FIFOステータス・レジスタがクリアされ、ウェイクアップ・タイマ以外のすべてのタイマが停止します ([汎用/応答なしタイマ・コントロール・レジスタ](#)のnrt\_envビットが1にセットされている場合、応答なしタイマは停止しません)。

コリジョン・レジスタと割込みレジスタもクリアされます。このコマンドは、送信するデータをFIFOに書き込む前に、送信の準備を行うシーケンスの先頭で送信される必要があります (ダイレクト・コマンドTransmit REQとTransmit WUPAの場合を除きます)。

en ([動作コントロール・レジスタ](#)のビット7) がセットされていて、水晶発振器の周波数が安定している場合に、このコマンドは受け付けられます。

ダイレクト・コマンドの連鎖は可能です。

ダイレクト・コマンドの終了によるIRQは生成されません。

### Transmitコマンド群

すべてのTransmitコマンド（Transmit With CRC、Transmit Without CRC、Transmit REQA、Transmit WUPA）は、トランスマッタが有効化されている（tx\_enビットがセットされている）場合のみ受け付けられます。

Transmit With CRCコマンドとTransmit Without CRCコマンドの送信前には、ダイレクト・コマンドClearを送信してから送信されるバイト数を設定して、送信データをFIFOに書き込む必要があります。

ダイレクト・コマンドのTransmit REQAとTransmit WUPAは、ISO14443AコマンドのREQAとWUPAを送信するためにそれぞれ用いられます。これら2つのコマンドの前にClearコマンドを送信する必要はありません。

Transmit REQAまたはTransmit WUPAの実行前には、最終バイトの中の有効ビット数（[送信バイト数レジスタ2](#)のnbt<sub>x</sub><2:0>）をゼロにセットしなければなりません。

ダイレクト・コマンドの連鎖は可能です。

ダイレクト・コマンドの終了によるIRQは生成されません。

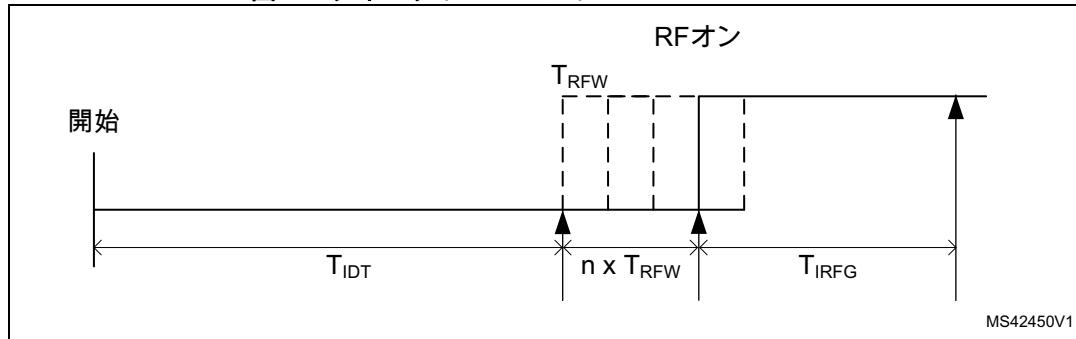

### NFC Field ONコマンド群

これらのコマンドは、RFコリジョン防止を実行して、コリジョンが検出されなかった場合にフィールドをオンにするために用いられます。[外部フィールド検出器閾値レジスタ](#)に設定されているコリジョン防止閾値が、RF\_IN入力の観測と、ST25R3911Bのアンテナに近接して、13.56 MHzフィールドを放射しているデバイスが他に存在するかどうかの判断に用いられます。コリジョンが検出されない場合には、リーダ・フィールドが自動的にオン（[動作コントロール・レジスタ](#)のtx\_enビットをセット）となり、NFCIP-1規格で定義された最小ガード時間の後に[タイマ/NFC割込みレジスタ](#)のl\_catフラグ付きでIRQが送信されて、Transmitコマンドを用いたメッセージ送信を開始可能であることをコントローラに通知します。

外部フィールドの存在が検出された場合には、l\_cacフラグ付きのIRQが送信されます。送信が行えない場合には、コリジョンが検出されなくなるまで、NFC Field ONコマンドを繰り返す必要があります。NFC Initial Field ONコマンドによって、NFCIP-1規格に則った初期コリジョン防止が実行されます。ここで、nの値は、[補助設定レジスタ](#)のnfc\_n1ビットとnfc\_n0ビットによって設定されます。

NFC Response Field ONコマンドによって、NFCIP-1規格に則った応答コリジョン防止が実行されます。ここでnの値は、[補助設定レジスタ](#)のnfc\_n1ビットとnfc\_n0ビットによって設定されます。

NFC Response Field ON with n=0コマンドによって、nを0とした応答コリジョン防止が実行されます。

実際のアクティブ遅延時間には、フィールドの非アクティブ化の検出、コントローラの処理遅延、NFC Field ONの送信の時間も含まれることから、実装されているアクティブ遅延時間は、NFCIP-1規格の下限値となります。

en（[動作コントロール・レジスタ](#)のビット7）がセットされていて、水晶発振器の周波数と振幅が両方とも安定している場合に、このコマンドは受け付けられます。

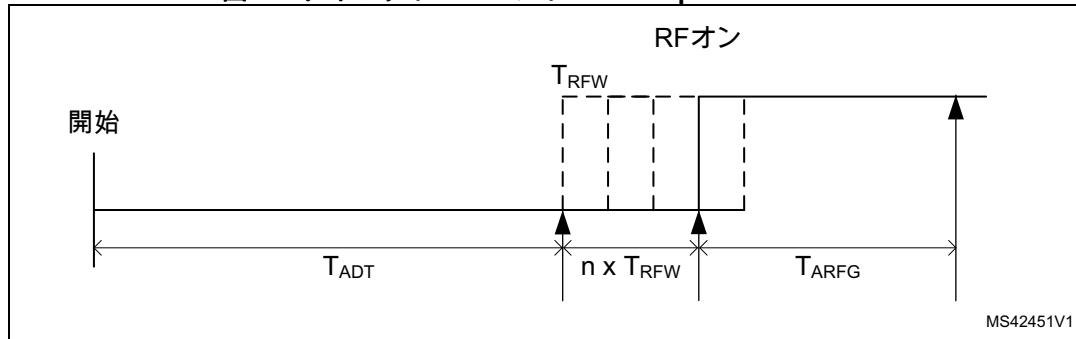

図 19. ダイレクト・コマンドNFC Initial Field ON

図 20. ダイレクト・コマンドNFC Response Field ON

表 10. NFC Field ONコマンド群のタイミング・パラメータ

| 記号         | パラメータ      | 値    | 単位  | コメント                  |

|------------|------------|------|-----|-----------------------|

| $T_{IDT}$  | 初期遅延時間     | 4096 | /fc | NFC Initial Field ON  |

| $T_{RWF}$  | Rx待ち時間     | 512  |     | -                     |

| $T_{IRFG}$ | 初期ガード時間    | >5   | ms  | NFC Initial Field ON  |

| $T_{ADT}$  | アクティブ遅延時間  | 768  | /fc | NFC Response Field ON |

| $T_{ARFG}$ | アクティブガード時間 | 1024 |     |                       |

### Go to Normal NFC Mode

このコマンドは、NFCターゲット・ビット・レート検出モードから通常モードに移行するために用いられます。さらに、[NFCIPビット・レート検出表示レジスタ](#)の内容が[ビット・レート設定レジスタ](#)にコピーされ、[補助設定レジスタ](#)のtr\_amビットが正しくセットされます。

### Analog Preset

このコマンドは、[モード設定レジスタ](#)と[ビット・レート設定レジスタ](#)の状態に基づいてレシーバとトランスマッタの設定をプリセットするために用いられます。サブキャリア・ビット・ストリーム・モードかBPSKビット・ストリーム・モードの場合には、このコマンドは使用しないでください。プリセットされるコンフィギュレーション・ビットのリストを[表 11](#)に示します。

表 11. レジスタ・プリセット・ビット

| ビット                                                                                                                                         | ビット<br>名称 | 機能                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| アドレス02h: <a href="#">表 20: 動作コントロール・レジスタ</a>                                                                                                |           |                                                                                                                                                                          |

| 5                                                                                                                                           | rx_chn    | <b>1:</b> 1チャネル有効化 → NFCIP-1アクティブ通信（イニシエータ、ターゲットとも）                                                                                                                      |

| 3                                                                                                                                           | tx_en     | <b>0:</b> TX動作無効化 → NFCIP-1アクティブ通信（イニシエータ、ターゲットとも）                                                                                                                       |

| 注: いずれかのターゲット・モードやNFCIP-1イニシエータ・モードでは、トランスマッタが有効化されていた場合、 <b>tx_en</b> ビットを0がセットされて無効化します。NFCIP-1モードでは、トランスマッタ・フィールドをオンにするのは、専用コマンドで制御されます。 |           |                                                                                                                                                                          |

| アドレス05h: <a href="#">表 26: ISO14443A / NFC 106kb/s設定レジスタ</a>                                                                                |           |                                                                                                                                                                          |

| 5                                                                                                                                           | nfc_f0    | <b>1:</b> Txの間にSB (F0) バイトとLENバイトを追加し、TXの間にSB (F0) バイトをスキップします。→ NFCIP-1アクティブ通信（イニシエータ、ターゲットとも）                                                                          |

| アドレス09h: <a href="#">表 34: 補助設定レジスタ</a>                                                                                                     |           |                                                                                                                                                                          |

| 5                                                                                                                                           | tr_am     | Tx変調種別（モード設定とTxビット・レートに依存）<br><b>0:</b> OOK → ISO144443A、NFCIP-1 106 kb/s（イニシエータ、ターゲットとも）、NFCフォーラム・タイプ1タグ<br><b>1:</b> AM → ISO144443B、FeliCa™、NFCIP-1 212 kb/sと424 kb/s |

| 4                                                                                                                                           | en_fd     | ピア検出閾値で外部フィールド検出器が有効化<br><b>0:</b> NFCIP-1アクティブ通信以外の全モード<br><b>1:</b> NFCIP-1アクティブ通信（イニシエータ、ターゲットとも）                                                                     |

| アドレス0Ah: <a href="#">表 35: レシーバ・コンフィギュレーション・レジスタ1</a>                                                                                       |           |                                                                                                                                                                          |

| 7                                                                                                                                           | ch_sel    | <b>0:</b> AMチャネル有効化 → NFCIP-1アクティブ通信（イニシエータ、ターゲットとも）                                                                                                                     |

| 6                                                                                                                                           | amd_sel   | AM復調器選択（Rxビット・レートに依存）<br><b>0:</b> ピーク検出器 → fc/16 (848 kb/s) 以下の全Rxビット・レート<br><b>1:</b> ミキサ → 全VHBR Rxビット・レート (fc/8とfc/4)                                                |

| 5                                                                                                                                           | lp2       | ローパス制御（モード設定とRxビット・レートに依存）、 <a href="#">表 3: レシーバのフィルタ選択とゲイン範囲</a> 参照                                                                                                    |

| 4                                                                                                                                           | lp1       |                                                                                                                                                                          |

| 3                                                                                                                                           | lp0       |                                                                                                                                                                          |

| 2                                                                                                                                           | h200      | 第1/第3ステージゼロ点設定（モード設定とRxビット・レートに依存）、 <a href="#">表 3: レシーバのフィルタ選択とゲイン範囲</a> 参照                                                                                            |

| 1                                                                                                                                           | h80       |                                                                                                                                                                          |

| 0                                                                                                                                           | z12k      |                                                                                                                                                                          |

| アドレス0Ch: <a href="#">表 37: レシーバ・コンフィギュレーション・レジスタ3</a>                                                                                       |           |                                                                                                                                                                          |

| 1                                                                                                                                           | lim       | 第1と第2ステージの出力をクリップ<br><b>0:</b> NFCIP-1アクティブ通信以外の全モード<br><b>1:</b> NFCIP-1アクティブ通信（イニシエータ、ターゲットとも）                                                                         |

| 0                                                                                                                                           | rg_nfc    | 第2と第3のゲインステージのゲインを強制的に減少<br><b>0:</b> NFCIP-1アクティブ通信以外の全モード<br><b>1:</b> NFCIP-1アクティブ通信（イニシエータ、ターゲットとも）                                                                  |

## Mask Receive DataとUnmask Receive Data