## 高性能NFCユニバーサルデバイス & EMVCoリーダ

データシート - 量産品データ

### 機能

- 動作モード

- リーダライタ

- カード・エミュレーション

- アクティブP2PおよびパッシブP2P

- RF通信

- EMVCo™ 3.0アナログおよびデジタル規格準拠

- NFC-A / ISO14443A (最大848kbit/s)

- NFC-B / ISO14443B (最大848kbit/s)

- NFC-F / FeliCa™ (最大424kbit/s)

- NFC-V / ISO15693 (最大53kbit/s)

- NFC-A / ISO14443AおよびNFC-F / FeliCa™のカード・エミュレーション

- アクティブP2PおよびパッシブP2Pのイニシエータ・モードおよびターゲット・モード (最大424kbit/s)

- MIFARE Classic®準拠プロトコルまたは他のカスタム・プロトコルを実装するための低レベル・モード

- 主な機能

- 電界強度が一定の制限範囲に収まるように制御するダイナミック・パワー出力 (DPO)

- オーバーシュートやアンダーシュートを低減するアクティブ波形補正 (AWS)

- ノイズが多い環境における受信を可能にするノイズ抑制レシーバ (NSR)

- 可変容量コンデンサによる自動アンテナ・チューニング (AAT)

- EMVCo3.0準拠のEMD処理回路を組み込み

- 最大限の信号対ノイズ比を実現する自動ゲイン制御およびスケルチ機能

- 低消費電力で動作する静電容量方式および電磁誘導方式のカード検出

- 低消費電力で動作するアクティブおよびパッシブのNFCターゲット・モード

- ASKの変調度を5% ~ 40%の範囲で調整可能

- システムのPSRR向上に効果的なレギュレータを組み込み

- ベースバンド・チャネルの総和復調機能または自動チャネル選択機能を備え、AM、PM、I/Qに対応した復調回路

- 2つの独立したシングルエンド・アンテナを駆動可能

- アンテナ電圧の振幅と位相、RSSI、オンチップ電源電圧、レギュレータ電圧の測定機能

- 外部通信インタフェース

- 512バイトFIFO

- 最大 10Mbit/s のシリアル・ペリフェラル・インターフェース (SPI)

- I<sup>2</sup>Cインターフェース (ファーストモード: 最大400Kbit/s、ファーストモードプラス: 最大1Mbit/s、ハイスピード・モード: 最大3.4Mbit/s)

- 電気的特性

- 2.4V ~ 5.5Vの広い動作電源電圧範囲

- 1.65V ~ 5.5Vの広いペリフェラル通信用電源電圧範囲

- 27.12MHz の水晶振動子で動作可能な水晶発振器により、高速な起動を実現

## 目次

|        |                           |    |

|--------|---------------------------|----|

| 1      | アプリケーション .....            | 11 |

| 2      | 概要 .....                  | 12 |

| 2.1    | システム図 .....               | 13 |

| 2.2    | ブロック図 .....               | 15 |

| 2.2.1  | トランスマッタ .....             | 15 |

| 2.2.2  | レシーバ .....                | 16 |

| 2.2.3  | 位相検出器と振幅検出器 .....         | 16 |

| 2.2.4  | 自動アンテナ・チューニング (AAT) ..... | 16 |

| 2.2.5  | A/D コンバータ .....           | 16 |

| 2.2.6  | 静電容量センサ .....             | 16 |

| 2.2.7  | 外部フィールド検出器 .....          | 17 |

| 2.2.8  | 水晶発振器 .....               | 17 |

| 2.2.9  | 電源レギュレータ .....            | 17 |

| 2.2.10 | POR とバイアス .....           | 17 |

| 2.2.11 | RC 発振器とウェイクアップ・タイマ .....  | 17 |

| 2.2.12 | 送信エンコード .....             | 18 |

| 2.2.13 | 受信デコード .....              | 18 |

| 2.2.14 | FIFO .....                | 18 |

| 2.2.15 | コントロール・ロジック .....         | 18 |

| 2.2.16 | ホスト・インターフェース .....        | 18 |

| 2.2.17 | パッシブ・ターゲット・メモリ .....      | 18 |

| 2.2.18 | P2RAM .....               | 18 |

| 3      | ピンおよび信号の説明 .....          | 19 |

| 4      | アプリケーション情報 .....          | 23 |

| 4.1    | 電源投入シーケンス .....           | 23 |

| 4.2    | 動作モード .....               | 23 |

| 4.2.1  | トランスマッタ .....             | 24 |

| 4.2.2  | レシーバ .....                | 26 |

| 4.2.3  | アンテナ・チューニング .....         | 31 |

| 4.2.4  | 静電容量センサ .....             | 31 |

| 4.2.5  | ウェイクアップ・モード .....         | 33 |

|        |                                                                   |    |

|--------|-------------------------------------------------------------------|----|

| 4.2.6  | 水晶発振器                                                             | 34 |

| 4.2.7  | タイマ                                                               | 34 |

| 4.2.8  | A/D コンバータ                                                         | 37 |

| 4.2.9  | 位相検出器と振幅検出器                                                       | 37 |

| 4.2.10 | 外部フィールド検出器                                                        | 38 |

| 4.2.11 | 電源系                                                               | 39 |

| 4.2.12 | オーバーシュート / アンダーシュート保護                                             | 42 |

| 4.2.13 | リーダ動作                                                             | 42 |

| 4.2.14 | リッスン・モード                                                          | 43 |

| 4.3    | 外部マイクロコントローラとの通信                                                  | 46 |

| 4.3.1  | 割り込みのインターフェース                                                     | 46 |

| 4.3.2  | 通信インターフェースの選択                                                     | 47 |

| 4.3.3  | シリアル・ペリフェラル・インターフェース (SPI)                                        | 48 |

| 4.3.4  | I <sup>2</sup> C インタフェース                                          | 53 |

| 4.4    | ダイレクト・コマンド                                                        | 58 |

| 4.4.1  | Set Default (デフォルト設定)                                             | 59 |

| 4.4.2  | Stop All Activities (全動作停止)                                       | 59 |

| 4.4.3  | Clear FIFO (FIFO のクリア)                                            | 60 |

| 4.4.4  | Transmit (送信) コマンド群                                               | 60 |

| 4.4.5  | NFC Field ON (NFC フィールド・オン) コマンド群                                 | 61 |

| 4.4.6  | Mask Receive Data (データ受信のマスク) と Unmask Receive Data (データ受信のマスク解除) | 62 |

| 4.4.7  | Change AM Modulation state (AM 変調状態変更)                            | 62 |

| 4.4.8  | Measure Amplitude (振幅測定)                                          | 63 |

| 4.4.9  | Reset RX Gain (受信ゲイン・リセット)                                        | 63 |

| 4.4.10 | Adjust Regulators (レギュレータ調整)                                      | 63 |

| 4.4.11 | Measure Phase (位相測定)                                              | 63 |

| 4.4.12 | Clear RSSI (RSSI クリア)                                             | 64 |

| 4.4.13 | Transparent Mode (トランスペアレント・モード)                                  | 64 |

| 4.4.14 | Calibrate Capacitive Sensor (静電容量センサ補正)                           | 64 |

| 4.4.15 | Measure Capacitance (静電容量測定)                                      | 64 |

| 4.4.16 | Measure Power Supply (電源測定)                                       | 64 |

| 4.4.17 | Test Access (テスト・アクセス)                                            | 65 |

| 4.5    | レジスタ                                                              | 66 |

| 4.5.1  | IO コンフィギュレーション・レジスタ 1                                             | 69 |

| 4.5.2  | IO コンフィギュレーション・レジスタ 2                                             | 70 |

| 4.5.3  | 動作コントロール・レジスタ                                                     | 71 |

# 参考資料

## 目次

ST25R3916/7

|        |                                        |     |

|--------|----------------------------------------|-----|

| 4.5.4  | モード設定レジスタ .....                        | 72  |

| 4.5.5  | ビット・レート設定レジスタ .....                    | 73  |

| 4.5.6  | ISO14443A および NFC 106kb/s 設定レジスタ ..... | 74  |

| 4.5.7  | ISO14443B 設定レジスタ 1 .....               | 75  |

| 4.5.8  | ISO14443B および FeliCa 設定レジスタ .....      | 76  |

| 4.5.9  | NFCIP-1 パッシブ・ターゲット設定レジスタ .....         | 77  |

| 4.5.10 | ストリーム・モード設定レジスタ .....                  | 78  |

| 4.5.11 | 補助設定レジスタ .....                         | 79  |

| 4.5.12 | EMD 抑制コンフィギュレーション・レジスタ .....           | 80  |

| 4.5.13 | サブキャリア開始タイマ・レジスタ .....                 | 81  |

| 4.5.14 | レシーバ・コンフィギュレーション・レジスタ 1 .....          | 82  |

| 4.5.15 | レシーバ・コンフィギュレーション・レジスタ 2 .....          | 83  |

| 4.5.16 | レシーバ・コンフィギュレーション・レジスタ 3 .....          | 84  |

| 4.5.17 | レシーバ・コンフィギュレーション・レジスタ 4 .....          | 84  |

| 4.5.18 | P2P レシーバ・コンフィギュレーション・レジスタ 1 .....      | 85  |

| 4.5.19 | コリレータ・コンフィギュレーション・レジスタ 1 .....         | 86  |

| 4.5.20 | コリレータ・コンフィギュレーション・レジスタ 2 .....         | 87  |

| 4.5.21 | マスク受信タイマ・レジスタ .....                    | 88  |

| 4.5.22 | 応答なしタイマ・レジスタ 1 .....                   | 89  |

| 4.5.23 | 応答なしタイマ・レジスタ 2 .....                   | 89  |

| 4.5.24 | タイマ /EMV コントロール・レジスタ .....             | 90  |

| 4.5.25 | 汎用タイマ・レジスタ 1 .....                     | 91  |

| 4.5.26 | 汎用タイマ・レジスタ 2 .....                     | 91  |

| 4.5.27 | PPON2 フィールド待機レジスタ .....                | 92  |

| 4.5.28 | スケルチ・タイマ・レジスタ .....                    | 93  |

| 4.5.29 | NFC フィールド・オン・ガード・タイマ・レジスタ .....        | 93  |

| 4.5.30 | メイン割り込みマスク・レジスタ .....                  | 94  |

| 4.5.31 | タイマ /NFC 割り込みマスク・レジスタ .....            | 94  |

| 4.5.32 | エラー / ウェイクアップ割り込みマスク・レジスタ .....        | 95  |

| 4.5.33 | パッシブ・ターゲット割り込みマスク・レジスタ .....           | 95  |

| 4.5.34 | メイン割り込みレジスタ .....                      | 96  |

| 4.5.35 | タイマ /NFC 割り込みレジスタ .....                | 97  |

| 4.5.36 | エラー / ウェイクアップ割り込みレジスタ .....            | 98  |

| 4.5.37 | パッシブ・ターゲット割り込みレジスタ .....               | 99  |

| 4.5.38 | FIFO ステータス・レジスタ 1 .....                | 100 |

| 4.5.39 | FIFO ステータス・レジスタ 2 .....                | 100 |

| 4.5.40 | コリジョン表示レジスタ .....                      | 101 |

# 参考資料

|        |                                    |     |

|--------|------------------------------------|-----|

| 4.5.41 | パッシブ・ターゲット表示レジスタ .....             | 102 |

| 4.5.42 | 送信バイト数レジスタ 1 .....                 | 103 |

| 4.5.43 | 送信バイト数レジスタ 2 .....                 | 103 |

| 4.5.44 | ビット・レート検出表示レジスタ .....              | 104 |

| 4.5.45 | A/D コンバータ出力レジスタ .....              | 105 |

| 4.5.46 | アンテナ・チューニング・コントロール・レジスタ 1 .....    | 106 |

| 4.5.47 | アンテナ・チューニング・コントロール・レジスタ 2 .....    | 106 |

| 4.5.48 | 送信ドライバ・レジスタ .....                  | 107 |

| 4.5.49 | 補助変調設定レジスタ .....                   | 109 |

| 4.5.50 | パッシブ・ターゲット変調レジスタ .....             | 110 |

| 4.5.51 | 送信ドライバ・タイミング・レジスタ .....            | 111 |

| 4.5.52 | 外部フィールド検出器アクティブ化閾値レジスタ .....       | 112 |

| 4.5.53 | 抵抗性 AM 変調レジスタ .....                | 113 |

| 4.5.54 | 外部フィールド検出器非アクティブ化閾値レジスタ .....      | 114 |

| 4.5.55 | 送信ドライバ・タイミング表示レジスタ .....           | 116 |

| 4.5.56 | レギュレータ電圧コントロール・レジスタ .....          | 117 |

| 4.5.57 | レギュレータ表示レジスタ .....                 | 118 |

| 4.5.58 | RSSI 表示レジスタ .....                  | 119 |

| 4.5.59 | ゲイン低減状態レジスタ .....                  | 120 |

| 4.5.60 | 静電容量センサ・コントロール・レジスタ .....          | 121 |

| 4.5.61 | 静電容量センサ表示レジスタ .....                | 121 |

| 4.5.62 | 補助表示レジスタ .....                     | 122 |

| 4.5.63 | オーバーシュート保護コンフィギュレーション・レジスタ 1 ..... | 123 |

| 4.5.64 | オーバーシュート保護コンフィギュレーション・レジスタ 2 ..... | 123 |

| 4.5.65 | アンダーシュート保護コンフィギュレーション・レジスタ 1 ..... | 124 |

| 4.5.66 | アンダーシュート保護コンフィギュレーション・レジスタ 2 ..... | 124 |

| 4.5.67 | ウェイクアップ・タイマ・コントロール・レジスタ .....      | 125 |

| 4.5.68 | 振幅測定コンフィギュレーション・レジスタ .....         | 126 |

| 4.5.69 | 振幅測定基準レジスタ .....                   | 126 |

| 4.5.70 | 振幅測定自動平均化表示レジスタ .....              | 127 |

| 4.5.71 | 振幅測定表示レジスタ .....                   | 127 |

| 4.5.72 | 位相測定コンフィギュレーション・レジスタ .....         | 128 |

| 4.5.73 | 位相測定基準レジスタ .....                   | 128 |

| 4.5.74 | 位相測定自動平均化表示レジスタ .....              | 129 |

| 4.5.75 | 位相測定表示レジスタ .....                   | 129 |

| 4.5.76 | 静電容量測定コンフィギュレーション・レジスタ .....       | 130 |

| 4.5.77 | 静電容量測定基準レジスタ .....                 | 130 |

# 参考資料

## 目次

ST25R3916/7

|          |                             |            |

|----------|-----------------------------|------------|

| 4.5.78   | 静電容量測定自動平均化表示レジスタ           | 131        |

| 4.5.79   | 静電容量測定表示レジスタ                | 131        |

| 4.5.80   | IC 識別レジスタ                   | 132        |

| <b>5</b> | <b>電気的特性</b>                | <b>133</b> |

| 5.1      | 絶対最大定格                      | 133        |

| 5.2      | 動作条件                        | 134        |

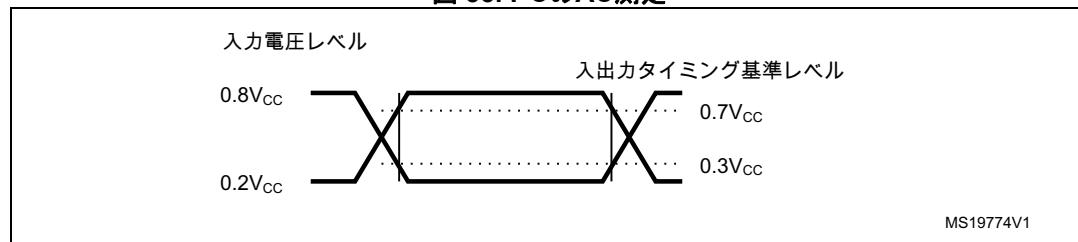

| 5.3      | デジタル入出力の DC/AC 特性           | 135        |

| 5.4      | 電気的特性                       | 136        |

| 5.5      | SPI インタフェースの特性              | 139        |

| 5.6      | I <sup>2</sup> C インタフェースの特性 | 141        |

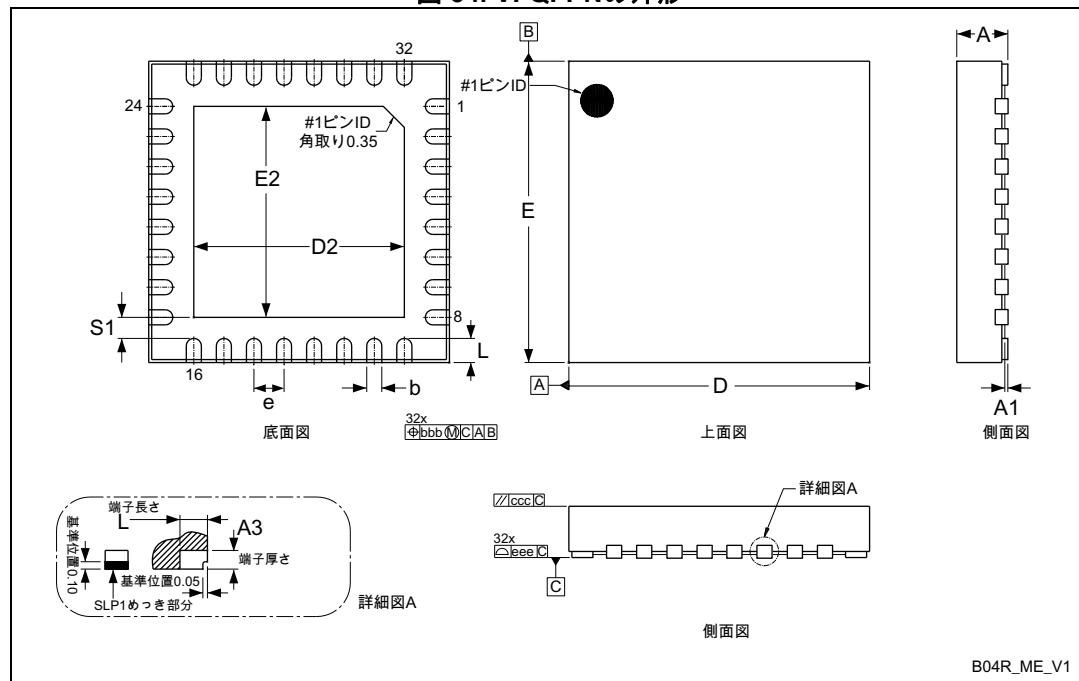

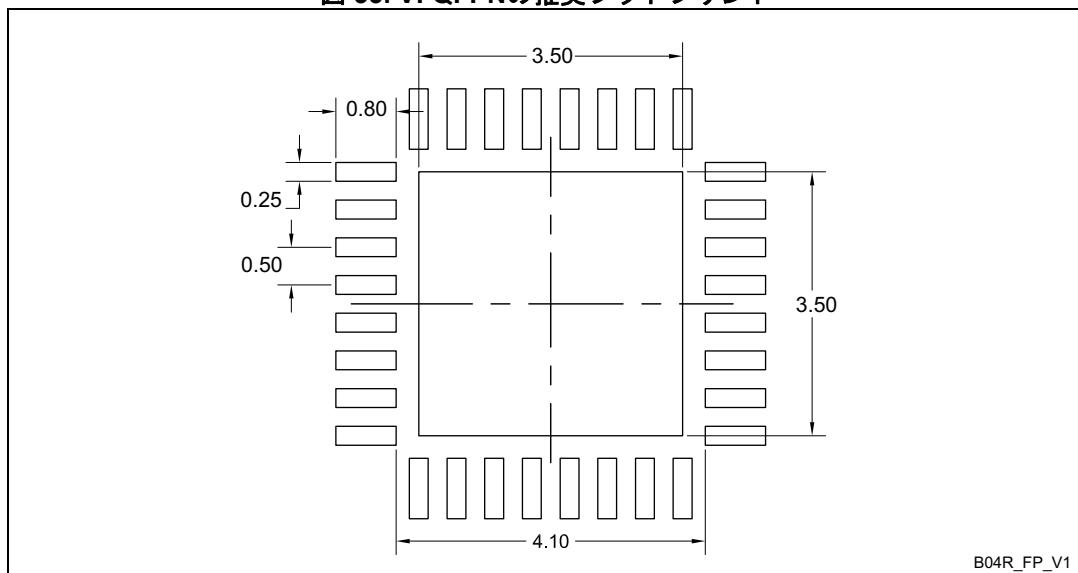

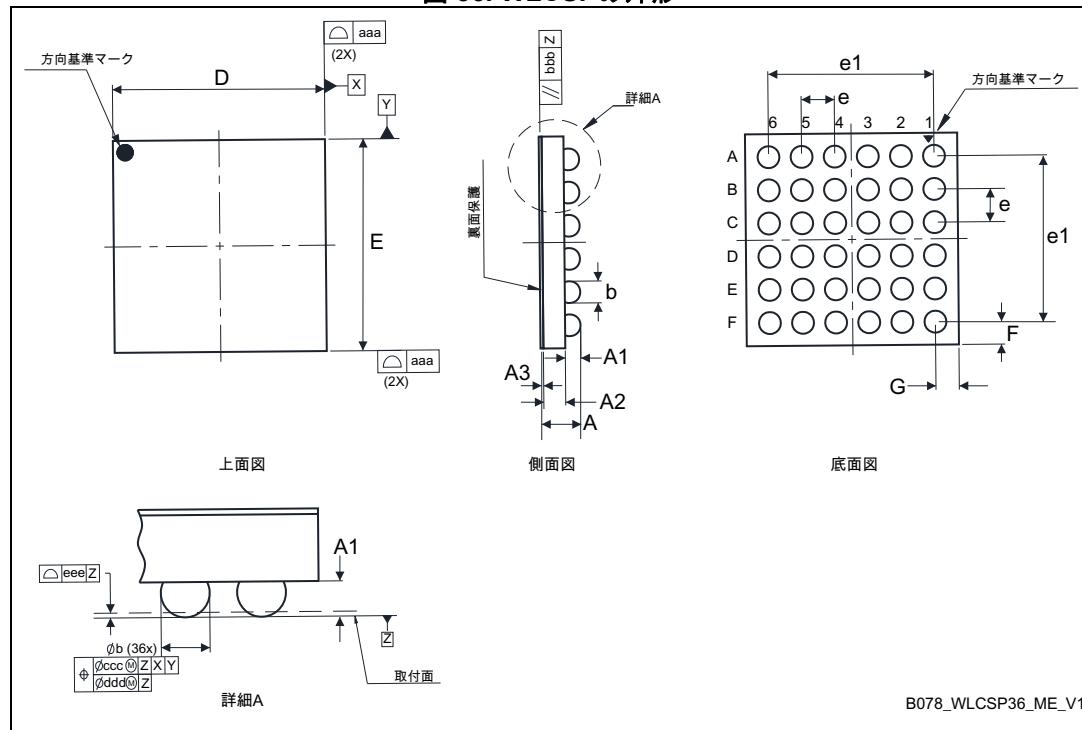

| <b>6</b> | <b>パッケージ情報</b>              | <b>145</b> |

| 6.1      | VFQFPN-32 パッケージ情報           | 145        |

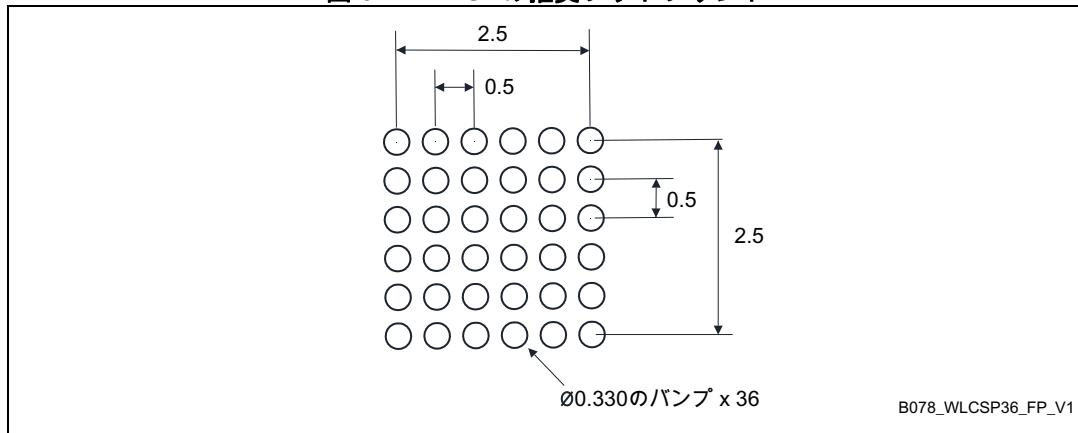

| 6.2      | WLCSP36 パッケージ情報             | 147        |

| <b>7</b> | <b>発注情報</b>                 | <b>149</b> |

| <b>8</b> | <b>改版履歴</b>                 | <b>150</b> |

## 表の一覧

|       |                                         |    |

|-------|-----------------------------------------|----|

| 表 1.  | 機能一覧                                    | 11 |

| 表 2.  | ST25R3916 - VFQFPN32 および WLCSP36 のピン割当て | 20 |

| 表 3.  | ST25R3917 - VFQFPN32 のピン割当て             | 21 |

| 表 4.  | 受信チャネルの選択                               | 26 |

| 表 5.  | ローパス制御                                  | 28 |

| 表 6.  | 初段と 3 段目のゼロ点設定                          | 28 |

| 表 7.  | PT_memory のアドレス空間                       | 45 |

| 表 8.  | NFC-212/424k SENS_RES フォーマット            | 45 |

| 表 9.  | IRQ 出力                                  | 46 |

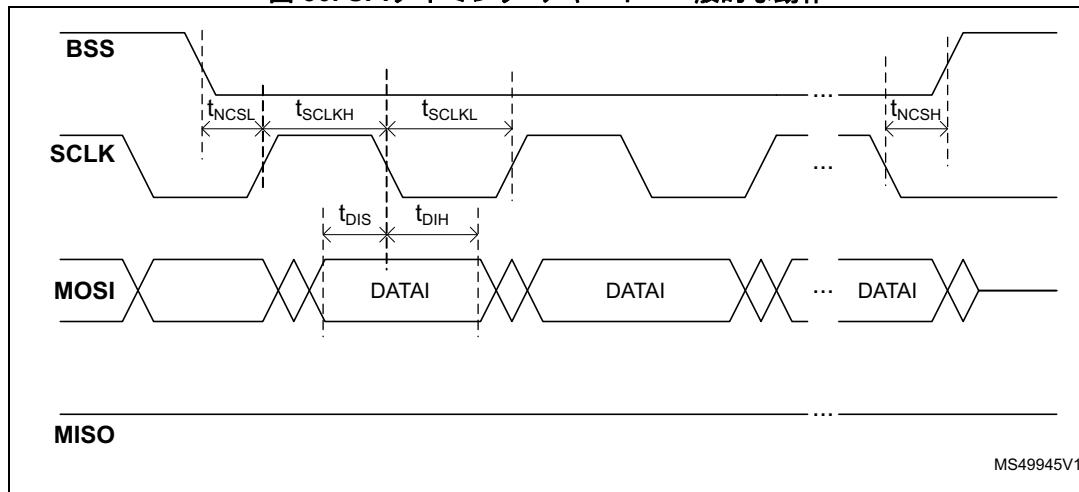

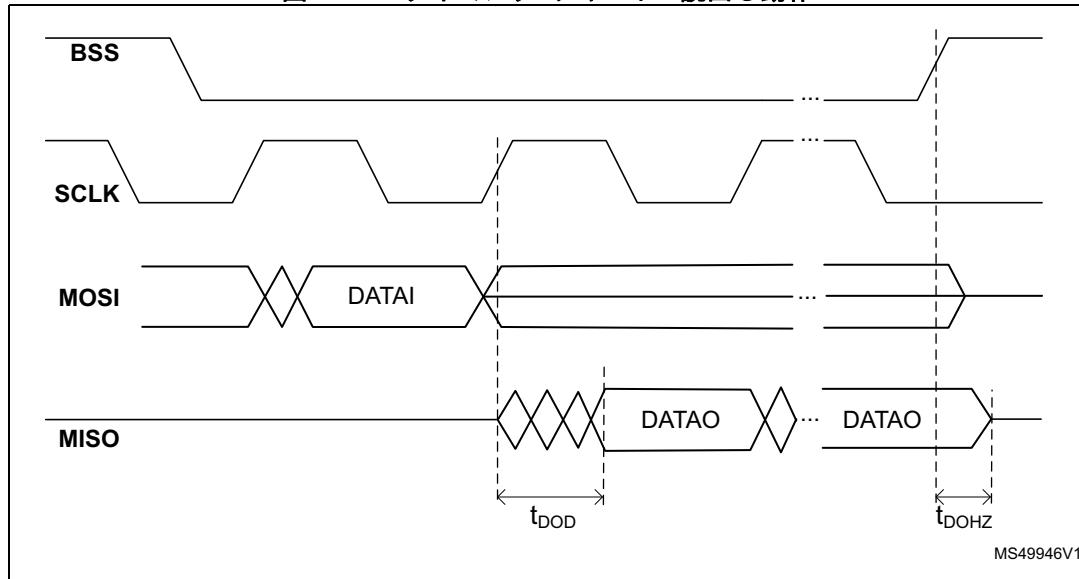

| 表 10. | シリアル・データ・インターフェース（4 線式インターフェース）の信号ライン   | 48 |

| 表 11. | SPI の動作モード                              | 49 |

| 表 12. | I <sup>2</sup> C インタフェースと割り込みの信号ライン     | 54 |

| 表 13. | ダイレクト・コマンド一覧                            | 58 |

| 表 14. | NFC Field ON コマンド群のタイミング・パラメータ          | 62 |

| 表 15. | アナログ・テストと観測レジスタ 1                       | 65 |

| 表 16. | テスト・アクセス・レジスタ - CSI ピンと CSO ピンの信号選択     | 65 |

| 表 17. | レジスター一覧 - 空間 A                          | 66 |

| 表 18. | レジスター一覧 - 空間 B                          | 68 |

| 表 19. | IO コンフィギュレーション・レジスタ 1                   | 69 |

| 表 20. | IO コンフィギュレーション・レジスタ 2                   | 70 |

| 表 21. | 動作コントロール・レジスタ                           | 71 |

| 表 22. | モード設定レジスタ                               | 72 |

| 表 23. | イニシエータ動作モード                             | 72 |

| 表 24. | ターゲット動作モード                              | 72 |

| 表 25. | ビット・レート設定レジスタ                           | 73 |

| 表 26. | ビット・レートのコード                             | 73 |

| 表 27. | ISO14443A および NFC 106kb/s 設定レジスタ        | 74 |

| 表 28. | ISO14443A 変調パルス幅                        | 74 |

| 表 29. | ISO14443B 設定レジスタ 1                      | 75 |

| 表 30. | ISO14443B および FeliCa 設定レジスタ             | 76 |

| 表 31. | 最小 TR1 のコード                             | 76 |

| 表 32. | NFCIP-1 パッシブ・ターゲット設定レジスタ                | 77 |

| 表 33. | ストリーム・モード設定レジスタ                         | 78 |

| 表 34. | サブキャリア・ストリーム・モードのサブキャリア周波数設定            | 78 |

| 表 35. | ストリーム・モードの送信変調器を制御する時間の設定               | 78 |

| 表 36. | 補助設定レジスタ                                | 79 |

| 表 37. | RW レシーバの動作                              | 79 |

| 表 38. | EMD 抑制コンフィギュレーション・レジスタ                  | 80 |

| 表 39. | サブキャリア開始タイマ・レジスタ                        | 81 |

| 表 40. | レシーバ・コンフィギュレーション・レジスタ 1                 | 82 |

| 表 41. | レシーバ・コンフィギュレーション・レジスタ 2                 | 83 |

| 表 42. | レシーバ・コンフィギュレーション・レジスタ 3                 | 84 |

| 表 43. | レシーバ・コンフィギュレーション・レジスタ 4                 | 84 |

| 表 44. | P2P レシーバ・コンフィギュレーション・レジスタ 1             | 85 |

| 表 45. | OOK の閾値レベル設定                            | 85 |

| 表 46. | コリレータ・コンフィギュレーション・レジスタ 1                | 86 |

| 表 47. | 相関器コンフィギュレーション・レジスタ 2                   | 87 |

| 表 48. | マスク受信タイマ・レジスタ                           | 88 |

| 表 49. | 応答なしタイマ・レジスタ 1                          | 89 |

# 参考資料

## 表の一覧

ST25R3916/7

|        |                                              |     |

|--------|----------------------------------------------|-----|

| 表 50.  | 応答なしタイマ・レジスタ 2.....                          | 89  |

| 表 51.  | タイマ /EMV コントロール・レジスタ .....                   | 90  |

| 表 52.  | トリガ源 .....                                   | 90  |

| 表 53.  | 汎用タイマ・レジスタ 1 .....                           | 91  |

| 表 54.  | 汎用タイマ・レジスタ 2 .....                           | 91  |

| 表 55.  | PPON2 フィールド待機レジスタ .....                      | 92  |

| 表 56.  | スケルチ・タイマ・レジスタ .....                          | 93  |

| 表 57.  | NFC フィールド・オン・ガード・タイマ・レジスタ .....              | 93  |

| 表 58.  | メイン割り込みマスク・レジスタ .....                        | 94  |

| 表 59.  | タイマ /NFC 割り込みマスク・レジスタ .....                  | 94  |

| 表 60.  | エラー / ウェイクアップ割り込みマスク・レジスタ .....              | 95  |

| 表 61.  | パッシブ・ターゲット割り込みマスク・レジスタ .....                 | 95  |

| 表 62.  | メイン割り込みレジスタ .....                            | 96  |

| 表 63.  | タイマ /NFC 割り込みレジスタ .....                      | 97  |

| 表 64.  | エラー / ウェイクアップ割り込みレジスタ .....                  | 98  |

| 表 65.  | パッシブ・ターゲット割り込みレジスタ .....                     | 99  |

| 表 66.  | FIFO ステータス・レジスタ 1 .....                      | 100 |

| 表 67.  | FIFO ステータス・レジスタ 2 .....                      | 100 |

| 表 68.  | コリジョン表示レジスタ .....                            | 101 |

| 表 69.  | パッシブ・ターゲット表示レジスタ .....                       | 102 |

| 表 70.  | 送信バイト数レジスタ 1 .....                           | 103 |

| 表 71.  | 送信バイト数レジスタ 2 .....                           | 103 |

| 表 72.  | ビット・レート検出表示レジスタ .....                        | 104 |

| 表 73.  | A/D コンバータ出力レジスタ .....                        | 105 |

| 表 74.  | アンテナ・チューニング・コントロール・レジスタ 1 .....              | 106 |

| 表 75.  | アンテナ・チューニング・コントロール・レジスタ 2 .....              | 106 |

| 表 76.  | 送信ドライバ・レジスタ .....                            | 107 |

| 表 77.  | AM 変調指數 .....                                | 107 |

| 表 78.  | RFO ドライバ抵抗 .....                             | 108 |

| 表 79.  | 補助変調設定レジスタ .....                             | 109 |

| 表 80.  | パッシブ・ターゲット変調レジスタ .....                       | 110 |

| 表 81.  | パッシブ・ターゲット・モードの変調状態および非変調状態でのドライバの出力抵抗 ..... | 110 |

| 表 82.  | 送信ドライバ・タイミング・レジスタ .....                      | 111 |

| 表 83.  | 外部フィールド検出器アクティブ化閾値レジスタ .....                 | 112 |

| 表 84.  | 抵抗性 AM 変調レジスタ .....                          | 113 |

| 表 85.  | 抵抗性 AM 変調で変調している状態でのドライバ出力抵抗 .....           | 113 |

| 表 86.  | 外部フィールド検出器非アクティブ化閾値レジスタ .....                | 114 |

| 表 87.  | RFI1 入力で見たピア検出閾値 .....                       | 115 |

| 表 88.  | RFI1 入力で見たコリジョン防止閾値 .....                    | 115 |

| 表 89.  | 送信ドライバ・タイミング表示レジスタ .....                     | 116 |

| 表 90.  | レギュレータ電圧コントロール・レジスタ .....                    | 117 |

| 表 91.  | レギュレータ表示レジスタ .....                           | 118 |

| 表 92.  | 安定化電圧 .....                                  | 118 |

| 表 93.  | RSSI 表示レジスタ .....                            | 119 |

| 表 94.  | RSSI .....                                   | 119 |

| 表 95.  | ゲイン低減状態レジスタ .....                            | 120 |

| 表 96.  | 静電容量センサ・コントロール・レジスタ .....                    | 121 |

| 表 97.  | 静電容量センサ表示レジスタ .....                          | 121 |

| 表 98.  | 補助表示レジスタ .....                               | 122 |

| 表 99.  | オーバーシュート保護コンフィギュレーション・レジスタ 1 .....           | 123 |

| 表 100. | オーバーシュート保護コンフィギュレーション・レジスタ 2 .....           | 123 |

| 表 101. | アンダーシュート保護コンフィギュレーション・レジスタ 1 .....           | 124 |

# 参考資料

|                                               |     |

|-----------------------------------------------|-----|

| 表 102. アンダーシュート保護コンフィギュレーション・レジスタ 2           | 124 |

| 表 103. ウェイクアップ・タイマ・コントロール・レジスタ                | 125 |

| 表 104. 標準ウェイクアップ時間                            | 125 |

| 表 105. 振幅測定コンフィギュレーション・レジスタ                   | 126 |

| 表 106. 振幅測定基準レジスタ                             | 126 |

| 表 107. 振幅測定自動平均化表示レジスタ                        | 127 |

| 表 108. 振幅測定表示レジスタ                             | 127 |

| 表 109. 位相測定コンフィギュレーション・レジスタ                   | 128 |

| 表 110. 位相測定基準レジスタ                             | 128 |

| 表 111. 位相測定自動平均化表示レジスタ                        | 129 |

| 表 112. 位相測定表示レジスタ                             | 129 |

| 表 113. 静電容量測定コンフィギュレーション・レジスタ                 | 130 |

| 表 114. 静電容量測定基準レジスタ                           | 130 |

| 表 115. 静電容量測定自動平均化表示レジスタ                      | 131 |

| 表 116. 静電容量測定表示レジスタ                           | 131 |

| 表 117. IC 識別レジスタ                              | 132 |

| 表 118. 絶対最大定格                                 | 133 |

| 表 119. 動作条件                                   | 134 |

| 表 120. CMOS I/O の特性                           | 135 |

| 表 121. ST25R3916/7 の電気的特性 (VDD = 3.3V)        | 136 |

| 表 122. ST25R3916/7 の電気的特性 (VDD = 5.5V)        | 137 |

| 表 123. ST25R3916/7 の電気的特性 (VDD = 2.4V)        | 138 |

| 表 124. SPI の特性 (5MHz)                         | 139 |

| 表 125. SPI の特性 (5MHz < 1/TSCLK < 10MHz)       | 139 |

| 表 126. AC 測定条件                                | 141 |

| 表 127. AC 測定条件 - I <sup>2</sup> C コンフィギュレーション | 141 |

| 表 128. 入力パラメータ                                | 141 |

| 表 129. DC 特性                                  | 141 |

| 表 130. 100kHz の AC 特性                         | 142 |

| 表 131. 400kHz の AC 特性                         | 142 |

| 表 132. 1MHz の AC 特性                           | 143 |

| 表 133. 3.4MHz の AC 特性                         | 143 |

| 表 134. VFQFPN の寸法データ                          | 145 |

| 表 135. WLCSP の寸法データ                           | 147 |

| 表 136. 文書改版履歴                                 | 150 |

| 表 137. 日本語版文書改版履歴                             | 150 |

## 図の一覧

|       |                                          |     |

|-------|------------------------------------------|-----|

| 図 1.  | 最小限のシステム構成 - シングル・エンド構成によるアンテナ駆動         | 13  |

| 図 2.  | 最小限のシステム構成 - 差動構成によるアンテナ駆動               | 14  |

| 図 3.  | ST25R3916/7 のブロック図                       | 15  |

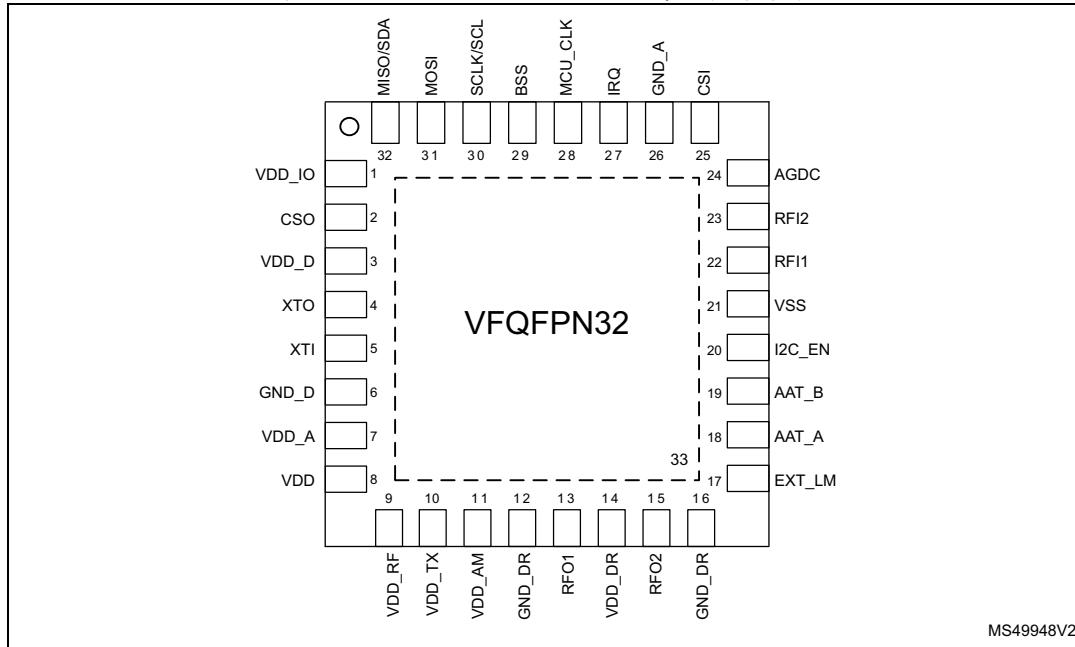

| 図 4.  | ST25R3916 QFN32 ピン配置（上面図）                | 19  |

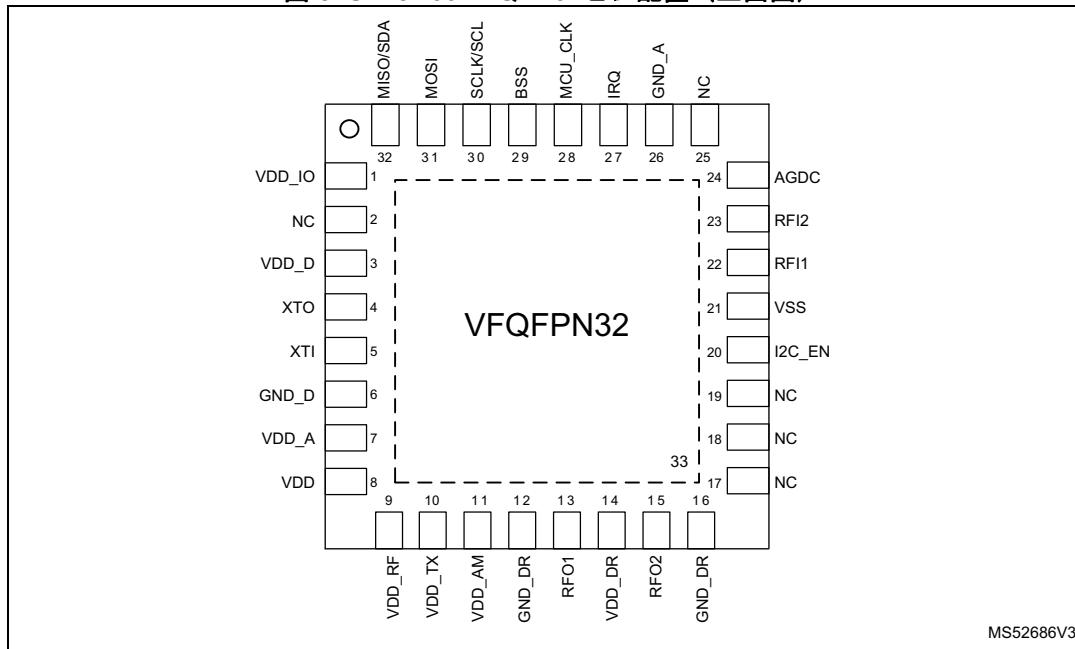

| 図 5.  | ST25R3917 QFN32 ピン配置（上面図）                | 19  |

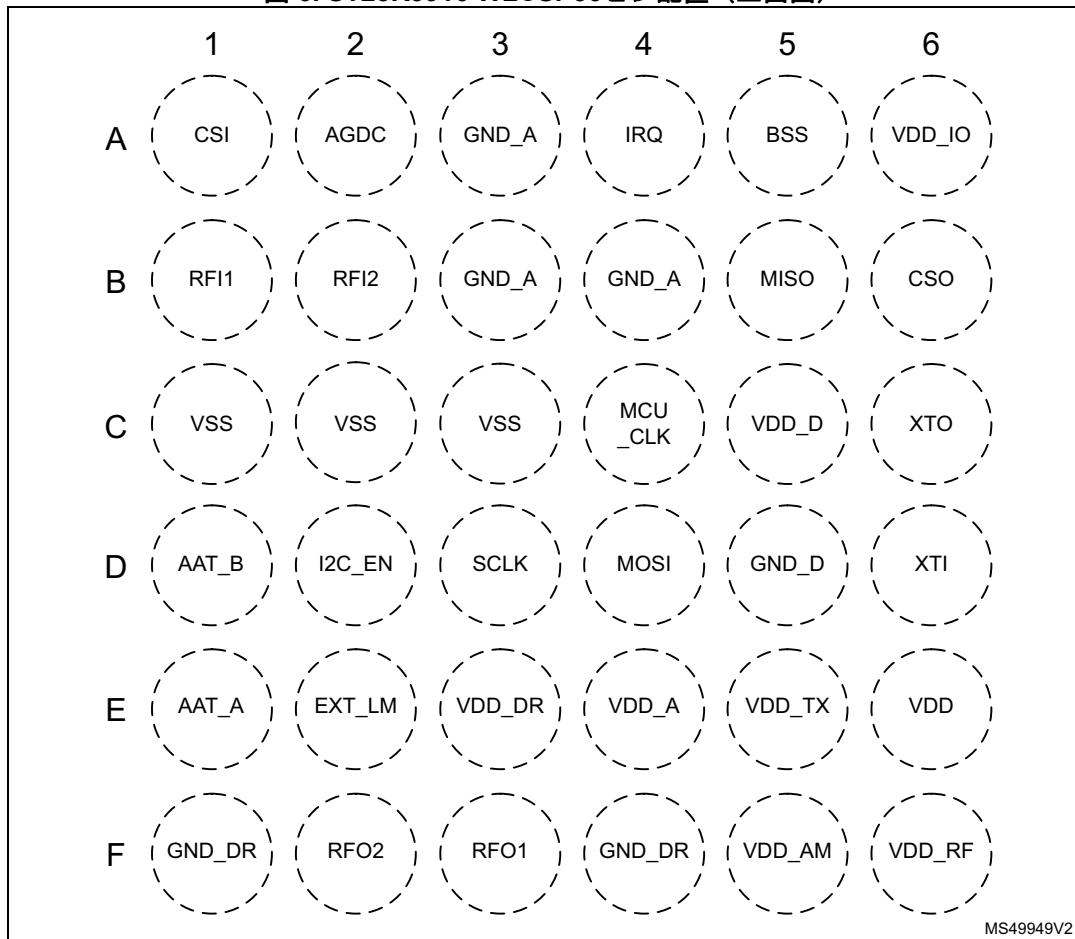

| 図 6.  | ST25R3916 WLCSP36 ピン配置（上面図）              | 20  |

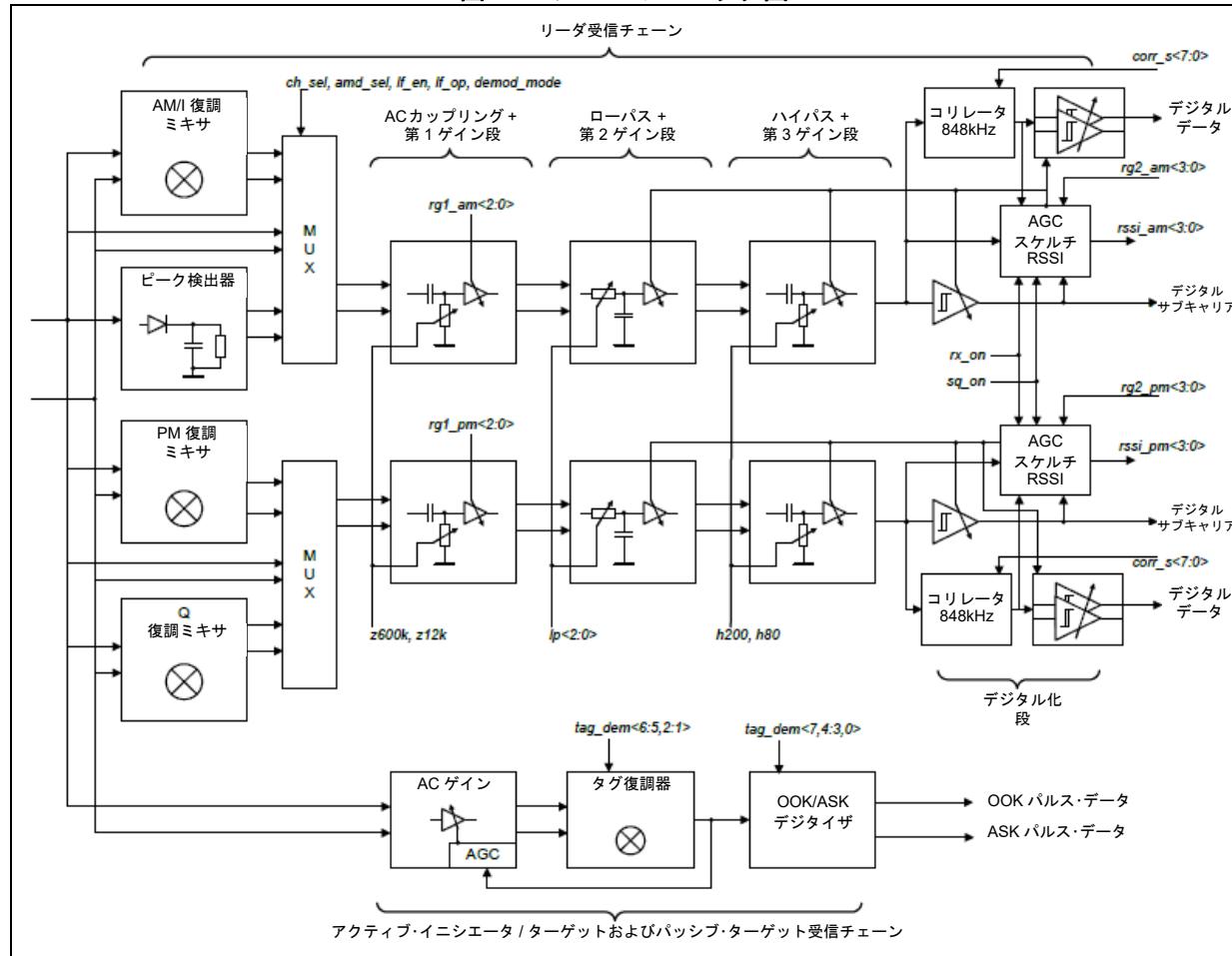

| 図 7.  | レシーバのブロック図                               | 27  |

| 図 8.  | 静電容量センサのブロック図                            | 32  |

| 図 9.  | 位相差が 90° の場合の位相検出器の入出力                   | 38  |

| 図 10. | 位相差が 135° の場合の位相検出器の入出力                  | 38  |

| 図 11. | ST25R3916/7 の電源系                         | 40  |

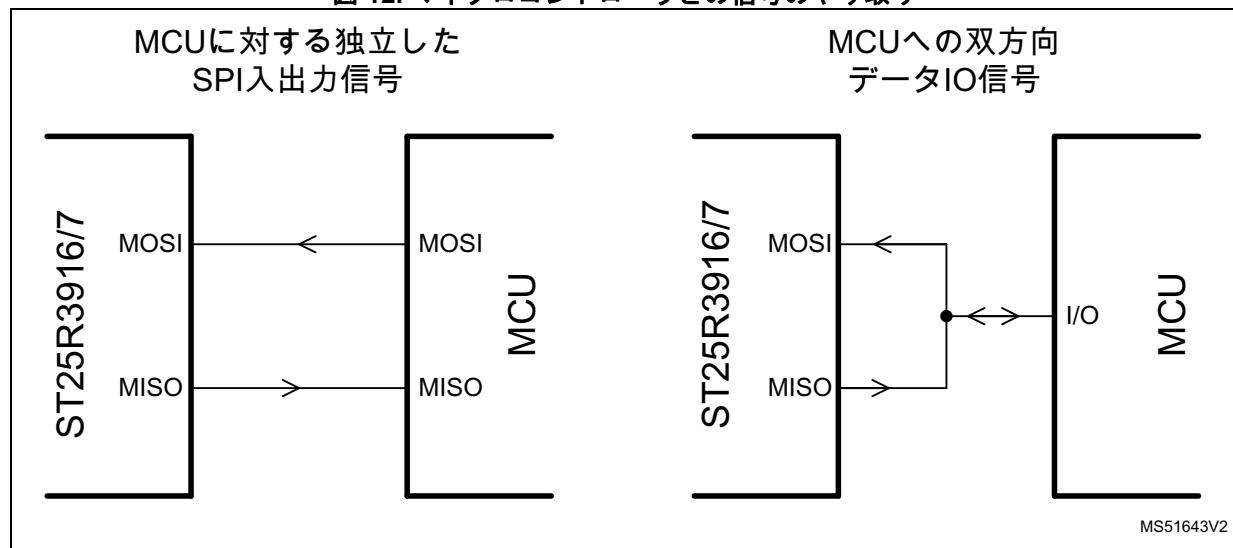

| 図 12. | マイクロコントローラとの信号のやり取り                      | 48  |

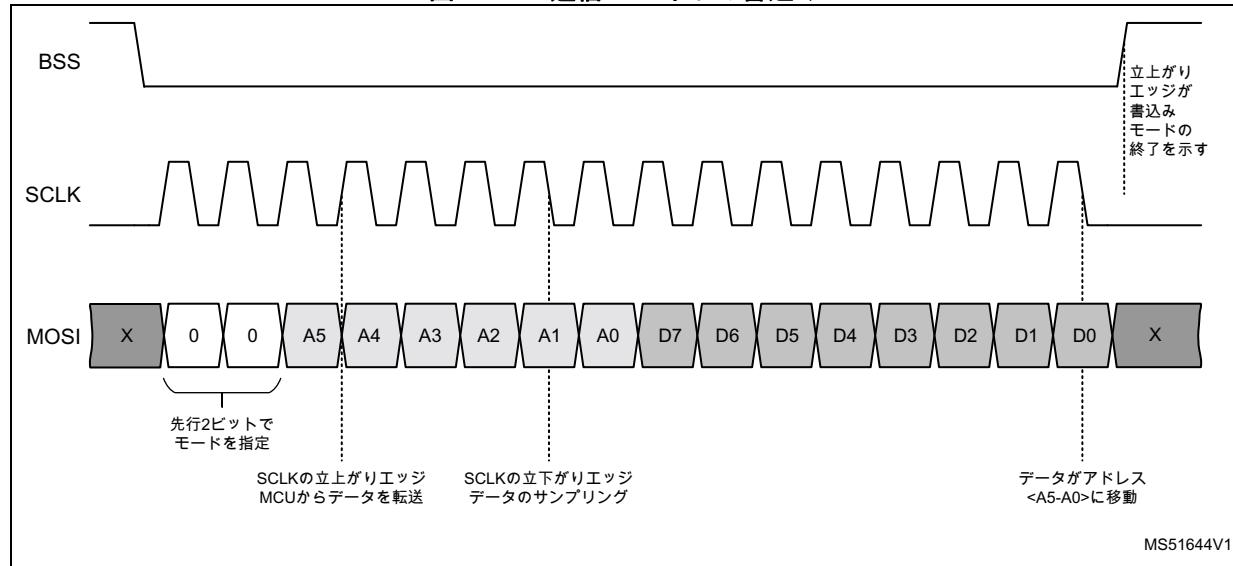

| 図 13. | SPI 通信 : 1 バイトの書き込み                      | 50  |

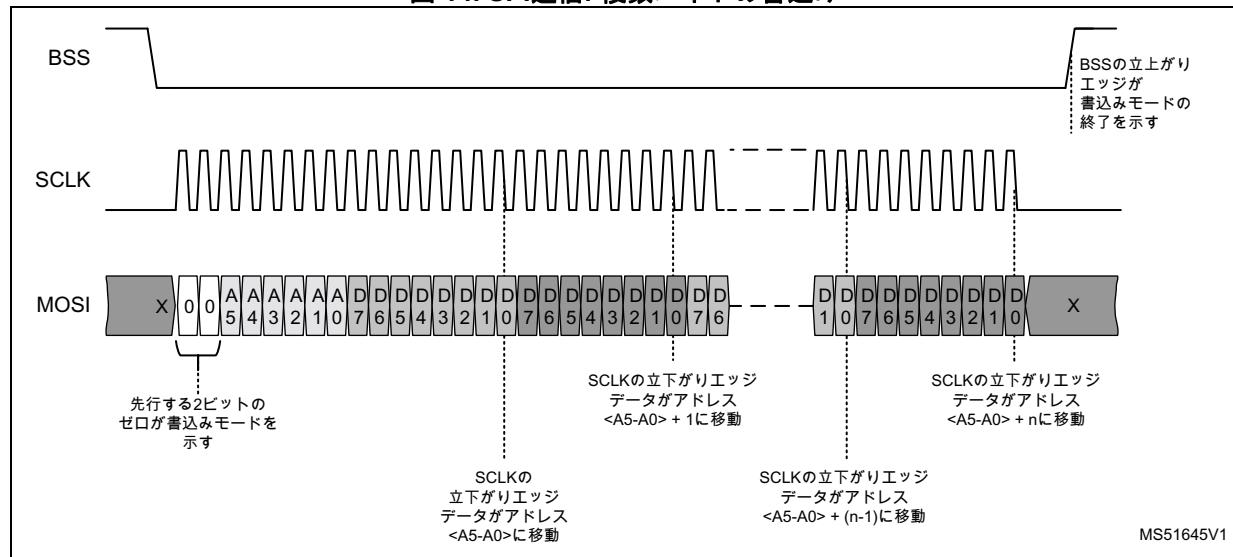

| 図 14. | SPI 通信 : 複数バイトの書き込み                      | 50  |

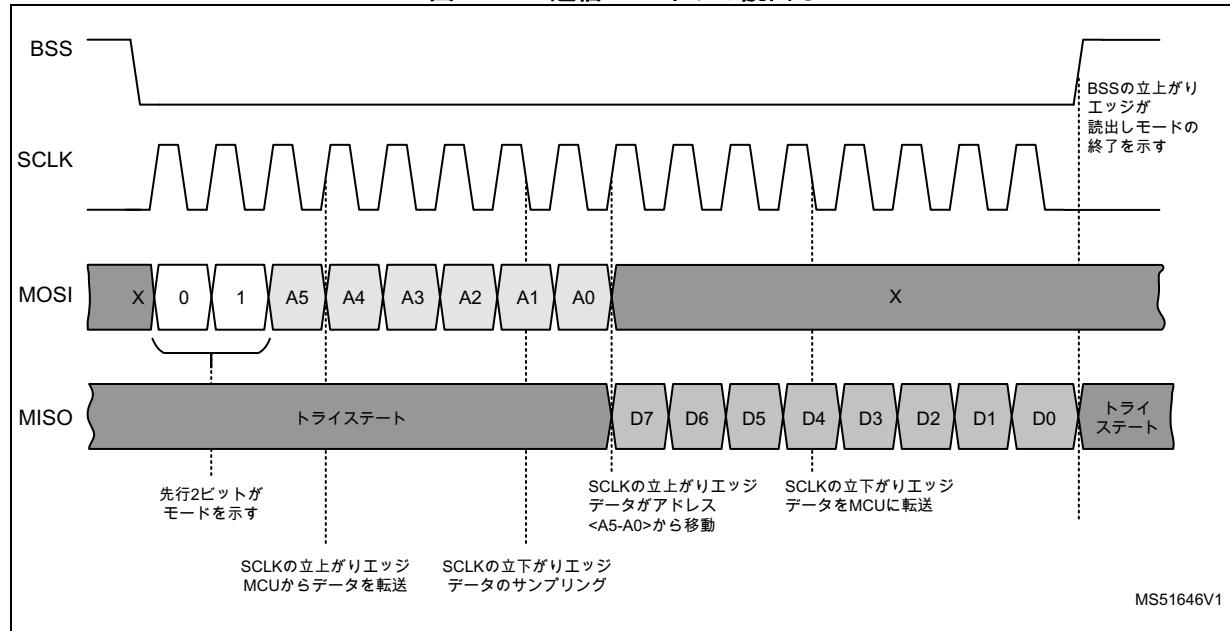

| 図 15. | SPI 通信 : 1 バイトの読み出し                      | 51  |

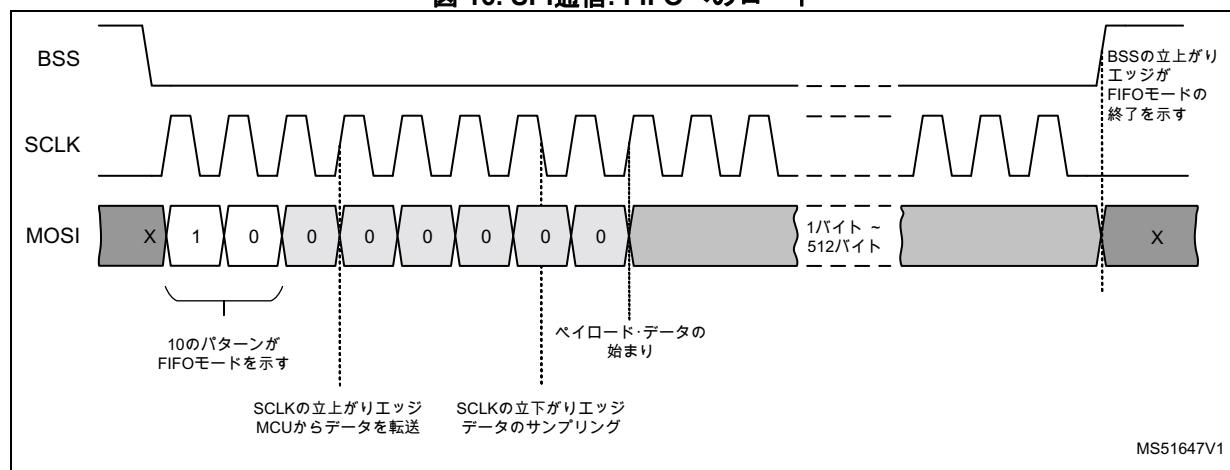

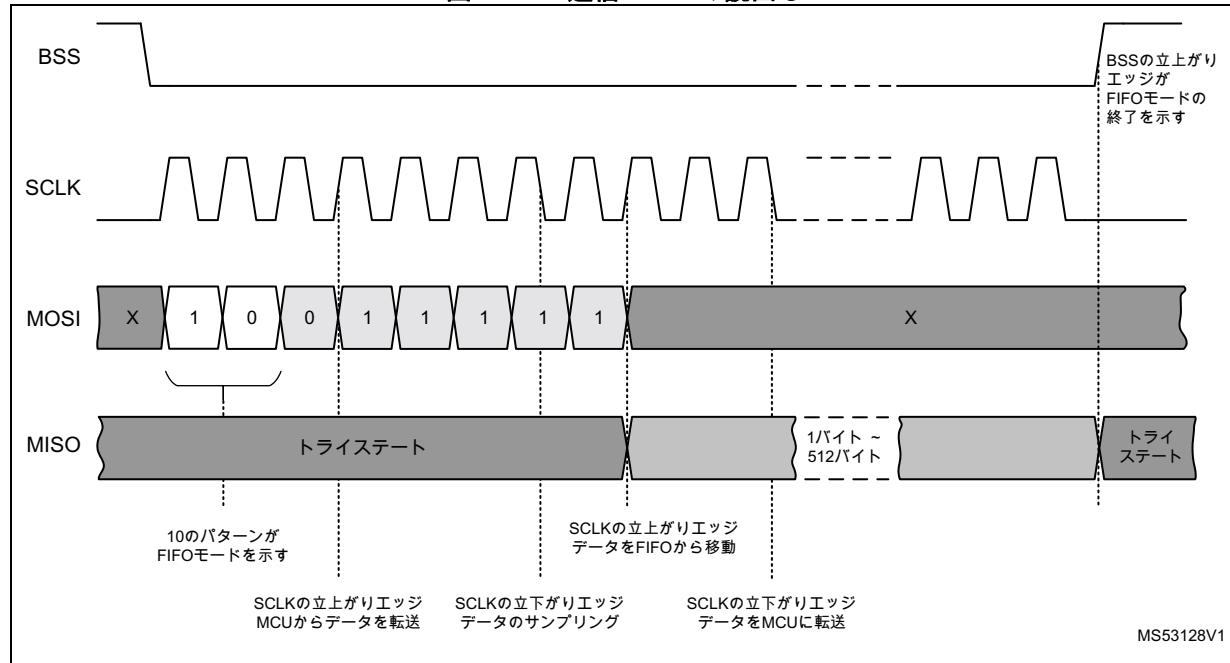

| 図 16. | SPI 通信 : FIFO へのロード                      | 51  |

| 図 17. | SPI 通信 : FIFO の読み出し                      | 52  |

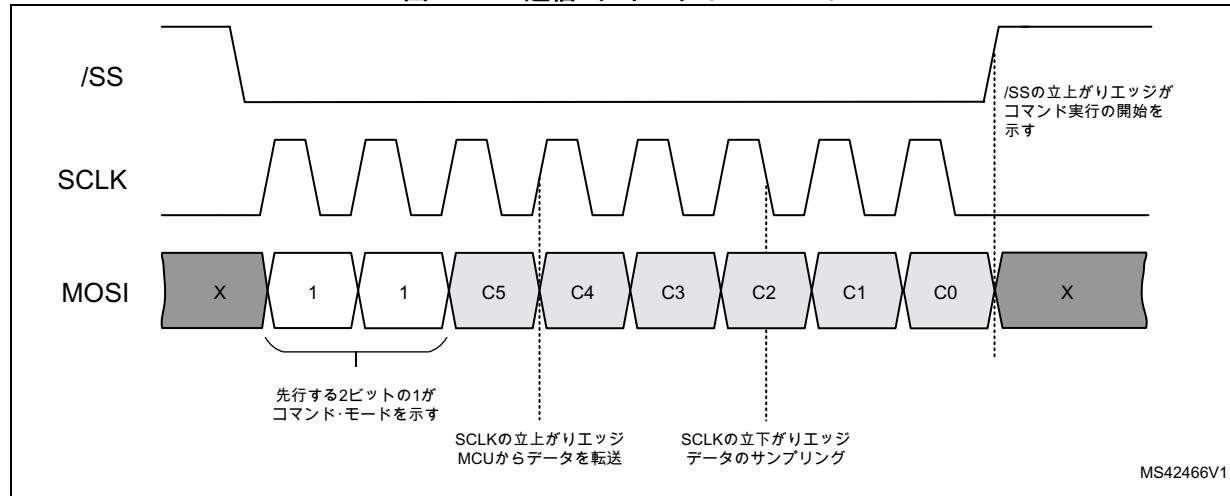

| 図 18. | SPI 通信 : ダイレクト・コマンド                      | 53  |

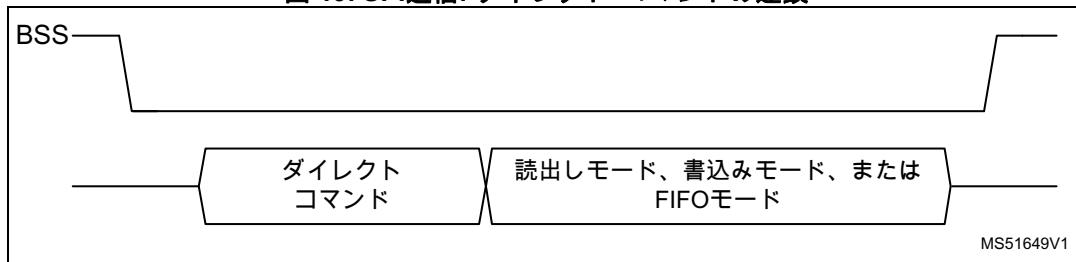

| 図 19. | SPI 通信 : ダイレクト・コマンドの連鎖                   | 53  |

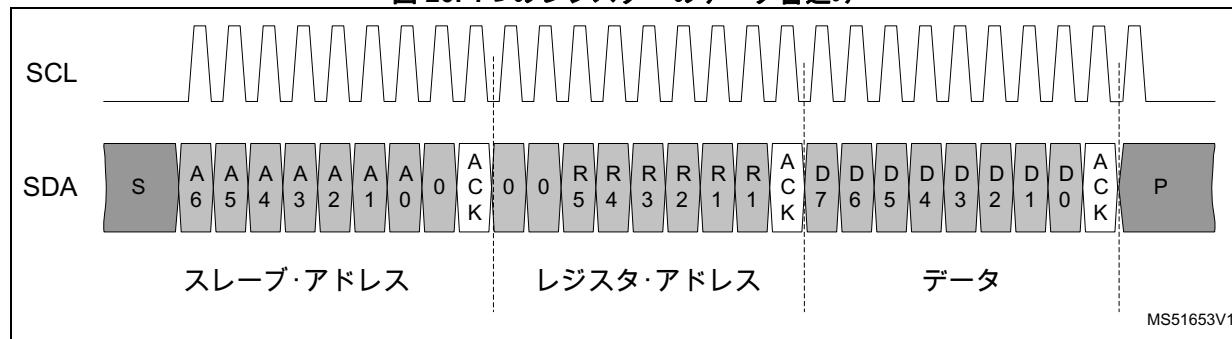

| 図 20. | 1 つのレジスタへのデータ書き込み                        | 54  |

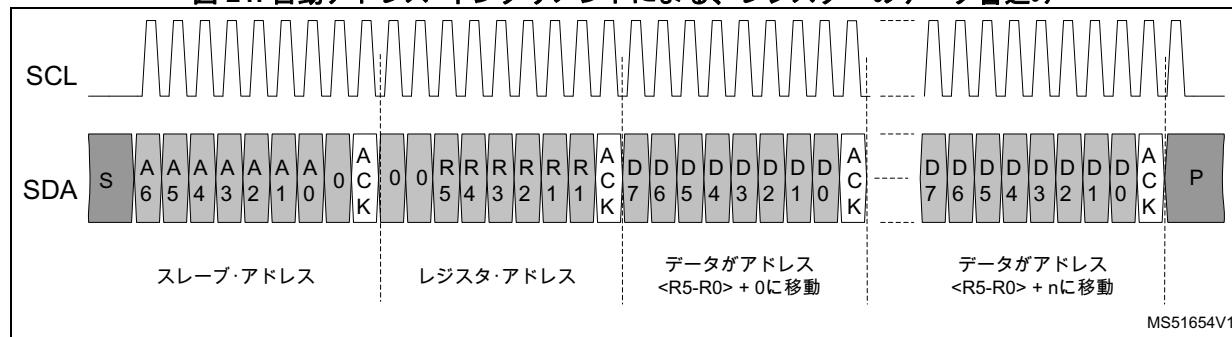

| 図 21. | 自動アドレス・インクリメントによる、レジスタへのデータ書き込み          | 54  |

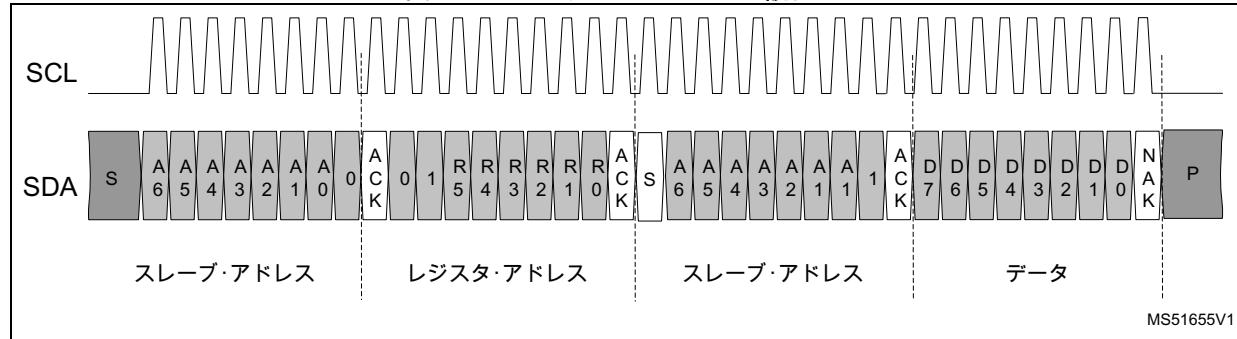

| 図 22. | レジスタからの 1 バイト読み出し                        | 55  |

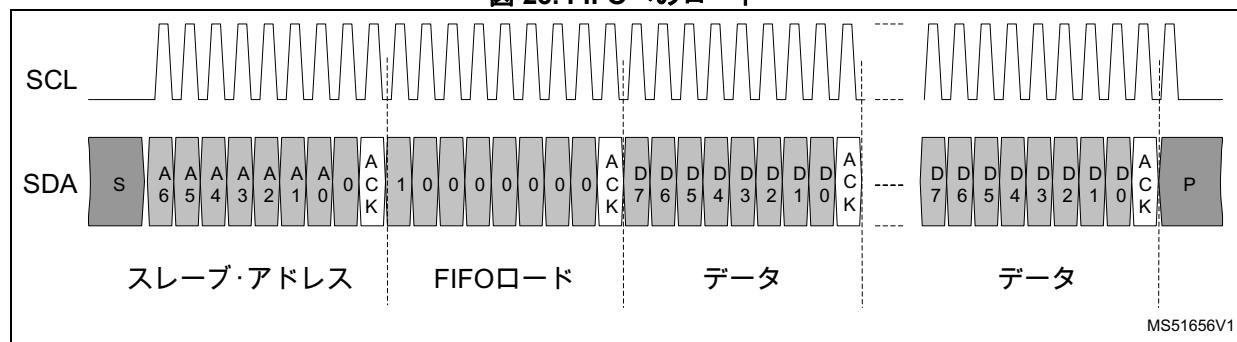

| 図 23. | FIFO へのロード                               | 55  |

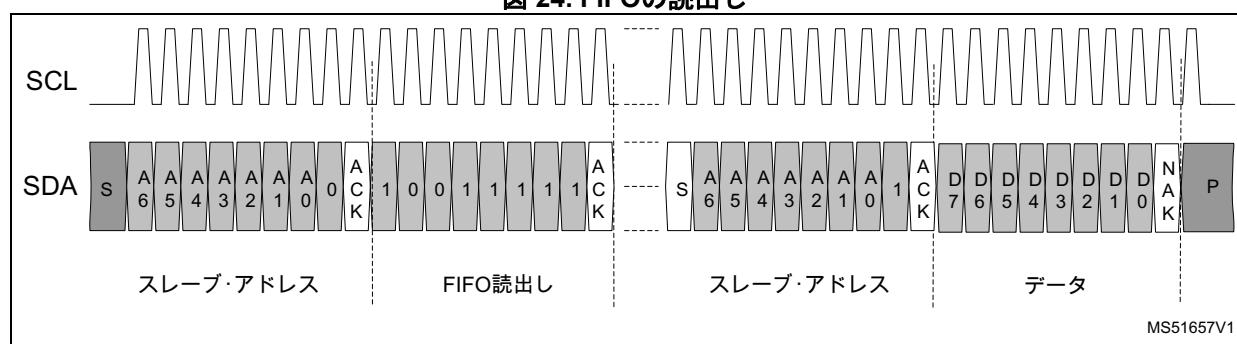

| 図 24. | FIFO の読み出し                               | 55  |

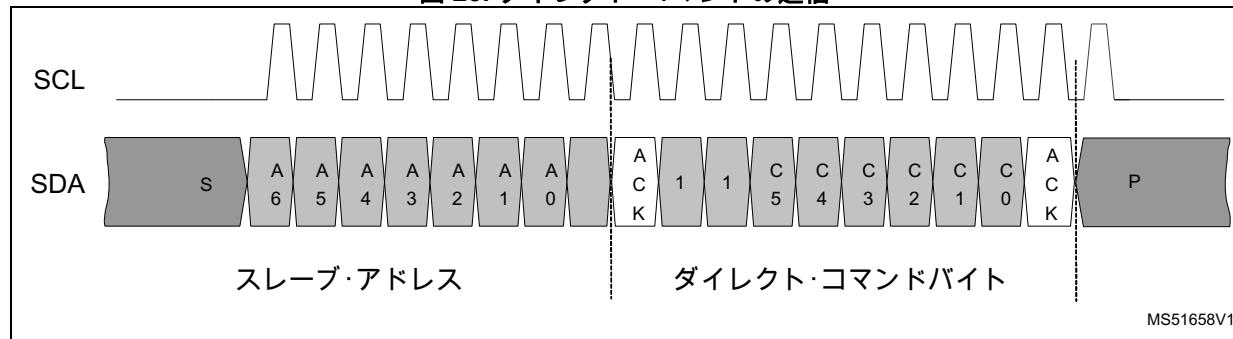

| 図 25. | ダイレクト・コマンドの送信                            | 56  |

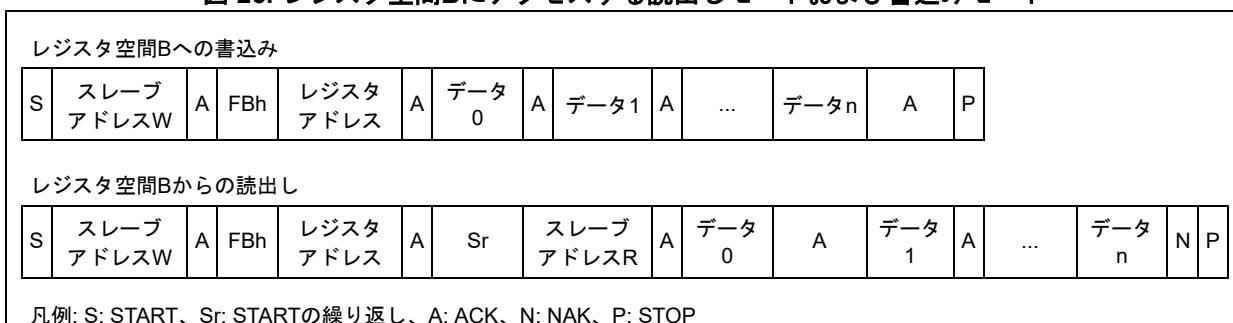

| 図 26. | レジスタ空間 B にアクセスする読み出しモードおよび書き込みモード        | 56  |

| 図 27. | I <sup>2</sup> C マスターによる先頭バイト直後のスレーブ読み出し | 57  |

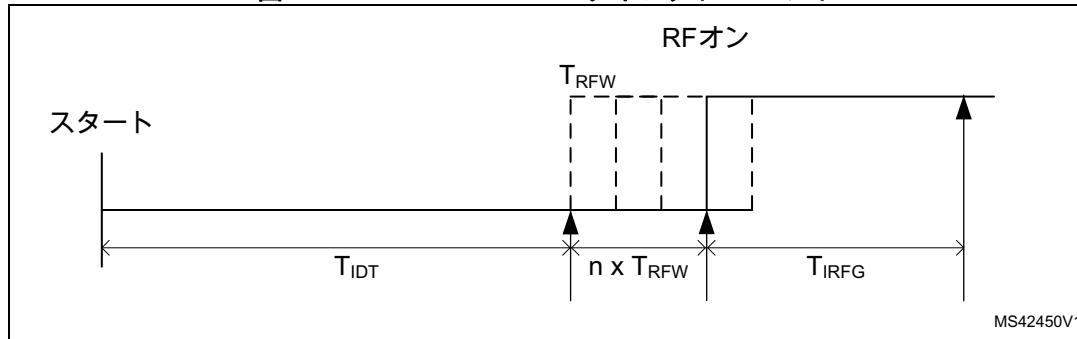

| 図 28. | NFC Initial Field ON ダイレクト・コマンド          | 61  |

| 図 29. | NFC Response Field ON ダイレクト・コマンド         | 61  |

| 図 30. | SPI タイミング・チャート - 一般的な動作                  | 140 |

| 図 31. | SPI タイミング・チャート - 読出し動作                   | 140 |

| 図 32. | I <sup>2</sup> C の AC 波形                 | 144 |

| 図 33. | I <sup>2</sup> C の AC 測定                 | 144 |

| 図 34. | VFQFPN の外形                               | 145 |

| 図 35. | VFQFPN の推奨フットプリント                        | 146 |

| 図 36. | WLCSP の外形                                | 147 |

| 図 37. | WLCSP の推奨フットプリント                         | 148 |

## 1 アプリケーション

ST25R3916およびST25R3917の各デバイス（以下、ST25R3916/7）は、以下をはじめとする幅広いNFCおよびHF RFIDのアプリケーションに最適な製品です。

- NFCフォーラム準拠のNFCユニバーサルデバイス

- EMVCo 3.0準拠の非接触決済端末

- ISO14443およびISO15693準拠のユニバーサルNFCデバイス

- FeliCa™リーダライタ

- リーダ・モードでは、NFCフォーラム規定の5つのタグ・タイプすべてに対応

- Kiovo、CTS、B'などの一般的な独自プロトコルのすべてに対応

これら2つのデバイスの主な相違点を表 1に示します。

表 1. 機能一覧

| 機能                                    | ST25R3916                                                               | ST25R3917 |

|---------------------------------------|-------------------------------------------------------------------------|-----------|

| ISO/IEC 14443 Type-A対応                | あり                                                                      |           |

| ISO/IEC 14443 Type-B対応                | あり                                                                      |           |

| ISO/IEC 15693対応                       | あり                                                                      |           |

| FeliCa™対応                             | あり                                                                      |           |

| NFCタグ読出し対応                            | NFC Type1タグ<br>NFC Type2タグ<br>NFC Type3タグ<br>NFC Type4タグ<br>NFC Type5タグ |           |

| ISO/IEC 18092パッシブ・イニシエータ・モード対応        | あり                                                                      |           |

| ISO/IEC 18092パッシブ・ターゲット・モード対応         | あり                                                                      | なし        |

| ISO/IEC 18092アクティブ・イニシエータ/ターゲット・モード対応 | あり                                                                      | なし        |

| 自動アンテナ・チューニング（AAT）対応                  | あり                                                                      | なし        |

| カード・エミュレーション対応                        | あり                                                                      | なし        |

| 静電容量センサ・ウェイクアップ対応                     | あり                                                                      | なし        |

| 誘導センサ・ウェイクアップ対応                       | あり                                                                      | なし        |

## 2 概要

ST25R3916/7は、高性能のNFCユニバーサルデバイスであり、該当する範囲でNFCイニシエータ、NFCターゲット、NFCリーダ、NFCカード・エミュレーションの各モードに対応しています。

EMVCo 3.0のアナログ規格とデジタル規格に完全対応したこのNFC ICは、POS端末アプリケーションに最適であり、ノイズ発生源となるLCDの近傍にアンテナがある場合のような過酷な環境でも、きわめて高速なEMVCo 3.0認証サイクルを実現します。

どちらのデバイスも、先進のアナログ・フロントエンド (AFE) と高度に集積化したデータ・フレーミング・システムを搭載しています。ISO 18092パッシブ/アクティブ・イニシエータ、ISO 18092パッシブ/アクティブ・ターゲット、高ビット・レートにも対応したNFC-A/B (ISO 14443A/B) リーダ、NFC-F (FeliCa™) リーダ、最大53kbpsのNFC-V (ISO 15693) リーダ、およびNFC-A/NFC-Fのカード・エミュレーションに対応します。

AFEおよびフレーミング・システムの独自動作モードであるストリーム・モードやトランスペアント・モードを使用すれば、上記以外のカスタム・プロトコルをリーダ・モードまたはカード・エミュレーション・モードで実装できます。

ST25R3916/7は、アンテナを高い効率で直接駆動する大電力のRF出力を提供します。

そのほかにも、ST25R3916/7は、低消費電力アプリケーションで競合製品には望めない各種機能を備えています。リーダのフィールドをオンにせずにカードの存在を検出する、低消費電力の静電容量センサを内蔵しています。アンテナ信号の振幅または位相を測定することによってもカードの存在を検出できます。ST25R3916/7は、低消費電力のRC発振器とウェイクアップ・タイマも内蔵し、選択された一定時間が経過すると自動的にウェイクアップし、タグが存在するかどうかを確認します。この確認では、静電容量、位相、または振幅による低消費電力のカード検出手法のいずれかまたは複数の組み合わせが使用されます。

ST25R3916/7は、幅広い電源電圧範囲 (2.4V ~ 5.5V) とペリフェラルI/O電圧範囲 (1.65V ~ 5.5V) による動作を目的として設計されています。

大電力のRF出力、低消費電力モード、幅広い電源電圧範囲を兼ね備え、公共系や産業系のNFCアプリケーションに最適です。

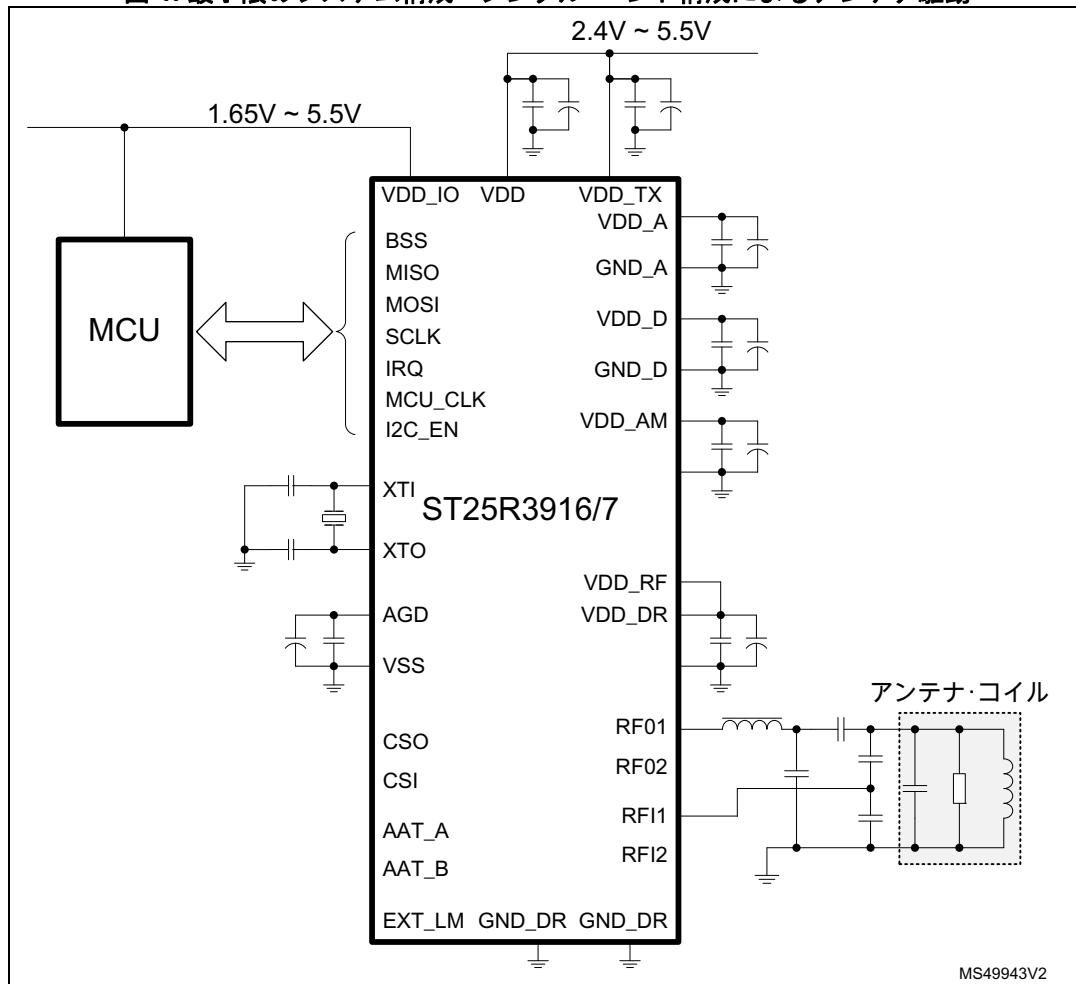

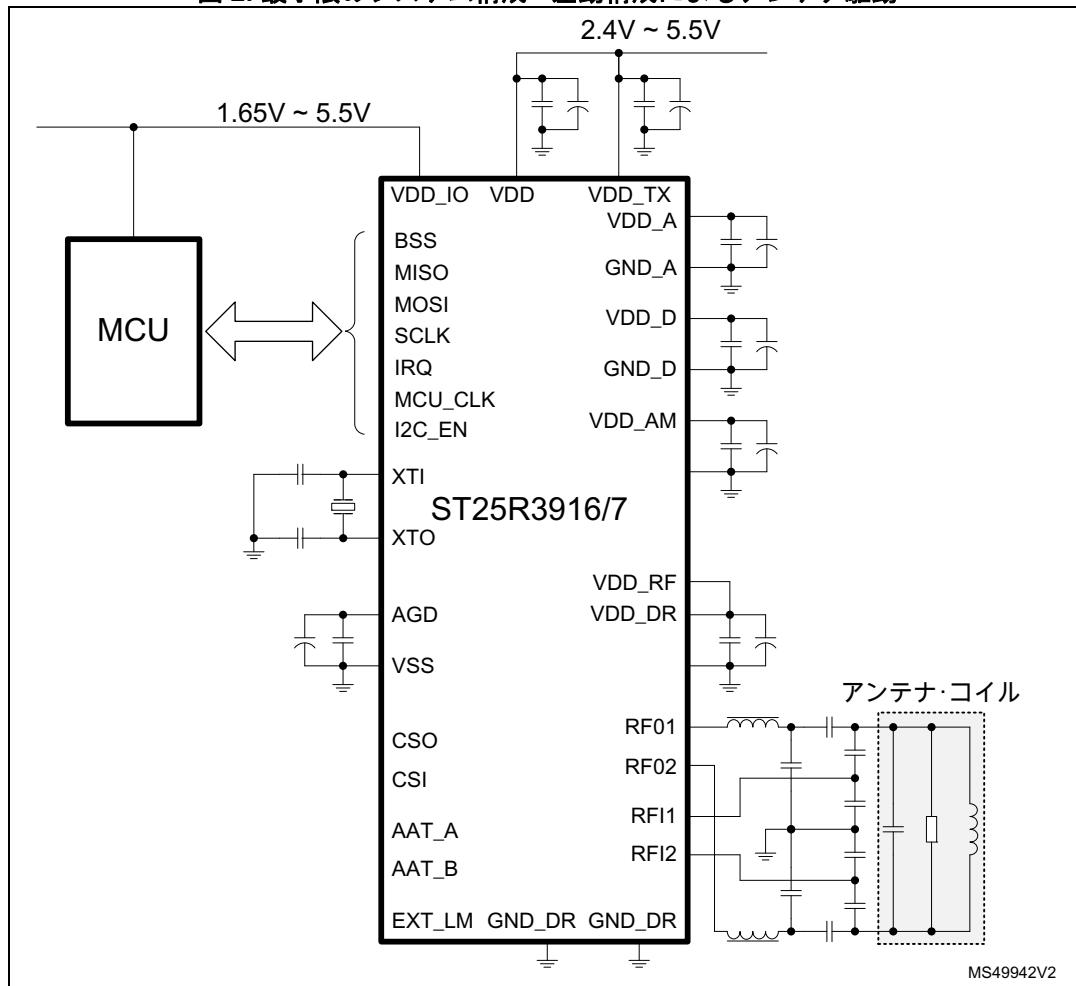

## 2.1 システム図

図 1と図 2に、それぞれシングル・エンド構成および差動構成のアンテナによる最小限のシステム構成を示します。いずれもEMCフィルタが使用されています。

図 1. 最小限のシステム構成 - シングル・エンド構成によるアンテナ駆動

# 参考資料

## 概要

ST25R3916/7

図2. 最小限のシステム構成 - 差動構成によるアンテナ駆動

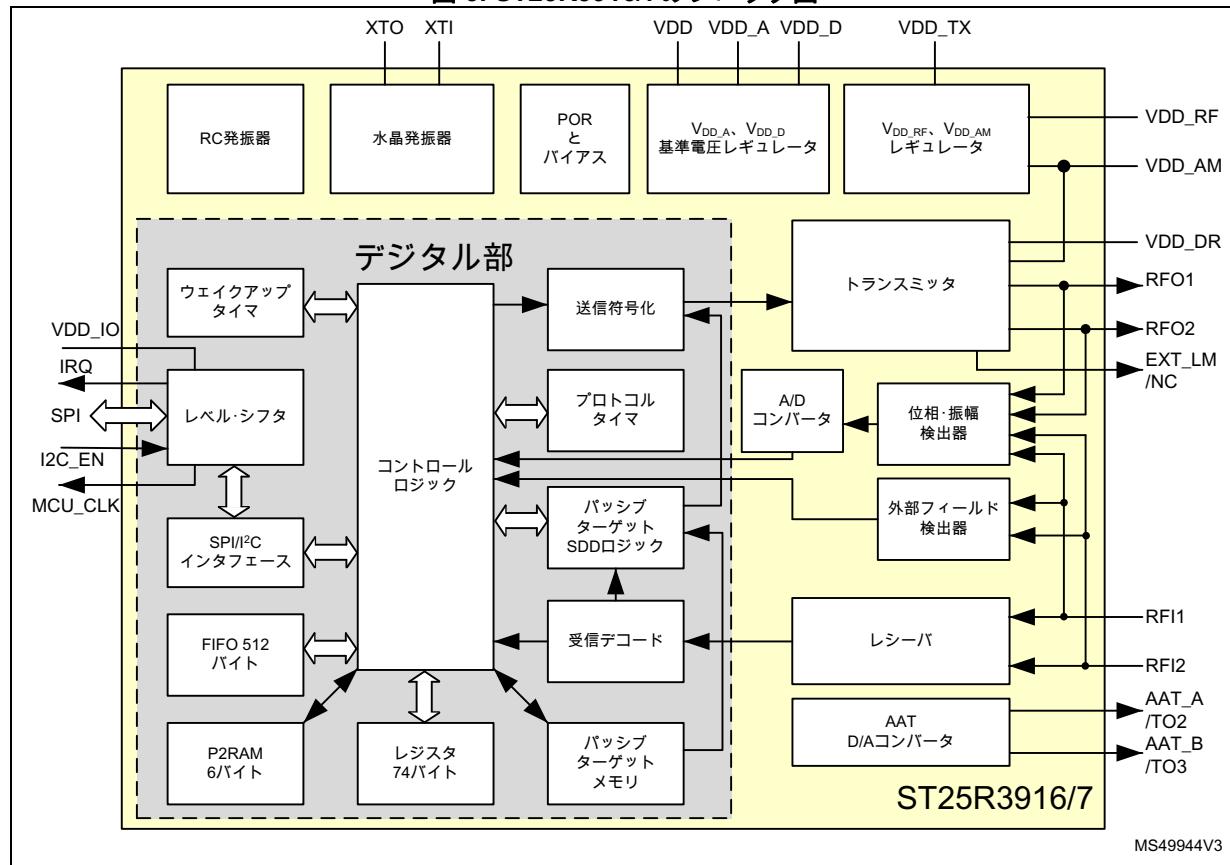

### 2.2 ブロック図

図 3にST25R3916/7のブロック図を示します。主な機能については、この後の各サブセクションで説明します。

図 3. ST25R3916/7のブロック図

#### 2.2.1 トランスマッタ

リーダ・モードでは、トランスマッタがRFO1とRFO2の両ピンを介して外部アンテナを駆動し、RFフィールドを生成します。シングル・エンド構成と差動構成のアンテナに対応しています。トランスマッタ・ブロックでは、送信するRF信号のOOK変調またはAM変調も実施します。

トランスマッタは、RFO1とRFO2の両ピンを独立した状態で使用して最大2つのアンテナをシングル・エンド構成で駆動できるほか、この2本のピンを組み合わせて1つのアンテナを差動構成で駆動することもできます。ドライバは、PCB上に実装されたアンテナを直接駆動できるほか、50Ωのケーブルで接続されたアンテナも駆動できるように設計されています。ただし、50Ωケーブルで接続されたアンテナでは、ST25R3916/7の高度な機能の中には十分に活用できないものがあります（アンテナ診断など）。

カード・エミュレーション・モードのトランスマッタでは、RFO1とRFO2を介してアンテナに接続する内部アンテナ・ドライバの抵抗値を変更することで負荷変調信号を生成します。また、EXT\_LMピンを介して外付けのMOSトランジスタを駆動する機能も備え、これによって負荷変調信号を生成することもできます。

### 2.2.2 レシーバ

レシーバは、13.56MHzのキャリア信号に重畠されたカード変調信号を検出します。レシーバは、一組の復調器、それに続く2つのゲインとフィルタのステージ、および最後のデジタイザ・ステージからなる、2つの受信チェーンで構成されます。復調器は、AM/PM復調器またはI/Q復調器として動作できます。フィルタ特性は、選択したRFモードとビット・レートに合わせて調整し、最適化した性能を得ることができます（周波数212kHz～848kHzのサブキャリアに対応しています）。レシーバは、フィルタ段のほかにも、ノイズが多い環境で信頼性に優れた動作を実現する機能をいくつか備えています（AGC、スケルチ）。

レシーバは、RFI1とRFI2ピンでアンテナに接続します。レシーバの出力は、復調およびデジタル化されたサブキャリア信号をデコードするフレーミング・ブロックに接続されています。

### 2.2.3 位相検出器と振幅検出器

位相検出器は、トランスマッタの出力信号（RFO1とRFO2）とレシーバの入力信号（RFI1とRFI2）との位相差を測定します。

振幅検出器は、レシーバ入力RFI1とRFI2間で差動RFキャリア信号の振幅を測定します。この差動振幅信号は、アンテナのLCタンクに発生するRF信号の振幅と正比例の関係にあります。

位相検出器と振幅検出器は、次のような複数の目的に使用できます。

- PM復調: RFI1とRFI2の位相差を測定することによって機能します（復調したLF信号をレシーバに供給します）

- アンテナの同調の確認: RFOxピンとRFIxピンの間の平均位相差を測定します。

- アンテナ電圧に比例する、RFI1ピンとRFI2ピンの信号振幅の測定

### 2.2.4 自動アンテナ・チューニング（AAT）

AATブロックは、2つの独立した8bit D/Aコンバータによって構成されます。これらのコンバータによって、外付けの可変コンデンサを制御する電圧を発生します。この電圧は、(0V～3.3V)の範囲でプログラムできます。

注： ハードウェアによるウェイクアップ機能と自動アンテナ・チューニング機能の併用はお勧めできません。詳細は、お近くのST営業所までお問い合わせください。

### 2.2.5 A/Dコンバータ

ST25R3916/7は、A/Dコンバータを搭載しています。複数のソースからの信号を多重化した信号を入力として、診断機能や低消費電力のカード検出に使用できます。A/D変換の結果は、ホスト・インターフェースから読出しが可能なレジスタに格納されます。

### 2.2.6 静電容量センサ

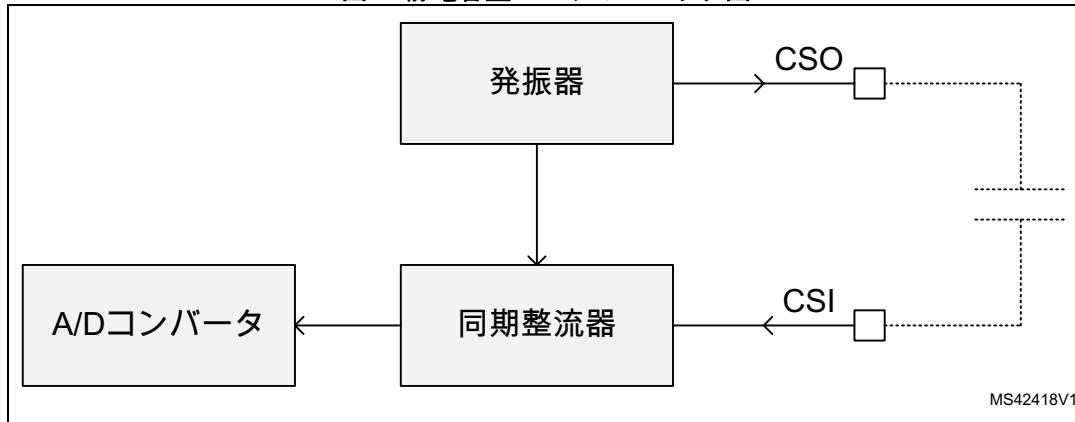

低消費電力でカードを検出する機能を実装するために、静電容量センサが使用されています。CSIピンおよびCSOピンに接続された2つの小さな銅板間の静電容量を測定します。カードや手のような物体が存在すると、この静電容量が変化します。

校正時に基準静電容量（環境の寄生静電容量に相当）を保存します。ST25R3916では、静電容量式の低消費電力カード検出モードにより、静電容量を定期的に測定して、その結果を保存されている基準値と比較します。測定した静電容量値と保存されている基準値との差が、レジスタに設定された閾値を超えると、外部コントローラに割り込みが送信されます。

## 2.2.7 外部フィールド検出器

外部フィールド検出器は、外部RFフィールドの存在を検出する低消費電力のブロックであり、アクティブまたはパッシブのターゲット・モードで使用されます。外部フィールド検出の閾値として、ピア検出およびコリジョン防止の2種類に対応しています。

ピア検出閾値は、アクティブとパッシブのピア・ツー・ピア・モードで使用し、ピア・デバイスでRFフィールドがオンにされたことを検出します。

コリジョン防止閾値は、RFコリジョン防止手順の実行時に使用し、外部RFフィールドの存在を検出します。

## 2.2.8 水晶発振器

水晶発振器は、27.12MHzの水晶振動子で動作します。起動時は、発振器の相互コンダクタンスを高くすることで、高速化を図っています。起動時間は水晶振動子の種類や温度などのパラメータによって異なるので、発振器の振幅を観測し、その動作が安定した時点で割り込みが生成されます。

発振器ブロックは、[IOコンフィギュレーション・レジスタ1](#)の設定に従い、外部マイクロコントローラ用のクロック信号 (MCU\_CLK) も供給します。

## 2.2.9 電源レギュレータ

電源レギュレータを内蔵することで、システム全体に対して高い電源電圧変動除去比 (PSRR) を保証しています。

アナログ・ブロック、デジタル・ブロック、RF出力ドライバのそれぞれに使用している3つの電圧レギュレータにより、ST25R3916/7からノイズ源を分離できます。4番目の電圧レギュレータは、アナログ・レシーバ用の基準電圧 (AGDCとアナログ・グランド) を生成します。

RF出力ドライバの電圧レギュレータは、システム電源の安定性とRF出力電力に応じてST25R3916/7で自動的に設定できます (詳細は[セクション 4.4.10: Adjust Regulators \(レギュレータ調整\)](#) 参照)。

## 2.2.10 PORとバイアス

このブロックは、他のすべてのブロックにバイアス電流と基準電圧を供給します。また、電源投入時および電源電圧低下時にリセット信号を発生するパワーオン・リセット (POR) 回路も備えています。

## 2.2.11 RC発振器とウェイクアップ・タイマ

ST25R3916/7は、カードの存在を低消費電力で検出する複数の機能 (静電容量センサ、位相測定、振幅測定) を備えています。RC発振器とレジスタで設定できるウェイクアップ・タイマは、低消費電力のカード検出モードで、定期的にカード検出動作を実行するために使用します。

注： ハードウェアによるウェイクアップ機能と自動アンテナ・チューニング機能の併用はお勧めできません。詳細は、お近くのST営業所までお問い合わせください。

### 2.2.12 送信エンコード

選択したRFモードとビット・レートに応じて送信フレームをエンコードするブロックです。SOF (Start Of Frame)、EOF (End Of Frame)、CRC、パリティ・ビットが自動的に生成されます。送信するデータはFIFOから取り出します。

ストリーム・モードではフレーミングを処理せず、FIFOには、そのままトランスマッタに送信される変調データが格納されます。

トランスペアレント・モードの場合は、フレーミング処理とともにFIFOもバイパスされ、MOSIピンからトランスマッタに変調信号を直接供給します。

### 2.2.13 受信デコード

選択したRFモードとビット・レートに応じて受信フレームをデコードするブロックです。SOF (Start Of Frame)、EOF (End Of Frame)、CRC、パリティ・ビットが自動的に検証され、除去されます。受信したデータはFIFOに書き込まれます。

ストリーム・モードではフレーミングを処理せず、デジタル化したサブキャリア信号がFIFOに直接格納されます。

トランスペアレント・モードでは、フレーミングおよびFIFOの動作が実行されません。デジタル化したサブキャリア信号によってMISOピンを直接駆動します。

### 2.2.14 FIFO

ST25R3916/7は、512バイトのFIFOを搭載しています。データの転送方向により、FIFOには受信したデータ、またはこれから送信するデータのいずれかが格納されます。

リーダ・モードのST25R3916/7では、最長8191バイトのフレームを送信でき、任意の長さのフレームを受信できます。カード・エミュレーション・モードでは、FIFOがバッファのように動作し、一度に送信または受信できるフレームの全長が512バイトに制限されます。

### 2.2.15 コントロール・ロジック

コントロール・ロジックは、デバイスの動作を設定するI/Oレジスタを備えています。

### 2.2.16 ホスト・インタフェース

外部マイクロコントローラとの通信用に、4線式のシリアル・ペリフェラル・インタフェース (SPI) と2線式のI<sup>2</sup>Cインタフェースを使用できます。SPIインタフェースとI<sup>2</sup>Cインタフェースはピンを互いに共用しており、どちらのインタフェースをアクティブにするかをI<sup>2</sup>C\_ENピンで選択します。

### 2.2.17 パッシブ・ターゲット・メモリ

ST25R3916デバイスは、パッシブ・ターゲット・モードおよびカード・エミュレーション・モードの設定データを保存する48バイトのRAMを搭載しています。

### 2.2.18 P2RAM

P2RAMには、ウェハ番号、ダイ位置、デバイスのサブバージョン、I<sup>2</sup>Cアドレスが格納されています。P2RAMは生産時に書き込まれます。

# 参考資料

## 3 ピンおよび信号の説明

図 4. ST25R3916 QFN32ピン配置（上面図）

図 5. ST25R3917 QFN32ピン配置（上面図）

# 参考資料

図 6. ST25R3916 WLCSP36ピン配置（上面図）

表 2. ST25R3916 - VFQFPN32およびWLCSP36のピン割当て

| VFQFPN32 | WLCSP | 名前              | 種類 <sup>(1)</sup> | 説明                                        |

|----------|-------|-----------------|-------------------|-------------------------------------------|

| 1        | A6    | VDD_IO          | P                 | ペリフェラル通信用正電源                              |

| 2        | B6    | CSO             | AO                | 静電容量センサ出力/テスト出力2                          |

| 3        | C5    | VDD_D           | AO                | デジタル電源レギュレータ出力                            |

| 4        | C6    | XTO             | AO                | 水晶発振器出力                                   |

| 5        | D6    | XTI             | AI/DI             | 水晶発振器入力（テスト・モードでクロック用デジタル入力として使用）         |

| 6        | D5    | GND_D           | P                 | デジタル・グランド                                 |

| 7        | E4    | VDD_A           | AO                | アナログ電源レギュレータ出力                            |

| 8        | E6    | V <sub>DD</sub> | P                 | 外部正電源                                     |

| 9        | F6    | VDD_RF          | AO                | アンテナ・ドライバ用の電源レギュレータ出力                     |

| 10       | E5    | VDD_TX          | P                 | 送信回路用外部正電源                                |

| 11       | F5    | VDD_AM          | AO                | AM変調用のドライバ電源レギュレータ出力                      |

| 12       | F4    | GND_DR          | P                 | アンテナ・ドライバのグランド（ドライバのV <sub>SS</sub> と同電位） |

| 13       | F3    | RFO1            | AO                | アンテナ・ドライバ出力                               |

# 参考資料

表 2. ST25R3916 - VFQFPN32およびWLCSP36のピン割当て (続き)

| VFQFPN32 | WLCSP    | 名前                  | 種類 <sup>(1)</sup> | 説明                                         |

|----------|----------|---------------------|-------------------|--------------------------------------------|

| 14       | E3       | VDD_DR              | P                 | アンテナ・ドライバ用正電源入力                            |

| 15       | F2       | RFO2                | AO                | アンテナ・ドライバ出力                                |

| 16       | F1       | GND_DR              | P                 | アンテナ・ドライバのグランド (ドライバのV <sub>SS</sub> と同電位) |

| 17       | E2       | EXT_LM              | AO                | 外部負荷変調用のMOSゲート・ドライバ                        |

| 18       | E1       | AAT_A               | AO                | 可変容量コンデンサAAT_A用のAAT同調電圧                    |

| 19       | D1       | AAT_B               | AO                | 可変容量コンデンサAAT_B用のAAT同調電圧                    |

| 20       | D2       | I <sup>2</sup> C_EN | DI                | I <sup>2</sup> Cインターフェース・イネーブル             |

| 21       | C1、C2、C3 | VSS                 | P                 | グランド、ダイ基板の電位                               |

| 22       | B1       | RFI1                | AI                | レシーバ入力                                     |

| 23       | B2       | RFI2                | AI                | レシーバ入力                                     |

| 24       | A2       | AGDC                | AIO               | アナログ基準電圧                                   |

| 25       | A1       | CSI                 | AIO               | 静電容量センサ入力/テスト出力1                           |

| 26       | A3、B3、B4 | GND_A               | P                 | アナログ・グランド                                  |

| 27       | A4       | IRQ                 | DO                | 割り込み要求出力                                   |

| 28       | C4       | MCU_CLK             | DO                | MCU用クロック出力                                 |

| 29       | A5       | BSS                 | DI                | SPIイネーブル (アクティブLow)                        |

| 30       | D3       | SCLK                | DI                | SPIクロック/I <sup>2</sup> Cクロック               |

| 31       | D4       | MOSI                | DI                | SPIデータ入力                                   |

| 32       | B5       | MISO                | DO_T              | SPIデータ出力/I <sup>2</sup> Cデータ・ライン           |

| 33       | NA       | NA                  | P                 | サーマル・パッド                                   |

1. P: 電源ピン

AIO: アナログI/O、AI: アナログ入力、AO: アナログ出力

DI: デジタル入力、DIPD: プルダウン付きデジタル入力、DO: デジタル出力、DO\_T: トライステート・デジタル出力、DIO: 双方向デジタル信号

表 3. ST25R3917 - VFQFPN32のピン割当て

| VFQFPN32 | 名前              | 種類 <sup>(1)</sup> | 説明                                 |

|----------|-----------------|-------------------|------------------------------------|

| 1        | VDD_IO          | P                 | ペリフェラル通信用正電源                       |

| 2        | NC              | -                 | このピンは接続してはなりません。                   |

| 3        | VDD_D           | AO                | デジタル電源レギュレータ出力                     |

| 4        | XTO             | AO                | 水晶発振器出力                            |

| 5        | XTI             | AI/DI             | 水晶発振器入力 (テスト・モードでクロック用デジタル入力として使用) |

| 6        | GND_D           | P                 | デジタル・グランド                          |

| 7        | VDD_A           | AO                | アナログ電源レギュレータ出力                     |

| 8        | V <sub>DD</sub> | P                 | 外部正電源                              |

| 9        | VDD_RF          | AO                | アンテナ・ドライバ用の電源レギュレータ出力              |

| 10       | VDD_TX          | P                 | 送信回路用外部正電源                         |

| 11       | VDD_AM          | AO                | AM変調用のドライバ電源レギュレータ出力               |

# 参考資料

表 3. ST25R3917 - VFQFPN32のピン割当て (続き)

| VFQFPN32 | 名前                  | 種類 <sup>(1)</sup> | 説明                                         |

|----------|---------------------|-------------------|--------------------------------------------|

| 12       | GND_DR              | P                 | アンテナ・ドライバのグランド (ドライバのV <sub>SS</sub> と同電位) |

| 13       | RFO1                | AO                | アンテナ・ドライバ出力                                |

| 14       | VDD_DR              | P                 | アンテナ・ドライバ用正電源入力                            |

| 15       | RFO2                | AO                | アンテナ・ドライバ出力                                |

| 16       | GND_DR              | P                 | アンテナ・ドライバのグランド (ドライバのV <sub>SS</sub> と同電位) |

| 17       | NC                  | -                 | このピンは接続してはなりません。                           |

| 18       | NC                  | -                 | このピンは接続してはなりません。                           |

| 19       | NC                  | -                 | このピンは接続してはなりません。                           |

| 20       | I <sup>2</sup> C_EN | DI                | I <sup>2</sup> Cインタフェース・イネーブル              |

| 21       | VSS                 | P                 | グランド、ダイ基板の電位                               |

| 22       | RFI1                | AI                | レシーバ入力                                     |

| 23       | RFI2                | AI                | レシーバ入力                                     |

| 24       | AGDC                | AIO               | アナログ基準電圧                                   |

| 25       | NC                  | -                 | このピンは接続してはなりません。                           |

| 26       | GND_A               | P                 | アナログ・グランド                                  |

| 27       | IRQ                 | DO                | 割り込み要求出力                                   |

| 28       | MCU_CLK             | DO                | MCU用クロック出力                                 |

| 29       | BSS                 | DI                | SPIイネーブル (アクティブLow)                        |

| 30       | SCLK                | DI                | SPIクロック/I <sup>2</sup> Cクロック               |

| 31       | MOSI                | DI                | SPIデータ入力                                   |

| 32       | MISO                | DO_T              | SPIデータ出力/I <sup>2</sup> Cデータ・ライン           |

| 33       | NA                  | P                 | サーマル・パッド                                   |

1. P: 電源ピン

AIO: アナログI/O、AI: アナログ入力、AO: アナログ出力

DI: デジタル入力、DIPD: ブルダウン付きデジタル入力、DO: デジタル出力、DO\_T: トライステート・デジタル出力、DIO: 双方向デジタル信号

## 4 アプリケーション情報

### 4.1 電源投入シーケンス

このデバイスは、電源が供給された時点でパワーダウン・モードに移行し、すべてのレジスタの内容がデフォルト状態に設定されます。

チップの温度が接合部温度よりも低い状態で内部過熱保護機能が動作しないように、電源投入後およびSet Default（デフォルト設定）コマンドの実行後に、3バイトのフレームFCh/04h/10h（レジスタへのアクセス、レジスタ・アドレス、レジスタ値）を送信する必要があります。

このICの基本的な設定手順は以下のとおりです。

1. **IOコンフィギュレーション・レジスタ1**と**IOコンフィギュレーション・レジスタ2**を適切に設定します。

2. 内部電圧レギュレータを設定します。高いPSRRをシステムに実現するためにダイレクト・コマンドAdjust Regulators（レギュレータ調整）を使用することを推奨します。

3. AATを使用する場合は、チューニングの手順を実行します。

上記の手順を実行すると、デバイスを使用できるようになります。

### 4.2 動作モード

ST25R3916/7の動作モードは、**動作コントロール・レジスタ**の内容で定義します。電源投入時、このレジスタのすべてのビットが'0'に設定され、ST25R3916/7はパワーダウン・モードの状態になります。このモードでは、動作している電源がPORとバイアス電源の一部のみなので、AFEの静的消費電力が最小限になります。レギュレータ自体は無効化されています。

このモードでもSPI/I<sup>2</sup>Cは機能するため、必要なコンフィギュレーション・レジスタはすべて設定できます。このモードではPT\_memoryとFIFOにはアクセスできません。

enビット（**動作コントロール・レジスタ**のビット7）では、水晶発振器、レギュレータ、AAT制御出力ピンを制御します。このビットをセットすると、デバイスはレディ・モードに移行し、水晶発振器とレギュレータが有効になります。発振器の振幅と周波数が安定すると、それが割り込みによってマイクロコントローラに通知されます。このモードで、PT\_memoryとFIFOにアクセスできるようになります。

レシーバとトランスマッタの両ブロックは互いに独立して有効になるので、一方をオフにしたまま、もう一方を動作状態にすることができます（rx\_enビットとtx\_enビットで制御）。この動作形態は、タグからの応答を想定していない状態で、リーダのフィールドは維持する必要がある場合に使用できます。別の例として、受信モード構成で実行するNFCIP-1アクティブ通信があります。この通信では、一方のイニシエータによってRFフィールドが生成され、他方は受信動作のみとなります。

**動作コントロール・レジスタ**のwuビットをアサートし、他のビットを'0'に設定すると、ST25R3916/7はウェイクアップ・モードに移行します。このモードは、カードの存在を低消費電力で検出する際に使用します。このモードでは、低消費電力RC発振器と、レジスタで設定が可能なウェイクアップ・タイマを使用して、定期的な測定の実行スケジュールを設定します。あらかじめ規定された基準との差異が検出されると、マイクロコントローラをウェイクアップする割り込みが送信されます。ウェイクアップをトリガするために、静電容量センサ、位相測定、振幅測定を使用できます。

### 4.2.1 トランスマッタ

トランスマッタは、同一のプッシュプル・ドライバ・ブロックを2つ備えており、それぞれRFO1ピンとRFO2ピンに接続されています。これらのドライバは、外付けアンテナのLCタンクを差動構成で駆動します。2つのドライバの一方のみを動作状態にすることもできます。[IOコンフィギュレーション・レジスタ1](#)のsingleビットをセットし、どちらのRFO/RFIを使用するかをrfo2ビットで指定します。

#### 出力抵抗

各ドライバは、バイナリ重み付けした値の出力抵抗を備えた8つのセグメントで構成されています。MSBのセグメントのオン抵抗値は $4\Omega$ （代表値）です。すべてのセグメントをオンにしたときの出力抵抗値は $2\Omega$ （代表値）です。通常は、すべてのセグメントがオンになり、通常状態での送信レベル（非変調）が規定されています。高インピーダンスのドライバを持つ回路を駆動するために、非変調レベルを駆動するときに特定のMSBセグメントをオフに切り換えることもできます。

[送信ドライバ・レジスタ](#)のd\_res<3:0>ビットは、通常送信時の抵抗値を規定します。デフォルト設定は、使用できる最小抵抗値です。

シングル・ドライバ・モードを使用すれば、アンテナのLCタンク部品の個数、つまりコストが半減しますが、出力電力も低下します。シングル・モードで2つのRFO出力に2つのアンテナのLCタンクを接続し、[IOコンフィギュレーション・レジスタ1](#)のrfo2ビットを制御して、これら2つを多重化することもできます。

データを送信するには、トランスマッタの出力レベルを変調する必要があります。AM変調とOOK変調の各方式に対応しています。この変調の種類は、[モード設定レジスタ](#)のtr\_amビットで設定します。

#### ドライバでの送信変調

OOK変調の場合（ISO14443Aなど）、トランスマッタのドライバではキャリア周波数の駆動が停止します。その結果、アンテナのLCタンクの振幅は減衰し、その時定数はLCタンクのQ値で決まります。

AM変調の場合（ISO14443Bなど）は、変調状態を駆動するドライバの電源電圧として、追加のレギュレータが供給する電圧 $V_{DD\_AM}$ を使用します。

AM変調のレベルは、[送信ドライバ・レジスタ](#)のam\_mod3:0ビットで設定します。

以下のプロトコルでは、AM変調を手動で有効にして、適切な変調レベルを設定する必要があります。

- ISO14443B

- FeliCa

- ISO15693（OOK以外の場合）

- NFCIP-1 212および424 kb/sのイニシエータまたはアクティブ・ターゲット

[送信ドライバ・レジスタ](#)では、適用する規格に応じた変調指数を5%~30%の範囲で設定できます。

#### パッシブ負荷変調

ST25R3916/7では、次の2種類の方法でパッシブ負荷変調を実現できます。

- 内部ドライバの負荷変調

- 外付けのMOSトランジスタとダイオードでアンテナの負荷を発生する負荷変調

ドライバによる負荷変調はIm\_dri、外付けMOSによる変調はIm\_extの各オプション・ビットでそれぞれ選択します。

通常、内部ドライバによる負荷変調と外付け負荷による変調は、いずれか一方を排他的に使用すべきですが、このデバイスでは両者を同時に使用して変調することも可能です。

ドライバによる負荷変調は、そのインピーダンスの変化に基づいて実行されます。通常、非変調状態に高インピーダンスを使用し、変調状態ではインピーダンスが低下するようにします。これにより、パッシブ・タグ変調と同様の変調を行うことができます。非変調状態に低インピーダンス、変調状態に高インピーダンスを使用することでドライバ負荷変調の極性を反転した設定にすることもできます。

非変調状態と変調状態の出力インピーダンスは、それぞれpt\_res3:0オプション・ビットとptm\_res3:0オプション・ビットで設定します。

外付けのMOSトランジスタとダイオードによる負荷変調は、Im\_extオプション・ビットで設定します。この場合、デジタル化した負荷変調信号（848kHzのサブキャリアまたは424/212kHzの変調信号）でEXT\_LMピンが駆動されます。EXT\_LMを使用して、外付けの変調MOSのゲートを駆動します。外付け負荷による変調の極性反転は、Im\_ext\_polビットで設定します。

pt\_res<3:0>の各ビットとptm\_res<3:0>の各ビットは、パッシブ・ターゲット・モード（reg 03h）に移行する前に設定しておく必要があります。パッシブ・ターゲット・モードでは、クロックが得られる状態（FDTも含めたPTデータ送信期間）でのみ送信ドライバ経由でそれらの抵抗値が負荷として見えるからです。

## トランスマッタの低速立ち上げ

トランスマッタを有効にすると、最大出力でアンテナのLCタンクが駆動されます。アンテナが放射するフィールドの立上がり速度はアンテナのLCタンクのQ値で決まります。

しかし、リーダ・システムの中には、リーダを有効にした後、そのフィールドを長い遷移時間を経て立ち上げることを必要とするものがあります。STIF（Syndicat des transports d'Ile de France）の仕様では、フィールドが10%から90%まで立ち上がるまでに要する遷移時間を10μs以上とすることを規定しています。

ST25R3916/7は、この機能に対応しています。このような遷移時間を実現するために、トランスマッタが無効なときは安定化電圧VDD\_RFを低くし、トランスマッタを有効にした時点で再度フィールドを立ち上げています。遷移時間の代表値は、3V電源で15μs、5V電源で20μsです。

低速遷移を実装する手順は次のとおりです。

- トランスマッタを無効にするときに**IOコンフィギュレーション・レジスタ2**のslow\_upビットを'1'に設定します。この状態を2ms以上維持してVDD\_RFの放電を待ちます。

- トランスマッタを有効にすると、その出力が低速で立ち上がります。

- コマンドを送信する前に、slow\_upの設定を'0'に戻します。

### 4.2.2 レシーバ

レシーバは、13.56MHzのキャリア周波数に重畠されたタグによるサブキャリア変調を復調します。サブキャリア信号のAM/PMまたはI/Qの復調、増幅、帯域通過フィルタ処理、デジタル化を実行します。さらに、RSSI測定、自動ゲイン制御（AGC）、スケルチ機能も実行します。

受信チェーンには、AMとPMの復調用に独立した2つのチャネルがあります。両方のチャネルが有効な場合、受信フレーミングを実行するチャネルはレシーバのロジックによって自動的に選択されます。[動作コントロール・レジスタ](#)のrx\_enビットを'1'に設定するとレシーバがオンになります。

[動作コントロール・レジスタ](#)には、rx\_chnビットとrx\_manビットもあります。これらは、復調チャネルを両方とも有効にするか、どちらか一方のみを有効にするかを設定します。rx\_manビットは、両方のチャネルが有効な場合に、チャネルの選択モード（自動または手動）を設定します。ch\_selビットは、デコードに使用するチャネルを選択します。

表 4. 受信チャネルの選択

| rx_chn | rx_man | ch_sel | 選択される受信チャネル    |

|--------|--------|--------|----------------|

| 0      | 0      | x      | 自動選択           |

| 0      | 1      | 0      | AMチャネルまたはIチャネル |

| 0      | 1      | 1      | PMチャネルまたはQチャネル |

| 1      | x      | 0      | AMチャネルまたはIチャネル |

| 1      | x      | 1      | PMチャネルまたはQチャネル |

図7. レシーバのブロック図

## 復調段

初段は、HFフィールド・キャリアに重畠された、タグのサブキャリア応答信号を復調します。AM復調には次の2種類のブロックが実装されています。

- ピーク検出器

- AM/I復調ミキサまたはPM/Q復調ミキサ

どちらの復調器を使用するかは、[レシーバ・コンフィギュレーション・レジスタ2](#)のamd\_selビットで選択します。

ピーク検出器は、ピーク・フォロワを使用してAM復調を実行します。正負両方のピークを追跡することで、同相信号をすべて除去します。ピーク検出器の復調ゲインGは0.7で、入力は復調器のRFI1入力からのみ取得します。

AM復調ミキサは、両方のレシーバ入力 (RFI1とRFI2) を同期整流します。この復調ミキサのゲインGは0.55です。PM復調にもミキサを使用します。PM復調ミキサは、1%の位相変化に対して60mVの差動信号を出力します (16.67mV/°)。

I/Q復調回路は、水晶発振器から生成したローカル発振器 (LO) 信号に90°の位相シフトを適用した信号で駆動する2つのミキサ回路で構成されます。2つのミキサの出力は、2つの等価なベース・バンド受信チェーンとデコード・ロジックに接続されています。

### フィルタ処理とゲイン段

レシーバ・チェーンは、帯域通過フィルタ特性を備えています。このフィルタ処理は、キャリア周波数、低周波ノイズ、DC成分を除去し、サブキャリア周波数が通過するように最適化されています。フィルタ処理とゲインの回路は3段構成です。初段と終段に1次のハイパス特性、中間段に2次のローパス特性を設定しています。

ゲイン特性とフィルタ処理特性は、アプリケーションに応じ、[レシーバ・コンフィギュレーション・レジスタ1](#)（フィルタ処理）、[レシーバ・コンフィギュレーション・レジスタ3](#)（初段の1次ゲイン）、[レシーバ・コンフィギュレーション・レジスタ4](#)（2段目と3段目のゲイン）に書き込むことで最適化できます。

初段のゲインは約20dBですが、2.5dB単位で6段階に低くすることができます。特殊なブースト・モードも用意されています。このモードを使用すると、最大ゲインがさらに5.5dB高くなります。初段のゲインを変更する手段は、[レシーバ・コンフィギュレーション・レジスタ3](#)への書き込みのみです。このレジスタのデフォルト設定では、最低ゲインが得られるようになっています。初段のデフォルトのゼロ点は60kHzですが、[レシーバ・コンフィギュレーション・レジスタ1](#)のオプション・ビットに書き込むことで、この値も40kHzまたは12kHzまで低くすることができます。オプション・ビットz600kをセットすることで、初段を600kHzの2次ハイパス・フィルタとして再設定することもできます。初段と3段目のゼロ点は、両方に共通の制御ビット（[表 6](#)参照）で制御します。

表 5. ローパス制御

| rec1<5>lp2 | rec1<4>lp1 | rec1<3>lp0 | -1 dBポイント |

|------------|------------|------------|-----------|

| 0          | 0          | 0          | 1200 kHz  |

| 0          | 0          | 1          | 600 kHz   |

| 0          | 1          | 0          | 300 kHz   |

| 1          | 0          | 0          | 2 MHz     |

| 1          | 0          | 1          | 7 MHz     |

| 上記以外       |            |            | 未使用       |

表 6. 初段と3段目のゼロ点設定

| rec1<3>z600k | rec1<2>h200 | rec1<1>h80 | rec1<0>z12k | 初段のゼロ点 | 3段目のゼロ点 |

|--------------|-------------|------------|-------------|--------|---------|

| 0            | 0           | 0          | 0           | 60kHz  | 400kHz  |

| 0            | 1           | 0          | 0           |        | 200kHz  |

| 0            | 0           | 1          | 0           | 40kHz  | 80kHz   |

| 0            | 0           | 0          | 1           | 12kHz  | 200MHz  |

| 0            | 0           | 1          | 1           |        | 80kHz   |

| 0            | 1           | 0          | 1           | 600kHz | 200MHz  |

| 1            | 0           | 0          | 0           |        | 400kHz  |

| 1            | 1           | 0          | 0           | 600kHz | 200MHz  |

| その他          |             |            |             |        | 未使用     |

2段目と3段目のゲインは23dBで、3dB単位で6段階に低くすることができます。これら2段のゲインは、AGCとスケルチによるループで制御できるほか、[レシーバ・コンフィギュレーション・レジスタ4](#)を使用して手動で設定することもできます。AGC、スケルチ、RSSIブロックを初期化するには、ダイレクト・コマンドReset RX Gain（受信ゲイン・リセット）を送信する必要があります。このコマンドを送信すると、現在のスケルチ設定がクリアされ、手動で低い値に設定したゲイン値が[レシーバ・コンフィギュレーション・レジスタ4](#)からロードされます。2段目は、2次のローパス・フィルタ特性を備え、[レシーバ・コンフィギュレーション・レジスタ1](#)のlp2ビットとlp0ビットにより、サブキャリア周波数に応じて通過帯域を調整できます。各種設定に対する-1dBの遮断周波数を表 5に示します。

## デジタル化段

デジタル化段は、レシーバから入力されるサブキャリア信号をデジタル化します。このデジタル信号は、レシーバのフレーミング・ロジックで処理されます。デジタル化段は、調整可能なデジタル化ウィンドウによるウインドウ・コンパレータで構成されています。このウインドウは-3dB単位で5段階に調整でき、その調整範囲は±33mV～±120mVです。デジタル化ウィンドウの調整は、AGCおよびスケルチのループで制御されます。また、[レシーバ・コンフィギュレーション・レジスタ4](#)によって手動で設定することもできます。

## AGC、スケルチ、およびRSSI

前述のとおり、2段目と3段目にあるゲイン段のゲインおよびデジタル化段のウインドウは、AGCとスケルチのループで制御されています。ここでは11通りの設定が可能です。デフォルト状態では、デジタイザのウインドウが最小、ゲインが最大に設定されています。最初の4つのステップでは、デジタイザのウインドウが3dB単位で大きくなり、次の6つのステップでは、さらに2段目と3段目のゲインが同様に3dB単位で低くなります。スケルチとAGCの開始設定の初期値は[レシーバ・コンフィギュレーション・レジスタ4](#)で設定します。ゲインを低くしたレジスタには、スケルチやAGCで設定された実際のゲインの状態と、[レシーバ・コンフィギュレーション・レジスタ4](#)での初期設定が表示されます。

## スケルチ

この機能は、ノイズの多い環境での動作を想定して設計されています。ノイズは、誤ってタグ応答の開始と判断される可能性があり、デコード・エラーの原因となります。

自動スケルチは、[レシーバ・コンフィギュレーション・レジスタ2](#)のsqm\_dynオプション・ビットによって有効になります。送信完了後18.88μsで自動的に動作を開始し、[スケルチ・タイマ・レジスタ](#)に設定された値にマスク受信タイマ（MRT）が達すると停止します。このモードは、タグ応答が想定されていない期間（MRTの期間）にタグ処理によって発生するノイズの抑制を主な目的としています。

スケルチは、スケルチ比が1と6の2つのモードで動作でき、これらのモードは[レシーバ・コンフィギュレーション・レジスタ2](#)のpulz\_61ビットで選択します。

スケルチ比1とは、メイン・デジタイザからのサブキャリア信号を観測し、その遷移の頻度が少なくなるようにシステム・ゲインを低くすることを意味します。50μsの期間に、このサブキャリア信号出力に3回以上遷移が発生した場合は、ゲインを3dB低くし、次の50μsで引き続き出力を観測します。50μs内の遷移が2回以下になるか、ゲイン低下幅が最大値に達するまで、この手順を繰り返します。このモードでは、デジタル化したサブキャリア出力を使用するプロトコルを主に想定しています。

スケルチ比6とは、デジタル化ウィンドウの6倍のウインドウを設定したウインドウ・コンパレータを使用して、上記と同様に遷移の頻度を観測して低くします。このモードでは、コリレータからの出力を使用するプロトコル（ISO-A、ISO-Bの相関受信）を想定しています。

スケルチ動作で得られたゲイン設定は、ダイレクト・コマンドReset RX Gain（受信ゲイン・リセット）（受信ゲイン・リセット）を送信することでクリアできます。

### AGC

AGC（自動ゲイン制御）は、レシーバ・チェーンとデジタル化段が飽和しないように、ゲインを低くする機能です。ゲインを適切に調整すれば、復調プロセスもシステム・ノイズの影響を受けにくくなります。

AGCのロジックは、rx\_on信号をHighにアサートすると動作を開始し、rx\_on信号をLowにリセットするときリセットされます。rx\_onビットがHighからLowに遷移するときに、レシーバのゲインの状態が[ゲイン低減状態レジスタ](#)に格納されます。後でこのレジスタを読み出すことで、前回の受信で使用されたゲイン設定の情報を得ることができます。

AGCシステムは、ウィンドウ・コンパレータおよび3または6に設定できるAGC比で構成されます。例えば、AGC比を6に設定した場合、このコンパレータのウィンドウは、データ・デジタル化ウィンドウの6倍になります。AGC機能が有効になると、出力に遷移がまったく見られなくなるまでゲインが低下します。このような手順により、デジタル化ウィンドウ・コンパレータが、そのウィンドウの最大6倍の大きさの入力で動作できます。

AGC比を3に設定した場合は、デジタル化ウィンドウ・コンパレータへの入力は、そのウィンドウの最大3倍に設定されます。

AGCの動作は、[レシーバ・コンフィギュレーション・レジスタ2](#)のagc\_en、agc\_m、agc\_alg、agc6\_3の各コントロール・ビットで制御します。

agc\_mビットは、AGCのモードを設定します。設定できるモードは2種類です。1つは、rx\_on信号がHighであるかぎり、受信プロセスの全期間にわたってAGCが動作するモードです。もう1つは、サブキャリアの最初の8パルスの間だけAGCが有効になるモードです。

agc\_algビットでは、2つのAGCアルゴリズムのいずれかを選択できます。AGCの動作を、プリセット（デジタイザのウィンドウとゲインを最大に設定）によって開始するか、リセット（デジタイザのウィンドウを最小、ゲインを最大に設定）によって開始するかを選択します。短いSOFを使用するプロトコル（106kbpsのISO14443Aなど）では、より高速な、プリセット設定によるアルゴリズムの使用をお勧めします。

### コリレータ

コリレータは、フィルタ処理された受信サブキャリアと848kHzとの相関を測定します。この相関測定の目的は、848kHzにおけるシステム感度を最大にすると同時に、他の周波数を除去することです。コリレータには、AMチャネル（またはIチャネル）用とPMチャネル（またはQチャネル）用の2つがあります。

コリレータは、[コリレータ・コンフィギュレーション・レジスタ1](#)と[コリレータ・コンフィギュレーション・レジスタ2](#)で設定します。

### RSSI

レシーバでは、両チャネルでのRSSI（受信信号強度インジケータ）も測定します。RSSI測定は、rx\_onの立上がりエッジから開始します。rx\_on信号がHighの期間に測定を継続し、rx\_onがLowになると測定値が保持されます。初期値の0から増加方向にのみ測定値が変化できるピーク・ホールド型です。AGCによってゲインが低下するたびにRSSI測定はリセットされ、0から再開されます。RSSIの測定結果は4ビット値であり、[RSSI表示レジスタ](#)を読み出すことで確認できます。

LSBの1ビットは2.8dBに相当し、最大値はDh (13d) です。

RSSI測定はピーク・ホールド型なので、測定結果は信号強度の変化に追随しません（最大値のみが保持されます）。RSSIの変化を追跡するには、ダイレクト・コマンド[Clear RSSI \(RSSIクリア\)](#)によってRSSIの各ビットをリセットし、測定を再開します。

## クロック抽出回路

クロック抽出回路は、RFI1とRFI2の差動信号を観測し、受信RFフィールドと同期したクロック信号を出力します。抽出したクロックは同期復調、フレーム遅延時間の補正、パッシブ送信時のデータ・タイミングの補正に使用されます。クロック抽出回路は、最小で60mV<sub>PP</sub>の入力信号まで動作します。

## 4.2.3 アンテナ・チューニング

ST25R3916/7は、外付けの可変コンデンサによるアンテナ・チューニングに対応しています。整合回路の所定の位置に可変コンデンサを接続し、制御出力ピン（AAT\_A、AAT\_B）のいずれかにチューニング制御電圧を接続します。

整合回路では、複数の可変コンデンサを直列構成または並列構成とすることができます。さまざまな構成例に関する情報は、アプリケーション・ノートAN5322（[www.st.com](http://www.st.com)より入手可能）に記載されています。

位相と振幅の検出ブロックを使用して共振周波数を確認します。マイクロコントローラのアルゴリズムで測定結果を評価し、AAT\_AとAAT\_Bの各出力ピンのチューニング電圧を調整します。この調整では、マイクロコントローラのファームウェアに記述された手順に従ってアンテナ・チューニング・コントロール・レジスタ1とアンテナ・チューニング・コントロール・レジスタ2を使用します。

AAT\_AとAAT\_Bピンの電圧は、enおよびaat\_enのオプション・ビットが両方セットされている場合に、アンテナ・チューニング・コントロール・レジスタ1とアンテナ・チューニング・コントロール・レジスタ2に従って動的に設定されます。

aat\_en=1、en=0の場合は、AAT\_AとAAT\_Bの電圧が1.5V ~ 2.2Vの範囲の固定値に設定されます（通常は1.9V）。

## 4.2.4 静電容量センサ

静電容量センサにより、2つのパッド間の静電容量を測定できます。この機能の使用例として、ウェイクアップ・モードや低消費電力カード検出があります。

静電容量測定系は、2つの電極から構成されます。一方は数百kHz範囲の固定周波数で電界を放射する励起電極（CSO）、もう一方は、検出電極（CSI）です。検出電極に生成された電荷量が、2極間の静電容量を表します。静電容量センサの電極は、対グランドの寄生容量（最大25pF）と入力リード抵抗（最大1MΩ）を許容できるように設計されています。

励起電極の周波数で検出電極に生成された電荷を同期整流回路で検出します。これにより、干渉を大幅に除去でき、寄生容量（励起電極を除くすべてのノードとの寄生容量）に対しても高い耐性が得られます。同期整流回路の出力は、励起電極と検出電極間の静電容量に線形比例するDC電圧です。このDC出力電圧を、絶対モードのA/Dコンバータで変換します。結果は、A/Dコンバータ出力レジスタに格納されます（セクション 2.2.5: A/Dコンバータも参照）。

図 8. 静電容量センサのブロック図

導電性の物体（人の手やタグ・アンテナの巻き線）が2つの電極に接近すると、励起電極と検出電極間の静電容量が変化します。これらの物体が2極間に結ぶ経路上で部分的にコンダクタンスとして機能することで、2極間の距離が「短く」なるからです。

静電容量の測定は、ダイレクト・コマンド [Measure Capacitance](#)（静電容量測定）を送信することで開始します。ST25R3916/7は、自動的にウェイクアップして定期的に静電容量を測定するように設定することもできます。格納された基準値または前回までの測定値の平均と、この測定結果を比較し、その差が事前設定値よりも大きい場合、IRQがトリガされ、コントローラをウェイクアップします（[セクション 4.2.5](#)も参照）。

静電容量センサのゲインは、[静電容量センサ・コントロール・レジスタ](#)で調整できます。デフォルトのゲインは2.8V/pF（代表値）、最大ゲインは6.5V/pF（代表値）です。A/Dコンバータの LSB は約7.8mVに相当するため、デフォルトのゲインでは、2.8fF/LSB（最大ゲインの場合は1.2fF/LSB）の感度が得られます。

静電容量の測定時間は200 $\mu$ s、測定中の消費電流は1.1mA（代表値）です。例えば、ウェイクアップ・モードで100msごとに静電容量を測定した場合、平均消費電流は5.8 $\mu$ Aになります（そのうち、3.6 $\mu$ Aはウェイクアップ・モードのスタンバイ電流）。

### 静電容量センサの補正

静電容量センサには、CSIとCSO間の寄生容量を内部補償する補正回路が組み込まれています。これにより、容量変化に関する情報の測定範囲を全域にわたって確保できます。補正の制御には5ビットを使用します。補正の最小単位は0.1pF、利用できる補正範囲は3.1pFです。[静電容量センサ・コントロール・レジスタ](#)に書き込むことによる手動補正、またはダイレクト・コマンド [Calibrate Capacitive Sensor](#)（静電容量センサ補正）を送信することによる自動補正が可能です。このコマンドの状態と、得られた補正值は[静電容量センサ表示レジスタ](#)に格納されます。

静電容量センサが水晶発振器やリーダ磁界と干渉しないようにして、結果の再現性を確保するため、静電容量の測定と補正是、パワーダウン・モードでのみ実行することを強く推奨します。

## 4.2.5 ウェイクアップ・モード

[動作コントロール・レジスタ](#)のwuビットをアサートし、他のビットを'0'に設定すると、ST25R3916/7はウェイクアップ・モードに移行します。このモードは、カードを低消費電力で検出するときに使用します。ST25R3916/7で可能な動作形態として、静電容量センサ、位相測定、振幅測定の3種類があります。内蔵された32kHzの低消費電力RC発振器と、レジスタで設定が可能なウェイクアップ・タイマを使用して、定期的な測定のスケジュールを設定します。

通常、カードの存在はポーリングによって検出します。ポーリングでは、リーダのフィールドを定期的にオンにし、RFコマンドを使用してコントローラでカードの有無を確認します。この手順は、コマンドを発行できるようになるまでリーダのフィールドを5msの間、オンにする必要があるため、多くの電力を消費します。

低消費電力のカード検出では、カードが存在することによってリーダの環境に発生する変化を測定します。変化が検出されると、コントローラに割り込みが送信されます。これによって、コントローラは通常のポーリング・ループを実行できます。

ウェイクアップ・モードのST25R3916/7では、設定されたリーダ環境測定を定期的に実行し、設定された基準値との差が検出されると、コントローラにIRQを送信します。

### カード検出

リーダのアンテナ・コイルにカードが接近することによって、アンテナのLCタンクで信号の位相と振幅が変化します。位相または振幅を測定するためにリーダでフィールドのアクティブ化に要する時間は、プロトコル実行コマンドの送信に必要なアクティブ化時間に比べてきわめて短く、最大でも20 $\mu$ sにすぎません。

また、測定中の電力レベルも、通常動作に比べて低く抑えられます。結合効果を生成するためにカードに電源を供給する必要がないからです。放射される電力は、RFO ドライバの抵抗値を変更することで低減できます。

静電容量センサは、2つの電極間の寄生容量の変化を検出します。この容量変化は、カードのアンテナまたはカードを持っている手によって発生します ([セクション 2.2.6: 静電容量センサ](#) 参照)。

レジスタの32hから3Ehは、ウェイクアップの設定と表示専用です。[ウェイクアップ・タイマ・コントロール・レジスタ](#)は、ウェイクアップ・モード設定のメイン・レジスタです。連続検出の間隔に対するタイムアウト時間や、どの測定を実行するかを、このレジスタで選択します。タイムアウトは10ms ~ 800msの範囲で設定でき、デフォルト値は100 msです。

レジスタの33hから3Dhは、使用可能な3種類の測定を設定し、測定結果を格納します。測定方法ごとに4つのレジスタが使用されます。

測定値と基準値の差が、設定された閾値を超えるとIRQが送信されます。基準値には、以下の2種類の設定方法があります。

- ST25R3916/7が、これまでの測定値に基づいて基準値を計算する方法

(自動平均化)

- コントローラで基準値を決定し、レジスタに格納する方法

4つのレジスタのうち、1番目は振幅測定コンフィギュレーション・レジスタです。このレジスタでは、IRQをトリガする基準との差、基準値の定義方法、自動平均化を使用する場合の前回の測定結果に対する重みを設定します。2番目のレジスタは、コントローラで基準値を設定する場合に、その値を格納します。3番目と4番目のレジスタは表示用です。3番目には自動平均化による基準値、4番目には前回の測定結果がそれぞれ格納されます。

実際にウェイクアップ・モードに移行する前に、ウェイクアップ・モード・コンフィギュレーション・レジスタを設定する必要があります。ウェイクアップ・モードが有効なまま、ウェイクアップ・モード設定を変更すると、予期しない動作の原因となることがあります。

### 自動平均化

自動平均化では、測定が終了するたびに基準値を再計算します。この計算には、最新の測定値、これまでの基準値、重みを使用します。新しい基準値の計算には、次の式を使用します。

$$\text{新基準} = \text{旧基準} - (\text{旧基準} - \text{測定値}) / \text{重み}$$

十分な精度が得られるように、計算は10ビットで実行されます。

自動平均化のプロセスは、デバイスの初期化後（電源投入後または[Set Default（デフォルト設定）](#)コマンドの実行後）、はじめてウェイクアップ・モードに移行したときに初期化されます。初期値は、測定基準レジスタ（例えば[振幅測定基準レジスタ](#)）の内容が0でなければ、そこから取得します。このレジスタの内容が0の場合は、最初の測定結果を初期値とします。

すべての測定コンフィギュレーション・レジスタには、割り込み生成の要因となる測定値を平均の計算に算入するかどうかを設定するビットがあります（[振幅測定基準レジスタ](#)のam\_aamビットなど）。

### 4.2.6 水晶発振器

27.12MHzの水晶振動子による水晶発振器の動作は、[動作コントロール・レジスタ](#)のenビットを'1'に設定すると有効になります。発振器の振幅が十分に大きくなつたとき、つまり周波数が安定すると、それが割り込みによってマイクロコントローラに通知されます（[メイン割り込みレジスタ](#)参照）。

発振器の状態は、[補助表示レジスタ](#)のosc\_okビットによって確認できます。発振器の周波数が安定すると、このビットが'1'に設定されます。

この発振器は、制御電流源によって給電されるインバータ段を基本としています。バイアス電流をフィードバック・ループで制御して、XTIピンの振幅を安定した1V<sub>PP</sub>に維持します。リーダの高速起動を可能にするため、発振器の振幅が750mV<sub>PP</sub>を超えた時点で割り込みが送信されます。

1/2の分周によって、デューティー・サイクルを50%とした13.56MHzの信号を実現しています。これにより、PW歪みが発生せず、トランスマッタの性能向上が望めます。

この発振器の出力は、クロック信号出力ピンMCU\_CLKの駆動にも使用されます。このクロックは外部マイクロコントローラで使用できます。MCU\_CLKピンは[IOコンフィギュレーション・レジスタ2](#)で設定します。

### 4.2.7 タイマ

ST25R3916/7は、各種タイマを搭載しているため、コントローラでカウンタを実行する必要があります。これにより、コントローラ・コードの実装や他のコントローラへの移植に要する工数を削減できます。

すべてのタイマに、それぞれに関連する1つ以上のコンフィギュレーション・レジスタが用意され、そこでタイムアウト時間や各種動作モードを設定できます。これらのコンフィギュレーション・レジスタは、それに対応するタイマが動作していないときに設定する必要があります。タイマが有効な状態でその設定を変更すると、予期しない動作の原因となることがあります。

すべてのタイマは、ダイレクト・コマンド[Stop All Activities（全動作停止）](#)によって停止します。

#### マスク受信タイマ（MRT）

このタイマがリーダ・モードで動作していると、送信完了後、タグからの応答が想定されない期間はrx\_on信号がLowに保持され、レシーバの動作とフレーミング・ロジックの受信プロセスがブロックされます。マスク受信タイマの動作中は、スケルチを有効にしていればスケルチが自動的にオンになります。MRTではIRQを生成しません。

MRTのタイムアウトは[マスク受信タイマ・レジスタ](#)で設定します。データ送信の完了時（EOFの終端）にMRTは自動的にカウントを開始します。

また、ダイレクト・コマンドStart Mask-receive timer（マスク受信タイマ起動）でトリガすることもできます。その場合、[スケルチ・タイマ・レジスタ](#)の設定に応じてスケルチが有効になります。

NFCIP-1のアクティブ・イニシエータ、アクティブ・ターゲット、パッシブ・ターゲット通信モードでは、相手側デバイスがフィールドを形成し、外部フィールド検出器のI\_eon信号がオンになるとMRTがカウントを開始します。

MRTは、mrt\_stepオプション・ビットの設定により、NFCIP1に必要な長時間のカウントにも対応できます。このビットは、fc/64とfc/512の間でステップ・サイズを切り替えます。

MRTは、低消費電力の初期NFCターゲット・モードでもカウントを開始します。イニシエータのフィールドが検出されると、コントローラでは、27kHzのRC発振器、レギュレータ、水晶発振器、レシーバ、MRTをオンにします。MRTがタイムアウトした時点で、レシーバ出力の観測が始まり、イニシエータのメッセージ開始を検出します。

低消費電力の初期NFCターゲット・モードが適切に動作するには、mrt\_step = 1を使用する必要があります。水晶発振器が安定するまでは、27kHzのRC発振器がMRTのクロック源として使用されます。これにより、水晶発振器がまだ動作していない場合でも、設定時間に対して、実際のMRT時間を良好な近似値として扱うことができます。

## 応答なしタイマ（NRT）

このタイマの目的は、送信の終了から一定の設定時間内に応答が検出されるかどうかを観測することです。このタイマがタイムアウトして生成される割り込みイベントは、[タイマ/NFC割り込みレジスタ](#)のI\_nreフラグによって通知されます。

NRTは[応答なしタイマ・レジスタ1](#)と[応答なしタイマ・レジスタ2](#)に書き込むことで設定します。動作オプションは、[タイマ/EMVコントロール・レジスタ](#)のnrt\_envビットとnrt\_stepビットの設定によって定義します。

NRTは、送信の完了時に自動的にカウントを開始します。

nrt\_stepビットは、応答なしタイマのカウント時間単位を設定します。64/fc (4.72μs) と4096/fcを選択でき、それぞれ最大で309msと19.8sのタイムアウトに対応します。

nrt\_envビットは、タイマの動作モードを設定します。

- このビットを'0'に設定すると（デフォルト・モード）、応答開始が検出されずにNRTがタイムアウトしたときにIRQが生成されます。さらに、レシーバを無効化するためにrx\_onがLowに設定されます。この逆の場合、つまりタイムアウト前にタグの応答開始が検出された場合、タイマは停止し、IRQは生成されません。

- このビットを'1'に設定した場合、タイマがタイムアウトすると無条件でIRQが生成されます。また、ダイレクト・コマンドStop all activities（全動作停止）で停止することもありません。これは、タグ応答が検出されたかどうかに関係なくIRQが生成されることを意味します。タイムアウトの間にタグ応答が処理されていた場合、その他の動作は実行されず、そのタグ応答は通常どおり受信されます。この逆の場合、つまりタグ応答が処理されていなかった場合は、レシーバが無効化されます。

NRTは、Start No-response timer（応答なしタイマ開始）コマンドによる起動も可能です。このコマンドは、応答なしタイマ・コントロール・レジスタに設定された範囲よりも長いタイムアウトをNRTに設定することを目的としています。このコマンドをタイマの動作中に送信すると、タイマはリセットされてからカウントを開始します。

応答なしタイマは、ダイレクト・コマンドのStop No-response Timer（応答なしタイマ停止）またはStop All Activities（全動作停止）によって停止できます。タイマは停止し、IRQは送信されません。これらのコマンドは、受信があるために応答なしタイマが停止しないときに、nrt\_emvモードで使用することを想定しています。

NFCIP-1アクティブ通信モードの場合、NRTの役割は、通常のリーダ・モードにおける動作と同じになります。応答開始が検出されずにNRTがタイムアウトすると、IRQが生成され、レシーバが無効化されます。ここでは以下の2つのモードを使用できます。

- nrt\_nfc = 0

- デバイスの送信フィールドがオフに切り替わると、汎用タイマを使用してカウントが開始されます。

- この動作は、アクティブ・イニシエータとターゲット・モードおよびビット・レート検出モードで使用できます。

- nrt\_nfc = 1

- ピア・フィールドがオンに切り替わると、タイマがカウントを開始します。

- この動作は、アクティブ・イニシエータおよびアクティブ・ターゲット・モードで使用できます。

ビット・レート検出モードでは、ピア・フィールドがオンに切り替わってもタイマのカウントが開始されません。ビット・レート検出モードからアクティブ・ターゲット・モードに遷移する場合、マイクロコントローラでデバイスをアクティブ・ターゲット・モードに再構成してからフィールドをオンにする必要があるからです。

NFCIP-1パッシブ・ターゲット・モードでは、応答なしタイマの機能は不要なので、自動的にカウントが開始されることはありません。

### PPON2タイマ

このタイマは、リーダ・モードでは使用されません。

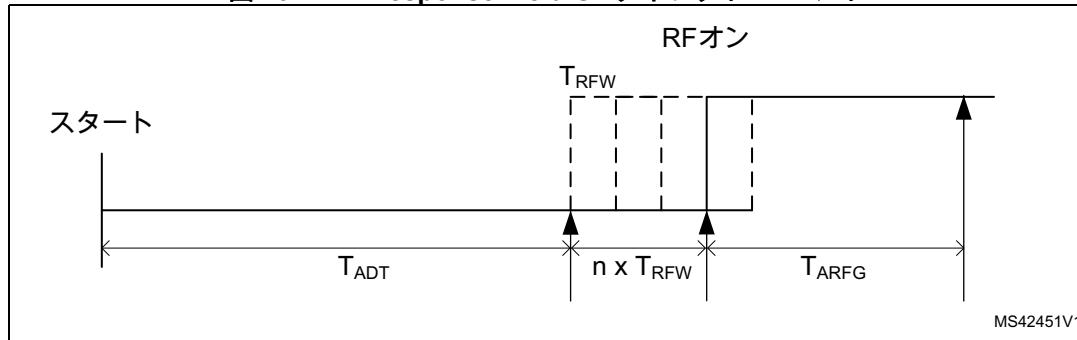

NFCIP-1モードでは、メッセージの送信を終了してトランスマッタがオフになると、このタイマが自動的にカウントを開始します。ピアNFCデバイスのフィールドのオンが検出されずに( $T_{ADT} + n^*T_{RFW}$ )、このタイマがタイムアウトすると、l\_ppon2 IRQが送信されます。

外部RFフィールドが時間内に検出された場合は、タイマが停止し、IRQは送信されません。

時間はPPON2フィールド待機レジスタで設定します。

### 汎用タイマ

このタイマのトリガは[タイマ/EMVコントロール・レジスタ](#)で設定します。受信プロセスの所要時間の調査(SOFの後、受信開始でトリガ)や、PICC応答時間に対するPCDのタイムアウトのカウント(EOFの後、受信終了でトリガ)に使用できます。

NFCIP-1アクティブ通信モードの場合は、フィールドのオフ切り替えに対するタイムアウトのカウントに使用できます。いずれの場合も、タイムアウト時にIRQが送信されます。

汎用タイマのカウントは、ダイレクト・コマンドStart General purpose timer（汎用タイマ起動）を送信して開始することもできます。このコマンドをタイマの動作中に送信すると、タイマはリセットされてからカウントを開始します。

## ウェイクアップ・タイマ

このタイマは、主にウェイクアップ・モードで使用します。ダイレクト・コマンドStart Wake-up Timer（ウェイクアップ・タイマ起動）を送信することで使用できます。このコマンドは、ウェイクアップ・モード以外のすべての動作モードで機能します。このコマンドを送信すると、ウェイクアップ・タイマのクロック源として使用されるRC発振器が動作を開始します。タイムアウト時間は[ウェイクアップ・タイマ・コントロール・レジスタ](#)で設定します。このタイマがタイムアウトすると、エラー/ウェイクアップ割り込みレジスタのI\_wtフラグによるIRQが送信されます。

ウェイクアップ・タイマは、他のタイマを使用できないパワーダウン・モードで使用します。このモードでは、ウェイクアップ・タイマ以外のタイマのクロック源となる水晶発振器が動作していないからです。ウェイクアップ・タイマのタイムアウトの許容誤差は、RC発振器の許容誤差で決まることに注意してください。

NFCIP-1パッシブ・ターゲット・モードでは、初期ピア・フィールドのオン検出からデバイスの一時的な有効化までのタイムアウトのカウントにウェイクアップ・タイマを使用します。

## 4.2.8 A/Dコンバータ

ST25R3916/7は、8ビットの逐次比較型A/Dコンバータを搭載しています。複数の信号源からの入力を多重化して、各種のダイレクト・コマンドや調整手順に使用できます。最後の変換結果は[A/Dコンバータ出力レジスタ](#)に格納されます。一般的な変換時間は224/fc (16.5μs) です。

A/Dコンバータには、絶対モードと相対モードの2つの動作モードがあります。

- 絶対モードでは、Low側の基準は0 V、High側の基準は2 Vです。これは、A/Dコンバータの入力範囲が0 V ~ 2 Vであり、コード00hは入力が0V以下であること、コードFFhは入力が2 V - 1 LSB以上であることを意味します。LSBは7.8125mVに相当します。

- 相対モードの場合、Low側の基準は $V_{DD\_A}$ の1/11、High側の基準は $V_{DD\_A}$ の10/11です。したがって、入力範囲は1/11  $V_{DD\_A}$  ~ 10/11  $V_{DD\_A}$ です。

相対モードは、位相測定でのみ使用します（位相検出器の出力は電源電圧に比例します）。その他の用途では、すべて絶対モードを使用します。

## 4.2.9 位相検出器と振幅検出器

このブロックは、振幅と位相の測定値を得るための入力をA/Dコンバータに供給するために使用します。この測定値は、ダイレクト・コマンド[Measure Amplitude](#)（振幅測定）および[Measure Phase](#)（位相測定）を使用して得ることが想定されています。

### 位相検出器

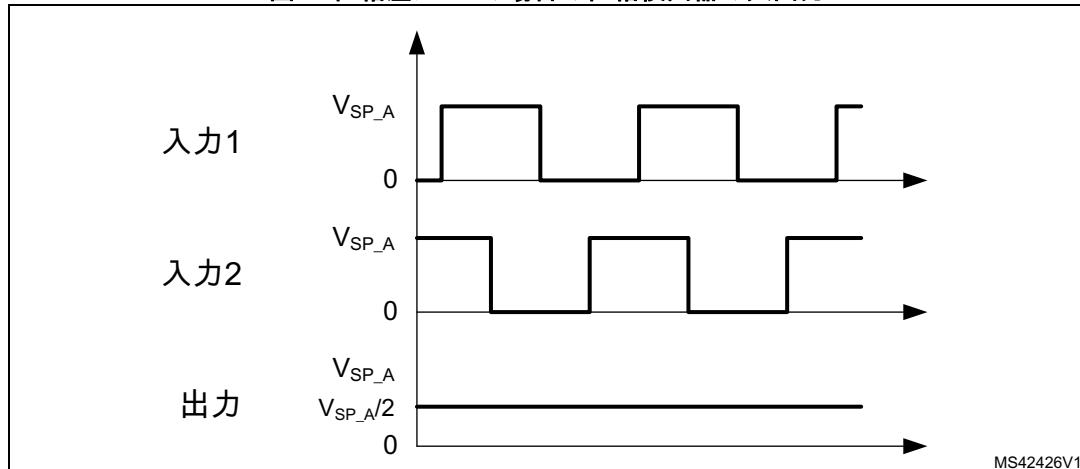

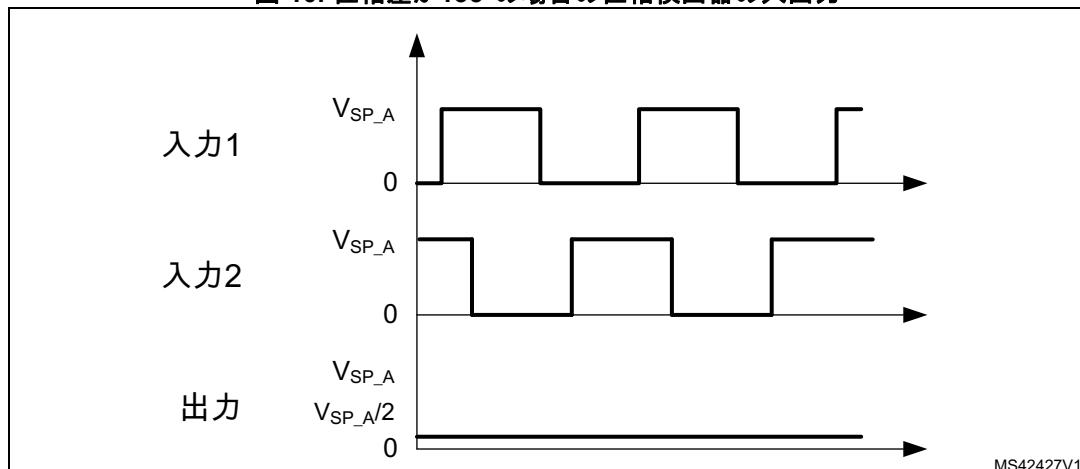

位相検出器は、トランスマッタの出力信号（RFO1とRFO2）とレシーバの入力信号（RFI1とRFI2）との位相差を測定します。この値は、アンテナのLCタンクの信号に比例します。これらの信号は、まずデジタル化コンバータを通過します。デジタル化した信号を、急峻なローパス・フィルタ特性を持つ位相検出器によって処理し、位相差の平均値を求めます。位相検出器の出力は、2つの入力間の位相差に反比例します。これらの入力間位相差が90°の場合、出力電圧は $V_{DD\_A}/2$ 、同位相の場合は $V_{DD\_A}$ 、逆位相の場合は0Vになります。ダイレクト・コマンド[Measure Phase](#)（位相測定）の実行時、この出力はA/Dコンバータの入力に多重化されます（このコマンドを実行中、A/Dコンバータは相対モードです）。A/Dコンバータの範囲が1/11 $V_{DD\_A}$  ~ 10/11 $V_{DD\_A}$ であることから、位相検出器の実際の検出範囲は17° ~ 163°になります。[図 9](#)と[図 10](#)に、位相差がそれぞれ90°および135°の場合について、位相検出器の2つの入力と1つの出力を示します。

図 9. 位相差が90°の場合の位相検出器の入出力

図 10. 位相差が135°の場合の位相検出器の入出力

## 振幅検出器

RFI1とRFI2ピンの信号を、自己ミキシング段の入力として使用します。この段の出力は、RFI1とRFI2ピンの信号の振幅に比例するDC電圧です。ダイレクト・コマンド[Measure Amplitude \(振幅測定\)](#)の実行時、この出力はA/Dコンバータの入力に多重化されます。

### 4.2.10 外部フィールド検出器

このブロックを使用して、RFフィールドを生成している外部デバイスを検出します。NFCIP-1アクティブ通信モードとパッシブ・ターゲット・モードで使用します。この検出器はen\_fd\_c<1:0>オプション・ビットで有効化します。外部フィールド検出器は、2種類の検出閾値であるピア検出とコリジョン防止に対応しています。これら2つの閾値は、[外部フィールド検出器アクティブ化閾値レジスタ](#)への書き込みによって別々に設定できます。検出器出力の実際の状態は、[補助表示レジスタ](#)を読み出すことで確認できます。このブロックへの入力はRFI1ピンの信号です。

両方の閾値に対して、アクティブ化と非アクティブ化のレベルを別々に設定できます。

外部フィールド・レベルが未検出の場合は、アクティブ化閾値を使用します。外部フィールド・レベルが検出されている場合は、非アクティブ化閾値を使用します。

アクティブ化閾値は、非アクティブ化閾値以上の値に設定する必要があります。

アクティブ化閾値を非アクティブ化閾値よりも大きくすると、2つのレベル差によるヒステリシス特性が得られます。

アクティブ化と非アクティブ化のレベルが等しい場合は、ヒステリシス特性が得られません。したがって、フィールドのオン/オフが複数回繰り返される状態を検出することで、選択した閾値付近に実際のフィールド・レベルが維持されていることを検証できます。

## ピア検出閾値

この閾値を使用して、NFC通信の相手であるピアNFCデバイスが放射するフィールドを検出します。この閾値は75mV ~ 800mV<sub>PP</sub>の範囲で選択できます。この閾値を有効にすると、検出器は低消費電力モードになります。外部フィールドが検出されたときのほか、外部フィールドがオフになったときにも割り込みが生成されます。このように実装されていることから、外部フィールドが消失したタイミングの検出にも使用できます。この機能を使用して、ピアNFCデバイス（イニシエータまたはターゲット）がRFフィールドの放射を停止したタイミングを検出できます。

低消費電力ピア検出モードで外部フィールド検出器を有効化するには、[動作コントロール・レジスターのen\\_fd\\_c<1:0>ビット](#)を設定します。

## コリジョン防止閾値

この閾値は、RFコリジョン防止シーケンスで使用します。このシーケンスは、NFC Field ON (NFCフィールド・オン) コマンド ([セクション 4.4.5: NFC Field ON \(NFCフィールド・オン\) コマンド群](#) 参照) を送信して実行します。この閾値は25mV ~ 800mV<sub>PP</sub>の範囲で選択できます。

## 4.2.11 電源系

ST25R3916/7には、3つの正電圧の電源ピンとしてVDD、VDD\_TX、VDD\_IOがあります。

VDDは主電源のピンです。ST25R3916/7の各ブロックの電源は、2つのレギュレータ ( $V_{DD\_A}$  と  $V_{DD\_D}$ ) を介して供給されます。

VDD\_TXは、トランスマッタ用の電源ピンです。この電源は、2つのレギュレータ ( $V_{DD\_RF}$  と  $V_{DD\_AM}$ ) を介して、トランスマッタに供給されます。 $V_{DD}$  の範囲として、2.4V ~ 5.5Vを使用できます。VDDとVDD\_TXは同じ電源に接続する必要があります。

$V_{DD\_IO}$ は、デジタル通信ピン (BSS、MISO、MOSI、SCLK、IRQ、MCU\_CLK) への供給レベルを設定するために使用します。デジタル通信ピンは、レベル・シフタを介してST25R3916/7のロジックに接続されます。したがって、内部電源電圧は $V_{DD\_IO}$ より高い場合もあれば低い場合もあります。 $V_{DD\_IO}$ の範囲として、1.65V ~ 5.5Vを使用できます。

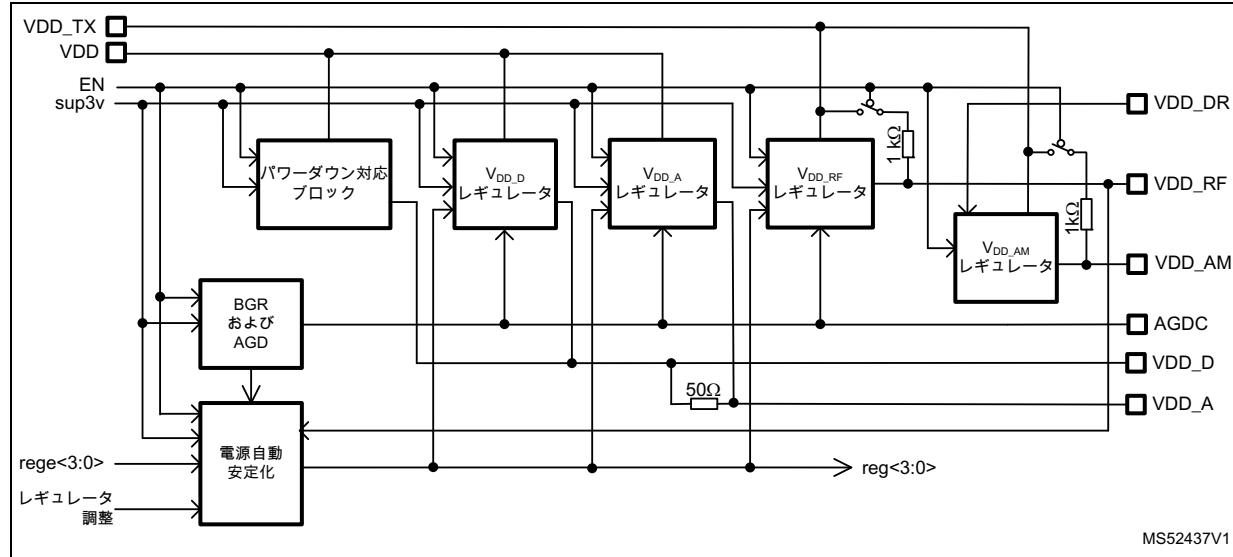

図 11に、ST25R3916/7の電源系の構成要素を示します。3つのレギュレータ、パワーダウンに対応するブロック、アナログ基準電圧 (AGDC) を生成するブロック、電源の自動調整手順を実行するブロックがあります。3つのレギュレータは、アナログ・ブロック ( $V_{DD\_A}$ )、ロジック ( $V_{DD\_D}$ )、トランスマッタ ( $V_{DD\_RF}$ ) に電源を供給します。5V電源の場合は、必ず $V_{DD\_A}$ と $V_{DD\_D}$ のレギュレータを使用する必要があります。3.3Vのみを使用するアナログ・ブロックとロジック・ブロックに安定化電圧を供給する必要があるからです。システムのPSRRの向上を図るために、3V電源の場合も $V_{DD\_A}$ と $V_{DD\_D}$ レギュレータを使用すること、またあらゆる電源電圧で $V_{DD\_RF}$ レギュレータを使用することも推奨します。

良好なPSRRを保持しつつ最大の安定化電圧が得られるように、安定化電圧が自動調整されます。すべてのレギュレータ・ピンには、それと対になる負電源ピンがあり、外部でグランド電位 ( $V_{SS}$ ) に接続します。図 1と図 2に、すべてのレギュレータを使用した場合の代表的なアプリケーション回路を示します。レギュレータの阻止コンデンサには2.2μFと10nFの並列接続、AGDCピンには1μFと10nFの並列接続をそれぞれ推奨します。

図 11. ST25R3916/7の電源系

レギュレータには、電源電圧に応じた2つの基本的な動作モードとして、3.3V電源モード（最大3.6V）と5V電源モード（最大5.5V）があります。この電源モードは、[IOコンフィギュレーション・レジスタ2](#)のsup3Vビットへの書き込みによって設定します。デフォルト設定は5Vであるため、3.3V電源の場合は電源投入後に、このビットを'1'に設定する必要があります。

3.3Vモードの場合、すべてのレギュレータは2.4V～3.4Vの範囲で同じ安定化電圧に設定されます。5Vモードの場合は、V<sub>DD\_RF</sub>のみを3.6V～5.1Vの範囲で設定でき、V<sub>DD\_A</sub>とV<sub>DD\_D</sub>は3.4V固定になります。

図 11には、電源系を制御する信号も示しています。これらのレギュレータ群はen信号がHighのときに動作します（enは[動作コントロール・レジスタ](#)のコンフィギュレーション・ビットです）。en信号がLowになると、ST25R3916/7は低消費電力のパワーダウン・モードに移行します。このモードでは、電源系の消費電力も最小限になります。

### V<sub>DD\_RF</sub>レギュレータ

このレギュレータの目的は、トランスマッタのPSRRを改善することです（トランスマッタの電源から放射されたノイズはレシーバにフィードバックされます）。V<sub>DD\_RF</sub>レギュレータの動作は、次の2つのレギュレータ用レジスタに書き込むことで設定し、読み出すことで確認できます。

- レギュレータ電圧コントロール・レジスタは、レギュレータのモードと安定化電圧を制御します。レギュレータのモードは、reg\_sビットで設定します。このビットを'0'に設定した場合は（デフォルト状態）、ダイレクト・コマンド[Adjust Regulators](#)（レギュレータ調整）で安定化電圧を設定します。reg\_sビットを'1'にアサートした場合は、同じレジスタのrege\_3～rege\_0ビットで安定化電圧を設定します。安定化電圧の調整範囲は、電源モードによって異なります。5V電源モードの場合、調整範囲は3.6V～5.1V（120mV単位）で、3.3V電源モードでは2.4V～3.6V（100mV単位）です。

- レギュレータ表示レジスタは、レギュレータ動作中の実際の安定化電圧を表示する読出し専用レジスタです。このレジスタは自動モードで特に有用です。ダイレクト・コマンド[Adjust Regulators](#)（レギュレータ調整）によって得られる実際の安定化電圧値を確認できるからです。

V<sub>DD\_RF</sub>レギュレータは、通常動作時のレギュレータ電流を350mA rmsに制限する電流リミッタを備えています。V<sub>DD\_RF</sub>レギュレータを電流制限モードで使用する場合は、[レギュレータ表示レジスタ](#)のi\_limビットをセットします。

トランスマッタから350mA rmsを超える出力電流が必要な場合、V<sub>DD\_RF</sub>レギュレータではトランスマッタに電源供給できません。この場合は、VDD\_RFとVDD\_DRを外部でVDD\_TXに接続する必要があります (VDD\_RFをVDD\_TXよりも高い電源電圧に接続することはできません)。

トランスマッタ電流による電圧低下が、ST25R3916/7による電力消費の主要因です。この電圧低下は、トランスマッタのドライバおよびV<sub>DD\_RF</sub>レギュレータの2ヶ所で発生します。このため、ダイレクト・コマンドのAdjust Regulators (レギュレータ調整) で安定化電圧を設定することを推奨します。レギュレータの電圧低下による電力消費を比較的少なく抑えながら、良好なPSRRが得られます。

パワーダウン・モードでは、V<sub>DD\_RF</sub>レギュレータは動作していません。VDD\_RFピンは、1 kΩの抵抗を介してVDD\_TXに接続されます。抵抗を介して接続することで、システムの電源投入や、パワーダウン・モードから他の動作モードへの遷移をスムーズに実行できます。

## V<sub>DD\_AM</sub>レギュレータ

このレギュレータを使用して、トランスマッタのAM変調に対応します。このレギュレータの出力電圧は、変調時のトランスマッタ電源に使用します。この出力は、トランスマッタに内部接続されています。また、VDD\_AMピンにはデカッピング・コンデンサ (2.2μF + 1 nF) が必要です。

V<sub>DD\_DR</sub>を基準電圧としていることから、電源電圧2.4V ~ 5.5Vの範囲で適切なV<sub>DD\_AM</sub>電圧と変調指数が得られます。

このレギュレータの出力電圧、つまり変調の設定は、am\_mod<3:0>オプション・ビットにより、5% ~ 30%の範囲で16段階に調整できます。

パワーダウン・モードでは、V<sub>DD\_AM</sub>レギュレータは動作していません。VDD\_AMピンは、V<sub>DD\_RF</sub>レギュレータの場合と同様に、1kΩの抵抗を介してVDD\_TXに接続されます。

## V<sub>DD\_A</sub>レギュレータとV<sub>DD\_D</sub>レギュレータ

V<sub>DD\_A</sub>レギュレータとV<sub>DD\_D</sub>レギュレータは、それぞれST25R3916/7のアナログ・ブロックとデジタル・ブロックに電源を供給します。3.3V電源モードの場合、V<sub>DD\_A</sub>とV<sub>DD\_D</sub>の安定化電圧は、V<sub>DD\_RF</sub>レギュレータと同じ電圧に設定されます。5V電源モードの場合、V<sub>DD\_A</sub>とV<sub>DD\_D</sub>の安定化電圧は3.4V固定です。

5V電源モードでは、V<sub>DD\_A</sub>レギュレータとV<sub>DD\_D</sub>レギュレータの使用が必須です。これら2つのピンから電源供給されるアナログ・ブロックとデジタル・ブロックでは、最大電源電圧が3.6Vの低電圧トランジスタを使用しているからです。3.3V電源モードでも、アナログ処理でのPSRRを改善するために、レギュレータの使用を強く推奨します。

低コストのアプリケーションでは、V<sub>DD\_D</sub>レギュレータを無効化し、V<sub>DD\_D</sub>を外部でV<sub>DD\_A</sub>に接続してデジタル・ブロックに給電することもできます ([IOコンフィギュレーション・レジスタ2](#)のvsdpd\_offコンフィギュレーション・ビット)。

## パワーダウン対応ブロック

パワーダウン・モードでは、消費電流を低減するためにレギュレータが無効化されます。このモードでは、V<sub>DD\_D</sub>とV<sub>DD\_A</sub>を3.6V未満に保持する低消費電力のパワーダウン対応ブロックが有効化されます。このモードにおける安定化電圧の代表値は、5V電源の場合に3.1V、3V電源の場合に2.2Vです。3.3V電源モードを設定すると、このブロックは無効化され、出力は1kΩの抵抗を介してVDDに接続されます。

パワーダウン対応ブロックの消費電流は、5V電源の場合で600nA (代表値) です。

## 電源電圧の測定

ダイレクト・コマンド[Measure Power Supply](#) (電源測定) を使用すると、V<sub>DD</sub>および安定化電圧のV<sub>DD\_A</sub>、V<sub>DD\_D</sub>、V<sub>DD\_RF</sub>を測定できます。

### 4.2.12 オーバーシュート/アンダーシュート保護

オーバーシュート/アンダーシュート保護機能を使用すると、困難なテスト条件下で送信波形を制御できるようになります。変調状態から非変調状態への遷移またはその逆の遷移時に追加の信号を生成するビット・パターンを、該当のレジスタに設定することで実現します。

ここでは、オーバーシュート・レジスタを使用して、この保護機能の動作を説明します。オーバーシュート保護機構は、ov\_pattern<13:0>にビットが書き込まれている状態でのみ有効です。ov\_pattern<13:0>を0に設定すると、オーバーシュート保護が暗黙的に無効になります。遷移後のすべてのクロック・サイクルでモード設定レジスタと送信ドライバ・レジスタの設定が適用されるからです。

ov\_tx\_mode<1:0>コントロール・ビットにオーバーシュートのモードを設定する必要があります。このモードによって、ビット・パターン全体の駆動レベルが決まります。以下の3種類のモードを使用できます。

- ov\_tx\_mode<1:0> = 00b: 対応するov\_patternビットが'1'の場合、トランスマッタの出力がV<sub>DD\_DR</sub>で駆動されます。

- ov\_tx\_mode<1:0> = 01b: 対応するov\_patternビットが'1'の場合、トランスマッタの出力がV<sub>DD\_AM</sub>で駆動されます。

- ov\_tx\_mode<1:0> = 10b: 対応するov\_patternビットが'1'の場合、トランスマッタの出力が停止します (Type Aのポーズと同様)。

ov\_pattern<13:0>のオーバーシュート保護パターンは、最下位ビット側から適用されます。変調状態から非変調状態への遷移後、最初の14クロック・サイクルでは、オーバーシュート保護パターンの14ビットそれぞれによって、各クロックに適用するドライバ・コンフィギュレーションが指定されます。つまり、ov\_pattern<0>は、変調状態から非変調状態に遷移した後の最初のクロック・サイクルに適用するドライバ・コンフィギュレーションを規定し、ov\_pattern<9>は、同じ遷移後の10番目のクロック・サイクルに適用するドライバ・コンフィギュレーションを規定します。15番目以降のクロック・サイクルでは、送信ドライバ・レジスタの設定が使用されます。

アンダーシュート保護も、キャリアの非変調状態から変調状態への遷移時に同様に動作します。

### 4.2.13 リーダ動作

動作コントロール・レジスタのenビットをセットしてレディ・モードに移行する必要があります。このモードで発振器が起動し、レギュレータが有効になります。発振器の動作が安定すると割り込みが送信され、安定したことがosc\_okビットに示されます。

つづいて、モード設定レジスタとビット・レート設定レジスタに書き込むことで動作モードとデータ・レートを設定します。さらに、動作モードに関連する、レシーバとトランスマッタの動作オプションを規定する必要があります。リーダからタグへの通信にAM変調を使用する動作モードを選択している場合は、変調の深さを設定する必要があります。

トランスポンダにコマンドを送信する前に、rx\_enとtx\_enビットをセットしてトランスマッタとレシーバを有効化します。NFC規格の中には、最初のコマンドを送信する前に、ある程度の期間リーダのフィールドをオンにしておくガード時間を規定しているものがあります (ISO14443の場合は5 ms)。この規定に適合するには、汎用タイマを使用してこの時間をカウントするか、NFCフィールド・オン・ガード・タイマ・レジスタで設定した時間を指定したNFC Field On (NFCフィールド・オン) コマンドを使用します。

## 送受信シーケンスの準備と実行

- ダイレクト・コマンドStop All Activities（全動作停止）を実行します。

- ダイレクト・コマンドReset RX Gain（受信ゲイン・リセット）を実行します。

- タイムを適宜設定します。

- 送信バイト数レジスタ1と送信バイト数レジスタ2で、送信するバイト数を設定します。

- 送信するバイトをFIFOに書き込みます（ダイレクト・コマンドREQAおよびWUPA以外の場合）。

- Transmit with CRC、Transmit without CRC、Transmit REQA、Transmit WUPAの各コマンドのうち、いずれか1つを送信します。

- すべてのデータの送信が終了すると、送信完了を知らせる割り込みがマイクロコントローラに送信されます（送信完了によるIRQ）。

送信の実行後、ST25R3916/7のレシーバが自動的に起動し、トランスポンダの応答を検出するためにRFI入力の観測を開始します。RSSIが起動し、AGCが有効になっていればAGCも起動します。レシーバからのサブキャリア信号がフレーミング・ブロックで処理され、FIFOにデータが格納されます。受信が完了し、すべてのデータがFIFOに格納されると、マイクロコントローラに割り込みが送信されます（受信完了によるIRQ）。さらに、FIFOにあるデータのバイト数がFIFOステータス・レジスタ1とFIFOステータス・レジスタ2に示されるので、マイクロコントローラはデータのダウンロードに進むことができます。

受信中にエラーまたはビット・コリジョンが検出された場合、該当のフラグを設定した割り込みが送信されます。これを受けたマイクロコントローラでは、適切な対応策を実施する必要があります。

FIFOよりも長いデータ・パケットを送信する必要がある場合、前述のシーケンスは異なるものになります。

送信開始前にFIFOにデータを用意します。データの送信中に、残りのバイト数がウォーター・レベルを下回ると割り込みが送信されます（FIFOウォーター・レベルによるIRQ）。この割り込みを受けたマイクロコントローラはFIFOにデータを追加します。データがすべて送信されると、送信完了を知らせる割り込みがマイクロコントローラに送信されます。

受信時の状況も同じです。受信ウォーター・レベルを上回るデータがFIFOにロードされると割り込みが送信され、マイクロコントローラはFIFOからデータを読み出します。この読み出しによって受信が完了すると、マイクロコントローラに割り込みが送信されます（受信完了によるIRQ）。さらに、まだ読み出していない残りのデータのバイト数がFIFOステータス・レジスタ1とFIFOステータス・レジスタ2に示されます。

## 4.2.14 リッスン・モード

ST25R3916/7のリッスン/ターゲット・モードは、モード設定レジスタのtargビットを'1'に設定することで有効になります。om<3:0>ビットの設定に応じて、さまざまなターゲット・ノードまたはリッスン・モードを実装できます。表 24: ターゲット動作モードを参照してください。

主なモードは、次のとおりです。

- NFCIP-1アクティブ・ターゲット

- カード・モードに使用するパッシブ・ターゲットおよびNFCIP-1パッシブ・ターゲット

### 固定リッスン通信モード

om3=0を設定したターゲット・モードのいずれかを選択すると、固定通信モードがアクティブになります。その他のomビットは通信のタイプを設定します。

### パッシブ・ターゲット

通信は、FIFOを介してホスト側で実行できるほか、NFCIP-1パッシブ・ターゲット設定レジスタの説明にあるように、自動応答を使用して実行することもできます。

このような自動応答として、NFC-A向けとした、SAKなどの完全なアンチコリジョンがあります。RATSやHLTAの処理はホストに委ねられます。NFC-Fの場合、SENSF\_RESを送信することでSENSF\_REQのみが処理されます。

NFC-Aの状態は、パッシブ・ターゲット表示レジスタとパッシブ・ターゲット割り込みレジスタのI\_wu\_aビットとI\_wu\_a\*ビットを観測して処理します。ダイレクト・コマンドGo to senseとGo to sleepにより、パッシブ・ターゲットの状態をホストから変更できます。

SENSF\_REQへの応答はI\_wu\_fビットで観測できます。

自動応答の内容は、PT\_memoryの内容で設定されます。

### NFCIP-1アクティブ・ターゲット

NFCIP-1アクティブ・ターゲット・モードでの動作に関連して、次のような設定があります。

- 動作コントロール・レジスタのen\_fd\_cビットの設定により、外部フィールド検出器を有効化します。フィールド検出器を使用することで、モード設定レジスタのnfc\_arの設定に応じて、ST25R3916/7から応答フィールドをオンにすることができます。

補助設定レジスタのnfc\_n<1:0>ビットによって、応答コリジョン防止シーケンスのタイミングが変化します。

- データ送信の完了からRFフィールドがオフになるまでの時間は汎用タイマで規定します。このタイマのトリガ源は、表 52: トリガ源 (gptc<2:0> = 011) に従い、送信の完了時に設定する必要があります。

- T\_ARFGが経過すると、I\_catフラグまたはI\_cacフラグが設定されます。T\_ARFGはNFCフィールド・オン・ガード・タイマ・レジスタで設定します。

- 外部フィールドがオンになるとMRTが起動します。nrt\_nfcによってNRTの動作を調整できます。

- ST25R3916/7は、自身のフィールドをオフにすると、PPON2タイマを起動するとともに、応答フィールドを検出するために、外部フィールド検出器の出力を観測します。PPON2タイマがタイムアウトするまでに外部フィールドが検出されないと、I\_ppon2フラグを設定したIRQが送信されます。

### ビット・レート検出モード

リッスン・モードは、いわゆるビット・レート検出モードから開始することもできます。このモードでは、通信モードが固定されていません。ターゲット・モードでom3を'1'に設定すると、ビット・レート検出モードがアクティブになります。

その他のomビットでは、識別する技術を設定します。これは、固定リッスン通信モードの拡張モードです。

最初のフレームの受信が始まると、ビット・レート検出モードでIRQ I\_nfctが送信され、ビット・レートが特定されたことが通知されます。これにより、ホストでは、ビット・レート検出表示レジスタのnfc\_rateを読み出すことで関連情報を取得できます。

最初のフレームをすべて受信したホストでは、モード設定レジスタのom<3:0>ビットによって目的の固定リッスン通信モードに設定することで、ビット・レート検出モードを終了できます。

d\_ac\_ap2pビットでNFCIP-1のアクティブ・フレームをフィルタ処理できます。

## 低消費電力フィールド検出

フィールド検出器を低電力モードで使用することにより、消費電力の観点から固定リッスン通信モードとビット・レート検出モードを機能強化できます。この場合は、ピアまたはリーダの外部フィールドを待機している間は、ST25R3916/7をパワーダウン・モード (`en=0`) に設定します。

このモードを使用するには、ビット・レート検出モードまたは固定リッスン通信モードを選択し、[動作コントロール・レジスタ](#)の`en`、`rx_en`、`tx_en`の各ビットを0にクリアする必要があります。

このモードでは、フィールド検出器に自動または手動のピア検出閾値を設定する必要があります。

ST25R3916/7では、外部フィールドを検出すると (`l_en`)、発振器とレシーバを一時的に有効にします。ホストでは、[動作コントロール・レジスタ](#)の`en`オプション・ビットと`rx_en`オプション・ビットを設定することで、この一時的な有効状態を10 ms以内に確定する必要があります。

その後は、通常のビット・レート検出または通常のターゲット通信を実行できます。

## PT\_memory

`PT_memory`を使用して、NFCIP-1パッシブ・ターゲットおよびNFC-Aカード/リッスン・モードのデータを格納します。[セクション 4.3](#)の説明にあるように、このメモリはホストのインターフェースを介してロードされます。

表 7. `PT_memory`のアドレス空間

| 位置      | 内容                   | データの使用法                                           |               |

|---------|----------------------|---------------------------------------------------|---------------|

| 0 ~ 9   | NFCID1 (4/7/予約済みバイト) | 4バイト: 位置0 ~ 3<br>7バイト: 位置0 ~ 6                    | NFC-Aアンチコリジョン |

| 10,11   | SENS_RES2:1          | SENS_REQ応答                                        |               |

| 12      | SELR_L1              | SEL Level 1応答                                     |               |

| 13      | SELR_L2              | SEL Level 2応答                                     |               |

| 14      | SELR_L3              | (今後の使用のために確保)                                     |               |

| 15,16   | NFCF_SC              | SENSF_REQのシステム・コード (SC) <sup>(1)</sup>            |               |

| 17 ~ 35 | 212/424ポーリング応答       | SENSF_RESフォーマット <sup>(2)</sup>                    |               |

| 36 ~ 47 | TSN - ランダムな数値        | スロット選択。4ビットのランダムな数値が24個保存されます。 <sup>(3) (4)</sup> | NFC-Fアンチコリジョン |

- SENSF\_RESは、SC=NFCF\_SCまたはSC=0xFFFFを受信した場合に送信されます。

- NFC-212/424k SENS\_RESフォーマット (表 8参照) SENSF\_RESの最後の2バイトは、SENSF\_REQのRCバイトに基づいて送信されます。

- NFC212/424ポーリング応答では、この4ビットのスロット番号が順番に使用されます。未使用のTSN番号が4つのみになると、`l_sl_wl`ビットによるIRQが送信されます。

- ポーリング・リクエストにあるスロット数に応じて、スロット番号の最上位側ビットが該当の数だけ使用されます。

表 8. NFC-212/424k SENS\_RESフォーマット

| バイト1 | バイト2 ~ 9 | バイト10 ~ 11 | バイト12 ~ 14 | バイト15     | バイト16      | バイト17 | バイト18 ~ 19 |

|------|----------|------------|------------|-----------|------------|-------|------------|

| 01h  | NFCID2   | PAD0       | PAD1       | MRTICHECK | MRTIUPDATE | PAD2  | [RD]       |

### 4.3 外部マイクロコントローラとの通信

ST25R3916/7は、マイクロコントローラとSPIインターフェースまたはI<sup>2</sup>Cインターフェースのいずれかを介して通信します。どちらのインターフェースを使用しても、ST25R3916/7はスレーブ・デバイスとして動作し、すべての通信はマイクロコントローラ側から開始します。コマンドの完了や外部イベント（ピア・デバイスのフィールド・オンなど）をマイクロコントローラに通知するために、ST25R3916/7はIRQピンに割り込み信号を出力します。また、MCU\_CLKピンを介してST25R3916/7からマイクロコントローラにクロック信号（設定可能）を供給できます。

#### 4.3.1 割り込みのインターフェース

ST25R3916/7は、4つの割り込みレジスタを搭載しています。

- メイン割り込みレジスタ

- タイマ/NFC割り込みレジスタ

- エラー/ウェイクアップ割り込みレジスタ

- パッシブ・ターゲット割り込みレジスタ

割り込み条件が満たされると、割り込みの発生要因を示すビットがセットされ、IRQピンがHighに遷移します。これを受けたマイクロコントローラはメイン割り込みレジスタを読み出し、割り込み発生要因を特定します。特定の割り込みレジスタを読み出すと、その内容は'0'にリセットされます。

IRQピンは、そのHigh遷移の原因となった割り込みビットが読み出されると、Lowに戻ります。

注： IRQ信号がセットされても、マイクロコントローラがただちにその割り込みレジスタを読み出さず、さらに別のイベントによって割り込みが発生すると、複数の割り込みビットがセットされることがあります。このような場合、最後の割り込みが発生したビットが読み出された時点でIRQピンがLowに遷移します。

特定の要因による割り込みが不要な場合は、割り込みマスク・レジスタの該当するビットを設定することで、その割り込みを無効にすることができます。特定の割り込み要因をマスクすると、その割り込みがあってもIRQラインはHighに遷移しませんが、IRQステータス・レジスタの割り込みステータス・ビットは通常どおりセットされます。

IRQステータス・レジスタを読み出すと、マスクした割り込みについてもビット内容が表示され、またクリアされます。

いくつかのマスクした割り込みのステータス・ビットがIRQイベントによって'1'に設定された状態で、これらの既にセットされているIRQステータス・ビットのいずれかでマスクを解除すると、IRQラインはただちにHighに遷移します。これにより、まだ読み出されていない割り込みイベントが存在するところがホスト・システムに通知されます。

表 9. IRQ出力

| 名前  | 信号     | レベル  | 内容       |

|-----|--------|------|----------|

| IRQ | デジタル出力 | CMOS | 割り込み出力ピン |

IRQラインとIRQステータス・ビットは次の場合にクリアされます。

- Set Default（デフォルト設定）

- IRQステータスの読み出し

- Stop All Activities（全動作停止）

- Clear FIFO（FIFOのクリア）

## FIFOウォーター・レベルとFIFOステータス・レジスタ、FIFOのリセット

ST25R3916/7は、512バイトのFIFOを搭載しています。送信時、コントロール・ロジックによってデータがシフトされます。このデータは、外部マイクロコントローラによって、フレーミング・ブロックを経てトランスマッタにロードしておきます。受信時は、復調したデータがFIFOに格納され、以後の時点では外部マイクロコントローラによってデータを受信できます。

[FIFOステータス・レジスタ2](#)には、送受信プロセスでFIFOに対するデータ処理に不具合があったこと（FIFOでのオーバーフローまたはアンダーフローの発生）を示す2ビットも設けられています。

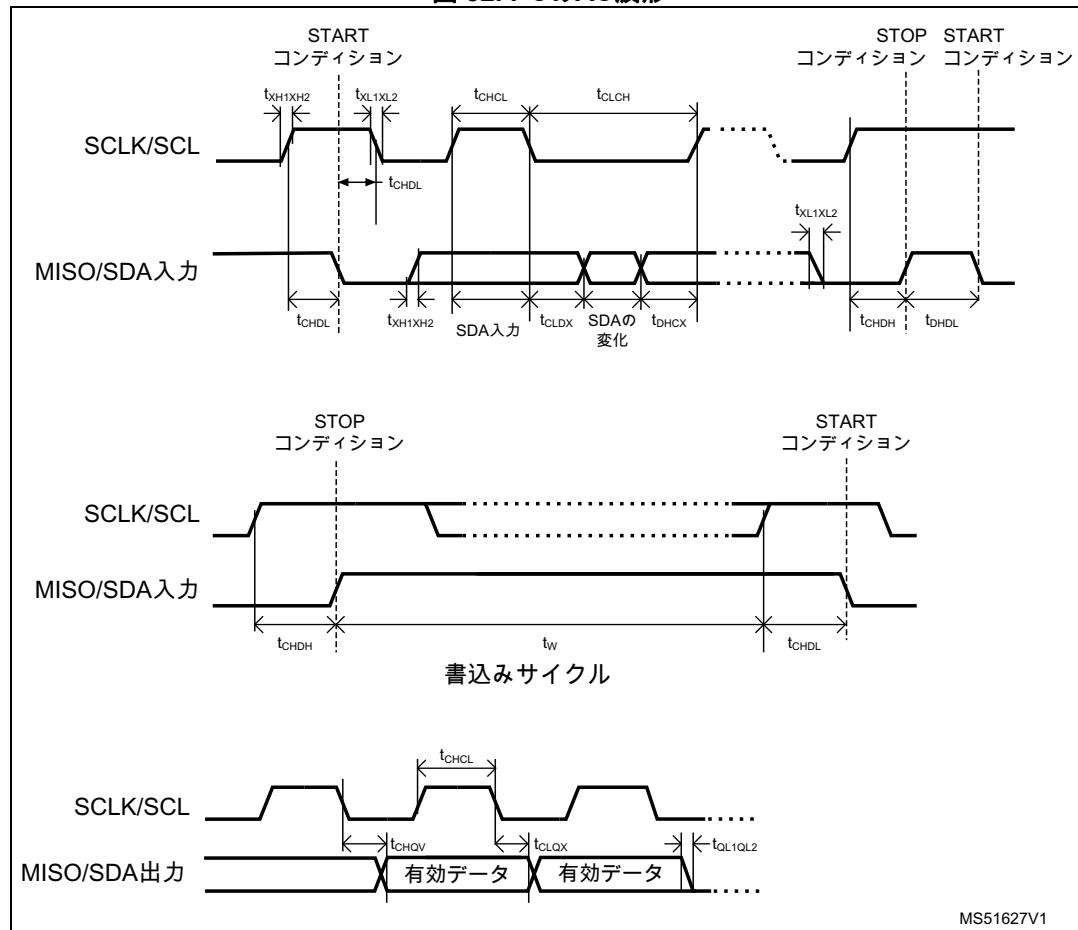

FIFOに収まらない過剰な量のデータが書き込まれると、FIFOオーバーフローのビットがセットされます。受信中にこのビットがセットされた場合は、ウォーター・レベルIRQに対応する処理を外部コントローラが直ちに実行しなかったために、受信したCRCバイトも含め、512バイトを超えるデータがFIFOに書き込まれています。その結果、受信データが破損しています。送信中にオーバーフローが発生した場合は、FIFOの容量を超える量のデータがコントローラによって書き込まれています。その結果、送信する予定のデータが破損しています。