## EPC Class1 Gen2準拠UHF RFIDリーダライタ

データシート

### 機能

- 電源電圧範囲 3.0 ~ 3.6 V

- 2.7 Vまで制限された動作が可能

- 最大PA電源電圧 4.3 V

- ペリフェラルI/O電源範囲 1.65 ~ 5.5 V

- 以下のプロトコルに対応:

- ISO 18000-6C (EPC Class1 Gen2)

- ISO 29143 (モバイルRFIDエア・インターフェース)

- ダイレクト・モードによるISO 18000-6A/B

- DRM: M4とM8に対して250 kHzフィルタと320 kHzフィルタ

- 電源レギュレータ内蔵

- 周波数ホッピング対応

- ASKまたはPR-ASK変調

- 自動I/Q選択

- 8ビット・リニアRSSIを用いたタグ・トラッキング用位相ビット

- 温度範囲: -40 ~ 85°C

- 48ピンQFN (7 x 7 x 0.9 mm) パッケージ

### 説明

ST25RU3993は、ISO 18000-6C、モバイルRFIDインテロゲータ用ISO 29143エア・インターフェース・プロトコル、ダイレクト・モード動作のためのISO 18000-6A/Bを含む、すべての関連プロトコルが実装されたEPC Class 1 Gen 2 RFIDリーダライタICです。オンチップVCOとパワー・アンプを内蔵しており、密集リーダ・モード(DRM)機能を含むRFID機能一式を備えています。また、周波数ホッピング、低レベル送信コーディング、低レベル・デコード、データ・フレーミング、CRCチェックに対応しています。

ST25RU3993は非常に低い消費電力で動作しますので、携帯電話のようなポータブルのバッテリ駆動機器に最適です。

7 x 7 mm QFNパッケージのST25RU3993は、非常に高感度でありながら、アンテナ反射効果と自己妨害に対する高い耐性を備えています。コストやサイズの制約によりアンテナ設計に妥協を強いられることが多いモバイル用途や組み込み用途では、このことは非常に重要です。高感度であるために、最終製品が簡単で安価なアンテナを用いても所定の読み込み範囲を得ることが可能となり、システム・コスト全体が押さえられます。

高度な集積化により、ST25RU3993に8ビット・マイクロコントローラを外付けするだけで、完全なRFIDリーダ・システムを構築できますので、複雑なRFIDコプロセッサは必要ありません。

# 目次

|          |                   |           |

|----------|-------------------|-----------|

| <b>1</b> | <b>説明</b>         | <b>10</b> |

| 1.1      | ブロック図             | 10        |

| <b>2</b> | <b>機能概要</b>       | <b>11</b> |

| 2.1      | 電源                | 13        |

| 2.1.1    | メイン・レギュレータ        | 13        |

| 2.1.2    | 内部 PA 電源レギュレータ    | 13        |

| 2.1.3    | ペリフェラル通信電源        | 13        |

| 2.1.4    | 自動電源レベル設定         | 13        |

| 2.1.5    | 電源モード             | 14        |

| 2.2      | ホスト通信             | 15        |

| 2.2.1    | レジスタへの書き込み        | 17        |

| 2.2.2    | レジスタからの読み込み       | 18        |

| 2.2.3    | ダイレクト・コマンド        | 19        |

| 2.2.4    | SPI インタフェース・タイミング | 23        |

| 2.2.5    | CLSYS 出力          | 25        |

| 2.2.6    | IO 信号レベルと出力特性     | 25        |

| 2.2.7    | OAD、OAD2 出力       | 26        |

| 2.3      | PLL/VCO 部         | 26        |

| 2.3.1    | 電圧制御発振器           | 27        |

| 2.3.2    | PLL プリスケーラと主分周器   | 27        |

| 2.3.3    | PLL 基準周波数         | 28        |

| 2.3.4    | 基準周波数源            | 28        |

| 2.3.5    | 位相周波数検出器とチャージ・ポンプ | 28        |

| 2.3.6    | ループ・フィルタ          | 28        |

| 2.3.7    | 周波数ホッピング・コマンド     | 28        |

| 2.3.8    | PLL の始動と周波数ホッピング  | 29        |

| 2.4      | デバイス・ステータス・コントロール | 29        |

| 2.5      | プロトコル・コントロール      | 29        |

| 2.6      | 送信部               | 30        |

| 2.6.1    | Tx データ処理とコーディング   | 30        |

| 2.6.2    | Tx 整形回路           | 30        |

| 2.6.3    | 局部発振器（LO）経路       | 31        |

| 2.6.4    | モジュレータ            | 31        |

|        |                                      |    |

|--------|--------------------------------------|----|

| 2.7    | Tx 出力 . . . . .                      | 32 |

| 2.8    | Tx 動作モード . . . . .                   | 32 |

| 2.8.1  | TX ノーマル・モード . . . . .                | 32 |

| 2.8.2  | TX ダイレクト・モード . . . . .               | 34 |

| 2.9    | レシーバ . . . . .                       | 34 |

| 2.9.1  | 入力ミキサ . . . . .                      | 35 |

| 2.9.2  | 局部発振器経路 . . . . .                    | 36 |

| 2.9.3  | 高速 AC 結合 . . . . .                   | 36 |

| 2.9.4  | Rx フィルタ . . . . .                    | 37 |

| 2.9.5  | IQ 選択 . . . . .                      | 40 |

| 2.9.6  | ビット・デコーダ . . . . .                   | 40 |

| 2.9.7  | データ・フレーマ . . . . .                   | 40 |

| 2.10   | データ受信モード . . . . .                   | 40 |

| 2.10.1 | Rx ノーマル・モード . . . . .                | 40 |

| 2.10.2 | Rx ダイレクト・モード . . . . .               | 43 |

| 2.10.3 | アンテナまたは指向性デバイスのチューニング支援モード . . . . . | 44 |

| 2.10.4 | 対数 RSSI . . . . .                    | 44 |

| 2.11   | A/D コンバータ . . . . .                  | 44 |

| 2.11.1 | 外部 RF パワー検出器 . . . . .               | 44 |

| 2.11.2 | 反射波 RF 電力インジケータ . . . . .            | 44 |

| 2.11.3 | 電源電圧測定 . . . . .                     | 45 |

| 2.11.4 | サブキャリア位相ビット付きリニア RSSI . . . . .      | 45 |

| 2.11.5 | 内部信号レベル検出器 . . . . .                 | 45 |

| 2.12   | インテロゲータ・コリジョン防止対応 . . . . .          | 46 |

| 3      | レジスタの説明 . . . . .                    | 47 |

| 3.1    | メイン・コントロール・レジスタ . . . . .            | 48 |

| 3.1.1  | デバイス・ステータス・コントロール・レジスタ . . . . .     | 49 |

| 3.1.2  | プロトコル選択レジスタ . . . . .                | 49 |

| 3.2    | コンフィギュレーション・レジスタ . . . . .           | 50 |

| 3.2.1  | Tx オプション・レジスタ . . . . .              | 50 |

| 3.2.2  | Rx オプション・レジスタ . . . . .              | 50 |

| 3.2.3  | TRcal ハイ・レジスタ . . . . .              | 51 |

| 3.2.4  | TRcal ロー・レジスタ . . . . .              | 51 |

| 3.2.5  | AutoACK 待ち時間レジスタ . . . . .           | 52 |

| 3.2.6  | Rx 応答なし時間レジスタ . . . . .              | 52 |

|        |                                                               |    |

|--------|---------------------------------------------------------------|----|

| 3.2.7  | Rx 待ち時間レジスタ .....                                             | 53 |

| 3.2.8  | Rx フィルタ設定レジスタ .....                                           | 53 |

| 3.2.9  | Rx ミキサ / ゲインレジスタ .....                                        | 54 |

| 3.2.10 | レギュレータ /PA バイアス・レジスタ .....                                    | 55 |

| 3.2.11 | RF 出力 /LO コントロール・レジスタ .....                                   | 56 |

| 3.2.12 | 補助レジスタ 1 .....                                                | 56 |

| 3.2.13 | 補助レジスタ 2 .....                                                | 57 |

| 3.2.14 | 測定コントロール・レジスタ .....                                           | 58 |

| 3.2.15 | VCO コントロール・レジスタ .....                                         | 58 |

| 3.2.16 | CP コントロール・レジスタ .....                                          | 59 |

| 3.2.17 | モジュレータ・コントロール・レジスタ 1 .....                                    | 60 |

| 3.2.18 | モジュレータ・コントロール・レジスタ 2 .....                                    | 60 |

| 3.2.19 | モジュレータ・コントロール・レジスタ 3 .....                                    | 61 |

| 3.2.20 | モジュレータ・コントロール・レジスタ 4 .....                                    | 62 |

| 3.2.21 | PLL 主レジスタ 1 .....                                             | 62 |

| 3.2.22 | PLL 主レジスタ 2 .....                                             | 63 |

| 3.2.23 | PLL 主レジスタ 3 .....                                             | 63 |

| 3.2.24 | PLL 補助レジスタ 1 .....                                            | 64 |

| 3.2.25 | PLL 補助レジスタ 2 .....                                            | 64 |

| 3.2.26 | PLL 補助レジスタ 3 .....                                            | 65 |

| 3.2.27 | インテロゲータ・コリジョン検出 /IQ 選択設定レジスタ .....                            | 65 |

| 3.2.28 | エミッタ結合ミキサ・オプション・レジスタ .....                                    | 66 |

| 3.3    | ステータス・レジスタ .....                                              | 67 |

| 3.3.1  | ステータス読み出しページ設定レジスタ .....                                      | 67 |

| 3.3.2  | AGC/ 内部ステータス表示レジスタ .....                                      | 67 |

| 3.3.3  | RSSI 表示レジスタ .....                                             | 68 |

| 3.3.4  | AGL/VCO/F_CAL/PilotFreq ステータス表示レジスタ (r2Cpage[1:0] = 00) ..... | 68 |

| 3.3.5  | AGL/VCO/F_CAL/PilotFreq ステータス・レジスタ (r2Cpage[1:0] = 01) .....  | 69 |

| 3.3.6  | AGL/VCO/F_CAL/PilotFreq ステータス・レジスタ (r2Cpage[1:0] = 10) .....  | 69 |

| 3.3.7  | ADC 読取り / レギュレータ設定表示レジスタ (r2Dpage[1:0] = 00) .....            | 70 |

| 3.3.8  | ADC 読取り / レギュレータ設定表示レジスタ (r2Dpage[1:0] = 01) .....            | 70 |

| 3.3.9  | コマンド・ステータス表示レジスタ .....                                        | 71 |

| 3.3.10 | バージョン・レジスタ .....                                              | 71 |

| 3.4    | 割込みレジスタ .....                                                 | 72 |

| 3.4.1  | 割込み有効化レジスタ 1 .....                                            | 72 |

| 3.4.2  | 割込み有効化レジスタ 2 .....                                            | 72 |

| 3.4.3  | 割込みレジスタ 1 .....                                               | 73 |

---

|       |                       |    |

|-------|-----------------------|----|

| 3.4.4 | 割込みレジスタ 2 .....       | 74 |

| 3.5   | 通信レジスタ .....          | 75 |

| 3.5.1 | FIFO ステータス・レジスタ ..... | 75 |

| 3.5.2 | Rx 長レジスタ 1 .....      | 75 |

| 3.5.3 | Rx 長レジスタ 2 .....      | 76 |

| 3.5.4 | Tx 設定レジスタ .....       | 76 |

| 3.5.5 | Tx 長レジスタ 1 .....      | 77 |

| 3.5.6 | Tx 長レジスタ 2 .....      | 77 |

| 3.5.7 | FIFO I/O レジスタ .....   | 78 |

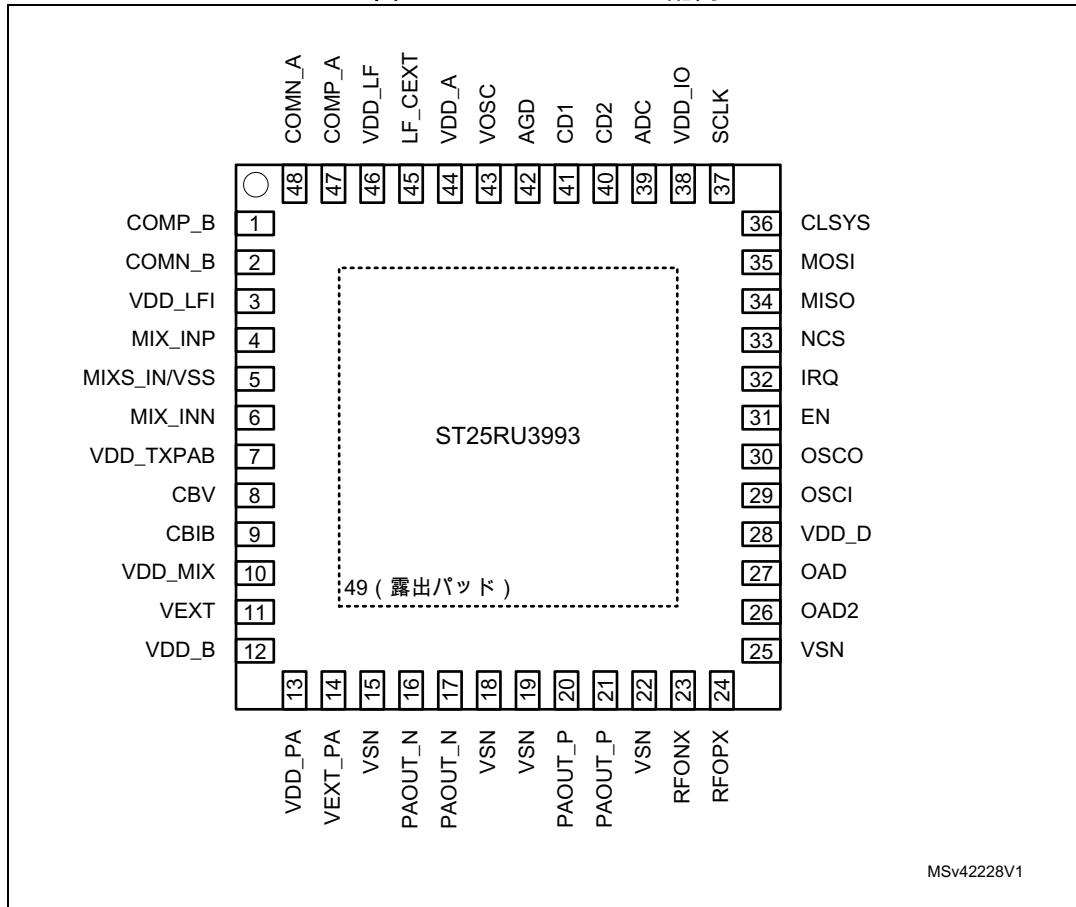

| 4     | ピン配列とピン説明 .....       | 79 |

| 5     | 電気的特性 .....           | 82 |

| 5.1   | 絶対最大定格 .....          | 82 |

| 5.2   | 動作条件 .....            | 83 |

| 5.3   | 標準動作特性 .....          | 86 |

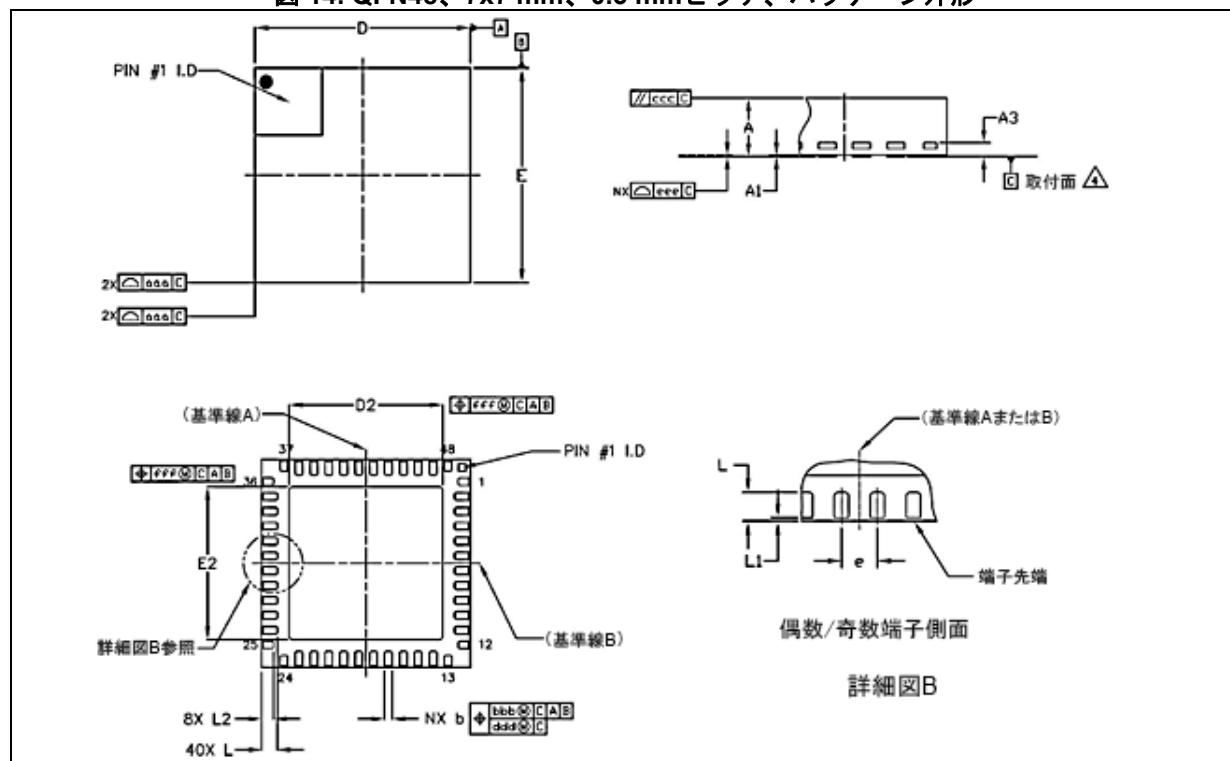

| 6     | パッケージ情報 .....         | 87 |

| 6.1   | QFN48 パッケージ情報 .....   | 87 |

| 7     | 部品番号 .....            | 89 |

| 8     | 改訂履歴 .....            | 90 |

## 表の一覧

|       |                                                               |    |

|-------|---------------------------------------------------------------|----|

| 表 1.  | 電源モード概要 .....                                                 | 15 |

| 表 2.  | シリアル・データ・インターフェース (SPI インタフェース) 信号ライン .....                   | 15 |

| 表 3.  | SPI データ・モード .....                                             | 16 |

| 表 4.  | ダイレクト・コマンド一覧 .....                                            | 19 |

| 表 5.  | SPI タイミング・パラメータ .....                                         | 23 |

| 表 6.  | ダイレクト・モードにおける I/O ピン再割り当て .....                               | 34 |

| 表 7.  | Rx フィルタ設定 (レジスタ 09h) .....                                    | 37 |

| 表 8.  | 対応リンクモードに対する推奨 Rx フィルタ設定 .....                                | 38 |

| 表 9.  | レジスタ・マップ .....                                                | 47 |

| 表 10. | デバイス・ステータス・コントロール・レジスタ .....                                  | 49 |

| 表 11. | プロトコル選択レジスタ .....                                             | 49 |

| 表 12. | Tx オプション・レジスタ .....                                           | 50 |

| 表 13. | Rx オプション・レジスタ .....                                           | 50 |

| 表 14. | TRcal ハイ・レジスタ .....                                           | 51 |

| 表 15. | TRcal ロー・レジスタ .....                                           | 51 |

| 表 16. | AutoACK 待ち時間レジスタ .....                                        | 52 |

| 表 17. | Rx 応答なし時間レジスタ .....                                           | 52 |

| 表 18. | Rx 待ち時間レジスタ .....                                             | 53 |

| 表 19. | Rx フィルタ設定レジスタ .....                                           | 53 |

| 表 20. | Rx ミキサ / ゲインレジスタ .....                                        | 54 |

| 表 21. | レギュレータ /PA バイアス・レジスタ .....                                    | 55 |

| 表 22. | RF 出力 /LO コントロール・レジスタ .....                                   | 56 |

| 表 23. | 補助レジスタ 1 .....                                                | 56 |

| 表 24. | 補助レジスタ 2 .....                                                | 57 |

| 表 25. | 測定コントロール・レジスタ .....                                           | 58 |

| 表 26. | VCO コントロール・レジスタ .....                                         | 58 |

| 表 27. | CP コントロール・レジスタ .....                                          | 59 |

| 表 28. | モジュレータ・コントロール・レジスタ 1 .....                                    | 60 |

| 表 29. | モジュレータ・コントロール・レジスタ 2 .....                                    | 60 |

| 表 30. | モジュレータ・コントロール・レジスタ 3 .....                                    | 61 |

| 表 31. | モジュレータ・コントロール・レジスタ 4 .....                                    | 62 |

| 表 32. | PLL 主レジスタ 1 .....                                             | 62 |

| 表 33. | PLL 主レジスタ 2 .....                                             | 63 |

| 表 34. | PLL 主レジスタ 3 .....                                             | 63 |

| 表 35. | PLL 補助レジスタ 1 .....                                            | 64 |

| 表 36. | PLL 補助レジスタ 2 .....                                            | 64 |

| 表 37. | PLL 補助レジスタ 3 .....                                            | 65 |

| 表 38. | インテロゲータ・コリジョン検出 /IQ 選択設定レジスタ .....                            | 65 |

| 表 39. | エミッタ結合ミキサ・オプション・レジスタ .....                                    | 66 |

| 表 40. | ステータス読出しページ設定レジスタ .....                                       | 67 |

| 表 41. | AGC/ 内部ステータス表示レジスタ .....                                      | 67 |

| 表 42. | RSSI 表示レジスタ .....                                             | 68 |

| 表 43. | AGL/VCO/F_CAL/PilotFreq ステータス表示レジスタ (r2Cpage[1:0] = 00) ..... | 68 |

| 表 44. | AGL/VCO/F_CAL/PilotFreq ステータス・レジスタ (r2Cpage[1:0] = 01) .....  | 69 |

| 表 45. | AGL/VCO/F_CAL/PilotFreq ステータス・レジスタ (r2Cpage[1:0] = 10) .....  | 69 |

| 表 46. | ADC 読取り / レギュレータ設定表示レジスタ (r2Dpage[1:0] = 00) .....            | 70 |

| 表 47. | ADC 読取り / レギュレータ設定表示レジスタ (r2Dpage[1:0] = 01) .....            | 70 |

| 表 48. | コマンド・ステータス表示レジスタ .....                                        | 71 |

| 表 49. | バージョン・レジスタ .....                                              | 71 |

|       |                                           |    |

|-------|-------------------------------------------|----|

| 表 50. | 割込み有効化レジスタ 1 .....                        | 72 |

| 表 51. | 割込み有効化レジスタ 2 .....                        | 72 |

| 表 52. | 割込みレジスタ 1 .....                           | 73 |

| 表 53. | 割込みレジスタ 2 .....                           | 74 |

| 表 54. | FIFO ステータス・レジスタ .....                     | 75 |

| 表 55. | Rx 長レジスタ 1 .....                          | 75 |

| 表 56. | Rx 長レジスタ 2 .....                          | 76 |

| 表 57. | Tx 設定レジスタ .....                           | 76 |

| 表 58. | Tx 長レジスタ 1 .....                          | 77 |

| 表 59. | Tx 長レジスタ 2 .....                          | 77 |

| 表 60. | FIFO I/O レジスタ .....                       | 78 |

| 表 61. | ST25RU3993 ピン定義 .....                     | 79 |

| 表 62. | 電気的パラメータ .....                            | 82 |

| 表 63. | 静電気放電 .....                               | 82 |

| 表 64. | 連続消費電力 .....                              | 82 |

| 表 65. | 温度範囲と保存条件 .....                           | 82 |

| 表 66. | 動作条件 .....                                | 83 |

| 表 67. | 差動ミキサ .....                               | 84 |

| 表 68. | シングルエンド・ミキサ .....                         | 84 |

| 表 69. | CMOS 入力（全 CMOS 入力に適用） .....               | 85 |

| 表 70. | CMOS 入力（全 CMOS 入力に適用） .....               | 85 |

| 表 71. | 標準動作特性 .....                              | 86 |

| 表 72. | QFN48、7x7 mm、0.5 mm ピッチ、パッケージ機械的データ ..... | 88 |

| 表 73. | 発注情報体系 .....                              | 89 |

| 表 74. | 文書改訂履歴 .....                              | 90 |

## 図の一覧

|       |                                 |    |

|-------|---------------------------------|----|

| 図 1.  | ST25RU3993 ブロック図                | 10 |

| 図 2.  | 基本 UHF リーダライタ・システム              | 11 |

| 図 3.  | 可能な SPI コンフィギュレーション             | 16 |

| 図 4.  | 単一バイト書込み                        | 17 |

| 図 5.  | アドレス自動インクリメントを使用したレジスタ書き込み      | 17 |

| 図 6.  | 単一バイト読み込み                       | 18 |

| 図 7.  | アドレス自動インクリメントを使用したレジスタからの読み込み   | 18 |

| 図 8.  | SPI 書込みタイミング                    | 24 |

| 図 9.  | SPI 読込みタイミング                    | 25 |

| 図 10. | PLL/VCO 部                       | 26 |

| 図 11. | 送信部                             | 30 |

| 図 12. | レシーバ部                           | 35 |

| 図 13. | ST25RU3993 ピン配列                 | 79 |

| 図 14. | QFN48、7x7 mm、0.5 mm ピッチ、パッケージ外形 | 87 |

# 1 説明

ST25RU3993デバイスは次の用途に最適です。

- 飲料販売機などコスト制約のあるコンスマーマ/産業向け組込み用途

- ハンドヘルド・リーダライタ

- モバイルUHF RFIDリーダライタ

- バッテリ駆動の据え置き型リーダライタ

## 1.1 ブロック図

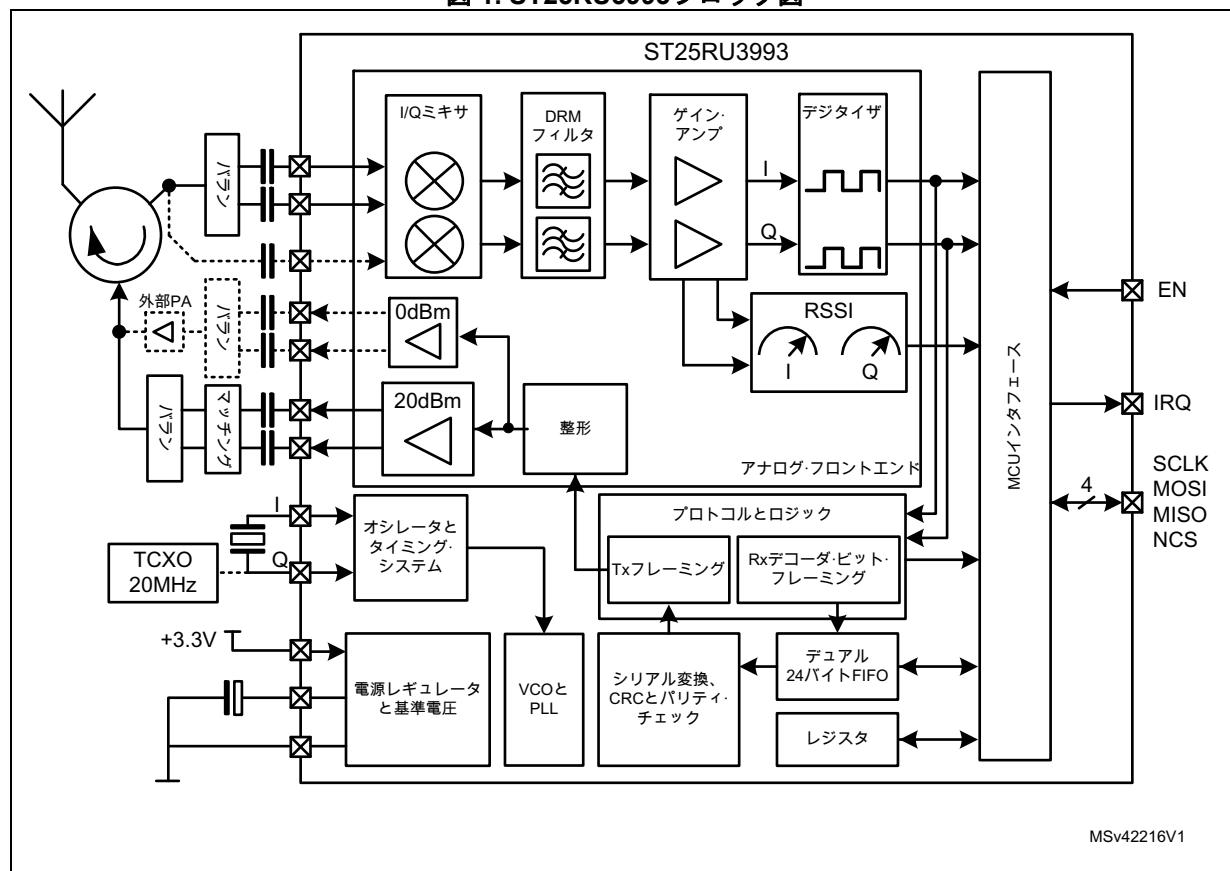

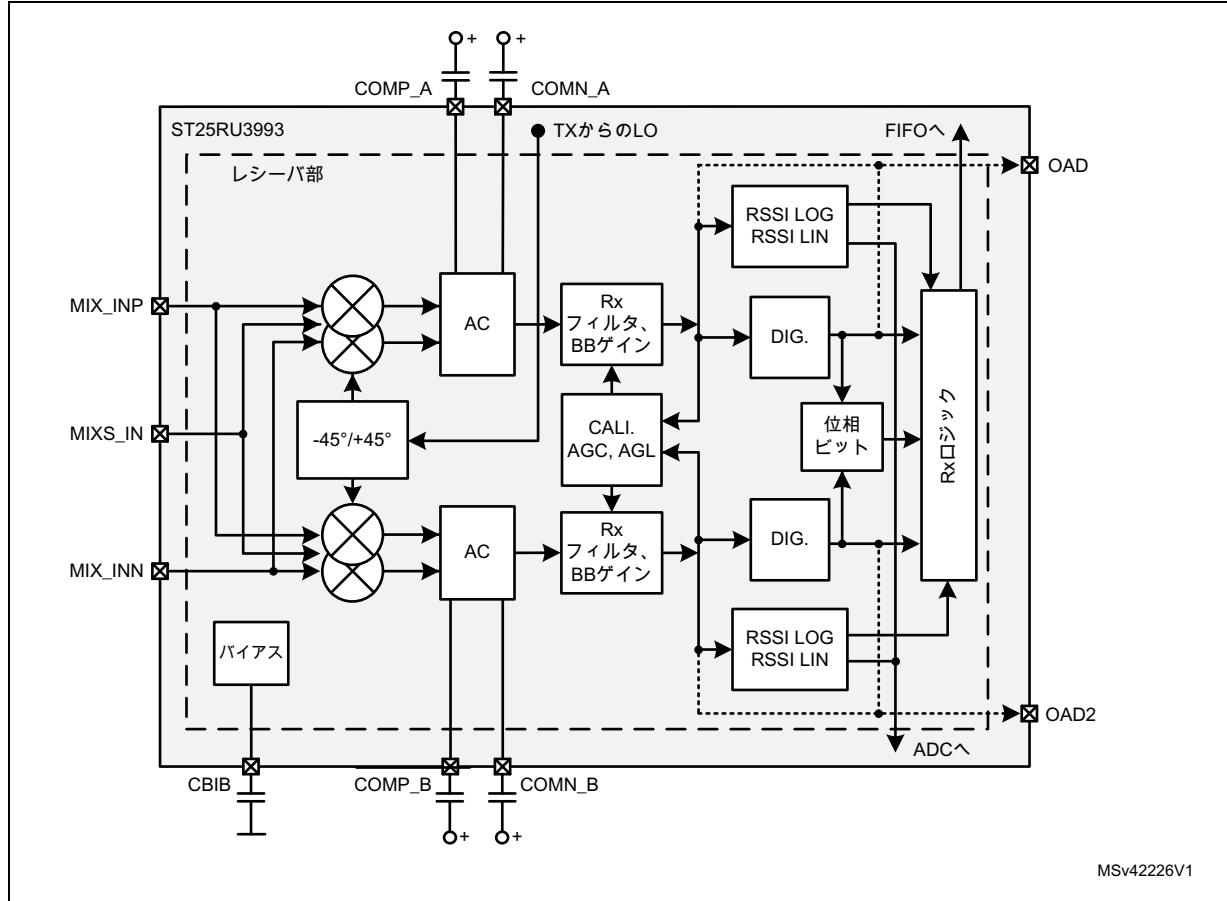

ブロック図を図1に示します。

図1. ST25RU3993ブロック図

## 2 機能概要

ST25RU3993 UHFリーダライタ・デバイスには、UHF RFIDリーダライタ用のアナログ・フロントエンドとプロトコル処理システムが内蔵されています。このチップは3.3 V電源で動作しますので、低電圧の低消費電力用途に最適です。

ETSI地域とFCC地域において使用されているDRMリンク周波数（対応リンク・モードは[セクション 2.9.4: Rx フィルタ参照](#)）での動作に対応しています。ノーマル・モードでEPC Class1 Gen2プロトコル（ISO 18000-6C）に、ダイレクト・モードでISO 18000-6A/Bにそれぞれ準拠しています。

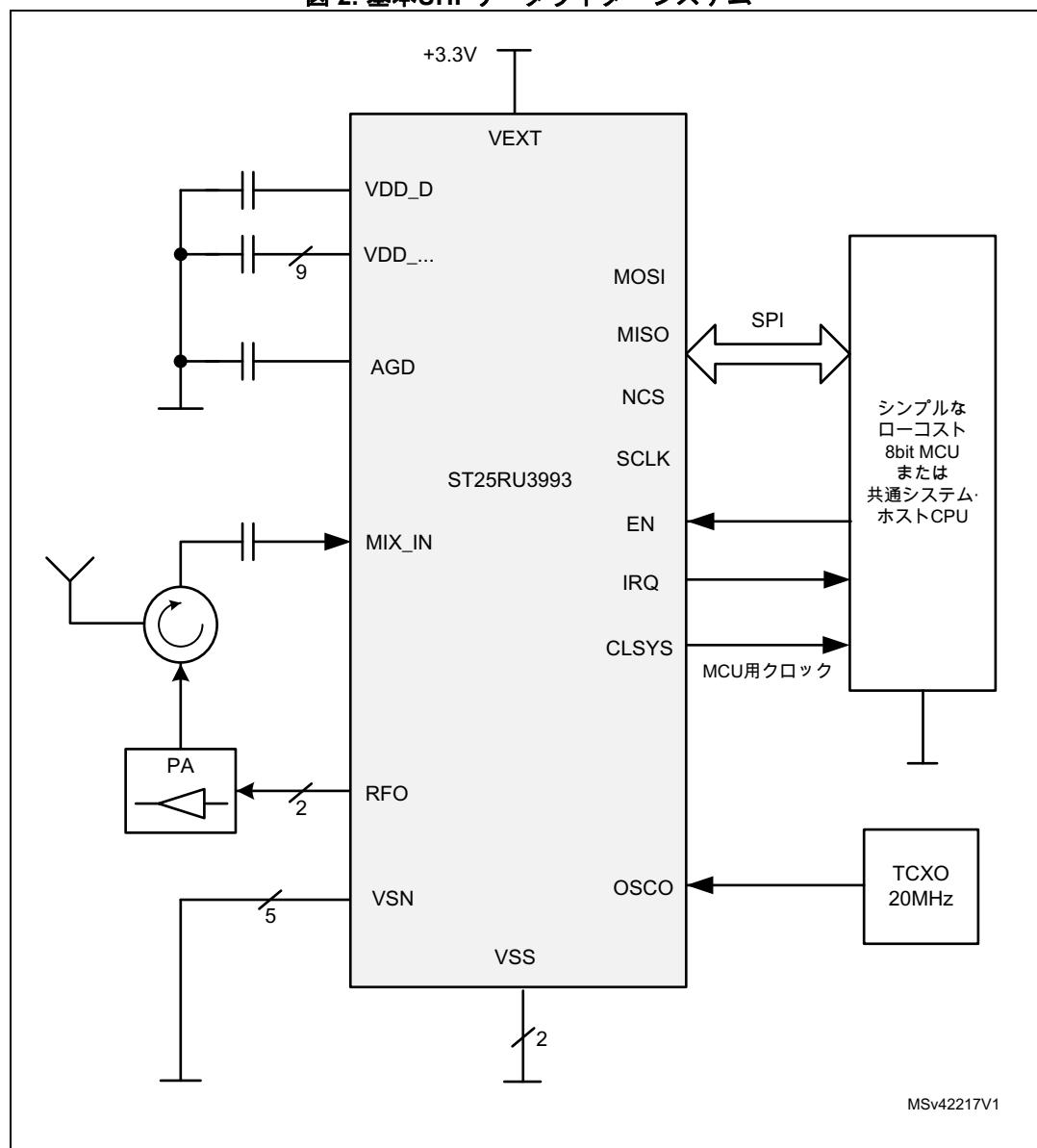

図 2. 基本UHFリーダライタ・システム

このRFIDリーダライタ・デバイスは、リーダライタ動作に必要なアナログ機能とデジタル機能をすべて備えており、EPC Class1 Gen2（ISO18000-6C）デジタル・プロトコルに完全対応した送受信部が含まれています。

このリーダライタは、デバイスのENピンを正論理レベルに設定することで有効化されます。ホスト・システム（MCU）とリーダライタ・デバイスとの間の通信には、4線式シリアル・ペリフェラル・インターフェース（SPI）が用いられます。IRQピンが論理Highレベルになることで、MCUはIRQ処理の通知を受けます。すべてのコントロール・レジスタに直接アクセスすることで、デバイスの構成とリーダライタ性能の微調整が行なえます。ベースバンド・データは、デュアル構成の24バイトFIFOバッファ・レジスタを介して、リーダライタ・デバイスとの転送が行われます。伝送システムには、パラレル/シリアル・データ変換、低レベル・データ・エンコーディング、FrameSyncとPreambleと巡回冗長検査（CRC）の自動生成が含まれています。

次の2本のトランスマッタ出力ポートが利用可能です。

- ローパワー高直線性0 dBm差動出力1本（そのパワーでシングルエンド50 Ω負荷を駆動）

- 内部PAにより増幅されたハイパワー差動出力1本（ハイパワー出力は最大で20 dBm供給し、シングルエンド50 Ω負荷が必要）

どちらの出力も、振幅シフトキーイング（ASK）または位相反転振幅シフトキーイング（PR-ASK）で整形された変調が可能です。内蔵の電源電圧レギュレータによって、リーダライタ・システム全体の電源リップル除去が保証されます。

レシーバ・システムはAM復調とPM復調の両方を確実に行い、独自開発の自動ゲイン・コントロール・システムを含んでいます。

選択式のゲイン段と信号帯域幅によって、広範囲な入力リンク周波数とビット・レートのオプションに対応可能です。AM変調とPM変調の信号強度が測定されており、[RSSI表示レジスタ](#)（2Bh）を通じてアクセス可能です。レシーバ出力は、デジタル化されたサブキャリア信号と内部サブキャリア・デコーダ出力のいずれかを選択可能です。内部デコーダ出力から、ビット・ストリームとデータ・クロックが得られます。

レシーバ・システムには、ベースバンド・データのフレーミング・システムが含まれています。システムはCRCチェックを実行し、データをバイト列に構成します。ここで得られたバイト列は、24バイトFIFOレジスタを通じてホスト・システムからアクセス可能です。

部品表（BOM）を可能な限り小さくするために、内蔵電圧制御発振器（VCO）を備えたオンボードPLL部、部分的に一体化されているループ・フィルタ、電源部、ADC部、ホスト・インターフェース部も含まれています。広範囲な用途に対応するため、このリーダライタ・デバイスは複数の構成に対応しています。レジスタ部によって、全ブロックの動作とふるまいの設定が行われます。

このデバイスには、VEXTピンとVEXT\_PAピンから電源を供給する必要があります。電源の接続を[電源](#)に示します。デバイスの起動時に、コンフィギュレーション・レジスタ群はデフォルト値にプリセットされます。デフォルト値は、すべてのオプション・ビットとともに、コンフィギュレーション・レジスタ表に記載されています。リーダライタ・デバイスとトランスポンダの間の通信は、リーダ・トーク・ファースト方式に従います。デバイスが起動し、レジスタの設定が終わると、RFフィールドをONとし最初のプロトコル・コマンドを送信することで、ホスト・システム（MCU）はトランスポンダとの通信を開始できます。送受信は次の2つのモードで行うことが出来ます。

- ノーマル・モード

- ダイレクト・モード

ノーマル・モードでは、ベースバンド・データはダブルFIFOバッファを通じて転送され、プロトコル・データ処理はすべて内部で行われます。ダイレクト・モードでは、送受信でエンコーダとデコーダがバイパスされますので、データ処理はMCUが行う必要があります。ダイレクト・モードでは、MCUがアナログ・フロントエンド処理をリアルタイムで実行可能です。

## 2.1 電源

このデバイスは、外部電源のノイズと妨害による影響を最小限に抑え、異なる内部構成要素間のデカップリングを向上するための、自前の電源システムを備えています。

正電源ピンは、VEXTとVEXT\_PAです。負電源ピンはすべてのVSNピンとVSSピンですが、露出ダイ・パッドも含まれます。電源リジェクションとデバイス性能を最適なものとするには、電源電圧が3.3 V以上である必要があります。電源電圧が3.0 V以上であれば、低下した電源リジェクション性能での動作が可能です。電源電圧がそれよりも低い（ただし2.7 Vまで）場合には、デバイス性能の低下を見込む必要があります。

### 2.1.1 メイン・レギュレータ

調整可能なレギュレータがセットで使用されており、デバイスのさまざまな内部構成要素に電源を供給します。大部分のレギュレータに対して共通となる入力ピンはVEXTです。レギュレータ出力は、VDD\_AとVDD\_LFとVDD\_DとVDD\_MIXとVDD\_Bの各ピンです。各レギュレータ出力には、GNDに対するシャント・コンデンサが必要となります。標準値は2.2  $\mu$ Fと100 pFであり、（最低でも）X5Rクラスのセラミック・コンデンサを推奨します。VDD\_LFIとVDD\_TXPABは電源入力ピンであり、VDD\_MIXに接続する必要があります。

安定化出力電圧は、[レギュレータ/PAバイアス・レジスタ \(0Bh\)](#) のオプション・ビットrvs[2:0]を使って、2.7 Vから最大3.4 Vまで、0.1 Vステップで設定可能です。ダイレクト・コマンドAutomatic Power Supply Level Setting (A2h) を使って、安定化出力電圧を、電源電圧V<sub>EXT</sub>よりも約300 mV低い電圧に自動調整することもできます。

### 2.1.2 内部PA電源レギュレータ

内部パワー・アンプには専用の電圧レギュレータが備わっています。入力ピンはVEXT\_PA、出力はVDD\_PAです。レギュレータには内部補償回路が備わっており、VDD\_PAに小容量の外付けコンデンサ（通常1 nF）が必要です。この電圧レギュレータは、負荷がかかった状態でのみ動作可能です。

安定化出力電圧は、[レギュレータ/PAバイアス・レジスタ \(0Bh\)](#) のオプション・ビットrvs\_rff[2:0]を使って、2.7 Vから最大3.4 Vまで、0.1 Vステップで設定可能です。ダイレクト・コマンドAutomatic Power Supply Level Setting (A2h) を使って、安定化出力電圧を、電源電圧V<sub>EXT</sub>よりも約300 mV低い電圧に自動調整することもできます。

rvs\_rff[2:0]の設定内容と自動電源レベル調整は値が異なるのが普通ですので、VDD\_PAには最も低い電圧レベルを自動選択するようにシステム設計されています。

### 2.1.3 ペリフェラル通信電源

ホスト・システム（MCU）との通信に使用される論理レベルは、広い電圧範囲で変動する可能性があります。VDD\_IO入力ピンを用いて、1.65 Vから5.5 Vまでの間でその論理レベルを設定します。電圧の不整合を回避するため、VDD\_IOをホスト・システムの電源に接続することを推奨します。

### 2.1.4 自動電源レベル設定

電源部には、レギュレータ内部で良好な電源リジェクションを得るために必要である、V<sub>EXT</sub>電源電圧よりも300 mVほど低い値にレギュレータを自動調整するシステムが含まれています。

ダイレクト・コマンドAutomatic Power Supply Level Setting (A2h) によって、このシステムが作動します。手動電源レベル調整に戻すには、ダイレクト・コマンドManual Power Supply Level Setting (A3h) を送信する必要があります。

ダイレクト・コマンド (A2h) を発行する前には、許容された目標周波数（840 MHzから960 MHz）の中にPLLを設定して、ロックする必要があります。

自動調整の開始時に、デバイスはレギュレータを3.4 Vに設定し、RFフィールドが通常の電源負荷をシミュレートできるようにします。このプロシージャの間、デバイスは安定化電圧を100 mVステップで低下させます。各ステップには300  $\mu$ sかかります。レギュレータが設定可能な最低電圧は2.7 Vです。

$V_{EXT}$ と安定化電圧との間の差が300 mV以上となるか、最終ステップに到達すると、プロシージャは停止します。その後、デバイスはRFフィールドを無効化し、Irq\_cmdビット（レジスタ36h）をHighにセットしてIRQリクエストを送信します。

## 2.1.5 電源モード

デバイスは、次の4種類の主な電源モードを備えています。

- パワー・ダウン・モード

- スタンバイ・モード

- ノーマル・モード – RF OFF

- ノーマル・モード – RF ON

### パワー・ダウン・モード

ENピンを論理Lowレベルに落とすと、デバイスはパワー・ダウン・モードとなります。このモードでは、回路は無効となります。

### スタンバイ・モード

オプション・ビットstby（レジスタ00h）をHighにセットすると、ノーマル・モードからスタンバイ・モードになります。スタンバイ・モードでは、電圧レギュレータと基準電圧システムと水晶発振器はローパワー・モードで動作します。PLLとトランスマッタ出力段とレシーバはオフになります。スタンバイ・モードとノーマル・モードとの切り替わりの間、レジスタ設定はすべて保持されます。通常、バイアス電圧と基準電圧はstby = 0から12 ms以内に安定します。それまでに、デバイスはRFフィールドの起動とデータ送信の用意が整います。

### ノーマル・モード – RF OFF

ENピンを論理Highレベルに設定すると、ノーマル・モードとなります。このモードでは、以下の内部ブロックが有効化されています。

- 電源レギュレータすべて

- 基準電源とバイアス・システム

- 水晶発振器

- RF発振器とPLL

ENピンが論理Highレベルに設定されると、バイアスと基準電圧は12 ms後（標準値）に安定します。それ以降、デバイスは内部レジスタとの相互作用が可能となります。基準周波数源が安定し、CLSYSクロックが有効になると、デバイスはその内部レジスタの設定内容に従って動作可能となります。水晶発振器が使用された場合、水晶振動子が安定するまでの時間は、使用する水晶の種類に依存します。標準的な時間は1.5 ~ 3 msとなります。[AGC/内部ステータス表示レジスタ](#) (2Ah) を読み込むことにより、MCUは水晶振動子の状態を確認できます。このレジスタのステータス・ビットosc\_ok = 1は、水晶の発振が安定しており、デバイスが動作可能であることを示します。

連続動作するTCXOが使用された場合、設定の必要があるのはOSCOピンのDCレベルだけであるため、内部クロックの整定は高速化されます。上記の同じosc\_okステータス・ビットのテストを流用可能です。

さらに500 ms（標準値）経過すると、デバイスは、トランスポンダとの通信のためにRFフィールドをオンにしてインベントリ・コマンドを送信する用意が整います。

## ノーマル・モード – RF ON

**デバイス・ステータス・コントロール・レジスタ** (00h) のrf\_onオプション・ビットを設定すると、デバイスは直ちにフィールドの立ち上げを始めます。立ち上げの時間と形状は、**ミュレータ・コントロール・レジスタ3** (15h) のtrfon[1:0]とlin\_modのオプション・ビットによって定義されます。RFフィールドの立ち上げが完了すると、ステータス・ビットrf\_ok (レジスタ2Ah) がHighにセットされます。さらにはIRQが生成され、irq\_anaステータス・ビット (レジスタ38h) がHighにセットされることで通知されます。

オプション・ビットrf\_onをLowにセットすると、フィールドの立ち下げが始まります。RFフィールドは、trfon[1:0]ビットとlin\_modビット (レジスタ15h) に従って減少します。このステップが完了すると、**AGC/内部ステータス表示レジスタ** (2Ah) のステータス・ビットrf\_okがLowにセットされ、irq\_anaステータス・ビットをHighとしてIRQが送信されます。

利用可能な電源モードと、各モード間の遷移時間が表1にまとめられています。

表1. 電源モード概要

| モード                | EN<br>ピン | Stby<br>オプション<br>ビット | rf_on<br>オプション<br>ビット | 消費電流  | モードに入るための時間<br>ダイレクト・モード                | モードからRFフィールドが<br>有効になるまでの時間                 |

|--------------------|----------|----------------------|-----------------------|-------|-----------------------------------------|---------------------------------------------|

| パワー<br>ダウソ         | L        | -                    | -                     | 1 μA  | ノーマル・モードから直ちに                           | 12 ~ 17 ms (水晶または<br>TCXOの起動 + バイアスの<br>起動) |

| スタンバイ              | H        | H                    | L                     | 3 mA  | ノーマル・モードから直ちに                           | 12 ~ 17 ms (水晶または<br>TCXOの起動 + バイアスの<br>起動) |

| ノーマル               | H        | L                    | L                     | 24 mA | 12 ~ 17 ms (水晶またはTCXO<br>の起動 + バイアスの起動) | 12.5 μs<br>(フィールドの立ち上げ)                     |

| RFフィールド<br>ONのノーマル | H        | L                    | H                     | 75 mA | 12.5 μs<br>(フィールドの立ち上げ)                 | NA                                          |

## 2.2 ホスト通信

デバイスとの通信には、標準の4線式シリアル・インターフェース (SPI) が、割込みリクエスト・ライン (IRQピン) とともに使用されます。MCUに対するシステム・クロック源として、追加のライン (CLSYS) を使用することもできます。

表2. シリアル・データ・インターフェース (SPIインターフェース) 信号ライン

| 名称    | 信号                 | 信号レベル | 説明                  |

|-------|--------------------|-------|---------------------|

| NCS   | デジタル入力             | CMOS  | SPIイネーブル (アクティブLow) |

| SCLK  | デジタル入力             | CMOS  | シリアル・クロック           |

| MOSI  | デジタル入力             | CMOS  | シリアル・データ入力          |

| MISO  | トライステート・<br>デジタル出力 | CMOS  | シリアル・データ出力          |

| IRQ   | デジタル出力             | CMOS  | 割込み要求出力             |

| CLSYS | デジタル出力             | CMOS  | MCUクロック出力           |

NCSピンをLowに設定すると、SPIインターフェースが有効化されます。NCSがHighの間は、SPIインターフェースの動作は停止しています。SPIインターフェースを使用しないときには、常にNCSをHighに保つことを推奨します。SCLKの立下りエッジでMOSIがサンプリングされます。SPI通信はバイト単位で行われます。(NCSがHighからLowになった後、) MOSIラインの最初のバイトの最初の2ビットによって、SPIの動作モードが定義されます。MSBビットは必ず最初に送信されます(アドレスとデータが該当)。

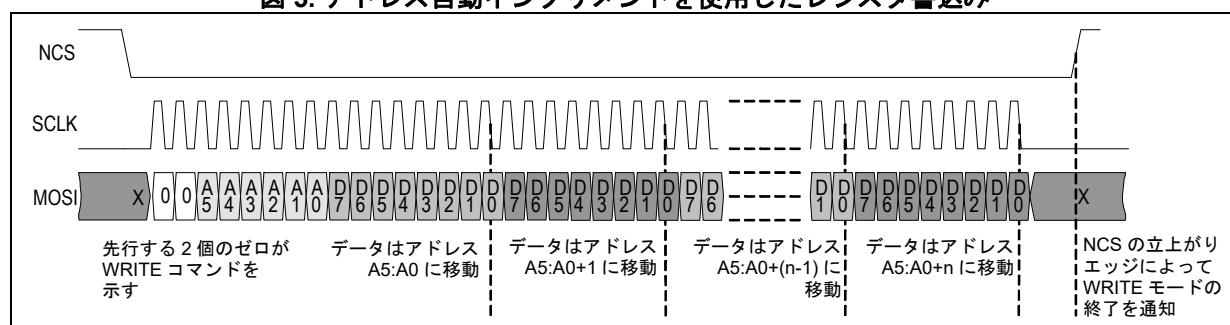

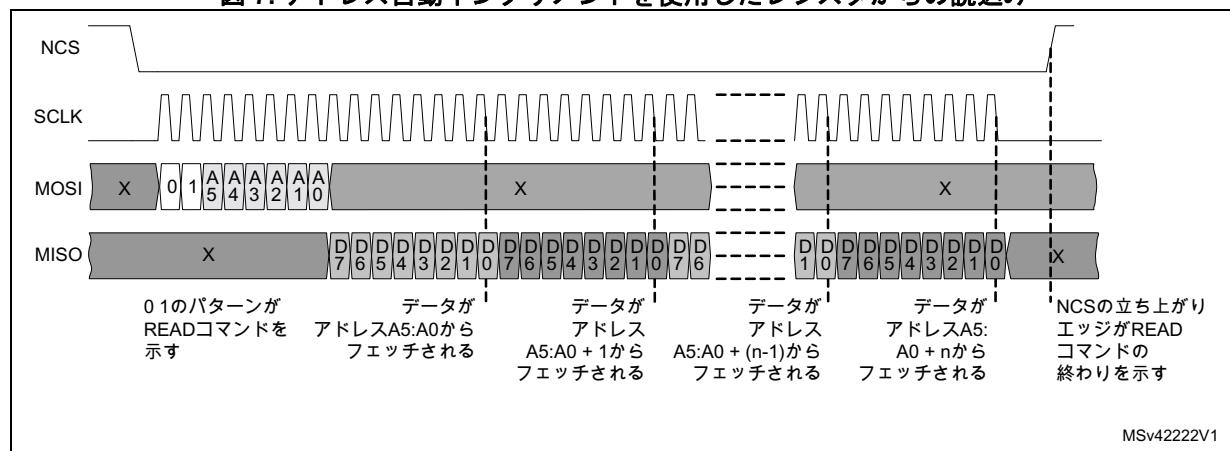

読み込みモードと書き込みモードは、複数バイト転送のアドレス自動インクリメントに対応しています。連続した読み込みまたは書き込みでは、最初のアドレスのみ送信する必要があります。アドレスは内部的にインクリメントされます。

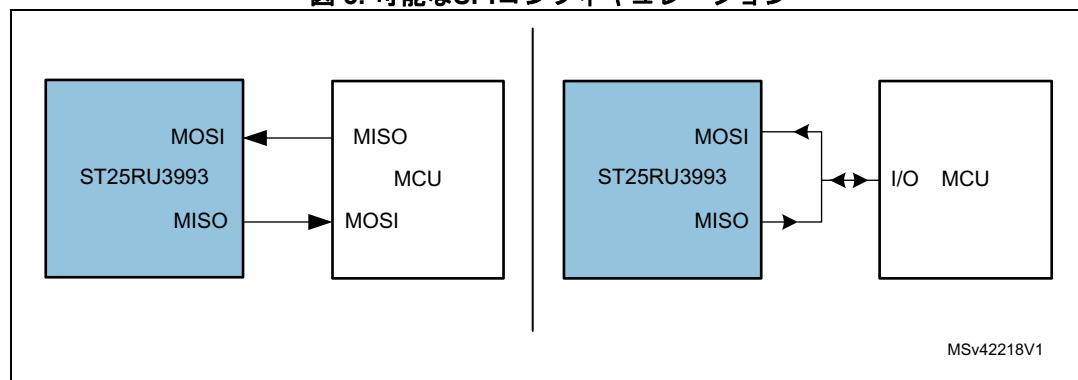

通常、MISO出力はトライステートであり、出力データ有効時にのみ駆動されます。これによって、MOSIラインとMISOラインを外部で短絡して、双方向信号を生成することが可能となります(図3参照)。

MISO出力がハイインピーダンスである間、[補助レジスタ1](#)(0Dh)のオプション・ビットmiso\_pd1とmiso\_pd2を設定することで、50 kΩプルダウン抵抗を有効にできます。

SPI相互接続の可能なオプションを図3に示します。

図3. 可能なSPIコンフィギュレーション

表3. SPIデータ・モード

| コマンド種別     | モード・パターン (MSBからLSB) |    |                    |    |    |    |    |    | モード関連データ                     |  |

|------------|---------------------|----|--------------------|----|----|----|----|----|------------------------------|--|

|            | モード                 |    | レジスタ・アドレス / コマンドID |    |    |    |    |    |                              |  |

|            | M1                  | M2 | X5                 | X4 | X3 | X2 | X1 | X0 |                              |  |

| 書き込み       | 0                   | 0  | A5                 | A4 | A3 | A2 | A1 | A0 | データ・バイト (自動インクリメントの場合は追加バイト) |  |

| 読み込み       | 0                   | 1  | A5                 | A4 | A3 | A2 | A1 | A0 | データ・バイト (自動インクリメントの場合は追加バイト) |  |

| ダイレクト・コマンド | 1                   | 0  | C5                 | C4 | C3 | C2 | C1 | C0 | -                            |  |

| RFU        | 1                   | 1  | X                  | X  | X  | X  | X  | X  | -                            |  |

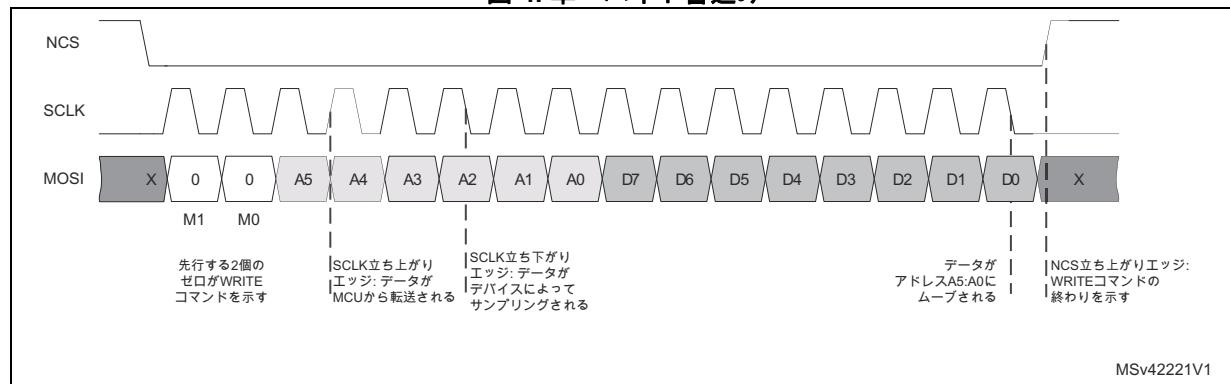

## 2.2.1 レジスタへの書き込み

単一バイトの場合と、アドレス自動インクリメントを用いた複数バイトの場合について、標準的なSPI書き込み通信の例を図4と図5に示します。SPI動作モード・ビット(M1とM2)に続いて、対象レジスタのアドレス・ビット(A5:A1)が送信されます。その後、自動インクリメントを使用するか否か次第で、データ・バイトが1バイトまたは複数バイト送信されます。通信は、NCSをHighに戻すことにより終了します。8ビット(1バイト)のパケットが送信される前にこれが発生した場合には、このレジスタへの書き込みは行われません。設定されたアドレスのレジスタが存在しない場合や、それが読み出し専用レジスタである場合にも、書き込みコマンドは成功しません。

単一バイトに対するSPI書き込みコマンドの例を図4に示します。

図4. 単一バイト書き込み

複数バイトにシグナルを送るSPI書き込みコマンドの例を図5に示します。

図5. アドレス自動インクリメントを使用したレジスタ書き込み

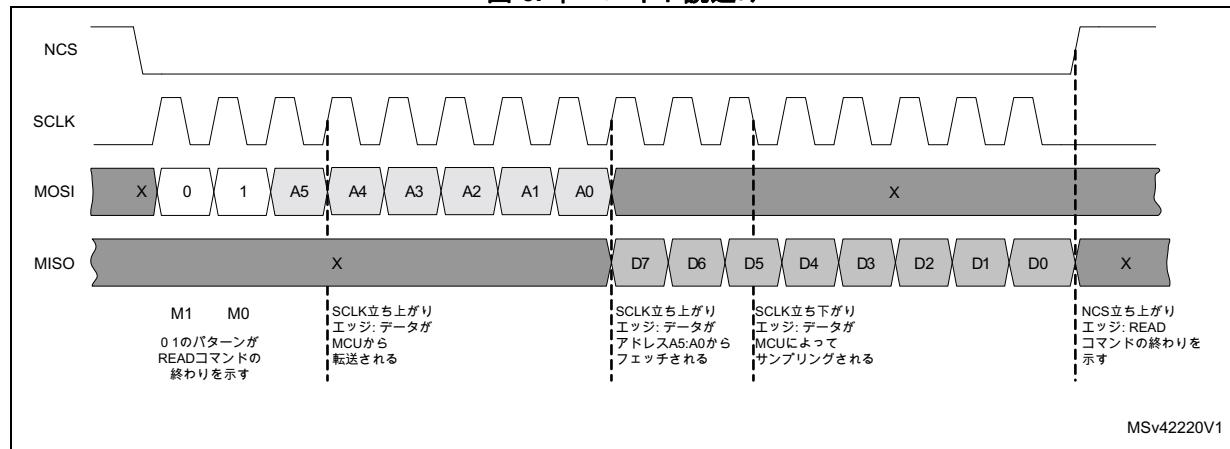

## 2.2.2 レジスタからの読み込み

SPI動作モード・ビット（M1とM0）の後、対象アドレスが送信されます。その後、データ・バイトが1バイトまたは複数バイトMISO出力に転送されます。SCLKの立下りエッジでMOSIがサンプリングされます。内部レジスタから読み込まれるデータは、SCLKの立上がりエッジでMISOピンに転送されますので、MCUIは立下りエッジでサンプリングする必要があります。レジスタのアドレスが存在しない場合には、オール0のデータがMISOに送信されます。

単一バイトに対する標準的なSPI読み込みコマンドの例を図6に示します。

図6. 単一バイト読み込み

複数バイトにシグナルを送るSPI読み込みコマンドの例を図7に示します。

図7. アドレス自動インクリメントを使用したレジスタからの読み込み

## 2.2.3 ダイレクト・コマンド

ダイレクト・コマンドにはパラメータがないため、送信の必要があるのは1バイトのみとなります。唯一の例外がQueryコマンドで、コマンド・バイトに続けて2バイトのパラメータ・バイト(FIFOに格納)が必要です。SPI動作モード・ビットがM1 = 1かつM0 = 0である場合に、ダイレクト・コマンドとなります。それに続く6ビットがダイレクト・コマンドIDの定義です。ダイレクト・コマンドは、SCLKの最終立下りエッジで実行されます。ダイレクト・コマンドの中にはすぐに実行されるものもありますが、特定時間要する処理(補正や測定など)を開始するものもあります。

**注意:** このようなコマンドの実行中には、SPIインターフェースで別の処理を開始しないことを推奨します。

ダイレクト・コマンドの実行後には、IRQ\_CMDビット(レジスタ38h)をHighにセットしてIRQリクエストが送信されます。

表 4. ダイレクト・コマンド一覧

| コード(16進) | コマンド                                       | ダイレクト実行 |

|----------|--------------------------------------------|---------|

| 80h      | Idle                                       | Y       |

| 81h      | Direct Mode                                | Y       |

| 83h      | Soft Init                                  | Y       |

| 84h      | Hop to Main Frequency                      | Y       |

| 85h      | Hop to Main Frequency                      | Y       |

| 87h      | Trigger AD Conversion                      | N       |

| 88h      | Trigger Rx Filter Calibration              | N       |

| 89h      | Decrease Rx Filter Calibration Data        | Y       |

| 8Ah      | Increase Rx Filter Calibration Data        | Y       |

| 90h      | Transmission with CRC                      | Y       |

| 91h      | Transmission with CRC Expecting Header Bit | Y       |

| 92h      | Transmission without CRC                   | Y       |

| 96h      | Block Rx                                   | Y       |

| 97h      | Enable Rx                                  | Y       |

| 98h      | Query                                      | Y       |

| 99h      | QueryRep                                   | Y       |

| 9Ah      | QueryAdjustUp                              | Y       |

| 9Bh      | QueryAdjustNic                             | Y       |

| 9Ch      | QueryAdjustDown                            | Y       |

| 9Dh      | ACK                                        | Y       |

| 9Fh      | ReqRN                                      | Y       |

| A2h      | Automatic power supply level setting       | N       |

| A3h      | Manual power supply level setting          | Y       |

| A4h      | Automatic VCO range selection              | N       |

| A5h      | Manual VCO range selection                 | Y       |

| A6h      | AGL On                                     | Y       |

| A7h      | AGL Off                                    | Y       |

表 4. ダイレクト・コマンド一覧（続き）

| コード（16進） | コマンド                                        | ダイレクト実行 |

|----------|---------------------------------------------|---------|

| A8h      | Store RSSI                                  | Y       |

| A9h      | Clear RSSI                                  | Y       |

| AAh      | Interrogator anti-collision support enable  | Y       |

| ABh      | Interrogator anti-collision support disable | Y       |

## ダイレクト・コマンドの説明

ST25RU3993が対応しているダイレクト・コマンドを以下に詳しく説明します。括弧内の値は、関連するコマンド・バイトを示します。

- **Direct mode** (81h) : デバイスがダイレクト・モードに入ります。

- **Soft init** (83h) : このコマンドによって、設定レジスタ群がそのデフォルト値にリセットされ、過去にトリガされていた機能はすべて終了します。

- **Hop to main frequency** (84h) : このコマンドによって、PLL主レジスタ1～3に定義されている周波数をPLLが強制的に使用します。PLL主レジスタがデフォルトで使用されます。

- **Hop to Main Frequency** (85h) : このコマンドによって、*PLL補助レジスタ1*と*PLL補助レジスタ2*と*PLL補助レジスタ3*に定義されている周波数設定をPLLが強制的に使用します。

- **Trigger A/D conversion** (87h) : このコマンドによって、内部8ビットA/Dコンバータを使用したアナログ/デジタル変換がトリガれます。詳細は、A/Dコンバータに関する説明を参照してください。

- **Trigger Rx filter calibration** (88h) : このコマンドによって、Rxフィルタ補正プロセッサがトリガれます。詳細は、Rxフィルタ補正に関する説明を参照してください。

- **Decrease Rx filter calibration data** (89h) と **Increase Rx filter calibration data** (8Ah) : これらのコマンドによって、自動取得されたRxフィルタ補正データが調整されます。詳細は、Rxフィルタ補正に関する説明を参照してください。

- **Transmission with CRC** (90h) : 転送コマンドを使用して、リーダライタからトランスポンダにデータを転送します。最初に、転送する完全バイトのバイト数を、不完全バイトのビット数を含めて、Tx長レジスタ (3Dhと3Eh) に設定する必要があります。その後に送信データをFIFOレジスタ (3Fh) にロードできます。最初のバイトがロードされると転送が始まります。転送シーケンスにはCRC-16が含まれています。

すべての送信データをロードする最適な方法は、アドレス3Dhで始まる連続書き込みモードを使用することです。

アドレス自動インクリメントを使用した例:

SPIデータ (MOSI) : 90h - 3Dh - 00h - 30h - AAh - BBh - CChは以下のように動作します。

- 90h: Transmission with CRC

- 3Dhに00hを書き込み

- 3Ehに30hを書き込み (3バイトを転送)

- アドレス3FhにAAh、BBh、CChを書き込み (転送されるFIFOデータ)

- **Transmission with CRC expecting header bit** (91h) : 前のコマンドと同様ですが、応答にヘッダ・ビットが見込まれていることについても、Rxデコード・ロジックに通知します。

- **Transmission without CRC** (92h) : ダイレクト・コマンドTransmission with CRCと同様ですが、CRC部は省略されます。

- **Block Rx** (96h) : **Block Rx**コマンドによって、レシーバのデジタル部 (ビット・デコーダとフレーマ) の動作が停止します。システムが雑音の多い環境で動作しており、Rxデジタル部のサブキャリア入力が始終切り替わってしまうような場合には、レシーバをオフにするのが有効です。アクティブ状態のレシーバはブリアンブルの検出を行っており、ノイズ・パターンが予想されている信号パターンに一致すると、割込みが生成されます。割込み要求が絶え間なく流れるのはMCUにとって問題となることがあります、Block RXコマンドを使用して受信デコーダを無効化することで、このような状況を回避可能です。Rx待ち時間の経過後、何らかのデータ送信の最後に、自動的にレシーバは再び有効化されます。Rx待ち時間を設定するには、Rx待ちタイマの項目を参照してください。Block Rxを停止する2番目の方法は、Enable Rx (97h) コマンドの送信です。

- **Enable Rx** (97h) : このコマンドによって、レシーバのアナログ部とデジタル部が受信の準備を行います。手動で受信をトリガするには、このコマンドを送信する必要があります。データ送信コマンドによって受信が自動的にトリガされる場合には、このコマンドを送信すべきではありません。

- **Query** (98h) : QueryコマンドによってEPC Queryが発行され、インベントリ・ラウンドが始まります。Queryコマンドには追加のデータ・バイトが2バイト必要であり、このデータはFIFO (3Fh) に書き込む必要があります。

FIFOの2バイトには次のデータが含まれている必要があります。“00”, DR, M, TRect, Sel, Session, Target, Q

これを合計すると15ビットとなり、LSBビットは無視されます。

最後に、トランスマッタは次のデータを送信します。

- プリアンブル

- コマンドID

- Txデータ (FIFOの2バイト)

- CRC-5

- 受信したRN16は、その後の通信ステップ (ACK、ReqRN) のために内部RN16レジスタに格納されます。RN16はFIFOにも格納されます。

- **QueryRep** (99h) : QueryRepコマンドは、EPC Gen2 QueryRepコマンドに続けてセッション・ビットを2ビット発行します。セッション・ビットは、**Tx設定レジスタ** (3Ch) から取得されます。受信したRN16は、その後の通信 (ACK、ReqRN) のために内部RN16レジスタに格納されます。RN16は、FIFOの中でもアクセス可能です。

- **QueryAdjustUp** (9Ah) : QueryAdjustUpダイレクト・コマンドは、EPC Gen2 QueryAdjustコマンドに続けて、セッション・ビットを2ビットと'up'パラメータ (利用可能スロット数を増加) を発行します。セッション・ビットは、**Tx設定レジスタ** (3Ch) から取得されます。受信したRN16は、その後の通信 (ACK、ReqRN) のために内部RN16レジスタに格納されます。RN16は、FIFOの中でもアクセス可能です。

- **QueryAdjustNic** (9Bh) : QueryAdjustNicコマンドは、EPC Gen2 QueryAdjustコマンドに続けて、セッション・ビットを2ビットと'no change'パラメータを発行します。セッション・ビットは、**Tx設定レジスタ** (3Ch) から取得されます。受信したRN16は、その後の通信 (ACK、ReqRN) のために内部RN16レジスタに格納されます。RN16は、FIFOの中でもアクセス可能です。

- **QueryAdjustDown** (9Ch) : QueryAdjustUpコマンドは、EPC Gen2 QueryAdjustコマンドに続けて、セッション・ビットを2ビットと'down'パラメータ (利用可能スロット数を減少) を発行します。セッション・ビットは、**Tx設定レジスタ** (3Ch) から取得されます。受信したRN16は、その後の通信 (ACK、ReqRN) のために内部RN16レジスタに格納されます。RN16は、FIFOの中でもアクセス可能です。

- **ACK** (9Dh) : ACKコマンドは、EPC ACKに続けて、最後に成功したQueryコマンドの間に内部RN16レジスタに格納されたRN16を発行します。

- **NAK** (9Eh) : NAKコマンドは、EPC Gen2 NAKコマンドをタグに発行します。

- **ReqRN** (9Fh) : ReqRNコマンドは、EPC Request RNをタグに発行します。最後に受信したRNはパラメータとして使用され、受信した新規のRN16 (ハンドル) は、その後の通信 (ACK、ReqRN) のために内部RN16レジスタに格納されます。新規のRN16はFIFOにも格納されます。

- **Automatic power supply level setting** (A2h) と **Manual power supply level setting** (A3h) : これらのコマンドによって、オンボード電圧レギュレータの自動調整がトリガされ、手動選択に戻ります。詳細は、ペリフェラル通信電源の説明を参照してください。

- **Automatic VCO range selection** (A4h) と **Manual VCO range selection** (A5h) : これらのコマンドによって、自動VCO範囲選択がトリガされ、手動VCO範囲選択に戻ります。詳細は、PLLとVCOの説明を参照してください。

- **AGL on** (A6h) と **AGL off** (A7h) : これらのコマンドによって、AGL動作のトリガと無効化が行われます。詳細は、AGLの説明を参照してください。

- **Store RSSI** (A8h) と **Clear RSSI** (A9h) : これらのコマンドによって、IQ決定回路に使用可能な受信信号強度インジケータ (RSSI) の格納とクリアが行われます。詳細は、IQ選択の説明を参照してください。

- **Interrogator anti-collision support enable** (AAh) と **Interrogator anti-collision support disable** (ABh) : これらのコマンドによって、ISO 29143に定義されているインテロゲータ・コリジョン防止対応の有効化と無効化が行われます。

### ダイレクト・コマンドの連鎖

即時実行されるダイレクト・コマンドには、その間でNCS信号を非アクティブとすることなく、読み込みや書き込みのような別のSPIコマンドを続けることができます。

## 2.2.4 SPIインターフェース・タイミング

表 5. SPIタイミング・パラメータ

| 記号                                                                          | パラメータ                     | 注記/条件                                                      | 最小 | 標準 | 最大 | 単位   |

|-----------------------------------------------------------------------------|---------------------------|------------------------------------------------------------|----|----|----|------|

| 一般項目 ( $VDD\_IO > 3\text{ V}$ 、 $CLOAD < 50\text{ pF}$ 、 $hs\_output = 1$ ) |                           |                                                            |    |    |    |      |

| $t_{SCLKH}$                                                                 | ビット・レート                   | -                                                          | -  | -  | 5  | Mbps |

| $t_{SCLKL}$                                                                 | クロックHigh時間                | -                                                          | 70 | -  | -  | ns   |

| $t_{NCNL}$                                                                  | クロックLow時間                 | -                                                          | 70 | -  | -  | ns   |

| $t_{NCSL}$                                                                  | NCSセットアップ時間               | NCS が High から Low に遷移してから SCLK が High に初めて遷移するまでの時間        | 10 | -  | -  | ns   |

| $t_{DIS}$                                                                   | データイン・セットアップ時間            | -                                                          | 10 | -  | -  | ns   |

| $t_{DIH}$                                                                   | データイン・ホールド時間              | -                                                          | 10 | -  | -  | ns   |

| $t_{NCSH}$                                                                  | NCSホールド時間<br>(読み込み/書き込み)  | 読み込みまたは書き込みの後、最後のSCLK立下りエッジから NCS が Low から High に遷移するまでの時間 | 10 | -  | -  | ns   |

| $t_{NCSH}$                                                                  | NCSホールド時間<br>(ダイレクト・コマンド) | ダイレクト・コマンドの後、最後のSCLK立下りエッジから NCS が Low から High に遷移するまでの時間  | 70 | -  | -  | ns   |

表 5. SPIタイミング・パラメータ（続き）

| 記号         | パラメータ                 | 注記/条件                                                                                | 最小 | 標準 | 最大 | 単位 |

|------------|-----------------------|--------------------------------------------------------------------------------------|----|----|----|----|

| 読み込みタイミング  |                       |                                                                                      |    |    |    |    |

| $t_{DOD}$  | データ・アウト遅延             | $V_{DD\_IO} \geq 3\text{ V}$ 、<br>$C_{LOAD} = 50\text{ pF}$ 、<br>$hs\_output = 1$    | -  | 30 | -  | ns |

| $t_{DOD}$  | データ・アウト遅延             | $V_{DD\_IO} \geq 1.65\text{ V}$ 、<br>$C_{LOAD} = 50\text{ pF}$ 、<br>$hs\_output = 1$ | -  | 60 | -  | ns |

| $t_{DOD}$  | データ・アウト遅延             | $V_{DD\_IO} \geq 3\text{ V}$ 、<br>$C_{LOAD} = 50\text{ pF}$ 、<br>$hs\_output = 0$    | -  | 90 | -  | ns |

| $t_{DOHZ}$ | データ・アウトからハイ・インピーダンス遅延 | SPIがMISOラインをリリースするまでの時間                                                              | -  | 40 | -  | ns |

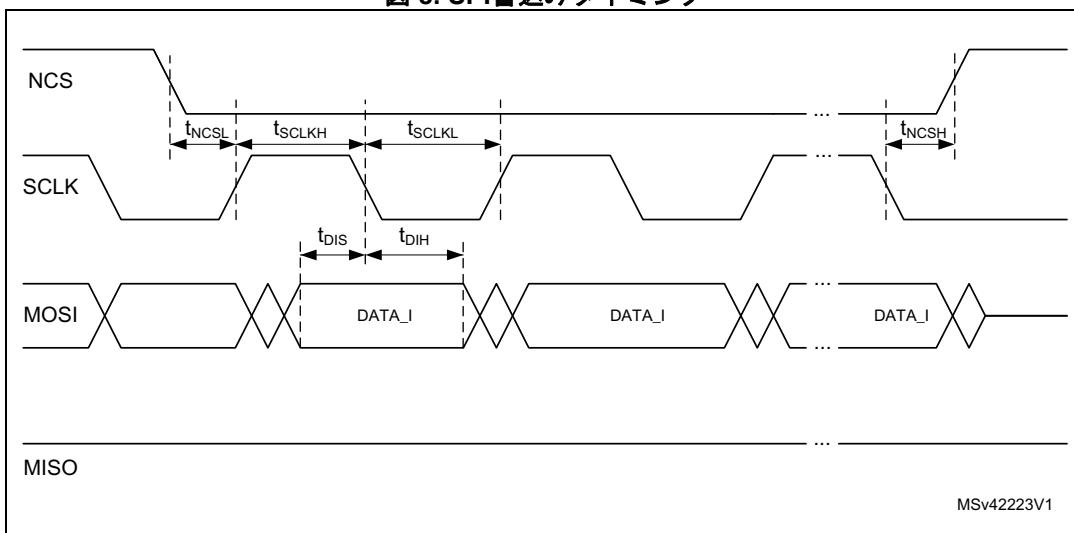

SPI書き込みコマンドに対応するタイミング波形とパラメータを図 8に示します。

図 8. SPI書き込みタイミング

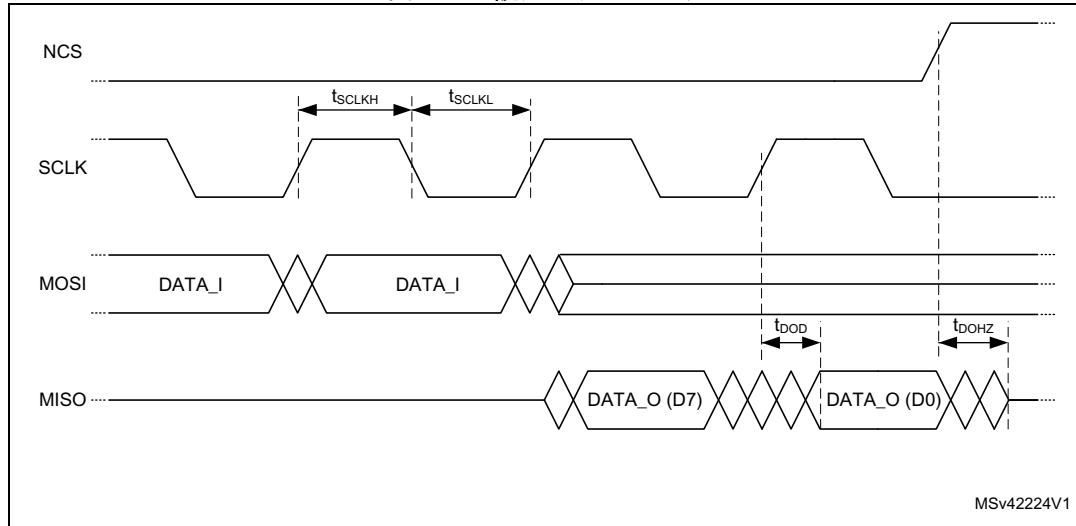

SPI読み込みコマンドに対応するタイミング波形とパラメータを図9に示します。

図9. SPI読み込みタイミング

## 2.2.5 CLSYS出力

CLSYS出力は、MCUのクロック源として使用するためのものです。利用可能な周波数を示します。

- 4 MHz

- 5 MHz

- 10 MHz

- 20 MHz

CLSYS周波数は、[補助レジスタ2 \(0Eh\)](#) のオプション・ビットclsys[2:0]によって定義されます。

## 2.2.6 IO信号レベルと出力特性

ホスト通信とCLSYSの論理Highレベルは、VDD\_IOピンに接続された電源電圧によって設定されます。論理Highレベルは1.65 Vから5.5 Vの範囲とすることができます。通信レベルとのマッチングを保証するため、VDD\_IOはホスト・システムのペリフェラル電源電圧に接続することを推奨します。

デジタル出力は、デフォルトで高速動作用に設定されています。MISO出力とIRQ出力に50 pFの容量性負荷、VDD\_IO電源が3 V以上という条件で、5 MHzのSPIクロックが可能です。50 pFの容量性負荷、VDD\_IO電源が1.65 V以上という条件で、3 MHzのSPIクロックが可能です。

デジタル出力信号の高調波成分を減らすため、[補助レジスタ1 \(0Dh\)](#) のオプション・ビットhs\_outputをLowに設定することにより、微弱でエッジに勾配の付いた信号となるようにデバイス出力を設定できます。この設定では、デバイスの別の内部構成要素とのホスト・システム通信による妨害の可能性についても緩和されます。このオプションを使用すると、MISOとIRQに最大で50 pFの容量性負荷、VDD\_IO電源が3 V以上という条件で、2 MHzのSPIクロックが可能です。

また、オプション・ビットopen\_dr (レジスタ0Dh) をHighにセットすると、オープン・ドレインNMOS出力を設定することもできます。このオプションを使用すると、MISOとIRQとCLSYSの各信号の高調波成分がさらに減少します。また、デバイスの他ブロックの動作に妨害を与えるおそれのあるクロスカッピング効果も減少します。

## 2.2.7 OAD、OAD2出力

OAD出力とOAD2出力は、アナログとデジタルのテスト出力です。アナログ出力として使用されると、受信したサブキャリア信号またはミキサ・アナログDC出力レベルは、これらのピンで多重化されます。信号はAGDレベルがセンター値となります。デジタル出力として使用されると、そのレベルはVDD\_IOで設定されます。[補助レジスタ1 \(0Dh\)](#) のオプション・ビットhs\_oadを設定することで、OADピンは高速出力として設定可能です。高調波成分が増加し、デバイスの高感度ピンに対するクロストークが増える可能性があるため、通常動作の間はhs\_oadを使用しないことを推奨します。

## 2.3 PLL/VCO部

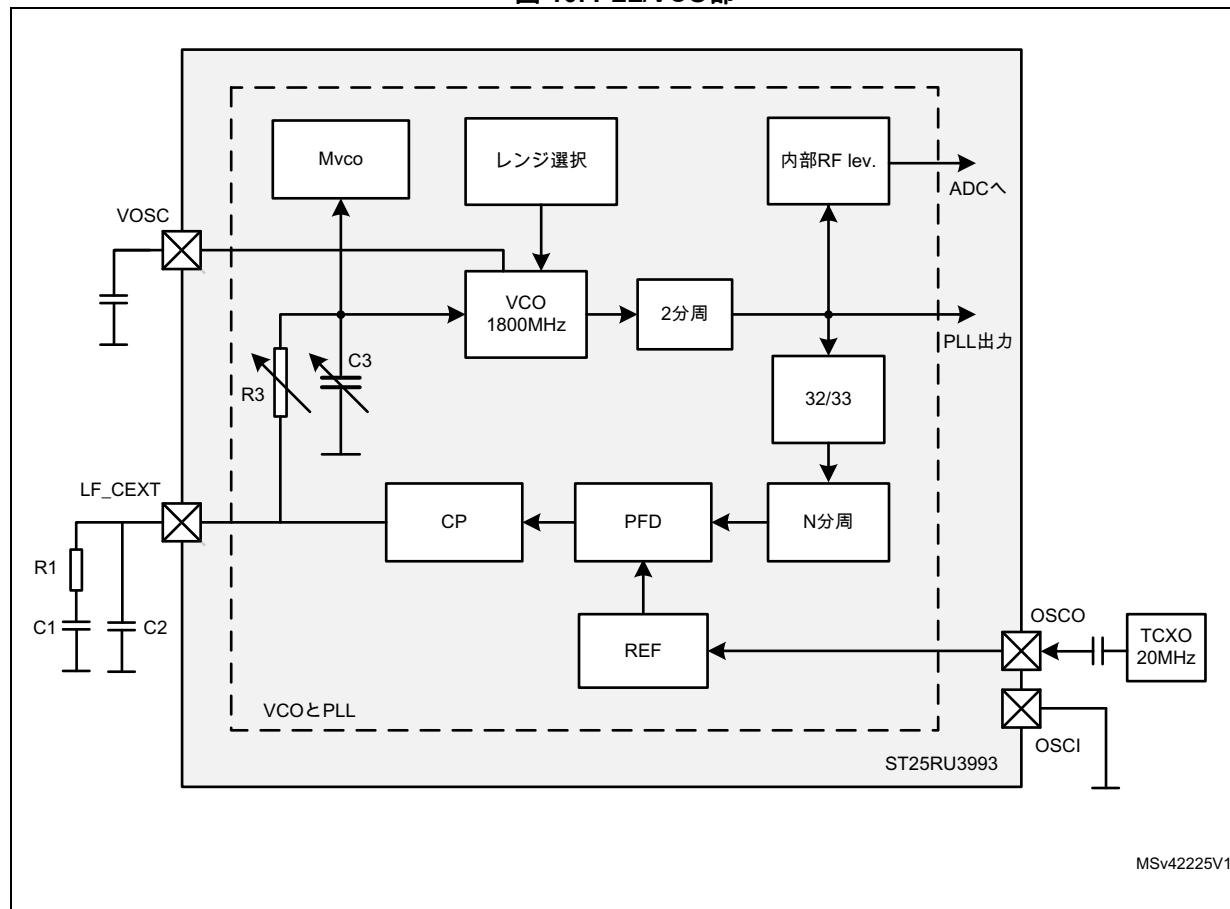

PLL部は、電圧制御発振器、プリスケーラ、主分周器と基準分周器、位相周波数検出器、チャージ・ポンプ、ループ・フィルタから構成されています。

ST25RU3993デバイスのPLL/VCO部の詳細なブロック図を図 10に示します。

図 10. PLL/VCO部

ループ・フィルタの部分を除くすべての構成要素はST25RU3993に内蔵されています。許容周波数動作範囲は、840 MHzから960 MHzまでとなります。

### 2.3.1 電圧制御発振器

VCOは、可変コンデンサとインダクタを含めて、完全に内蔵されています。周波数制御入力ピンはLF\_CEXTです。有効電圧範囲は0.5 VとV<sub>DD\_A</sub> - 0.5 Vの間となります。[VCOコントロール・レジスタ\(11h\)](#)のオプション・ビットeosc[2:0]は、発振器ノイズと消費電流の最適化に使用されます。電源デカップリングは、VOSCピンを通じて行われます。内部VCO周波数は1800 MHzの範囲で設定され、VCO引き込み効果を低減するために内部で2分周されます。VCOのゲインを減らして、可能な限り低い位相ノイズを得るために、1800 MHz VCOの同調曲線は16セグメント（範囲）に分割されます。

#### VCO同調範囲選択

[VCOコントロール・レジスタ\(11h\)](#)のオプション・ビットvco\_r[3:0]を設定することで、VCO同調範囲の選択が手動で行えます。ダイレクト・コマンドAutomatic VCO Range Selection (A4h)を使用すれば、自動選択を開始できます。ダイレクト・コマンドManual VCO Range Selection (A5h)を送信すれば、手動選択に戻ることができます。Automatic VCO Range Selection (A4h)コマンドによって、適切なVCOセグメントを見つける検索アルゴリズムが始動します。このアルゴリズムが完了すると、Irq\_cmdおよび[コマンド・ステータス表示レジスタ\(2Eh\)](#)のautovco\_doneステータス・ビットがHighにセットされて、IRQリクエストが送信されます。

#### VCO同調範囲ステータスの読み出し

自動セグメント検索アルゴリズムの結果は、vco\_ri[7:4]によって示されます。この値は、オプション・ビットr2Cpage[1:0] = 01b（レジスタ29h）であるときには、[AGL/VCO/F\\_CAL/PilotFreqステータス・レジスタ\(r2Cpage\[1:0\] = 01\)\(2Ch\)](#)を通じてデバイスから読み出すことができます。

#### VCO制御電圧測定

[VCOコントロール・レジスタ\(11h\)](#)のオプション・ビットmvcoをHighに設定することで、VCO制御電圧を測定できます。3ビットからなる結果であるvco\_ri[2:0]は、r2Cpage[1:0] = 01b（レジスタ29h）として、[AGL/VCO/F\\_CAL/PilotFreqステータス・レジスタ\(r2Cpage\[1:0\] = 01\)\(2Ch\)](#)から読むことができます。通常動作中は、レジスタ11hのオプション・ビットmvcoはLowに保持されなければなりません。1800 MHz VCOの使用に関する詳細は、専用のアプリケーション・ノートに記載されています。

### 2.3.2 PLLプリスケーラと主分周器

32/33分周プリスケーラは、N分周器によって制御されています。その分周比は、[PLL主レジスタ1](#)と[PLL主レジスタ3\(17h ~ 19h\)](#)または[PLL補助レジスタ1](#)と[PLL補助レジスタ3\(1Ah-1Ch\)](#)によって定義されます。3つの主（補助）レジスタの下位10ビットによってA値が定義され、その次の上位10ビットによってB値が定義されます。A値とB値によって、主分周器の分周比は以下の式のように定義されます。

$$N = B \cdot 32 + A \cdot 33$$

2つのレジスタ[PLL主レジスタ1](#)および[PLL主レジスタ3](#)ならびに[PLL補助レジスタ1](#)および[PLL補助レジスタ3](#)は、ダイレクト・コマンドHop to Main Frequency (84h)とHop to Auxiliary Frequency (85h)を使用した、周波数ホッピングに対応するためのものです。

### 2.3.3 PLL基準周波数

基準周波数は、[PLL主レジスタ1](#) (17h) のRefFreq[2:0]ビットによって選択されます。利用可能な値を以下に示します。

- 125 kHz

- 100 kHz

- 50 kHz

- 25 kHz

### 2.3.4 基準周波数源

基準周波数のために、20 MHzの周波数源が必要となります。外付け発振器 (TCXO) または水晶振動子が使用可能です。TCXOを使用する場合にはそれをOSCOピンに接続し、OSCIピンはGNDに短絡する必要があります。TCXOの信号は正弦波の形をしていて、AC結合されている必要があります。レベルは、0.8 Vppから3 Vppまでの範囲である必要があります。Txキャリア周波数の前後±20 MHzで区切られたスペクトル信号成分を最小限に抑えるため、OSCOレベルはできるだけ小さくすることを推奨します。このモードでのOSCO入力インピーダンスの標準値は9 kΩであり、9 pFが並列となっています。OSCIピンとOSCOピンの間には、適切な負荷コンデンサをGNDにシャント構成とした状態で、水晶振動子を接続する必要があります。15 pFから20 pFまでの範囲の負荷コンデンサを推奨します。共振用の直列抵抗は最大で30 Ωとする必要があります。安定した水晶発振を高速化するため、水晶発振器は高速モードで起動されます。その後、デバイスは低消費電力モードに戻ります。通常、デバイスの動作には低消費電力モードが用いられます。[補助レジスタ2](#) (0Eh) のオプション・ビットxosc[1:0]は、水晶振動子動作モードの手動制御のために用意されています。

### 2.3.5 位相周波数検出器とチャージ・ポンプ

基準周波数と分周されたRF周波数は、LF\_CEXTピンに接続されたチャージ・ポンプを駆動する位相周波数検出器で比較されます。チャージ・ポンプ電流は、[CPコントロール・レジスタ](#) (12h) のオプション・ビットcp[2:0]を使用して、150 μAと2350 μAの間で選択可能です。

### 2.3.6 ループ・フィルタ

ループ・フィルタは、外付け部分と内蔵部分から構成されます。1段目（直列コンデンサ、直列抵抗、シャント・コンデンサ）は外付けであり、LF\_CEXTピンに接続されます。2段目（R3/C3フィルタ）は、LF\_CEXTピンとVCO制御入力の間に内部接続されています。

ループ・フィルタの内蔵部（R3とC3）の値は、いずれもCP制御レジスタ (12h) の中にある、オプション・ビットLF\_R3[7:6]とLF\_C3[5:3]によって選択可能です。R3は30 kΩから100 kΩまでの範囲に、C3は20 pFから200 pFまでの範囲にそれぞれ設定できます。

### 2.3.7 周波数ホッピング・コマンド

主PLLレジスタか補助PLLレジスタかいずれかの主分周比を設定するダイレクト・コマンドであるHop to Main Frequency (84h) とHop to Auxiliary Frequency (85h) を発行することにより、周波数ホッピングが可能です。ホスト・システム (MCU) は、現地法規に則った正しい周波数ホッピングの実行に責任があります。

### 2.3.8 PLLの始動と周波数ホッピング

RFフィールドを有効化する前に、ホスト・システムは、[CPコントロール・レジスタ](#) (12h) ならびに[PLL主レジスタ1](#)と[PLL主レジスタ2](#)と[PLL主レジスタ3](#) (17h, 18h, 19h) を通じて、PLLを設定する必要があります。PLLは、上記選択肢の1つを使用してロックされる必要があります。ある周波数での動作中にいつでも、ホスト・システムは補助PLL主レジスタをフィルできます。周波数ホッピングが実行される必要がある場合にのみ、周波数ホッピングのダイレクト・コマンドをデバイスに送信する必要があります。

## 2.4 デバイス・ステータス・コントロール

デバイスの主要機能は、[デバイス・ステータス・コントロール・レジスタ](#) (00h) の中で制御されます。オプション・ビットrf\_onを設定することにより、内部トランスマッタブロックとレシーバブロックが有効化されます。初回のRFフィールドの立上げは、[Txオプション・レジスタ](#) (02h) のオプション・ビットTari[2:0]と、[モジュレータ・コントロール・レジスタ3](#) (15h) のオプション・ビットtrfon[1:0]によって定義されます。

利用可能な値を以下に示します。

- 100  $\mu$ s

- 200  $\mu$ s

- 400  $\mu$ s

- 指定済みTari

これが完了すると、[AGC/内部ステータス表示レジスタ](#) (2Ah) のrf\_okビットがセットされ、irq\_anaビットとともにIRQが送信されます。rf\_onビットをLowに設定することにより、立上がりトランジエントと同様にRFフィールドが立ち下げられ、irq\_anaビットをセットしたIRQが送信されます。rec\_onビットによって有効化されるのはレシーバのみです。agc\_onビットによって、AGC機能が有効化されます。stbyビットによって、デバイスはスタンバイ・モードに入ります。

## 2.5 プロトコル・コントロール

主要なプロトコル・パラメータは、[プロトコル選択レジスタ](#) (01h) の中で選択されます。オプション・ビットprot[2:0]は、EPC Class1 Gen2動作では000bに、ISO18000-6A/B FM0デコーダ動作では001bに設定する必要があります。AutoACK[1:0]ビットによって、自動インベントリ・ラウンド・シケンスが有効となり、その深さが設定されます。可能なモードは次の3モードです。

- 自動処理なし

- 自動ACK

- 自動ACK + ReqRN

オプション・ビットRX\_crc\_n = 1によって、内部CRCチェックを行ない受信が設定されます。その場合、CRCは、それ以外のデータ・バイトと同様にFIFOに渡されるだけとなります。EPC Gen 2プロトコルにおいて、これはEPC応答の一部が欠落している場合に有用な機能となります。トランスマッタが送出し、格納されたCRCは、実際の転送データに対して計算されたものではなく、それゆえに無効なCRCであるためです。dir\_modeビットによって、ダイレクト・モードで動作中の出力信号の種別が設定されます。また、このビットによって、受信中のすべてのデコードと信号検出の自動処理が無効となります。連続してアナログ測定を行うときには、このビットをHighにすることを推奨します。

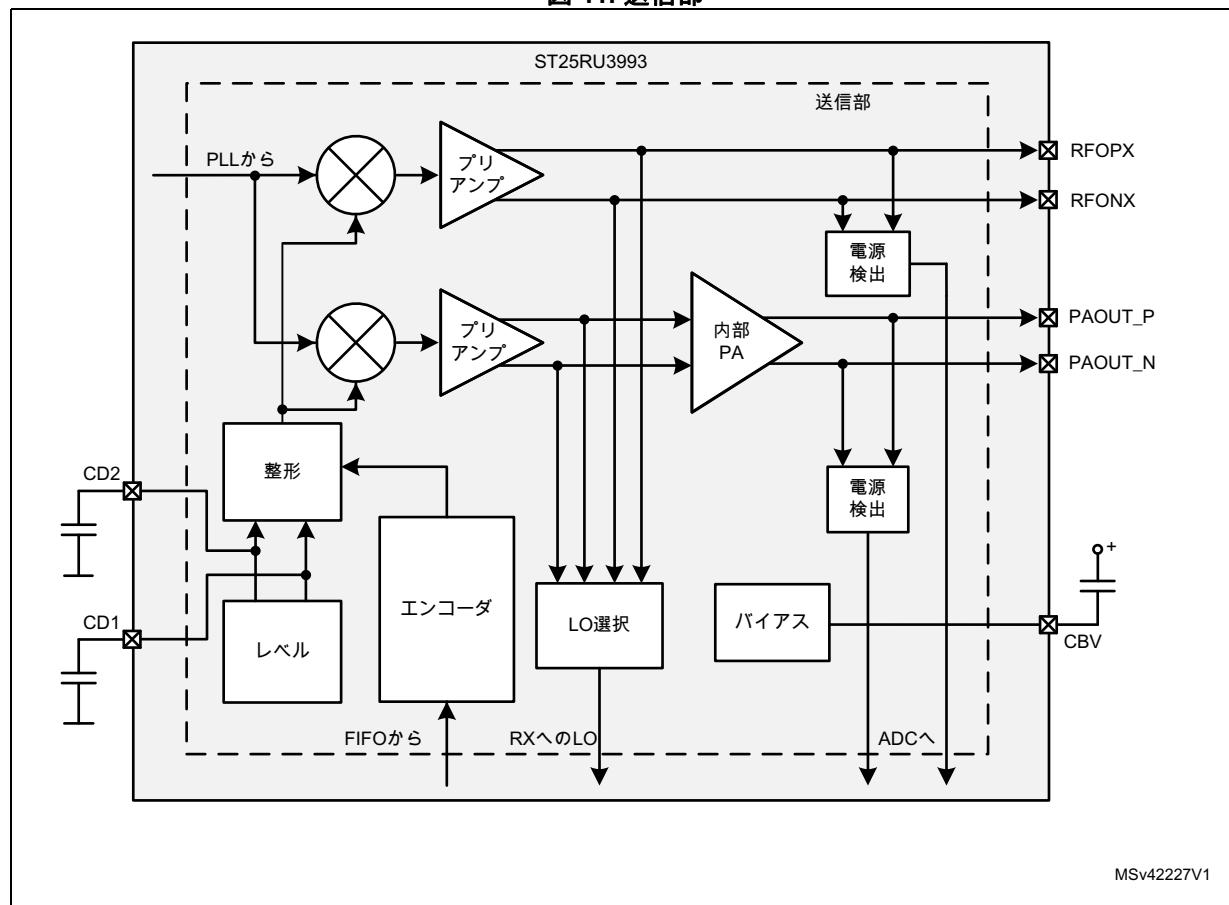

## 2.6 送信部

トランスマッタ部は、データ処理、エンコード部、整形回路、モジュレータ、増幅回路から構成されています。

図 11. 送信部

RFキャリアは整形された送信データによって変調され、送信のために（前置）増幅されます。

### 2.6.1 Txデータ処理とコーディング

データ処理部がFIFOからベースバンド・データを取り出し、Gen2プロトコル（PIE）に従ってエンコードします。プリアンプまたはフレームシンクを追加してCRCを計算します。このデジタル変調信号は整形回路に送られます。

### 2.6.2 Tx整形回路

変調整形はダブルD/Aコンバータによって制御されます。最初の5ビット対数コンバータが、最小と最大（Vpp）の変調信号レベルを定める2つの電圧を生成します。この2つの電圧は、ノイズ・レベルができるだけ押さえるために、CD1ピンとCD2ピンに接続された外付けコンデンサ2個によるフィルタをかけられ、整形回路の基準として用いられます。2番目の9ビット・リニア・コンバータによって、デジタル変調信号は正弦波またはリニアに成形されたアナログ変調信号へと変換されます。整形回路の出力は、補間後にモジュレータ入力に接続されます。

## 2.6.3 局部発振器（LO）経路

位相ノイズ除去を向上するため、局部発振器信号がプリアンプ段の出力から抽出されます。最適な動作のため、プリアンプのレベルは定格値（レジスタ15hのTX\_lev[4:0]で設定）に近い値である必要があります。低いレベルが使用される場合には、オプション・ビットeTX[7]を使って、LO信号を約6 dB上げることができます。その短所は受信ノイズが増加することです。

## 2.6.4 モジュレータ

モジュレータは、デジタル変調信号を整形したものでRFキャリアを変調します。内部モジュレータは、ASK変調とPR-ASK変調に対応しています。

### Txレベル / 波形調整

出力レベルと変調波形の特性は、[モジュレータ・コントロール・レジスタ1](#)と[モジュレータ・コントロール・レジスタ4](#)（13h ~ 16h）によって制御されます。出力信号のレベルは、[モジュレータ・コントロール・レジスタ3](#)（15h）のオプション・ビットTX\_lev[4:0]によって調整されます。良好な性能を得るためにには、リーダライタの出力パワーがST25RU3993の定格出力パワーに近くなるように、リーダライタ・デバイスの外付け回路を設計することをお薦めします。一時的にパワーを落として動作する必要がある場合には、オプション・ビットTX\_lev[4:0]を使用してください。

正弦波整形カリニア整形かは、レジスタ（15h）のオプション・ビットlin\_modによって設定されます。PR-ASK変調は、オプション・ビットpr\_askをHighにセットすることで選択されます。PR-ASKを選択した場合には、オプション・ビットdel\_len[5:0]を用いて、デリミタ長を9.6 μsから15.9 μsまでの範囲で調整します。Tari = 25 μsでは、PR-ASKとASKのデリミタ形状が利用可能です。より精度の高いタイミングが得られるASKトランジェントは、レジスタ15hのオプション・ビットook\_askで選択可能です。Tari = 12.5 μsと6.25 μsでは、ASKのデリミタ形状のみが利用可能です。

ASK変調は、オプション・ビットpr\_askをLowにセットすることで選択されます。ASK変調では、オプション・ビットook\_askを設定することで、デリミタ長の調整が可能です。この場合、ook\_askビットで100% ASK変調を設定し、上記PR-ASKモードと同様に、del\_len[5:0]ビットを使ってデリミタ長の設定を行います。

変調トランジェントのレートは選択されたTari設定に自動調整されますが、オプション・ビットask\_rate[1:0]（レジスタ13h）による再調整が可能です。変調信号の遷移をより滑らかにするために、[モジュレータ・コントロール・レジスタ1](#)（13h）のオプション・ビットe\_lpfを用いて、オプションのローパス・フィルタを有効化できます。aux\_modビットとmain\_modビットによって、ローパワー出力と内部PA出力のどちらの経路に変調信号が接続されるかが設定されます。[RF出力/LOコントロール・レジスタ](#)（0Ch）のeTX[3:0]ビットにより出力の1つが有効化され、それに対応するaux\_modビットまたはmain\_modビットがLowである場合、出力は有効化されますが変調はされません（デバイスは連続波形信号のみを出力します）。

## 2.7 Tx出力

次の2本のTx差動出力ポートが利用可能です。

- 差動ローパワー高直線性出力（定格 0 dBm）

- 差動ハイパワー出力（定格 20 dBm）

ハイパワーRF信号を生成するために、ローパワー出力を使用して外部PAを駆動してできます。内部ハイパワー出力は、中近距離の読み取り範囲要件の用途に適したアンテナを直接駆動するために使用できます。

### ローパワー出力

差動ローパワー高直線性RF出力（~0 dBm）は、外付けアンプの駆動に使用するためのものです。50 Ωシステムで最適な動作を行うためには、VDD\_Bに接続された外付けRFチョークとデカッピング・コンデンサとインピーダンス比2:1のバランが、RFOPXピンとRFONXピンから構成されるRF出力に必要となります。RF出力/LOコントロール・レジスタ（0Ch）のeTX[1:0]ビットによって、出力が有効化されます。これらのビットを使用することで、RF出力ピンの電流能力を調整できます。

### ハイパワー出力

差動ハイパワー出力ピンは、内部パワー・アンプ出力PAOUT\_PとPAOUT\_Nの出力です。50 Ωシステムで動作するには、VDD\_PAに接続されたRFチョークとインピーダンス・マッチング回路が必要となります。レジスタ0Chのオプション・ビットeTX[4]とeTX[3:2]によって、アンプが有効化されます。eTX[3:2]ビットによって、内部プリアンプ段のバイアスも設定されます。内部PAが有効化されると、PA電源レギュレータは自動的に有効となります。内部PAのバイアス電流は、[レギュレータ/PAバイアス・レジスタ](#)（0Bh）のオプション・ビットpa\_bias[1:0]によって設定されます。

## 2.8 Tx動作モード

### 2.8.1 TXノーマル・モード

ベースバンド・データは24バイトFIFOに転送され、すべての信号処理（プロトコル・エンコード、ブリアンブルまたはフレームシンクの付加、CRC、信号整形、変調）は内部で行われます。その後、データは変調パルス・レベルにコーディングされ、モジュレータに送信されます。これは、MCUはデータが入ったFIFOをロードするだけで済むことを意味します。

#### 送信開始

ノーマル・モードでデータ送信を開始するには、3つの手段があります。

最初の手段は、次の関連ダイレクト・コマンドの後に、送信すべきバイト数に関する情報とベースバンド・データを送信することでトリガ可能なデータ送信です。

- Transmission with CRC (90h)

- Transmission with CRC Expecting Header Bit (91h)

- Transmission without CRC (92h)

[Tx長レジスタ1](#)と[Tx長レジスタ2](#)（3Dhと3Eh）に書き込む必要のあるバイト数とそのデータ自体を、[FIFO I/Oレジスタ](#)（3Fh）に格納する必要があります。どちらの処理も、連続した書き込みコマンド1回で実行できます。最初のバイトがFIFOに完全に書き込まれると転送が始まります。

送信をトリガする2番目の手段では、EPC Class1 Gen2プロトコルに関連する次のダイレクト・コマンドの1つを用います。

- インベントリ・コマンド:

- Query (98h)

- QueryRep (99h)

- QueryAdjustUp (9Ah)

- QueryAdjustNic (9Bh)

- QueryAdjustDown (9Ch)

- ACK (9Dh)

- ReqRN (9Fh)

この場合、コマンドを受信すると同時に送信が始まります。

データ送信の3番目の手段は、AutoACKモードのどれかを用いるものです。この場合には、直前の受信が成功すると、ACKまたはReqRnが自動送信されます。

データ送信の間、[FIFOステータス・レジスタ](#) (39h) のTX\_statusビットがセットされます。データ送信が完了すると、リーダライタ・デバイスは、IRQ\_TXビットをHighにセットしてIRQリクエストを送信します。

## プロトコル調整

EPC Class1 Gen 2プロトコルでは送信パラメータの調整が可能です。対応している3種類のTari値は、[Txオプション・レジスタ](#) (02h) のオプション・ビットTari[1:0]を変更することによって選択されます。(PIEエンコードされた)論理値のH期間の長さは、[Txオプション・レジスタ](#) (02h) のオプション・ビットTXOne[1:0]によって選択されます。ダイレクト・コマンドQuery (98h) のセッション・パラメータは、[Tx設定レジスタ](#) (3Ch) のオプション・ビットS1とS0によって設定されます。後方散乱リンク周波数を設定するTRcalは、Queryコマンド送信の中に含まれています。TRcalは、TRcalレジスタ (04hと05h) のオプション・ビットTRcal[11:0]によって設定されます。

**注意：**ソフトウェア設計者は、送信QueryコマンドのTRcal[11:0]ビットとRX\_LF[3:0]ビットとDRビットがGen2プロトコルに準拠しているように、気を付ける必要があります。厳密な説明は、[EPC Class1 Gen2またはISO18000-6Cのプロトコル説明](#)に記載されています。通常送信でTRcalデータが必要である場合には、[Tx設定レジスタ](#) (3Ch) のオプション・ビットForce\_TRcalで設定可能です。巡回冗長検査は、CRC-16/に替えてCRC-5とすることができます。通常送信では、[Tx設定レジスタ](#) (3Ch) のオプション・ビットTXCRC\_5を設定することにより行われます。

## 送信FIFO

リーダライタ・デバイスは、完全独立の24バイトFIFOバッファ・レジスタ2本を備えており、1本は送信用、1本は受信用です。これらのFIFOは同じアドレスを共有しています。FIFOアドレス3Fhに書き込むことによりデータは送信FIFOに渡され、レジスタ・アドレス3Fhから読み込むことにより受信FIFOから値がフェッチされます。この手法によって、直前に受信したデータがMCUIによって読み出される前に、新しい送信を開始することが出来ます。

送信するデータ・バイト数がFIFOバッファのサイズを超えている場合には、MCUIは最初にFIFOレジスタを24バイトだけをファイルする必要があります。このリーダライタ・デバイスは送信を開始し、FIFOが残り6バイトだけとなると、割込み要求を送信し、[割込みレジスタ1](#) (37h) のirq\_fifoによる通知が行われます。割込みを受信すると、MCUIはレジスタ37hから読み込む必要があります。このレジスタを読み込むことで、ホスト・システムは割込みの要因を知り、それと同時に割込みビットをクリアします。この後、MCUIは使用可能なFIFOサイズを考慮の上で、残った送信データ・バイトをFIFOに置きます。送信データ・バイトがすべてFIFOに送信済みである場合には、ホスト・システムは最後のデータが送信されるまで待ちます。送信の終了は、レジスタ37hのIRQリクエストirq\_TXIによって、MCUIに伝えられます。2本の[Tx長レジスタ1](#)と[Tx長レジスタ2](#) (3Dhと3Eh) は、不完全なバイトの送

信に対応しています。MCUは、完全なバイトのバイト数と、送信すべき残りビットのビット数を設定する必要があります。

## 2.8.2 TXダイレクト・モード

リーダライタ・デバイスのプロトコル処理対応をすべてバイパスして、アナログ機能だけを使用するときには、ダイレクト・モードが選択されます。

### ダイレクト・モードの開始と終了

ダイレクト・モードに入るには、ダイレクト・コマンドDirect Mode (81h) の送信に続けて、NCSをLowからHighに変化させる必要があります。ダイレクト・モードは、NCSがHighに保たれている限りは有効のままとなります。ダイレクト・モードを終了するには、NCSをHighからLowに変化させた直後に、ダイレクト・コマンドBlock Rx (96h) を送信する必要があります。それと同じく引き続くNCSのLow期間の間は、SPIインターフェースを介した通常通信が再び可能です。

### ダイレクト・モード・シグナル

ダイレクト・モード中のI/Oピンの再割り当てを表6に示します。異なる受信出力オプションは、[プロトコル選択レジスタ](#) (01h) のオプション・ビットdir\_modeに関連しています。

表6. ダイレクト・モードにおけるI/Oピン再割り当て

| ピン名称 | ビット・ストリームとビット・クロック出力<br>(dir_mode = 0) | サブキャリア出力<br>(dir_mode = 1) |

|------|----------------------------------------|----------------------------|

| MOSI | Txデータ入力                                | Txデータ入力                    |

| SCLK | Rx入力イネーブル                              | Rx入力イネーブル                  |

| MISO | Rxデータ出力                                | Iチャネル・サブキャリア出力             |

| IRQ  | Rxビット・クロック出力                           | Qチャネル・サブキャリア出力             |

ダイレクト・モードでは、MCUは、送信変調入力ピンMOSI (Txデータ入力) を直接制御しなければなりません。RFフィールドは、MOSIがHighであればHighレベルに、MOSIがLowであればLowレベルに設定されます。回路は、[モジュレータ・コントロール・レジスタ1](#)と[モジュレータ・コントロール・レジスタ3](#) (13h ~ 15h) の設定内容に従ってフィールドを整形し、シグナルを送信します。

## 2.9 レシーバ

レシーバ部は、2個の入力ミキサに続く、高速AC結合段、ゲイン段、フィルタ段とデジタイザから構成されています。2本の受信信号は、決定回路とビット・デコーダとフレーマに送られ、ブリアンブルの除去とCRCのチェックが行われます。チェック済みでフレーム化されたベースバンド・データは、24バイト[FIFO I/Oレジスタ](#) (3Fh) を通じてMCUからアクセス可能です。

レシーバ部は、[デバイス・ステータス・コントロール・レジスタ](#) (00h) のオプション・ビットrec\_onまたはrf\_onによってアクティブになります。リーダライタ・デバイスがそれまでにノーマル・モード (EN=Hかつstby=0) であった場合、標準的なバイアス整定時間は3 msです。ENピンまたはstbyのHighからLowへの変化とともにrec\_onビットがセットされた場合には、ノーマル・モードの起動タイミングが優先されます。

ST25RU3993デバイスのレシーバ部の詳細なブロック図を図 12に示します。

図 12. レシーバ部

## 2.9.1 入力ミキサ

2個の入力ミキサは90°シフトのLO信号で駆動され、IQ復調回路を構成します。IQデモジュレータ・アーキテクチャの採用により、AM入力信号は同相チャネル(I)で復調され、PM入力信号は直交位相(Q)チャネルで復調されます。AM入力信号とPM入力信号が混じっているものは、両方の受信チャネルで復調されます。この構成により、変調種別を切り替えることで生じる通信の欠落が抑制されるため、たとえレシーバの入力においてトランスポンダが振幅変調か位相変調を示した場合であっても、信頼性のある動作となります。差動入力ミキサとシングルエンド入力ミキサが利用可能です。

### 差動入力ミキサ

MIX\_INPピンとMIX\_INNピンが差動Rxミキサに対する入力です。これらの入力は、外部回路にAC結合されている必要があります。起動時には、デバイスは自動的に差動Rxミキサを選択します。差動Rxミキサが使用されない場合には、入力ピンはGNDに短絡する必要があります。レシーバのノイズと入力範囲の特性を最適化するために、差動Rxミキサには入力範囲を調整する設定項目が含まれています。環境の反射率とアンテナの特性次第では、レシーバの入力RF電圧は、差動Rxミキサの動作が損なわれるレベルまで増加することができます。このような場合には、**Rxミキサゲインレジスタ(0Ah)**のオプション・ビットmix\_ir[0]をHighに設定することで、内部入力アッテネータを有効にして、入力範囲を拡大できます。不要反射波電力(自己妨害)が小さい場合には、ホスト・システムは、オプション・ビットmix\_ir[1]を設定することによりミキサ変換ゲインを増加させて、レシーバの全体感度を向上可能です。この設定の欠点は、入力ダイナミック・レンジが減少することです。

エミッタ結合ミキサ・オプション・レジスタ (22h) は次のようにも設定できます。

- emix\_vr[0]: (i2x) ミキサ・ゲイン・モードにおける差動Rxミキサ範囲を増加 (~3dB)

- emix\_vr[1]: (vsp\_low) 差動Rxミキサのバイアス点を低電源電圧に適応

- iadd\_sink[2:0]: 差動Rxミキサ負荷段を選択

### シングルエンド入力ミキサ

シングルエンド入力ミキサはエミッタ結合入力の配置となっています。MIXS\_IN入力ピンは、GNDに対するDC経路を有しており、RF入力信号に対してAC結合されている必要があります。シングルエンド入力ミキサは、[補助レジスタ1](#) (0Dh) のs\_mixビットによって有効化される必要があります。

以下に示すオプションは、ミキサ入力範囲と感度と消費電流に対するさまざまな要件に対して、ミキサの動作を最適化するために用意されています。

- mix\_ir[1:0]: [Rxミキサ/ゲインレジスタ](#) (0Ah) の内部ミキサ・インピーダンスとゲインを選択

- emix\_vr[2:0]: [エミッタ結合ミキサ・オプション・レジスタ](#) (22h) のミキサ入力電圧範囲を選択

- id2x, id1x5, iadd\_sink[2:0]: [TRcalハイ・レジスタ](#) (04h) と [エミッタ結合ミキサ・オプション・レジスタ](#) (22h) のミキサ負荷段電流を選択

## 2.9.2 局部発振器経路

位相ノイズ除去を向上するため、RFOPXかRFONXか内部PAの内部プリアンプ段から局部発振器信号を抽出することができます。LO信号を取る信号源は、[RF出力/LOコントロール・レジスタ](#) (0Ch) のオプション・ビットeTX[6]によって選択されます。定格よりも低い出力RFレベルが使用される場合には、オプション・ビットeTX[7]をHighに設定して、LO信号を約6 dB上げることができます。この設定の欠点は、受信ノイズが増加することです。

## 2.9.3 高速AC結合

内部フィードバックAC結合システムは、送信変調が開始される前に、DC動作点を格納します。データ送信の後、システムは徐々にハイパス時定数を調整しますので、受信前に非常に高速な整定時間が得られます。EPC Class1 Gen 2プロトコルの最高ビットレートに必要となる短いTx-Rx遷移時間に対応するには、このようなシステムが必要となります。

## 2.9.4 Rx フィルタ

### フィルタ配置

Rx フィルタは、以下の4つのフィルタ段から構成されています。

- 500 kHzまたは600 kHzの隣接チャネルを抑圧するノッチ特性を備えた4次橋円ローパスこのフィルタは、DRM動作において、1dB圧縮ポイントがETSIでは360 kHz、FCCチャネル間隔では280 kHzとなるように設定可能です。このフィルタ段は、次の1種類の非DRM設定が可能です。

- BLF = 640 kHzに対して、800 kHzローパス・コーナー周波数

- 72 kHzから200 kHzに調整可能な1dB圧縮ポイントを備えた2次ハイパス・チェビシェフ・フィルタこのフィルタ段は、より低いLF周波数に対してオフ（そのゲイン段のみ）にすることができます。

- DRM動作において、ETSIでは360 kHz、FCCチャネル間隔では280 kHzに1dB圧縮ポイントを備えた2次ハイパス・チェビシェフ・フィルタこのフィルタ段は、次の3種類の非DRM設定が可能です。

- BLF = 640 kHzに対して、800 kHzローパス・コーナー周波数

- BLF = 160 kHzに対して、180 kHzローパス・コーナー周波数

- BLF = 40 kHzに対して、72 kHzローパス・コーナー周波数

- 72 kHzから200 kHzに調整可能な1dB圧縮ポイントを備えた2次ハイパス・チェビシェフ・フィルタこのフィルタ段は、より低いBLFとFM0コーディングに対して、-3 dB周波数が5.5 kHzまたは12 kHzである1次ハイパスに再構成可能です。

### Rx フィルタ特性

Rx フィルタ特性は、[Rx フィルタ設定レジスタ \(09h\)](#) のオプション・ビットを通じて設定されます。オプション・ビット hp[3:1] はバイパス・コーナー周波数を設定し、lp[3:1] はローパス・コーナー周波数を設定します。byp1ビットとbyp2ビットによって数段がバイパスされ、より低い後方散乱リンク周波数での動作が可能となります。異なるフィルタ段の設定によってお互いに部分的な影響を与え合いますので、多くの異なる総合フィルタ特性を得ることができます。レジスタ 09h は FFh にセットしてください。使用可能なレジスタ設定とその標準的な Rx フィルタ特性を [表 7](#) に示します。

**表 7. Rx フィルタ設定 (レジスタ 09h)**

| フィルタ設定                   | -3 dB HP周波数 | -3 dB LP周波数 | 40 kHzにおける減衰量 | 600 kHzにおける減衰量 | 1.2 MHzにおける減衰量 |

|--------------------------|-------------|-------------|---------------|----------------|----------------|

| BLF = 640 kHz            |             |             |               |                |                |

| reg09:00                 | 220 kHz     | 770 kHz     | -55 dB        | -              | -35 dB         |

| reg09:07                 | 80 kHz      | 770 kHz     | -18 dB        | -              | -35 dB         |

| BLF = 320 kHz (ETSI DRM) |             |             |               |                |                |

| reg09:20                 | 200 kHz     | 380 kHz     | -50 dB        | -40 dB         | -54 dB         |

| reg09:27                 | 75 kHz      | 380 kHz     | -18 dB        | -40 dB         | -54 dB         |

| BLF = 250 kHz (FCC DRM)  |             |             |               |                |                |

| reg09:30                 | 200 kHz     | 320 kHz     | -50 dB        | -45 dB         | -55 dB         |

| reg09:37                 | 75 kHz      | 320 kHz     | -18 dB        | -45 dB         | -55 dB         |

| BLF = 160 kHz            |             |             |               |                |                |

| reg09:3B                 | 110 kHz     | 245 kHz     | -             | -52 dB         | -56 dB         |

| reg09:3F                 | 55 kHz      | 245 kHz     | -             | -52 dB         | -56 dB         |

| BLF = 40 kHz             |             |             |               |                |                |

| reg09:FF                 | 7 kHz       | 80 kHz      | -             | -60 dB         | -55 dB         |

## 推奨フィルタ設定

すべてのフィルタ設定が動作中に有用であるわけではありません。[表 8](#) 表8に示したものが推奨レジスタ設定であり、これによって、対応するリンク周波数とRxコーディングに対して、最適なRxフィルタ総合特性が得られます。

**表 8. 対応リンクモードに対する推奨Rxフィルタ設定**

| リンク周波数  | Rxコーディング | レジスタ09h設定 |

|---------|----------|-----------|

| DRMモード  |          |           |

| 320 kHz | M4       | 24h       |

|         | M8       |           |

| 250 kHz | M4       | 34h       |

|         | M8       |           |

| 他の対応モード |          |           |

| 40 kHz  | FM0      | FFh       |

|         | M2       |           |

|         | M4       |           |

|         | M8       |           |

| 160 kHz | FM0      | BFh       |

|         | M2       | 3Fh       |

|         | M4       |           |

|         | M8       |           |

| 640 kHz | M4       | 04h       |

|         | M8       |           |

## Rxフィルタ補正

内部抵抗とコンデンサの値のプロセスばらつきと温度変動を補償するため、フィルタ補正プロシージャを利用できます。補正プロシージャは、ダイレクト・コマンドTrigger Rx Filter Calibration (88h) によってトリガれます。補正是5 ms（最大値）後に完了しますが、起動後と初回受信前、その後も折に触れて、特に大幅な温度変化が発生した場合には、トリガされる必要があります。

この補正の結果は、r2Cpage[1:0] = 10bとした[AGL/VCO/F\\_CAL/PilotFreqステータス・レジスタ\(r2Cpage\[1:0\] = 01\)](#) (2Ch) のステータス・ビットlp\_cal[3:0]とhp\_cal[3:0]によって示されます。標準的な補正結果の値は88hです。[補助レジスタ2](#) (0Eh) の有効化オプション・ビットf\_cal\_hp\_chgが先にHighにセットされていた場合、自動補正された値は、ダイレクト・コマンドのDecrease Rx Filter Calibration Data (89h) とIncrease Rx Filter Calibration Data (8Ah) で調整可能です。

hp\_cal[3:0]はフィルタ特性のパイパス部分に影響を与え、lp\_cal[3:0]はフィルタ特性のローパス部分に影響を与えることに留意してください。どちらも4%ステップです。範囲は30%です。

## Rxゲインとデジタイザのヒステリシス

受信チェーンのRxゲインとデジタイザのヒステリシスを調整して、信号対雑音干渉比を最適化できます。調整方法としては次の3種類あります。

- 手動

- AGC

- AGL

### 手動調整

この調整方法は、*Rxミキサ/ゲインレジスタ* (0Ah) のオプション・ビットを設定することによって行われます。gain[2:0]ビットによってデジタイザのヒステリシスが1ステップあたり3 dB (7ステップ) 増加し、gain[5:4]ビットによってベースバンド・アンプのゲインが1ステップあたり3 dB (3ステップ) 変化します。変化の符号 (増加または減少) は、オプション・ビットgain\_signによって設定されます。

### AGC

内蔵AGCには、受信プリアンブルの最初の期間に動作するシステムが含まれています。部分的にデジタイザのヒステリシスを変更し (ステップ1~4)、ベースバンド・ゲインを変更します (ステップ5~7)。ヒステリシスとベースバンド・ゲインは両方のチャネルに対して等しく変更され、より強い信号が正しくデジタイズされるように、IチャネルとQチャネルの間の比を維持します。*デバイス・ステータス・コントロール・レジスタ* (00h) のオプション・ビットagc\_onをHighに設定することで、AGCを有効にできます。AGCの状態は、*AGC/内部ステータス表示レジスタ* (2Ah) のステータス・ビットagc[2:0]によって確認可能です。レジスタ値は、3 dBステップの数を示しています。

### AGL

この調整は、環境ノイズと妨害のために受信状態が悪い場合に、感度を低下させる別の手段となります。ダイレクト・コマンドEnable Rx (97h) 送信後のrf\_ok = 1の間、ならびに保留となっている実トランスポンダ応答が存在しない時間の間、AGLはダイレクト・コマンドAGL On (A6h) によってトリガ可能です。このことは、RF立ち上げが完了していなければならず、レシーバが妨害信号を受信する用意が整っていることを意味します。この自動機能によって、各チャネルに対して個別に、雑音妨害レベルの少し上のレベルまでデジタイザのヒステリシスが増加します。AGL動作に必要な最長時間は1 msです。各チャネルに対するAGL結果の状況は、r2Cpage[1:0] = 00bとした*AGL/VCO/F\_CAL/PilotFreqステータス表示レジスタ* (r2Cpage[1:0] = 00) (2Ch) のステータス・ビットagi[5:0]を読むことにより確認可能です。レジスタ値は、3 dBステップでのステップ数を示しています。有効なステップは4個あり、ステップ5~7は無効なステップ (0 dB) です。AGLは、ダイレクト・コマンドAGL Off (A7h) により停止します。結果は格納されており、ダイレクト・コマンドAGL Off (A7h) が送信されるまで有効なままになっています。

AGCとAGLの差は、AGCがデータ・パケット受信を開始するたびに動作するのに対して、AGLはダイレクト・コマンドAGL On (A6h) 送信時にのみ動作する点です。

AGCとAGLのどちらも*Rxミキサ/ゲインレジスタ* (0Ah) のgain[2:0]ビットで動作しますので、排他的に使用する必要があります。手動設定の優先度は下がります。システム・ゲインの設定は、一般に、どのタグも送信していないときには、良好な（通常の）状態において、デジタイザ出力に発生する遷移の数は少なくなるようなレベルである必要があります。このような場合には、AGLにも変化はみられません。

## 2.9.5 IQ選択

2つの受信信号はデジタル化と評価が行われます。決定回路は、その後の処理のために、同相信号チャネルと直交信号チャネルのどちらか、受信信号が良好である方を選択します。選択された信号チャネルは、[AGL/VCO/F\\_CAL/PilotFreqステータス表示レジスタ \(r2Cpage\[1:0\] = 00\)](#) (2Ah) のステータス・ビットin\_selectを読み出すことによって確認可能です。このビットは、プリアンブルの最後から次回送信開始まで有効です。FM0 Rxエンコードでは、データ・パケット先頭における受信サブキャリアのデジタル表現の評価に基づいて、選択が行われます。Miller Rxエンコードでは、対数RSSI測定による選択に対応しています。RSSIが考慮されるのは、RSSI測定値 (IまたはQ) の1つ以上が[インテロゲータ・コリジョン検出/IQ選択設定レジスタ \(1Dh\)](#) のオプション・ビットIQsel\_Th[3:0]によって設定された値よりも大きい場合です。ノイズRSSIを考慮すれば、更なる改善が可能です。このモード (有効なRFフィールドと、次の受信で使用されるミキサとゲインの全設定値が必要) を有効化するには、ダイレクト・コマンドEnable Rx (97h) とStore RSSI (A8h) を送信します。その結果として、実際のパイロットRSSIと格納されたノイズRSSIの差だけがIQの決定に寄与することになります。

## 2.9.6 ビット・デコーダ

ビット・デコーダは、[Rxオプション・レジスタ \(03h\)](#) のオプション・ビットRX\_cod[2:0]とRX\_LF[3:0]によって設定されたプロトコルに従って、サブキャリアでコード化された信号をビット・ストリーム・データに変換します。システムはデータ・クロックとシリアル・データ・ビットを抽出し、プリアンブルを除去します。デコーダのロジックは、ノイズや妨害によって部分的に壊れたサブキャリア信号のデコードが可能であるように、許容誤差が最大となるように設計されています。EPC Class1 Gen2プロトコルでは、FM0エンコードとすべてのMillerエンコードされた信号に対して、デコーダは長いRxプリアンブル (TExt = 1) に対応しています。Miller4エンコードとMiller8エンコードの信号に対して、短いRxプリアンブル (TExt = 0) に対応しています。

## 2.9.7 データ・フレーマ

シリアル・ビット・ストリームは、データ・フレーマでバイト列にフォーマットされます。CRCバイトはチェック後に除去され、純粋なベースバンド・データが残ります。このデータは24バイトFIFOレジスタに送信され、そこからMCUは読み出すことができます。レシーバは、不完全なバイト列の転送にも対応しています。

## 2.10 データ受信モード

デバイスはノーマル・モードかダイレクト・モードで動作可能です。

### 2.10.1 Rxノーマル・モード

ノーマル・モードでは、受信データはFIFOに格納されます。

#### 受信開始

受信はデータ送信の最後に自動的にトリガれます。

受信を開始する2番目の方法は、ダイレクト・コマンドEnable Rx (97h) を送信することにより手動で実行されます。正常な動作のため、[プロトコル選択レジスタ \(01h\)](#) のdir\_modeビットは0にセットする必要があります。

受信を開始する3番目の手段は、AutoACKモードのどれかを用いるもので、PC+EPCとHandleを取得するために自動的に受信がトリガれます。

## Rx待ちタイマ

Rx待ちタイマは、データ送信の終了とデータ受信の開始の間の待ち時間を設定します。この期間の間、デコーダは動作していません。これによって、送信動作またはノイズや妨害に起因するトランジエントにより発生するおそれのある不正受信が防止されます。Rx待ちタイマは、[Rx待ち時間レジスタ \(08h\)](#) のオプション・ビットRXw[7:0]によって設定されます。Rx待ちタイマのステップ・サイズは6.4 μsです。

## Rx応答なしタイマ

Rx応答なしタイマは、コリジョン防止アルゴリズムの受信スロットでスタートし、タグから応答が届くまでを計測します。設定時間内にタグからの応答が受信されない場合、受信は終了し、IRQ\_norespビットがセットされてIRQがトリガれます。[割込み有効化レジスタ1 \(35h\)](#) のオプション・ビットe\_irq\_norespがセットされている場合には、Rx応答なしタイマによる受信の終了はありません。したがって受信は、ダイレクト・コマンドBlock Rx (96h) を送信することにより手動で終了する必要があります。このモードは、応答時間が長いことがあるか、それが定義されていないコマンドのために設計されています。Rx応答なしタイマは、[Rx応答なし時間レジスタ \(07h\)](#) によって制御されます。この時間は25.6 μsステップで設定されます。タイマがFFhに設定された場合、Rx応答なし時間は26.2 msに固定されます。

## デコーダ動作

データ受信の間は[FIFOステータス・レジスタ \(39h\)](#) のRx\_statusビットがHighにセットされ、データ送信が完了すると、リーダライタ・デバイスはIRQ\_RXビットをセットしてIRQリクエストを発行します。Rx FIFOバッファには24バイト格納可能です。受信データのバイト数が18を超えた場合には、IRQ\_fifoビット（レジスタ37h）がHighにセットされたIRQリクエストによって、FIFOからのデータ移動が必要であることをMCUに伝えます。データ・フォーマットがCRCにエラーが検出されると、MCUは、IRQ\_errビットがHighにセットされたIRQリクエストによる警告を受けます。エラー要因に関する情報は、[割込みレジスタ2 \(38h\)](#) から読み込むことができます。受信エラーの場合には、リーダライタとタグがほぼ同等のタイム・フローを維持するように、システムは予想されたビット数をそのまま受信します。

## Rx長レジスタ

一般に、予想される受信長は受信開始前に設定される必要があります。そうではない場合には、実際の長さが取得可能となった時点で、受信中に受信長が更新されます。通常のデータ送信（ダイレクト・コマンド90h、91h、92h）の最後に受信がトリガされると、受信長は[Rx長レジスタ1](#)と[Rx長レジスタ2 \(3Ahと3Bh\)](#) のオプション・ビットRXl[11:0]によって設定される必要があります。

ダイレクトQueryコマンド群（98h、99h、9Ah、9Bh、9Ch）では、待ち受けているRN16のために、Rx長は16ビットに事前設定されています。ダイレクト・コマンドReqRN (9Fh) では、ハンドルとCRCを受信するために、Rx長は内部的に32ビットに設定されています。PC + EPCの受信中に限っては、受信長は事前にはわかりません。このケースをカバーするため、内部のプロトコル・ロジックで最初の受信バイトが確認され、最初のPCバイトに含まれている値に従ってRx長が調整されます。ダイレクト・コマンドEnable Rx (97h) によって受信が手動でトリガされる場合には、Rx長は[Rx長レジスタ1](#)と[Rx長レジスタ2 \(3Ahと3Bh\)](#) のオプション・ビットRXl[11:0]によって設定される必要があります。AutoACKプロシージャのどれかが使用される場合には、自動インベントリ・コマンド・シーケンスの間に受信したタグ応答すべてに対して、Rx長は自動的にセットされます。

おそらくは将来的なプロトコル拡張や特定用途向けのタグ機能のために、自動的にセットされたRx長が実際のタグ・データ長と一致しない場合には、MCUは受信中に予想されたRx長を変更できます。自動設定されたPC+EPC長の場合には、2番目の受信バイトの後にRx長の変更が可能です。MCUは、2バイト（PC+EPCフィールドのPC部分）受信後に追加の割込みをリクエストできます。MCUは、現在進行中の受信の長さが設定されている2バイトを読み出して、Rx長レジスタを更新することができます。2番目のバイトの後のIRQリクエストは、[Rx長レジスタ1 \(3Ah\)](#) のオプション・ビットfifo\_dir\_irq2

によって有効化されます。このモードの副作用は、FIFOの中にもCRCバイトが現れることです。2番目のバイトを実際に受信したことは、[割込みレジスタ1](#)(37h)の中でHighにセットされたIRQ\_2nd\_byte IRQビットによって通知されます。実際のRx長が後にしか得られない場合には、[Rx長レジスタ1](#)(3Ah)のオプション・ビットrep\_irq2を設定することにより、2番目のバイトの割込み機能を拡張して、4番目、6番目…の受信バイトの後に追加のIRQリクエストをトリガすることができます。狙った受信バイト数の割込みが受信されたときに、オプション・ビットrep\_irq2をクリアすることで、残りの受信に対するそれ以上の割込みが防止されます。

Gen2コマンドの一部では、タグが通常応答で応答することも、エラーコードで応答することもあります。この2種類の応答は長さが異なります。MCUの更なる支援のため、オプション・ビットauto\_errcode\_RXIが用意されました。このオプション・ビットがセットされると、プロトコル・ロジックは受信したヘッダ・ビットを確認し、エラー・コードの受信が検出された場合、その予想される受信長を41ビット（Gen2エラー応答長）に調整します。

## RN16レジスタ

EPC Class1 Gen2プロトコルでは、インベントリ・ラウンドの中のタグ応答とそれに続くリーダライタ・コマンドの間の時間はやや不足しています。MCUがFIFOからRN16（またはハンドル）を読み込んでFIFOに書き戻す処理を支援するために、最後に受信したRN16を格納するための特別なレジスタが、デバイスに組み込まれています。RN16は、ダイレクトQueryコマンド群のどれかを最後に正常受信した後に格納されます。最後に格納されたRN16は、ACKコマンドの中で自動的に使われます。

## AutoAckモード

AutoACKモードによって、1台のトランスポンダに対してインベントリ・コマンド・シーケンスが自動実行されます。その目的は、MCUとリーダライタ・デバイスの間のやり取りの回数を最小限に抑えることにより、時間がクリティカルな作業からMCUを解放することです。AutoAckモードは、[プロトコル選択レジスタ](#)(01h)のオプション・ビットAutoACK[1:0]を設定することにより有効化されます。次のモードが利用可能です。

- AutoACK[1:0] = 00b: クエリのみ

- AutoACK[1:0] = 01b: 各クエリ・コマンドの後にACKが続く

- AutoACK[1:0] = 10b: 各クエリ・コマンドの後にACKとReqRNが続く

自動インベントリ・コマンド・シーケンスは、ダイレクトQueryコマンド群（98h、99h、9Ah、9Bh、9Ch）によってトリガれます。RN16が正常に受信されると、肯定応答コマンドACKとそれに続く受信の準備とトリガが自動的に行われます。PC+EPCが正常に受信されると、ハンドルのリクエスト(ReqRN)の準備とトリガが自動的に行われます。さらに、適切なRx長の設定が行なわれ、受信データ(PC+EPC、Handle)がFIFOに入れられます。MCUはベースバンド・データを読み出し、次のQueryコマンドをトリガして、インベントリ・ラウンドまたはタグ・オープン状態で使用可能な別のタグ・コマンドを継続します。

ホスト・システム(MCU)が処理する必要のある割込みの回数は、次に示すように最小限に抑えられます。

- 何も受信していない場合は、IRQ\_norespシグナルが送られます。

- EPCが18バイトよりも長い場合は、IRQ\_fifoシグナルが送られます。これによって、FIFOからデータを読み出す必要があることが通知されます。

- EPCとHandleの受信の終了時にIRQ\_RXシグナルが送られます。これによって、1つのAutoACKステップが完了したことも通知されます。エラーがない場合には、FIFOから利用可能なデータを読み出す必要があります。

- AutoACKプロシージャの終了時にIRQ\_AutoACKシグナルが送られますが、これは、RN16の受信が行われていて、シーケンス中に少なくともACKコマンドが発行されたことを意味しています。

- プロシージャの間にエラーが発生した場合には、IRQ\_errシグナルが送られます。

インベントリ・ラウンドを正常に制御するため、ホスト・システムは、空のコリジョン防止スロットとコリジョンが発生したスロットを区別する必要があります。

- `IRQ_AutoACK`を伴わない`IRQ_noresp`は、Queryコマンドに応答がなかったことを意味しています。これは、インベントリ・プロシージャの実際の空スロットを表します。

- `IRQ_AutoACK`を伴う`IRQ_noresp`または`IRQ_AutoACK`を伴う`IRQ_err`は、RN16の受信が行われていることと、プロシージャの中で空スロットまたは受信エラーが後に発生したことを意味しています。おそらくは、フィールドの中に未確認のトランスポンダが存在します。ただし、特定の設定と条件では、フィルタがかけられた受信ノイズ・レベルがデジタル化ヒステリシスの閾値を超えていて、システムがそれをタグ信号と認識していることも意味しています。

ノーマル・モード受信の他の場合に使用されるのと同様に、AutoACK機能では、[Rx応答なし時間レジスタ](#) (07h) と[Rx待ち時間レジスタ](#) (08h) が使用されます。EPC Class1 Gen2プロトコルに従って、T2時間の設定に追加のタイマが使用されます。この時間は[AutoACK待ち時間レジスタ](#) (06h) で設定されます。このタイマは受信期間の最後にスタートし、次回データ送信がトリガされる時間を規定します。

### テスト出力付きノーマル・モード

ノーマル・モード時とボードのデバッグ中に動作を監視するために、[測定コントロール・レジスタ](#) (10h) の次の手段が利用可能です。

- 両受信チャネル (IとQ) のデジタル化サブキャリア信号は、オプション・ビット `Tcomb[1:0]` を01bに設定することで有効化されます。出力はOADとOAD2です。

- Tx変調出力と選択されたデジタル化サブキャリア信号チャネルは、オプション・ビット `Tcomb[1:0]` を10bに設定することで有効化されます。出力はOAD (TX) とOAD2 (Rx) です。

- 両受信チャネル (IとQ) のアナログサブキャリア信号は、オプション・ビット `e_anaout[1:0]` を01bに設定することで有効化されます。出力はOADとOAD2です。アナログ出力はデジタル出力よりも優先度が低くなります。

## 2.10.2 Rxダイレクト・モード

ダイレクト・モードにおける受信は、SCLKピン (Rx入力イネーブル) をHighに設定することでトリガれます。ダイレクト・モードでタグからデータを受信する際には、オプション・ビットの設定次第で3つの選択肢があります。

- プロトコルに従って内部でデコードされたビット・ストリームとビット・クロックは、`dir_mode` = 0によって有効化され、[プロトコル選択レジスタ](#) (01h) のオプション・ビット `prot[2:0]` と[Rxオプション・レジスタ](#) (03h) のオプション・ビット `RX_cod[2:0]` と `RX_LF[3:0]` によって設定されます。出力はMISOピンとIRQピンです。

- 両受信チャネル (IとQ) のデジタル化サブキャリア信号は、[プロトコル選択レジスタ](#) (01h) のオプション・ビット `dir_mode` をHighに設定することで有効化されます。出力はMISOピンとIRQピンです。

- 両受信チャネル (IとQ) のアナログサブキャリア信号は、[測定コントロール・レジスタ](#) (10h) のオプション・ビット `e_anaout[1:0]` を01bに設定することで有効化されます。出力はOADピンとOAD2ピンです。

ダイレクト・モードへの入り方とこのモードでのI/Oピンの再割り当ての詳細は、[セクション 2.8.2: TXダイレクト・モード](#)を参照してください。

### 2.10.3 アンテナまたは指向性デバイスのチューニング支援モード

反射の少ないTxパワーを得るために、アンテナまたは指向性デバイスを積極的にチューニングする必要があります。正しいチューニングを可能とするために、入ってくる反射波電力の振幅情報と位相情報が、ミキサ2個の出力DCレベルを通じて利用できます。ミキサ2個のDCレベル出力のアナログ表現は、[測定コントロール・レジスタ](#) (10h) のe\_anaout[1:0]を10bに設定することにより、OAD出力とOAD2出力から得られます。受信中にチューニングを行う場合には、レシーバの有効化タイミングを知るためにEnable\_RX信号が必要となります。[測定コントロール・レジスタ](#) (10h) のTcomb[1:0]が11bであれば、この情報はADCピンから取得可能です。チューニング・データを取得する別な方法は、A/Dコンバータの項目に記載されているように、反射波電力レベルのデジタル表現を読み込むものです。

### 2.10.4 対数RSSI

レシーバ部には、対数RSSI（受信信号強度インジケータ）ブロックが2個含まれています。これらのブロックは、両信号チャネル (IとQ) の出力に接続されています。それぞれのRSSIの読み取り値は、r2Bpage[3:0] = 0110bとした[RSSI表示レジスタ](#) (2Bh) の2番目の受信バイトに、データ受信中に格納されます。RSSIの結果は、次回送信開始まで有効です。

## 2.11 A/Dコンバータ

8ビットオンボードA/Dコンバータは、外部パワー検出器に対応しており、内部診断回路に接続できます。入力範囲は±1Vで、AGD電圧 (1.6 V) がセンター値となります。LSB側7ビットが絶対出力レベルに関する情報であり、MSBは符号ビットとして働きます (Highは正の値、Lowは負の値を示します)。A/D変換の信号源は、[測定コントロール・レジスタ](#) (10h) のオプション・ビットmsel[3:0]によって選択されます。変換は、ダイレクト・コマンドTrigger AD conversion (87h) によってトリガされ、その結果は、r2Dpage[1:0] = 00b ([ステータス読み出しページ設定レジスタ](#)) とした[ADC読み取りリ/レギュレータ設定表示レジスタ](#) (r2Dpage[1:0] = 00) (2Dh) を通じて入手可能です。A/D変換は20 μs後に完了し、オプション・ビットIRQ\_cmd ([割込みレジスタ2](#)) がセットされてIRQリクエストが送信されます。

### 2.11.1 外部RFパワー検出器

PAの後か方向性結合器の入力結合ポートに外部RFパワー検出器を配置可能であり、実際のRF出力パワーを測定できるようになります。結果として得られるパワー検出器からのアナログ電圧は、リーダライタ・デバイスのADCピンに接続できます。この電圧レベルのデジタル表現は、msel[3:0] = 0011b ([測定コントロール・レジスタ](#)) として、オンボードA/Dコンバータを用いて取得可能です。

### 2.11.2 反射波RF電力インジケータ

レシーバには入力RFレベル・インジケータが含まれており、回路診断用として、またはアンテナ周囲環境の問題点の検出用として使用されます。低品質アンテナからの反射 (S11) と、反射アンテナの環境、指向性のデバイスからの漏れによって、ミキサ入力におけるキャリア・レベル（自己妨害レベル）が増加します。キャリア・レベルが上昇すると復調ノイズが増加しますので、ミキサ入力における不要キャリア・レベルを最低限に保つことが必須条件です。ミキサ2個の入力に見られる反射キャリアは、ゼロ周波数にダウントラベルされます。ミキサ出力におけるDCレベル2つは入力RFレベルに比例しており、RF入力レベルの測定用として使用できます。ミキサのDCレベルは、キャリア入力位相にも依存しています。ミキサ2個のDC出力レベルは、オプション・ビットmsel[3:0]を0001bと0010bに設定することにより、オンボードA/Dコンバータに接続できます。オプション・ビットid2xとid1x5は、反射波RF電力レベル・インジケータのゲインを適応させます。

### 2.11.3 電源電圧測定

A/Dコンバータは、電源電圧 $V_{EXT}$ と $V_{EXT\_PA}$ 、 $V_{DD\_B}$ 、 $V_{DD\_PA}$ の測定にも用いることができます。変換結果次第で、MCUは電源電圧レギュレータの設定方針を決定できます。オプション・ビット $msel[3:0]$ を以下のように設定することによって、選択された電圧は、A/Dコンバータ入力（VINPUT）に接続されます。

- $V_{EXT}$ : 0111b

- $V_{DD\_B}$ : 1000 b

- $V_{EXT\_PA}$ : 1001 b

- $V_{DD\_PA}$ : 1010 b

変換は、ダイレクト・コマンドTrigger AD conversion (87h) によって開始され、その結果は、 $r2Dpage[1:0] = 00b$ （ステータス読み出しページ設定レジスタ）とした[ADC読み取り/レギュレータ設定表示レジスタ \(r2Dpage\[1:0\] = 01\)](#) (2Dh) から入手可能です。

変換結果は次の式によって与えられます。

$$\text{ADCレジスタ値} = \frac{(V_{input} - 1.6) \cdot 0.8 - 1.6}{0.0079}$$

ここで、ADCレジスタ値はレジスタ2Dhの値、 $V_{input}$ はA/Dコンバータ入力におけるアナログ電圧（ボルト単位）です。

### 2.11.4 サブキャリア位相ビット付きリニアRSSI

両信号チャネル（IとQ）の復調されたピーク・ツー・ピーク電圧は、二重サンプル・アンド・ホールド回路に接続され、タグのプリアンブル（パイロット・トーン）の終わりでサンプリングされます。受信中にも受信後にもA/D変換が可能です。オプション・ビット $msel[3:0]$ を1011bに、 $msel[3:0]$ を1100b（[測定コントロール・レジスタ](#)）に設定して、ダイレクト・コマンドTrigger AD conversion (87h) によって変換をトリガすることにより、MCUは、内部リニアA/Dコンバータを用いて2つの電圧の変換と読み出しが可能です。結果は、 $r2Dpage[1:0] = 00b$ （[ステータス読み出しページ設定レジスタ](#)）として、[ADC読み取り/レギュレータ設定表示レジスタ \(r2Dpage\[1:0\] = 01\)](#) (2Dh) から入手できます。リニアRSSIでは、サンプリングされた電圧は、ADCの全範囲を使用するようにシフトされます。最小サンプル値はADCの結果で-127となり、最大サンプル値はADCの結果で127となります。[AGC/内部ステータス表示レジスタ \(2Ah\)](#)のステータス・ビット $subc\_phase$ は、サンプリングされたピーク・ツー・ピーク電圧2個（IとQ）が、サンプリング時点で同相であったのか、逆相であったのかを示します。この位相ビットは、パイロット・トーンの終わりから受信の終わりまで有効であり、受信が終わる前に読み出される必要があります。リニア（絶対）なIとQのRSSI値と位相ビット情報を使用すれば、システムはその中のRSSI位相情報を検出できます。

### 2.11.5 内部信号レベル検出器

内部信号レベル検出器が内部VCOの出力に配置されていますので、内部RFキャリアのレベル測定が可能です。オプション・ビット $msel[3:0]$ を0100bとすると、選択された電圧はA/Dコンバータ入力に接続されます。変換プロセッサの詳細は、A/Dコンバータに関する説明を参照してください。この内部信号レベル検出器は診断専用ですので、出力パワーの測定には使用しないでください。

## 2.12 インテロゲータ・コリジョン防止対応

ISO 29143の機能を有効とするために、RSSIベースのインテロゲータ・コリジョン防止対応が用意されています。この機能は、ダイレクト・コマンドInterrogator Anti-collision Support Enable (AAh) によって有効化されます。ISO 29143の提案に従って、システムは受信したサブキャリア信号のRSSIエンベロープを監視し、少なくとも受信データ・パケットのどこかでRSSIレベルが既定の閾値を超えた場合に、MCUに通知を行います。また、当該ポイントにおけるデータ・パケットのRSSIとタイミング・データの格納も行います。

次のRSSI値が格納されます。

- パイロット・トーンにおけるRSSI

- データにおけるRSSI

- 電文中的最大RSSI値

次のタイミング・データが格納されます。

- 既定の閾値を超過した最初の時間

- 閾値を超過した時間の長さ

- 初回プロトコル違反の時間

時間は受信ビットに関連付けられます。

既定のコリジョン検出閾値は、[インテロゲータ・コリジョン検出/IQ選択設定レジスタ](#) (1Dh) のICD\_Th[3:0]ビットにあります。この機能を有効とするには、ダイレクト・コマンドInterrogator Anti-collision Support Enable (AAh) を送信する必要があります。この機能を無効とするには、ダイレクト・コマンドInterrogator Anti-collision Support Disable (ABh) を送信する必要があります。ピークRSSI値とタイミング・データをクリアするには、ダイレクト・コマンドInterrogator Anti-collision Support Disable (ABh) を再び使用します。

### 3 レジスタの説明

6bit長のレジスタ・アドレスを16進表記で示します。リーダライタ・デバイスに実装されたレジスタには、次の2種類があります。

- リード/ライトレジスタ

- リードオンリ-表示レジスタ

レジスタには、シリアル・インターフェースを通じてアクセス可能です。

表 9. レジスタ・マップ

| アドレス<br>(16進) | 主な機能        | 内容                     | 種類 |

|---------------|-------------|------------------------|----|

| 00            | メイン・コントロール  | デバイス・ステータス・コントロール・レジスタ | RW |

| 01            |             | プロトコル選択レジスタ            | RW |

| 02            |             | Txオプション・レジスタ           | RW |

| 03            |             | Rxオプション・レジスタ           | RW |

| 04            |             | TRcalハイ・レジスタ           | RW |

| 05            |             | TRcalロー・レジスタ           | RW |

| 06            |             | AutoACK待ち時間レジスタ        | RW |

| 07            |             | Rx応答なし時間レジスタ           | RW |

| 08            |             | Rx待ち時間レジスタ             | RW |

| 09            |             | Rxフィルタ設定レジスタ           | RW |

| 0A            |             | Rxミキサ/ゲインレジスタ          | RW |

| 0B            |             | レギュレータ/PAバイアス・レジスタ     | RW |

| 0C            |             | RF出力/LOコントロール・レジスタ     | RW |

| 0D            |             | 補助レジスタ1                | RW |

| 0E            |             | 補助レジスタ2                | RW |

| 10            | コンフィギュレーション | 測定コントロール・レジスタ          | RW |

| 11            |             | VCOコントロール・レジスタ         | RW |

| 12            |             | CPコントロール・レジスタ          | RW |

| 13            |             | モジュレータ・コントロール・レジスタ1    | RW |

| 14            |             | モジュレータ・コントロール・レジスタ2    | RW |

| 15            |             | モジュレータ・コントロール・レジスタ3    | RW |

| 16            |             | モジュレータ・コントロール・レジスタ4    | RW |

| 17            |             | PLL主レジスタ1              | RW |

| 18            |             | PLL主レジスタ2              | RW |

| 19            |             | PLL主レジスタ3              | RW |

| 1A            |             | PLL補助レジスタ1             | RW |

| 1B            |             | PLL補助レジスタ2             | RW |

表 9. レジスタ・マップ (続き)

| アドレス<br>(16進) | 主な機能        | 内容                                                        | 種類                                       |

|---------------|-------------|-----------------------------------------------------------|------------------------------------------|

| 1C            | コンフィギュレーション | PLL補助レジスタ3                                                | RW                                       |

| 1D            |             | インテロゲータ・コリジョン検出/IQ選択設定レジスタ                                | RW                                       |

| 22            |             | エミッタ結合ミキサ・オプション・レジスタ                                      | RW                                       |

| 29            | ステータス       | ステータス読み出しページ設定レジスタ                                        | RW                                       |

| 2A            |             | AGC/内部ステータス表示レジスタ                                         | R                                        |

| 2B            |             | RSSI表示レジスタ                                                | R                                        |

| 2C            |             | AGL/VCO/F_CAL/PilotFreqステータス表示レジスタ<br>(r2Cpage[1:0] = 00) | R                                        |

| 2D            |             | AGL/VCO/F_CAL/PilotFreqステータス・レジスタ<br>(r2Cpage[1:0] = 01)  | R                                        |

| 2E            |             | ADC読み取り/レギュレータ設定表示レジスタ (r2Dpage[1:0] = 00)                | R                                        |

| 33            |             | コマンド・ステータス表示レジスタ                                          | R                                        |

| 35            |             | バージョン・レジスタ                                                | R                                        |

| 36            | 割込み         | 割込み有効化レジスタ1                                               | RW                                       |

| 37            |             | 割込み有効化レジスタ2                                               | RW                                       |

| 38            |             | 割込みレジスタ1                                                  | R                                        |

| 39            |             | 割込みレジスタ2                                                  | R                                        |

| 3A            | 通信          | FIFOステータス・レジスタ                                            | R                                        |

| 3B            |             | Rx長レジスタ1                                                  | RW                                       |

| 3C            |             | Rx長レジスタ2                                                  | RW                                       |

| 3D            |             | Tx設定レジスタ                                                  | RW                                       |

| 3E            |             | Tx長レジスタ1                                                  | RW                                       |

| 3F            |             | Tx長レジスタ2                                                  | RW                                       |

|               |             | FIFO I/O レジスタ                                             | T <sub>x</sub> : W<br>R <sub>x</sub> : R |

レジスタ解説表には、ビット名とともに、デバイスへの電源投入後 (EN=L) のデフォルト値が記載されています。短い機能説明とコメントが記載されています。

### 3.1 メイン・コントロール・レジスタ

レジスタ解説表には、ビット名とともに、デバイスへの電源投入後 (EN=L) のデフォルト値が記載されています。短い機能説明とコメントが記載されています。

### 3.1.1 デバイス・ステータス・コントロール・レジスタ

アドレス: 00h

種類: RW

表 10. デバイス・ステータス・コントロール・レジスタ

| ビット | 名称     | デフォルト | 機能                 | コメント                                           |

|-----|--------|-------|--------------------|------------------------------------------------|

| 7   | stby   | 0     | スタンバイ・モード          | 0: ノーマル・モード<br>1: スタンバイ・モード                    |

| 6   | RFU    | 0     | 未使用                | RFUです。セットしないでください。                             |

| 5   | RFU    | 0     | 未使用                | RFUです。セットしないでください。                             |

| 4   | RFU    | 0     | 未使用                | RFUです。セットしないでください。                             |

| 3   | RFU    | 0     | 未使用                | RFUです。セットしないでください。                             |

| 2   | agc_on | 0     | AGCイネーブル           | 0: AGC OFF<br>1: AGC ON                        |

| 1   | rec_on | 0     | レシーバ・イネーブル         | 0: レシーバが無効<br>1: レシーバが有効                       |

| 0   | rf_on  | 0     | トランスマッタとレシーバのイネーブル | 0: Tx RFフィールドとレシーバが無効<br>1: Tx RFフィールドとレシーバが有効 |

### 3.1.2 プロトコル選択レジスタ

アドレス: 01h

種類: RW

表 11. プロトコル選択レジスタ

| ビット | 名称         | デフォルト | 機能         | コメント                                                                                                |

|-----|------------|-------|------------|-----------------------------------------------------------------------------------------------------|

| 7   | RX_crc_n   | 0     | CRCなし受信    | 0: CRCありRx<br>1: CRCなしRx                                                                            |