# 4-channel high-side driver with STi<sup>2</sup>Fuse protection for automotive power distribution applications

## **Features**

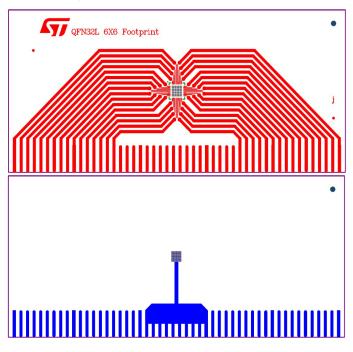

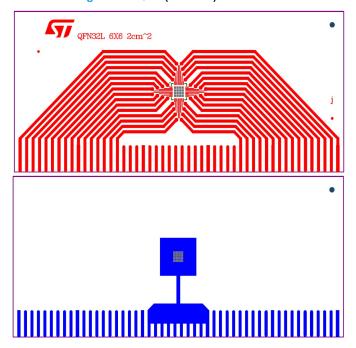

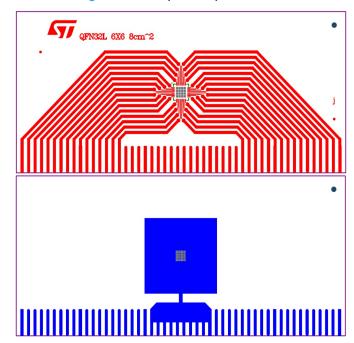

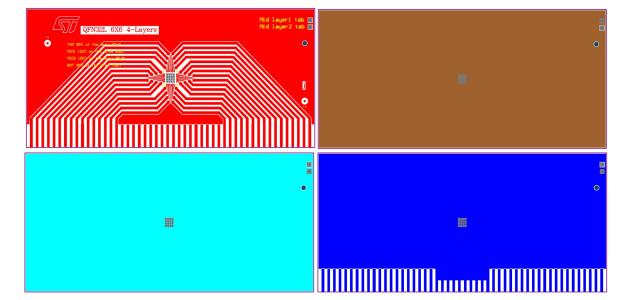

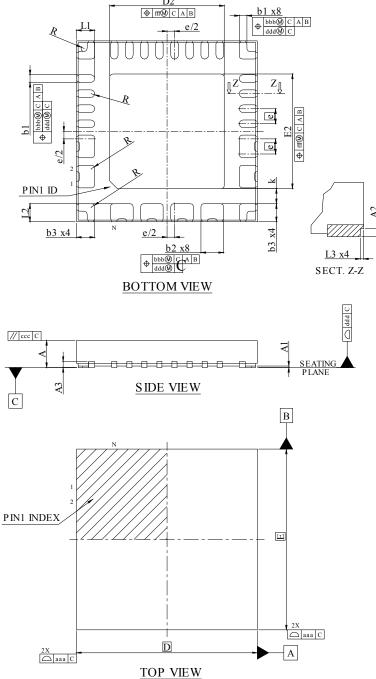

QFN 6x6 mm

| Product status link |  |

|---------------------|--|

| VNF9Q20F            |  |

| Product summary       |               |  |  |  |  |

|-----------------------|---------------|--|--|--|--|

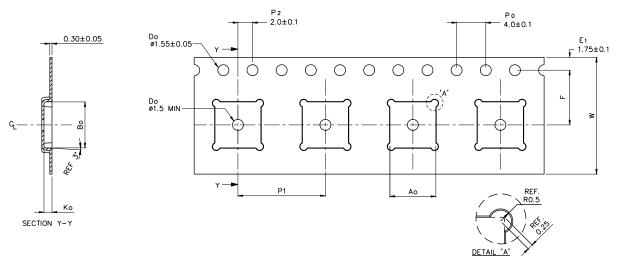

| Order code VNF9Q20FTR |               |  |  |  |  |

| Package               | QFN 6x6       |  |  |  |  |

| Packing               | Tape and reel |  |  |  |  |

| Channel    | V <sub>CC</sub> | R <sub>ON</sub> typ. | I <sub>LIMH</sub> typ. |  |

|------------|-----------------|----------------------|------------------------|--|

| 0, 1, 2, 3 | 28 V            | 21.5 mΩ              | 34.5 A                 |  |

- General

- Quad channel with 24-bit ST-SPI for full diagnostic and digital current sense feedback

- Integrated 10-bit ADC for digital current sense

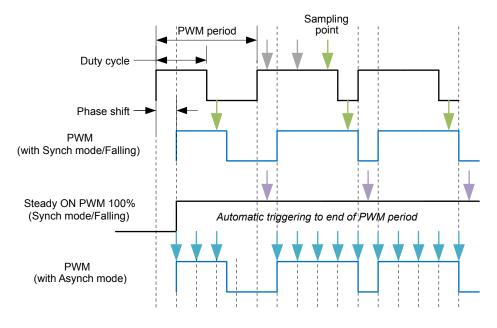

- Integrated PWM engine with independent phase shift and frequency generation (for each channel)

- Programmable Bulb/LED mode for all channels

- Advanced limp-home functions for robust fail-safe system

- Very low standby current

- Optimized electromagnetic emissions

- Very low electromagnetic susceptibility

- Control through direct inputs and/or SPI

- Compliant with European directive 2002/95/EC

- Capacitive loads charging mode

- Diagnostic functions

- Digital proportional load current sense

- Synchronous diagnostic of overload, short to GND and harness protection

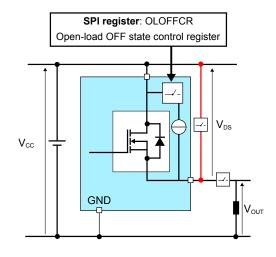

- Asynchronous diagnostic of output shorted to V<sub>CC</sub> and OFF-state openload

- Built In Self-Test for ADC and harness protection

- Programmable case overtemperature warning

- Protections

- Full configurable wire harness protection (STi<sup>2</sup>Fuse)

- Load current limitation

- Self-limiting of fast thermal transients

- Latch-off or programmable time limited auto restart (power limitation and overtemperature shutdown)

- Undervoltage shutdown

- Overvoltage clamp

- Load dump protected

- Protection against loss of ground

## **Description**

The VNF9Q20F is a device made using STMicroelectronics VIPower technology. It is intended for driving resistive or inductive loads directly connected to the ground.

The device is protected against voltage transients on the V<sub>CC</sub> pin. Programming, control, and diagnostics are implemented via the SPI bus. A digital current sense feedback for each channel is provided through an integrated 10-bit ADC. Dedicated trimming bits allow adjusting the ADC reference current.

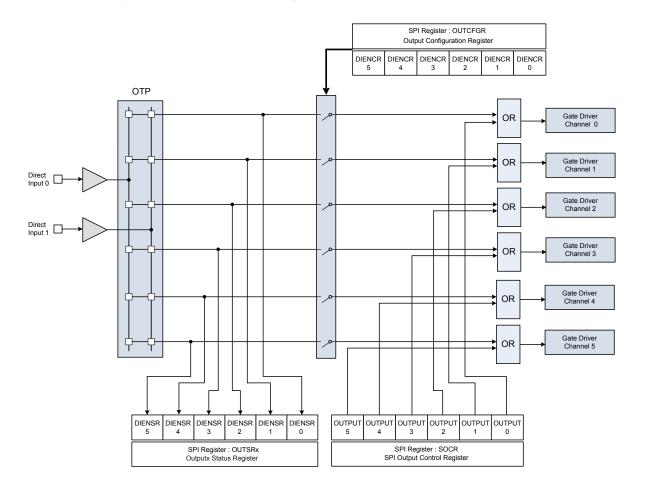

The device is equipped with 4 outputs controllable via SPI or 2-OTP assignable direct inputs. Real-time diagnostic is available through the SPI bus (open-load, output short to  $V_{CC}$ , overtemperature, communication error, power limitation or latch off). The device detects open-load in OFF-state conditions.

The VNF9Q20F embeds the STMicroelectronics proprietary I $^2$ t functionality, featuring an intelligent circuit breaking aimed at protecting PCB traces, connectors and wire harness from overheating, with no impact on load transients like inrush currents and capacitance charging. This function is set by two parameters called I<sub>NOM</sub> and t<sub>NOM</sub>: there are 3 dedicated bits, per each parameter, to set respectively I<sub>NOM</sub> (nominal current) and t<sub>NOM</sub> (nominal timing). The I $^2$ t curve parameters can be individually set per each channel.

The VNF9Q20F can limit the dissipated power to a safe level up to thermal shutdown intervention. Thermal shutdown can be configured as latched off or programmable time limited auto restart.

The output current limitation protects the device in case of overload.

The device enters a fail-safe mode in case of communication loss with the microcontroller, reset of digital memory or watchdog monitoring time-out event. In fail-safe mode, the 4 outputs can be directly controlled by dedicated, assignable direct inputs.

It is also possible to configure the VNF9Q20F in parallel mode (CH0//CH1 only) through a dedicated OTP bit. The VNF9Q20F features an operative condition called capacitive charging mode (CCM), which is available in both fail-safe and normal device states and with channels configured in bulb mode.

DS13909 - Rev 8 page 2/111

## 1 Block diagram and pin description

Vcc Clamp Undervoltage  $V_{\text{REG}}$ VREG d OUT₀ H | OUT₃ Off state Openload Output shorted to Vcc  $V_{\text{DD}}$ **Current Sense** Current Sense CSN SDI 24-bit SPI **Current Sense** SDO Temperature Monitoring Multiplexer SCK Logic ADC **Current Sense** Shadow PWM\_CLK Programmable i²t Registers PWM Engine 5-bit Priority Protection STDBY\_NOT phase ADC BIST Fallback clock Manager OTP / Limp shift (400kHz)  $\mathsf{DI}_0$ i<sup>2</sup>t BIST  $\mathsf{DI}_1$ Capacitive Charging (CCM) GND

Figure 1. Block diagram

DS13909 - Rev 8 page 3/111

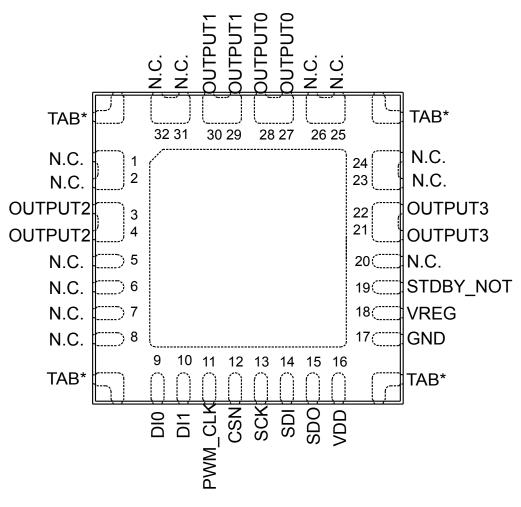

Figure 2. Connection diagram

\*: Electrically connected to TAB. Those pins are intented for thermo-mechanical purpose only. They have to be soldered, but must be electrically isolated at PCB level.

Table 1. Pin functionality description

| Pin #                               | Name     | Function                                                                                                                                       |

|-------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| TAB                                 | VCC      | Battery connection: this is the backside TAB and is the direct connection to drain Power MOSFET switches.                                      |

| 1, 2, 5-8, 20, 23,<br>24-26, 31, 32 | N.C.     | Not connected pin.                                                                                                                             |

| 3, 4                                | OUTPUT2  | Power OUTPUT 2: direct connection to the source Power MOSFET channel 2.                                                                        |

| 9, 10                               | DI0, DI1 | Direct input: direct control for OUTx in limp-home mode. Configurable as OR combination with the relevant SPI OUTx control bit in normal mode. |

| 11                                  | PWM_CLK  | External clock of PWM engine.                                                                                                                  |

| 12                                  | CSN      | Chip select not (active low): it is the selection pin of the device. It is a CMOS compatible input.                                            |

| 13                                  | SCK      | Serial clock: it is a CMOS compatible input.                                                                                                   |

| 14                                  | SDI      | Serial data input: transfers data to be written serially into the device on the SCK rising edge.                                               |

| 15                                  | SDO      | Serial data output: transfers data serially out of the device on the SCK falling edge.                                                         |

| 16                                  | VDD      | DC supply input for the SPI interface. 3.3 V and 5 V compatible.                                                                               |

DS13909 - Rev 8 page 4/111

| Pin#   | Name      | Function                                                                                                                        |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| 17     | GND       | Ground connection: this pin serves as the ground connection for the logic part of the device.                                   |

| 18     | VREG      | DC output of internal preregulator (4.7 V) generated from $V_{CC}$ to supply VREG pin and digital control circuit.              |

| 10     | VILG      | Connect a low ESR capacitor (2 $\mu F)$ in series with a resistor (120 $\Omega)$ close to this pin referenced to device ground. |

| 19     | STDBY_NOT | Standby mode enabler (active low).                                                                                              |

| 21, 22 | OUTPUT3   | Power OUTPUT 3: direct connection to the source Power MOSFET channel 3.                                                         |

| 27, 28 | OUTPUT0   | Power OUTPUT 0: direct connection to the source Power MOSFET channel 0.                                                         |

| 29, 30 | OUTPUT1   | Power OUTPUT 1: direct connection to the source Power MOSFET channel 1.                                                         |

DS13909 - Rev 8 page 5/111

## 2 Functional description

## 2.1 Device interfaces

- SPI: bi-directional interface, accessing RAM/ROM registers (CSN, SCK, SDI, SDO).

- PWM CLK: PWM engine external clock.

- Dlx: multipurpose pins configurable through OTP.

- MCUext bit = 1 (default): input pins for outputs control while the device is in fail-safe mode or normal mode.

- MCUext bit = 0: DI0 assumes digital diagnostic function while DI1 works as global I²t protection unlatch controller (active high).

- V<sub>REG</sub>: DC output of internal preregulator (4 V–6 V). DC supply input for the digital control part. A capacitor

in series with a resistor should be connected between this pin and GND

- V<sub>DD</sub>: DC supply of the SPI Interface. 3.3 V and 5 V compatible. A further external diode might be connected from V<sub>DD</sub> pin (anode) to V<sub>REG</sub> pin (cathode) to ensure a redundant supply to the digital part.

- STDBY\_NOT: Standby mode enabler (active low).

DS13909 - Rev 8 page 6/111

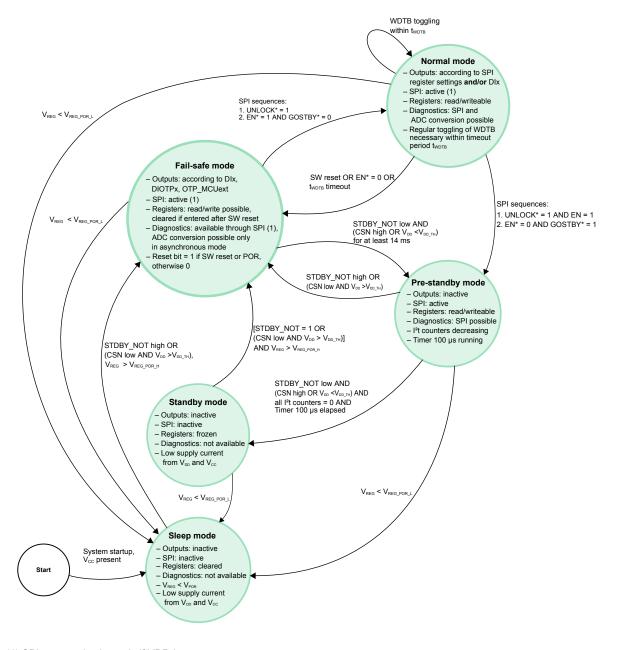

## 2.2 State diagrams and operating modes

The device and the channel state diagrams are reported in Figure 3 and Figure 4 respectively; whilst the Table 2 shows the description of the operating modes.

Figure 3. Device state diagram

(1) SPI communication only if VDD is present.

As showed in the above figure, the device features five different operating modes:

- Standby mode

- Fail-safe mode

- Pre-standby mode

- Normal mode

- Sleep mode

The entering/leaving conditions as well as the operating modes characteristics are described in the Table 2.

DS13909 - Rev 8 page 7/111

Table 2. Operating modes

| Operating mode                                                                                                                | Entering conditions                                                                                                                                                                                                                                                                                                  | Leaving conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Start:<br>transition phase<br>(not operating<br>mode) where<br>neither V <sub>REG</sub> nor<br>V <sub>CC</sub> are available. | -                                                                                                                                                                                                                                                                                                                    | The device leaves this phase to enter sleep mode when:  System startup, V <sub>CC</sub> present                                                                                                                                                                                                                                                                                                                                                                            | VREG < VREG_POR_H  VCC < VUSD  Outputs: OFF  SPI: inactive  Registers: reset values  Diagnostics: not available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Sleep mode:<br>in this state, the<br>device has very low<br>consumption<br>(I <sub>DDstdby</sub> , I <sub>SOFF</sub> )        | From start phase: as soon as V <sub>bat</sub> > V <sub>USD</sub> is applied to V <sub>CC</sub> pin  From normal or fail-safe mode or pre-standby mode or standby mode: V <sub>REG</sub> < V <sub>REG_POR_L</sub>                                                                                                     | The device leaves this state to enter fail-safe mode when:  • V <sub>REG</sub> > V <sub>REG_POR_H</sub>                                                                                                                                                                                                                                                                                                                                                                    | VREG < VREG_POR_H  Outputs: OFF  SPI: inactive  Registers: reset values  Diagnostics: not available  Very low supply current from VDD and VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Standby mode:<br>in this state, the<br>device has low<br>consumption                                                          | From pre-standby mode: As soon as STDBY_NOT low AND (CSN high OR V <sub>DD</sub> < V <sub>DD_TH</sub> ) AND all I²t counters = 0 AND t <sub>stdby</sub> elapsed                                                                                                                                                      | The device leaves this state to enter sleep mode when:  VREG < VREG_POR_L;  The device leaves this state to enter fail-safe mode when:  STDBY_NOT high OR (CSN low AND VDD > VDD_TH)                                                                                                                                                                                                                                                                                       | V <sub>REG</sub> > V <sub>REG_POR_H</sub> Outputs: OFF     SPI: inactive     Registers: not readable     Diagnostics: not available     Low supply current from V <sub>DD</sub> and V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fail-safe mode:<br>(Limp-home)                                                                                                | • From pre-standby mode: STDBY_NOT = 1 OR (CSN low AND VDD > VDD_TH) • From standby mode: [STDBY_NOT = 1 OR (CSN low AND VDD > VDD_TH)] AND VREG > VREG_POR_H • From normal mode: EN_bit = 0 OR WDTB timeout (twDTB) OR SW reset • From sleep mode: [STDBY_NOT = 1 OR (CSN low AND VDD > VDD_TH)], VREG > VREG_POR_H | If V <sub>REG</sub> < V <sub>REG_POR_L</sub> , the device enters sleep mode  If STDBY_NOT = 0 AND (CSN high OR V <sub>DD</sub> < V <sub>DD_TH</sub> ) for at least t <sub>prestdby</sub> , the device enters pre-standby mode  If the SPI sends the following sequence, the device enters normal mode:  1st communication frame:  UNLOCK bit = 1  2nd communication frame:  EN bit = 1 AND GOSTBY bit = 0  This procedure avoids entering the normal mode unintentionally. | V <sub>REG</sub> > V <sub>REG_POR_H</sub> Outputs: according toDIx, DIOTPx, MCUext     SPI: active     Registers: read/write possible, cleared if entered after SW reset     Diagnostics: available through SPI, ADC conversion available only in asynchronous mode     Reset bit: set to 1 if the last state is Standby mode or in case the last command is a SW reset; it is reset to 0 at the first SPI access     Protections: available. In case of over temperature or power limitation, the outputs work in auto-restart.     Harness protection: available for all channels. The channels are configured in autorestart mode if MCUext bit = 1 |

| Normal mode:<br>the transition to this<br>device state is<br>possible ONLY from<br>fail-safe state.                           | • If it is in fail-safe AND the SPI sends the following sequence:  1st communication frame:  • UNLOCK = 1  2nd communication frame:  • GOSTBY = 0 AND EN = 1  This procedure avoids entering the normal mode unintentionally.                                                                                        | If V <sub>REG</sub> < V <sub>REG_POR_L</sub> , the device enters the sleep mode  If the SPI clears the EN bit (EN bit = 0), the device enters the failsafe  If WDTB is not toggled within the timeout period t <sub>WDTB</sub> , the device enters fail-safe mode  If the SPI sends a SW reset, the device enters the fail-safe mode and all the registers are cleared  If the SPI sends the following sequence, the device enters the pre-standby mode:                   | Outputs: according to SPI register settings and/or DIx SPI active Diagnostic: available Registers: read/write is allowed Protections: available. The outputs can be set to "latch" or "time limited auto-restart". In "time limited auto-restart", the outputs are automatically switched on after an over temperature or power limitation event for a limited cumulated time duration; whilst in "latch", the relevant status register must be cleared to switch them on again. Harness protection: available for all channels. The channels are configured in latch mode;                                                                            |

DS13909 - Rev 8 page 8/111

| Operating mode                                                                                                           | Entering conditions                                                                                                                                                                                                                                                                                                                                                                                                                                   | Leaving conditions                                                                                                                                                                                                                                                     | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1st communication frame:  • UNLOCK bit = 1 AND EN bit =1  2nd communication frame:  • GOSTBY bit = 1 AND EN bit = 0  This procedure avoids entering the pre-standby mode unintentionally.                                                                              | Reset bit = 0 Regular toggling of WDTB is necessary within timeout period t <sub>WDTB</sub>                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pre-standby mode                                                                                                         | If it is in fail-safe mode AND STDBY_NOT low AND (CSN high OR V <sub>DD</sub> < V <sub>DD_TH</sub> ) for a time t > t <sub>prestdby</sub> If it is in normal mode AND the SPI sends the following sequence:  1st communication frame:  UNLOCK = 1 AND EN = 1  2nd communication frame:  GOSTBY = 1 AND EN = 0  (It is recommended to set also UNLOCK = 0, in this second frame). This procedure avoids entering the pre-standby mode unintentionally. | To fail-safe mode:  If STDBY_NOT = 1 OR (CSN low and V <sub>DD</sub> > V <sub>DD_TH</sub> )  To standby mode:  If STDBY_NOT = 0 AND (CSN high or V <sub>DD</sub> < V <sub>DD_TH</sub> ) AND all I²t counters = 0 and tstdby elapsed  To sleep mode:  VREG < VREG_POR_L | Outputs: OFF SPI: active Diagnostic: available Registers: read/write is allowed Protections: active I²t counters decreasing and t <sub>stdby</sub> timer running                                                                                                                                                                                                                                                                                                                                                          |

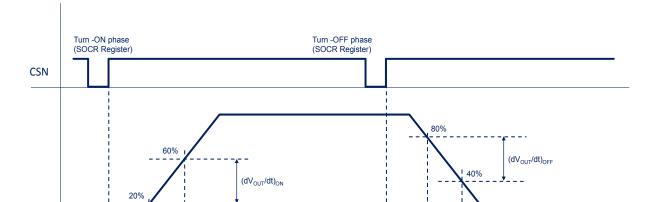

| Capacitive<br>charging mode<br>(CCM): this is not<br>device operating<br>mode, but channel<br>specific operating<br>mode | From fail-safe mode:  • If MCUext = 1 AND after 5 consecutive rising edges on DIx pins within t <sub>CCM_EN</sub> , the corresponding channels will enter CCM, according to DIx OTP configuration.  • If MCUext = 0 AND after 5 consecutive rising edges on DI1 pin within t <sub>CCM_EN</sub> , according to OTP programming, relevant channels will enter CCM.  From normal mode:  • Set CAPCRx bit in SOCR register.                               | Automatically after t <sub>CCM_DIS</sub> time frame in both fail-safe and normal states.     In normal mode, also through a SPI frame, setting EXIT_CAPCRx bit in SOCR register whenever within t <sub>CCM_DIS</sub> time frame                                        | Harness protections: disabled  LED mode: disabled  SPI: active  Latch-OFF delay time (t <sub>D_RESTART</sub> ) after TSD event is disabled  Related parameters reported in Table 67                                                                                                                                                                                                                                                                                                                                       |

| Battery<br>undervoltage:<br>transition phase<br>(not device<br>operating mode)                                           | Any mode: V <sub>CC</sub> < V <sub>USD</sub>                                                                                                                                                                                                                                                                                                                                                                                                          | If V <sub>DD</sub> present AND<br>V <sub>REG</sub> > V <sub>REG_POR_H</sub>                                                                                                                                                                                            | Digital current-sense diagnostic: not available  Output stages are off regardless SPI or DIx status  SPI: active Diagnostic: available Registers: reading is possible  VCCUV flag set, SPI registers content retained If VCC > VUSD + VUSDhyst, the device comes back to the last mode and the VCCUV flag is cleared.  If VREG < VREG_POR_L during VCC increasing, the device is reset: the last operation mode is lost, the logic part is unpowered and the device enters Standby mode as soon as VCC > VUSD + VUSDhyst. |

DS13909 - Rev 8 page 9/111

| Operating mode                                                                 | Entering conditions                          | Leaving conditions                           | Characteristics                                                                                                                                               |

|--------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                |                                              |                                              | During this case, if the DIx is changed, the operation mode is not changed and the output state will be changed accordingly after V <sub>CC</sub> recovering. |

|                                                                                |                                              |                                              | Digital current-sense diagnostic: not available                                                                                                               |

|                                                                                |                                              |                                              | Output Stages are off regardless SPI or DIx status                                                                                                            |

| Battery<br>undervoltage:<br>transition phase<br>(not device<br>operating mode) |                                              |                                              | SPI: active but communication not possible                                                                                                                    |

|                                                                                |                                              |                                              | Diagnostic: NOT available                                                                                                                                     |

|                                                                                | Any mode: V <sub>CC</sub> < V <sub>USD</sub> | If V <sub>DD</sub> NOT present AND           | Registers: reading is not possible                                                                                                                            |

|                                                                                |                                              | V <sub>REG</sub> > V <sub>REG_POR_H</sub>    | V <sub>CCUV</sub> flag set, SPI registers content retained. SPI register content reading always possible                                                      |

|                                                                                |                                              |                                              | If $V_{CC} > V_{USD} + V_{USDhyst}$ , the device comes back to the last mode and the $V_{CCUV}$ flag is cleared.                                              |

|                                                                                |                                              |                                              | In this case, the operation mode is not changed and the output state is changed accordingly after $V_{CC}$ recovering.                                        |

|                                                                                |                                              |                                              | Digital current-sense diagnostic: not available                                                                                                               |

|                                                                                |                                              |                                              | Output stages are off regardless SPI or DIx status                                                                                                            |

|                                                                                |                                              | If V <sub>REG</sub> < V <sub>REG_POR_L</sub> | The device is reset, the last operation mode is lost, the logic is unpowered and the device enters sleep mode as soon as $V_{CC} > V_{USD} + V_{USDhyst}$ .   |

## Transition to fail-safe mode from sleep mode and standby mode

It is mandatory to send a software reset command after the transition to fail-safe mode from sleep mode or standby mode.

## Transition to fail-safe mode from normal mode, using the SPI register

Only one frame is needed: write "CTRL" 0x0001.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 OC1 OC0 Address CMD 0 0 0 1 0 1 0 0 **GOSTBY** UNLOCK Not Used Not Used ΕN PWM TRIG Not Used Not Used DATA1 0 0 0 0 0 0 0 0 LOCKbit5 LOCKbit4 LOCKbit3 LOCKbit2 LOCKbit1 LOCKbit0 **PWMSYNC** Parity DATA2 0 0 0 0 0 0 0 1

Table 3. Frame 1 (write CTRL 0x0001)

## Transition to fail-safe mode from normal mode by SW-reset

SPI Reset occurs by using the "read device information" command (applicable only on ROM area) at the reserved ROM address 0x3F. This is equivalent of sending a 0xFF command.

Only one frame is needed: read "ROM" 0x3F 0x--.

DS13909 - Rev 8 page 10/111

| Table 4. F | rame 1 | : read ( | (ROM) | 0x3F | 0x |

|------------|--------|----------|-------|------|----|

|------------|--------|----------|-------|------|----|

|       | Bit 7            | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------------------|-------|---------|-------|-------|-------|-------|-------|

| CMD   | OC1              | OC0   | Address |       |       |       |       |       |

|       | 1                | 1     | 1       | 1     | 1     | 1     | 1     | 1     |

| DATA1 | X <sup>(1)</sup> | X     | X       | X     | X     | X     | X     | Х     |

|       | 0                | 0     | 0       | 0     | 0     | 0     | 0     | 0     |

| DATA2 | Х                | Х     | X       | X     | X     | X     | X     | Х     |

|       | 0                | 0     | 0       | 0     | 0     | 0     | 0     | 0     |

<sup>1.</sup> X = do not care. At least one of these bits must be zero, as 0xFFFF frame is not allowed.

The entry to the Fail Safe mode can occur due to the CSN timeout.

In this specific case, the following procedure must be executed to leave the Fail Safe mode:

- Removing the cause of the CSN stuck

- Toggling the CSN pin for a min t<sub>SHCH</sub> (time to release the SDO line), see parameter in Table 51

- Sending the SPI frames

If the above procedure is not respected, the first SPI frame will be rejected and the state transition will fail.

## Transition from fail-safe mode to normal mode is performed by two special SPI sequences

- Frame 1: write "CTRL"0x4000

- Frame 2: write "CTRL"0x0800

Table 5. Frame 1 (write CTRL0x4000)

|       | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2        | Bit 1    | Bit 0    |  |

|-------|-----------|-----------|----------|----------|----------|--------------|----------|----------|--|

| CMD   | OC1       | OC0       |          | Address  |          |              |          |          |  |

| CIVID | 0         | 0         | 0        | 1        | 0        | 1            | 0        | 0        |  |

| DATA1 | GOSTBY    | UNLOCK    | Not Used | Not Used | EN       | PWM_<br>TRIG | Not Used | Not Used |  |

|       | 0         | 1         | 0        | 0        | 0        | 0            | 0        | 0        |  |

| DATA2 | LOCKbit 5 | LOCKbit 4 | LOCKbit3 | LOCKbit2 | LOCKbit1 | LOCKbit0     | PWMSYNC  | Parity   |  |

| DATAZ | 0         | 0         | 0        | 0        | 0        | 0            | 0        | 0        |  |

Table 6. Frame 2 (write CTRL0x0800)

|       | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|-------|-----------|-----------|----------|----------|----------|----------|----------|----------|

| CMD   | OC1       | OC0       | Address  |          |          |          |          |          |

| CIVID | 0         | 0         | 0        | 1        | 0        | 1        | 0        | 0        |

| DATA1 | GOSTBY    | UNLOCK    | Not Used | Not Used | EN       | PWM_TRIG | Not Used | Not Used |

| DAIAI | 0         | 0         | 0        | 0        | 1        | 0        | 0        | 0        |

| DATAS | LOCKbit 5 | LOCKbit 4 | LOCKbit3 | LOCKbit2 | LOCKbit1 | LOCKbit0 | PWMSYNC  | Parity   |

| DATA2 | 0         | 0         | 0        | 0        | 0        | 0        | 0        | 0        |

## Transition from normal mode to pre-standby mode using SPI: two frames needed

- Frame 1: write "CTRL"0x4800

- Frame 2: write "CTRL"0x8000

DS13909 - Rev 8 page 11/111

|  | Table 7. Frame 1 | (write CTRL 0x4800) | - Normal mode to | pre-standby mode |

|--|------------------|---------------------|------------------|------------------|

|--|------------------|---------------------|------------------|------------------|

|       | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|-------|-----------|-----------|----------|----------|----------|----------|----------|----------|

| CMD   | OC1       | OC0       |          |          | Α        | ddress   |          |          |

| CIVID | 0         | 0         | 0        | 1        | 0        | 1        | 0        | 0        |

| DATA1 | GOSTBY    | UNLOCK    | Not Used | Not Used | EN       | PWM_TRIG | Not Used | Not Used |

| DAIAI | 0         | 1         | 0        | 0        | 1        | 0        | 0        | 0        |

| DATAS | LOCKbit 5 | LOCKbit 4 | LOCKbit3 | LOCKbit2 | LOCKbit1 | LOCKbit0 | PWMSYNC  | Parity   |

| DATA2 | 0         | 0         | 0        | 0        | 0        | 0        | 0        | 0        |

Table 8. Frame 2 (write CTRL 0x8000)-Normal mode to pre-standby mode

|       | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|-------|-----------|-----------|----------|----------|----------|----------|----------|----------|

| CMD   | OC1       | OC0       |          |          | А        | ddress   |          |          |

| CIVID | 0         | 0         | 0        | 1        | 0        | 1        | 0        | 0        |

| DATA1 | GOSTBY    | UNLOCK    | Not Used | Not Used | EN       | PWM_TRIG | Not Used | Not Used |

| DAIAI | 1         | 0         | 0        | 0        | 0        | 0        | 0        | 0        |

| DATA2 | LOCKbit 5 | LOCKbit 4 | LOCKbit3 | LOCKbit2 | LOCKbit1 | LOCKbit0 | PWMSYNC  | Parity   |

| DATAZ | 0         | 0         | 0        | 0        | 0        | 0        | 0        | 0        |

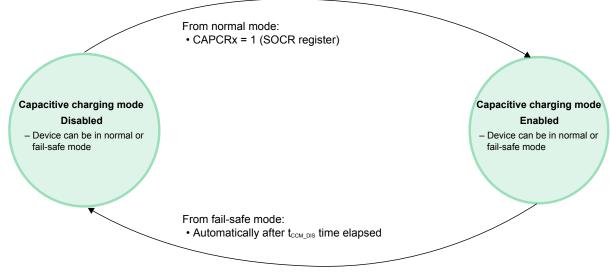

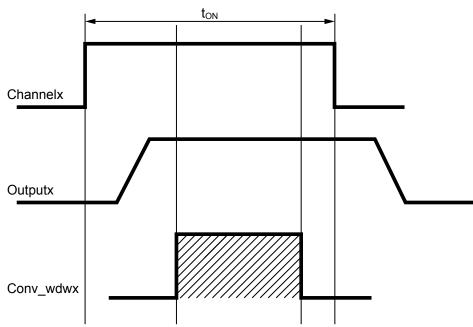

Figure 4. Channel state diagram (CCM)

#### From fail-safe mode:

- MCUext = 1 AND after 5 consecutive rising edges on DIx pins within tCCM\_EN (channels according to DIx OTP configuration).

- MCUext = 0 AND after 5 consecutive rising edges on DI1 pin within tCCM\_EN (relevant channels according to OTP programming)

## From normal mode:

- setting EXIT\_CAPCRx bit in SOCR register whenever within t<sub>CCM\_DIS</sub> time

- $\bullet$  Automatically after  $t_{\tt CCM\_DIS}$  time elapsed

DS13909 - Rev 8 page 12/111

## 3 Protections

## 3.1 Thermal case temperature monitoring and pre-warning

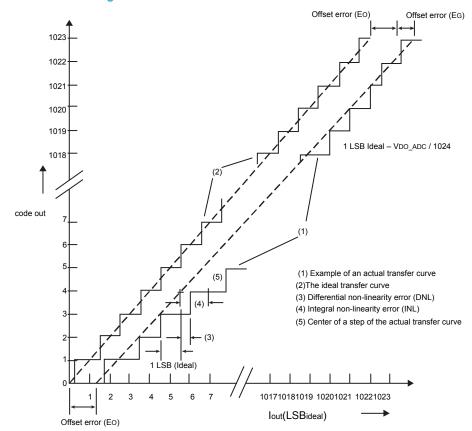

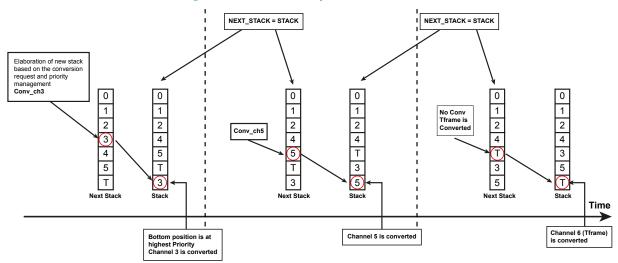

Case-temperature is constantly monitored via a 10-bit ADC converter and data is available in the dedicated status register (thermal sensor voltage register, address 0x31h).

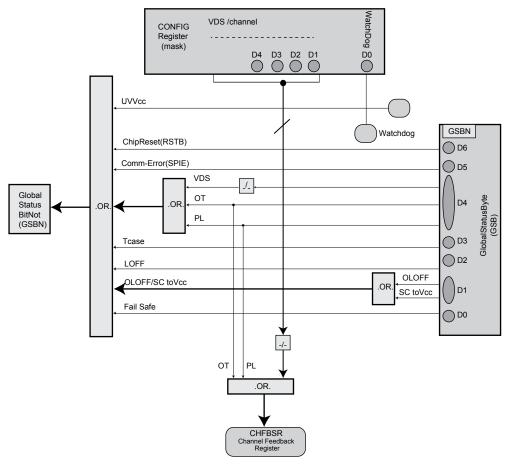

Three different thermal warnings TW1, TW2, TW3 will be mirrored in all the OUTSRx status registers (addresses from 0x20h to 0x23h), referring to 120 °C, 130 °C and 140 °C frame temperature thresholds, respectively. On top of that, the content of TW1 bit is reflected in the Global Status Byte (bit1 –  $T_{CASE}$ ). This bit is set if the frame temperature is greater than the threshold (120 °C) and can be used as a global temperature pre-warning. The bit is cleared automatically when the frame temperature drops below the case-temperature reset threshold ( $T_{CR1}$ ).

## 3.2 Junction overtemperature (OT)

If the junction temperature of a channel rises above the shutdown temperature  $T_{TSD}$ , an overtemperature (OT) event is detected.

The channel is switched OFF and the corresponding bit in the Address OUTSRx register - Channel Feedback Status Register (CHFBSR) is set. As a consequence, the thermal shutdown bit (TSD/PL, bit 4) in the Global Status Byte and the Global Error Flag are set.

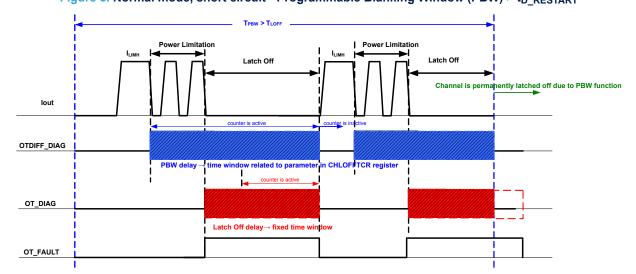

In Normal Mode, each output channel can be either set in latched OFF or time limited auto-restart operation in case of a junction over temperature event.

- In latched OFF operation: the output remains switched OFF until the junction temperature falls below the reset threshold T<sub>R</sub>. In order to restart the channel, after elapsing of restart delay time (t<sub>D\_RESTART</sub>), the MCU shall reset the latch-off event by refreshing the programmed value in the dedicated register (CHLOFFTCR1 or CHLOFFTCR0). The action will clear the corresponding CHLOFFSR bit in Output Status Register OUTSRx and the bit 4 (TSD/PL bit) in the Global Status Byte.

- In time limited auto-restart operation: during the programmed time, the output is switched off as described and switches on again automatically when the junction temperature falls below the reset temperature T<sub>R</sub> and restart delay time (t<sub>D\_RESTART</sub>) is elapsed. In order to allow asynchronous diagnostic, the status bit is latched during OFF state of the channel and it is automatically cleared when the junction temperature falls below the thermal reset temperature (T<sub>RS</sub>) of OT detection. It has to be mentioned that the time limited autorestart (t<sub>BLANKING</sub>) and restart delay time (t<sub>D\_RESTART</sub>) are contemporarily running, so in case t<sub>BLANKING</sub> is programmed with a smaller value as t<sub>D\_RESTART</sub> the channel will stay latched-off after the first OT intervention. After the programmed time has elapsed, the output remains switched OFF and acts as latch-off mode.

In fail-safe mode the channel works in auto-restart mode with restart delay time to RESTART after each OT event.

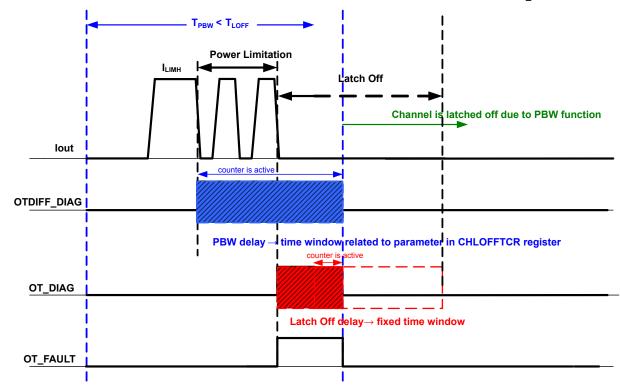

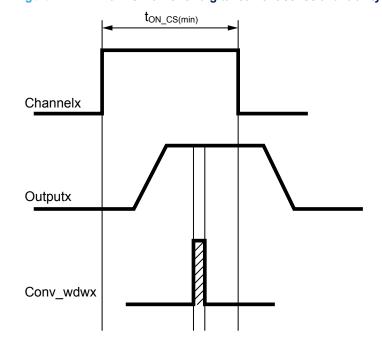

Figure 5. Normal mode, short circuit - Programmable Blanking Window (PBW) > t<sub>D. RESTART</sub>

DS13909 - Rev 8 page 13/111

Figure 6. Normal mode, short circuit - Programmable Blanking Window (PBW) < t<sub>D</sub> RESTART

## 3.3 Power limitation (PL)

If the difference between junction temperature and case temperature ( $\Delta T = T_J - T_C$ ) rises above the power limitation threshold  $\Delta T_{PLIM}$ , a power limitation event is detected.

The corresponding bit in the OUTSRx register - Channel Feedback Status bit (CHFBSR) - is set. The channel is switched OFF and therefore the power limitation bit (TSD/PL, bit 4) in the Global Status Byte and the Global Error Flag are set.

In normal mode, each output channel can be either set in latched OFF or time limited auto-restart operation in case of a power limitation event.

- In latched off operation: the output remains switched OFF until the difference between junction temperature and case temperature (ΔT = T<sub>J</sub> T<sub>C</sub>) decreases below ΔTPLIMR. In order to restart the channel, the MCU shall reset the latch-off event by refreshing the programmed value in the dedicated register (CHLOFFTCR1 or CHLOFFTCR0). The action will clear the corresponding CHLOFFSR bit in the Output Status Register OUTSRx and bit 4 (TSD/PL) in the Global Status Byte.

- In time limited auto-restart: during the programmed time, the output is switched off as described and switches on again automatically when the difference between junction temperature and case temperature (ΔT = T<sub>J</sub> T<sub>C</sub>) decreases below Δ<sub>TPLIMR</sub>. In order to allow asynchronous diagnostic, the status bit is latched during OFF-state of the channel and it is automatically cleared when the difference between junction temperature and case temperature (ΔT = T<sub>J</sub> T<sub>C</sub>) decreases below ΔT<sub>PLIMRS</sub>. After the programmed time has elapsed, the output remains switched OFF and acts as in latch-off mode.

- In Fail Safe mode the channel works in auto-restart mode.

- To improve the performances vs load compatibility test,  $\Delta T_J$  value is set at 80°C for  $V_{CC}$  < 17.5 V, whilst it is set at 55 °C for  $V_{CC}$  > 17.5 V.

- In capacitive charge mode (CCM) ΔT<sub>.1</sub> value is set at 35°C.

## 3.4 Overload protection—Output current limitation (I<sub>I IMH</sub>)

In case of soft overload leading a channel to any output current level (including current limitation) with an output voltage above the current sense shut down threshold, the programmed I<sup>2</sup>t curve will be still verified by the implemented algorithm.

DS13909 - Rev 8 page 14/111

During short circuit condition or medium/hard overload, the output voltage does not overcome current sense shut down threshold then, the current sense is not operative, the I²t curve is not verified by the implemented algorithm but the harness protection shall work according to the ILIM LATCHx setting.

On top of that, the device output current is clamped to the current limitation threshold (I<sub>LIMH</sub>).

The device behavior in current limitation can be set by a dedicated OTP bit (ILIM LATCHx) - 1x channel:

- If ILIM\_LATCHx = 1: channel is switched off (after t<sub>FILTER\_OL</sub>) and latched. In order to restart the channel, the MCU shall reset the latch-off event by refreshing the programmed value in the dedicated register (CHLOFFTCR1 or CHLOFFTCR0). The action will clear the corresponding CHLOFFSR bit in Output Status Register OUTSRx and bit 4 in the Global Status Byte.

- If ILIM LATCHx = 0: channel is set in auto-restart mode, allowing power limitation.

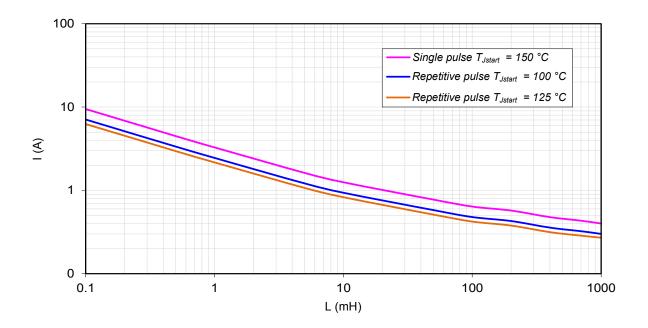

## 3.5 Electronic harness protection (STi<sup>2</sup>Fuse)

The VNF9Q20F embeds the STMicroelectronics proprietary I²t functionality, featuring an intelligent circuit breaking aimed at protecting PCB traces, connectors and wire harness from overheating, with no impact on load transients like inrush currents and capacitance charging. The electronic wire harness protection, I²t protection, is active in all operating modes, except in:

- Standby mode when the device is in the lowest quiescent current consumption mode and all analog and digital functions are in idle mode and output stages are off. Also, when a channel is in CCM, capacitive charging mode, the I²t protection on that specific channel is disabled.

- In CCM mode the wire harness remains in any case fully protected, since CCM mode is the latest aborted after t<sub>CCM\_DIS</sub> with low RMS current.

- In LED mode, when the channel is operating in high R<sub>DSON</sub> and low current limitation mode. In this case, the wires are protected by the intrinsic thermal I-t capability of the device.

- In reverse battery condition when outputs are automatically activated.

In all other conditions, the wire harness protection is active and works fully autonomous and in particular does not require any MCU control or supervision. The I²t protection functionality is equipped with specific safety mechanism such as built-in self-tests (BIST) for the current sense block responsible for acquiring the load current and the I²t block itself, which makes this function ASILx ready. In the ITCNTSR register the current value of the integrated I²t budget is reported and allows the application to monitor how much of the available I²t budget is actually consumed.

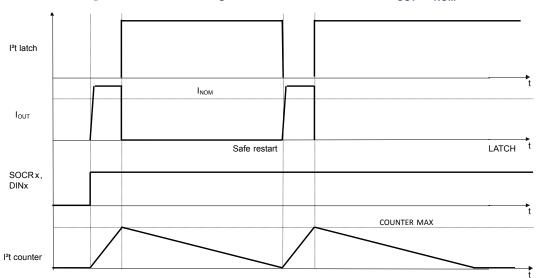

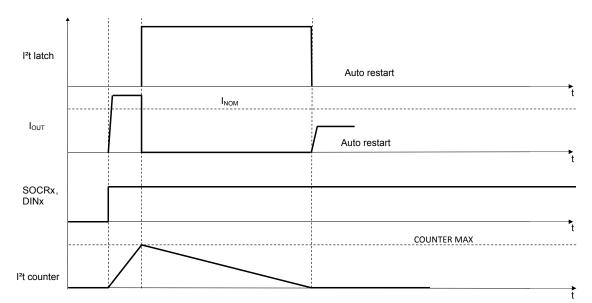

At each POR an internal flag Safe\_Restart is set. This flag allows the device to automatically restart after first harness protection triggering, then the Safe\_Restart flag is reset (see Figure 7.  $I^2t$  counter: single safe restart after POR with  $I_{OUT} > I_{NOM}$ ).

Figure 7. I2t counter: single safe restart after POR with I<sub>OUT</sub> > I<sub>NOM</sub>

DS13909 - Rev 8 page 15/111

The l²t protection is based on a continuous RMS output current calculation. The current sense for l²t calculation is sampled for each channel every  $t_{-}$  l²t \_SAMPLE (given by the internal base frequency for l²t state machine  $f_{CLK}$ ) with linearity ensured up to  $I_{LIMH}$ . Since the current sense block is not active in the hard short circuit condition or whenever the output voltage drops below the current sense shutdown threshold ( $V_{OUT\_FSD}$ ), the behavior of the channel when in current limitation is programmable (see Section 3.4: Overload protection—Output current limitation ( $I_{LIMH}$ )).

In the case ILIM\_LATCHx is programmed in latch-off mode, the current sense, and consequently the I²t protection function are always active when output is on (for the exceptions see above).

In case ILIM\_LATCHx is programmed in auto restart mode, the current sense, and consequently the I²t protection function are active as long as the output voltage remains above the current sense shutdown threshold (V<sub>OUT\_FSD</sub>). As soon as the output voltage drops below the current sense shutdown threshold (V<sub>OUT\_FSD</sub>), for example through a hard short circuit, the current sense is inhibited. In such condition however the I²t wire harness protection is still operative, integrating with the fastest counter speed, while RMS current is maintained at a low value, thanks to the power limitation protection, hence still effectively protecting the wire.

The shape of the actual I²t protection curve is a staircase curve, which is determined by two configurable parameters, I\_NOM and t\_NOM. Both parameters are accessible through the SPI FSITCRx register, read-and writeable.

#### Nominal time t<sub>NOM</sub>

The default  $t_{NOM}$  parameter is programmed by 3 OTP bits (TNOM0, TNOM1, TNOM2, for each channel). Its default value is 300 s.

| Nominal time value | TNOM2 | TNOM1 | TNOM0 |

|--------------------|-------|-------|-------|

| 300 s (default)    | 0     | 0     | 0     |

| 257 s              | 0     | 0     | 1     |

| 214 s              | 0     | 1     | 0     |

| 172 s              | 0     | 1     | 1     |

| 129 s              | 1     | 0     | 0     |

| 86 s               | 1     | 0     | 1     |

| 44 s               | 1     | 1     | 0     |

| 1 s                | 1     | 1     | 1     |

Table 9. Nominal time

#### Nominal current INOM

The default I<sub>NOM</sub> parameter is programmed by 3 OTP bits (INOM0, INOM1, INOM2, for each channel). Its default value is 6 A.

**Table 10. Nominal current**

| Nominal current value | INOM2 | INOM1 | INOM0 |

|-----------------------|-------|-------|-------|

| 1.5 A                 | 0     | 0     | 1     |

| 2 A                   | 0     | 1     | 0     |

| 2.5 A                 | 0     | 1     | 1     |

| 3 A                   | 1     | 0     | 0     |

| 3.5 A                 | 1     | 0     | 1     |

| 4 A                   | 1     | 1     | 0     |

| 5 A                   | 1     | 1     | 1     |

| 6 A (default)         | 0     | 0     | 0     |

DS13909 - Rev 8 page 16/111

Note:

In parallel mode, the  $l^2t$  protection function is available. In this case, the configuration data are applied only to CH0. Effectively the  $l_{NOM}$  value is doubled.

The value of  $I_{NOM}$  represents the level of steady state current, which can be accepted for infinite time in the system consisting of IC, routing, connectors, wiring, and load. The value of  $t_{NOM}$  specifies how fast the staircase curve reaches the  $I_{NOM}$  value.

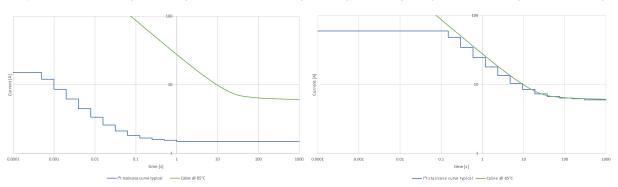

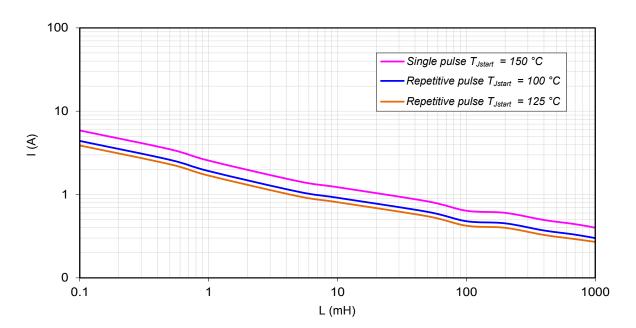

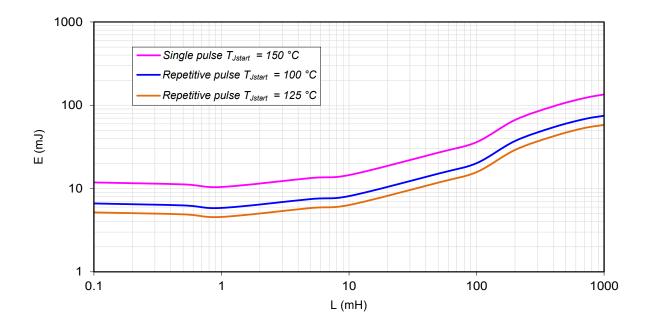

The Figure 8 depicts the  $I^2t$  staircase protection curve with a configuration of  $I_{NOM} = 4$  A and  $t_{NOM} = 300$  s and for comparison the  $I^2t$  isothermic curve of a wire with 0.13 mm<sup>2</sup> cross section at  $T_A = 85$  °C heating up to 150 °C. It can be seen that the  $I^2t$  staircase protection curve is always left below the wire isothermic curve, which means the  $I^2t$  protection algorithm protects the wire from carrying an RMS current, which would lead to a higher temperature increase than the one of the isothermic curve.

CH0 and CH1 can be paralleled by setting a specific bit in the OTP memory map. In this case only the configuration data of channel 0 applies and the value of  $I_{NOM}$  is effectively doubled while  $R_{DSon}$  is effectively halved.

0.0001 0.001 0.01 0.1 1 10 100 1000 time [s]

−I²t staircase curve typical −−− Cable @ 85°C

Figure 8. Protection curve with  $I_{NOM} = 4$  A and  $t_{NOM} = 300$  s vs a 0.13 mm<sup>2</sup> wire isothermic curve

DS13909 - Rev 8 page 17/111

0.0001 0.001 0.01 0.1 1 10 100 1000 time [s]

Figure 9. Protection curve in parallel mode with  $I_{NOM}$  = 6 A and  $t_{NOM}$  = 300 s vs a 0.17 mm<sup>2</sup> wire isothermic curve

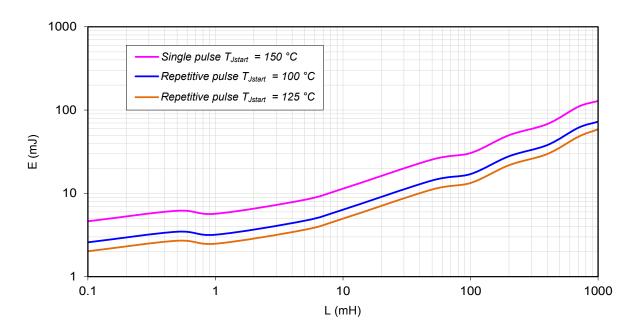

The  $I^2t$  protection curve can be moved in y-direction by changing the  $I_{NOM}$  value and in x-direction changing the  $t_{NOM}$  value. The following figure represents the total range of  $I^2t$  the device can cover, ranging from  $I_{NOM-MIN} = 1.5$  A with  $t_{NOM-MIN} = 1$  s up to  $I_{NOM-MAX} = 6$  A with  $t_{NOM-MAX} = 300$  s.

Figure 10. Lowest  $I_{NOM}$  and  $t_{NOM}$  (left hand) and highest  $I_{NOM}$  and  $t_{NOM}$  (right hand) configuration setting

Note:

In the highest configuration settings, a 0.13 mm<sup>2</sup> wire is not protected as the I<sup>2</sup>t staircase curve intersects with the isothermic curve of the wire.

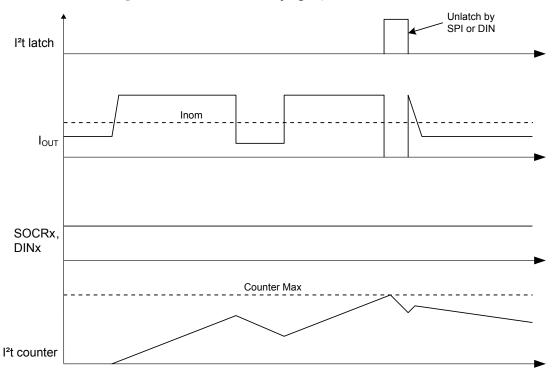

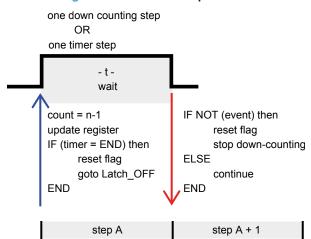

The I²t protection curve consists of 13 steps, each of them corresponding to a specific current threshold. Whenever the load current exceeds a threshold, a counter is counting up. If for instance looking at the example in Figure 8, the current would exceed the value of  $I_{NOM} = 4$  A, but stay below the current threshold of the next step, which is set at 1.03\*  $I_{NOM}$  about, the counter would reach its threshold value after  $t_{NOM} = 300$  s, the harness protection is triggered and the output channel is automatically latched off.

Diagnostic about I²t intervention is available through SPI with the ITOFFSRx bit in the OUTSRx output status register and bit 3 in the global status byte. Both bits are set when the output channel is latched off for wire harness I²t protection. An additional diagnostic indication is available, depending on the configuration of MCUext bit in the OTP memory area. The following table explains the functionality of DINx pins depending on the MCUext bit setting.

DS13909 - Rev 8 page 18/111

Table 11. DINx pin functionality

| MCUext bit  | DIN0                                                          | DIN1                                                  |

|-------------|---------------------------------------------------------------|-------------------------------------------------------|

| 0           | Global I²t status (active low) OR combination of all channels | Global I²t unlatch pin for all channels (active high) |

| 1 (default) | Direct input                                                  | Direct input                                          |

In case MCUext = 0, DIN0 acts as an open drain global I²t status pin with an OR combination of all channels. The DIN0 pin is active low, in case at least one channel has latched off for wire harness I²t protection. The I²t latch can be cleared by clearing:

The ITOFFSRx bit through R&C command

FIXED\_DROP(m)

16

4

1

Or

• Low to high transition on DIN1 pin, it remains at high level for at least t\_DIN\_UNLATCH, then pulls low DIN1 pin. If more than one channel is latched for wire harness I²t protection, this unlatches all channels at the same time.

Consequently, bit 3 in the global status byte is cleared and the channel is restarted. The I<sup>2</sup>t counter is NOT reset, it keeps its actual value reached during down-counting while the channel was latched.

In the case MCUext = 0, both possibilities for unlatching are available in normal mode and fail-safe mode. However, ITOFFSRx bit and bit 3 in the global status byte is cleared only through the R&C command.

In case MCUext = 1, diagnostic and unlatch control is available only through SPI; however, in fail-safe mode wire harness I²t protection is in auto restart mode, unlatching the channel when the I²t counter counted down to 0.

The speed of the counter up-counting (fixed drop, refer to Table 12) is increased every time the load current reaches the next staircase current threshold of the  $I^2t$  curve. Every time the load current drops below the  $I_{NOM}$  threshold the counter is decreasing. The speed of the down-counting depends on how far the load current is below the  $I_{NOM}$ . This algorithm perfectly emulates a continuous RMS (root mean square) current integration, which in fact is the proper indicator to measure the losses in the wire by Joule effect, causing the temperature rise in the wire.

I<sub>OUT</sub> range 0.25\*I<sub>NOM</sub> ÷ 0 0.5\*I<sub>NOM</sub> ÷ 0.25\*I<sub>NOM</sub>

$0.75*I_{NOM} \div 0.5*I_{NOM}$

$I_{NOM} \div 0.75*I_{NOM}$

Table 12. FIXED DROP table

The concept of up and down-counting for RMS current control is illustrated in the figure below:

DS13909 - Rev 8 page 19/111

Figure 11. I<sup>2</sup>t counter with varying I<sub>NOM</sub> latch and unlatch

The last (13<sup>th</sup>) step of the I²t protection staircase curve is equal to 10 \*  $I_{NOM}$ . Whenever the load current exceeds the 13<sup>th</sup> threshold, the output channel is latched off immediately within  $t_{doff}$  +  $t_f$ , protecting the integrity of the board net power supply.

The  $I^2t$  block is supplied from an internal voltage regulator supplied by  $V_{REG}$ . Therefore, as soon as  $V_{REG}$  drops below  $V_{REG\_POR\_L}$ , the accumulated  $I^2t$  counter value is reset and the device enters in sleep mode.

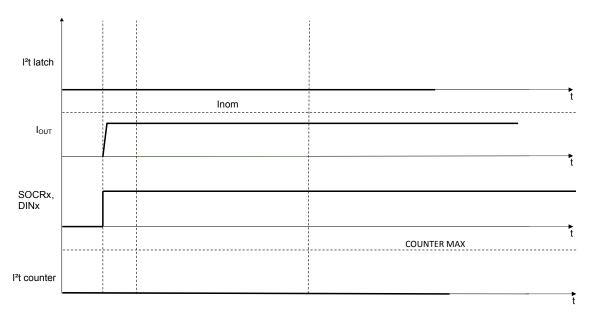

Figure 12. I<sup>2</sup>t counter after POR with I<sub>OUT</sub> > I<sub>NOM</sub>

DS13909 - Rev 8 page 20/111

Figure 13. I<sup>2</sup>t counter after POR with I<sub>OUT</sub> < I<sub>NOM</sub>

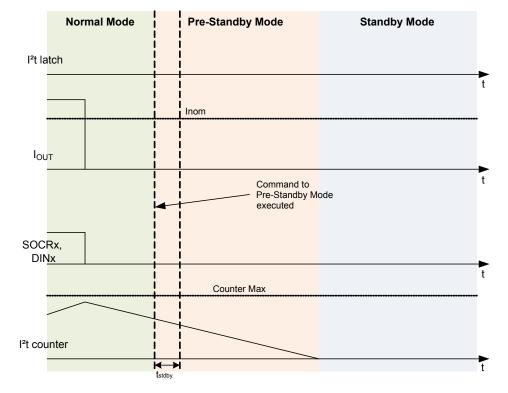

The transition from pre-standby mode to standby mode requires all channels I<sup>2</sup>t counters have counted down to 0 (see Figure 14).

Figure 14. Transition to standby mode with I<sup>2</sup>t counter running

All protections work in parallel, so the most restrictive one intervenes independently of the others.

## 3.6 Reverse battery turn-on

In the reverse battery condition, the outputs are automatically activated and all protections are not active. The self turn-on feature cannot be disabled.

DS13909 - Rev 8 page 21/111

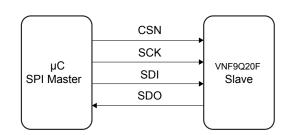

## 4 SPI functional description

## 4.1 SPI communication

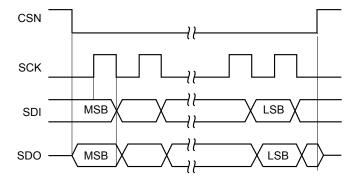

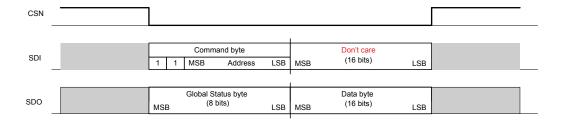

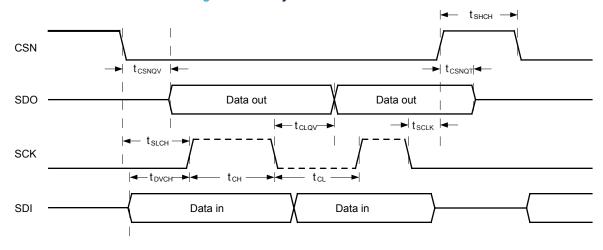

The SPI communication is based on a standard ST-SPI 24-bit interface, using CSN, SDI, SDO and SCK signal lines.

Input data are shifted into SDI, MSB first while output data are shifted out on SDO, MSB first.

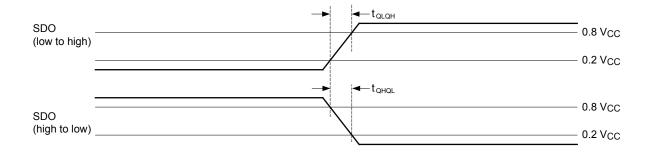

## 4.1.1 Signal description

During all operations,  $V_{DD}$  must be held stable and within the specified valid range:  $V_{DD}$  min to  $V_{DD}$  max. The  $V_{REG}$  must be held stable and within the specified range,  $V_{REG}$  min to  $V_{REG}$  max, to supply the digital part.

Table 13. SPI signal description

| Name                            | Function                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

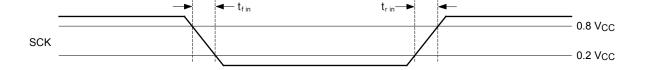

| Serial<br>clock<br>SCK          | This input signal provides the timing of the serial interface. Data present at serial data input (SDI) are latched on the rising edge of the serial clock (SCK). Data on serial data output (SDO) change after the falling edge of the serial clock (SCK freq > 1 MHz).                                                                                          |

| Serial<br>data input<br>SDI     | This input signal is used to transfer data serially into the device. It receives data to be written. Values are sampled on the rising edge of the serial clock (SCK).                                                                                                                                                                                            |

| Serial<br>data<br>output<br>SDO | This output signal is used to transfer data serially out of the device. Data are shifted out on the falling edge of the serial clock (SCK).                                                                                                                                                                                                                      |

|                                 | When this input signal is high, the device is deselected and serial data output (SDO) is high-Z. Driving this input Low enables the communication. The communication must start on a Low level of serial clock (SCK). Data are accepted only if exactly 24 bits have been shifted in.                                                                            |

|                                 | Note: As per the ST_SPI standard, in the case of failing communication:                                                                                                                                                                                                                                                                                          |

|                                 | CSN stuck at HIGH:                                                                                                                                                                                                                                                                                                                                               |

| Chip<br>select<br>CSN           | <ul> <li>If the device is in normal mode, a WDTB timeout forces the device into fail-safe mode. The serial data out (SDO) remains in high impedance (high-Z). Any valid communication arrived after this event is accepted by the device.</li> <li>CSN stuck at LOW:</li> </ul>                                                                                  |

| CON                             | <ul> <li>In this case and whatever the mode of the device, a CSN timeout protection is<br/>activated and force the device to release the SPI bus. Then the serial data out<br/>(SDO) will go into high impedance (high-Z)</li> </ul>                                                                                                                             |

|                                 | A reset of the CSN timeout (see t <sub>SHCH</sub> in Table 51) is activated with a transition Low to high on the CSN pin (or with a power on reset or software reset). With this reset, the serial data out (SDO) is released and any valid communication is accepted by the device. Without this reset, the next communication is not considered by the device. |

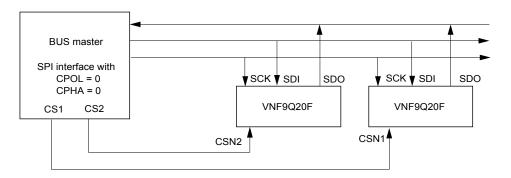

## 4.1.2 Connecting to the SPI bus

A schematic view of the architecture between the bus and devices can be seen in the Figure 16.

All input data bytes are shifted into the device, MSB first. The serial data input (SDI) is sampled on the first rising edge of the serial clock (SCK) after chip select (CSN) goes low. All output data bytes are shifted out of the device on the falling edge of SCK, MSB first on the first falling edge of the chip select (CSN).

DS13909 - Rev 8 page 22/111

#### 4.1.3 SPI mode

Supported SPI mode during a communication phase can be seen in the following figure:

Figure 15. Supported SPI mode

This device can be driven by a microcontroller with its SPI peripheral running in the following mode:

CPOL = 0, CPHA = 0

Figure 16. Bus master and two devices in a normal configuration

## 4.2 SPI protocol

## 4.2.1 SDI, SDO format

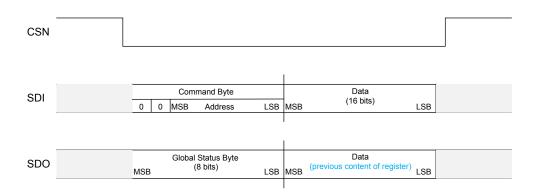

SDI format during each communication frame starts with a command byte. It begins with two bits of operating code (OC0, OC1) which specify the type of operation (read, write, read and clear status, read device information) and it is followed by a 6-bit address (A0:A5). The command byte is followed by two input data bytes (D15:D8) and (D7:D0).

DS13909 - Rev 8 page 23/111

## Table 14. Command byte

| MSB |     |    |    |    |    |    | LSB |

|-----|-----|----|----|----|----|----|-----|

| OC1 | OC0 | A5 | A4 | A3 | A2 | A1 | A0  |

#### Table 15. Input data byte 1

| MSB |     |     |     |     |     |    | LSB |

|-----|-----|-----|-----|-----|-----|----|-----|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8  |

#### Table 16. Input data byte 2

| MSB |    |    |    |    |    |    | LSB               |

|-----|----|----|----|----|----|----|-------------------|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 <sup>(1)</sup> |

#### 1. D0 is the parity bit.

SDO format during each communication frame starts with a specific byte called Global Status Byte (see GSB byte for more details of bit0-bit7). This byte is followed by two output data bytes (D15:D8) and (D7:D0).

Table 17. Global status byte

| MSB  |      |      |      |      |      |      | LSB  |

|------|------|------|------|------|------|------|------|

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

Table 18. Output data byte 1

| MSB |     |     |     |     |     |    | LSB |

|-----|-----|-----|-----|-----|-----|----|-----|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8  |

Table 19. Output data byte 2

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

## 4.2.2 Operating code definition

The SPI interface features four different addressing modes which are listed in Table 20:

Table 20. Operating codes

| OC1 | OC0 | Meaning                         |

|-----|-----|---------------------------------|

| 0   | 0   | Write operation                 |

| 0   | 1   | Read operation                  |

| 1   | 0   | Read and clear status operation |

| 1   | 1   | Read device information         |

## Write mode

The write mode of the device allows to write the content of the input data byte into the addressed register (see list of registers in Table 25). Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first.

During the same sequence the outgoing data are shifted out MSB first on the falling edge of the CSN pin and the subsequent bits on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status Byte and the second to the previous content of the addressed register.

DS13909 - Rev 8 page 24/111

Figure 17. SPI write operation

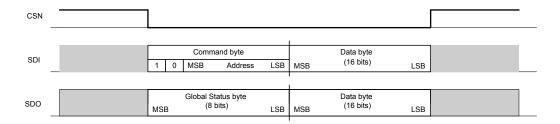

#### Read mode

The read mode of the device allows to read and to check the state of any register. Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first.

The command byte allows to determine which register content is read, whilst the other two data bytes are "don't care".

In case of a read mode on an unused address, the global status/error byte on the SDO pin is followed by 0x0000 word.

In order to avoid inconsistency between the Global Status byte and the Status register, the Status register contents are frozen during the SPI communication.

CSN Command Byte SDI (16bit) MSB Address LSB LSB MSE Global Status Byte Data SDO (8bit) (16bit) MSB LSB MSB LSB

Figure 18. SPI read operation

#### Read and clear status command

The read and clear status operation is used to clear the content of the addressed status register (see Table 25). A read and clear status operation with address 0x3Fh clears all Status registers simultaneously.

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which register content is read and the payload bits set to 1 into the data byte determine the bits into the register which have to be cleared.

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status byte and the second to the content of the addressed register.

In order to avoid inconsistency between the Global Status byte and the Status register, the Status register contents are frozen during SPI communication.

DS13909 - Rev 8 page 25/111

Figure 19. SPI read and clear operation

#### Read device information

Specific information can be read but not modified during this mode. Accessible data can be seen in Table 26. Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which information is read whilst the other two data bytes are "don't care".

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status byte and the second to the content of the addressed register and the third byte is 0x00.

Note:

ROM is based on the 8-bit registers, then even if 16 bits are returned, only the second byte contains the addressed ROM register.

Figure 20. SPI read device information

## 4.2.3 Special commands

#### 0xFF - SW Reset: set all control registers to default (ROM access)

An OpCode '11' (read device information) addressed at '111111' forces a Software Reset of the device, second and third bytes are "don't care" provided that at least one bit is zero.

Note:

An OpCode '11' at address '111111' with data field equal to '11111111111111' on the SPI frame is recognized as a frame error and SPIE bit of GSB is set.

Table 21. 0xFF: SW\_Reset

| Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |  |

|-------|---------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|       | Command |       |       |       |       |       |       |  |  |  |  |  |

| OC1   | OC0     |       |       | Add   | ress  |       |       |  |  |  |  |  |

| 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1     |  |  |  |  |  |

| DATA1 | X       | Х     | Х     | Х     | X     | Х     | Х     |  |  |  |  |  |

| DAIAI | 0       | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |  |

| DATA2 | X       | Х     | Х     | Х     | Χ     | Х     | Х     |  |  |  |  |  |

| DATAZ | 0       | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |  |

DS13909 - Rev 8 page 26/111

Note:  $X = do \ not \ care.$

## 0xBF - clear all status registers (RAM access)

When an OpCode '10' (read and clear operation) at address b'111111 is performed.

Table 22. Clear all status registers (RAM access)

| Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |  |

|-------|---------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|       | Command |       |       |       |       |       |       |  |  |  |  |  |

| OC1   | OC0     |       |       | Add   | ress  |       |       |  |  |  |  |  |

| 1     | 0       | 1     | 1     | 1     | 1     | 1     | 1     |  |  |  |  |  |

| DATA1 | Х       | Х     | Х     | Х     | Х     | Х     | Х     |  |  |  |  |  |

| DATA1 | 0       | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |  |

| DATA2 | Х       | Х     | Х     | Х     | Х     | X     | Х     |  |  |  |  |  |

| DATAZ | 0       | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |  |

Note:  $X = do \ not \ care.$

Note: Reset value = the value of the register after a power on.

Default value = the default value of the register. Currently this is equivalent to the reset value.

Cleared register = explicitly read and clear of the register, if it is not write-protected.

## 4.3 Register map

The device contains a set of RAM registers used for device configuration, the device status and ROM registers for device identification. Since ST-SPI is used, Global Status byte defines the device status, containing fault information.

## 4.3.1 Global status byte description

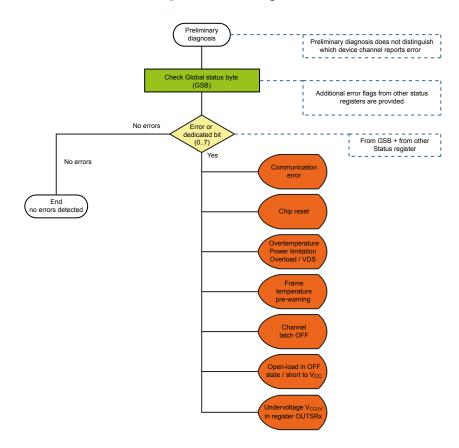

The data shifted out on SDO during each communication starts with a specific byte called global status byte. This one is used to inform the microcontroller about global faults which can happen at channel-side level (that is, like thermal shutdown...) or on the SPI interface (like watchdog monitoring timeout event, communication error, ...). This specific register has the following format:

Table 23. Global Status Byte (GSB)

| MSB  |      |      |        |        |      |       | LSB |

|------|------|------|--------|--------|------|-------|-----|

| GSBN | RSTB | SPIE | TSD/PL | ITLOFF | LOFF | TCASE | FS  |

Table 24. Global Status Byte

| Bit                            | Name               | Reset | Content                                                                                                                                                                                                                                                       |

|--------------------------------|--------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 Global status bit not (GSBN) |                    | 0     | The GSBN is a logically NOR combination of Bit 0 to Bit 6. This bit can also be used as Global Status Flag without starting a complete communication frame as it is present directly after pulling CSN low.                                                   |

| 6                              | Reset bit (RSTB)   | 1     | The RSTB indicates a device reset. In case this bit is set, all internal Control Registers are set to default and kept in that state until the bit is cleared.  The reset bit is automatically cleared by any valid SPI communication                         |

| 5                              | 5 SPI error (SPIE) |       | The SPIE is a logical OR combination of errors related to a wrong SPI communication (SCK count and SDI stuck at errors).  The SPIE bit is automatically set when SDI is stuck at High or Low. The SPIE is automatically cleared by a valid SPI communication. |

DS13909 - Rev 8 page 27/111

| Bit | Name                                                                         | Reset | Content                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-----|------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4   | Thermal shutdown<br>(TSD) or power<br>limitation (PL)                        | 0     | This bit is set in case of thermal shutdown or power limitation.                                                                                                                                                                                                                                  |  |  |  |  |  |