life.augmented

**PM0223**

## プログラミング・マニュアル

Cortex<sup>®</sup>-M0+ プログラミング・マニュアル (STM32L0、

STM32G0、STM32WL および STM32WB シリーズ用)

### 概要

このプログラミング・マニュアルには、アプリケーションやシステムレベルのソフトウェアの開発者向けの情報が記載されています。本書では、STM32L0、STM32G0、STM32WL および STM32WB シリーズ MCU で使用される Cortex<sup>®</sup>-M0+ プロセッサのプログラミング・モデル、命令セット、およびコア・ペリフェラルについて詳しく説明します。

Cortex<sup>®</sup>-M0+ は、マイクロコントローラに統合するために設計された高性能の 32 ビット・プロセッサです。開発者に次のような大きなメリットを提供します。

- 抜群の処理性能と高速な割込み処理の融合

- 幅広いブレークポイント・オプションによって強化されたシステム・デバッグ機能

- 効率的なプロセッサ・コア、システム、およびメモリ

- 内蔵スリープ・モードによる超低消費電力

- プラットフォーム・セキュリティ

# 目次

|          |                                     |           |

|----------|-------------------------------------|-----------|

| <b>1</b> | <b>本書について</b>                       | <b>8</b>  |

| 1.1      | 表記規則                                | 8         |

| 1.2      | レジスタに関する略記                          | 9         |

| 1.3      | Cortex-M0+ プロセッサおよびコア・ペリフェラルについて    | 10        |

| 1.3.1    | システムレベル・インターフェース                    | 11        |

| 1.3.2    | 設定可能な統合デバッグ機能                       | 11        |

| 1.3.3    | Cortex-M0+ プロセッサの特徴の概要              | 11        |

| 1.3.4    | Cortex-M0+ のコア・ペリフェラル               | 12        |

| <b>2</b> | <b>Cortex-M0+ プロセッサ</b>             | <b>13</b> |

| 2.1      | プログラマ・モデル                           | 13        |

| 2.1.1    | ソフトウェアの実行に対するプロセッサのモードと特権レベル        | 13        |

| 2.1.2    | スタック                                | 13        |

| 2.1.3    | コア・レジスタ                             | 14        |

| 2.1.4    | 例外と割込み                              | 19        |

| 2.1.5    | データ型                                | 20        |

| 2.1.6    | Cortex マイクロコントローラ・ソフトウェア・インターフェース標準 | 20        |

| 2.2      | メモリ・モデル                             | 21        |

| 2.2.1    | メモリの領域、タイプ、および属性                    | 22        |

| 2.2.2    | メモリ・システムでのメモリ・アクセスの順序付け             | 22        |

| 2.2.3    | メモリ・アクセスの動作                         | 23        |

| 2.2.4    | キャッシュと共有メモリに対する追加のメモリ・アクセス制約        | 24        |

| 2.2.5    | ソフトウェアによるメモリ・アクセスの順序付け              | 24        |

| 2.2.6    | メモリのエンディアン形式                        | 25        |

| 2.3      | 例外モデル                               | 27        |

| 2.3.1    | 例外状態                                | 27        |

| 2.3.2    | 例外のタイプ                              | 27        |

| 2.3.3    | 例外ハンドラ                              | 29        |

| 2.3.4    | ベクタ・テーブル                            | 30        |

| 2.3.5    | 例外の優先度                              | 31        |

| 2.3.6    | 例外の開始と復帰                            | 31        |

| 2.4      | フォールト処理                             | 34        |

| 2.4.1    | ロックアップ                              | 34        |

|          |                                 |           |

|----------|---------------------------------|-----------|

| 2.5      | 電源管理 .....                      | 35        |

| 2.5.1    | SLEEP モードへの移行 .....             | 35        |

| 2.5.2    | SLEEP モードからのウェイクアップ .....       | 36        |

| 2.5.3    | 外部イベント入力 .....                  | 36        |

| 2.5.4    | 電源管理に関するプログラミングのヒント .....       | 36        |

| <b>3</b> | <b>Cortex-M0+ 命令セット .....</b>   | <b>37</b> |

| 3.1      | 命令セットの概要 .....                  | 37        |

| 3.2      | 組込み関数 .....                     | 40        |

| 3.3      | 命令の説明について .....                 | 41        |

| 3.3.1    | オペランド .....                     | 41        |

| 3.3.2    | PC または SP を使用した場合の制限事項 .....    | 41        |

| 3.3.3    | シフト演算 .....                     | 41        |

| 3.3.4    | アドレスのアライメント .....               | 43        |

| 3.3.5    | PC 相対式 .....                    | 43        |

| 3.3.6    | 条件付き実行 .....                    | 44        |

| 3.4      | メモリ・アクセス命令 .....                | 46        |

| 3.4.1    | ADR .....                       | 47        |

| 3.4.2    | LDR と STR (イミディエート・オフセット) ..... | 48        |

| 3.4.3    | LDR と STR (レジスタ・オフセット) .....    | 49        |

| 3.4.4    | LDR (PC 相対) .....               | 50        |

| 3.4.5    | LDM と STM .....                 | 51        |

| 3.4.6    | PUSH と POP .....                | 53        |

| 3.5      | 汎用データ処理命令 .....                 | 54        |

| 3.5.1    | ADC、ADD、RSB、SBC、および SUB .....   | 55        |

| 3.5.2    | AND、ORR、EOR、および BIC .....       | 57        |

| 3.5.3    | ASR、LSL、LSR、および ROR .....       | 58        |

| 3.5.4    | CMP および CMN .....               | 60        |

| 3.5.5    | MOV および MVN .....               | 61        |

| 3.5.6    | MULS .....                      | 62        |

| 3.5.7    | REV、REV16、および REVSH .....       | 63        |

| 3.5.8    | SXT および UXT .....               | 64        |

| 3.5.9    | TST .....                       | 65        |

| 3.6      | 分岐命令と制御命令 .....                 | 66        |

| 3.6.1    | B、BL、BX、および BLX .....           | 67        |

|          |                                              |           |

|----------|----------------------------------------------|-----------|

| 3.7      | その他の命令 .....                                 | 69        |

| 3.7.1    | BKPT .....                                   | 70        |

| 3.7.2    | CPS .....                                    | 71        |

| 3.7.3    | DMB .....                                    | 72        |

| 3.7.4    | DSB .....                                    | 73        |

| 3.7.5    | ISB .....                                    | 74        |

| 3.7.6    | MRS .....                                    | 75        |

| 3.7.7    | MSR .....                                    | 76        |

| 3.7.8    | NOP .....                                    | 77        |

| 3.7.9    | SEV .....                                    | 78        |

| 3.7.10   | SVC .....                                    | 79        |

| 3.7.11   | WFE .....                                    | 80        |

| 3.7.12   | WFI .....                                    | 81        |

| <b>4</b> | <b>Cortex-M0+ のコア・ペリフェラル .....</b>           | <b>82</b> |

| 4.1      | Cortex-M0+ のコア・ペリフェラルについて .....              | 82        |

| 4.2      | ネスト化されたベクタ割込みコントローラ .....                    | 83        |

| 4.2.1    | CMSIS を使用した Cortex-M0+ NVIC レジスタへのアクセス ..... | 83        |

| 4.2.2    | 割込みセット・イネーブル・レジスタ .....                      | 84        |

| 4.2.3    | 割込みクリア・イネーブル・レジスタ .....                      | 85        |

| 4.2.4    | 割込みセット・ペンディング・レジスタ .....                     | 85        |

| 4.2.5    | 割込みクリア・ペンディング・レジスタ .....                     | 86        |

| 4.2.6    | 割込み優先度のレジスタ .....                            | 86        |

| 4.2.7    | レベル割込みとパルス割込み .....                          | 87        |

| 4.2.8    | NVIC 使用のヒントとコツ .....                         | 88        |

| 4.3      | システム制御ブロック .....                             | 89        |

| 4.3.1    | Cortex-M0+ SCB レジスタの CMSIS マッピング .....       | 89        |

| 4.3.2    | CPUID レジスタ .....                             | 90        |

| 4.3.3    | 割込み制御およびステート・レジスタ (ICSR) .....               | 90        |

| 4.3.4    | ベクタ・テーブル・オフセット・レジスタ .....                    | 92        |

| 4.3.5    | アプリケーション割込みおよびリセット制御レジスタ .....               | 93        |

| 4.3.6    | システム制御ブロック .....                             | 94        |

| 4.3.7    | 設定および制御レジスタ .....                            | 95        |

| 4.3.8    | システム・ハンドラ優先度レジスタ .....                       | 95        |

| 4.3.9    | SCB 使用のヒントとコツ .....                          | 96        |

| 4.4      | SysTick タイマ (STK) .....                      | 97        |

| 4.4.1    | SysTick 制御およびステータス・レジスタ (STK_CSR) .....      | 97        |

---

|       |                                   |     |

|-------|-----------------------------------|-----|

| 4.4.2 | SysTick 再ロード値レジスタ (STK_RVR) ..... | 98  |

| 4.4.3 | SysTick 現在値レジスタ (STK_CVR) .....   | 98  |

| 4.4.4 | SysTick 較正值レジスタ (STK_CALIB) ..... | 99  |

| 4.4.5 | SysTick 使用のヒントとコツ .....           | 99  |

| 4.5   | メモリ保護ユニット .....                   | 100 |

| 4.5.1 | MPU タイプ・レジスタ .....                | 102 |

| 4.5.2 | MPU 制御レジスタ .....                  | 103 |

| 4.5.3 | MPU 領域番号レジスタ .....                | 104 |

| 4.5.4 | MPU 領域ベース・アドレス・レジスタ .....         | 105 |

| 4.5.5 | MPU 領域属性およびサイズ・レジスタ .....         | 106 |

| 4.5.6 | MPU アクセス許可属性 .....                | 107 |

| 4.5.7 | MPU の不一致 .....                    | 108 |

| 4.5.8 | MPU 領域の更新 .....                   | 108 |

| 4.5.9 | MPU 設計のヒントとコツ .....               | 109 |

| 4.6   | I/O ポート .....                     | 110 |

| 5     | 改版履歴 .....                        | 111 |

## 表の一覧

|       |                                             |     |

|-------|---------------------------------------------|-----|

| 表 1.  | プロセッサ・モード、実行特権レベル、使用するスタックのオプションの概要.....    | 14  |

| 表 2.  | コア・レジスタ・セットの概要 .....                        | 14  |

| 表 3.  | PSR レジスタの組合せ .....                          | 16  |

| 表 4.  | APSR ビット割当て .....                           | 16  |

| 表 5.  | IPSR のビット割当て .....                          | 17  |

| 表 6.  | EPSR のビット割当て.....                           | 17  |

| 表 7.  | PRIMASK レジスタのビット割当て .....                   | 18  |

| 表 8.  | 制御レジスタのビット割当て .....                         | 19  |

| 表 9.  | メモリ・アクセスの順序 (1) .....                       | 23  |

| 表 10. | メモリ・アクセスの動作.....                            | 23  |

| 表 11. | メモリ領域の共有可能性とキャッシュ・ポリシー .....                | 24  |

| 表 12. | さまざまな例外タイプのプロパティ .....                      | 28  |

| 表 13. | 例外からの復帰動作 .....                             | 33  |

| 表 14. | Cortex-M0+ 命令.....                          | 37  |

| 表 15. | 一部の Cortex-M0+ 命令を生成するための CMSIS 組込み関数 ..... | 40  |

| 表 16. | 特殊レジスタにアクセスするための CMSIS 組込み関数 .....          | 40  |

| 表 17. | 条件コードのサフィックス .....                          | 45  |

| 表 18. | メモリ・アクセス命令.....                             | 46  |

| 表 19. | データ処理命令 .....                               | 54  |

| 表 20. | ADC、ADD、RSB、SBC および SUB オペランドの制限事項.....     | 56  |

| 表 21. | 分岐命令と制御命令 .....                             | 66  |

| 表 22. | 分岐範囲 .....                                  | 67  |

| 表 23. | その他の命令 .....                                | 69  |

| 表 24. | コア・ペリフェラルのレジスタ領域 .....                      | 82  |

| 表 25. | NVIC レジスタの概要 .....                          | 83  |

| 表 26. | CMSIS の NVIC アクセス関数.....                    | 83  |

| 表 27. | NVIC_IPRx ビット割当て .....                      | 87  |

| 表 28. | CMSIS NVIC 制御関数 .....                       | 88  |

| 表 29. | SCB レジスタの概要 .....                           | 89  |

| 表 30. | ICSR ビット割当て .....                           | 91  |

| 表 31. | システム・フォールト・ハンドラ優先度フィールド .....               | 95  |

| 表 32. | システム・タイマのレジスタの概要 .....                      | 97  |

| 表 33. | メモリ属性の概要 .....                              | 100 |

| 表 34. | MPU レジスタの概要 .....                           | 101 |

| 表 35. | SIZE フィールドの値の例 .....                        | 107 |

| 表 36. | C、B、S のエンコード .....                          | 107 |

| 表 37. | AP エンコード .....                              | 107 |

| 表 38. | マイクロコントローラのメモリ領域属性 .....                    | 109 |

| 表 39. | 文書改版履歴 .....                                | 111 |

| 表 40. | 日本語版文書改版履歴 .....                            | 111 |

## 図の一覧

|       |                                 |     |

|-------|---------------------------------|-----|

| 図 1.  | Cortex-M0+ の実装 .....            | 10  |

| 図 2.  | プロセッサのコア・レジスタ .....             | 14  |

| 図 3.  | APSR、IPSR、およびEPSR のビット割当て ..... | 16  |

| 図 4.  | 制御ビット割当て .....                  | 19  |

| 図 5.  | メモリマップ .....                    | 21  |

| 図 6.  | リトルエンディアン形式の例 .....             | 26  |

| 図 7.  | ベクタ・テーブル .....                  | 30  |

| 図 8.  | スタック・フレーム .....                 | 32  |

| 図 9.  | ASR#3 .....                     | 42  |

| 図 10. | LSR#3 .....                     | 42  |

| 図 11. | LSL #3 .....                    | 43  |

| 図 12. | ROR #3 .....                    | 43  |

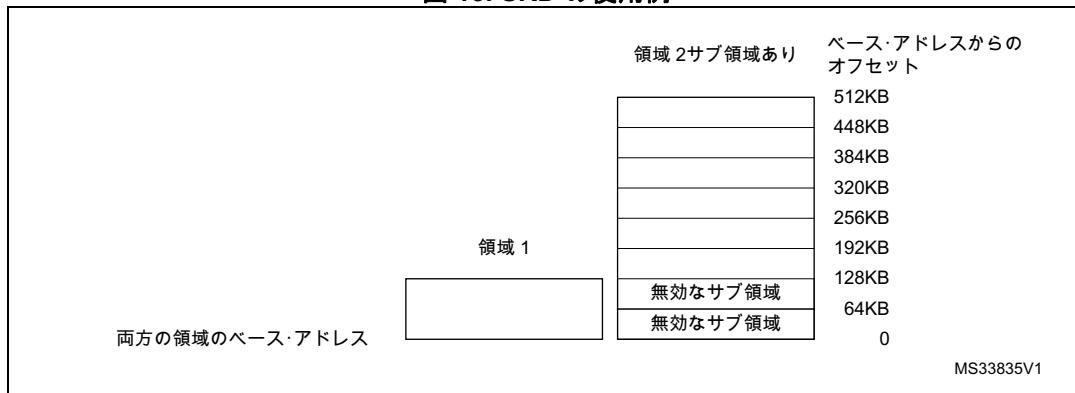

| 図 13. | SRD の使用例 .....                  | 109 |

# 1 本書について

本書には、アプリケーションおよびシステムレベルのソフトウェアの開発に必要な情報が記載されています。デバッグに関連するコンポーネント、機能、動作についての情報は含まれません。

マイクロコントローラのソフトウェアおよびハードウェアを扱うエンジニアを対象にした資料であり、Arm<sup>®(a)</sup> 製品に対する経験の有無は問いません。

## 1.1 表記規則

本書の表記規則は次のとおりです。

*italic* 重要な注意事項を強調し、特別な用語を紹介し、内部の相互参照と引用を示します。

**bold** メニュー名などのユーザ・インターフェース要素の強調に太字を使用します。信号名も太字で示します。適宜、記述リスト内の用語にも使用します。

`monospace` コマンド、ファイル名、プログラム名、ソース・コードなどキーボードから入力可能なテキストを表します。

`monospace italic` コマンドやオプションで使用可能な略語を表します。コマンド名またはオプション名をすべて入力する代わりに、下線部分の文字だけを入力することができます。

`monospace bold italic` 特定の値に置き換えられる引数は等幅フォントのテキストで表されます。

`monospace bold` サンプル・コード以外で使用される言語キーワードを示します。

`<および>` コードまたはコード・フラグメント内でアセンブラー構文の置き換えが可能な用語を囲みます。例：

LDRSB<cond> <Rt>, [<Rn>, #<offset>]

a. Arm は、米国内およびその他の地域にある Arm Limited 社（またはその子会社）の登録商標です。

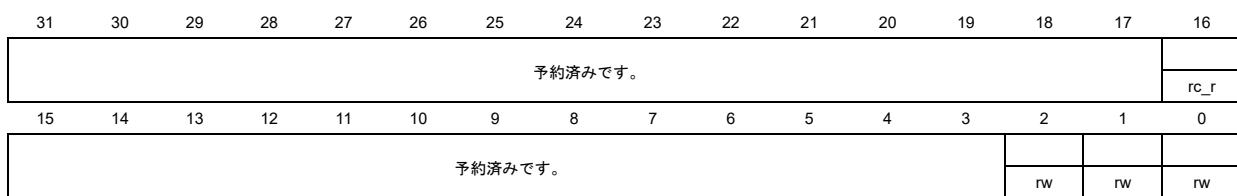

## 1.2 レジスタに関する略記

レジスタの説明では、次の略記が使用されます。

読み出し／書き込み (rw) これらのビットは、ソフトウェアによる読み出しと書き込みができます。

読み出し専用 (r) これらのビットは、ソフトウェアによる読み出しがみが可能です。

書き込み専用 (w) このビットは、ソフトウェアによる書き込みのみが可能です。

ビットを読み出すと、リセット値が返されます。

読み出し／クリア (rc\_w) このビットは、ソフトウェアによって読み出すことができ、任意の値を書き込むことによってクリアできます。

読み出し／クリア (rc\_w1) このビットは、ソフトウェアによって読み出すことができ、“1”を書き込むことによってクリアできます。

“0”を書き込んでも、ビットの値は変化しません。

読み出し／クリア (rc\_w0) このビットは、ソフトウェアによって読み出すことができ、“0”を書き込むことによってクリアできます。

“1”を書き込んでも、ビットの値は変化しません。

反転 (t) このビットは、ソフトウェアによって“1”を書き込むことで反転だけできます。“0”を書き込んでも、ビットの値は変化しません。

予約済み (Res.) 予約済みビットであり、リセット値に保持する必要があります。

## 1.3 Cortex-M0+ プロセッサおよびコア・ペリフェラルについて

Cortex-M0+ プロセッサは、幅広い組込みアプリケーション向けに設計されたエントリレベルの 32 ビット Arm® Cortex プロセッサです。開発者に次のような大きなメリットを提供します。

- 学習とプログラムが容易なシンプルなアーキテクチャ

- 超低電力、エネルギー効率に優れた動作

- 卓越したコード密度

- 高性能な決定性の割込み処理

- Cortex-M プロセッサ・ファミリとの上位互換

- プラットフォームに対する、オプションの内蔵メモリ保護ユニット (MPU) による堅牢なセキュリティ

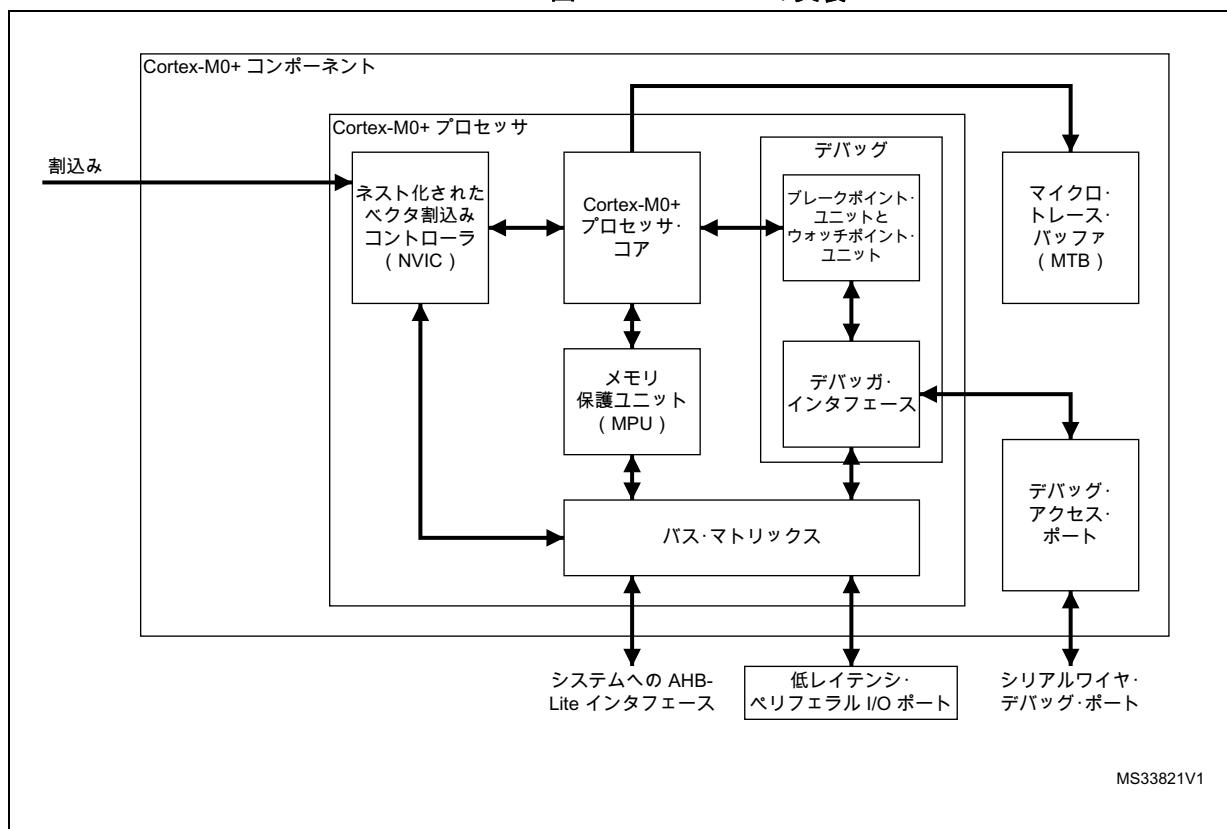

図 1. Cortex-M0+ の実装

Cortex-M0+ プロセッサは、ファン・ノイマン型 2 段パイプライン・アーキテクチャを採用し、面積と電力を高度に最適化した 32 ビット・プロセッサ・コア上に構築されています。コンパクトで強力な命令セットと徹底的に最適化された設計によって並外れたエネルギー効率を実現し、シングルサイクル乗算器など、ハイエンドの処理ハードウェアを搭載しています。

Cortex-M0+ プロセッサは、16 ビット Thumb® 命令セットをベースにし、Thumb-2 テクノロジを採用した ARMv6-M アーキテクチャを実装しています。これにより、他の 8 ビットおよび 16 ビット・マイクロコントローラより高いコード密度を保ちつつ、最新の 32 ビット・アーキテクチャならではの並外れた性能を発揮します。

Cortex-M0+ プロセッサは、設定可能なネスト化されたベクタ割込みコントローラ (NVIC) を綿密に統合して業界トップクラスの割込み性能を提供します。NVIC の特徴は次のとおりです。

- ・ ノンマスカブル割込み (NMI) 機能。

- ・ ゼロジッタ割込みオプション。

- ・ 4 段階の割込み優先度レベル。

プロセッサ・コアと NVIC を密接に統合することで、割込みサービス・ルーチン (ISR) の実行を高速化し、割込みレイテンシを大幅に短縮しています。これを実現するのが、レジスタのハードウェア・スタッキングと、多重ロードおよび多重ストア動作を中止および再開する機能です。割込みハンドラはアセンブラー・ラッパー・コードを一切必要としないため、ISR のあらゆるコード・オーバーヘッドが取り除かれます。テールチェイン最適化も、ISR の切替え時のオーバーヘッドを著しく短縮します。

NVIC は低電力設計の最適化のために、スリープ・モードを搭載していますが、これにはデバイス全体の迅速なパワーダウンを可能にするディープ・スリープ機能も含まれます。

### 1.3.1 システムレベル・インターフェース

Cortex-M0+ プロセッサは、高速、低レイテンシのメモリ・アクセスを実現するため、AMBA® テクノロジによるシングル・システムレベルのインターフェースを備えています。

Cortex-M0+ プロセッサは、きめ細かくメモリを制御するオプションのメモリ保護ユニット (MPU) を備えているため、アプリケーションは複数の特権レベルを使用し、コード、データ、スタックをタスクごとに分離および保護できます。これらの機能を備えることは、車載システム用途など多くの組込み用途に不可欠な要件になっています。

### 1.3.2 設定可能な統合デバッグ機能

Cortex-M0+ プロセッサは、ハードウェアのブレークポイントとウォッチポイントのオプションを拡大した、完全なハードウェア・デバッグ・ソリューションを実装します。これにより、マイクロコントローラや他の小型パッケージ・デバイスに最適な <2 ピンのシリアル・ワイヤ・デバッグ (SWD) ポート> を介して、プロセッサ、メモリ、およびペリフェラルに対するシステム可視性が高まります。

### 1.3.3 Cortex-M0+ プロセッサの特徴の概要

- ・ Thumb-2 テクノロジを使用した Thumb 命令セット

- ・ 32 ビット性能による高いコード密度

- ・ ユーザ・モードと特権モードの実行

- ・ ツールとバイナリの Cortex-M プロセッサ・ファミリとの上位互換

- ・ 超低電力 SLEEP モードの搭載

- ・ 効率的なコード実行によりプロセッサ・クロックの低速化と SLEEP 期間の増加が可能

- ・ シングルサイクル 32 ビット・ハードウェア乗算器

- ・ ゼロジッタ割込み処理

- ・ セキュリティ重視のアプリケーション向けのメモリ保護ユニット (MPU)

- ・ 低レイテンシで、高速なペリフェラル I/O ポート

- ・ ベクタ・テーブル・オフセット・レジスタ

- ・ 幅広いデバッグ機能

### 1.3.4 Cortex-M0+ のコア・ペリフェラル

コア・ペリフェラルは、以下のとおりです。

#### ネスト化されたベクタ割込みコントローラ (NVIC)

NVIC は、低レイテンシの割込み処理をサポートする内蔵割込みコントローラです。

#### システム制御ブロック

システム制御ブロック (SCB) は、プログラマ向けに用意されたプロセッサへのモデル・インターフェースです。システムの実装情報と、システム例外の設定、制御、報告などのシステム制御機能を提供します。

#### システム・タイマ

システム・タイマの SysTick は、24bit のカウントダウン・タイマです。リアルタイム OS (RTOS) のティック・タイマまたは単純なカウンタとして使用します。

#### メモリ保護ユニット

メモリ保護ユニット (MPU) は、各種メモリ領域に対してメモリ属性を定義することでシステムの信頼性を向上させます。最大 8 つの異なる領域と、必要に応じて事前定義が可能なバックグラウンド領域が提供されます。

#### I/O ポート

I/O ポートは、緊密に結合されたペリフェラルに対して、シングルサイクルのロードとストアを提供します。

## 2 Cortex-M0+ プロセッサ

### 2.1 プログラマ・モデル

このセクションでは、Cortex-M0+ のプログラマ・モデルについて説明します。個々のコア・レジスタの説明に加えて、ソフトウェアの実行、およびスタックに対するプロセッサのモードや、特権レベルの情報も提示します。

#### 2.1.1 ソフトウェアの実行に対するプロセッサのモードと特権レベル

このプロセッサには、以下のモードがあります。

スレッド・モード アプリケーション・ソフトウェアを実行します。プロセッサはリセット状態が解除されるとスレッド・モードに移行します。

ハンドラ・モード 例外を処理します。すべての例外処理が終了すると、プロセッサはスレッド・モードに戻ります。

ソフトウェア実行には、次の特権レベルがあります。

非特権 ソフトウェアには以下の制限があります。

- MSR および MRS 命令を使用したシステム・レジスタへのアクセスが制限され、CPS 命令を使用した割込みのマスクはできません。

- システム・タイマ、NVIC、システム制御ブロックにはアクセスできません。

- メモリやペリフェラルへのアクセスが制限される場合があります。

非特権ソフトウェアは非特権レベルで実行されます。

特権 ソフトウェアは、すべての命令を使用できるとともにすべてのリソースへのアクセスが可能です。

特権ソフトウェアは特権レベルで実行されます。

スレッド・モードの場合、ソフトウェア実行に対する特権の有無は CONTROL レジスタによって制御します（[18 ページの CONTROL レジスタを参照](#)）。ハンドラ・モードの場合、ソフトウェア実行には常に特権が与えられます。

スレッド・モードでは、特権ソフトウェアのみが、ソフトウェア実行に対する特権レベルを変更するため、CONTROL レジスタへの書き込みが可能です。非特権ソフトウェアは、特権ソフトウェアに制御を移すためのスーパーバイザ・コールを実行するために、SVC 命令を使用できます。

#### 2.1.2 スタック

このプロセッサは完全降順スタックを使用します。これは、スタック・ポインタがスタック・メモリに最後にスタックされた項目を指すことを意味します。プロセッサがスタックに新しい項目をプッシュすると、スタック・ポインタがデクリメントされ、その項目が新しいメモリ位置に書き込まれます。プロセッサには、メイン・スタックとプロセス・スタックの 2 つのスタックが搭載され、それぞれ独立したスタック・ポインタのコピーを持ちます（[15 ページのスタック・ポインタを参照](#)）。

スレッド・モードの場合、プロセッサがメイン・スタックとプロセス・スタックのどちらを使用するかは、CONTROL レジスタによって制御されます（[18 ページの CONTROL レジスタを参照](#)）。ハンドラ・モードでは、プロセッサは常にメイン・スタックを使用します。プロセッサ動作には、次のような選択肢があります。

表 1. プロセッサ・モード、実行特権レベル、使用するスタックのオプションの概要

| プロセッサ・モード | 実行対象     | ソフトウェア実行の特権レベル          | 使用するスタック                            |

|-----------|----------|-------------------------|-------------------------------------|

| スレッド      | アプリケーション | 特権または非特権 <sup>(1)</sup> | メイン・スタックまたはプロセス・スタック <sup>(1)</sup> |

| ハンドラ      | 例外ハンドラ   | 常に特権                    | メイン・スタック                            |

1. 18 ページのCONTROL レジスタを参照

### 2.1.3 コア・レジスタ

プロセッサのコア・レジスタを次に説明します。

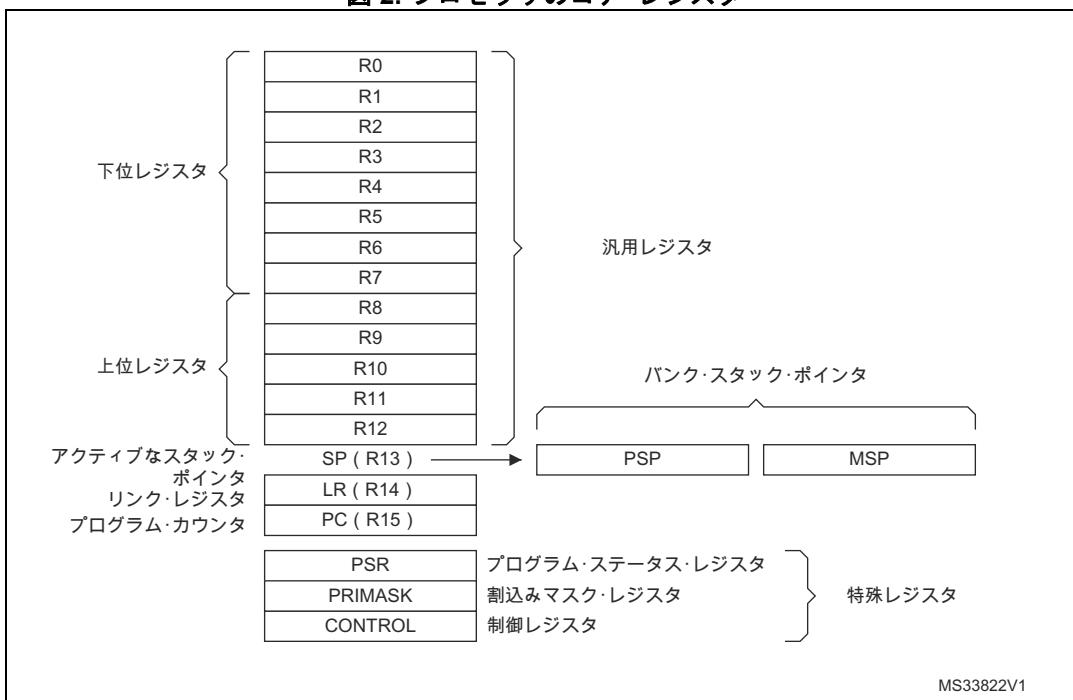

図 2. プロセッサのコア・レジスタ

表 2. コア・レジスタ・セットの概要

| 名前     | タイプ <sup>(1)</sup> | リセット値             | 説明                         |

|--------|--------------------|-------------------|----------------------------|

| R0-R12 | RW                 | 不明                | 15 ページの汎用レジスタを参照してください。    |

| MSP    | RW                 | 説明を参照             | 15 ページのスタック・ポインタを参照してください。 |

| PSP    | RW                 | 不明                | 15 ページのスタック・ポインタ           |

| LR     | RW                 | 不明                | 15 ページのリンク・レジスタ            |

| PC     | RW                 | 説明を参照             | 15 ページのプログラム・カウンタ          |

| PSR    | RW                 | 不明 <sup>(2)</sup> | 15 ページのプログラム・ステータス・レジスタ    |

表 2. コア・レジスタ・セットの概要（続き）

|         |    |            |                                  |

|---------|----|------------|----------------------------------|

| APSR    | RW | 不明         | 16 ページのアプリケーション・プログラム・ステータス・レジスタ |

| IPSR    | RO | 0x00000000 | 17 ページの割込みプログラム・ステータス・レジスタ       |

| EPSR    | RO | 不明         | 17 ページの例外プログラム・ステータス・レジスタ        |

| PRIMASK | RW | 0x00000000 | 18 ページの優先度マスク・レジスタ               |

| CONTROL | RW | 0x00000000 | 18 ページのCONTROL レジスタ              |

1. スレッド・モードとハンドラ・モードでのプログラム実行時のアクセス・タイプを示しています。デバッグ時のアクセス・タイプは異なる場合があります。

2. ビット [24] は T ビットであり、リセット・ベクタのビット [0] からロードされます。

## 汎用レジスタ

R0 ~ R12 は、データ操作のための 32 ビット汎用レジスタです。

## スタック・ポインタ

スタック・ポインタ (SP) はレジスタ R13 です。スレッド・モードでは、CONTROL レジスタのビット [1] によって、以下のどちらのスタック・ポインタを使用するかを示します。

- 0 = メイン・スタック・ポインタ (MSP)。これがリセット値です。

- 1 = プロセス・スタック・ポインタ (PSP)。

リセット時、プロセッサは MSP にアドレス 0x00000000 の値をロードします。

## リンク・レジスタ

リンク・レジスタ (LR) はレジスタ R14 です。サブルーチン、関数呼出し、および例外の復帰情報を格納します。リセットしたときの LR の値は不定です。

## プログラム・カウンタ

プログラム・カウンタ (PC) はレジスタ R15 です。現在のプログラム・アドレスを格納します。リセット時、プロセッサは PC にリセット・ベクタ（アドレス 0x00000004）の値をロードします。この値のビット [0] は、リセット時に EPSR の T ビットにロードされ、1 である必要があります。

## プログラム・ステータス・レジスタ

プログラム・ステータス・レジスタ (PSR) は、以下のレジスタを組み合わせたものです。

- アプリケーション・プログラム・ステータス・レジスタ (APSR)。

- 割込みプログラム・ステータス・レジスタ (IPSR)。

- 実行プログラム・ステータス・レジスタ (EPSR)。

これらのレジスタは、32 ビット PSR 内の互いに重ならないビットフィールドとして割り当てられます。PSR ビット割当てを次に示します。

図 3. APSR、IPSR、およびEPSR のビット割当て

|      |         |    |    |    |    |    |    |    |         |  |  |  |         |      |  |   |

|------|---------|----|----|----|----|----|----|----|---------|--|--|--|---------|------|--|---|

|      | 31      | 30 | 29 | 28 | 27 | 25 | 24 | 23 |         |  |  |  | 6       | 5    |  | 0 |

| APSR | N       | Z  | C  | V  |    |    |    |    |         |  |  |  | 予約済みです。 |      |  |   |

| IPSR |         |    |    |    |    |    |    |    | 予約済みです。 |  |  |  |         | 例外番号 |  |   |

| EPSR | 予約済みです。 |    | T  |    |    |    |    |    | 予約済みです。 |  |  |  |         |      |  |   |

これらのレジスタに個別に、あるいは任意に組み合わせてアクセスするには、MSR または MRS 命令の引数としてこれらのレジスタ名を指定します。例：

- MRS 命令で PSR を使用して、3つすべてのレジスタを読み出します。

- MSR 命令で APSR を使用して、APSR に書き込みます。

PSR の組合せと属性は次のとおりです。

表 3. PSR レジスタの組合せ

| 表 3.1 CR レジスターの組合せ |                       |                     |

|--------------------|-----------------------|---------------------|

| レジスタ               | タイプ                   | 組合せ                 |

| PSR                | RW <sup>(1)、(2)</sup> | APSR、EPSR、および IPSR。 |

| IEPSR              | RO                    | EPSR および IPSR。      |

| IAPSR              | RW <sup>(1)</sup>     | APSR および IPSR。      |

| EAPSR              | RW <sup>(2)</sup>     | APSR および EPSR。      |

1. プロセッサは IPSR のビットへの書き込みを無視します。

2. EPSR のビットを読み出すとゼロが返され、プロセッサはこれらのビットへの書き込みを無視します。

プログラム・ステータス・レジスタへのアクセス方法の詳細については、[75 ページのMRS](#)および[76 ページのMSR](#)の命令の説明を参照してください。

アプリケーション・プログラム・ステータス・レジスター

APSR には、前回の命令実行によって設定された現在の条件フラグの状態が格納されます。属性については、[14 ページの表 2](#)のレジスタ概要を参照してください。ビット割当てを次に示します。

表 4. APSR ビット割当て

表 4. AFGR ビット割当て

| ビット    | 名前 | 説明              |

|--------|----|-----------------|

| [31]   | N  | ネガティブ・フラグ。      |

| [30]   | Z  | ゼロ・フラグ。         |

| [29]   | C  | キャリーまたはボロー・フラグ。 |

| [28]   | V  | オーバーフロー・フラグ。    |

| [27:0] | -  | 予約済み。           |

APSR のネガティブ、ゼロ、キャリーまたはボロー、およびオーバーフローの各フラグについての詳細は、[44 ページの条件フラグ](#)を参照してください。

### 割込みプログラム・ステータス・レジスタ

IPSR には、現在の割込みサービス・ルーチン (ISR) の例外の番号が格納されます。属性については、[14 ページの表 2](#)のレジスタ概要を参照してください。ビット割当てを次に示します。

**表 5. IPSR のビット割当て**

| ビット    | 名前   | 機能                                                                                                                                                                                                                                                               |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:6] | -    | 予約済みです。                                                                                                                                                                                                                                                          |

| [5:0]  | 例外番号 | これは現在の例外の番号です。<br>0 = スレッド・モード<br>1 = 予約済み<br>2 = NMI<br>3 = HardFault<br>4-10 = 予約済み<br>11 = SVCall<br>12、13 = 予約済み<br>14 = PendSV<br>15 = SysTick   予約済み<br>16 = IRQ0<br>.<br>.<br>47 = IRQ31<br>48-63 = 予約済み<br>詳細は、 <a href="#">27 ページの例外のタイプ</a> を参照してください。 |

### 例外プログラム・ステータス・レジスタ

EPSR は、Thumb 状態ビットを格納します。

EPSR の属性については、[14 ページの表 2](#)のレジスタの概要を参照してください。ビット割当てを次に示します。

**表 6. EPSR のビット割当て**

| ビット     | 名前 | 機能          |

|---------|----|-------------|

| [31:25] | -  | 予約済み。       |

| [24]    | T  | Thumb 状態ビット |

| [23:0]  | -  | 予約済み。       |

アプリケーション・ソフトウェアから MRS 命令を使用して EPSR を直接読み出そうとすると、常にゼロが返されます。MRS 命令による EPSR への書き込み動作は無視されます。フォールト・ハンドラは、スタックされた PSR 内の EPSR の値を調べることで、フォールトの原因を特定することができます。

[31 ページの例外の開始と復帰](#)を参照してください。以下によって T ビットを 0 にクリアできます。

- BLX、BX、および POP{PC} 命令。

- 例外から復帰したときのスタックされた xPSR 値からの復元。

- 例外の開始時のベクタ値のビット [0]。

T ビットが 0 の状態で命令を実行すると HardFault またはロックアップが発生します。詳細については、[34 ページの2.4.1：ロックアップ](#)を参照してください。

### 中断可能で中断後からリスタート可能な命令

中断可能で中断後からリスタート可能な命令は、LDM と STM、PUSH、POP、および MULS です。これらの命令のいずれかの実行中に割込みが発生した場合、プロセッサは命令の実行を中止します。割込み処理の後、プロセッサは命令の実行を最初からリスタートします。

### 例外マスク・レジスタ

例外マスク・レジスタは、プロセッサによる例外処理を無効にします。タイミング重視のタスクまたはアトミック性を必要とするコード・シーケンスに影響を与える可能性がある例外を無効にします。

例外を有効にする、または再度有効にするには、MSR および MRS 命令を使用するか、CPS 命令を使用して、PRIMASK の値を変更します。詳細については、[75 ページの3.7.6 : MRS](#)、[76 ページの3.7.7 : MSR](#)、および[71 ページの3.7.2 : CPS](#)を参照してください。

### 優先度マスク・レジスタ

PRIMASK レジスタは、設定可能な優先度を持つすべての例外のアクティブ化を禁止します。属性については、[14 ページの表 2](#)のレジスタ概要を参照してください。ビット割当てを次に示します。

表 7. PRIMASK レジスタのビット割当て

| ビット    | 名前 | 機能                                                                     |

|--------|----|------------------------------------------------------------------------|

| [31:1] | -  | 予約済み。                                                                  |

| [0]    | PM | 優先順位の設定が可能な割込みマスク：<br>0 = 影響なし。<br>1 = 設定可能な優先度を持つすべての例外のアクティブ化を禁止します。 |

### CONTROL レジスタ

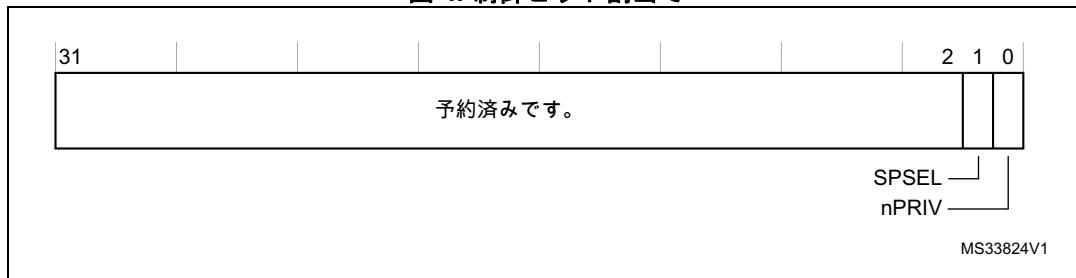

CONTROL レジスタは、使用されるスタック、およびプロセッサがスレッド・モードにある場合のソフトウェア実行の特権レベルを管理します。属性については、[14 ページの表 2](#)のレジスタ概要を参照してください。ビット割当てを次に示します。

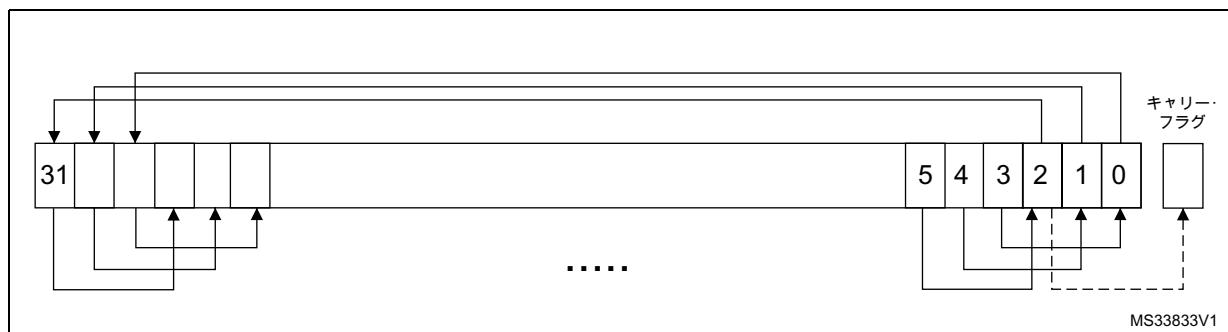

図 4. 制御ビット割当て

表 8. 制御レジスタのビット割当て

| ビット    | 名前    | 機能                                                                                                                |

|--------|-------|-------------------------------------------------------------------------------------------------------------------|

| [31:2] | -     | 予約済み。                                                                                                             |

| [1]    | SPSEL | 現在のスタックを定義します。<br>0 = MSP が現在のスタック・ポインタです。<br>1 = PSP が現在のスタック・ポインタです。<br>ハンドラ・モードでは、このビットはゼロとして読み出され、書き込みは無視します。 |

| [0]    | nPRIV | スレッド・モードの特権レベルを定義します。<br>0 = 特権<br>1 = 非特権                                                                        |

ハンドラ・モードでは常に MSP が使用されます。このため、ハンドラ・モードで動作中のプロセッサは、CONTROL レジスタのアクティブなスタック・ポインタ・ビットへの明示的な書き込みを無視します。CONTROL レジスタは、例外の開始または例外からの復帰のメカニズムによって自動的に更新されます。

OS 環境では、スレッド・モードで動作するスレッドはプロセス・スタックを使用し、カーネルおよび例外ハンドラはメイン・スタックを使用することを推奨します。

スレッド・モードではデフォルトで MSP が使用されます。スレッド・モードで使用していたスタック・ポインタを PSP に切り替えるには、MSR 命令を使用して、アクティブなスタック・ポインタ・ビットを 1 にセットします（[75ページの3.7.6 : MSRを参照](#)）。

**注：**スタック・ポインタを変更する場合、ソフトウェアは MSR 命令の直後に ISB 命令を使用する必要があります。これによって、ISB の後の命令が確実に新しいスタック・ポインタを使用して実行できます。[74ページの3.7.5 : ISBを参照](#)してください。

## 2.1.4 例外と割込み

Cortex-M0+ プロセッサは、割込みとシステム例外をサポートしています。プロセッサとネスト化されたベクタ割込みコントローラ (NVIC) がすべての例外の優先度を決定し、処理します。割込みまたは例外は、ソフトウェア制御の通常のフローを変化させます。プロセッサは、リセットを除くすべての例外の処理にハンドラ・モードを使用します。詳細は、[32 ページの例外の開始](#)および[33 ページの例外からの復帰](#)を参照してください。

NVIC レジスタは割込み処理を制御します。詳細については、[83ページの4.2 : ネスト化されたベクタ割込みコントローラ](#)を参照してください。

## 2.1.5 データ型

プロセッサは、以下のとおりです。

- 以下のデータ型をサポートします。

- 32 ビット・ワード

- 16 ビット・ハーフワード

- 8 ビット・バイト

- すべてのデータ・メモリ・アクセスを、リトルエンディアンまたはビッグエンディアンとして管理します。命令メモリとプライベート・ペリフェラル・バス (PPB) へのアクセスは、常にリトルエンディアンです。詳細については、[22ページの2.2.1：メモリの領域、タイプ、および属性](#) を参照してください。

## 2.1.6 Cortex マイクロコントローラ・ソフトウェア・インタフェース標準

Arm® では、Cortex-M0+ マイクロコントローラのプログラミング向けに、Cortex マイクロコントローラ・ソフトウェア・インタフェース標準 (CMSIS) を制定しています。CMSIS は、デバイス・ドライバ・ライブラリ内に統合されています。CMSIS では、Cortex-M0+ マイクロコントローラ・システムに対して、以下を定義しています。

- 以下を実行するための共通の方法

- ペリフェラル・レジスタへのアクセス

- 例外ベクタの定義

- 以下の名称

- コア・ペリフェラルのレジスタ

- コア例外ベクタ

- RTOS カーネル用のデバイスに依存しないインタフェース

CMSIS には、Cortex-M0+ プロセッサのコア・ペリフェラルのアドレス定義およびデータ構造が含まれます。また、TCP/IP スタックとフラッシュ・ファイル・システムからなるミドルウェア・コンポーネント向けの、オプションのインタフェースも含まれています。

CMSIS では、テンプレート・コードの再利用や、さまざまなミドルウェア・ベンダが提供する CMSIS 準拠のソフトウェア・コンポーネントの組合せを可能にすることで、ソフトウェア開発を簡素化しています。ソフトウェア・ベンダは CMSIS を拡張して、ペリフェラルの定義やそれらのペリフェラルのアクセス機能を含めることができます。

本書は、CMSIS によって定義されたレジスタ名を記載し、プロセッサ・コアおよびコア・ペリフェラルに対応する CMSIS 関数についても簡単に説明しています。

**注：**本書で使用するレジスタの短縮名は CMSIS によって定義されたものです。これらの短縮名は、他のドキュメントで使用されているアーキテクチャ上の短縮名と異なる場合があります。

以降のセクションでは、CMSIS の詳細について説明します。

- [36ページの2.5.4：電源管理に関するプログラミングのヒント](#)

- [40ページの3.2：組込み関数](#)

- [83ページの4.2.1：CMSIS を使用した Cortex-M0+ NVIC レジスタへのアクセス](#)

- [88 ページのNVIC のプログラミングのヒント](#)

## 2.2 メモリ・モデル

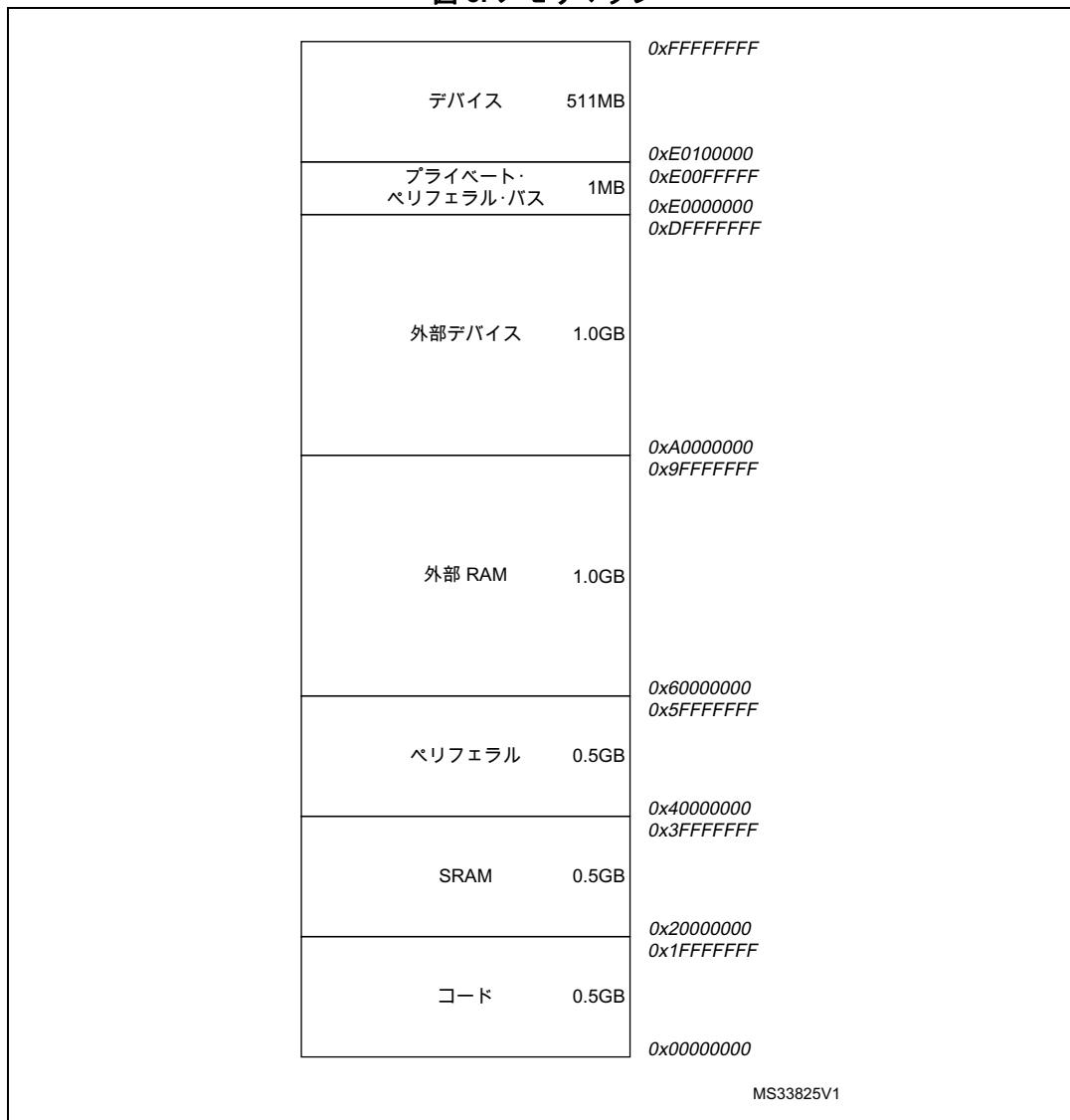

このセクションでは、プロセッサのメモリ・マップおよびメモリ・アクセスの動作について説明します。プロセッサには、最大 4GB のアドレス指定可能なメモリを提供する固定されたメモリ・マップがあります。メモリ・マップは、以下のとおりです。

図 5. メモリマップ

プロセッサでは、コア・ペリフェラルのレジスタ向けに、プライベート・ペリフェラル・バス (PPB) のアドレス範囲の領域を確保しています ([10ページの1.3 : Cortex-M0+ プロセッサおよびコア・ペリフェラルについて](#) を参照)。

## 2.2.1 メモリの領域、タイプ、および属性

メモリ・マップと MPU のプログラミングにより、複数の領域に分割されます。各領域にはメモリ・タイプが定義され、一部の領域ではその追加のメモリ属性も設定されています。メモリ・タイプとメモリ属性が、その領域へのアクセス動作を決定します。

メモリ・タイプに次のようなものがあります。

ノーマル プロセッサは、効率を高めるためトランザクションの順番を変えたり、投機的読出しを実行することができます。

デバイス プロセッサは、デバイス・メモリへの他のトランザクションや Strongly-ordered メモリへのトランザクションとの相対的なトランザクション順序を保持します。

Strongly-ordered プロセッサは、他のすべてのトランザクションとの相対的なトランザクション順序を保持します。

デバイス・メモリと Strongly-ordered メモリに対して順序付けの要件が異なるため、メモリ・システムはデバイス・メモリへの書き込みをバッファできますが、Strongly-ordered メモリへの書き込みはバッファできません。

追加のメモリ属性として、次のようなものがあります。

共有可能 共有可能なメモリ領域に対して、メモリ・システムは、複数のバス・マスタを持つシステム（たとえば、DMA コントローラを持つプロセッサ）内のバス・マスタ間のデータ同期を行います。

Strongly-ordered メモリは常に共有可能です。

複数のバス・マスタが共有不可能なメモリ領域にアクセスできる場合、ソフトウェアは、バス・マスタ間のデータの一貫性を確保する必要があります。

<この説明は、メモリが複数のプロセッサ間で共有されているシステムでデバイスが使用される可能性がある場合にのみ必要です。>

実行不可 (XN) プロセッサが命令へのアクセスを禁止することを意味します。メモリの XN 領域からフェッチされた命令を実行した場合、HardFault 例外が発生します。

## 2.2.2 メモリ・システムでのメモリ・アクセスの順序付け

明示的なメモリ・アクセス命令によって発生するほとんどのメモリ・アクセスについて、順序の変更が命令シーケンスの動作に影響を与えない限り、メモリ・システムは、アクセスが完了する順序がプログラムにおける命令の順序と一致することを保証しません。通常は、プログラムが正しく実行されるために、2つのメモリ・アクセスがプログラム順に完了することが必要な場合、ソフトウェアで、これらのメモリ・アクセス命令の間にメモリ・バリア命令を挿入する必要があります（[22ページの2.2.2：メモリ・システムでのメモリ・アクセスの順序付け](#)を参照）。

ただし、デバイス・メモリおよび Strongly-ordered メモリへのアクセスの順序付けの一部については、メモリ・システムによって保証されます。2つのメモリ・アクセス命令 A1 と A2 について、プログラム順では A1 が A2 より前に出現する場合、これら 2つの命令によって発生するメモリ・アクセスの順序は次のようになります。

表 9. メモリ・アクセスの順序<sup>(1)</sup>

| A1                    | A2 | ノーマル・アクセス | デバイス・アクセス |      | Strongly-ordered アクセス |

|-----------------------|----|-----------|-----------|------|-----------------------|

|                       |    |           | 共有不可      | 共有可能 |                       |

| ノーマル・アクセス             | -  | -         | -         | -    | -                     |

| デバイス・アクセス、共有不可        | -  | <         | -         | -    | <                     |

| デバイス・アクセス、共有可能        | -  | -         | <         | <    | <                     |

| Strongly-ordered アクセス | -  | <         | <         | <    | <                     |

MS33826V1

1. - メモリ・システムがアクセスの順序を保証していないことを意味します。

< アクセスがプログラム順に従うこと、つまり A1 は常に A2 より前に出現することを意味します。

## 2.2.3 メモリ・アクセスの動作

メモリ・マップの各領域へのアクセスは、次のように動作します。

表 10. メモリ・アクセスの動作<sup>(1)</sup>

| アドレス範囲                  | メモリ領域       | メモリ・タイプ           | XN | 説明                                                                 |

|-------------------------|-------------|-------------------|----|--------------------------------------------------------------------|

| 0x00000000 - 0x1FFFFFFF | コード         | ノーマル              | -  | プログラム・コードの実行可能領域。この領域にデータを配置することも可能です。                             |

| 0x20000000 - 0x3FFFFFFF | SRAM        | ノーマル              | -  | データの実行可能領域。この領域にコードを配置することも可能です。                                   |

| 0x40000000 - 0x5FFFFFFF | ペリフェラル      | デバイス              | XN | 外部デバイス・メモリ。                                                        |

| 0x60000000 - 0x9FFFFFFF | 外部 RAM      | ノーマル              | -  | データの実行可能領域。                                                        |

| 0xA0000000 - 0xDFFFFFFF | 外部デバイス      | デバイス              | XN | 外部デバイス・メモリ。                                                        |

| 0xE0000000 - 0xE00FFFFF | 専用ペリフェラル・バス | Strongly- ordered | XN | この領域には、NVIC、システム・タイマ、システム制御ブロックが含まれます。<br>この領域ではワード・アクセスのみを使用できます。 |

1. 詳細については、[22 ページのメモリの領域、タイプ、および属性](#)を参照してください。

コード、SRAM、外部 RAM の領域にプログラムを保持できます。

MPU は、このセクションに示したデフォルトのメモリ・アクセス動作を上書きできます。詳細については、[100ページの4.5：メモリ保護ユニット](#)を参照してください。

## 2.2.4 キャッシュと共有メモリに対する追加のメモリ・アクセス制約

システムにキャッシュまたは共有メモリが含まれている場合、表 11 に示すように、一部のメモリ領域には追加のアクセス制約があり、一部の領域は分割されています。

表 11. メモリ領域の共有可能性とキャッシュ・ポリシー

| アドレス範囲                  | メモリ領域       | メモリ・タイプ <sup>(1)</sup> | 共有可能性 <sup>(1)</sup> | キャッシュ・ポリシー <sup>(2)</sup> |

|-------------------------|-------------|------------------------|----------------------|---------------------------|

| 0x00000000 - 0x1FFFFFFF | コード         | ノーマル                   | -                    | WT                        |

| 0x20000000 - 0x3FFFFFFF | SRAM        | ノーマル                   | -                    | WBWA                      |

| 0x40000000 - 0x5FFFFFFF | ペリフェラル      | デバイス                   | -                    | -                         |

| 0x60000000 - 0x7FFFFFFF | 外部 RAM      | ノーマル                   | -                    | WBWA                      |

| 0x80000000 - 0x9FFFFFFF |             |                        |                      | WT                        |

| 0xA0000000 - 0xBFFFFFFF | 外部デバイス      | デバイス                   | 共有可能                 | -                         |

| 0xC0000000 - 0xDFFFFFFF |             |                        | 共有不可                 | -                         |

| 0xE0000000 - 0xE00FFFFF | 専用ペリフェラル・バス | Strongly- ordered      | 共有可能                 | -                         |

| 0xE0100000 - 0xFFFFFFF  | デバイス        | デバイス                   | -                    | -                         |

1. 詳細は、22ページの2.2.1：メモリの領域、タイプ、および属性を参照してください。

2. WT = ライトスルー、書き込み割当てなし WBWA = ライトバック、書き込み割当て

## 2.2.5 ソフトウェアによるメモリ・アクセスの順序付け

プログラム・フロー内の命令の順序は、対応するメモリ・トランザクションの順序を必ずしも保証するわけではありません。この原因は、以下のとおりです。

- プロセッサは、命令シーケンスの動作に影響を与えない限り、効率向上のために一部のメモリ・アクセスの順序を入れ換える場合がある。

- メモリ・マップ内のメモリまたはデバイスのウェイト・ステートが異なる場合がある。

- バッファされるメモリ・アクセスや投機的なメモリ・アクセスが存在する。

22 ページのメモリ・システムでのメモリ・アクセスの順序付けに、メモリ・システムがメモリ・アクセスの順序を保証する場合についての説明が記載されています。それらの場合に該当せず、メモリ・アクセスの順序が重要な場合は、ソフトウェアにメモリ・バリア命令を挿入して、強制的にアクセスを順序付ける必要があります。プロセッサでは、以下のメモリ・バリア命令を用意しています。

DMB

データ・メモリ・バリア (DMB) 命令は、未処理のメモリ・トランザクションが、後続のメモリ・トランザクションよりも前に完了することを保証します。72 ページのDMB を参照してください。

|                       |                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------|

| DSB                   | データ同期バリア (DSB) 命令は、未処理のメモリ・トランザクションが、後続の命令を実行する前に完了することを保証します。 <a href="#">73 ページのDSB</a> を参照してください。       |

| ISB                   | 命令同期バリア (ISB) 命令は、完了したすべてのメモリ・トランザクションの影響が、後続の命令によって認識可能であることを保証します。 <a href="#">74 ページのISB</a> を参照してください。 |

| メモリ・バリア命令の使用例を次に示します。 |                                                                                                            |

|                                                                 |                                                                                                                           |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| ベクタ・テーブル                                                        | プログラムでベクタ・テーブル内のエントリを変更してから対応する例外を有効にする場合は、これらの操作の間に DMB 命令を使用します。これにより、例外が有効になった直後にその例外が取得された場合、プロセッサは確実に新しい例外ベクタを使用します。 |

| 自己修正コード                                                         | プログラムに自己修正コードが含まれる場合、プログラムのコード修正直後に ISB 命令を使用します。これにより、後続の命令が必ず更新されたプログラムを使って実行されるようになります。                                |

| メモリ・マップの切替え                                                     | システムがメモリ・マップの切替えメカニズムを備えている場合、メモリ・マップの切替え後に DSB 命令を使用します。これにより、後続の命令が必ず更新されたメモリ・マップを使って実行されるようになります。                      |

| MPU プログラミング                                                     | ISB 命令または例外からの復帰の前に DSB を使用して、後続の命令が新しい MPU 設定を使用するようにする必要があります。                                                          |

| VTOR プログラミング                                                    | プログラムが VTOR の値を更新する場合は、DMB 命令を使用して、新しいベクタ・テーブルが後続の例外に使用されるようにします。                                                         |

| システム制御ブロックなどの Strongly-ordered メモリへのアクセスでは、DMB 命令を使用する必要はありません。 |                                                                                                                           |

## 2.2.6 メモリのエンディアン形式

プロセッサは、メモリを 0 から昇順に番号が付けられたバイトの線形配列としてとらえます。たとえば、バイト 0 ~ 3 は最初にストアされるワードを、バイト 4 ~ 7 は 2 番目にストアされるワードを保持します。[リトルエンディアン形式](#)は、データのワードがどのようにメモリに格納されるかを示したものです。

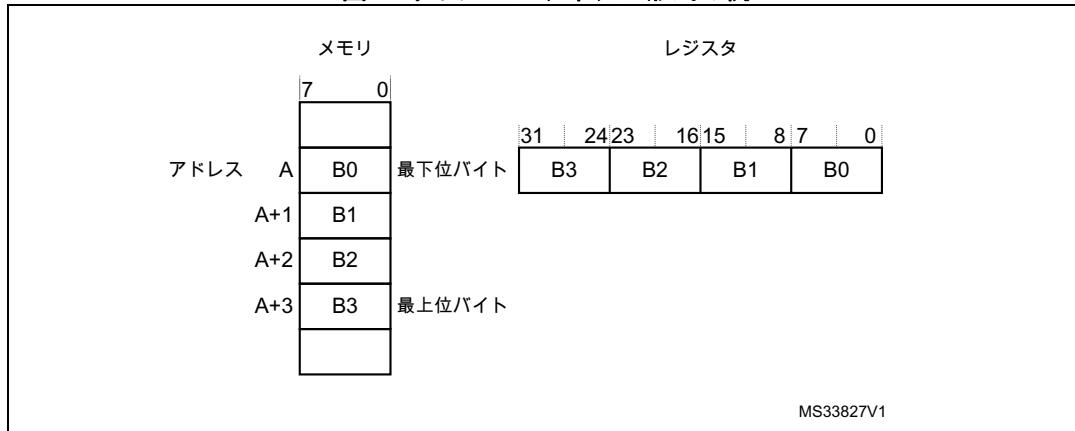

### リトルエンディアン形式

リトルエンディアン形式では、プロセッサは、ワードの最下位バイト (lsbyte) を一番小さい番号のバイトにストアし、最上位バイト (msbyte) を一番大きい番号のバイトにストアします。例：

図 6. リトルエンディアン形式の例

## 2.3 例外モデル

このセクションでは、例外モデルについて説明します。

### 2.3.1 例外状態

各例外は、次のいずれかの状態です。

|            |                                                             |

|------------|-------------------------------------------------------------|

| 非アクティブ     | 例外はアクティブでも保留中でもありません。                                       |

| 保留中        | 例外はプロセッサによる処理の待機中です。                                        |

|            | ペリフェラルまたはソフトウェアからの割込み要求により、対応する割込みの状態が保留中に変化することがあります。      |

| アクティブ      | 例外はプロセッサにより処理中で、完了していません。                                   |

|            | 注： 例外ハンドラは、他の例外ハンドラの実行に割り込むことができます。この場合、両方の例外がアクティブ状態になります。 |

| アクティブかつ保留中 | 例外はプロセッサにより処理中であり、さらに同じソースの別の例外が保留中です。                      |

### 2.3.2 例外のタイプ

例外のタイプを次に示します。

|           |                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| リセット      | リセットは、パワーアップまたはウォーム・リセットによって起動されます。例外モデルでは、リセットは特殊な形式の例外として扱われます。リセットがアサートされると、命令のどの時点においても、プロセッサの動作が停止します。リセットがネゲートされると、ベクタ・テーブルのリセット・エントリにより提供されるアドレスから実行が再開されます。実行は、スレッド・モードで特権実行として再開されます。                                                |

| NMI       | ノンマスクブル割込み (NMI) は、ペリフェラルからの信号またはソフトウェアからのトリガによって発生します。これは、リセット以外では、優先度が最も高い例外です。常に有効であり、優先度は -2 に固定されています。NMI は、 <ul style="list-style-type: none"><li>他の例外によって、マスクされたり、アクティビ化を妨げられることはありません。</li><li>リセット以外の例外によって横取りされることはありません。</li></ul> |

| HardFault | HardFault は、通常または例外の処理中のエラーによって発生する例外です。HardFault の優先度は -1 に固定されています。これは、設定可能な優先度を持つどの例外よりも優先度が高いことを意味します。                                                                                                                                    |

| SVCall    | スーパバイザ・コール (SVC) は、SVC 命令によりトリガされる例外です。OS 環境では、アプリケーションは SVC 命令を使用して OS カーネル関数やデバイス・ドライバにアクセスできます。                                                                                                                                            |

| PendSV    | PendSV は割込み駆動のシステムレベル・サービス要求です。OS 環境では、他にアクティブな例外が存在しない場合に PendSV を使用してコンテキストを切り替えます。                                                                                                                                                         |

|           |                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------|

| SysTick   | SysTick例外は、システム・タイマが0に達したときに生成する例外です。ソフトウェアでSysTick例外を生成することもできます。OS環境では、プロセッサはこの例外をシステム・ティックとして使用できます。     |

| 割込み (IRQ) | 割込み (IRQ)は、ペリフェラルによる信号またはソフトウェアの要求によって生成される例外です。割込みはすべて、命令の実行に対して非同期です。システム内で、ペリフェラルは割込みを使用してプロセッサとやりとりします。 |

表 12. さまざまな例外タイプのプロパティ

| 例外番号 <sup>(1)</sup> | IRQ<br>番号 <sup>(1)</sup> | 例外のタイプ    | 優先順位                | ベクタ・アドレス <sup>(2)</sup>             | アクティブ化 |

|---------------------|--------------------------|-----------|---------------------|-------------------------------------|--------|

| 1                   | -                        | リセット      | -3、最高               | 0x00000004                          | 非同期    |

| 2                   | -14                      | NMI       | -2                  | 0x00000008                          | 非同期    |

| 3                   | -13                      | HardFault | -1                  | 0x0000000C                          | 同期     |

| 4 ~ 10              | -                        | 予約済みです。   | -                   | -                                   | -      |

| 11                  | -5                       | SVCall    | 設定可能 <sup>(3)</sup> | 0x0000002C                          | 同期     |

| 12 ~ 13             | -                        | 予約済みです。   | -                   | -                                   | -      |

| 14                  | -2                       | PendSV    | 設定可能 <sup>(3)</sup> | 0x00000038                          | 非同期    |

| 15                  | -1                       | SysTick   | 設定可能 <sup>(3)</sup> | 0x0000003C                          | 非同期    |

| 15                  | -                        | 予約済みです。   | -                   | -                                   | -      |

| 16 以上               | 0 以上                     | 割込み (IRQ) | 設定可能 <sup>(3)</sup> | 0x00000040 以上<br><small>(4)</small> | 非同期    |

1. ソフトウェア層を簡素化するため、CMSISはIRQ番号のみを使用します。割込み以外の例外には負値を使用します。IPSRは、例外番号を返します（[17ページの割込みプログラム・ステータス・レジスタ](#)を参照）。

2. 詳細については、[30ページの図 7. : ベクタ・テーブル](#)を参照してください。

3. [86ページの4.2.6 : 割込み優先度のレジスタ](#)を参照

4. 4 ずつ増加します。

リセット以外の非同期例外の場合、プロセッサは、例外がトリガされてから例外ハンドラを開始するまでに、追加の命令を実行できます。

特権ソフトウェアは、[28ページの表 12](#)で優先度設定可能と記載されている例外を無効にできます（[85ページの4.2.3 : 割込みクリア・イネーブル・レジスタ](#)を参照）。

HardFaultの詳細については、[34ページの2.4 : フォールト処理](#)を参照してください

### 2.3.3 例外ハンドラ

プロセッサは、以下を使用して例外を処理します。

**割込みサービス・ルーチン (ISR)** IRQ0 ~ IRQ31 の割込みは、ISR が処理する例外です。

**フォールト・ハンドラ** HardFault は、フォールト・ハンドラによって処理される唯一の例外です。

**システム・ハンドラ** NMI、PendSV、SVCALL、SysTick、および HardFault はすべて、システム・ハンドラが処理するシステム例外です。

### 2.3.4 ベクタ・テーブル

ベクタ・テーブルには、スタック・ポインタのリセット値、およびすべての例外ハンドラの開始アドレス（例外ベクタとも呼ばれます）が格納されています。[30 ページの図 7](#)に、ベクタ・テーブルの例外ベクタの順序を示します。各ベクタの最下位ビットは、例外ハンドラが Thumb コードに書き込まれたことを示す、1 である必要があります。

図 7. ベクタ・テーブル

| 例外番号 | IRQ 番号 | ベクタ       | オフセット |

|------|--------|-----------|-------|

| 47   | 31     | IRQ31     | 0xBC  |

| .    | .      | .         | .     |

| 18   | 2      | IRQ2      | 0x48  |

| 17   | 1      | IRQ1      | 0x44  |

| 16   | 0      | IRQ0      | 0x40  |

| 15   | -1     | SysTick   | 0x3C  |

| 14   | -2     | PendSV    | 0x38  |

| 13   |        | 予約済みです。   |       |

| 12   |        |           |       |

| 11   | -5     | SVCall    | 0x2C  |

| 10   |        |           |       |

| 9    |        |           |       |

| 8    |        |           |       |

| 7    |        | 予約済みです。   |       |

| 6    |        |           |       |

| 5    |        |           |       |

| 4    |        |           |       |

| 3    | -13    | HardFault | 0x10  |

| 2    | -14    | NMI       | 0x0C  |

| 1    |        | リセット      | 0x08  |

|      |        | SP 初期値    | 0x04  |

|      |        |           | 0x00  |

MS33828V1

システム・リセット時に、ベクタ・テーブルはアドレス 0x00000000 に固定されます。特権ソフトウェアは、ベクタ・テーブルのサイズと TBLOFF 設定の粒度に関してベクタ・テーブルの開始アドレスを別のメモリ位置に再配置するため VTOR に書き込むことができます（[セクション 4.3.4 : ベクタ・テーブル・オフセット・レジスタ](#)を参照）。

### 2.3.5 例外の優先度

[28 ページの表 12](#)に示すように、すべての例外には次のように優先度が関連付けられています。

- 優先度の値が小さいほど、優先順位が高いことを示します。

- リセット、HardFault、および NMI を除くすべての例外の優先度は設定可能です。

ソフトウェアで優先度が設定されない場合、優先度を設定可能なすべての例外の優先度は 0 になります。例外の優先度の設定の詳細については、次を参照してください。

- [95 ページの 4.3.8 : システム・ハンドラ優先度レジスタ](#)

- [86 ページの 4.2.6 : 割込み優先度のレジスタ](#)

**注 :** 設定可能な優先度の値の範囲は、0 ~ 192 (64 刻み) です。固定された負の優先度値を持つリセット、HardFault、および NMI 例外は、常に他のどの例外よりも優先度が高くなります。

IRQ[0] に大きい優先度値を、IRQ[1] に小さい優先度値を割り当てることは、IRQ[1] のほうが IRQ[0] より優先度が高いことを意味します。IRQ[1] と IRQ[0] の両方がアサートされている場合、IRQ[0] より先に IRQ[1] が処理されます。

同じ優先度を持つ複数の例外が保留中の場合、例外番号が最も小さい例外が優先されます。たとえば、同じ優先度を持つ IRQ[0] と IRQ[1] が保留中の場合、IRQ[1] より先に IRQ[0] が処理されます。

プロセッサが例外ハンドラを実行中に、それより優先度の高い例外が発生した場合、例外ハンドラは横取りされます。例外を処理中にその例外と同じ優先度の例外が発生した場合、例外番号に関係なく、ハンドラは横取りされません。ただし、新しい割込みのステータスは保留中になります。

### 2.3.6 例外の開始と復帰

例外処理の説明では、次の用語を使用します。

**横取り** プロセッサが例外ハンドラを実行しているとき、処理されている例外より優先度が高い例外が発生すると、例外ハンドラが横取りされる可能性があります。

例外が別の例外を横取りする場合、これらをネストされた例外と呼びます。詳細については、[32 ページの例外の開始](#)を参照してください。

**復帰** 例外ハンドラが完了し、次の条件が満たされたときに発生します。

- 処理されるための十分な優先度を持つ保留中の例外が存在しない。

- 完了した例外ハンドラが、後着の例外を処理していなかった。

プロセッサは、スタックをポップして、プロセッサの状態を割込み発生前の状態に復元します。詳細については、[33 ページの例外からの復帰](#)を参照してください。

**テール チェイン** 例外処理を高速化するメカニズムです。例外ハンドラの完了時に、例外開始要件を満たす保留中の例外が存在する場合、スタックのポップはスキップされて、新しい例外ハンドラに制御が移されます。

**後着** 横取りを高速化するメカニズムです。例外の状態を保存している途中で、それより優先度の高い例外が発生した場合、プロセッサは優先度の高い例外の処理に切り替えて、その例外のベクタ・フェッチを開始します。状態保存は後着の影響を受けません。保存される状態はどちらの例外でも同じだからです。後着の例外の例外ハンドラから復帰するときは、通常のテールチェイン・ルールが適用されます。

## 例外の開始

例外は、十分な優先度を持つ保留中の例外が存在し、次のどちらかの条件が満たされる場合に開始されます。

- プロセッサがスレッド・モードである。

- 新しい例外の優先度が処理されている例外より高い(この場合は新しい例外が処理されている例外を横取りする)。

例外が別の例外を横取りする場合、これらの例外はネストされています。

十分な優先度とは、例外の優先順位が、マスク・レジスタによって設定されている制限よりも高いことを意味します ([18 ページの例外マスク・レジスタ](#) を参照)。これより低い優先度を持つ例外は保留され、プロセッサによって処理されません。

プロセッサは、例外を取得するとき、それがテールチェインされている例外または後着の例外である場合を除いて、情報を現在のスタックにプッシュします。この動作はスタッキングと呼ばれ、8 データ・ワードの構造はスタック・フレームと呼ばれます。スタック・フレームには、次の情報が含まれています。

図 8. スタック・フレーム

スタッキングの直後のスタック・ポインタは、スタック・フレームの最下位アドレスを示しています。スタック・フレームはダブルワード・アドレスにアライメントされます。

スタック・フレームには、復帰アドレスが含まれています。これは、割り込まれたプログラムの次の命令のアドレスです。この値は、割り込まれたプログラムが再開されるように、例外からの復帰時に PC に復元されます。

プロセッサは、ベクタ・テーブルから例外ハンドラの開始アドレスを読み出すベクタ・フェッチを実行します。スタッキングが完了すると、プロセッサは例外ハンドラの実行を開始し、それと同時に EXC\_RETURN 値を LR に書き込みます。これは、スタック・フレームに対応するスタック・ポインタおよび例外ハンドラが開始される前のプロセッサの動作モードを示します。

例外を開始する間にそれより優先度の高い例外が発生しなかった場合、プロセッサは、例外ハンドラの実行を開始し、それに対応する割込みのステータスを自動的に保留中からアクティブに変更します。

例外を開始する間にそれより優先度の高い別の例外が発生した場合、プロセッサは、この例外の例外ハンドラの実行を開始し、その前の例外のステータスは保留中のままで変更しません。これは、後着のケースです。

## 例外からの復帰

例外からの復帰は、プロセッサがハンドラ・モードであり、次のいずれかの命令を実行して PC を EXC\_RETURN 値に設定しようとすると発生します。

- A PC をロードする POP 命令。

- B 任意のレジスタを使用する PBX 命令。

プロセッサは、例外の開始時に EXC\_RETURN 値を LR に保存します。例外メカニズムはこの値を使用して、プロセッサが例外ハンドラを完了したタイミングを検出します。EXC\_RETURN 値のビット [31:4] は 0xFFFFFFFF です。プロセッサがこのパターンに一致する値を PC にロードすると、その操作が通常の分岐操作ではなく、例外が完了したことを探出します。その結果、例外復帰のシーケンスが開始されます。EXC\_RETURN 値のビット [3:0] は、[33 ページの表 13](#)に示すように、必要な復帰スタイルとプロセッサ・モードを示します。

表 13. 例外からの復帰動作

| EXC_RETURN | 説明                                                                      |

|------------|-------------------------------------------------------------------------|

| 0xFFFFFFF1 | ハンドラ・モードに戻ります。<br>例外からの復帰では、メイン・スタックから状態を取得します。<br>実行では復帰後に MSP を使用します。 |

| 0xFFFFFFF9 | スレッド・モードに戻ります。<br>例外からの復帰では、MSP から状態を取得します。<br>実行では復帰後に MSP を使用します。     |

| 0xFFFFFFF0 | スレッド・モードに戻ります。<br>例外からの復帰では、PSP から状態を取得します。<br>実行では復帰後に PSP を使用します。     |

| その他のすべての値  | 予約済み。                                                                   |

## 2.4 フォールト処理

フォールトは、例外のサブセットです（[27ページの2.3：例外モデル](#)を参照）。フォールトはすべて結果として、HardFault 例外を取得するか、NMI または HardFault ハンドラで発生した場合はロックアップを引き起こします。フォールトが発生するのは以下の場合です。

- SVCall 以上の優先度での SVC 命令の実行。

- デバッガがアタッチされていない状態での BKPT 命令の実行。

- ロードまたはストアでシステムが生成したバス・エラー。

- XN メモリ・アドレスからの命令の実行。

- システムがバス・フォールトを生成した場所からの命令の実行。

- ベクタ・フェッチでシステムが生成したバス・エラー。

- 未定義の命令の実行。

- T ビットが以前に 0 にクリアされた結果として Thumb 状態にない場合の命令の実行。

- アラインされていないアドレスへのロードまたはストアの試行。

- 特権違反または管理されていない領域へのアクセス試行による MPU フォールト。

注： 固定優先度の HardFault ハンドラを横取りできるのは、リセットと NMI のみです。HardFault は、リセット、NMI、または別の HardFault を除くすべての例外を横取りできます。

### 2.4.1 ロックアップ

NMI ハンドラまたは HardFault ハンドラの実行時にフォールトが発生した場合、あるいは MSP を使用して例外復帰時に PSR をアンスタッカする際にバス・エラーが発生した場合、プロセッサはロックアップ状態になります。ロックアップ状態のプロセッサは、命令を一切実行しません。プロセッサは、次のいずれかが発生するまでロックアップ状態のままであります。

- リセットされる。

- デバッガによって停止される。

- NMI が発生し、現在のロックアップが HardFault ハンドラ内にある。

注： NMI ハンドラでロックアップ状態が発生した場合、その後の NMI では、プロセッサのロックアップ状態は変わりません。

## 2.5 電源管理

Cortex-M0+ プロセッサの SLEEP モードは、消費電力を削減します。

- SLEEP モードでは、プロセッサのクロックが停止します。

- ディープ SLEEP モードでは、超低電力モードに移行します。

SCR の SLEEPDEEP ビットにより、使用する SLEEP モードを選択します ([94ページの4.3.6 : システム制御ロック](#) を参照)。ディープ SLEEP モードに移行する際、PWR\_CR レジスタの PDSS ビットが、停止モードまたはスタンバイ・モードへの移行を選択します。詳細については、リファレンスマニュアルの「低電力モード」の章を参照してください。

このセクションでは、SLEEP モードに移行するメカニズムおよび SLEEP モードからウェイクアップするための条件について説明します。

### 2.5.1 SLEEP モードへの移行

このセクションでは、ソフトウェアがプロセッサを SLEEP モードに移行するために使用できるメカニズムについて説明します。

システムは、プロセッサをウェイクアップするデバッグ操作など、偽のウェイクアップ・イベントを生成できます。このため、ソフトウェアが、そのようなイベントの後にプロセッサを SLEEP モードに戻すことができる必要があります。たとえば、プロセッサを SLEEP モードに戻すアイドル・ループをプログラムに組み込むことができます。

#### 割込みを待機

割込みを待機 (WFI) 命令は、ただちに SLEEP モードへの移行を発生させます。プロセッサは、WFI 命令を実行すると、命令の実行を停止して、SLEEP モードに移行します。詳細については、[81ページの3.7.12 : WFI](#) を参照してください。

#### イベント待機

イベント待機命令 WFE は、1 ビットのイベント・レジスタの値を条件として、SLEEP モードへの移行を発生させます。プロセッサは WFE 命令を実行すると、イベント・レジスタの値をチェックします。

- |   |                                                      |

|---|------------------------------------------------------|

| 0 | プロセッサは命令の実行を停止して、SLEEP モードに移行します。                    |

| 1 | プロセッサはレジスタを 0 にセットし、SLEEP モードに移行することなく、引き続き命令を実行します。 |

詳細については、[80ページの3.7.11 : WFE](#) を参照してください。

イベント・レジスタが 1 の場合、プロセッサは WFE 命令の実行時に SLEEP モードにすることはできません。これは通常、外部イベントのアサートのためか、またはシステム内の別のプロセッサにより SEV 命令が実行されているためです ([78ページの3.7.9 : SEV](#) を参照)。ソフトウェアはこのレジスタに直接アクセスすることはできません。

#### Sleep-on-exit

SCR の SLEEPONEXIT ビットが 1 にセットされている場合、プロセッサは例外ハンドラの実行を完了してスレッド・モードに戻ると、ただちに SLEEP モードに移行します。このメカニズムは、割込みの発生時にプロセッサの実行のみが必要なアプリケーションで使用されます。

## 2.5.2 SLEEP モードからのウェイクアップ

プロセッサがウェイクアップする条件は、SLEEP モードへの移行を引き起こしたメカニズムによって異なります。

### WFI または sleep-on-exit からのウェイクアップ

通常プロセッサは、例外の開始を引き起こすのに十分な優先度の例外を検出した場合にのみウェイクアップします。

一部の組込みシステムでは、プロセッサのウェイクアップ後、割込みハンドラの実行前に、システムの復元タスクを実行する必要がある場合があります。これを実現するには、PRIMASK.PM ビットを 1 にセットします。有効で現在の例外優先度より高い優先度の割込みが入った場合、プロセッサはウェイクアップしますが、PRIMASK.PM をゼロにセットするまで割込みハンドラを実行しません。PRIMASK の詳細については、[18 ページの例外マスク・レジスタ](#) を参照してください。

### WFE からのウェイクアップ

プロセッサは次の場合にウェイクアップします。

- 例外の開始を引き起こすのに十分な優先度の例外を検出した場合。

- 外部イベント信号を検出した場合 ([36 ページの 2.5.3 : 外部イベント入力](#) を参照)。

- マルチプロセッサ・システムで、システム内の別のプロセッサが SEV 命令を実行した場合。

また、SCR の SEVONPEND ビットが 1 にセットされている場合、新しい保留中の割込みは、その割込みが無効、あるいは例外の開始を引き起こすのに十分な優先度を持っていなくても、イベントをトリガし、プロセッサをウェイクアップします。SCR の詳細については、[94 ページの 4.3.6 : システム制御ブロック](#) を参照してください。

## 2.5.3 外部イベント入力

プロセッサは外部イベント入力信号を供給します。この信号は、ペリフェラルによって生成される可能性があります。この信号を使用しない場合は LOW にしてください。

この信号は、WFE からプロセッサをウェイクアップするか、内部の WFE イベント・レジスタを 1 にセットして後の WFE 命令でプロセッサが SLEEP モードに移行してはいけないことを示します ([35 ページのイベント待機](#) を参照)。

## 2.5.4 電源管理に関するプログラミングのヒント

ISO/IEC C は直接 WFI、WFE および SEV 命令を生成できません。これらの命令に対して、CMSIS では次の組込み関数を用意しています。

```

void __WFE(void) // Wait for Event

void __WFI(void) // Wait for Interrupt

void __SEV(void) // Send Event

```

## 3 Cortex-M0+ 命令セット

### 3.1 命令セットの概要

プロセッサは Thumb 命令セット・バージョンを実装しています。表 14 にサポートされる命令を示します。

表 14 で、

- 山かっこ (<>) は、オペランドの代替形式を囲みます。

- 中かっこ ({}) は、任意のオペランドおよびニーモニック部分を囲みます。

- オペランド列はすべてが示されているわけではありません。

命令およびオペランドの詳細については、該当する命令の説明を参照してください。

表 14. Cortex-M0+ 命令

| ニーモニック | オペランド                 | 概要                     | フラグ        | セクション                       |

|--------|-----------------------|------------------------|------------|-----------------------------|

| ADCS   | {Rd}, Rn, Rm          | キャリー付き加算               | N, Z, C, V | <a href="#">55ページの3.5.1</a> |

| ADD{S} | {Rd}, Rn, <Rm   #imm> | 加算                     | N, Z, C, V | <a href="#">55ページの3.5.1</a> |

| ADR    | Rd, label             | レジスタに対する PC 相対アドレス     | -          | <a href="#">47ページの3.4.1</a> |

| ANDS   | {Rd}, Rn, Rm          | ビット単位論理積               | N, Z       | <a href="#">57ページの3.5.2</a> |

| ASRS   | {Rd}, Rm, <Rs   #imm> | 算術右シフト                 | N, Z, C    | <a href="#">58ページの3.5.3</a> |

| B{cc}  | label                 | 分岐 {条件付き}              | -          | <a href="#">67ページの3.6.1</a> |

| BICS   | {Rd}, Rn, Rm          | ビット・クリア                | N, Z       | <a href="#">57ページの3.5.2</a> |

| BKPT   | #imm                  | ブレークポイント               | -          | <a href="#">70ページの3.7.1</a> |

| BL     | label                 | リンク付き分岐                | -          | <a href="#">67ページの3.6.1</a> |

| BLX    | Rm                    | リンク付き間接分岐              | -          | <a href="#">67ページの3.6.1</a> |

| BX     | Rm                    | 間接分岐                   | -          | <a href="#">67ページの3.6.1</a> |

| CMN    | Rn, Rm                | 否定比較                   | N, Z, C, V | <a href="#">60ページの3.5.4</a> |

| CMP    | Rn, <Rm   #imm>       | 比較                     | N, Z, C, V | <a href="#">60ページの3.5.4</a> |

| CPSID  | i                     | プロセッサ状態の変更、割込みを無効にする   | -          | <a href="#">71ページの3.7.2</a> |

| CPSIE  | i                     | プロセッサ状態の変更、割込みを有効にする   | -          | <a href="#">71ページの3.7.2</a> |

| DMB    | -                     | データ・メモリ・バリア            | -          | <a href="#">72ページの3.7.3</a> |

| DSB    | -                     | データ同期バリア               | -          | <a href="#">73ページの3.7.4</a> |

| EORS   | {Rd}, Rn, Rm          | 排他的論理和                 | N, Z       | <a href="#">57ページの3.5.2</a> |

| ISB    | -                     | 命令同期バリア                | -          | <a href="#">74ページの3.7.5</a> |

| LDM    | Rn{!}, reglist        | 多重レジスタ・ロード、ポスト・インクリメント | -          | <a href="#">51ページの3.4.5</a> |

| LDR    | Rt, label             | PC 相対アドレスからのレジスタ・ロード   | -          | <a href="#">48ページの3.4.2</a> |

| LDR    | Rt, [Rn, <Rm   #imm>] | レジスタ・ロード (ワード)         | -          | <a href="#">48ページの3.4.2</a> |

表 14. Cortex-M0+ 命令 (続き)

| ニーモニック | オペランド                   | 概要                     | フラグ        | セクション        |

|--------|-------------------------|------------------------|------------|--------------|

| LDRB   | $Rt, [Rn, <Rm #imm>]$   | レジスタ・ロード (バイト)         | -          | 48ページの3.4.2  |

| LDRH   | $Rt, [Rn, <Rm #imm>]$   | レジスタ・ロード (ハーフワード)      | -          | 48ページの3.4.2  |

| LDRSB  | $Rt, [Rn, <Rm #imm>]$   | レジスタ・ロード (符号付きバイト)     | -          | 48ページの3.4.2  |

| LDRSH  | $Rt, [Rn, <Rm #imm>]$   | レジスタ・ロード (符号付きハーフワード)  | -          | 48ページの3.4.2  |

| LSLS   | $\{Rd\}, Rn, <Rs #imm>$ | 論理左シフト                 | N, Z, C    | 58ページの3.5.3  |

| LSRS   | $\{Rd\}, Rn, <Rs #imm>$ | 論理右シフト                 | N, Z, C    | 58ページの3.5.3  |

| MOV{S} | $Rd, Rm$                | 転送                     | N, Z       | 61ページの3.5.5  |

| MRS    | $Rd, spec\_reg$         | 特殊レジスタの内容の汎用レジスタへの転送   | -          | 75ページの3.7.6  |

| MSR    | $spec\_reg, Rm$         | 汎用レジスタの内容の特殊レジスタへの転送   | N, Z, C, V | 76ページの3.7.7  |

| MULS   | $Rd, Rn, Rm$            | 乗算、32ビットの結果            | N, Z       | 62ページの3.5.6  |

| MVNS   | $Rd, Rm$                | ビット単位否定                | N, Z       | 61ページの3.5.5  |

| NOP    | -                       | 何もしない                  | -          | 77ページの3.7.8  |

| ORRS   | $\{Rd\}, Rn, Rm$        | 論理和                    | N, Z       | 57ページの3.5.2  |

| POP    | $reglist$               | レジスタをスタックからポップ         | -          | 53ページの3.4.6  |

| PUSH   | $reglist$               | レジスタをスタックにプッシュ         | -          | 53ページの3.4.6  |

| REV    | $Rd, Rm$                | ワードのバイト反転              | -          | 63ページの3.5.7  |

| REV16  | $Rd, Rm$                | パック・ハーフワードのバイト反転       | -          | 63ページの3.5.7  |

| REVSH  | $Rd, Rm$                | 符号付きハーフワードのバイト反転       | -          | 63ページの3.5.7  |

| RORS   | $\{Rd\}, Rn, Rs$        | 右ローテート                 | N, Z, C    | 58ページの3.5.3  |

| RSBS   | $\{Rd\}, Rn, #0$        | 反転減算                   | N, Z, C, V | 55ページの3.5.1  |

| SBCS   | $\{Rd\}, Rn, Rm$        | キャリー付き減算               | N, Z, C, V | 55ページの3.5.1  |

| SEV    | -                       | イベント送信                 | -          | 78ページの3.7.9  |

| STM    | $Rn!, reglist$          | 複数レジスタのストア、ポスト・インクリメント | -          | 51ページの3.4.5  |

| STR    | $Rt, [Rn, <Rm #imm>]$   | レジスタ・ストア(ワード)          | -          | 48ページの3.4.2  |

| STRB   | $Rt, [Rn, <Rm #imm>]$   | レジスタ・ストア(バイト)          | -          | 48ページの3.4.2  |

| STRH   | $Rt, [Rn, <Rm #imm>]$   | レジスタ・ストア(ハーフワード)       | -          | 48ページの3.4.2  |

| SUB{S} | $\{Rd\}, Rn, <Rm #imm>$ | 減算                     | N, Z, C, V | 55ページの3.5.1  |

| SVC    | #imm                    | スーパバイザ・コール             | -          | 79ページの3.7.10 |

| SXTB   | $Rd, Rm$                | 符号拡張 (バイト)             | -          | 64ページの3.5.8  |

表 14. Cortex-M0+ 命令 (続き)

| ニーモニック | オペランド    | 概要             | フラグ  | セクション        |

|--------|----------|----------------|------|--------------|

| SXTH   | $Rd, Rm$ | 符号拡張 (ハーフワード)  | -    | 64ページの3.5.8  |

| TST    | $Rn, Rm$ | 論理 AND ベースのテスト | N, Z | 65ページの3.5.9  |

| UXTB   | $Rd, Rm$ | ゼロ拡張 (バイト)     | -    | 64ページの3.5.8  |

| UXTH   | $Rd, Rm$ | ゼロ拡張 (ハーフワード)  | -    | 64ページの3.5.8  |

| WFE    | -        | イベント待機         | -    | 80ページの3.7.11 |

| WFI    | -        | 割込み待機          | -    | 81ページの3.7.12 |

## 3.2 組込み関数

ISO/IEC C コードは、一部の Cortex-M0+ 命令には直接アクセスできません。このセクションでは、これらの命令を生成できる組込み関数について説明します。これらは、CMSIS から提供されますが、C コンパイラから提供される場合もあります。C コンパイラが適切な組込み関数をサポートしていない場合は、インライン・アセンブラーを使用して関連する命令にアクセスする必要があります。

CMSIS では、ISO/IEC C コードで直接アクセスできない命令を生成するため、以下の組込み関数を提供しています。

**表 15. 一部の Cortex-M0+ 命令を生成するための CMSIS 組込み関数**

| 命令      | CMSIS 組込み関数                          |

|---------|--------------------------------------|

| CPSIE i | void __enable_irq(void)              |

| CPSID i | void __disable_irq(void)             |

| ISB     | void __ISB(void)                     |

| DSB     | void __DSB(void)                     |

| DMB     | void __DMB(void)                     |

| NOP     | void __NOP(void)                     |

| REV     | uint32_t __REV(uint32_t int value)   |

| REV16   | uint32_t __REV16(uint32_t int value) |

| REVSH   | uint32_t __REVSH(uint32_t int value) |

| SEV     | void __SEV(void)                     |

| WFE     | void __WFE(void)                     |

| WFI     | void __WFI(void)                     |

CMSIS では、MRS および MSR 命令を使用して特殊レジスタにアクセスするための関数も多数用意しています。

**表 16. 特殊レジスタにアクセスするための CMSIS 組込み関数**

| 特殊レジスタ  | アクセス | CMSIS 関数                                 |

|---------|------|------------------------------------------|

| PRIMASK | 読み出し | uint32_t __get_PRIMASK (void)            |

|         | 書き込み | void __set_PRIMASK (uint32_t value)      |

| CONTROL | 読み出し | uint32_t __get_CONTROL (void)            |

|         | 書き込み | void __set_CONTROL (uint32_t value)      |

| MSP     | 読み出し | uint32_t __get_MSP (void)                |

|         | 書き込み | void __set_MSP (uint32_t TopOfMainStack) |

| PSP     | 読み出し | uint32_t __get_PSP (void)                |

|         | 書き込み | void __set_PSP (uint32_t TopOfProcStack) |

### 3.3 命令の説明について

以下に示すセクションでは、命令の使用方法について説明します。

- オペランド

- PC または SP を使用した場合の制限事項

- シフト演算

- アドレスのアライメント

- PC 相対式

- 条件付き実行

#### 3.3.1 オペランド

命令のオペランドには、Arm® レジスタ、定数、またはその他の命令固有のパラメータを指定できます。命令はオペランドに作用し、多くの場合、その結果をデスティネーション・レジスタに格納します。その命令にデスティネーション・レジスタが存在する場合、これは通常他のオペランドの前に指定されます。

#### 3.3.2 PC または SP を使用した場合の制限事項

多くの命令は、オペランドまたはデスティネーション・レジスタにプログラム・カウンタ (PC) とスタック・ポインタ (SP) を使用できないか、またはそれらのどちらを使用できるかに関する制約があります。詳細については、命令の説明を参照してください。

**注 :** PC を BX、BLX、または POP の命令で更新する場合、正常に実行するためには、任意のアドレスのビット [0] を 1 にする必要があります。これは、このビットがデスティネーション命令セットを示しており、Cortex-M0+ プロセッサでは Thumb 命令のみがサポートされているためです。BL または BLX 命令でビット [0] の値を LR に書き込むと、自動的に値 1 が割り当てられます。

#### 3.3.3 シフト演算

レジスタのシフト演算では、レジスタ内のビットが指定のビット数（シフト長）だけ左または右に転送します。レジスタのシフトは、ASR、LSR、LSL、および ROR 命令によって直接実行できます。結果はデスティネーション・レジスタに書き込まれます。

指定可能なシフト長はシフトの種類と命令によって異なります（各命令の説明を参照）。シフト長が 0 の場合、シフトは行われません。レジスタのシフト演算では、指定したシフト長が 0 の場合を除き、キャリー・フラグが更新されます。以下のサブセクションでは、さまざまなシフト演算と、これらの演算がキャリー・フラグに与える影響について説明します。ここでは、Rm はシフトされる値を保持するレジスタを、n はシフト長を表します。

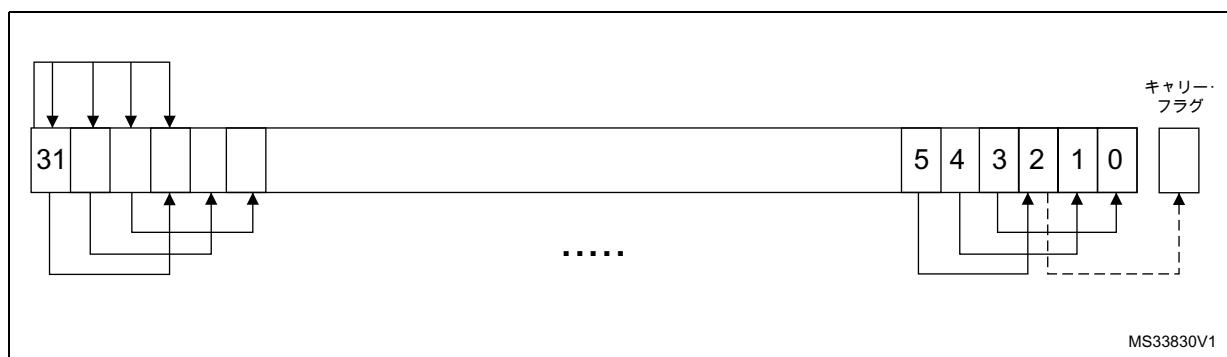

##### ASR

n ビットの算術右シフトです。レジスタ Rm の左側  $32-n$  ビットを右に n 枠転送し、演算結果の右側  $32-n$  ビットが得られます。さらに、レジスタの元のビット [31] の値が左側 n ビットにコピーされます。[42 ページの図 9](#)を参照してください。

ASR 演算を使用すると、レジスタ Rm の符号付きの値を  $2^n$  で除算し、その結果を負の無限大に丸めることができます。

命令が ASRS の場合、キャリー・フラグは、レジスタ Rm からシフトアウトされた最後のビット（ビット [n-1]）に更新されます。

**注 :** n が 32 以上の場合、結果のすべてのビットが 0 にクリアされます。

n が 33 以上でキャリー・フラグが更新される場合、0 に更新されます。

図 9. ASR#3

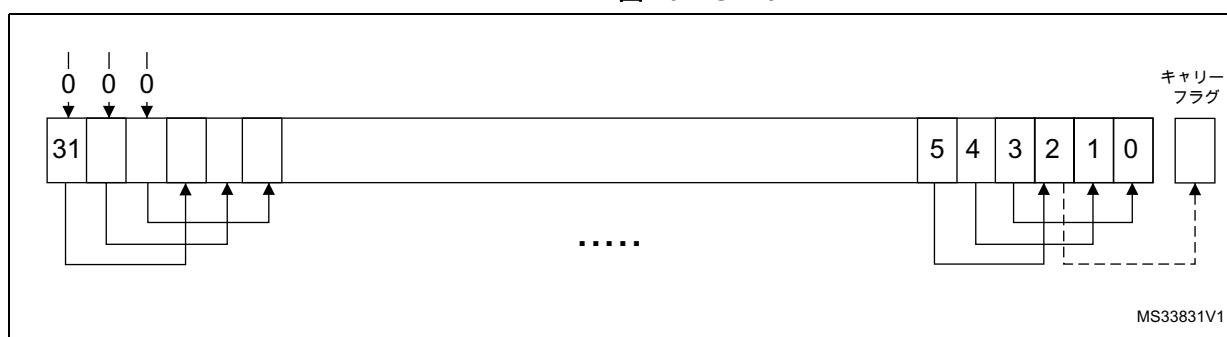

## LSR

$n$  ビットの論理右シフトです。レジスタ  $R_m$  の左側  $32-n$  ビットを右に  $n$  衝転送し、演算結果の右側  $32-n$  ビットが得られます。さらに、左  $n$  ビットを 0 にセットします。[42 ページの図 10](#)を参照してください。

LSR 演算を使用すると、レジスタ  $R_m$  の値を  $2^n$  で除算できます（値が符号なし整数と見なされる場合）。

命令が LSRS の場合、キャリー・フラグは、レジスタ  $R_m$  からシフトアウトされた最後のビット（ビット  $[n-1]$ ）に更新されます。

注：

n が 32 以上の場合、結果のすべてのビットが 0 にクリアされます。

n が 33 以上でキャリー・フラグが更新される場合、0 に更新されます。

図 10. LSR#3

## LSL

$n$  ビットの論理左シフトです。レジスタ  $R_m$  の右側  $32-n$  ビットを左に  $n$  衝転送し、演算結果の左側  $32-n$  ビットが得られます。さらに、右  $n$  ビットを 0 にセットします。[43 ページの図 11](#)を参照してください。

LSL 演算を使用すると、レジスタ  $R_m$  の値を  $2^n$  倍することができます（値が符号なしの整数または 2 の補数となる符号付き整数と解釈される場合）。このとき警告なしでオーバーフローが発生する場合があります。

命令が LSLS の場合、キャリー・フラグは、レジスタ  $R_m$  からシフトアウトされた最後のビット（ビット  $[32-n]$ ）に更新されます。これらの命令を LSL#0 とともに使用した場合、キャリー・フラグへの影響はありません。

注：

n が 32 以上の場合、結果のすべてのビットが 0 にクリアされます。

n が 33 以上でキャリー・フラグが更新される場合、0 に更新されます。

図 11. LSL #3

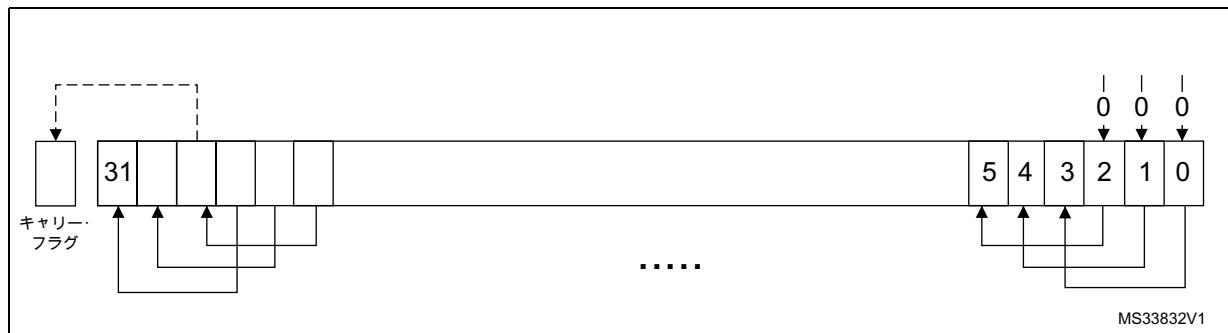

ROR

$n$  ビットの右ローテートです。レジスタ  $Rm$  の左側  $32-n$  ビットを右に  $n$  ビット転送し、演算結果の右側  $32-n$  ビットが得られます。さらに、レジスタの右  $n$  ビットを左  $n$  ビットに転送します。[43 ページの図 12](#) を参照してください。

命令が RORS の場合、キャリー・フラグは、レジスタ  $Rm$  の最後のビット・ローテーション（ビット [n-1]）に更新されます。

注：  $n$  が 32 の場合、結果の値は  $Rm$  の値と同じになります。また、キャリー・フラグが更新される場合は、 $Rm$  のビット [31] に更新されます。

32 を超えるシフト長  $n$  と ROR を指定した場合、シフト長  $n-32$  と ROR を指定した場合と動作は同じになります。

図 12. ROR #3

### 3.3.4 アドレスのアライメント

アラインド・アクセスとは、ワード境界で整列されたアドレスがワード、またはマルチワード・アクセスに使用される、あるいはハーフワード境界で整列されたアドレスがハーフワード・アクセスに使用される操作です。バイト・アクセスは常にアラインされます。

Cortex-M0+ プロセッサでのアンアラインド・アクセスはサポートされていません。アンアラインド・メモリ・アクセス操作を実行しようとすると、HardFault 例外が発生します。

### 3.3.5 PC 相対式

PC 相対式、すなわちラベルは、命令またはリテラル・データのアドレスを表すシンボルです。命令内では、PC 値に対して数値オフセットを加算または減算した値として表現されます。アセンブラーでは、ラベルおよび現在の命令のアドレスから必要なオフセットを計算します。オフセットが大きすぎる場合、アセンブラーによってエラーが生成されます。

注：ほとんどの命令では、PC の値は現在の命令のアドレスに 4 バイトを加算した値になります。アセンブリでは、ラベルにある数値を加算または減算したものや、[PC, #imm] の形式の表現など、他の構文が PC 相対式として許容される場合があります。

### 3.3.6 条件付き実行

ほとんどのデータ処理命令では、操作の結果に従って、アプリケーション・プログラム・ステータス・レジスタ (APSR) の条件フラグを更新します ([16 ページのアプリケーション・プログラム・ステータス・レジスタ](#) を参照)。すべてのフラグを更新する命令もあれば、サブセットのみを更新する命令もあります。フラグが更新されない場合は、元の値が保持されます。命令の影響を受けるフラグについては、該当する命令の説明を参照してください。

別の命令によってセットされた条件フラグに基づいて、以下のいずれかの時点で条件付き分岐命令を実行できます。

- フラグを更新した命令の直後。

- フラグを更新していない任意の数の命令の後。

Cortex-M0+ プロセッサでは、条件付き実行は、条件分岐を使用することによって可能です。

このセクションでは以下の内容について説明します。

- [44 ページの条件フラグ](#)

- [45 ページの条件コードのサフィックス](#)

#### 条件フラグ

APSR には次の条件フラグが含まれます。

|   |                                                       |

|---|-------------------------------------------------------|

| N | 演算結果が負の場合は、1 にセットされます。それ以外の場合は、0 にクリアされます。            |

| Z | 演算結果がゼロの場合は、1 にセットされます。それ以外の場合は、0 にクリアされます。           |

| C | 演算の結果としてキャリーが発生した場合は、1 にセットされます。それ以外の場合は、0 にクリアされます。  |

| V | 演算によってオーバーフローが発生した場合は、1 にセットされます。それ以外の場合は、0 にクリアされます。 |

APSR の詳細については、[15 ページのプログラム・ステータス・レジスタ](#) を参照してください。

キャリーは以下の場合に発生します。

- 加算の結果が  $2^{32}$  以上の場合。

- 減算の結果が正またはゼロの場合。

- シフトまたはローテート命令の結果として。

オーバーフローは、ビット [31] に格納されている結果の符号が、無限精度で演算が実行された場合の結果の符号と一致しない場合に発生します。以下に例を示します。

- 2 つの負の値の加算結果が正の値になる場合。

- 2 つの正の値の加算結果が負の値になる場合。

- 負の値から正の値を減算した結果が正の値になる場合。

- 正の値から負の値を減算した結果が負の値になる場合。

比較演算は、結果が破棄されることを除き、CMP の場合は減算と、CMN の場合は加算と同じです。詳細については、該当する命令の説明を参照してください。

## 条件コードのサフィックス

条件付き分岐は、構文の説明では、 $B\{cond\}$  と表記しています。条件コードが指定されている分岐命令は、APSR の条件コード・フラグが指定した条件を満たしている場合にのみ実行されます。それ以外の場合、分岐命令は無視されます。[表 17](#) に、使用できる条件コードを示します。

[表 17](#) では、条件コードのサフィックスと、N、Z、C、およびV の各フラグとの関係も示します。

表 17. 条件コードのサフィックス

| サフィックス          | フラグ              | 意味                                 |

|-----------------|------------------|------------------------------------|

| EQ              | Z = 1            | 等しい、最後のフラグ設定結果はゼロでした。              |

| NE              | Z = 0            | 等しくない、最後のフラグ設定結果はゼロ以外でした。          |

| CS<br>または<br>HS | C = 1            | 以上（符号なし）。                          |

| CC<br>または<br>LO | C = 0            | 未満（符号なし）。                          |

| MI              | N = 1            | 負。                                 |

| PL              | N = 0            | 正または 0。                            |

| VS              | V = 1            | オーバーフロー。                           |

| VC              | V = 0            | オーバーフローなし。                         |

| HI              | C = 1 かつ Z = 0   | より大きい（符号なし）。                       |

| LS              | C = 0 または Z = 1  | 以下（符号なし）。                          |

| GE              | N = V            | 以上（符号付き）。                          |

| LT              | N != V           | より小さい（符号付き）。                       |

| GT              | Z = 0 かつ N = V   | より大きい（符号付き）。                       |

| LE              | Z = 1 または N != V | 以下（符号付き）。                          |

| AL              | すべて              | 無条件。サフィックスが指定されていない場合は、これがデフォルトです。 |

### 3.4 メモリ・アクセス命令

表 18 に、メモリ・アクセス命令を示します。

表 18. メモリ・アクセス命令

| ニーモニック    | 概要                        | 参照先                                     |

|-----------|---------------------------|-----------------------------------------|

| ADR       | PC 相対アドレスの生成              | 47ページの3.4.1 : ADR                       |

| LDM       | レジスタの多重ロード                | 51ページの3.4.5 : LDM と STM                 |

| LDR{type} | イミディエート・オフセットを使ったレジスタ・ロード | 48ページの3.4.2 : LDR と STR (イミディエート・オフセット) |

| LDR{type} | レジスタ・オフセットを使ったレジスタ・ロード    | 49ページの3.4.3 : LDR と STR (レジスタ・オフセット)    |

| LDR       | PC 相対アドレスからのレジスタ・ロード      | 50ページの3.4.4 : LDR (PC 相対)               |

| POP       | レジスタをスタックからポップ            | 53ページの3.4.6 : PUSH と POP                |

| PUSH      | レジスタをスタックにプッシュ            | 53ページの3.4.6 : PUSH と POP                |

| STM       | レジスタの多重ストア                | 51ページの3.4.5 : LDM と STM                 |

| STR{type} | イミディエート・オフセットを使ったレジスタ・ストア | 48ページの3.4.2 : LDR と STR (イミディエート・オフセット) |

| STR{type} | レジスタ・オフセットを使ったレジスタ・ストア    | 49ページの3.4.3 : LDR と STR (レジスタ・オフセット)    |

### 3.4.1 ADR

PC 相対アドレスを生成します。

#### 構文

ADR Rd, label

ここで、

Rd デスティネーション・レジスタです。

label PC 相対式です。[43ページの3.3.5 : PC 相対式を参照してください。](#)

#### 動作

ADR は、イミディエート値を PC に追加することによって、アドレスを生成し、結果をデスティネーション・レジスタに書き込みます。

ADR は PC 相対アドレスであるため、位置独立コードの生成を容易にします。

ADR を使用して BX または BLX 命令のターゲット・アドレスを生成する場合、正常に実行するには、生成するアドレスのビット [0] を 1 にセットする必要があります。

#### 制限事項

この命令の場合、Rd は R0 ~ R7 を指定する必要があります。アドレス指定されたデータ値は、ワード整列され、現在の PC の 1020 バイト以内にある必要があります。

#### 条件フラグ

この命令によるフラグの変更はありません。

#### 例

ADR R1, TextMessage ; TextMessage というラベルの位置のアドレス値を；

R1 に書き込む

ADR R3, [PC,#996] ; R3 を PC + 996 の値に設定する。

### 3.4.2 LDR と STR (イミディエート・オフセット)

イミディエート・オフセットを使ったロードとストア。

#### 構文

```

LDR Rt, [<Rn | SP> {, #imm}]

LDR<B|H> Rt, [Rn {, #imm}]

STR Rt, [<Rn | SP>, {, #imm}]

STR<B|H> Rt, [Rn {, #imm}]

```

ここで、

|            |                                                        |

|------------|--------------------------------------------------------|

| <i>Rt</i>  | ロードまたはストアするレジスタです。                                     |

| <i>Rn</i>  | メモリ・アドレスのベースとなるレジスタです。                                 |

| <i>imm</i> | <i>Rn</i> からのオフセットです。 <i>imm</i> が省略されている場合、ゼロと想定されます。 |

#### 動作

LDR、LDRB、LDRH の各命令は、*Rt* で指定されるレジスタに、メモリからワード、バイト、またはハーフワードのデータ値をロードします。ワード未満のサイズは、*Rt* で指定されるレジスタに書き込まれる前に 32 ビットにゼロ拡張されます。

STR、STRB、STRH の各命令は、*Rt* で指定されるシングル・レジスタ内のワード、最下位バイト、下位ハーフワードをメモリに格納します。ロードまたはストアのためのメモリ・アドレスは、*Rn* と SP のいずれかで指定されるレジスタの値とイミディエート値 *imm* の合計です。

#### 制限事項

これらの命令の場合 :

- *Rd* と *Rn* では R0 ~ R7 のみを指定する必要があります。

- *imm* の条件 :

- ベース・レジスタに SP を使用する LDR と STR については、0 ~ 1020 の範囲で、4 の倍数の整数。

- ベース・レジスタに R0 ~ R7 を使用する LDR と STR については、0 ~ 124 の範囲で、4 の倍数の整数。

- LDRH と STRH については、0 ~ 62 の範囲で、2 の倍数の整数。

- LDRB と STRB については、0 ~ 31 の範囲

- 計算されたアドレスは、トランザクションのバイト数で割り切れなければなりません。[43 ページの3.3.4 : アドレスのアライメント](#)を参照してください。

#### 条件フラグ

これらの命令によるフラグの変更はありません。

#### 例

```

LDR R4, [R7 ; R7 のアドレスから R4 をロードする。

STR R2, [R0,#const-struc] ; const-struc は,

; 0 ~ 1020 の範囲内の定数に評価される式。

```

### 3.4.3 LDR と STR (レジスタ・オフセット)

レジスタ・オフセットを使ったロードとストア。

#### 構文

```

LDR Rt, [Rn, Rm]

LDR<B|H> Rt, [Rn, Rm]

LDR<SB|SH> Rt, [Rn, Rm]

STR Rt, [Rn, Rm]

STR<B|H> Rt, [Rn, Rm]

```

ここで、

- |           |                          |

|-----------|--------------------------|

| <i>Rt</i> | ロードまたはストアするレジスタです。       |

| <i>Rn</i> | メモリ・アドレスのベースとなるレジスタです。   |

| <i>Rm</i> | オフセットとして使用される値を含むレジスタです。 |

#### 動作

LDR、LDRB、LDRH、LDRSB、LDRSH は *Rt* で指定されるレジスタに、ワード、ゼロ拡張バイト、ゼロ拡張ハーフワード、符号拡張バイト、符号拡張ハーフワードの値をメモリからロードします。

STR、STRB、STRH は、*Rt* で指定されるシングル・レジスタ内のワード、最下位バイト、下位ハーフワードをメモリに格納します。

ロードまたはストアのためのメモリ・アドレスは、*Rn* と *Rm* で指定される各レジスタの値の合計です。

#### 制限事項

これらの命令の場合：

- *Rt*、*Rn*、*Rm* では R0 ~ R7 のみを指定する必要があります。

- 計算されたメモリ・アドレスは、ロードまたはストアのバイト数で割り切れなければなりません。[43ページの3.3.4 : アドレスのアライメント](#)を参照してください。

#### 条件フラグ

これらの命令によるフラグの変更はありません。

#### 例

```

STR R0, [R5, R1]           ; R0 の値を R5 と R1 の合計に等しいアドレスに

; ストア

LDRSH R1, [R2, R3]          ; (R2 + R3) で指定されたメモリ・アドレスから

; ハーフワードをロードし、32 ビットに符号拡張して

; R1 に書き込む。

```

### 3.4.4 LDR (PC 相対)

メモリからのレジスタ・ロード（リテラル）。

#### 構文

LDR Rt, label

ここで、

Rt ロードするレジスタです。

label PC 相対式です。[43ページの3.3.5 : PC 相対式を参照してください。](#)

#### 動作

Rt で指定されるレジスタを、label で指定されるメモリ内のワードからロードします。

#### 制限事項

これらの命令の場合、label は現在の PC の 1020 バイト以内にあり、ワード整列されている必要があります。

#### 条件フラグ

これらの命令によるフラグの変更はありません。

#### 例

```

LDR    R0, LookUpTable ; LookUpTable とラベル付けされたアドレスからの

; ワード・データを R0 にロードする。

LDR    R3, [PC, #100]   ; R3 に (PC + 100) のメモリ・ワードをロードする。

```

### 3.4.5 LDM と STM

複数レジスタのロードとストア。

#### 構文

LDM Rn{!}, reglist

STM Rn!, reglist

ここで、

Rn メモリ・アドレスのベースとなるレジスタです。

! ライトバックサフィックス。

reglist ロードまたはストアするレジスタのリストを中かっこで囲んで指定します。レジスタ範囲も指定できます。複数のレジスタまたはレジスタ範囲を指定する場合は、コンマで区切る必要があります ([51 ページの例](#)を参照)。

LDMIA と LDMFD は LDM の同義語です。LDMIA は、各アクセス後にインクリメントされるベース・レジスタを表します。LDMFD を使用することで、完全降順スタックからデータをポップできます。

STMIA と STMEA は STM の同義語です。STMIA は、各アクセス後にインクリメントされるベース・レジスタを表します。STMEA を使用することで、空き昇順スタックヘデータをプッシュできます。

#### 動作

LDM 命令は、Rn に基づくメモリ・アドレスからワード値を reglist のレジスタにロードします。

STM 命令は、reglist のレジスタのワード値を Rn に基づくメモリ・アドレスにストアします。

アクセスに使用されるメモリ・アドレスは、Rn で指定されるレジスタの値から  $Rn + 4 * (n-1)$  で指定されるレジスタまでの値の範囲 (n は reglist 内のレジスタ数) で 4 バイト間隔となります。アクセスはレジスタ番号の昇順に発生し、最小の番号のレジスタが最下位のメモリ・アドレスを使用し、最大の番号のレジスタが最上位のメモリ・アドレスを使用します。ライトバックサフィックスが指定されている場合、 $Rn + 4 * n$  で指定されるレジスタの値が Rn で指定されるレジスタにライトバックされます。

#### 制限事項

これらの命令の場合 :

- reglist と Rn は R0 ~ R7 に制限されます。

- ライトバックサフィックスは必ず使用する必要がありますが、reglist にも Rn が格納される LDM が命令の場合を除きます。この場合、ライトバックサフィックスを使用できません。

- Rn で指定されるレジスタの値は、ワード整列されていなければなりません。詳細については、[43 ページの 3.3.4 : アドレスのアライメント](#) を参照してください。

- STM については、Rn が reglist に含まれている場合、リストの先頭レジスタでなければなりません。

#### 条件フラグ

これらの命令によるフラグの変更はありません。

#### 例

```

LDM      R0, {R0, R3, R4}      ; LDMIA は LDM の同義語

STMIA   R1!, {R2-R4, R6}

```

### 誤用例

STM R5!, {R4, R5, R6} ; R5 にストアされる値は予測不能

LDM R2, {} ; リストには少なくとも 1 つのレジスタが必要

### 3.4.6 PUSH と POP

完全降順スタックヘレジスタをプッシュ、および完全降順スタックからレジスタをポップ。

#### 構文

```

PUSH reglist

POP reglist

```

ここで、

**reglist** 空でないレジスタのリストを中かっこで囲んで指定します。レジスタ範囲も指定できます。複数のレジスタまたはレジスタ範囲を指定する場合は、コンマで区切る必要があります。

#### 動作

**PUSH** はレジスタをスタックにストアし、最小の番号のレジスタが最下位のメモリ・アドレスを使用して、最大の番号のレジスタが最上位のメモリ・アドレスを使用します。

**POP** はレジスタをスタックからロードし、最小の番号のレジスタが最下位のメモリ・アドレスを使用して、最大の番号のレジスタが最上位のメモリ・アドレスを使用します。

完全降順スタックを実装し、**PUSH** は最上位のメモリ・アドレスとして SP レジスタの値から 4 を引いた値を使用して、**POP** は最下位のメモリ・アドレスとして SP レジスタの値を使用します。完了時に、**PUSH** は最下位のストア値の位置をポイントするように SP レジスタを更新し、**POP** はロードされた最上位の位置の上の位置をポイントするように SP レジスタを更新します。

**POP** 命令で **reglist** に PC が含まれている場合、この **POP** 命令の完了時にこの位置への分岐を発生させます。PC で読み出した値のビット [0] は、APSR の T ビットの更新に使用されます。正常な操作を保証するには、このビットを 1 にする必要があります。

#### 制限事項

これらの命令の場合：

- **reglist** は R0 ~ R7 のみを使用する必要があります。

- 例外は **PUSH** では LR、**POP** では PC になります

#### 条件フラグ

これらの命令によるフラグの変更はありません。

#### 例

```

PUSH {R0,R4-R7}      ; R0、R4、R5、R6、R7 をスタックにプッシュする

PUSH {R2,LR}          ; R2 とリンクレジスタをスタックにプッシュする

POP {R0,R6,PC}        ; R0、R6 および PC をスタックからポップし、新しい PC に

; 分岐する

```

### 3.5 汎用データ処理命令

表 19 にデータ処理命令を示します。

表 19. データ処理命令

| ニーモニック | 概要                        | 参照先                                   |

|--------|---------------------------|---------------------------------------|

| ADCS   | キャリー付き加算                  | 55ページの3.5.1 : ADC、ADD、RSB、SBC、および SUB |

| ADD{S} | 加算                        | 55ページの3.5.1 : ADC、ADD、RSB、SBC、および SUB |

| ANDS   | 論理積                       | 57ページの3.5.2 : AND、ORR、EOR、および BIC     |

| ASRS   | 算術右シフト                    | 58ページの3.5.3 : ASR、LSL、LSR、および ROR     |

| BICS   | ビット・クリア                   | 57ページの3.5.2 : AND、ORR、EOR、および BIC     |

| CMN    | 否定比較                      | 60ページの3.5.4 : CMP および CMN             |

| CMP    | 比較                        | 60ページの3.5.4 : CMP および CMN             |

| EORS   | 排他的論理和                    | 57ページの3.5.2 : AND、ORR、EOR、および BIC     |

| LSLS   | 論理左シフト                    | 58ページの3.5.3 : ASR、LSL、LSR、および ROR     |

| LSRS   | 論理右シフト                    | 58ページの3.5.3 : ASR、LSL、LSR、および ROR     |

| MOV{S} | 転送                        | 61ページの3.5.5 : MOV および MVN             |

| MULS   | 乗算                        | 62ページの3.5.6 : MULS                    |

| MVNS   | 転送して否定                    | 61ページの3.5.5 : MOV および MVN             |

| ORRS   | 論理和                       | 57ページの3.5.2 : AND、ORR、EOR、および BIC     |

| REV    | ワード内のバイト順序反転              | 63ページの3.5.7 : REV、REV16、および REVSH     |

| REV16  | 各ハーフワード内のバイト順序反転          | 63ページの3.5.7 : REV、REV16、および REVSH     |

| REVSH  | 下位ハーフワード内のバイト順序を反転させ、符号拡張 | 63ページの3.5.7 : REV、REV16、および REVSH     |

| RORS   | 右ローテート                    | 58ページの3.5.3 : ASR、LSL、LSR、および ROR     |

| RSBS   | 反転減算                      | 55ページの3.5.1 : ADC、ADD、RSB、SBC、および SUB |

| SBCS   | キャリー付き減算                  | 55ページの3.5.1 : ADC、ADD、RSB、SBC、および SUB |

| SUBS   | 減算                        | 55ページの3.5.1 : ADC、ADD、RSB、SBC、および SUB |

| SXTB   | 符号拡張 (バイト)                | 64ページの3.5.8 : SXT および UXT             |

| SXTH   | 符号拡張 (ハーフワード)             | 64ページの3.5.8 : SXT および UXT             |

| UXTB   | ゼロ拡張 (バイト)                | 64ページの3.5.8 : SXT および UXT             |

| UXTH   | ゼロ拡張 (ハーフワード)             | 64ページの3.5.8 : SXT および UXT             |

| TST    | テスト                       | 65ページの3.5.9 : TST                     |

### 3.5.1 ADC、ADD、RSB、SBC、および SUB

キャリー付き加算、加算、反転減算、キャリー付き減算、および減算。

#### 構文

```

ADCS {Rd,} Rn, Rm

ADD{S} {Rd,} Rn, <Rm|#imm>

RSBS {Rd,} Rn, Rm, #0

SBCS {Rd,} Rn, Rm

SUB{S} {Rd,} Rn, <Rm|#imm>

```

ここで、

S ADD または SUB 命令によるフラグ更新を起動させます。

Rd 結果レジスタを指定します。

reglist 最初のソース・レジスタを指定します。

Imm 定数イミディエート値を指定します。

オプションの Rd レジスタ指示子が省略された場合、Rn と同じ値を取ると想定されます。たとえば、ADDS R1,R2 は ADDS R1,R1,R2 と同等に扱われます。

#### 動作

ADCS 命令は、Rn の値を Rm の値に付加し、キャリー・フラグがセットされている場合はさらに 1 が付加されます。また Rd で指定されたレジスタに結果を配置し、N、Z、C、V の各フラグを更新します。

ADD 命令は、Rn の値を Rm の値または imm で指定されるイミディエート値に付加し、結果を Rd で指定されるレジスタに配置します。

ADDS 命令は、ADD と同じ演算を実行し、N、Z、C、V の各フラグも更新します。

RSBS 命令は、Rn の値をゼロから減算し、算術的な負の値を生成し、結果を Rd で指定されるレジスタに配置して、N、Z、C、V の各フラグを更新します。

SBCS 命令は、Rm の値を Rn の値から減算し、キャリー・フラグがクリアされている場合は、結果から 1 が引かれます。この命令は、結果を Rd で指定されるレジスタに配置し、N、Z、C、V の各フラグを更新します。

SUB 命令は、Rm の値または imm で指定されるイミディエート値を減算します。この後、Rd で指定されるレジスタに結果を配置します。

SUBS 命令は、SUB と同じ演算を実行し、N、Z、C、V の各フラグも更新します。

ADC および SBC を使用してマルチワード算術演算を構成できます ([56 ページの例](#)を参照)。

[47ページの3.4.1 : ADR](#)も参照してください。

#### 制限事項

[表 20](#) に、レジスタ指示子の正規の組合せと、各命令で使用できるイミディエート値を一覧にしています。