life.augmented

**PM0253**

## プログラミング・マニュアル

STM32F7 シリーズおよび STM32H7 シリーズ

Cortex<sup>®</sup>-M7 プロセッサプログラミングマニュアル

### 概要

このプログラミング・マニュアルには、アプリケーションやシステムレベルのソフトウェアの開発者向けの情報が記載されています。本書では、STM32F7 シリーズおよび STM32H7 シリーズ Cortex<sup>®</sup>-M7 プロセッサのプログラミング・モデル、命令セット、およびコア・ペリフェラルについて詳しく説明します。

STM32F7 シリーズおよび STM32H7 シリーズ Cortex-M7 プロセッサは、マイクロコントローラ市場向けに設計された高性能な 32 ビットプロセッサです。

Arm<sup>®</sup> Cortex<sup>®</sup>-M7 は、Cortex-M プロセッサの中で最高性能を持ったものです。これは 6 段のスーパー・スカラ・パイプラインを、AXI、AHB、キャッシュ、密結合メモリなどを搭載した柔軟性の高いシステムやメモリ・インターフェースと組み合わせ、高い整数、浮動小数点、および、DSP 性能をもった STM32F7 シリーズ、および STM32H7 シリーズ MPU を提供します。また、複数のメモリ・インターフェースへのロード／ロードおよびロード／ストア命令ペアの二重発行もサポートしています。

Cortex-M7 プロセッサも、これまで同様の使いやすさや、C 言語と相性の良いプログラマのモデルを利用しており、これまでの Cortex-M プロセッサやツールと完全なバイナリ互換です。すべての Cortex-M プロセッサと共に、

Arm Cortex-M の開発エコシステムによる完全なサポートを利用できます。ソフトウェアに互換性があるので、Cortex-M3 や Cortex-M4 プロセッサからの移行も容易に行えます。

# 目次

|          |                                                                                                             |           |

|----------|-------------------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>本書について .....</b>                                                                                         | <b>14</b> |

| 1.1      | 表記規則 .....                                                                                                  | 14        |

| 1.2      | レジスタに関する略記 .....                                                                                            | 15        |

| 1.3      | Cortex®-M7 プロセッサおよびコア・ペリフェラルについて .....                                                                      | 15        |

| 1.3.1    | システム・レベル・インタフェース .....                                                                                      | 17        |

| 1.3.2    | 設定可能な統合デバッグ機能 .....                                                                                         | 17        |

| 1.3.3    | Cortex®-M7 プロセッサの特徴と利点の概要 .....                                                                             | 18        |

| 1.3.4    | Cortex®-M7 プロセッサのコア・ペリフェラル .....                                                                            | 18        |

| <b>2</b> | <b>Cortex-M7 プロセッサ .....</b>                                                                                | <b>19</b> |

| 2.1      | プログラマ・モデル .....                                                                                             | 19        |

| 2.1.1    | ソフトウェアの実行に対するプロセッサのモードと特権レベル .....                                                                          | 19        |

| 2.1.2    | スタック .....                                                                                                  | 19        |

| 2.1.3    | コア・レジスタ .....                                                                                               | 20        |

| 2.1.4    | 例外と割込み .....                                                                                                | 28        |

| 2.1.5    | データ型 .....                                                                                                  | 28        |

| 2.1.6    | Cortex Microcontroller Software Interface Standard<br>(Cortex マイクロコントローラ・ソフトウェア・インタフェース規格)<br>(CMSIS) ..... | 29        |

| 2.2      | Cortex®-M7 の構成 .....                                                                                        | 30        |

| 2.3      | メモリ・モデル .....                                                                                               | 32        |

| 2.3.1    | メモリの領域、タイプ、および属性 .....                                                                                      | 33        |

| 2.3.2    | メモリ・システムでのメモリ・アクセスの順序付け .....                                                                               | 33        |

| 2.3.3    | メモリ・アクセスの動作 .....                                                                                           | 34        |

| 2.3.4    | ソフトウェアによるメモリ・アクセスの順序付け .....                                                                                | 36        |

| 2.3.5    | メモリのエンディアン形式 .....                                                                                          | 36        |

| 2.3.6    | 同期プリミティブ .....                                                                                              | 37        |

| 2.3.7    | 同期プリミティブのプログラミングのヒント .....                                                                                  | 38        |

| 2.4      | 例外モデル .....                                                                                                 | 39        |

| 2.4.1    | 例外状態 .....                                                                                                  | 39        |

| 2.4.2    | 例外のタイプ .....                                                                                                | 39        |

| 2.4.3    | 例外ハンドラ .....                                                                                                | 41        |

| 2.4.4    | ベクタテーブル .....                                                                                               | 42        |

| 2.4.5    | 例外の優先度 .....                                                                                                | 43        |

|       |                                        |    |

|-------|----------------------------------------|----|

| 2.4.6 | 割込み優先度のグループ化 .....                     | 43 |

| 2.4.7 | 例外の開始と復帰 .....                         | 44 |

| 2.5   | フォールト処理 .....                          | 46 |

| 2.5.1 | フォールト・タイプ .....                        | 47 |

| 2.5.2 | フォールトの移行とハード・フォールト .....               | 47 |

| 2.5.3 | 同期および非同期バス・フォールト .....                 | 48 |

| 2.5.4 | フォールト・ステータス・レジスタとフォールト・アドレス・レジスタ ..... | 49 |

| 2.5.5 | ロックアップ .....                           | 49 |

| 2.6   | 電源管理 .....                             | 49 |

| 2.6.1 | SLEEP モードへの移行 .....                    | 50 |

| 2.6.2 | SLEEP モードからのウェイクアップ .....              | 50 |

| 2.6.3 | 外部イベント入力 .....                         | 51 |

| 2.6.4 | 電源管理に関するプログラミングのヒント .....              | 51 |

| 3     | Cortex-M7 命令セット .....                  | 52 |

| 3.1   | 命令セットの概要 .....                         | 52 |

| 3.1.1 | 他の Cortex プロセッサとのバイナリ互換性 .....         | 60 |

| 3.2   | CMSIS 関数 .....                         | 61 |

| 3.3   | 命令の説明について .....                        | 62 |

| 3.3.1 | オペランド .....                            | 62 |

| 3.3.2 | PC または SP を使用した場合の制限事項 .....           | 63 |

| 3.3.3 | フレキシブル第 2 オペランド .....                  | 63 |

| 3.3.4 | シフト演算 .....                            | 64 |

| 3.3.5 | アドレスのアライメント .....                      | 67 |

| 3.3.6 | PC 相対式 .....                           | 67 |

| 3.3.7 | 条件付き実行 .....                           | 68 |

| 3.3.8 | 命令の幅の選択 .....                          | 70 |

| 3.4   | メモリ・アクセス命令 .....                       | 71 |

| 3.4.1 | ADR .....                              | 72 |

| 3.4.2 | LDR と STR (イミディエート・オフセット) .....        | 72 |

| 3.4.3 | LDR と STR (レジスタ・オフセット) .....           | 75 |

| 3.4.4 | LDR と STR (非特権) .....                  | 76 |

| 3.4.5 | LDR (PC 相対) .....                      | 77 |

| 3.4.6 | LDM と STM .....                        | 78 |

| 3.4.7 | PLD .....                              | 80 |

| 3.4.8 | PUSH と POP .....                       | 81 |

|        |                                |     |

|--------|--------------------------------|-----|

| 3.4.9  | LDREX と STREX .....            | 82  |

| 3.4.10 | CLREX .....                    | 83  |

| 3.5    | 汎用データ処理命令 .....                | 84  |

| 3.5.1  | ADD、ADC、SUB、SBC、および RSB .....  | 86  |

| 3.5.2  | AND、ORR、EOR、BIC、および ORN .....  | 88  |

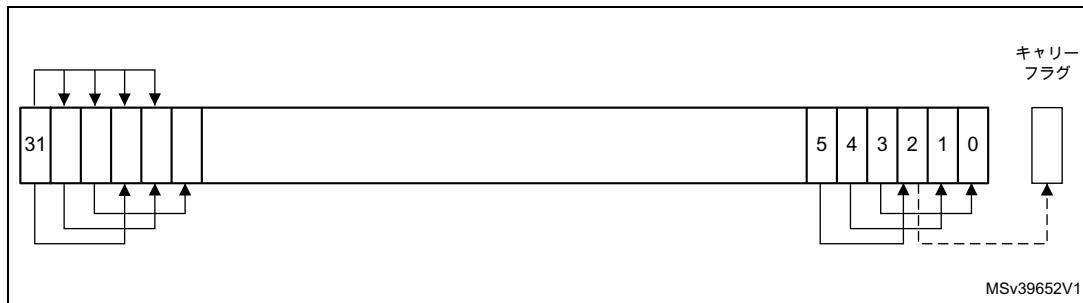

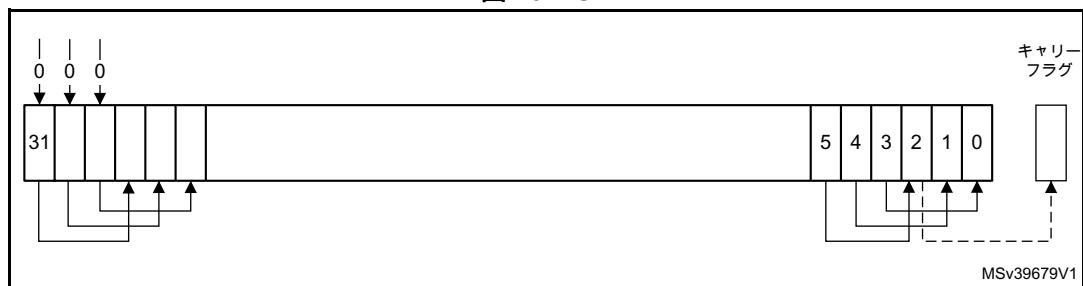

| 3.5.3  | ASR、LSL、LSR、ROR、および RRX .....  | 89  |

| 3.5.4  | CLZ .....                      | 90  |

| 3.5.5  | CMP および CMN .....              | 91  |

| 3.5.6  | MOV および MVN .....              | 92  |

| 3.5.7  | MOVT .....                     | 93  |

| 3.5.8  | REV、REV16、REVSH、および RBIT ..... | 94  |

| 3.5.9  | SADD16 および SADD8 .....         | 95  |

| 3.5.10 | SHADD16 および SHADD8 .....       | 96  |

| 3.5.11 | SHASX および SHSAX .....          | 97  |

| 3.5.12 | SHSUB16 および SHSUB8 .....       | 98  |

| 3.5.13 | SSUB16 および SSUB8 .....         | 99  |

| 3.5.14 | SASX および SSAX .....            | 100 |

| 3.5.15 | TST および TEQ .....              | 101 |

| 3.5.16 | UADD16 および UADD8 .....         | 102 |

| 3.5.17 | UASX および USAX .....            | 103 |

| 3.5.18 | UHADD16 および UHADD8 .....       | 104 |

| 3.5.19 | UHASX および UHSAX .....          | 105 |

| 3.5.20 | UHSUB16 および UHSUB8 .....       | 106 |

| 3.5.21 | SEL .....                      | 107 |

| 3.5.22 | USAD8 .....                    | 107 |

| 3.5.23 | USADA8 .....                   | 108 |

| 3.5.24 | USUB16 および USUB8 .....         | 109 |

| 3.6    | 乗算および除算命令 .....                | 110 |

| 3.6.1  | MUL、MLA、および MLS .....          | 111 |

| 3.6.2  | UMULL、UMAAL、UMLAL .....        | 112 |

| 3.6.3  | SMLA および SMLAW .....           | 113 |

| 3.6.4  | SMLAD .....                    | 114 |

| 3.6.5  | SMLAL および SMLALD .....         | 115 |

| 3.6.6  | SMLSD および SMLSID .....         | 117 |

| 3.6.7  | SMMLA および SMMLS .....          | 119 |

| 3.6.8  | SMMUL .....                    | 120 |

| 3.6.9  | SMUAD および SMUSD .....          | 121 |

|         |                                   |     |

|---------|-----------------------------------|-----|

| 3.6.10  | SMUL および SMULW .....              | 122 |

| 3.6.11  | UMULL、UMLAL、SMULL および SMLAL ..... | 124 |

| 3.6.12  | SDIV および UDIV .....               | 125 |

| 3.7     | 飽和命令 .....                        | 126 |

| 3.7.1   | SSAT および USAT .....               | 127 |

| 3.7.2   | SSAT16 および USAT16 .....           | 128 |

| 3.7.3   | QADD および QSUB .....               | 129 |

| 3.7.4   | QASX および QSAX .....               | 130 |

| 3.7.5   | QDADD および QDSUB .....             | 131 |

| 3.7.6   | UQASX および UQSAX .....             | 132 |

| 3.7.7   | UQADD および UQSUB .....             | 133 |

| 3.8     | パック命令と展開命令 .....                  | 134 |

| 3.8.1   | PKHBT および PKHTB .....             | 135 |

| 3.8.2   | SXT および UXT .....                 | 136 |

| 3.8.3   | SXTA および UXTA .....               | 137 |

| 3.9     | ビット・フィールドの命令 .....                | 138 |

| 3.9.1   | BFC および BFI .....                 | 139 |

| 3.9.2   | SBFX および UBFX .....               | 140 |

| 3.9.3   | SXT および UXT .....                 | 141 |

| 3.10    | 分岐命令と制御命令 .....                   | 142 |

| 3.10.1  | B、BL、BX、および BLX .....             | 142 |

| 3.10.2  | CBZ および CBNZ .....                | 144 |

| 3.10.3  | IT .....                          | 145 |

| 3.10.4  | TBB および TBH .....                 | 147 |

| 3.11    | 浮動小数点命令 .....                     | 148 |

| 3.11.1  | VABS .....                        | 150 |

| 3.11.2  | VADD .....                        | 150 |

| 3.11.3  | VCMP、VCMPE .....                  | 151 |

| 3.11.4  | VCVT、VCVTR（浮動小数点数と整数間） .....      | 152 |

| 3.11.5  | VCVT（浮動小数点数と固定小数点間） .....         | 153 |

| 3.11.6  | VCVTB、VCVTT .....                 | 154 |

| 3.11.7  | VDIV .....                        | 154 |

| 3.11.8  | VFMA、VFMS .....                   | 155 |

| 3.11.9  | VFNMA、VFNMS .....                 | 156 |

| 3.11.10 | VLDM .....                        | 156 |

| 3.11.11 | VLDR .....                        | 157 |

|         |                                              |     |

|---------|----------------------------------------------|-----|

| 3.11.12 | VMLA、VMLS .....                              | 158 |

| 3.11.13 | VMOV (イミディエート) .....                         | 159 |

| 3.11.14 | VMOV レジスタ .....                              | 159 |

| 3.11.15 | VMOV (スカラから Arm コア・レジスタへ) .....              | 160 |

| 3.11.16 | VMOV (Arm コア・レジスタと単精度レジスタの間) .....           | 160 |

| 3.11.17 | VMOV (2 つの Arm コア・レジスタと 2 つの単精度レジスタの間) ..... | 161 |

| 3.11.18 | VMOV (2 つの Arm コア・レジスタと 1 つの倍精度レジスタ) .....   | 161 |

| 3.11.19 | VMOV (Arm コア・レジスタからスカラへ) .....               | 162 |

| 3.11.20 | VMRS .....                                   | 162 |

| 3.11.21 | VMSR .....                                   | 163 |

| 3.11.22 | VMUL .....                                   | 163 |

| 3.11.23 | VNEG .....                                   | 164 |

| 3.11.24 | VNMLA、VNMLS、VNMUL .....                      | 164 |

| 3.11.25 | VPOP .....                                   | 165 |

| 3.11.26 | VPUSH .....                                  | 166 |

| 3.11.27 | VSQRT .....                                  | 166 |

| 3.11.28 | VSTM .....                                   | 167 |

| 3.11.29 | VSTR .....                                   | 167 |

| 3.11.30 | VSUB .....                                   | 168 |

| 3.11.31 | VSEL .....                                   | 169 |

| 3.11.32 | VMAXNM、VMINNM .....                          | 169 |

| 3.11.33 | VCVTA、VCVTN、VCVTP、VCVTM .....                | 170 |

| 3.11.34 | VRINTR、VRINTX .....                          | 170 |

| 3.11.35 | VRINTA、VRINTN、VRINTP、VRINTM、VRINTZ .....     | 171 |

| 3.12    | その他の命令 .....                                 | 172 |

| 3.12.1  | BKPT .....                                   | 172 |

| 3.12.2  | CPS .....                                    | 173 |

| 3.12.3  | DMB .....                                    | 174 |

| 3.12.4  | DSB .....                                    | 174 |

| 3.12.5  | ISB .....                                    | 175 |

| 3.12.6  | MRS .....                                    | 175 |

| 3.12.7  | MSR .....                                    | 176 |

| 3.12.8  | NOP .....                                    | 177 |

| 3.12.9  | SEV .....                                    | 177 |

| 3.12.10 | SVC .....                                    | 178 |

| 3.12.11 | WFE .....                                    | 178 |

| 3.12.12 | WFI .....                                    | 179 |

|          |                                              |            |

|----------|----------------------------------------------|------------|

| <b>4</b> | <b>Cortex-M7 ペリフェラル .....</b>                | <b>180</b> |

| 4.1      | Cortex-M7 ペリフェラルについて .....                   | 180        |

| 4.2      | ネスト化されたベクタ割込みコントローラ .....                    | 181        |

| 4.2.1    | CMSIS を使用した Cortex®-M7 NVIC レジスタへのアクセス ..... | 182        |

| 4.2.2    | 割込みセット・イネーブル・レジスタ .....                      | 182        |

| 4.2.3    | 割込みクリア・イネーブル・レジスタ .....                      | 183        |

| 4.2.4    | 割込みセット・ペンディング・レジスタ .....                     | 183        |

| 4.2.5    | 割込みクリア・ペンディング・レジスタ .....                     | 184        |

| 4.2.6    | 割込みアクティブ・ビット・レジスタ .....                      | 185        |

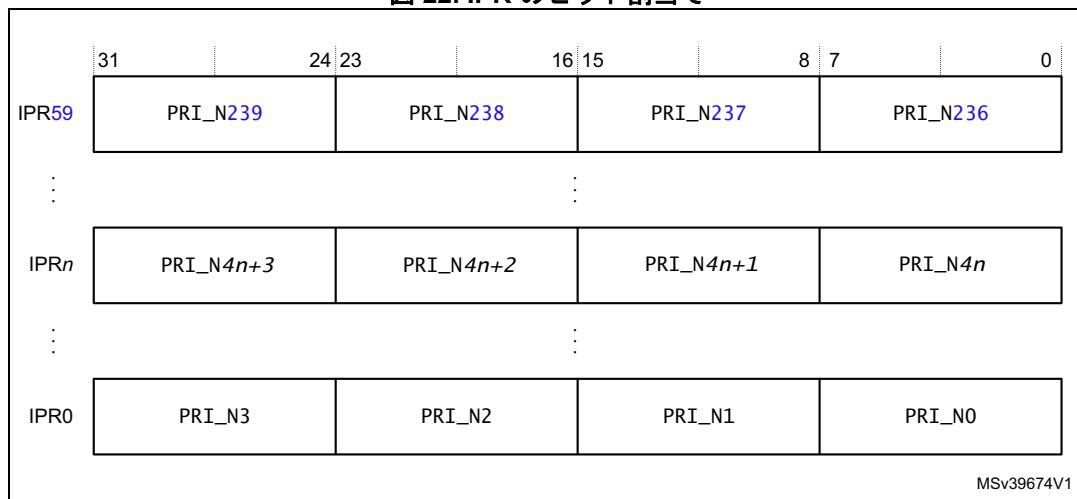

| 4.2.7    | 割込み優先度レジスタ .....                             | 185        |

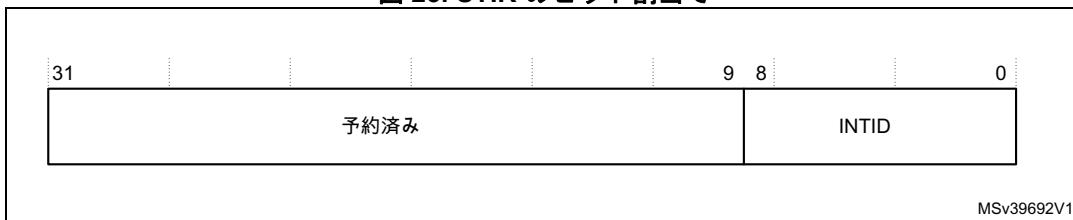

| 4.2.8    | ソフトウェア・トリガ割込みレジスタ .....                      | 186        |

| 4.2.9    | レベル割込みとパルス割込み .....                          | 187        |

| 4.2.10   | NVIC 設計のヒントとコツ .....                         | 188        |

| 4.3      | システム制御ブロック .....                             | 189        |

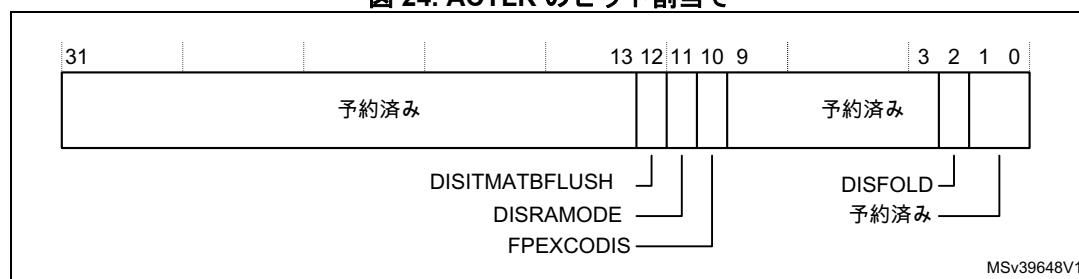

| 4.3.1    | 補助制御レジスタ .....                               | 190        |

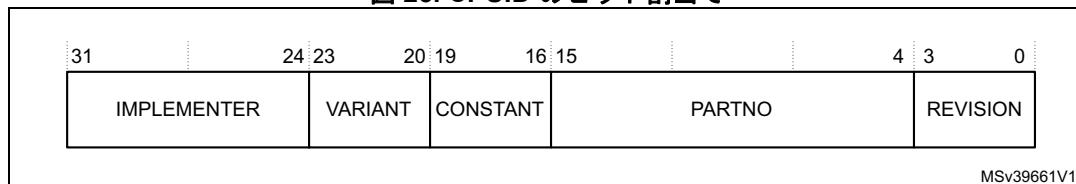

| 4.3.2    | CPUID ベース・レジスタ .....                         | 191        |

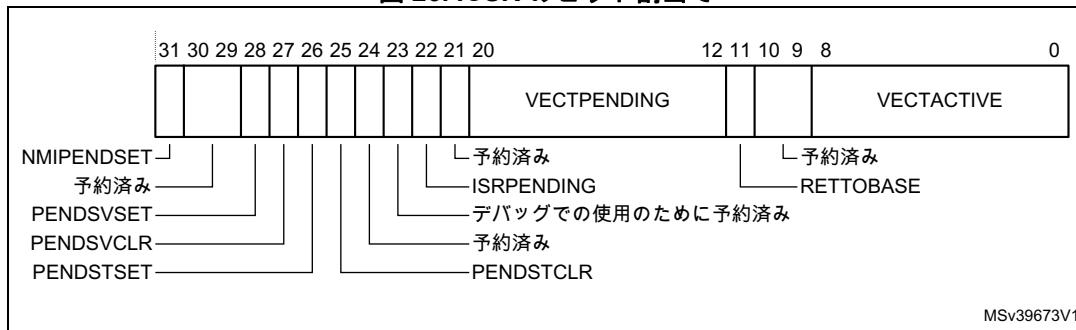

| 4.3.3    | 割込み制御およびステート・レジスタ .....                      | 191        |

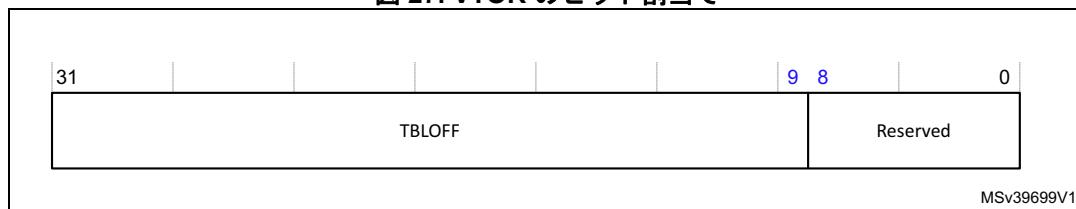

| 4.3.4    | ベクタ・テーブル・オフセット・レジスタ .....                    | 194        |

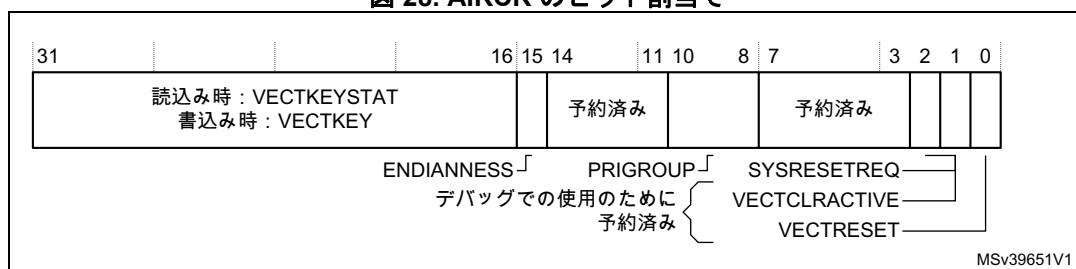

| 4.3.5    | アプリケーション割込みおよびリセット制御レジスタ .....               | 194        |

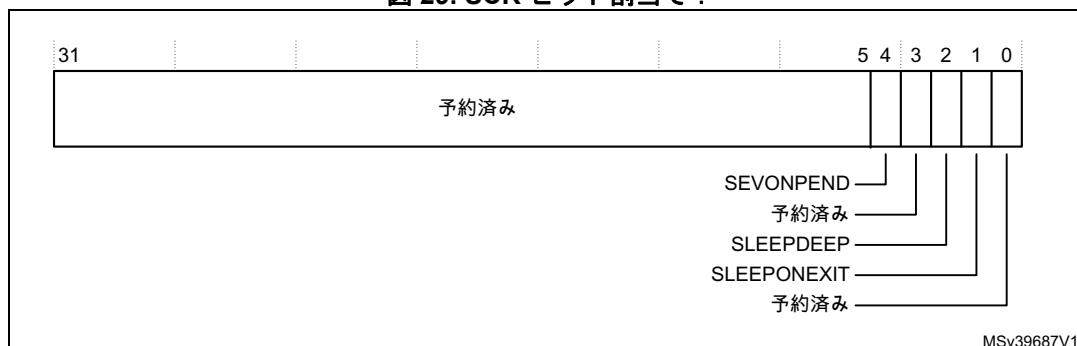

| 4.3.6    | システム制御レジスタ .....                             | 196        |

| 4.3.7    | 設定および制御レジスタ .....                            | 197        |

| 4.3.8    | システム・ハンドラ優先度レジスタ .....                       | 199        |

| 4.3.9    | システム・ハンドラ制御およびステート・レジスタ .....                | 201        |

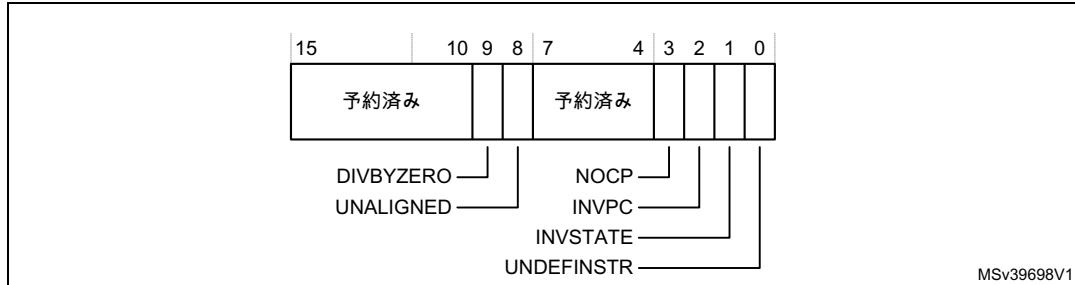

| 4.3.10   | 設定可能なフォールト・ステータス・レジスタ .....                  | 202        |

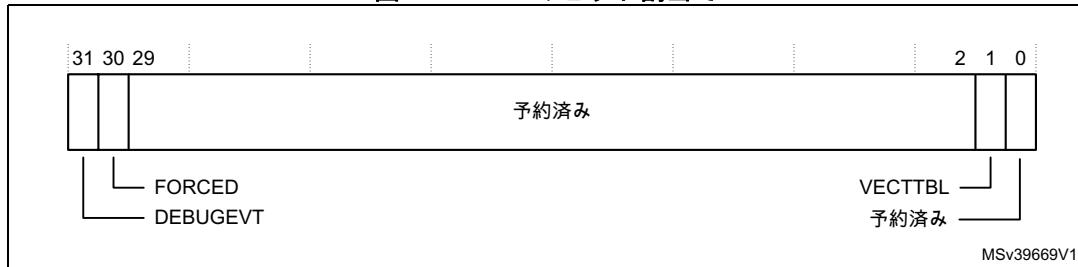

| 4.3.11   | ハード・フォールト・ステータス・レジスタ .....                   | 207        |

| 4.3.12   | メモリ管理フォールト・アドレス・レジスタ .....                   | 208        |

| 4.3.13   | バス・フォールト・アドレス・レジスタ .....                     | 209        |

| 4.3.14   | システム制御ブロック設計のヒントとコツ .....                    | 209        |

| 4.4      | システム・タイマ、SysTick .....                       | 210        |

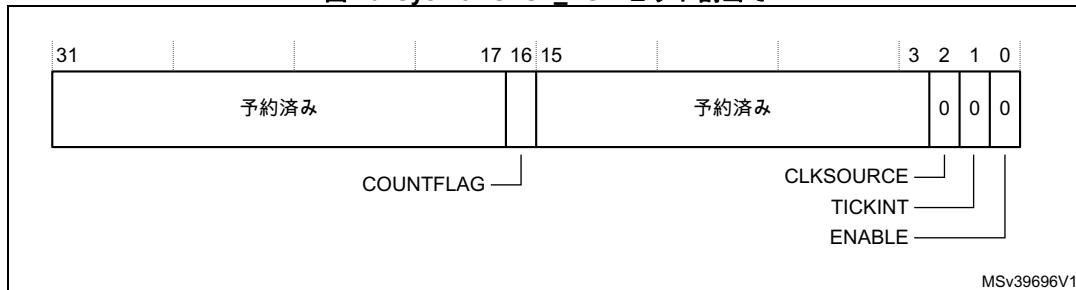

| 4.4.1    | SysTick 制御およびステータス・レジスタ .....                | 210        |

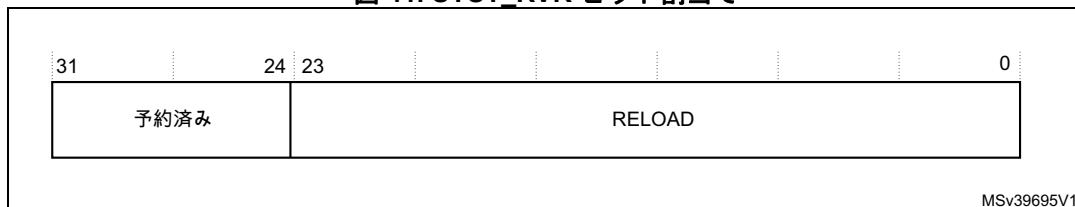

| 4.4.2    | SysTick RELOAD 値レジスタ .....                   | 211        |

| 4.4.3    | SysTick 現在値レジスタ .....                        | 212        |

| 4.4.4    | SysTick 較正值レジスタ .....                        | 212        |

| 4.4.5    | SysTick 設計のヒントとコツ .....                      | 213        |

| 4.5      | プロセッサの機能 .....                               | 214        |

| 4.5.1    | キャッシュ・レベル ID レジスタ .....                      | 214        |

|       |                                             |     |

|-------|---------------------------------------------|-----|

| 4.5.2 | キャッシュ・タイプ・レジスタ .....                        | 215 |

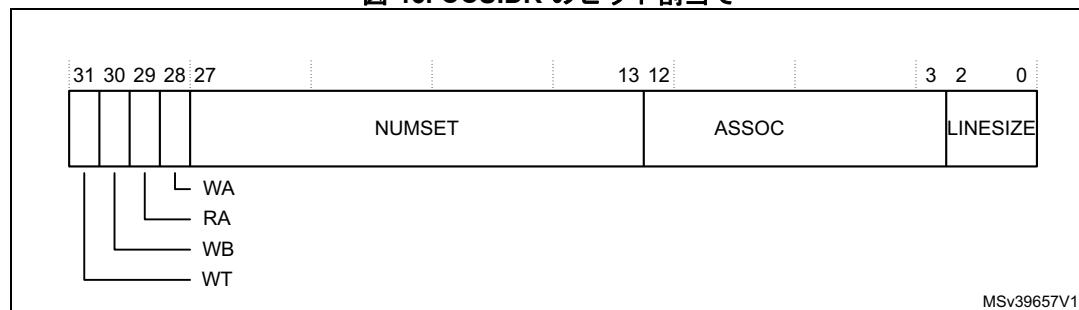

| 4.5.3 | キャッシュ・サイズ ID レジスタ .....                     | 216 |

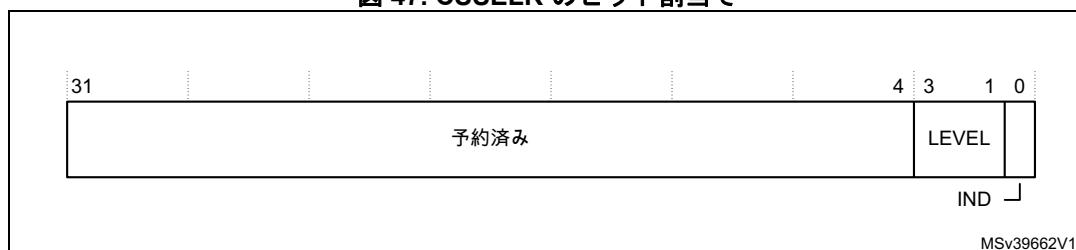

| 4.5.4 | キャッシュ・サイズ選択レジスタ .....                       | 217 |

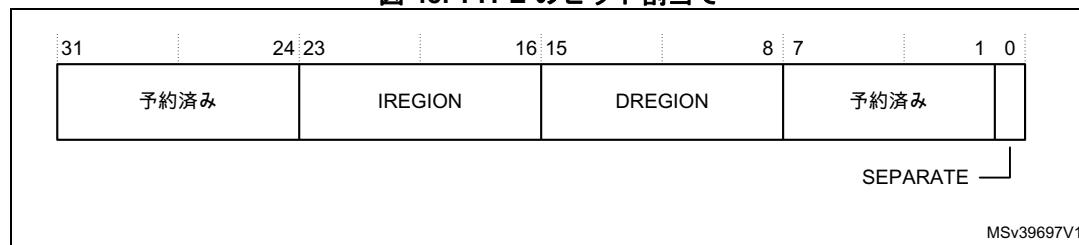

| 4.6   | メモリ保護ユニット .....                             | 218 |

| 4.6.1 | MPU タイプ・レジスタ .....                          | 220 |

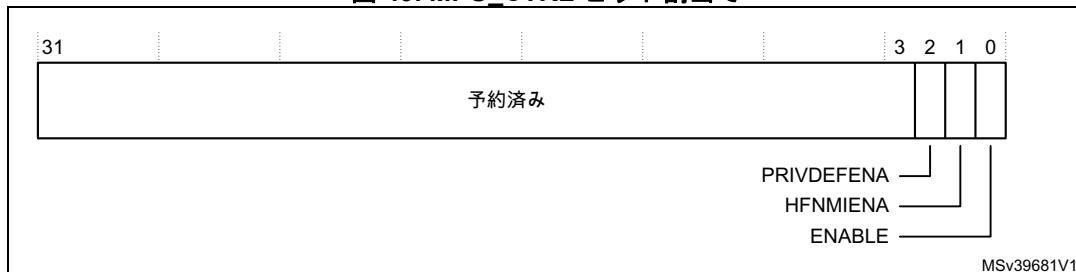

| 4.6.2 | MPU 制御レジスタ .....                            | 220 |

| 4.6.3 | MPU 領域番号レジスタ .....                          | 222 |

| 4.6.4 | MPU 領域ベース・アドレス・レジスタ .....                   | 222 |

| 4.6.5 | MPU 領域属性およびサイズ・レジスタ .....                   | 223 |

| 4.6.6 | MPU アクセス許可属性 .....                          | 225 |

| 4.6.7 | MPU の不一致 .....                              | 226 |

| 4.6.8 | MPU 領域の更新 .....                             | 226 |

| 4.6.9 | MPU 設計のヒントとコツ .....                         | 228 |

| 4.7   | 浮動小数点ユニット .....                             | 229 |

| 4.7.1 | コプロセッサ・アクセス制御レジスタ .....                     | 230 |

| 4.7.2 | 浮動小数点コンテキスト制御レジスタ .....                     | 230 |

| 4.7.3 | 浮動小数点コンテキスト・アドレス・レジスタ .....                 | 232 |

| 4.7.4 | 浮動小数点ステータス制御レジスタ .....                      | 232 |

| 4.7.5 | 浮動小数点デフォルト・ステータス制御レジスタ .....                | 234 |

| 4.7.6 | FPU の有効化 .....                              | 234 |

| 4.7.7 | FPU 例外割込みの有効化とクリア .....                     | 235 |

| 4.8   | キャッシュのメンテナンス操作 .....                        | 236 |

| 4.8.1 | フル命令キャッシュ操作 .....                           | 237 |

| 4.8.2 | アドレスによる命令およびデータ・キャッシュ操作 .....               | 237 |

| 4.8.3 | セットウェイによるデータ・キャッシュ操作 .....                  | 237 |

| 4.8.4 | CMSIS を使用した Cortex®-M7 キャッシュのメンテナンス操作 ..... | 238 |

| 4.8.5 | L1 キャッシュの初期化と有効化 .....                      | 238 |

| 4.8.6 | フォールト処理の考慮事項 .....                          | 240 |

| 4.8.7 | キャッシュ・メンテナンスの設計のヒントとコツ .....                | 240 |

| 4.9   | アクセス制御 .....                                | 241 |

| 4.9.1 | 命令およびデータ密結合メモリの制御レジスタ .....                 | 242 |

| 4.9.2 | AHBP 制御レジスタ .....                           | 244 |

| 4.9.3 | 補助キャッシュ制御レジスタ .....                         | 245 |

| 4.9.4 | AHB スレーブ制御レジスタ .....                        | 246 |

| 4.9.5 | 補助バス・フォールト・ステータス・レジスター .....                | 247 |

| 5     | 改版履歴 .....                                  | 249 |

# 表の一覧

|       |                                               |     |

|-------|-----------------------------------------------|-----|

| 表 1.  | プロセッサ・モード、実行特権レベル、スタックの使用オプションの概要 .....       | 20  |

| 表 2.  | コア・レジスタ・セットの概要 .....                          | 20  |

| 表 3.  | PSR レジスタの組合せ .....                            | 22  |

| 表 4.  | APSR のビット割当て .....                            | 23  |

| 表 5.  | IPSR のビット割当て .....                            | 23  |

| 表 6.  | EPSR のビット割当て .....                            | 24  |

| 表 7.  | PRIMASK レジスタのビット割り当て .....                    | 25  |

| 表 8.  | FAULTMASK レジスタのビット割り当て .....                  | 26  |

| 表 9.  | BASEPRI レジスタのビット割り当て .....                    | 26  |

| 表 10. | コントロール レジスタのビット割り当て .....                     | 27  |

| 表 11. | STM32F746xx/STM32F756xx Cortex®-M7 の構成 .....  | 30  |

| 表 12. | STM32F76xxx/STM32F77xxx Cortex®-M7 の構成 .....  | 30  |

| 表 13. | STM32F72xxx/STM32F73xxx Cortex®-M7 の構成 .....  | 31  |

| 表 14. | STM32H7 シリーズ Cortex®-M7 の構成 .....             | 31  |

| 表 15. | メモリ・アクセスの順序 .....                             | 33  |

| 表 16. | メモリ・アクセスの動作 .....                             | 34  |

| 表 17. | メモリ領域の共有可能性とキャッシングのポリシー .....                 | 35  |

| 表 18. | 排他アクセス命令のための CMSIS 関数 .....                   | 38  |

| 表 19. | さまざまな例外タイプのプロパティ .....                        | 40  |

| 表 20. | 例外からの復帰動作 .....                               | 46  |

| 表 21. | フォールト .....                                   | 47  |

| 表 22. | フォールト・ステータス・レジスタとフォールト・アドレス・レジスタ .....        | 49  |

| 表 23. | Cortex®-M7 命令 .....                           | 52  |

| 表 24. | 一部の Cortex®-M7 プロセッサ命令を生成するための CMSIS 関数 ..... | 61  |

| 表 25. | 特殊レジスタにアクセスするための CMSIS 関数 .....               | 62  |

| 表 26. | 条件コードの接尾文字 .....                              | 69  |

| 表 27. | メモリ・アクセス命令 .....                              | 71  |

| 表 28. | オフセット範囲 .....                                 | 74  |

| 表 29. | オフセット範囲 .....                                 | 78  |

| 表 30. | データ処理命令 .....                                 | 84  |

| 表 31. | 乗算および除算命令 .....                               | 110 |

| 表 32. | 飽和命令 .....                                    | 126 |

| 表 33. | パック命令と展開命令 .....                              | 134 |

| 表 34. | パック命令と展開命令 .....                              | 138 |

| 表 35. | 分岐命令と制御命令 .....                               | 142 |

| 表 36. | 分岐範囲 .....                                    | 143 |

| 表 37. | 浮動小数点命令 .....                                 | 148 |

| 表 38. | その他の命令 .....                                  | 172 |

| 表 39. | コア・ペリフェラルのレジスタ領域 .....                        | 180 |

| 表 40. | NVIC レジスタの概要 .....                            | 181 |

| 表 41. | CMSIS の NVIC アクセス関数 .....                     | 182 |

| 表 42. | ISER ビット割り当て .....                            | 182 |

| 表 43. | ICER ビット割り当て .....                            | 183 |

| 表 44. | ISPR ビット割り当て .....                            | 184 |

| 表 45. | ICPR ビット割り当て .....                            | 184 |

| 表 46. | IABR のビット割り当て .....                           | 185 |

| 表 47. | IPR ビット割り当て .....                             | 186 |

| 表 48. | STIR ビット割り当て .....                            | 186 |

| 表 49. | CMSIS NVIC 制御関数 .....                         | 188 |

|        |                                 |     |

|--------|---------------------------------|-----|

| 表 50.  | システム制御ブロックのレジスタの概要 .....        | 189 |

| 表 51.  | ACTLR ビット割当て .....              | 190 |

| 表 52.  | CPUID ビット割当て .....              | 191 |

| 表 53.  | ICSR のビット割当て .....              | 192 |

| 表 54.  | VTOR ビット割当て .....               | 194 |

| 表 55.  | AIRCR のビット割当て .....             | 195 |

| 表 56.  | 優先度のグループ化 .....                 | 195 |

| 表 57.  | SCR ビット割当て .....                | 196 |

| 表 58.  | CCR ビット割当て .....                | 197 |

| 表 59.  | システム・フォールト・ハンドラ優先度フィールド .....   | 199 |

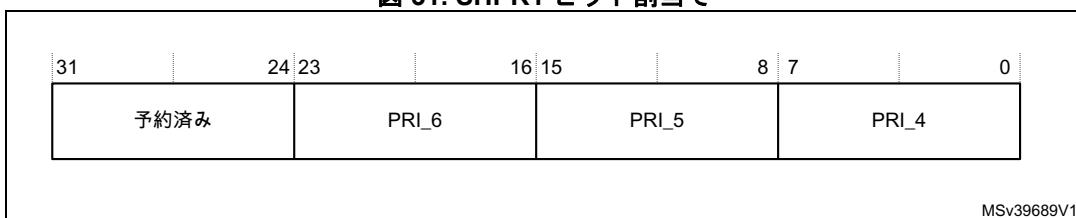

| 表 60.  | SHPR1 レジスタのビット割当て .....         | 200 |

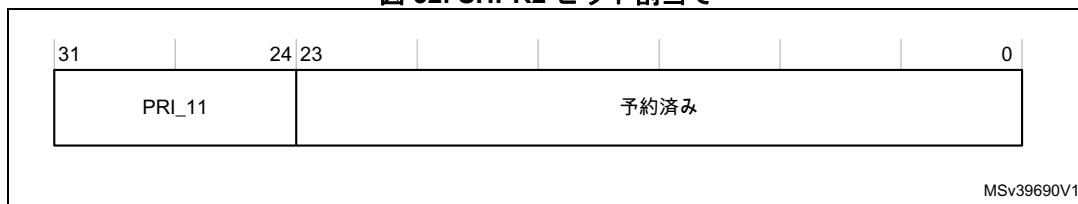

| 表 61.  | SHPR2 レジスタのビット割当て .....         | 200 |

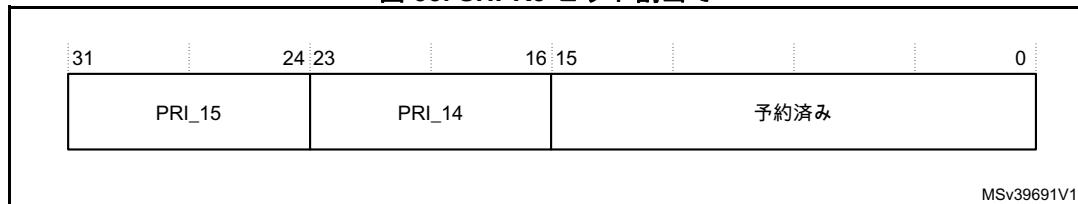

| 表 62.  | SHPR3 レジスタのビット割当て .....         | 200 |

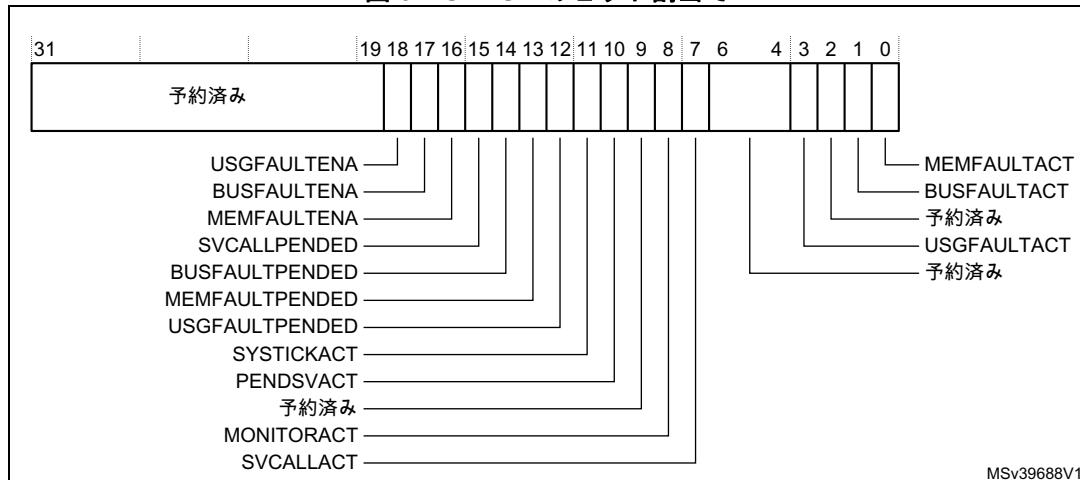

| 表 63.  | SHCSR ビット割当て .....              | 201 |

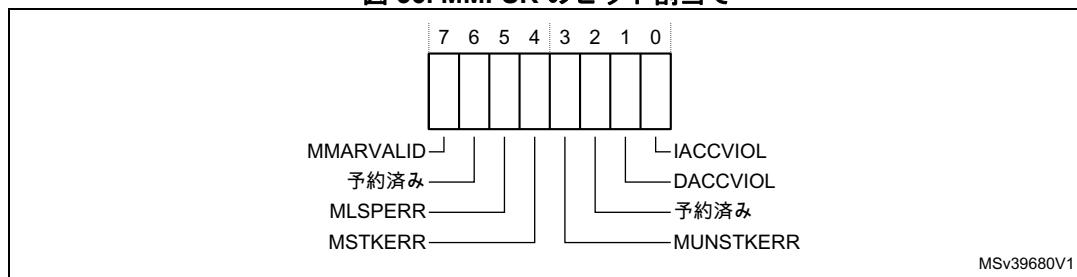

| 表 64.  | MMFSR ビット割当て .....              | 203 |

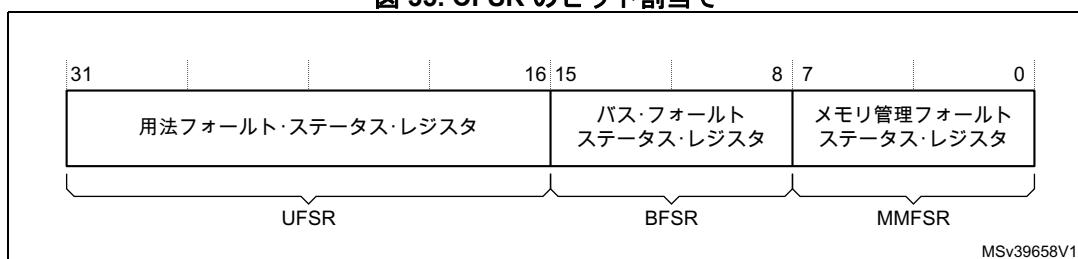

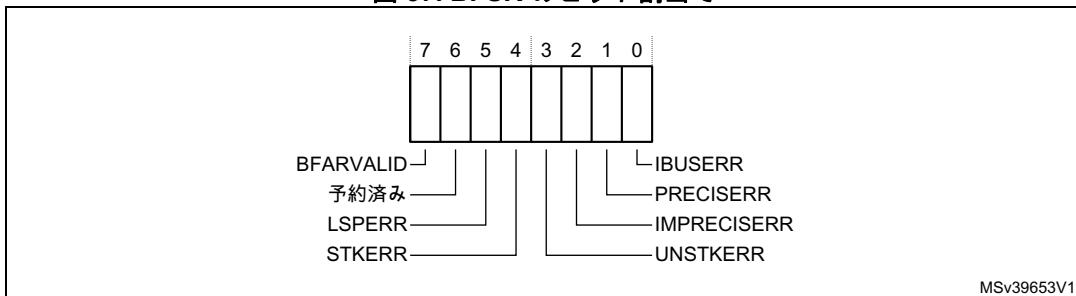

| 表 65.  | BFSR ビット割当て .....               | 204 |

| 表 66.  | UFSR ビット割当て .....               | 206 |

| 表 67.  | HFSR ビット割当て .....               | 207 |

| 表 68.  | MMFAR ビット割当て .....              | 208 |

| 表 69.  | BFAR ビット割当て .....               | 209 |

| 表 70.  | システム制御のための CMSIS 関数 .....       | 209 |

| 表 71.  | システム・タイマのレジスタの概要 .....          | 210 |

| 表 72.  | SysTick SYST_CSR ビット割当て .....   | 210 |

| 表 73.  | SYST_RVR ビット割当て .....           | 211 |

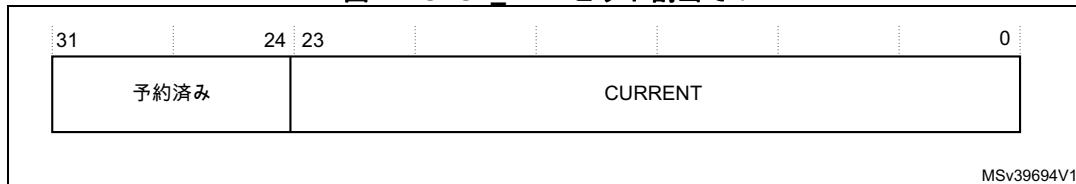

| 表 74.  | SYST_CVR ビット割当て .....           | 212 |

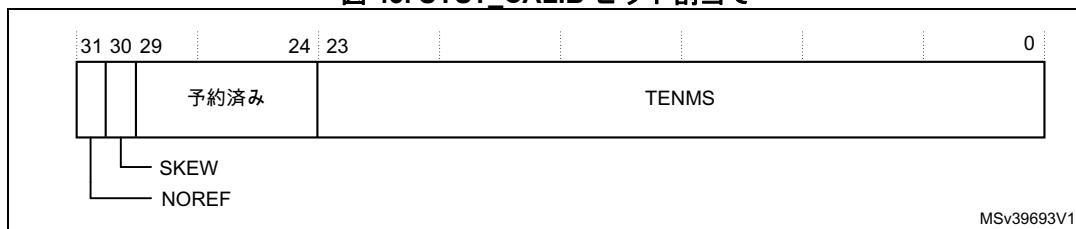

| 表 75.  | SYST_CALIB ビット割当て .....         | 212 |

| 表 76.  | SysTick 制御のための CMSIS 関数 .....   | 213 |

| 表 77.  | 識別スペースの概要 .....                 | 214 |

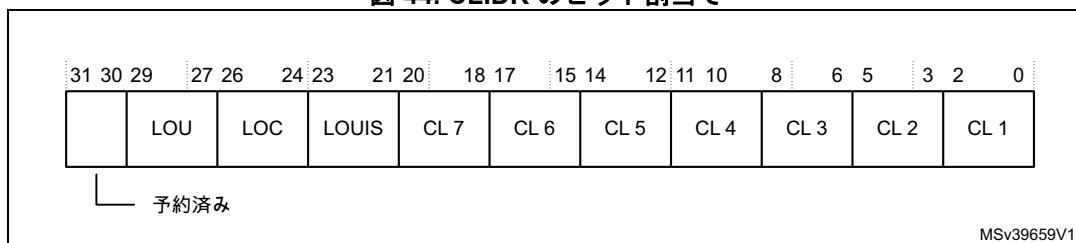

| 表 78.  | CLIDR ビット割当て .....              | 214 |

| 表 79.  | CTR ビット割当て .....                | 215 |

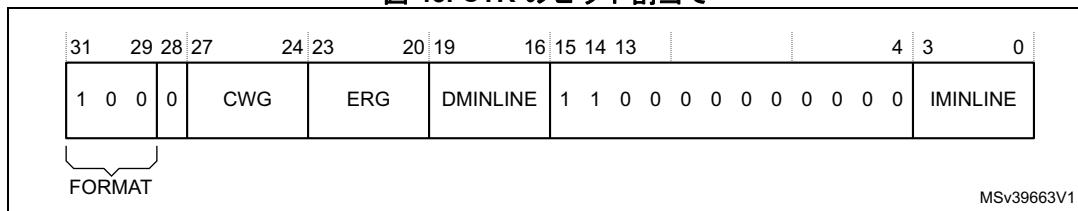

| 表 80.  | CCSIDR ビット割当て .....             | 216 |

| 表 81.  | CCSIDR エンコード .....              | 217 |

| 表 82.  | CSSELR ビット割当て .....             | 217 |

| 表 83.  | メモリ属性の概要 .....                  | 218 |

| 表 84.  | MPU レジスタの概要 .....               | 219 |

| 表 85.  | TYPE のビット割当て .....              | 220 |

| 表 86.  | MPU_CTRL ビット割当て .....           | 221 |

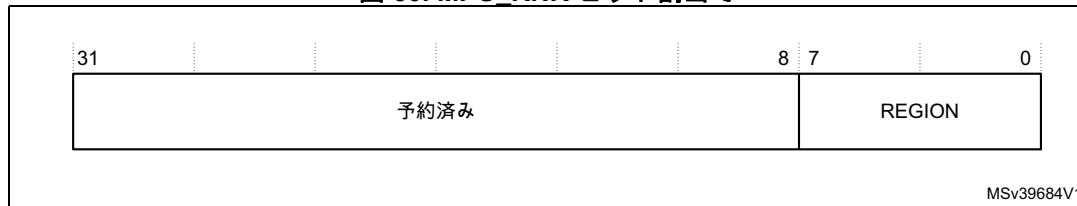

| 表 87.  | MPU_RNR ビット割当て .....            | 222 |

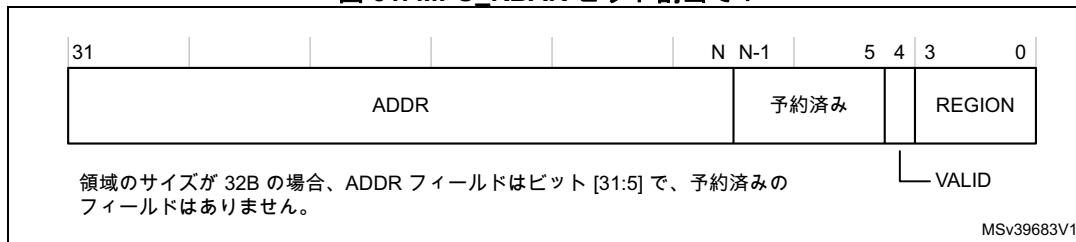

| 表 88.  | MPU_RBAR ビット割当て .....           | 223 |

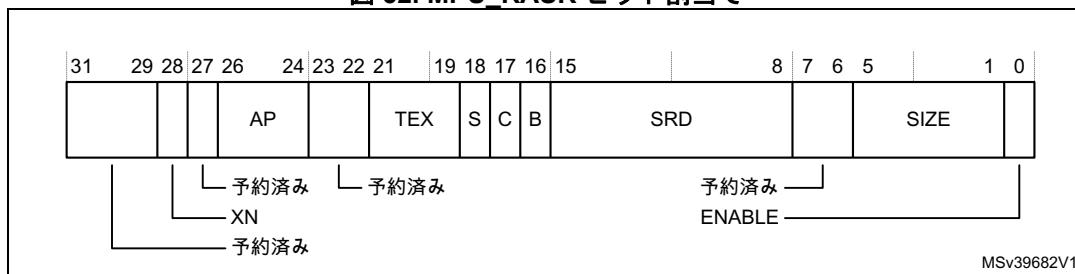

| 表 89.  | MPU_RASR ビット割当て .....           | 224 |

| 表 90.  | SIZE フィールドの値の例 .....            | 224 |

| 表 91.  | TEX、C、B、S のエンコード .....          | 225 |

| 表 92.  | メモリ属性エンコードのキャッシュ・ポリシー .....     | 226 |

| 表 93.  | AP エンコード .....                  | 226 |

| 表 94.  | Cortex®-M7 浮動小数点システム・レジスタ ..... | 229 |

| 表 95.  | CPACR ビット割当て .....              | 230 |

| 表 96.  | FPCCR ビット割当て .....              | 231 |

| 表 97.  | FPCAR ビット割当て .....              | 232 |

| 表 98.  | FPSCR ビット割当て .....              | 232 |

| 表 99.  | FPDSCR ビット割当て .....             | 234 |

| 表 100. | キャッシュ・メンテナンス空間レジスタの概要 .....     | 236 |

| 表 101. | キャッシュ操作レジスタのビット割当て .....        | 237 |

---

|        |                                 |     |

|--------|---------------------------------|-----|

| 表 102. | セットウェイ・ビット割当てによるキャッシュ操作 .....   | 237 |

| 表 103. | CMSIS アクセス・キャッシュのメンテナンス操作 ..... | 238 |

| 表 104. | アクセス制御レジスタの概要 .....             | 241 |

| 表 105. | ITCMCR および DTCMCR のビット割当て ..... | 242 |

| 表 106. | AHBPCR ビット割当て .....             | 244 |

| 表 107. | CACR ビット割当て .....               | 245 |

| 表 108. | AHBSCR ビット割当て .....             | 246 |

| 表 109. | ABFSR ビット割当て .....              | 247 |

| 表 110. | 文書改版履歴 .....                    | 249 |

| 表 111. | 日本語版文書改版履歴 .....                | 249 |

## 図の一覧

|       |                                     |     |

|-------|-------------------------------------|-----|

| 図 1.  | STM32 Cortex®-M7 の実装プロセッサ . . . . . | 16  |

| 図 2.  | プロセッサのコア・レジスタ . . . . .             | 20  |

| 図 3.  | APSR、IPSR、およびEPSR のビット割当て . . . . . | 22  |

| 図 4.  | PRIMASK のビット割当て : . . . . .         | 25  |

| 図 5.  | FAULTMASK のビット割当て . . . . .         | 25  |

| 図 6.  | BASEPRI のビット割当て . . . . .           | 26  |

| 図 7.  | 制御ビット割り当て . . . . .                 | 27  |

| 図 8.  | プロセッサ・メモリ・マップ . . . . .             | 32  |

| 図 9.  | リトルエンディアン形式 . . . . .               | 37  |

| 図 10. | ベクターテーブル . . . . .                  | 42  |

| 図 11. | 例外スタック・フレーム . . . . .               | 45  |

| 図 12. | ASR . . . . .                       | 65  |

| 図 13. | LSR . . . . .                       | 65  |

| 図 14. | LSL . . . . .                       | 66  |

| 図 15. | ROR . . . . .                       | 66  |

| 図 16. | RRX . . . . .                       | 67  |

| 図 17. | ISER のビット割当て . . . . .              | 182 |

| 図 18. | ICER のビット割当て . . . . .              | 183 |

| 図 19. | ISPR のビット割当て . . . . .              | 183 |

| 図 20. | ICPR のビット割当て . . . . .              | 184 |

| 図 21. | IABR のビット割当て . . . . .              | 185 |

| 図 22. | IPR のビット割当て . . . . .               | 185 |

| 図 23. | STIR のビット割当て . . . . .              | 186 |

| 図 24. | ACTLR のビット割当て . . . . .             | 190 |

| 図 25. | CPUID のビット割当て . . . . .             | 191 |

| 図 26. | ICSR のビット割当て . . . . .              | 192 |

| 図 27. | VTOR のビット割当て . . . . .              | 194 |

| 図 28. | AIRCR のビット割当て . . . . .             | 194 |

| 図 29. | SCR ビット割当て : . . . . .              | 196 |

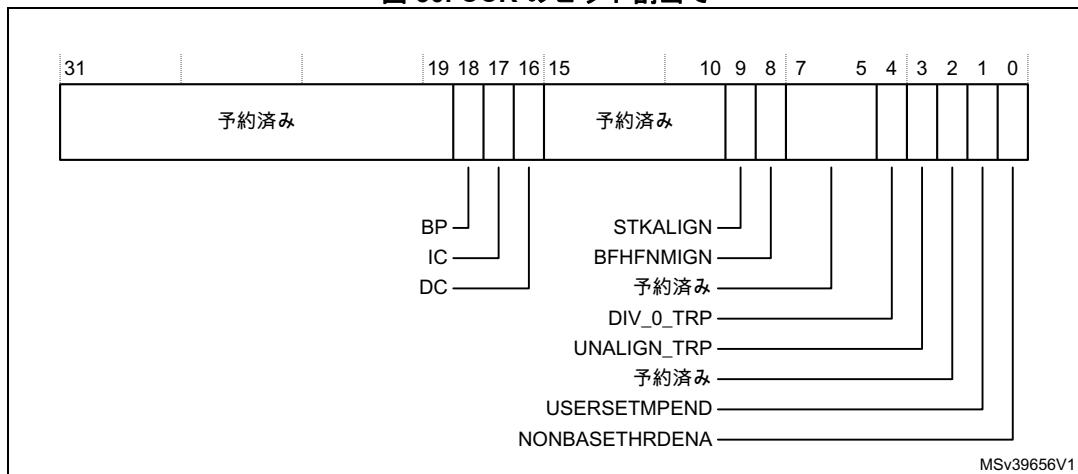

| 図 30. | CCR のビット割当て . . . . .               | 197 |

| 図 31. | SHPR1 ビット割当て . . . . .              | 199 |

| 図 32. | SHPR2 ビット割当て . . . . .              | 200 |

| 図 33. | SHPR3 ビット割当て . . . . .              | 200 |

| 図 34. | SHCSR のビット割当て . . . . .             | 201 |

| 図 35. | CFSR のビット割当て . . . . .              | 202 |

| 図 36. | MMFSR のビット割当て . . . . .             | 203 |

| 図 37. | BFSR のビット割当て . . . . .              | 204 |

| 図 38. | UFSR のビット割当て . . . . .              | 206 |

| 図 39. | HFSR のビット割当て . . . . .              | 207 |

| 図 40. | SysTick SYST_CSR ビット割当て . . . . .   | 210 |

| 図 41. | SYST_RVR ビット割当て . . . . .           | 211 |

| 図 42. | SYST_CVR ビット割当て : . . . . .         | 212 |

| 図 43. | SYST_CALIB ビット割当て . . . . .         | 212 |

| 図 44. | CLIDR のビット割当て . . . . .             | 214 |

| 図 45. | CTR のビット割当て . . . . .               | 215 |

| 図 46. | CCSIDR のビット割当て . . . . .            | 216 |

| 図 47. | CSSELR のビット割当て . . . . .            | 217 |

| 図 48. | TYPE のビット割当て . . . . .              | 220 |

| 図 49. | MPU_CTRL ビット割当て . . . . .           | 221 |

|       |                               |     |

|-------|-------------------------------|-----|

| 図 50. | MPU_RNR ビット割当て .....          | 222 |

| 図 51. | MPU_RBAR ビット割当て .....         | 223 |

| 図 52. | MPU_RASR ビット割当て .....         | 224 |

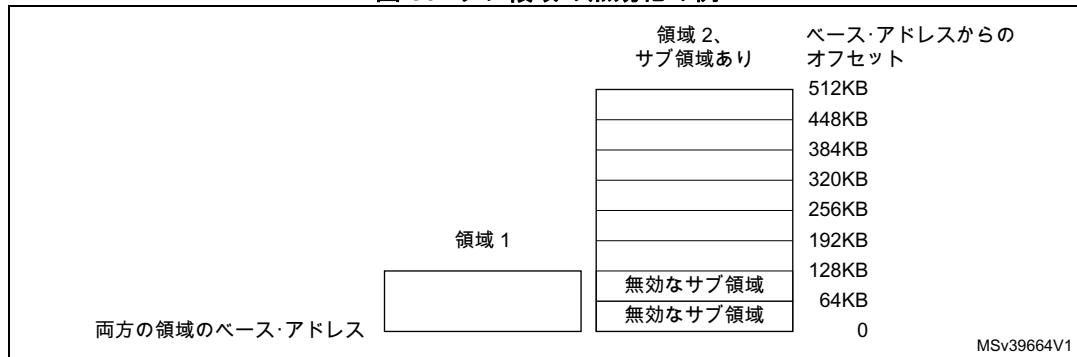

| 図 53. | サブ領域の無効化の例 .....              | 228 |

| 図 54. | CPACR のビット割当て .....           | 230 |

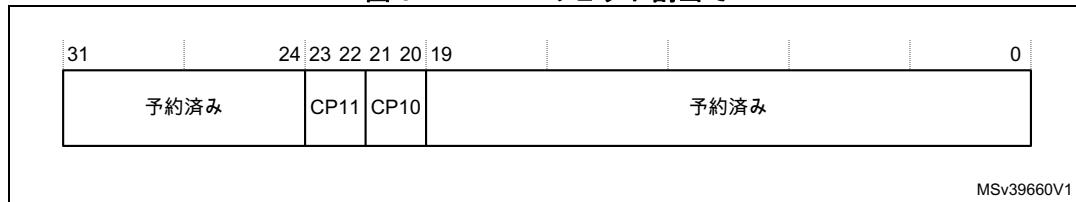

| 図 55. | FPCCR のビット割当て .....           | 230 |

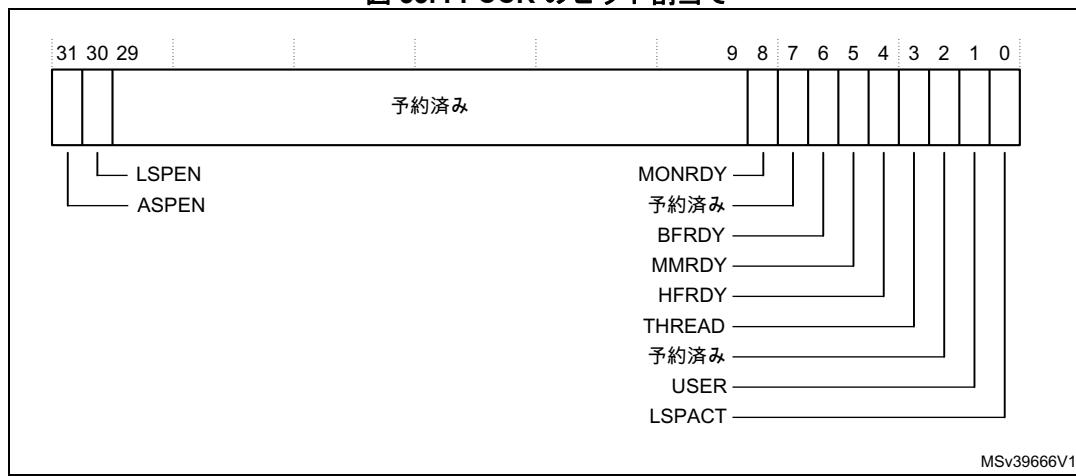

| 図 56. | FPCAR のビット割当て .....           | 232 |

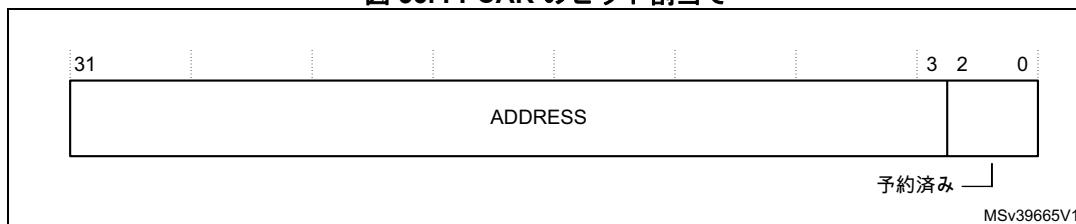

| 図 57. | FPSCR のビット割当て .....           | 232 |

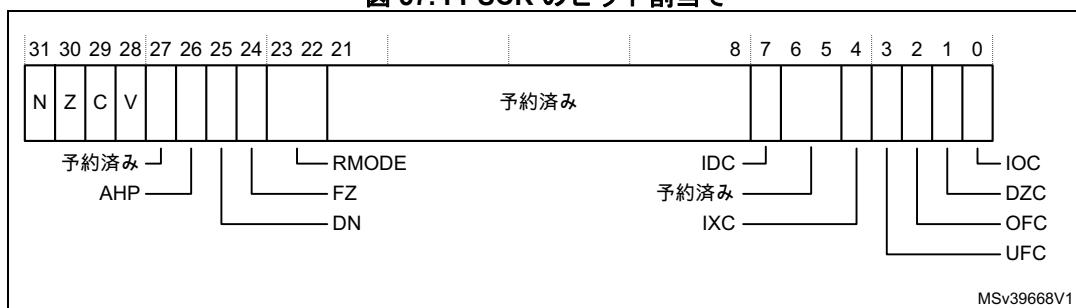

| 図 58. | FPDSCR のビット割当て .....          | 234 |

| 図 59. | キャッシュ操作のビット割当て .....          | 237 |

| 図 60. | ITCMR および DTCMR ビットの割当て ..... | 242 |

| 図 61. | AHBPCR のビット割当て .....          | 244 |

| 図 62. | CACR のビット割当て .....            | 245 |

| 図 63. | AHBSCR のビット割当て .....          | 246 |

| 図 64. | ABFSR ビット割当て .....            | 247 |

# 1 本書について

本書には、アプリケーションおよびシステムレベルのソフトウェアの開発に必要な情報が記載されています。デバッグに関連するコンポーネント、機能、動作についての情報は含まれません。

マイクロコントローラのソフトウェアおよびハードウェアを扱うエンジニアを対象にした資料であり、Arm 製品に対する経験の有無は問いません。

## 1.1 表記規則

本書の表記規則は次のとおりです。

***italic*** 重要な注記を強調したり、特別な用語の説明、内部の相互参照や引用を表示したりします。

****bold**** メニュー名などのユーザ・インターフェース要素の強調に太字を使用します。信号名も太字で示します。適宜、記述リスト内の用語にも使用します。

***monospace*** コマンド、ファイル名、プログラム名、ソース・コードなどキーボードから入力可能なテキストを表します。

**monospace** コマンドやオプションの許容されている略称を表します。コアではフル・コマンドやオプション名の代わりに、下線を引いたテキストを入力することができます。

***monospace italic*** 特定の値に置き換えられる引数は等幅フォントのテキストで表されます。

***monospace bold*** サンプル・コード以外で使用される言語キーワードを示します。

**<および>** コードまたはコード・フラグメント内でアセンブラー構文の置き換えが可能な用語を囲みます。例：

LDRSB<cond> <Rt>, [<Rn>, #<offset>]

## 1.2 レジスタに関する略記

レジスタの説明では、次の略記が使用されます。

|                  |                                                                               |

|------------------|-------------------------------------------------------------------------------|

| 読み出し／書き込み (rw)   | これらのビットは、ソフトウェアによる読み出しと書き込みができます。                                             |

| 読み出し専用 (r)       | これらのビットは、ソフトウェアによる読み出しがみが可能です。                                                |

| 書き込み専用 (w)       | このビットは、ソフトウェアによる書き込みのみが可能です。<br>ビットを読み出すと、リセット値が返されます。                        |

| 読み出し／クリア (rc_w)  | このビットは、ソフトウェアによって読み出すことができるほか、「任意の値」を書き込むことによってクリアすることもできます。                  |

| 読み出し／クリア (rc_w1) | このビットは、ソフトウェアによって読み出すことができ、「1」を書き込むことによってクリアできます。<br>「0」を書き込んでも、ビットの値は変化しません。 |

| 読み出し／クリア (rc_w0) | このビットは、ソフトウェアによって読み出すことができ、「0」を書き込むことによってクリアできます。<br>「1」を書き込んでも、ビットの値は変化しません。 |

| 反転 (t)           | このビットは、ソフトウェアによって「1」を書き込むことで反転だけできます。「0」を書き込んでも、ビットの値は変化しません。                 |

| 予約済み (Res.)      | 予約済みビットであり、リセット値に保持する必要があります。                                                 |

## 1.3 Cortex®-M7 プロセッサおよびコア・ペリフェラルについて

Cortex®-M7 プロセッサは、マイクロコントローラ市場向けに設計された高性能の 32bit プロセッサです。開発者に次のような大きなメリットを提供します。

- 抜群の処理性能と高速な割込み処理の融合。

- 幅広いブレークポイント設定やトレース機能によって強化されたシステム・デバッグ機能。

- 効率的なプロセッサ・コア、システム、およびメモリ。

- 統合された SLEEP モードによる低消費電力。

- プラットフォームに対する、内蔵Memory Protection Unit（メモリ保護ユニット）（MPU）による堅牢なセキュリティ。

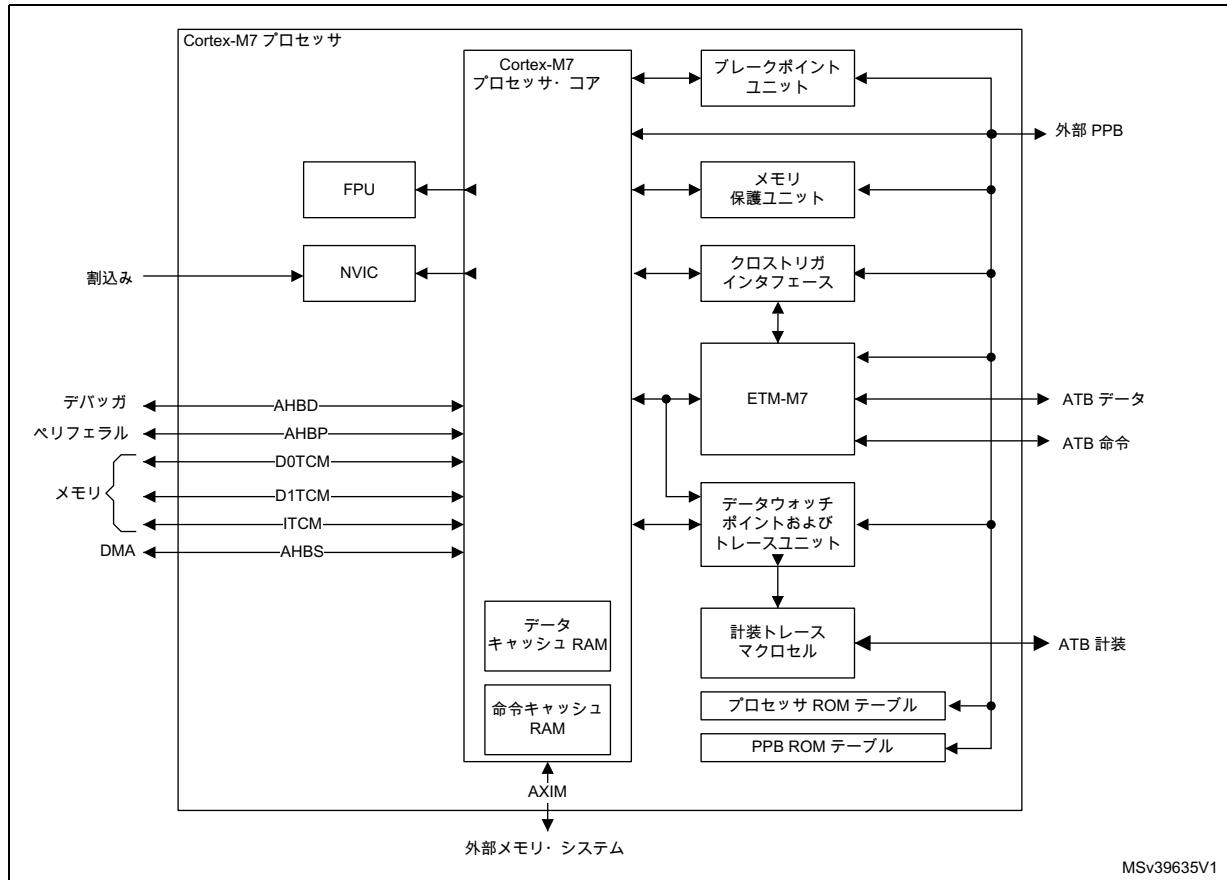

図 1. STM32 Cortex®-M7 の実装プロセッサ

MSv39635V1

Cortex®-M7 プロセッサは、6 段パイプラインを備えたハーバード・アーキテクチャの高性能プロセッサ・コアを基盤として構築されているため、要求の厳しい組込みアプリケーションに最適です。この、インオーダー・スーパースカラ・プロセッサは、効率的な命令セットと徹底的に最適化された設計によって並外れた電力効率を実現し、IEEE754 準拠の単精度および倍精度浮動小数点演算、シングルサイクルや SIMD の多彩な乗算、および積和演算、飽和演算、専用ハードウェア除算などを実行する、ハイエンドの処理ハードウェアを搭載しています。

Cortex®-M7 プロセッサでは、コスト重視の機器の設計を容易にするため、システム・コンポーネントを高密度で結合してプロセッサ占有面積を縮小するとともに、割込み処理とシステム・デバッグ機能を大幅に強化しています。Thumb-2 テクノロジに基づいた Thumb® バージョンの命令セットを搭載することで、コード密度を高め、必要なプログラム・メモリ容量を抑えます。Cortex®-M7 の命令セットは、8bit および 16bit マイクロコントローラの高いコード密度を保つつつ、最新の 32bit アーキテクチャならではの並外れた性能を発揮します。

Cortex®-M7 プロセッサは、設定可能な NVIC を綿密に統合して業界トップクラスの割込み性能を提供します。NVIC は Non Maskable Interrupt (ノンマスクアブル割込み) (NMI) 機能を備え、最大 256 レベルの割込み優先度を提供します。プロセッサ・コアと NVIC を密接に統合することで、interrupt service routines (割込みサービス・ルーチン) (ISR) の実行を高速化し、割込みレイテンシを大幅に短縮しています。これを実現するのが、レジスタのハードウェア・スタッキングと、多重ロードおよび多重ストア動作をサスペンドする機能です。割込みハンドラはアセンブラー・コードに折り返しを必要としないため、ISR のあらゆるコード・オーバーヘッドが取り除かれます。テールチェイン最適化も、ISR の切り換え時のオーバーヘッドを著しく短縮します。

低電力設計を最適化するため、NVIC は、プログラム状態を保持したままデバイス全体の迅速なパワーダウンを可能にする、DEEP SLEEP 機能を含む SLEEP モードを内蔵しています。

自動フォールト検知とハンドリングを内蔵することで、信頼性を向上しています。Cortex®-M7 プロセッサは、メモリ・アクセスにECC と SECDED を使用し、Memory Build-in Self Test (メモリ内蔵のセルフ・テスト) (MBIST) 機能があります。Cortex®-M7 プロセッサは二重冗長なので、ロックステップでも動作が可能です。MCU ベンダが信頼性機能設定を決定するため、これはデバイスやファミリーにより異なることがあります。

命令のスループットを向上するために、Cortex®-M7 プロセッサは、ある特定の命令ペアを同時に実行することができます。これを二重発行と呼びます。

### 1.3.1 システム・レベル・インターフェース

Cortex®-M7 プロセッサは、高速、低レイテンシのメモリ・アクセスを実現するため、AMBA® テクノロジによる複数のインターフェースを備えています。これはアンアライド・データ・アクセスをサポートします。

Cortex®-M7 プロセッサは、きめ細かくメモリを制御する MPU を備えているため、アプリケーションは複数の特権レベルを活用し、コード、データ、スタックをタスクごとに分離および保護できます。これらの機能を備えることは、車載用途など多くの組込み用途に不可欠な要件となりつつあります。

### 1.3.2 設定可能な統合デバッグ機能

Cortex®-M7 プロセッサは、総合的なハードウェア・デバッグ・ソリューションを搭載しています。これにより、従来の JTAG ポートまたはマイクロコントローラやその他の小型パッケージ・デバイスに最適な 2 ピンのSerial Wire Debug (シリアル・ワイヤ・デバッグ) (SWD) ポートのいずれかを介して、プロセッサやメモリに対するシステム可視性が高まります。MCU ベンダがデバッグ機能設定を決定するため、これはデバイスやファミリーにより異なることがあります。

システム・トレースに関しては、データ・ウォッチポイントやプロファイリング・ユニットに加えて Instrumentation Trace Macrocell (計装トレース・マクロセル) (ITM) が統合されています。これらのトレース機能が生成するシステム・イベントを簡単にコスト効率よくプロファイリングできるように、シリアル・ワイヤ・ビューア (SWV) によって、ソフトウェア生成メッセージ、データ・トレース、プロファイリング情報といったストリーム・データを單一ピンを介してエクスポートできます。

オプションの CoreSight テクノロジー・コンポーネント、Embedded Trace Macrocell (エンベデッド・トレース・マクロセル)™ (ETM) は、他に類を見ない命令トレースとデータ・トレース・キャプチャを、従来のトレースユニットよりはるかに小さな領域で実現し、多くの低コスト MCU で完全な命令トレースを初めて可能としました。

ブレークポイント・ユニットは、デバッガが使用することができる、最大 8 つのハードウェア・ブレークポイント・コンパレータを提供します。

### 1.3.3 Cortex®-M7 プロセッサの特徴と利点の概要

- システム・ペリフェラルとの密接な統合による占有面積と開発コストの削減。

- Thumb 命令セットによる 32bit 性能と高いコード密度の両立。

- IEEE754 準拠の単精度および倍精度 Floating-Point Unit (浮動小数点ユニット) (FPU)。

- システム・コンポーネントの電源制御の最適化。

- 統合された SLEEP モードによる省電力化。

- 高速なコード実行によりプロセッサ・クロックの低速化と SLEEP モード期間の増加が可能。

- ハードウェア除算と高速デジタル信号処理指向の積和。

- 信号処理のための飽和演算

- 速度重視のアプリケーション向けの高性能な決定性の割込み処理。

- 安全性が重視されるアプリケーション向け MPU。

- 命令キャッシュおよびデータ・キャッシュ内蔵の Arm Cortex®-M7。

- キャッシュ、DMA ポート付き Tightly-Coupled Memory (密結合メモリ) (TCM) などのメモリ・システム機能と、高性能 AXI 外部メモリ・インターフェース。

- TCM へのシステム・アクセスのための、専用 AHB スレーブ (AHBS) インタフェース。

- 幅広いデバッグおよびトレース機能：

- シリアル・ワイヤ・デバッグおよびシリアル・ワイヤ・トレースにより、デバッグやトレース、コード・プロファイリングに必要なピン数が削減されます。

### 1.3.4 Cortex®-M7 プロセッサのコア・ペリフェラル

Cortex®-M7 プロセッサのコア・ペリフェラルは次のとおり。

#### ネスト化されたベクタ割込みコントローラ

NVIC は、低レイテンシの割込み処理をサポートする内蔵割込みコントローラです。

#### システム制御ブロック

System Control Block (システム制御ブロック) (SCB) は、プログラマ向けに用意されたプロセッサへのモデル・インターフェースです。システムの実装情報と、システム例外の設定、制御、報告などのシステム制御機能を提供します。

#### 統合命令およびデータ・キャッシュ

命令キャッシュおよびデータ・キャッシュは、頻繁にアクセスするデータや命令への高速アクセスを提供し、システム・ベース・メモリを使用した場合の平均性能向上をサポートします。

#### システム・タイマ

システム・タイマの SysTick は、24bit のカウントダウン・タイマです。Real Time Operating System (リアルタイム OS) (RTOS) のティック・タイマまたは単純なカウンタとして使用します。

#### メモリ保護ユニット

Memory Protection Unit (メモリ保護ユニット) (MPU) は、各種メモリ領域に対してメモリ属性を定義することでシステムの信頼性を向上させます。最大 8 つの異なる領域と、必要に応じて事前定義が可能なバックグラウンド領域が提供されます。

#### 浮動小数点ユニット

FPU は、32 ビット単精度および 64 ビット倍精度浮動小数点値の、IEEE754 に準拠した動作を提供します。

## 2 Cortex-M7 プロセッサ

### 2.1 プログラマ・モデル

このセクションでは、Cortex®-M7 のプログラマ・モデルについて説明します。個々のコア・レジスタの説明に加えて、ソフトウェアの実行およびスタックに対するプロセッサのモードや特権レベルの情報も提示します。

#### 2.1.1 ソフトウェアの実行に対するプロセッサのモードと特権レベル

このプロセッサには、以下のモードがあります。

**スレッド・モード** アプリケーション・ソフトウェアを実行します。プロセッサはリセット状態が解除されるとスレッド・モードに移行します。

**ハンドラ・モード** 例外を処理します。すべての例外処理が終了すると、プロセッサはスレッド・モードに戻ります。

ソフトウェア実行には、次の特権レベルがあります。

**非特権** ソフトウェア：

- MSR および MRS 命令を使ったシステム・レジスタへのアクセスに制限され、マスク割り込みに CPS 命令は使用できません。

- システム・タイマ、NVIC、システム制御ブロックにはアクセスできません。

- メモリやペリフェラルへのアクセスが制限される場合があります。

非特権ソフトウェアは非特権レベルで実行されます。

**特権** ソフトウェアは、すべての命令を使用でき、すべてのリソースにアクセスできます。

特権ソフトウェアは特権レベルで実行されます。

スレッド・モードでは、ソフトウェア実行に対する特権の有無は CONTROL レジスタによって制御します ([27 ページの CONTROL レジスタ を参照](#))。ハンドラ・モードでは、ソフトウェア実行は常に特権を持ちます。

特権ソフトウェアのみ、CONTROL レジスタへ書込みを行って、スレッド・モードでのソフトウェア実行に対する特権レベルを変更することができます。非特権ソフトウェアは SVC 命令を使って、特権ソフトウェアに制御を移すためのスーパバイザ・コールを実行することができます。

#### 2.1.2 スタック

このプロセッサは完全降順スタックを使用します。つまり、スタック・ポインタはメモリ内にスタッカされた最後の項目のアドレスを保持しています。プロセッサがスタックに新しい項目をプッシュすると、スタック・ポインタがデクリメントされ、その項目が新しいメモリ位置に書き込まれます。プロセッサには、メイン・スタックとプロセス・スタックの 2 つのスタックが搭載され、それぞれのポインターは独立したレジスタに保持されています ([21 ページのスタック・ポインタ を参照](#))。

スレッド・モードの場合、プロセッサがメイン・スタックとプロセス・スタックのどちらを使用するかは、CONTROL レジスタによって制御されます ([27 ページの CONTROL レジスタ を参照](#))。ハンドラ・モードでは、プロセッサは常にメイン・スタックを使用します。プロセッサ動作には、次のような選択肢があります。

表 1. プロセッサ・モード、実行特権レベル、スタックの使用オプションの概要

| プロセッサ・モード | 実行に使用    | ソフトウェア実行の特権レベル          | 使用するスタック                            |

|-----------|----------|-------------------------|-------------------------------------|

| スレッド      | アプリケーション | 特権または非特権 <sup>(1)</sup> | メイン・スタックまたはプロセス・スタック <sup>(1)</sup> |

| ハンドラ      | 例外ハンドラ   | 常に特権                    | メイン・スタック                            |

1. [27 ページのCONTROL レジスタ](#) を参照してください。

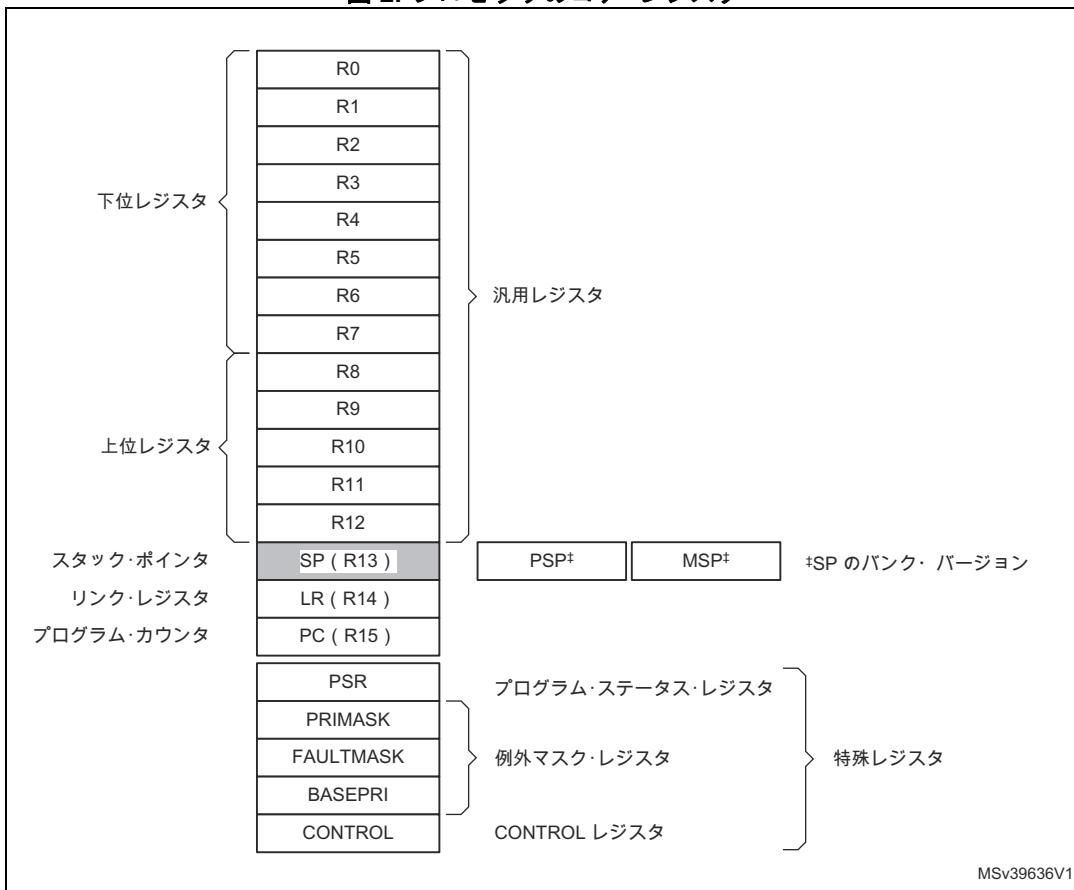

### 2.1.3 コア・レジスタ

プロセッサのコア・レジスタは、次のとおりです。

図 2. プロセッサのコア・レジスタ

表 2. コア・レジスタ・セットの概要

| レジスタ      | 名前     | タイプ <sup>(1)</sup> | 必要な特権 <sup>(2)</sup> | リセット値 | 説明                                          |

|-----------|--------|--------------------|----------------------|-------|---------------------------------------------|

| 汎用レジスタ    | R0-R12 | RW                 | 両方                   | 不明    | <a href="#">21 ページの汎用レジスタ</a> を参照してください。    |

| スタック・ポインタ | MSP    | RW                 | 両方                   | 説明を参照 | <a href="#">21 ページのスタック・ポインタ</a> を参照してください。 |

| スタック・ポインタ | PSP    | RW                 | 両方                   | 不明    | <a href="#">21 ページのスタック・ポインタ</a>            |

表 2. コア・レジスタ・セットの概要（続き）

| レジスタ                      | 名前        | タイプ <sup>(1)</sup> | 必要な特権 <sup>(2)</sup> | リセット値                     | 説明                               |

|---------------------------|-----------|--------------------|----------------------|---------------------------|----------------------------------|

| リンク・レジスタ                  | LR        | RW                 | 両方                   | 0xFFFFFFFF                | 21 ページのリンク・レジスタ                  |

| プログラム・カウンタ                | PC        | RW                 | 両方                   | 説明を参照                     | 21 ページのプログラム・カウンタ                |

| プログラム・ステータス・レジスタ          | PSR       | RW                 | 両方                   | 0x01000000 <sup>(3)</sup> | 22 ページのプログラム・ステータス・レジスタ          |

| アプリケーション・プログラム・ステータス・レジスタ | APSR      | RW                 | 両方                   | 不明                        | 23 ページのアプリケーション・プログラム・ステータス・レジスタ |

| 割込みプログラム・ステータス・レジスタ       | IPSR      | RO                 | 特権                   | 0x00000000                | 23 ページの割込みプログラム・ステータス・レジスタ       |

| 例外プログラム・ステータス・レジスタ        | EPSR      | RO                 | 特権                   | 0x01000000 <sup>(3)</sup> | 24 ページの例外プログラム・ステータス・レジスタ        |

| 優先度マスク・レジスタ               | PRIMASK   | RW                 | 特権                   | 0x00000000                | 25 ページの優先度マスク・レジスタ               |

| フォールト・マスク・レジスタ            | FAULTMASK | RW                 | 特権                   | 0x00000000                | 25 ページのフォールト・マスク・レジスタ            |

| ベース優先度マスク・レジスタ            | BASEPRIS  | RW                 | 特権                   | 0x00000000                | 25 ページの優先度マスク・レジスタ               |

| 制御レジスタ                    | CONTROL   | RW                 | 特権                   | 0x00000000                | 27 ページのCONTROL レジスタ              |

1. スレッド・モードとハンドラ・モードでのプログラム実行時のアクセス・タイプを示しています。デバッグ時のアクセス・タイプは異なる場合があります。

2. 両方というエントリは、特権と非特権の両方のソフトウェアがそのレジスタにアクセスできることを示しています。

3. MRS 命令を実行するとき、EPSR はゼロとして読み込まれます。

## 汎用レジスタ

R0 ~ R12 は、データ操作のための 32bit 汎用レジスタです。

## スタック・ポインタ

スタック・ポインタ (SP) はレジスタ R13 です。スレッド・モードでは、CONTROL レジスタのビット [1] によって、以下のどちらのスタック・ポインタを使用するかを示します。

- 0=Main Stack Pointer (メイン・スタック・ポインタ) (MSP) これがリセット値です。

- 1=Process Stack Pointer (プロセス・スタック・ポインタ) (PSP)

リセット時、プロセッサは MSP にアドレス 0x00000000 の値をロードします。

## リンク・レジスタ

リンク・レジスタ (LR) はレジスタ R14 です。サブルーチン、関数呼び出し、および例外の復帰情報を格納します。リセット時、プロセッサは LR に値 0xFFFFFFFF をセットします。

## プログラム・カウンタ

プログラム・カウンタ (PC) はレジスタ R15 です。現在のプログラム・アドレスを格納します。リセット時、プロセッサは PC にリセット・ベクタ (アドレス 0x00000004) の値をロードします。この値のビット [0] は、リセット時に EPSR の T ビットにロードされ、1 である必要があります。

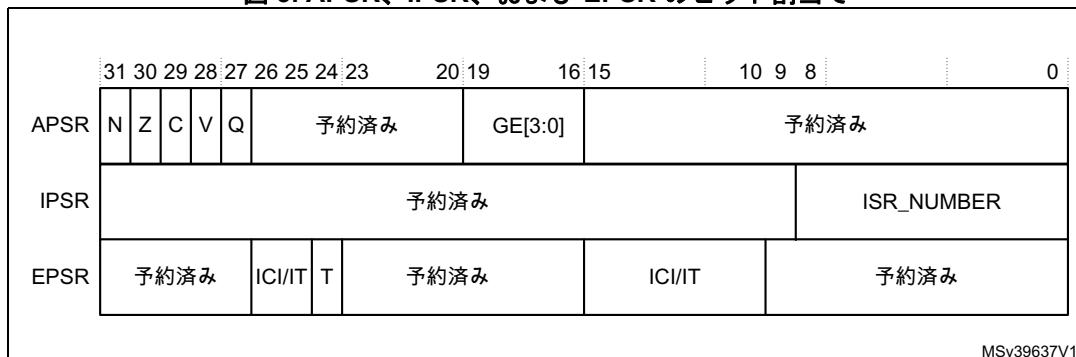

## プログラム・ステータス・レジスタ

Program Status register (プログラム・ステータス・レジスタ) (PSR) は、以下のレジスタを組み合わせたものです。

- Application Program Status register (アプリケーション・プログラム・ステータス・レジスタ) (APSR)

- Interrupt Program Status register (割込みプログラム・ステータス・レジスタ) (IPSR)。

- Execution Program Status register (実行プログラム・ステータス・レジスタ) (EPSR)。

これらのレジスタは、32bit PSR 内の互いに重ならないビットフィールドです。ビット割当てを次に示します。

図 3. APSR、IPSR、および EPSR のビット割当て

これらのレジスタに個別に、あるいは任意に組み合わせてアクセスするには、MSR または MRS 命令の引数としてこれらのレジスタ名を指定します。例 :

- MRS 命令で PSR を使用して、3つすべてのレジスタを読み出します。

- MSR 命令で APSR\_nzcvq を使用して、APSR の N、Z、C、V、Q の各ビットに書き込みます。

PSR の組合せと属性は次のとおりです。

表 3. PSR レジスタの組合せ

| レジスタ  | タイプ                    | 組合せ                |

|-------|------------------------|--------------------|

| PSR   | RW <sup>(1)</sup> .(2) | APSR、EPSR、および IPSR |

| IEPSR | RO                     | EPSR および IPSR      |

| IAPSR | RW <sup>(1)</sup>      | APSR および IPSR      |

| EAPSR | RW <sup>(2)</sup>      | APSR および EPSR      |

1. プロセッサは IPSR のビットへの書き込みを無視します。

2. EPSR のビットを読み出すとゼロが返され、プロセッサはこれらのビットへの書き込みを無視します。

プログラム・ステータス・レジスタへのアクセス方法の詳細については、[175 ページのMRS](#) および [176 ページのMSR](#) の命令の説明を参照してください。

## アプリケーション・プログラム・ステータス・レジスタ

APSR には、前回の命令実行によって設定された現在の条件フラグの状態が格納されます。属性については、[23 ページの表 4](#) のレジスタの概要を参照してください。ビット割当てを次に示します。

**表 4. APSR のビット割当て**

| ビット     | 名前      | 説明                                                    |

|---------|---------|-------------------------------------------------------|

| [31]    | N       | 負のフラグ                                                 |

| [30]    | Z       | ゼロ・フラグ                                                |

| [29]    | C       | キャリーまたはボロー・フラグ                                        |

| [28]    | V       | オーバーフロー・フラグ                                           |

| [27]    | Q       | DSP オーバーフローおよびサチュレーション・フラグ                            |

| [26:20] | -       | 予約済みです。                                               |

| [19:16] | GE[3:0] | 以上フラグ。詳細については、 <a href="#">107 ページのSEL</a> を参照してください。 |

| [15:0]  | -       | 予約済みです。                                               |

## 割込みプログラム・ステータス・レジスタ

IPSR には、現在の割込みサービス・ルーチン (ISR) の例外タイプの番号が格納されます。属性については、[23 ページの表 5](#) のレジスタの概要を参照してください。ビット割当てを次に示します。

**表 5. IPSR のビット割当て**

| ビット    | 名前         | 機能                                                                                                                                                                                                                                                                                                                                   |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:9] | -          | 予約済みです。                                                                                                                                                                                                                                                                                                                              |

| [8:0]  | ISR_NUMBER | <p>これは現在の例外の番号です。</p> <p>0 = スレッド・モード<br/>1 = 予約済み<br/>2 = NMI<br/>3 = ハード・フォールト<br/>4 = メモリ管理<br/>5 = バス・フォールト<br/>6 = 用法フォールト<br/>7-10 = 予約済み<br/>11 = SVCall<br/>12 = デバッグ用に予約済み<br/>13 = 予約済み<br/>14 = PendSV<br/>15 = SysTick<br/>16 = IRQ0<br/>。<br/>。<br/>256 = IRQ239</p> <p>詳細は、<a href="#">39 ページの例外のタイプ</a>を参照してください。</p> |

## 例外プログラム・ステータス・レジスタ

EPSR には、Thumb 状態ビットおよび次のいずれかの実行状態ビットが格納されます。

- If-Then (IT) 命令。

- 割り込まれた多重ロードまたは多重ストア命令の中断可能で中断後から継続可能な命令 (ICI) フィールド。

EPSR の属性については、[24 ページの表 6](#) のレジスタの概要を参照してください。ビット割当てを次に示します。

**表 6. EPSR のビット割当て**

| ビット              | 名前  | 機能                                                                   |

|------------------|-----|----------------------------------------------------------------------|

| [31:27]          | -   | 予約済み。                                                                |

| [26:25], [15:10] | ICI | 中断可能で中断後から継続可能な命令ビット ( <a href="#">24 ページの中断可能で中断後から継続可能な命令</a> を参照) |

| [26:25], [15:10] | IT  | IT 命令の実行状態ビットを示します ( <a href="#">145 ページの IT</a> を参照)。               |

| [24]             | T   | Thumb 状態ビット ( <a href="#">Thumb 状態</a> を参照)                          |

| [23:16]          | -   | 予約済み。                                                                |

| [9:0]            | -   | 予約済み。                                                                |

アプリケーション・ソフトウェアから MSR 命令を使用して EPSR を直接読み出そうとすると、常にゼロが返されます。アプリケーション・ソフトウェアでの MSR 命令による EPSR への書き込み動作は無視されます。

## 中断可能で中断後から継続可能な命令

LDM、STM、PUSH、POP、VLDM、VSTM、VPUSH、または VPOP 命令の実行中に割込みが発生した場合、プロセッサは次のように処理します。

- 多重ロードまたは多重ストア操作を一時的に停止します。

- 次のレジスタ・オペランドを多重操作で EPSR のビット [15:12] に格納します。

割込み処理の後、プロセッサは次のように動作します。

- ビット [15:12] が示すレジスタに復帰します。

- 多重ロードまたは多重ストア命令の実行を再開します。

EPSR に ICI の実行状態が保持されている場合、ビット [26:25,11:10] はゼロになります。

## If-Then ブロック

If-Then ブロックには、IT 命令に続いて最大 4 つの命令が含まれます。ブロック内の各命令は条件付きです。これらの命令に対する条件はすべて同じか、一部の条件を他の部分と反転させることができます。詳細については、[145 ページの IT](#) を参照してください。

## Thumb 状態

Cortex®-M7 プロセッサは、Thumb 状態での命令の実行のみをサポートしています。以下によって T ビットを 0 にクリアできます。

- BLX、BX、および POP{PC} 命令。

- 例外から復帰したときのスタックされた xPSR 値からの復元。

- 例外の開始時またはリセット時のベクタ値のビット [0]。

T ビットが 0 の状態で命令を実行するとフォールトまたはロックアップが発生します。詳細については、[49 ページのロックアップ](#)を参照してください。

### 例外マスク・レジスタ

例外マスク・レジスタは、プロセッサによる例外処理を無効にします。タイミング重視のタスクに影響を与える可能性がある例外を無効にします。

例外マスク・レジスタにアクセスするには MSR および MRS 命令を使用するか、CPS 命令を使用して、PRIMASK または FAULTMASK の値を変更します。詳細は、[175 ページの MRS](#)、[176 ページの MSR](#)、および [173 ページの CPS](#) を参照してください。

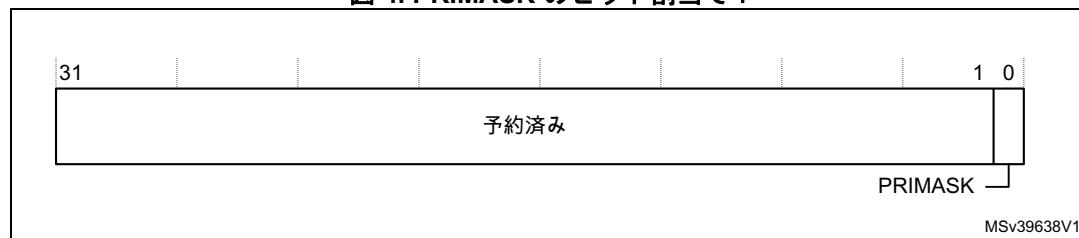

### 優先度マスク・レジスタ

PRIMASK レジスタは、設定可能な優先度を持つすべての例外のアクティブ化を禁止します。属性については、[表 7](#) のレジスタ概要を参照してください。ビット割当てを次に示します。

**図 4. PRIMASK のビット割当て：**

**表 7. PRIMASK レジスタのビット割り当て**

| ビット    | 名前      | 機能                                                                |

|--------|---------|-------------------------------------------------------------------|

| [31:1] | -       | 予約済み。                                                             |

| [0]    | PRIMASK | 優先化可能な割込みマスク：<br>0 = 影響なし。<br>1 = 設定可能な優先度を持つすべての例外のアクティブ化を禁止します。 |

### フォールト・マスク・レジスタ

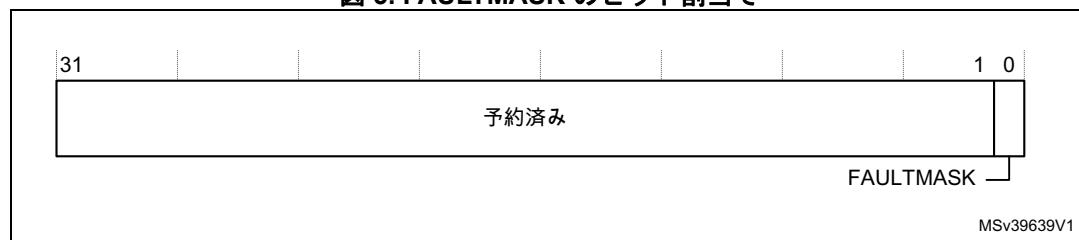

FAULTMASK レジスタは Non Maskable Interrupt (ノンマスカブル割込み) (NMI) を除くすべての例外のアクティブ化を禁止します。属性については、[26 ページの表 8](#) のレジスタ概要を参照してください。ビット割当てを次に示します。

**図 5. FAULTMASK のビット割当て**

表 8. FAULTMASK レジスタのビット割り当て

| ビット    | 名前        | 機能                                                           |

|--------|-----------|--------------------------------------------------------------|

| [31:1] | -         | 予約済み。                                                        |

| [0]    | FAULTMASK | 優先化可能な割込みマスク：<br>0 = 影響なし。<br>1 = NMIを除くすべての例外のアクティブ化を禁止します。 |

プロセッサは、NMI ハンドラを除くすべての例外ハンドラの終了時に、FAULTMASK ビットを 0 にクリアします。

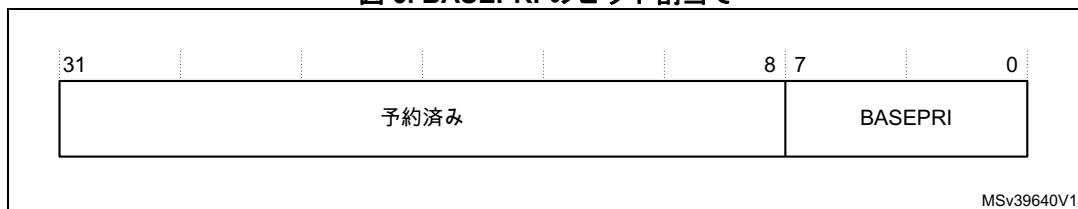

### ベース優先度マスク・レジスタ

BASEPRI レジスタは、例外処理に対する最低優先度を定義します。BASEPRI をゼロ以外の値にセットすると、優先度レベルが BASEPRI 値以下のすべての例外のアクティブ化を禁止します。属性については、[26 ページの表 9 のレジスタ概要](#)を参照してください。ビット割り当てを次に示します。

図 6. BASEPRI のビット割り当て

表 9. BASEPRI レジスタのビット割り当て

| ビット    | 名前                     | 機能                                                                                                     |

|--------|------------------------|--------------------------------------------------------------------------------------------------------|

| [31:8] | -                      | 予約済み。                                                                                                  |

| [7:0]  | BASEPRI <sup>(1)</sup> | 優先度マスク・ビット：<br>0x00 影響はありません。<br>ゼロ以外：例外処理のベース優先度を定義します。<br>プロセッサは、BASEPRI の値以上の優先度の値を持つすべての例外を処理しません。 |

- このフィールドは、割込み優先度レジスタの優先度フィールドと同じです。デバイスはこのフィールドのビット [7:M] のみ実装し、ビット [M-1:0] は 0 として読み出され、書き込みは無視されます。詳細については、[23 ページの割込みプログラム・ステータス・レジスタ](#) を参照してください。優先度フィールドの値が大きいほど、例外の優先度は低いことに注意してください。

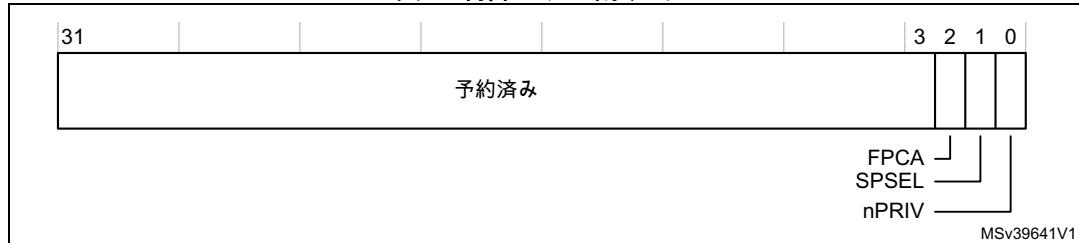

## CONTROL レジスタ

CONTROL レジスタは、使用されるスタック、およびプロセッサがスレッド・モードにある場合のソフトウェア実行の特権レベルを管理し、FPU状態がアクティブかどうかを示します。属性については、[27 ページの表 10](#) のレジスタ概要を参照してください。ビット割当てを次に示します。

図 7. 制御ビット割り当て

表 10. コントロール レジスタのビット割当て

| ビット    | 名前    | 機能                                                                                                                                                                      |

|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:3] | -     | 予約済み。                                                                                                                                                                   |

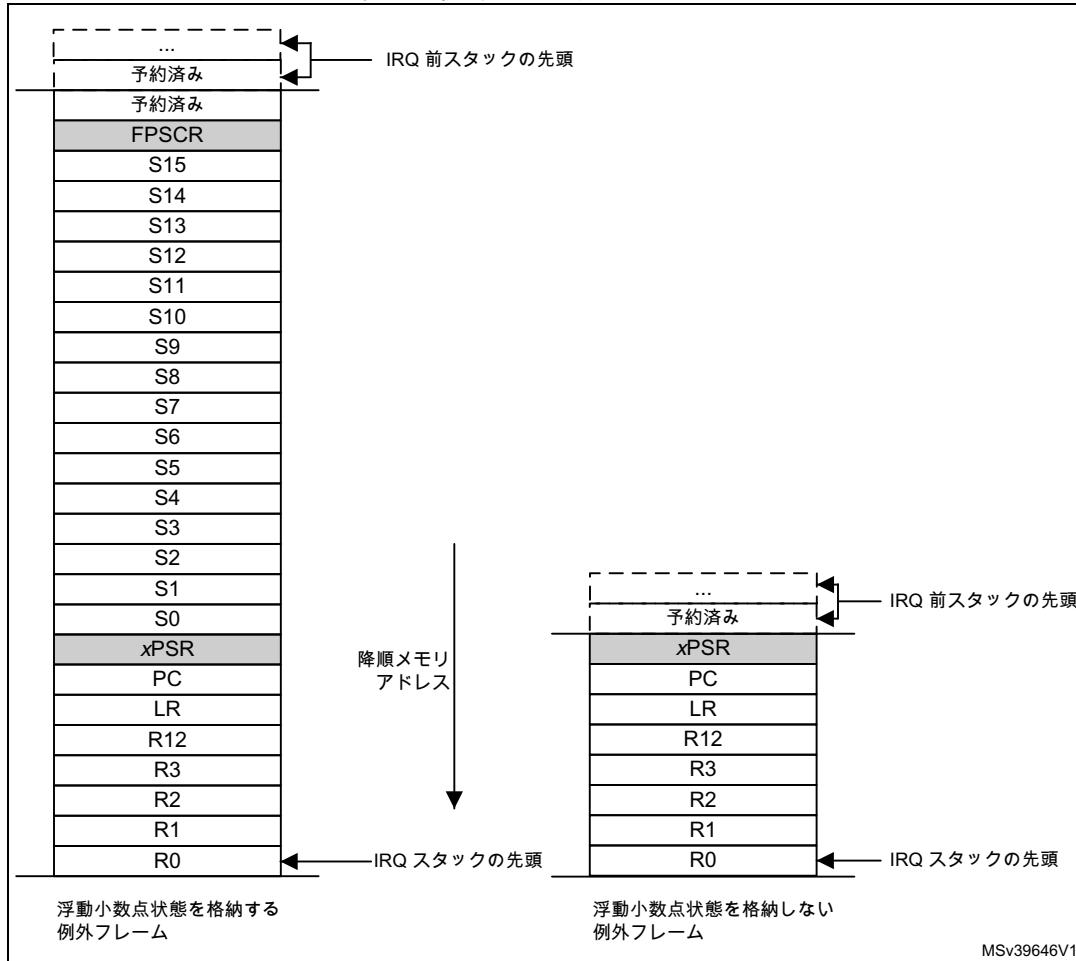

| [2]    | FPCA  | 浮動小数点コンテキストが現在アクティブであるかどうかを示します。<br>0 : 浮動小数点コンテキストはアクティブではありません。<br>1 : 浮動小数点コンテキストがアクティブです。<br>例外を処理する際に、浮動小数点の状態を維持すべきかどうかを、このビットに基づいて判断します。                         |

| [1]    | SPSEL | 現在アクティブなスタック・ポインタを定義します。<br>0 = MSP が現在のスタック・ポインタです。<br>1 = PSP が現在のスタック・ポインタです。<br>ハンドラ・モードでは、このビットはゼロとして読み出され、書き込みは無視します。Cortex®-M7 プロセッサは、例外からの復帰時に、このビットを自動的に更新します。 |

| [0]    | nPRIV | スレッド・モードの特権レベルを定義します：<br>0 = 特権。<br>1 = 非特権。                                                                                                                            |

ハンドラ・モードでは常に MSP が使用されます。このため、ハンドラ・モードで動作中のプロセッサは、CONTROL レジスタのアクティブなスタック・ポインタ・ビットへの明示的な書込みを無視します。例外開始および復帰メカニズムが、EXC\_RETURN 値に基づいて CONTROL レジスタを自動的に更新します。[46 ページの表 20](#) を参照してください。

OS 環境では、スレッド・モードで動作するスレッドはプロセス・スタックを使用し、カーネルおよび例外ハンドラはメイン・スタックを使用することを Arm 社では推奨します。

スレッド・モードではデフォルトで MSP が使用されます。スレッド・モードで使用していたスタック・ポインタを PSP に切り替えるには、以下のいずれかを実行します。

- MSR 命令を使用して、現在アクティブなスタック・ポインタ・ビット、CONTROL.SPSELbit、を 1 にセットします ([176 ページの MSR](#) を参照)。

- 適切な EXC\_RETURN 値により例外からスレッド・モードへ復帰します ([46 ページの表 20](#) を参照)。

スタック・ポインタを変更する場合、ソフトウェアは MSR 命令の直後に ISB 命令を使用する必要があります。これによって、ISB 命令の後の命令が確実に新しいスタック・ポインタを使用して実行できます。[175 ページの ISB](#) を参照してください。

## 2.1.4 例外と割込み

Cortex<sup>®</sup>-M7 プロセッサは、割込みとシステム例外をサポートしています。プロセッサとNVICがすべての例外の優先度を決定し、処理します。例外は、ソフトウェア制御の通常のフローを変化させます。プロセッサは、リセットを除くすべての例外の処理にハンドラ・モードを使用します。詳細は、[44 ページの例外の開始](#)および[46 ページの例外からの復帰](#)を参照してください。

NVIC レジスタは割込み処理を制御します。詳細については、[181 ページのネスト化されたベクタ割込みコントローラ](#)を参照してください。

## 2.1.5 データ型

プロセッサは、以下のとおりです。

- 以下のデータ型をサポートします。

- 32 ビットワード

- 16 bit ハーフワード

- 8 bit バイト

- 32 ビット単精度浮動小数点数

- 64 ビット倍精度浮動小数点数

- すべてのデータ・メモリ・アクセスをリトルエンディアンとして管理します。詳細については、[33 ページのメモリの領域、タイプ、および属性](#)を参照してください。

## 2.1.6 Cortex Microcontroller Software Interface Standard (Cortex マイクロコントローラ・ソフトウェア・インターフェース規格) (CMSIS)

Cortex Microcontroller Software Interface Standard (Cortex マイクロコントローラ・ソフトウェア・インターフェース規格) (CMSIS) では、Cortex®-M7 マイクロコントローラ・システムに対して、以下を定義しています。

- 以下の実行するための共通の方法

- ペリフェラル・レジスタへのアクセス

- 例外ベクタの定義

- 以下の名称

- コア・ペリフェラルのレジスタ

- コア例外ベクタ

- RTOS カーネル用のデバイスに依存しないインターフェース (デバッグ・チャネルを含む)。

CMSIS には、Cortex®-M7 プロセッサのコア・ペリフェラルのアドレス定義およびデータ構造が含まれます。

CMSIS では、テンプレート・コードの再利用や、さまざまなミドルウェア・ベンダが提供する CMSIS 準拠のソフトウェア・コンポーネントの組合せを可能にすることで、ソフトウェア開発を簡素化しています。ソフトウェア・ベンダは CMSIS を拡張して、ペリフェラルの定義やそれらのペリフェラルのアクセス機能を含めることができます。

本書は、CMSIS によって定義されたレジスタ名を記載し、プロセッサ・コアおよびコア・ペリフェラルに対応する CMSIS 関数についても簡単に説明しています。

本書で使用するレジスタの短縮名は CMSIS によって定義されたものです。これらの短縮名は、他のドキュメントで使用されているアーキテクチャ上の短縮名と異なる場合があります。

以降のセクションでは、CMSIS の詳細について説明します。

- [51 ページの電源管理に関するプログラミングのヒント](#)を参照してください。

- [61 ページのCMSIS 関数](#)を参照してください。

- [213 ページのSysTick 設計のヒントとコツ](#)

- [182 ページのCMSIS を使用した Cortex®-M7 NVIC レジスタへのアクセス](#)を参照してください。

- [188 ページのNVIC のプログラミングのヒント](#)を参照してください。

- [238 ページのCMSIS を使用した Cortex®-M7 キャッシュのメンテナンス操作](#)

## 2.2 Cortex®-M7 の構成

表 11、表 12 そして 表 13 は STM32F7 シリーズ Cortex-M7 の構成を表示します。

表 11. STM32F746xx/STM32F756xx Cortex®-M7 の構成

| 機能            | STM32F746xx/STM32F756xx                               |

|---------------|-------------------------------------------------------|

| 浮動小数点ユニット     | 単精度浮動小数点ユニット                                          |

| MPU           | 8 領域                                                  |

| 命令 TCM のサイズ   | Flash TCM : 1 MB<br>RAM ITCM : 16 KB                  |

| データ TCM のサイズ  | 64 KB                                                 |

| 命令キャッシュのサイズ   | 4 KB                                                  |

| データ・キャッシュのサイズ | 4 KB                                                  |

| キャッシュ ECC     | 実装なし                                                  |

| 割込み優先順位レベル    | 16 の優先順位レベル                                           |

| IRQ 数         | 98                                                    |

| WIC、CTI       | 実装なし                                                  |

| デバッグ          | JTAG および、シリアルワイヤデバッグポート<br>8 つのブレークポイントと 4 つのウォッチポイント |

| ITM サポート      | データトレース (DWT)、および計装トレース (ITM)                         |

| ETM サポート      | 命令トレースインターフェース                                        |

表 12. STM32F76xxx/STM32F77xxx Cortex®-M7 の構成

| 機能            | STM32F76xxx/STM32F77xxx                               |

|---------------|-------------------------------------------------------|

| 浮動小数点ユニット     | 倍精度および単精度浮動小数点ユニット                                    |

| MPU           | 8 領域                                                  |

| 命令 TCM のサイズ   | Flash TCM : 2 MB<br>RAM ITCM : 16 KB                  |

| データ TCM のサイズ  | 128 KB                                                |

| 命令キャッシュのサイズ   | 16 KB                                                 |

| データ・キャッシュのサイズ | 16 KB                                                 |

| キャッシュ ECC     | 実装なし                                                  |

| 割込み優先順位レベル    | 16 の優先順位レベル                                           |

| IRQ 数         | 110                                                   |

| WIC、CTI       | 実装なし                                                  |

| デバッグ          | JTAG および、シリアルワイヤデバッグポート<br>8 つのブレークポイントと 4 つのウォッチポイント |

| ITM サポート      | データトレース (DWT)、および計装トレース (ITM)                         |

| ETM サポート      | 命令トレースインターフェース                                        |

表 13. STM32F72xxx/STM32F73xxx Cortex®-M7 の構成

| 機能            | STM32F72xxx/STM32F73xxx                               |

|---------------|-------------------------------------------------------|

| 浮動小数点ユニット     | 単精度浮動小数点ユニット                                          |

| MPU           | 8 領域                                                  |

| 命令 TCM のサイズ   | Flash TCM : 512 KB<br>RAM ITCM : 16 KB                |

| データ TCM のサイズ  | 64 KB                                                 |

| 命令キャッシュのサイズ   | 8 KB                                                  |

| データ・キャッシュのサイズ | 8 KB                                                  |

| キャッシング ECC    | 実装なし                                                  |

| 割込み優先順位レベル    | 16 の優先順位レベル                                           |

| IRQ 数         | 104                                                   |

| WIC、CTI       | 実装なし                                                  |

| デバッグ          | JTAG および、シリアルワイヤデバッグポート<br>8 つのブレークポイントと 4 つのウォッチポイント |

| ITM サポート      | データトレース (DWT)、および計装トレース (ITM)                         |

| ETM サポート      | 命令トレースインターフェース                                        |

表 14 に、STM32H7 シリーズ Cortex-M7 の構成を示します。

表 14. STM32H7 シリーズ Cortex®-M7 の構成

| 機能            | STM32H7 シリーズ                                          |

|---------------|-------------------------------------------------------|

| 浮動小数点ユニット     | 倍精度および単精度浮動小数点ユニット                                    |

| MPU           | 16 領域                                                 |

| 命令 TCM のサイズ   | RAM ITCM : 64 KB                                      |

| データ TCM のサイズ  | 128 KB                                                |

| 命令キャッシュのサイズ   | 16 KB                                                 |

| データ・キャッシュのサイズ | 16 KB                                                 |

| キャッシング ECC    | 実装されます。                                               |

| 割込み優先順位レベル    | 16 の優先順位レベル                                           |

| IRQ 数         | 149                                                   |

| WIC、CTI       | WIC 未実装、CTI 実装                                        |

| デバッグ          | JTAG および、シリアルワイヤデバッグポート<br>8 つのブレークポイントと 4 つのウォッチポイント |

| ITM サポート      | データトレース (DWT)、および計装トレース (ITM)                         |

| ETM サポート      | 命令トレースインターフェース                                        |

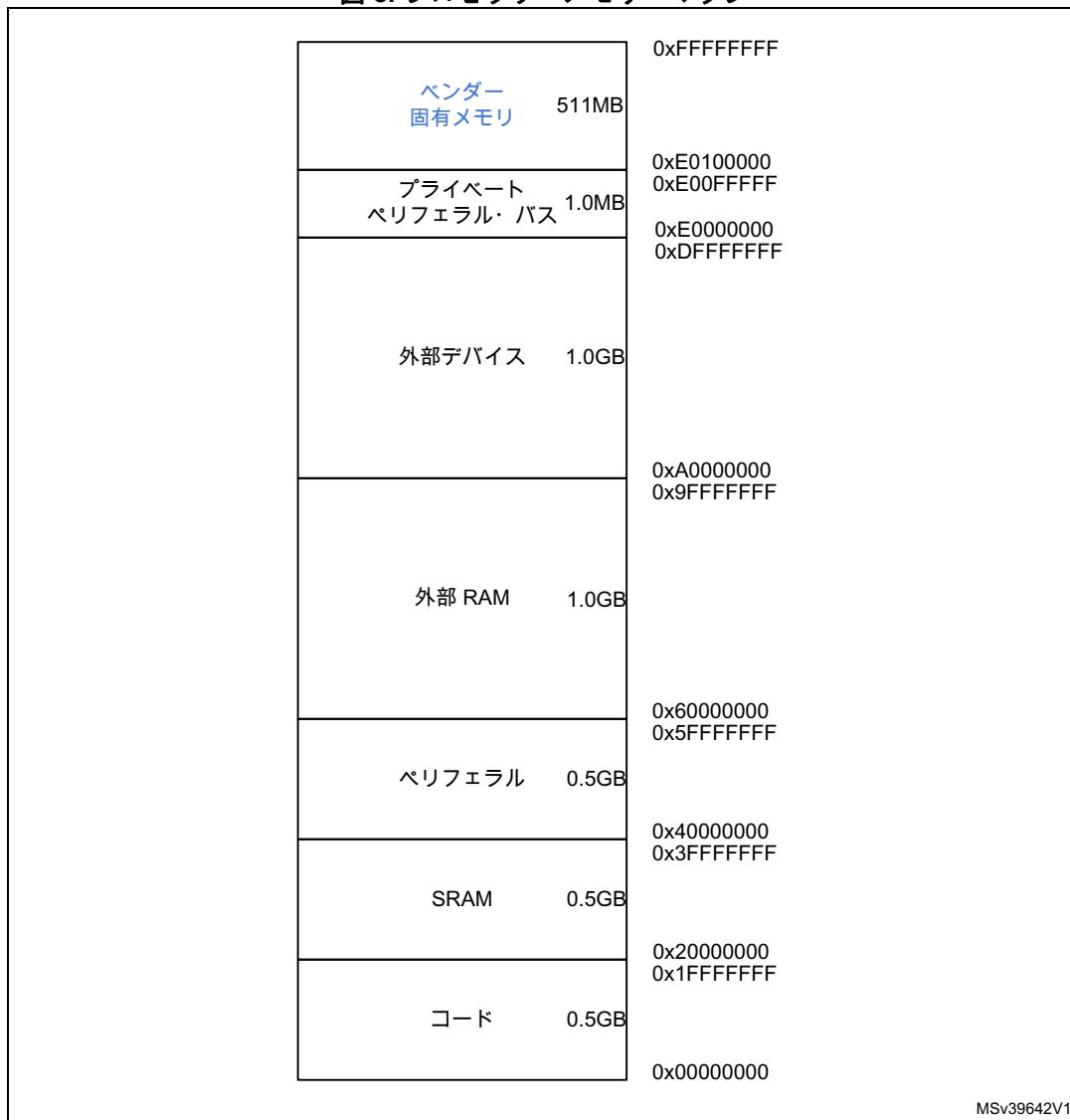

## 2.3 メモリ・モデル

このセクションでは、プロセッサのメモリ・マップおよびメモリ・アクセスの動作について説明します。プロセッサには、最大 4 GB のアドレス指定可能なメモリを提供する固定されたデフォルトのメモリ・マップがあります。メモリ・マップは次のとおりです。

図 8. プロセッサ・メモリ・マップ

プロセッサでは、コア・ペリフェラルのレジスタ向けに、プライベート・ペリフェラル・バス (PPB) のアドレス範囲の領域を確保しています ([180 ページの Cortex-M7 ペリフェラルについて](#)を参照)。

### 2.3.1 メモリの領域、タイプ、および属性

メモリ・マップと MPU のプログラミングにより、メモリ・マップは複数の領域に分割されます。各領域にはメモリ・タイプが定義され、一部の領域ではその追加のメモリ属性も設定されています。メモリ・タイプとメモリ属性が、その領域へのアクセス動作を決定します。

メモリ・タイプに次のようなものがあります。

**ノーマル** プロセッサは、効率を高めるためトランザクションの順番を変えたり、投機的読出しを実行することができます。

**デバイス (Device) および Strongly-ordered** プロセッサは、デバイス・メモリへの他のトランザクションや Strongly-ordered メモリへのトランザクションとの相対的なトランザクション順序を保持します。

デバイス・メモリと Strongly-ordered メモリに対して順序付けの要件が異なるため、メモリ・システムはデバイス・メモリへの書き込みをバッファできますが、Strongly-ordered メモリへの書き込みはバッファできません。

追加のメモリ属性として、次のようなものがあります。

**共有可能 (shareable)** 共有可能なメモリ領域の場合、メモリ・システムは、たとえば、DMA コントローラを備えたプロセッサなど、複数のバス・マスタを備えるシステム内のバス・マスタ間のデータ同期を提供します。

Strongly-ordered メモリは常に共有可能です。

複数のバス・マスタが共有不可メモリ領域にアクセスできる場合、ソフトウェアでバス・マスタ間のデータのコヒーレンシを保証する必要があります。

**実行不可 (XN)** プロセッサが命令へのアクセスを禁止することを意味します。メモリの XN 領域からフェッチされた命令を実行すると、ハード・�オルト例外が生成されます。

### 2.3.2 メモリ・システムでのメモリ・アクセスの順序付け

明示的なメモリ・アクセス命令によって発生するほとんどのメモリ・アクセスについて、メモリ・システムは、アクセスが完了する順序がプログラムにおける命令の順序と一致することを保証しません。順序を変更しても、命令シーケンスの動作には影響しないことが条件です。通常は、プログラムが正しく実行されるために、2つのメモリ・アクセスがプログラム順に完了することが必要な場合、ソフトウェアで、これらのメモリ・アクセス命令の間にメモリ・バリア命令を挿入する必要があります（[2.3.4 : 36ページのソフトウェアによるメモリ・アクセスの順序付け](#)を参照）。

ただし、デバイス・メモリおよび Strongly-ordered メモリへのアクセスの順序付けの一部については、メモリ・システムによって保証されます。2つのメモリ・アクセス命令 A1 と A2 について、プログラム順では A1 が A2 より前に出現する場合、これら 2つの命令によって発生するメモリ・アクセスの順序は次のようになります。

表 15. メモリ・アクセスの順序<sup>(1)</sup>

| A1             | A2        |           |      |                       |

|----------------|-----------|-----------|------|-----------------------|

|                | ノーマル・アクセス | デバイス・アクセス |      | Strongly-ordered アクセス |

|                |           | 共有不可      | 共有可能 |                       |

| ノーマル・アクセス      | -         | -         | -    | -                     |

| デバイス・アクセス、共有不可 | -         | <         | -    | <                     |

表 15. メモリ・アクセスの順序<sup>(1)</sup> (続き)

| A1                    | A2        |           |      |                       |

|-----------------------|-----------|-----------|------|-----------------------|

|                       | ノーマル・アクセス | デバイス・アクセス |      | Strongly-ordered アクセス |

|                       |           | 共有不可      | 共有可能 |                       |

| デバイス・アクセス、共有可能        | -         | -         | <    | <                     |

| Strongly-ordered アクセス | -         | <         | <    | <                     |

1. - はメモリ・システムがアクセスの順序を保証していないことを意味します。

< は、アクセスがプログラム順に従うこと、つまり A1 は常に A2 より前に出現することを意味します。

### 2.3.3 メモリ・アクセスの動作

メモリ・マップの各領域へのアクセスは、次のように動作します。

表 16. メモリ・アクセスの動作<sup>(1)</sup>

| アドレス範囲                  | メモリ領域       | メモリタイプ           | XN | 説明                                                                                       |

|-------------------------|-------------|------------------|----|------------------------------------------------------------------------------------------|

| 0x00000000 - 0x1FFFFFFF | エンコード       | ノーマル             | -  | プログラム・コードの実行可能領域。ここにデータを書き込むこともできます。<br>命令フェッチとデータアクセスは、ITCM または AXIM インタフェースを介して実行されます。 |

| 0x20000000 - 0x3FFFFFFF | SRAM        | ノーマル             | -  | データの実行可能領域。ここにコードを入力することもできます。<br>命令フェッチとデータアクセスは、DTCM または AXIM インタフェースを介して実行されます。       |

| 0x40000000 - 0x5FFFFFFF | ペリフェラル      | デバイス             | XN | 外部デバイス・メモリ<br>データアクセスは、AHBP または AXIM インタフェースを介して実行されます。                                  |

| 0x60000000 - 0x9FFFFFFF | 外部 RAM      | ノーマル             | -  | データの実行可能領域。<br>命令フェッチとデータアクセスは、AXIM インタフェースを介して実行されます。                                   |

| 0xA0000000 - 0xDFFFFFFF | 外部デバイス      | デバイス             | XN | 外部デバイス・メモリ<br>命令フェッチとデータアクセスは、AXIM インタフェースを介して実行されます。                                    |

| 0xE0000000 - 0xE00FFFFF | 専用ペリフェラル・バス | Strongly-ordered | XN | この領域には、NVIC、システム・タイマ、システム制御ブロックが含まれます。<br>この領域ではワードアクセスのみを使用できます。                        |

| 0xE0100000 - 0xFFFFFFF  | ベンダ固有デバイス   | デバイス             | XN | この領域へのアクセスは、ベンダー固有のペリフェラルです。                                                             |

1. 詳細については、33 ページのメモリの領域、タイプ、および属性 を参照してください。

コード、SRAM、外部RAMの領域にプログラムを保持できます。

MPU は、このセクションに示したデフォルトのメモリ・アクセス動作を上書きできます。詳細については、218 ページのメモリ保護ユニットを参照してください。

### キャッシュおよび共有メモリに対する追加のメモリアクセスの制約

システムにキャッシュや共有メモリが内蔵されている場合、一部のメモリ領域には追加のアクセスの制約があり、表 17 に示すように、一部の領域は再分割されます。

表 17. メモリ領域の共有可能性とキャッシュのポリシー

| アドレス範囲                  | メモリ領域       | メモリタイプ <sup>(1)</sup> | 共有可能性 <sup>(1)</sup> | キャッシュポリシー <sup>(2)</sup> |

|-------------------------|-------------|-----------------------|----------------------|--------------------------|

| 0x00000000 - 0x1FFFFFFF | エンコード       | ノーマル                  | 共有不可                 | WT                       |

| 0x20000000 - 0x3FFFFFFF | SRAM        | ノーマル                  | 共有不可                 | WBWA                     |

| 0x40000000 - 0x5FFFFFFF | ペリフェラル      | デバイス                  | 共有不可                 | -                        |

| 0x60000000 - 0x7FFFFFFF | 外部 RAM      | ノーマル                  | 共有不可                 | -                        |

| 0x80000000 - 0x9FFFFFFF |             |                       |                      | WT                       |

| 0xA0000000 - 0xBFFFFFFF | 外部デバイス      | デバイス                  | 共有可能                 | -                        |

| 0xC0000000 - 0xDFFFFFFF |             |                       | 共有不可                 | -                        |

| 0xE0000000 - 0xE00FFFFF | 専用ペリフェラル・バス | Strongly-ordered      | 共有可能                 | -                        |

| 0xE0100000 - 0xFFFFFFF  | ベンダ固有デバイス   | デバイス                  | 共有不可                 | -                        |

1. 詳細は、セクション 2.3.1 : 33 ページのメモリの領域、タイプ、および属性を参照してください。

2. WT = ライトスルー、書き込み割当てなし WBWA = ライトバック、書き込み割当てあり

### 命令プリフェッチと分岐予測

Cortex®-M7 プロセッサには、次の機能があります。

- 実行前の命令のプリフェッチ。

- 分岐先アドレスからの投機的プリフェッチ

### 2.3.4 ソフトウェアによるメモリ・アクセスの順序付け

プログラム・フロー内の命令の順序は、対応するメモリ・トランザクションの順序を必ずしも保証するわけではありません。これは、次の理由によるものです。

- プロセッサは、命令シーケンスの動作に影響を与えない限り、効率向上のために一部のメモリ・アクセスの順序を入れ換える場合がある。

- プロセッサが複数のバス・インターフェースを備えている。

- メモリ・マップ内のメモリまたはデバイスのウェイト・ステートが異なる。

- バッファされるメモリ・アクセスや投機的なメモリ・アクセスが存在する。

[33 ページのメモリ・システムでのメモリ・アクセスの順序付け](#)に、メモリ・システムがメモリ・アクセスの順序を保証する場合についての説明が記載されています。それらの場合に該当せず、メモリ・アクセスの順序が重要な場合は、ソフトウェアにメモリ・バリア命令を挿入して、強制的にアクセスを順序付ける必要があります。プロセッサでは、以下のメモリ・バリア命令を用意しています。

|            |                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DMB</b> | Data Memory Barrier (データ・メモリ・バリア) (DMB) 命令は、未処理のメモリ・トランザクションが、後続のメモリ・トランザクションよりも前に完了することを保証します。 <a href="#">174 ページのDMB</a> を参照してください。            |

| <b>DSB</b> | Data Synchronization Barrier (データ同期バリア) (DSB) 命令は、未処理のメモリ・トランザクションが、後続の命令を実行する前に完了することを保証します。 <a href="#">174 ページのDSB</a> を参照してください。              |

| <b>ISB</b> | Instruction Synchronization Barrier (命令同期バリア) (ISB) 命令は、完了したすべてのメモリ・トランザクションの影響が、後続の命令によって認識可能であることを保証します。 <a href="#">175 ページのISB</a> を参照してください。 |

### MPU プログラミング

ISB 命令または例外からの復帰の前に DSB を使用して、後続の命令が新しい MPU 設定を使用するようになります。

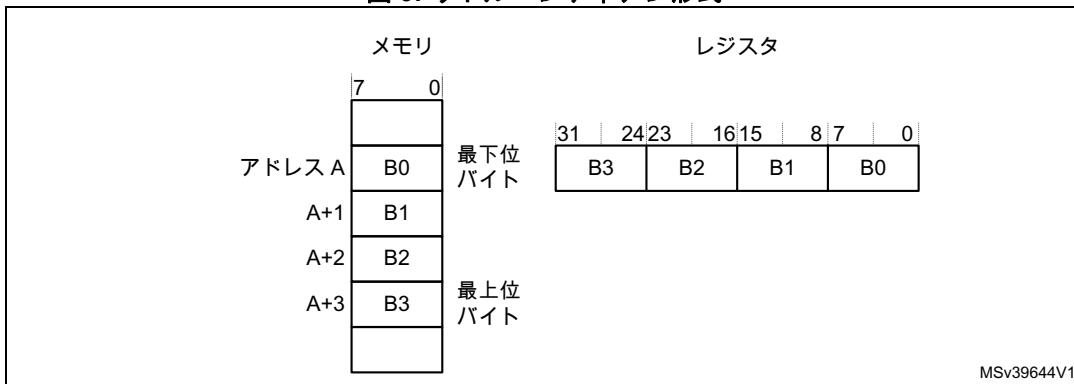

### 2.3.5 メモリのエンディアン形式

プロセッサは、メモリを 0 から昇順に番号が付けられたバイトの線形配列としてとらえます。たとえば、バイト 0 ~ 3 は最初にストアされるワードを、バイト 4 ~ 7 は 2 番目にストアされるワードを持します。[36 ページのリトルエンディアン形式](#)に、ワードのデータをメモリに格納する方法を示します。

#### リトルエンディアン形式

リトルエンディアン形式では、プロセッサは、ワードの最下位バイトを一番小さい番号のバイトにストアし、最上位バイトを一番大きい番号のバイトにストアします。例：

図 9. リトルエンディアン形式

## 2.3.6 同期プリミティブ

Cortex®-M7 プロセッサの命令セットのサポートには、同期プリミティブのペアが含まれます。同期プリミティブは、スレッドまたはプロセスがメモリ位置への排他的なアクセスを得るために使用できる非ブロックング・メカニズムを提供します。ソフトウェアは、保証された読み出し-変更-書き込みのメモリ更新シーケンスの実行やセマフォ・メカニズムに、同期プリミティブを使用できます。

同期プリミティブのペアは、次の要素で構成されます。

### 排他的ロード命令

メモリ位置の値の読み出しに使用され、その位置への排他的なアクセスを要求します。

### 排他的ストア命令

同じメモリ位置への書き込みに使用され、ステータス・ビットをレジスタに返します。このビットの値は、以下を意味します。

0 : そのスレッドまたはプロセスがメモリへの排他的なアクセスを獲得し、書き込みは成功であることを示します。

1 : そのスレッドまたはプロセスはメモリへの排他的なアクセスを獲得できず、書き込みは実行されなかったことを示します。

排他ロード命令と排他ストア命令のペアには次のものがあります。

- ワード命令 LDREX と STREX。

- ハーフワード命令 LDREXH と STREXH。

- バイト命令 LDREXB と STREXB

ソフトウェアでは、排他ロード命令とそれに対応する排他ストア命令を合わせて使用する必要があります。

メモリ位置の排他的な読み出し／変更／書き込みを実行するには、ソフトウェアは次の手順に従う必要があります。

1. 排他ロード命令を使用して、その位置の値を読み出します。

2. 必要に応じて値を修正します。

3. 排他ストア命令を使用して、そのメモリ位置に新しい値のライトバックを試行します。

4. 返されたステータス・ビットをテストします。このビットの値は、以下を意味します。

0 : 読出し-変更-書き込みは正常に完了しました。

1 : 書込みは実行されませんでした。これは、ステップ 1 で返された値が古くなっている可能性があることを示します。ソフトウェアが読み出し／変更／書き込みのシーケンスを再試行する必要があります。

ソフトウェアは、同期プリミティブを使用して次のようにセマフォを実装できます。

1. 排他ロード命令を使用してセマフォ・アドレスを読み出して、セマフォが解放されているかどうかをチェックします。

2. セマフォが解放されている場合、排他ストア命令を使用してセマフォ・アドレスに要求値を書き込みます。

3. ステップ 2 から返されたステータス・ビットが排他ストアが成功したことを示している場合、セマフォの要求は完了しています。しかし、排他ストアが失敗した場合は、ソフトウェアがステップ 1 を実行した後に別のプロセスがそのセマフォを要求していた可能性があります。

Cortex®-M7 プロセッサには、プロセッサが排他ロード命令を実行した事実をタグ付けする排他アクセス・モニタが含まれています。プロセッサがマルチプロセッサ・システムに属していて、アドレスがメモリの共有領域にある場合はさらに、各プロセッサによる排他アクセスでアドレス指定したメモリ位置を、システムがグローバルにタグ付けします。

プロセッサは、次の場合に排他アクセスのタグを削除します。

- CLREX 命令を実行した場合。

- STREX 命令を実行した場合（書き込みが成功したかどうかは無関係）。

- 例外が発生した場合。これは、プロセッサが複数のスレッド間のセマフォ競合を解決できることを意味します。

マルチプロセッサ実装では：

- CLREX 命令の実行は、プロセッサのローカルな排他アクセス・タグのみ削除します。

- STREX 命令または例外の実行は、プロセッサのローカルな排他アクセス・タグを削除します。

- 共有メモリ領域に対する STREX 命令の実行でも、システム内のプロセッサのグローバル排他的アクセスタグが削除されることがあります。

同期プリミティブ命令の詳細については、[82 ページの LDREX と STREX](#) および [83 ページの CLREX](#) を参照してください。

### 2.3.7 同期プリミティブのプログラミングのヒント

ISO/IEC C は直接排他アクセス命令を生成できません。これらの命令の生成に対して、CMSIS では次の組込み関数を用意しています。

**表 18. 排他アクセス命令のための CMSIS 関数**

| 命令     | CMSIS 関数                                           |

|--------|----------------------------------------------------|

| LDREX  | uint32_t __LDREXW (uint32_t *addr)                 |

| LDREXH | uint16_t __LDREXH (uint16_t *addr)                 |

| LDREXB | uint8_t __LDREXB (uint8_t *addr)                   |

| STREX  | uint32_t __STREXW (uint32_t value, uint32_t *addr) |

| STREXH | uint32_t __STREXH (uint16_t value, uint16_t *addr) |

| STREXB | uint32_t __STREXB (uint8_t value, uint8_t *addr)   |

| CLREX  | void __CLREX (void)                                |

例 :

```

uint16_t value;

uint16_t *address = 0x20001002;

value = __LDREXH (address);      // load 16-bit value from memory address

0x20001002

```

## 2.4 例外モデル

このセクションでは、例外モデルについて説明します。次の内容を説明します。

- [例外状態](#)を参照してください。

- [例外のタイプ](#)を参照してください。

- [41 ページの例外ハンドラ](#)を参照してください。

- [42 ページのベクタテーブル](#)を参照してください。

- [43 ページの例外の優先度](#)を参照してください。

- [43 ページの割込み優先度のグループ化](#)を参照してください。

- [44 ページの例外の開始と復帰](#)を参照してください。

### 2.4.1 例外状態

各例外は、次のいずれかの状態です。

|                   |                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------|

| <b>非アクティブ</b>     | 例外はアクティブでも保留中でもありません。                                                                   |

| <b>ペンディング</b>     | 例外はプロセッサによる処理の待機中です。                                                                    |

|                   | ペリフェラルまたはソフトウェアからの割込み要求により、対応する割込みの状態が保留中に変化することがあります。                                  |

| <b>アクティブ</b>      | 例外はプロセッサにより処理中で、完了していません。<br>注：例外ハンドラは、他の例外ハンドラの実行に割り込むことができます。この場合、両方の例外がアクティブ状態になります。 |

| <b>アクティブかつ保留中</b> | 例外はプロセッサにより処理中であり、さらに同じソースの別の例外が保留中です。                                                  |

### 2.4.2 例外のタイプ

例外のタイプを次に示します。

|             |                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>リセット</b> | リセットは、パワーアップまたはウォーム・リセットによって起動されます。例外モデルでは、リセットは特殊な形式の例外として扱われます。リセットがアサートされると、命令のどの時点においても、プロセッサの動作が停止します。リセットがネゲートされると、ベクタ・テーブルのリセット・エントリにより提供されるアドレスから実行が再開されます。実行は、スレッド・モードで特権実行として再開されます。                                                     |

| <b>NMI</b>  | ノンマスカブル割込み（NMI）は、ペリフェラルからの信号またはソフトウェアからのトリガによって発生します。これは、リセット以外では、優先度が最も高い例外です。常に有効であり、優先度は -2 に固定されています。NMI は、 <ul style="list-style-type: none"> <li>• 他の例外によって、マスクされたり、アクティブ化を妨げられることはありません。</li> <li>• リセット以外の例外によって横取りされることはありません。</li> </ul> |

|                  |                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| <b>HardFault</b> | ハード・フォルトは、通常処理または例外処理でのエラーが原因で発生する例外です。ハード・フォルトの優先度は -1 に固定されています。これは、設定可能な優先度を持つ他の例外よりも優先度が高いことを意味します。                      |

| <b>SVCALL</b>    | <i>Supervisor Call</i> (スーパーバイザ・コール) (SVC) は、SVC 命令によりトリガされる例外です。OS 環境では、アプリケーションは SVC 命令を使用して OS カーネル関数やデバイス・ドライバにアクセスできます。 |

| <b>PendSV</b>    | PendSV は割込み駆動のシステムレベル・サービス要求です。OS 環境では、他にアクティブな例外が存在しない場合に PendSV を使用してコンテキストを切り替えます。                                        |

| <b>SysTick</b>   | SysTick 例外は、システム・タイマが 0 に達したときに生成する例外です。ソフトウェアで SysTick 例外を生成することもできます。OS 環境では、プロセッサはこの例外をシステム・ティックとして使用できます。                |

| <b>割込み (IRQ)</b> | 割込み (IRQ) は、ペリフェラルによる信号またはソフトウェアの要求によって生成される例外です。割込みはすべて、命令の実行に対して非同期です。システム内で、ペリフェラルは割込みを使用してプロセッサとやりとりします。                 |

表 19. さまざまな例外タイプのプロパティ

| 例外番号 <sup>(1)</sup> | IRQ<br>番号 <sup>(1)</sup> | 例外のタイプ     | 優先順位                | ベクタアドレス <sup>(2)</sup>       | アクティブ化               |

|---------------------|--------------------------|------------|---------------------|------------------------------|----------------------|

| 1                   | -                        | リセット       | -3、最高               | 0x00000004                   | 非同期                  |

| 2                   | -14                      | NMI        | -2                  | 0x00000008                   | 非同期                  |

| 3                   | -13                      | HardFault  | -1                  | 0x0000000C                   | 同期                   |

| 4                   | -12                      | MemManage  | 設定可能 <sup>(3)</sup> | 0x00000010                   | 同期                   |

| 5                   | -11                      | BusFault   | 設定可能 <sup>(3)</sup> | 0x00000014                   | 正確な場合は同期、不正確な場合は、非同期 |

| 6                   | -10                      | UsageFault | 設定可能 <sup>(3)</sup> | 0x00000018                   | 同期                   |

| 7~10                | -                        | 予約済みです。    | -                   | -                            | -                    |

| 11                  | -5                       | SVCALL     | 設定可能 <sup>(3)</sup> | 0x0000002C                   | 同期                   |

| 12~13               | -                        | 予約済みです。    | -                   | -                            | -                    |

| 14                  | -2                       | PendSV     | 設定可能 <sup>(3)</sup> | 0x00000038                   | 非同期                  |

| 15                  | -1                       | SysTick    | 設定可能 <sup>(3)</sup> | 0x0000003C                   | 非同期                  |

| 15                  | -                        | 予約済みです。    | -                   | -                            | -                    |

| 16 以上               | 0 以上                     | 割込み (IRQ)  | 設定可能 <sup>(4)</sup> | 0x00000040 以上 <sup>(5)</sup> | 非同期                  |

1. ソフトウェア層を単純化するため、CMSIS は IRQ 番号のみを使用します。割込み以外の例外には負の値を使用します。IPSR は、例外番号を返します。[23 ページの割込みプログラム・ステータス・レジスタ](#) を参照してください。

2. 詳細については、[図 10 : 42 ページのベクタテーブル](#) を参照してください。

3. [199 ページのシステム・ハンドラ優先度レジスタ](#) を参照してください。

4. [185 ページの割込み優先度レジスタ](#) を参照

5. 4 ずつ増加します。

リセット以外の非同期例外の場合、プロセッサは、例外がトリガされてから例外ハンドラを開始するまでに、追加の命令を実行できます。

特権ソフトウェアは、40 ページの表 19 で優先度設定可能と記載されている例外を無効にできます。

- 201 ページのシステム・ハンドラ制御およびステート・レジスタ

- 183 ページの割込みクリア・イネーブル・レジスタを参照してください。

ハード・フォールト、メモリ管理フォールト、バス・フォールト、用法フォールトの詳細については、[セクション 2.5 : 46 ページのフォールト処理](#)を参照してください。

### 2.4.3 例外ハンドラ

プロセッサは、以下を使用して例外を処理します。

**割込みサービス・ルーチン (ISR)**      IRQ0 ~ IRQ239 の割込みは、ISR が処理する例外です。

**フォールト・ハンドラ**      ハード・フォールト、メモリ管理フォールト、用法フォールト、およびバス・フォールトは、フォールト・ハンドラによって処理されるフォールト例外です。

**システム・ハンドラ**      NMI、PendSV、SVCall、SysTick、およびフォールト例外はすべて、システム・ハンドラが処理するシステム例外です。

## 2.4.4 ベクターテーブル

ベクターテーブルには、スタック・ポインタのリセット値、およびすべての例外ハンドラの開始アドレス（例外ベクタとも呼ばれます）が格納されています。[42 ページの図 10](#) に、ベクターテーブルの例外ベクタの順序を示します。各ベクタの最下位ビットは、例外ハンドラが Thumb コードであることを示す、1 である必要があります。[24 ページのThumb 状態](#) を参照してください。

図 10. ベクターテーブル

| 例外番号 | IRQ 番号 | オフセット  | ベクタ        |

|------|--------|--------|------------|

| 255  | 239    | 0x03FC | IRQ239     |

| .    | .      | .      | .          |

| 18   | 2      | 0x004C | IRQ2       |

| 17   | 1      | 0x0048 | IRQ1       |

| 16   | 0      | 0x0044 | IRQ0       |

| 15   | -1     | 0x0040 | SysTick    |

| 14   | -2     | 0x003C | PendSV     |

| 13   |        | 0x0038 | 予約済み       |

| 12   |        |        | デバッグ用に予約済み |

| 11   | -5     | 0x002C | SVCall     |

| 10   |        |        | 予約済み       |

| 9    |        |        |            |

| 8    |        |        |            |

| 7    |        |        |            |

| 6    | -10    | 0x0018 | 用法フォールト    |

| 5    | -11    | 0x0014 | バス・フォールト   |

| 4    | -12    | 0x0010 | メモリ管理フォールト |

| 3    | -13    | 0x000C | ハード・フォールト  |

| 2    | -14    | 0x0008 | NMI        |

| 1    |        | 0x0004 | リセット       |

|      |        | 0x0000 | SP 初期値     |

MSv39645V1

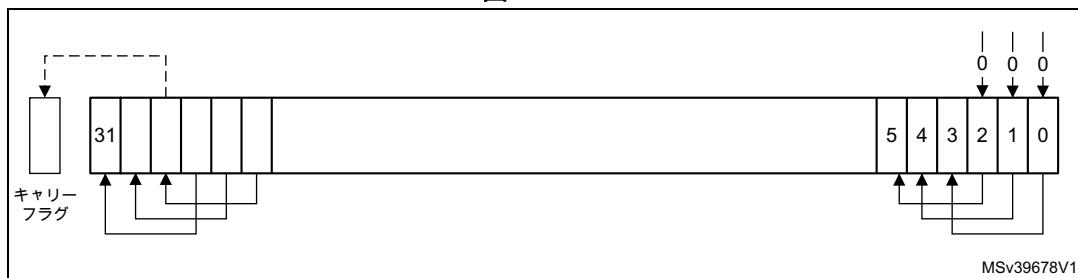

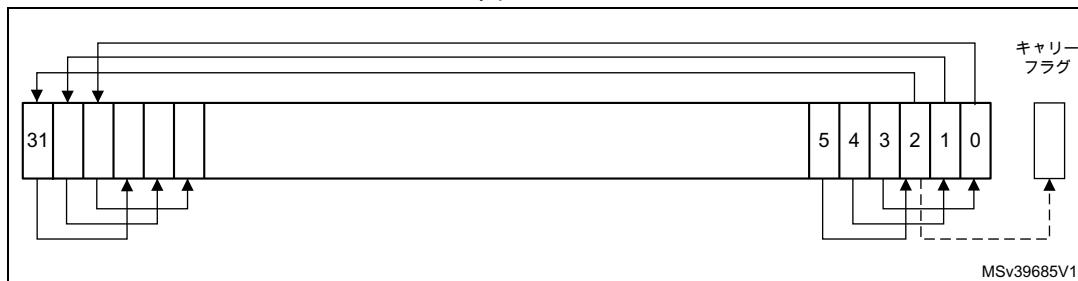

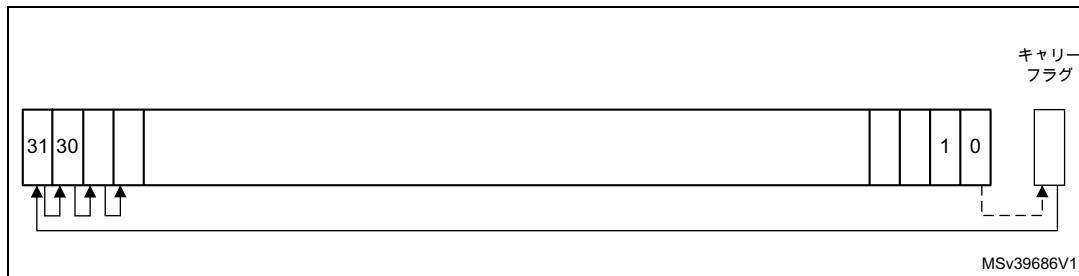

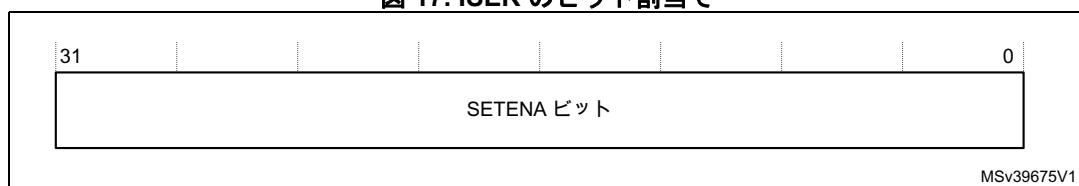

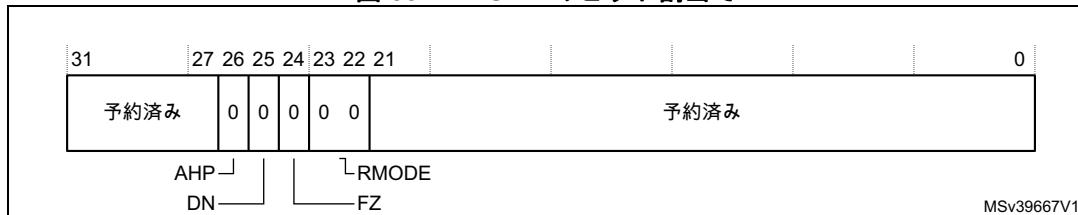

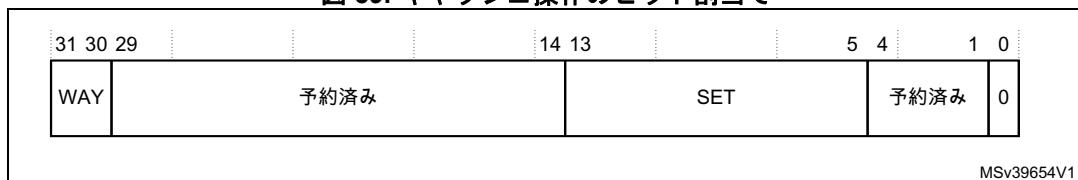

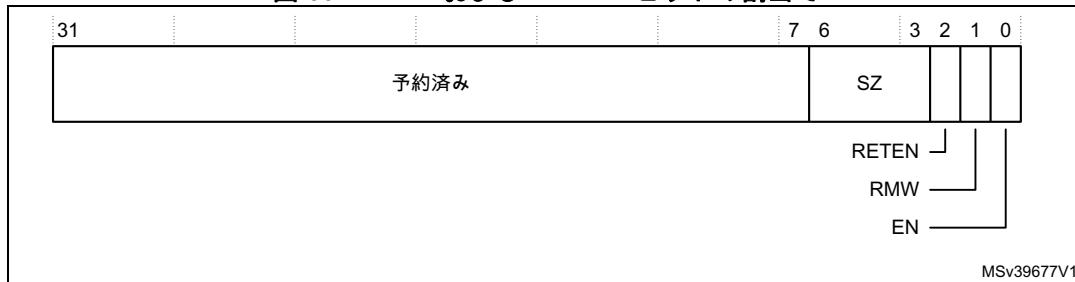

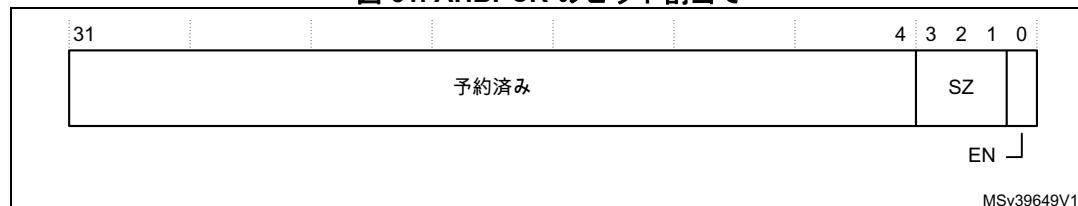

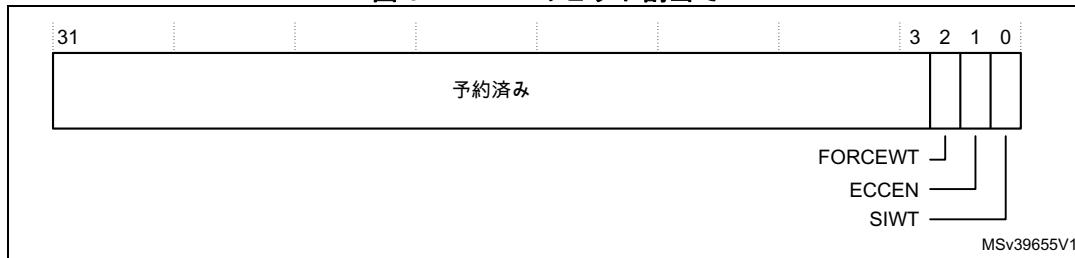

システム・リセット時のベクターテーブル・アドレスは 0x00000000 です。特権ソフトウェアは、VTOR への書き込みによって、ベクターテーブルの開始アドレスを 0x00000000 ~ 0xFFFFFFF80 の範囲の別のメモリ位置に再配置できます。