## 使用 4 引脚 MOSFET 的优势

Antonino Gaito, Marc Laudani, Massimo Nania, Cristiano Gianluca Stella

## 简介

电源设计对整个系统的电气效率和对处理所有功率转化的半导体器件的结温越来越重视。

迄今为止，在所有的半导体器件中，晶体管是最重要的一种，几乎所有的晶体管都是三个引脚器件（MOSFET, BJT, IGBT），相对于二极管，它们具有一个驱动部分，这使它们对功率操作和输入信号之间相互作用的问题更为敏感。虽然这份应用笔记重点描述功率 MOSFET，在某些情况下，根据被切换的电流能力和切换速度，其结果也适用其他的功率晶体管。这个文档的目的是要说明三引脚器件的局限性，以及详细描述使用第四驱动引脚，也被称为开尔文源极（Kelvin source）的优点。

对一个三引脚器件而言，每一个开关周期（开通或关断），源极配线的杂散电感加上开关电流斜率会产生一个与 MOSFET 驱动电压信号 ( $V_{GS}$ ) 相反的电压信号。此电压信号减缓了开关速度，增加了每个周期的开关损耗。开尔文源极的引入允许该驱动信号，也就是指到开尔文源极的驱动网络从 功率路径分离开。在这种情况下，有可能获得一个不受功率路径上非常大的和快速变化的电流的任何干扰的驱动信号。其结果是减少晶体管的总功率损耗，获得较低的工作温度，而且更可靠和更持久的电源系统。

## 目录

|          |                                              |           |

|----------|----------------------------------------------|-----------|

| <b>1</b> | <b>描述</b>                                    | <b>3</b>  |

| 1.1      | 采用的研究方法                                      | 4         |

| 1.2      | 寄生电感的影响                                      | 7         |

| 1.2.1    | 关断过程                                         | 10        |

| 1.2.2    | 开通过程                                         | 11        |

| 1.3      | 3引脚器件和4引脚器件的效率和器件表面温度, 以及在不同输出功率时开通和关断损耗对比分析 | 12        |

| <b>2</b> | <b>开通损耗和关断损耗: 实验波形</b>                       | <b>15</b> |

| <b>3</b> | <b>结论</b>                                    | <b>17</b> |

| <b>4</b> | <b>参考文献</b>                                  | <b>17</b> |

| <b>5</b> | <b>修订版本</b>                                  | <b>18</b> |

## 1 描述

以下文件的目的是要分析评估意法半导体 MDmeshM5 超结 MOSFET 的性能，该器件采用额外驱动引脚的 TO247-4 引线封装。

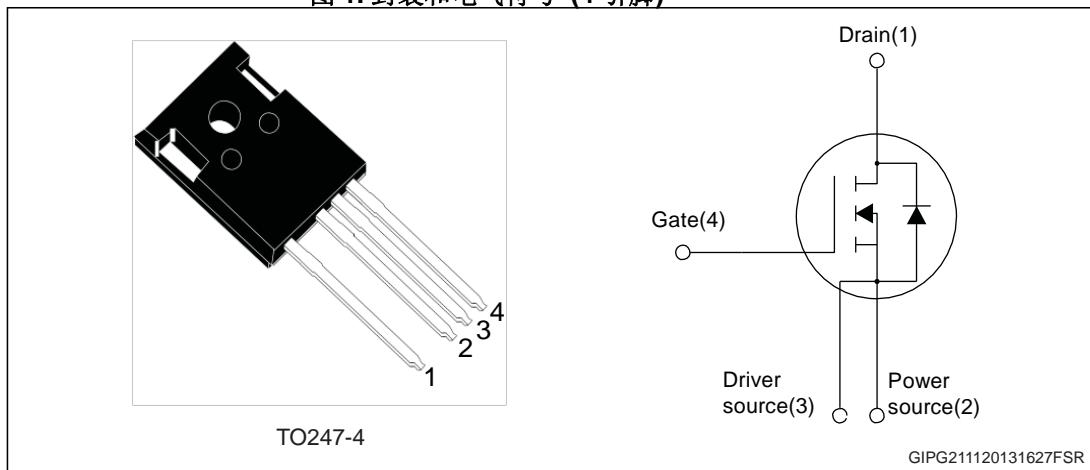

新器件的电气符号和封装见图 1。注意重新定位的漏极，源极和栅极，以及引入的开尔文引脚（引脚 3），引脚间始终确保正确的爬电距离。

图 1. 封装和电气符号 (4 引脚)

演示电源板（图 2）用于测试，它是用于工业应用的 2 千瓦的 PFC，采用了 ST 的专利技术 FOT（固定关断时间）控制。PFC 工作在 CCM 模式，可直接从交流电源 185 和 265 V<sub>RMS</sub> 之间提供一个 400 V 的稳定直流总线。之所以选择这个系统，因为它可以分析开关系统的寄生效应，此外，CCM 的工作模式允许在开通和关断切换过程中作分析。表 1 显示了主要的电气规格。

表 1. 电气规格

| Parameter                    | Value                                           |

|------------------------------|-------------------------------------------------|

| V <sub>in</sub>              | from 185 V <sub>ac</sub> to 265 V <sub>ac</sub> |

| Line frequency               | 50 Hz                                           |

| Output voltage               | 400 V <sub>dc</sub>                             |

| Max output voltage           | 2000 W                                          |

| Output voltage ripple        | 5%                                              |

| Max switching frequency      | 55 kHz                                          |

| Ripple (Kr) inductor current | 0.25                                            |

| IC in used                   | L6563                                           |

图 2. 使用 TO247-4 (4 引脚) 的 PFC 2 kW 演示板

GIPG211120131727FSR

## 1.1 采用的研究方法

通常，在电子供电系统，反馈网络用来实现对电气参数的控制（对 DC / DC 变换器而言，这可以是输出电压和输出电流或其中的一个）。为了控制系统中的电流，电阻器通常被串联连接到被控制的回路中，形成输入和输出网络之间的公共路径。从该元件传来的信息，传感电阻器上的电压信号被用作控制信号，并发送至驱动器的引脚。该引脚连接到驱动器内的内部比较器的一个输入端，它的输出信号被用于调节功率开关的导通时间。

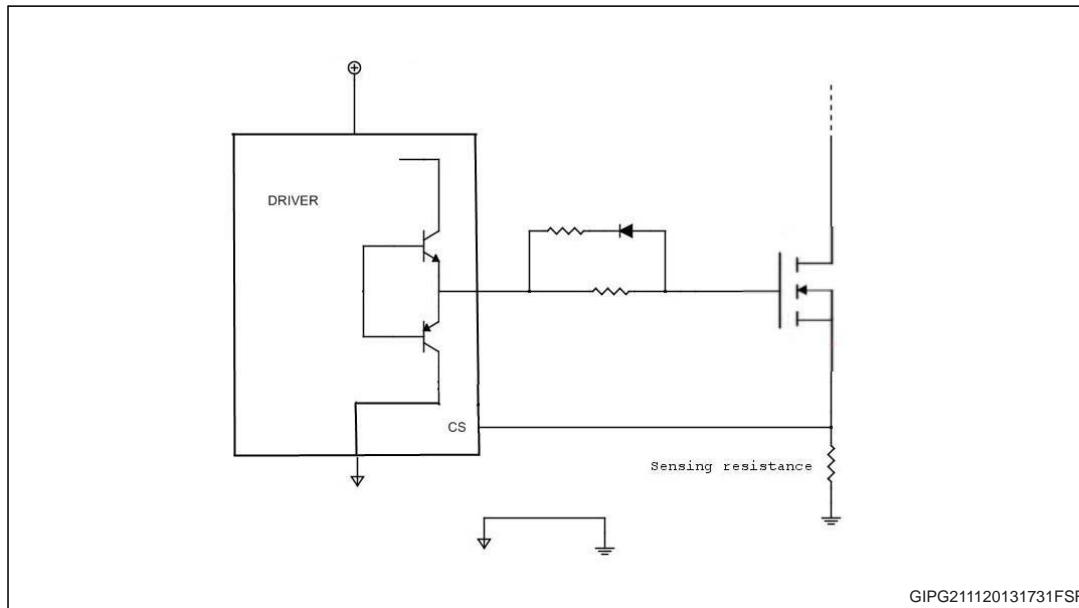

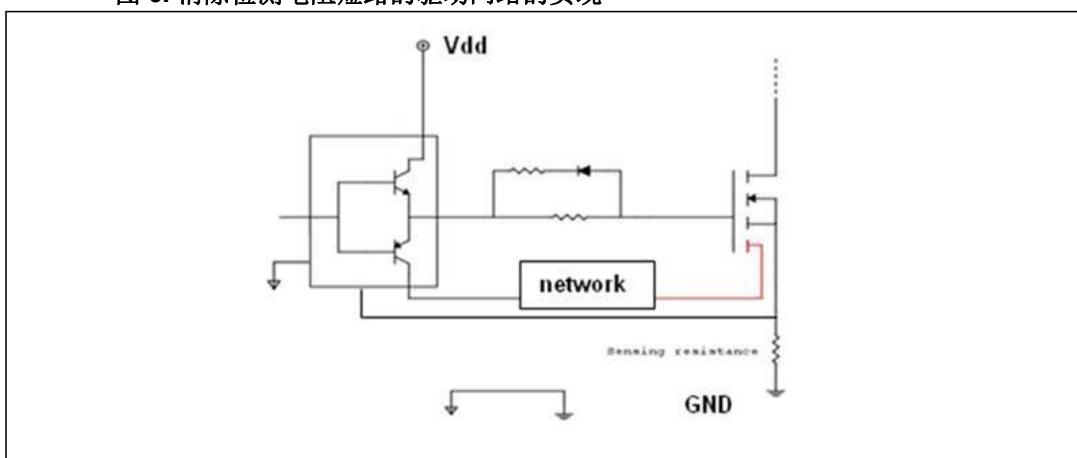

当电源开关需要特定的源/灌电流（sink/source），驱动器由推挽作输出（图 3）。这是电流采样反馈网络，好处是增加了输入阻抗，而缺点在于输出网络对驱动电路的影响。减小这一缺点的一种可能的方法是将输入电路从输出网络分开，这就是由意法半导体提出的方案。

图 3. 功率器件推挽驱动原理图

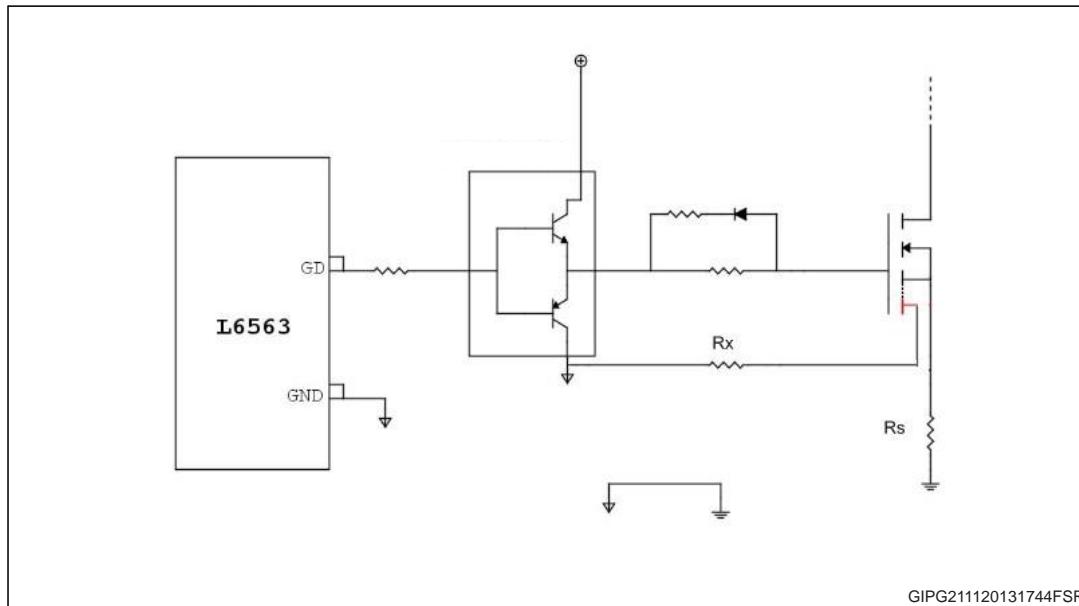

电流放大器可以直接集成在驱动器内部或与驱动器输出串联置于外部。该解决方案用于意法半导体的演示板。演示板用 L6563 作驱动，一个电阻器与功率器件的源极串联，来检测信号用作电流控制（图 4）。

图 4. L6563 和推挽相连作为驱动的原理图

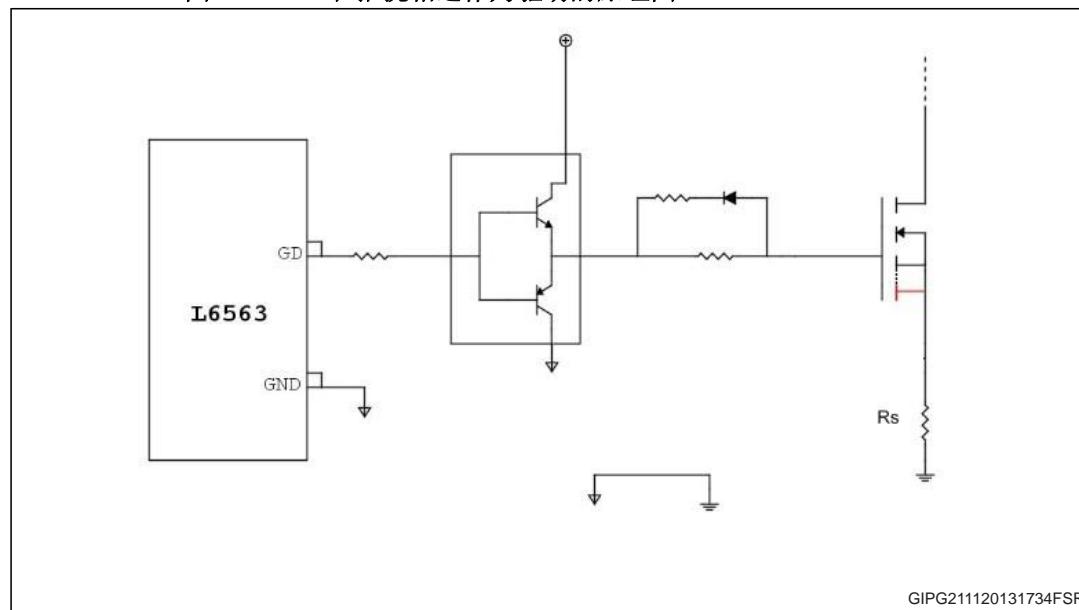

为了正确使用添加了感测引脚的新器件，该方案必须对驱动网络稍作修改。事实上，如果我们用 4 引脚版本（T0247-4）直接替代标准的 3 引脚 T0-247 MOSFET，我们就可能短路检测电阻和丢失来自检测电阻的任何信息（图 5）。

图 5. 短路检测电阻的风险

图 6 表明，由于推挽缓冲电路的接地和感应源极引脚连接，并且由于电源引脚在内部与它短路，造成检测电阻的短路。

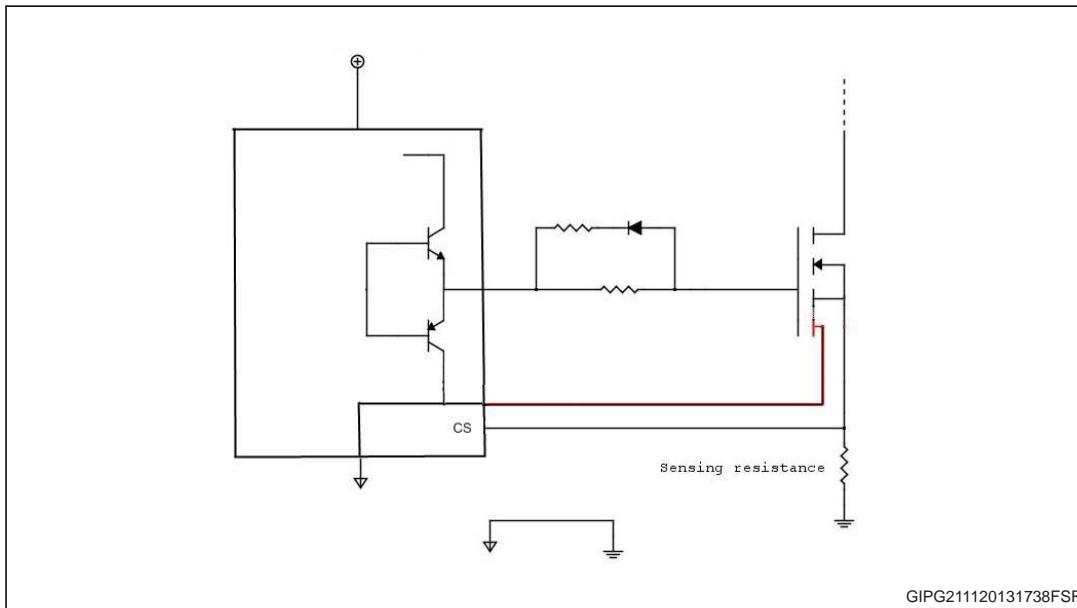

所以，当采用 4 引脚封装的器件时，必须使用特别的措施来保持系统的正常功能（图 6）。

图 6. 消除检测电阻短路的驱动网络的实现

下面的解决方案在 ST 演示板上得以实现：

- 在系统中，检测电阻  $Rs$  的值是 18 毫欧（图 4）。

- 当使用 4 引脚的 MOSFET 时，采用如图 7 所示的连接，以消除检测电阻  $Rs$  短路的可能性。

图 7. 演示板相关驱动网络部分

重要的是, 相对于流过检测电阻  $R_s$  的电流, 流过  $R_x$  的电流是可以忽略的。因此,  $R_x$  选择一个  $1\Omega$  电阻。

## 1.2 寄生电感的影响

一般, 在驱动快速开关器件超结 MOSFET 时, 有必要减少封装的影响和由于布局引入的寄生效应。通常检测的是低电压大电流的 MOSFET, 对这方面的要求是众所周知的。但是, 当使用一个高电压器件时, 其中间隙和爬电距离的要求时必须考虑时, 会发生什么呢?

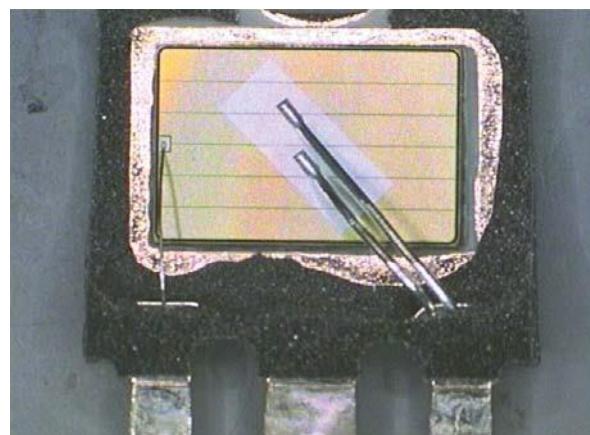

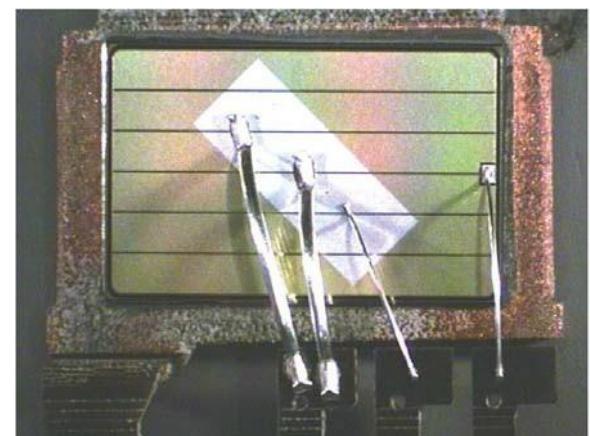

本章节演示单源极引脚的寄生电感的影响, 该引线与管芯(图 8 和图 9)相连。

封装的影响是由内部引线键合所限制。有几种方法来计算此效应的大小, 首先分析导线的寄生电感。

图 8. 功率器件引线键合图

GIPG211120131748FSR

图 9. 4 引脚功率器件引线键合图

GIPG211120131751FSR

如果我们用如下等式:

等式 1

$$L = l \left( \ln \frac{4l}{d} - 1 \right) \times 200 \times 10^{-9}$$

$l$  是引线的长度,  $d$  是引线的直径, 我们可以估计单一源极键合引线的杂散电感:

等式 2

$$l \approx 12 \times 10^{-3} \text{m}$$

$$d = 15 \text{ mls} = 0.381 \times 10^{-3} \text{m}$$

等式 3

$$L = I \left( \ln \frac{4l}{d} - 1 \right) \times 200 \times 10^{-9} \approx 9.2 \text{nH}$$

第二种用来估算  $L_s$  的方法是使用仿真工具。通过对键合引线的长度和截面的因子分解，HFSS 电磁模拟器工具能给出结果如下：

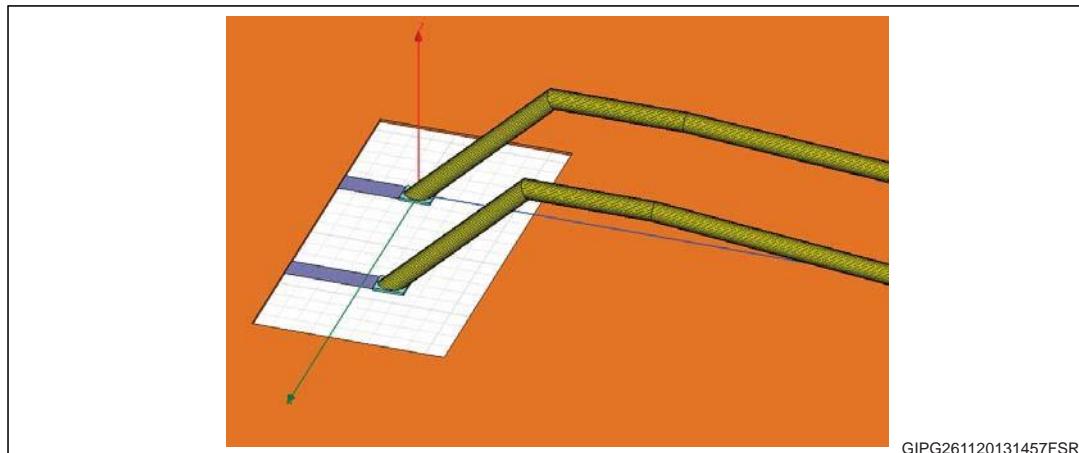

图 10. HFSS 工具分析键合引线

在这事例中，仿真数值为 8.9 nH.

此数据在实验室得到测量证实，Figure 11 表示的寄生电感在 4 nH 左右，因为在源极有两根导线平行使用。

Figure 11. Wires bonding for the HFSS tool

鉴于这些数据，我们可以继续研究其对系统的影响。

在了解寄生电感对开关换向影响之前，我们先考虑感性负载的切换：寄生效应的影响与切换阶段的电流斜率以及切换时间相关。

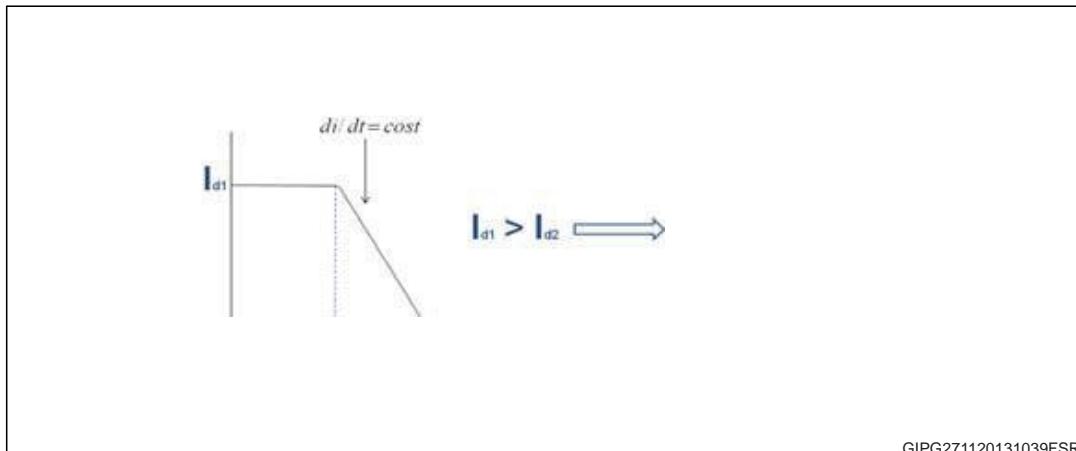

也就是说，对于一个固定值的  $L_d$ ，（当  $di / dt$  为常数），当输出功率增加，并且开关电流也增加时，延迟时间就越明显（图 12）。

图 12. 电感寄生效应和电流开关的关系

这个理论上的情形由开关瞬间关断开通时的实验数据得到证实。

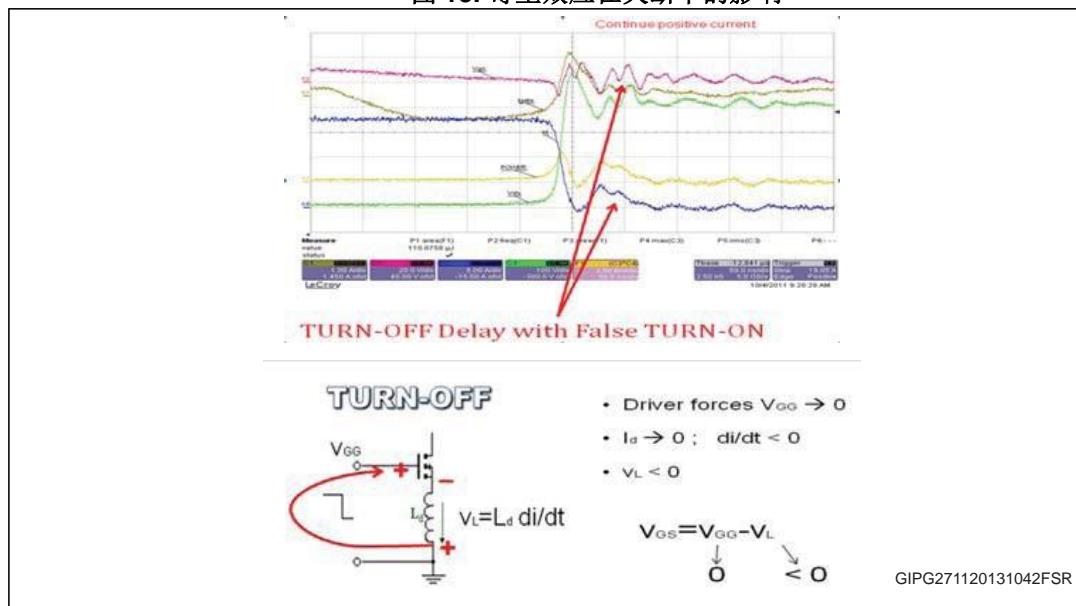

### 1.2.1 关断过程

如果我们参看图 13，显示在高功率下的关断过程，当驱动强迫输出为零  $V_{GG} = 0$  时，MOSFET 被强制关闭，但由于杂散电感所产生的负的额外电压导致关断延迟，因此产生较高的关断开关损耗。这甚至会导致错误的导通现象，从而可以进一步增加关断功率损耗。

图 13. 寄生效应在关断中的影响

事实上，在栅极和源极引脚的实际电压，等于驱动电压和寄生过电压之间的差，变为正值，完全等同于所产生的额外电压。

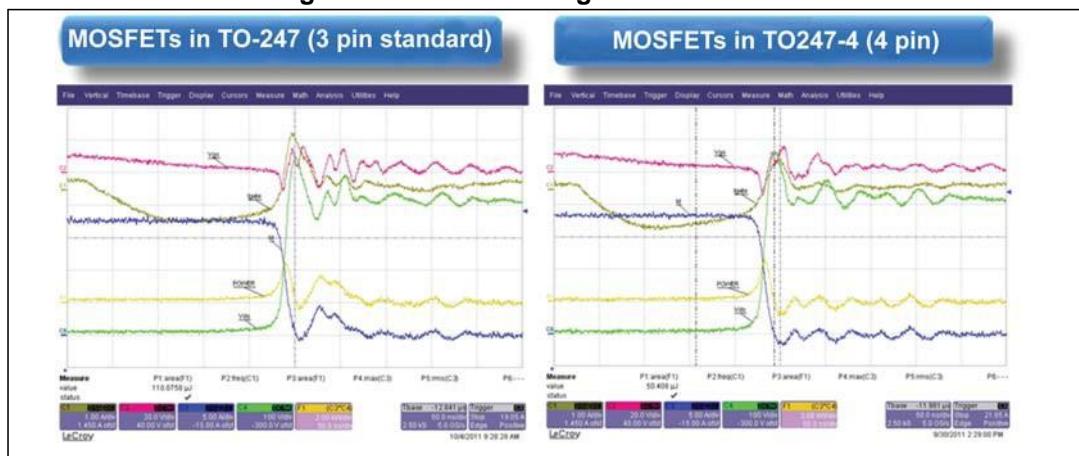

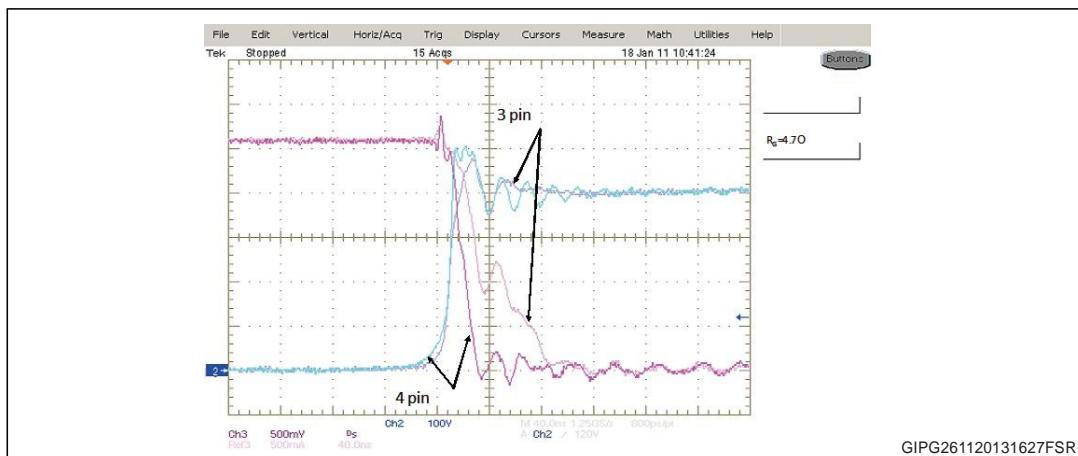

这一方面是通过标准的 3 引脚方案与 4 引脚方案之间的波形比较得到证实。在图 14 中，表示该具体方面。

图 14. 3 引脚器件和 4 引脚器件关断性能比较

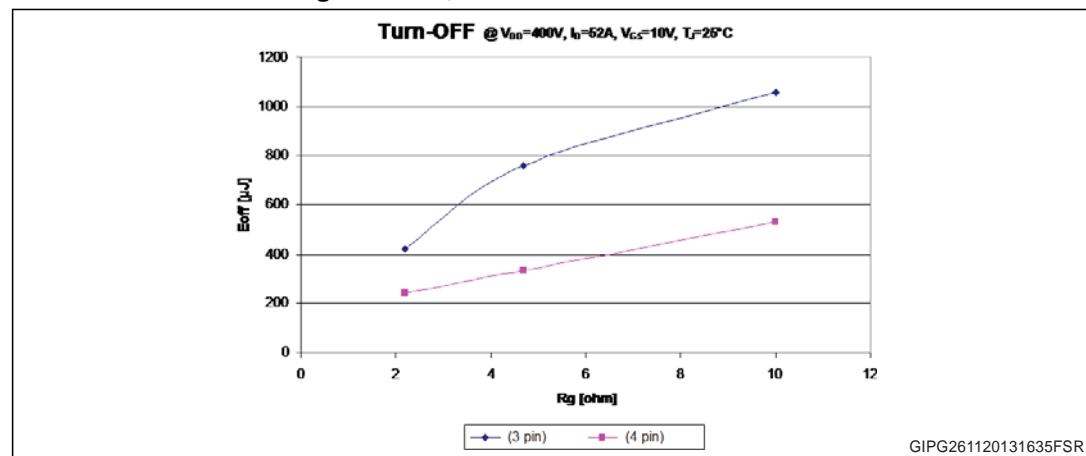

当改变  $R_{GATE}$  阻值，加速或延迟关断，可以改善减少功率损耗。

图 15. 不同  $R_g$  电阻值下，关断损耗比较

## 1.2.2 开通过程

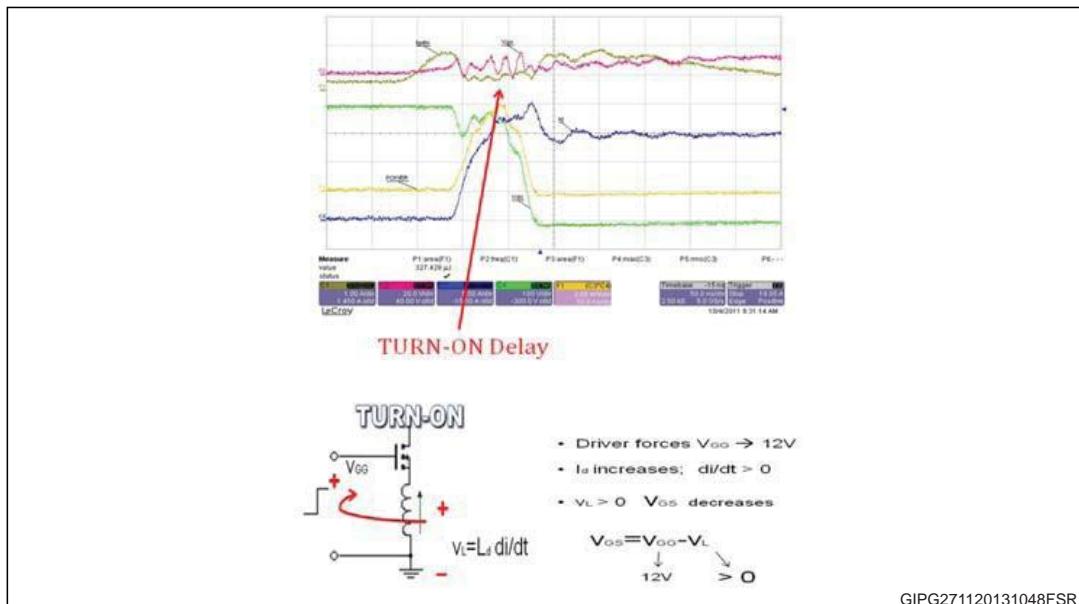

同样在开通时，当强制驱动  $V_{GG}=12$  V，MOSFET 导通，在杂散电感产生的正的额外电压导致开启延迟，降低了  $V_{GS}$  的有效值，产生更高的开关损耗，增加总开关功率耗散（图 16）

图 16. 寄生效应在开通过程中的影响

在这种情况下，因为负的额外电压的产生，所以在栅极和源极间的实际电压变得比设定的完全开通该器件的阈值电压要低。这一方面通过标准的 3 引脚方案与 4 引脚方案之间的波形比较，在图 17 和图 18 中得到证实。

### 1.3 3 引脚器件和 4 引脚器件的效率和器件表面温度, 以及在不同输出功率时开通和关断损耗对比分析

4 引脚方案的效果是减少晶体管的总功率损失，这意味着更低的操作温度，而且更可靠和更持久的动力系统。在前面的章节中，我们所看到的是寄生电感在单个开关瞬间的影响。为了了解整个系统总的效果，在不同的输出功率等级上对热特性和节能方面作更深入的分析。

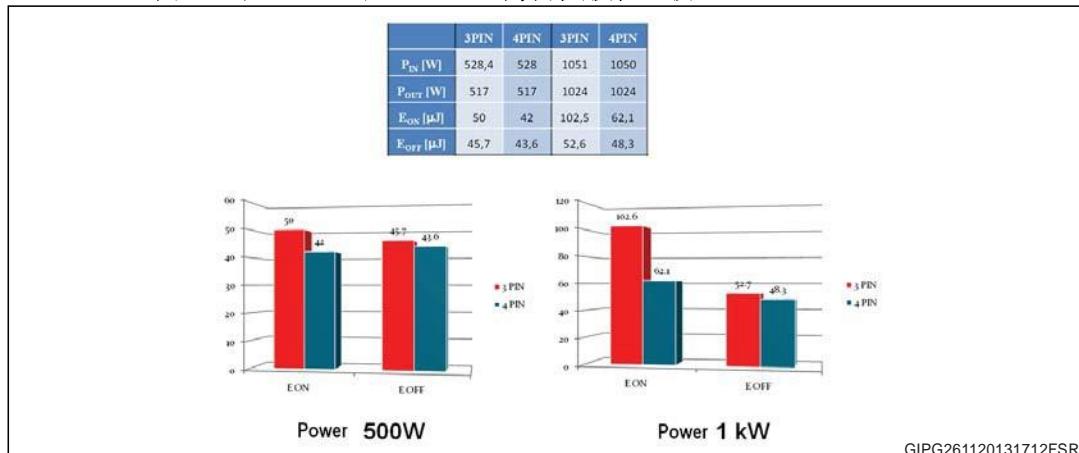

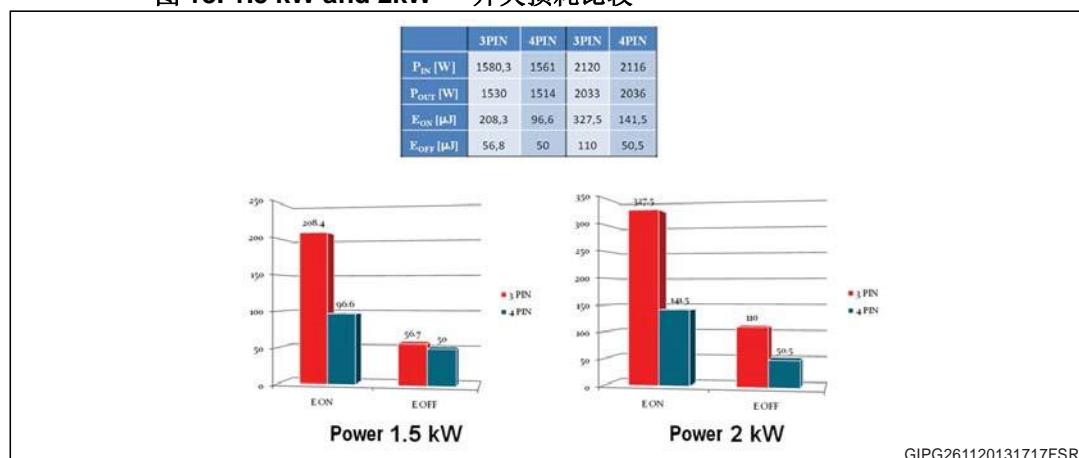

下图给出了在不同的功率等级，同时使用 3 引脚和 4 引脚方案，比较开关损耗数据，

图 17. 在 500 W 和 1 kW<sup>(a)</sup> 下, 开关损耗比较图 18. 1.5 kW and 2kW<sup>(a)</sup> 开关损耗比较

图 17 和图 18 表明，当功率增加，电流值增加时，4 引脚方案具有更大的影响。具体地说，开通损耗的减小是始终存在的，随着功率的增加，而在关断损耗上的降低也更加明显，

因此在整个功率范围内，新的解决方案都有优势，并且市场一直在寻求节能方案，它允许实现新的散热和效率的目标。

a. For MDmesh M5 MOSFETs in TO-247 (3 pin) and MDmesh M5 MOSFETs in TO247-4 (4 pin)

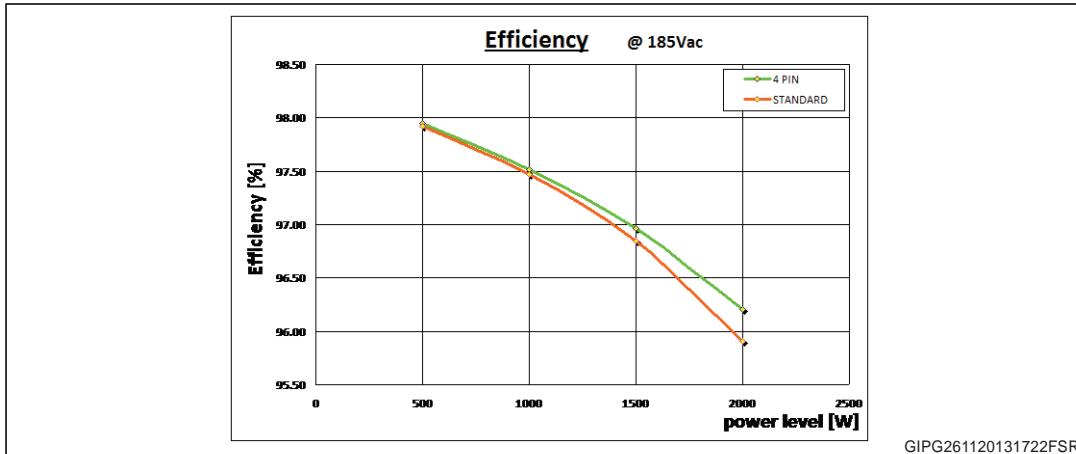

图 19. 不同功率等级下效率比较

在低功率输出时，效率方面的改善是可以忽略不计，但是当功率升高时，就比较明显。在最大功率（2 千瓦），演示板的效率明显提高了 0.32%。

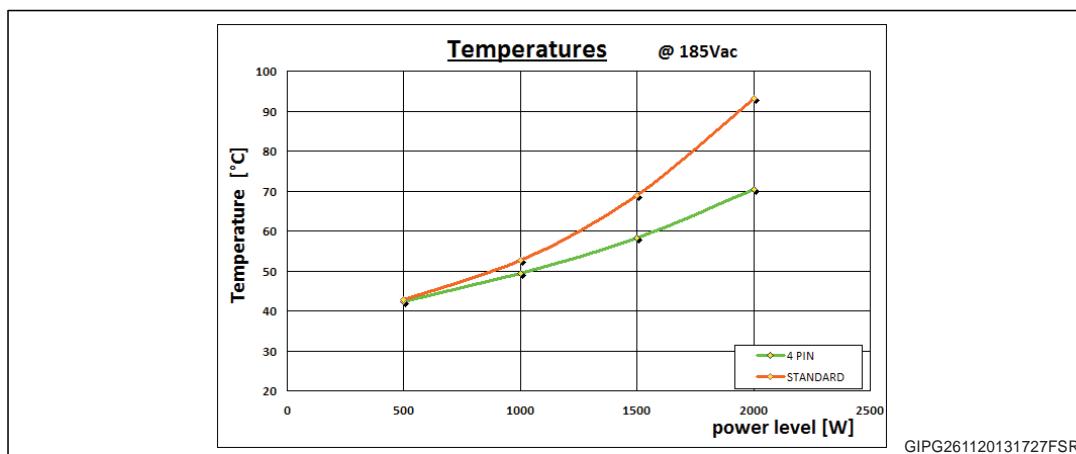

图 20. 不同功率等级下，器件结温比较

从热特性看，器件的温度差异在低功率时已比较明显，在最大负载时相差高达 20°C。

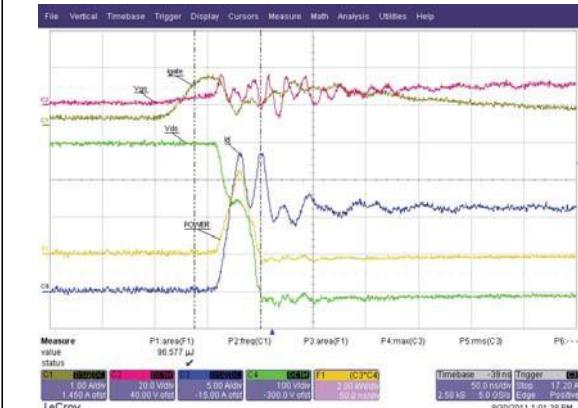

## 2 开通损耗和关断损耗: 实验波形

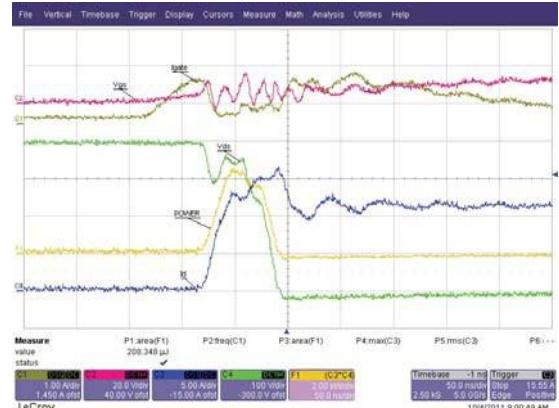

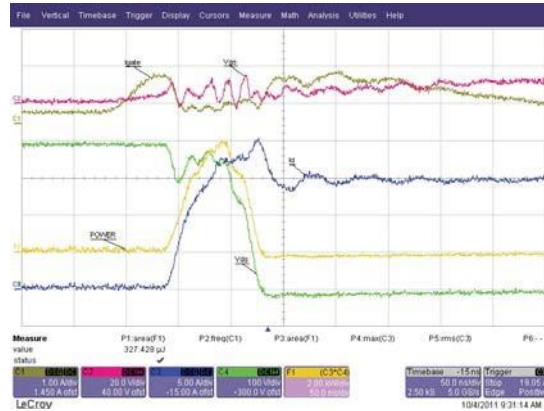

**Figure 21. Waveforms and power losses during the turn-on commutation @ 1.5 kW for MDmesh M5 MOSFETs in TO247-4 (4 pin)**

GIPG271120130959FSR

**Figure 22. Waveforms and power losses during the turn-on commutation @ 1.5 kW for MDmesh M5 MOSFETs in TO247 (3 pin)**

GIPG271120131004FSR

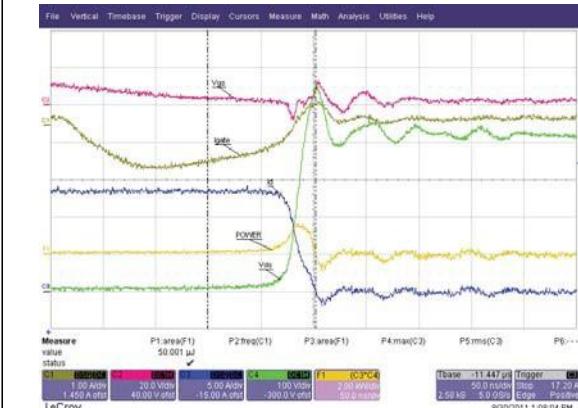

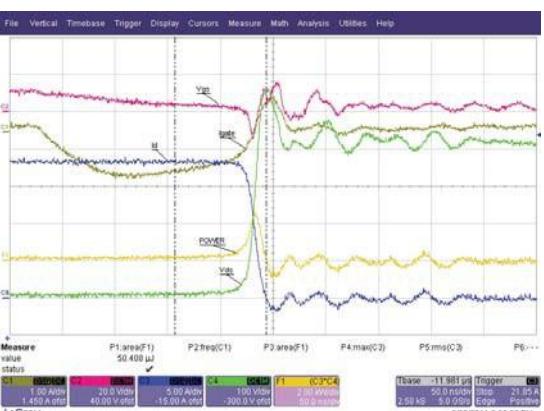

**Figure 23. Waveforms and power losses during the turn-off commutation @ 1.5 kW for MDmesh M5 MOSFETs in TO247-4 (4 pin)**

GIPG271120131007FSR

**Figure 24. Waveforms and power losses during the turn-off commutation @ 1.5 kW for MDmesh M5 MOSFETs in TO247 (3 pin)**

GIPG271120131011FSR

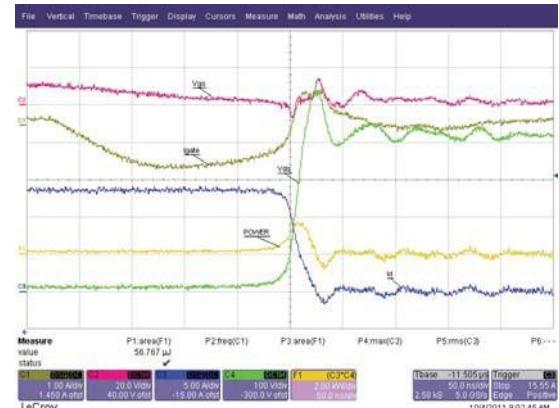

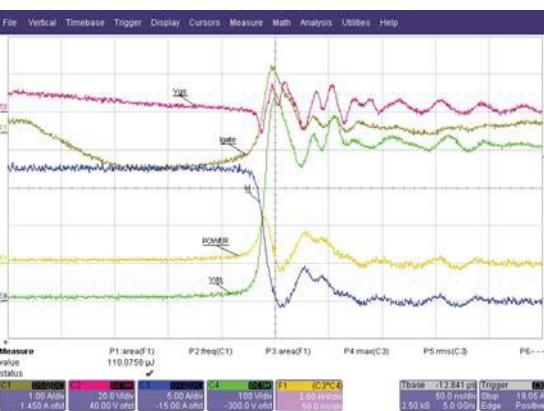

**Figure 25. Turn-on details @ 2 kW for MDmesh M5 MOSFETs in TO247-4 (4 pin)**

GIPG271120131014FSR

**Figure 26. Turn-on details @ 2 kW for MDmesh M5 MOSFETs in TO-247 (3 pin)**

GIPG271120131017FSR

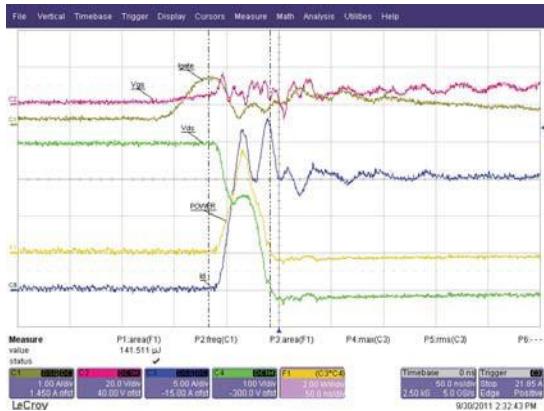

**Figure 27. Turn-off details @ 2 kW for MDmesh M5 MOSFETs in TO247-4 (4 pin)**

GIPG271120131022FSR

**Figure 28. Turn-off details @ 2 kW for MDmesh M5 MOSFETs in TO-247 (3 pin)**

GIPG271120131030FSR

### 3 结论

4 引脚（驱动）方案的引入极大地提高了功率 MOSFET 器件的动态性能，当器件开关电流和输出功率更大时，更加明显。测试结果表明，有驱动源极封装的 MDmesh™M5 器件在关断时，当开关电流大于 10A，好处比较明显，当然其优点适用于所有的功率范围。在不同功率等级，效率也有不同程度的提高。而在应用市场中，功率等级总是不断增加，所以在当今市场竞争非常激烈的条件下，节能系统效率的一个小小提高都代表了很大的优势。

就拿演示板来说，最大输出功率（2 千瓦）时，节能 7 瓦。但是最重要的好处是在于热特性：事实上，一个系统小幅度的功率损耗就被转化为比较大的功率器件温差（20°C 左右）。较低的工作温度允许使用较小的散热片来减少板上空间，更重要的是，可以提高整个系统的可靠性。

### 4 参考文献

1. N. Mohan, T. M. Undeland, W. P. Robbins: "Power Electronics: converters, applications, and design", Second edition, John Wiley & Sons, New York, 1995.

2. Won-suk Choi, Dong-kook Son, Markus Hallenberger and Sungmo Young "Driving and Layout Requirements for Fast Switching MOSFETs."

3. Y. Xiao, H. Shah, T. P. Chow and R. J. Gutmann "Analytical Modeling and Experimental Evaluation of Interconnect Parasitic Inductance on MOSFET Switching Characteristics"

4. Jon Mark Hancock, "Super junction FETs Boost Efficiency in PWMs", in Power Electronics Technology, July 2005, pp. 20-29.

5. G. Sorrentino, M. Melito, F. Chimento, S. Musumeci, A. Raciti "SiC Diodes and MDmesh™ 2nd Generation Devices Improve Efficiency in PFC Applications", Proceedings of the 4th International Conference on Integrated Power Electronics Systems, CIPS 2006, 7-9th June 2006, Napoli, Italy, pp. 195-199.

6. C. Adragna Application Note AN1792, "Design of fixed-off-time-controlled PFC pre-regulators with the L6562", STMicroelectronics, November 2003.

7. STMicroelectronics, AN2951 "3 kW fixed-off-time (FOT) power factor correction", June 2010.

## 5 版本历史

Table 2. 文档版本历史

| 日期         | 版本 | 变更    |

|------------|----|-------|

| 29-01-2015 | 1  | 初始版本。 |

| 07-05-2015 | 2  | 文档小改动 |

Table 3. 中文文档版本历史

| 日期         | 版本 | 变更     |

|------------|----|--------|

| 30-05-2017 | 1  | 中文初始版本 |

**重要通知 - 请仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和/或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用，ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。所有其他产品或服务名称均为其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。本文档的中文版本为英文版本的翻译件，仅供参考之用；若中文版本与英文版本有任何冲突或不一致，则以英文版本为准。

© 2017 STMicroelectronics - 保留所有权利