## 引言

STM32WB系列微控制器集成了用于低功耗蓝牙<sup>®</sup>的高品质RF收发器和802.15.4无线电解决方案。

与传统电路相比，需要特别注意RF板的布局。

在高频率下，铜互联部件（走线）表现为功能电路元件，这些元件会引入可能降低RF性能的干扰。走线和焊盘所产生的寄生成分对电路的整体性能具有显著影响。必须仔细遵循布局规则，以减轻这些影响并实现所需性能。

本文档介绍了为实现MCU的最佳性能而采取的预防措施。该描述基于用于2层PCB的特定QFN48 / QFN68参考板以及用于4层PCB的QFN68 Nucleo板。

这些指南具有通用性，需要根据具体应用进行调整。

# 目录

|          |                              |           |

|----------|------------------------------|-----------|

| <b>1</b> | <b>RF基础知识</b>                | <b>6</b>  |

| 1.1      | 术语                           | 6         |

| 1.1.1    | 功率                           | 6         |

| 1.1.2    | 增益                           | 6         |

| 1.1.3    | 损耗                           | 6         |

| 1.1.4    | 反射系数、电压驻波比和回波损耗              | 6         |

| 1.1.5    | 谐波                           | 7         |

| 1.1.6    | 杂散                           | 7         |

| 1.1.7    | 互调                           | 7         |

| 1.2      | 阻抗匹配                         | 7         |

| 1.3      | 史密斯圆图                        | 7         |

| 1.3.1    | 归一化阻抗                        | 8         |

| 1.3.2    | 读取史密斯圆图                      | 8         |

| <b>2</b> | <b>参考板原理图</b>                | <b>12</b> |

| <b>3</b> | <b>Nucleo板 (MB1355C) 原理图</b> | <b>15</b> |

| <b>4</b> | <b>元件选择</b>                  | <b>21</b> |

| 4.1      | 电容                           | 21        |

| 4.2      | 电感                           | 22        |

| 4.3      | SMPS                         | 23        |

| 4.4      | 外部晶振                         | 24        |

| <b>5</b> | <b>PCB层叠和技术</b>              | <b>25</b> |

| 5.1      | 射频传输线                        | 25        |

| 5.2      | PCB基板选择                      | 25        |

| 5.3      | 2层PCB                        | 26        |

| 5.4      | 4层PCB                        | 27        |

| <b>6</b> | <b>2层PCB的布局建议</b>            | <b>28</b> |

| 6.1      | 关键部件                         | 28        |

| 6.1.1    | RF                           | 28        |

---

|           |                                |           |

|-----------|--------------------------------|-----------|

| 6.1.2     | SMPS                           | 29        |

| 6.1.3     | LSE                            | 30        |

| <b>7</b>  | <b>4层PCB Nucleo板MB1355C</b>    | <b>31</b> |

| 7.1       | 关键部件                           | 37        |

| 7.1.1     | RF                             | 37        |

| 7.1.2     | SMPS                           | 37        |

| 7.1.3     | LSE                            | 38        |

| 7.1.4     | 天线                             | 39        |

| <b>8</b>  | <b>带IPD的UFQFN48/VFQFN68参考板</b> | <b>41</b> |

| <b>9</b>  | <b>结论</b>                      | <b>44</b> |

| <b>10</b> | <b>版本历史</b>                    | <b>45</b> |

## 表格索引

|     |          |    |

|-----|----------|----|

| 表1. | 外部元件     | 12 |

| 表2. | 电容温度范围   | 22 |

| 表3. | 文档版本历史   | 45 |

| 表4. | 中文文档版本历史 | 45 |

# 图片索引

|      |                                                |    |

|------|------------------------------------------------|----|

| 图1.  | 史密斯圆图 .....                                    | 8  |

| 图2.  | 串联 .....                                       | 9  |

| 图3.  | 史密斯导纳圆图 .....                                  | 9  |

| 图4.  | 并联 .....                                       | 10 |

| 图5.  | 有关阻抗和导纳的史密斯圆图 .....                            | 10 |

| 图6.  | 带VSWR的史密斯圆图 .....                              | 11 |

| 图7.  | 通过免费的史密斯软件来调整网络 .....                          | 11 |

| 图8.  | UFQFPN48参考板 .....                              | 13 |

| 图9.  | VFQFPN68参考板 .....                              | 14 |

| 图10. | 原理图 - GPIO和XTAL、MB1355C .....                  | 16 |

| 图11. | 原理图 - RF部分、MB1355C .....                       | 17 |

| 图12. | 原理图 - 外部连接器、MB1355C .....                      | 18 |

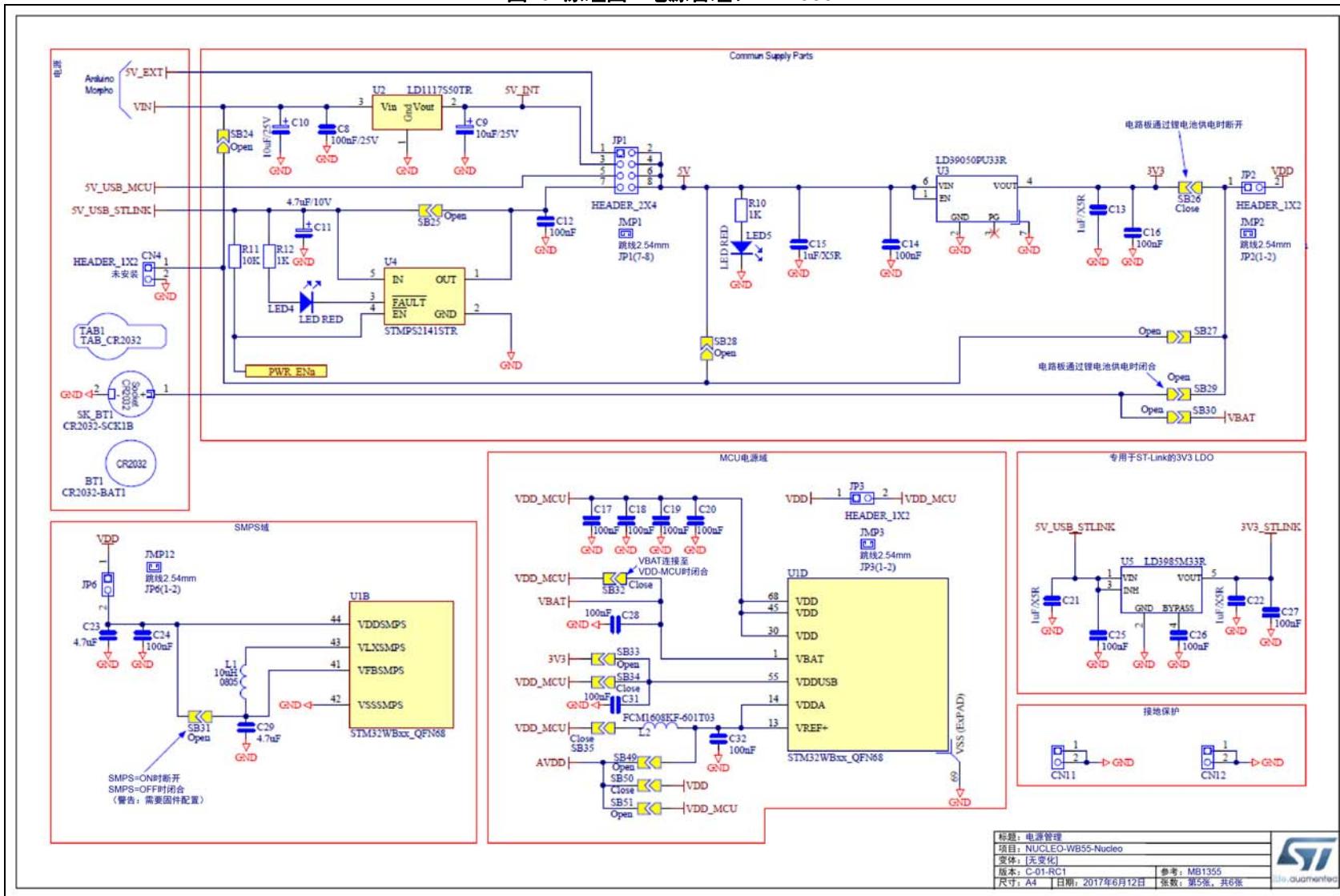

| 图13. | 原理图 - 电源管理、MB1355C .....                       | 19 |

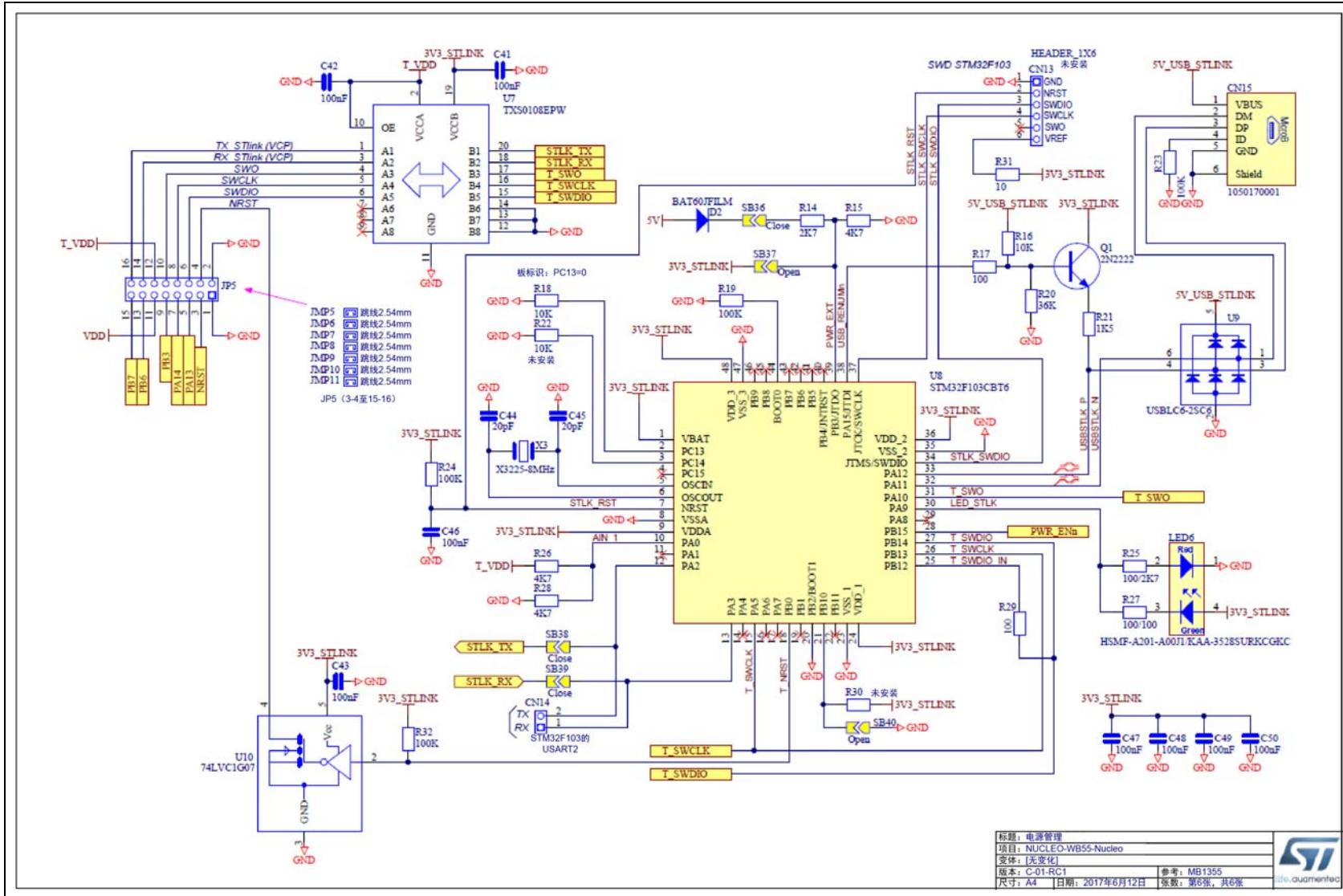

| 图14. | 原理图 - ST LINK、MB1355C .....                    | 20 |

| 图15. | 电容器等效电路 .....                                  | 21 |

| 图16. | 电容器阻抗vs频率 .....                                | 21 |

| 图17. | 电感等效电路 .....                                   | 22 |

| 图18. | 电感器阻抗vs频率 .....                                | 23 |

| 图19. | 外部晶振的连接 .....                                  | 24 |

| 图20. | 共面波导 (CPW) .....                               | 25 |

| 图21. | 2层PCB .....                                    | 26 |

| 图22. | 2层PCB - 用于UFQFPN48和VFQFPN68的参考板 .....          | 26 |

| 图23. | 4层PCB .....                                    | 27 |

| 图24. | 4层PCB - 用于VFQFPN68的Nucleo板 .....               | 27 |

| 图25. | UFQFPN48的PCB布局 (从左到右: 全部、顶层和底层) .....          | 28 |

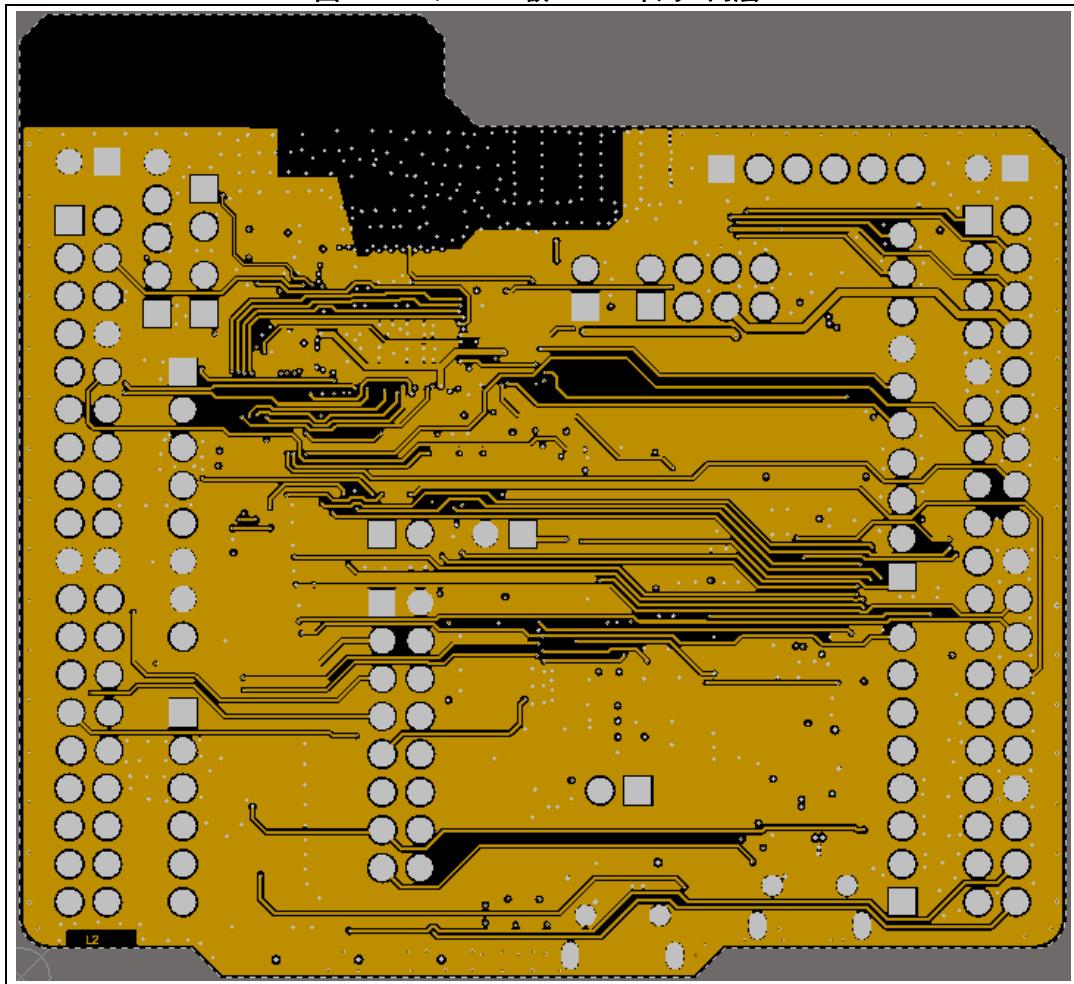

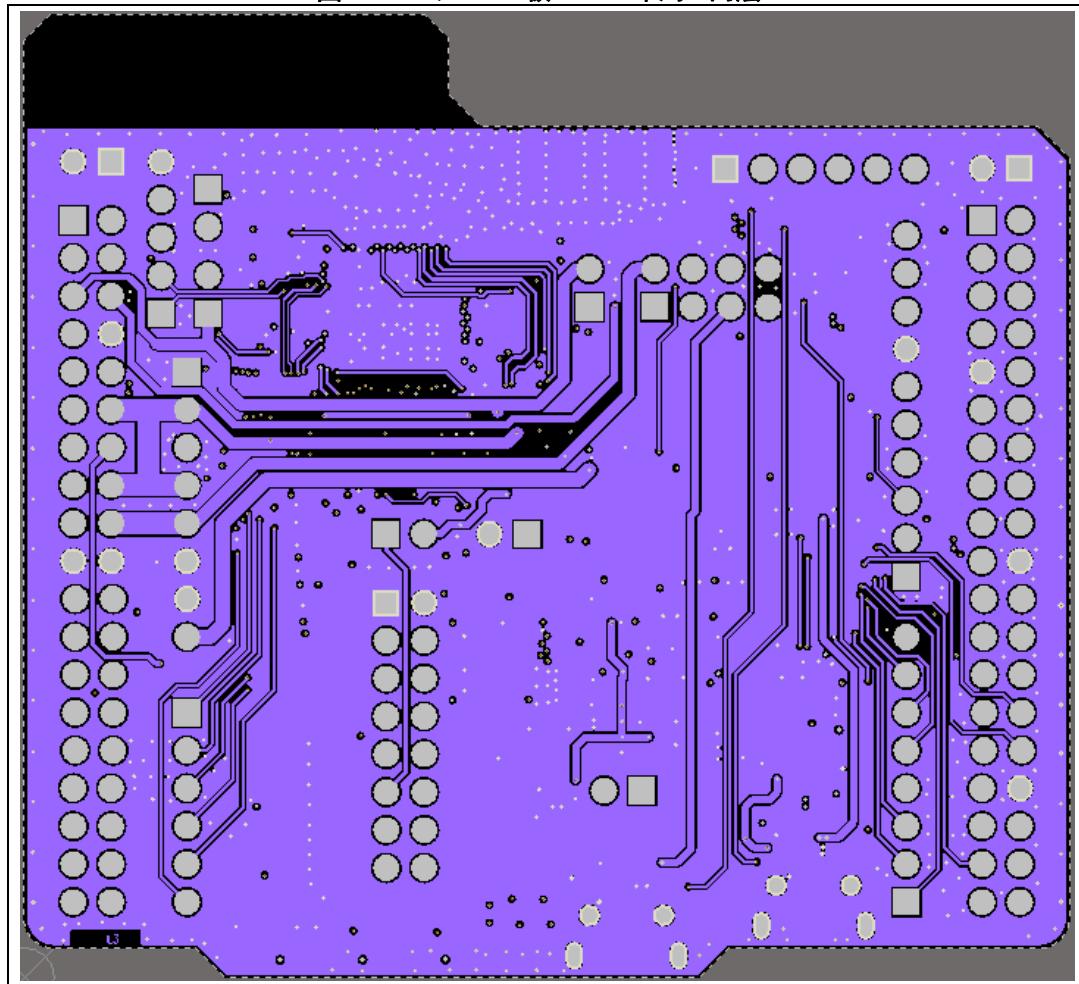

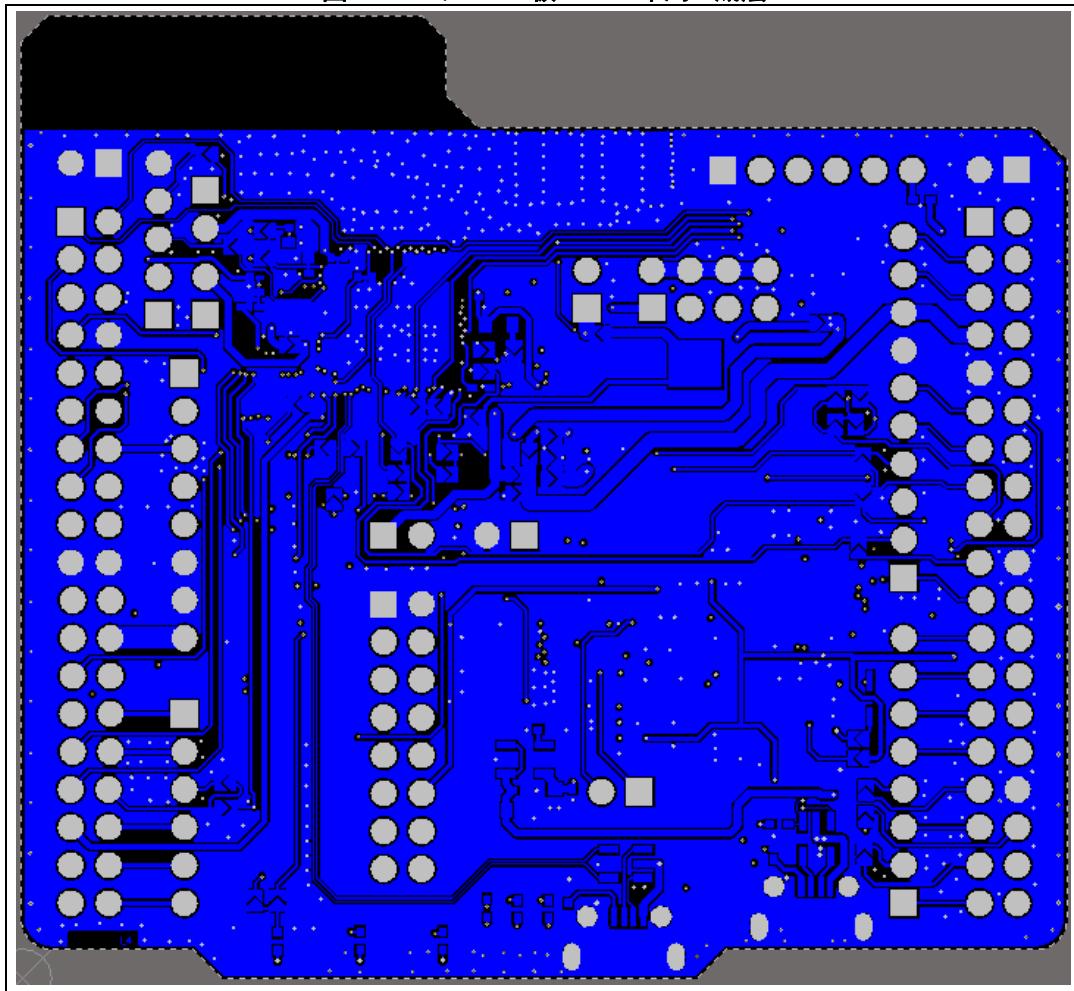

| 图26. | VFQFPN68的PCB布局 (从左到右: 全部、顶层和底层) .....          | 28 |

| 图27. | RF的PCB布局细节 (左侧为UFQFPN48、右侧为VFQFPN68) .....     | 29 |

| 图28. | SMPS部件的PCB布局细节 (左侧为UFQFPN48、右侧为VFQFPN68) ..... | 29 |

| 图29. | LSE的PCB布局细节 (左侧为UFQFPN48、右侧为VFQFPN68) .....    | 30 |

| 图30. | VFQFPN68板 .....                                | 31 |

| 图31. | VFQFPN68板 - PCB布局 - 所有层 .....                  | 32 |

| 图32. | VFQFPN68板 - PCB布局 - 顶层 .....                   | 33 |

| 图33. | VFQFPN68板 - PCB布局 - 内层1 .....                  | 34 |

| 图34. | VFQFPN68板 - PCB布局 - 内层2 .....                  | 35 |

| 图35. | VFQFPN68板 - PCB布局 - 底层 .....                   | 36 |

| 图36. | RF的PCB布局细节 .....                               | 37 |

| 图37. | SMPS的PCB布局细节 .....                             | 38 |

| 图38. | LSE的PCB布局细节 .....                              | 38 |

| 图39. | 天线的PCB布局细节 .....                               | 39 |

| 图40. | 天线路由的PCB布局细节 .....                             | 39 |

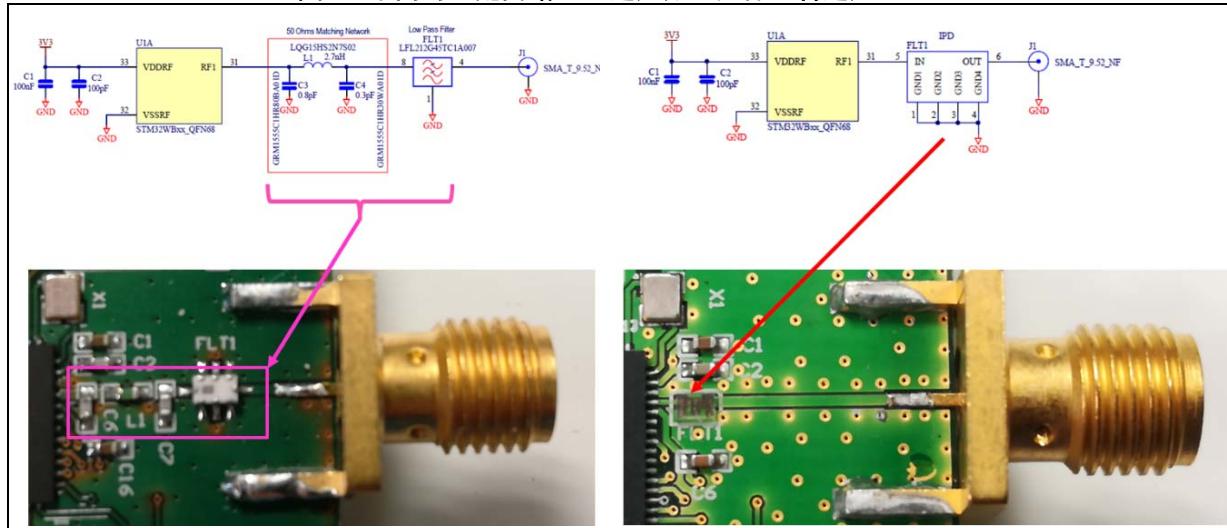

| 图41. | 不同的匹配网络 (左边是分立元件、右边是IPD) .....                 | 41 |

| 图42. | MLPF-WB55-01E3板的RF性能 .....                     | 41 |

| 图43. | IPD封装 (无凸块CSP) .....                           | 42 |

| 图44. | 采用分离匹配网络 (左) 和IPD (右) 的PCB布局 .....             | 43 |

# 1 RF基础知识

本节涵盖了用于RF板设计的通用术语和定义。

以下参考资料可为用户提供帮助。

|                                          |                            |                                                                                 |

|------------------------------------------|----------------------------|---------------------------------------------------------------------------------|

| 1 Paul Horowitz和<br>Winfield Hill        | 《电子艺术》<br>(第3版)            | 剑桥大学出版社                                                                         |

| 2 Roger C. Palmer                        | 《为通信系统而设计的RF电路简介》<br>(第2版) | 纽恩士出版社                                                                          |

| 3 Christopher Bowick                     | 《射频电路设计》(第2版)              | 纽恩士出版社                                                                          |

| 4 Joseph J. Carr和<br>George W. Hippisley | 《实用天线手册》<br>(第5版)          | 麦格希教育出版社                                                                        |

| 5 史密斯圆图 (免费软件)                           |                            | <a href="http://www.fritz.dellsperger.net">http://www.fritz.dellsperger.net</a> |

| 6 共面波导计算器 (免费软件)                         |                            | <a href="http://wcalc.sourceforge.net">http://wcalc.sourceforge.net</a>         |

## 1.1 术语

### 1.1.1 功率

该单位以dBm表示，用于衡量RF信号强度：**dBm=10LogP**，其中P为以mW为单位的功率。其计算方式为：

- 1 pW = -90 dBm

- 10 μW = -20 dBm

- 1 mW = 0 dBm

- 2 mW = 3 dBm

- 10 mW = 10 dBm

### 1.1.2 增益

增益（以dB表示）是RF器件的输出和输入功率之间的比率。负值对应于衰减。

### 1.1.3 损耗

如果电路的两个级之间存在阻抗不匹配、传输线设计不正确或PCB材料选择不正确的问题，则会出现信号功率损耗，并非所有功率能从某一级传输到下一级。还存在固有损耗，如介电损耗，这取决于用于制造电路板的层压板和材料。

### 1.1.4 反射系数、电压驻波比和回波损耗

当信号通过传输线从信号源流向负载时，如果传输线与负载的特征阻抗不匹配，则部分信号将被反射回信号源。反射信号的极性和幅度取决于负载阻抗是高于还是低于线路阻抗。

反射系数 ( $\Gamma$ ) 用于衡量反射波幅度与入射波幅度之间的对应关系, 即  $\Gamma = (Z - Z_0) / (Z + Z_0) = (z - 1) / (z + 1)$ 。

电压驻波比 (VSWR) 用于衡量连接点处的阻抗匹配精度。它为反射系数的函数, 用以下公式表示:  $VSWR = (1 + |\Gamma|) / (1 - |\Gamma|)$ 。如果VSWR为1, 则无反射功率。

回波损耗 (RL) 是反射系数的函数, 但以dB表示:  $RL = 20 \log |\Gamma|$ 。

### 1.1.5 谐波

谐波频率为输入频率 (基频) 的整数倍。

### 1.1.6 杂散

杂散频率为输入频率 (不需要的频率) 的非整数倍。

### 1.1.7 互调

当两个RF信号混合在一起时, 互调产物信号由两个信号之和与之差的整数倍组成。

## 1.2 阻抗匹配

为优化射频性能, 必须调整天线到芯片输入的阻抗匹配, 以及芯片输出到天线的阻抗匹配。

如果该适应较差, 则会在RX/TX链中带来损耗。这些损耗会使所发送信号的灵敏度和幅度立即降低。这些不适应如果足够严重, 则会增加TX谐波电平。

因此, 努力尽可能适应RF链路非常重要。对于STM32WB的低功耗蓝牙<sup>®</sup>带宽, 尤其是在RF频率方面, 杂散元素 (如PCB走线电感和层电容、走线长度) 对阻抗匹配具有显著影响。为在负载和STM32WB之间实现最佳TX/RX预算 (信号和能量的最佳传输), 在两个模块之间需要专用的匹配网络。

当源的内部电阻等于负载的电阻时, 以最大功率传输。当扩展到具有与频率有关的信号的电路时, 为实现最大功率传输, 负载阻抗必须为源阻抗的复共轭。

## 1.3 史密斯圆图

史密斯圆图 ([图 1](#)) 用于确定匹配网络。

### 1.3.1 归一化阻抗

归一化阻抗 $z$ 为复阻抗（ $r$ 为实部、 $x$ 为虚部）： $z = r + jx = Z / Z_0$ ，其中 $Z_0$ 为特征阻抗，通常为常数（在我们的例子中， $Z_0 = 50 \Omega$ ）。

对于电容， $z = -j / (2 \pi * f * C * Z_0)$ ，对于电感， $z = j (2 \pi * f * L) / Z_0$ 。

### 1.3.2 读取史密斯圆图

史密斯圆图用归一化阻抗 $z = Z / Z_0$ 表示。

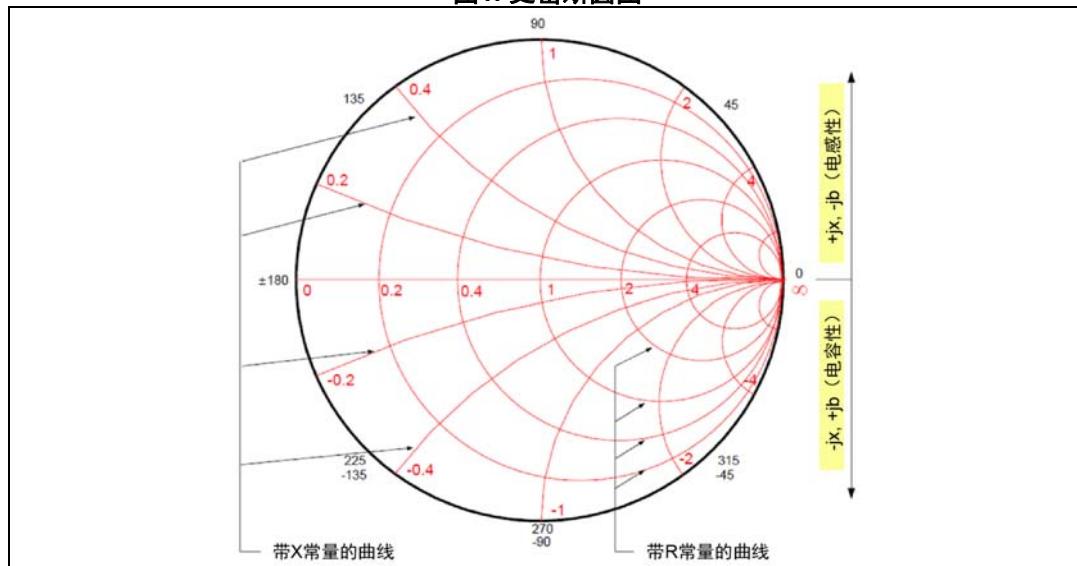

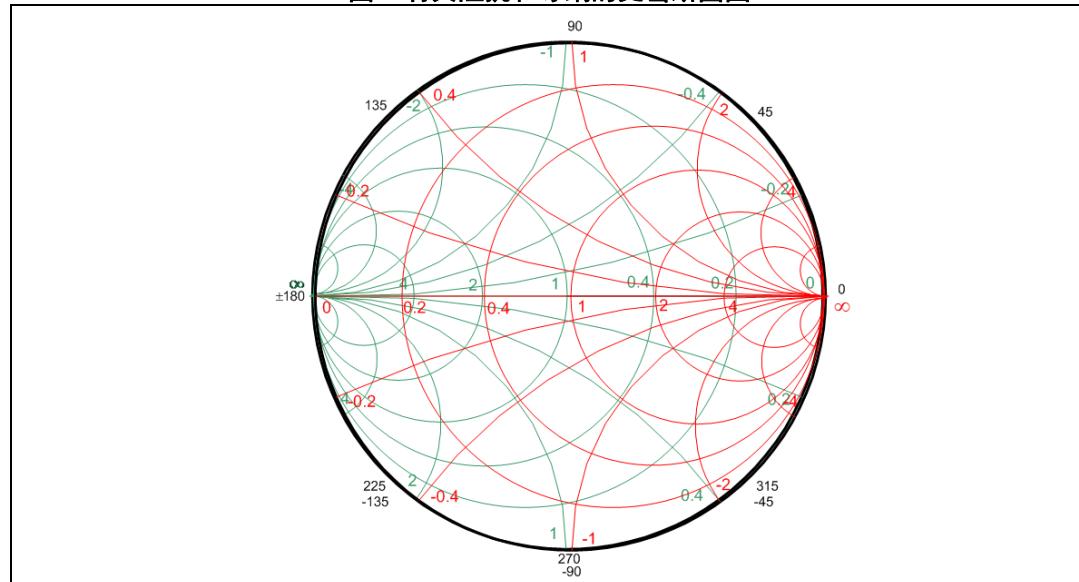

图1. 史密斯圆图

如果 $Z_0 = 50 \Omega$ ，当存在匹配时（ $Z = Z_0$ ）， $50 \Omega$ 下的归一化阻抗为1，这是史密斯圆图的中心。匹配网络的搜索目标是朝这一点收敛。

史密斯圆图的水平轴表示纯电阻：在左侧， $z = 0$ （短路），在右侧， $z = \infty$ 。

X轴上方的区域表示带感应电抗（复阻抗的正虚部）或电容性电纳（复导纳的正虚部）的阻抗。

X轴下方的区域表示带电容性电抗（复阻抗的负虚部）或电感性电纳（复导纳的负虚部）的阻抗。

#### 串联电感或电容

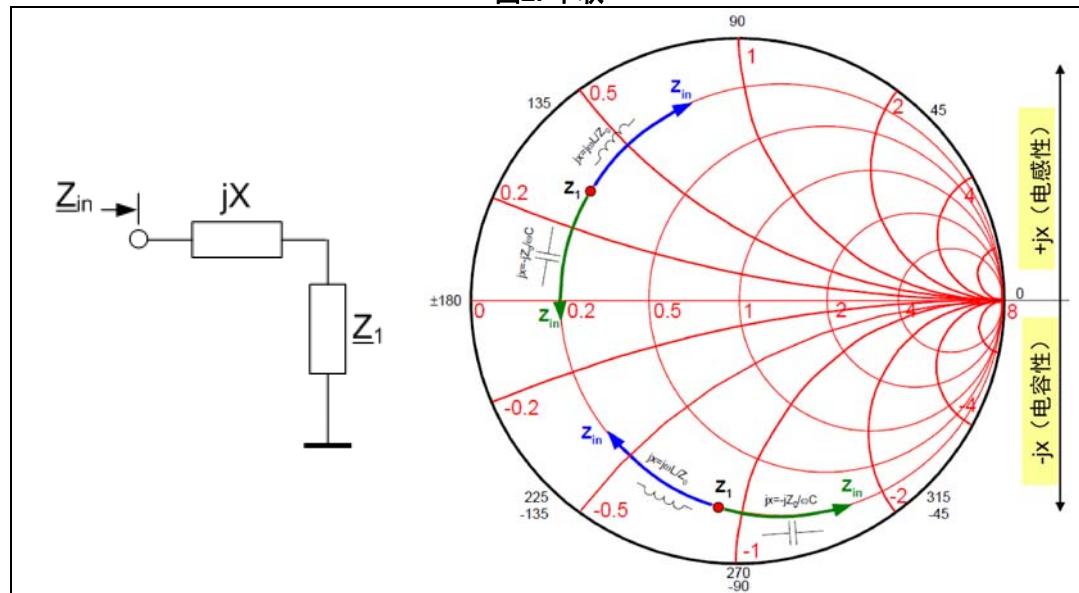

如果电感或电容与负载阻抗 $Z_1$ 串联，则产生的阻抗 $Z_{in}$ 按图2所示移动。

图2. 串联

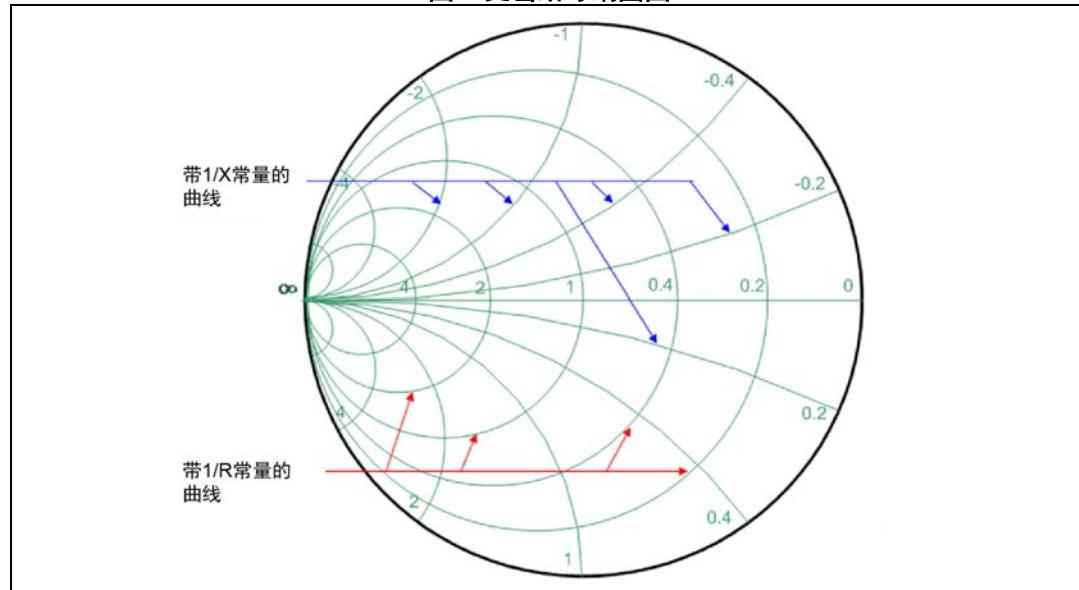

对于归一化阻抗 ( $z$ ) 中的史密斯圆图，史密斯圆图可以用归一化导纳 ( $y = 1/z$ ) 表示，如图3所示。

图3. 史密斯导纳圆图

### 并联电感或电容

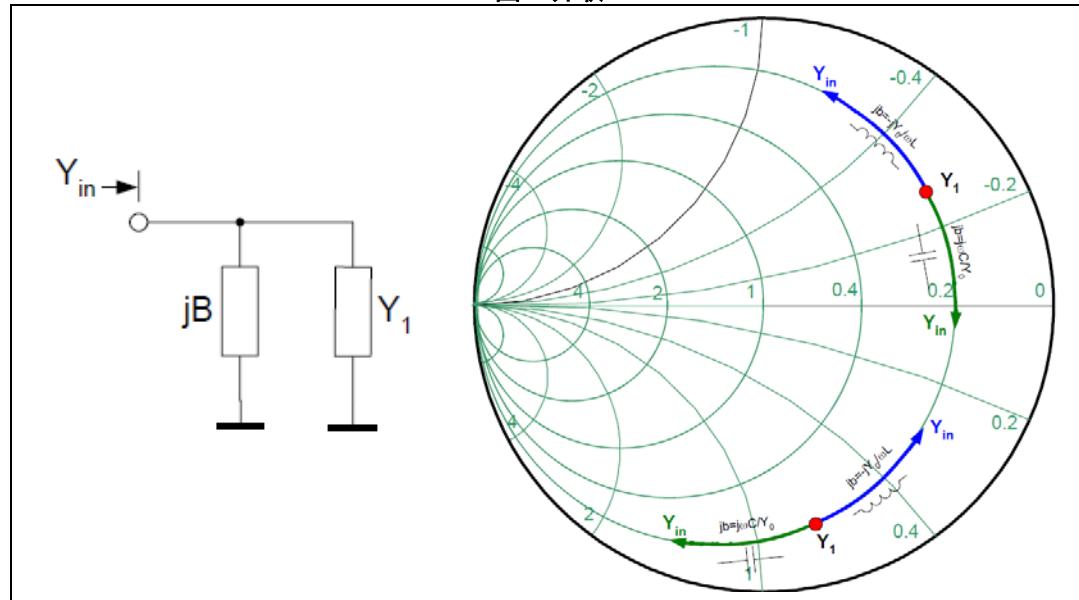

如果电感或电容与负载导纳  $Y_1$  并联，则产生的阻抗  $Y_{in}$  按图4所示移动。

图4. 并联

在图5中，史密斯圆图位于阻抗和导纳平面中。

图5. 有关阻抗和导纳的史密斯圆图

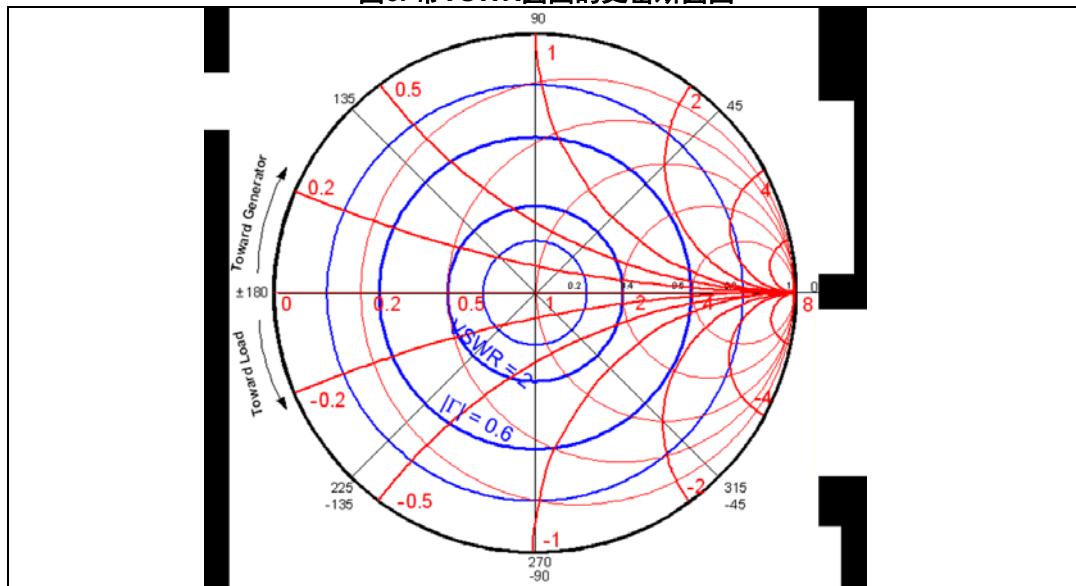

带常量VSWR的圆是可以从史密斯圆图中获得的额外信息，即使这些圆未显示。这些圆具有相同的中心，并且其值是与中心右侧的水平轴交点处的值（参见图6）。

图6. 带VSWR圆圈的史密斯圆图

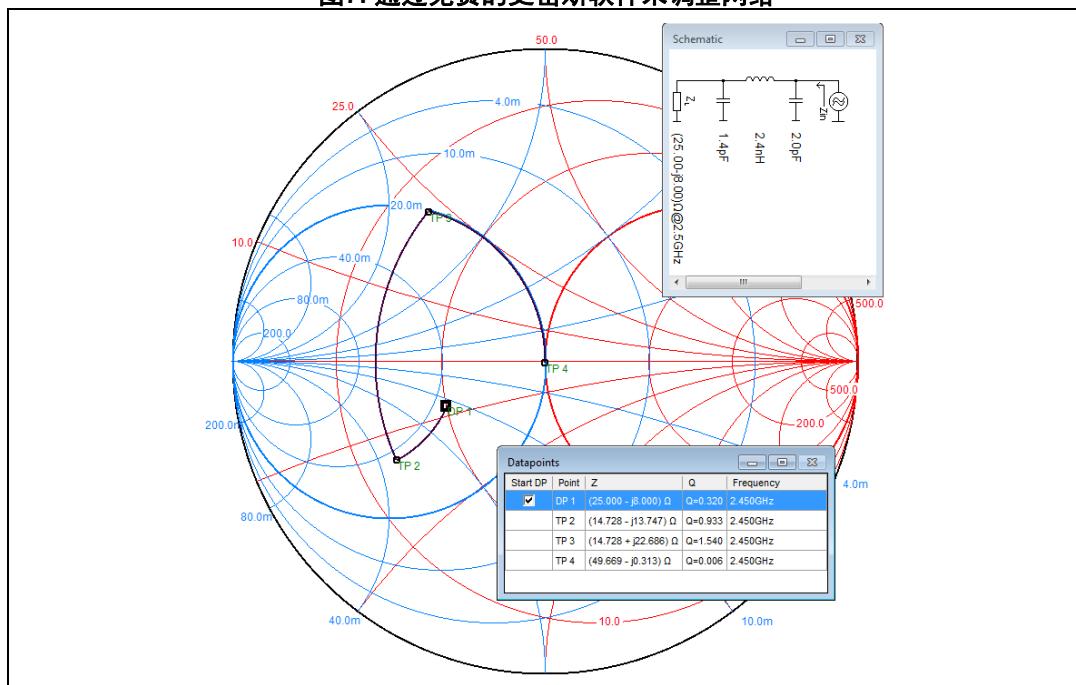

图 7 是免费软件“史密斯圆图”的一个示例：从  $Z_L = (25.00 - j*8.00) \Omega$  开始（在史密斯圆图上以 DP1 表示），其目标是获得  $Z_{in} = 50 \Omega$ 。通过添加（串联或并联）电感或电容，阻抗朝图中心收敛。

图7. 通过免费的史密斯软件来调整网络

## 2 参考板原理图

STM32WB系列微控制器基于Arm<sup>®(a)</sup>内核。

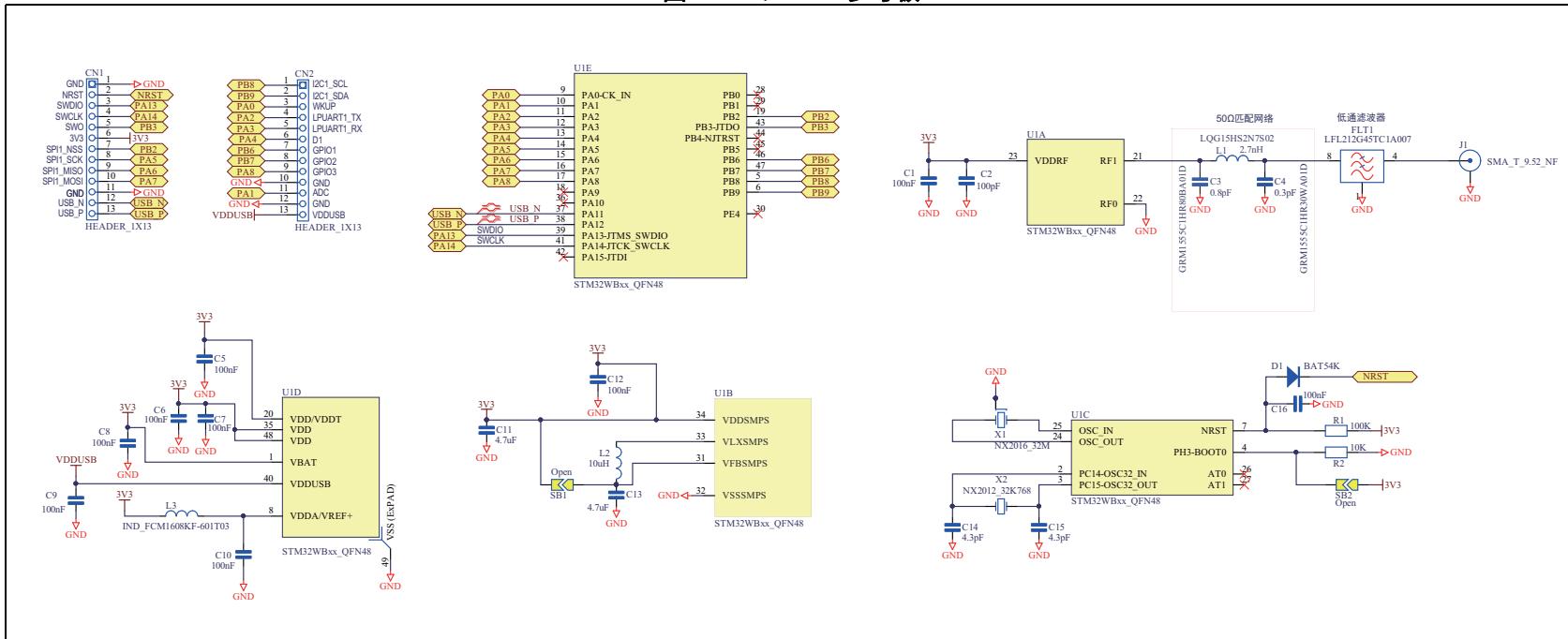

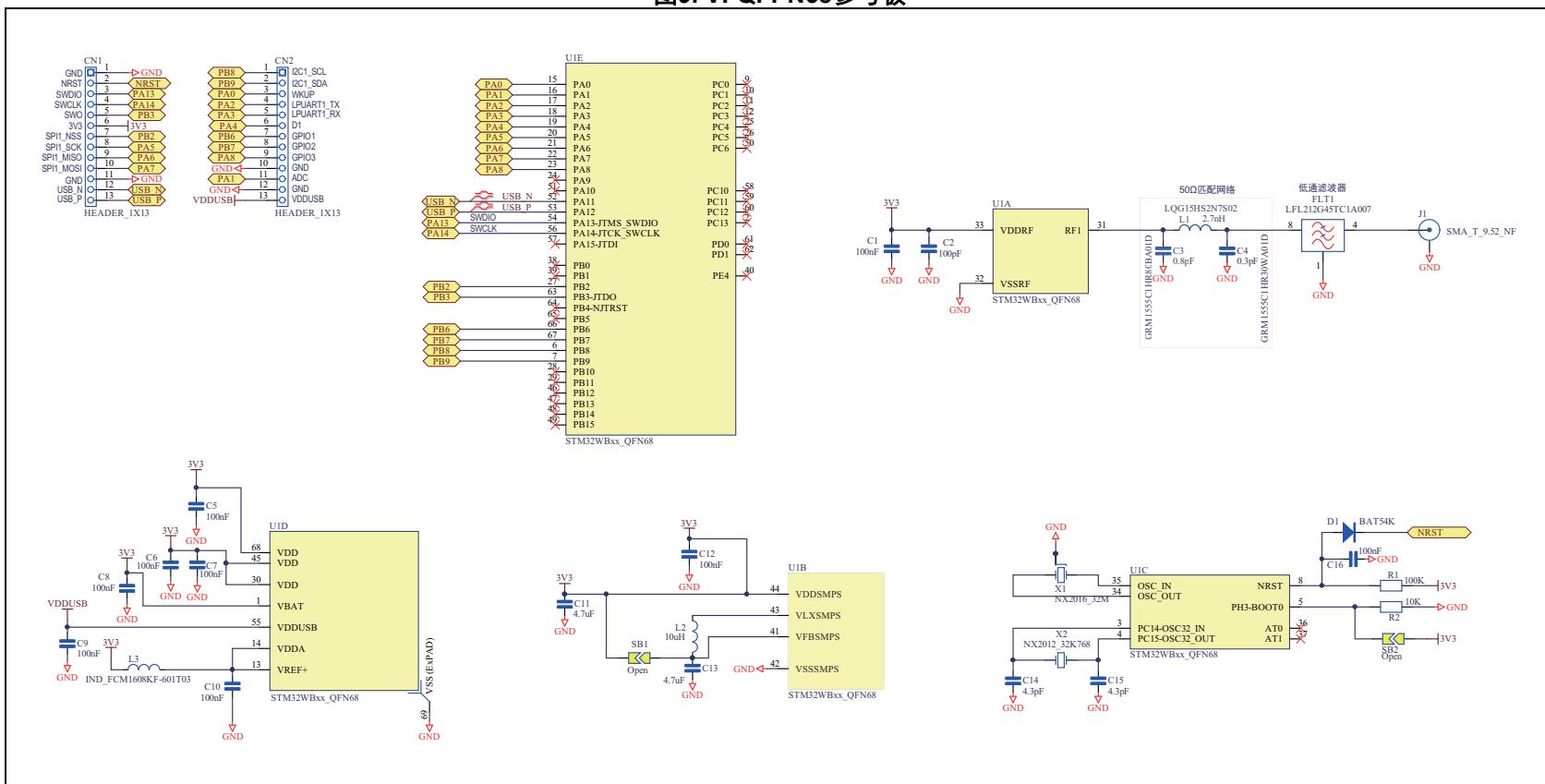

图 8和图 9中的原理图分别表示UFQFPN48和VFQFPN68封装的2层参考板。RF输出仅来自SMA。下一段中描述的两层PCB的所有布局指南均基于这些板。

表1. 外部元件

| 元件         | 说明                |

|------------|-------------------|

| C1, C2     | $V_{DDRF}$ 的去耦电容  |

| C3, C4     | 匹配电容              |

| C5, C6, C7 | $V_{DD}$ 的去耦电容    |

| C8         | $V_{BAT}$ 的去耦电容   |

| C9         | $V_{DDUSB}$ 的去耦电容 |

| C10        | $V_{DDA}$ 的去耦电容   |

| C12        | SMPS的去耦电容         |

| C11, C13   | DC-DC转换器滤波电容      |

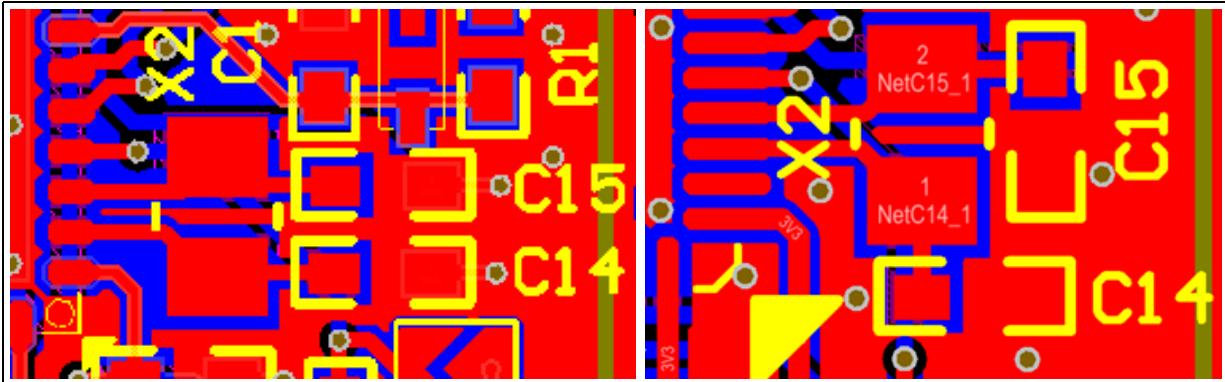

| C14, C15   | X2电容              |

| C16        | NRST引脚的去耦电容       |

| D1         | NRST引脚的二极管保护      |

| FLT1       | 集成低通滤波器           |

| L1         | 匹配电感              |

| L2         | DC-DC转换器电感        |

| L3         | $V_{DDA}$ 的滤波电感   |

| R1         | NRST的上拉电阻         |

| R2         | 启动选择器电阻           |

| U1         | STM32WBxx         |

| X1         | 高频晶振              |

| X2         | 低频晶振              |

arm

a. Arm是Arm Limited（或其子公司）在美国和/或其他地区的注册商标。

图8. UFQFPN48参考板

图9. VFQFPN68参考板

### 3 Nucleo板 (MB1355C) 原理图

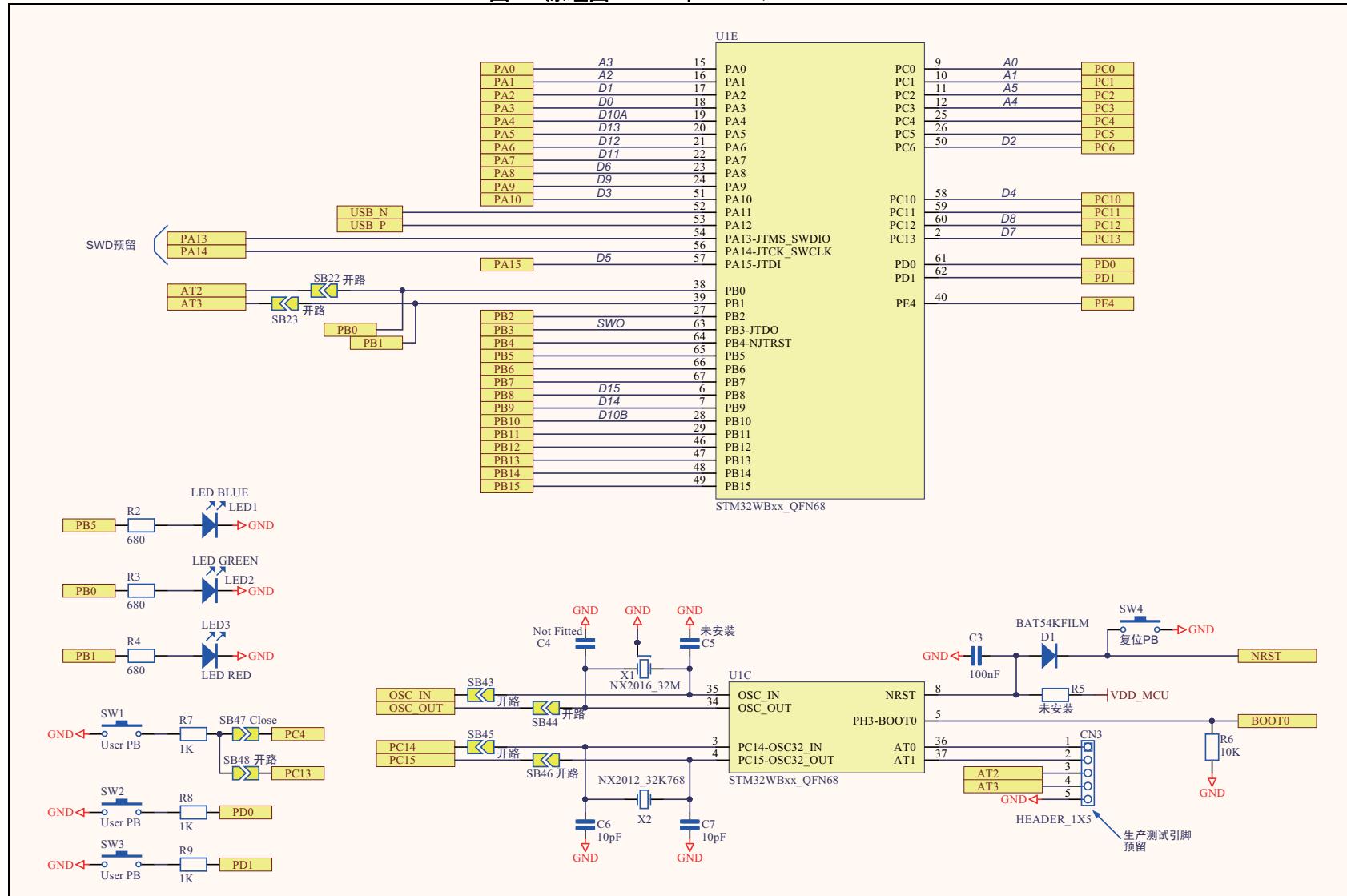

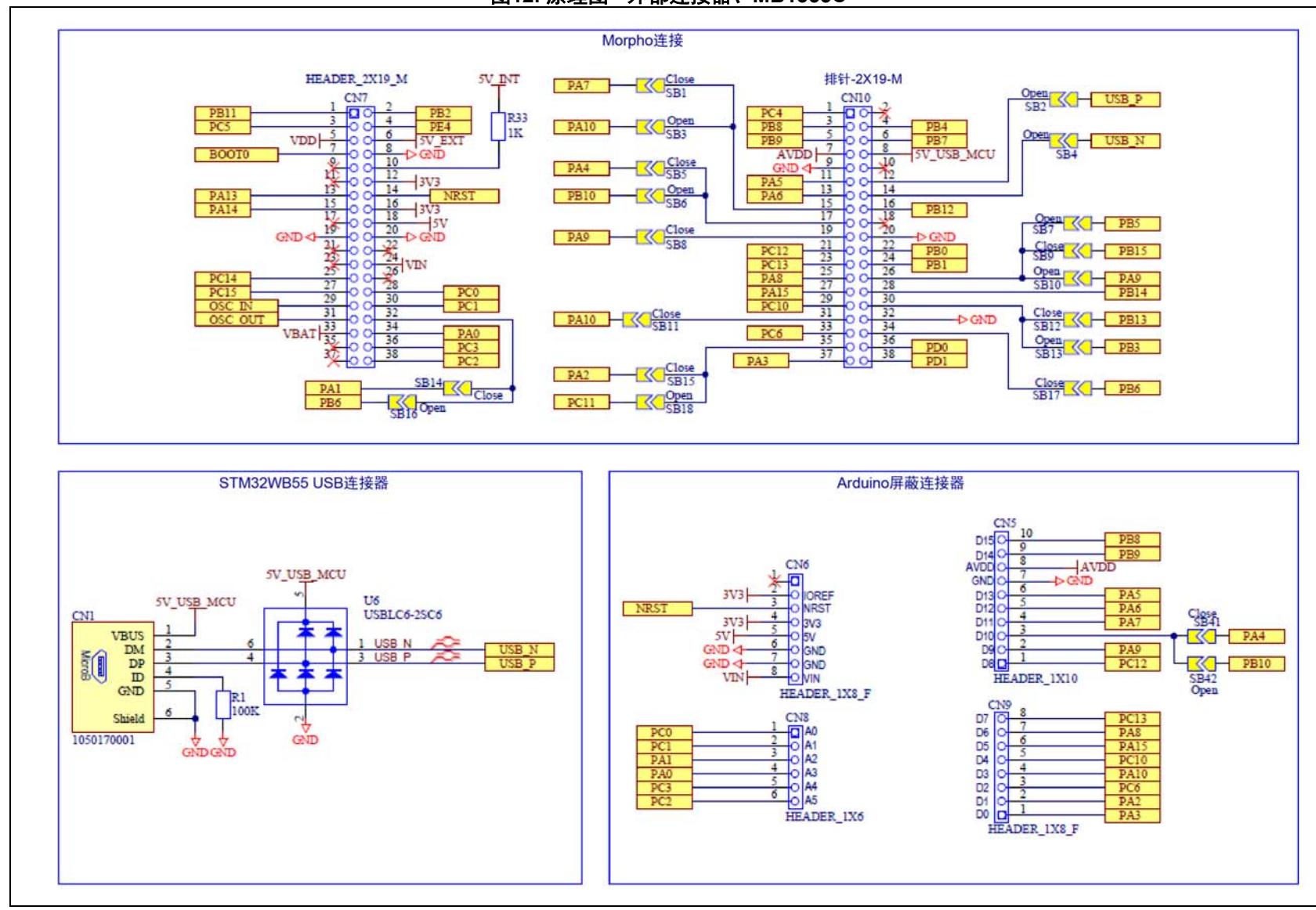

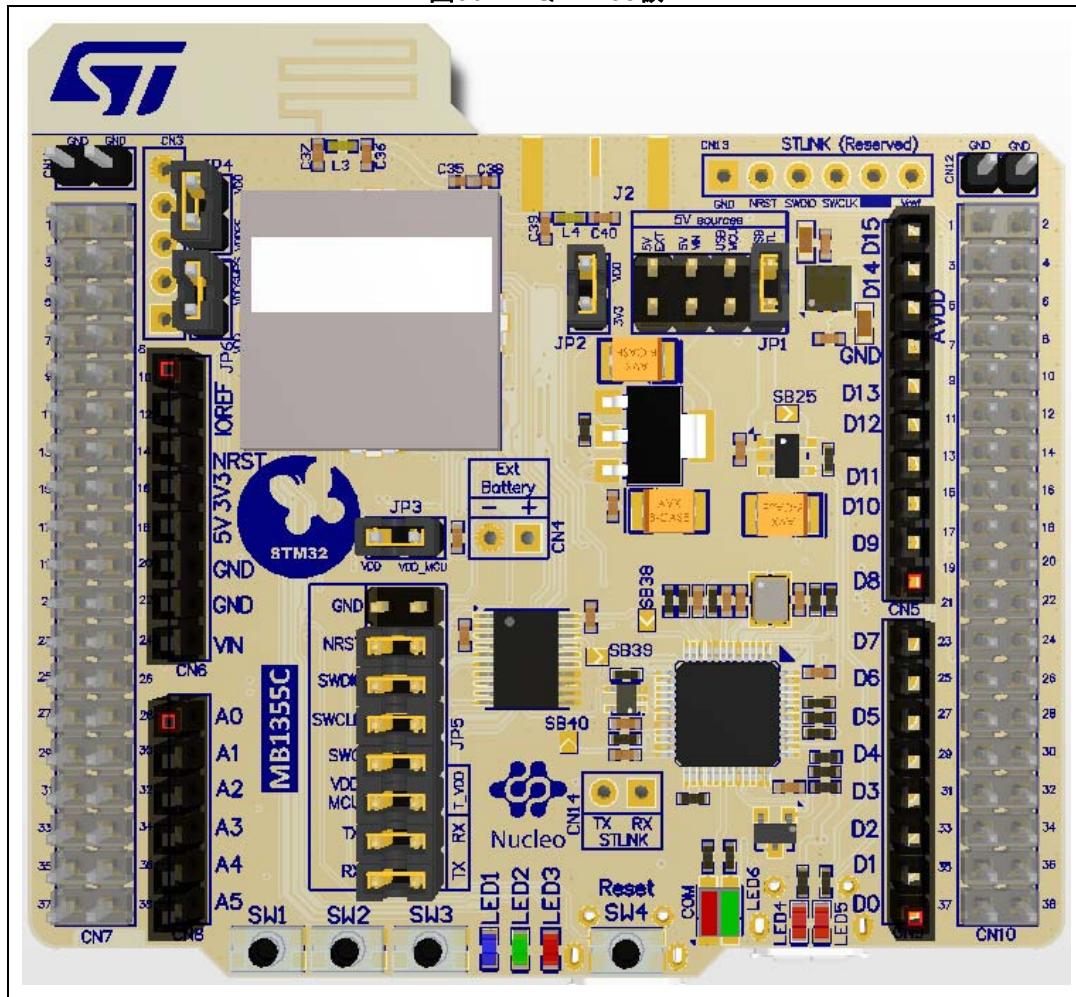

图 10 到 14 中的原理图是指 VFQFPN68 封装的 Nucleo 板。

这是一个完整的应用板，可通过 SMA 或天线输出 RF 信号。以下章节中针对 4 层 PCB 描述的所有布局指南均基于此板。

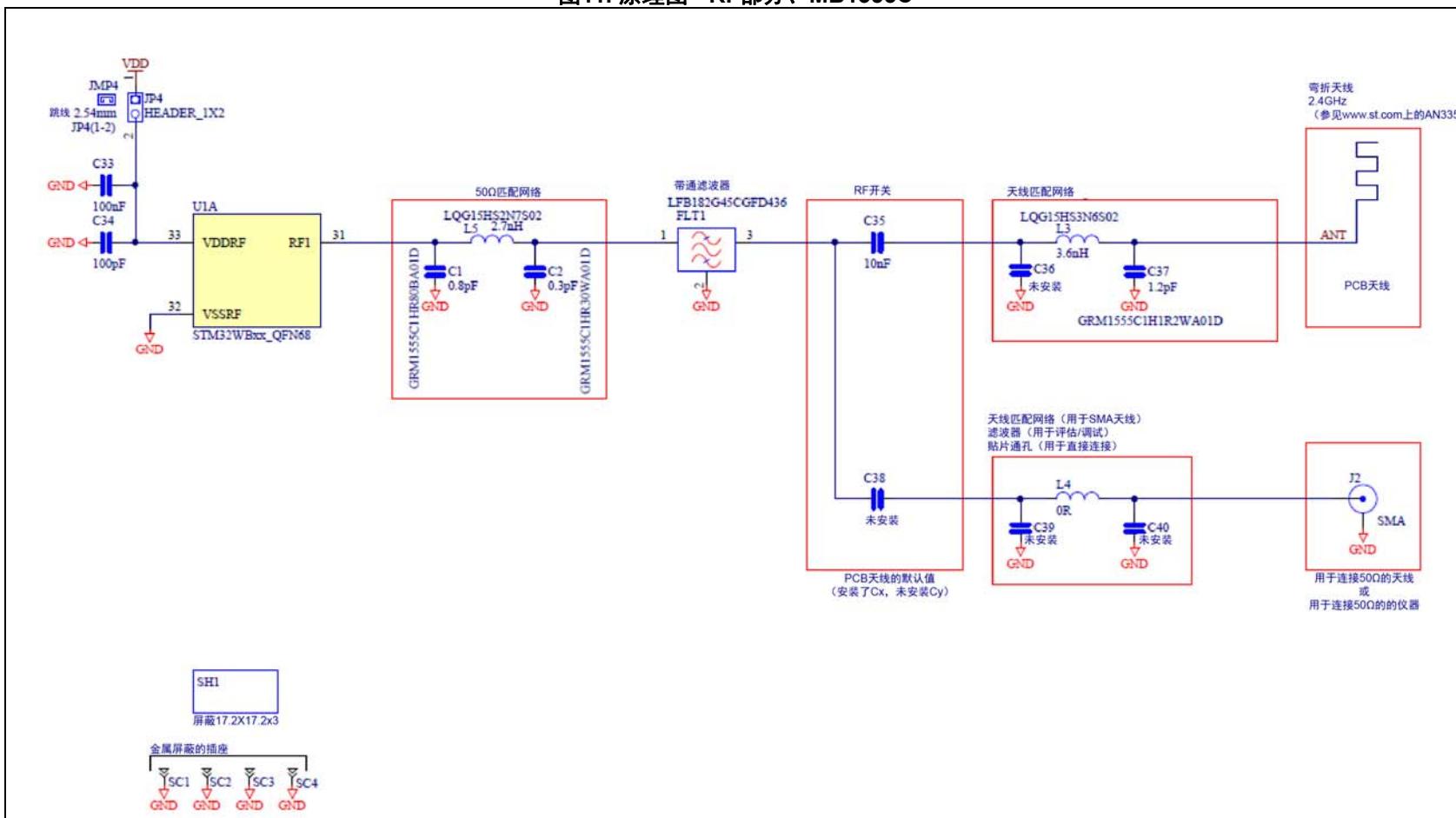

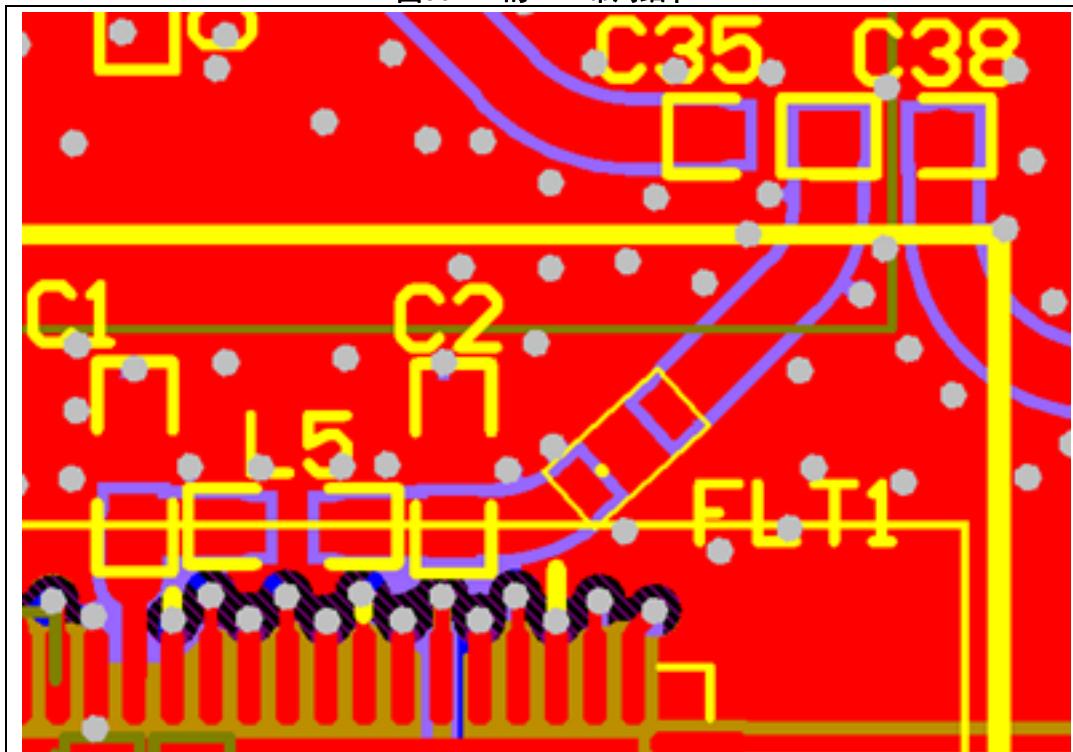

图 11 表示 VFQFPN68 Nucleo 板的 RF 部件。RF 输出可连接到印刷天线（如果焊接 C35）或 SMA 连接器，如参考板（如果焊接 C38）。请注意，默认情况下未安装 SMA 连接器。

STM32WB 在其输出和天线之间需要一个低通滤波器，以确保其传输的谐波符合 BLE 和 FCC 规定。

该滤波器必须至少呈现以下衰减：

|          |               |          |

|----------|---------------|----------|

| – ATT H2 | 4800 – 5825   | 最小-49 dB |

| – ATT H3 | 7200 – 7500   | 最小-45 dB |

| – ATT H4 | 9600 – 10000  | 最小-38 dB |

| – ATT H5 | 12000 - 12500 | 最小-37 dB |

集成滤波器 FLT1 是带通滤波器，比用于参考板的低通滤波器更具选择性。得益于该滤波器，可在更受相邻通信频段干扰的环境中使用 Nucleo 板，不过其插入损耗（滤波器的输入和输出之间的衰减）要高于低通滤波器的插入损耗。

图10. 原理图 - GPIO和XTAL、MB1355C

图11. 原理图 - RF部分、MB1355C

图12. 原理图 - 外部连接器、MB1355C

图13. 原理图 - 电源管理、MB1355C

图14. 原理图 - ST LINK、MB1355C

## 4 元件选择

在低功耗蓝牙<sup>®</sup>带宽中，更普遍的是在高频中，外部组件的选择至关重要，因为这会直接影响应用性能。

### 4.1 电容

电容器是一种无源电子元件，用于将能量储存于电场中。它们采用不同的制造技术、材料（如双层、聚酯、聚丙烯）和尺寸。对于RF设计，建议在表面贴装版本上使用陶瓷电容。

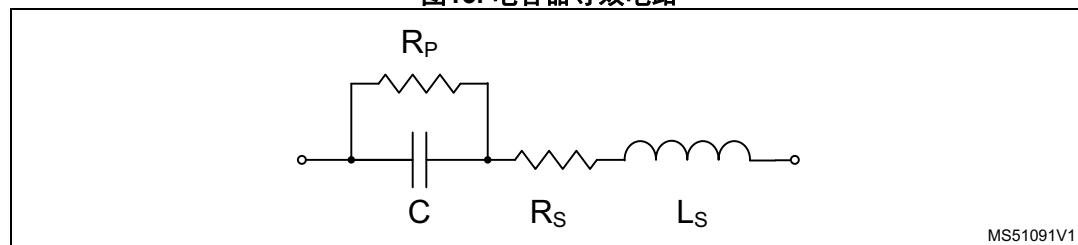

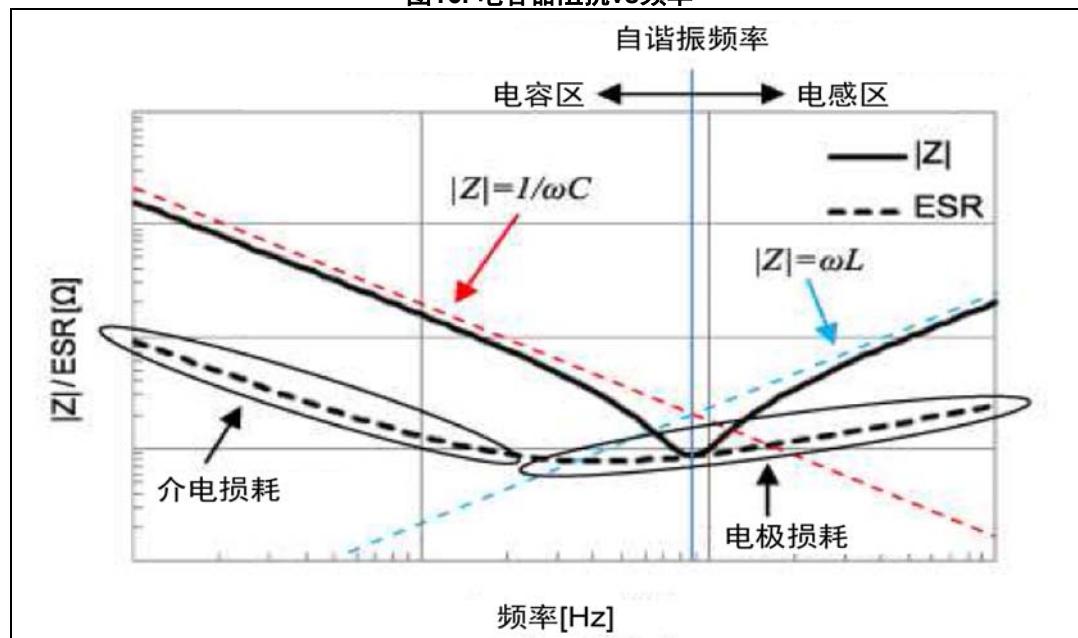

电容的等效电路如图15所示。电阻 $R_p$ 表示其泄漏电流，而 $R_s$ 为等效串联电阻（ESR），表示电容的所有欧姆损耗。电感 $L_s$ 为等效串联电感（ESL），其值为SRF（自谐振频率）的函数。从图16中可以看到，电容的阻抗在低频下为电容性阻抗，在SRF下为电阻性阻抗，在较高频率下为电感性阻抗。

图15. 电容器等效电路

图16. 电容器阻抗vs频率

对于RF匹配，多层陶瓷电容具有线性温度系数、低损耗，并在不同时间、温度和频率下具有稳定的电气性能。SMD（表面贴装器件）用于0402封装，实现了性能与处理之间的良好折中。

对于RF去耦，必须选择电容值，使得要去耦的频率接近或略高于电容的自谐振频率。

对于DC-DC转换器，由于电容的品质因数与其ESR成反比，因此建议使用具有低插入损耗和良好品质因数的电容器。电容需要X7R或X5R电介质。

表2. 电容温度范围

| 最低温度 |                 | 最高温度 |                   | 温度范围内的变化 |           |

|------|-----------------|------|-------------------|----------|-----------|

| 代码   | 温度              | 代码   | 温度                | 代码       | 变化 (%)    |

| X    | -55 °C (-67 °F) | 4    | +65 °C (+149 °F)  | P        | ±10       |

|      |                 | 5    | +85 °C (+185 °F)  | R        | ±15       |

| Y    | -30 °C (-22 °F) | 6    | +105 °C (+221 °F) | S        | ±22       |

|      |                 | 7    | +125 °C (+257 °F) | T        | +22 / -33 |

| Z    | +10 °C (+50 °F) | 8    | +150 °C (+302 °F) | U        | +22 / -56 |

|      |                 | 9    | +200 °C (+392 °F) | V        | +22 / -82 |

## 4.2 电感

电感器是一种无源电子元件，用于将能量储存于磁场中。由于制造技术和制造材料不同，电感器间各不相同。

对于RF设计，需要通过高Q（品质因数 =  $\text{Im}[Z] / \text{Re}[Z]$ ）来降低插入损耗，通常建议使用空气芯电感器。这些电感器不使用由铁磁材料制成的磁芯，而是缠绕在塑料、陶瓷或其他非磁性材料上。SMD还与0402封装一起使用。

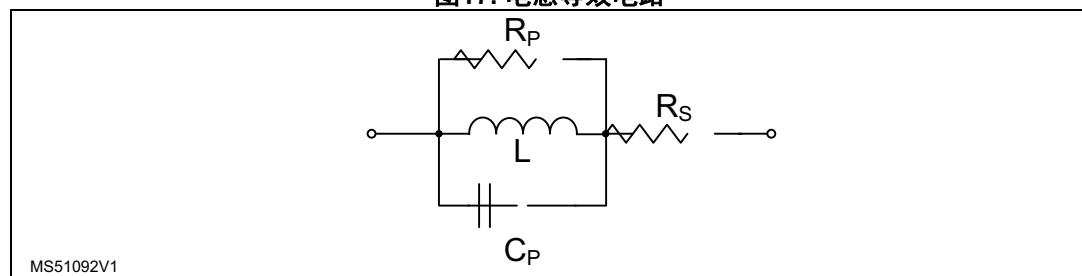

电感的等效电路如图17所示。电阻 $R_s$ 表示绕组线和端子引起的损耗，其值随温度而增加。电阻 $R_p$ 表示磁芯损耗，它随频率、温度和电流而变化。电容 $C_p$ 与绕组有关。

图17. 电感等效电路

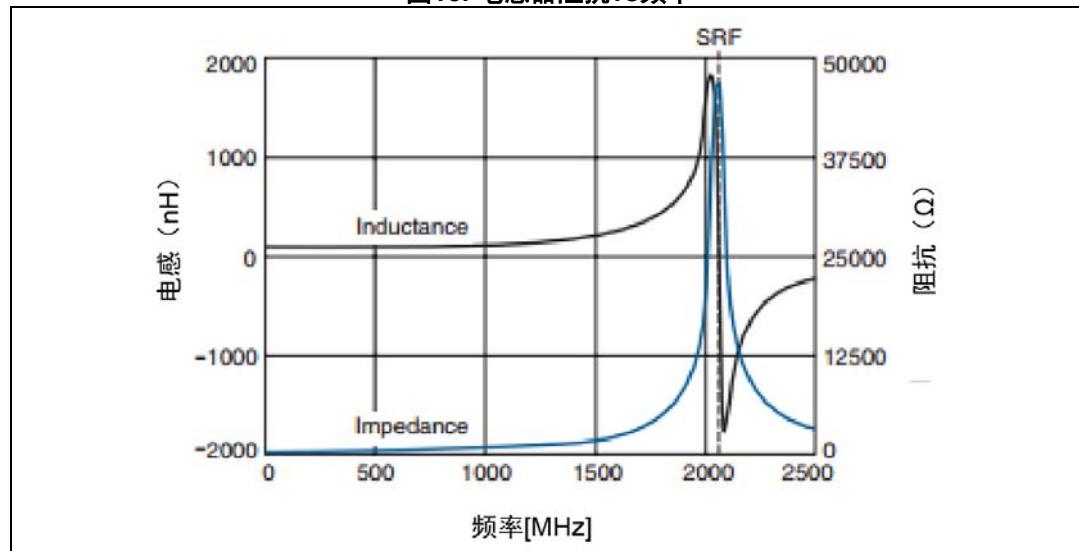

如图 18 所示，在SRF 处，阻抗和电感处于最大值。在较低/较高的频率下，阻抗和电感随频率增加/降低。

图18. 电感器阻抗vs频率

对于RF匹配和去耦，使用具有中等Q的电感可在应用成本和RF性能之间实现良好的折中。

对于DC/DC转换器，标称值为10  $\mu$ H。电感值影响峰间纹波电流、输出电压波纹和效率。所选电感必须根据其直流电阻和饱和电流来确定额定值。

务必使用原理图中所示的组件，以便在参考板的给定PCB布局中实现最佳RF性能。

## 4.3 SMPS

STM32WBxx微控制器嵌入了开关模式电源（SMPS），可在 $V_{DD}$ 足够高时提高电源效率。

为了不影响RF性能，该SMPS的开关频率与RF主时钟源HSE同步。SMPS的允许频率为4或8 MHz。请注意，在低功耗模式的RF启动阶段，将使用HSI来代替HSE，以实现相比在启动SMPS和数字逻辑之前从HSE稳定开始等待更快的唤醒速度。

已向该降压SMPS添加了两个特定功能，这些功能与STM32WB微控制器支持的所有低功耗模式有关：

为正常操作，SMPS需要一个电感和两个电容，其值取决于目标性能，以及机械设计中允许的PCB面积和总高度。

为实现最佳功耗性能，应选择4 MHz，以产生与4.7  $\mu$ F大电容相关的10  $\mu$ H电感。对于较小的尺寸，尤其是在使用非常小的电感时，可选择8 MHz，从而可以使用与4.7  $\mu$ F大电容相关的2.2  $\mu$ H电感。

必须使用另一个4.7 $\mu$ F电容来对V<sub>DDSMPS</sub>电源进行去耦。所有这些外部组件必须具有尽可能低的ESR值。请注意，V<sub>DDSMPS</sub>必须连接到V<sub>DD</sub>，电压上升和下降必须满足STM32WB数据手册中所述的条件。

## 4.4 外部晶振

STM32WB微控制器提供两个带外部晶振的振荡器。

RF子系统使用频率为32 MHz的HSE（高速外部）。晶体X1必须尽可能靠近振荡器引脚OSC\_IN和OSC\_OUT，以最大限度减轻输出失真和缩短启动稳定时间。负载电容集成在芯片上，可通过内部寄存器并根据所选晶振进行调整。默认情况下，板上使用的NDK公司的NX2016的负载电容为8 pF。

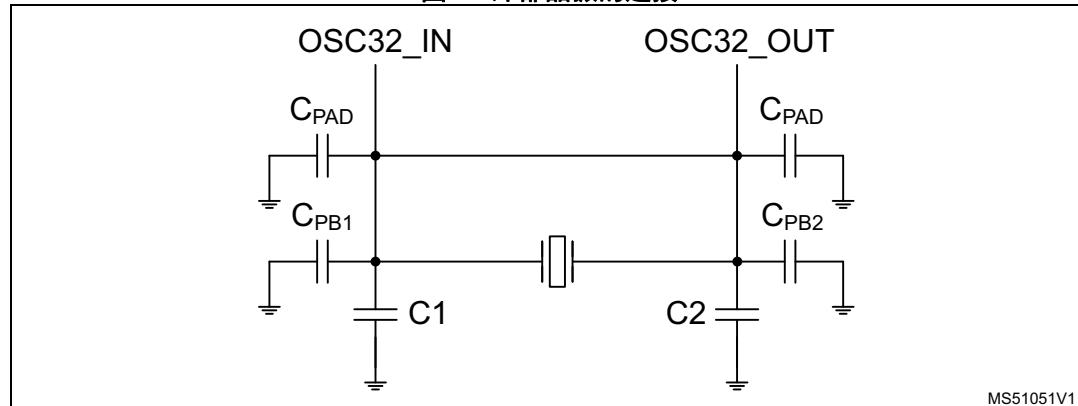

RTC子系统使用频率为32.768 kHz的LSE（低速外部）。必须对C<sub>1</sub>和C<sub>2</sub>值进行调整，以满足对所选晶振的推荐负载电容C<sub>0</sub>的要求。低C<sub>0</sub>值可实现低功耗和快速启动时间。相反，较高的C<sub>0</sub>可带来更出色的频率稳定性。

根据图19，晶振的总负载电容C<sub>0</sub>为C<sub>0</sub> = [(C<sub>1</sub> + C<sub>PA</sub>D + C<sub>PB1</sub>) \* (C<sub>2</sub> + C<sub>PA</sub>D + C<sub>PB2</sub>)] / (C<sub>1</sub> + C<sub>PA</sub>D + C<sub>PB1</sub> + C<sub>2</sub> + C<sub>PA</sub>D + C<sub>PB2</sub>)，其中：

- C<sub>PA</sub>D考虑了STM32WB焊盘、SMD元件C<sub>1</sub>和C<sub>2</sub>以及晶体本身的寄生电容。

- C<sub>PB1</sub>和C<sub>PB2</sub>代表PCB布线寄生电容。必须通过将X2、C<sub>1</sub>和C<sub>2</sub>布置在芯片附近来最大限度地降低这些寄生电容，从而提高噪声抑制的稳健性。

- C<sub>1</sub>和C<sub>2</sub>必须通过独立通孔接地。

图19. 外部晶振的连接

## 5 PCB层叠和技术

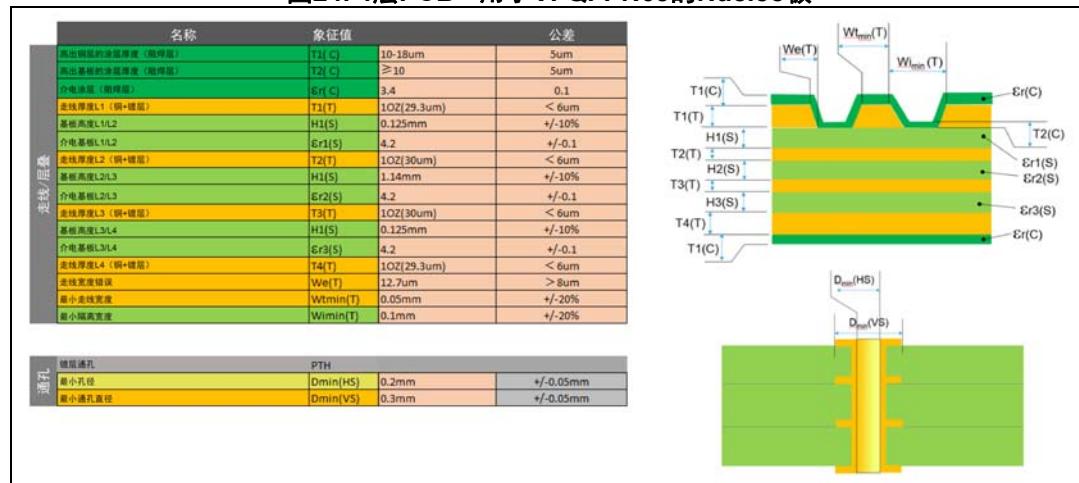

必须仔细设计RF频率下的PCB走线，因为其长度为信号波长的一部分。此外，RF频率下的PCB走线的阻抗取决于走线厚度、走线高出接地层的高度以及PCB介电材料的介电常数和损耗角正切。另一个重要参数为本段所述的PCB层叠。

为获得最佳性能，RF板通常采用至少两层或四层的设计。

### 5.1 射频传输线

PCB上的传输线可在外部层（微带线和共面波导），或者埋入内部层（带状线）实现。

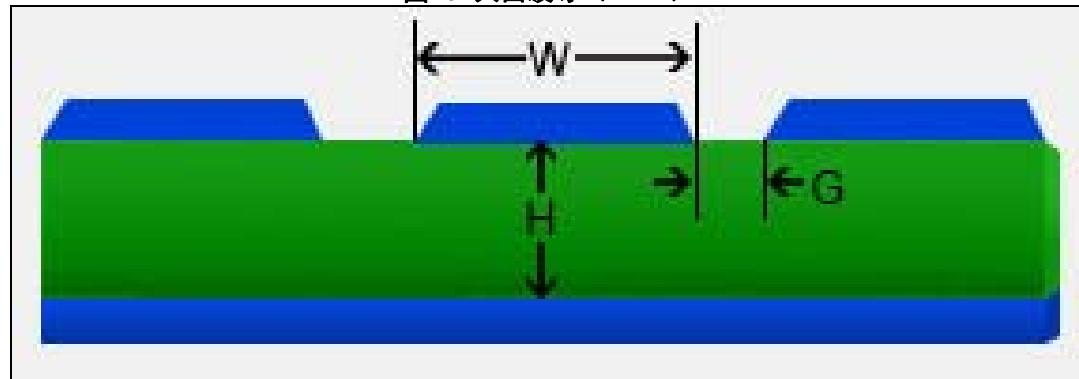

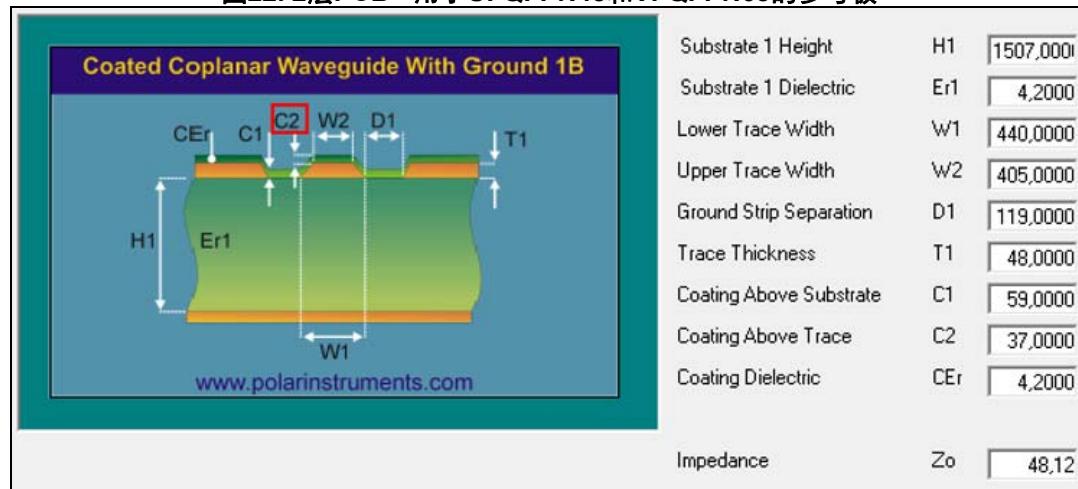

共面波导（CPW）传输线由两个接地层之间（通过间隙G将它们隔开）的宽度为W的中心信号线组成（参见图 20）。中心线和接地层位于厚度为H的介电基板的表面上。

图20. 共面波导（CPW）

存在名为GCPW或CPWG的CPW版本，它具有与电介质相对的接地层。

### 5.2 PCB基板选择

有不同类型的PCB基板，尽管采用相同的基本材料（玻璃）制造，但其中一些基板具有更适合RF产品的受控参数。RF设计中使用的PCB基板是FR-4（阻燃4）基板。已知这种材料在干燥和潮湿条件下可保持其高机械值和电绝缘品质，但这以损失不同频率和损耗下的介电常数稳定性为代价。

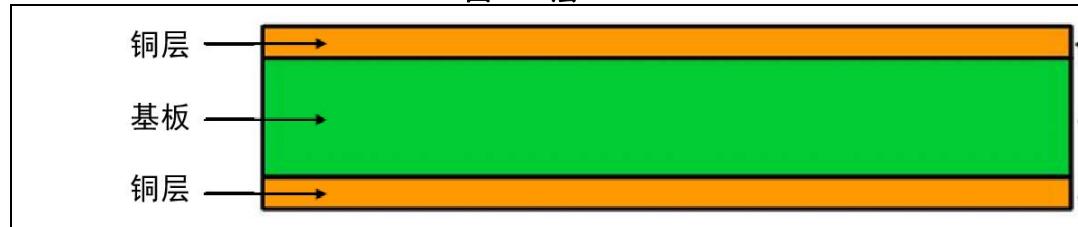

### 5.3 2层PCB

对于2层PCB（参见图 21），顶层用于RF信号和布线，而底层用于在RF区域下接地，以及其它部件的走线。RF区域下的接地层必须连续，否则回路电流可能增加，并会降低RF性能。

图21. 2层PCB

2层PCB提供了更便宜的解决方案，可实现相当于4层PCB的性能，但需要仔细的信号走线和元件放置。

UFQFPN48和VFQFPN68的参考板的2层PCB的定义如图 22中所示。

图22. 2层PCB - 用于UFQFPN48和VFQFPN68的参考板

## 5.4 4层PCB

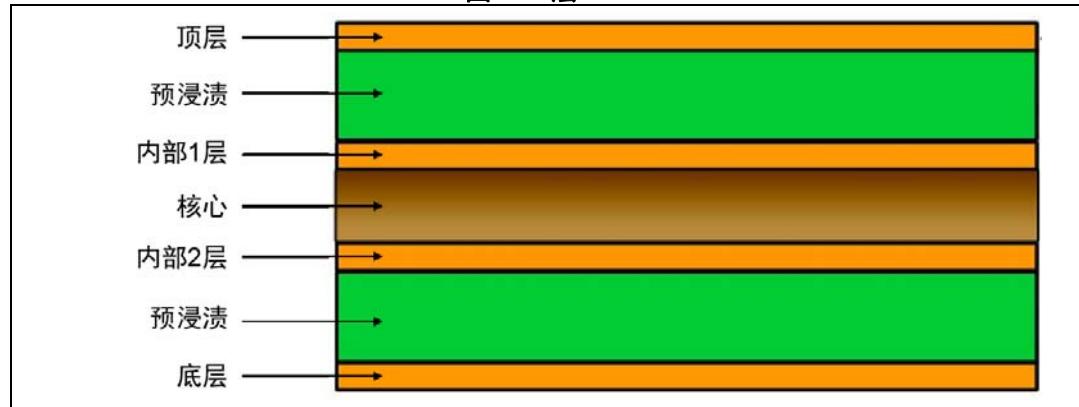

对于图23中所示的4层PCB，建议采用以下布置：

- 顶层：顶层的RF信号和布线。

- 内部1层：RF区域下接地，以及其它部件的走线。

- 内部2层：供电和低频走线。

- 底层：低频走线。

图23. 4层PCB

4层PCB解决方案更加复杂和昂贵。在此情况下，必须使用填充激光孔和埋藏式孔将走线连至内部焊球。

图图24中显示了用于VFQFPN68的Nucleo板的4层PCB定义。

图24. 4层PCB - 用于VFQFPN68的Nucleo板

## 6 2层PCB的布局建议

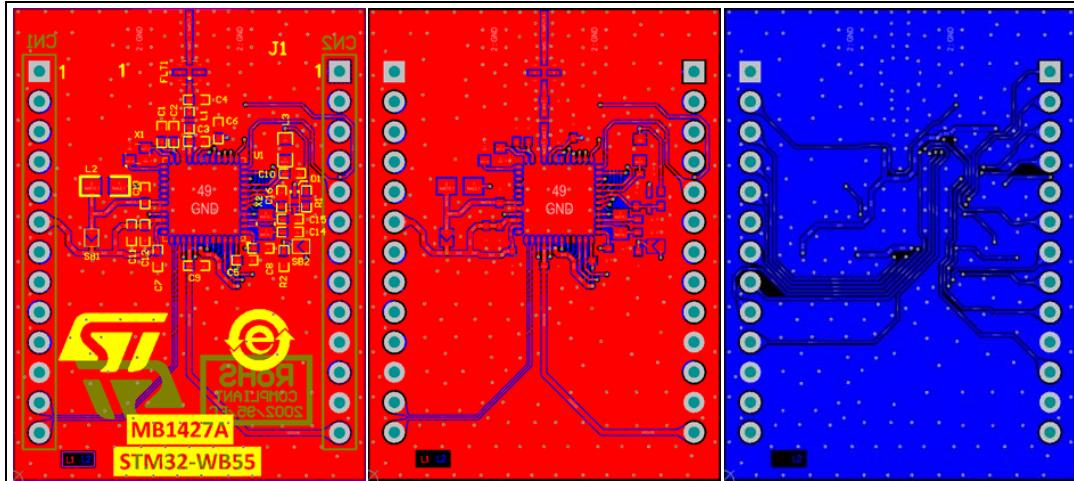

图25. UFQFPN48的PCB布局（从左到右：全部、顶层和底层）

图26. VFQFPN68的PCB布局（从左到右：全部、顶层和底层）

### 6.1 关键部件

布局中的三个关键部件为RF、SMPS和LSE。

#### 6.1.1 RF

为获得最佳RF性能（尤其是最大传输功率、最佳接收灵敏度以及足够的杂散和谐波抑制），在RF1输出引脚和RF低通滤波器之间需要一个匹配网络。

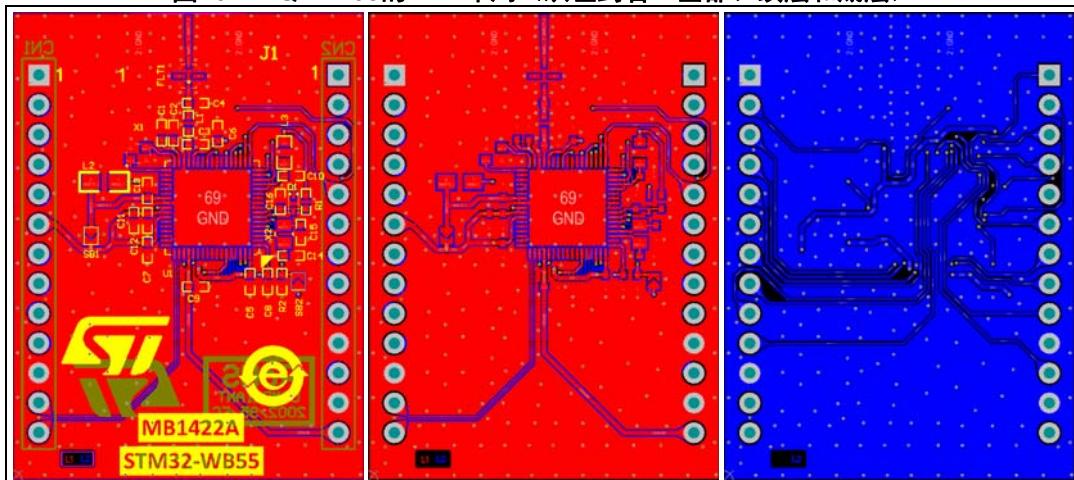

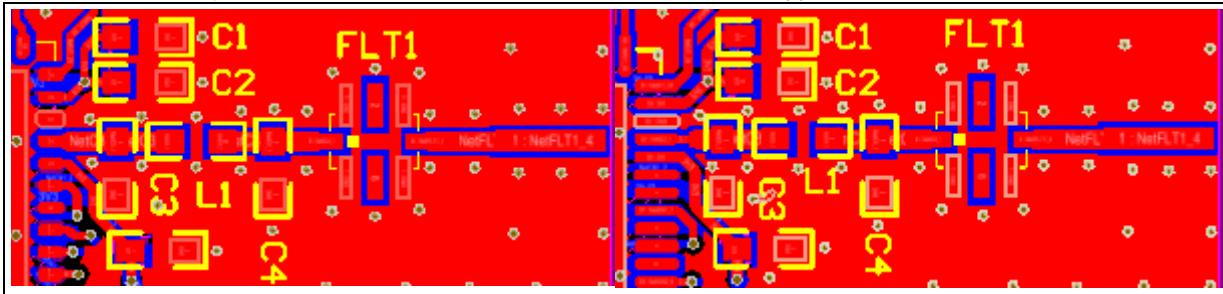

该网络由分立LC PI滤波器以及集成低通滤波器组成。C3和L1的作用为将STM32WB的RF引脚阻抗调整为 $50\ \Omega$ ，这是SMA所必须的阻抗。C4和集成低通滤波器FLT1用于抑制谐波频率。C3、C4和L1的值取决于[第2节：参考板原理图](#)中详述的参考板PCB定义。

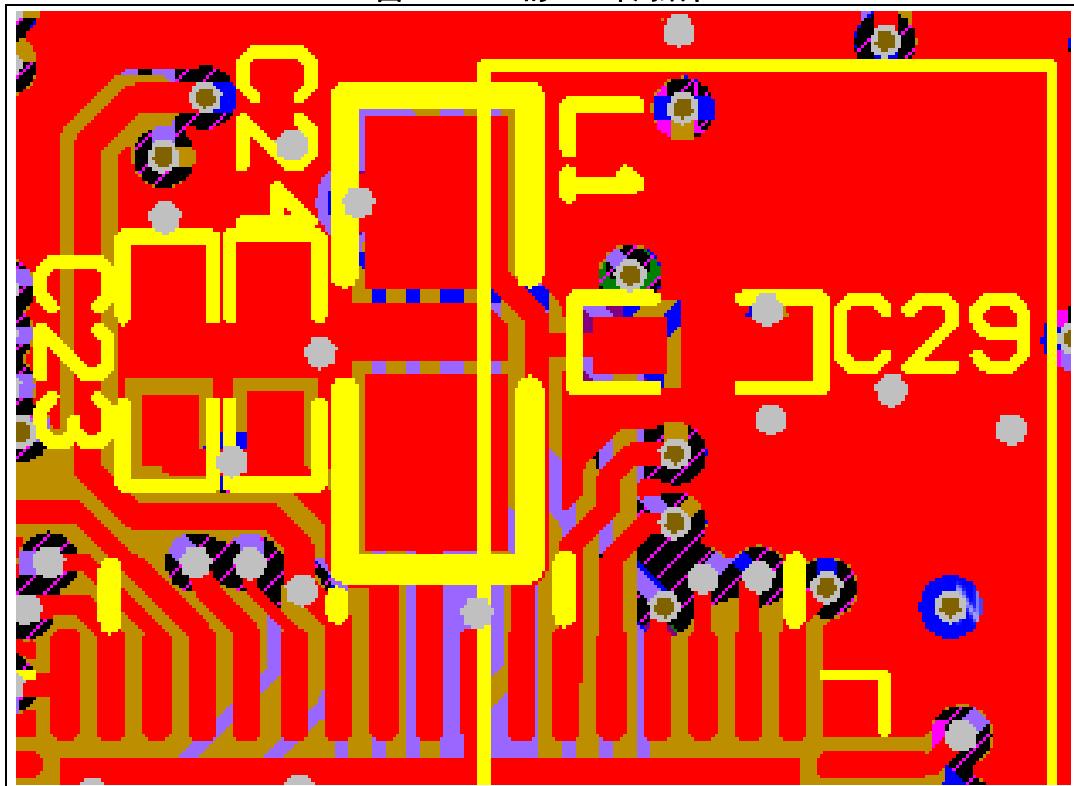

图27. RF的PCB布局细节（左侧为UFQFPN48、右侧为VFQFPN68）

使用的低通滤波器FLT1具有用于区分方向的标记。遵循PCB上所指示的方向（滤波器的结构不完全对称，属性随安装方向而变化）。

还建议将匹配网络布置在尽可能靠近RF输出的地方，以避免在匹配网络的每个组件之间构成长走线。低通滤波器FLT1的输出和SMA连接器之间的走线长度可变，如果阻抗始终为50  $\Omega$ ，则走线长度取决于应用。

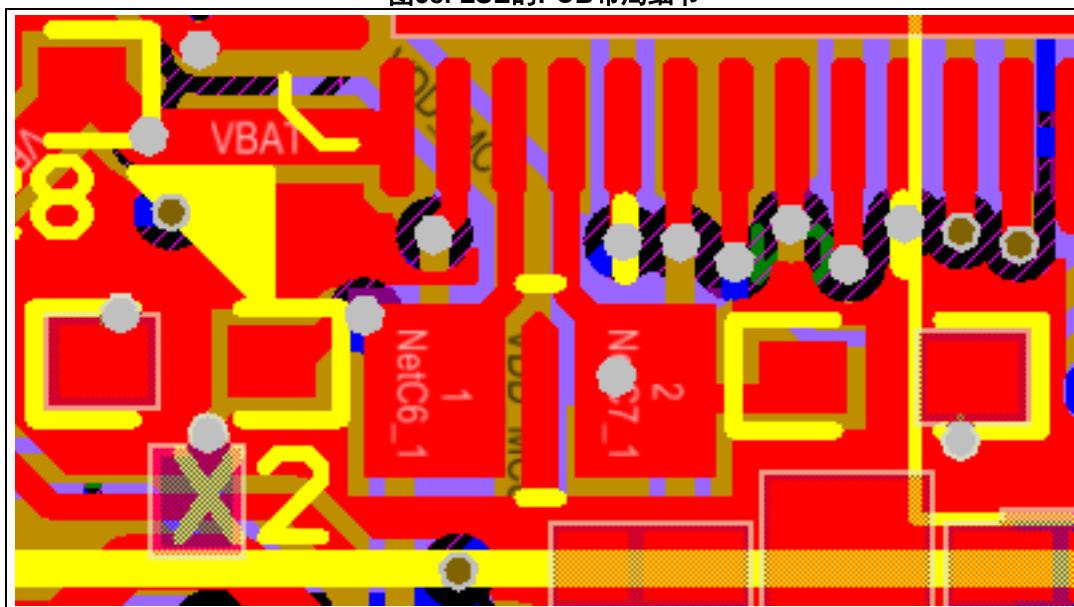

### 6.1.2 SMPS

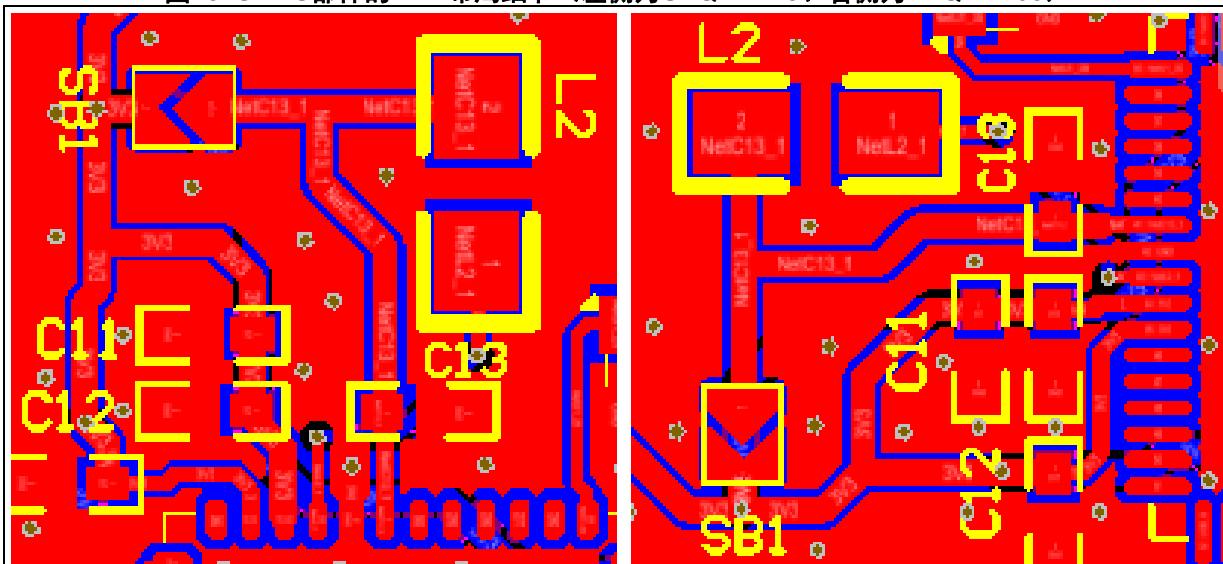

除了[第 4.3节: SMPS](#)中给出的建议以外，为避免当STM32WB处于SMPS模式时出现严重的电流环，建议将C11、C12和C13布置在尽可能靠近STM32WB上的相应引脚的位置。请勿忘记将焊盘接地，以获得强大的电流回流路径。

图28. SMPS部件的PCB布局细节（左侧为UFQFPN48、右侧为VFQFPN68）

### 6.1.3 LSE

如[第 4.4 节：外部晶振](#)中所示，将X2、C14和C15布置在尽可能靠近STM32WB上的相应引脚的位置。

图29. LSE的PCB布局细节（左侧为UFQFPN48、右侧为VFQFPN68）

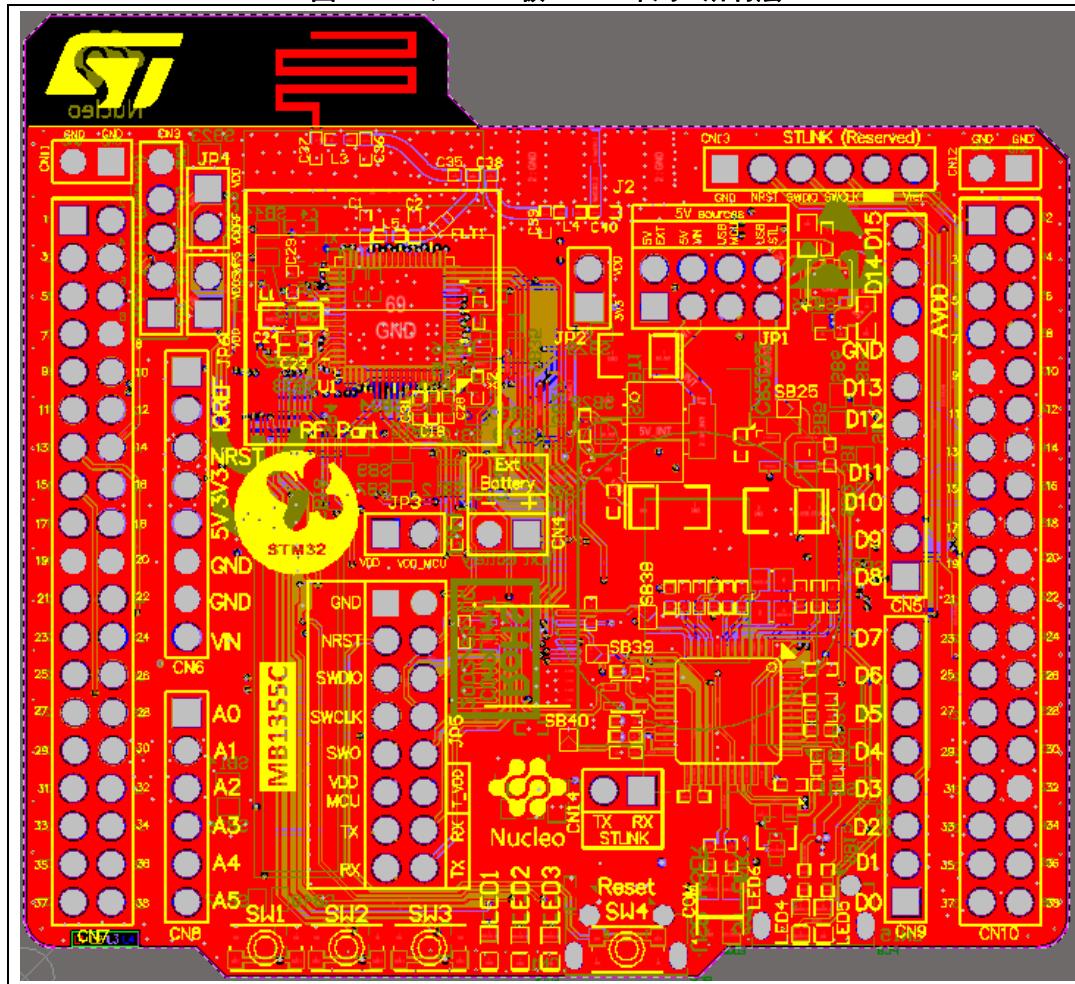

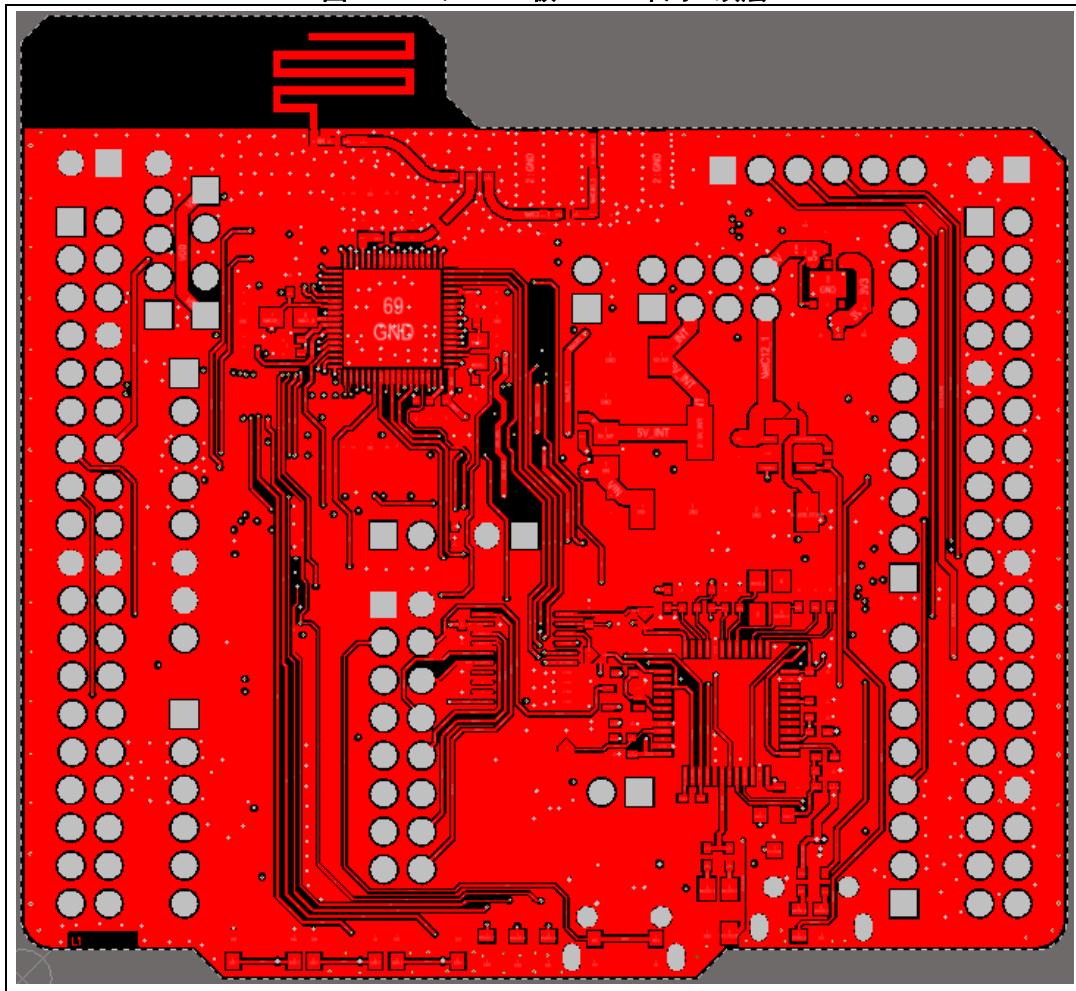

## 7 4层PCB Nucleo板MB1355C

图30. VFQFPN68板

图31. VFQFPN68板 - PCB布局 - 所有层

图32. VFQFPN68板 - PCB布局 - 顶层

图33. VFQFPN68板 - PCB布局 - 内层1

图34. VFQFPN68板 - PCB布局 - 内层2

图35. VFQFPN68板 - PCB布局 - 底层

## 7.1 关键部件

至于参考板，布局中的关键部件为RF、SMPS和LSE，以及该电路板上可用的PCB天线。

在该电路板上，FLT1滤波器已被更换为带通滤波器，以改善蜂窝设备的阻塞性能。但是，此滤波器会使2.4 GHz的有用BLE信号衰减的更严重，并导致1.5到2 dB的TX最大输出电平和灵敏度降低。

### 7.1.1 RF

匹配网络由C1和L5组成。C2和集成带通滤波器FLT1用于抑制杂散和谐波频率。C1、C2和L5的值取决于[第 5.4 节：4层PCB](#)中详述的PCB定义。

图36. RF的PCB布局细节

建议将匹配网络布置在尽可能靠近RF输出的地方，以避免在匹配网络的每个组件之间构成长走线。需要合理布置FLT1的方向，以将所有元件包含在屏蔽盒内。

### 7.1.2 SMPS

将C23、C24和C29布置在尽可能靠近STM32WB上的相应引脚的位置。请勿忘记将焊盘接地，以获得强大的电流回流路径。

图37. SMPS的PCB布局细节

### 7.1.3 LSE

将X2、C14和C15布置在尽可能靠近STM32WB上的相应引脚的位置，并沿芯片布置，以将其包含在屏蔽盒中。

图38. LSE的PCB布局细节

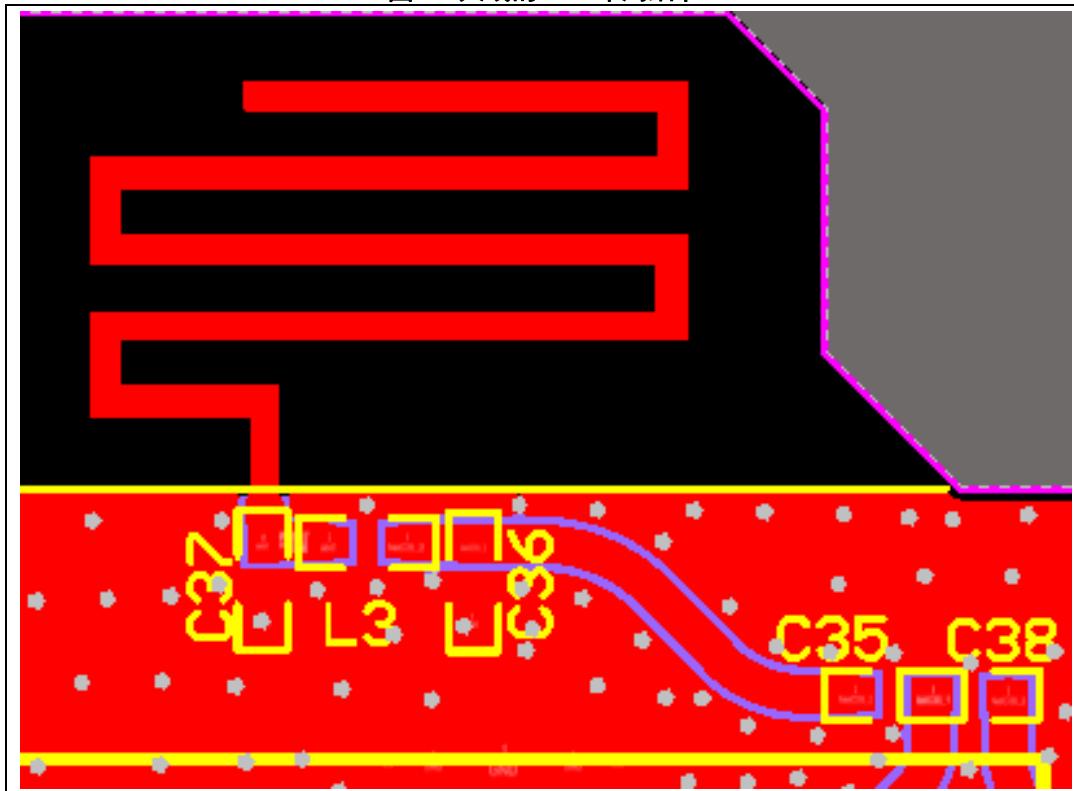

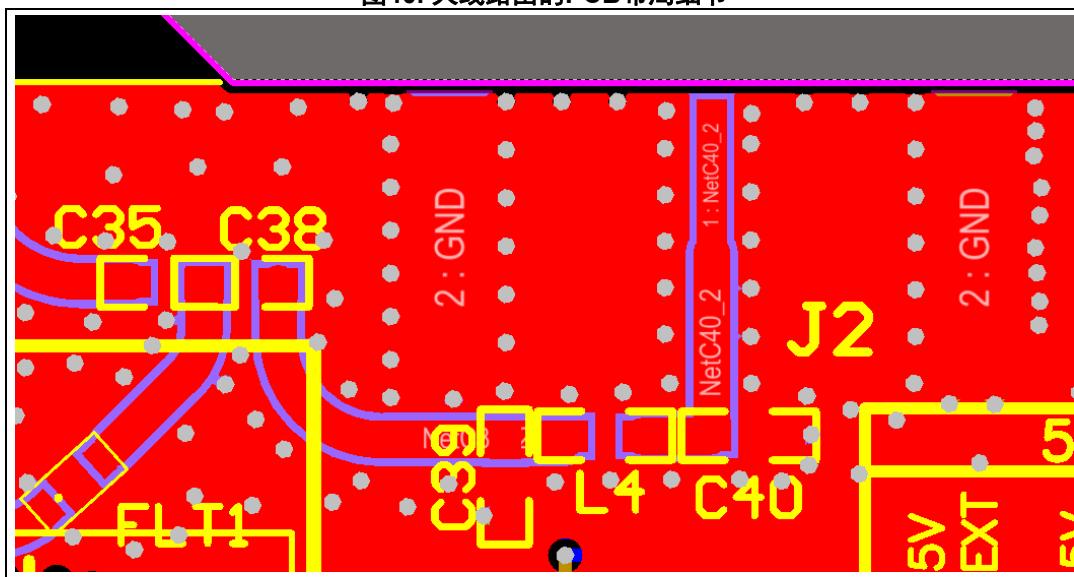

### 7.1.4 天线

通过将阻抗电路与由L3、C36和C37组成的PI网络相匹配，可将PCB天线的阻抗调整为所需的50 Ω（参见图 39）。有关此天线的更多详细信息，请参见[www.st.com](http://www.st.com)上提供的应用笔记AN5129。

图39. 天线的PCB布局细节

图40. 天线路由的PCB布局细节

在屏蔽盒外部有两个电容C35和C38（[图 40](#)）。如果输出路由到PCB天线，则焊接C35。如果输出路由到SMA，则焊接C38。

如果外部天线连接到SMA (J2)，则由L4、C39和C40组成的另一个PI网络可用于匹配阻抗。

## 8 带IPD的UFQFN48/VFQFN68参考板

IPD（集成无源器件）的目标为取代分立匹配网络以及集成低通滤波器，并保持相当的TX/RX性能。图41显示了两种方法之间的差异。

图41. 不同的匹配网络（左边是分立元件、右边是IPD）

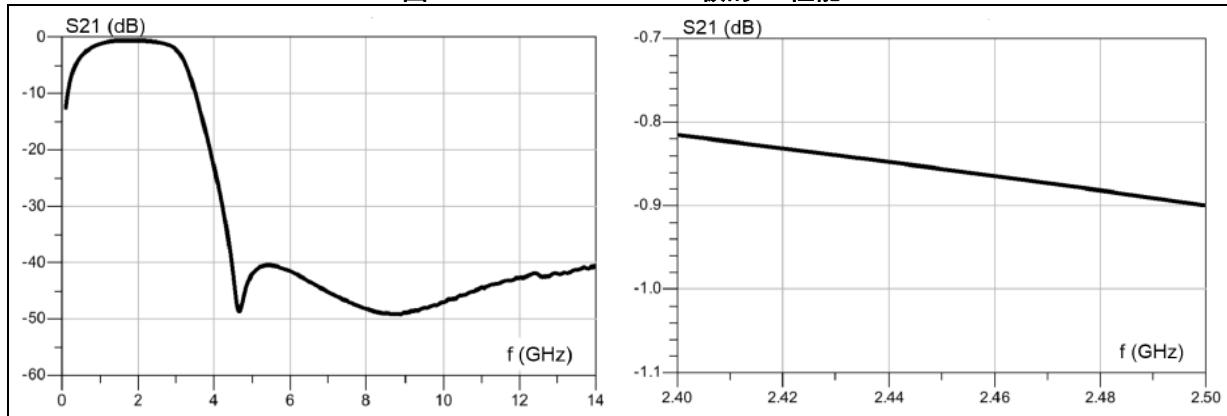

根据QFN封装的所需规格（尤其是参考平面中的STM32WB所呈现的阻抗）和参考板的2层PCB特性，开发出了MLPF-WB55-01E3板（DS12804，“与STM32WB55Cx/Rx相匹配的2.4GHz低通滤波器”，可通过[www.st.com](http://www.st.com)获得相关信息）。图42的左侧和右侧分别显示了其传输和插入损耗性能（均以dB表示）。

图42. MLPF-WB55-01E3板的RF性能

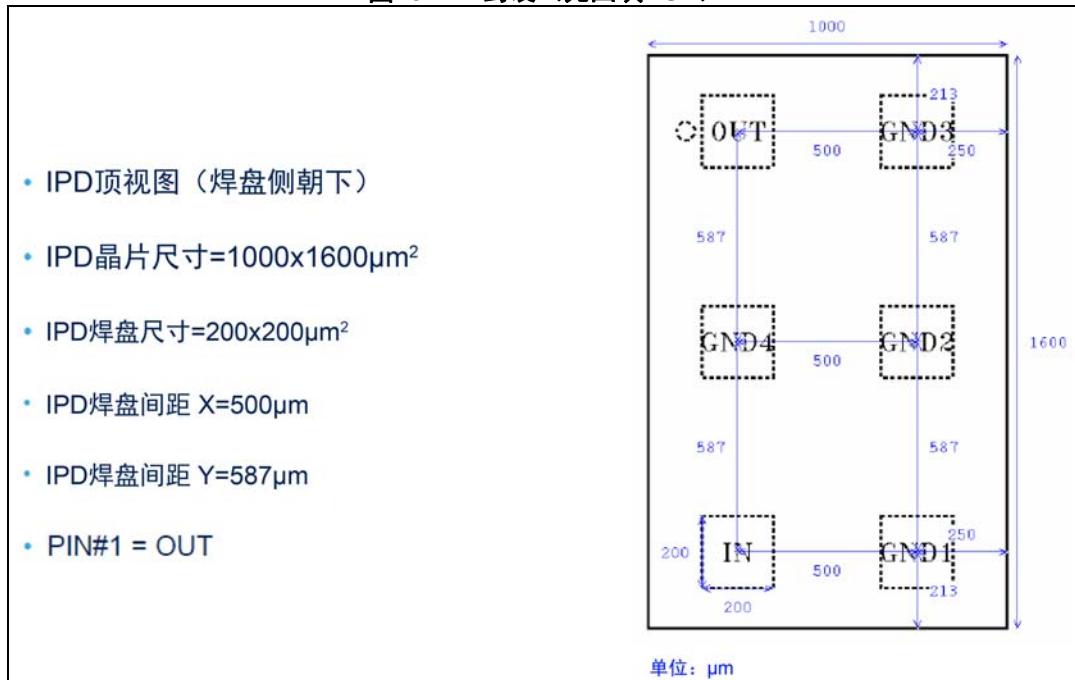

IPD封装的底视图如图 43中所示。

图43. IPD封装（无凸块CSP）

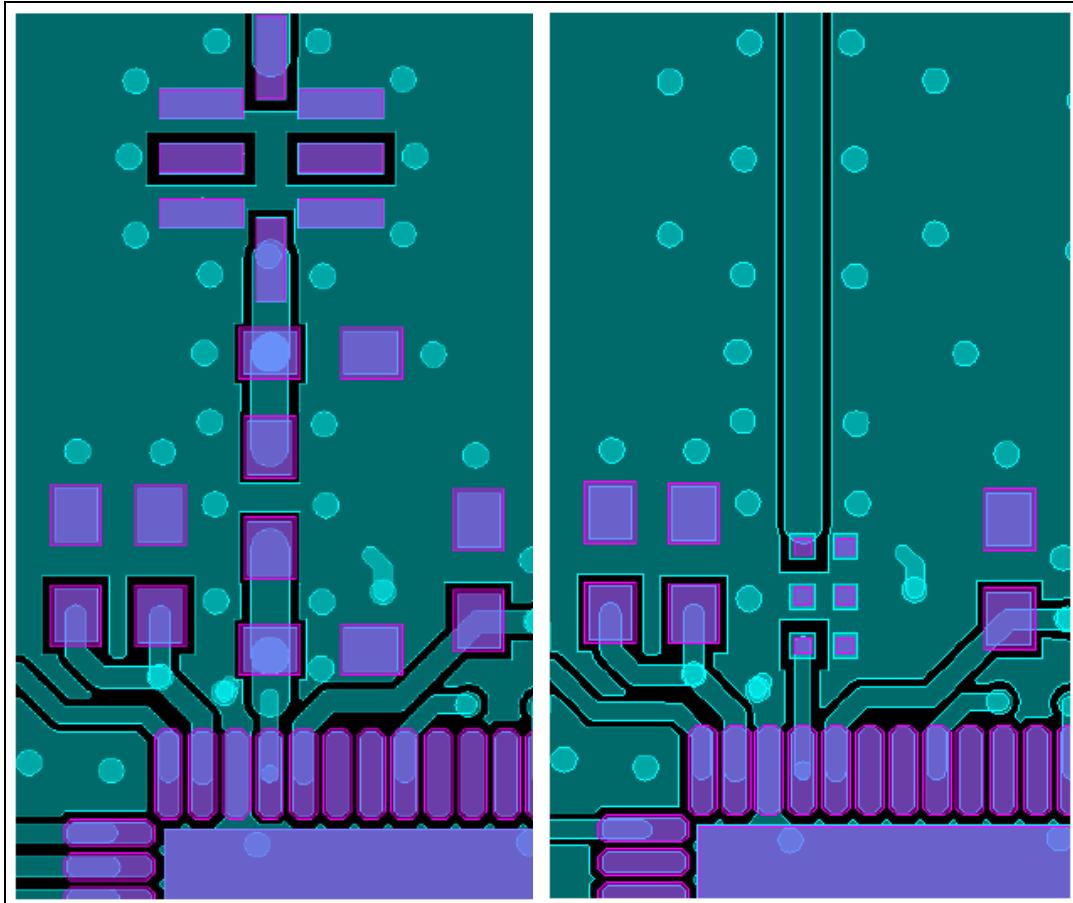

因此，可大大简化PCB，如图44所示。

图44. 采用分离匹配网络（左）和IPD（右）的PCB布局

请注意，可以进一步减小IPD输出和RF输出之间的走线长度，以减小PCB的尺寸。这可以通过降低该走线长度所造成的损耗来改善RF性能。

总之，IPD参考MLPF-WB55-01E3可替代2层PCB QFN封装的STM32WB的RF输出网络（仍需要天线滤波器）。与分立RF输出网络相比，这将缩减PCB尺寸和材料清单，同时确保相同的RF性能。IPD解决方案的另一个优点为量产的性能稳定性（与分立元件相比，参数离散度更低）。

## 9 结论

STM32WB系列微控制器集成了高性能RF前端。

为实现最佳TX和RX性能，在PCB设计期间必须解决几个方面的问题：

- PCB技术选择（层数、基底技术）

- 天线匹配和滤波网络计算

- 地平面以及关键RF元件的放置和走线

- SMPS和LSE元件的放置（如果使用）

本应用笔记提供了有用的指南，这些指南用于帮助用户实现STM32WB数据手册中所述的性能。

## 10 版本历史

表3. 文档版本历史

| 日期         | 版本 | 变更                                                  |

|------------|----|-----------------------------------------------------|

| 2018年9月14日 | 1  | 初始版本。                                               |

| 2019年1月18日 | 2  | 增加了 <a href="#">第 8 节：带IPD的UFQFN48/VFQFN68参考板</a> 。 |

| 2019年1月28日 | 3  | 文档分类由限于ST公司变为公开发布。                                  |

表4. 中文文档版本历史

| 日期         | 版本 | 变更      |

|------------|----|---------|

| 2021年7月14日 | 1  | 中文初始版本。 |

**重要通知 - 请仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和 / 或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用，ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息，请参考 [www.st.com/trademarks](http://www.st.com/trademarks)。所有其他产品或服务名称均为其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2021 STMicroelectronics - 保留所有权利