STM32MP151、STM32MP153、

以及STM32MP157系列硬件开发入门

## 引言

本应用笔记展示了如何使用STM32MP151、STM32MP153和STM32MP157系列，同时讲述了基于这些MPU产品开发应用所需的最低硬件资源要求。

本应用笔记为系统设计人员提供了所需的开发板硬件实现概述，关注如下特性：

- 电源

- 封装选择

- 时钟管理

- 复位控制

- 自举模式设置

- 调试管理。

本文还包括了参考设计原理图，说明了其主元件、接口和模式。

# 目录

|       |                                   |    |

|-------|-----------------------------------|----|

| 1     | 概述 . . . . .                      | 8  |

| 2     | 参考文档 . . . . .                    | 8  |

| 3     | 词汇表 . . . . .                     | 9  |

| 4     | 电源 . . . . .                      | 11 |

| 4.1   | 引言 . . . . .                      | 12 |

| 4.1.1 | 独立 ADC 和 DAC 转换器电源和参考电压 . . . . . | 12 |

| 4.1.2 | 电池备份 . . . . .                    | 13 |

| 4.1.3 | 稳压器 . . . . .                     | 13 |

| 4.2   | 电源方案 . . . . .                    | 14 |

| 4.3   | 复位和电源监控 . . . . .                 | 17 |

| 4.3.1 | 上电复位(POR)/掉电复位(PDR) . . . . .     | 17 |

| 4.3.2 | 可编程电压检测器 (PVD) . . . . .          | 17 |

| 4.3.3 | 应用和系统复位 . . . . .                 | 18 |

| 5     | 封装 . . . . .                      | 20 |

| 5.1   | 封装选择 . . . . .                    | 20 |

| 5.2   | 引脚复用映射 . . . . .                  | 22 |

| 5.3   | 各版本之间的封装兼容性 . . . . .             | 23 |

| 6     | 时钟 . . . . .                      | 28 |

| 6.1   | HSE OSC时钟 . . . . .               | 28 |

| 6.1.1 | 外部源 (HSE 旁路) . . . . .            | 29 |

| 6.1.2 | 外部晶振/陶瓷谐振器 (HSE晶振) . . . . .      | 29 |

| 6.2   | LSE OSC时钟 . . . . .               | 30 |

| 6.2.1 | 外部源 (LSE 旁路) . . . . .            | 30 |

| 6.2.2 | 外部晶振/陶瓷谐振器 (LSE 晶振) . . . . .     | 30 |

| 6.3   | 时钟安全系统 (CSS) . . . . .            | 31 |

| 6.3.1 | HSE 上的 CSS . . . . .              | 31 |

| 6.3.2 | LSE 上的 CSS . . . . .              | 31 |

| 7     | 自举配置 . . . . .                    | 32 |

|           |                                           |           |

|-----------|-------------------------------------------|-----------|

| 7.1       | 自举模式选择 . . . . .                          | 32        |

| 7.2       | 自举引脚连接 . . . . .                          | 33        |

| 7.3       | 嵌入式自举模式 . . . . .                         | 35        |

| <b>8</b>  | <b>调试管理 . . . . .</b>                     | <b>36</b> |

| 8.1       | 引言 . . . . .                              | 36        |

| 8.2       | SWJ 调试端口（串行接口和 JTAG） . . . . .            | 36        |

| 8.3       | 引脚排列和调试端口引脚 . . . . .                     | 36        |

| 8.3.1     | JTAG引脚上的内部上拉和下拉电阻 . . . . .               | 36        |

| 8.3.2     | 使用标准JTAG连接器的调试端口连接 . . . . .              | 37        |

| 8.3.3     | 使用STDC14连接器的调试端口和UART连接 . . . . .         | 38        |

| 8.3.4     | 并行跟踪和HDP . . . . .                        | 39        |

| 8.3.5     | 调试触发器和LED . . . . .                       | 41        |

| <b>9</b>  | <b>建议 . . . . .</b>                       | <b>42</b> |

| 9.1       | 印刷电路板 . . . . .                           | 42        |

| 9.2       | 元件位置 . . . . .                            | 42        |

| 9.3       | 接地和供电 ( $V_{SSx}$ 、 $V_{DDx}$ ) . . . . . | 42        |

| 9.4       | IO速度设置 . . . . .                          | 42        |

| 9.5       | PCB层叠和技术 . . . . .                        | 46        |

| 9.6       | 去耦 . . . . .                              | 50        |

| 9.7       | ESD/EMI保护 . . . . .                       | 50        |

| 9.8       | 敏感信号 . . . . .                            | 51        |

| 9.9       | 不使用的I/O和特性 . . . . .                      | 51        |

| <b>10</b> | <b>参考设计示例 . . . . .</b>                   | <b>52</b> |

| 10.1      | 说明 . . . . .                              | 52        |

| 10.1.1    | 时钟 . . . . .                              | 52        |

| 10.1.2    | 复位 . . . . .                              | 53        |

| 10.1.3    | 自举模式 . . . . .                            | 53        |

| 10.1.4    | SWD/JTAG接口 . . . . .                      | 53        |

| 10.1.5    | 电源 . . . . .                              | 54        |

| 10.1.6    | DDR3/DDR3L SDRAM . . . . .                | 57        |

| 10.1.7    | LpDDR2/LpDDR3 SDRAM . . . . .             | 58        |

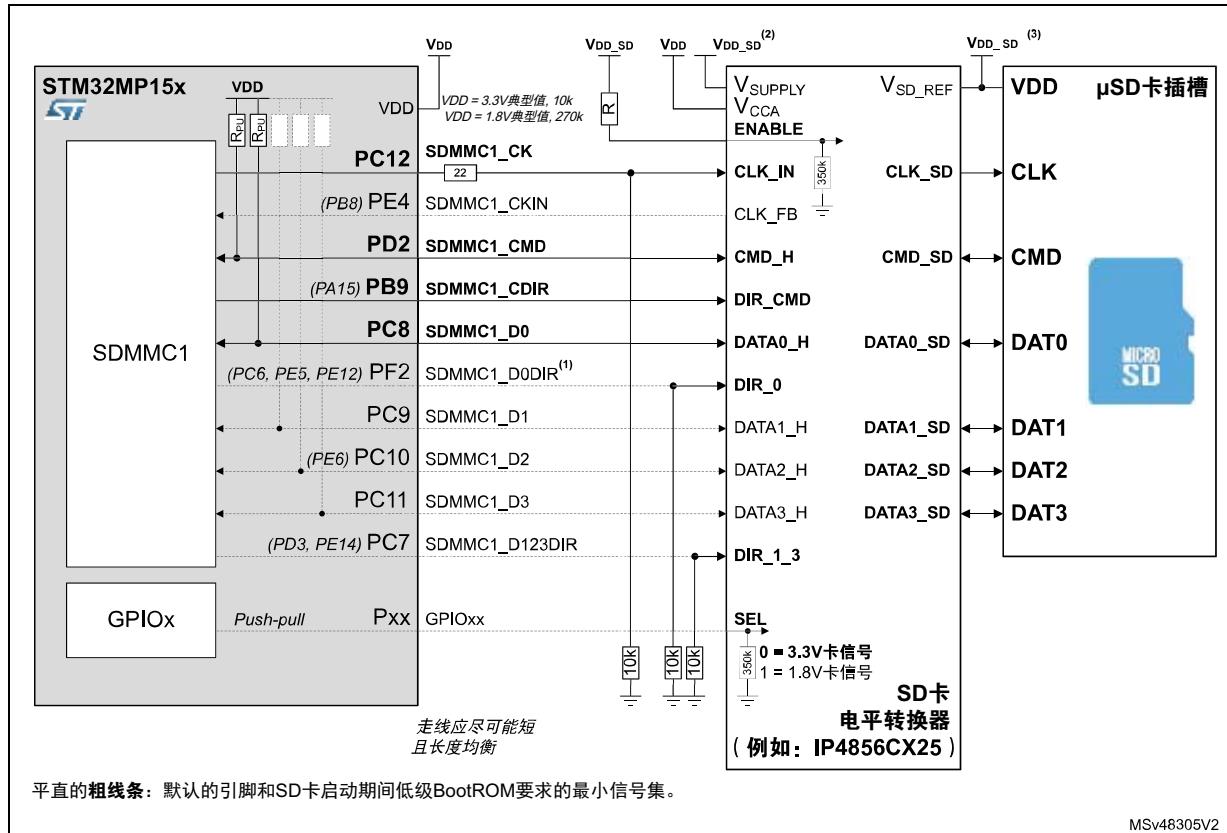

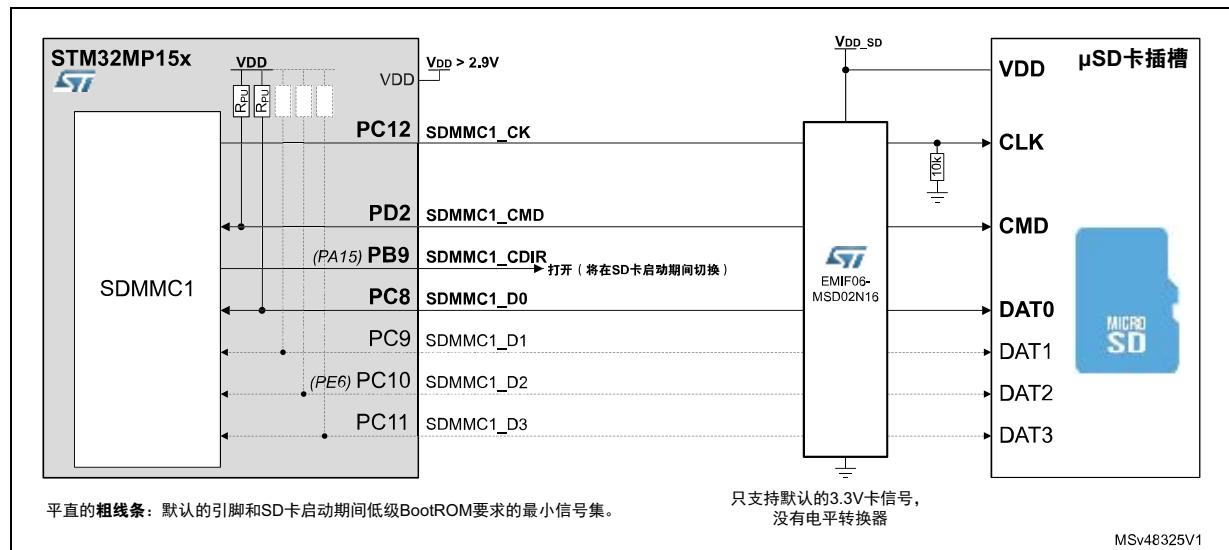

| 10.1.8    | SD卡 . . . . .                             | 59        |

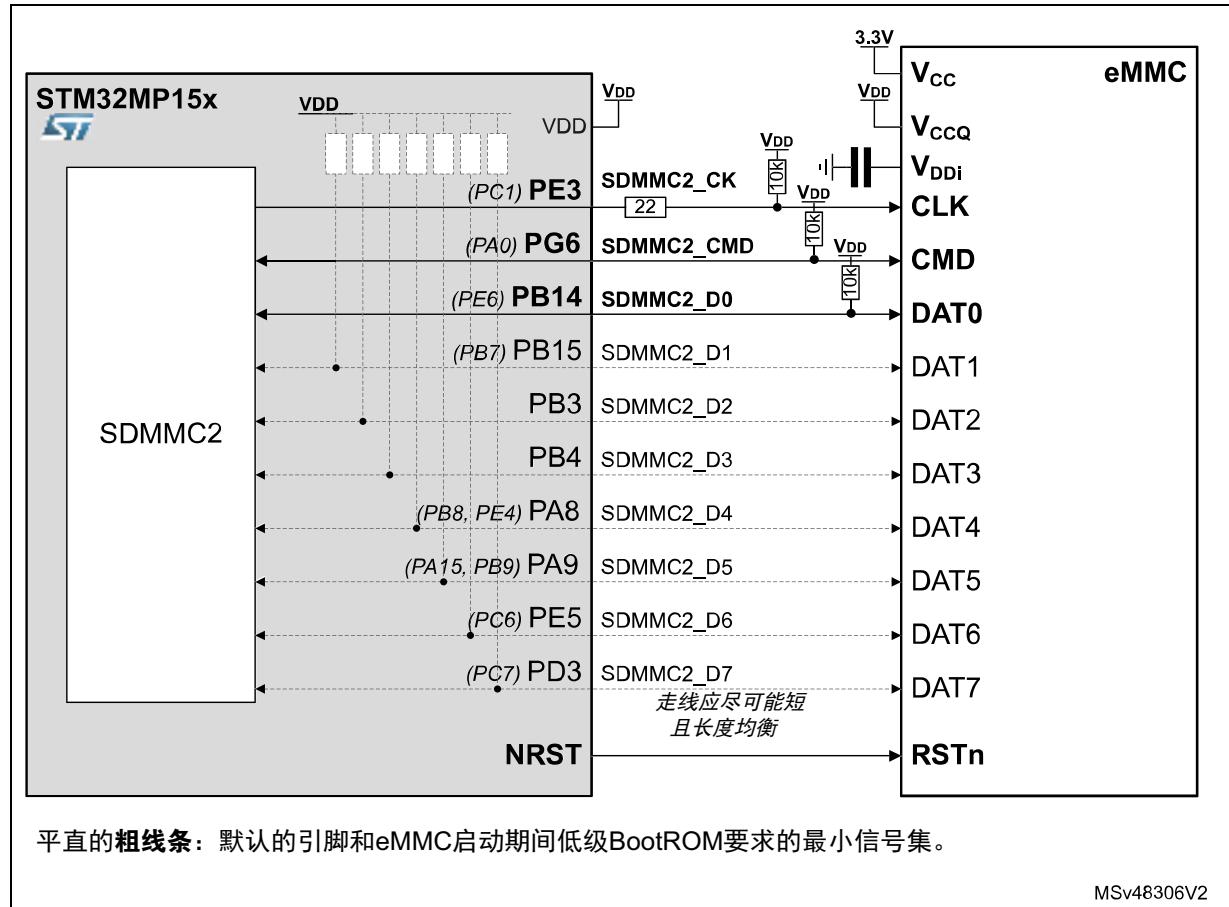

| 10.1.9    | eMMC™ Flash . . . . .                     | 61        |

---

|                                          |           |

|------------------------------------------|-----------|

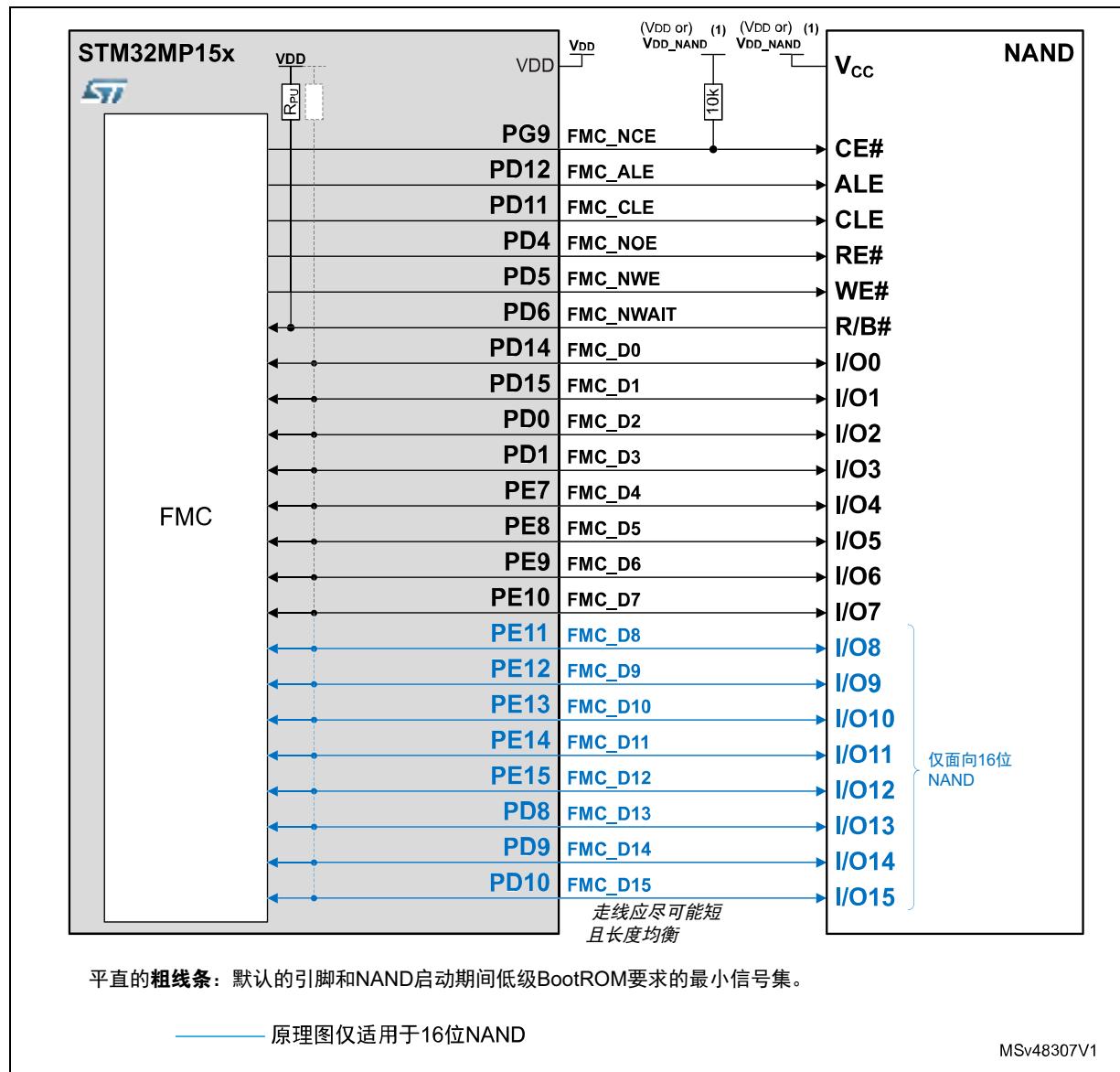

| 10.1.10 SLC NAND-Flash . . . . .         | 63        |

| 10.1.11 串行NOR-Flash/NAND-Flash . . . . . | 64        |

| 10.1.12 USB: . . . . .                   | 66        |

| 10.1.13 以太网 . . . . .                    | 69        |

| 10.1.14 显示串行接口（DSI） . . . . .            | 74        |

| <b>11 版本历史 . . . . .</b>                 | <b>76</b> |

## 表格索引

|      |                                                        |    |

|------|--------------------------------------------------------|----|

| 表1.  | 参考文档 .....                                             | 8  |

| 表2.  | 词汇表 .....                                              | 9  |

| 表3.  | ANASWVDD和EN_BOOSTER的推荐设置 .....                         | 13 |

| 表4.  | 封装的推荐去耦量 .....                                         | 16 |

| 表5.  | 封装总览 .....                                             | 20 |

| 表6.  | 与封装有关的主要功能变化 .....                                     | 21 |

| 表7.  | 器件兼容性汇总 .....                                          | 23 |

| 表8.  | 用于16x16 LFBGA354的STM32MP151xxx和STM32MP153xxx的兼容性 ..... | 24 |

| 表9.  | 用于10x10 TFBGA257的STM32MP151xxx和STM32MP153xxx的兼容性 ..... | 25 |

| 表10. | 用于12x12 TFBGA361的STM32MP151xxx和STM32MP153xxx的兼容性 ..... | 26 |

| 表11. | 用于18x18 LFBGA448的STM32MP151xxx和STM32MP153xxx的兼容性 ..... | 27 |

| 表12. | 自举模式 .....                                             | 32 |

| 表13. | VDD = 3.3 V典型值时的OSPEEDR设置示例 .....                      | 43 |

| 表14. | VDD = 1.8 V典型值时的OSPEEDR设置示例 .....                      | 44 |

| 表15. | 振荡器或晶振的HSE BOM .....                                   | 52 |

| 表16. | UART可能的自举引脚 .....                                      | 53 |

| 表17. | USB封装长度匹配值 .....                                       | 68 |

| 表18. | DSI封装长度匹配值 .....                                       | 75 |

| 表19. | 文档版本历史 .....                                           | 76 |

| 表20. | 中文文档版本历史 .....                                         | 76 |

# 图片目录

|      |                                             |    |

|------|---------------------------------------------|----|

| 图1.  | 供电方案 . . . . .                              | 11 |

| 图2.  | 上电复位/掉电复位波形 . . . . .                       | 17 |

| 图3.  | PVD 阈值 . . . . .                            | 18 |

| 图4.  | 复位引脚电路简图 . . . . .                          | 19 |

| 图5.  | STM32CubeMX示例截图 . . . . .                   | 22 |

| 图6.  | 16x16 LFBGA354兼容性 . . . . .                 | 24 |

| 图7.  | 10x10 TFBGA257兼容性 . . . . .                 | 25 |

| 图8.  | 12x12 TFBGA361兼容性 . . . . .                 | 26 |

| 图9.  | 18x18 LFBGA448兼容性 . . . . .                 | 27 |

| 图10. | HSE外部时钟 . . . . .                           | 28 |

| 图11. | HSE晶振/陶瓷谐振器 . . . . .                       | 28 |

| 图12. | LSE外部时钟 . . . . .                           | 30 |

| 图13. | LSE晶振/陶瓷谐振器 . . . . .                       | 30 |

| 图14. | 启动模式选择样例 . . . . .                          | 33 |

| 图15. | BOOT引脚典型接线原理图 . . . . .                     | 34 |

| 图16. | 启动流程简图 . . . . .                            | 35 |

| 图17. | 主机到板的连接 . . . . .                           | 36 |

| 图18. | JTAG/SWD MIPI10连接器实现示例 . . . . .            | 37 |

| 图19. | JTAG/SWD/UART VCP STDC14连接器实现示例 . . . . .   | 38 |

| 图20. | Mictor-38上带JTAG/SWD的并行跟踪端口实现示例 . . . . .    | 40 |

| 图21. | LED连接示例 . . . . .                           | 41 |

| 图22. | 各种负载和电压下的IO速度总结 . . . . .                   | 43 |

| 图23. | 6层PCB层叠示例 . . . . .                         | 46 |

| 图24. | 4层PCB层叠示例 . . . . .                         | 47 |

| 图25. | 0.8 mm脚间距封装的PCB规则示例 . . . . .               | 48 |

| 图26. | 0.5 mm脚间距封装的PCB规则示例 . . . . .               | 49 |

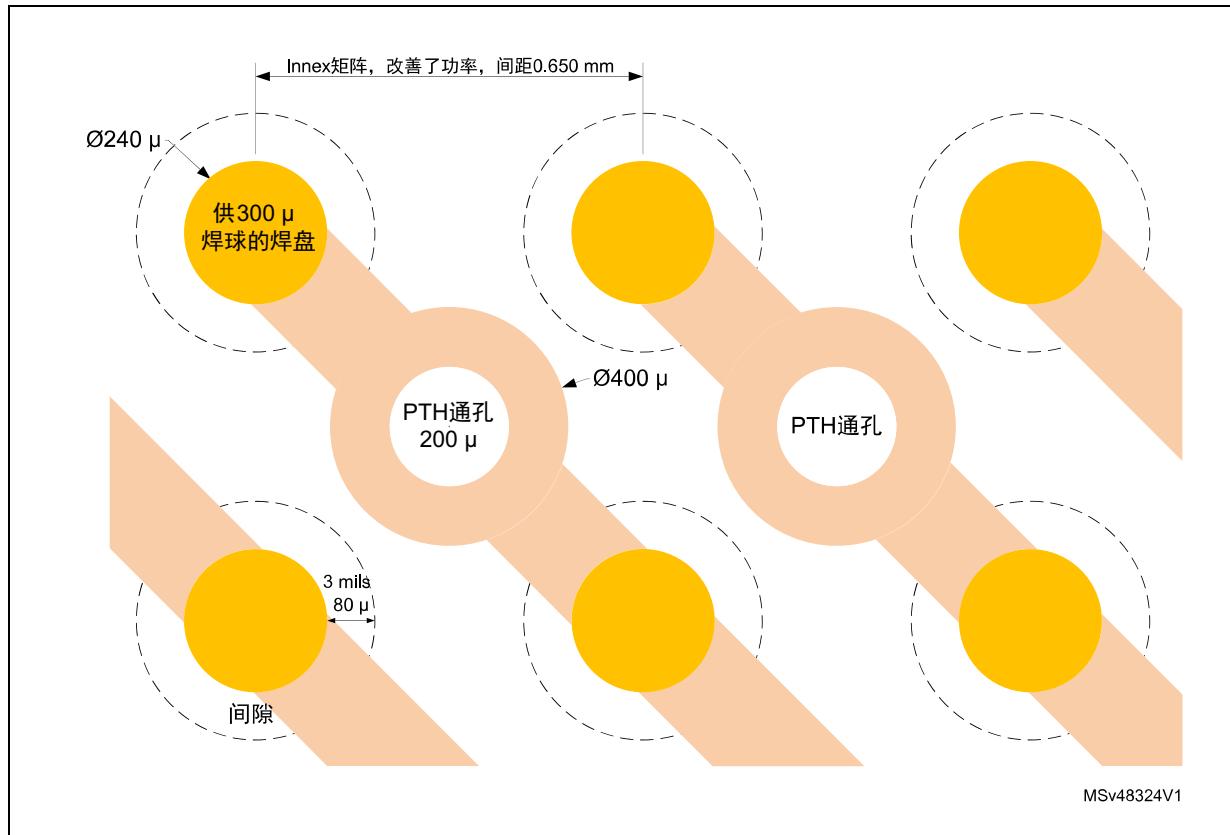

| 图27. | 改善了功率的0.65mm脚间距内焊球PCB规则示例 . . . . .         | 49 |

| 图28. | 去耦布局示例 . . . . .                            | 50 |

| 图29. | HSE推荐的振荡器/晶振选项的原理图 . . . . .                | 52 |

| 图30. | 采用DDR3L的3.3 V I/O分立电源示例 . . . . .           | 54 |

| 图31. | 采用DDR3L的3.3 V I/O的PMIC示例 . . . . .          | 55 |

| 图32. | 采用LPDDR2/LPDDR3的1.8 V I/O的PMIC示例 . . . . .  | 56 |

| 图33. | DDR3L 16/32位连接示例 . . . . .                  | 57 |

| 图34. | LPDDR2/LPDDR3 32位连接示例 . . . . .             | 58 |

| 图35. | 带外部电平转换器的SD卡连接示例 . . . . .                  | 60 |

| 图36. | 带3.3 V I/O的SD卡连接示例 . . . . .                | 61 |

| 图37. | eMMC™连接示例 . . . . .                         | 62 |

| 图38. | SLC NAND-Flash连接示例 . . . . .                | 63 |

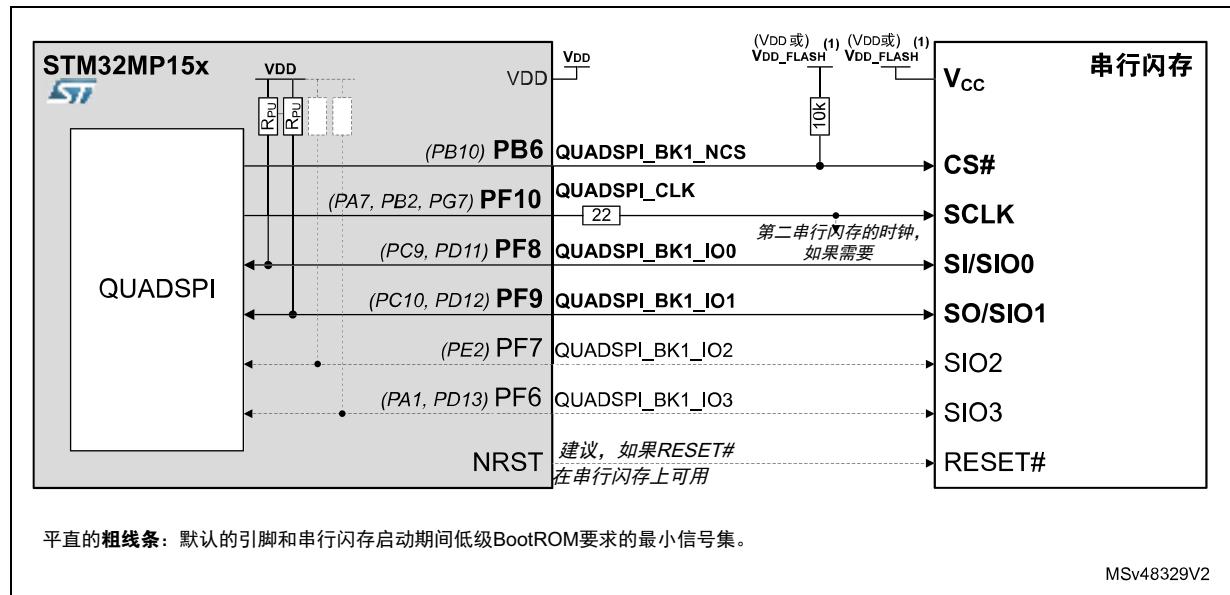

| 图39. | 串行Flash连接示例 . . . . .                       | 64 |

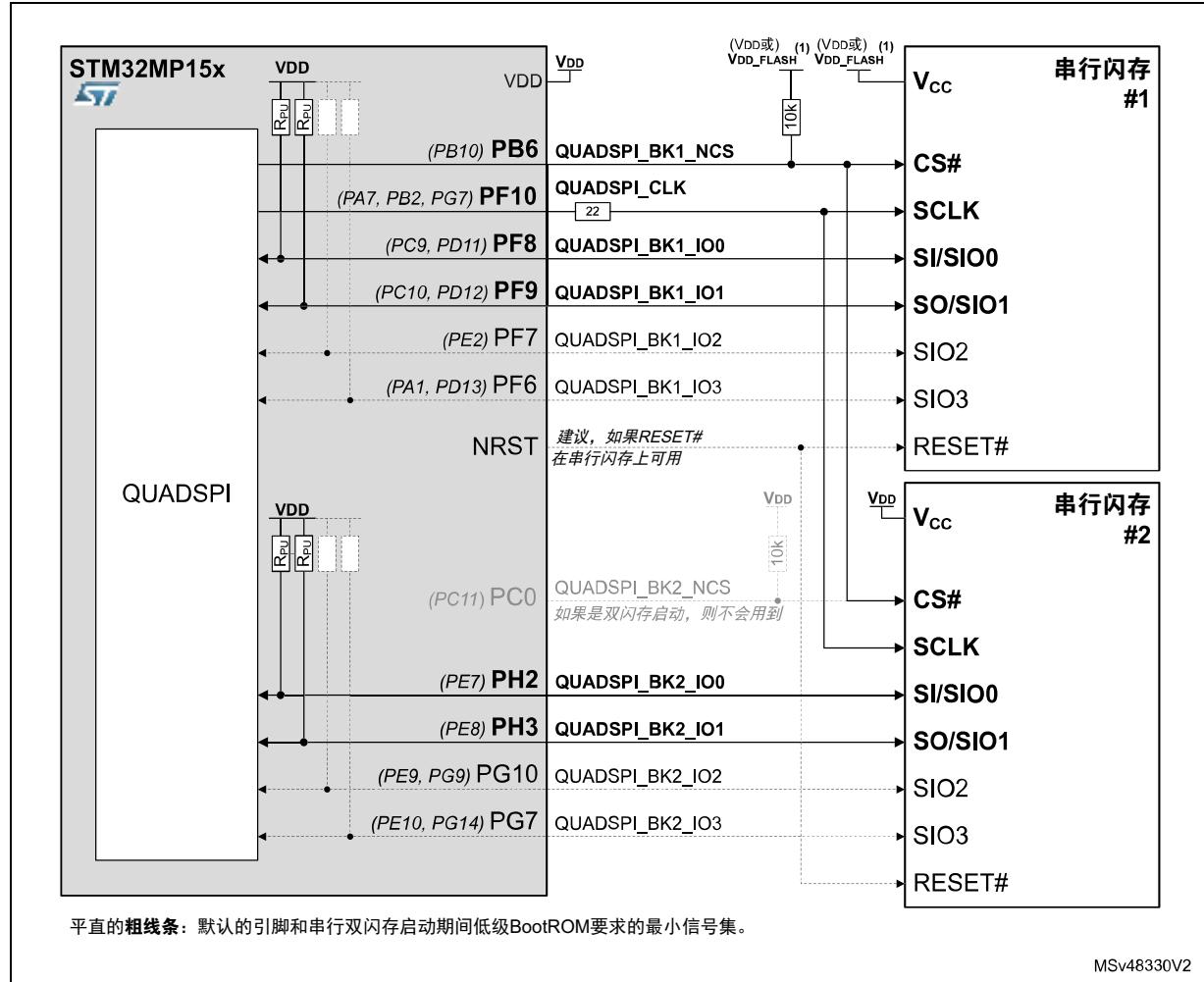

| 图40. | 双串行Flash连接示例 . . . . .                      | 65 |

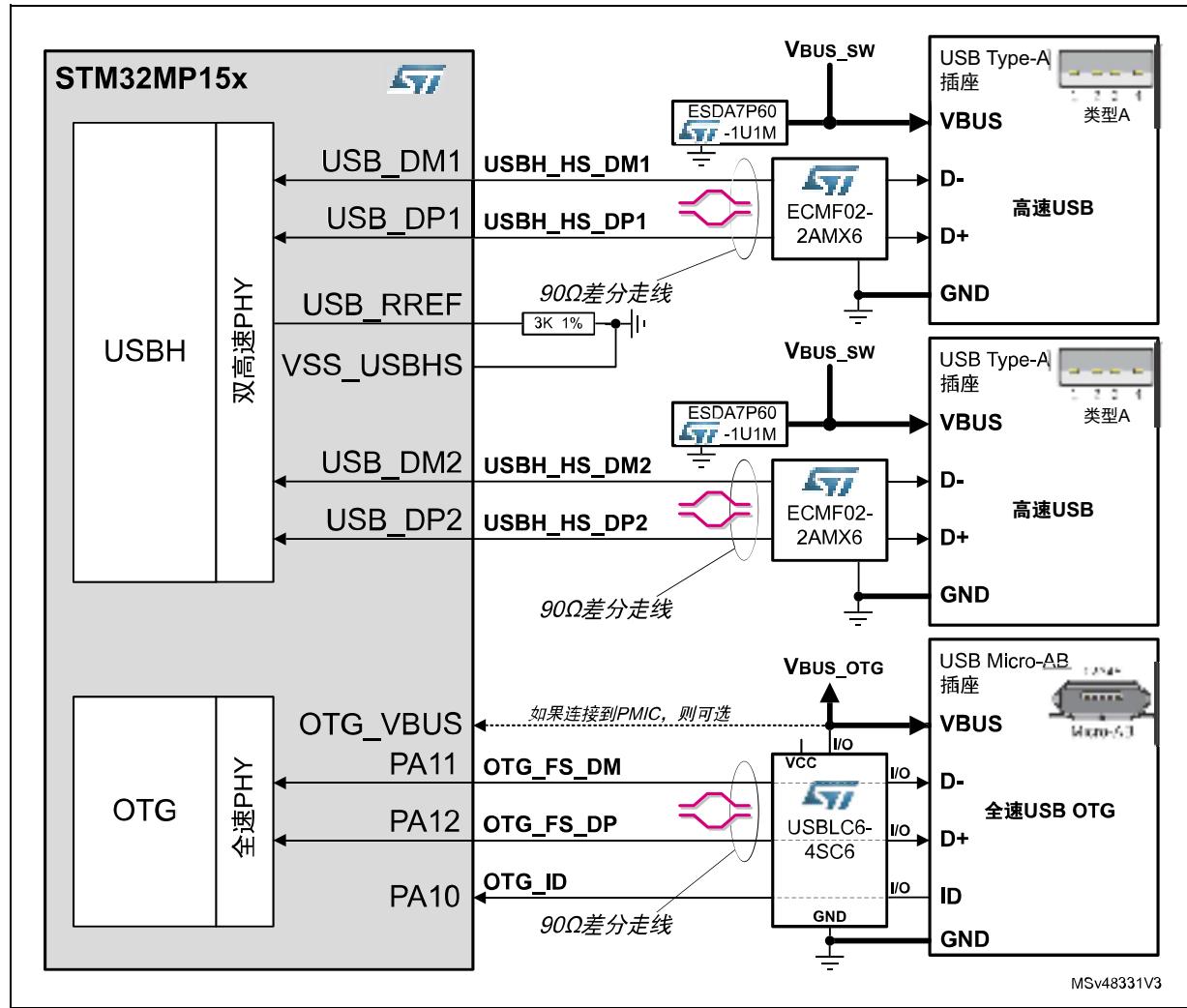

| 图41. | USB 2端口主机高速 + OTG全速连接示例 . . . . .           | 66 |

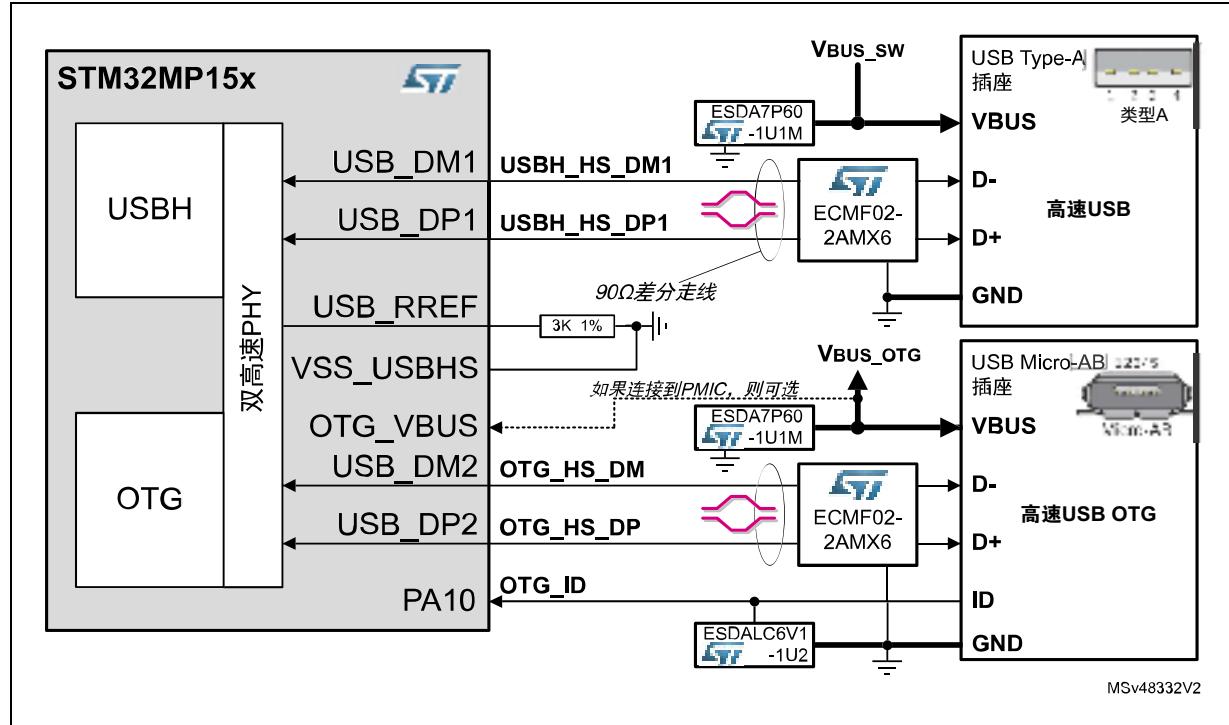

| 图42. | USB主机高速 + OTG高速连接示例 . . . . .               | 67 |

| 图43. | 适用于0.8 mm焊球间距封装的USB高速PCB走线示例 . . . . .      | 68 |

| 图44. | 10/100M以太网PHY连接示例 . . . . .                 | 69 |

| 图45. | 具有来自RCC的REFCLK的10/100M以太网PHY连接示例 . . . . .  | 70 |

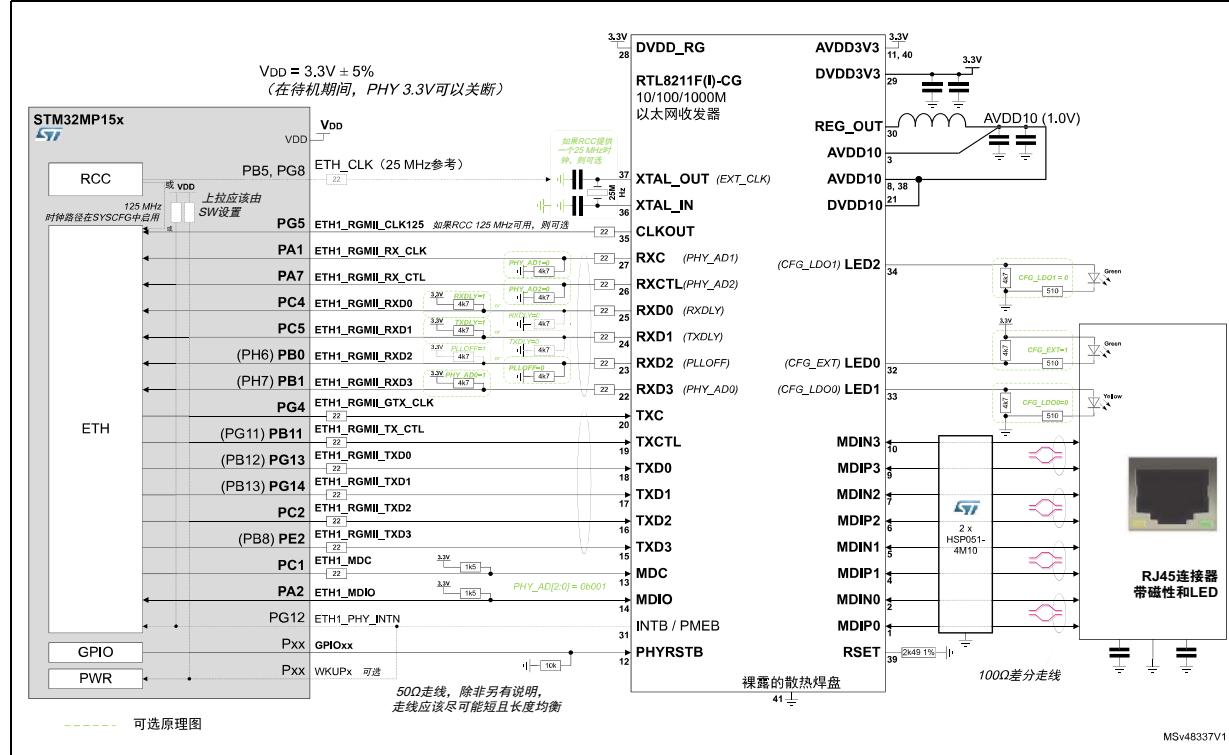

| 图46. | VDD=3.3 V (RTL8211E)的千兆以太网PHY连接示例 . . . . . | 71 |

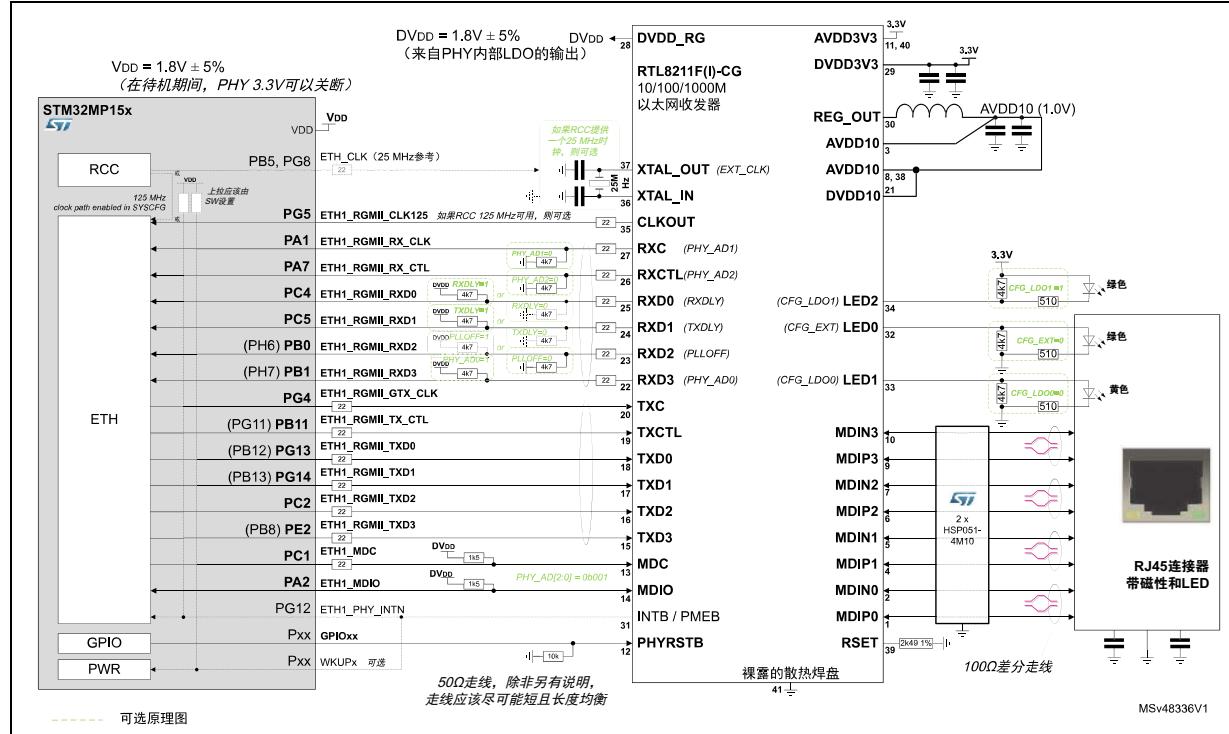

| 图47. | VDD=3.3 V (RTL8211F)的千兆以太网PHY连接示例 . . . . . | 72 |

| 图48. | VDD=1.8 V (RTL8211F)的千兆以太网PHY连接示例 . . . . . | 72 |

---

|      |                                                    |    |

|------|----------------------------------------------------|----|

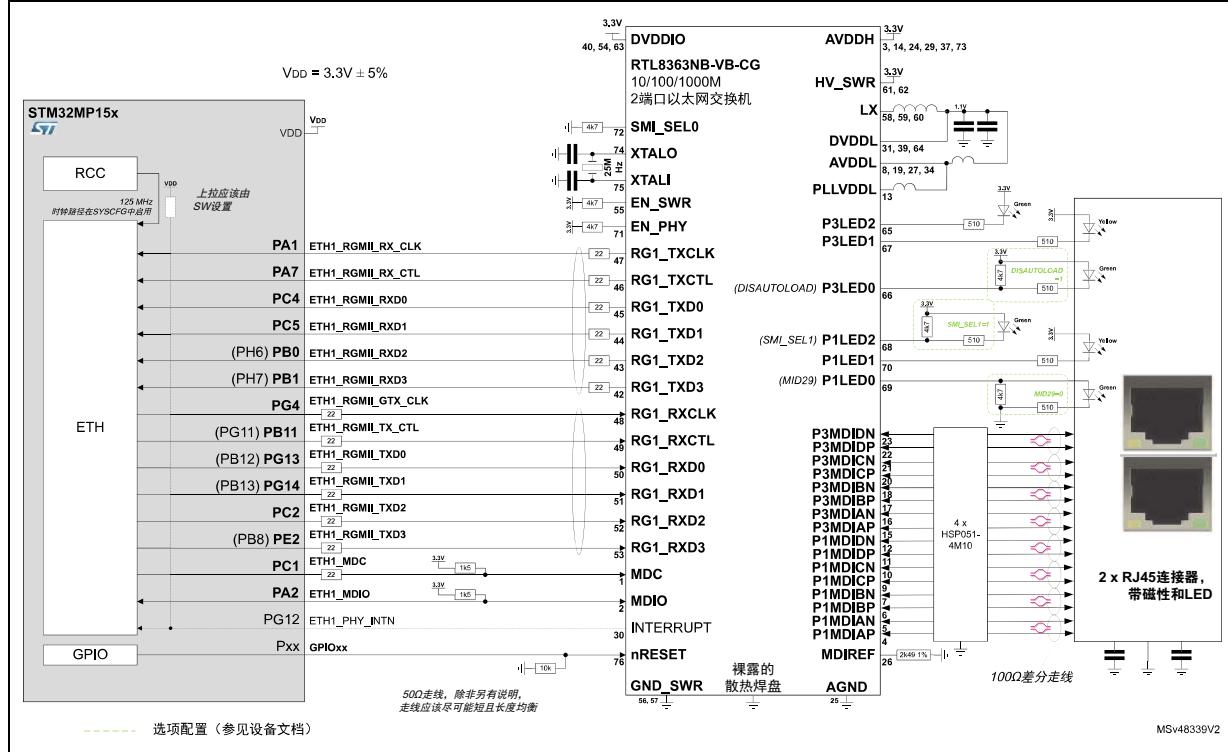

| 图49. | VDD = 3.3 V (RTL8363NB-VG)的千兆以太网2端口交换机示例 . . . . . | 73 |

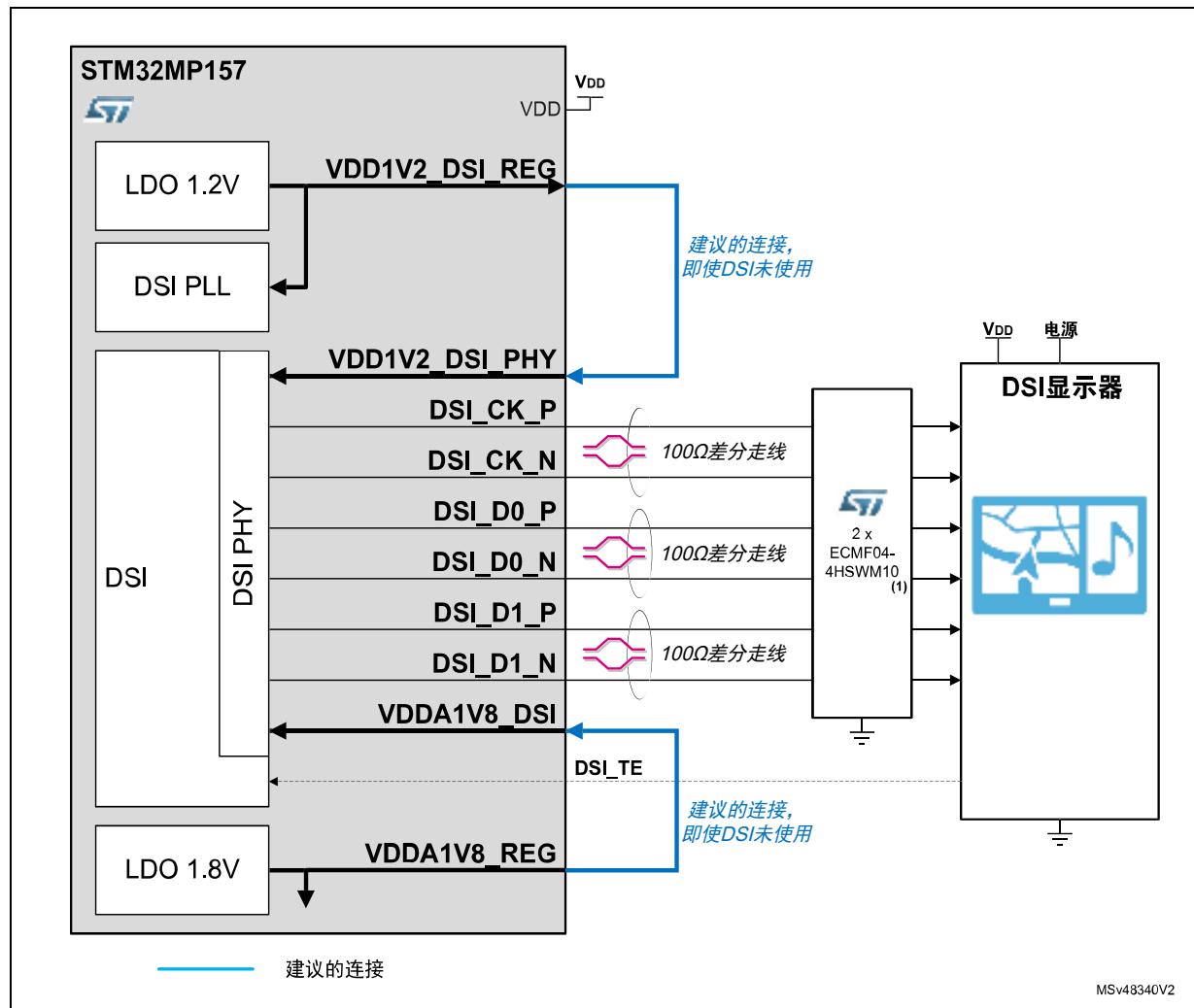

| 图50. | 采用DSI的显示连接示例 . . . . .                             | 74 |

| 图51. | 适用于0.8 mm焊球间距封装的DSI接口PCB走线示例 . . . . .             | 75 |

## 1 概述

本文档适用于基于Arm<sup>®</sup>(a)的器件。

## 2 参考文档

以下文档可从[www.st.com](http://www.st.com)获得。

表1. 参考文档

| 参考      | 标题                                       |

|---------|------------------------------------------|

| AN2867  | ST微控制器振荡器设计指南                            |

| AN1709  | ST微控制器EMC设计指南                            |

| AN5275  | STM32MP1系列自举程序中使用的USB DFU/USART协议        |

| AN5168  | STM32MP1系列MPU的DDR配置                      |

| AN5089  | STM32MP1系列和STPMIC1硬件 / 软件集成              |

| AN5122  | STM32MP1系列DDR存储器布线指南                     |

| AN5256  | STM32MP151、STM32MP153和STM32MP157分立电源硬件集成 |

| UM2535  | 带STM32MP157 MPU的评估板                      |

| UM2534  | 探索套件，采用STM32MP157 MPU                    |

| RM0441  | 基于Arm <sup>®</sup> 的STM32MP151高级32位MPU   |

| RM0442  | 基于Arm <sup>®</sup> 的STM32MP153高级32位MPU   |

| RM0436  | 基于Arm <sup>®</sup> 的STM32MP157高级32位MPU   |

| DS12500 | STM32MP151A/D数据手册                        |

| DS12501 | STM32MP151C/F数据手册                        |

| DS12502 | STM32MP153A/D数据手册                        |

| DS12503 | STM32MP153C/F数据手册                        |

| DS12504 | STM32MP157A/D数据手册                        |

| DS12505 | STM32MP157C/F数据手册                        |

a. Arm是Arm Limited（或其子公司）在美国和/或其他地区的注册商标。

### 3 词汇表

表2. 词汇表

| 术语      | 意义                                       |

|---------|------------------------------------------|

| ADC     | 模数转换器                                    |

| AHB     | 高级高性能总线                                  |

| CSI     | 低功耗内部振荡器                                 |

| CTI     | 交叉触发接口                                   |

| DAC     | 数模转换器                                    |

| DAP     | 调试访问端口                                   |

| DDRCTRL | 双倍数据速率SDRAM控制器。支持LPDDR2和DDR3/DDR3L协议     |

| DDRPHYC | DDR物理接口控制                                |

| DSI     | 显示串行接口主机                                 |

| ETH     | 以太网控制器                                   |

| EXTI    | 扩展中断和事件控制器                               |

| FMC     | 灵活存储控制器                                  |

| GPIO    | 通用输入输出                                   |

| HDP     | 硬件调试端口                                   |

| HSE     | 高速外部石英振荡器                                |

| HSI     | 高速内部振荡器                                  |

| I2C     | 内部IC总线                                   |

| IWDG    | 独立看门狗                                    |

| JTAG    | 联合测试行动小组 调试接口                            |

| LSE     | 低速外部石英振荡器                                |

| LSI     | 低速内部振荡器                                  |

| MDIOS   | 管理数据输入/输出从设备 用于控制以太网物理接口的接口              |

| OTG     | USB on the Go 使接口能够连接主机或设备的一种USB标准       |

| OTP     | 一次性程序存储器                                 |

| PMIC    | 电源管理集成电路 通过信号和串行接口提供具有很大可控性的各种平台电源的外部电路。 |

| PWR     | 电源控制                                     |

| QUADSPI | 四路数据通道串行外设接口                             |

| RCC     | 复位和时钟控制                                  |

| ROM     | 只读存储器                                    |

| RTC     | 实时时钟                                     |

| SDMMC   | 安全数字和多媒体卡接口。支持SD、MMC、eMMC和SDIO协议         |

表2. 词汇表（续）

| 术语      | 意义             |

|---------|----------------|

| SMPS    | 开关模式电源         |

| SPI     | 串行外设接口         |

| STM     | 系统跟踪宏单元        |

| SW      | 软件             |

| SWD     | 串行线调试          |

| SWO     | 单线输出。一个跟踪端口    |

| SYSCFG  | 系统配置           |

| TAMP    | IP篡改检测         |

| TEMP    | 温度传感器          |

| UART    | 通用异步收发器        |

| USART:  | 通用同步/异步收发器     |

| USB:    | 通用串行总线         |

| USBH    | USB主机控制器       |

| VREFBUF | ADC/DAC电压参考缓冲器 |

## 4 电源

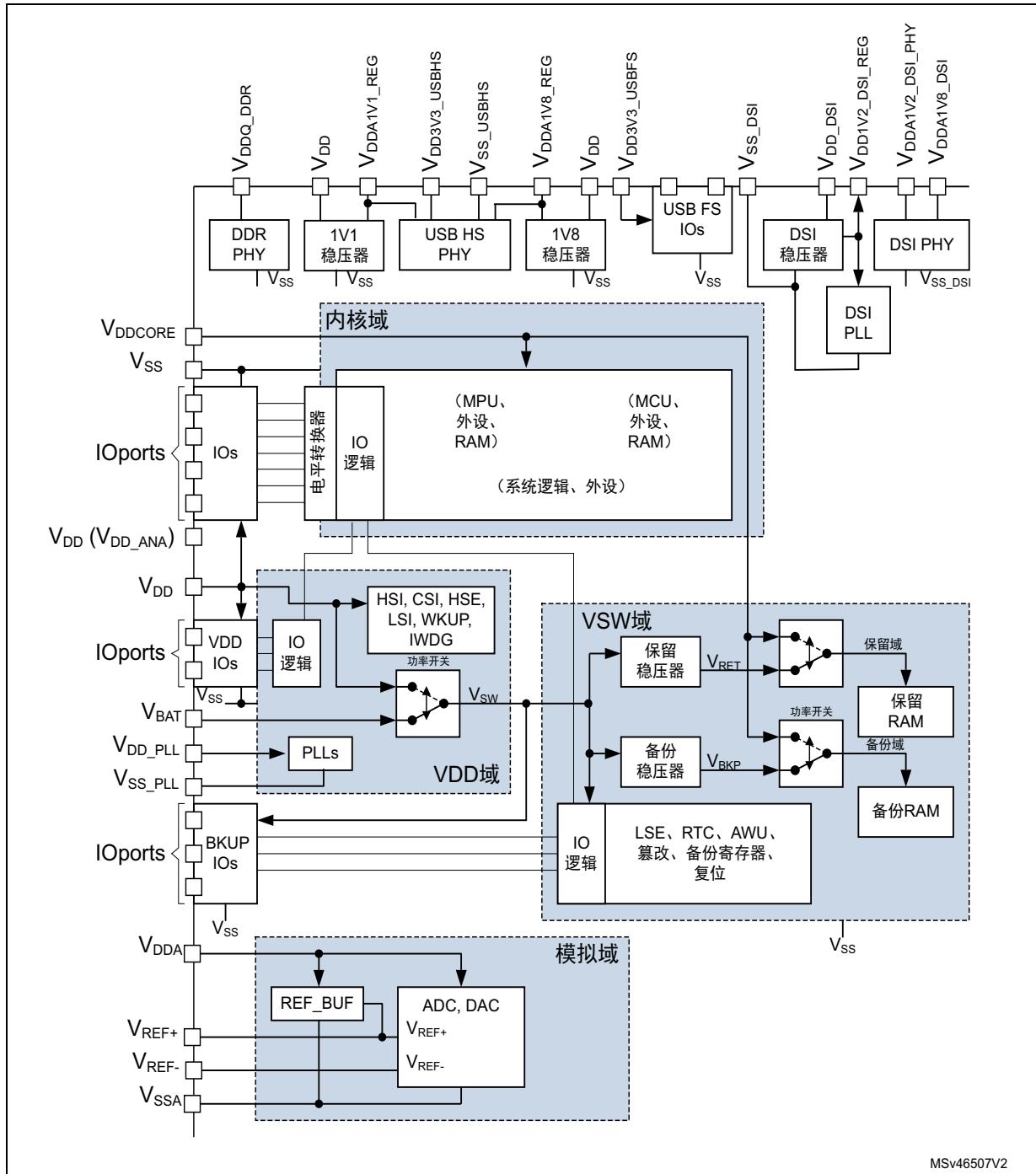

图1. 供电方案

MSv46507V2

## 4.1 引言

注：

参见产品数据手册中的详细信息和正常操作点。

- 主IO供电电压 ( $V_{DD}$ ) 范围为1.71 V到3.6 V。

- 核心逻辑工作供电电压 ( $V_{DDCORE}$ ) 范围为1.18 V到1.25 V。

- USB供电电压 ( $V_{DD3V3\_USBHS}$  和  $V_{DD3V3\_USBFS}$ ) 范围为3.07 V到3.6 V。

- 嵌入式稳压器用于为一些内部模块供电。

– DSI的1.2 V LDO由  $V_{DD1V2\_DSI\_REG}$  提供，用于为DSI PLL和  $V_{DD1V2\_DSI\_PHY}$  引脚供电。电压范围为1.15 V到1.26 V。

– DSI和USB的1.8 V LDO由  $V_{DDA1V8\_REG}$  提供，用于为USB内部和  $V_{DDA1V8\_DSI}$  供电。

当  $BYPASS\_REG1V8 = V_{DD}$  时， $V_{DDA1V8\_REG}$  必须从外部供电。在这种情况下，电压范围为1.65 V到1.95 V。

– USB的1.1 V LDO由  $V_{DD1V1\_REG}$  提供，用于外部去耦。

注：不得使用嵌入式稳压器为外部组件供电。

- 当主电源  $V_{DD}$  断电时，可通过  $V_{BAT}$  电压为实时时钟(RTC)和备份寄存器供电。该内部电源在  $V_{BAT}$  和  $V_{DD}$  之间有一个自动开关，并被称为  $V_{SW}$  域，也用于为PI8、PC13、PC14、PC15引脚供电。

$V_{BAT}$  的电压范围1.20 V到3.6 V。

当  $V_{DD}$  高于  $V_{BAT}$  时，可在  $V_{BAT}$  上为外部备用电压器件（如超级电容器）启用小充电电流。

### 4.1.1 独立 ADC 和 DAC 转换器电源和参考电压

为了提高转换精度和动态范围，ADC、DAC和参考电压源均配有独立电源，可以单独滤波并屏蔽PCB上的噪声。

模拟工作供电电压 ( $V_{DDA}$ ) 范围为1.71 V到3.6 V（DAC只能在  $V_{DDA}$  高于或等于1.8 V时使用）。

- ADC/DAC/VREFBUF 电压源从单独的  $V_{DDA}$  引脚输入。

- $V_{SSA}$  引脚提供了独立的电源接地连接。

在所有情况下， $V_{SSA}$  引脚应该外部连接到相同的供电地，而不是  $V_{SS}$ 。

#### 外部VREF

用户可在  $V_{REF+}$  上连接输入独立的ADC/DAC外部参考电压。 $V_{REF+}$  上的电压可能介于1.62 V和  $V_{DDA}$  之间。

注：

为能够运行，DAC需要  $V_{REF+}$  高于1.8 V。

#### 内部VREF

用户可在VREFBUF模块中使能  $V_{REF+}$  上的内部参考电压。

$V_{REF+}$  上的电压可在1.5 V、1.8 V、2.048 V和2.5 V之间选择。

当  $V_{REF+}$  引脚上具有内部VREF时，如果负载保持在数据手册中的值以内，则内部VREF可用于外部（如用于模拟比较器参考）。

注：

为能够运行，DAC需要  $V_{REF+}$  高于1.8 V。

**注:**  $V_{REFBUF}$ 需要 $V_{DDA}$ 等于或高于 $V_{REF+} + 0.3\text{ V}$ 。

**注意:** 当存在Vref-引脚时（取决于封装）， $V_{REF-}$ 必须从外部连至 $V_{SSA}$ 。

### 用于ADC模拟输入开关的升压器

ADC输入与模拟开关复用，当 $V_{DDA}$ 电源电压低于2.7 V时，模拟开关的性能会降低。为最大限度地发挥ADC模拟性能，可通过 $V_{DD}$ （如果高压2.7 V）或 $V_{DDA}$ 的嵌入式3.3 V升压器为模拟开关供电。

在SYSCFG\_PMCR寄存器中完成控制。

**表3. ANASWVDD和EN\_BOOSTER的推荐设置**

| $V_{DDA}$<br>(V) | $V_{DD}$<br>(V) | --> | SYSCFG_PMCR.<br>ANASWVDD | SYSCFG_PMCR.<br>EN_BOOSTER | 开关<br>电源           | ADC模拟性能 |

|------------------|-----------------|-----|--------------------------|----------------------------|--------------------|---------|

| >2.7             | 1.71至3.6        | -   | 0                        | 0                          | $V_{DDA}$ (>2.7 V) | 最大值     |

| <2.7             | >2.7            | -   | 1                        | 0                          | $V_{DD}$ (>2.7 V)  |         |

|                  | <2.7            | -   | 0                        | 1 <sup>(1)</sup>           | 升压器 (~3.3 V)       |         |

|                  |                 |     |                          | 0 <sup>(2)</sup>           | $V_{DDA}$ (<2.7 V) | 降低      |

1. 升压电压可能需要50 微秒才能稳定下来。

2. 如果可以接受ADC模拟性能降低，禁用升压器最多可节省250 微安的电流。

### 4.1.2 电池备份

为了在 $V_{DD}$ 关闭后保留备份寄存器BKPSRAM和RETRAM的内容，可以将 $V_{BAT}$ 引脚连接到由电池或其它电源供电的可选备用电压。

$V_{BAT}$ 引脚还为RTC单元供电，因此即使当主数字供电（ $V_{DD}$ ）关闭时RTC也能工作。 $V_{BAT}$ 电源的开关由复位模块中内置的掉电复位（PDR）电路进行控制。

若应用中没有使用外部电池，则需要将 $V_{BAT}$ 外部连至 $V_{DD}$ 。

### 4.1.3 稳压器

如果BYPASS\_REG1V8 =  $V_{SS}$ ，则在上电复位后始终使能1.8 V LDO（用于USB和DSI）。这不受(LP/LPLV-)Stop影响，但在进入待机模式时会被禁用。

上电复位后始终使能1.1 V LDO（用于USB）。这不受(LP/LPLV-)Stop影响，但在进入待机模式时会被禁用。

1.2 V LDO（用于DSI）在系统复位后被禁用，在使用DSI前必须通过软件启用。这不受(LP/LPLV-)Stop影响，但在进入待机模式时会被禁用。

**注:** 除非特别说明，否则不得使用嵌入式稳压器为外部组件供电。

## 4.2 电源方案

电路由多个电源供电：

- $V_{DD}$ 是IO的主电源，在待机模式期间，内部部件保持供电。有用电压范围为1.71 V到3.6 V（如1.8 V、2.5 V、3.0 V或3.3 V典型值）

- 这些电源必须连接到外部去耦电容（参见表 4）。

- $V_{DD\_DSI}$ 、 $V_{DD\_PLL}$ 和 $V_{DD\_ANA}$ 必须连接至 $V_{DD}$

- $V_{DDCORE}$ 是主数字电压，可在待机模式期间从外部关闭。运行模式下的电压范围为1.18 V~1.25/1.38 V（典型值为1.2/1.34 V）。

- 该电源必须连接到外部去耦电容（参见表 4）

- 可在特定停止模式下进一步减小 $V_{DDCORE}$ 。这涉及PWR\_ON信号（如对于STPMIC1、外部电源管理IC）或PWR\_LP信号（对于SMPS分立组件）

- $V_{BAT}$ 引脚可连至外部电池( $1.2 \text{ V} < V_{BAT} < 3.6 \text{ V}$ )。

- 如果使用RETRAM，则最小 $V_{BAT}$ 为1.4 V

- 如果应用不支持备用电池，则建议将该引脚连接到 $V_{DD}$ 。

- 如果应用支持备用电池，则建议在 $V_{BAT}$ 和 $V_{SS}$ 之间添加一个100 nF的陶瓷去耦电容。

- 如果应用在 $V_{BAT}$ 上使用超级电容器，则不需要额外的去耦。

- $V_{DDA}$ 引脚是模拟(ADC/DAC/VREFBUF)电源，必须连接到外部去耦电容（参见表 4）。

- $V_{REF+}$ 引脚可连至 $V_{DDA}$ 外部供电电源。如果将独立的内部或外部参考电压施加到 $V_{REF+}$ 上，则必须在该引脚和 $V_{REF-}$ 之间连接去耦电容（参见表 4）。请参见第 4.1.1 节。

进一步过滤模拟噪声的方法：

- $V_{DDA}$ 可通过基于电感器的滤波器连接到 $V_{DD}$ 。

- $V_{DDQ\_DDR}$ 是DDR IO电源，必须将其连接到外部去耦电容（参见表 4）。

- 连接DDR3内存时的电压范围为1.425 V到1.575 V（1.5 V典型值）

- 连接DDR3L内存时的电压范围为1.283 V到1.45 V（1.35 V典型值）

- 连接LPDDR2或LPDDR3内存时的电压范围为1.14 V到1.3 V（1.2 V典型值）

- $V_{DDA1V2\_DSI\_REG}$ 引脚是内部稳压器的输出引脚，必须将其连接到外部去耦电容（参见表 4）。

- $V_{DDA1V2\_DSI\_REG}$ 从内部连接到DSI PLL。

- $V_{DDA1V2\_DSI\_PHY}$ 为模拟DSI PHY电源。电压范围为1.15 V到1.26 V（1.2 V典型值） $V_{DDA1V2\_DSI\_PHY}$ 应连接到 $V_{DDA1V2\_DSI\_REG}$ 。

- $V_{DD3V3\_USBHS}$ 和 $V_{DD3V3\_USBFS}$ 分别为USB高速和全速PHY电源。电压范围为3.07 V到3.6 V。必须一起连接到外部去耦电容（参见表 4）。

$V_{DD3V3\_USBFS}$ 用于为OTG\_VBUS和OTG\_ID (PA10)引脚供电。因此，当使用USB高速双角色端口或USB高速设备时，也必须为 $V_{DD3V3\_USBFS}$ 供电。如果不使用，应将其连接到 $V_{DD}$ 。

- $V_{DDA1V8\_REG}$ 引脚是内部稳压器的输出引脚，必须将其连接到外部去耦电容（参见表 4）。

- $V_{DDA1V8\_REG}$ 从内部连接到USB PHY和USB PLL。

- 默认情况下使能内部 $V_{DDA1V8\_REG}$  稳压器，可通过软件进行控制。它在待机期间始终关闭。

- 对于1.8 V稳压器配置，有个特定的BYPASS\_REG1V8引脚应连接到 $V_{SS}$ 或 $V_{DD}$ ，以激活或禁用稳压器。当 $V_{DD}$ 低于2.25 V时，必须绕过1.8 V稳压器：

- BYPASS\_REG1V8 =  $V_{DD}$ 。在这种情况下， $V_{DDA1V8\_REG}$ 引脚应连接至 $V_{DD}$ （如果低于1.98V）或专用的1.65 V - 1.98 V电源（1.8 V典型值）。

- BYPASS\_REG1V8 =  $V_{SS}$ 。在这种情况下， $V_{DD}$ 必须高于2.25 V，以使1.8 V稳压器能够正常工作。

- 有关详细信息，请参见第 4.1.3 节和相关的器件数据手册的“嵌入式稳压器特性”部分。

- $V_{DDA1V8\_DSI}$ 是模拟DSI电源。电压范围为1.65 V到1.98 V（1.8 V典型值）应连接到 $V_{DDA1V8\_REG}$ 并且必须连接到外部去耦电容（参见表 4）。

- $V_{DDA1V1\_REG}$ 引脚是内部稳压器的输出引脚，必须将其连接到外部去耦电容（参见表 4）。电压范围为1.045 V到1.155 V（1.1 V典型值）

- $V_{DDA1V1\_REG}$ 从内部连接到USB PHY。

- 默认情况下使能内部 $V_{DDA1V1\_REG}$  稳压器，可通过软件进行控制。它在待机期间始终关闭。

**注意：**除非 $V_{DDA1V8\_REG}$ 存在，否则 $V_{DD3V3\_USBHS}$ 不得存在，不然会使STM32MP15x系列产品永久损坏。必须通过PMIC或在分立元件电源应用中通过外部元件来确保电源次序。

**注意：**所有电源接地 ( $V_{SS}$ 、 $V_{SS\_ANA}$ 、 $V_{SS\_PLL}$ 、 $V_{SS\_USBHS}$ 、 $V_{SS\_DSI}$ 、 $V_{SSA}$ 和 $V_{REF-}$ ) 均应与电源层连接在一起。

表4. 封装的推荐去耦电容数量<sup>(1)</sup>

| 电源引脚                                                    | 去耦点 <sup>(2)</sup>                         | 值                            | LFBGA354 | TFBGA257           | TFBGA361           | LFBGA448 | 注释                                                                |

|---------------------------------------------------------|--------------------------------------------|------------------------------|----------|--------------------|--------------------|----------|-------------------------------------------------------------------|

| V <sub>BAT</sub>                                        | V <sub>SS</sub>                            | 100 nF                       | 1        | 1                  | 1                  | 1        | 如果V <sub>BAT</sub> 连接至V <sub>DD</sub> 或使用超级电容器替代电池，则可以忽略          |

| V <sub>DDCORE</sub>                                     | V <sub>SS</sub>                            | 1 μF <sup>(3)</sup>          | 15       | 15                 | 15                 | 15       | 不包括PMIC/SMPS上的电容                                                  |

| V <sub>DDQ_DDR</sub>                                    | V <sub>SS</sub>                            | 1 nF                         | 2        | 2                  | 2                  | 2        | 不包括PMIC/SMPS上的电容和DDR内存上的附加电容                                      |

|                                                         |                                            | 3.3 nF                       | 0        | 3                  | 0                  | 0        |                                                                   |

|                                                         |                                            | 1 μF <sup>(3)</sup>          | 4        | 2                  | 7                  | 7        |                                                                   |

| V <sub>DD_ANA</sub>                                     | V <sub>SS_ANA</sub>                        | 1 μF <sup>(3)</sup>          | 1        | - <sup>(4)</sup>   | 1                  | 1        | -                                                                 |

| V <sub>DD_PLL</sub> , V <sub>DD_PLL2</sub>              | V <sub>SS_PLL</sub> , V <sub>SS_PLL2</sub> | 1 μF <sup>(3)</sup>          | 2        | - <sup>(4)</sup>   | - <sup>(4)</sup>   | 2        | 不包括PMIC/SMPS上的电容。                                                 |

| V <sub>DD</sub> , V <sub>DD_DSI</sub>                   | V <sub>SS</sub>                            | 1 μF <sup>(3)</sup>          | 4        | 4                  | 4                  | 4        |                                                                   |

| V <sub>DD1V2_DSI_REG</sub> , V <sub>DD1V2_DSI_PHY</sub> | V <sub>SS_DSI</sub>                        | 2.2 μF <sup>(3)</sup>        | 1        | -                  | 1                  | 1        | -                                                                 |

|                                                         | V <sub>SS</sub>                            |                              | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                   |

| V <sub>DDA1V8_REG</sub>                                 | V <sub>SS_USBHS</sub>                      | 2.2 μF <sup>(3)</sup>        | 1        | -                  | 1                  | 1        | -                                                                 |

|                                                         | V <sub>SS</sub>                            |                              | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                   |

| V <sub>DDA1V8_DSI</sub>                                 | V <sub>SS_DSI</sub>                        | 1 μF <sup>(3)</sup>          | 1        | -                  | 1                  | 1        | V <sub>DDA1V8_DSI</sub> 必须连接到V <sub>DDA1V8_REG</sub>              |

|                                                         | V <sub>SS</sub>                            |                              | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                   |

| V <sub>DDA1V1_REG</sub>                                 | V <sub>SS_USBHS</sub>                      | 2.2 μF <sup>(3)</sup>        | 1        | -                  | 1                  | 1        | -                                                                 |

|                                                         | V <sub>SS</sub>                            |                              | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                   |

| V <sub>DD3V3_USBHS</sub> , V <sub>DD3V3_USBFS</sub>     | V <sub>SS_USBHS</sub>                      | 1 μF <sup>(3)</sup>          | 1        | -                  | 1                  | 1        | -                                                                 |

| V <sub>DD3V3_USB</sub>                                  | V <sub>SS</sub>                            |                              | -        | 1 <sup>(5)</sup>   | -                  | -        |                                                                   |

| V <sub>DDA</sub>                                        | V <sub>SSA</sub>                           | 100 nF + 1 μF <sup>(3)</sup> | 1+1      | 1+1                | 1+1                | 1+1      | V <sub>SSA</sub> 必须连接到V <sub>SS</sub> 层                           |

| V <sub>REF+</sub>                                       | V <sub>REF-</sub> 和V <sub>SSA</sub>        | 100 nF + 1 μF <sup>(3)</sup> | 1+1      | -                  | -                  | 1+1      | V <sub>REF-</sub> 必须先连接到V <sub>SSA</sub> ，然后连接到V <sub>SS</sub> 平面 |

|                                                         | V <sub>SSA</sub>                           |                              | -        | 1+1 <sup>(6)</sup> | 1+1 <sup>(6)</sup> | -        | V <sub>SSA</sub> 必须连接到V <sub>SS</sub> 层                           |

- 此表可作为指导原则，电容器的实际数量和值可根据不同的参数进行调整：电容器的尺寸、电容器的介电质、PCB工艺、以及使用产品电源完整性仿真的结果。

- 所有V<sub>SS\_x</sub>和V<sub>SSA</sub>均必须连接到公共V<sub>SS</sub>层。

- 多层陶瓷电容型（MLCC）。

- 电源在内部与V<sub>DD</sub>合并。

- 供电回路在内部与V<sub>SS</sub>合并。

- V<sub>REF-</sub>在内部与V<sub>SSA</sub>合并。

## 4.3 复位和电源监控

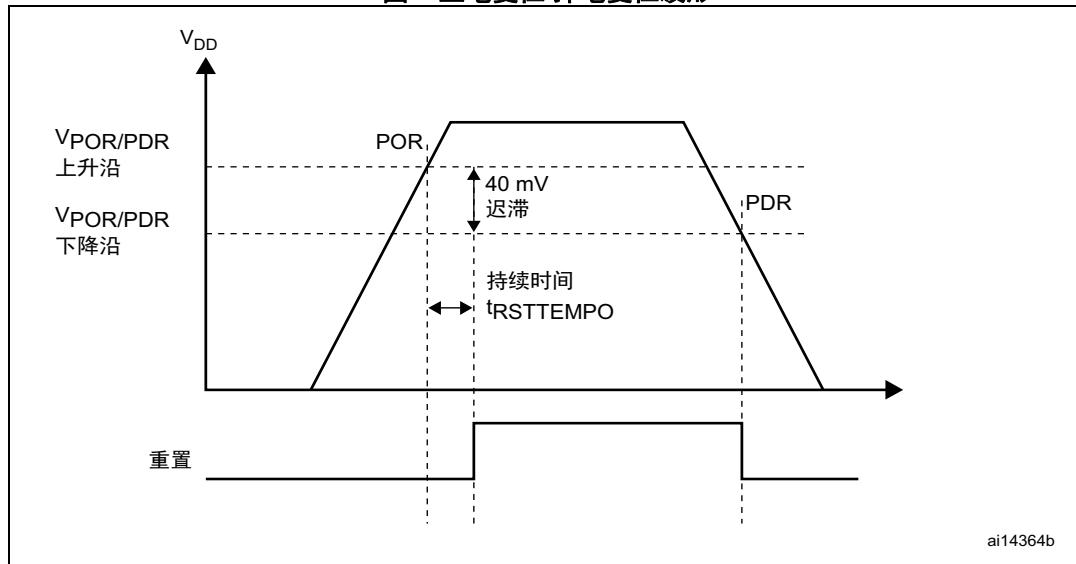

### 4.3.1 上电复位(POR)/掉电复位(PDR)

本器件内部集成有POR/PDR电路，可以从1.71 V开始正常工作。

当 $V_{DD}$ 低于指定阈值 $V_{POR/PDR}$ 时，器件无需外部复位电路便会保持复位状态。有关上电/掉电复位阈值的相关详细信息，请参见产品数据手册的电气特性部分。

图2. 上电复位/掉电复位波形

- $t_{RSTTEMPO}$ 大约为2.6ms。 $V_{POR/PDR}$ 的上升沿为1.67V（典型值）， $V_{POR/PDR}$ 下降沿为1.63V（典型值）。有关实际值，请参见STM32MP15x数据手册。

通过PDR\_ON引脚可禁用内部上电复位（POR）/掉电复位（PDR）电路。在这种情况下，外部供电监控器应监控 $V_{DD}$ ，应一直将器件保持在复位模式，直到 $V_{DD}$ 高于指定门限。

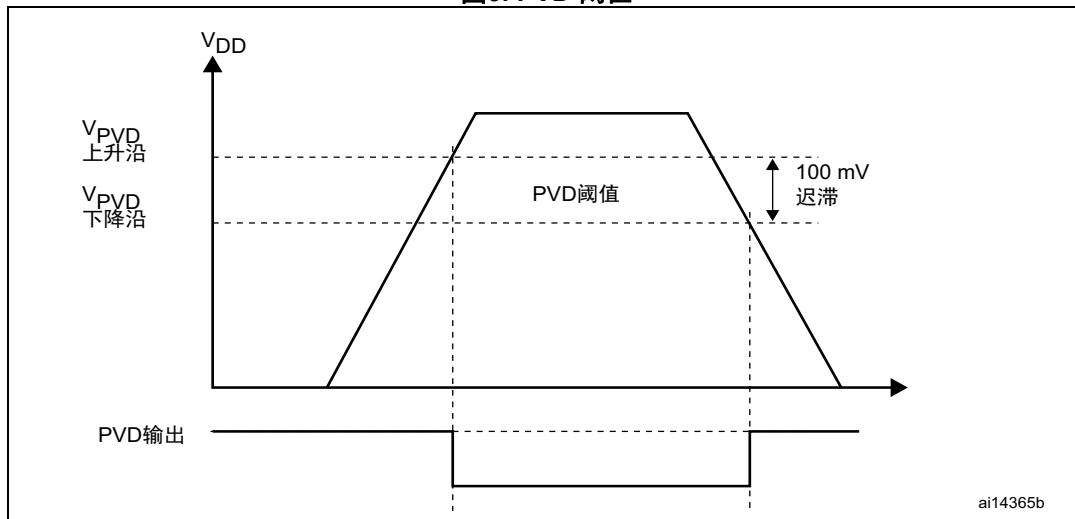

### 4.3.2 可编程电压检测器 (PVD)

用户可以使用PVD监视 $V_{DD}$ 电源，将其与电源控制寄存器（PWR\_CR）中PLS[2:0]位所选的阈值进行比较。

通过PVDE位置位来使能PVD。

电源控制/状态寄存器（PWR\_CR）中提供了PVDO标志，用于指示 $V_{DD}$ 是大于还是小于PVD阈值。该事件内部连接到EXTI线16，如果通过EXTI寄存器使能，则可以产生中断。当 $V_{DD}$ 降至PVD阈值以下以及/或者当 $V_{DD}$ 升至PVD阈值以上时，可以产生PVD输出中断，具体取决于EXTI线16上升沿/下降沿的配置。该功能的用处之一就是在中断服务程序中执行紧急关闭系统的任务。

图3. PVD 阈值

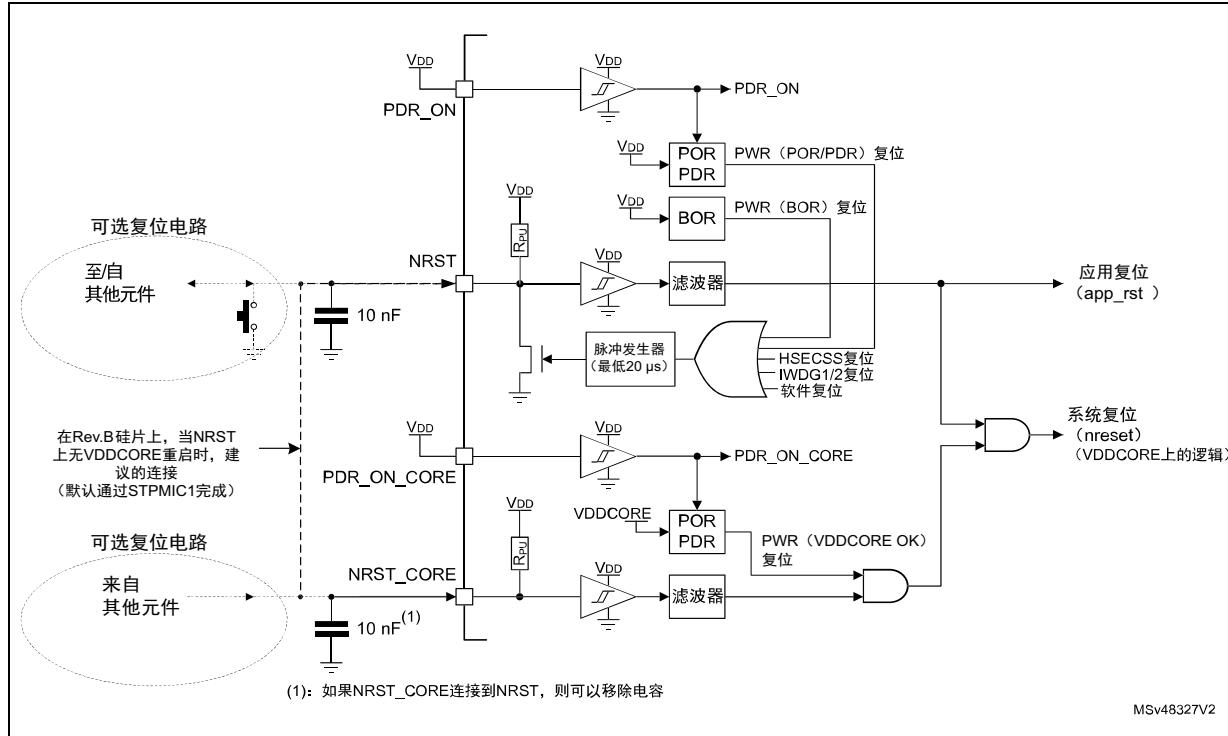

#### 4.3.3 应用和系统复位

通过以下源之一产生应用复位 (app\_rst) :

- 通过NRST管脚复位,

- 通过por\_rst信号复位（通常被称为上电复位）,

- 通过bor\_rst信号复位（通常被称为欠压复位）,

- 通过独立看门狗1复位(iwdg1\_RST),

- 通过独立看门狗2复位(iwdg2\_RST),

- 借助AIRCR寄存器（MCYSRST）由Cortex-M4 (MCU)进行软件复位

如果选项字节OPT MCU\_SYSRST\_EN允许软件复位,

- 当Cortex-A7 (MPU)将RCC中的MPSYSRST位设为“1”时，由RCC进行软件复位,

- HSE故障，时钟安全系统功能被激活（hcscs\_RST）。

通过以下源之一产生系统复位 (nreset) :

- 通过app\_rst信号复位（应用复位）,

- 通过vcore\_rst信号复位。

**注:** 当系统处于待机状态时， $V_{DDCORE}$ 关闭，但 $V_{DD}$ 仍存在。因此，当系统退出待机模式时， $vcore\_rst$ 信号被激活，从而产生nreset复位。

**注:** 在Rev.B (DBGMCU\_IDC.REV\_ID=0x2000)硅片上，当NRST上无 $V_{DDCORE}$ 重启

(默认情况下通过STPMIC1来完成) 时，建议将NRST连接到NRST\_CORE。有关详细信息，请参见产品勘误表。

有关复位覆盖范围的详细信息，请参见参考手册中的RCC部分。

图4. 复位引脚电路简图

## 5 封装

### 5.1 封装选择

封装选择必须考虑一些主要取决于应用的限制。

下面汇总了常见的一些限制：

- 需要的接口数量。

某些接口在有的封装上可能没有。

某些接口组合在有的封装上可能没有。

有关详细信息，请参见产品数据手册

- PCB技术限制。

窄间距和高焊球密度可能要求更多的PCB层数和更高级的PCB，这需要使用微通孔（激光通孔）技术进行层叠

- 封装高度

- 可用的PCB面积

- 散热限制（较大的封装具有更好的散热能力）

表5. 封装总览

| 大小(mm) <sup>(1)</sup> | 16 x 16  | 10 x 10  | 12 x 12  | 18 x 18  |

|-----------------------|----------|----------|----------|----------|

| 最小间距 (mm)             | 0.8      | 0.5      | 0.5      | 0.8      |

| 高度(mm)                | 1.4      | 1.2      | 1.2      | 1.4      |

| 销售序号                  | LFBGA354 | TFBGA257 | TFBGA361 | LFBGA448 |

| STM32MP151xxx         | X        | X        | X        | X        |

| STM32MP153xxx         | X        | X        | X        | X        |

| STM32MP157xxx         | X        | X        | X        | X        |

1. 典型主体尺寸。

表6. 与封装有关的主要功能变化

| 封装            |                | TFBGA257                                        | LFBGA354                          | TFBGA361        | LFBGA448          |

|---------------|----------------|-------------------------------------------------|-----------------------------------|-----------------|-------------------|

| 封装            | 主体尺寸 (mm)      | 10x10                                           | 16x16                             | 12x12           | 18x18             |

|               | 脚间距(mm)        | 0.5<br>(中心0.65)                                 | 0.8                               | 0.5<br>(中心0.65) | 0.8               |

|               | 厚度 (mm)        | <1.2                                            | <1.4                              | <1.2            | <1.4              |

|               | 焊球数            | 257                                             | 354                               | 361             | 448               |

| SDRAM         | LPDDR2/3       | 16位533 MHz                                      | 可达1GByte,<br>单存储区                 | -               | 可达1GByte,<br>单存储区 |

|               |                | 32位533 MHz                                      | -                                 | 可达1GB, 单存<br>储区 | -                 |

|               | DDR3/3L        | 16位533 MHz                                      | 可达1GB, 单存储区                       |                 |                   |

|               |                | 32位533 MHz                                      | -                                 | 高达1GB, 单存储区     |                   |

| FMC           | 并行地址/数据8/16位   | -                                               | 4 × CS, 高达4 × 64 MB               |                 |                   |

|               | 并行AD-Mux 8/16位 | 4 × CS, 高达4 × 64 MB                             |                                   |                 |                   |

|               | NAND 8/16 位    | 有, 2 × CS, SLC, BCH4/8                          |                                   |                 |                   |

| 千兆以太网         |                | -                                               | 支持PTP和EEE的MII、RMII、<br>GMII、RGMII |                 |                   |

| 10/100M以太网    |                | 支持PTP和EEE的MII、RMII                              |                                   |                 |                   |

| 带中断的GPIO (总数) |                | 98                                              | 148                               | 176             |                   |

| -             | 安全GPIO         | -                                               | 8                                 |                 |                   |

|               | 唤醒引脚           | 4                                               | 6                                 |                 |                   |

|               | 防篡改引脚 (主动防篡改)  | 2 (1)                                           | 3 (1)                             |                 |                   |

| 高达16位同步ADC    |                | 2 (在16/14/12/10/8位上分别高达0.25/4.4/5/5.7/6.7 Msps) |                                   |                 |                   |

| -             | 低噪音16位 (差分)    | -                                               | 2 (1)                             |                 |                   |

|               | 16位 (差分)       | 6 (1)                                           | 7 (1)                             |                 |                   |

|               | 14位 (差分)       | 11 (3)                                          | 13 (3)                            |                 |                   |

|               | ADC通道总数        | 17                                              | 22                                |                 |                   |

5.2 引脚复用映射

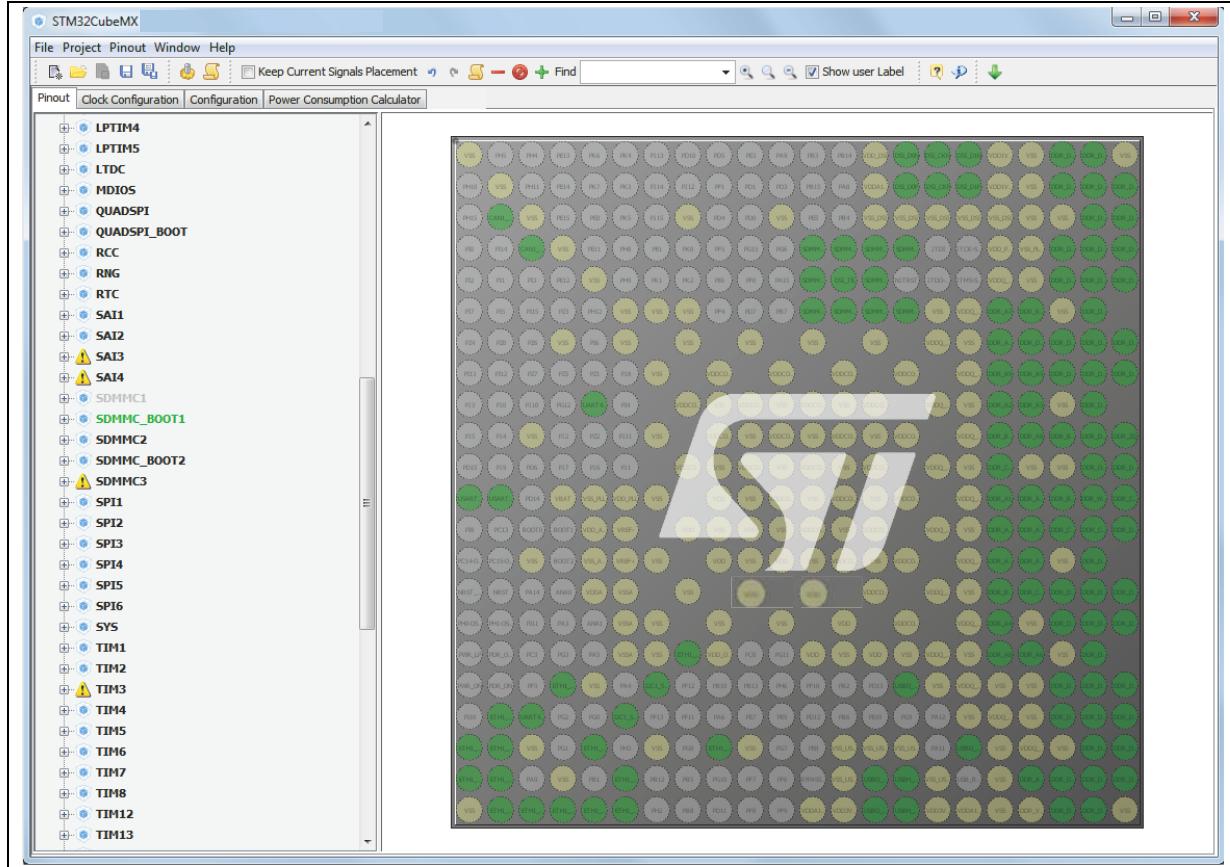

为了更容易地探索外设复用映射，建议使用STM32CubeMX工具，该工具可以在[www.st.com](http://www.st.com)上获得。

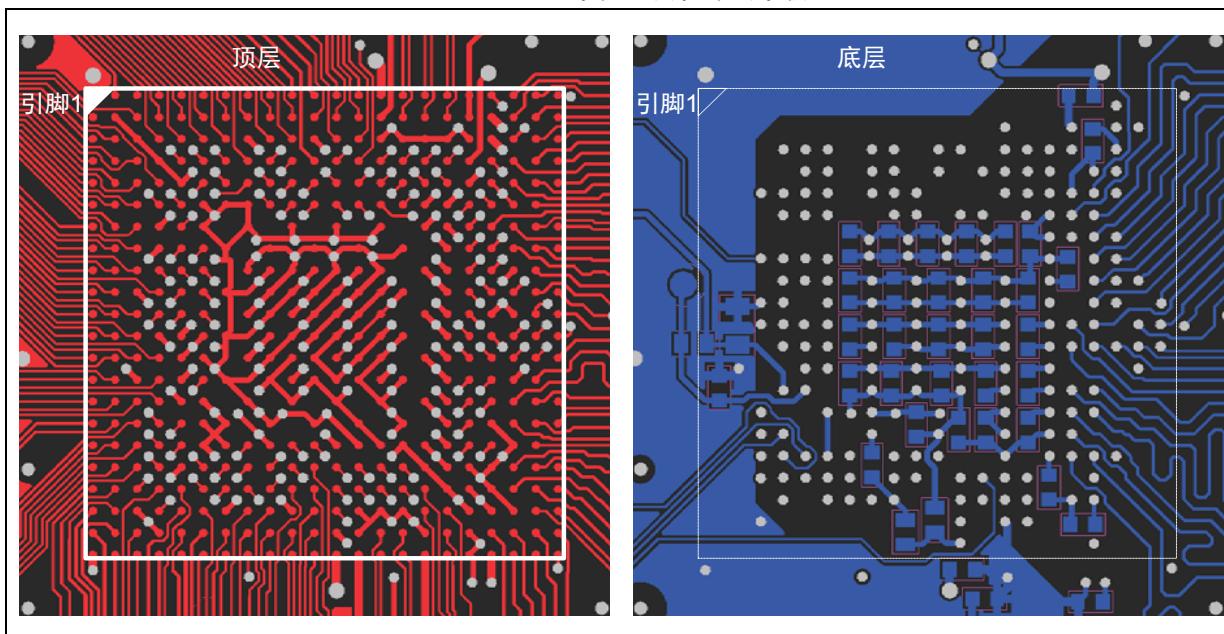

图5. STM32CubeMX示例截图

### 5.3 各版本之间的封装兼容性

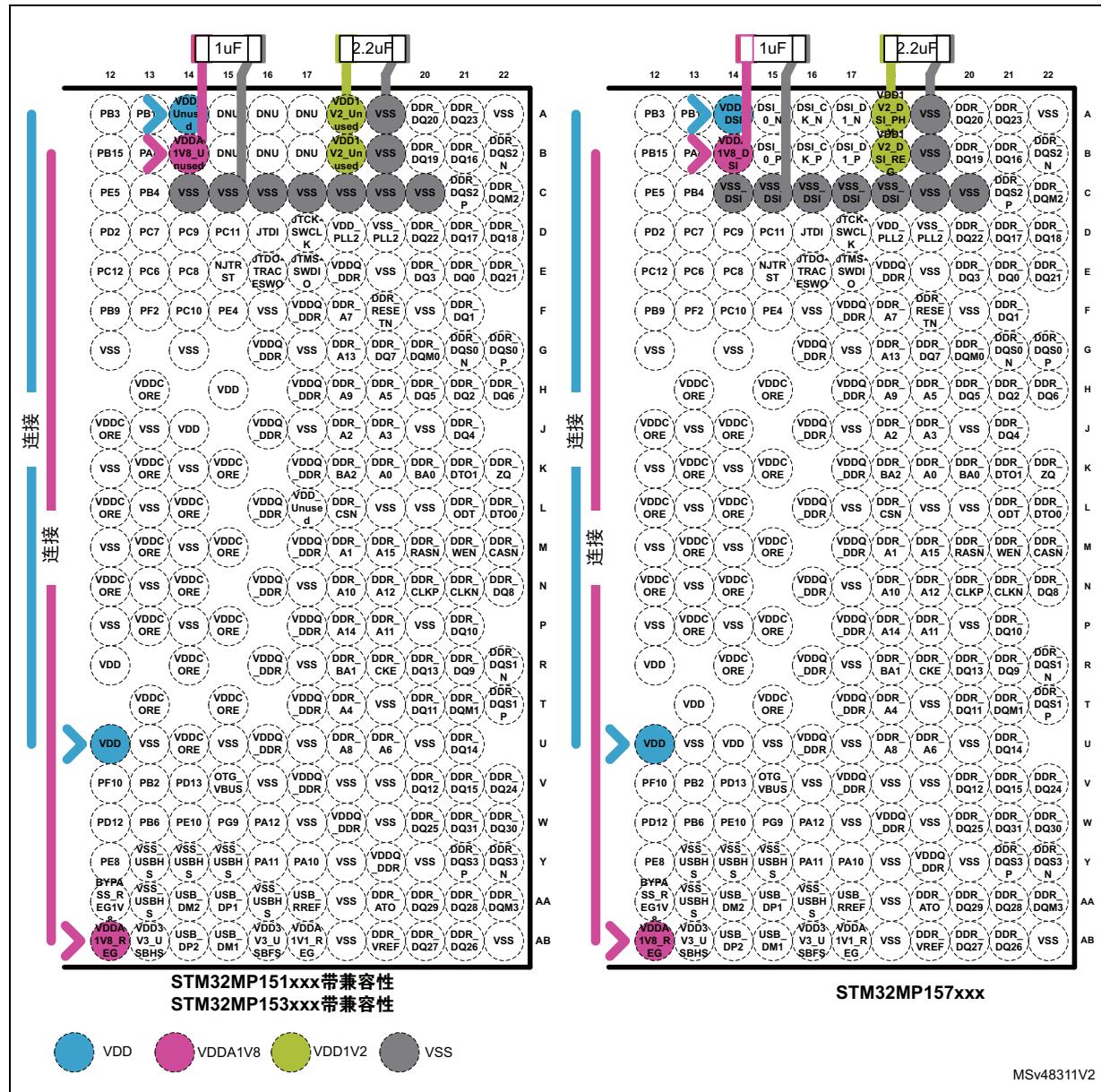

STM32MP151xxx、STM32MP153xxx器件与STM32MP157xxx器件略有不同。但是，只需少量的额外连接，便可以构建兼容的PCB。

表7. 器件兼容性汇总

| 专用PCB         | 使用的器件         |               |                               |

|---------------|---------------|---------------|-------------------------------|

|               | STM32MP151xxx | STM32MP153xxx | STM32MP157xxx                 |

| STM32MP151xxx | 兼容            | 兼容            | 兼容可能性<br>(参见表8到表11<br>和图6到图9) |

| STM32MP153xxx | 兼容            | 兼容            |                               |

| STM32MP157xxx | 兼容            | 兼容            | 兼容                            |

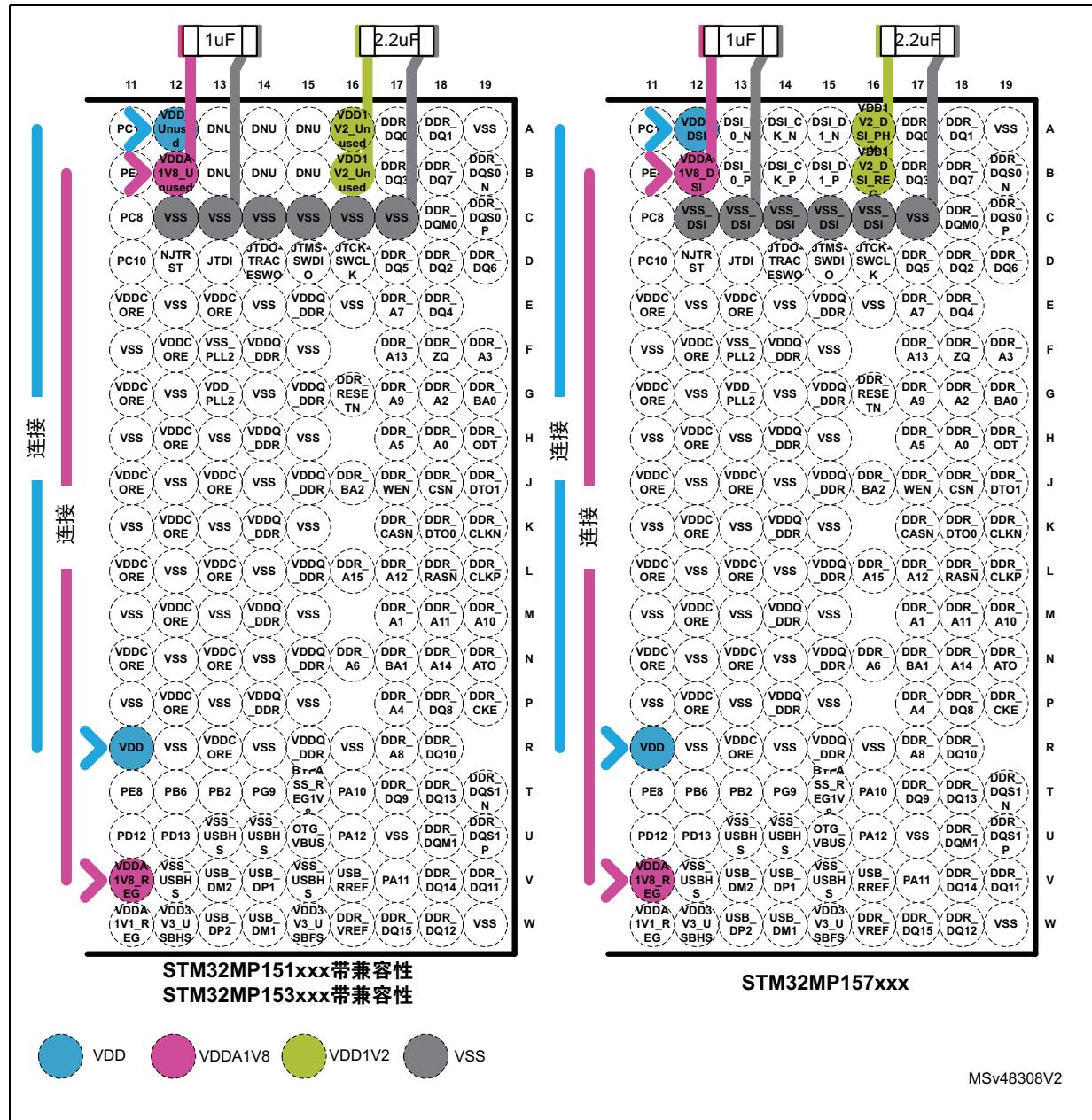

表8. 用于16x16 LFBGA354的STM32MP151xxx和STM32MP153xxx的兼容性

| 要添加的焊球连接             | STM32MP151xxx  | STM32MP153xxx               | STM32MP157xxx |

|----------------------|----------------|-----------------------------|---------------|

| B12至V11 (VDD1V8_REG) | VDDA1V8_Unused | VDDA1V8_DSI                 |               |

| A16至B16 + 1 μF至VSS   | VDD1V2_Unused  | VDD1V2_PHY / VDD1V2_DSI_REG |               |

| A12至VDD              | VDD_Unused     | VDD_DSI                     |               |

图6. 16x16 LFBGA354兼容性

注：该图只是为了帮助理解，并未显示实际的板走线和元件尺寸/布置。

表9. 用于10x10 TFBGA257的STM32MP151xxx和STM32MP153xxx的兼容性

| 要添加的焊球连接             | STM32MP151xxx  | STM32MP153xxx                   | STM32MP157xxx |

|----------------------|----------------|---------------------------------|---------------|

| 1B6至1H5 (VDD1V8_REG) | VDDA1V8_Unused | VDDA1V8_DSI                     |               |

| 1B7至1A7 + 1 μF至VSS   | VDD1V2_Unused  | VDD1V2_DS1_PHY / VDD1V2_DS1_REG |               |

| C13至VDD              | VDD_Unused     | VDD_DSI                         |               |

图7. 10x10 TFBGA257兼容性

注:

该图只是为了帮助理解，并未显示实际的板走线和元件尺寸/布置。

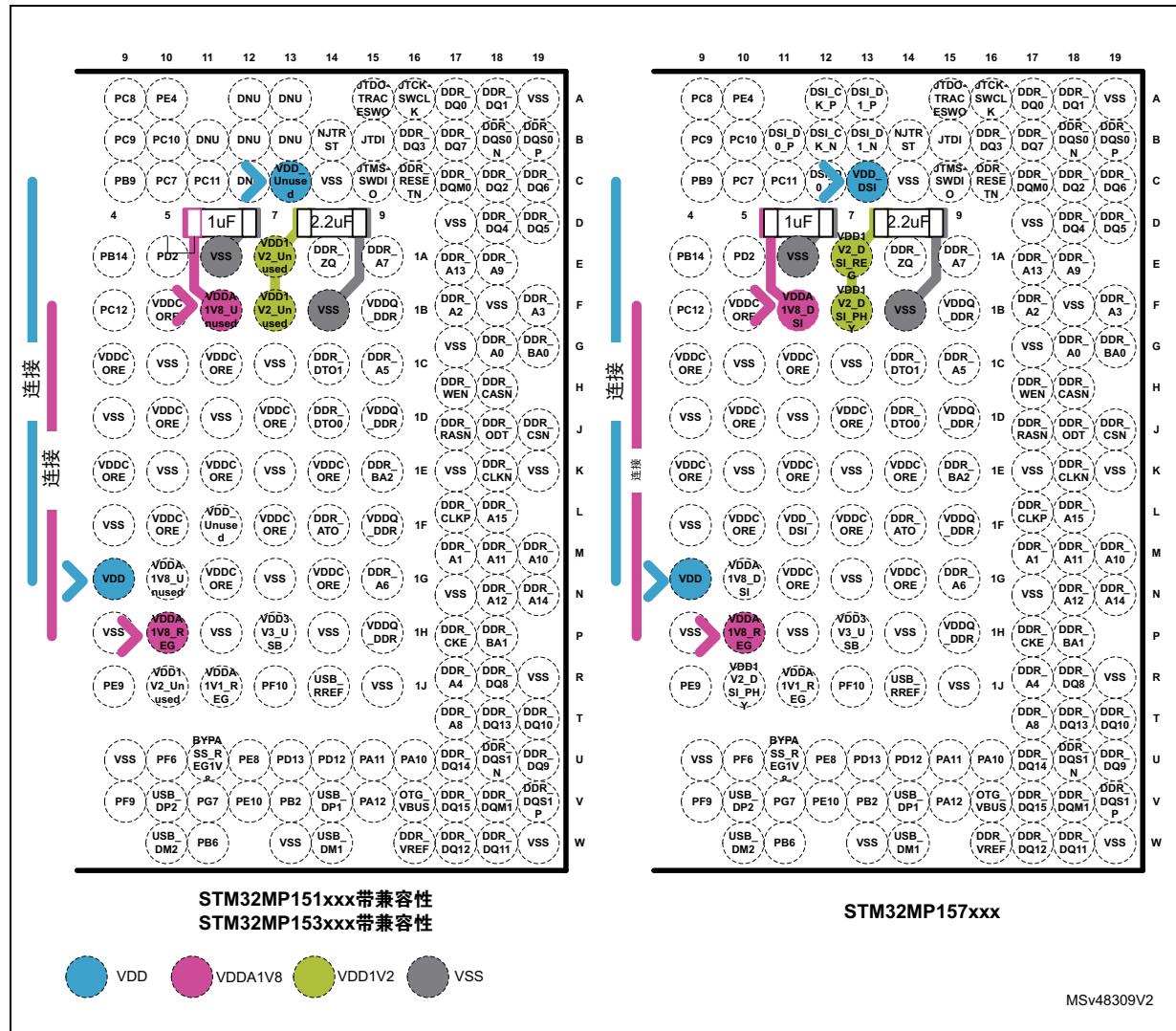

表10. 用于12x12 TFBGA361的STM32MP151xxx和STM32MP153xxx的兼容性

| 要添加的焊球连接              | STM32MP151xxx  | STM32MP153xxx | STM32MP157xxx                   |

|-----------------------|----------------|---------------|---------------------------------|

| C14至AB14 (VDD1V8_REG) | VDDA1V8_Unused |               | VDDA1V8_DSI                     |

| C17至C18 + 1 μF至VSS    | VDD1V2_Unused  |               | VDD1V2_DS1_PHY / VDD1V2_DS1_REG |

| B18至VDD               | VDD_Unused     |               | VDD_DSI                         |

图8. 12x12 TFBGA361兼容性

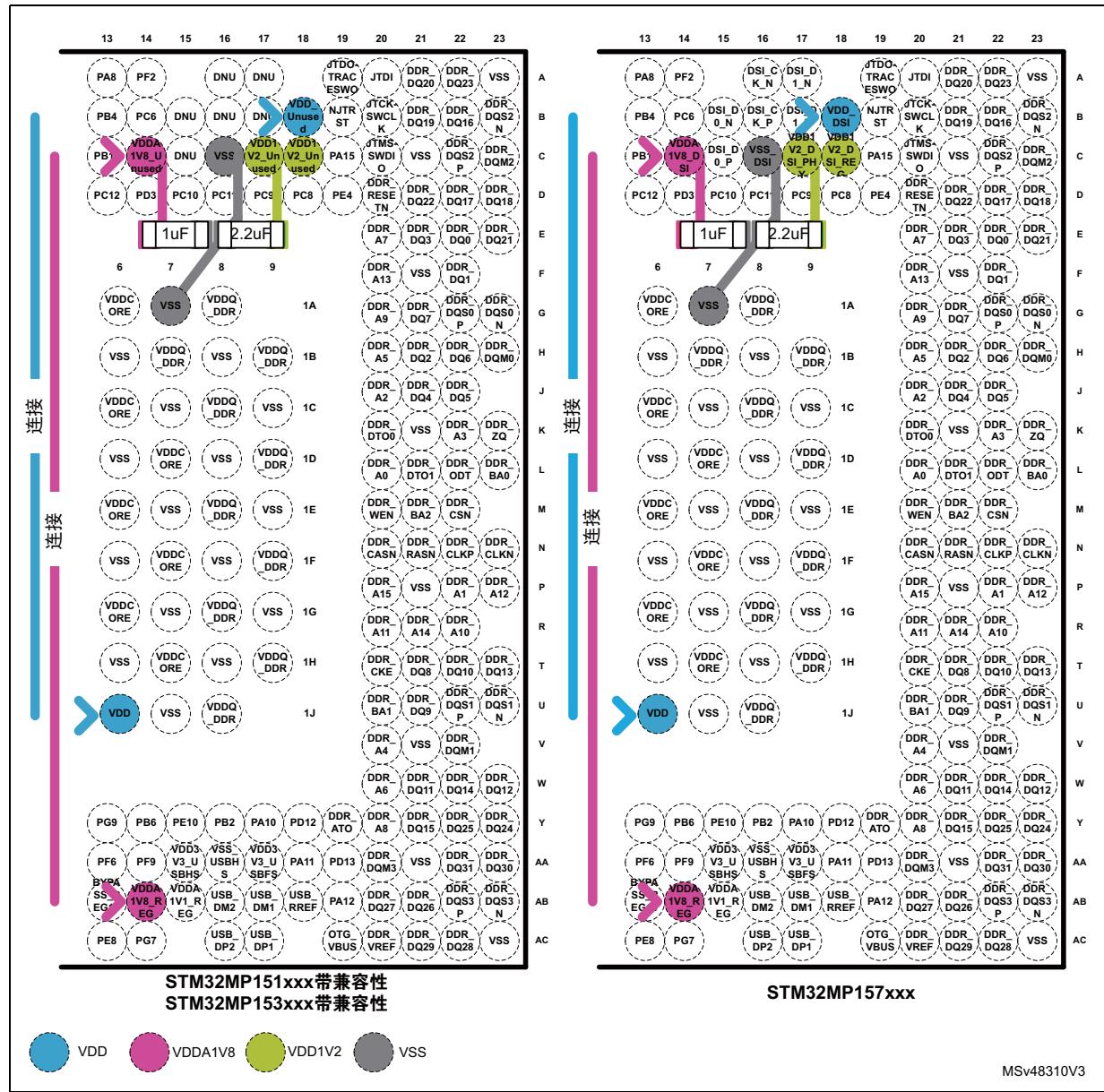

**表11. 用于18x18 LFBGA448的STM32MP151xxx和STM32MP153xxx的兼容性**

| 要添加的焊球连接                | STM32MP151xxx  | STM32MP153xxx                      | STM32MP157xxx |

|-------------------------|----------------|------------------------------------|---------------|

| B14至AB12 (VDD1V8_REG)   | VDDA1V8_Unused | VDDA1V8_DSI                        |               |

| A18至B18 + 1 $\mu$ F至VSS | VDD1V2_Unused  | VDD1V2_DSI_PHY /<br>VDD1V2_DSI_REG |               |

| A14至VDD                 | VDD_Unused     | VDD_DSI                            |               |

图9. 18x18 LFBGA448兼容性

注：该图只是为了帮助理解，并未显示实际的板走线和元件尺寸/布置。

## 6 时钟

可以使用不同的时钟源驱动子系统时钟：

- HSI振荡器时钟（高速内部时钟信号）

- CSI振荡器时钟（低功耗内部时钟信号）

- HSE振荡器时钟（高速外部时钟信号）

- PLL1/2/3/4时钟

- PLL\_DSI用于产生DSI时钟（高达1 GHz）<sup>(a)</sup>

- PLL\_USB用于产生USB时钟（高达480 MHz）

器件具有两个次级时钟源：

- 32 kHz低速内部RC（LSIRC），该RC用于驱动独立看门狗，也可选择提供给RTC用于停机/待机模式下的自动唤醒。

- 32.768 kHz低速外部晶振（LSE晶振），用于驱动实时时钟(RTCCLK)

每个时钟源都可以单独打开或者在未使用时关闭，以降低功耗。

若需时钟树的说明，请参考RM0436、RM0441、RM0442参考手册。

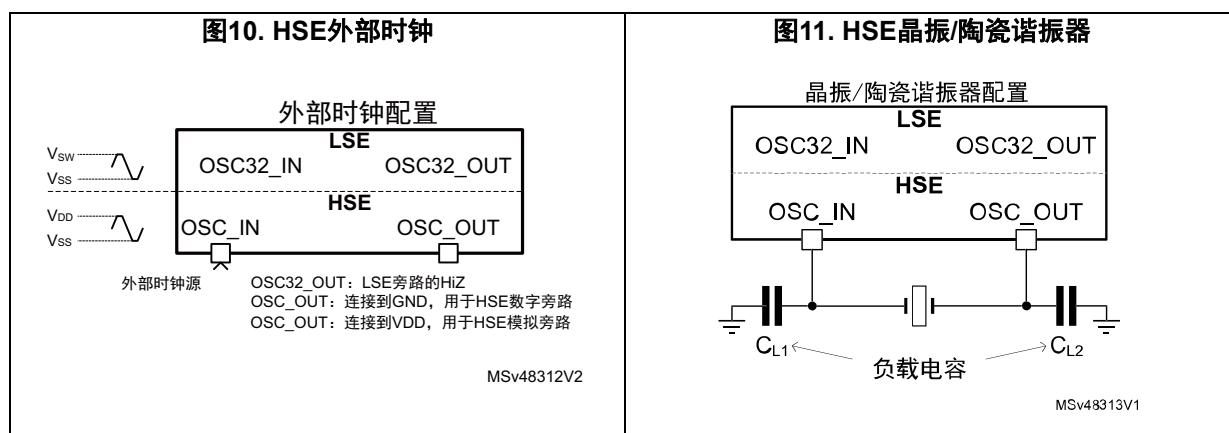

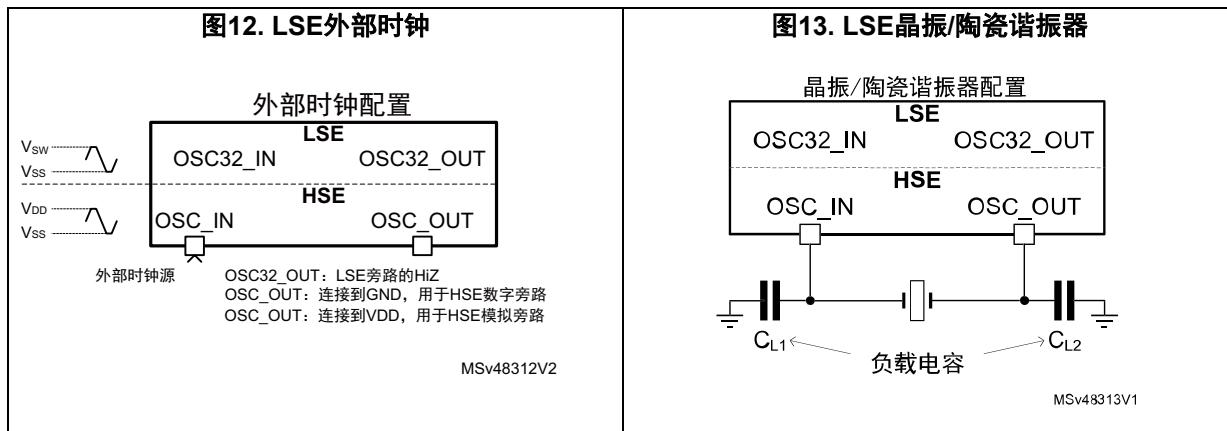

### 6.1 HSE OSC时钟

高速外部时钟信号(HSE)有2个时钟源：

- HSE用户外部时钟（参见图 10）

- HSE外部晶振/陶瓷谐振（参见图 11）

1. 参见ST微控制器振荡器设计指南应用说明（AN2867）。

2. 负载电容 $C_L$ 的公式如下： $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$ ，其中 $C_{stray}$ 为引脚电容以及与电路板或PCB走线相关的电容。典型情况下，它在2 pF和4 pF之间。参考第9节：建议第42页以使其值最小。

a. 可用性取决于STM32MP15x系列产品器件。

### 6.1.1 外部源 (HSE 旁路)

在此模式下，必须提供外部时钟源。它的频率可以是从8到50 MHz（参考STM32MP15x数据手册获取实际最大值）。

必须通过占空比约为50%的外部数字 ( $V_{IL}/V_{IH}$ ) 或模拟（最小幅度为200 mV峰-峰值）时钟信号来驱动OSC\_IN引脚。

**注：**为了允许USB启动，BootROM通过在启动阶段（即在NRST上升沿）检查OSC\_OUT连接自动选择HSE模式：

- OSC\_OUT连接到GND（最大1千欧）：HSE数字旁路

- OSC\_OUT连接到VDD（最大1千欧）：HSE模拟旁路

- OSC\_OUT高阻抗或连接到晶振/陶瓷谐振器：HSE晶振/陶瓷谐振器模式。

使用旁路时，可通过PWR\_ON使能外部时钟发生器，以节省功耗（即待机时禁用）。在这种情况下，OSC\_IN时钟输入应在PWR\_ON上升沿产生后的10 ms内保持稳定。

### 6.1.2 外部晶振/陶瓷谐振器 (HSE晶振)

外部振荡器频率范围为8至48 MHz。

外部振荡器的优点是主时钟精度非常高。相关的硬件配置如图 11所示。使用一个24 MHz的晶振频率对于得到精确的USB高速时钟是一个好的选择。

晶振/陶瓷谐振器和负载电容必须尽可能地靠近振荡器的引脚，以尽量减小输出失真和起振稳定时间。负载电容值必须根据所选晶振/陶瓷谐振器的不同做适当调整。

对于 $C_{L1}$ 和 $C_{L2}$ ，建议使用可满足晶振/陶瓷谐振器的要求且大小介于5 pF到25 pF（典型值）之间的NP0/C0G电容。 $C_{L1}$ 和 $C_{L2}$ 的大小通常相同。晶振制造商指定的负载电容通常是 $C_{L1}$ 和 $C_{L2}$ 的串联组合。确定 $C_{L1}$ 和 $C_{L2}$ 的规格时，必须将PCB和引脚的电容考虑在内（引脚与电路板的电容可粗略地估算为10 pF）。

更多信息请参考ST微控制器振荡器设计指南应用说明（AN2867）和产品数据手册中的电气特性部分。

## 6.2 LSE OSC时钟

低速外部时钟信号(LSE)有2个时钟源：

- LSE用户外部时钟（参见图 12）

- LSE外部晶振/陶瓷谐振（参见图 13）

1. “LSE晶振/陶瓷谐振器”图片：

强烈建议使用负载电容  $C_L \leq 12.5 \text{ pF}$  的谐振器。

2. “LSE外部时钟”和“LSE晶振/陶瓷谐振器”图片：

OSC32\_IN和OSC32\_OUT引脚也可用作GPIO，但建议在同一应用中不要既用作RTC又用作GPIO引脚。

### 6.2.1 外部源 (LSE 旁路)

在此模式下，必须提供外部时钟源。最高频率不超过 1 MHz。必须通过占空比约为50%的外部数字 (VIL/VIH) 或模拟 (最小幅度为200 mV峰-峰值) 时钟信号来驱动OSC32\_IN引脚，同时OSC32\_OUT引脚必须保持为高阻抗 (请参见图 12)。旁路模式的配置以及数字和模拟之间的选择在RCC寄存器内完成。

### 6.2.2 外部晶振/陶瓷谐振器 (LSE 晶振)

LSE晶振是32.768 kHz低速外部晶振或陶瓷谐振器。可作为实时时钟外设 (RTC) 的时钟源来提供时钟/日历或其它定时功能，具有功耗低且精度高的优点。

谐振器和负载电容必须尽可能地靠近振荡器的引脚，以尽量减小输出失真和起振稳定时间。负载电容值  $C_{L1}$  和  $C_{L2}$  必须根据所选振荡器的不同做适当调整。

更多信息请参考 ST微控制器振荡器设计指南专用应用说明 (AN2867) 和产品数据手册的电气特性部分。

## 6.3 时钟安全系统 (CSS)

详细信息可以在产品参考手册中找到（参见[表 1：参考文档](#)）。

### 6.3.1 HSE 上的 CSS

时钟安全系统可通过软件激活。激活后，时钟监测器将在 HSE 振荡器启动延迟后使能，并在此振荡器停止时被关闭。

- 如果在HSE振荡器时钟上检测到故障，则可能产生系统复位，并向TAMP模块发出信号，以进行安全保护。

### 6.3.2 LSE 上的 CSS

时钟安全系统可通过软件激活。激活后，时钟监测器将在 LSE 振荡器启动延迟后使能，并在此振荡器停止时被关闭。

- 如果在LSE振荡器时钟上检测到故障，则RTC/TAMP时钟源将停止，并向TAMP模块发出信号，以进行安全保护。

## 7 自举配置

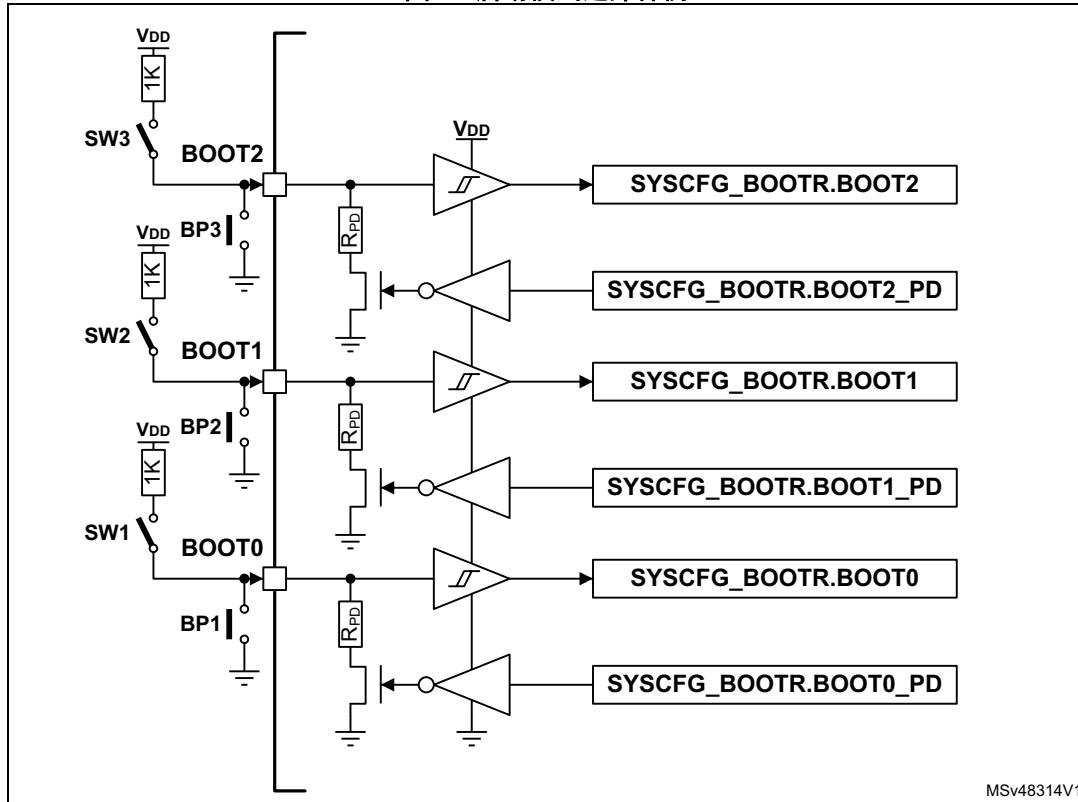

### 7.1 自举模式选择

在STM32MP15x系列产品器件中，可通过BOOT[2:0]引脚选择不同的自举模式。预留配置在表中以灰色突出显示。

表12. 自举模式

| BOOT2 | BOOT1 | BOOT0 | 初始自举模式                      | 注释                                                                                        |

|-------|-------|-------|-----------------------------|-------------------------------------------------------------------------------------------|

| 0     | 0     | 0     | UART和USB <sup>(1)</sup>     | 等待以下传入连接：<br>– 默认引脚上的USART2/3/6和USART4/5/7/8<br>– OTG_HS_DP/DM引脚上的USB高速设备 <sup>(2)</sup>  |

| 0     | 0     | 1     | 串行NOR-Flash <sup>(3)</sup>  | QUADSPI <sup>(5)</sup> 上的串行NOR-Flash                                                      |

| 0     | 1     | 0     | eMMC™ <sup>(3)</sup>        | SDMMC2（默认） <sup>(5)(6)</sup> 上的eMMC™                                                      |

| 0     | 1     | 1     | NAND-Flash <sup>(3)</sup>   | FMC上的SLC NAND-Flash                                                                       |

| 1     | 0     | 0     | 保留                          | 用于在不通过闪存启动的情况下进行调试访问 <sup>(4)</sup>                                                       |

| 1     | 0     | 1     | SD卡 <sup>(3)</sup>          | SDMMC1（默认）上的SD卡 <sup>(5)(6)</sup>                                                         |

| 1     | 1     | 0     | UART和USB <sup>(1)(3)</sup>  | 等待以下传入连接：<br>– 默认引脚上的USART2/3/6和USART4/5/7/8<br>– OTG_HS_DP/DM引脚 <sup>(2)</sup> 上的USB高速设备 |

| 1     | 1     | 1     | 串行NAND-Flash <sup>(3)</sup> | QUADSPI <sup>(5)</sup> 上的串行NAND-Flash                                                     |

1. 可通过OTP设置禁用。

2. 如果OTP未针对不同频率进行编程，则USB需要24 MHz HSE时钟/晶振（参见[第 7.3节：嵌入式自举模式](#)）。

3. 可通过OTP设置更改启动源（如SD卡上的初始启动，然后是通过OTP设置的eMMC）。

4. Cortex-A7 Core0在无限循环翻转PA13，Cortex-M4在RETRAM上无限循环。

5. 可通过OTP改变默认引脚。

6. 或者，可通过OTP选择该默认接口以外的另一个SDMMC接口。

复位后，BootROM会对BOOT引脚上的值进行采样。由用户决定在退出复位前设置BOOT[2:0]引脚，以选择所需的自举模式。

BOOT引脚也可以在稍后通过软件重新采样（例如，通过读取SYSCFG.BOOTR\_BOOT[2:0]字段）或在退出待机模式时通过BootROM重新采样。因此，这些引脚必须始终保持所需的自举模式配置。

在停止模式期间，当BOOT[2:0]引脚连接到V<sub>DD</sub>时，由于默认情况下启用了三个嵌入式下拉电阻，一些电流流经下拉电阻。

只需通过将SYSCFG\_BOOTR\_BOOT[2:0]\_PD字段的值设为等于在SYSCFG\_BOOTR\_BOOT[2:0]字段中读取的值，软件就可以禁用与V<sub>DD</sub>相连的引脚上的下拉电阻，这样可以节省数十微安的功率。由于每次退出待机后，SYSCFG\_BOOTR寄存器复位，所以必须再次执行该操作。请注意，在待机期间，BOOT[2:0]引脚被设为三态，即使连接到V<sub>DD</sub>，也无电流流入BOOT[2:0]引脚。

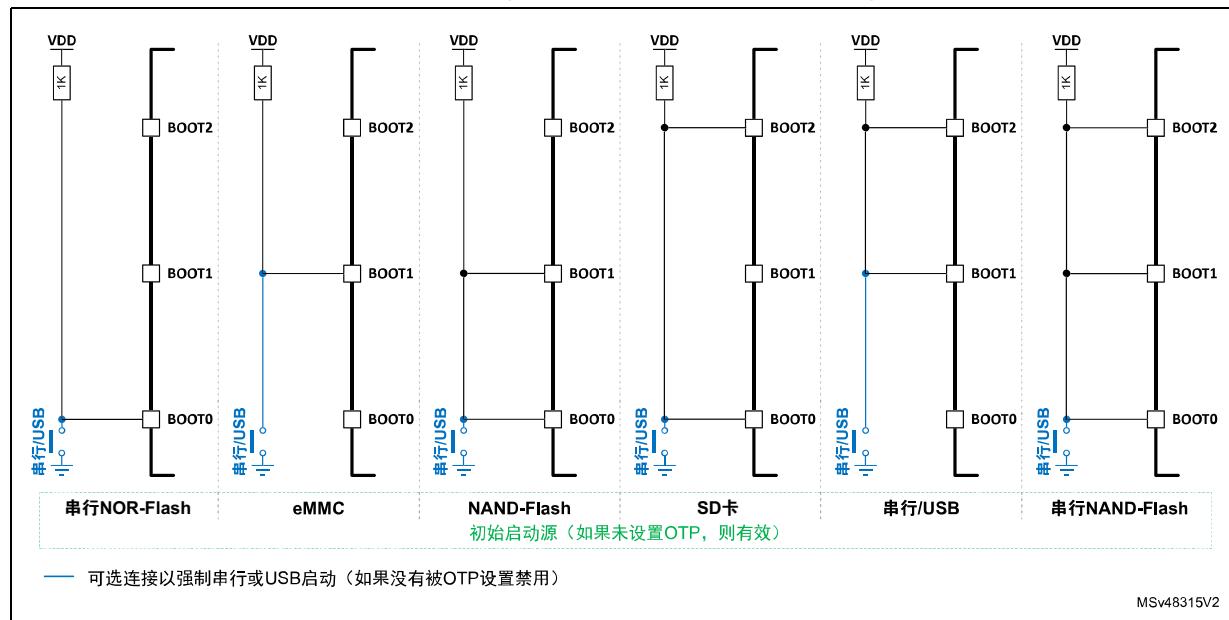

## 7.2 自举引脚连接

图 14 显示了选择 STM32MP15x 系列产品器件的自举存储器所需的外部连接示例。

图14. 启动模式选择样例

尽管具有各种软件恢复方案，但也存在闪存内容错误或损坏的风险（如用户错误、编入坏闪存内容、断电），系统可能无法启动（也被称为“变砖”）。

请注意，在空闪存上，启动代码会自动切换到UART/USB连接。

可能需要有一种强制使用UART/USB连接的方法，以对电路板闪存进行重新编程（如在售后服务、固件更新）。

在一些情况下，初始启动在与常规启动不同的闪存上完成（如通过SD卡进行初始启动，这种情况下在诸如串行NOR、串行NAND、eMMC或SLC NAND的另一个闪存中复制二进制数据）。由于初始启动代码可通过设置相关的OTP位来强制将来通过编程的闪存启动，因此可以实现这一功能（参见图 16）。这样就可以实现简单灵活的大规模量产，而无需干预启动引脚。

最终电路板的典型连接示例如图 15 中所述。

可通过多种方式实现“开关”：按钮、焊接桥、连接器触点、测试点等，但在正常产品启动期间默认为“开路”，以避免电流流入外部电阻器。

请注意，为满足产品安全要求，OTP配置可能会强制使用或禁用任何启动源。

图15. BOOT引脚典型接线原理图

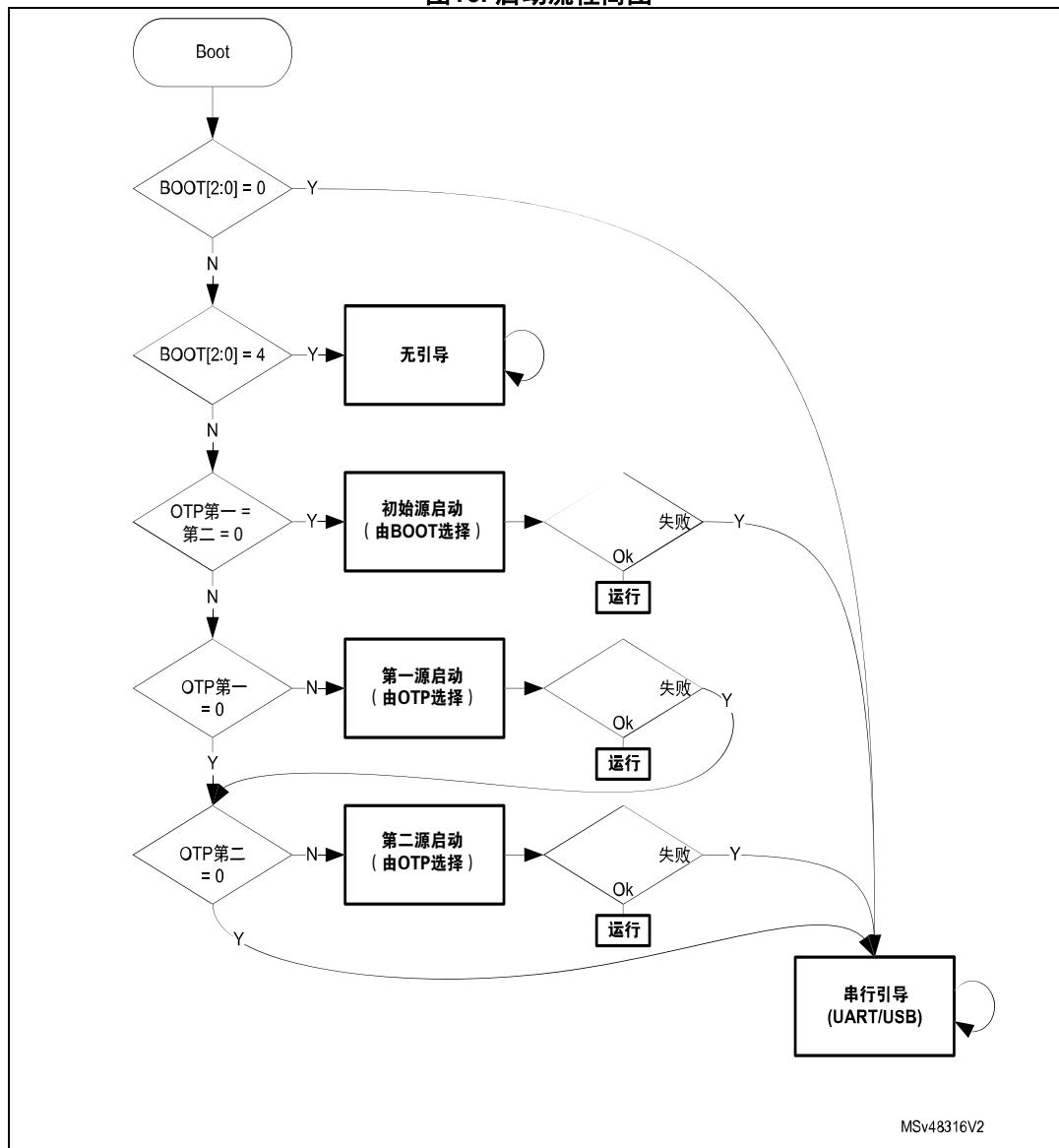

## 7.3 嵌入式自举模式

该嵌入式自举程序位于BootROM存储器中。

有关其他信息，请参见：STM32MP1系列自举程序中使用的USB DFU/USART协议（AN5275）（表1）。

在启动期间，QUADSPI、FMC、SDMMC和USART外设通过内部64 MHz振荡器（HSI）工作。但是，USB OTG HS器件只有在存在外部时钟（HSE）的情况下才能工作，默认时钟频率为24 MHz（或者，在OTP设置中使用8、10、12、14、16、20、24、25、26、28、32、36、40和48 MHz的频率和/或采用自动频率检测）。

图16. 启动流程简图

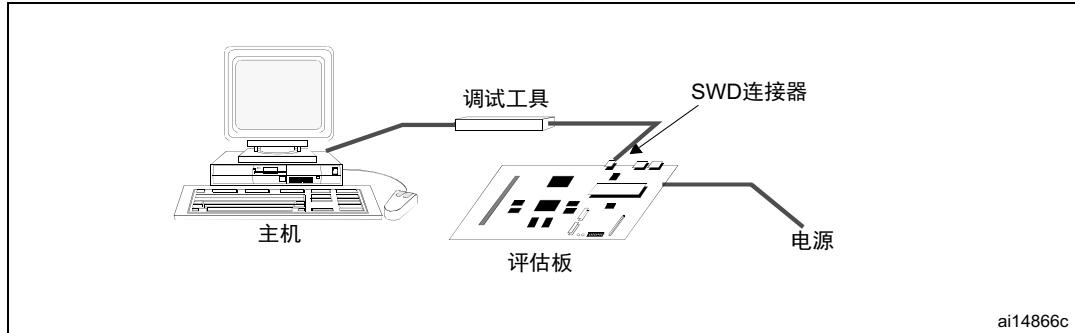

## 8 调试管理

### 8.1 引言

主机/目标接口为连接主机与应用板的硬件设备。此接口由三部分组成：硬件调试工具、JTAG或SWD连接器，以及连接主机与调试工具的电缆。

[图 17](#)显示了主机到评估板的连接。

图17. 主机到板的连接

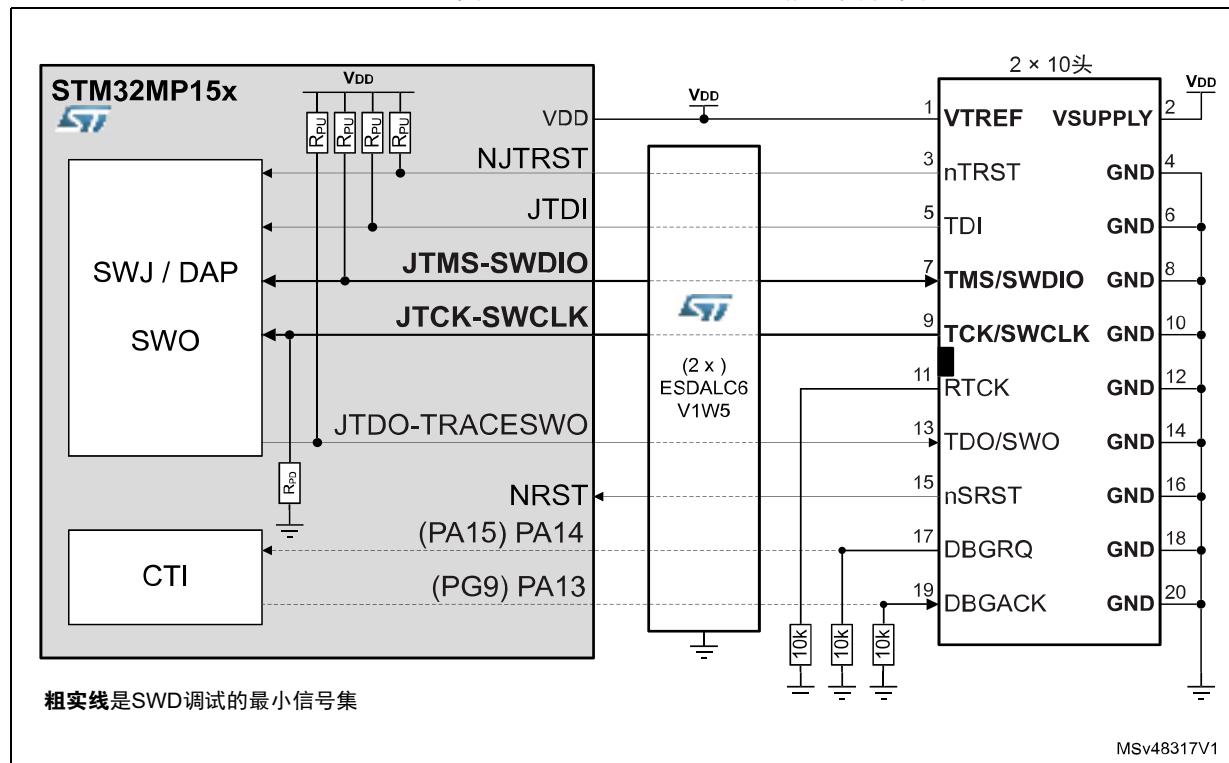

### 8.2 SWJ 调试端口（串行接口和 JTAG）

STM32MP15x系列产品内核集成了串行/JTAG调试端口(SWJ-DP)。该端口是 Arm® 标准 CoreSight™ 调试端口，具有 JTAG-DP (5 引脚) 接口和 SW-DP (2 引脚) 接口。

- JTAG调试端口(JTAG-DP)提供用于连接到AHP-AP端口的5引脚标准JTAG接口。

- 串行线调试端口(SW-DP)提供用于连接到AHB-AP端口的2引脚（时钟+数据）接口。

- SW-DP的2个引脚与JTAG-DP的5个JTAG引脚中的2个引脚复用。

### 8.3 引脚排列和调试端口引脚

#### 8.3.1 JTAG引脚上的内部上拉和下拉电阻

为避免I/O电平浮空，STM32MP15x系列产品在JTAG引脚上内置有内部上拉和下拉电阻：

- NJTRST: 内部上拉

- JTDI: 内部上拉

- JTDO-TRACESWO: 内部上拉

- JTMS/SWDIO: 内部上拉

- JTCK-SWCLK: 内部下拉

注：

JTAG IEEE 标准建议在 TDI、TMS、nTRST 上增加上拉电阻，但对 TCK 没有特殊建议。然而，对于 STM32MP15x 系列产品，有一个集成的下拉电阻用于 JTCK。

由于带有上拉和下拉电阻，因此无需添加外部电阻。

### 8.3.2 使用标准JTAG连接器的调试端口连接

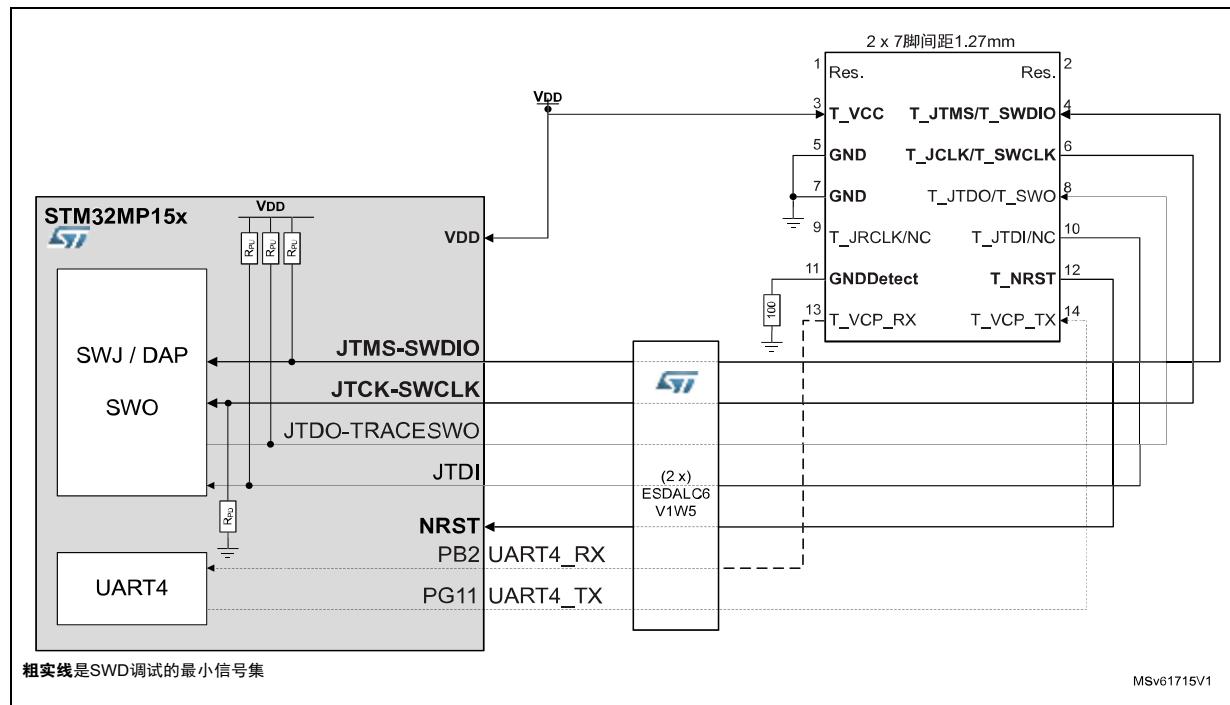

图 18 显示了 STM32MP15x 系列产品和标准 JTAG/SWD 连接器之间的连接。

图18. JTAG/SWD MIPI10连接器实现示例

注： TRACESWO 引脚上的单线跟踪仅适用于 Cortex-M4 内核。要跟踪所有内核活动，必须使用并行跟踪端口（参见第 8.3.4 节：并行跟踪和 HDP）。

### 8.3.3 使用STDC14连接器的调试端口和UART连接

图 19 显示了 STM32MP15x 系列产品与 STDC14 连接器之间的连接，包括 UART 虚拟 COM 端口连接。

STDC14 头的参考示例为 FTSH-107-01-L-DV-K-A

图19. JTAG/SWD/UART VCP STDC14连接器实现示例

注： TRACESWO 引脚上的单线跟踪仅适用于 Cortex-M4 内核。要跟踪所有内核活动，必须使用并行跟踪端口（参见第 8.3.4 节：并行跟踪和 HDP）。

注： STDC14 连接器采用（从引脚 3 到引脚 12） Arm10 引脚布局（Arm Cortex 调试连接器）。

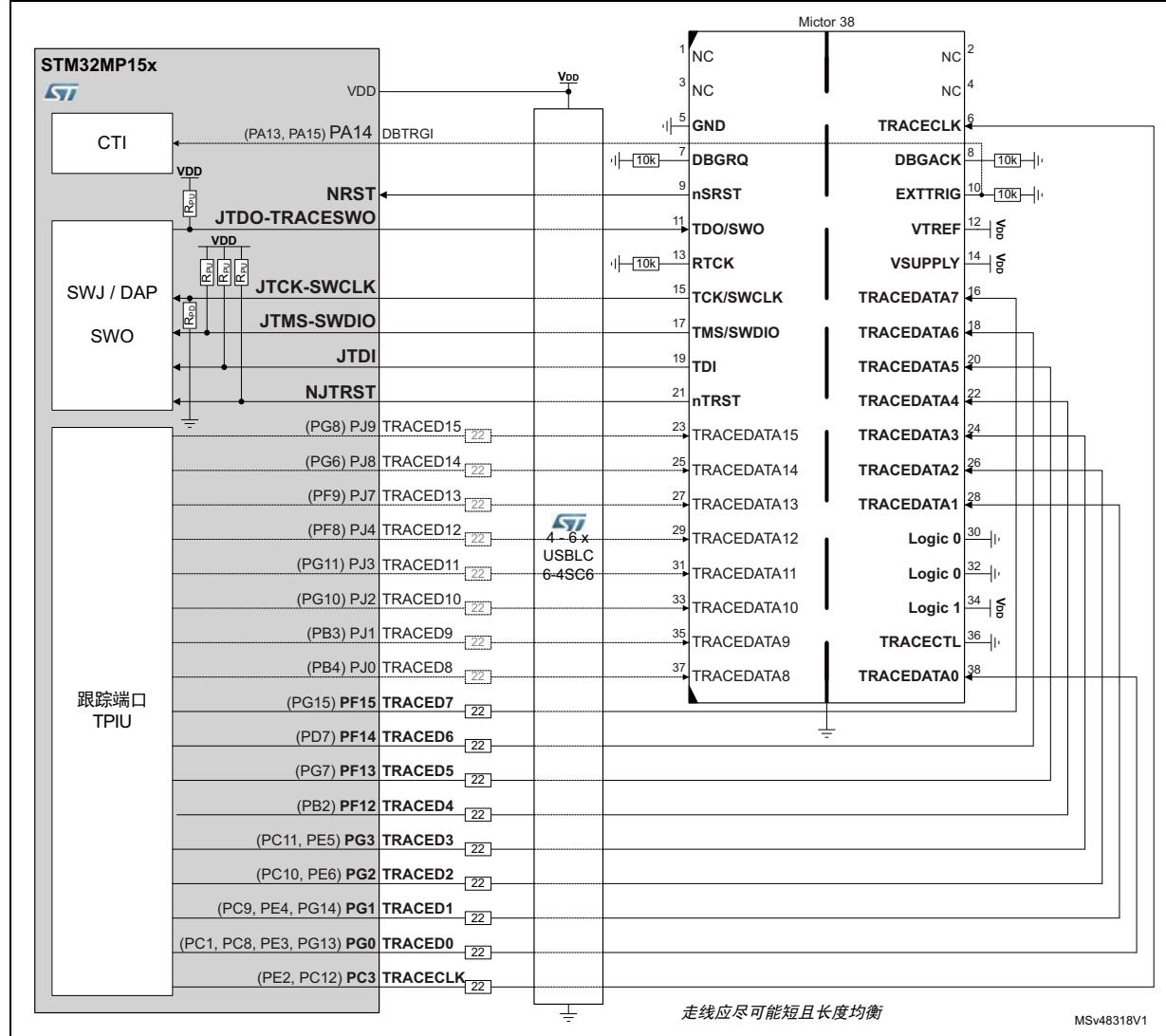

### 8.3.4 并行跟踪和HDP

#### 并行跟踪

TRACED[15:0]和TRACECLK信号作为IO引脚上的复用功能提供。用户可以选择跟踪数据数量N = 1、2、4、8或16个引脚。跟踪数据越少，可用跟踪带宽越低，在不出现跟踪溢出的前提下（STM32MP15x系列产品中有8 Kb的缓冲）可跟踪的信息越少（如跟踪源、代码和/或数据跟踪的数量）。对于每种产品，对可用功能和跟踪总线进行权衡可能会导致在产品开发过程中使用跟踪时功能变少。

此跟踪符合Arm® CoreSight™跟踪要求，并需要专用跟踪工具，以便解释和关联通过SWD或JTAG完成的调试。

有关跟踪端口接口CoreSight™组件的更多信息，请参见产品参考手册和《ARM® CoreSight™ SoC-400技术参考手册》。

请注意，为了有效跟踪带宽，TRACECLK应尽可能快地运行，同时在所有并行跟踪信号上保持良好的信号完整性。这取决于电路板和连接器选择、GPIO强度设置（GPIO\_OSPEEDR寄存器）和V<sub>DD</sub>电压。

使用V<sub>DD</sub> = 1.8 V时，可能需要对OTP位和寄存器SYSCFG\_IOWTRLSETR（HSLVEN\_TRACE位）进行设置，以确保在用于跟踪信号的焊盘上获得最佳速度。

---

**警告：**当V<sub>DD</sub>高于2.7 V时，不得置位UHSLVEN和HSLVEN，否则可能造成IC永久损坏。

---

图20. Mictor-38上带JTAG/SWD的并行跟踪端口实现示例

### 硬件调试端口

一些内部信号可用于深度调试。需要内部知识以及示波器或逻辑分析仪。有关更多信息，请参阅产品参考手册和数据手册。

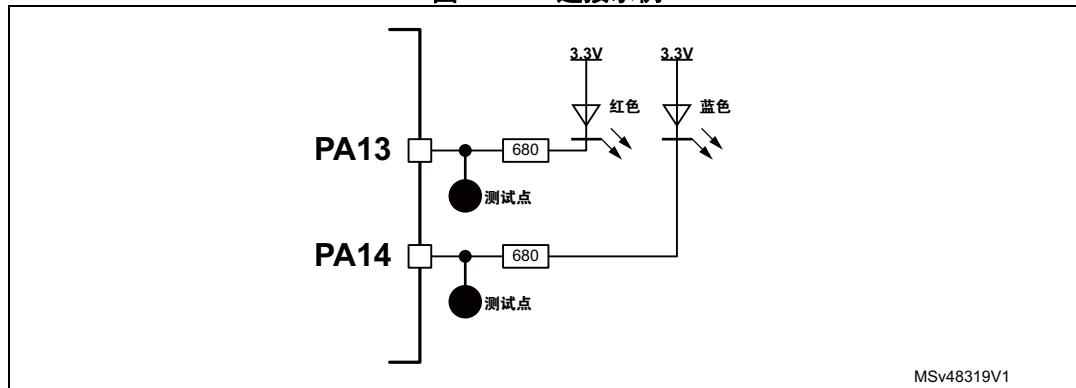

### 8.3.5 调试触发器和LED

CoreSight™交叉触发接口（CTI）可在引脚上作为DBTRGI和DBTRGO使用。

DBTRGI可由外部用户信号生成，并可以在CoreSight™组件内编程，以便在调试模式（中断）中启动/停止跟踪或进入特定内核。

DBTRGO可由CTI生成，以便从外部查看其中一个CoreSight™组件（内核中断、跟踪启动等）已达到的触发条件。

DBTRGO可在PA13、PA14或PG9上获得。

DBTRGI可在PA13、PA14或PA15上获得。

PA13特定行为（详情请参见启动文档）：

- 在启动阶段，如果启动失败，则将PA13引脚设置为低漏极开路（即错误LED点亮）。

- 在UART/USB启动期间，PA13引脚以大约5Hz的速率切换开漏，直到连接开始（即错误LED快速闪烁）。

- 当BOOT[2:0]=0b100（未启动，用于特定调试），PA13以大约5kHz的速率切换漏极开路（即错误LED发出弱光）。

- 在所有其他情况下，PA13保持其复位值，即高阻抗，直至进行软件设置。

如图21中所示，在PA13上设置一个红色LED是个好主意。

LED对于快速发出系统活动的视觉信号很有用。因此，使用PA13和PA14是一个不错的选择。这无法避免在PA13或PA14上使用DBTRGI和DBTRGO进行调试（假设软件在该特定调试期间停止控制LED）。

图21. LED连接示例

## 9 建议

### 9.1 印刷电路板

出于技术原因，必须使用多层印刷电路板（PCB），该电路板必须具有专用于接地（ $V_{SS}$ ）的独立层，以及专用于供电（如 $V_{DD}$ 和 $V_{DDCORE}$ ）的另一层。这样才能实现不错的去耦和屏蔽效果。

### 9.2 元件位置

为了减少PCB上的交叉耦合，PCB的初始布局必须对不同的电路的EMI贡献进行区分，不同的电路包括噪声、大电流电路、低电压电路和数字部分。

### 9.3 接地和供电 ( $V_{SSx}$ 、 $V_{DDx}$ )

由于STM32MP15x系列产品系列中涉及大功率和高频率，必须使用至少有4层的PCB，该PCB必须具有用于 $V_{SSx}$ 和 $V_{DDx}$ 的专用供电层。

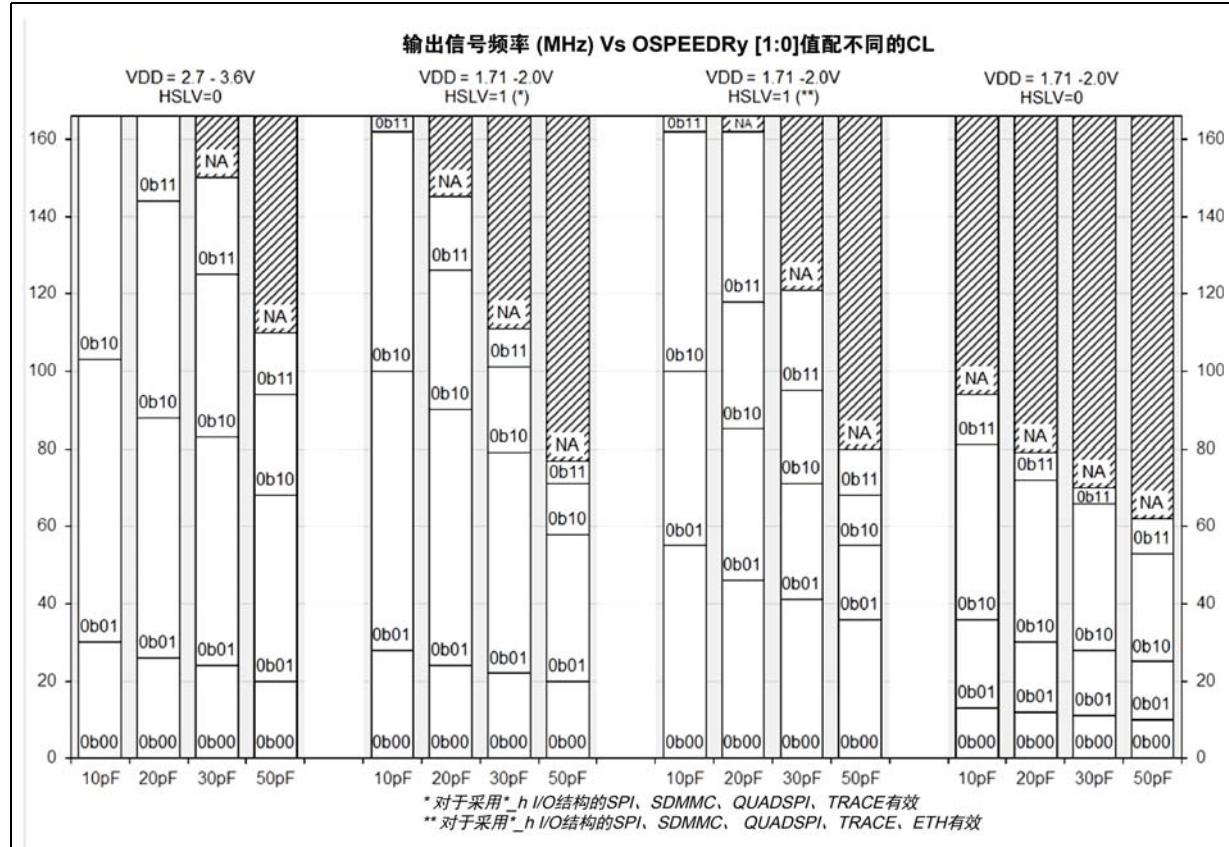

### 9.4 IO速度设置

必须在IO上设置正确的输出驱动，以便有足够的上升和下降时间，同时避免额外的振铃和噪声。

当对IO速度没有特定要求时，必须将OSPEEDR设为0。

大致上，以下图表和表格可用于根据信号频率和容性负载快速选择正确设置。如果出现信号完整性问题，该设置可能需要量身定制。

在大多数情况下，需要在SYSCFG中使能IO补偿。有关更多详细信息，请参见产品数据手册。

注： 在异步或单边沿时钟数据通道（如SDR）的情况下，最大有效数据切换频率实际上仅为数据率的一半。例如，以10 Mbit/s运行的SPI的数据信号具有5 MHz的最大频率（例如，输出串行数据01010101...），但时钟信号的最大频率为10 MHz。在双边沿时钟数据通道（如DDR）中，时钟和数据具有相同的最大切换频率。

注： 如果OTP位PRODUCT\_BELOW\_2V5=0（默认状态），则不考虑HSLVEN\_xxx位。

注： 当 $VDD > 2.7V$ 时， $HSLVEN_xxx=1$ 且product\_below\_2V5=1 的设定可能会损坏IC。

图22. 各种负载和电压下的IO速度总结

表13. VDD = 3.3 V典型值时的OSPEEDR设置示例

| 外设                         | 信号    | 切换速率<br>(MHz) | OSPEEDR CL=30 pF |                   | OSPEEDR CL=10 pF |    |

|----------------------------|-------|---------------|------------------|-------------------|------------------|----|

|                            |       |               | 1                | 2                 | 1                | 2  |

| FMC异步                      | 数据/控制 | 50            | 1                | 中速                | 1                | 中速 |

| FMC同步                      | CLK   | 100           | 2                | 高速                | 1                | 中速 |

|                            | 数据/控制 | 50            | 1                | 中速                | 1                | 中速 |

| QUADSPI (SDR)              | CLK   | 133           | 2                | 高速 <sup>(1)</sup> | 2                | 高速 |

|                            | 数据/控制 | 66.5          | 1                | 中速                | 1                | 中速 |

| QUADSPI (DDR)              | 全部    | 66.5          | 1                | 中速                | 1                | 中速 |

| LTDC (HDMI) <sup>(2)</sup> | CLK   | 74.25         | 1                | 中速                | 1                | 中速 |

|                            | 数据/控制 | 37.125        | 1                | 中速                | 1                | 中速 |

| LTDC <sup>(2)</sup>        | CLK   | 90            | 2                | 高速                | 1                | 中速 |

|                            | 数据/控制 | 45            | 1                | 中速                | 1                | 中速 |

| LTDC                       | CLK   | 48            | 1                | 中速                | 1                | 中速 |

|                            | 数据/控制 | 24            | 0                | 低速                | 0                | 低速 |

| TIM/LPTIM                  | 全部    | 5             | 0                | 低速                | 0                | 低速 |

表13. VDD = 3.3 V典型值时的OSPEEDR设置示例（续）

| 外设          | 信号    | 切换速率<br>(MHz) | OSPEEDR CL=30 pF |                   | OSPEEDR CL=10 pF |

|-------------|-------|---------------|------------------|-------------------|------------------|

| I2C         | 全部    | 1             | 0                | 低速                | 0                |

| USART:      | 全部    | 5             | 0                | 低速                | 0                |

| SPI         | CLK   | 50            | 1                | 中速                | 1                |

|             | 数据/控制 | 25            | 1                | 中速                | 0                |

| (SAI)       | MCLK  | 15            | 0                | 低速                | 0                |

|             | CLK   | 1             | 0                | 低速                | 0                |

|             | 数据/控制 | 0.5           | 0                | 低速                | 0                |

| MDIOS       | 全部    | 5             | 0                | 低速                | 0                |

| SDMMC (SDR) | CLK   | 133           | 2                | 高速 <sup>(1)</sup> | 2                |

|             | 数据/控制 | 66.5          | 1                | 中速                | 1                |

| SDMMC (DDR) | 全部    | 52            | 1                | 中速                | 1                |

| FDCAN       | 全部    | 5             | 0                | 低速                | 0                |

| ETH (MII)   | CLK   | 50            | 1                | 中速                | 1                |

|             | 数据/控制 | 25            | 1                | 中速                | 0                |

| ETH (RMII)  | 全部    | 50            | 1                | 中速                | 1                |

| ETH (GMII)  | CLK   | 125           | 2                | 高速                | 2                |

|             | 数据/控制 | 62.5          | 1                | 中速                | 1                |

| ETH (RGMII) | 全部    | 125           | 2                | 高速                | 2                |

| ETH (MDIO)  | MDIO  | 2.5           | 0                | 低速                | 0                |

| TRACE       | 全部    | 133           | 3                | 超高速               | 2                |

|             |       | 100           | 2                | 高速                | 1                |

1. CL=20 pF时的值。

2. HSE需要外部振荡器。

表14. VDD = 1.8 V典型值时的OSPEEDR设置示例<sup>(1)</sup>

| 外设                           | 信号    | 切换速率<br>(MHz) | OSPEEDR CL=30 pF |                    | OSPEEDR CL=10 pF |

|------------------------------|-------|---------------|------------------|--------------------|------------------|

| FMC异步                        | 数据/控制 | 50            | 2                | 高速                 | 2                |

| FMC同步                        | CLK   | 69            | 3                | 超高速                | 3                |

|                              | 数据/控制 | 34.5          | 2                | 高速                 | 1                |

| QUADSPI (SDR) <sup>(2)</sup> | CLK   | 133           | 3                | 超高速 <sup>(3)</sup> | 2                |

|                              | 数据/控制 | 66.5          | 1                | 中速                 | 1                |

| QUADSPI (DDR) <sup>(2)</sup> | 全部    | 66.5          | 1                | 中速                 | 1                |

| LTDC (HDMI)                  | CLK   | 74.25         | 3                | 超高速 <sup>(3)</sup> | 3                |

|                              | 数据/控制 | 37.125        | 2                | 高速                 | 2                |

表14. VDD = 1.8 V典型值时的OSPEEDR设置示例<sup>(1)</sup> (续)

| 外设                         | 信号    | 切换速率<br>(MHz)) | OSPEEDR CL=30 pF     | OSPEEDR CL=10 pF |

|----------------------------|-------|----------------|----------------------|------------------|

| LTDC                       | CLK   | 69             | 3 超高速                | 3 超高速            |

|                            | 数据/控制 | 34.5           | 2 高速                 | 1 中速             |

| TIM/LPTIM                  | 全部    | 5              | 0 低速                 | 0 低速             |

| I2C                        | 全部    | 1              | 0 低速                 | 0 低速             |

| USART:                     | 全部    | 5              | 0 低速                 | 0 低速             |

| SPI <sup>(4)</sup>         | CLK   | 50             | 1 中速                 | 1 中速             |

|                            | 数据/控制 | 25             | 1 中速                 | 0 低速             |

| (SAI)                      | MCLK  | 15             | 1 中速                 | 1 中速             |

|                            | CLK   | 1              | 0 低速                 | 0 低速             |

|                            | 数据/控制 | 0.5            | 0 低速                 | 0 低速             |

| MDIOS                      | 全部    | 5              | 0 低速                 | 0 低速             |

| SDMMC (SDR) <sup>(5)</sup> | CLK   | 133            | 3 超高速 <sup>(3)</sup> | 2 高速             |

|                            | 数据/控制 | 66.5           | 1 中速                 | 1 中速             |

| SDMMC (DDR) <sup>(5)</sup> | 全部    | 52             | 1 中速                 | 1 中速             |

| FDCAN                      | 全部    | 5              | 0 低速                 | 0 低速             |

| ETH (MII) <sup>(6)</sup>   | CLK   | 50             | 1 中速                 | 0 低速             |

|                            | 数据/控制 | 25             | 0 低速                 | 0 低速             |

| ETH (RMII) <sup>(6)</sup>  | 全部    | 50             | 1 中速                 | 0 低速             |

| ETH (GMII) <sup>(6)</sup>  | CLK   | 125            | 3 超高速 <sup>(3)</sup> | 2 高速             |

|                            | 数据/控制 | 62.5           | 1 中速                 | 1 中速             |

| ETH (RGMII) <sup>(6)</sup> | 全部    | 125            | 3 超高速 <sup>(3)</sup> | 2 高速             |

| ETH (MDIO)                 | MDIO  | 2.5            | 0 低速                 | 0 低速             |

| TRACE <sup>(7)</sup>       | 全部    | 133            | 3 超高速 <sup>(3)</sup> | 2 高速             |

|                            |       | 100            | 2 高速                 | 1 中速             |

1. 仅在设置OTP位PRODUCT\_BELOW\_2V5的情况下才考虑HSLVEN\_xxx=1。

2. HSLVEN\_QUADSPI=1。

3. CL=20pF时的值。

4. HSLVEN\_SPI=1。

5. HSLVEN\_SDMMC=1。

6. HSLVEN\_ETH=1。

7. HSLVEN\_TRACE=1。

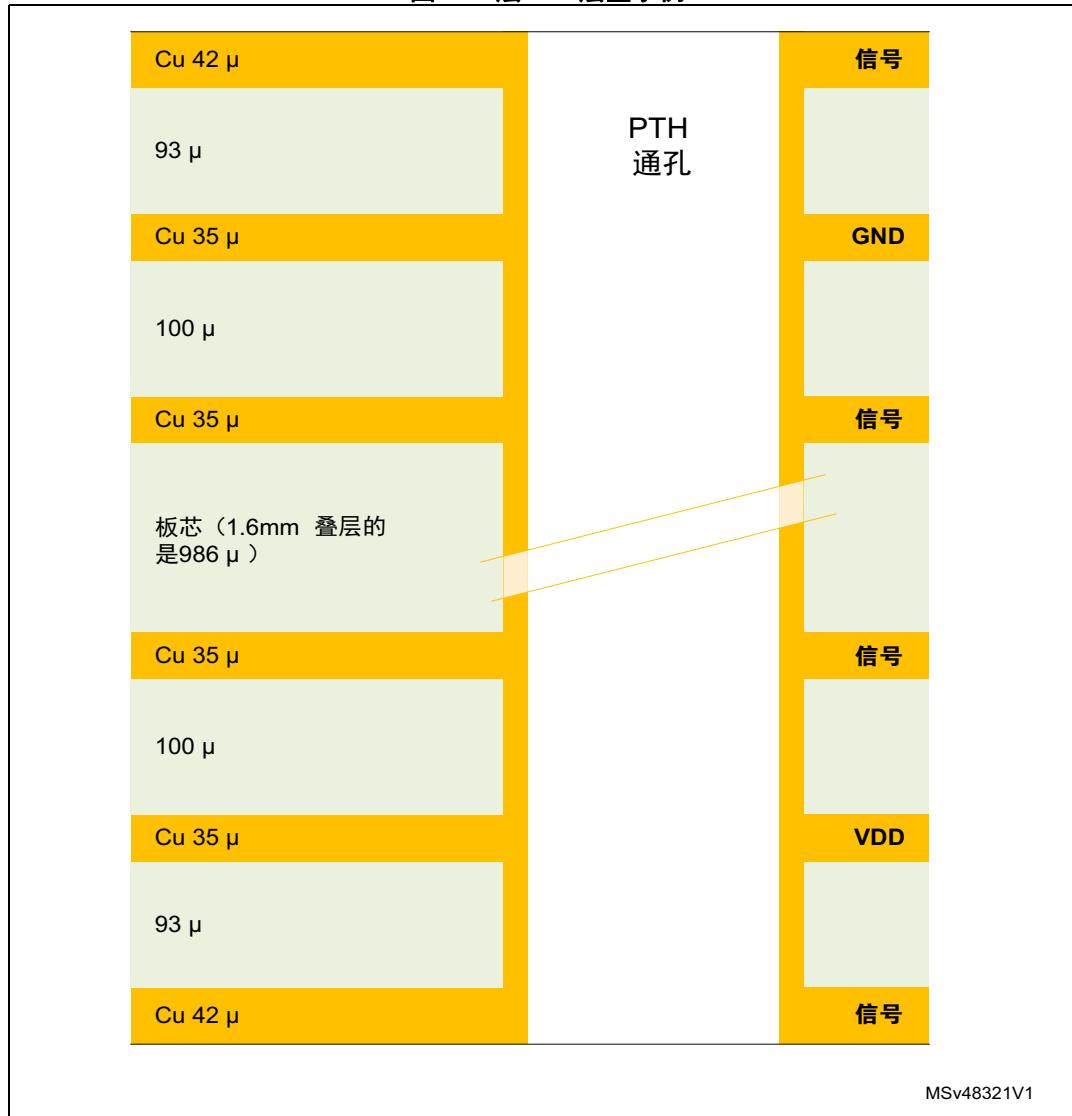

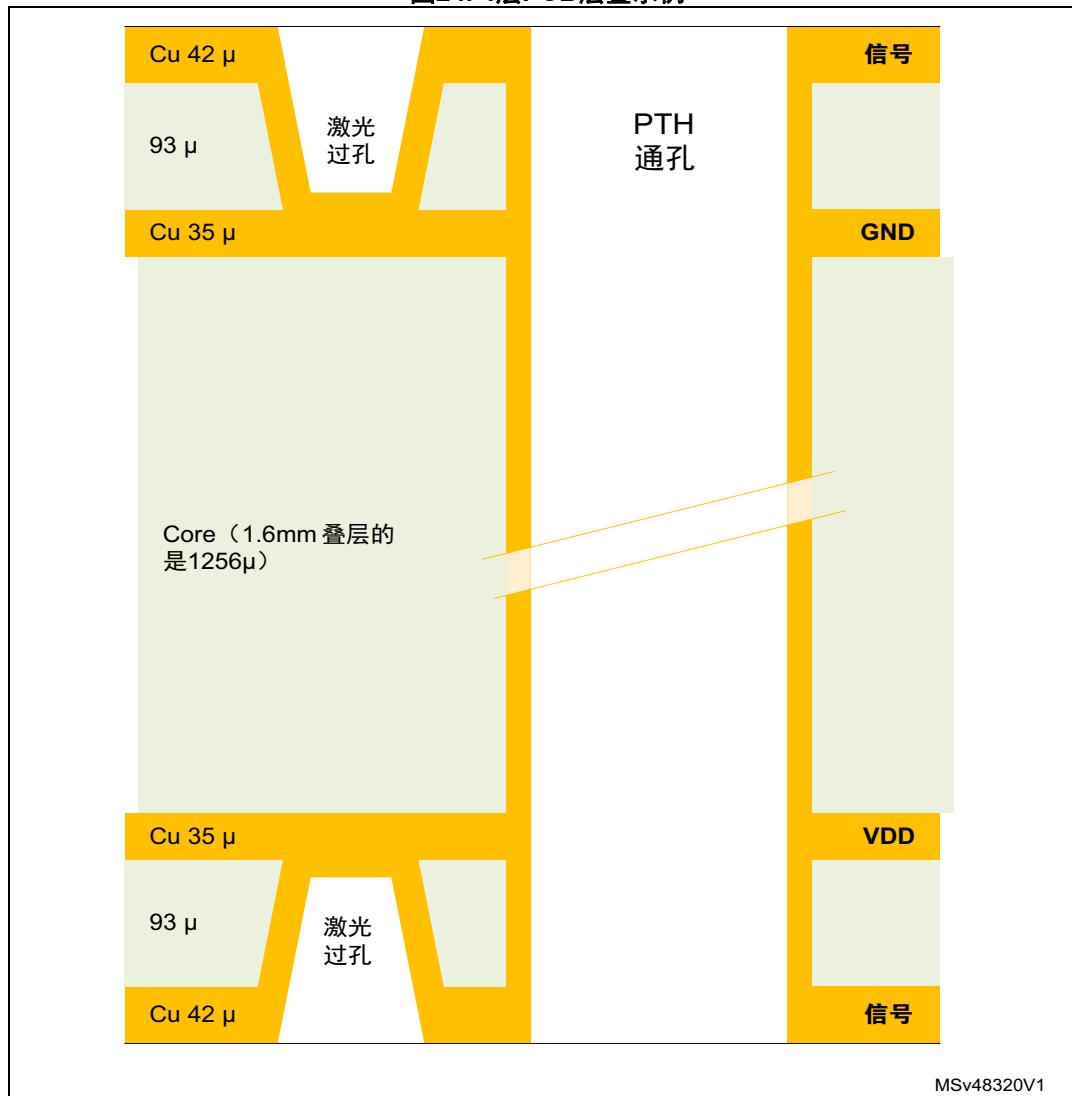

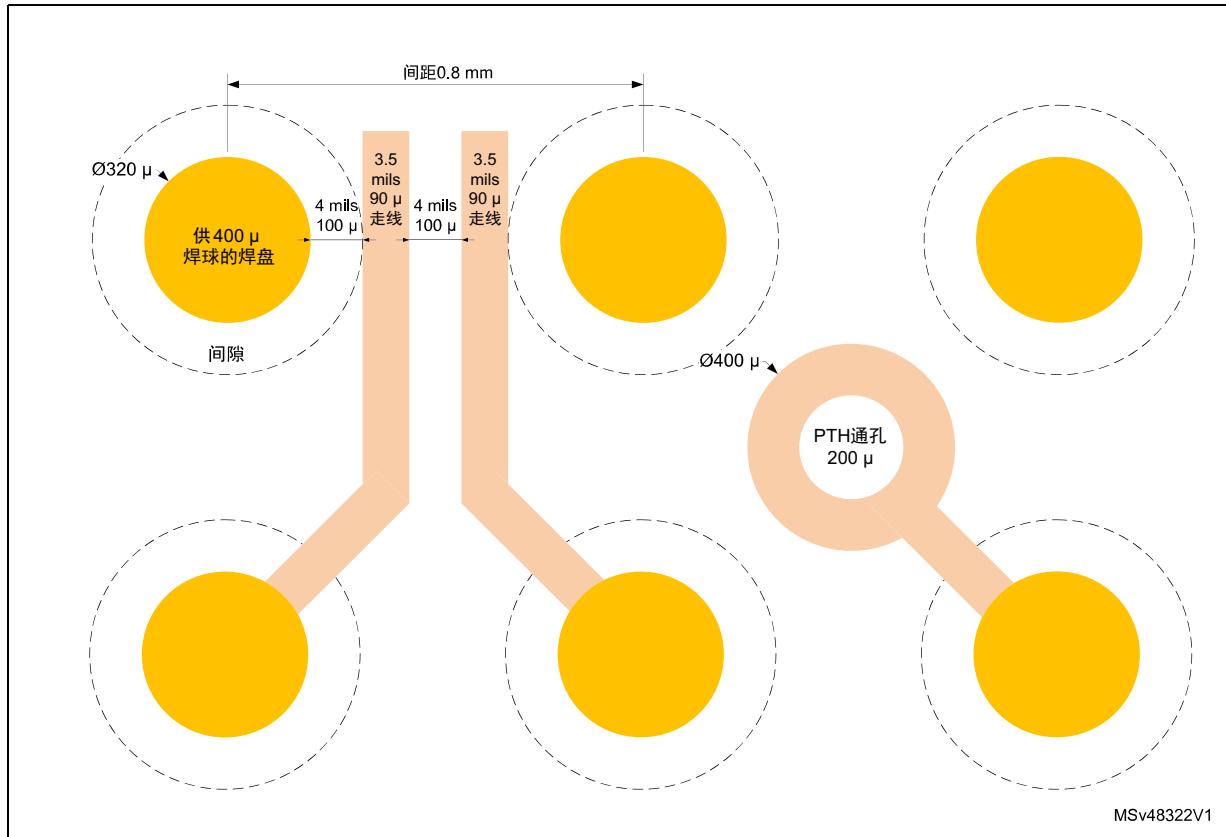

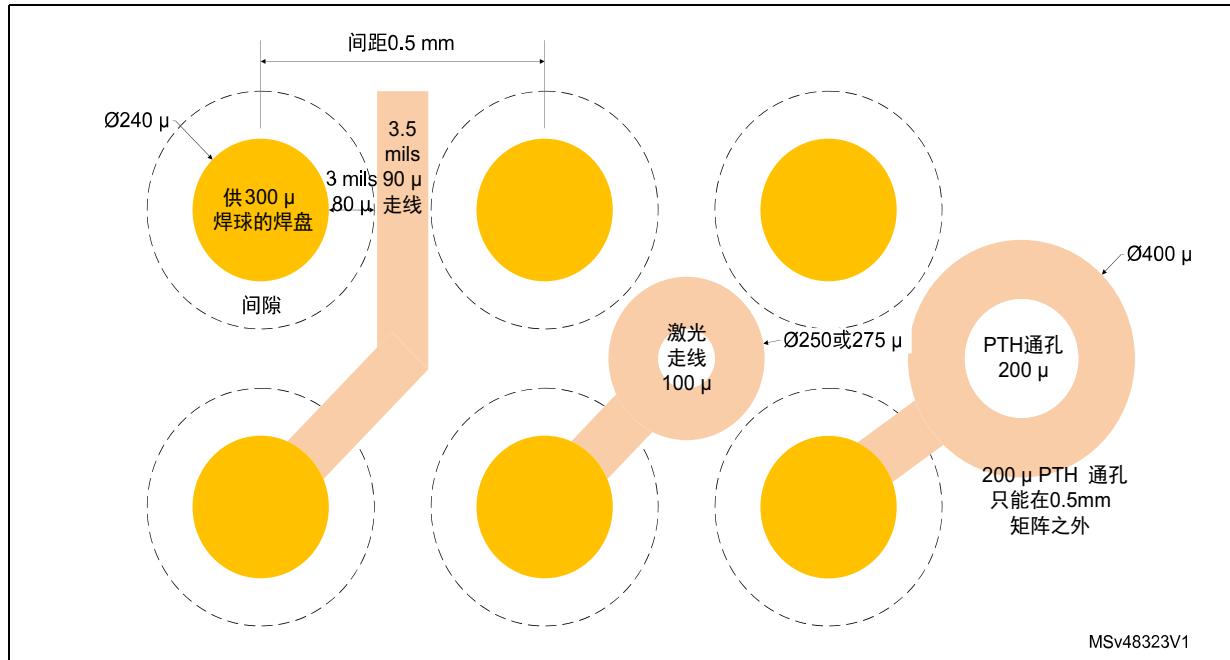

## 9.5 PCB层叠和技术

必须在PCB成本与电气连接容易性之间进行权衡。以下示例为只有PTH的4层或6层PCB（适用于0.8mm的脚间距封装）或同时具有PTH和激光钻孔的4层PCB（适用于0.5mm的脚间距封装）。

请注意，外焊球间距为0.5 mm的一些STM32MP15x系列产品封装提供间距为0.65 mm的中心焊球矩阵，以改善功率，并允许焊球之间具有大PTH通孔。与小型埋入式激光钻孔相比，这可以确保更出色的电源连接，并优化了导热性。

图23. 6层PCB层叠示例

图24. 4层PCB层叠示例

图25. 0.8 mm脚间距封装的PCB规则示例

图26. 0.5 mm脚间距封装的PCB规则示例

图27. 改善了功率的0.65mm脚间距内焊球PCB规则示例

## 9.6 去耦

所有供电和接地引脚都必须适当连至供电电源。这些连接，包括焊盘、线、过孔，都必须有尽可能低的阻抗。典型情况下，这可通过使用粗的线宽做到，最好在多层PCB中使用专用供电层。

此外，每个供电电源对都应使用陶瓷电容（大多数情况下为100 nF或1  $\mu$ F，参见表 4）去耦。这些电容需要尽量靠近适当的引脚，或在这些引脚PCB的下面。确切值可能取决于应用。[图 28](#)显示了此类去耦布置的典型布局。

图28. 去耦布局示例

1. 内层的PTH通孔连接电源和去耦电容以灰色显示。

## 9.7 ESD/EMI保护

从产品开发开始就应该考虑静电放电（ESD）与电磁干扰（EMI），因为在后期处理这些问题时可能非常复杂和昂贵。

ESD和EMI由全球标准推动（如IEC 61000、JESD 22），大多数国家/地区均要求在认证后才能在产品上附加强制标志（如CE、FCC）。

ESD和EMI也由标准化接口认证或要求（如USB）推动。

尽管具有STM32MP15x系列产品嵌入了器件级ESD保护，但最终产品保护应通过外部组件完成，尤其是最终产品中供外部用户访问的接口（例如，以太网、USB、SD卡）。

某些组件提供ESD保护以及EMI共模滤波（如用于USB的ECMF02-2AMX6）。

[第 10 节：参考设计示例](#)中提供了一些ESD/EMI保护示例。

有关更多详细信息，请参阅[ST微控制器EMC设计指南应用说明\(AN1709\)](#)。

## 9.8 敏感信号

当设计应用时，可仔细研究下述信号以提高电磁兼容性（EMC）性能：

- 临时扰动会永久影响运行过程的信号（中断和握手选通信号就是这个情况，但LED指令不是这个情况）。

对于这些信号，可使用地线包围、更短的长度、附近没有噪声和敏感的走线（串扰影响）提高EMC性能。

对于数字信号，两种逻辑状态必须达到可能的最佳电气裕量，建议使用慢施密特触发器以消除寄生状态。

- 噪声信号（时钟等）

- 敏感信号（高阻等）

有关更多详细信息，请参阅[ST微控制器EMC设计指南应用说明\(AN1709\)](#)。

## 9.9 不使用的I/O和特性

STM32MP15x系列产品为多种应用而设计，通常一个应用不会使用100%的资源。

为了提高EMC性能，不使用的时钟、计数器、I/O都不应浮空，例如，I/O应该设置为0或者1（上拉或者下拉至不用的I/O引脚），并且不使用的功能应被“冻结”或禁用。

## 10 参考设计示例

### 10.1 说明

以下章节中提供了一些示例，以帮助用户将主要和关键接口连接到STM32MP15x系列产品。

#### 10.1.1 时钟

STM32MP15x系列产品使用两个时钟源，具有以下选择：

- LSE: 32.768 kHz晶振用于嵌入式RTC

- HSE: 24 MHz晶振或外部振荡器作为STM32MP15x系列产品主时钟

请参见[第6节：时钟第28页](#)。

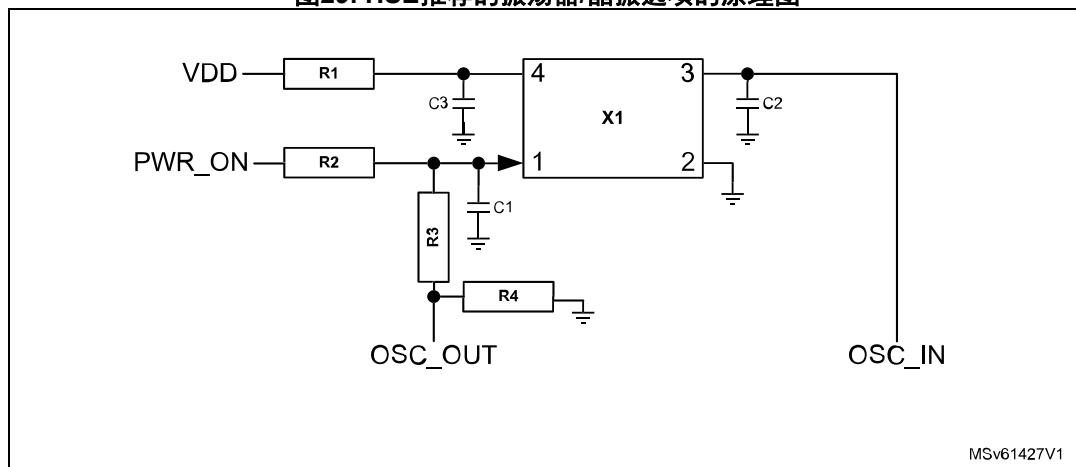

**图29. HSE推荐的振荡器/晶振选项的原理图**

**表15. 振荡器或晶振的HSE BOM**

| -  | 振荡器             | 晶振              |

|----|-----------------|-----------------|

| X1 | NZ2016SH 24 MHz | NX2016SA 24 MHz |

| R1 | 10 ohms         | -               |

| R2 | 10 Kohms        | -               |

| R3 | -               | 0 ohm           |

| R4 | 1Kohm           | -               |

| C1 | -               | 6.8 pF          |

| C2 | -               | 6.8 pF          |

| C3 | 10 nF           | -               |

### 10.1.2 复位

图 4 中的 NRST 复位信号为低电平有效。复位源包括：

- 复位按钮

- 通过 JTAG 连接器连接的调试器。

请参见 [第 4.3 节：复位和电源监控 第 17 页](#)。

### 10.1.3 自举模式

通过设置永久导线或开关 SW3 (BOOT2)、SW2 (BOOT1) 和 SW1 (BOOT0) 以及内部 OTP 来配置启动选项。参见 [第 7 节：自举配置 第 32 页](#)。

如果 UART 启动使用其中一个可能的 U(S)ARTx\_RX 引脚（参考 STM32MP1 系列维基百科），以避免在 BootROM 接收并解码初始化字符之前向主机发送浮动信号，则需要在相应的 U(S)ARTx\_TX 引脚上设一个 10 kOhm 的 V<sub>DD</sub> 上拉电阻。

表16. UART可能的自举引脚

| 外设                   | 信号 | 引脚   |

|----------------------|----|------|

| USART2               | RX | PA3  |

|                      | TX | PA2  |

| USART3               | RX | PB12 |

|                      | TX | PB10 |

| UART4 <sup>(1)</sup> | RX | PB2  |

|                      | TX | PG11 |

| UART5                | RX | PB5  |

|                      | TX | PB13 |

| USART6               | RX | PC7  |

|                      | TX | PC6  |

| UART7                | RX | PF6  |

|                      | TX | PF7  |

| UART8                | RX | PE0  |

|                      | TX | PE1  |

1. 推荐默认 UART 给 Linux 控制台（即作为 STLINK STDC14 连接器上的 VCP）。

### 10.1.4 SWD/JTAG 接口

参考设计显示了 STM32MP15x 系列产品和某些标准连接器之间的连接。请参见 [第 8 节：调试管理 第 36 页](#)。

注：如果可用，建议将调试器探针系统的复位引脚连接到 NRST，以便能够通过调试器复位应用。

## 10.1.5 电源

请参见第4节：电源第11页。

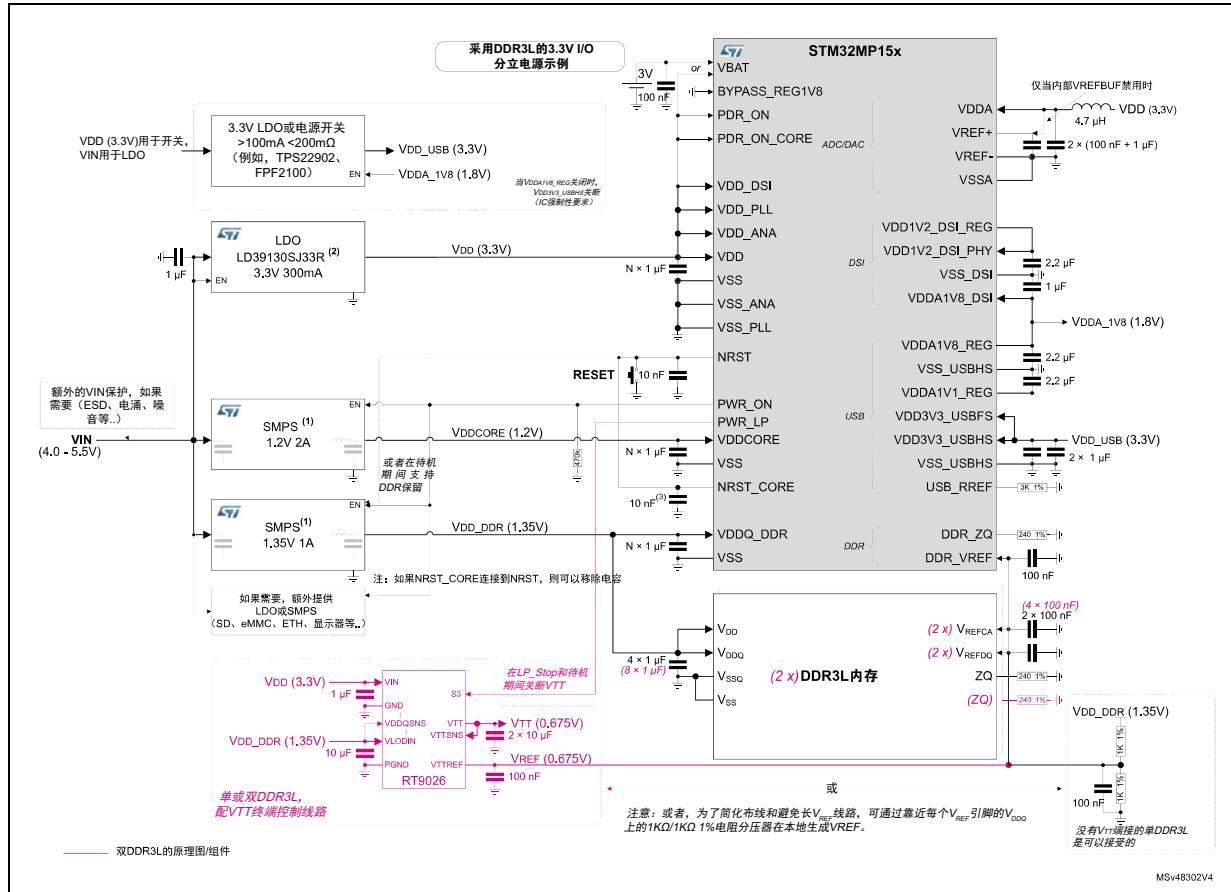

### 采用DDR3L的3.3 V I/O分立电源示例

该参考设计示例针对不强调降低功耗的低成本DDR3L简单3.3 V IO平台。支持睡眠/停止/待机模式。

可支持LP-Stop以及具有DDR3L保持功能的低功耗待机，但由于使用DDR3L时没有进行自刷新的低功耗目标，所以此功能意义不大。

另请参见STM32MP151、STM32MP153和STM32MP157分立电源硬件集成（AN5256）。

图30. 采用DDR3L的3.3 V I/O分立电源示例

- 未显示其他SMPS组件。

- 也可以使用更小的NCP161AFCT330。

- 如果NRST\_CORE连接到NRST，则可以移除NRST\_CORE引脚上的10 nF电容。

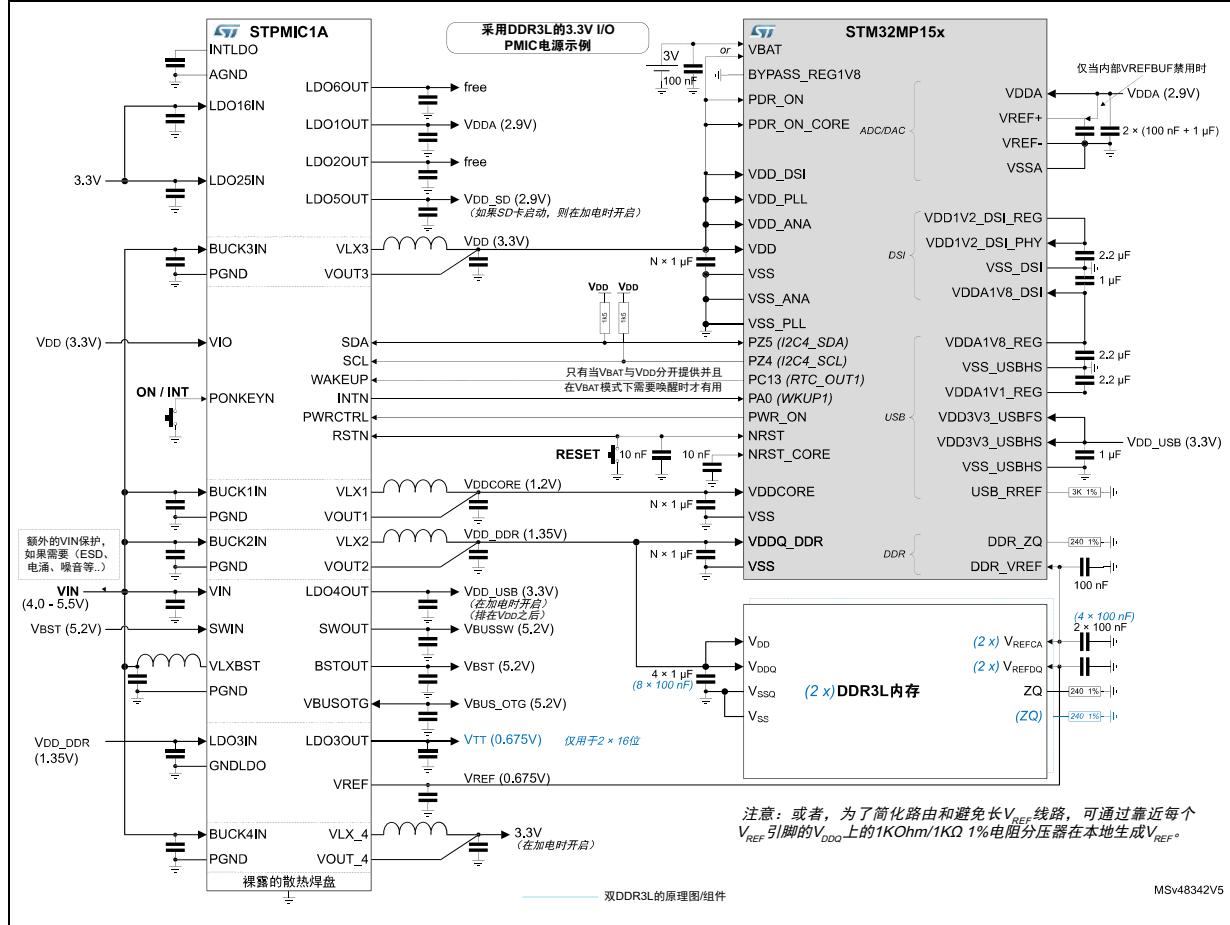

### 采用DDR3L的3.3 V I/O PMIC电源示例

该参考设计示例针对采用低成本DDR3L和高集成度PMIC的复杂3.3 V IO平台。通常，所有平台组件均可以由PMIC供电。得益于PMIC I2C和边带信号，支持全电源控制。支持睡眠/停止/待机模式。有关PMIC组件的详细信息，请参见PMIC文档。

图31. 采用DDR3L的3.3 V I/O的PMIC示例

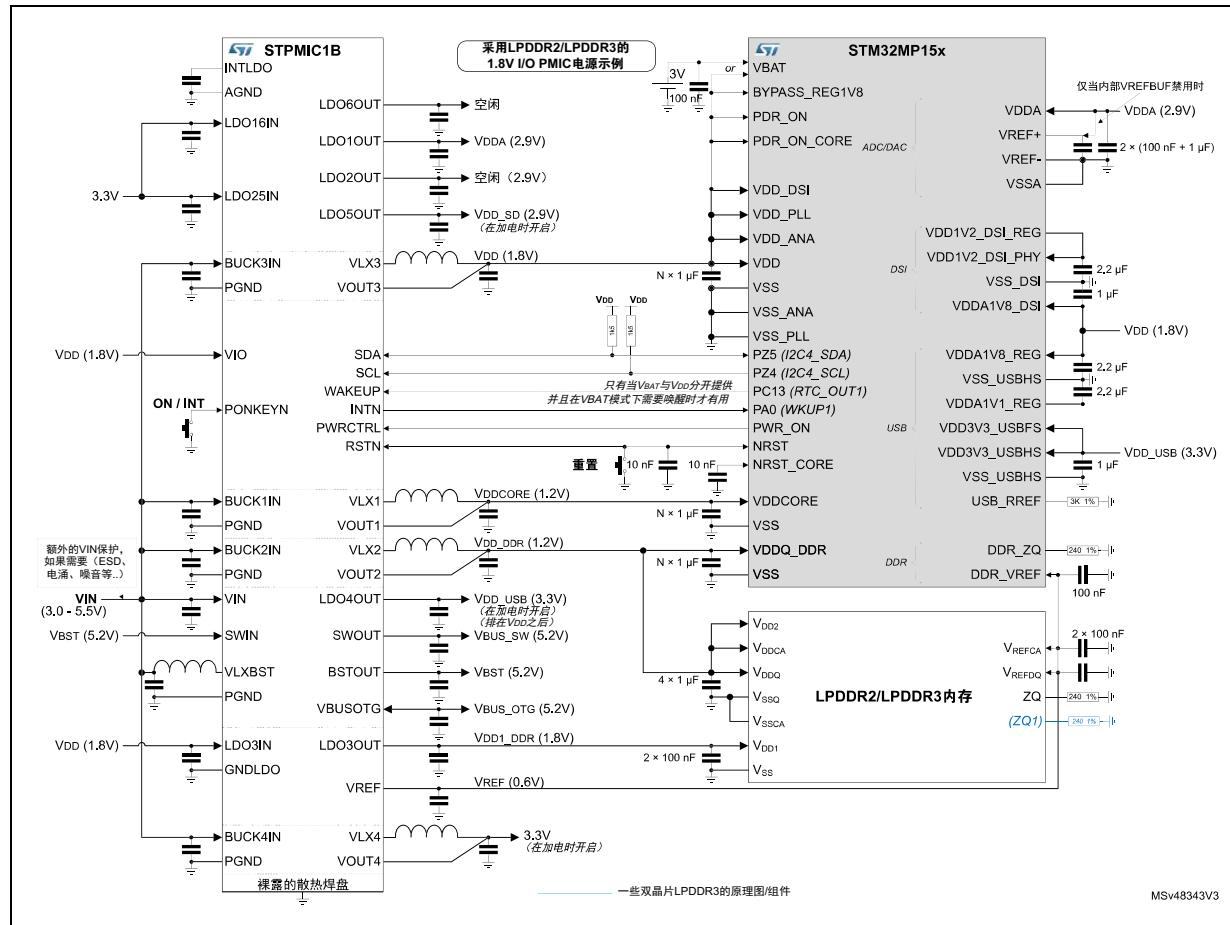

### 采用LPDDR2/LPDDR3的1.8V I/O PMIC电源示例

该参考设计示例针对采用低功耗LPDDR2/LPDDR3和高集成度PMIC的复杂1.8V IO平台。通常，所有平台组件均可以由PMIC供电。得益于PMIC I2C和边带信号，支持全电源控制。支持睡眠/停止/待机模式以及具有LPDDR2/LPDDR3保持功能的极低功耗待机模式。有关PMIC组件的详细信息，请参见PMIC文档

图32. 采用LPDDR2/LPDDR3的1.8 V I/O的PMIC示例

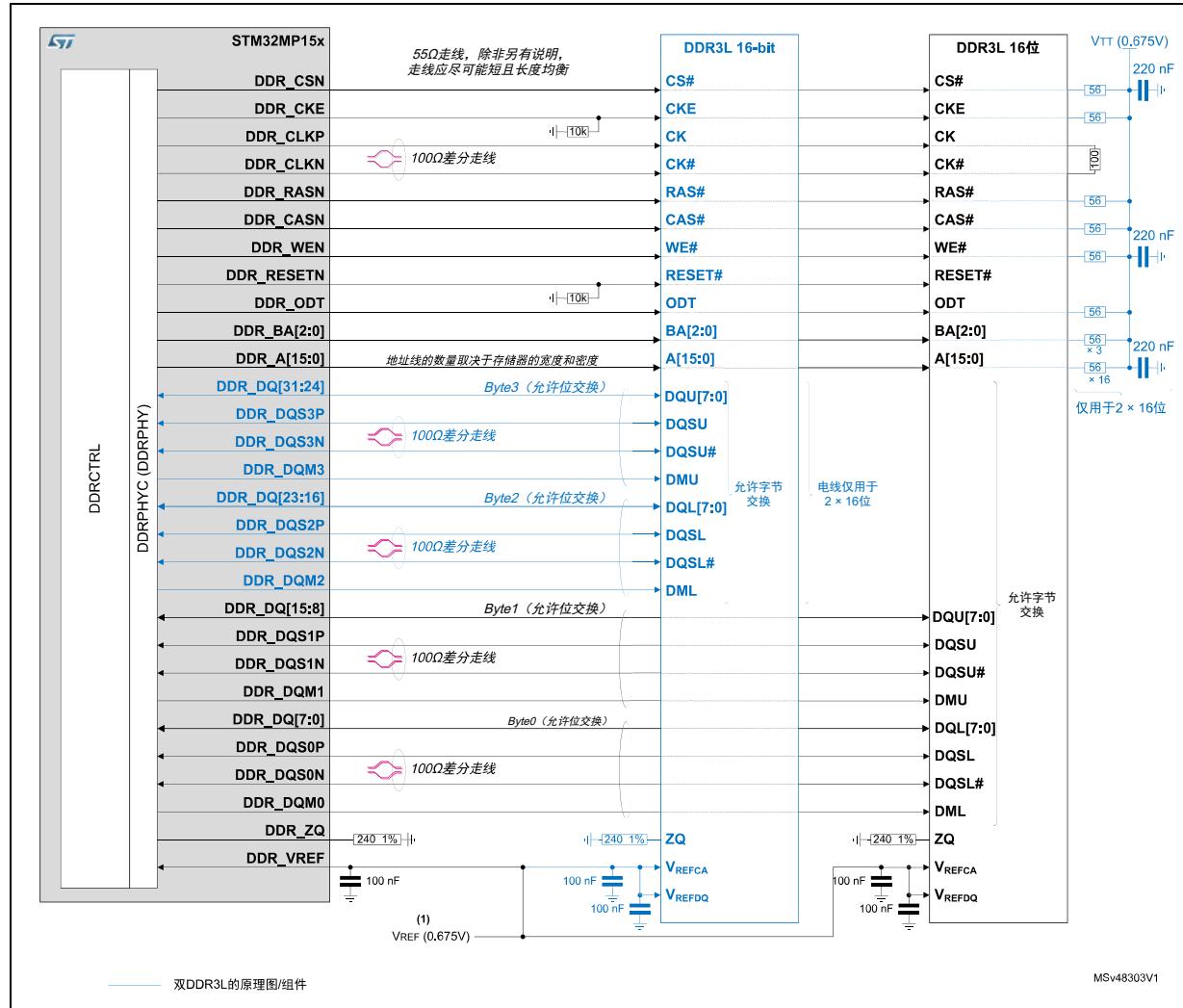

### 10.1.6 DDR3/DDR3L SDRAM

DDR3与DDR3L的区别仅在于电源电压（1.5 V vs 1.35 V）和 $V_{REF}$ 电平（0.75 V vs 0.675 V）。DDR3L已取代大多数DDR3设计。

应在DDR\_ZQ与 $V_{SS}$ 之间连接一个240 Ohm 1%的电阻。该电阻不得与每个DDR3/DDR3L组件所需的ZQ电阻共用。

对于2x16位器件，连接端接电压（VTT）电源的阻抗匹配电阻网络应布置在尽可能靠近最后一个器件的位置。为避免阻抗不连续，必须采用“Fly-by”布线技术。以下示例中的值应适用于大多数情况，但可以根据每侧IO驱动强度和PCB阻抗进行调整。

图33. DDR3L 16/32位连接示例

- 或者，为了简化布线和避免长 $V_{REF}$ 线路，可通过靠近每个 $V_{REF}$ 引脚的 $V_{DDQ}$ 上的1KOhm/1KOhm 1%电阻分压器在本地生成 $V_{REF}$ 。

- 未显示电源和去耦电容。

在STM32MP1系列DDR存储器路由指南应用说明（AN5122）中对详细布线示例进行了说明。

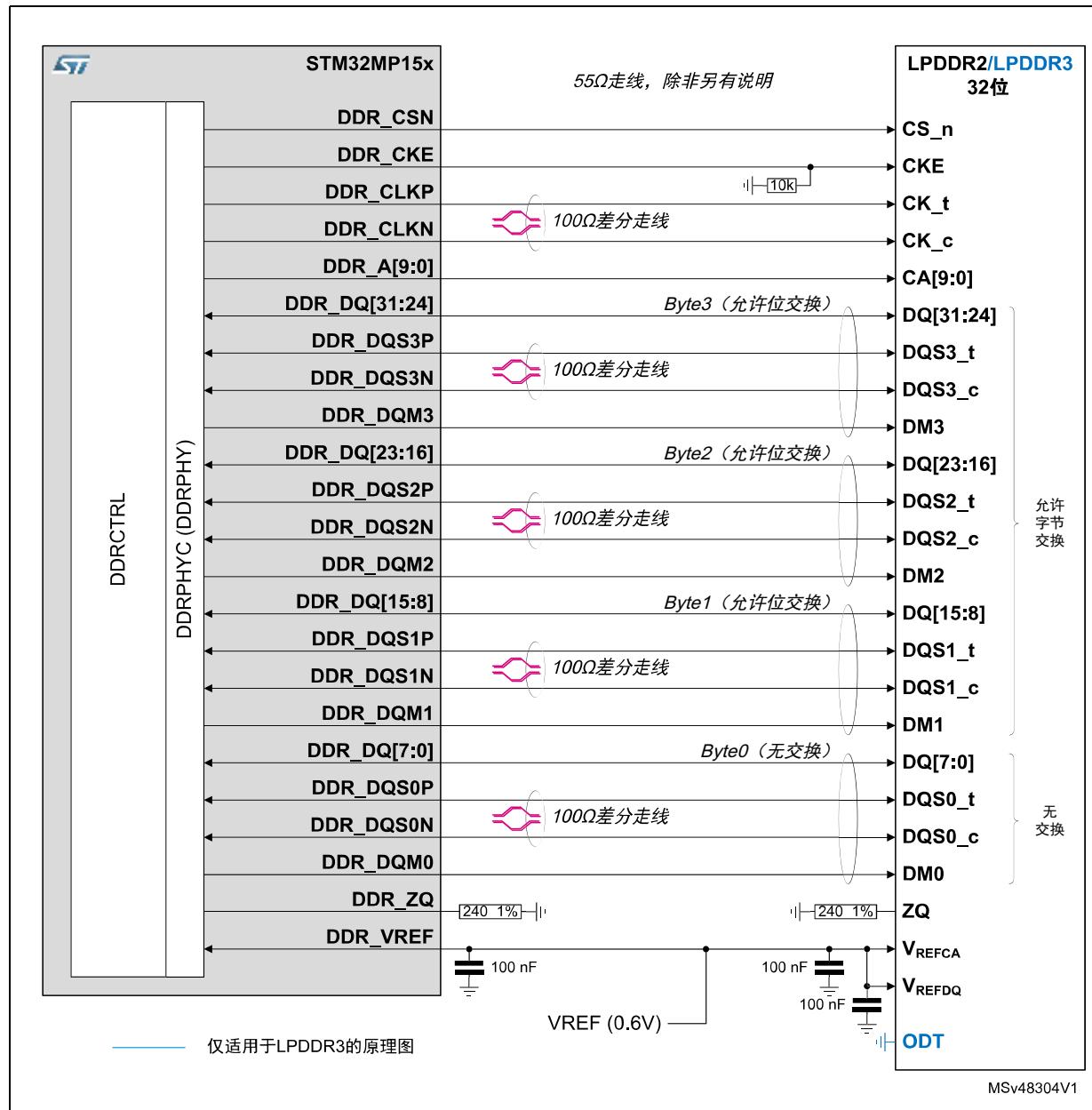

### 10.1.7 LpDDR2/LpDDR3 SDRAM

应在DDR\_ZQ与V<sub>SS</sub>之间连接一个240 Ohm 1%的电阻。该电阻不得与LPDDR2/LPDDR3组件所需的一个或多个ZQ电阻共用。

图34. LPDDR2/LPDDR3 32位连接示例

- 未显示电源和去耦电容。

在STM32MP1系列DDR存储器路由指南应用说明 (AN5122) 中对详细布线示例进行了说明。

### 10.1.8 SD卡

#### 外部电平转换器

通过它可使用更快的UHS-I模式（高达SDR50和DDR50，即50 MB/s的总线速度），这需要切换到1.8 V的卡I/O电压（SD卡通过3 V的卡I/O启动）。

注：由于启动始终在“标准”模式（3 V IO）下进行，如果UHS-I中的应用使用了此卡，则在复位或待机后需要重启卡电源。

该示例与可能介于1.71 V和3.6 V之间的MPU IO电压 $V_{DD}$ 无关。如果 $V_{DD}$ 为1.8 V（典型值），则必须使用外部电平转换器，因为“标准”模式下的所有SD卡启动事务均使用3 V信号电压。

请注意，良好的信号完整性取决于电路板、GPIO强度设置（GPIO\_OSPEEDR寄存器）和 $V_{DD}$ 电压。

使用 $V_{DD} = 1.8$  V时，可能需要对OTP位和寄存器SYSCFG\_IOWTRSETR（HSLVEN\_SDMMC位）进行置位，以确保在用于SDMMC输出的引脚上获得最佳速度。

---

**警告：**当 $V_{DD}$ 高于2.7 V时，不得置位UHSIEN和HSLVEN，否则可能造成IC永久损坏。

---

如果需要，阻抗匹配电阻应尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据IO驱动强度和PCB阻抗进行调整。

图35. 带外部电平转换器的SD卡连接示例

- 在启动阶段未使用SDMMC1\_D0DIR，因为该阶段只从SD卡DAT0请求读取数据。然而，需要SDMMC1\_D0DIR下拉电阻，以确保从卡到MPU的正确DATA0\_SD方向。

- 如果用于USH-I，则 $V_{DD\_SD}$ 必须切断1ms以上，以便能够重启（复位或待机退出时）。如果 $V_{DD} > V_{DD\_SD}$ ，则使用 $V_{DD}$ 。

- 如果用于USH-I，则 $V_{DD\_SD}$ 必须切断1ms以上，以便能够重启（复位或待机退出时）。

- 未显示去耦电容。

在 $V_{DD\_SD}$ 关闭前（如待机前），必须通过SDMMC1驱动器将进入卡的所有信号设为0或高阻态。

### 直接3.3 V IO电压

这是需要 $V_{DD} > 2.9\text{ V}$ 的更简单接口，仅限于标准SD卡速度（高达25 MB/s的高速总线速度）。由于高密度SD卡需要高电流，为在待机期间限制功率， $V_{DD\_SD}$ 可以与 $V_{DD}$ 隔离，但它们之间的电平应在200 mV以内，除非通过切断 $V_{DD\_SD}$ 来节能时。

图36. 带3.3 V I/O的SD卡连接示例

### 10.1.9 eMMC™ Flash

请注意，良好的信号完整性取决于电路板、GPIO强度设置（GPIO\_OSPEEDR寄存器）和 $V_{DD}$ 电压。

使用 $V_{DD} = 1.8\text{ V}$ 时，可能需要对OTP位和寄存器SYSCFG\_ICTRLSETR（HSLVEN\_SDMMC位）进行置位，以确保在用于SDMMC输出的焊盘上获得最佳速度。

**警告：**当 $V_{DD}$ 高于2.7 V时，不得置位UHSLVEN和HSLVEN，否则可能造成IC永久损坏。

如果需要，阻抗匹配电阻应尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据IO驱动强度和PCB阻抗进行调整。

图37. eMMC™连接示例

1. 未显示去耦电容。

默认情况下，在eMMC中禁用RSTn，如果eMMC电源未重启，则必须在eMMC寄存器中启用RSTn，以便在复位后能够重启。

如果存储器IO电源可独立于V<sub>DD</sub>关闭，则NRST不能直接连接到存储器复位引脚，可使用以下选项：

- 如果存储器支持内部上电复位，则存储器复位引脚可保持开路。

- 通过肖特基二极管与NRST侧的阴极连接

否则，当其IO电源不存在时，NRST可能会被存储器内部保护功能下拉为低电平（这可能导致不必要的平台复位）。

请参考存储器文档以验证存储器复位引脚要求（尤其是在复位引脚上存在内部上电复位和/或内部上拉时）

### 10.1.10 SLC NAND-Flash

支持单个8位或16位SLC NAND存储器设备（CE# = FMC\_NCE）以及两个独立的8位SLC NAND存储器设备（device1 CE# = FMC\_NCE和device2 CE# = FMC\_NCE2）。

请注意，仅在连接到FMC\_NCE的SLC NAND存储器设备上执行启动。

图38. SLC NAND-Flash连接示例

1. V<sub>DD\_NAND</sub>必须切断1ms以上才能重启（复位或待机退出时）。

2. 未显示去耦电容。

注：仅支持单层单元(SLC) NAND-Flash，并采用汉明、BCH4或BCH8纠错算法。

### 10.1.11 串行NOR-Flash/NAND-Flash

**注:** 由于启动始终在“SPI”模式下完成，如果应用程序在多条数据线路中设置串行Flash或者扇区寻址已更改，则在复位或退出待机后需要重启串行Flash电源。

请注意，良好的信号完整性取决于电路板、GPIO强度设置（GPIO\_OSPEEDR寄存器）和V<sub>DD</sub>电压。

使用V<sub>DD</sub> = 1.8 V时，可能需要对OTP位和寄存器SYSCFG\_ICTRLSETR（HSLVEN\_QUADSPI位）进行置位，以确保在用于SDMMC输出的焊盘上获得最佳速度。

**警告：**当V<sub>DD</sub>高于2.7 V时，不得置位UHSLVEN和HSLVEN，否则可能造成IC永久损坏。

如果需要，阻抗匹配电阻应尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据IO驱动强度和PCB阻抗进行调整。

图39. 串行Flash连接示例

1. V<sub>DD\_FLASH</sub>必须切断1ms以上才能重启（复位或待机退出时）。

2. 未显示去耦电容。

图40. 双串行Flash连接示例

1.  $V_{DD\_FLASH}$ 必须切断1ms以上才能重启（复位或待机退出时）。

2. 未显示去耦电容。

如果存储器IO电源可独立于 $V_{DD}$ 关闭，则NRST不能直接连接到存储器复位引脚，可使用以下选项：

- 如果存储器支持内部上电复位，则存储器复位引脚可保持开路。

- 通过肖特基二极管，阴极侧连接NRST

否则，当其IO电源不存在时，NRST可能会被存储器内部保护功能下拉为低电平（这可能导致不必要的平台复位）。

请参考存储器文档以验证存储器复位引脚要求（尤其是在复位引脚上存在内部上电复位和/或内部上拉时）

### 10.1.12 USB:

注：某些外部组件支持USB Type-C，有关专用应用说明，请参见[www.st.com](http://www.st.com)。

应在USB\_RREF与VSS\_USBHS之间连接一个3 kOhm 1%的电阻（或如果所选封装中没有VSS\_USBHS，则用VSS替代）。

图41. USB 2端口主机高速 + OTG全速连接示例

注：在OTG IP上，通过使用Micro-B插座来替代Micro-AB，并让OTG\_ID引脚保持未连接，也可以支持USB全速设备。

图42. USB主机高速 + OTG高速连接示例

注：在OTG IP上，通过使用Micro-B插座来替代Micro-AB，并让OTG\_ID引脚保持未连接，也可以支持USB高速设备。

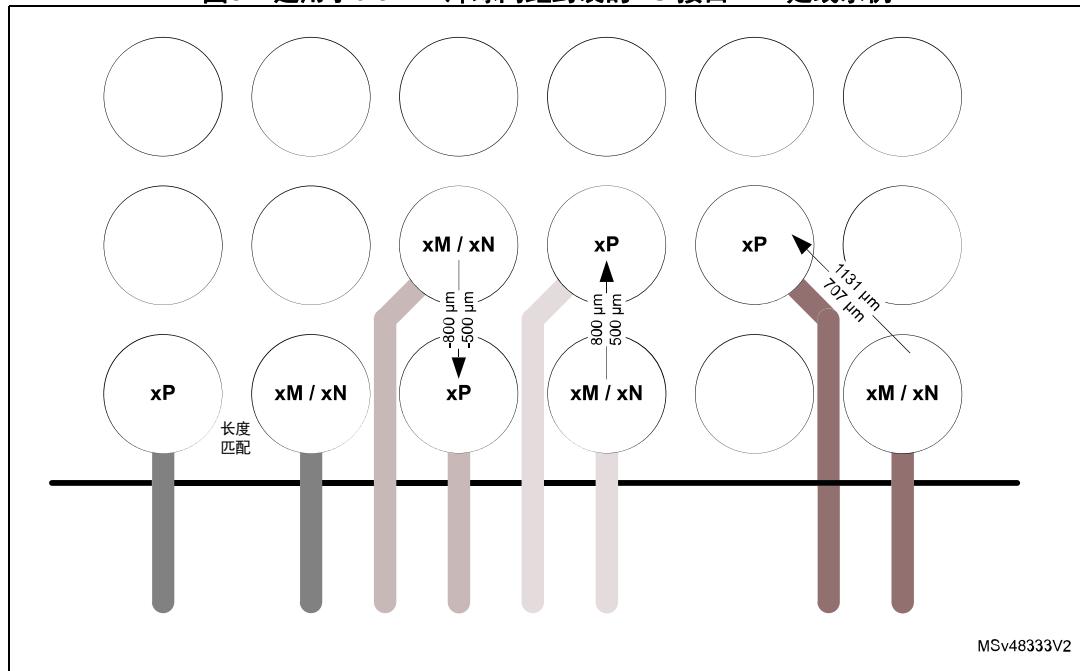

### USB高速PCB走线长度匹配

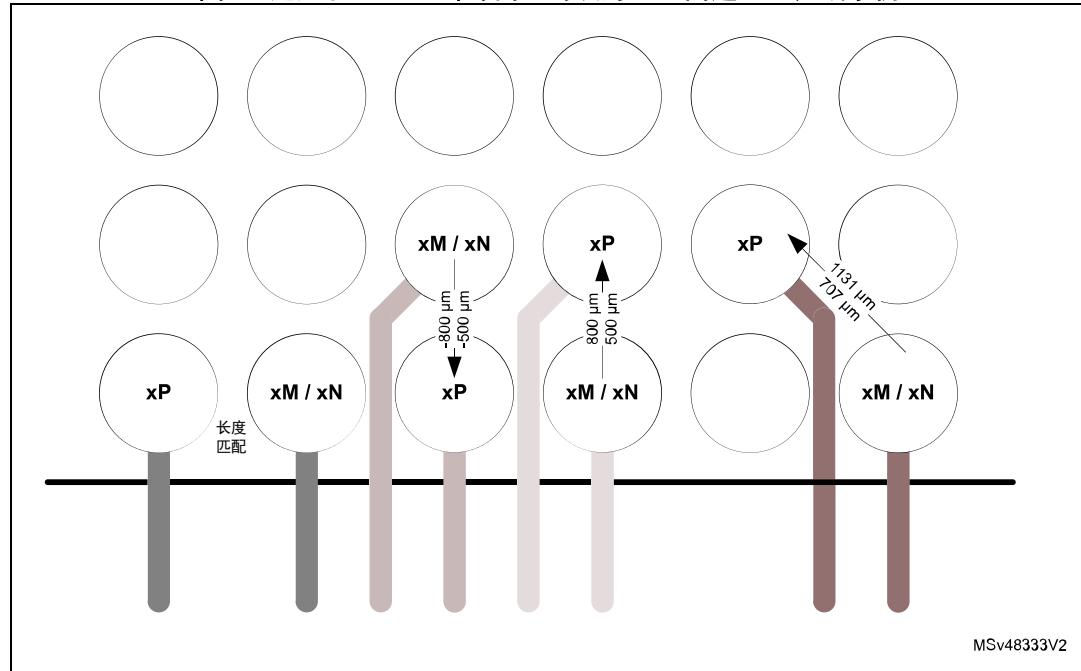

每个封装都经过优化，以便在差分对信号焊球不直接位于相邻焊球上时实现更简单的长度匹配。示例：在焊球间距为0.8 mm的封装上，当差分对位于不同的行上时，封装已具有约800 μm长的内部差异，以便根据USB标准要求，在最大限度降低或甚至没有额外布线复杂性的前提下使PCB走线与总长度匹配。下表显示了PCB工具要考虑的焊球级DM - DP长度差异（内部封装）。

表17. USB封装长度匹配值

| 引脚名称    | TFBGA257           |        | LFBGA354           |         | TFBGA361           |         | LFBGA448        |         |

|---------|--------------------|--------|--------------------|---------|--------------------|---------|-----------------|---------|

|         | (10 x 10脚间距0.5 mm) |        | (16 x 16脚间距0.8 mm) |         | (12 x 12脚间距0.5 mm) |         | (18x18脚间距0.8mm) |         |

|         | 焊球位置               | 长度差异   | 焊球位置               | 长度差异    | 焊球位置               | 长度差异    | 焊球位置            | 长度差异    |

| USB_DM1 | W14                | 486 μm | W14                | 818 μm  | AB17               | -507 μm | AB15            | 792 μm  |

| USB_DP1 | V14                |        | V14                |         | AC17               |         | AA15            |         |

| USB_DM2 | W10                | 494 μm | V13                | -816 μm | AB16               | -500 μm | AA14            | -850 μm |

| USB_DP2 | V10                |        | W13                |         | AC16               |         | AB14            |         |

图43. 适用于0.8 mm焊球间距封装的USB高速PCB走线示例

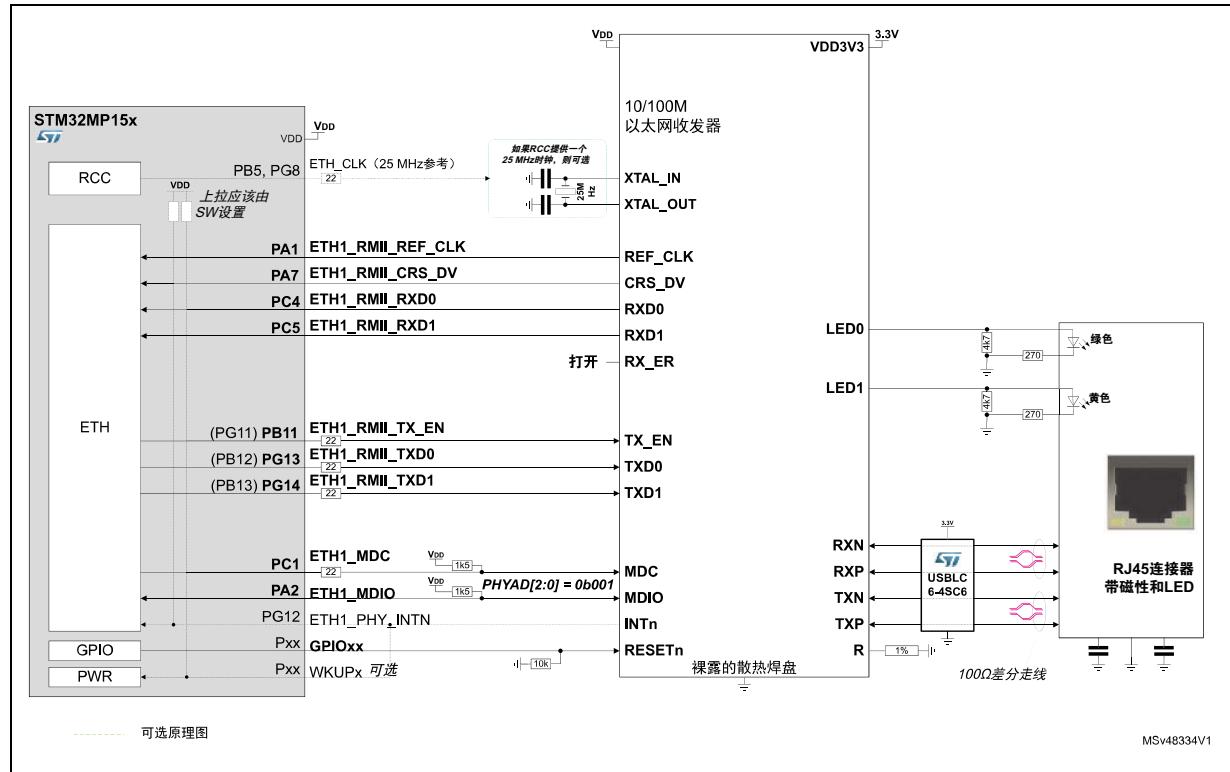

### 10.1.13 以太网

#### 10/100M以太网

请注意，良好的信号完整性取决于电路板、GPIO强度设置（GPIO\_OSPEEDR寄存器）和V<sub>DD</sub>电压。

如果需要，阻抗匹配电阻应尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据每侧IO驱动强度和PCB阻抗进行调整。

图44. 10/100M以太网PHY连接示例

- 未显示去耦电容。

或者，如果PHY允许并且RCC可提供精确的50 MHz时钟（可能必须根据HSE石英频率和RCC其他外设/内核时钟频率设置进行检查），可由STM32MP15x系列产品向PHY提供50 MHz的ETH\_CLK，且REF\_CLK在两侧均未连接。这可以在某些PHY上节省BOM、面积以及一些功率。

图45. 具有来自RCC的REFCLK的10/100M以太网PHY连接示例

1. 未显示去耦电容。

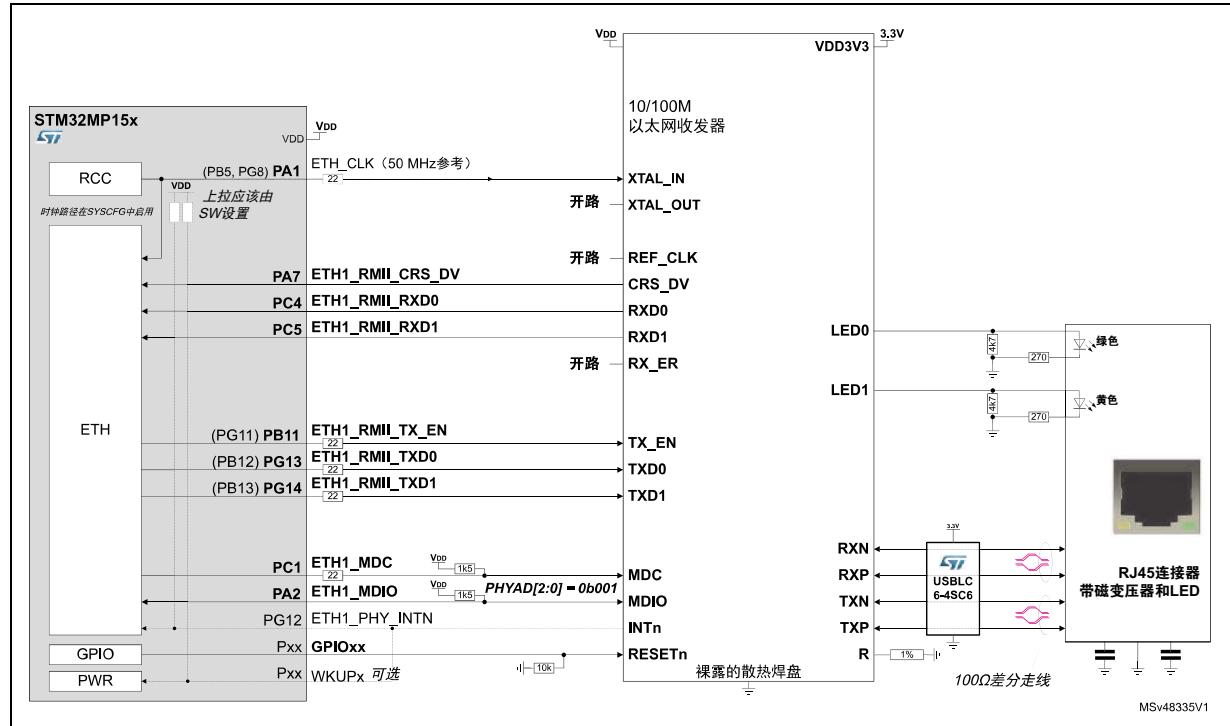

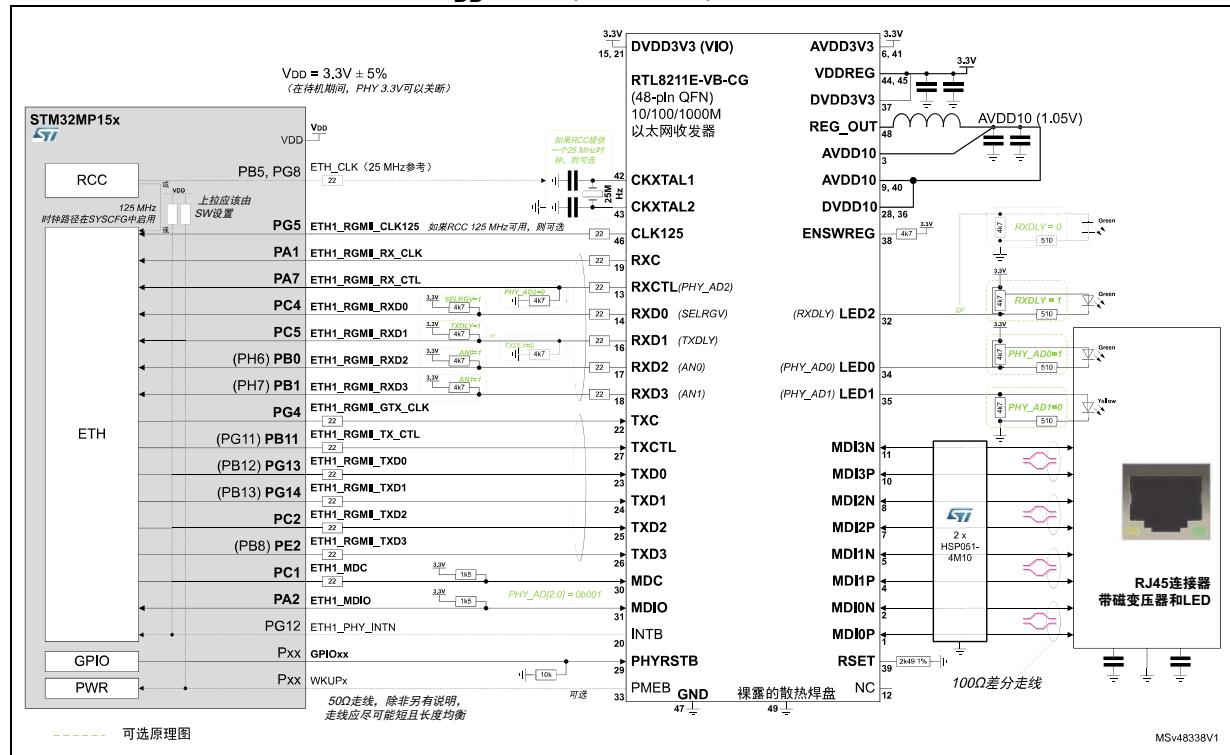

## 千兆以太网

请注意，良好的信号完整性取决于电路板、GPIO强度设置（GPIO\_OSPEEDR寄存器）和V<sub>DD</sub>电压。

使用V<sub>DD</sub> = 1.8 V时，需要对OTP位和寄存器SYSCFG\_ICTRLSETR（HSLVEN\_ETH位）进行置位，以确保在用于以太网输出的焊盘上获得最佳速度。

**警告：**当V<sub>DD</sub>高于2.7 V时，不得置位UHSLVEN，否则可能造成IC永久损坏。

如果需要，阻抗匹配电阻应尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据每侧IO驱动强度和PCB阻抗进行调整。

图46. V<sub>DD</sub>=3.3 V (RTL8211E)的千兆以太网PHY连接示例

- 未显示去耦电容。

图47.  $V_{DD}=3.3\text{ V}$  (RTL8211F)的千兆以太网PHY连接示例

1. 未显示去耦电容。

图48.  $V_{DD}=1.8\text{ V}$  (RTL8211F)的千兆以太网PHY连接示例

1. 未显示去耦电容。

图49.  $V_{DD} = 3.3V$  (RTL8363NB-VG)的千兆以太网2端口交换机示例

1. 未显示去耦电容。

### 10.1.14 显示串行接口（DSI）

图50. 采用DSI的显示连接示例

1. ECMF04-4HSWM10包括用于WLAN/BT频段的共模滤波器。仅对于ESD保护，可将HSP051-4M10作为替代品（类似但尺寸不同）。

2. 未显示去耦电容。

3. DSI的可用性取决于STM32MP15x 器件的系列。

### DSI接口PCB走线长度匹配

每个封装都经过优化，以便在差分对信号焊球不直接位于相邻焊球上时实现更简单的长度匹配。示例：在焊球间距为0.8 mm的封装上，当差分对位于不同的行上时，封装已具有约800 μm长的内部差异，以便在最大限度降低或甚至没有额外布线复杂性的前提下使PCB走线与总长度匹配。[表 18](#)显示了PCB工具要考虑的焊球级DM - DP长度差异（内部封装）。

**表18. DSI封装长度匹配值**

| 引脚名称    | TFBGA257           |         | LFBGA354           |        | TFBGA361           |        | LFBGA448        |        |

|---------|--------------------|---------|--------------------|--------|--------------------|--------|-----------------|--------|

|         | (10 x 10脚间距0.5 mm) |         | (16 x 16脚间距0.8 mm) |        | (12 x 12脚间距0.5 mm) |        | (18x18脚间距0.8mm) |        |

|         | 焊球位置               | 长度差异    | 焊球位置               | 长度差异   | 焊球位置               | 长度差异   | 焊球位置            | 长度差异   |

| DSI_CKN | B12                | -505 μm | A14                | 822 μm | A16                | 490 μm | A16             | 867 μm |

| DSI_CKP | A12                |         | B14                |        | B16                |        | B16             |        |

| DSI_D0N | C12                | -736 μm | A13                | 781 μm | b15                | 514 μm | A15             | 791 μm |

| DSI_D0P | B11                |         | B13                |        | C15                |        | b15             |        |

| DSI_D1N | B13                | -507 μm | A15                | 804 μm | A17                | 505 μm | A17             | 785 μm |

| DSI_D1P | A13                |         | b15                |        | B17                |        | B17             |        |

**图51. 适用于0.8 mm焊球间距封装的DSI接口PCB走线示例**

## 11 版本历史

表19. 文档版本历史

| 日期         | 版本 | 变更                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019年2月1日  | 1  | 初始版本。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2020年4月14日 | 2  | <p>更新了：</p> <ul style="list-style-type: none"> <li>- 封面以STM32MP151、STM32MP153和STM32MP157系列替换STM32MP1系列。</li> <li>- <a href="#">表 1: 参考文档</a>.</li> <li>- <a href="#">第 4.1 节: 引言</a>USB电源</li> <li>- <a href="#">第 4.2 节: 电源方案</a>.</li> <li>- <a href="#">表 4: 封装的推荐去耦量</a>.</li> <li>- <a href="#">图 8: 12x12 TFBGA361兼容性</a>.</li> <li>- <a href="#">图 30: 采用DDR3L的3.3 V I/O分立电源示例</a>.</li> <li>- <a href="#">图 31: 采用DDR3L的3.3 V I/O的PMIC示例</a></li> <li>- <a href="#">图 41: USB 2端口主机高速 + OTG全速连接示例</a>.</li> <li>- <a href="#">图 49: VDD = 3.3 V (RTL8363NB-VG)的千兆以太网2端口交换机示例</a>.</li> </ul> <p>删除了：</p> <ul style="list-style-type: none"> <li>- ‘ST1S31PUR SMPS详细信息’图</li> <li>- ‘1.2 V 2A组件示例’表</li> <li>- ‘1.35 V 1A组件示例’表</li> </ul> |

表20. 中文文档版本历史

| 日期          | 版本 | 变更      |

|-------------|----|---------|

| 2020年12月12日 | 1  | 中文初始版本。 |

**重要通知 - 请仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和 / 或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用，ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息，请参考 [www.st.com/trademarks](http://www.st.com/trademarks)。所有其他产品或服务名称均为其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2020 STMicroelectronics - 保留所有权利