製品概要

概要

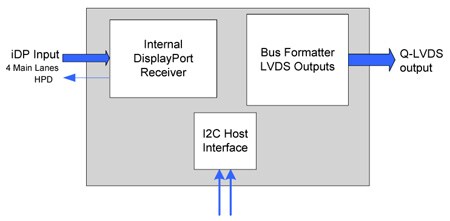

The STiDP880 is an internal DisplayPort to high-speed Dual LVDS/Quad LVDS converter IC targeted for the interconnection between a TV controller SOC and panel TCON. STiDP880 is a VESA iDP compliant device, implementing a single link internal DisplayPort input comprising four Main Link lanes and HPD, which operates without a sideband channel. This device supports the standard iDP link rate of 3.24 Gbps per lane with a total link bandwidth of 12.96 Gbps, allowing interface connectivity for a wide range of panels up to FHD 120 Hz and 10 bits per color. The advanced equalizer built in this device offers robust performance over FFC and UTP type cables.

The STiDP880 supports RGB video color formats with color depth of 10 and 8 bits. This device offers LVDS output interface configurable to map a wide range of pixel data mapping, such as JEIDA, non-JEIDA, and VESA types. The Quad LVDS interface supports video signals up to 400 MHz pixel rate with flexible channel and lane swapping options. In Dual LVDS configuration, STiDP880 can support up to 300 MHz pixel rate.

The STiDP880 is designed to operate in standalone mode (without any programming from an external microcontroller) with default configuration of four lanes DP input and QLVDS output with non-JEIDA mapping. However, the device is configurable from an external microcontroller through I2C host interface for custom configuration.

-

特徴

- Internal DisplayPort (iDP) receiver

- Compliant with iDP specification

- 3.24 Gbps per lane

- 1, 2, or 4 lanes

- HPD pulse assertion as per iDP standard

- Supports video timings up to 1920 x 1080 (FHD) 120 Hz/10-bit color

- Interface compatibility with wide range of panels

- Quad LVDS interface up to 100 MHz per channel (400 MHz pixel rate)

- High speed dual-link LVDS up to 150 MHz per channel (300 MHz pixel rate)

- Supports JEIDA, non-JEIDA, VESA pixel data mappings

- Supports Asynchronous Scrambler Seed Reset (ASSR) for premium contents reception

- Configurable through I2C host interface

- Supports Spread Spectrum for EMI/RFI reduction

- Robust interoperability – supports FFC and UTP type cables

- Low power operation; 20 mW standby

- パッケージ

- 164 LFBGA (12 x 12 mm/0.8 mm pitch)

- HF and RoHS compliant

- Power supply voltages

- 3.3 V I/O; 1.2 V core

- ESD

- 2 KV HBM, 200 V MM, 600V CDM

- Internal DisplayPort (iDP) receiver