Product overview

概要

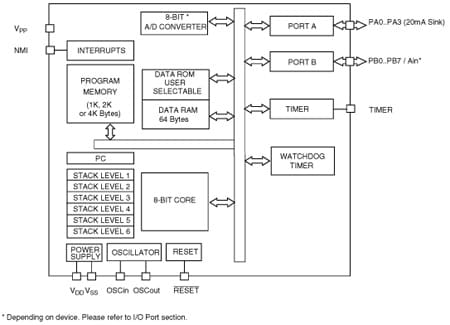

The ST6208C, 09C, 10C and 20C devices are low cost members of the ST62xx 8-bit HCMOS family of microcontrollers, which is targeted at low to medium complexity applications. All ST62xx devices are based on a building block approach: a common core is surrounded by a number of on-chip peripherals.

The ST62E20C is the erasable EPROM version of the ST62T08C, T09C, T10C and T20C devices, which may be used during the development phase for the ST62T08C, T09C, T10C and T20C target devices, as well as the respective ST6208C, 09C, 10C and 20C ROM devices.

OTP and EPROM devices are functionally identical. OTP devices offer all the advantages of user programmability at low cost, which make them the ideal choice in a wide range of applications where frequent code changes, multiple code versions or last minute programmability are required.

The ROM based versions offer the same functionality, selecting the options defined in the programmable option bytes of the OTP/EPROM versions in the ROM option list (See Section 11.6 on page 96).

The ST62P08C/P09C/P10C/P20C are the Factory Advanced Service Technique ROM (FASTROM) versions of ST62T08C, T09C, T10C and T20C OTP devices.

They offer the same functionality as OTP devices, but they do not have to be programmed by the customer (See Section 11 on page 90).

These compact low-cost devices feature a Timer comprising an 8-bit counter with a 7-bit programmable prescaler, an 8-bit A/D Converter with up to 8 analog inputs (depending on device) and a Digital Watchdog timer, making them well suited for a wide range of automotive, appliance and industrial applications.

For easy reference, all parametric data are located in Section 11 on page 90.

-

All features

- Instruction Set\t\t

8-bit data manipulation\t\t 40 basic instructions\t\t 9 addressing modes\t\t Bit manipulation\t\t - Analog Peripheral\t\t

8-bit ADC with 4 or 8 input channels (except on ST6208C)\t\t - Memories\t\t

1K, 2K or 4K bytes Program memory (OTP, EPROM, FASTROM or ROM) with read-out protection\t\t 64 bytes RAM\t\t - Interrupt Management\t\t

4 interrupt vectors plus NMI and RESET\t\t 12 external interrupt lines (on 2 vectors)\t\t - Clock, Reset and Supply Management\t\t

Enhanced reset system\t\t Low Voltage Detector (LVD) for Safe Reset\t\t Clock sources: crystal/ceramic resonator or RC network, external clock, backup oscillator (LFAO)\t\t Oscillator Safeguard (OSG)\t\t 2 Power Saving Modes: Wait and Stop\t\t - 2 Timers\t\t

Configurable watchdog timer\t\t 8-bit timer/counter with a 7-bit prescaler\t\t - Development Tools\t\t

Full hardware/software development package\t\t - 12 I/O Ports\t\t

12 multifunctional bidirectional I/O lines\t\t 8 alternate function lines\t\t 4 high sink outputs (20mA)\t\t

- Instruction Set\t\t

回路ダイアグラム

EDA Symbols, Footprints and 3D Models

すべてのリソース

| Resource title | Version | Latest update | Actions | Details | ダウンロード |

|---|

Schematic Pack (1)

| Resource title | Version | Latest update | Actions | Options | ||

|---|---|---|---|---|---|---|

| 1.0 | 01 Aug 2015 | 01 Aug 2015 |